Thin film transistor array substrate and manufacturing method thereof

A technology for thin film transistors and array substrates, applied in the field of thin film transistor array substrates and their manufacturing, can solve the problems of complex structure, reducing pixel aperture ratio, limiting the arrangement and area of pixel electrodes 21, etc. rate, and the effect of improving product performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0067] Specific embodiments of the present invention will be described in detail below. It should be noted that the embodiments described here are for illustration only, and are not intended to limit the present invention.

[0068] Thin Film Transistor Array Substrate

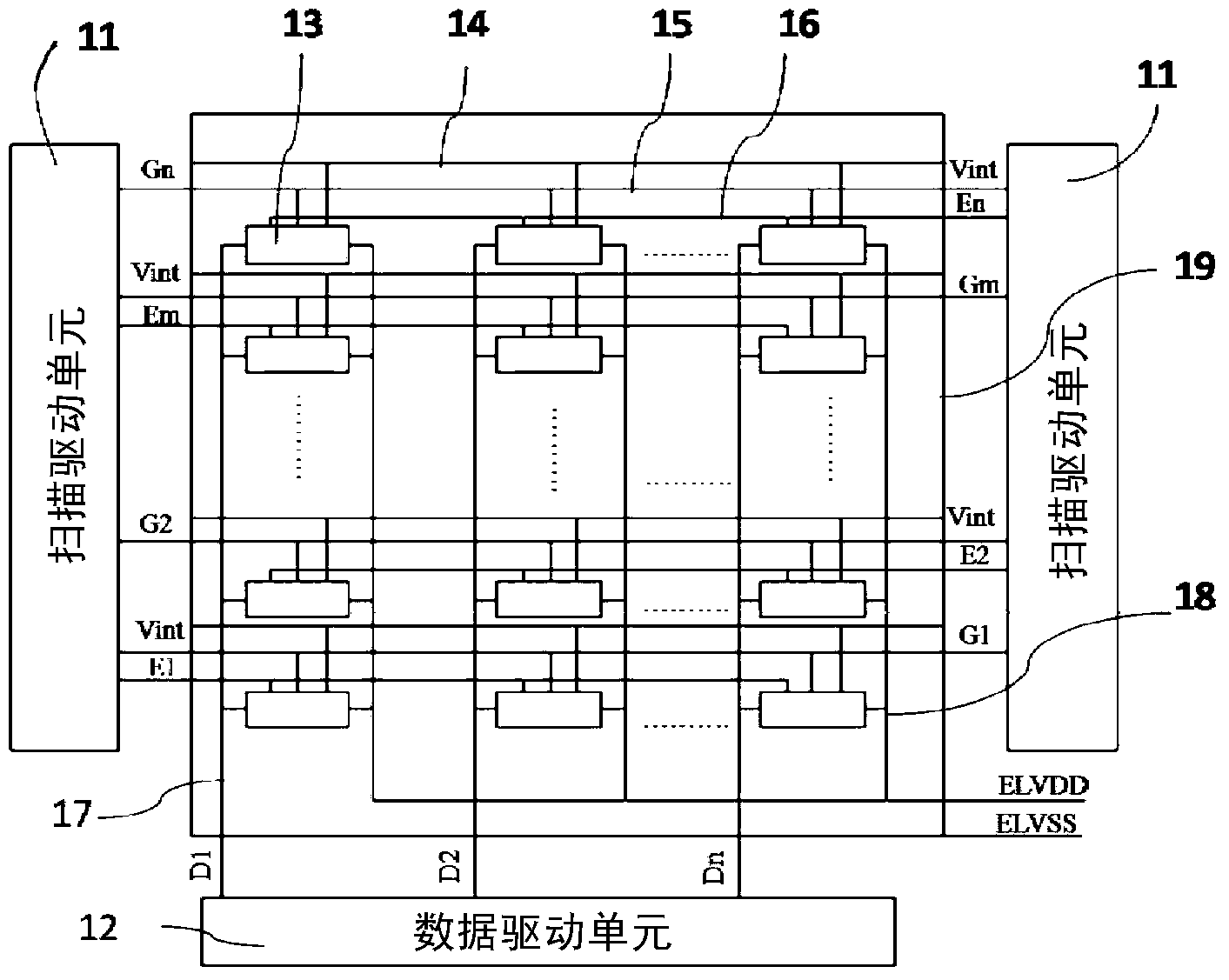

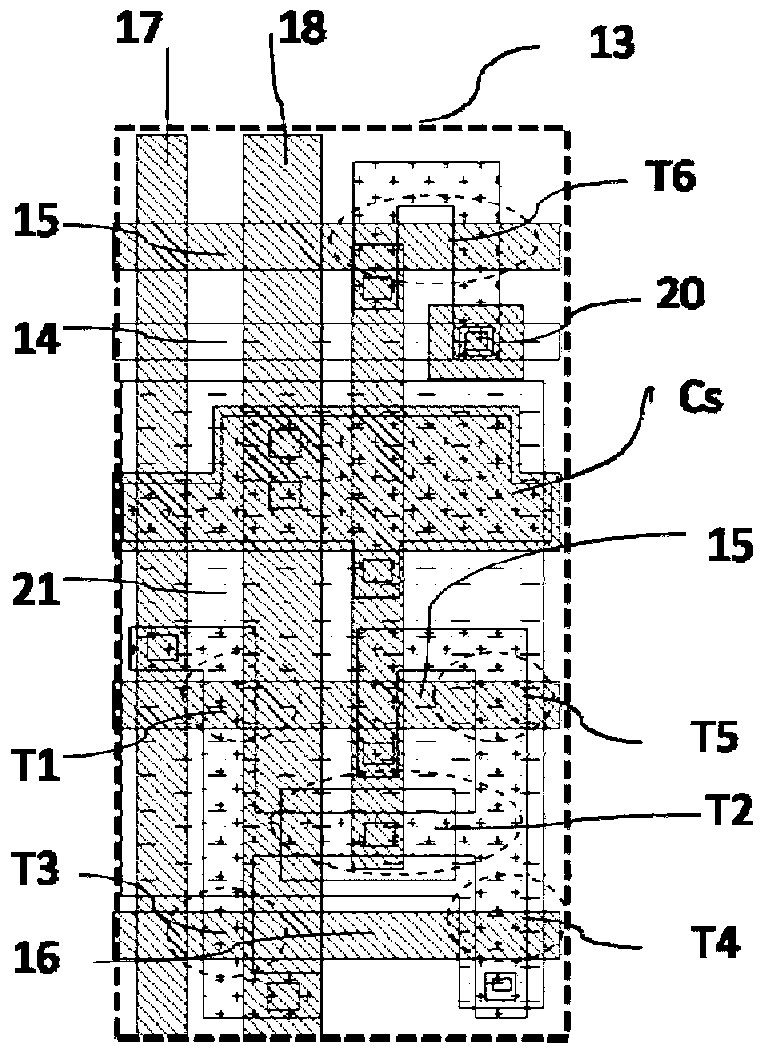

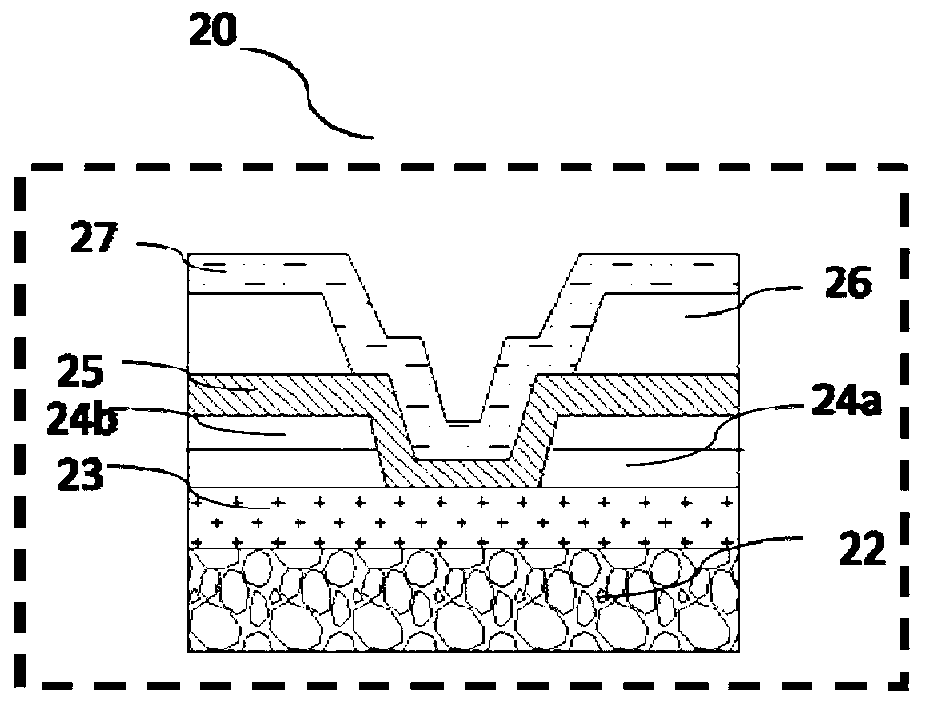

[0069] Such as Figure 4 As shown, the TFT array substrate for driving organic light emitting diodes of the present invention includes a substrate 22, an insulating layer formed on the substrate 22, a power line 18, a data line 17 and an initialization power line 14 formed on the insulating layer, The planarization layer 26 covering the power supply line 18 , the data line 17 and the initialization power supply line 14 , and the pixel electrodes formed on the planarization layer 26 .

[0070] Further, the TFT array substrate of the present invention further includes a scanning line driving unit 11 , a data line driving unit 12 and a plurality of pixels 13 .

[0071] The scanning line driving unit 11 includes...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More