Patents

Literature

547 results about "Surface etching" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Surface Etching is a method of cutting a design, logo or text into smooth surface. Surface Carving is similar to Etching, but cuts much deeper into the material and producing a three dimensional effect.

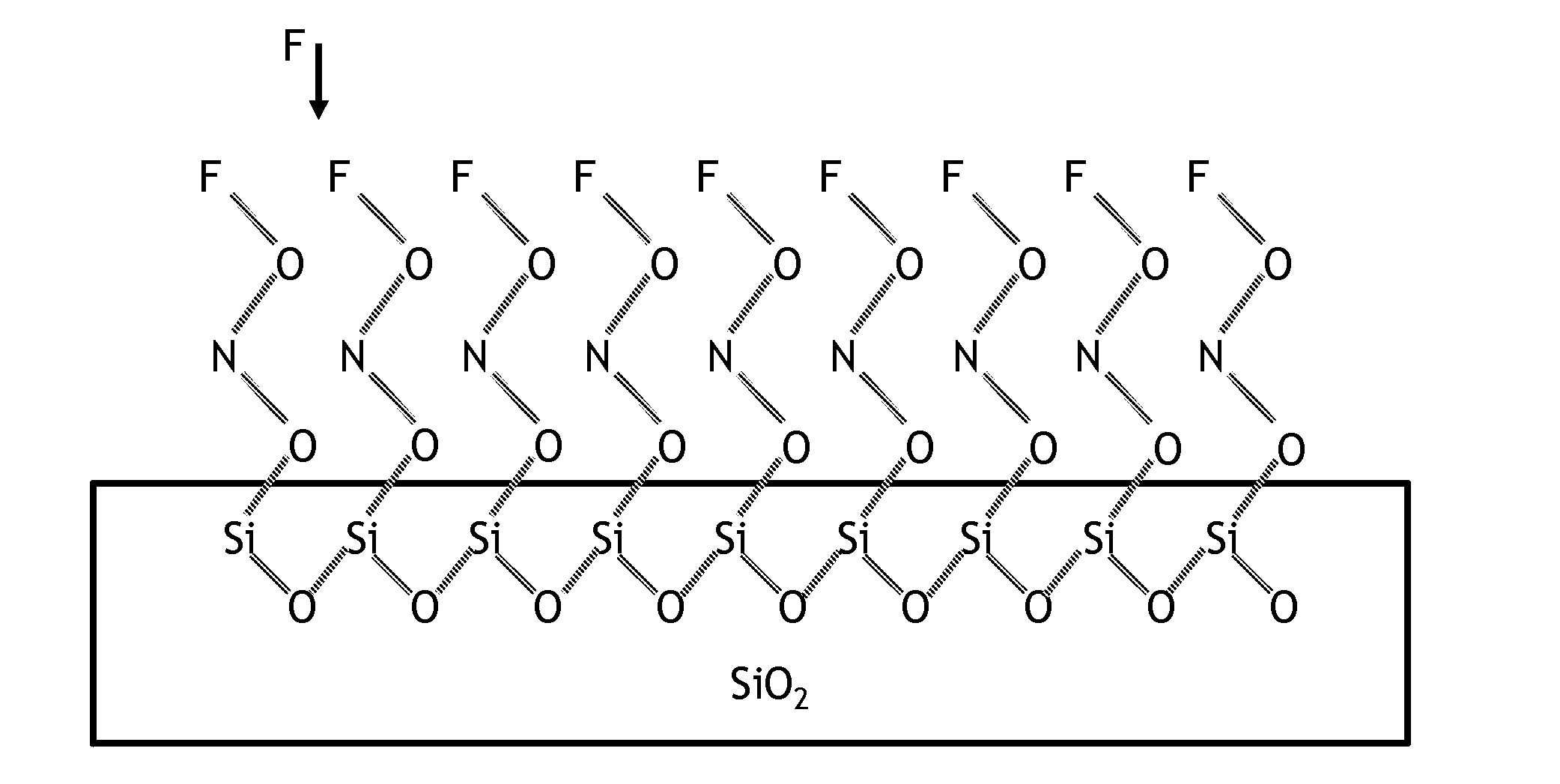

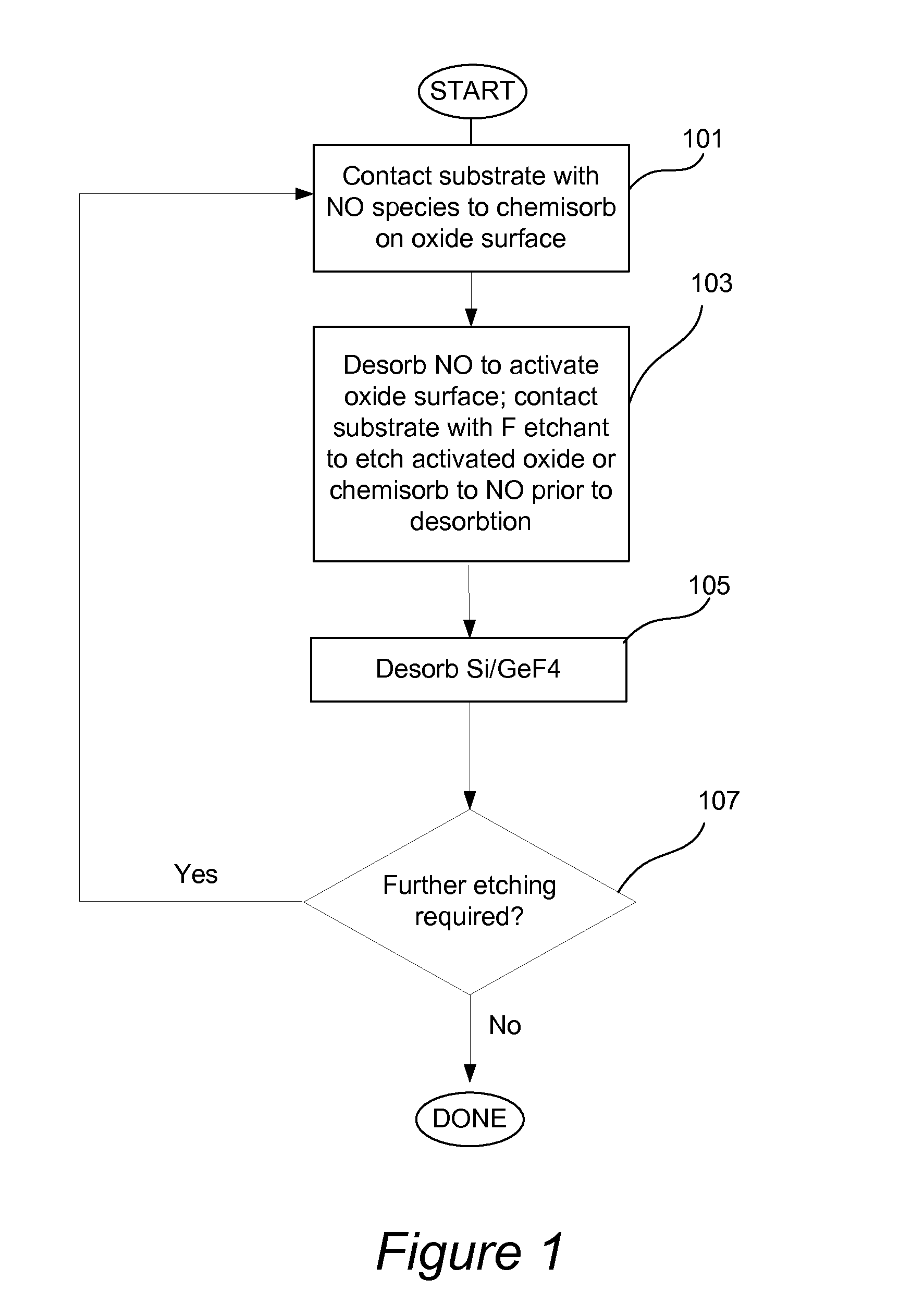

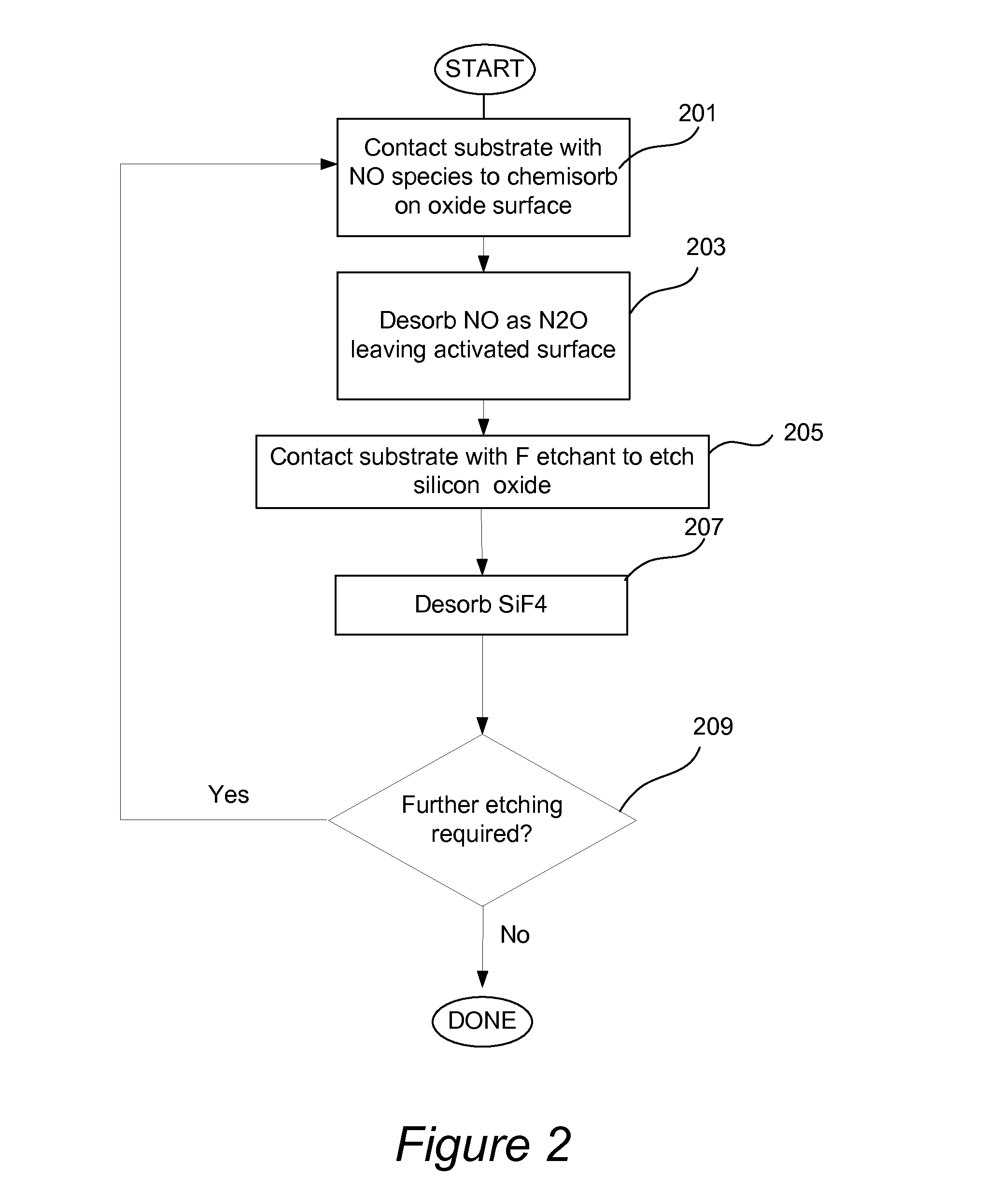

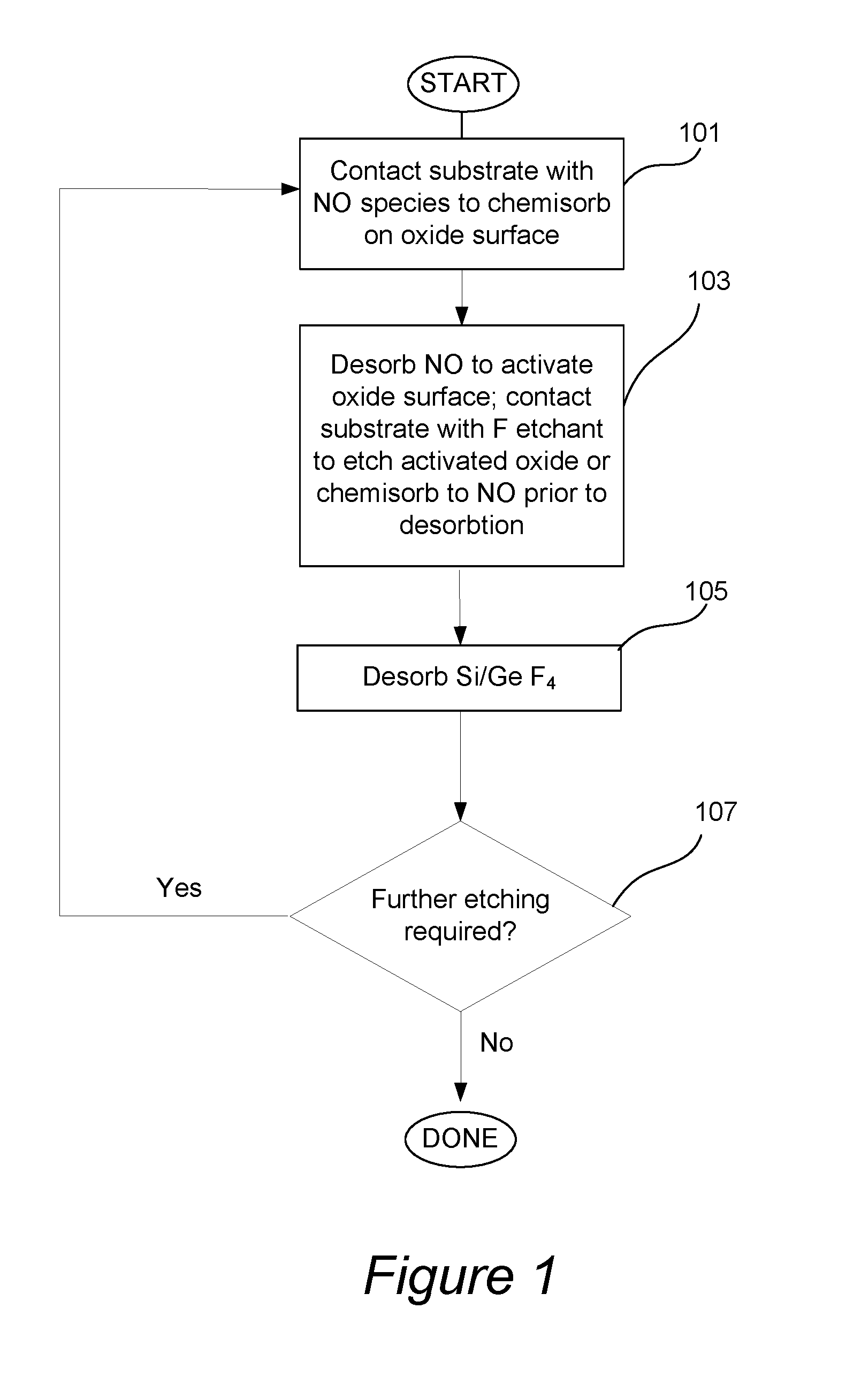

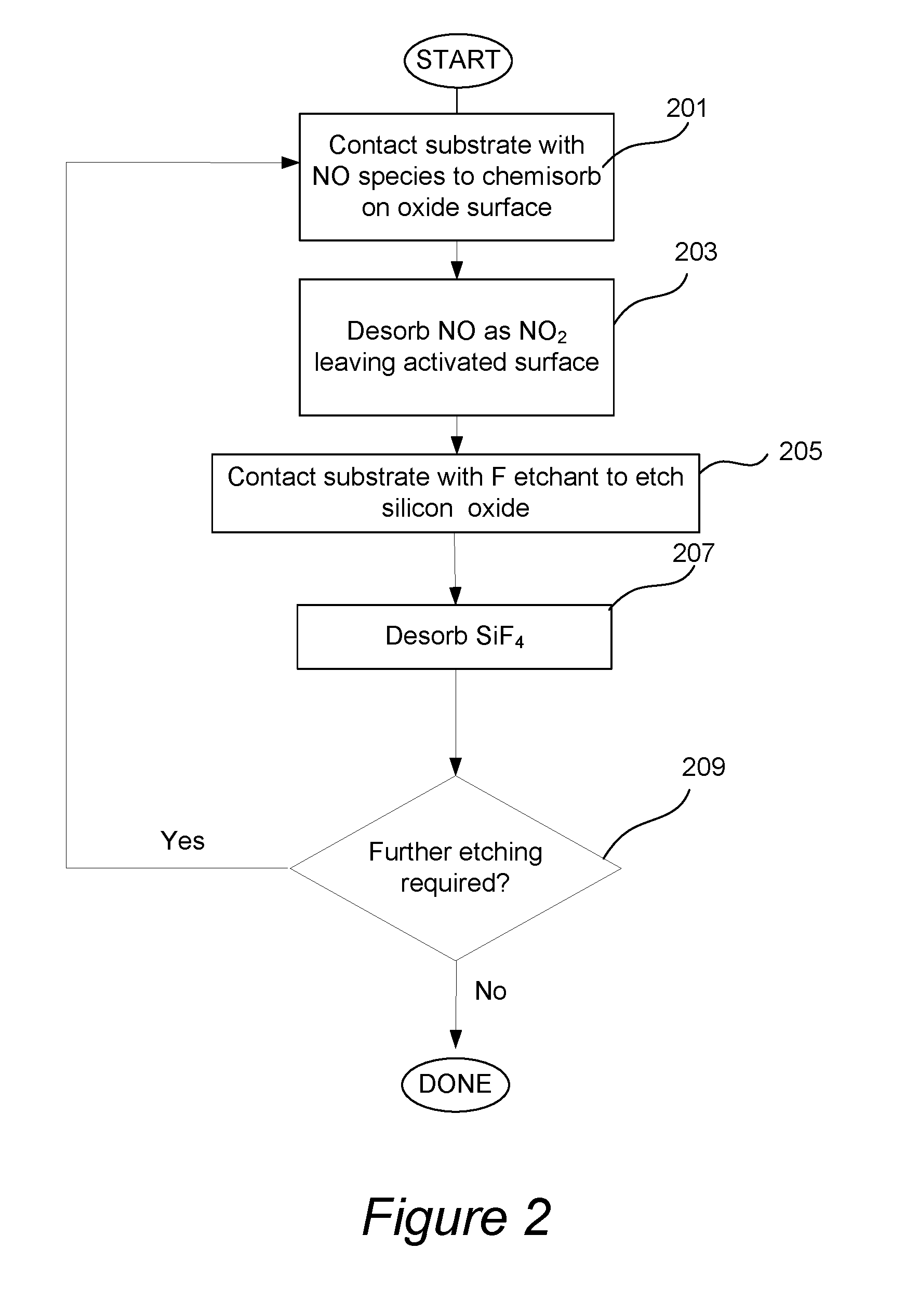

Isotropic atomic layer etch for silicon oxides using no activation

ActiveUS20160196969A1Electric discharge tubesSemiconductor/solid-state device manufacturingGate dielectricSilicon oxide

Methods for controlled isotropic etching of layers of silicon oxide and germanium oxide with atomic scale fidelity are provided. The methods make use of NO activation of an oxide surface. Once activated, a fluorine-containing gas or vapor etches the activated surface. Etching is self-limiting as once the activated surface is removed, etching stops since the fluorine species does not spontaneously react with the un-activated oxide surface. These methods may be used in interconnect pre-clean applications, gate dielectric processing, manufacturing of memory devices, or any other applications where accurate removal of one or multiple atomic layers of material is desired.

Owner:LAM RES CORP

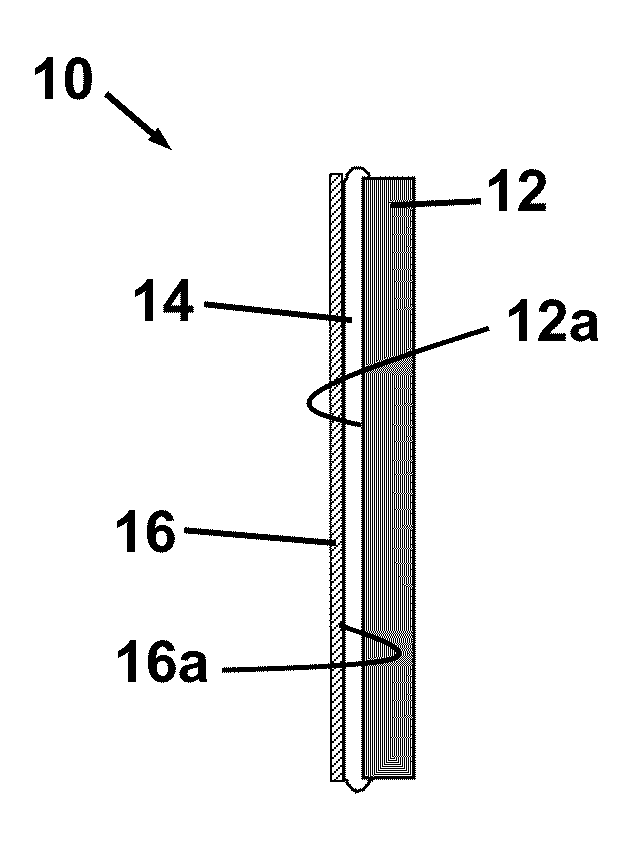

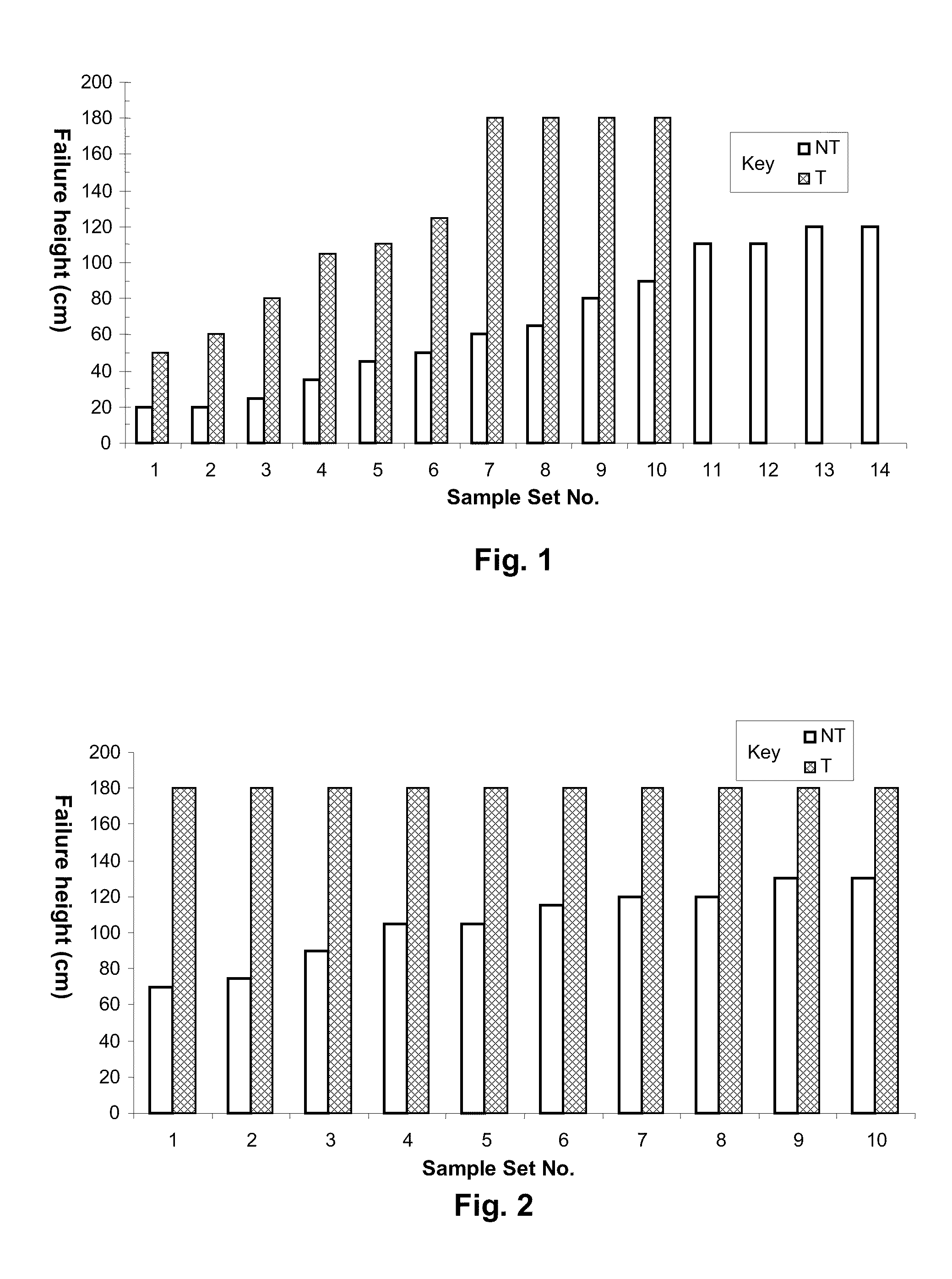

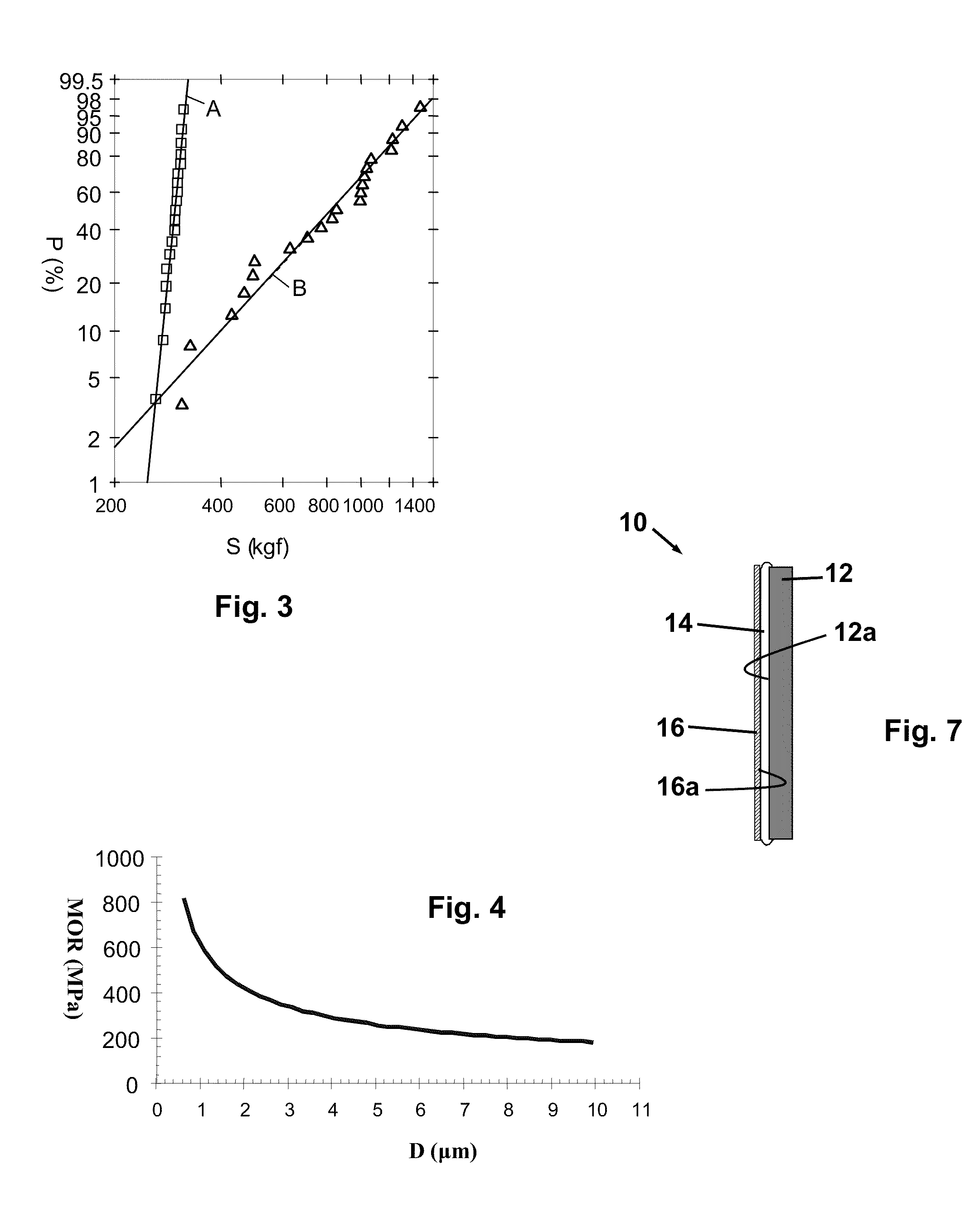

Impact-damage-resistant glass sheet

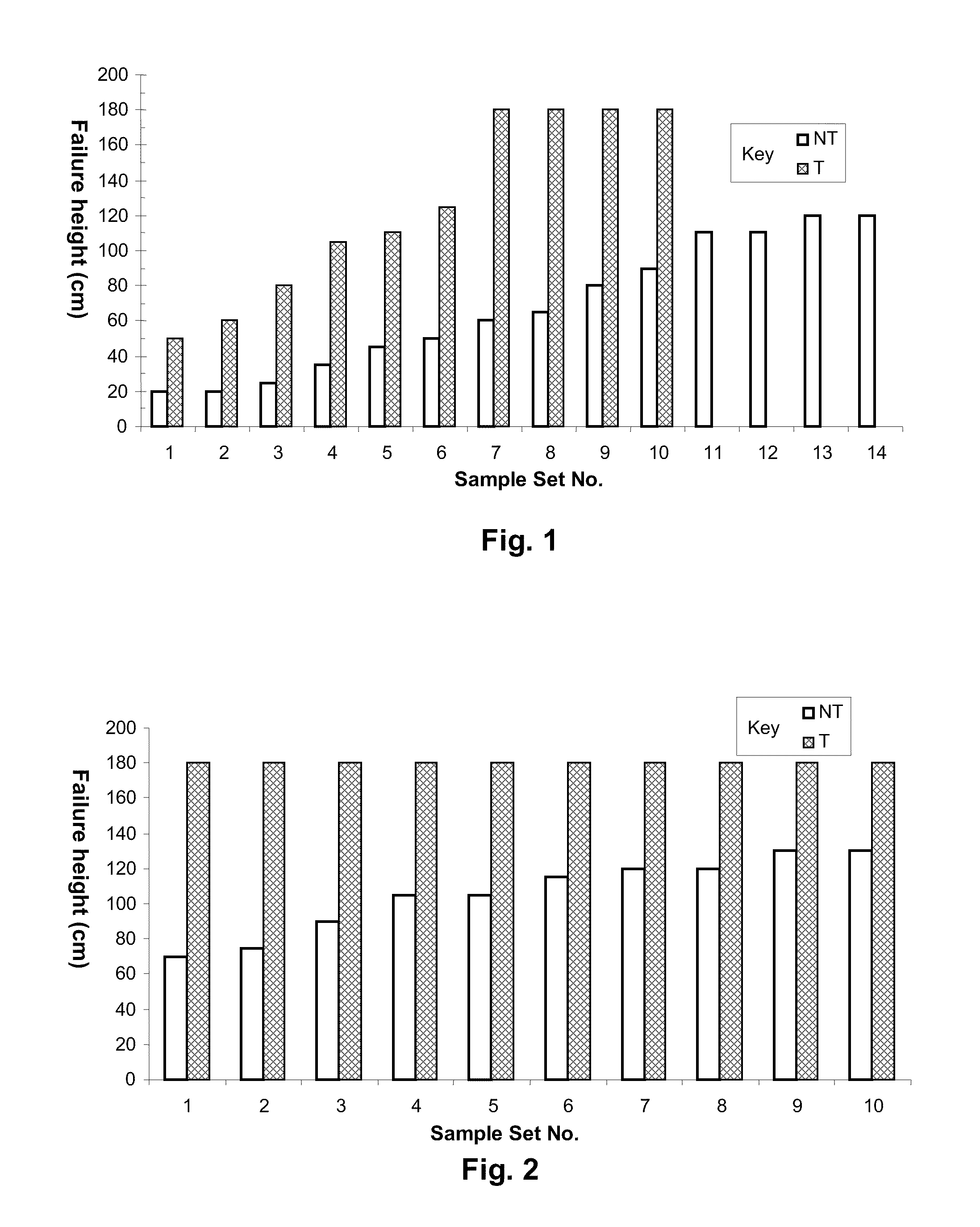

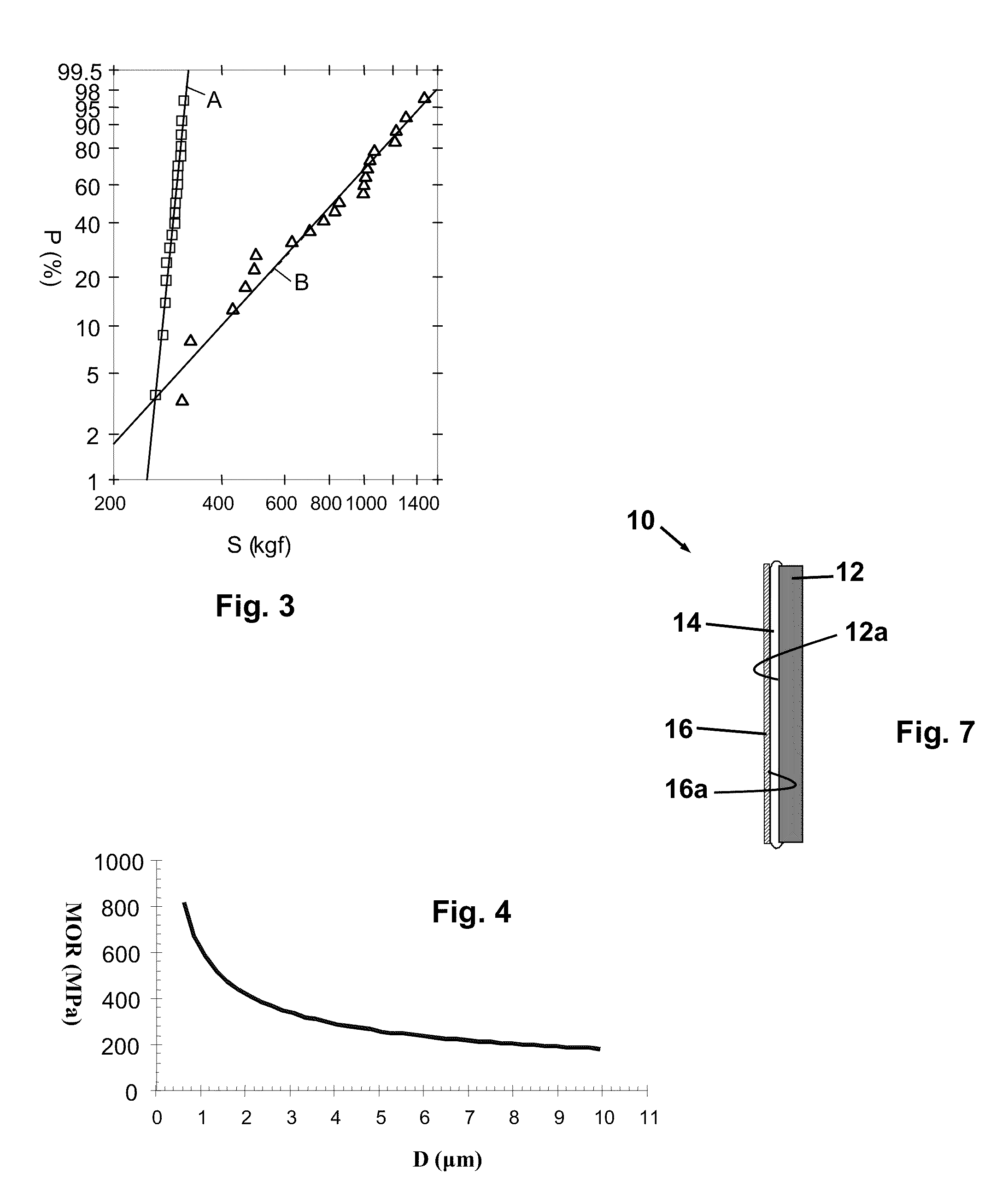

ActiveUS20110165393A1Increased and more consistent resistanceImprove flexural strengthSynthetic resin layered productsRecord information storageGlass coverDisplay device

Impact-damage-resistant glass sheet comprising at least one chemically etched surface in combination with a tempering surface compression layer, the glass sheet exhibiting a high standardized ball drop failure height and a high flexural modulus of rupture strength, useful to provide damage-resistant glass cover sheets for consumer electronic video display devices, is provided by subjecting thin glass sheet to a combination of a surface tempering treatment and a surface etching treatment that improves strength while maintaining the optical glass sheet properties required for video display applications.

Owner:CORNING INC

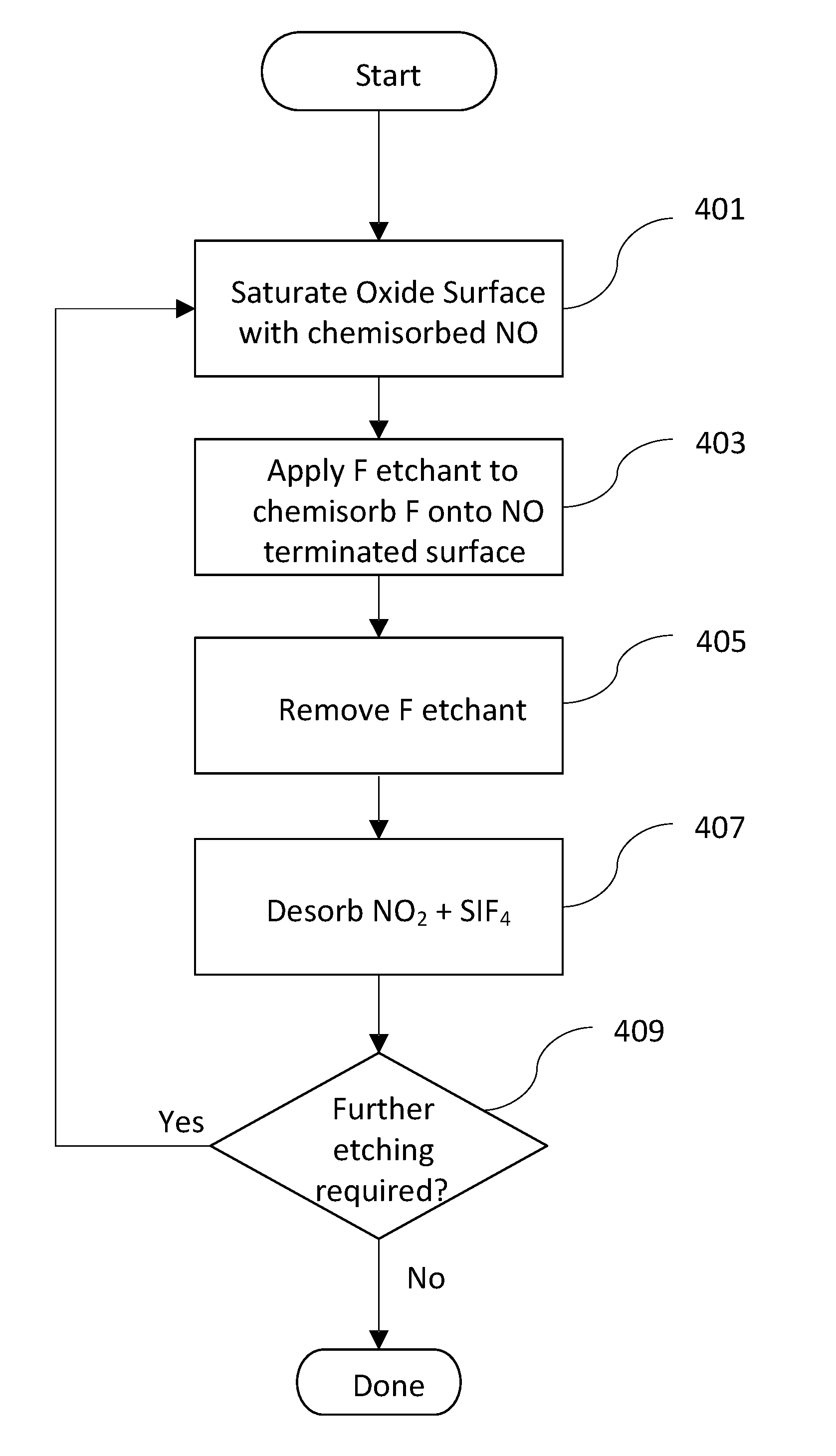

Isotropic atomic layer etch for silicon oxides using no activation

ActiveUS9425041B2High selectivityReduce defective rateElectric discharge tubesSemiconductor/solid-state device manufacturingGate dielectricSilicon oxide

Methods for controlled isotropic etching of layers of silicon oxide and germanium oxide with atomic scale fidelity are provided. The methods make use of NO activation of an oxide surface. Once activated, a fluorine-containing gas or vapor etches the activated surface. Etching is self-limiting as once the activated surface is removed, etching stops since the fluorine species does not spontaneously react with the un-activated oxide surface. These methods may be used in interconnect pre-clean applications, gate dielectric processing, manufacturing of memory devices, or any other applications where accurate removal of one or multiple atomic layers of material is desired.

Owner:LAM RES CORP

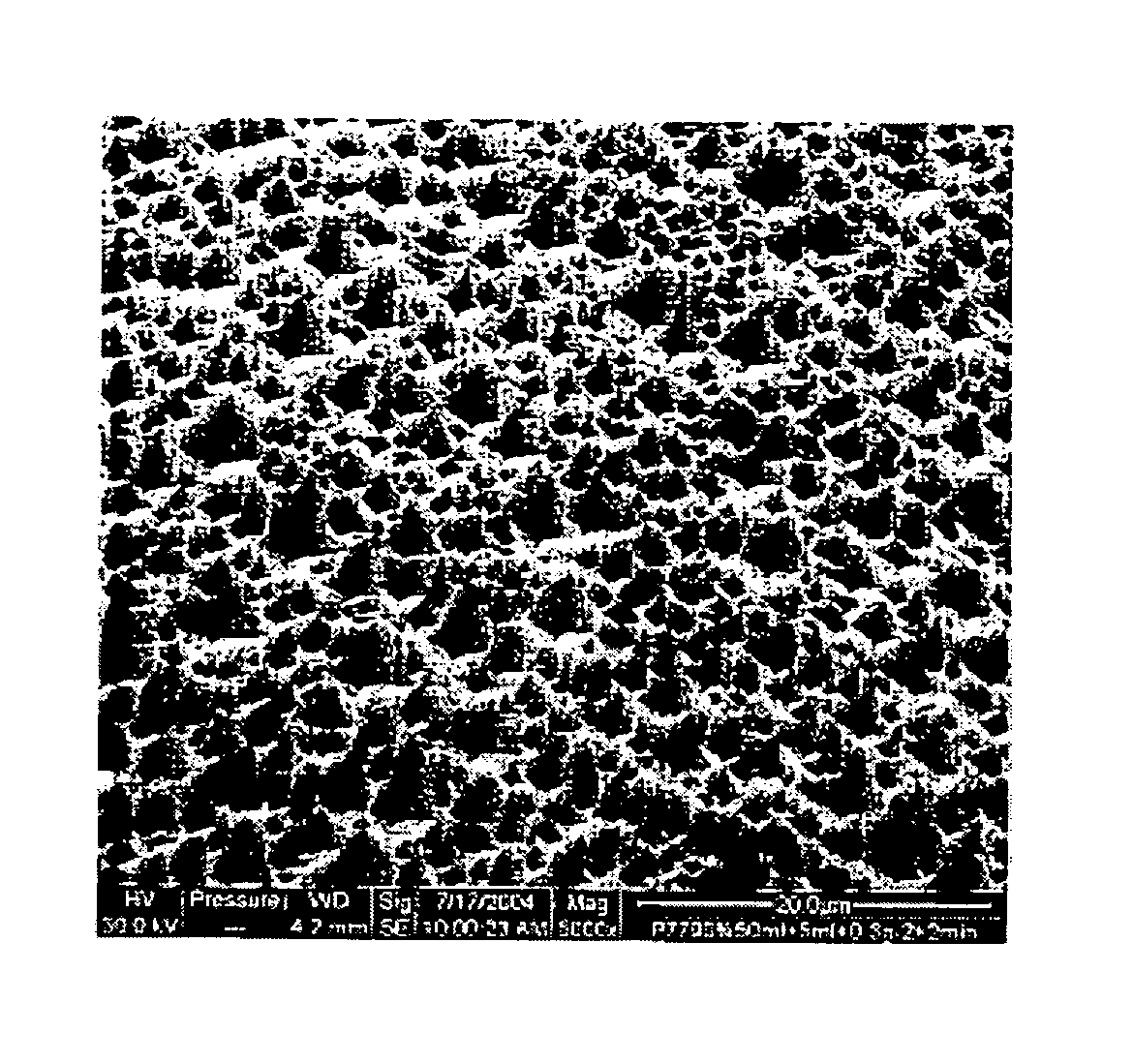

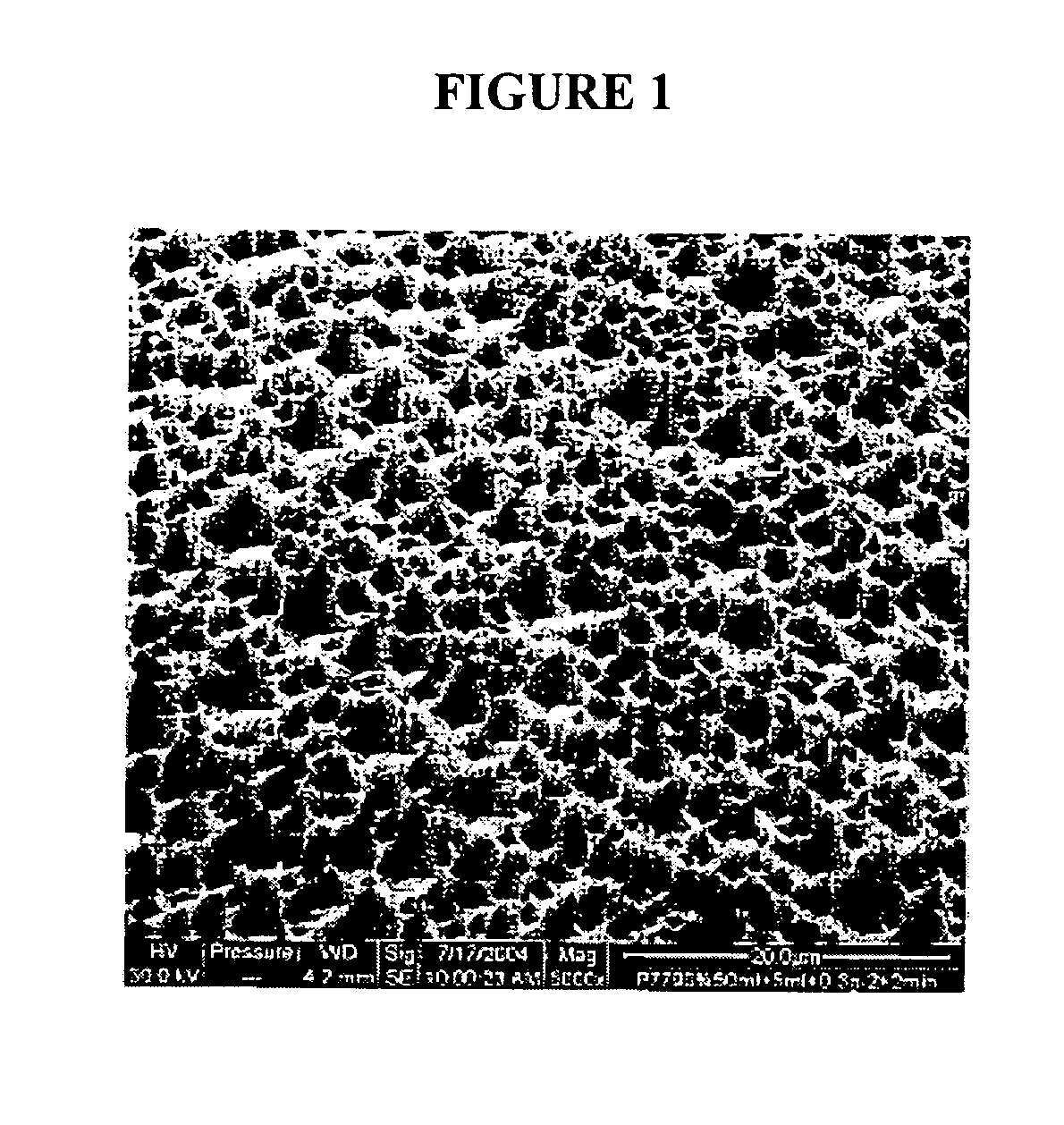

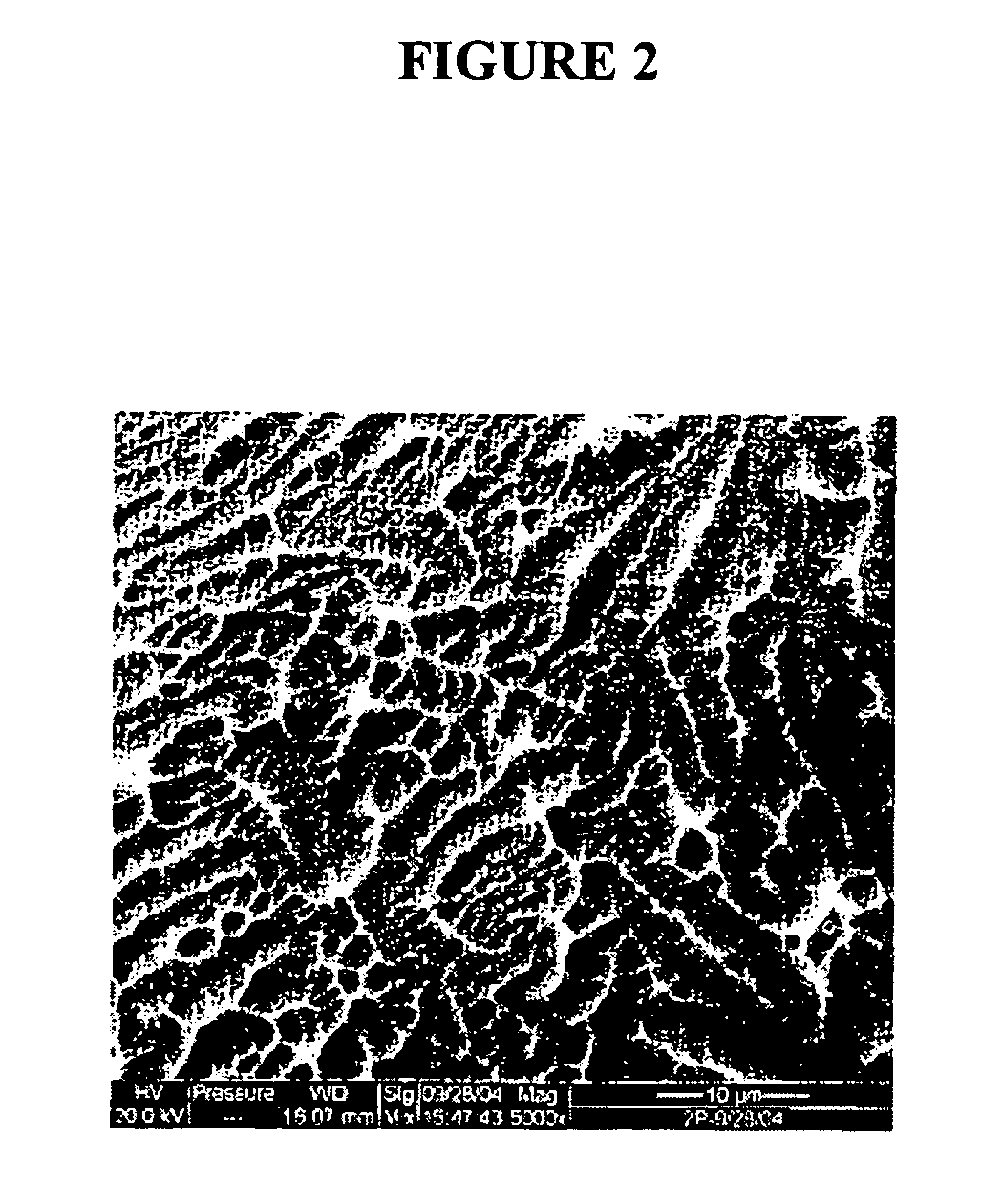

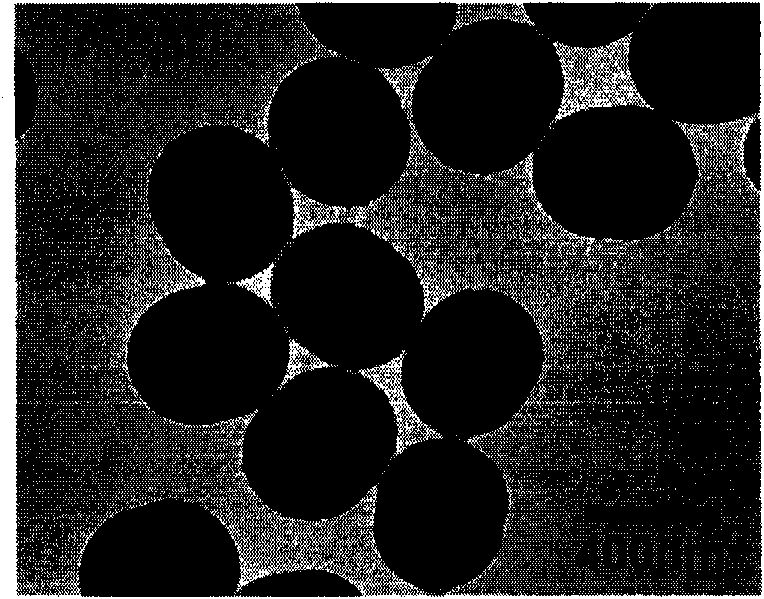

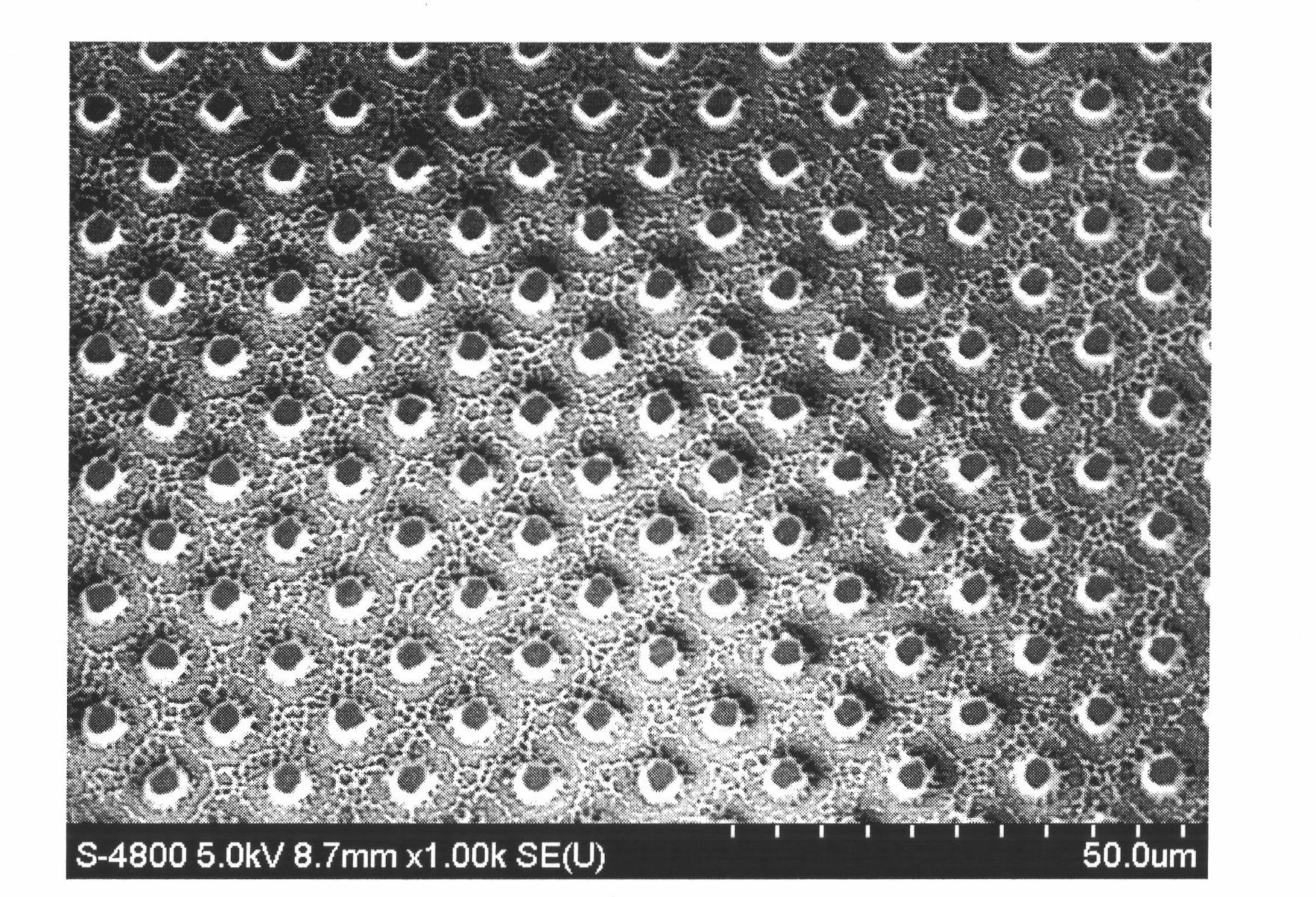

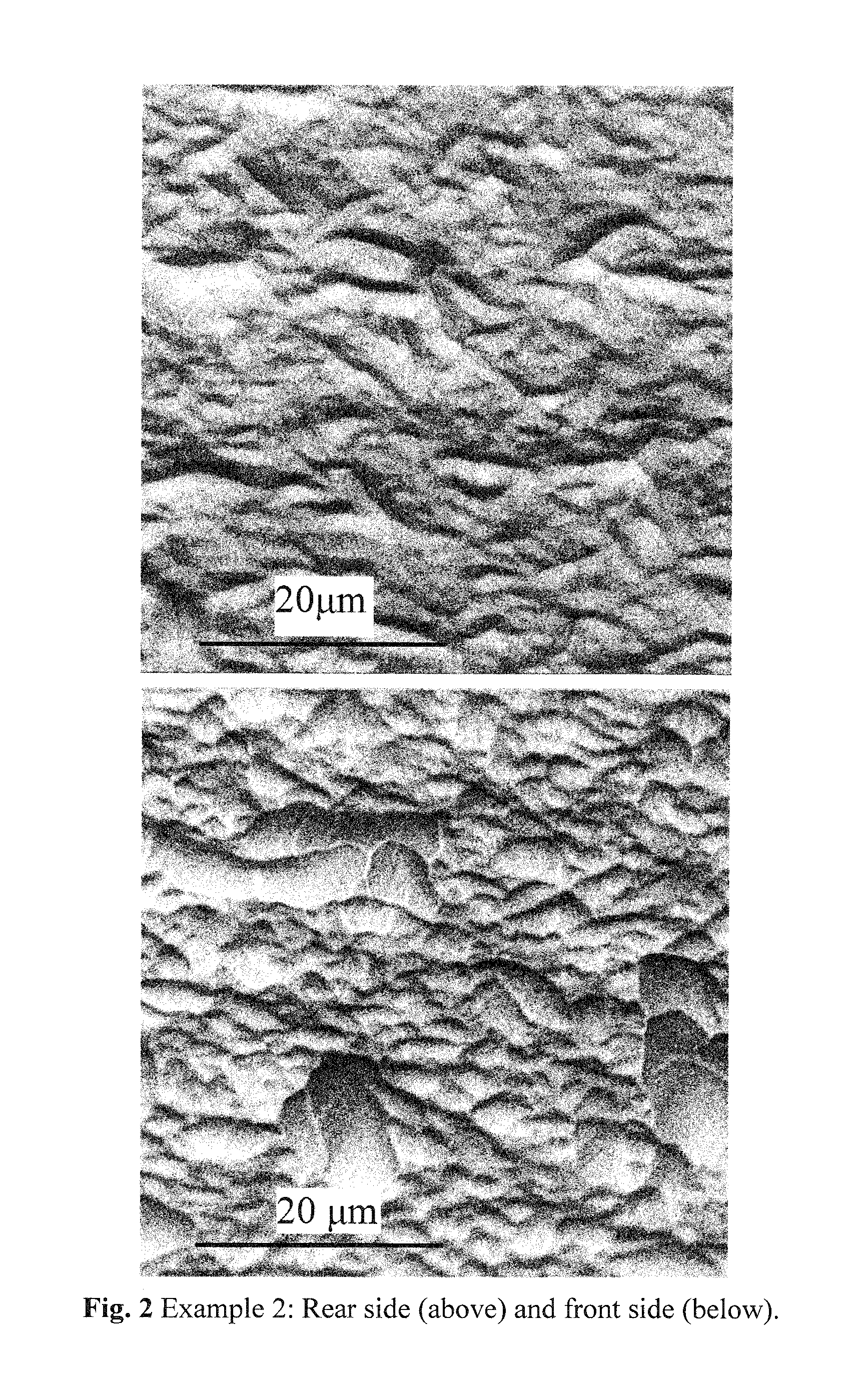

Implants with textured surface and methods for producing the same

ActiveUS20060289388A1High retention rateConvenient coatingImpression capsDecorative surface effectsMicrometerChloride

Compositions and methods are provided for preparing a metal substrate having a uniform textured surface with a plurality of indentations with a diameter in the nanometer and micrometer range. The textured surface is produced by exposing the substrate to an etching fluid comprising a hydrohalic acid and a mixture of a hydrohalic acid and an oxyacid, a chloride containing compound, and an oxidant. The etching solution can be used at ambient temperature. This textured surface enhances adherence of coatings or cells onto the textured surface, improves the retention of proteins on the surface, and encourages bone in-growth.

Owner:DEPUY PROD INC

Compound Janus colloid particle and modified Janus colloid particle as well as preparation methods thereof

The invention discloses a compound Janus colloid particle and a modified Janus colloid particle as well as preparation methods thereof. Inorganic particles are taken as seeds, and a silane coupling agent modification method, a seed emulsion polymerization method, an inorganic surface etching method, method for inducing recombination functional materials by using polymer gel, and the like are combined to prepare inorganic / polymer, inorganic / inorganic, inorganic / metallic, inorganic / metallic oxide Janus particles. The structure and the size of the Janus particle can be controlled by controlling the activity of reactants, feeding speed, and the concentration of reactants, and the compounding of various kinds of materials can be realized. The Janus particle provided by the invention not only has good dispersibility, but also has good strength and size stability.

Owner:INST OF CHEM CHINESE ACAD OF SCI

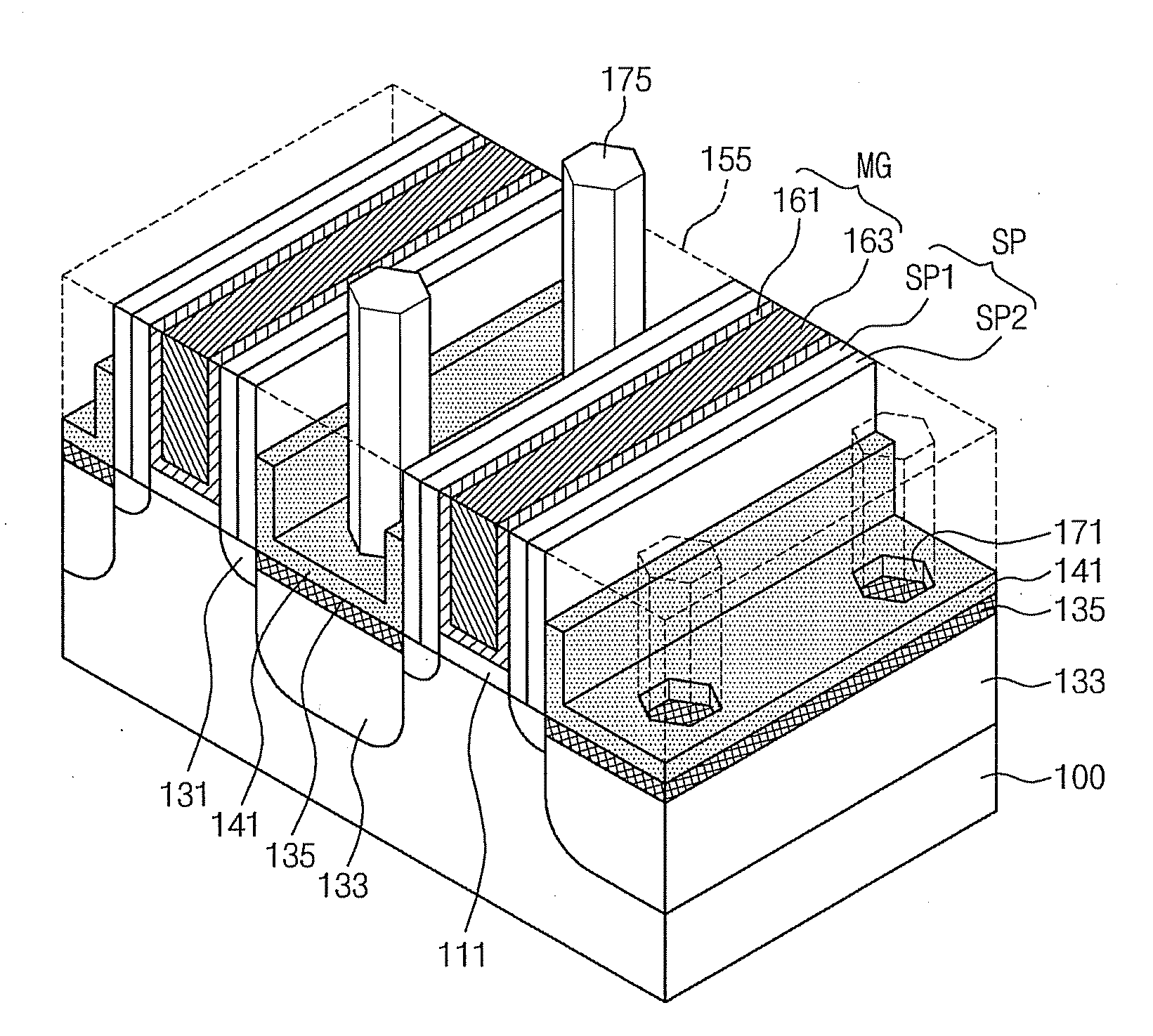

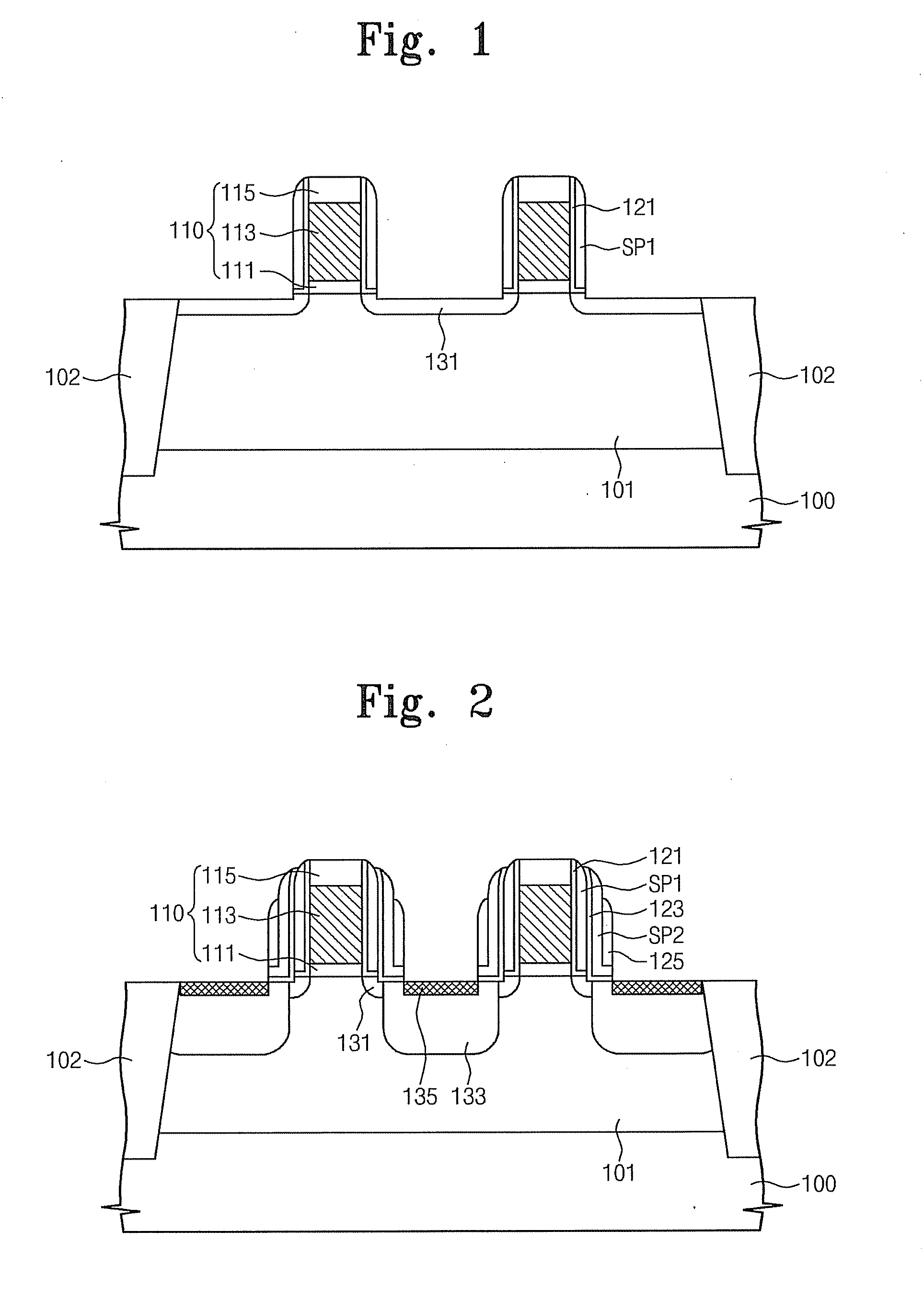

Semiconductor devices and methods for manufacturing the same

InactiveUS20120086048A1TransistorSemiconductor/solid-state device detailsInsulation layerDevice material

Semiconductor devices and methods of manufacturing semiconductor devices. A semiconductor device includes a metal gate electrode stacked on a semiconductor substrate with a gate insulation layer disposed therebetween, spacer structures disposed on the semiconductor substrate at both sides of the metal gate electrode, source / drain regions formed in the semiconductor substrate at the both sides of the metal gate electrode, and an etch stop pattern including a bottom portion covering the source / drain regions and a sidewall portion extended from the bottom portion to cover a portion of sidewalls of the spacer structures, in which an upper surface of the sidewall portion of the etch stop pattern is positioned under an upper surface of the metal gate electrode.

Owner:SAMSUNG ELECTRONICS CO LTD

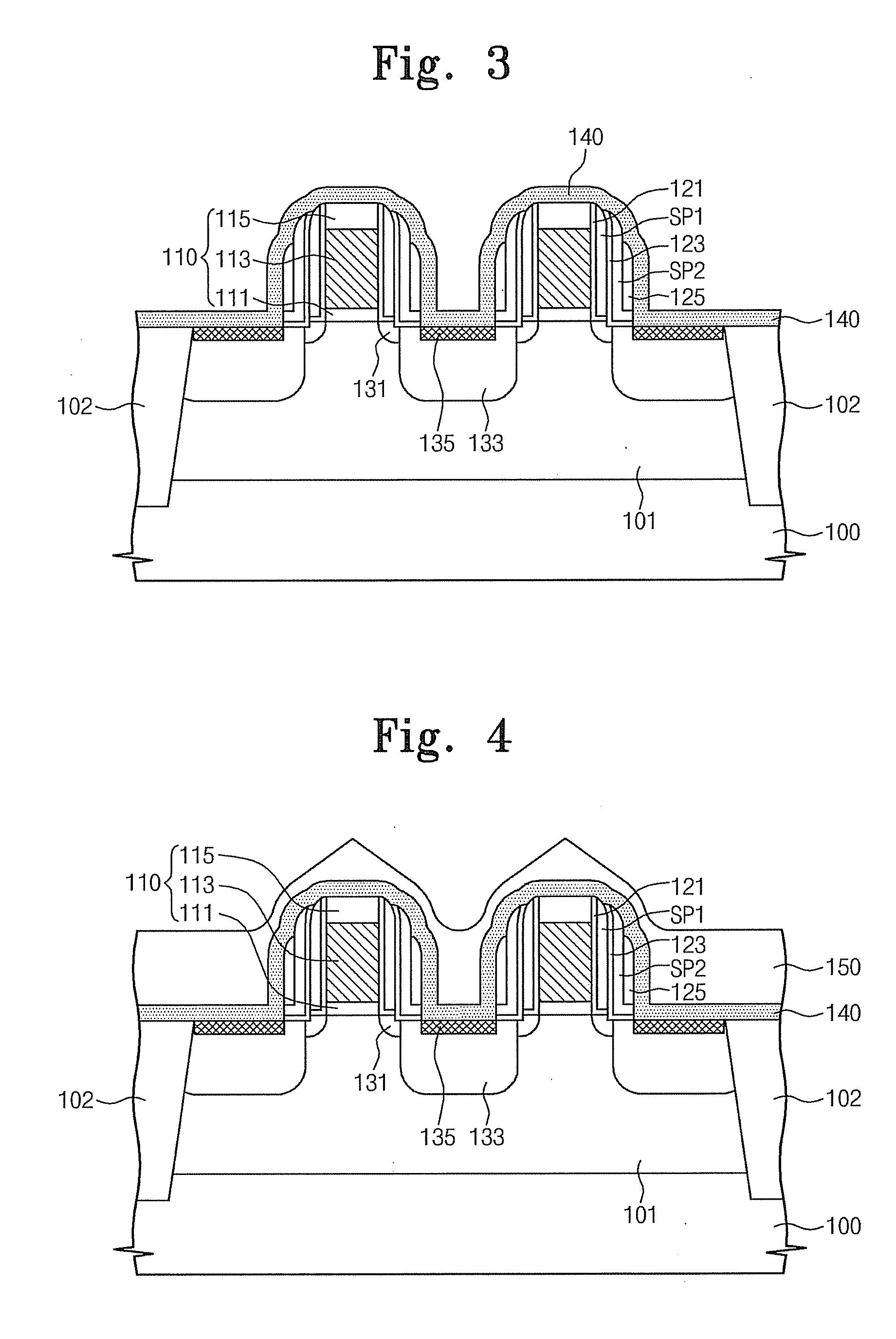

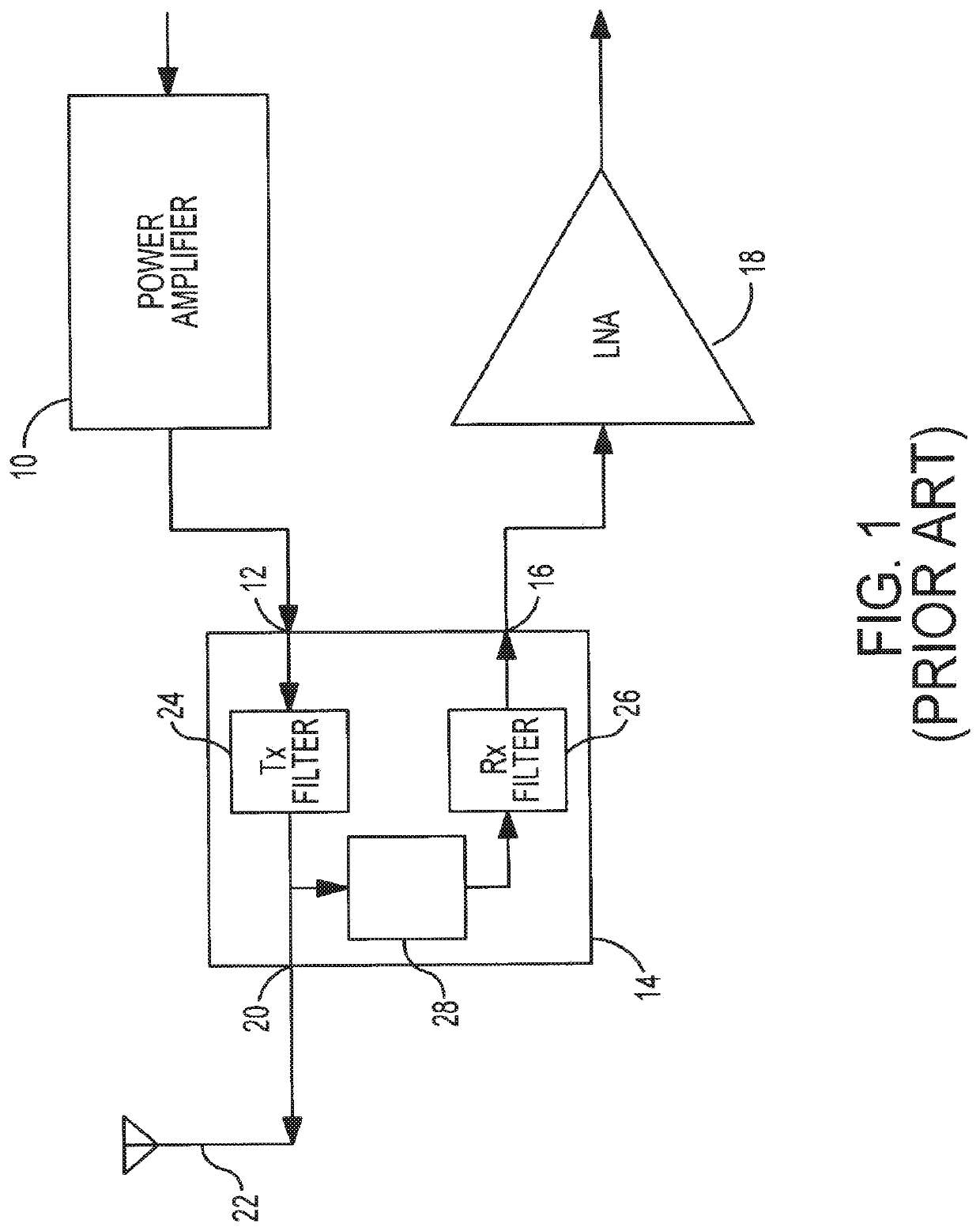

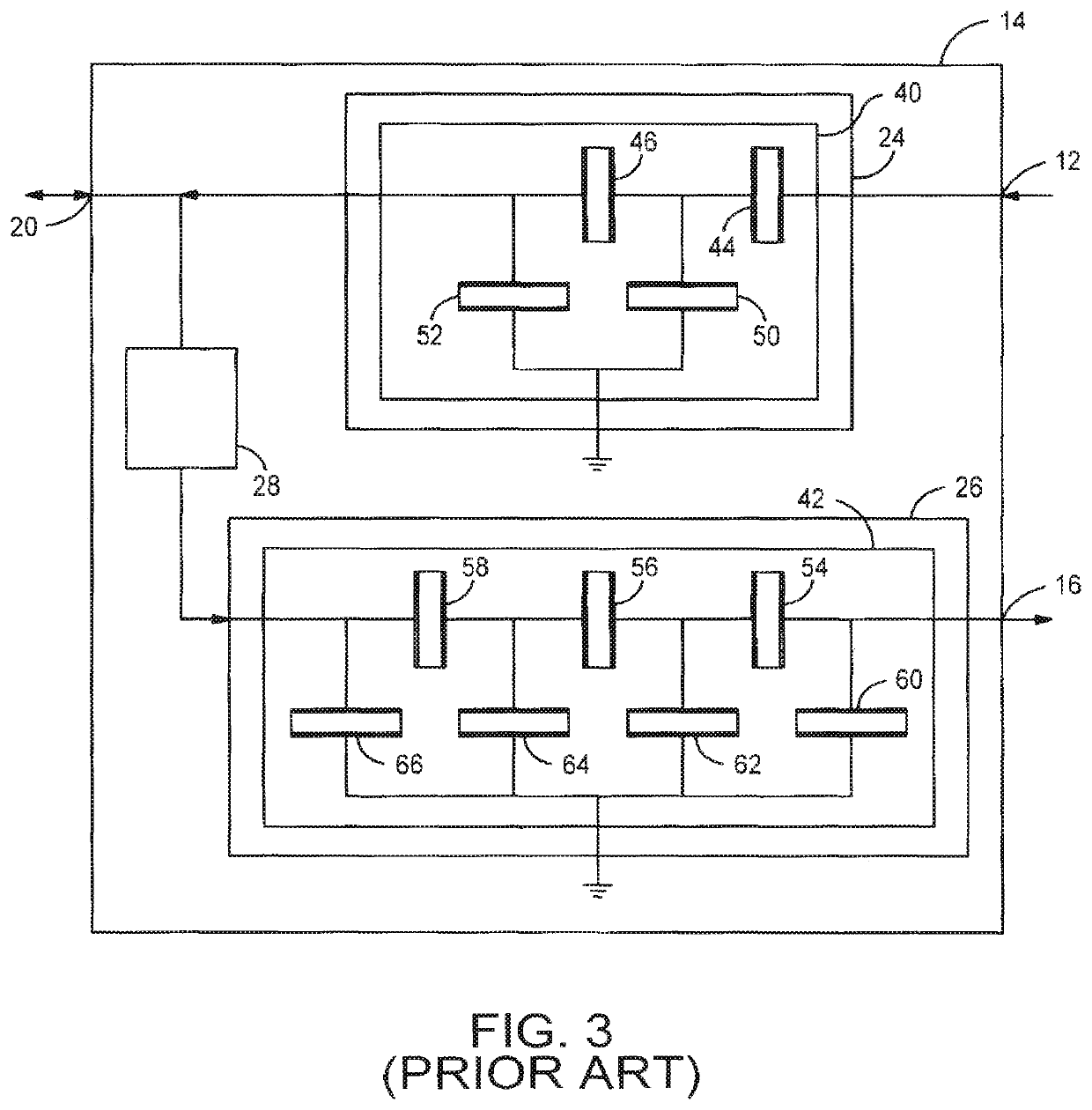

Effective coupling coefficients for strained single crystal epitaxial film bulk acoustic resonators

ActiveUS11211918B2Lower effective coupling coefficientImprove performancePiezoelectric/electrostrictive device manufacture/assemblyImpedence networksBand-pass filterSingle crystal

In an array of single crystal acoustic resonators, the effective coupling coefficient of first and second strained single crystal filters are individually tailored in order to achieve desired frequency responses. In a duplexer embodiment, the effective coupling coefficient of a transmit band-pass filter is lower than the effective coupling coefficient of a receive band-pass filter of the same duplexer. The coefficients can be tailored by varying the ratio of the thickness of a piezoelectric layer to the total thickness of electrode layers or by forming a capacitor in parallel with an acoustic resonator within the filter for which the effective coupling coefficient is to be degraded. Further, a strained piezoelectric layer can be formed overlying a nucleation layer characterized by initial surface etching and piezoelectric layer deposition parameters being configured to modulate a strain condition in the strained piezoelectric layer to adjust piezoelectric properties for improved performance in specific applications.

Owner:AKOUSTIS INC

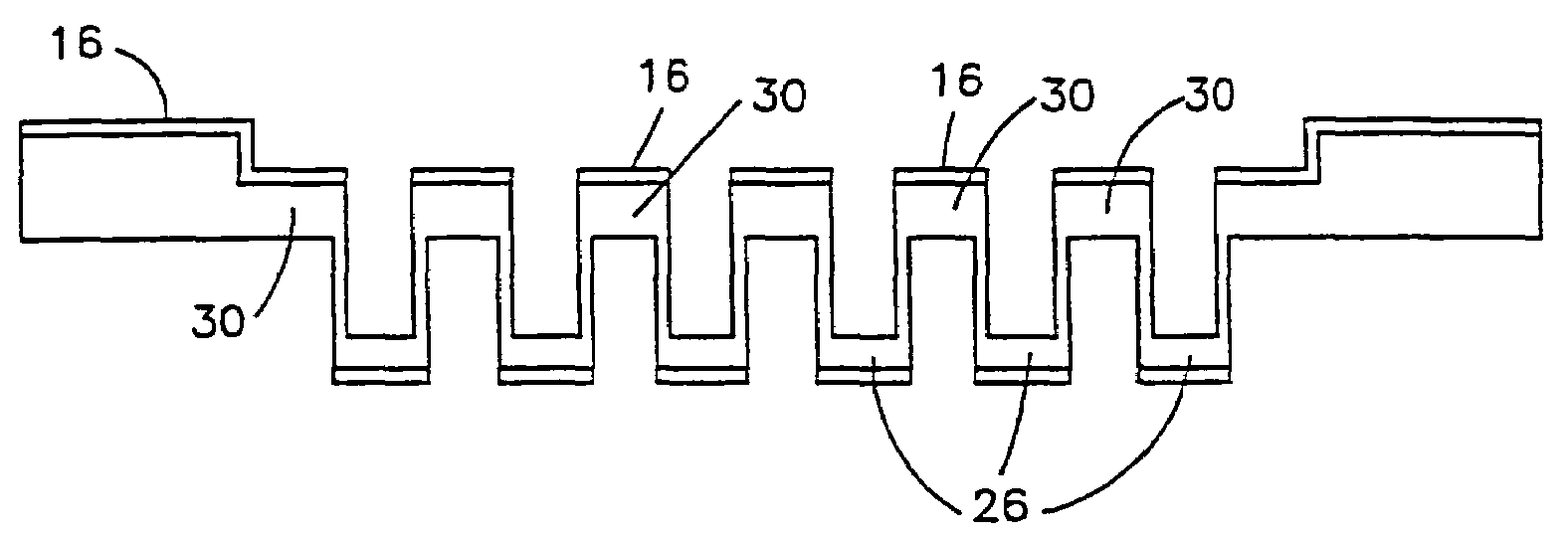

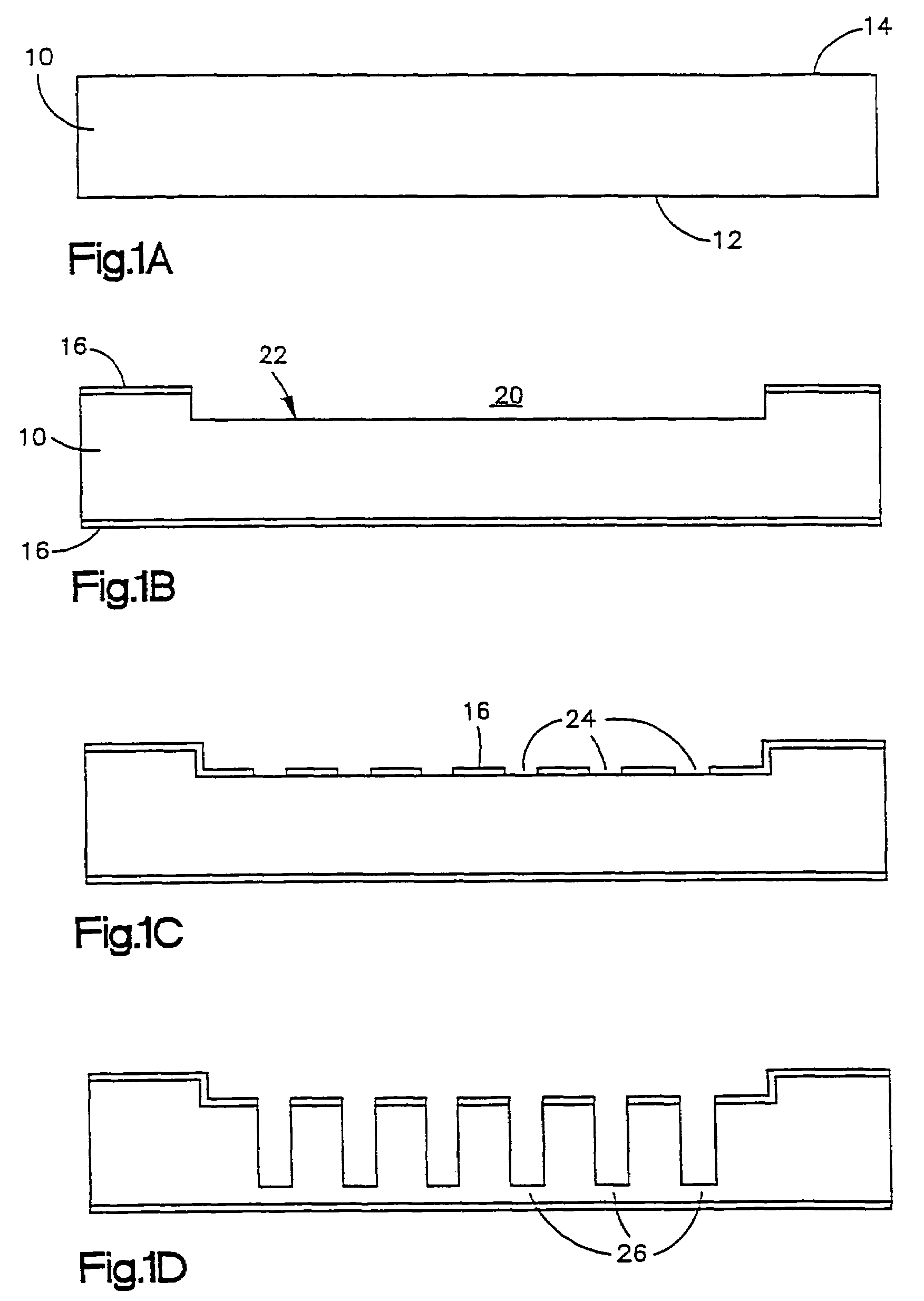

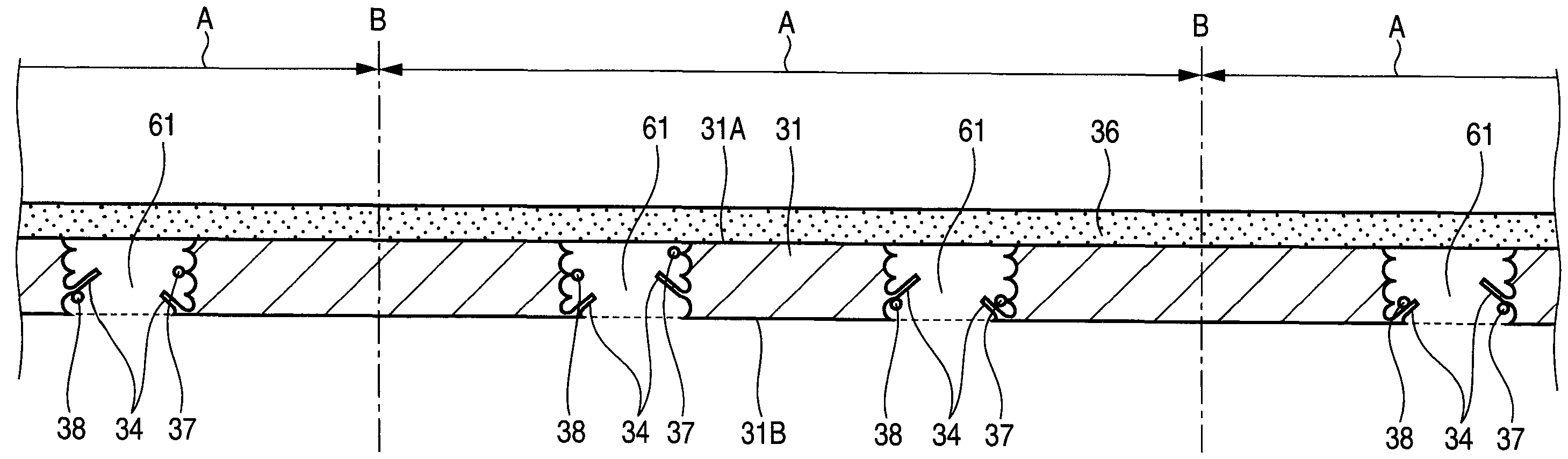

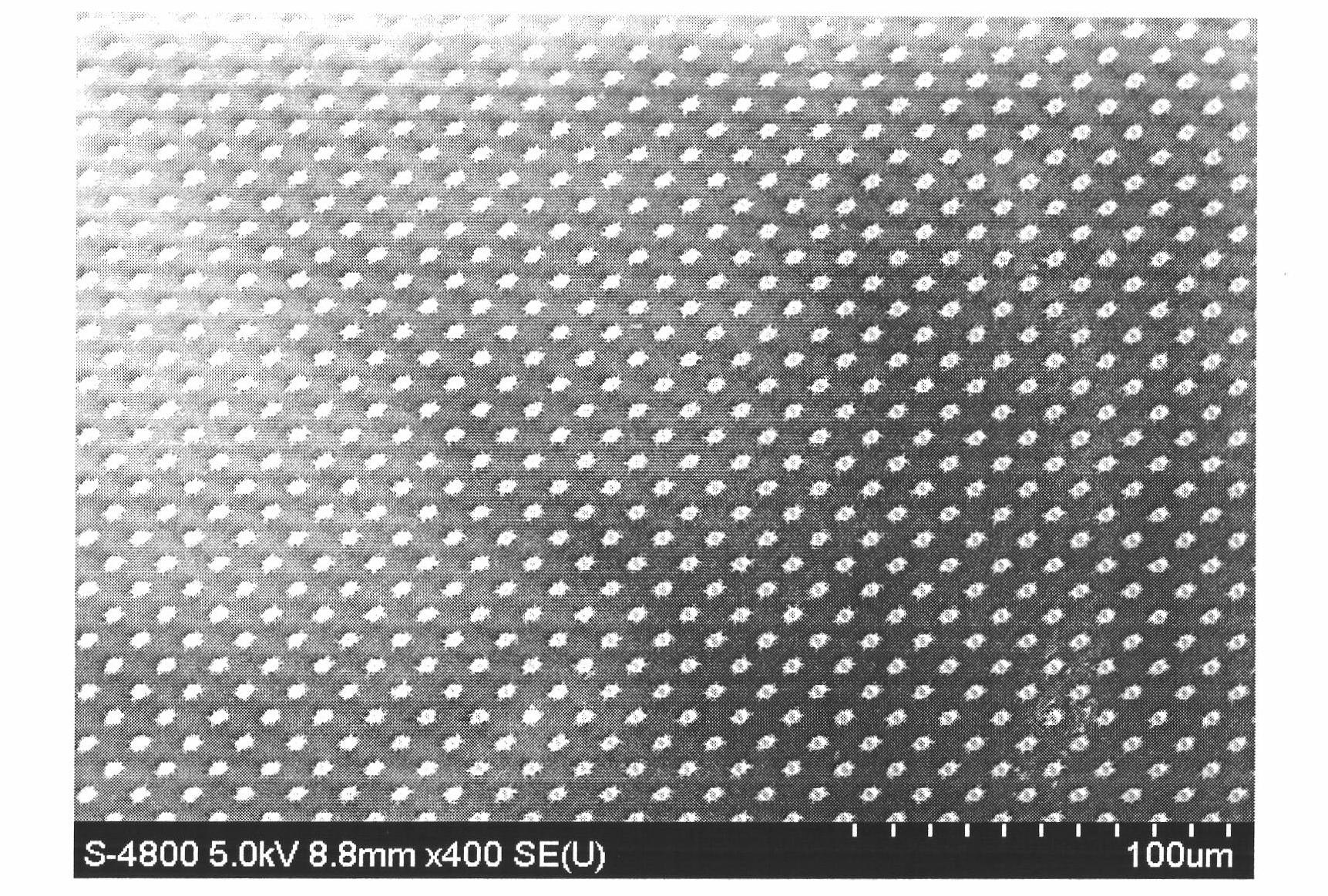

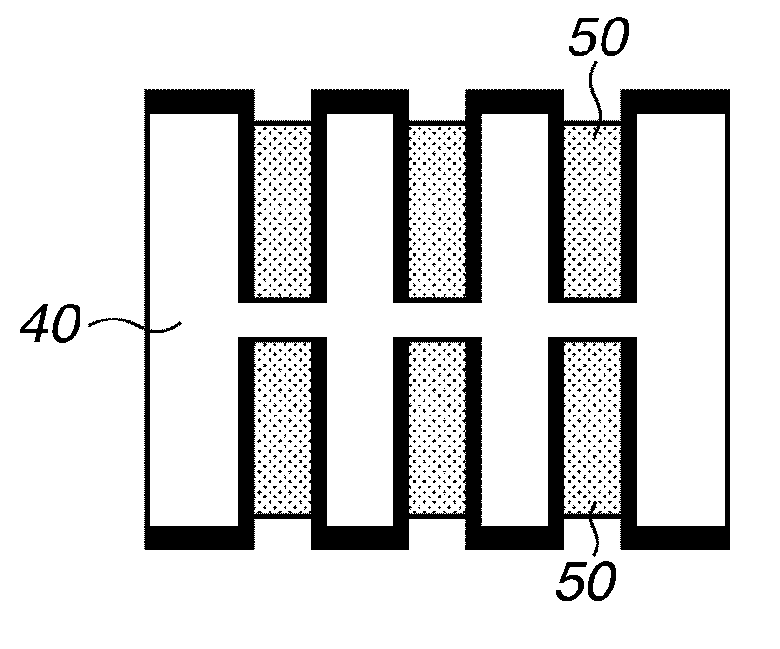

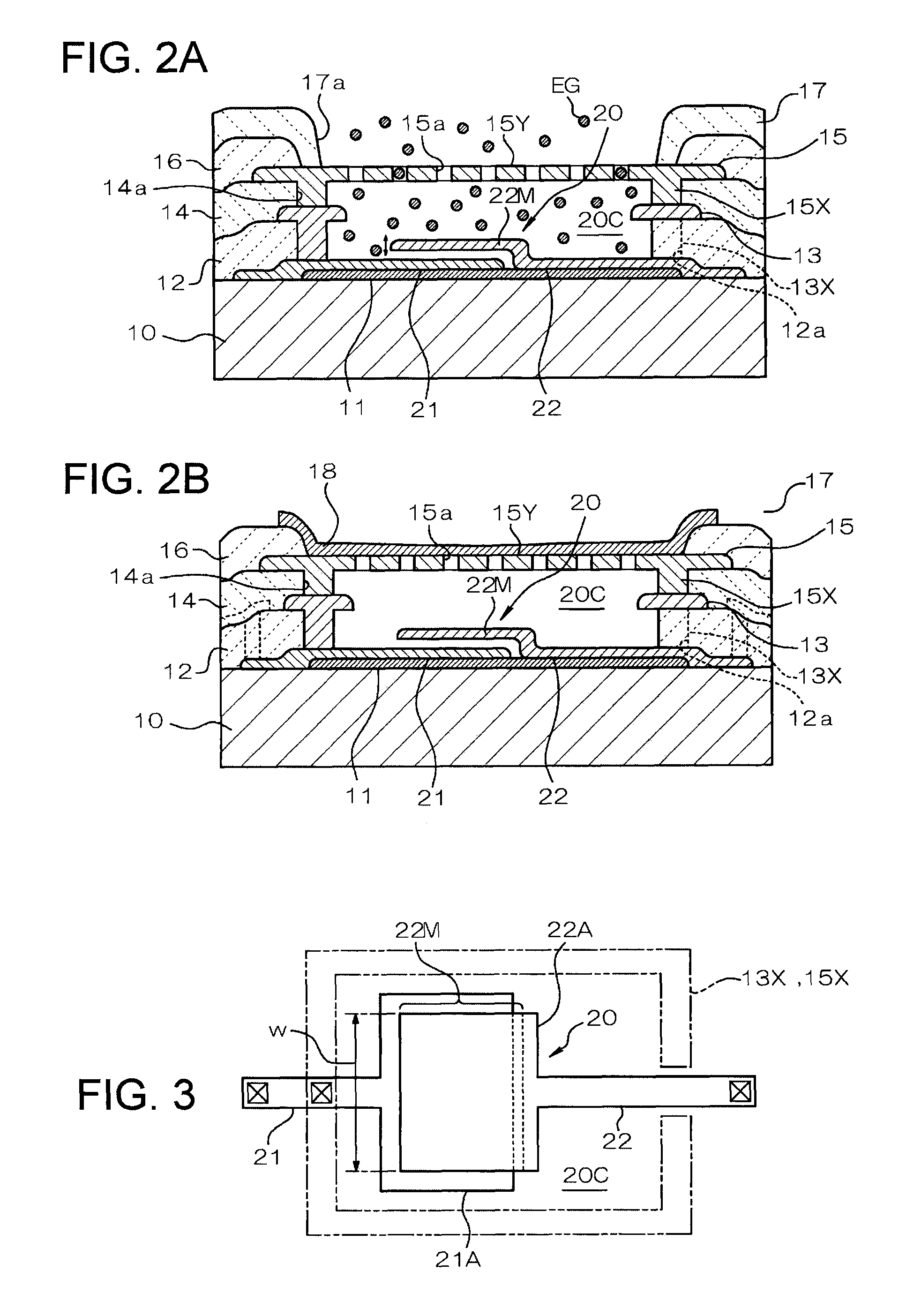

Microneedle array module and method of fabricating the same

A microneedle array module is disclosed comprising a multiplicity of microneedles affixed to and protruding outwardly from a front surface of a substrate to form the array, each microneedle of the array having a hollow section which extends through its center to an opening in the tip thereof. A method of fabricating the microneedle array module is also disclosed comprising the steps of: providing etch resistant mask layers to one and another opposite surfaces of a substrate to predetermined thicknesses; patterning the etch resistant mask layer of the one surface for outer dimensions of the microneedles of the array; patterning the etch resistant mask layer of the other surface for inner dimensions of the microneedles of the array; etching unmasked portions of the substrate from one and the other surfaces to first and second predetermined depths, respectively; and removing the mask layers from the one and the other surfaces. One embodiment of the method includes the steps of: providing an etch resistant mask layer to the other surface of the substrate to a predetermined thickness; patterning the etch resistant mask layer of the other surface to define a reservoir region in the substrate; and etching away the unmasked reservoir region of the substrate to form a reservoir well in the other surface of the substrate. A layer of material may be provided to the other surface to enclose the reservoir well and a passageway is provided through the layer to the well region.

Owner:THE CLEVELAND CLINIC FOUND

Chemical etching liquid for metals and etching method

The invention provides a chemical etching liquid for metals. The chemical etching liquid comprises ferric chloride, hydrochloric acid, phosphoric acid, hydrogen nitrate, a corrosion inhibitor and a surface active agent. The corrosion inhibitor is at least one of hexamethylene tetramine, ethidene diamine, triethanolamine and heptadecane amide; and the surface active agent is one or two of sodium lauryl benzenesulfate and dodecyl alcohol amine. The invention further discloses a chemical etching method for metals; with the method, the metals are etched through spraying the etching liquid; and the etching liquid is provided by the invention. The etching liquid provided by the invention can be applied to surface etching of various metals, particularly stainless steel, copper and aluminum alloy; and since the metals can be etched with the same etching liquid, the consumption of equipment is reduced.

Owner:南通麦特隆新材料科技有限公司

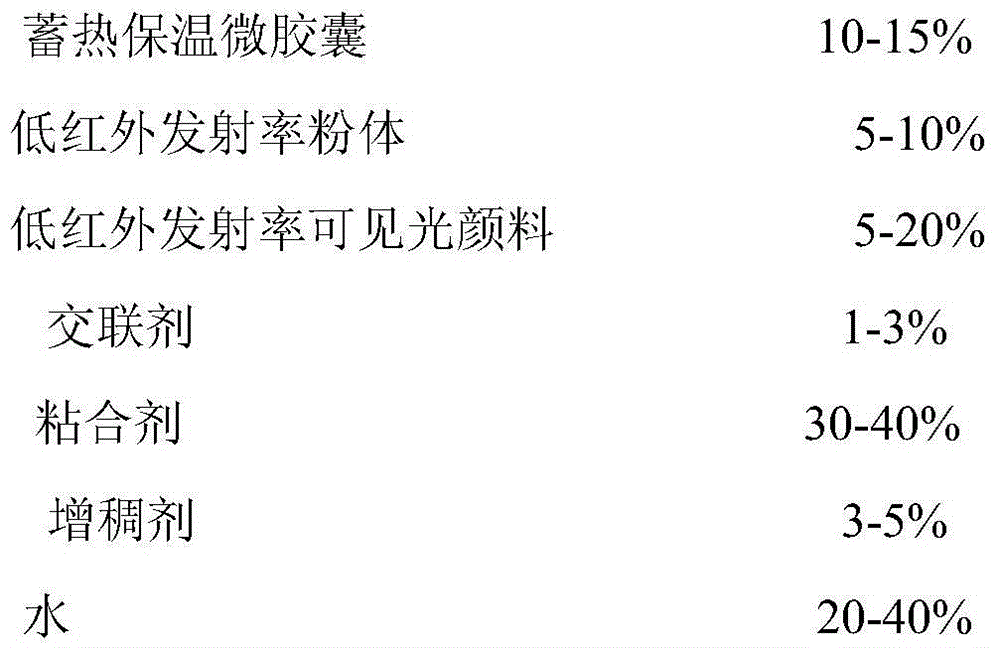

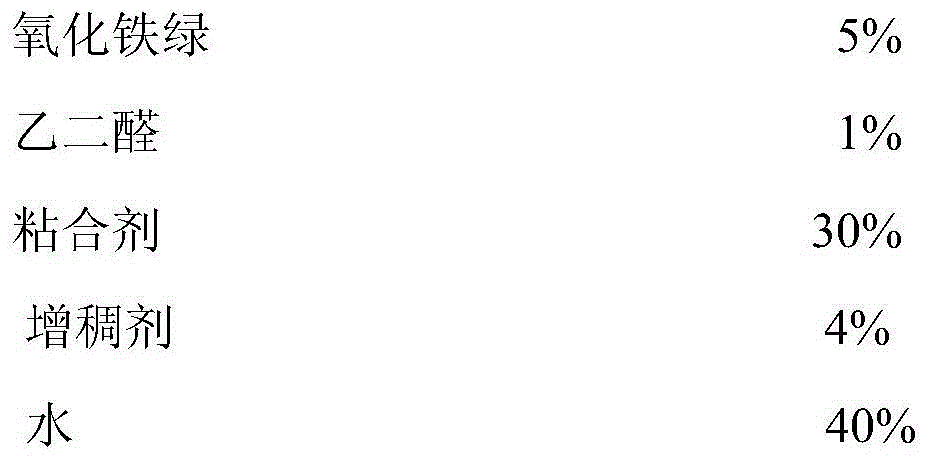

Method for preparing stealthy fabric with double functions of radar stealth and infrared stealth

ActiveCN104060474AImprove bonding fastnessExcellent infrared stealth effectPhysical treatmentMulti bandPolyurethane adhesive

The invention belongs to the field of absorbing material research, and particularly relates to a method for preparing stealthy fabric with double functions of radar stealth and infrared stealth. According to the method, the binding strength of a radar stealth layer and textile is improved by using electrostatic interaction between plasma grafting-introduced carboxyl and polyaniline absorbing materials and the surface etching effect of low-temperature plasma; the binding strength of the radar and the infrared stealth layers and the textile is improved by using the reactivity between a binary aldehyde crosslinking agent and amino on a polyaniline polymer and a microcapsule wall material and a polyurethane adhesive; the obtained stealth coating is not only good in binding strength with the textile, but also light in quality and good in durability, and has multi-band stealth effects of radar, infrared light and visible light.

Owner:江苏华宏昌明科技有限公司

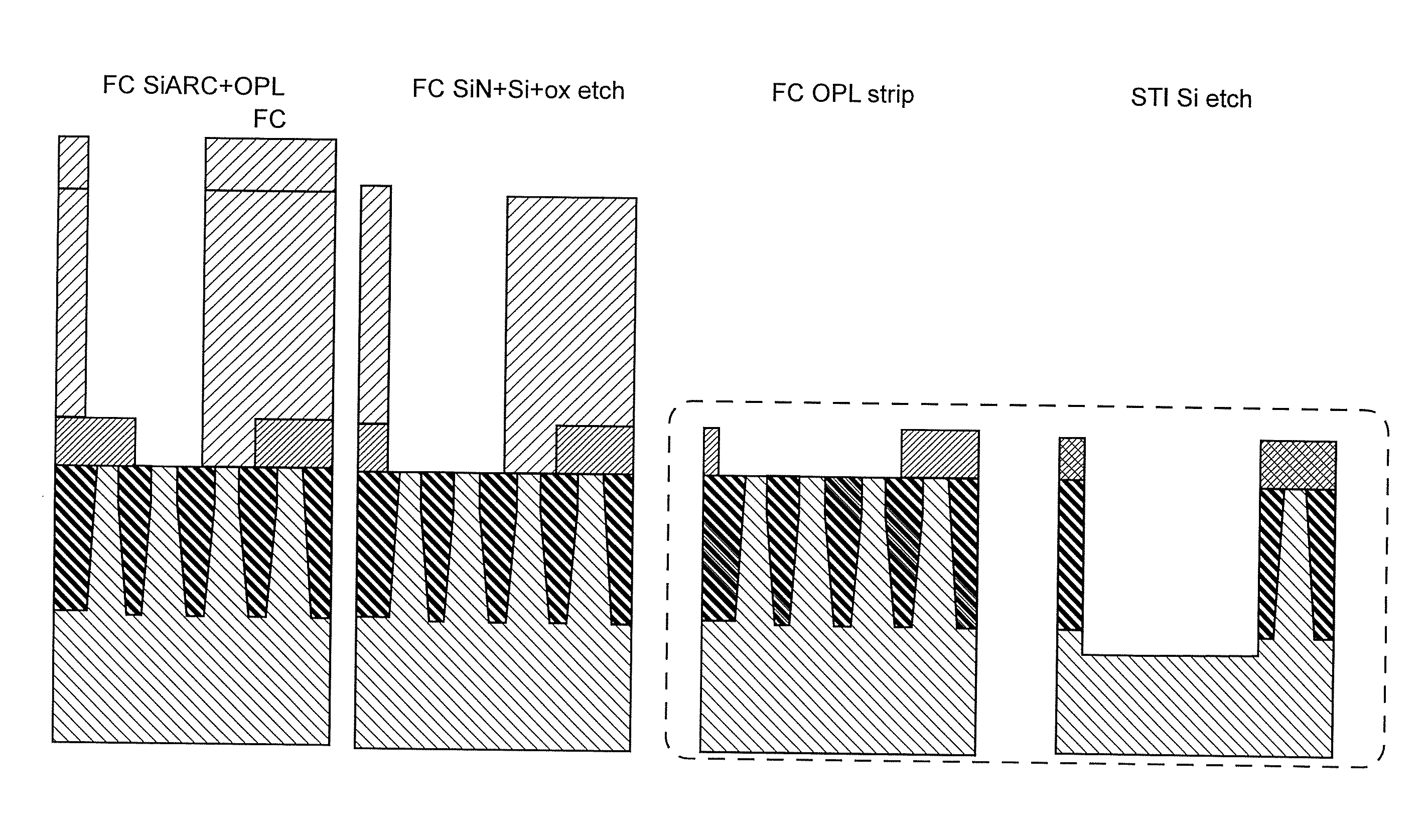

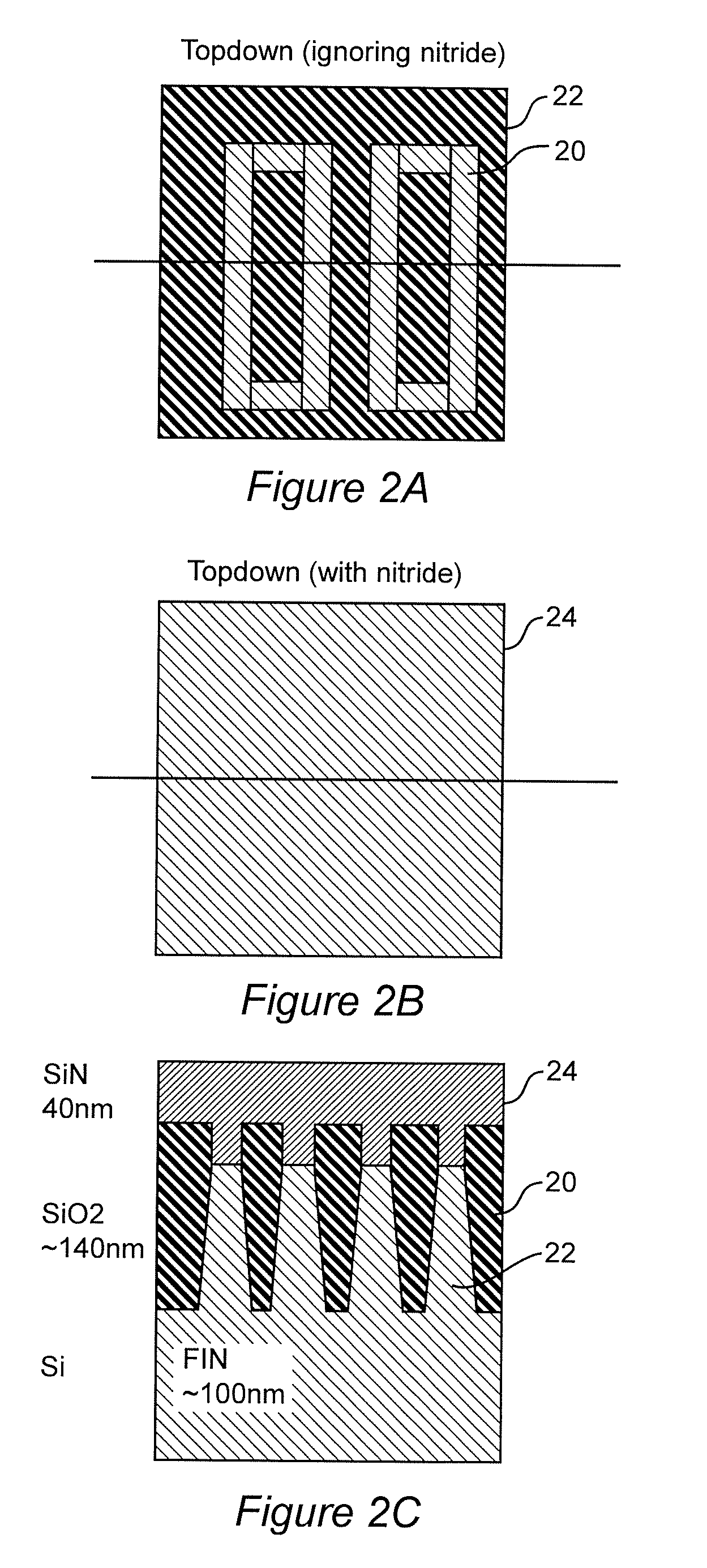

finFET isolation by selective cyclic etch

InactiveUS20150145065A1High selectivityEasy to controlTransistorSolid-state devicesSemiconductor materialsEngineering

Etching interleaved structures of semiconductor material forming fins of finFETs and local isolation material interposed between the fins is performed alternately and cyclically by alternating etchants cyclically such as by alternating gases during reactive ion etching. Etchants are preferably alternated when one of the semiconductor material and the local isolation material protrudes above the other by a predetermined distance. Since protruding surfaces are etched more rapidly than recessed surfaces, the overall etching process is accelerated and completed in less time such that erosion of other materials to which the etchants are less than optimally selective is reduced and allow improved etching of trenches for improved isolation structures to be formed.

Owner:GLOBALFOUNDRIES INC

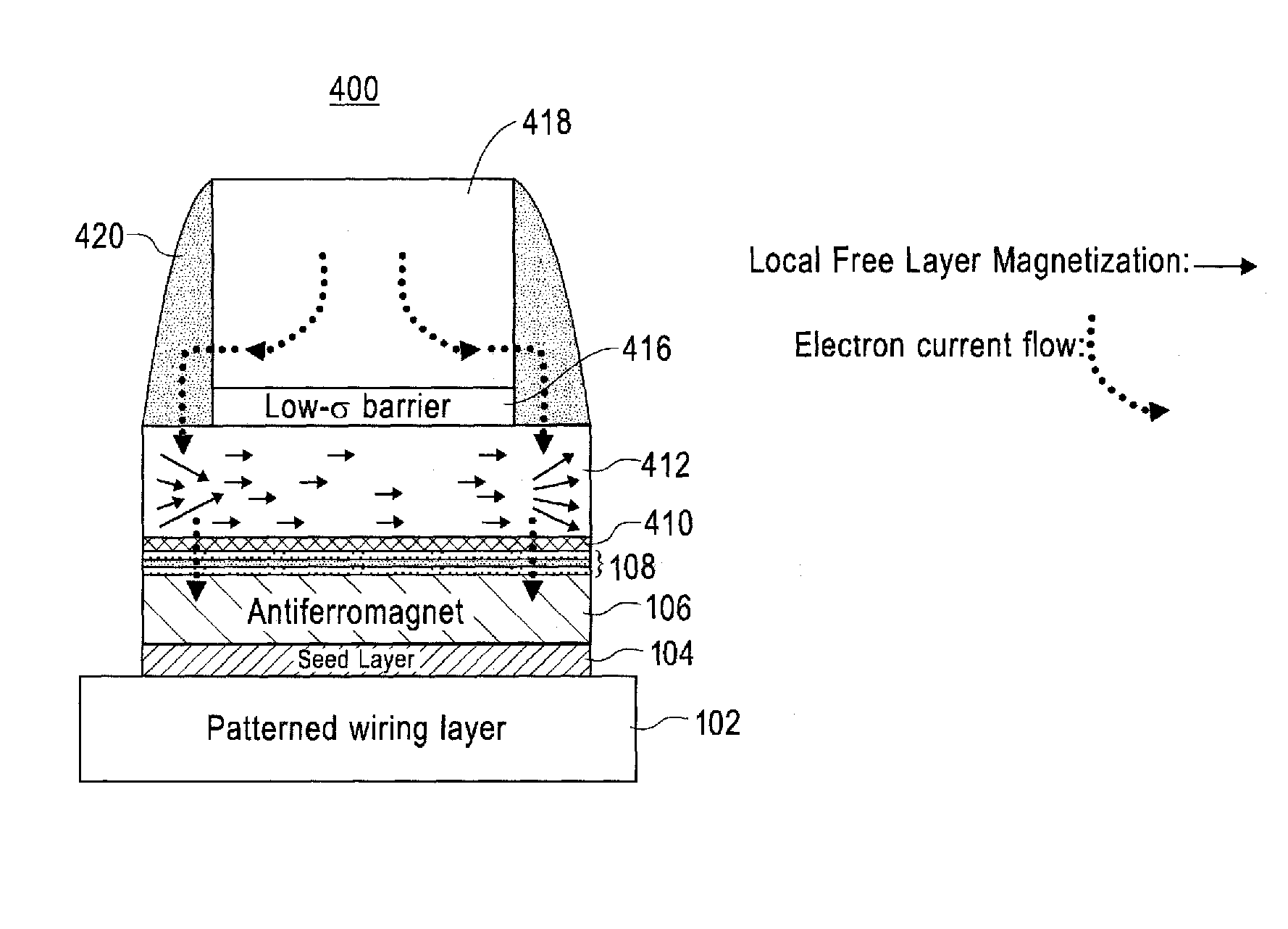

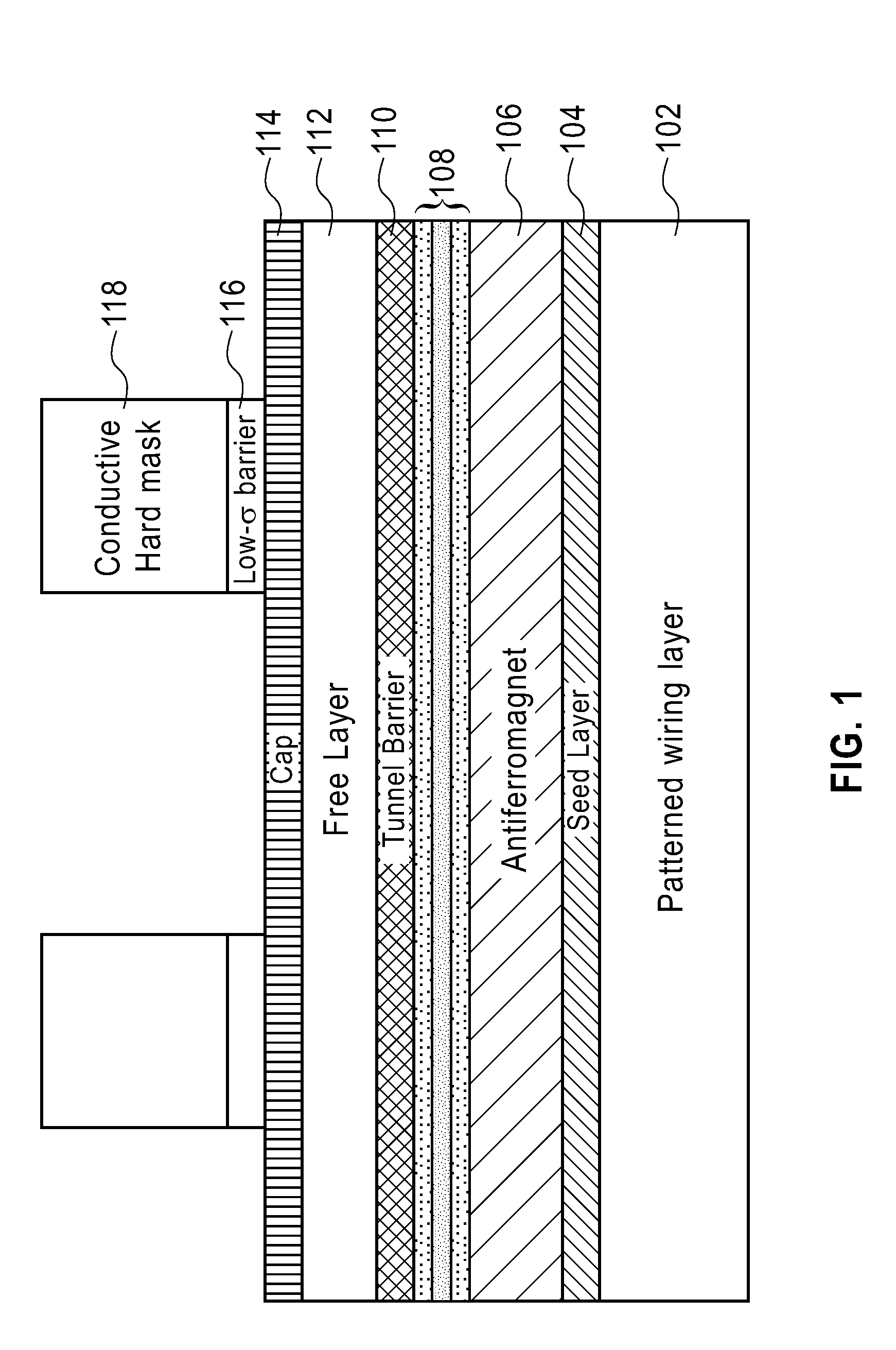

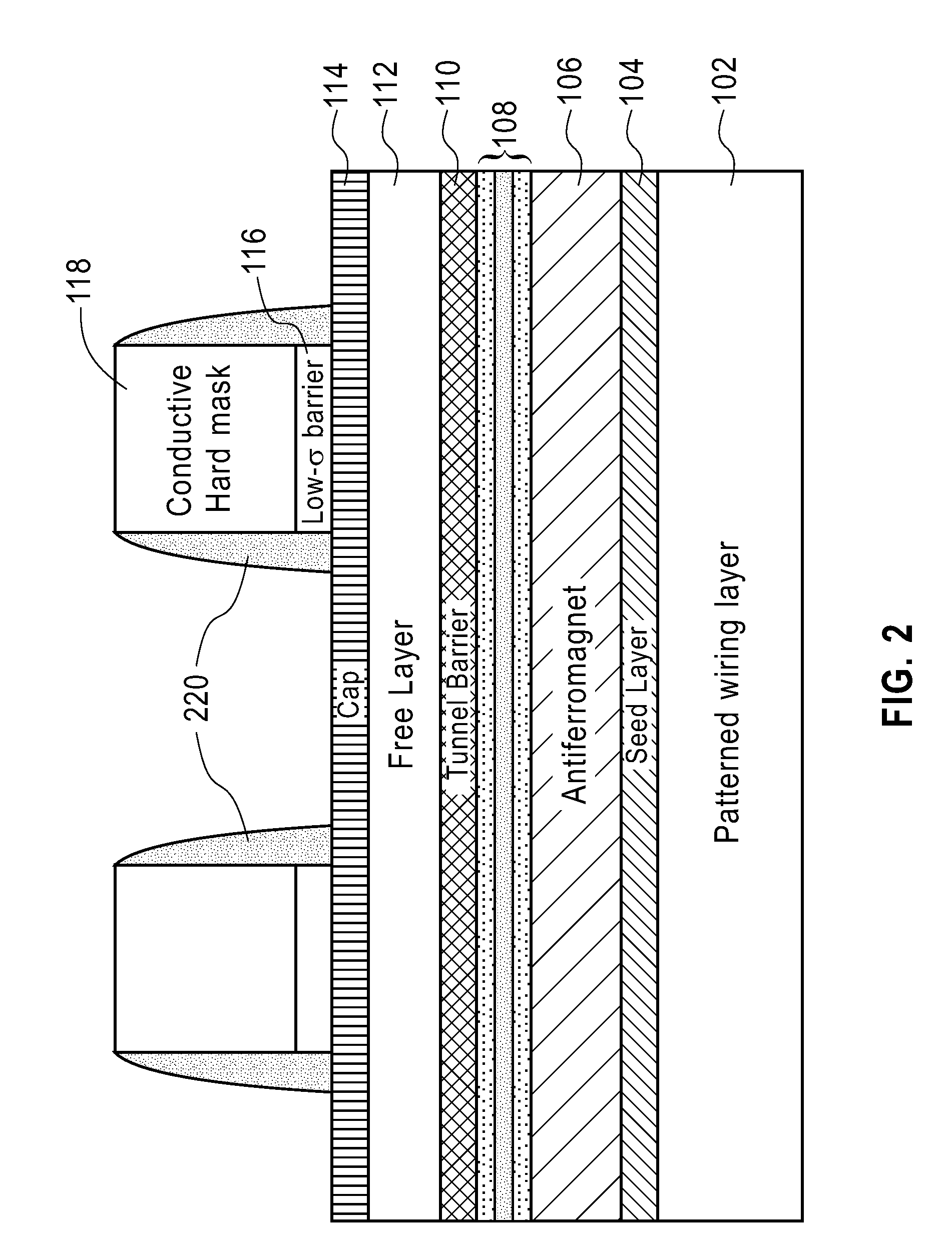

Sidewall coating for non-uniform spin momentum-transfer magnetic tunnel junction current flow

ActiveUS7989224B2Efficient transferIncrease volumeMagnetic-field-controlled resistorsSemiconductor/solid-state device manufacturingPower flowSpins

A magnetic tunnel junction device comprises a substrate including a patterned wiring layer. A magnetic tunnel junction (MTJ) stack is formed over the wiring layer. A low-conductivity layer is formed over the MTJ stack and a conductive hard mask is formed thereon. A spacer material is then deposited that includes a different electrical conductivity than the low conductivity layer. The spacer material is etched from horizontal surfaces so that the spacer material remains only on sidewalls of the hard mask and a stud. A further etch process leaves behind the sidewall-spacer material as a conductive link between a free magnetic layer and the conductive hard mask, around the low-conductivity layer. A difference in electrical conductivity between the stud and the spacer material enhances current flow along the edges of the free layer within the MTJ stack and through the spacer material formed on the sidewalls.

Owner:INT BUSINESS MASCH CORP

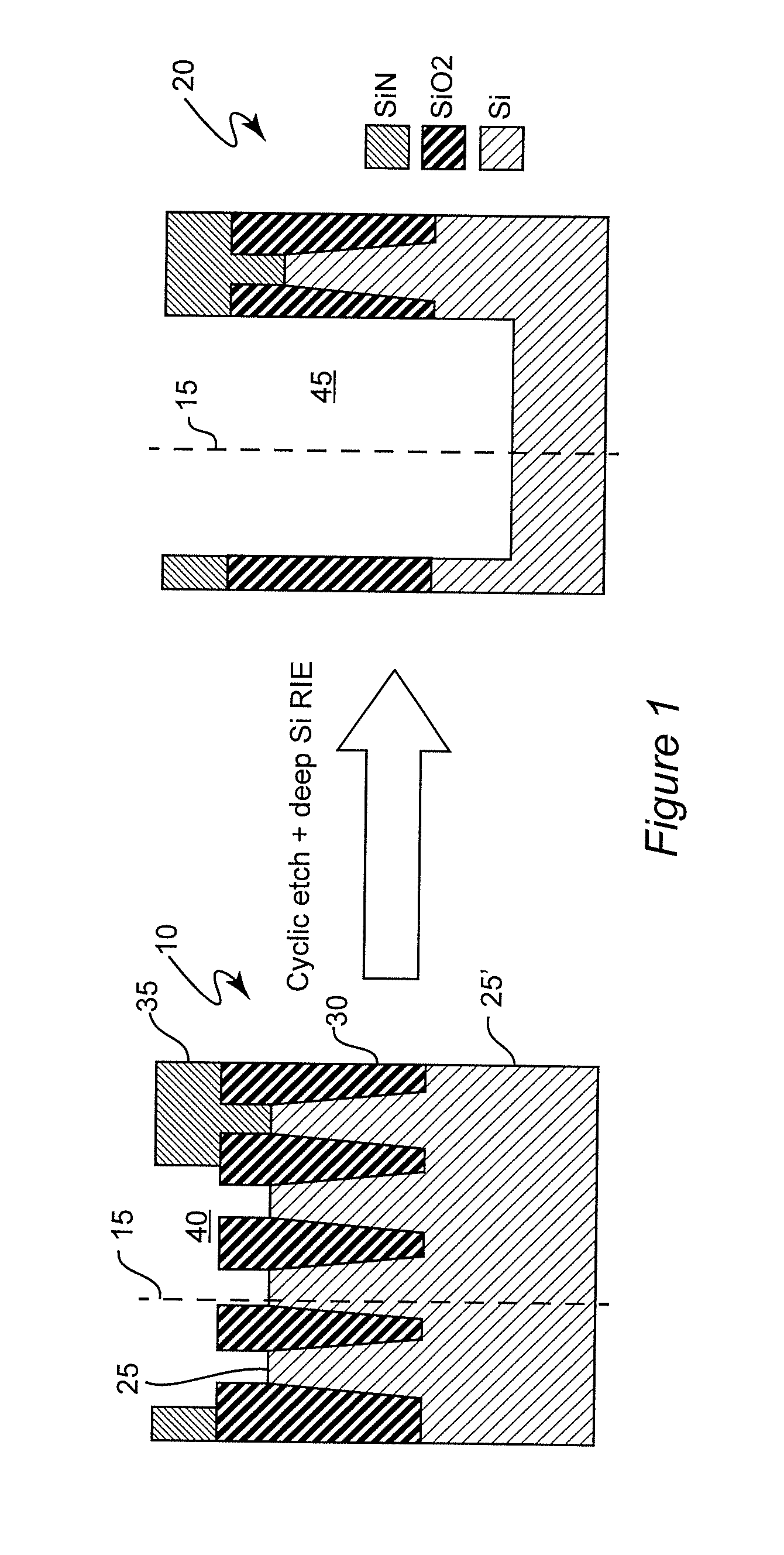

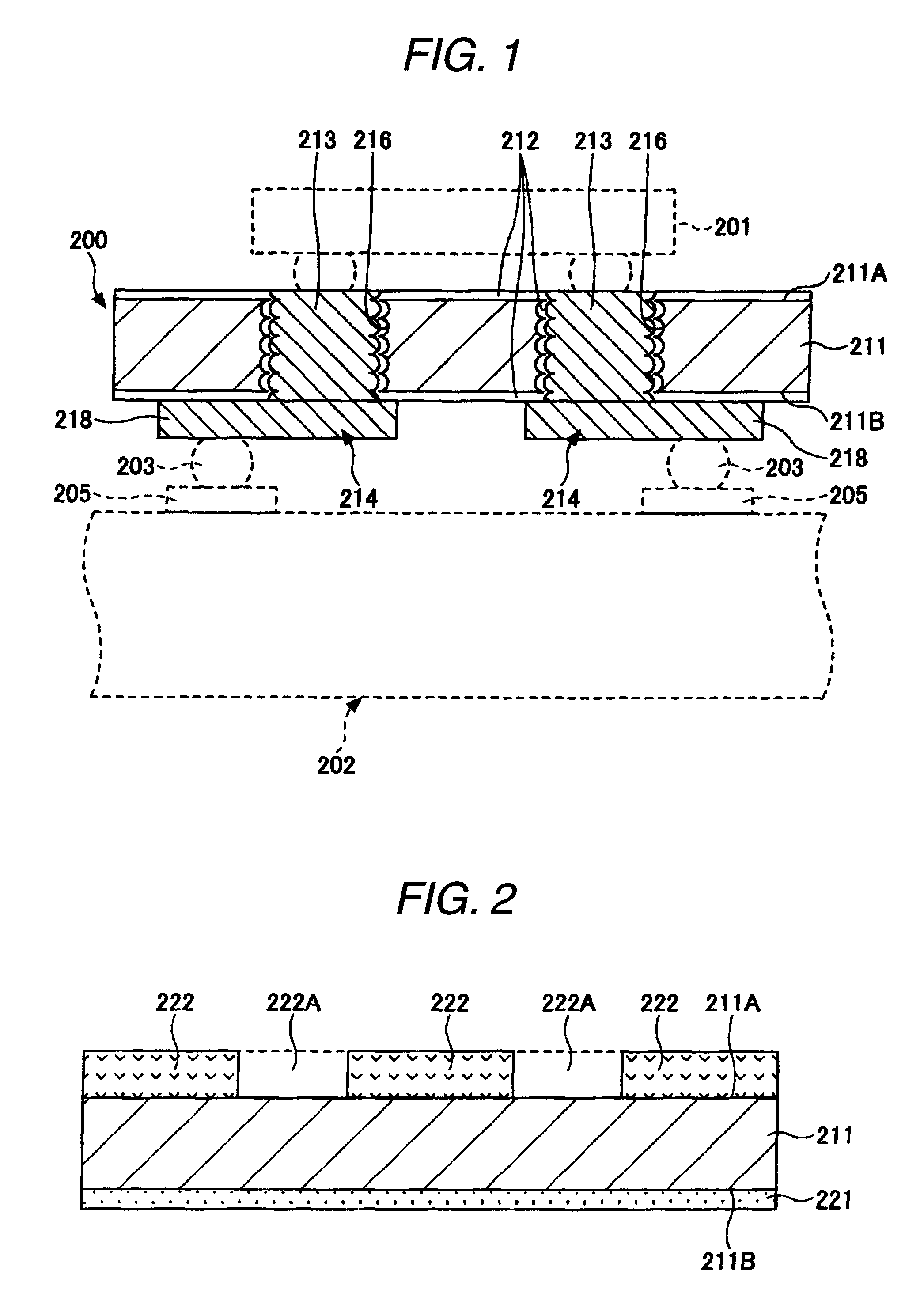

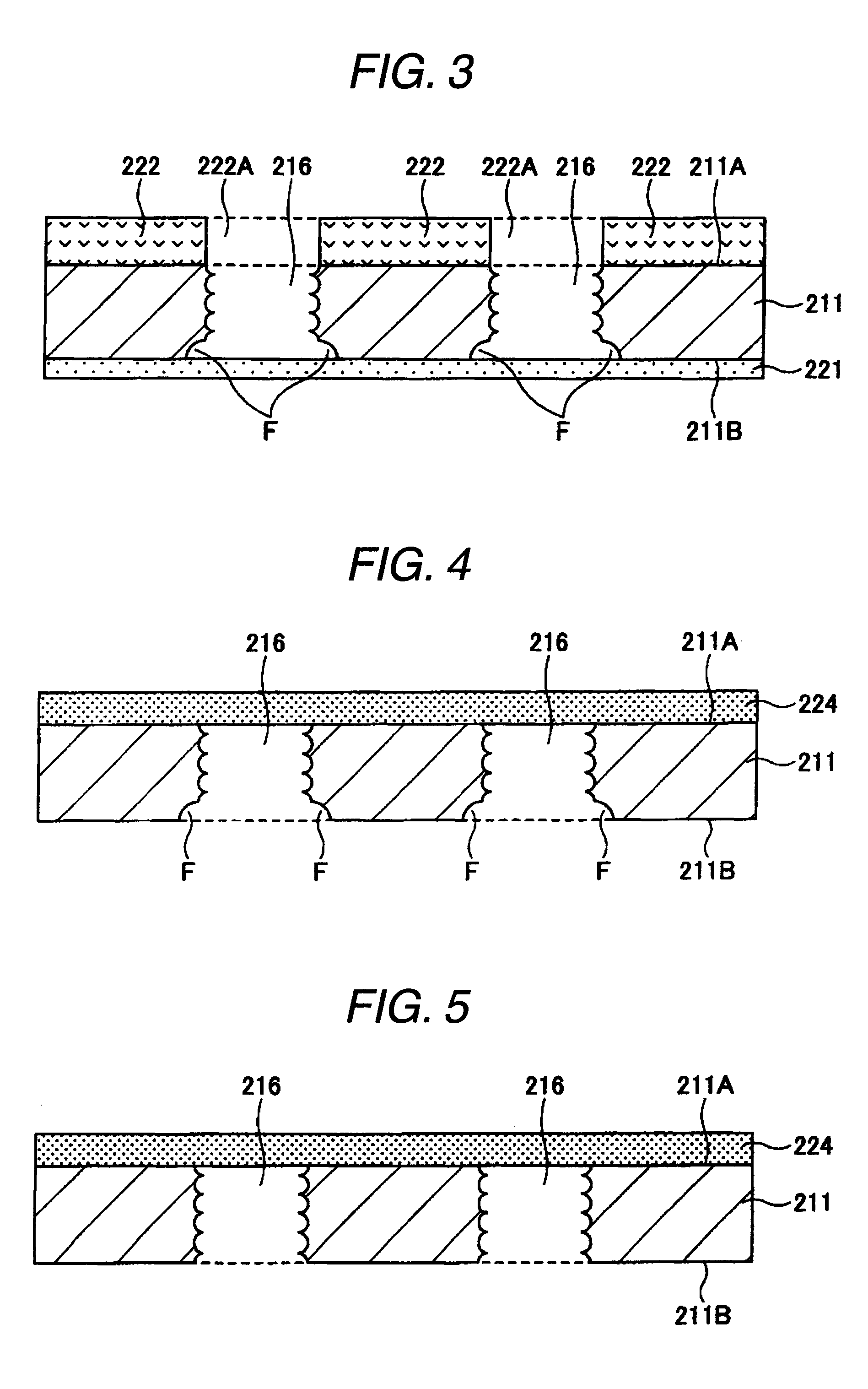

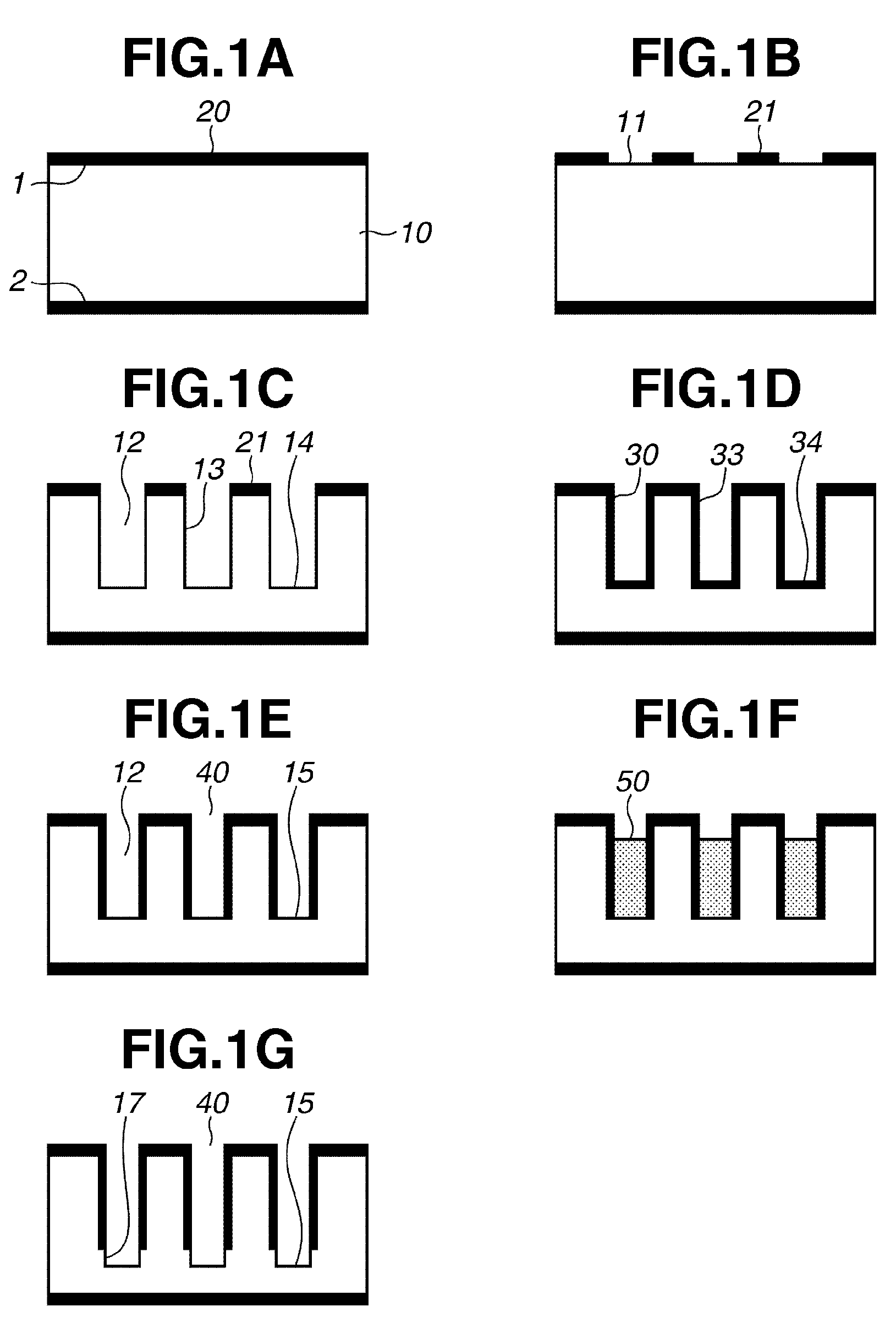

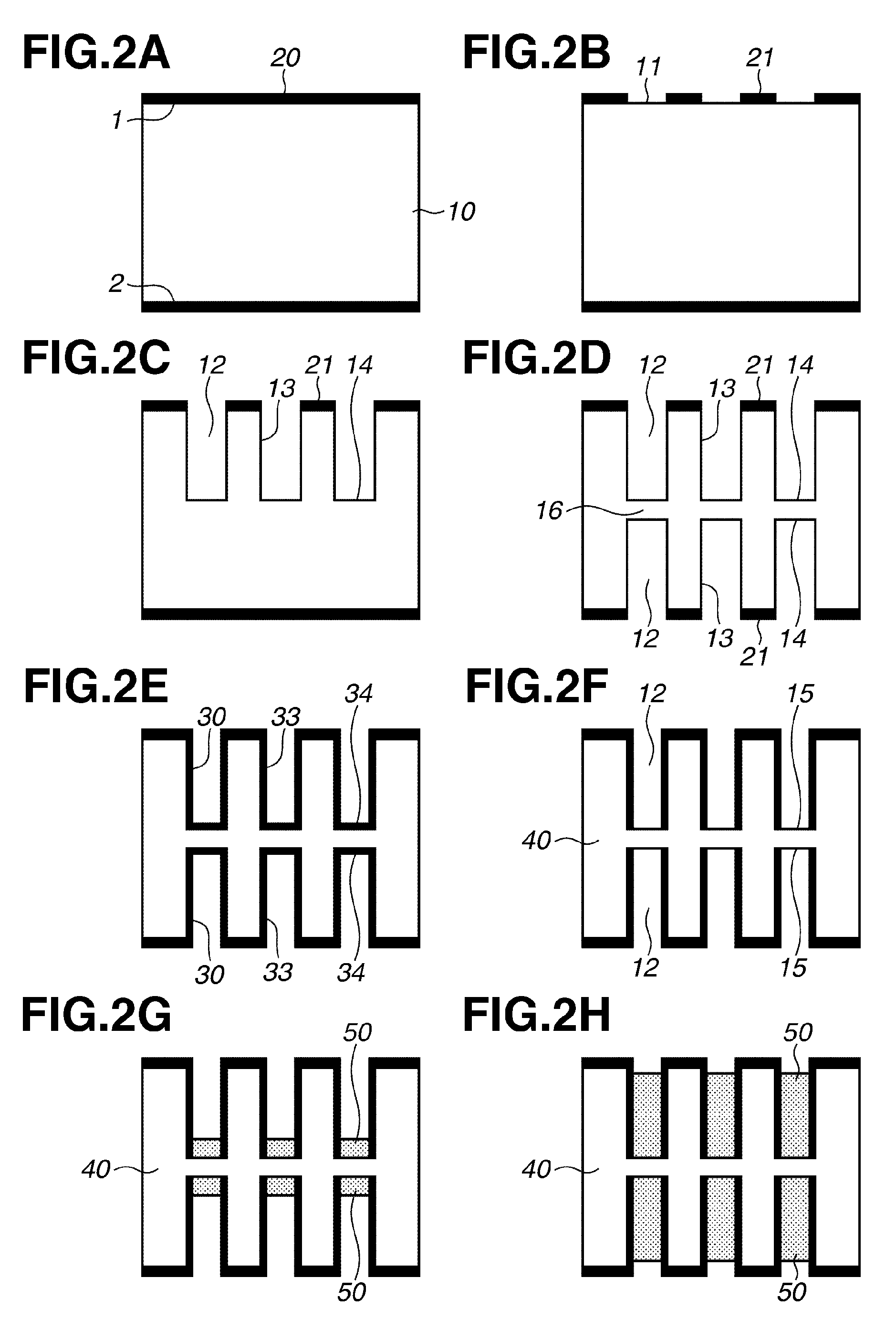

Method of manufacturing substrate

InactiveUS7795140B2Semiconductor/solid-state device detailsSolid-state devicesThermal oxideElectrode

A method of manufacturing a substrate, includes: (a) forming the through hole by etching the silicon substrate from a first surface of the silicon substrate by a Bosch process; (b) forming a thermal oxide film such that the thermal oxide film covers the first surface of the silicon substrate, a second surface of the silicon substrate opposite to the first surface, and a surface of the silicon substrate corresponding to a side surface of the through hole, by thermally oxidizing the silicon substrate where the through hole is formed; (c) removing the thermal oxide film; (d) forming an insulating film such that the insulating film covers the first and second surfaces of the silicon substrate and the surface of the silicon substrate corresponding to the side surface of the through hole; and (e) forming the through electrode in the through hole on which the insulating film is formed.

Owner:SHINKO ELECTRIC IND CO LTD

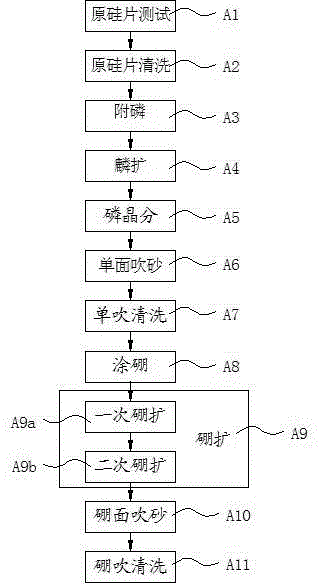

Manufacturing process of transient voltage suppression diode chip

ActiveCN103606521AStress reliefReduce defectsSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringPhotoresist

The invention discloses a manufacturing process of a transient voltage suppression diode chip. The manufacturing process of the transient voltage suppression diode chip includes two production processes: a diffusion process and a GPP process. The steps of the diffusion process include original silicon wafer testing, original silicon wafer washing, phosphorus attachment, phosphorus diffusion, phosphorus wafer separation, single side sand blasting, single blasting washing, boron coating, boron diffusion, boron wafer separation, boron side sand blasting, and boron blasting washing, wherein the step of boron diffusion comprises primary boron diffusion and secondary boron diffusion; and the steps of the GPP process sequentially include oxidation, primary photoetching, groove etching, photoresist sintering, groove washing, SIPOS passive film formation, glassivation, secondary photoetching, surface etching, and nickel-gold plating. The manufacturing process of the transient voltage suppression diode chip in the invention reduces defects of the chip, enables voltage distribution to be relatively concentrated, and reduces reverse leakage current at the same time.

Owner:南通康芯半导体科技有限公司

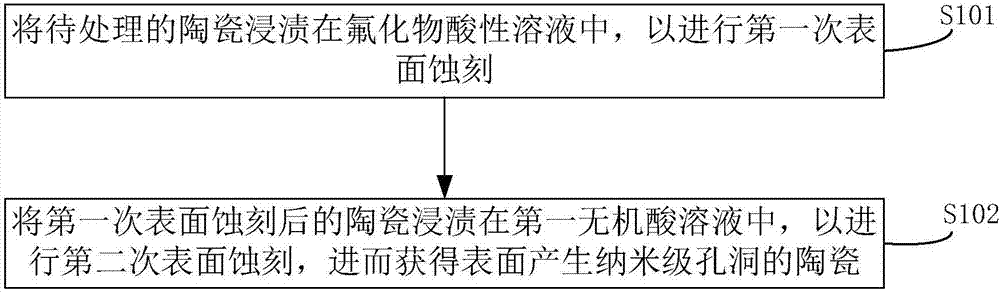

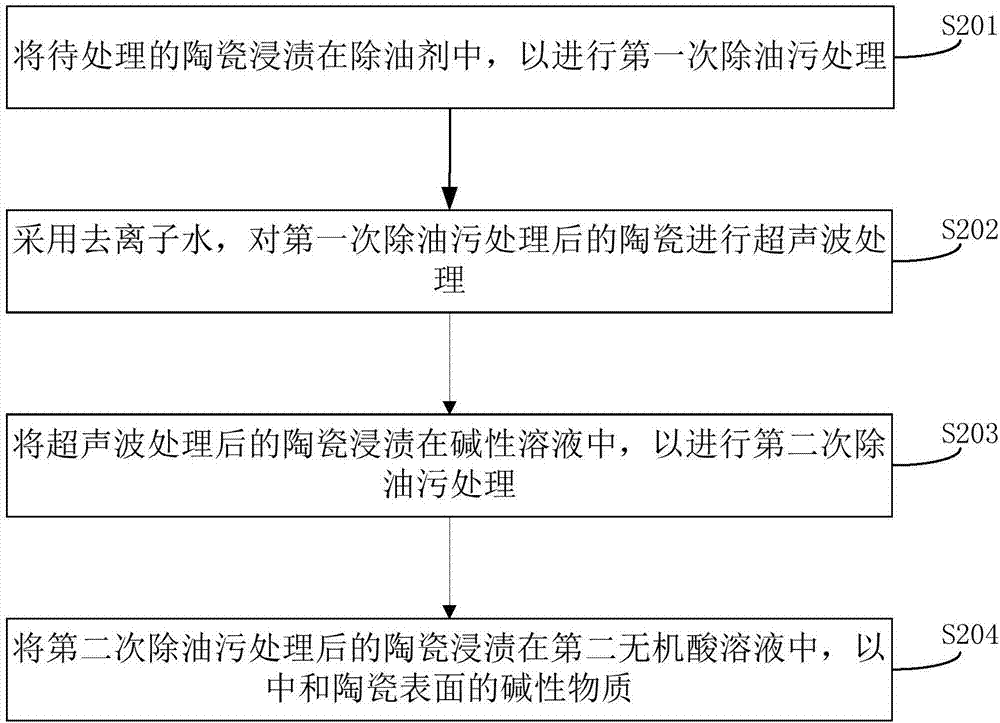

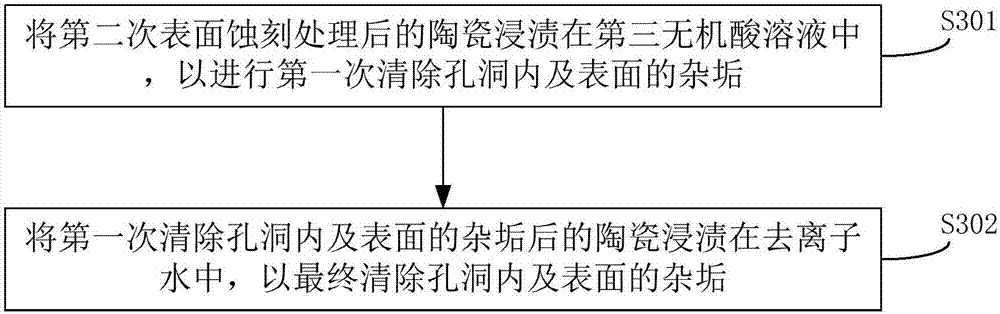

Ceramic surface treatment method, ceramic product and ceramic plastic composite body

ActiveCN107010998AImprove permeabilityPromote infiltrationCoatingsPlastic injection moldingInjection moulding

The invention discloses a ceramic surface treatment method, a ceramic product and a ceramic plastic composite body. The method comprises the following steps of soaking ceramic to be treated into a fluoride acid solution so as to perform primary surface etching; soaking the ceramic subjected to primary surface etching into a first inorganic acid solution so as to perform secondary surface etching; further obtaining the ceramic with nanometer level holes on the surface. By using the mode, the ceramic with the nanometer hole structures can be prepared; after the plastic injection molding forming, the bonding force of the product is high; the combination is very tight.

Owner:GUANGDONG EVERWIN PRECISION TECH

Durable super-hydrophilic or super-hydrophobic plastic surface and preparation method thereof

InactiveCN109251345AWill not melt and deformPlay a protective effectCoatingsSilica particleLaser etching

The invention discloses a durable super-hydrophilic or super-hydrophobic plastic surface and a preparation method thereof. The method comprises the following steps of: (1) etching a micron-scale structure on the surface of a plastic substrate by using a laser etching instrument, and then cleaning and drying the etched plastic substrate; (2) preparing hydrophilic or hydrophobic modified nano-silica; (3) coating the surface of the dried plastic substrate obtained in the Step (1) with a prepared a colloidal solution of a bonding layer, drying, and then coating with a hydrophilic or hydrophobic modified nano-silica particle solution, and drying to obtain the durable super-hydrophilic or super-hydrophobic plastic surface. The preparation method of the invention is carried out at a low temperature, which ensures that the plastic substrate will not be molten or deform and guarantees the durability of the super-hydrophilic or super-hydrophobic plastic surface. The preparation method has a goodindustrial application prospect.

Owner:SOUTH CHINA UNIV OF TECH

Impact-damage-resistant glass sheet

ActiveUS8889254B2Increased and more consistent resistanceImprove flexural strengthSynthetic resin layered productsRecord information storageGlass coverFlexural modulus

Impact-damage-resistant glass sheet comprising at least one chemically etched surface in combination with a tempering surface compression layer, the glass sheet exhibiting a high standardized ball drop failure height and a high flexural modulus of rupture strength, useful to provide damage-resistant glass cover sheets for consumer electronic video display devices, is provided by subjecting thin glass sheet to a combination of a surface tempering treatment and a surface etching treatment that improves strength while maintaining the optical glass sheet properties required for video display applications.

Owner:CORNING INC

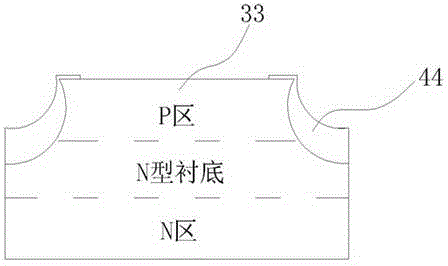

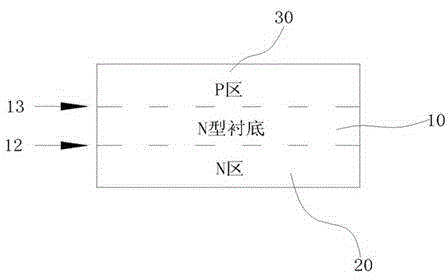

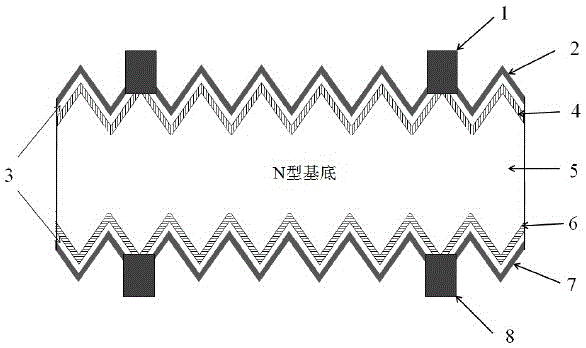

Double-sided N-type crystalline silicon cell and preparation method thereof

InactiveCN105047742AIncrease the open circuit voltageImprove current efficiencyFinal product manufacturePhotovoltaic energy generationChemical solutionBack surface field

The invention discloses a double-sided N-type crystalline silicon cell comprising a front AgAl electrode, a front antireflection film, a boron emitter passivation layer, a boron emitter p+ layer, an N-type silicon wafer, a phosphorus diffusion n+ back surface field layer, a back passivation layer, a back antireflection film, and a back Ag electrode. The front and the back of the cell are textured surfaces, and both sides can receive light and generate electricity. The boron emitter passivation layer and the back passivation layer are prepared at the same time by growing SiO2 layers through thermal oxidation in a low-temperature dry method, which reduces the interface-state density and the rate of interface recombination. A laminated film composed of a borosilicate glass layer and a silicon nitride layer formed in the diffusion process is used as a boron emitter protection layer. Therefore, boron diffusion surface etching and phosphorous diffusion cross contamination caused by chemical solution are prevented effectively, multiple times of etching and mask deposition in the process are reduced, and the technological process is simplified.

Owner:中国东方电气集团有限公司

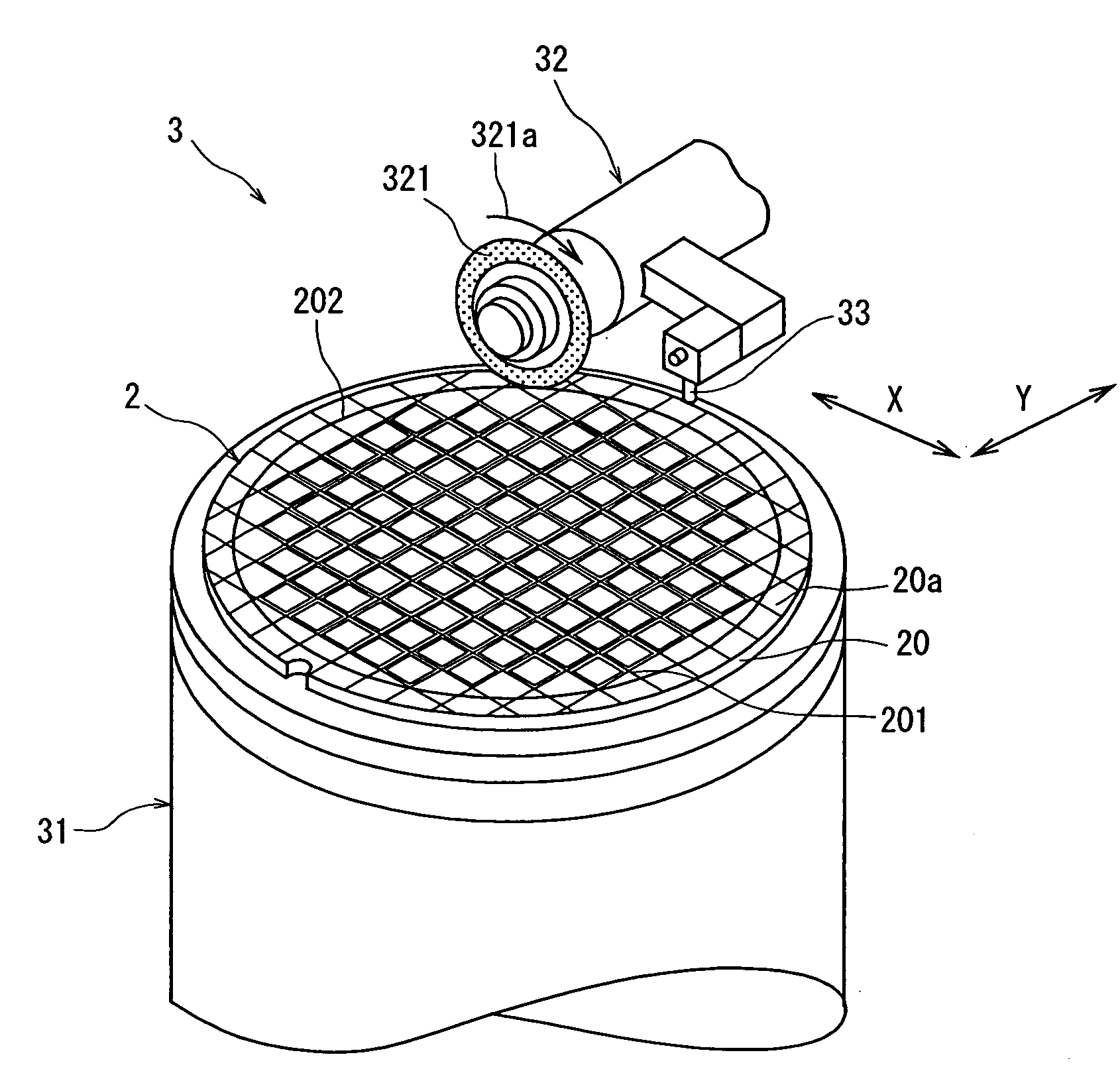

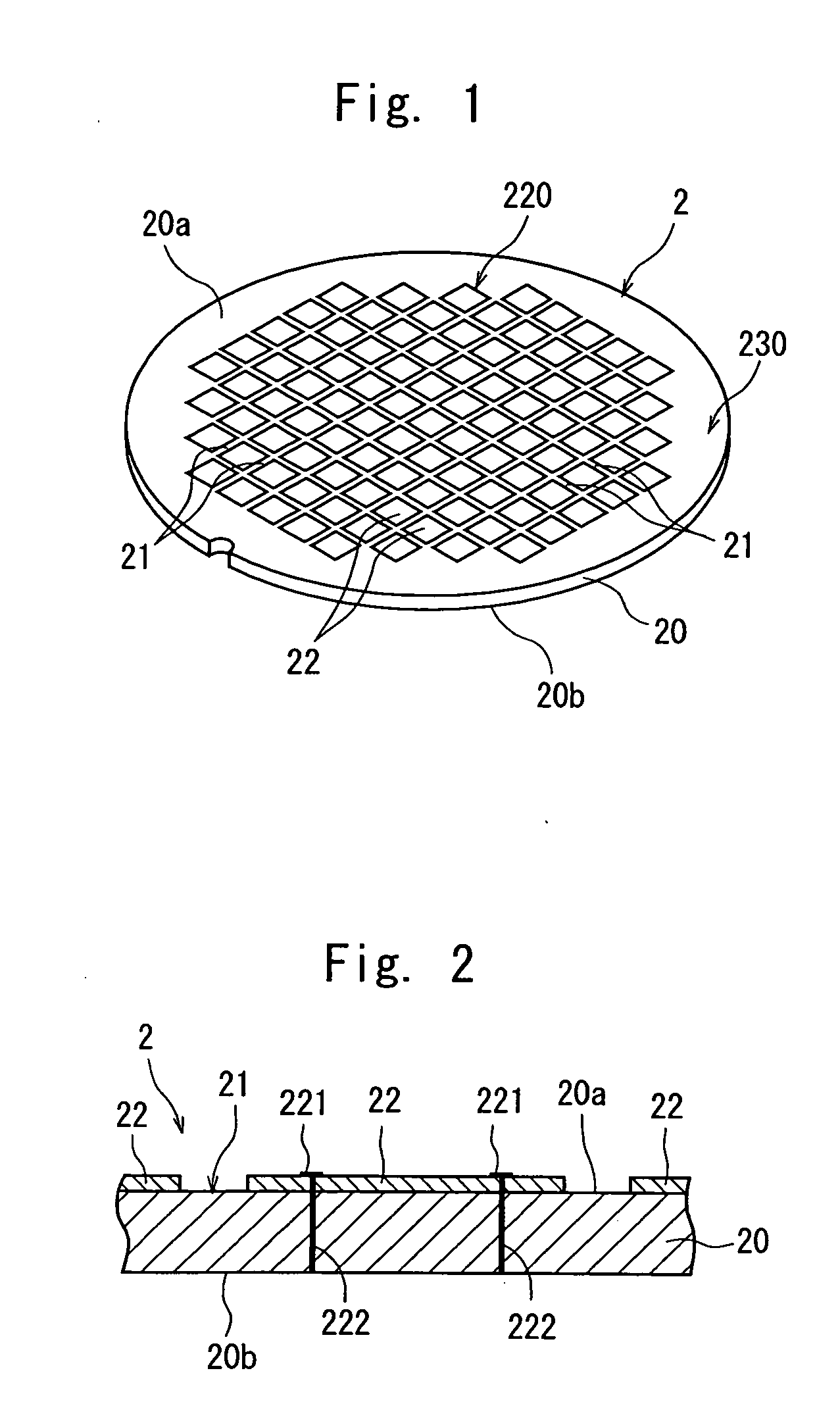

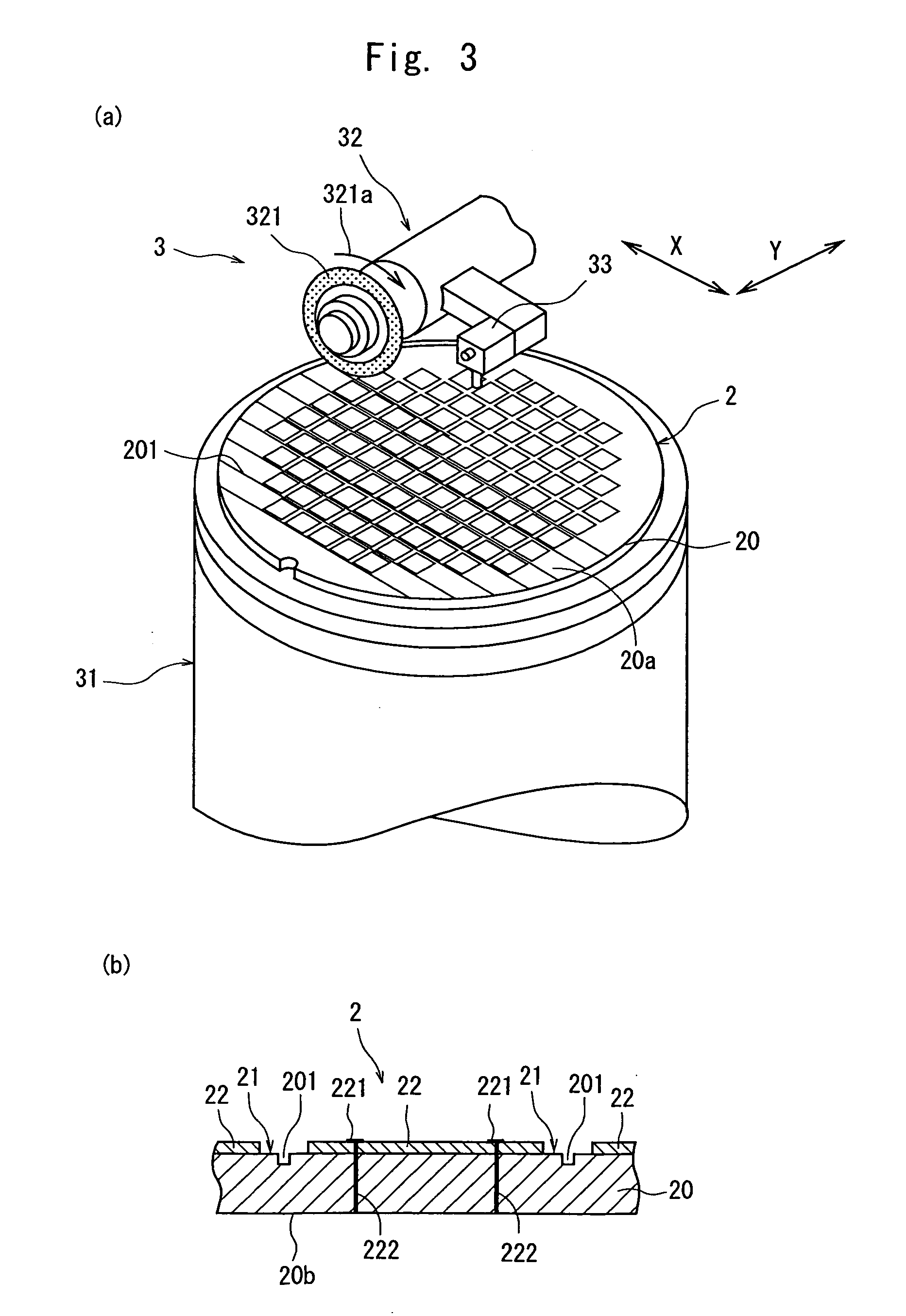

Wafer processing method

ActiveUS20090042368A1Improve bending strengthEasy to carrySemiconductor/solid-state device manufacturingEngineeringSurface grinding

A wafer processing method for dividing, along streets, a wafer having a device area where devices are formed in a plurality of areas sectioned by the plurality of streets arranged in a lattice pattern on the front surface of a substrate and a peripheral extra area and comprising electrodes which are embedded in the substrate of the device area, comprising a dividing groove forming step for forming dividing grooves having a depth corresponding to the final thickness of each device along the streets; an annular groove forming step for forming an annular groove having a depth corresponding to the final thickness of each device along the boundary between the device area and the peripheral extra area; a protective member affixing step for affixing a protective member to the front surface of the wafer; a rear surface grinding step for grinding a rear surface corresponding to the device area of the substrate of the wafer to expose the dividing grooves and the annular groove to the rear surface of the substrate of the wafer and form an annular reinforcing portion in an area corresponding to the peripheral extra area; and a rear surface etching step for etching the rear surface of the substrate of the wafer to project the electrodes from the rear surface of the substrate.

Owner:DISCO CORP

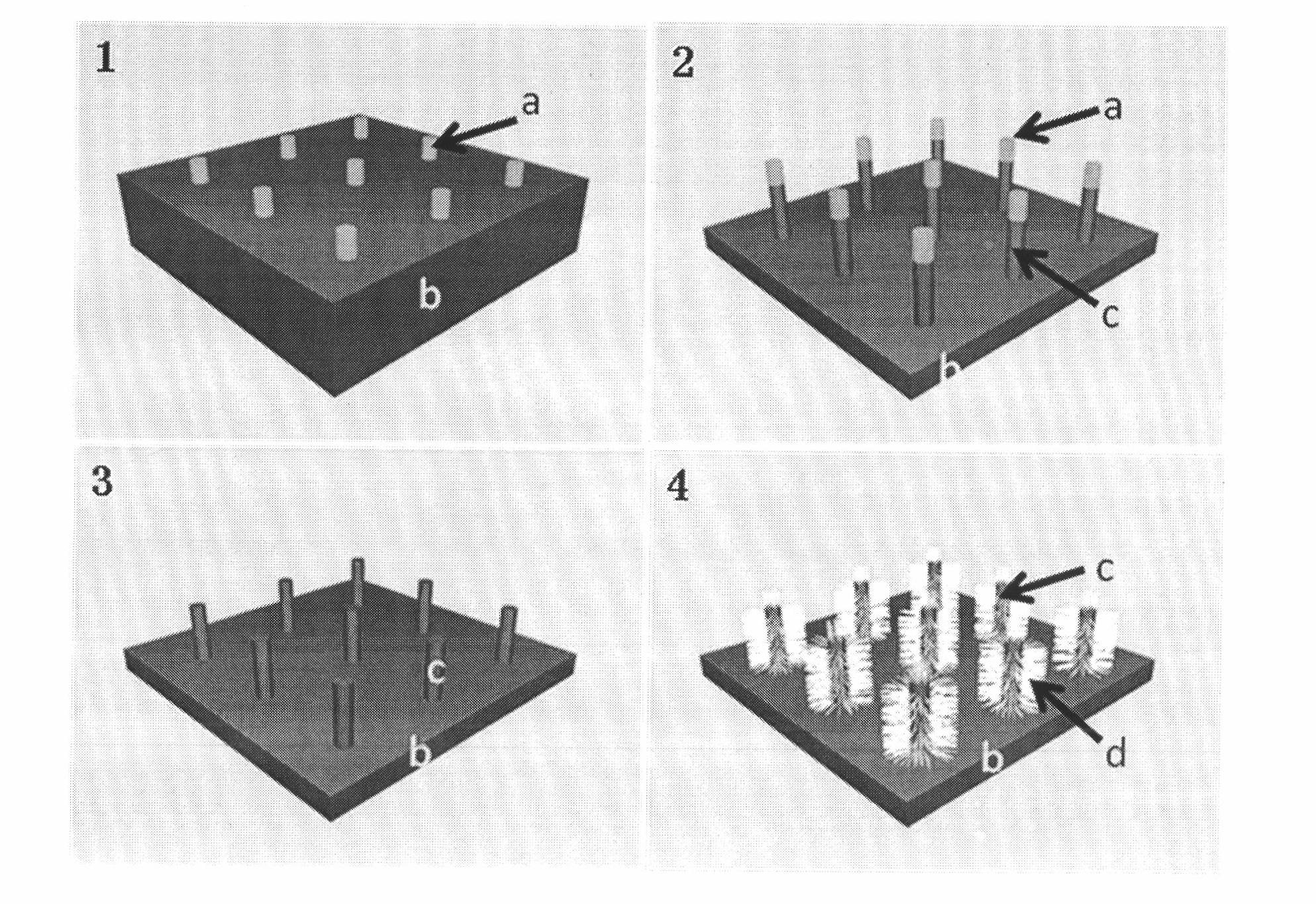

Preparation method of super-hydrophobic surface

InactiveCN102553812AGood mechanical propertiesNot easy to damagePolycrystalline material growthFrom normal temperature solutionsProtein secondary structureOptoelectronics

The invention discloses a method for preparing a super-hydrophobic surface on a surface of a random high molecular material, particularly a high molecular membrane material. The method comprises preparing a cylindrical array first stage structure on the surface of a random high molecular substrate by using a method of surface etching, wherein the cylindrical array is made of a material same as the material of the substrate; further depositing a zinc oxide seeding layer on the surface of the cylindrical array first stage structure; afterwards putting the substrate into a growth liquid in a growing zinc oxide nano-line array, then a second stage structure of the growing zinc oxide nano-line array grows from the surface of the first stage structure; dipping the high molecular substrate prepared with the first and the second stage structures into a solution with hydrophobic substances; after the surfaces of the first and second stage structures of the high molecular substrate are materialized together with the hydrophobic substances, taking out the high molecular substrate, and drying to obtain the desired super-hydrophobic surface.

Owner:LANZHOU UNIVERSITY

Microstructure manufacturing method

ActiveUS20110168908A1Easy to manufactureHigh precisionMaterial analysis using wave/particle radiationSolid-state devicesMicrostructure fabricationMetal

A microstructure manufacturing method includes forming a first insulating film on an Si substrate, exposing an Si surface by removing a part of the first insulating film, forming a recessed portion by etching the Si substrate from the exposed Si surface, forming a second insulating film on a sidewall and a bottom of the recessed portion, forming an Si exposed surface by removing at least a part of the second insulating film formed on the bottom of the recessed portion, and filling the recessed portion with a metal from the Si exposed surface by electrolytic plating.

Owner:CANON KK

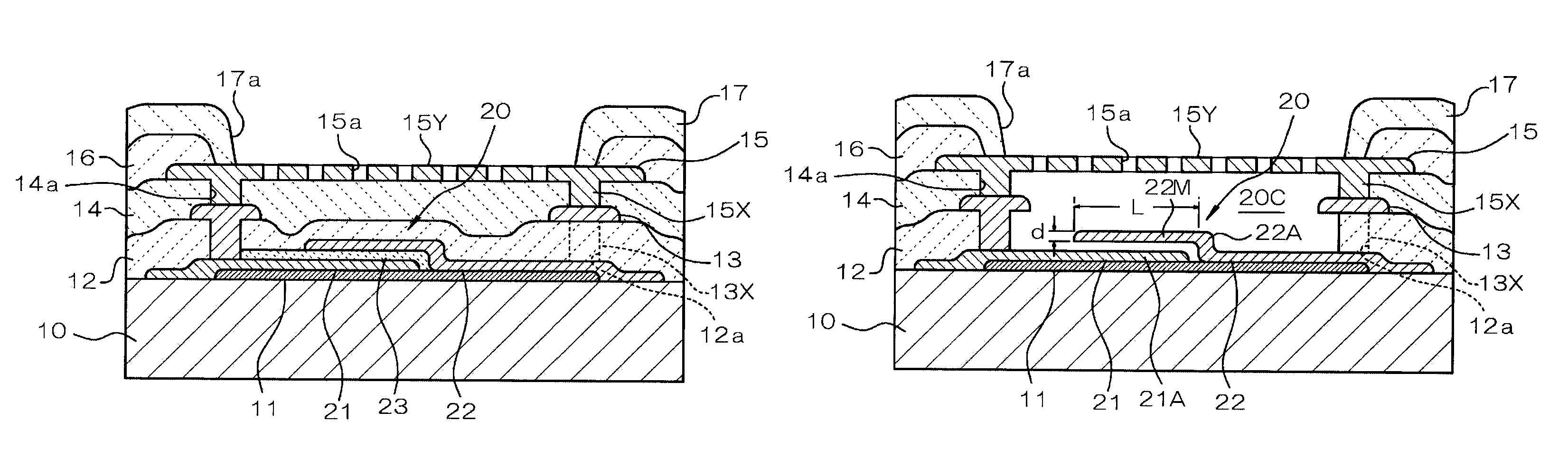

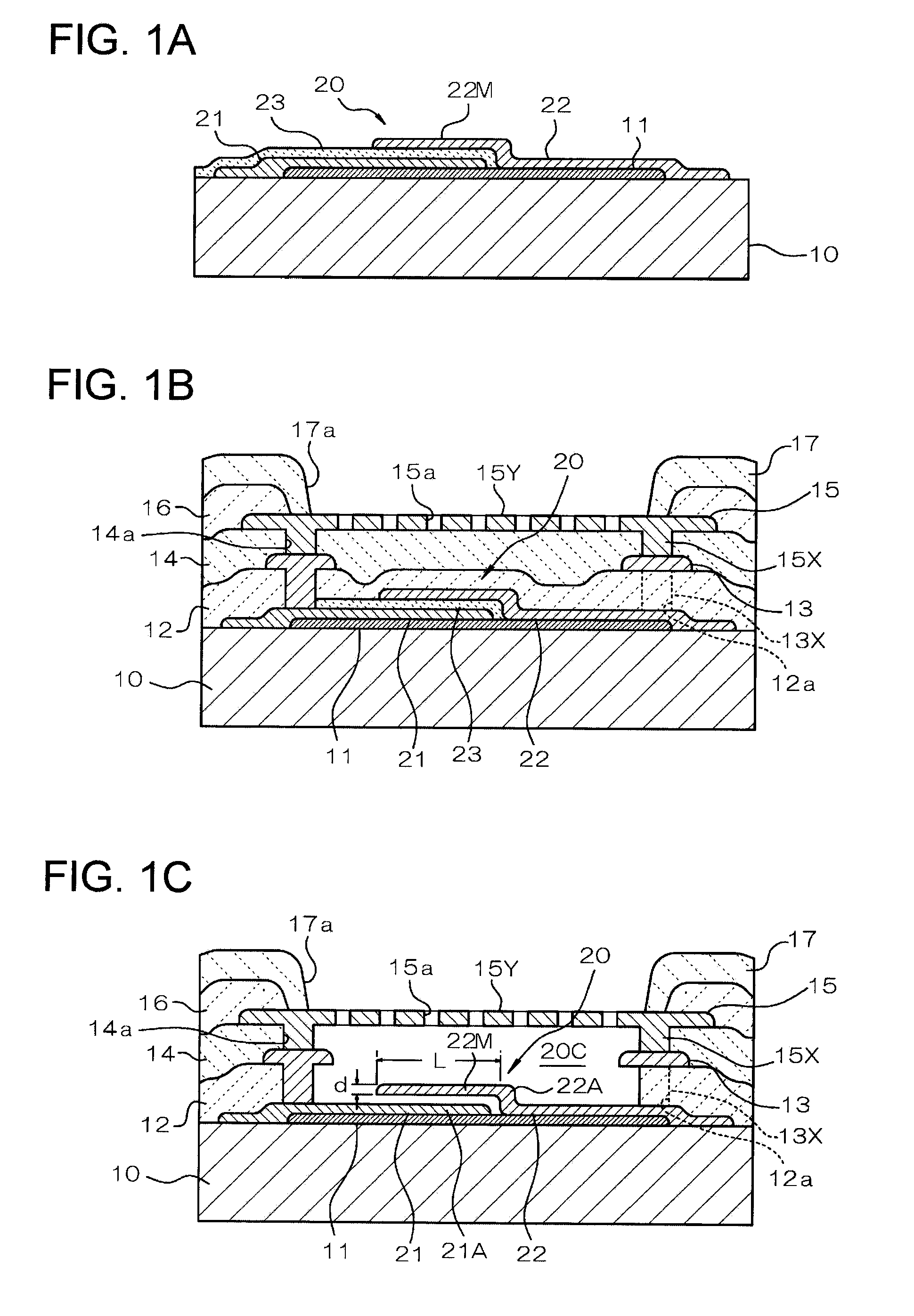

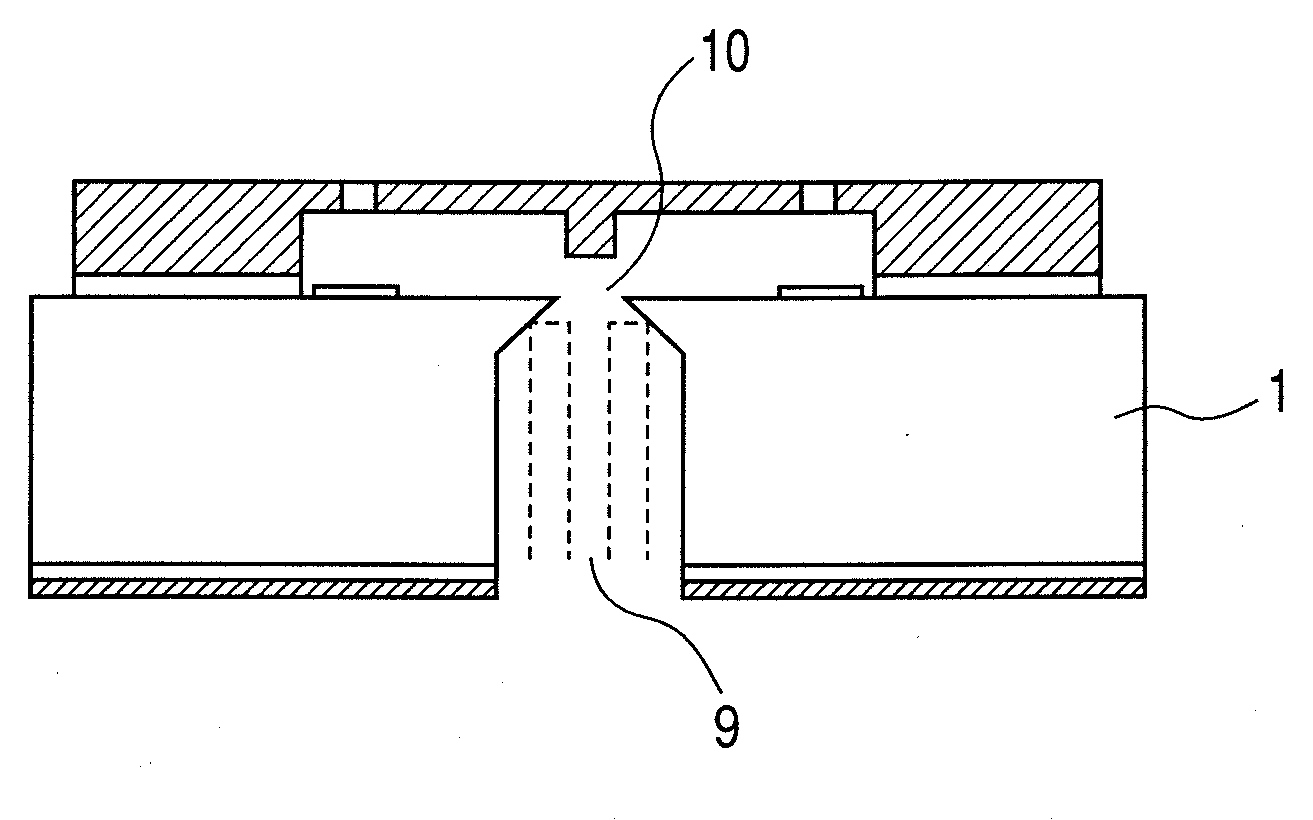

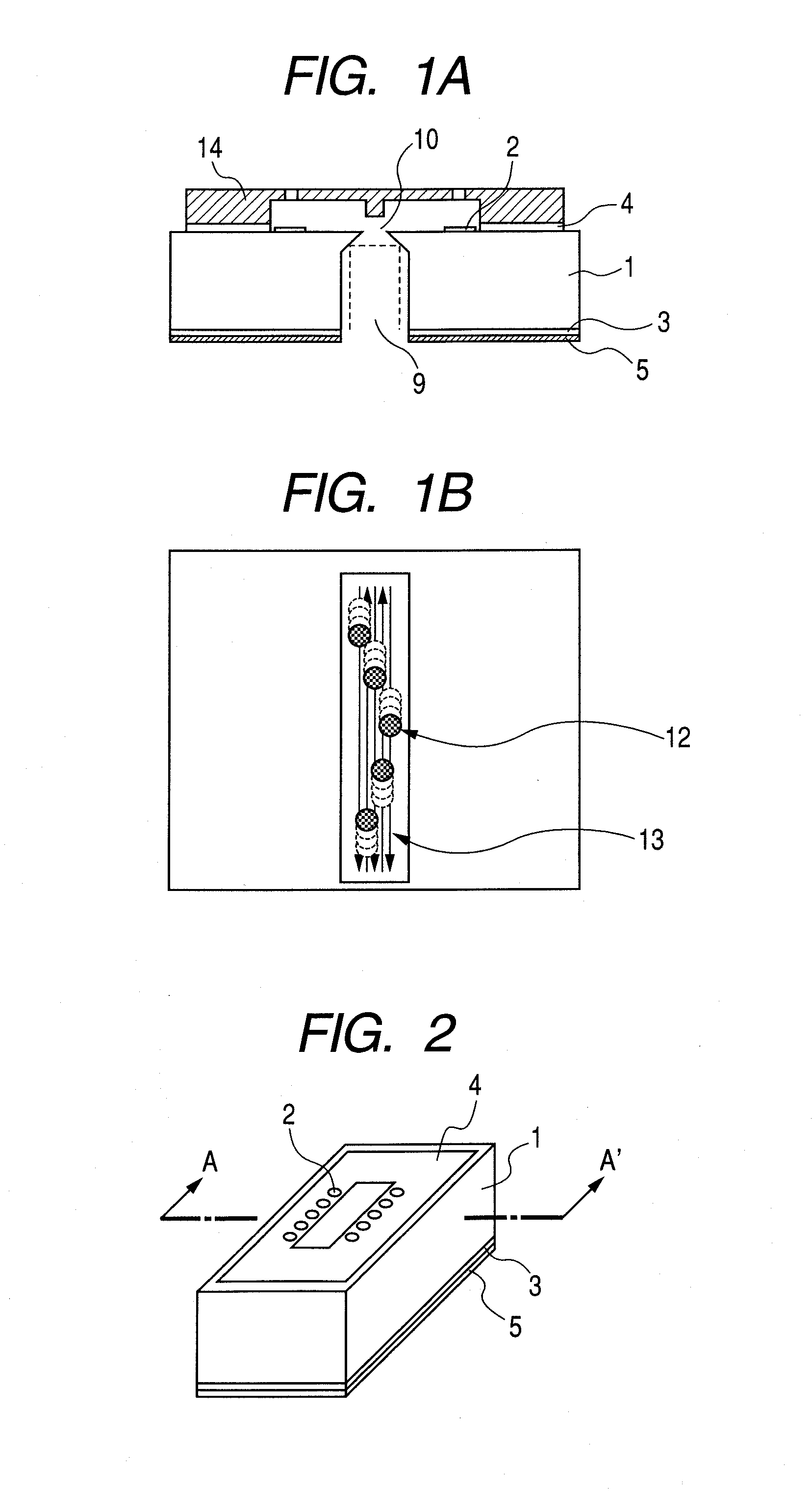

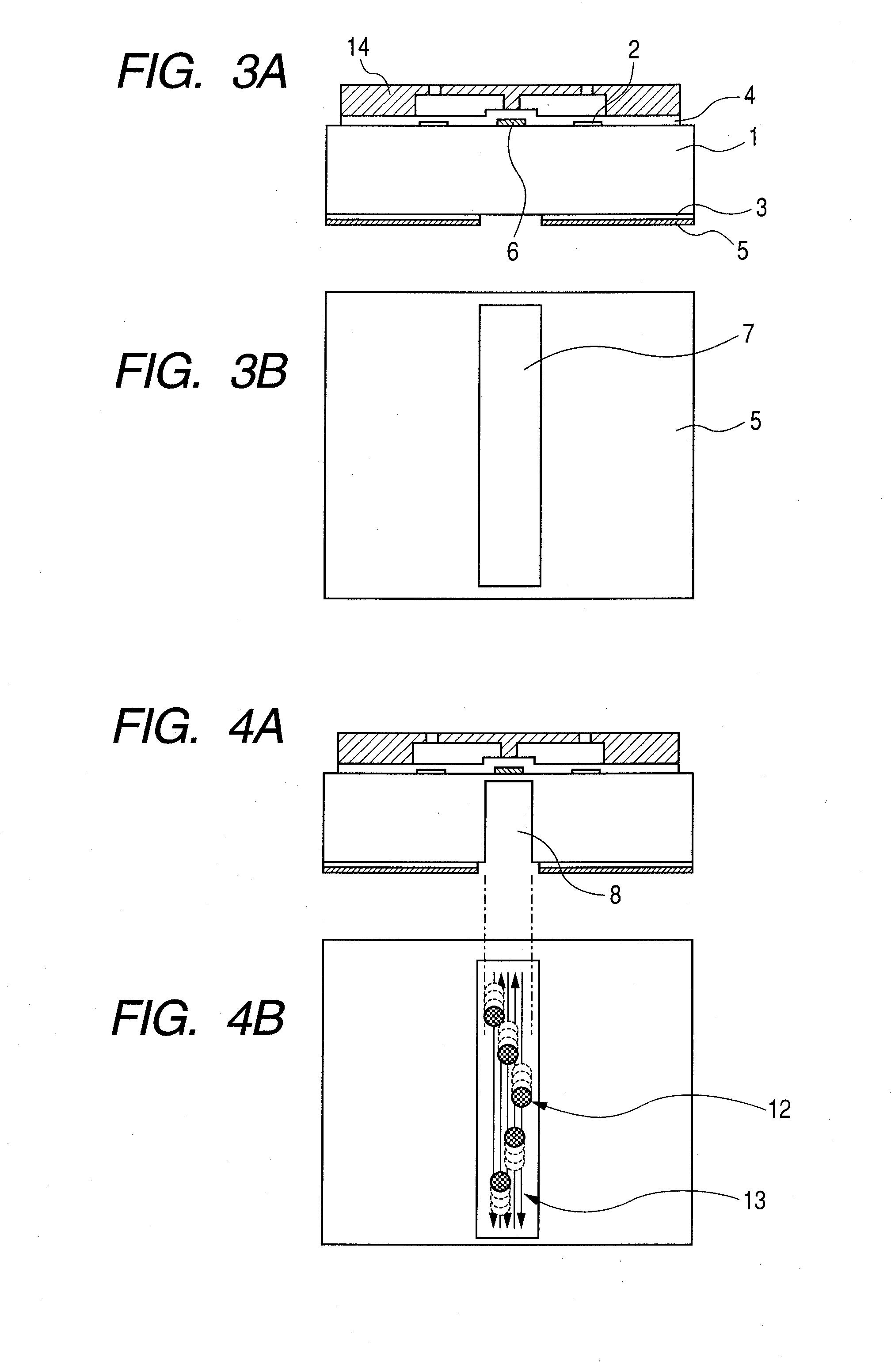

Method of manufacturing MEMS device

InactiveUS8026120B2Great advantageReduce stepsImpedence networksSemiconductor/solid-state device manufacturingGas phaseEngineering

A method of manufacturing an MEMS device includes: forming a covering structure having an MEMS structure and a hollow portion, which is located on a periphery of the MEMS structure and is opened to an outside, on a substrate; and performing surface etching for the MEMS structure in a gas phase by supplying an etching gas to the periphery of the MEMS structure from the outside.

Owner:SEIKO EPSON CORP

Semiconductor Devices and Methods of Forming Thereof

ActiveUS20140264651A1Decorative surface effectsSemiconductor/solid-state device manufacturingEngineeringSemiconductor

In accordance with an embodiment of the present invention, a method of forming a semiconductor device includes forming a sacrificial layer over a first surface of a workpiece having the first surface and an opposite second surface. A membrane is formed over the sacrificial layer. A through hole is etched through the workpiece from the second surface to expose a surface of the sacrificial layer. At least a portion of the sacrificial layer is removed from the second surface to form a cavity under the membrane. The cavity is aligned with the membrane.

Owner:INFINEON TECH AG

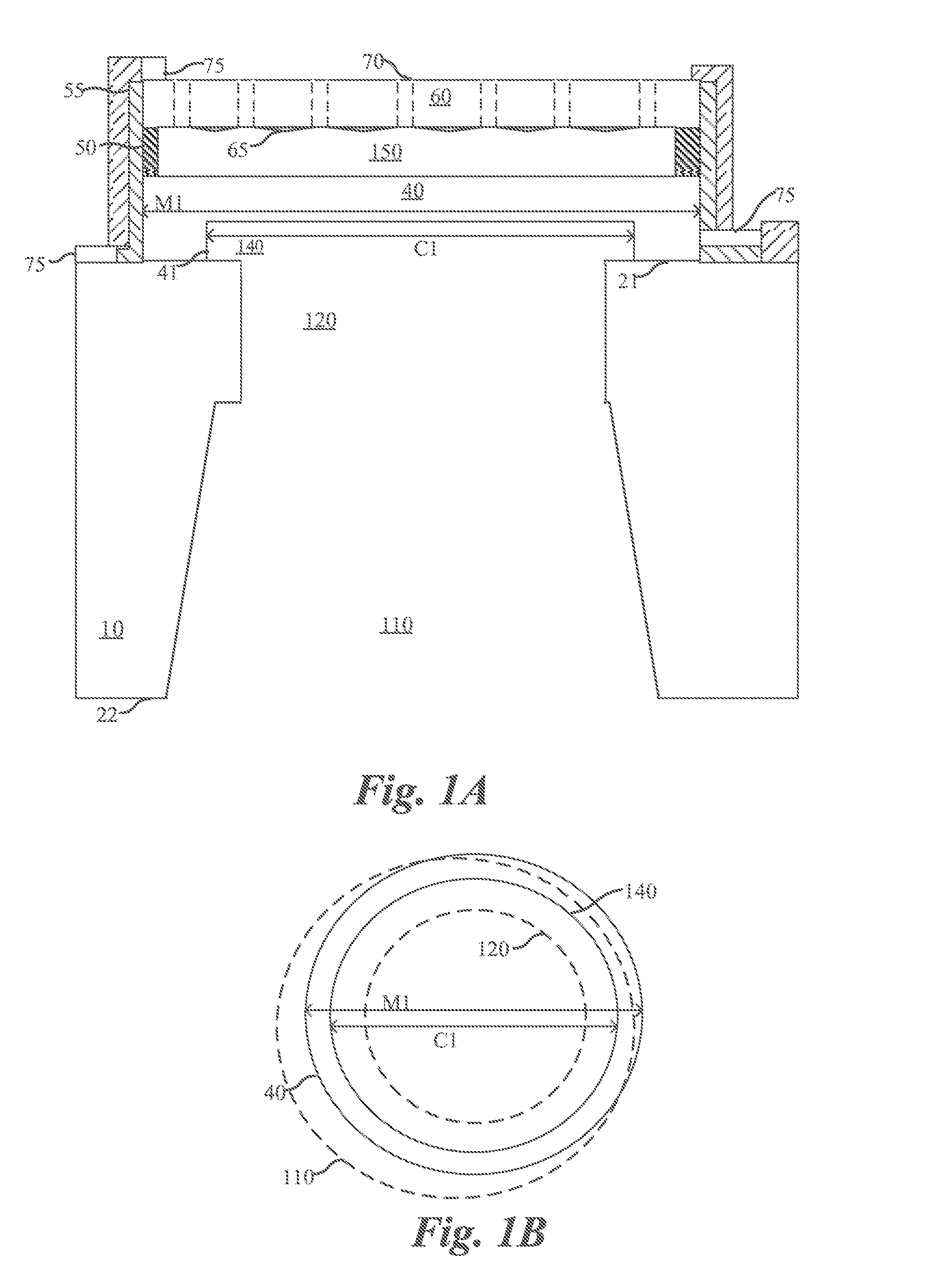

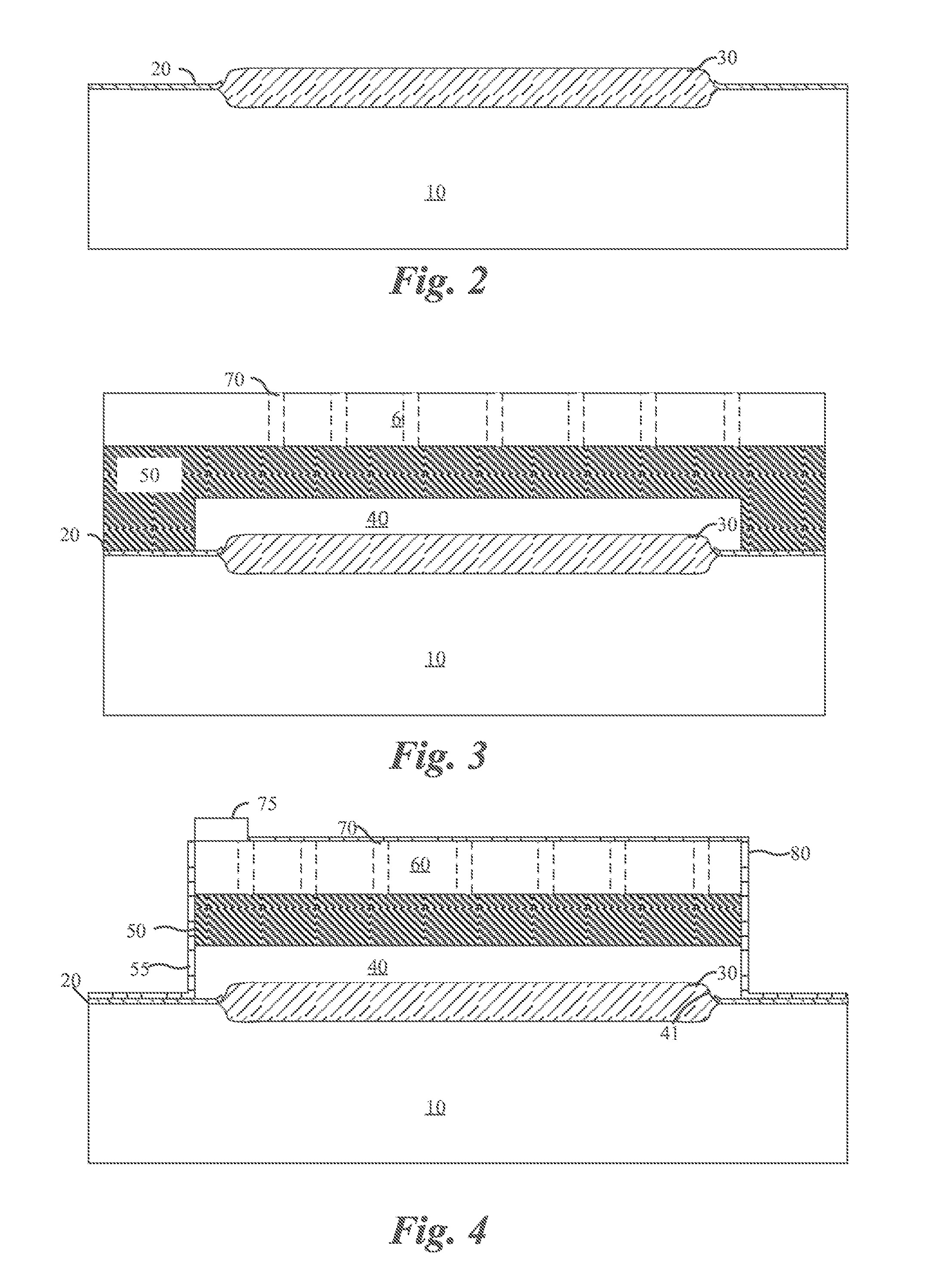

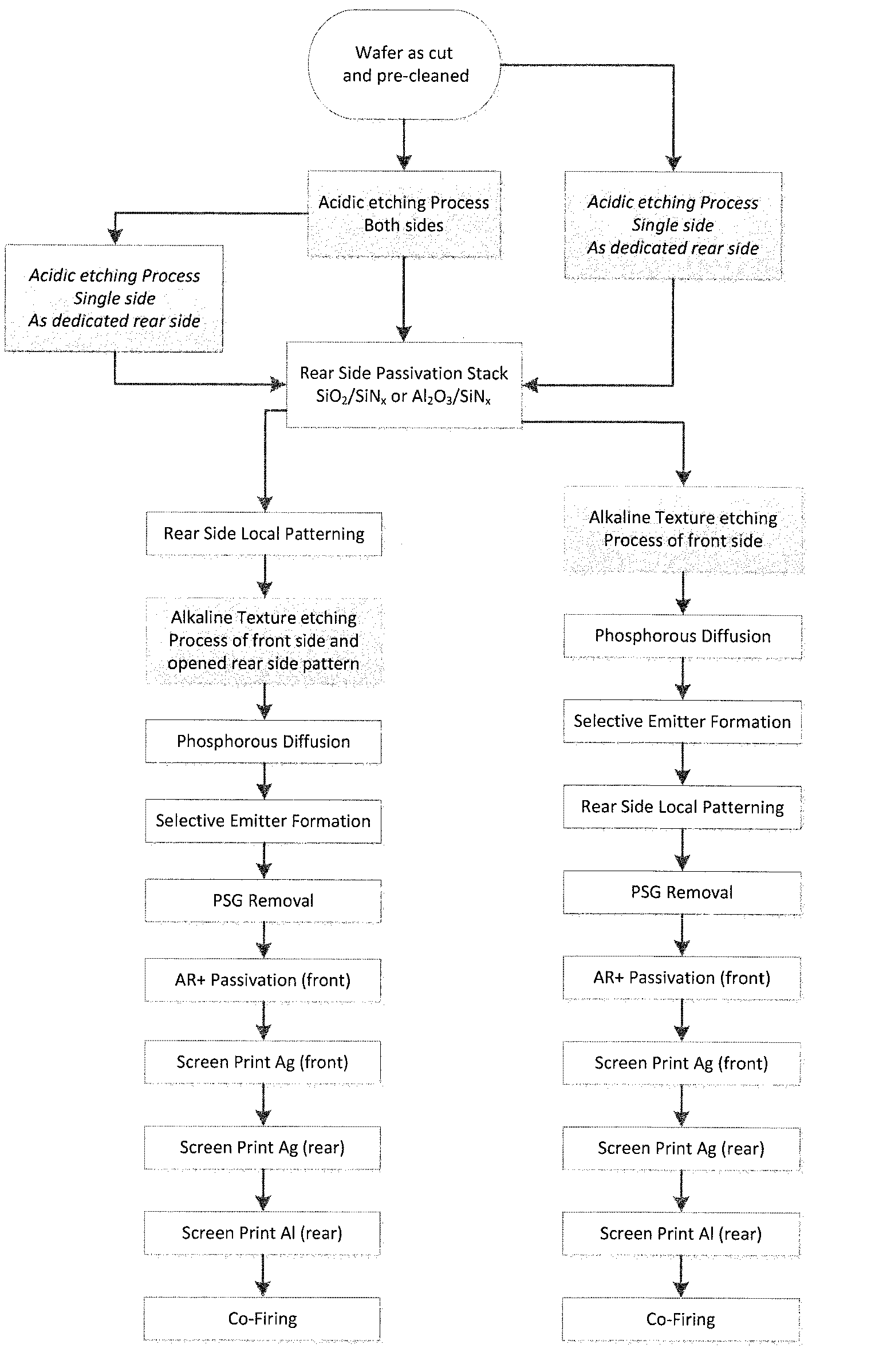

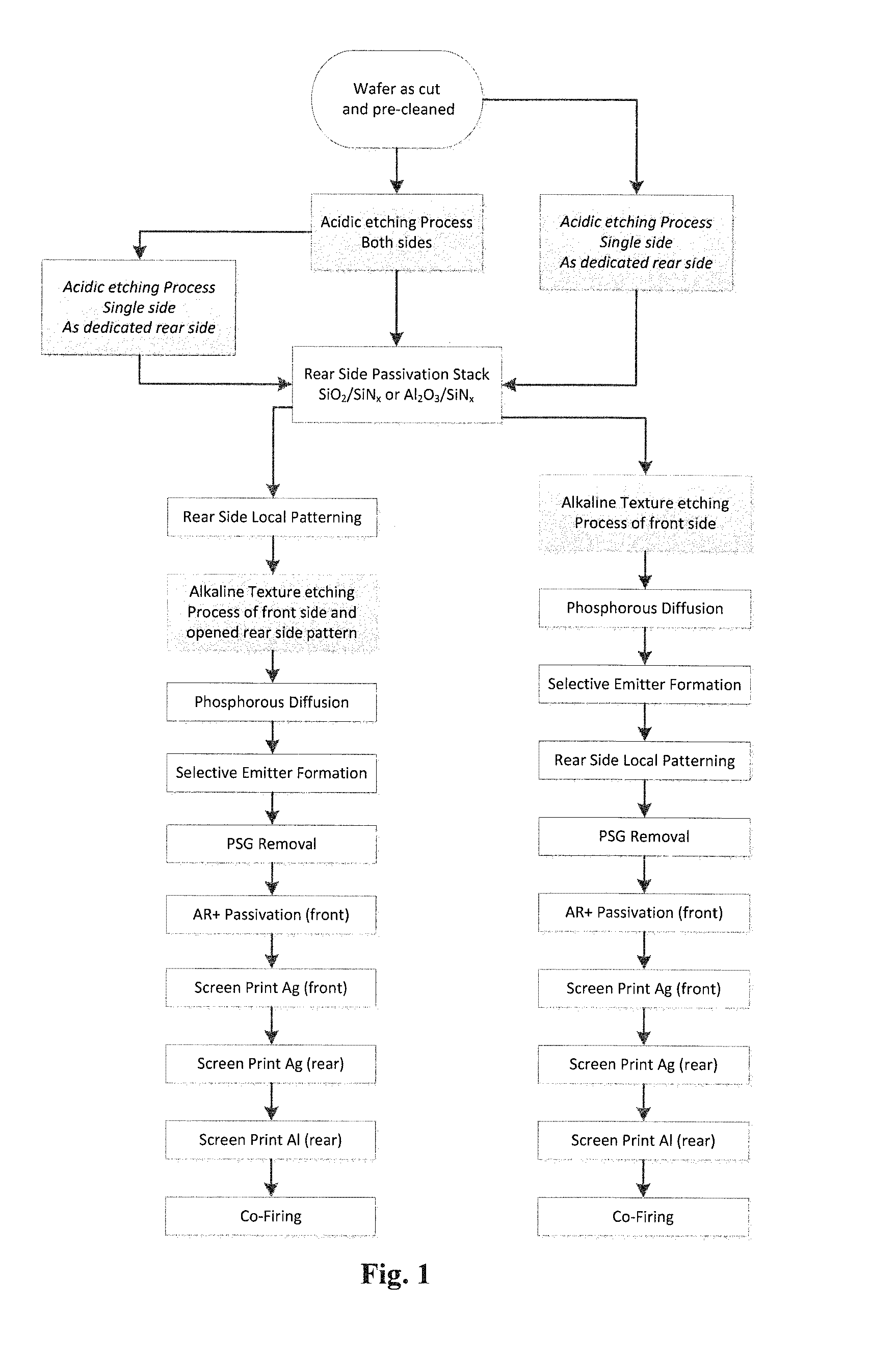

Acidic etching process for si wafers

InactiveUS20150040983A1Improve effectivenessControl roughnessFinal product manufactureSemiconductor/solid-state device detailsAlkaline etchingSilicon

The present invention relates to a method for acidic surface etching of a silicon wafer, such as those used for solar cells, comprising contacting at least one surface of a silicon wafer as cut with an acidic etching agent, provided that the wafer is, prior to the acidic etching, not subjected to an alkaline etching step or process. Further, the present invention is directed to Si wafer, photovoltaic cells, PERC photovoltaic cells and solar modules produced according to the method of the present invention.

Owner:SOLARWORLD AMERICAS

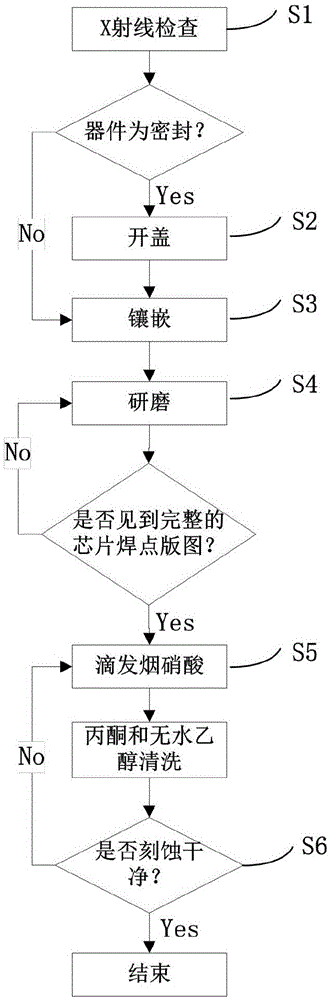

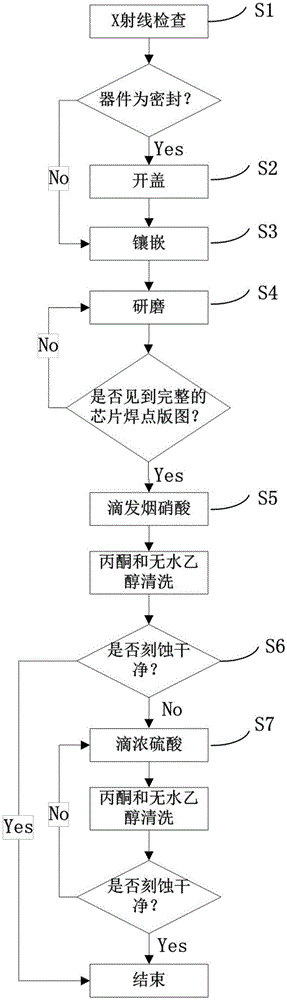

Unsealing method for flip-chip packaging device

InactiveCN105092326AReduce package sizeAccurately determinePreparing sample for investigationPlastic packagingX-ray

A related unsealing method for a flip-chip packaging device comprises the following steps: S100) performing X-ray detection on the device, so as to obtain a device X-ray photograph; S200) performing device inlaying; S300) performing grinding on the inlayed device by taking the X-ray photograph as a reference; S400) performing acid dropping and cleaning on the ground device; S500) performing microscope detection, returning to the step S400) is the chip surface residue is detected, and stopping until the chip surface etching is clean. The beneficial effects comprise that the method is applicable to all flip-chip packaging devices at present, and comprises sealing, ceramic packaging and plastic packaging; through X-ray detection, the chip welding spot layout is determined, the grinding ending point can be precisely determined, and insufficient grinding and excessive grinding are both avoided; and through the process of manually dropping an acid and performing microscope detection and dropping the acid again, the etching degree is strictly controlled, the unsealing quality is guaranteed, and the welding spots and boding spots of a chip are prevented from being automatically excessively corroded.

Owner:METROLOGY & MEASUREMENT CENT OF CHINA ACADEMY OF ENG PHYSICS

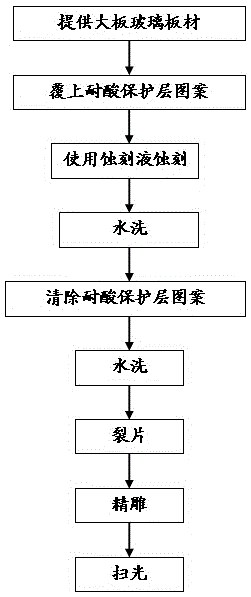

Manufacturing method of 3D (three-dimensional) glass plate

ActiveCN105152540AIncrease productivityImprove yield rateDecorative surface effectsTelephone set constructionsEngravingMetallurgy

The invention discloses a manufacturing method of a 3D (three-dimensional) glass plate. The manufacturing method includes the steps of S1, providing a large glass plate; S2, coating the large glass plate with an acid-resisting protective layer pattern; S3, etching a surface of the large glass plate with an acidic etchant, and etching the surface of the large glass plate to obtain a plurality of grooves; S4, performing washing with water; S5, removing the acid-resisting protective layer pattern from the surface of the large glass plate with an alkaline reagent; S6, performing washing with water; S7, splitting the large glass plate into a plurality of small glass plates, and providing the middle of each small glass plate with a recess; S8, using a CNC engraving and milling machine to engrave and mill a sidewall of the recess in one side of each small glass plate to form a curved surface, enabling smooth connection between the bottom of the recess and other parts of this surface of the small glass plate, using the CNC engraving and milling machine to engrave and mill the other side of the small glass plate to provide the edge of this surface of the small glass plate with an arc surface reversely curved; S9, using a brush-polishing machine to brush-polish the small glass plates. The manufacturing method of the 3D glass plate provided by the invention enables improvement of productivity and yield.

Owner:深圳市汇隆源科技有限公司

Electroplating method for double-side and multilayer flexible printed circuit board

ActiveCN102316677APoor improvementImprove yieldPrinted circuit manufactureCopper platingCompound (substance)

The invention provides an electroplating method for a double-side and multilayer flexible printed circuit board, which sequentially comprises the following steps of copper foil cutting, mechanical drilling of a first through hole, hole blackening, primary dry film pressing, primary exposure, primary development, pattern electroplating, chemical grinding, secondary dry film pressing, secondary exposure, secondary development, circuit etching and dry film removal. The pattern electroplating comprises the processes that a copper-clad plate is in contact with electroplating liquid, a copper layer is plated between positions without dry film coverage including the first through hole and circuit patterns, and the copper layer is not plated and covered on the surface of a circuit pattern without the dry film coverage. The circuit etching comprises the processes that the copper-clad plate is in contact with etching liquid, and the circuit patterns are etched onto the surface of the copper-clad plate. The electroplating method has the advantages that the circuit patterns are formed during the electroplating exposure, the copper plating is adopted between circuits so that products become hard, the products can be preferably protected, the folding crease is prevented, and the circuit defects can be obviously avoided. The method only adopts once dry film removal, the cost is reduced, the delivery speed is accelerated, simultaneously, the folding crease is also prevented, and the qualification rate of finished products is improved.

Owner:深圳市合力泰光电有限公司

Manufacture method of multilayer gradient nano-composite diamond film of surface of die steel

ActiveCN103160781AImprove bindingOvercome stressVacuum evaporation coatingSputtering coatingGas phaseBinding force

The invention discloses a manufacture method of a multilayer gradient nano-composite diamond film of the surface of die steel. The manufacture method includes that a plunger undergoing conventional pretreatment is arranged in a vacuum system of a magnetron sputtering composite vapor deposition system, and multiple layers of gradient films are sequentially deposited. Each layer of the multiple gradient transition layers undergoes high-temperature annealing treatment and argon ion surface etching treatment so as to improve binding force of the films and a base. The defects of high internal stress and poor adhesive force and the like of a conventional diamond film on the surface of the mold steel are overcome.

Owner:LANZHOU INST OF CHEM PHYSICS CHINESE ACAD OF SCI

Method of manufacturing substrate for liquid discharge head

InactiveUS20090065482A1Improve forming accuracyMiniaturizationRecording apparatusDecorative surface effectsLaser processingEngineering

Provided is a method of manufacturing a substrate for a liquid discharge head, the substrate including a silicon substrate with a liquid supply opening formed therein, the method including: forming one processed portion by laser processing on the substrate from one surface of the substrate; expanding the one processed portion to form a recess portion by performing laser processing at a position which overlaps a part of the one processed portion and does not overlap another part of the one processed portion; and etching from the one surface the substrate with the recess portion formed therein to form the liquid supply opening.

Owner:CANON KK

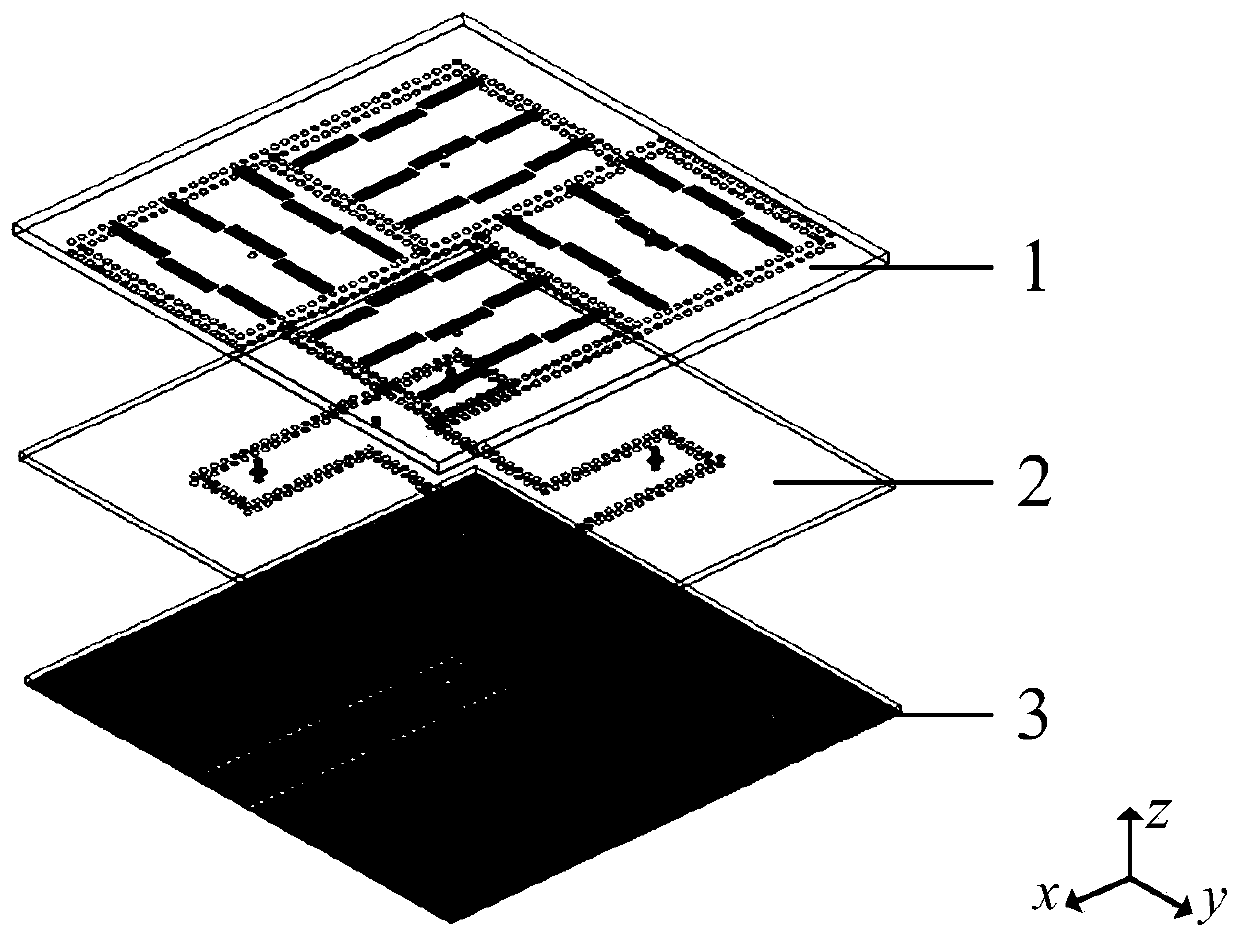

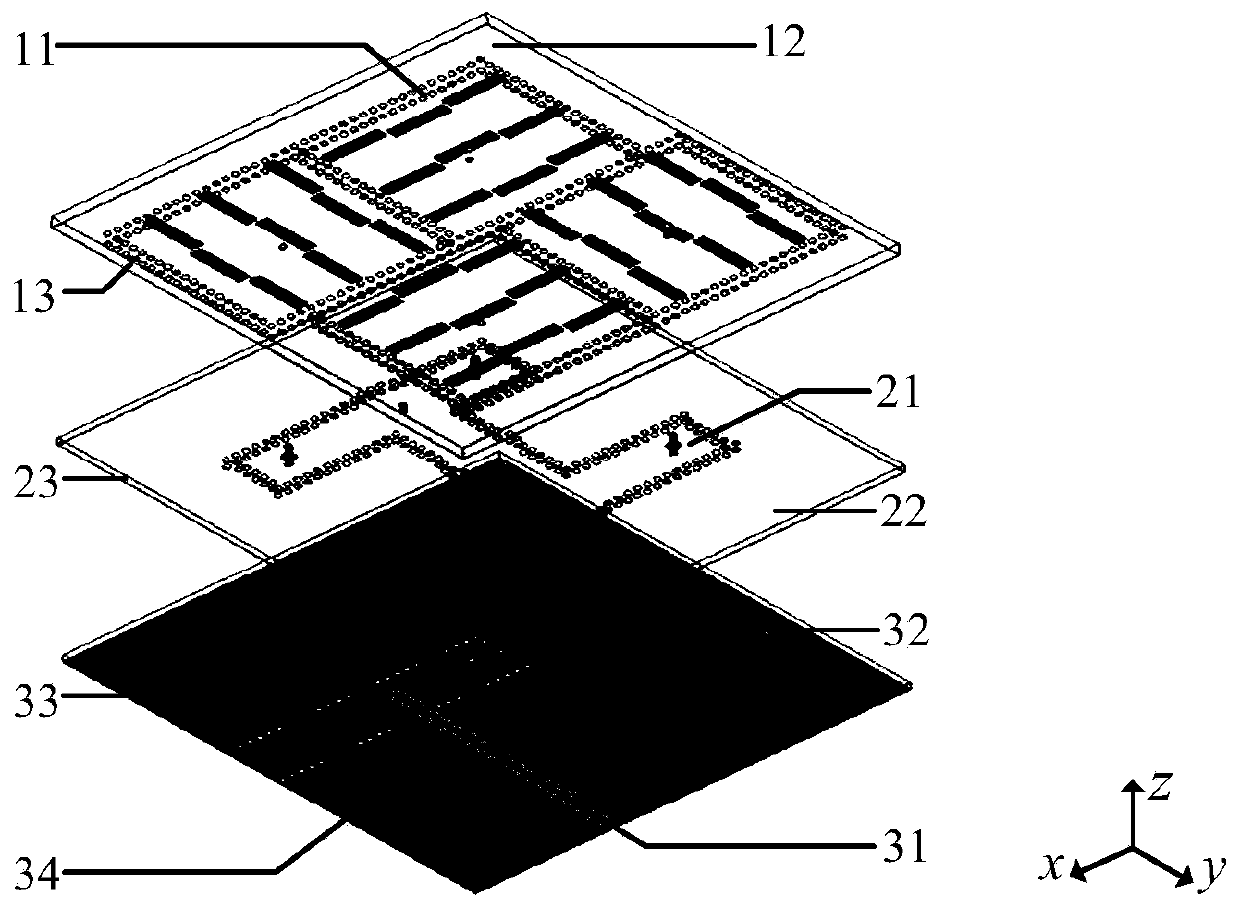

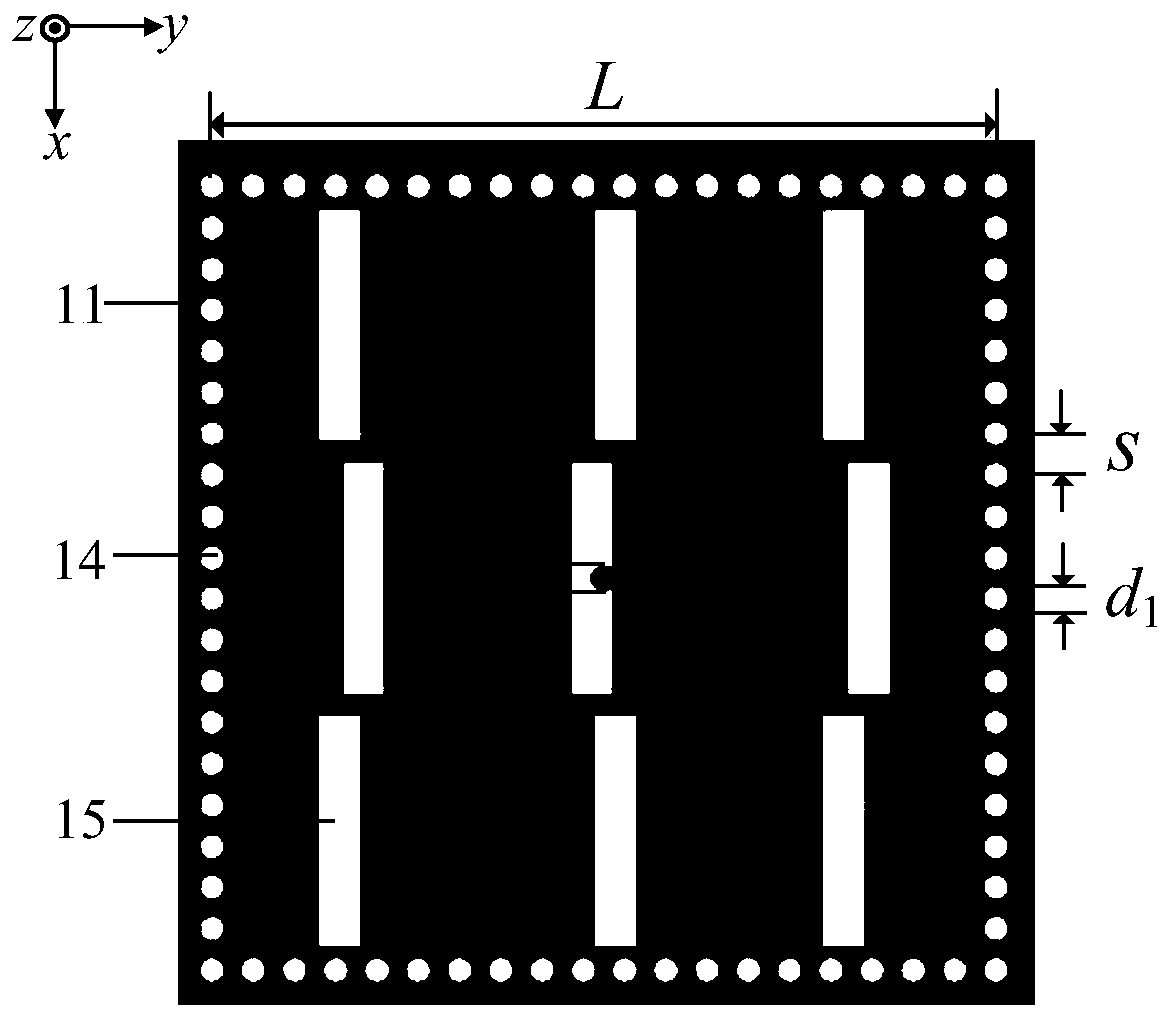

Back cavity gap circularly polarized millimeter wave antenna based on substrate integrated waveguide (SIW)

PendingCN110265787AOvercoming the technical problem of narrow axial ratio bandwidthImprove radiation efficiencyRadiating elements structural formsAntennas earthing switches associationResonant cavityDielectric plate

Disclosed is a back cavity gap circularly polarized millimeter wave antenna based on substrate integrated waveguide (SIW). The back cavity gap circularly polarized millimeter wave antenna comprises a radiation layer, a power division layer and a feed layer; the radiation layer is composed of a SIW square resonant cavity, a first metal patch and a first rectangular dielectric plate; the power division layer is composed of a power divider, a second metal patch and a second rectangular dielectric plate; the feed layer is composed of a SIW structure, a third metal patch, a third rectangular dielectric plate and a fourth metal patch; the SIW square resonant cavity is provided with a first metal through hole, a rectangular gap is etched in the upper surface and a through hole is formed in the center in a run-through mode; the power divider is composed of a second metal through hole and probes, a power division layer rectangular coupling gap is etched in the center position, circular coupling gaps are formed in the periphery, and the probes penetrate through the respective circular coupling gaps; and the SIW structure is etched with a feed layer rectangular coupling gap and a feed layer metal through hole. The feed network transmission characteristic of the antenna is high, the gain in the working frequency band is high and the bandwidth is wide, and the antenna has the advantages of being simple in feeding structure, low in profile and compact in structure.

Owner:XIDIAN UNIV