cmos integrated process bjt structure and its manufacturing method

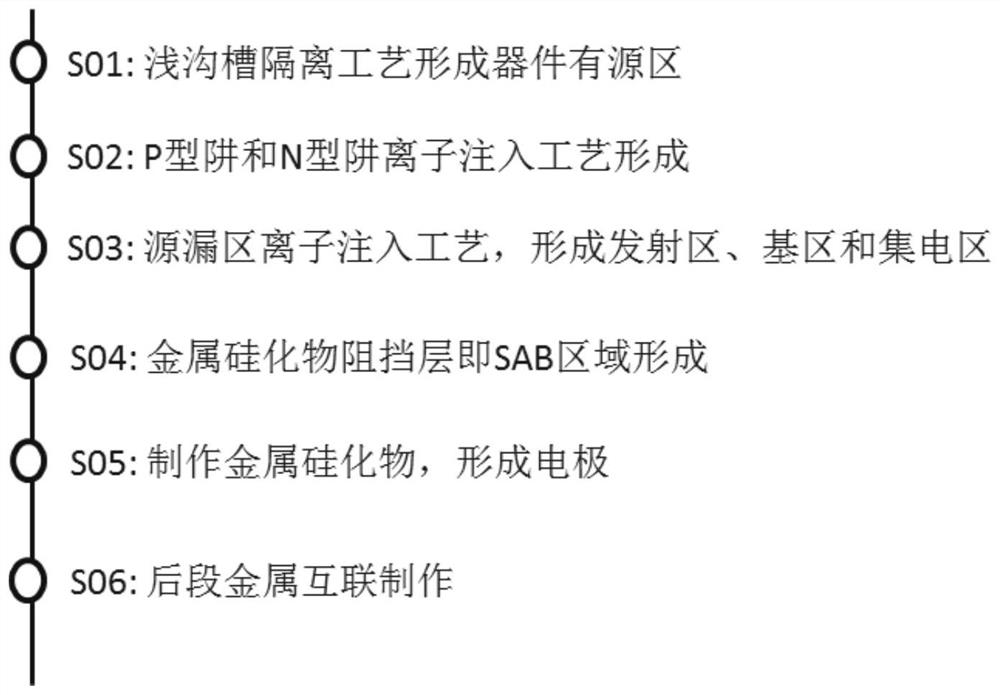

A manufacturing method and process technology, applied in the field of CMOS integrated process BJT structure, CMOS integrated process BJT manufacturing, can solve the problems of improvement limitation of divot process uniformity of height difference between AA and STI area, difficult control of divot process uniformity, etc., to achieve Improve the uniformity of current gain, improve the distribution of data, and increase the effect of current gain

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

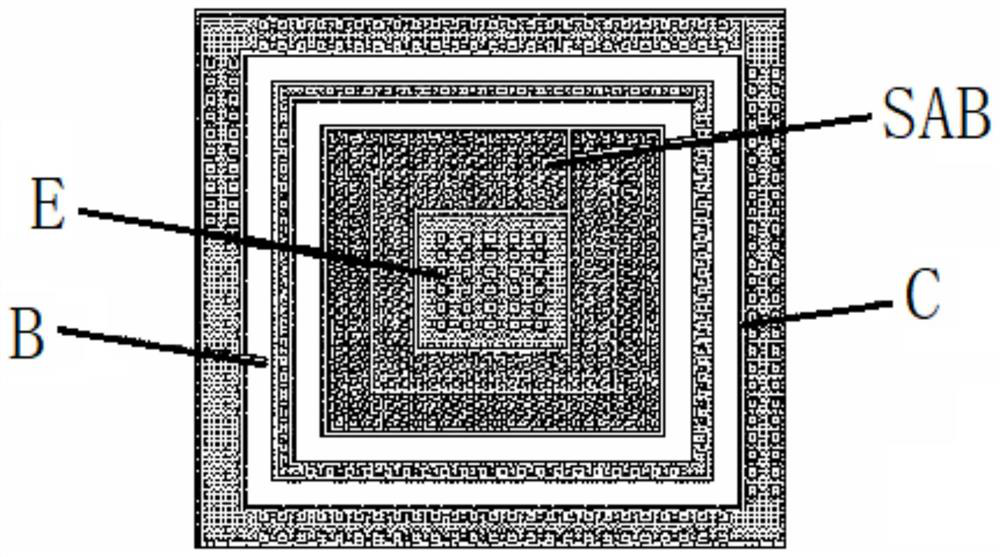

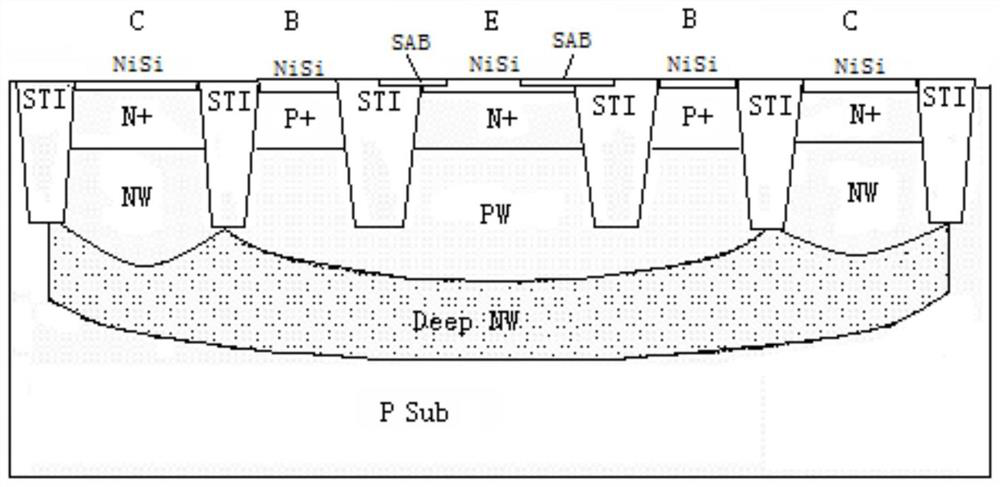

[0074] The first embodiment of the BJT structure of the CMOS integration process provided by the present invention includes: P well and N well arranged in parallel on a silicon substrate, a first shallow trench isolation is formed at the critical position of the P well and the N well, and a first shallow trench is formed in the P well There is a second shallow trench isolation, a first P+ doped region is formed in the P well between the first shallow trench isolation and the second shallow trench isolation, and a first P+ doped region is formed in the N well beside the first shallow trench isolation The first N+ doped region, the second N+ doped region is formed in the P well on the other side of the second shallow trench isolation, the second N+ doped region is formed with a parallel first electrode and a barrier layer, the first P+ A second electrode is formed on the doped region, and a third electrode is formed on the first N+ doped region; wherein, a flat layer is deposited...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More