Metal oxide semiconductor (MOS) transistor and formation method thereof

A MOS transistor and semiconductor technology, applied in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problems that cannot be further reduced, and achieve the effect of reducing influence and weakening junction capacitance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

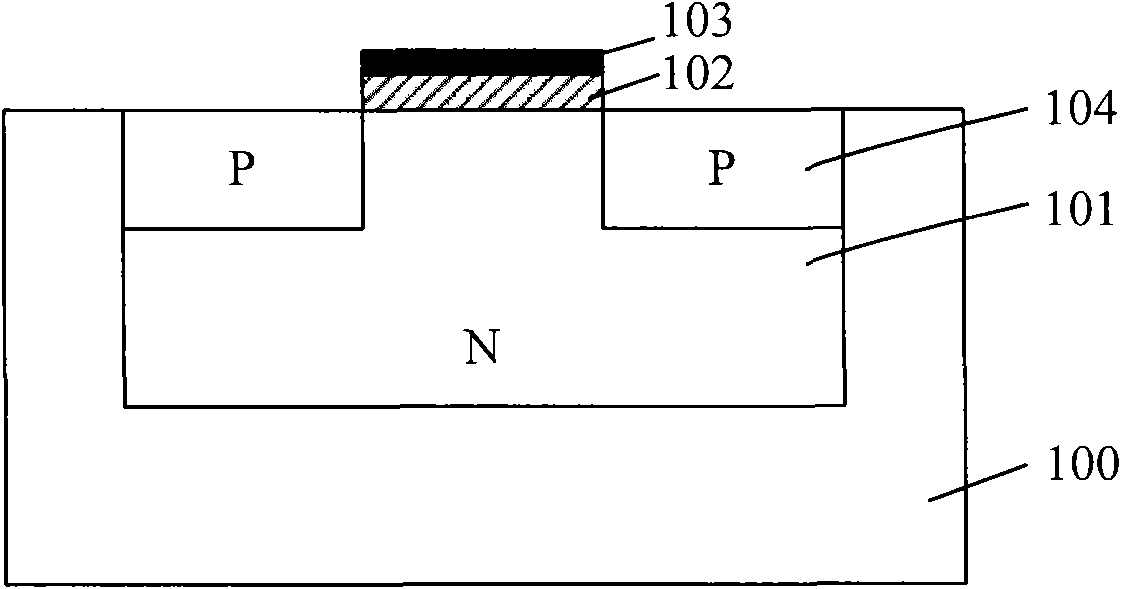

[0031] It is known from the background technology that in the manufacturing process of MOS transistors, the doping concentration near the interface between the isolation well and the source and drain regions determines the size of the junction capacitance in the MOS transistor, so reduce the doping concentration there as much as possible Can effectively eliminate junction capacitance. The doping concentration here can be reduced by performing anti-phase doping on the isolation well to neutralize the two opposite doping substances.

[0032] The invention provides a method for forming a MOS transistor, the process of which is as follows: Figure 5 As shown, the specific implementation is as follows:

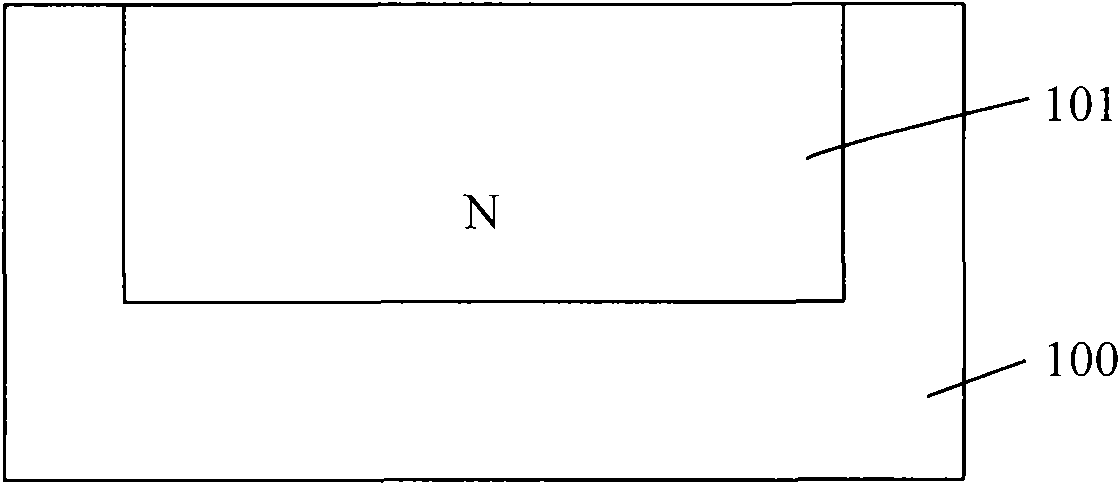

[0033] S1, first forming an isolation well on the semiconductor substrate by multiple ion implantation;

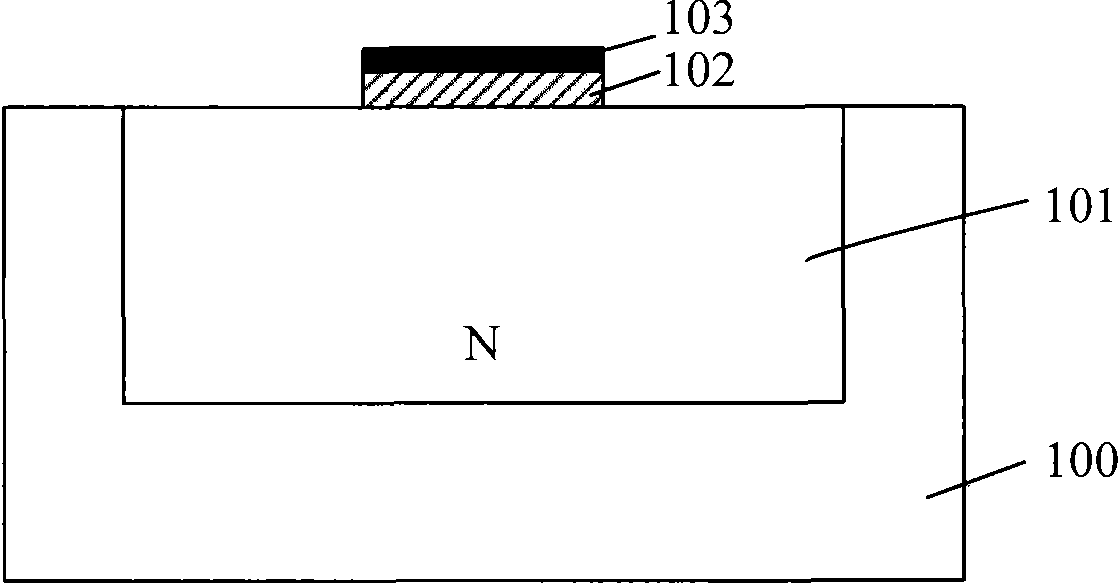

[0034] S2. Perform reverse-phase ion implantation on the isolation well;

[0035] Among them, if a PMOS is formed, the isolation well is an N well, and the dopant used in th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More