Bidirectional tri-path turn-on high-voltage ESD protective device

An ESD protection, three-path technology, applied in the direction of semiconductor devices, electrical solid state devices, circuits, etc., can solve the problems of increasing the design difficulty of high-voltage ESD protection devices, narrowing the ESD design window, and easily entering the latch state, etc., to achieve the realization of High-voltage ESD protection, small on-resistance, and the effect of increasing the discharge path

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

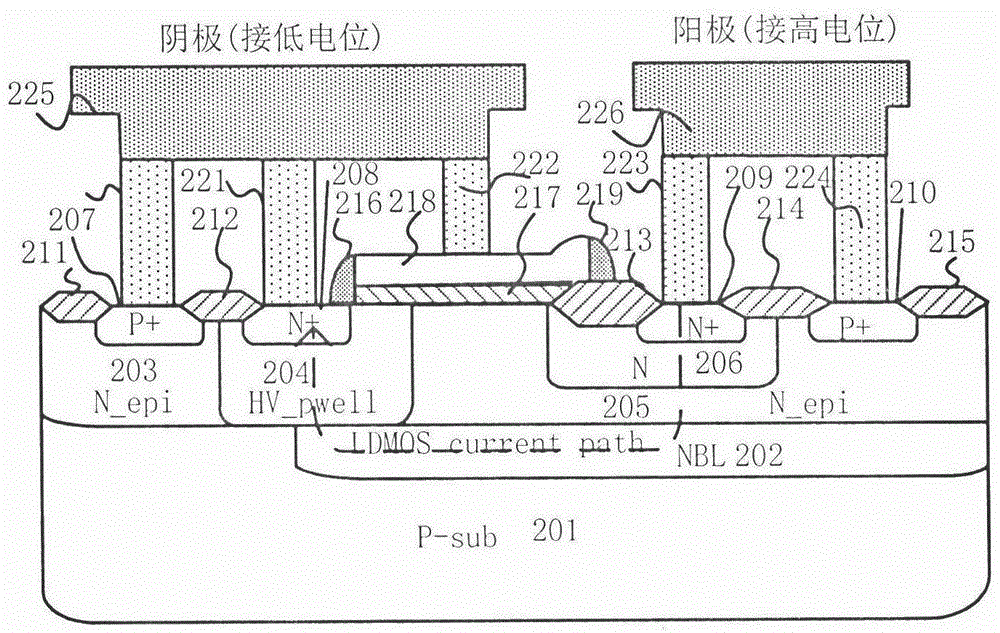

[0028] The present invention proposes a bidirectional three-path high-voltage ESD protection device combining SCR and NLDMOS, because its trigger voltage is mainly affected by the impurity concentration of the heavily doped N-type buried layer, and it has a longer current conduction path, so the energy efficiency reduces the trigger voltage of the device, increases the maintenance voltage and the secondary breakdown current, and at the same time has the function of bidirectional ESD protection, and also has the advantages of small leakage current, small on-resistance, and fast response speed.

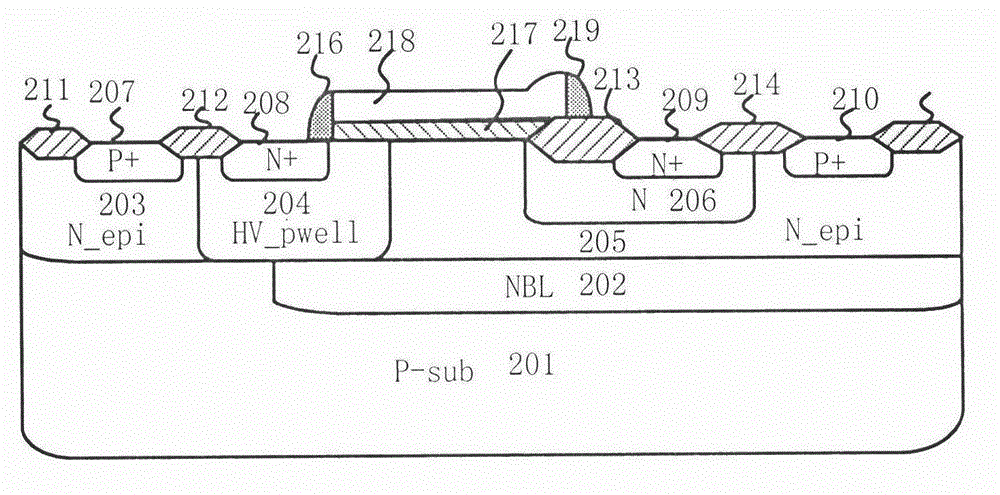

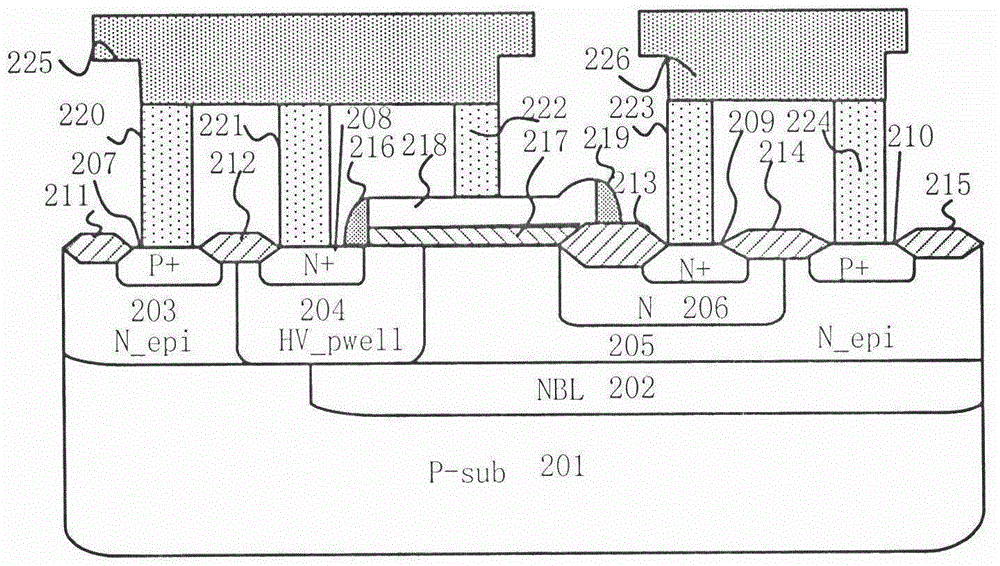

[0029] Such as figure 1 As shown, it is a cross-sectional view of the structure of an example device of the present invention, specifically a high-voltage ESD protection device with bidirectional and three-path conduction combined with SCR and NLDMOS, including a P-substrate 201, an N+ buried layer 202, and left / right N-type Epitaxy 203, 205, high voltage P well 204, drift region 206, m...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More