Patents

Literature

237results about How to "Increase holding voltage" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

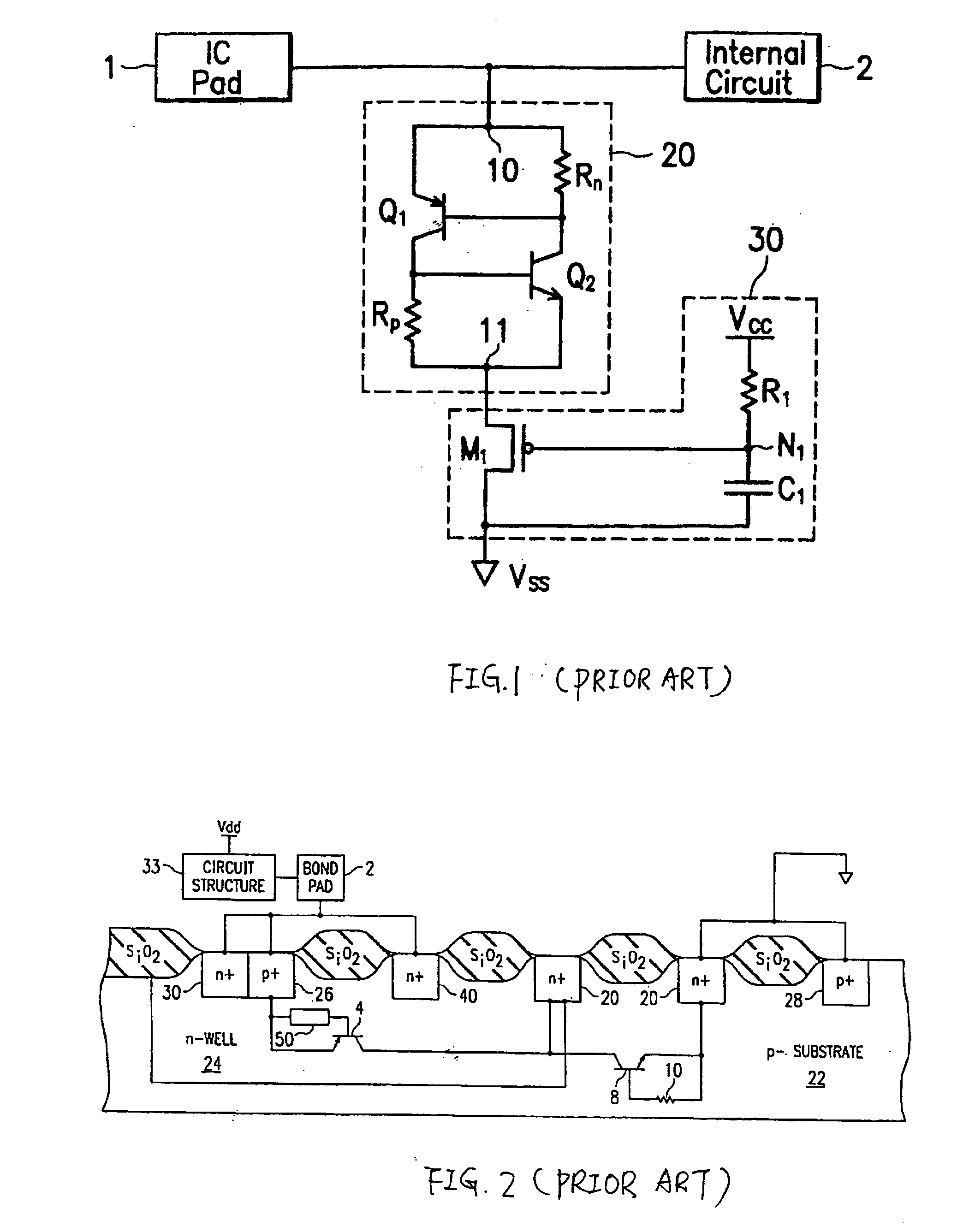

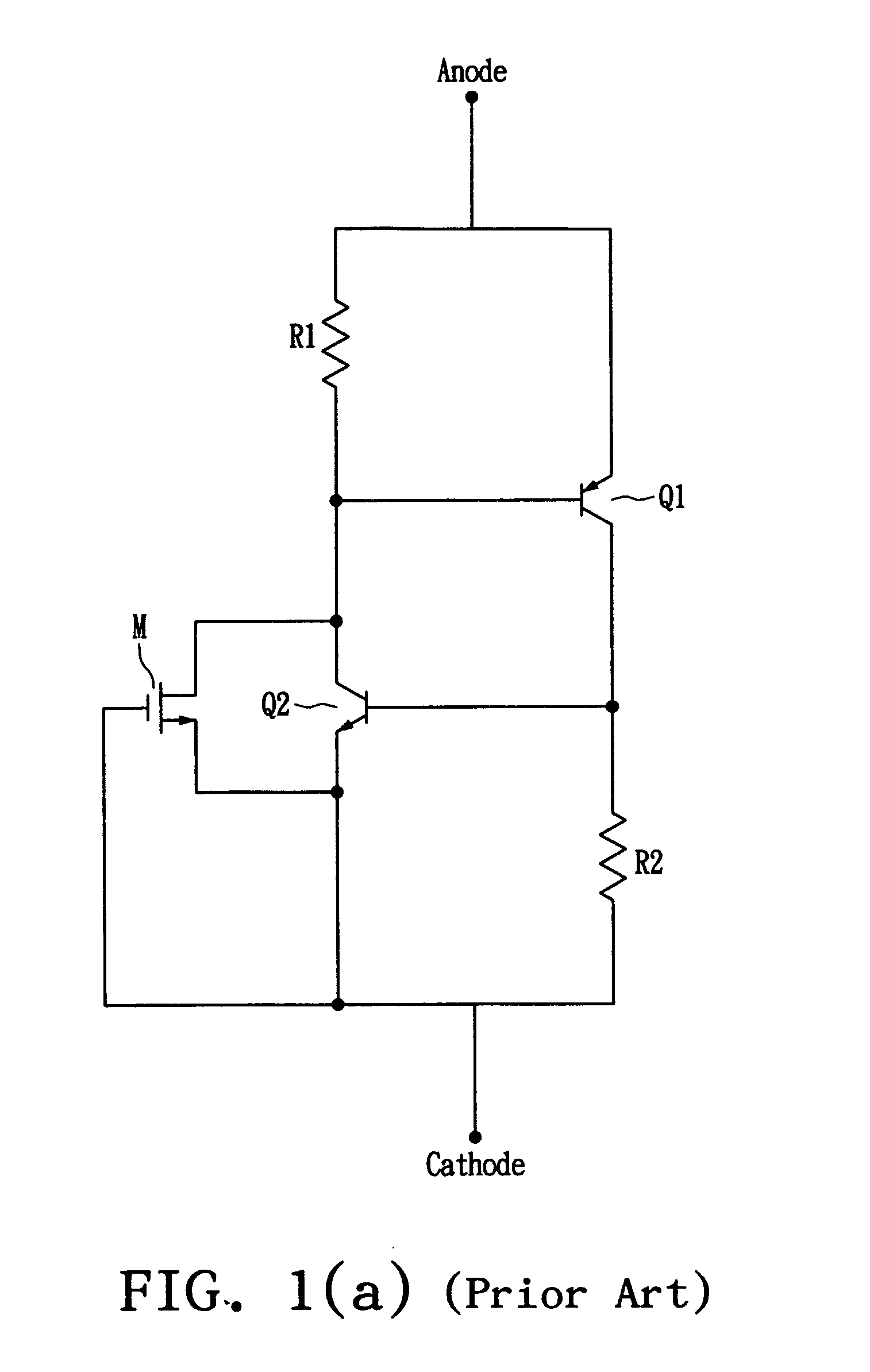

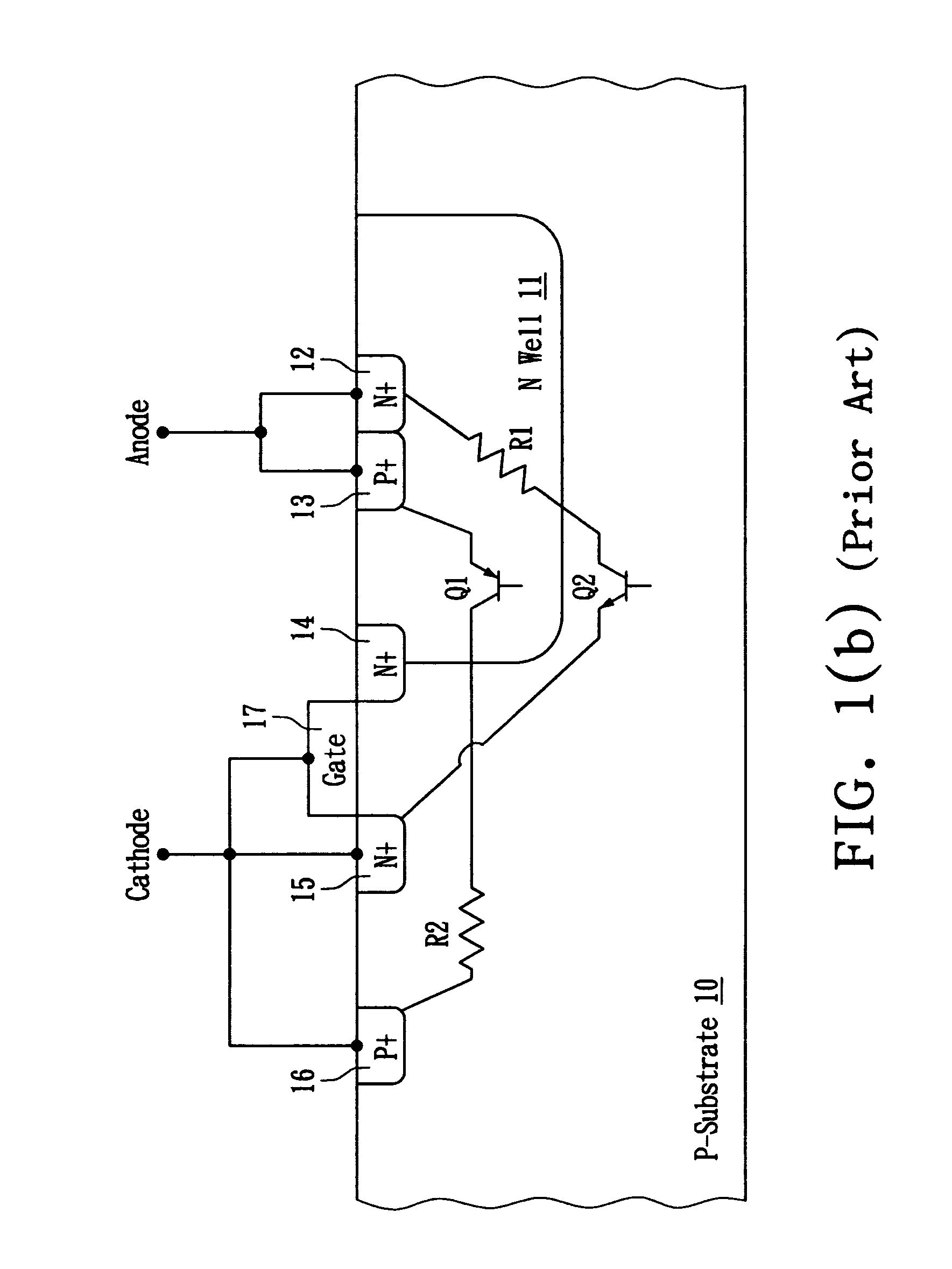

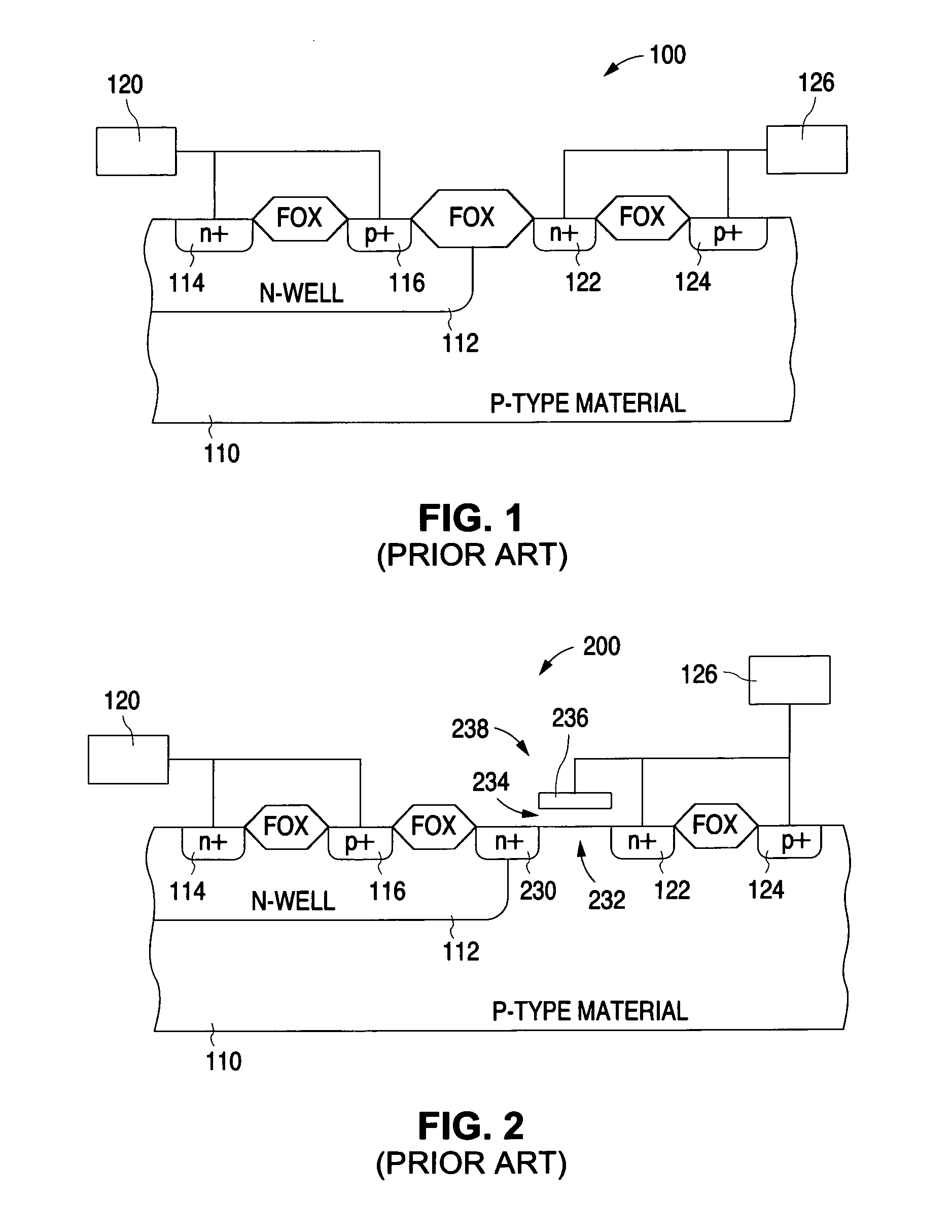

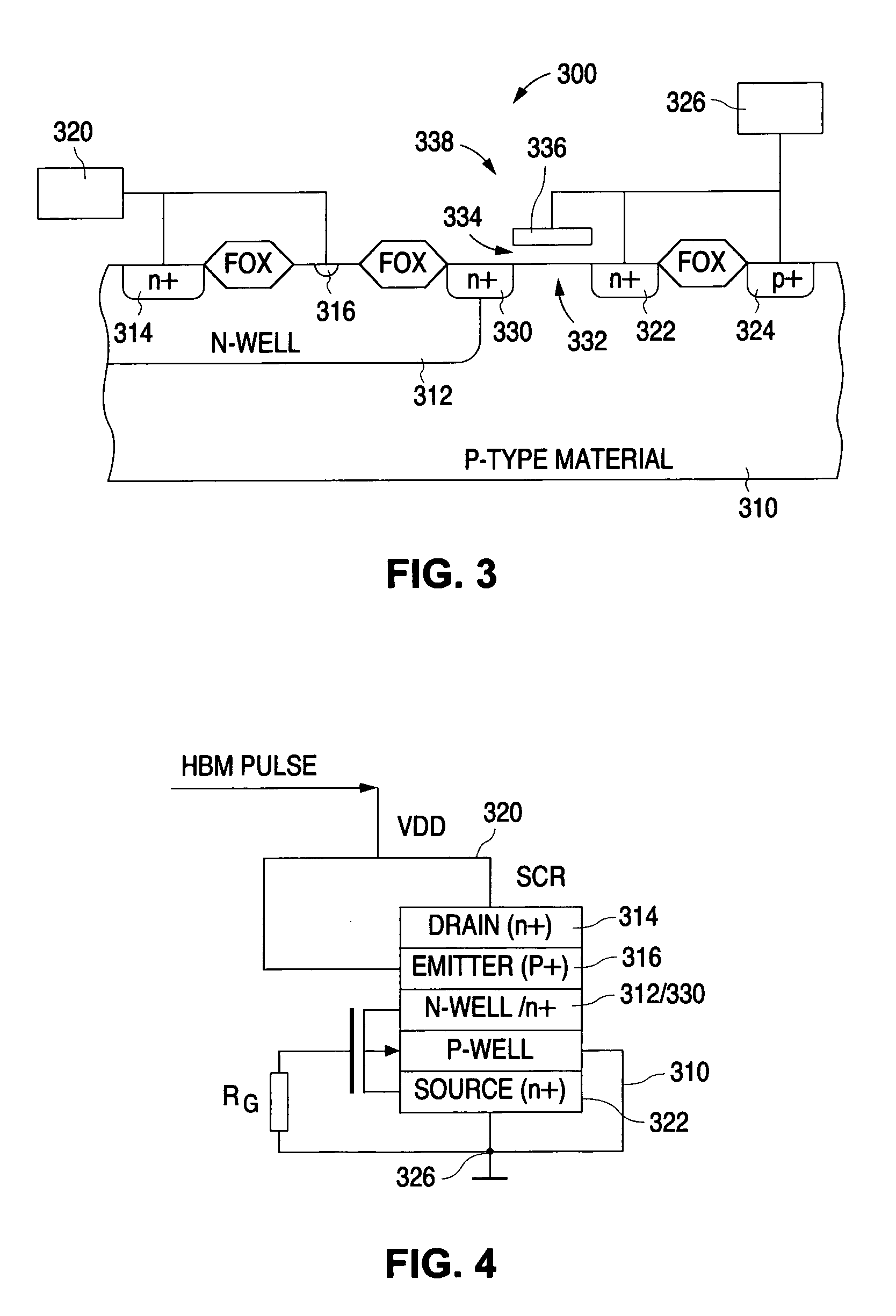

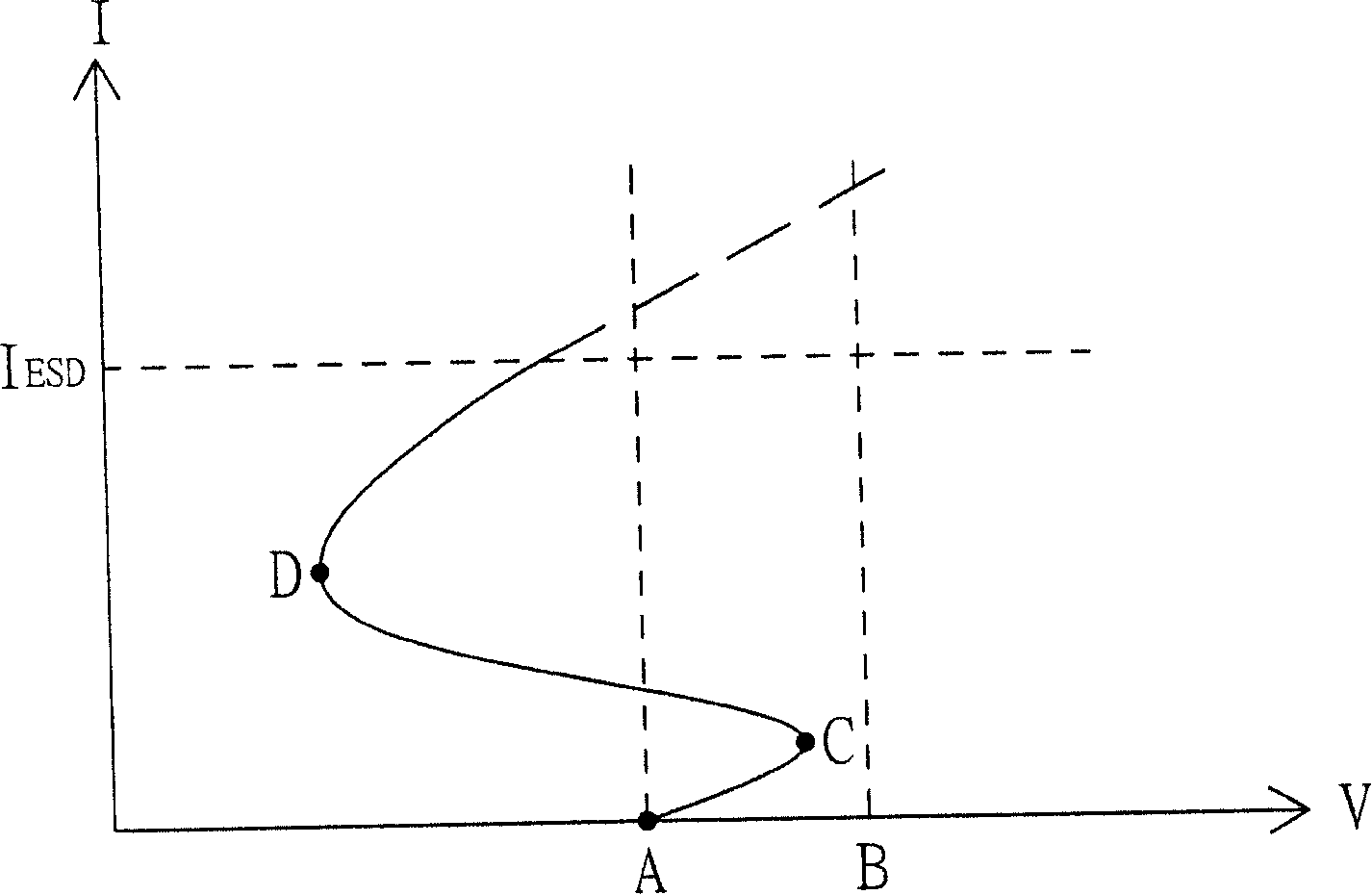

Silocon-controlled rectifier with dynamic holding voltage for on-chip electrostatic discharge protection

InactiveUS20040100746A1Increase holding voltageReduce voltageTransistorSolid-state devicesSilicon-controlled rectifierEngineering

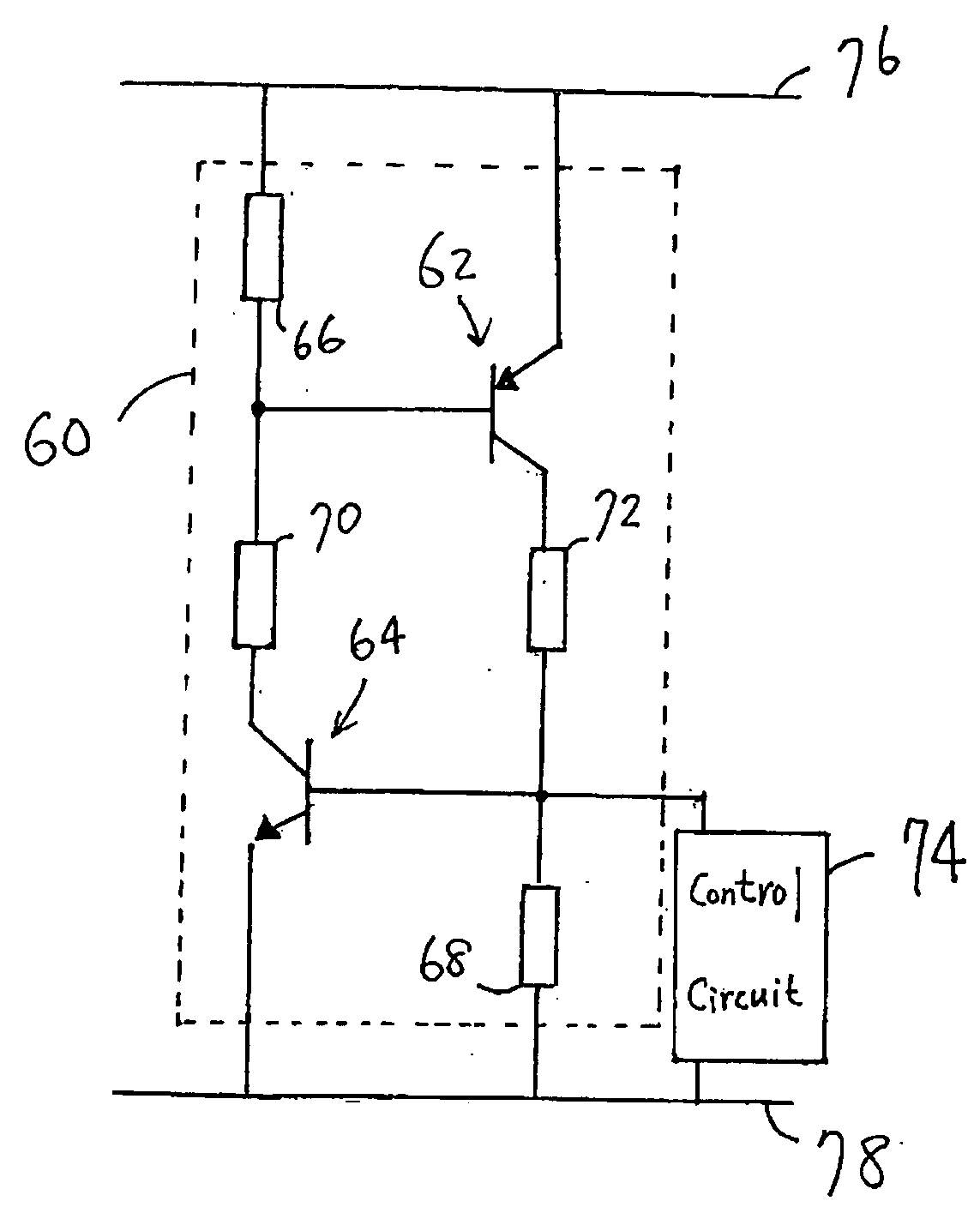

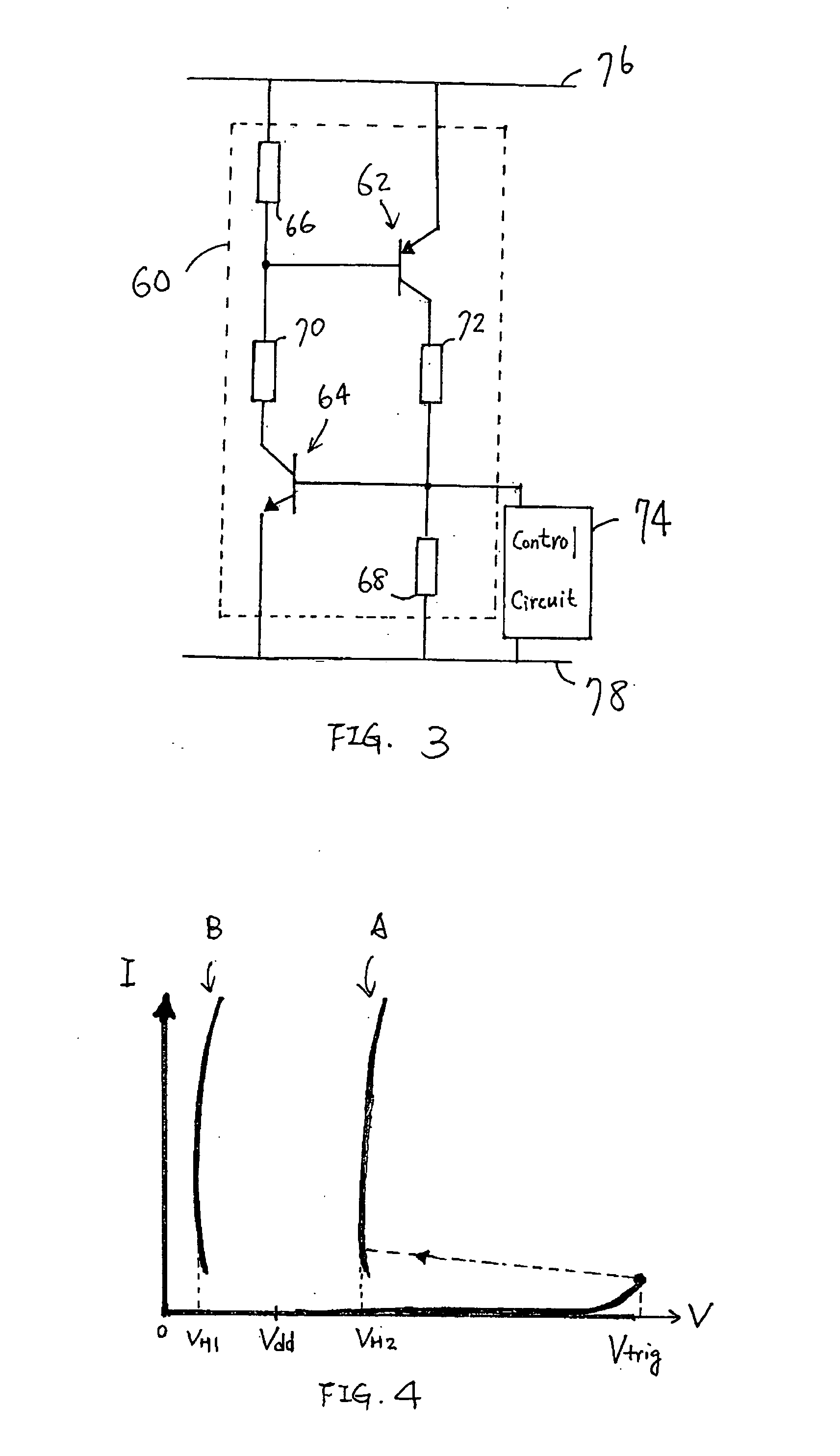

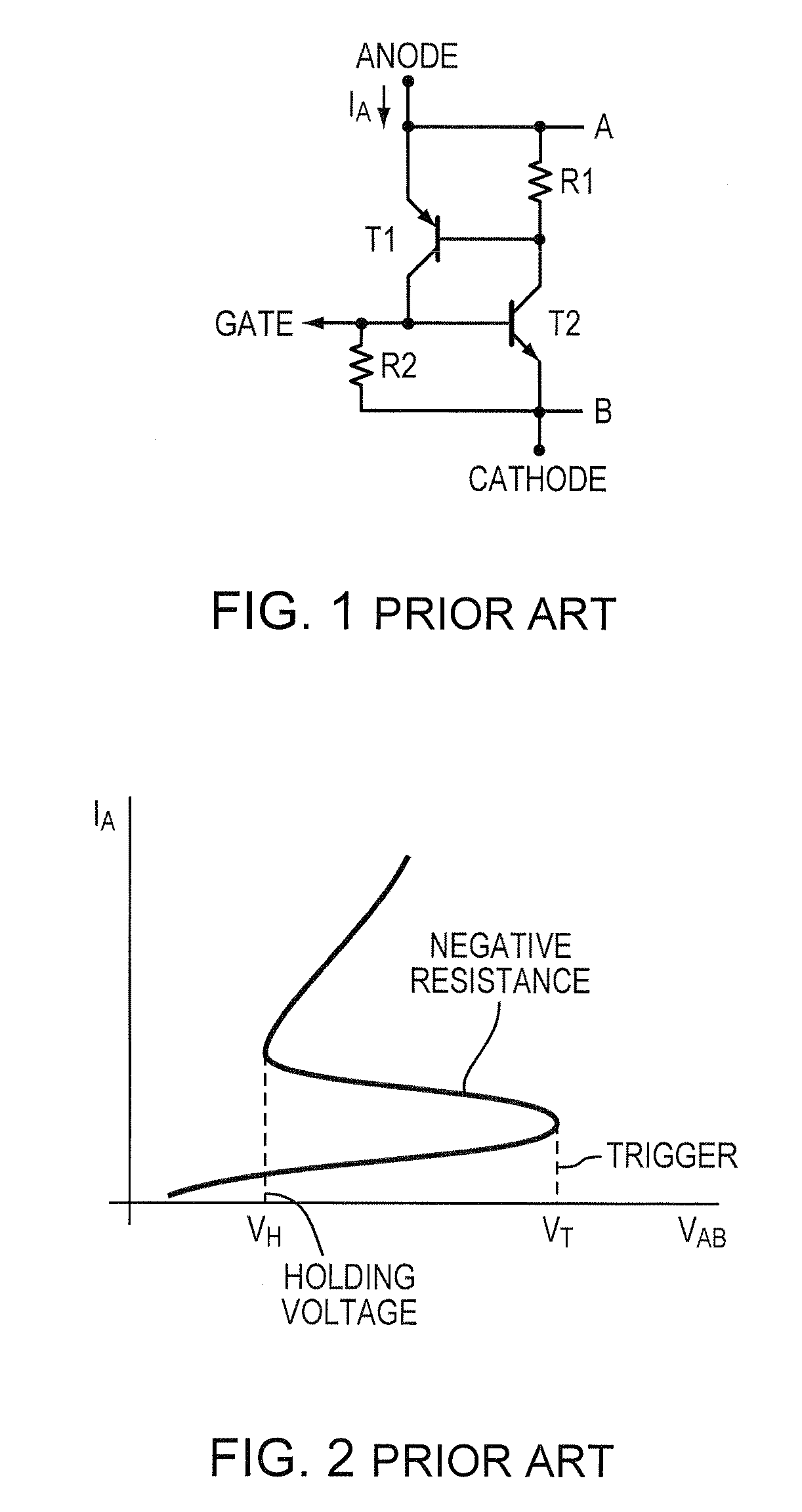

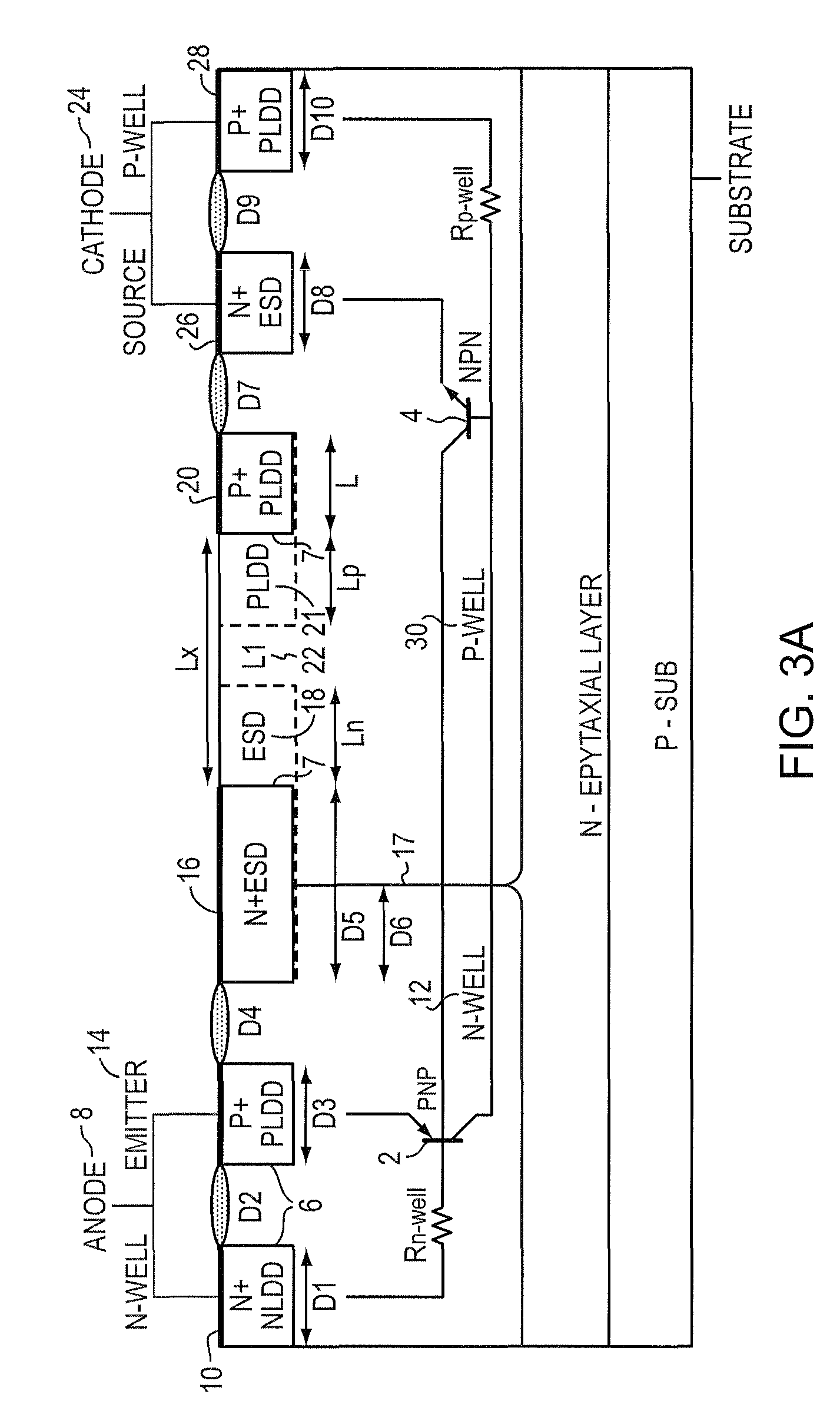

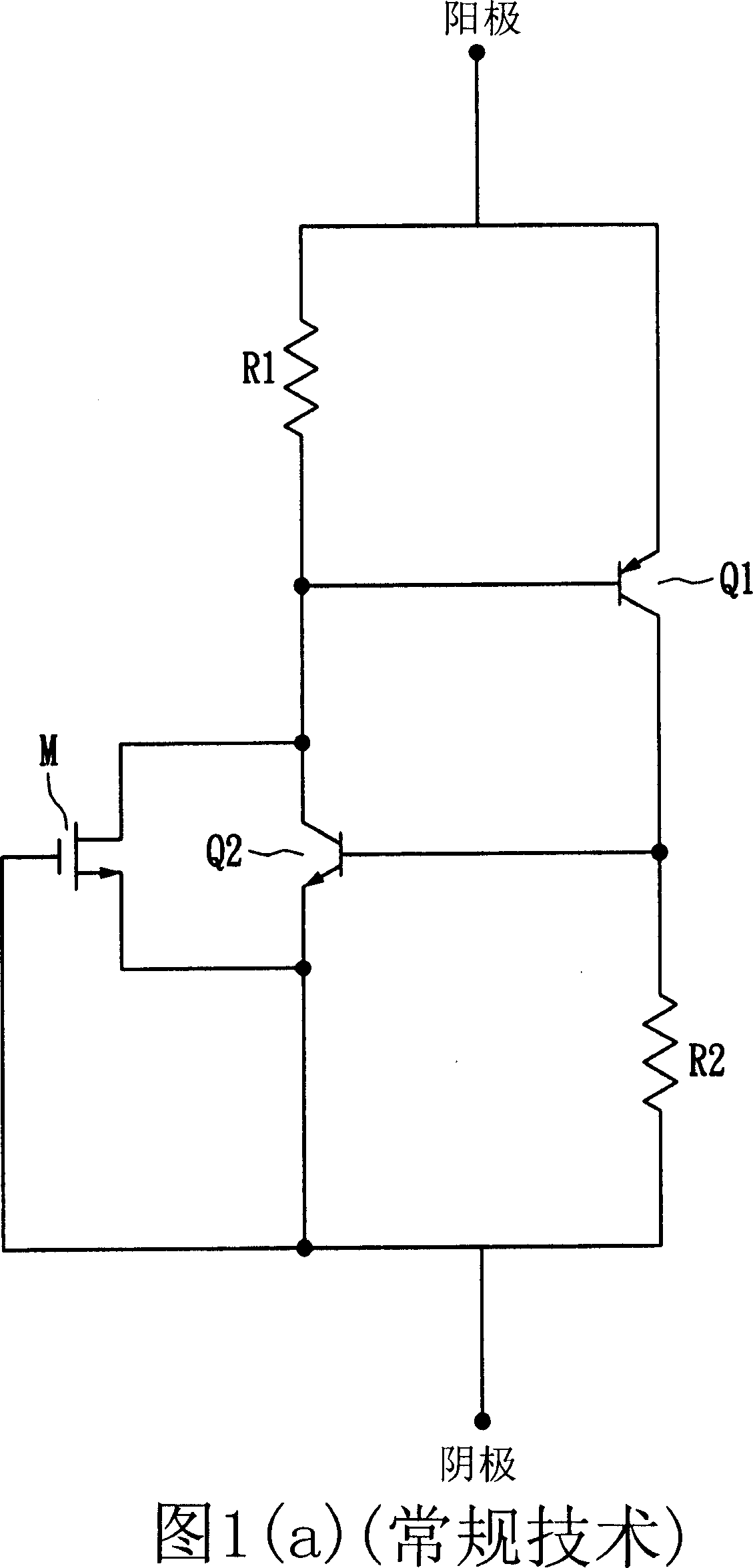

An integrated circuit for electrostatic discharge (ESD) protection that comprises a silicon-controlled rectifier (SCR), a first transistor of a first type integrally formed with the SCR including a first gate, a second transistor of a second type integrally formed with the SCR including a second gate, and a control circuit in response to a first voltage applied to the first and second gates providing a first holding voltage to the SCR to keep the SCR from latching-up, and in response to a second voltage applied to the first and second gates providing a second holding voltage to the SCR to keep the SCR in the latch-up state.

Owner:IND TECH RES INST

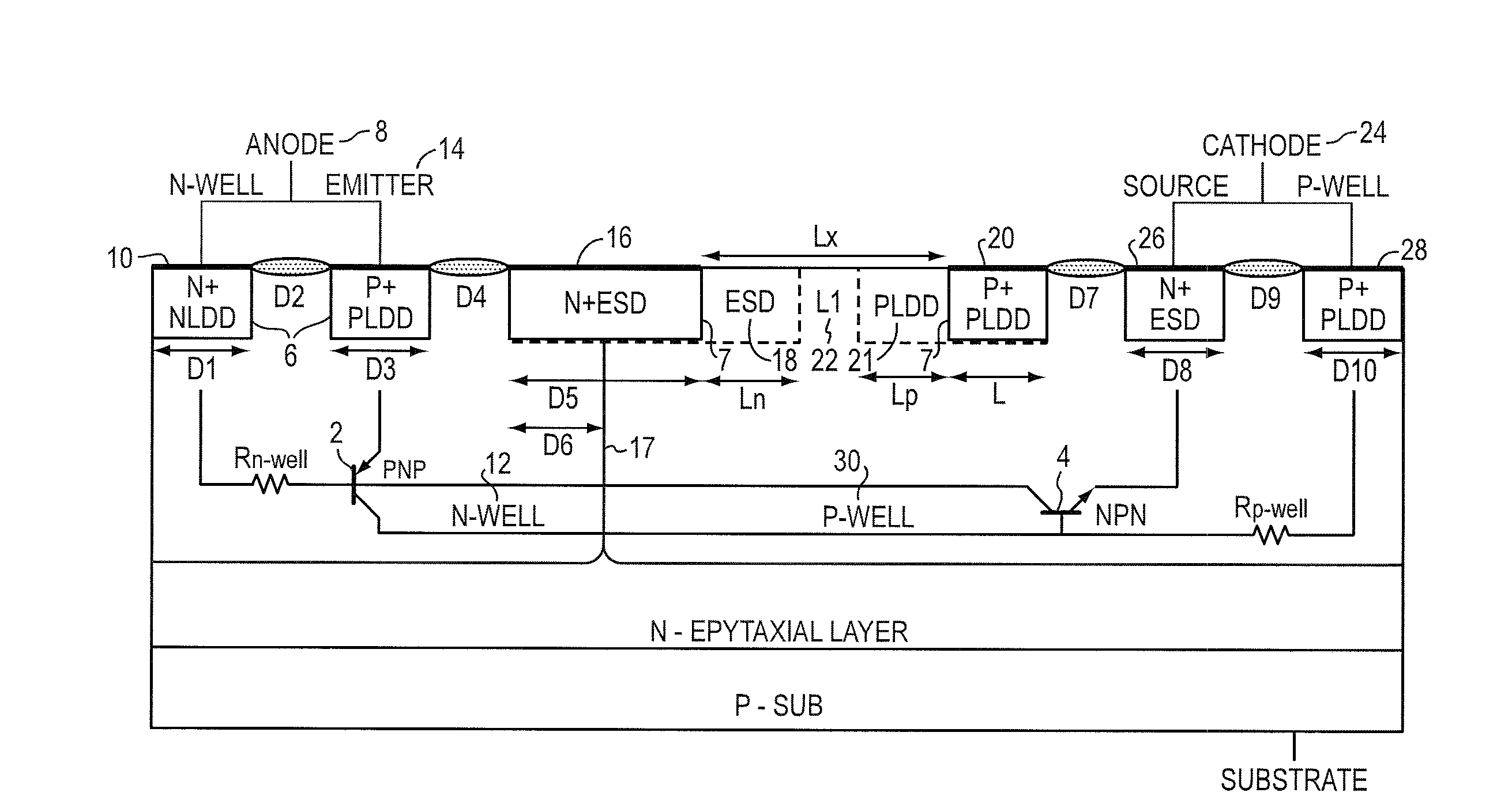

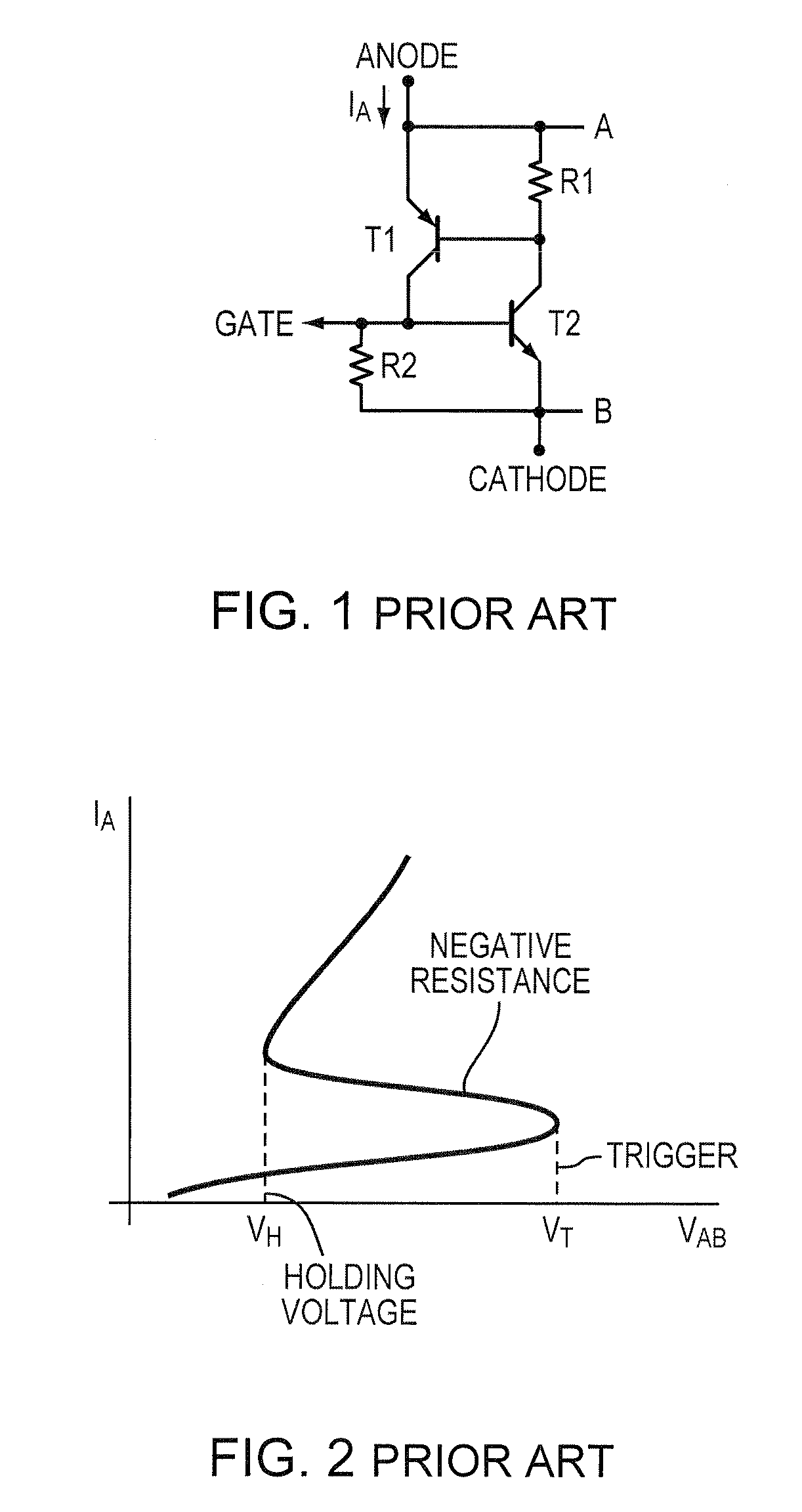

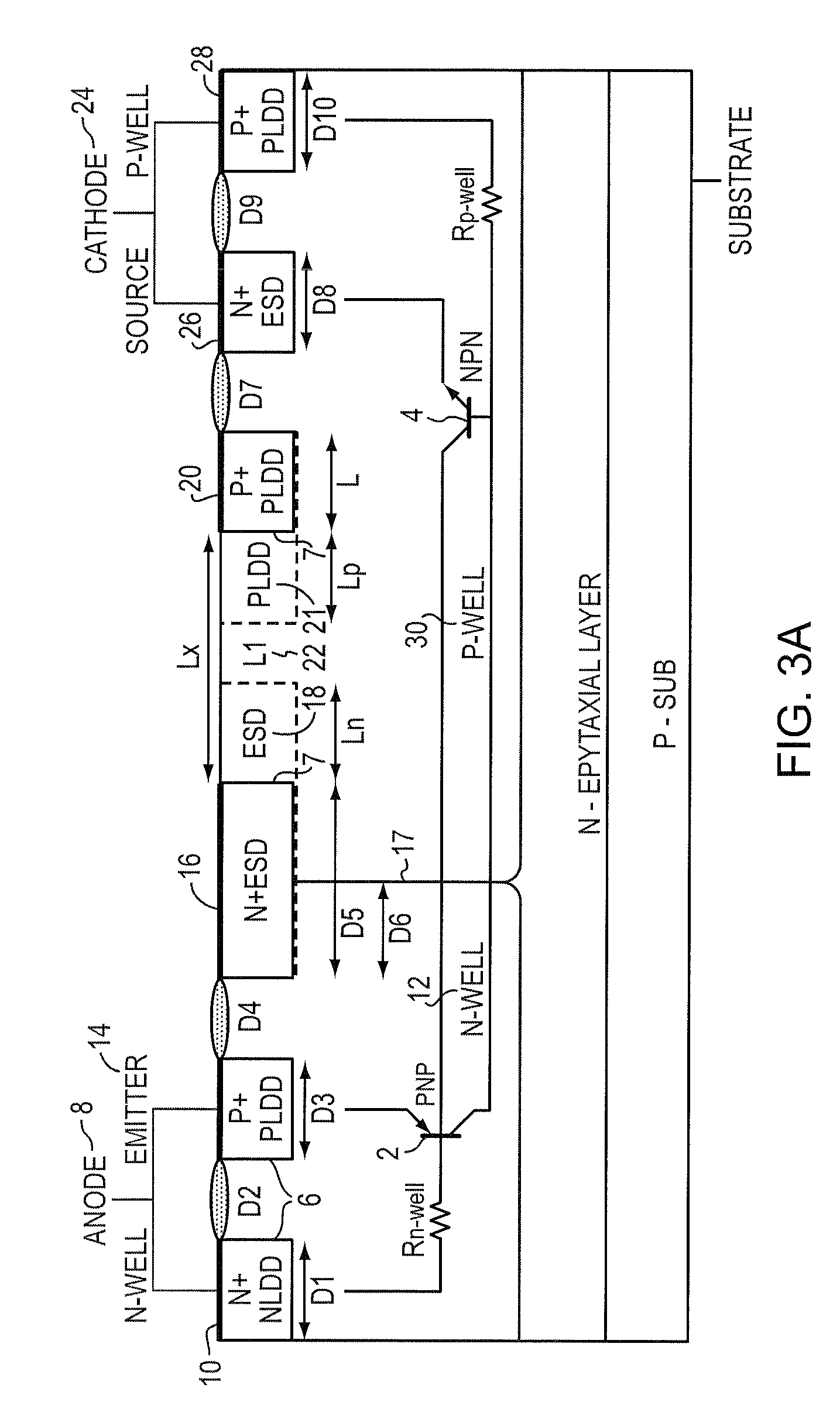

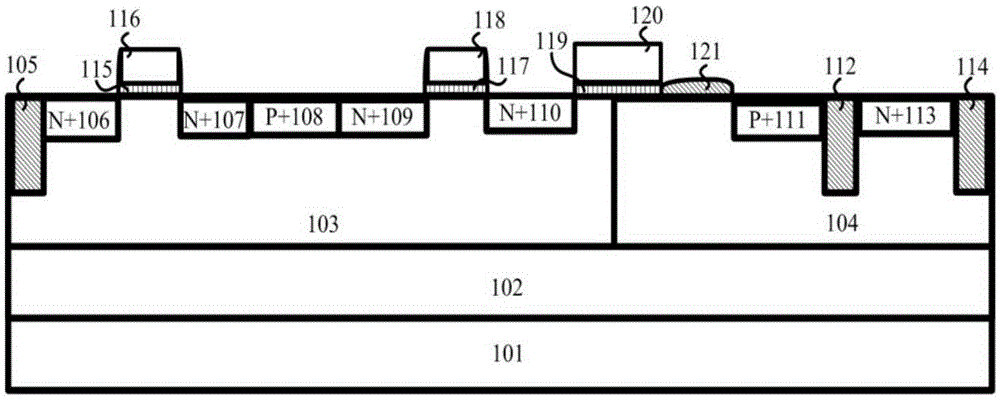

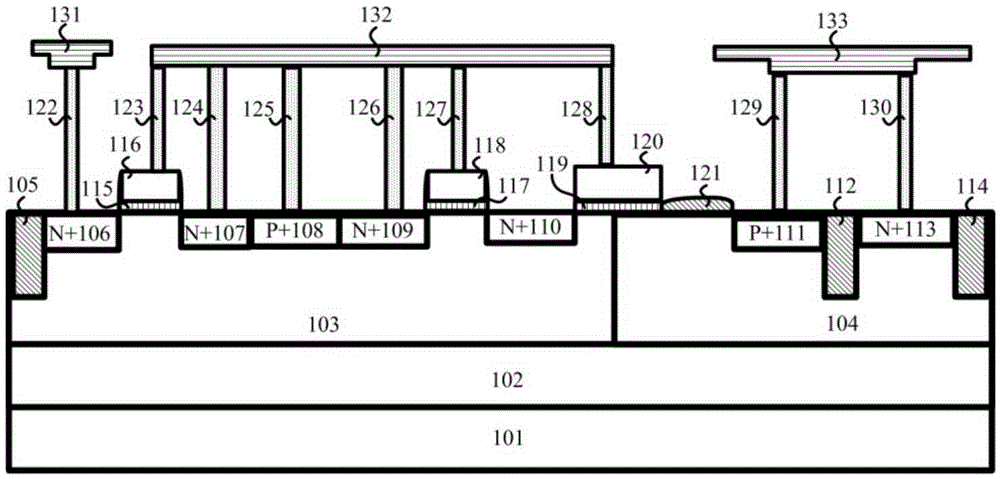

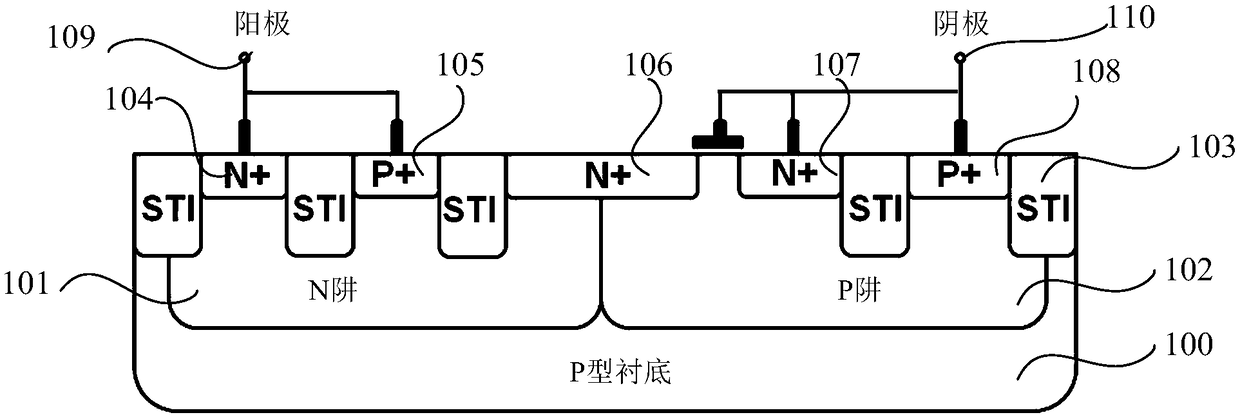

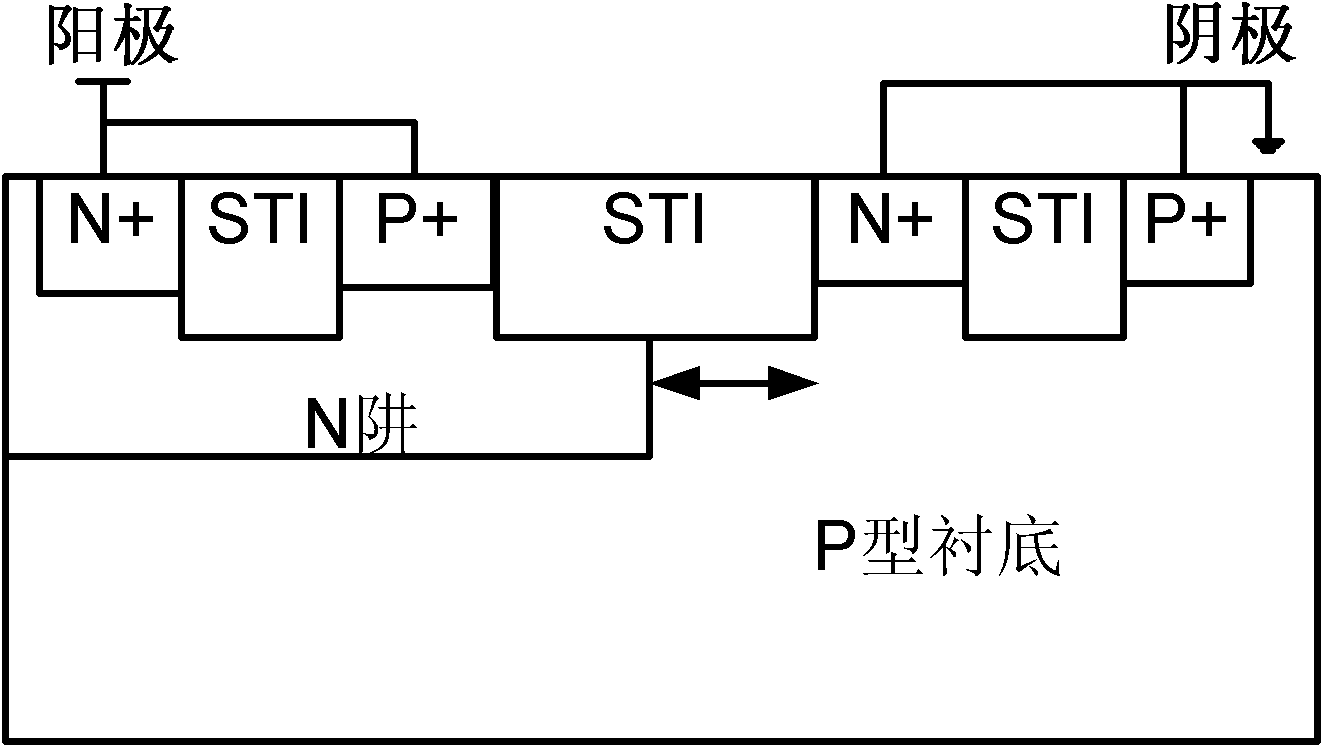

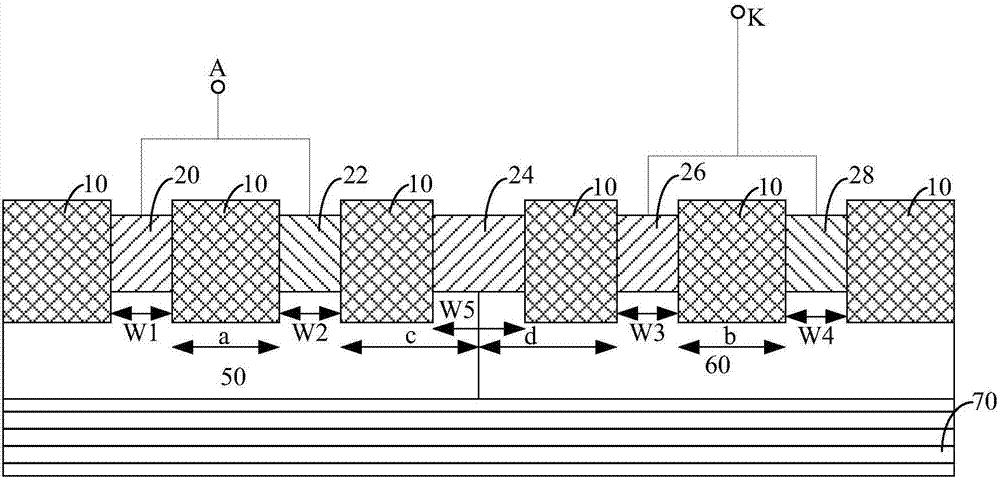

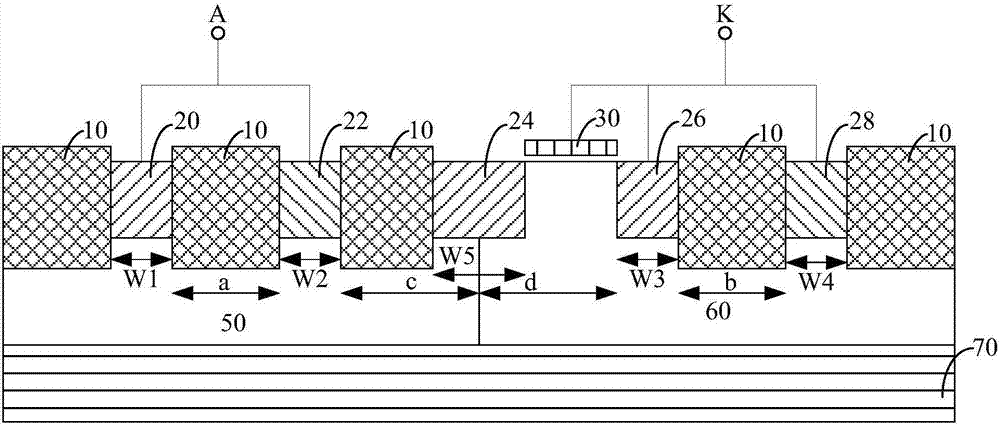

Un-assisted, low-trigger and high-holding voltage SCR

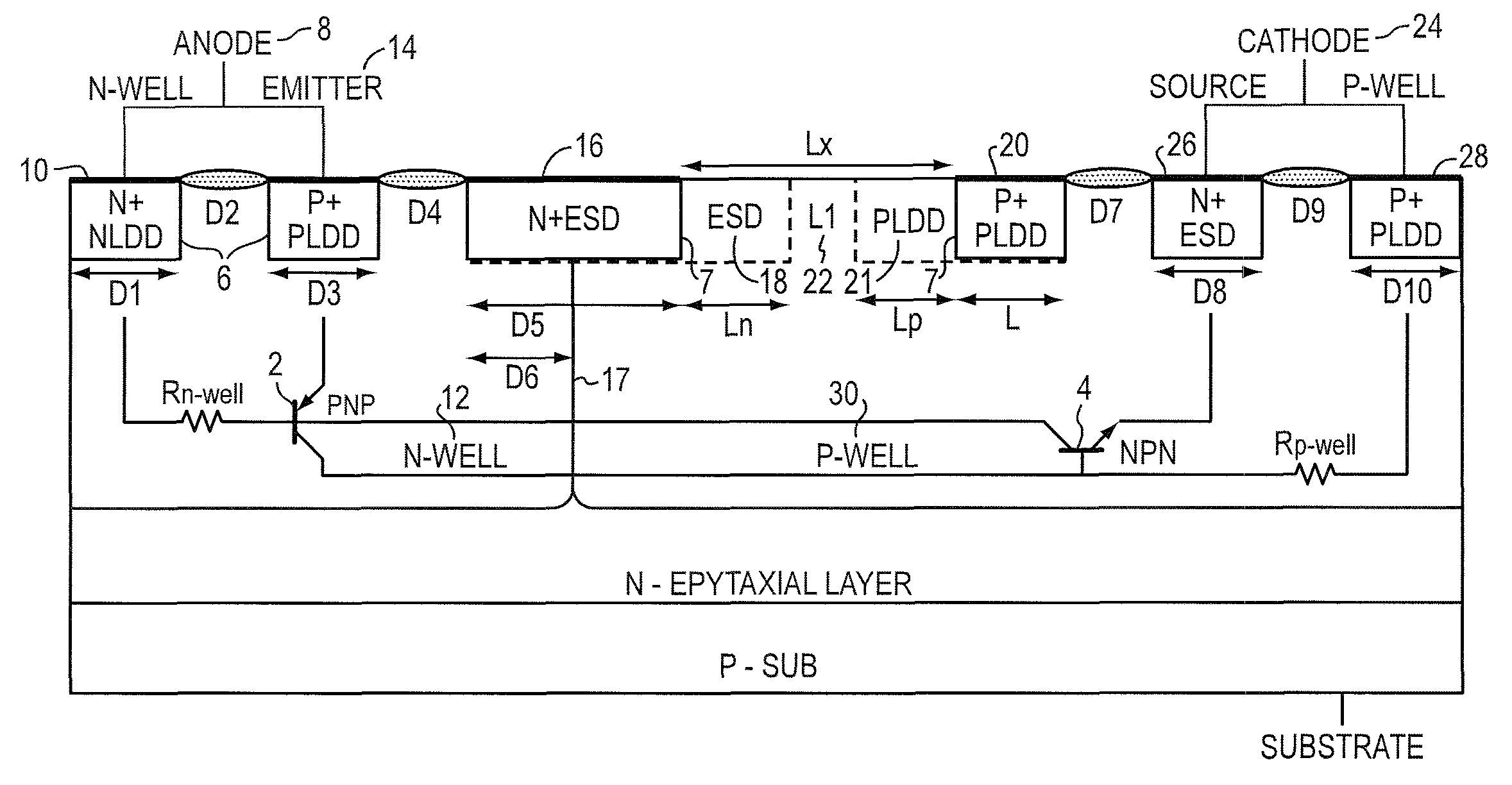

ActiveUS7719026B2Sacrificing ESD protection robustnessHigh n-type doping densityTransistorThyristorEngineeringExternal circuit

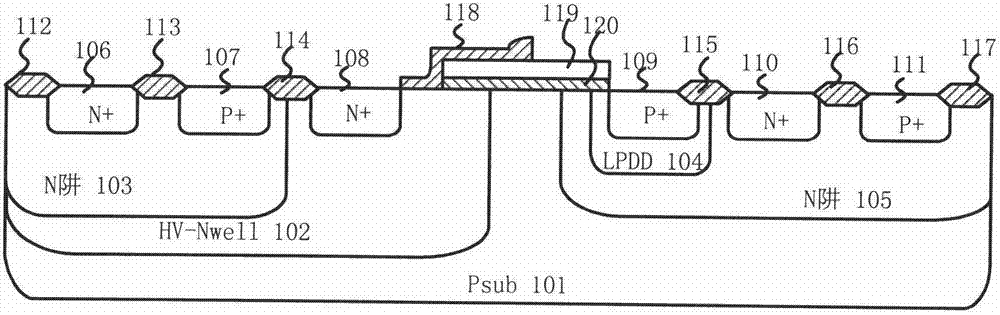

A protective SCR integrated circuit device is disclosed built on adjacent N and P wells and defining an anode and a cathode. In addition to the anode and cathode contact structures, the device has an n-type stack (N+ / ESD) structure bridging the N-Well and the P-Well, and a p-type stack (P+ / PLDD) structure in the P-Well. The separation of the n-type stack structure and the p-type stack structure provides a low triggering voltage without involving any external circuitry or terminal, that together with other physical dimensions and processing parameters also provide a relatively high holding voltage without sacrificing the ESD protection robustness. In an embodiment, the triggering voltage may be about 8V while exhibiting a holding voltage, that may be controlled by the lateral dimension of the n-type stack of about 5-7 V.

Owner:SEMICON COMPONENTS IND LLC

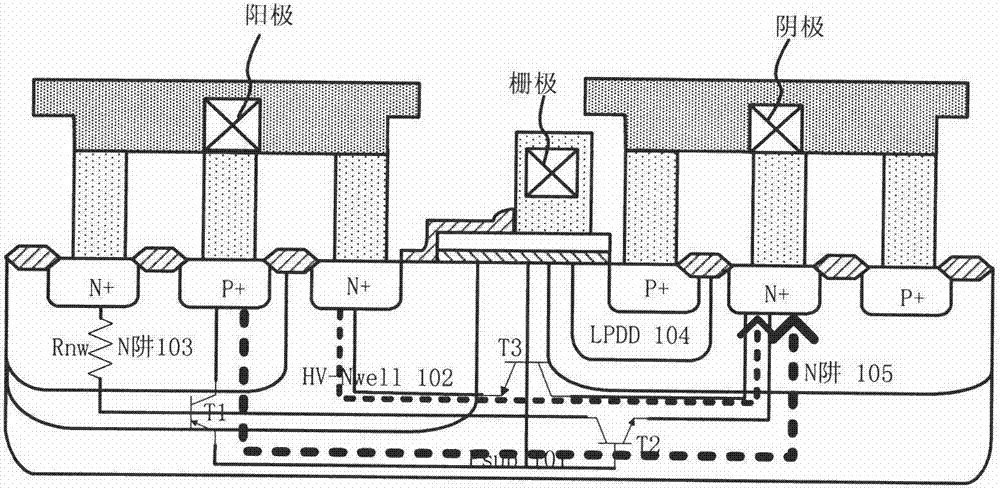

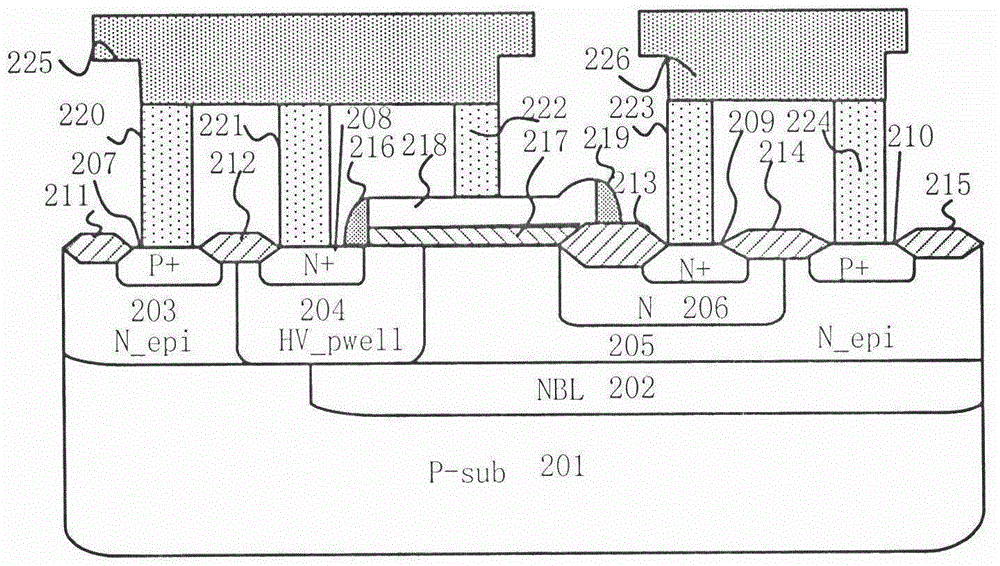

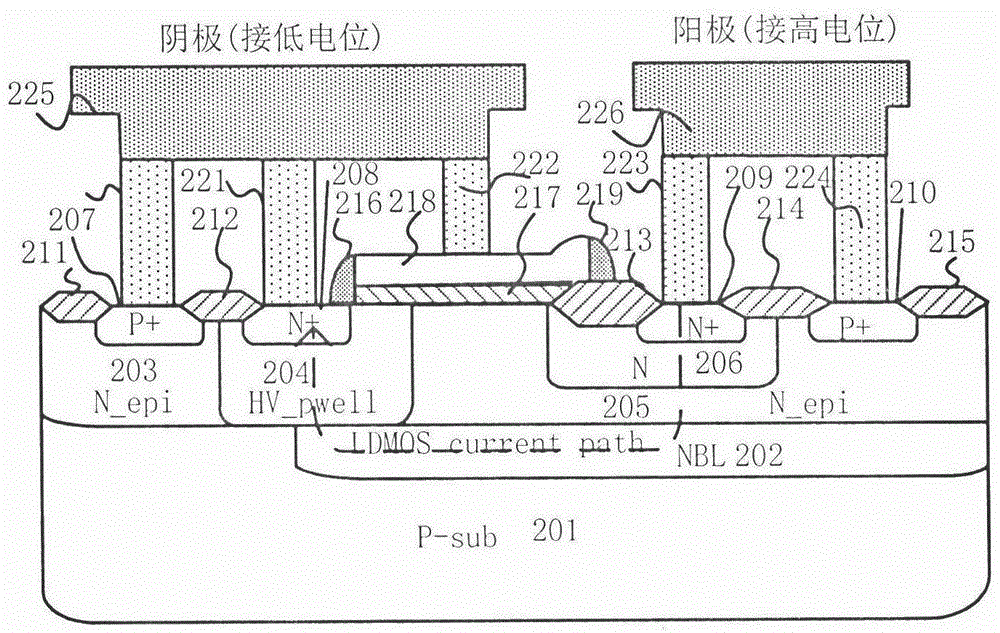

High-voltage ESD (electro-static discharge) protective device triggered by bidirectional substrate

ActiveCN102969312AOpen fastLarge secondary breakdown currentSolid-state devicesSemiconductor devicesSilicon-controlled rectifierThin oxide

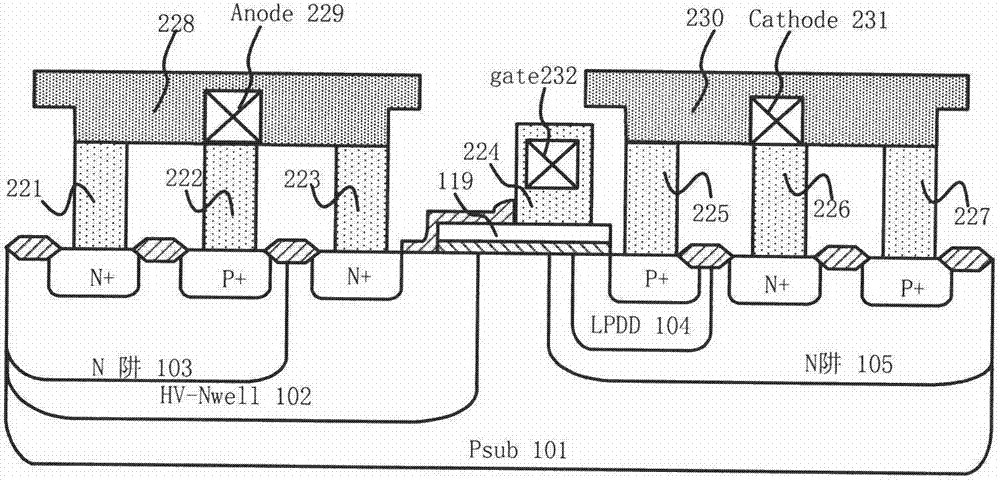

The invention discloses a high-voltage ESD (electro-static discharge) protective device triggered by a bidirectional substrate. The high-voltage ESD protective device triggered by the bidirectional substrate can be used for an on-chip IC (integrated circuit) ESD protective circuit and mainly comprises a substrate Psub, a high-voltage deep N trap, a lightly doped p-type drift region, a first highly doped N+ injection region, a first P+ injection region, a second N+ injection region, a second P+ injection region, a third N+ injection region, a third P+ injection region, a polycrystalline silicon grid, a grid thin oxide layer and a plurality of field oxide isolation regions. Reverse PN nodes at the interface part of the high-voltage N well or the N well and the substrate can be triggered and conducted through the forward and reverse ESD high-voltage pulse effect, two structures of internal SCR (silicon controlled rectifier) and LDMOS (laterally diffused metal oxide semiconductor) operate at the same time so as to form an ESD current discharge path to improve the secondary breakdown current of the device and lower the conducted resistance. The maintaining voltage of the device is improved through hoisting the channel length of the LDMOS device, the internal structure design as well as optimization of layout hierarchy, and the high-performance ESD protection is realized.

Owner:铜陵汇泽科技信息咨询有限公司

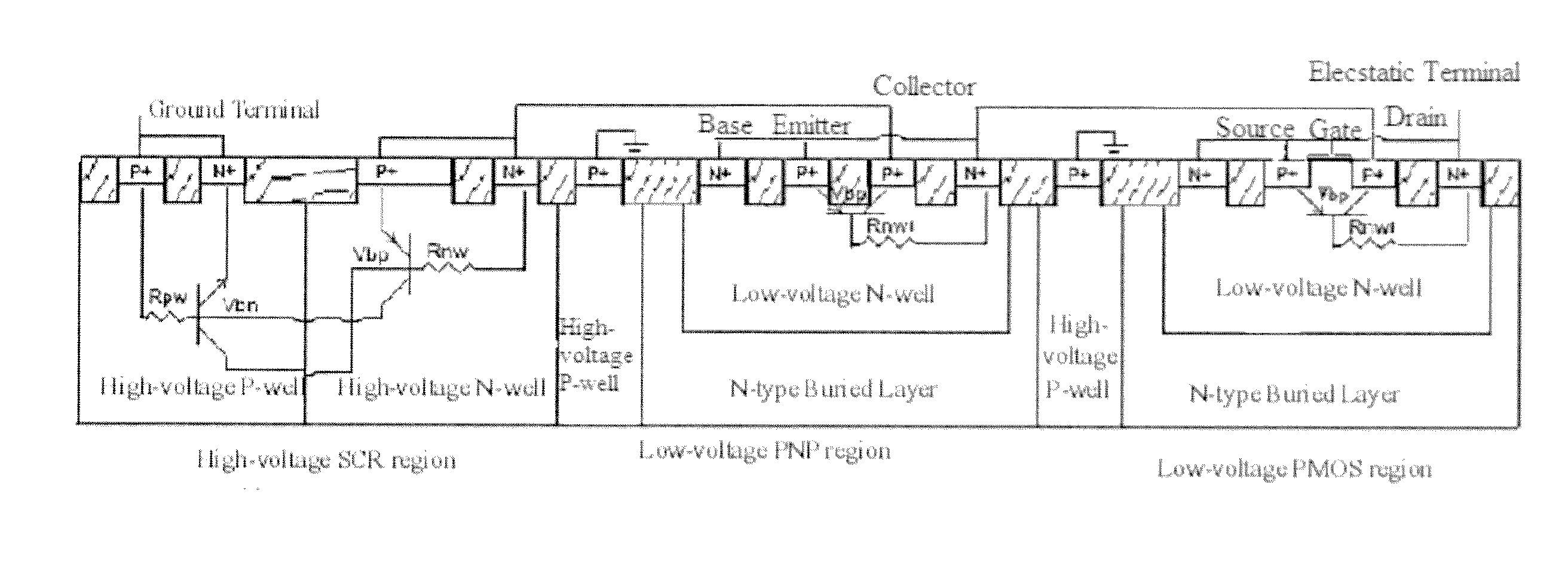

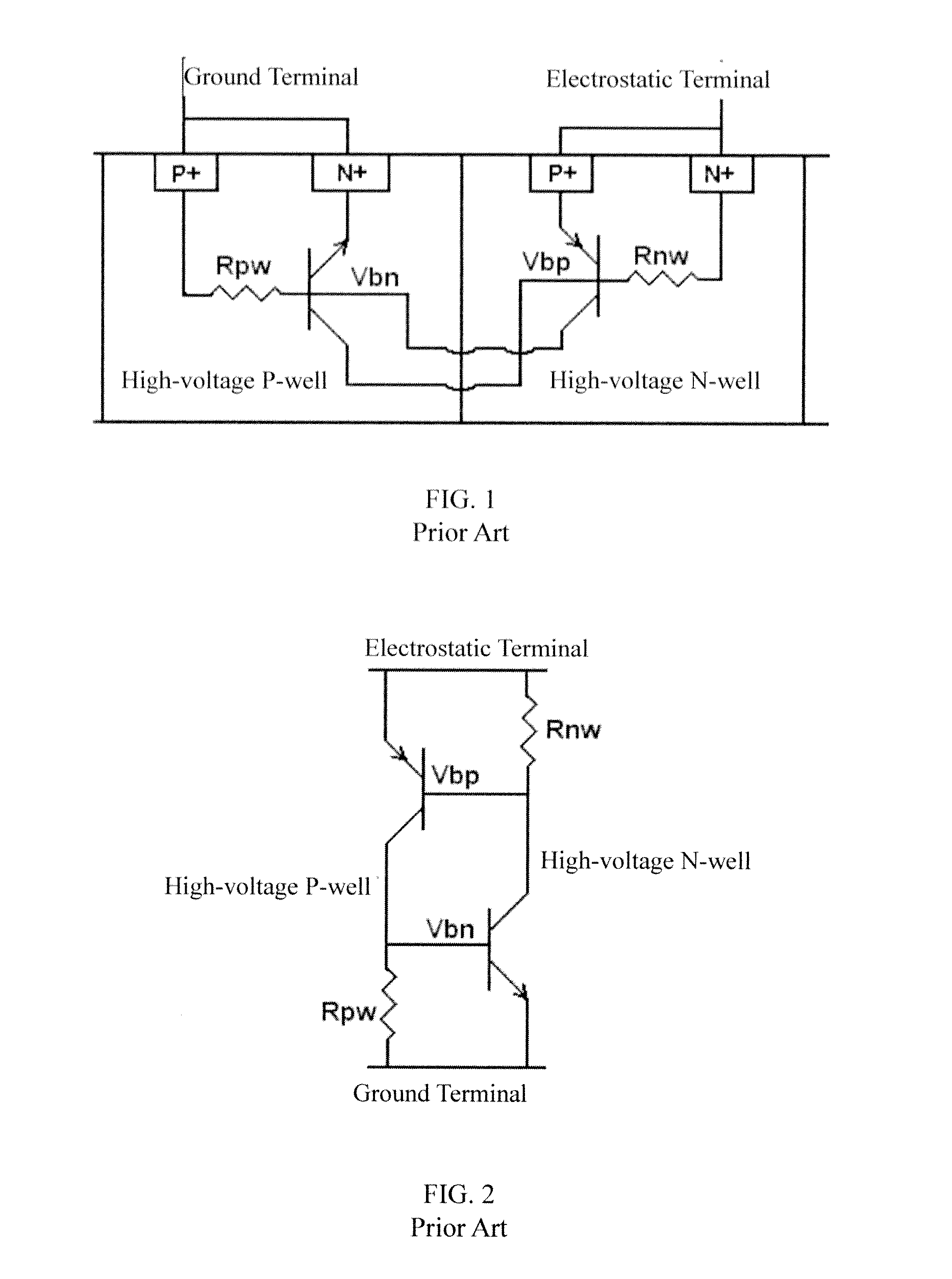

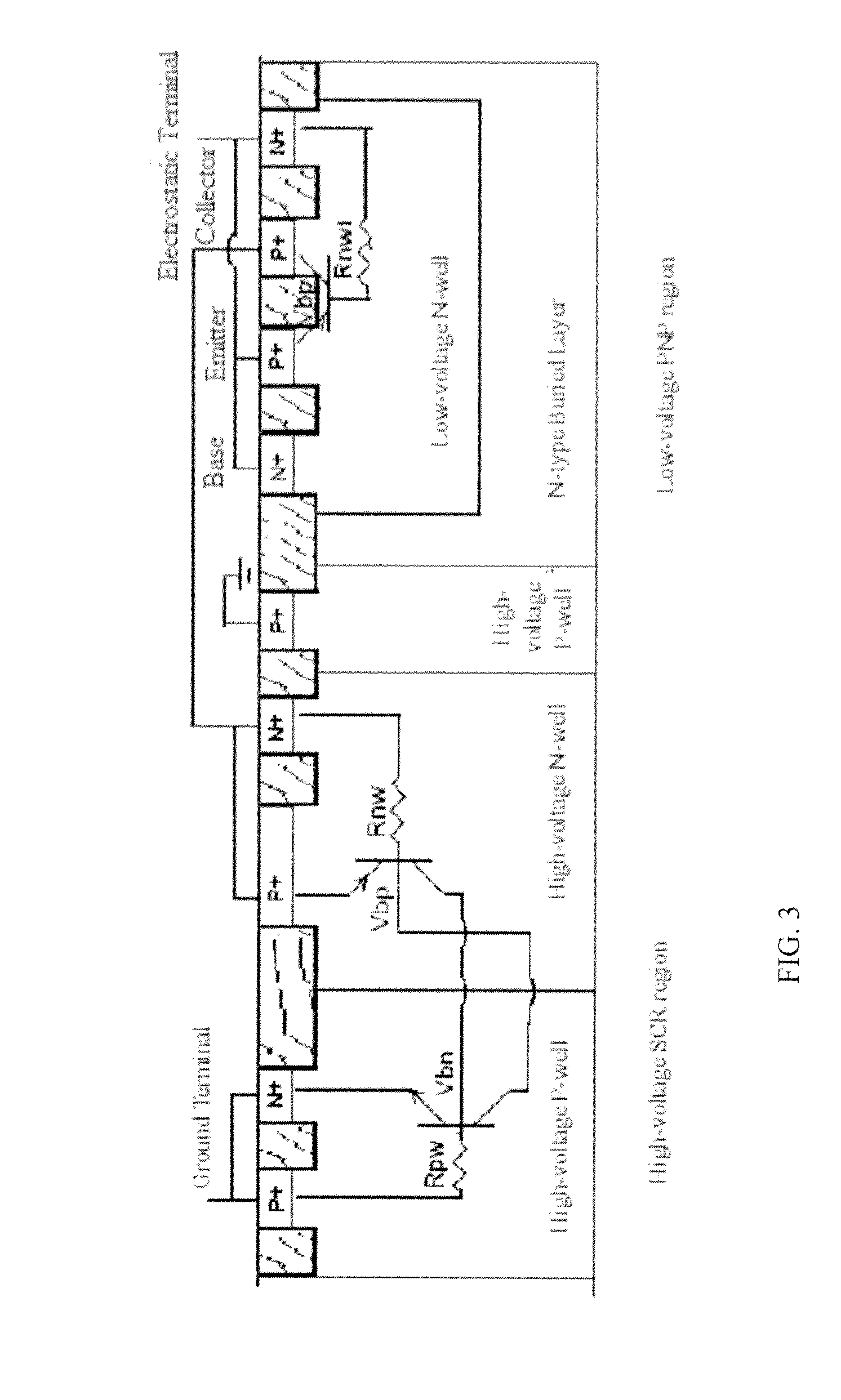

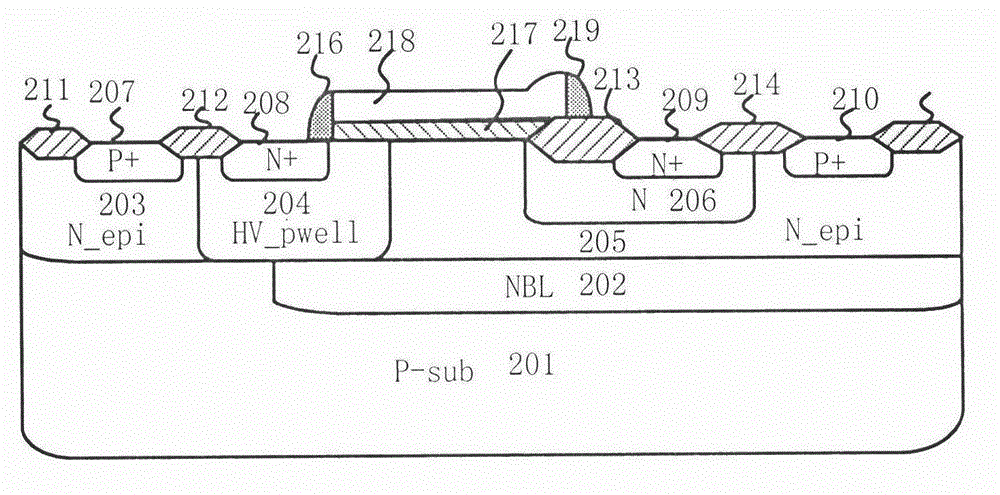

High-voltage ESD protection device

ActiveUS20120091503A1Reduce riskEffective regulationTransistorSolid-state devicesEngineeringHigh pressure

The present invention discloses a high-voltage ESD protection device including a silicon controlled rectifier and a first PNP transistor. The silicon controlled rectifier includes a high-voltage P-well and N-well; a first N+ and P+ diffusion region are formed in the high-voltage P-well; a second N+ and P+ diffusion region are formed in the high-voltage N-well. The first PNP transistor comprises an N-type buried layer; a low-voltage N-well formed in the N-type buried layer; and a base, emitter and collector formed in the low-voltage N-well. The base and emitter are shorted together; the collector is shorted to the second N+ diffusion region and the second P+ diffusion region; the first N+ diffusion region is shorted to the first P+ diffusion region to act as a ground terminal. The high-voltage ESD protection device can effectively adjust the ESD trigger voltage and improve the snapback sustaining voltage after the device is switched on.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

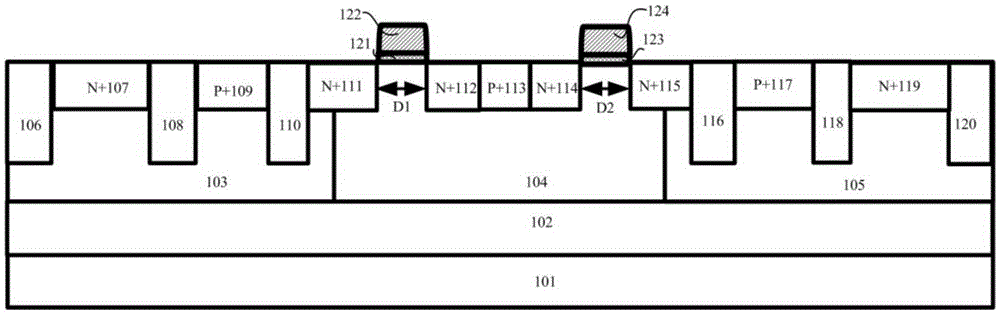

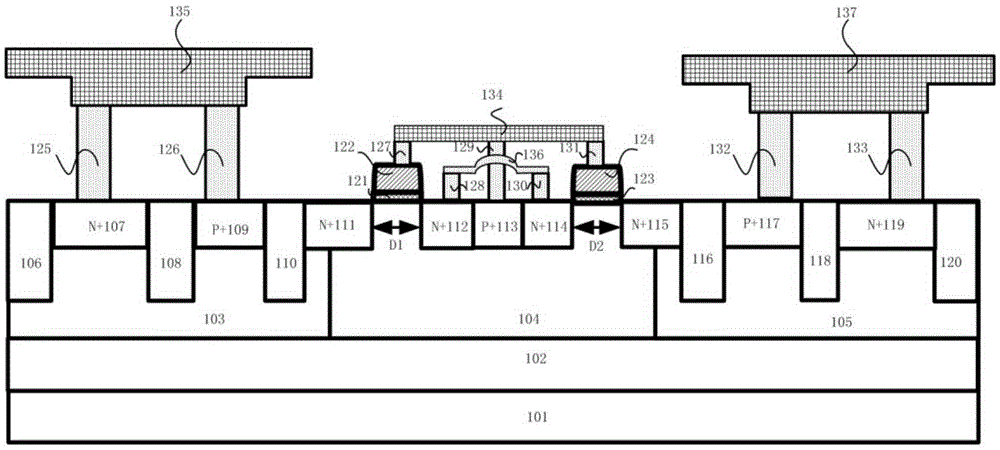

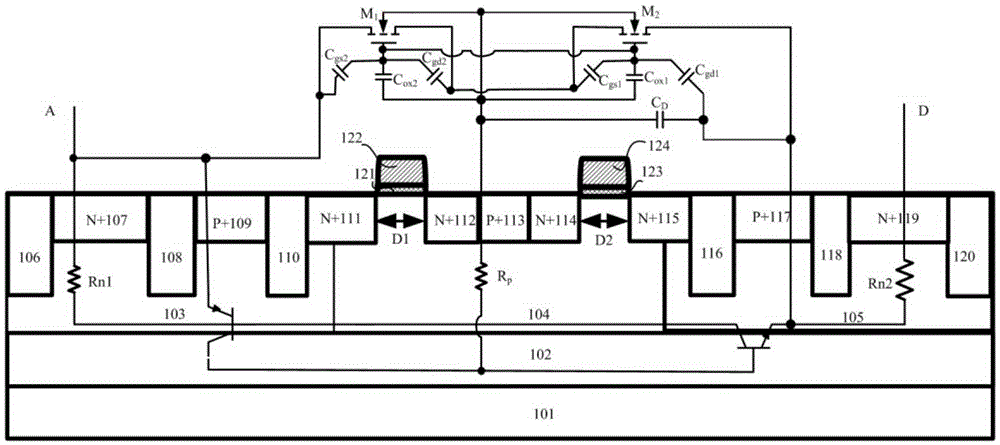

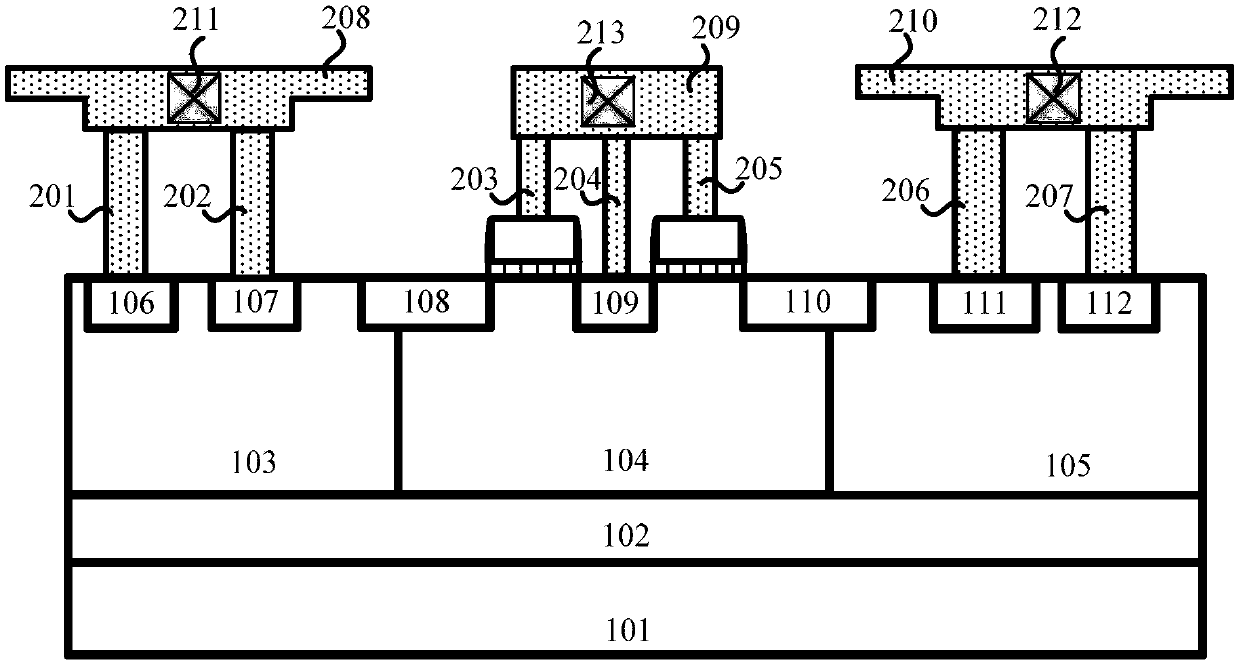

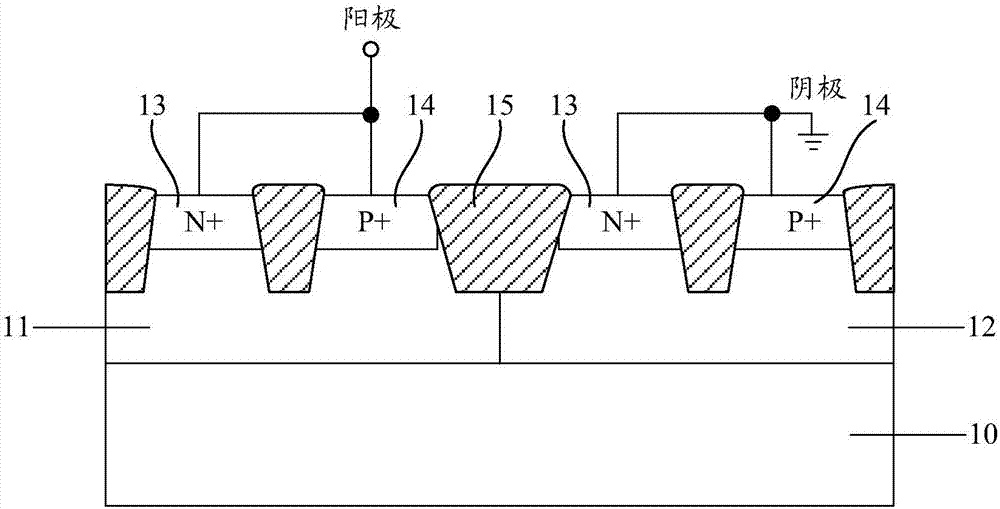

Electronic static discharge (ESD) protection device with bidirectional silicon controlled rectifier (SCR) structure embedded with interdigital N-channel metal oxide semiconductor (NMOS)

ActiveCN105428354AEnhanced ESD robustnessRealize two-way protectionTransistorSemiconductor/solid-state device detailsSilicon-controlled rectifierEngineering

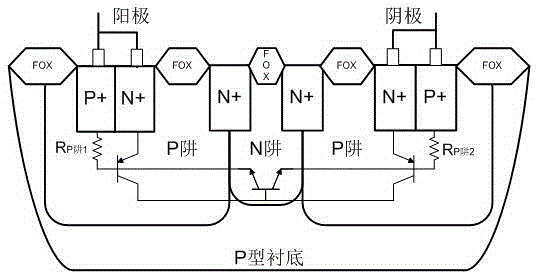

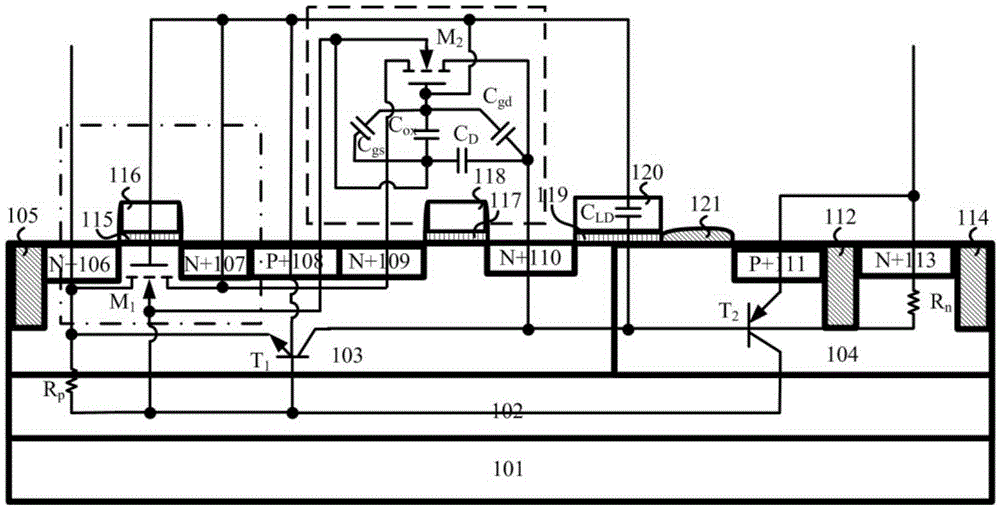

An electronic static discharge (ESD) protection device with a bidirectional silicon controlled rectifier (SCR) structure embedded with an interdigital N-channel metal oxide semiconductor (NMOS) can be applied to an ESD protection circuit of an on-chip integrated circuit (IC) and mainly comprises a P substrate, a P epitaxial layer, a first N pit, a P pit, a second N pit, a first N+ injection region, a first P+ injection region, a second N+ injection region, a third N+ injection region, a second P+ injection region, a fourth N+ injection region, a fifth N+ injection region, a third P+ injection region, a sixth N+ injection region, a plurality of poly-silicon gates, a plurality of thin gate oxide layers and a plurality of shallow isolation grooves. On one hand, under the positive and negative ESD pulse effects, an ESD current discharge path with a symmetric structure and complete same electrical property exists in the device, the ESD current discharge ability of the device can be improved, and bidirectional protection of an ESD pulse is achieved; and on the other hand, the interdigital NMOS composed of an NMOS M<1> and an NMOS M<2> and a parasitic P pit resistor form a resistance-capacitance coupling current path, so that the ESD robustness of the device is enhanced, the current density in an SCR current conduction path is reduced, the conduction resistance of the SCR is increased, and the maintaining voltage is increased.

Owner:JIANGNAN UNIV

Bidirectional tri-path turn-on high-voltage ESD protective device

ActiveCN102983133ACorrection for weak robustnessCorrection speedSolid-state devicesSemiconductor devicesHigh pressurePolysilicon gate

The invention provides a bidirectional tri-path turn-on high-voltage ESD (Electro-Static Discharge) protective device which can be used in an on-chip IC (Integrated Circuit) high-voltage ESD protective circuit. The bidirectional tri-path turn-on high-voltage ESD protective device comprises a P minus substrate, an N plus buried layer, a left N-type epitaxy, a right N-type epitaxy, a drifting area, a high-voltage P trap, a drain region, a source region, a polysilicon gate, a positive pole contact area and a negative pole contact area, wherein the drifting area, the high-voltage P trap, the drain region, the source region and the polysilicon gate form an NLDMOS (laterally diffused metal oxide semiconductor) structure, and the positive pole contact area, the N plus buried layer, the high-voltage P trap and the source region form a positive SCR (semiconductor control rectifier)structure, so that two high-voltage ESD current discharge paths are formed to improve secondary striking current of the device and reduce the turn-on resistance and trigger voltage; and the negative pole contact area, the left N-type epitaxy, the high-voltage P trap, the N plus buried layer and the drain region form a reverse SCR structure to form a reverse high-voltage ESD current discharge path. The current paths of the two SCR structures are longer, so that the maintaining voltage of the device can be improved, bidirectional discharge of ESD current can be realized, and the device has bidirectional ESD protection function.

Owner:铜陵汇泽科技信息咨询有限公司

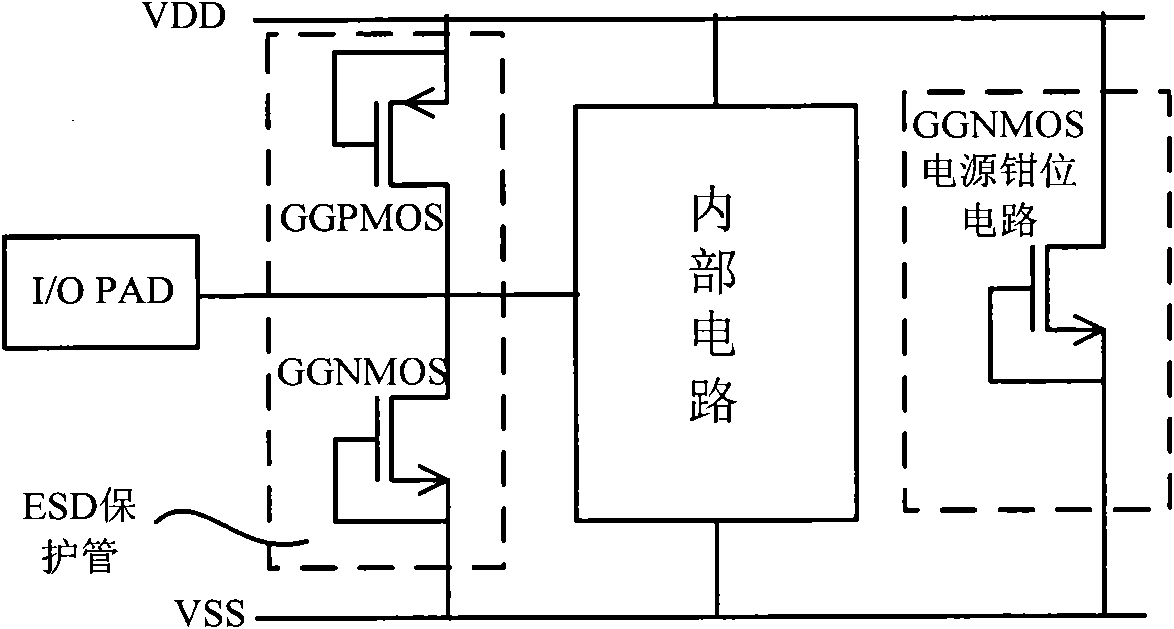

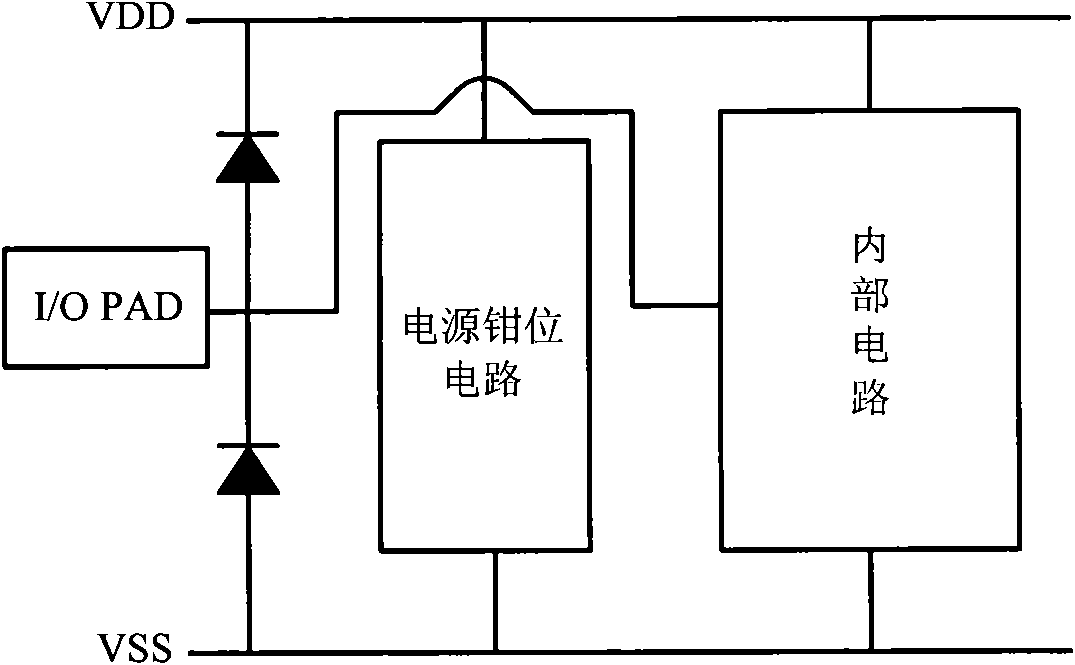

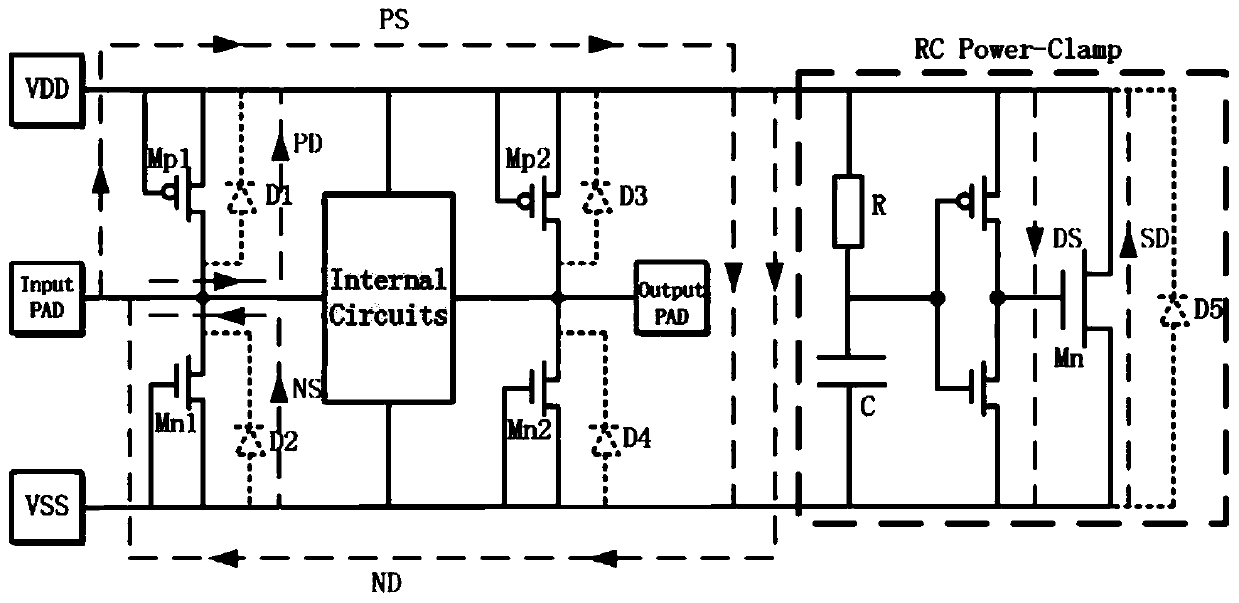

Low-voltage SCR (Silicon Controlled Rectifier) structure for ESD (Electronic Static Discharge) protection of integrated circuit chip

InactiveCN102034811AImprove protectionLower the trigger voltageSolid-state devicesDiodeSilicon-controlled rectifierLow voltage

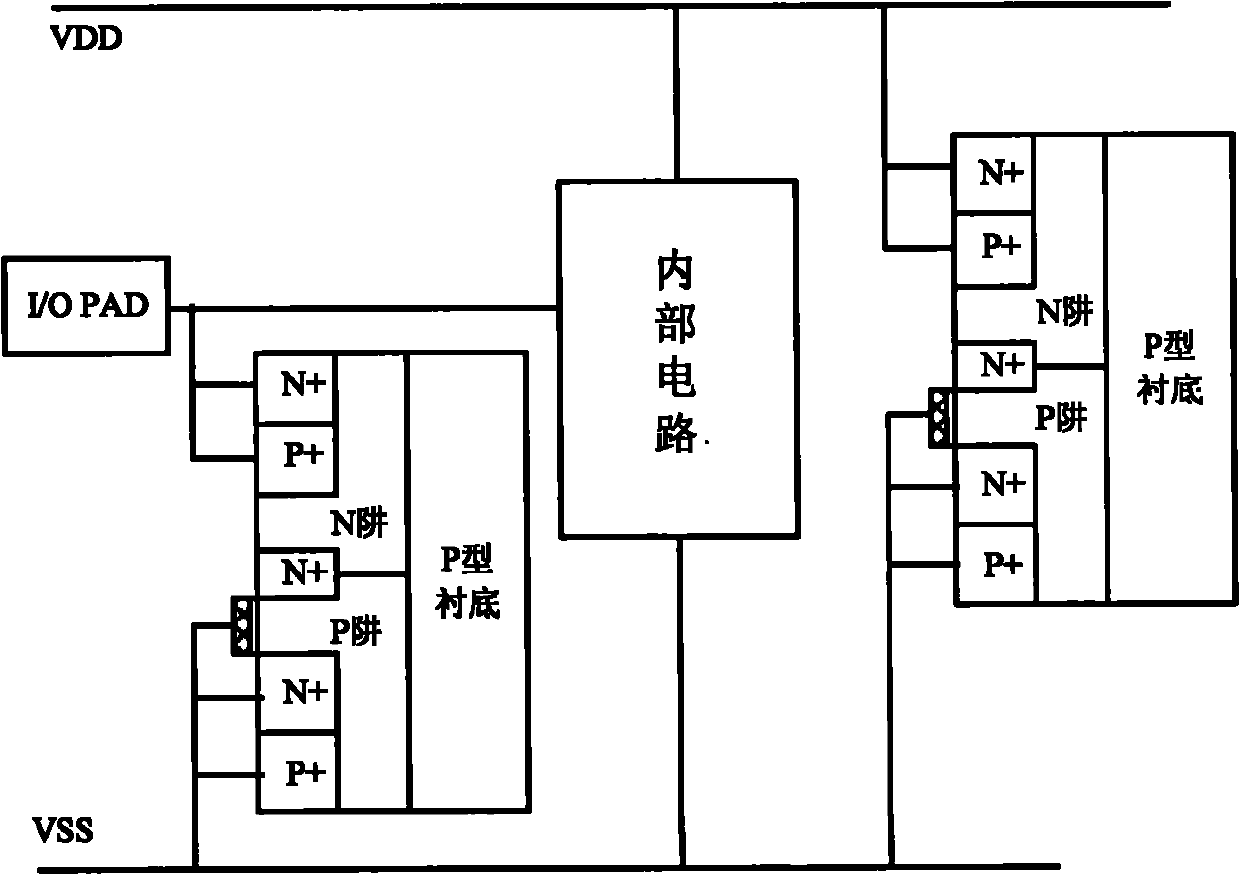

The invention relates to a low-voltage SCR (Silicon Controlled Rectifier) structure for ESD (Electronic Static Discharge) protection of an integrated circuit chip, belonging to the technical field of electronics. The structure comprises two kinds of low-voltage SCR ESD protection devices, wherein the first kind of SCR ESD protection device integrates two N-well diodes and two NMOSs (N-channel Metal Oxide Semiconductors); the N-well diodes are connected between I / O (Input / Output) and a VDD (Virtual Device Driver); the NMOSs are connected between the VDD and VSS (Visual Source Safe); and the N-well diodes and the NMOSs form an SCR structure which provides ESD protection between PS and PD modes and VDD-VSS. The second kind of device integrates two P-well diodes and two PMOSs (P-channel Metal Oxide Semiconductors), wherein the P-well diodes are connected between the I / O and the VSS, and the PMOSs are connected between the VSS and the VDD, and the P-well diodes and the PMOSs jointly form an SCR structure which provides ESD protection between ND and NS modes and VDD-VSS. According to the invention, the chip has higher maintaining voltage and latch-up resistance effect during normal working and has lower triggering voltage and higher triggering speed during ESD; and the low-voltage SCR structure can effectively reduce the relative chip-occupying area of the protection devices and decrease parasitic capacitance at the same time of providing a plurality of modes of ESD protection functions and excellent ESD protection performance.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

SCR ESD protective structure with high maintaining voltage

InactiveCN101764151AGood ESD protection abilityEliminates latch-upThyristorSemiconductor/solid-state device detailsOptoelectronicsElectrostatic discharge

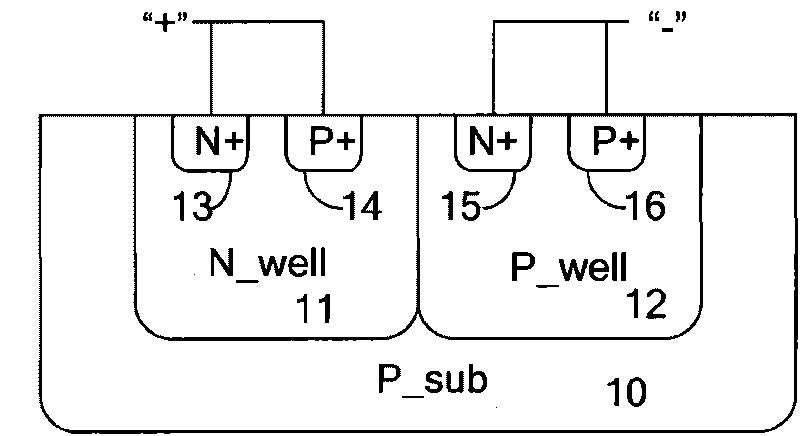

The invention relates to an electrostatic discharge protective SCR structure with high maintaining voltage, which is formed on a device; the device comprises a P-type substrate, an N type buried layer is arranged on the P-type substrate, an N type well is arranged on the N type buried layer, a P-type well parallel to the N type well is also arranged on the P-type substrate, a first N+ doping region and a first P+ doping region are arranged in the N type well, the first N+ doping region and the first P+ doping region are led out through a contact hole and are connected together for being used as the anode of the device, a second N+ doping region and a second P+ doping region are arranged in the P+ doping region, the second N+ doping region and the second P+ doping region are led out through the contact hole and are connected together for being used as the cathode of the device. The SCR structure is composed of the P+ doping region, the N+ doping region and the P-type well region in the N type well and the N+ doping region in the P-type well, the N well resistance is increased by the buried layer between the P-type substrate and the N type well under a maintaining state, so as to increase the maintaining voltage.

Owner:SUZHOU POWERON IC DESIGN

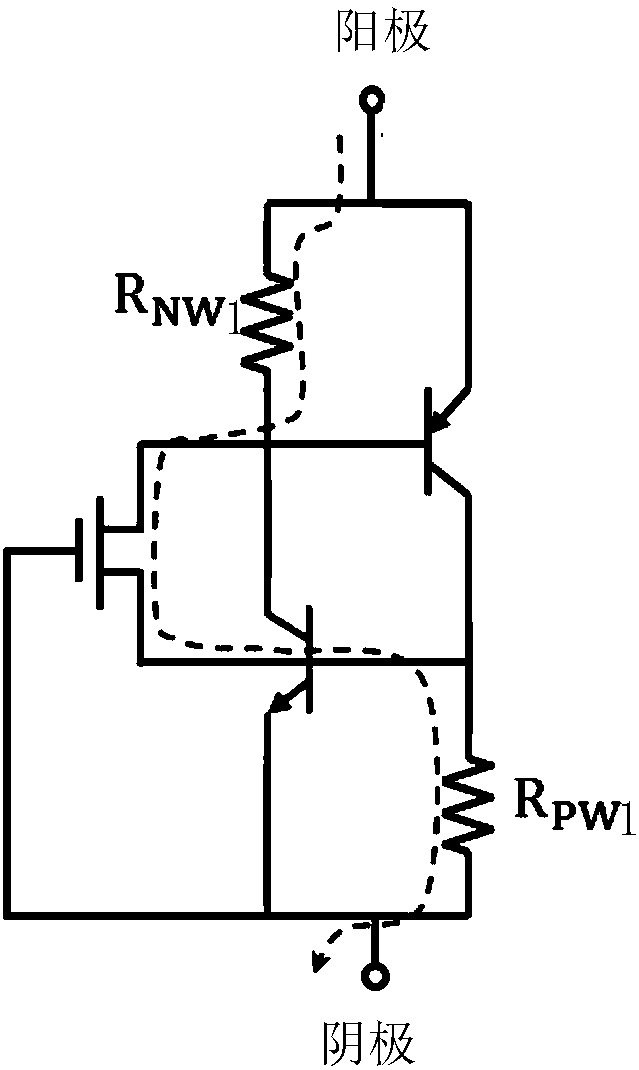

Low voltage triggering silicon controlled rectifier and circuit thereof

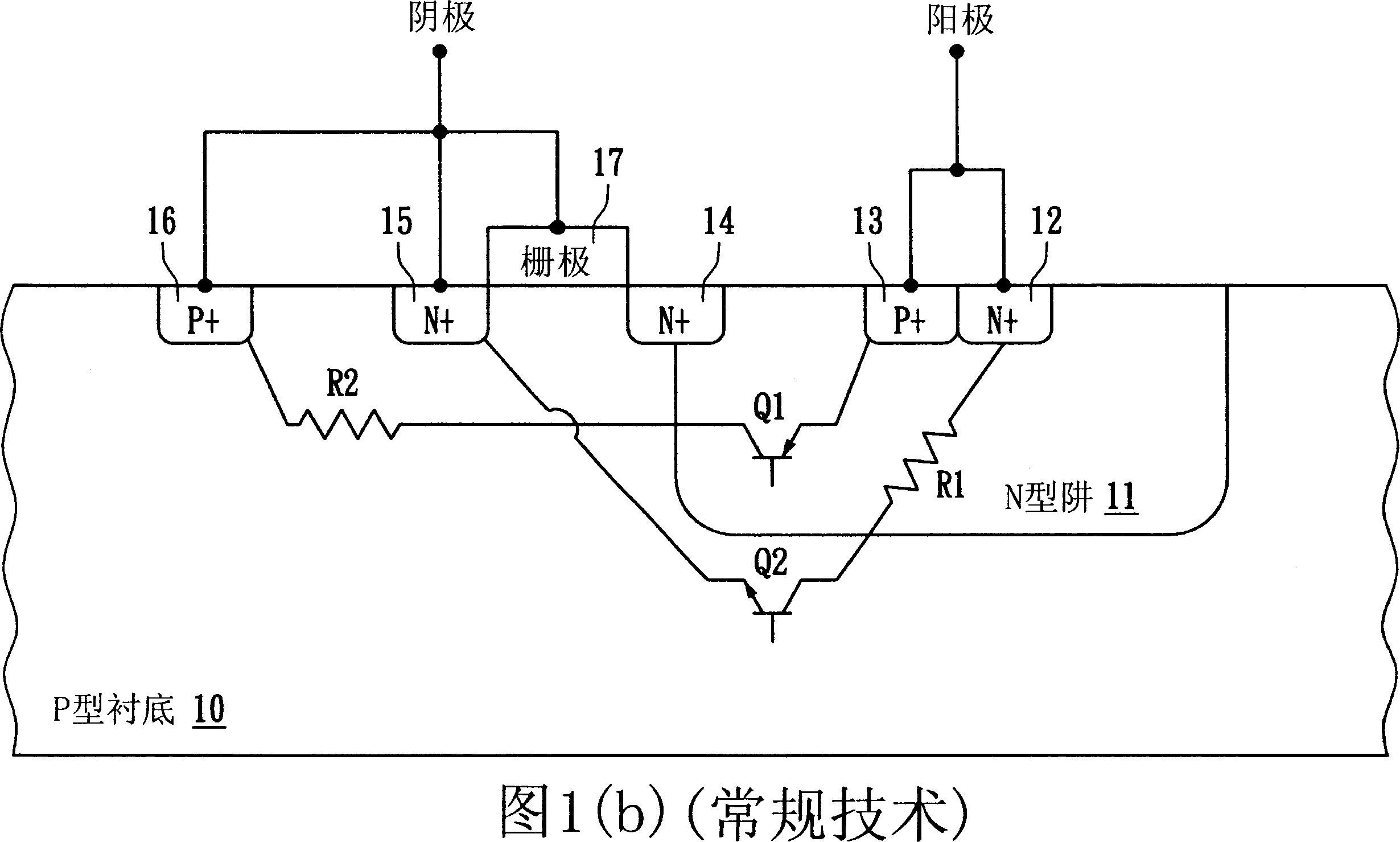

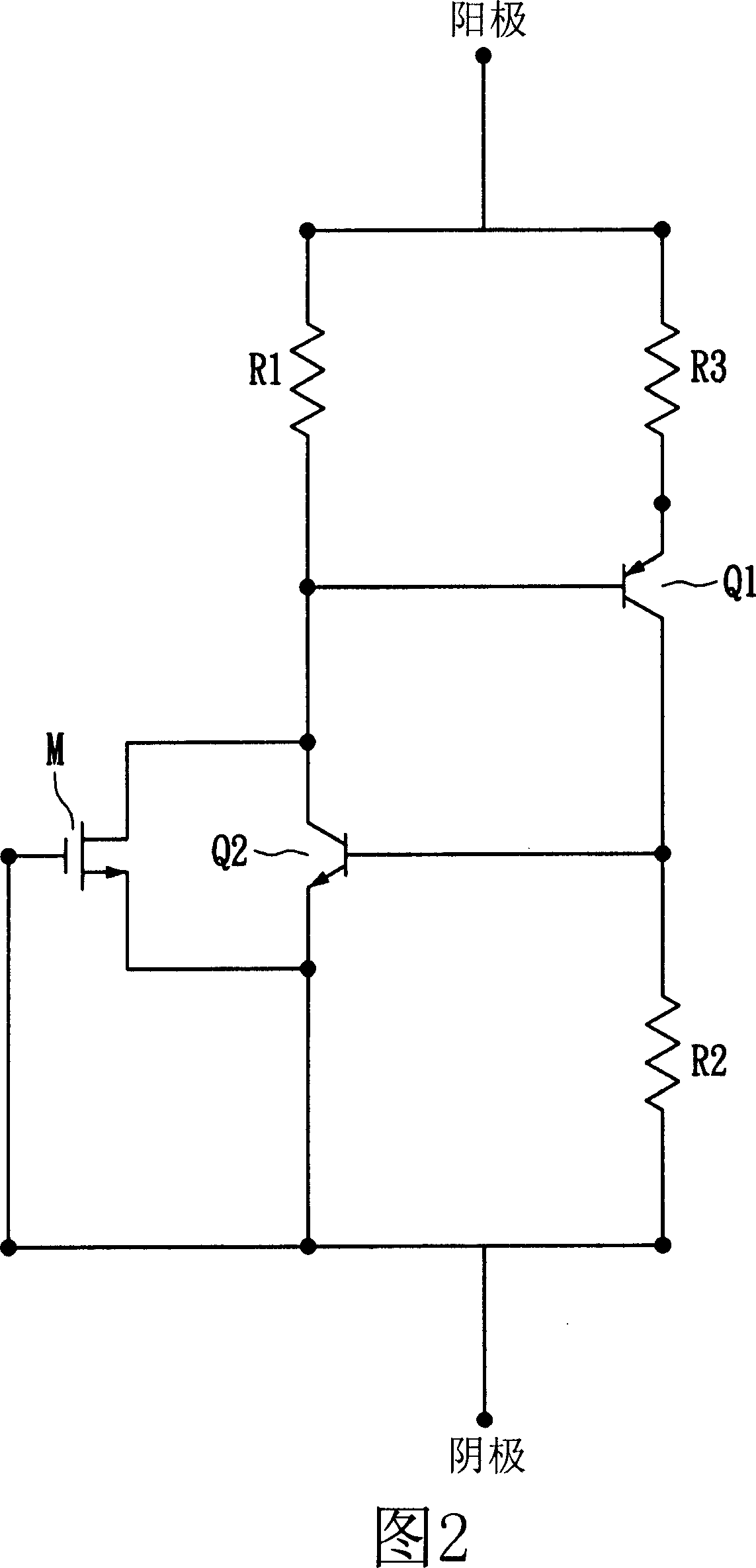

InactiveUS20070228412A1Increase holding voltageTransistorThyristorSilicon-controlled rectifierLow voltage

A low voltage triggering silicon controlled rectifier (LVTSCR) is disclosed. The LVTSCR utilizes an added resistor disposed in a second doped region between the anode of the LVTSCR and the emitter of the parasitical bipolar PNP transistor to increase the holding voltage thereof when the LVTSCR is triggered. The LVTSCR includes a semiconductor substrate with a first conductive type and a gate. The semiconductor substrate includes a first doped region with a second conductive type, a second doped region with the first conductive type, a third doped region with the second conductive type, a fourth doped region with the second conductive type and a fifth doped region with the first conductive type. The gate is applied with a lower triggering voltage to trigger the LVTSCR.

Owner:ADVANCED ANALOG TECH INC

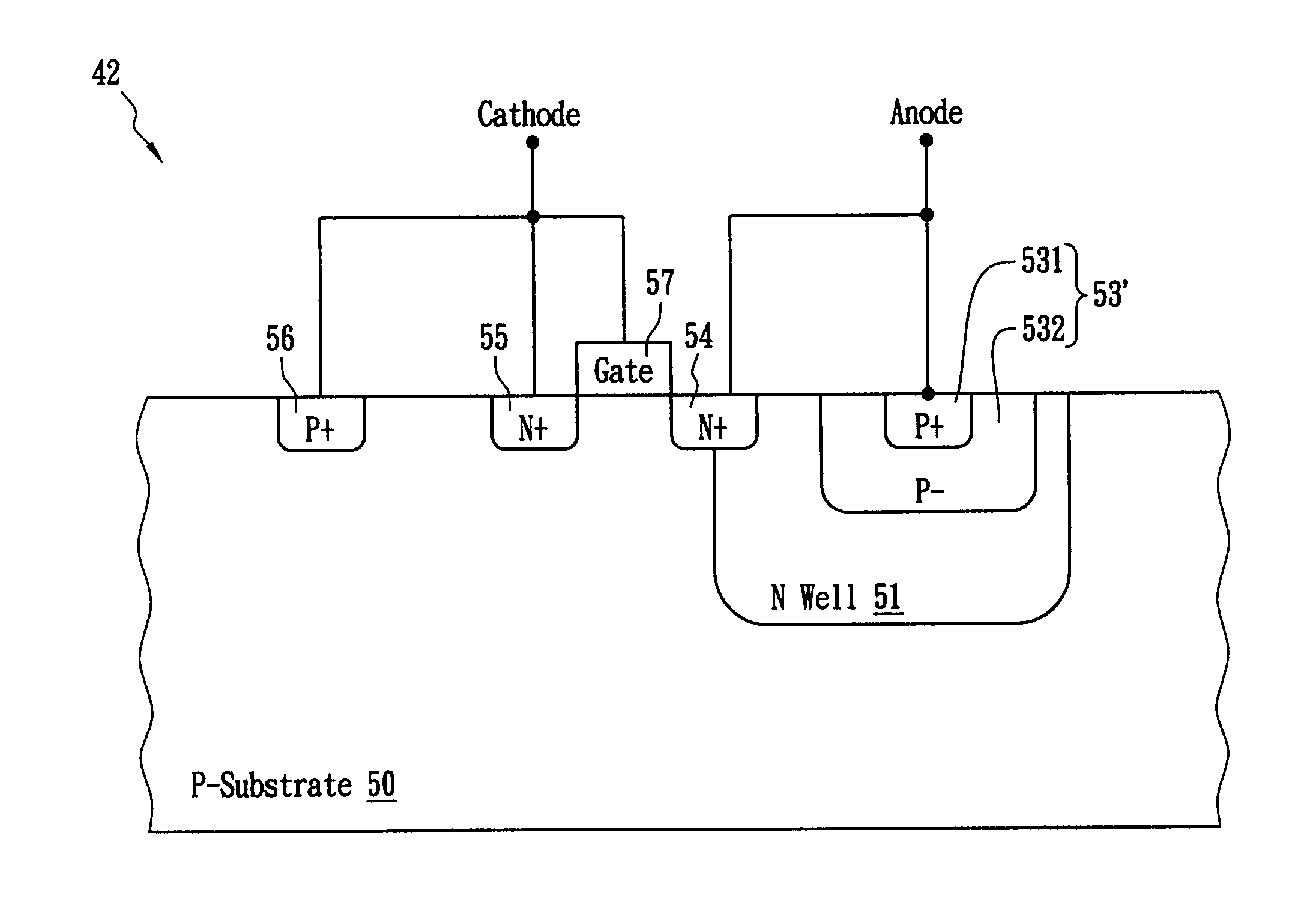

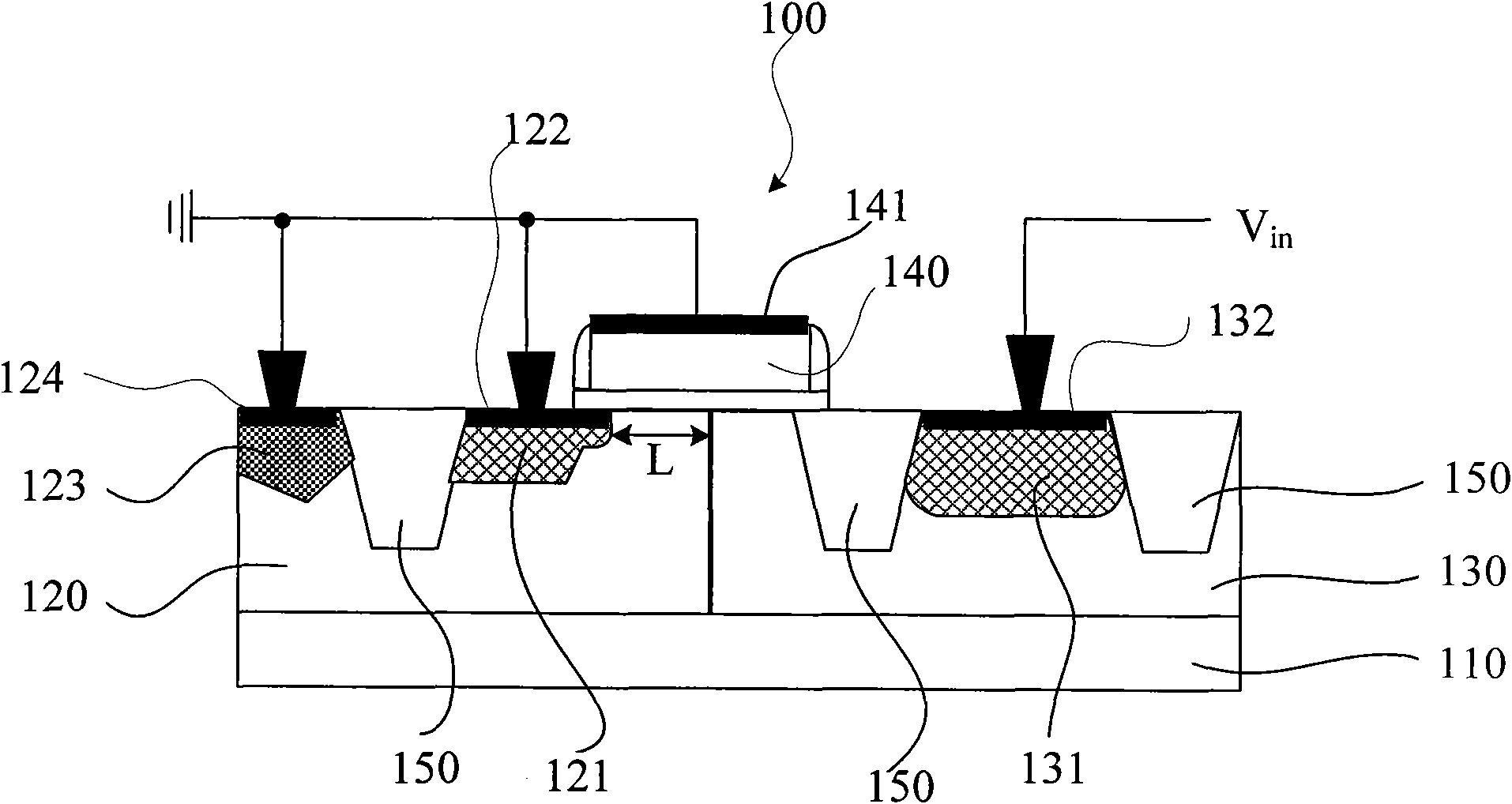

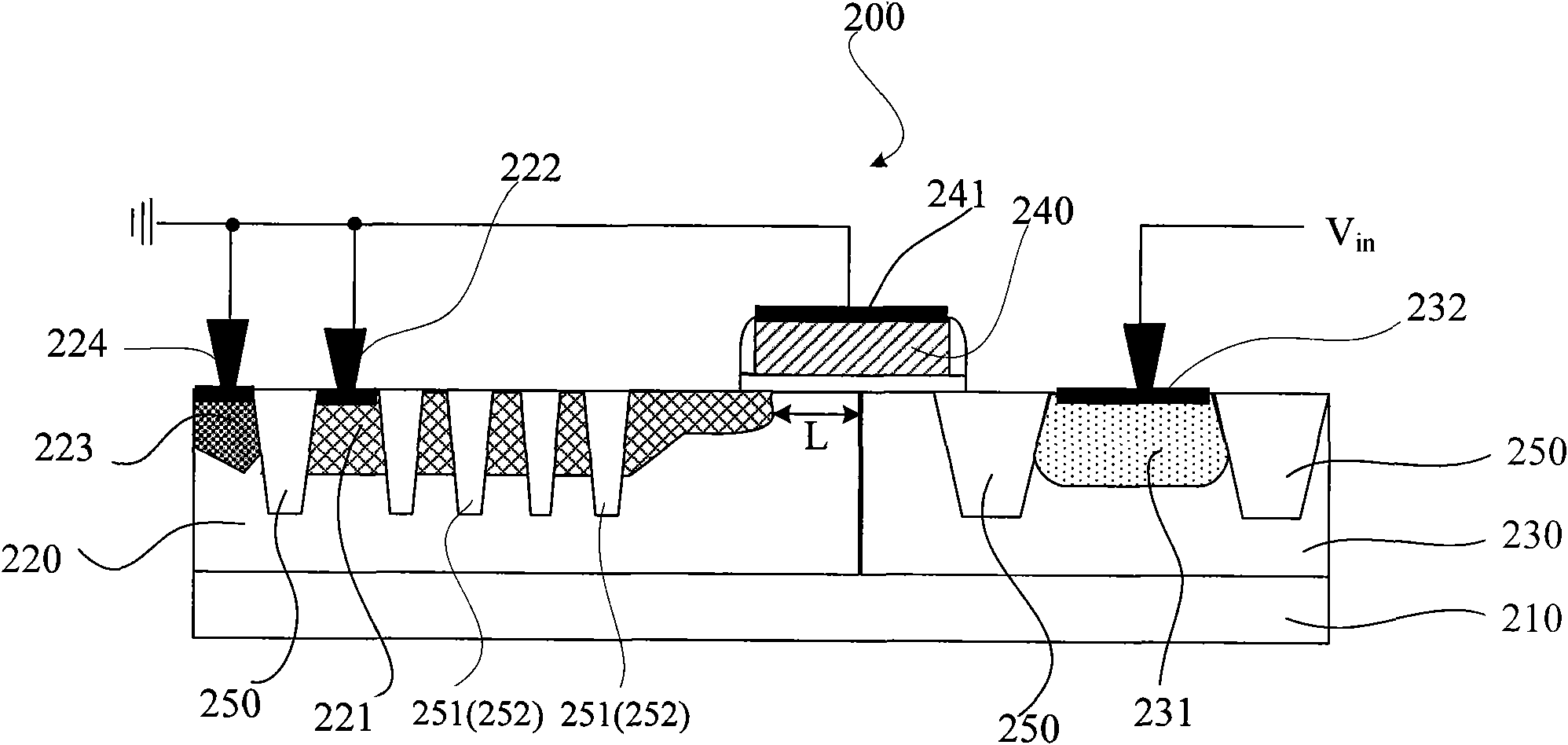

Un-assisted, low-trigger and high-holding voltage scr

ActiveUS20080253046A1Sacrificing ESD protection robustnessHigh n-type doping densityTransistorSemiconductor/solid-state device detailsEngineeringIntegrated circuit

A protective SCR integrated circuit device is disclosed built on adjacent N and P wells and defining an anode and a cathode. In addition to the anode and cathode contact structures, the device has an n-type stack (N+ / ESD) structure bridging the N-Well and the P-Well, and a p-type stack (P+ / PLDD) structure in the P-Well. The separation of the n-type stack structure and the p-type stack structure provides a low triggering voltage, that together with other physical dimensions and processing parameters also provide a relatively high holding voltage. In an embodiment, the triggering voltage may be about 8V while exhibiting a holding voltage, that may be controlled by the lateral dimension of the n-type stack of about 5-7 V.

Owner:SEMICON COMPONENTS IND LLC

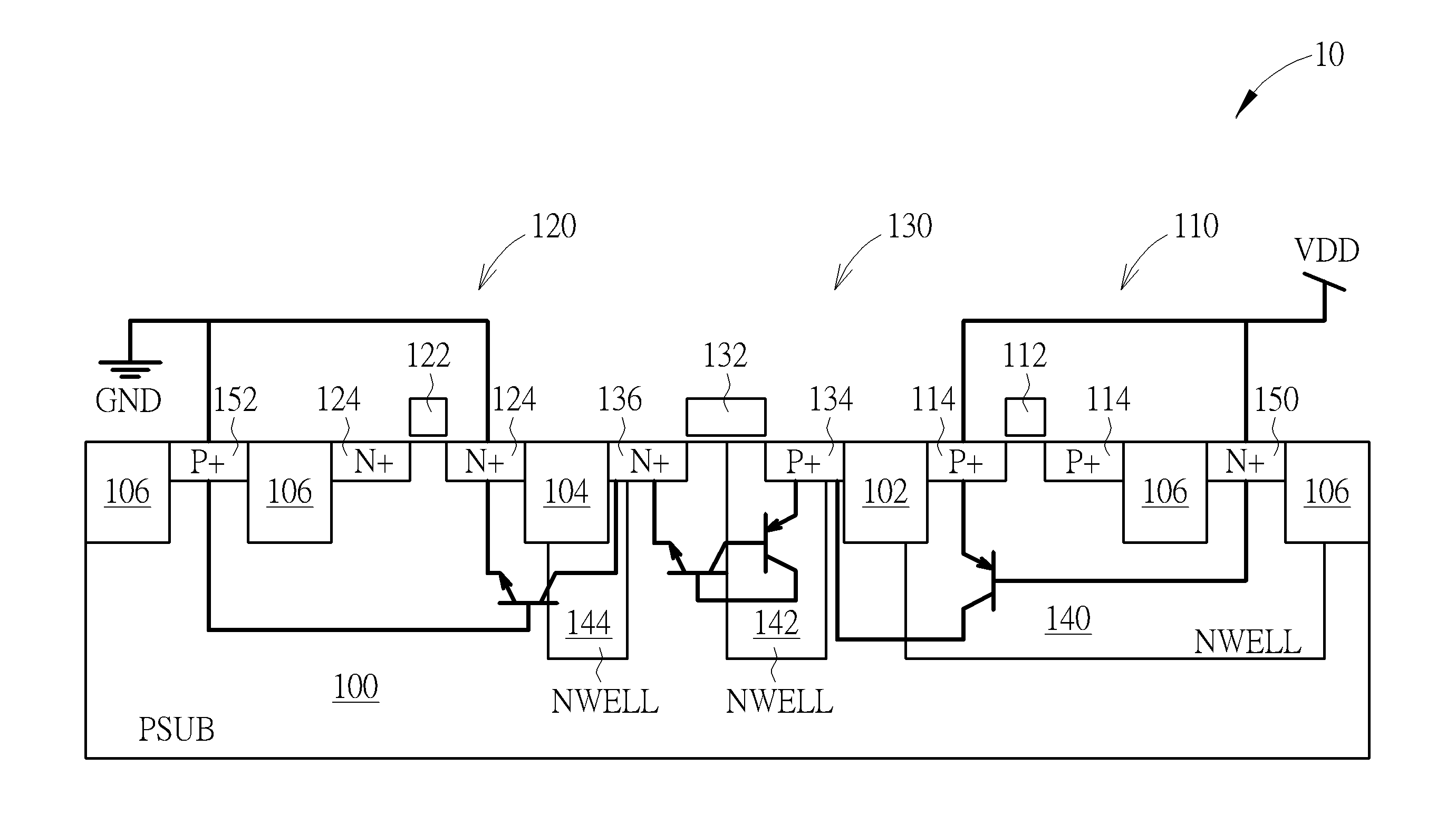

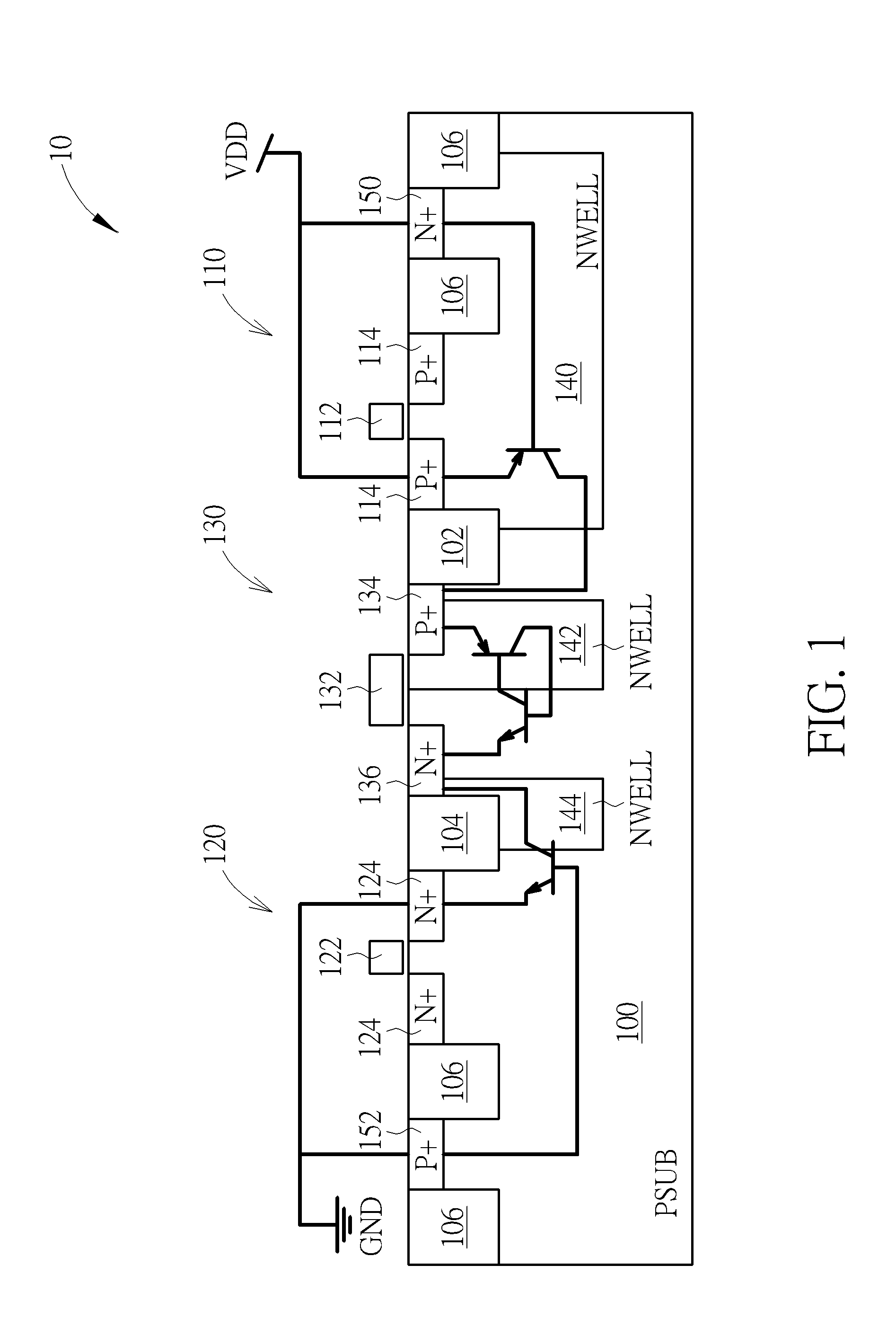

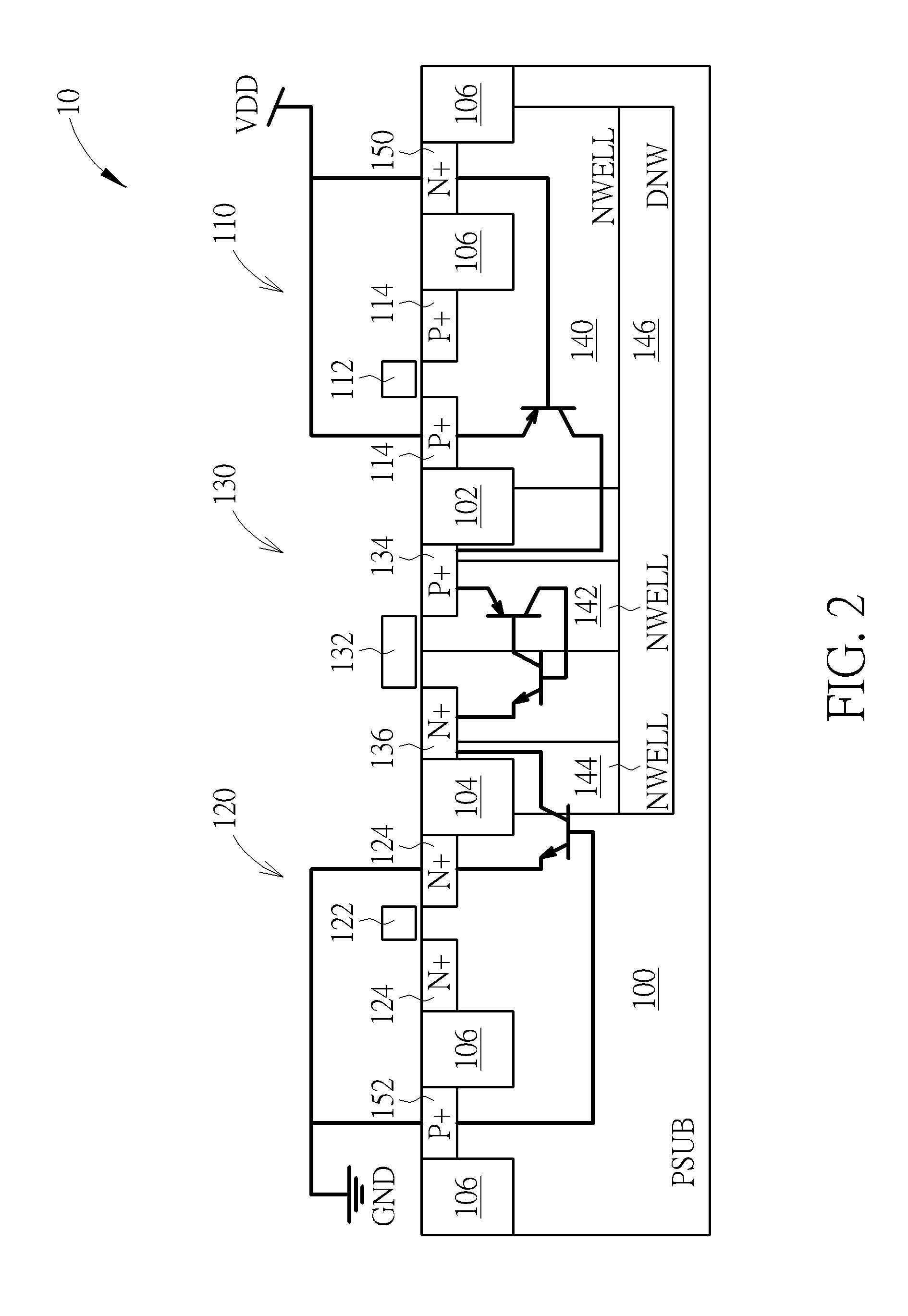

Complementary metal-oxide-semiconductor device

ActiveUS20150123184A1Increase holding voltageIncrease layout areaTransistorSemiconductor/solid-state device detailsCMOSEngineering

A CMOS device includes a substrate, a pMOS transistor and an nMOS transistor formed on the substrate, and a gated diode. The gated diode includes a floating gate formed on the substrate in between the pMOS transistor and the nMOS transistor and a pair of a p-doped region and an n-doped region formed in the substrate and between the pMOS transistor and the nMOS transistor. The n-doped region is formed between the floating gate and the nMOS transistor, and the p-doped region is formed between the floating gate and the pMOS transistor.

Owner:UNITED MICROELECTRONICS CORP

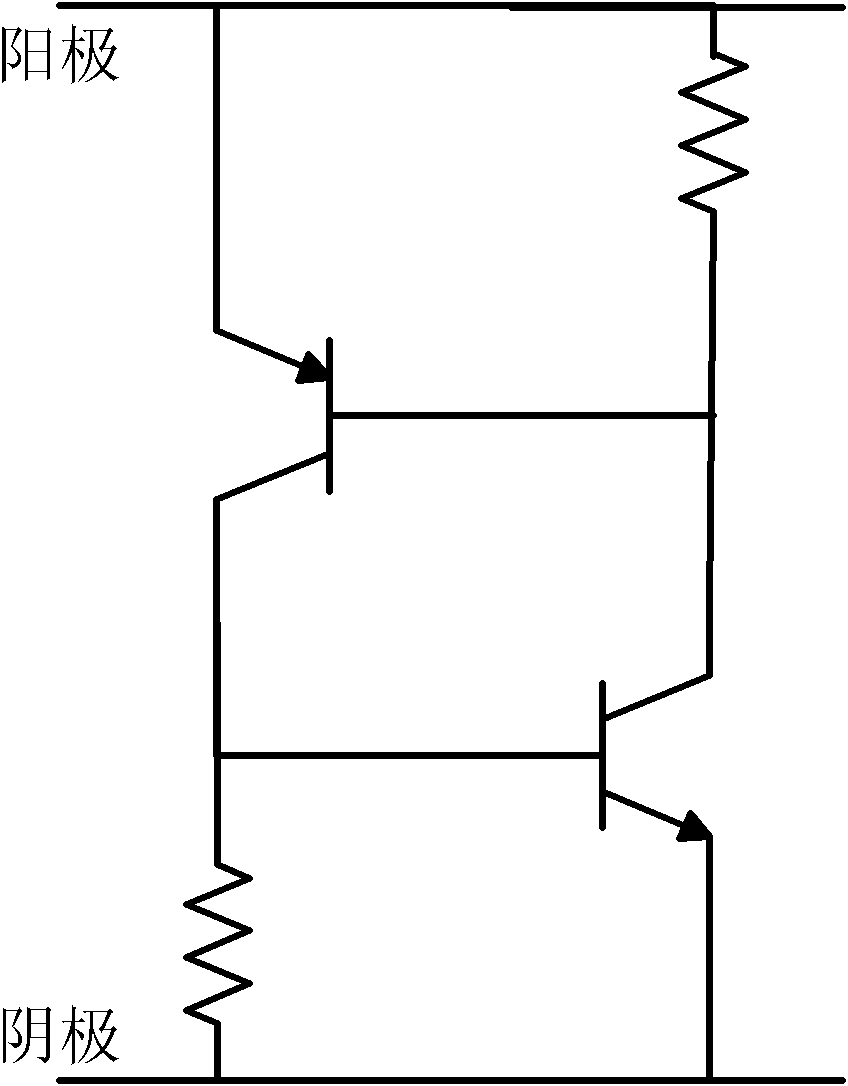

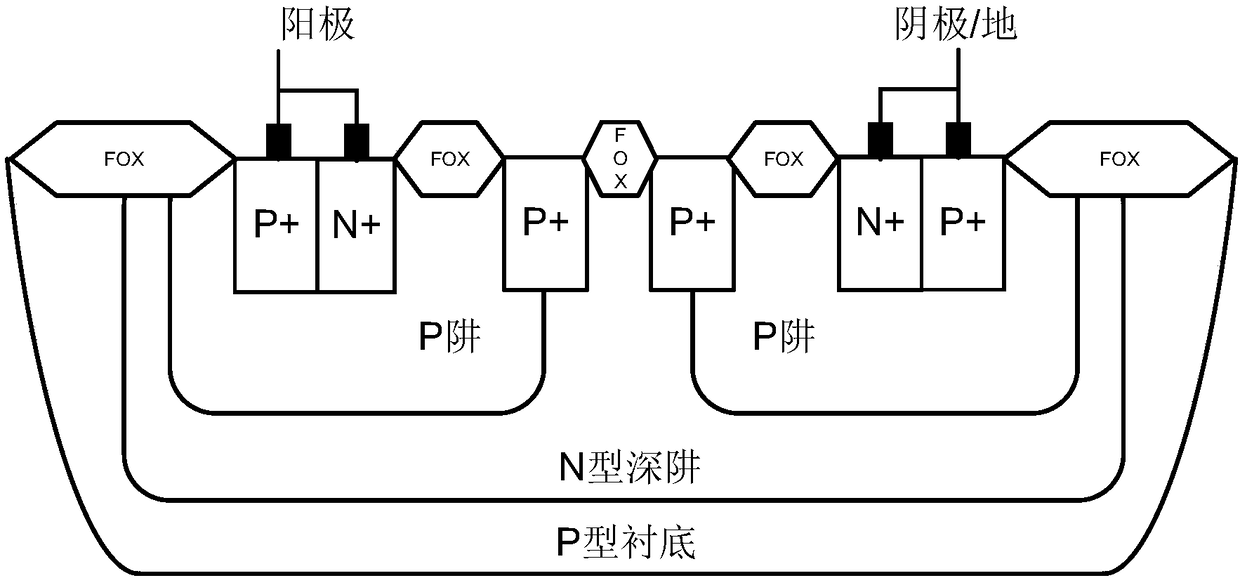

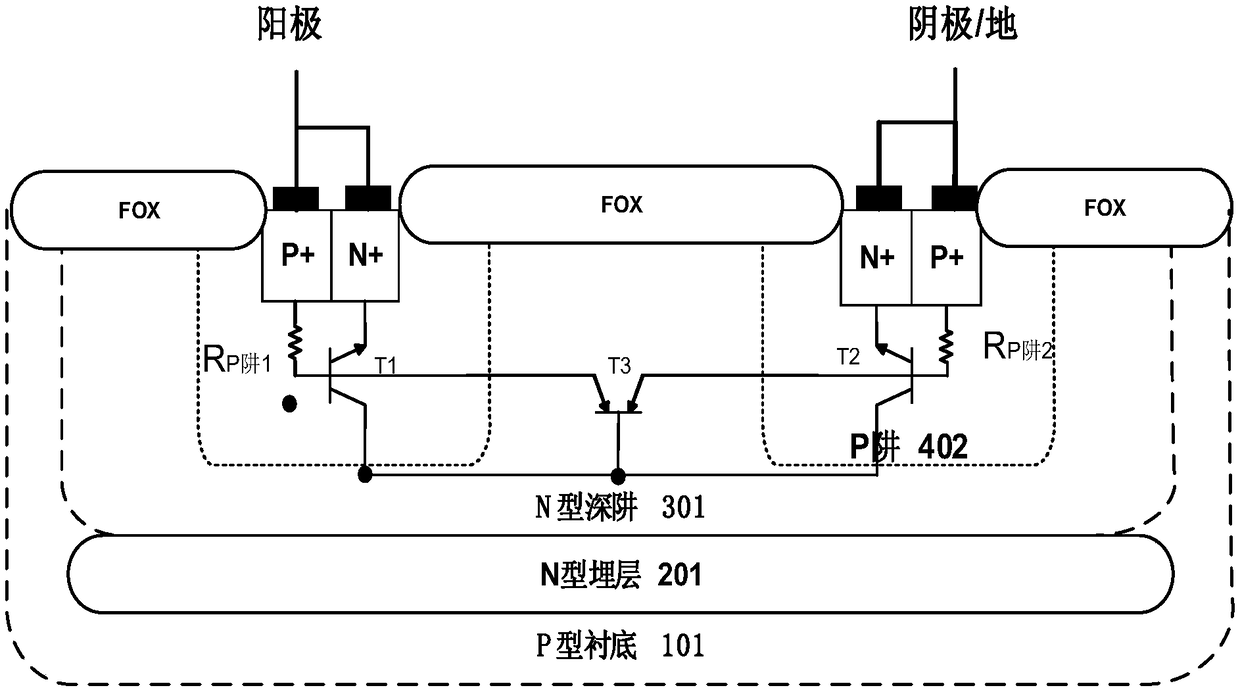

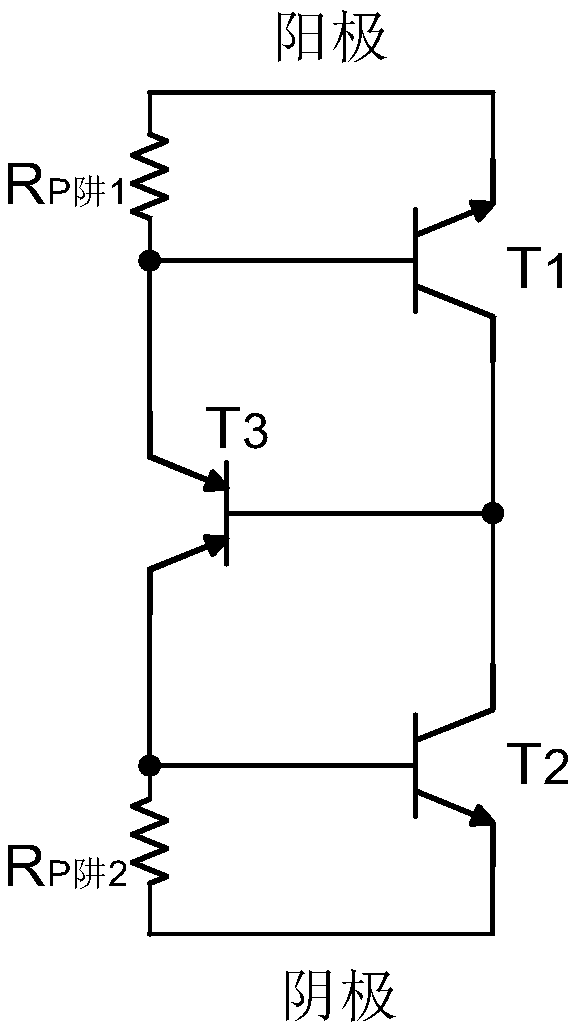

Bidirectional transient voltage suppression device

ActiveCN105374815AIncrease holding voltageImprove electrostatic discharge capacity per unit areaThyristorSolid-state devicesOvervoltageTransient voltage suppressor

The invention discloses an NPNPN-type bidirectional transient voltage suppression device which is based on a silicon planar process, has high maintaining voltage and high peak current, and is capable of bidirectionally clamping transient overvoltage. The NPNPN-type bidirectional transient voltage suppression device comprises a P-type substrate, wherein an N-type deep pit is arranged on the P-type substrate, a first P pit, a first N pit and a second P pit are arranged in the N-type deep pit, a first P+ injection region, a first N+ injection region, a second N pit and a second N+ injection region are sequentially arranged in the P pit from left to right, the second N+ injection region bridges the first P pit and the first N pit, a third N+ injection region, a third N pit, a fourth N+ injection region and a fifth P+ injection are sequentially arranged in the second P pit from left to right, the third N+ injection region bridges the second P pit and the first N pit, the first P+ injection region and the first N+ injection region are connected with a positive electrode, and the fourth N+ injection region and the second P+ injection region are connected to a negative electrode. The device can be used for transient overvoltage suppression on a chip pin with a signal level of (-5)V to (+5)V.

Owner:SUPERESD MICROELECTRONICS TECH CO LTD

Low trigger voltage silicon control rectifier and its circuit

InactiveCN101047178AIncrease the trigger voltageLower the trigger voltageSolid-state devicesSemiconductor devicesSilicon-controlled rectifierElectrical conductor

The present invention relates to a low voltage triggering silicon controlled rectifier (SCR). It is characterized by that it utilizes addition of second doped zone which is set between the described low voltage triggering silicon controlled rectifier anode and its parasitic PNP transistor emitter to raise the holding voltage when the described low voltage triggering silicon controlled rectifier is triggered. The described low voltage triggering silicon controlled rectifier includes a semiconductor substrate with first conducting type and a grid. The described semiconductor substrate contains a first doped zone with second conducting type, a second doped zone with first conducting type, a third doped zone with second conducting type, a fourth doped zone with second conducting type and a fifth doped zone with first conducting type. The described grid is characterized by utilizing lower trigger voltage to trigger the described low voltage triggering silicon controlled rectifier.

Owner:ADVANCED ANALOG TECH INC

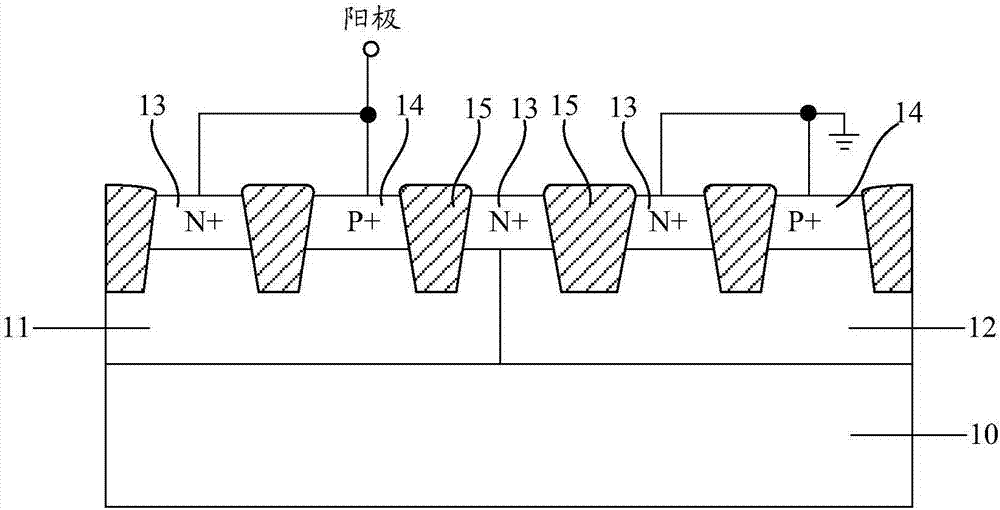

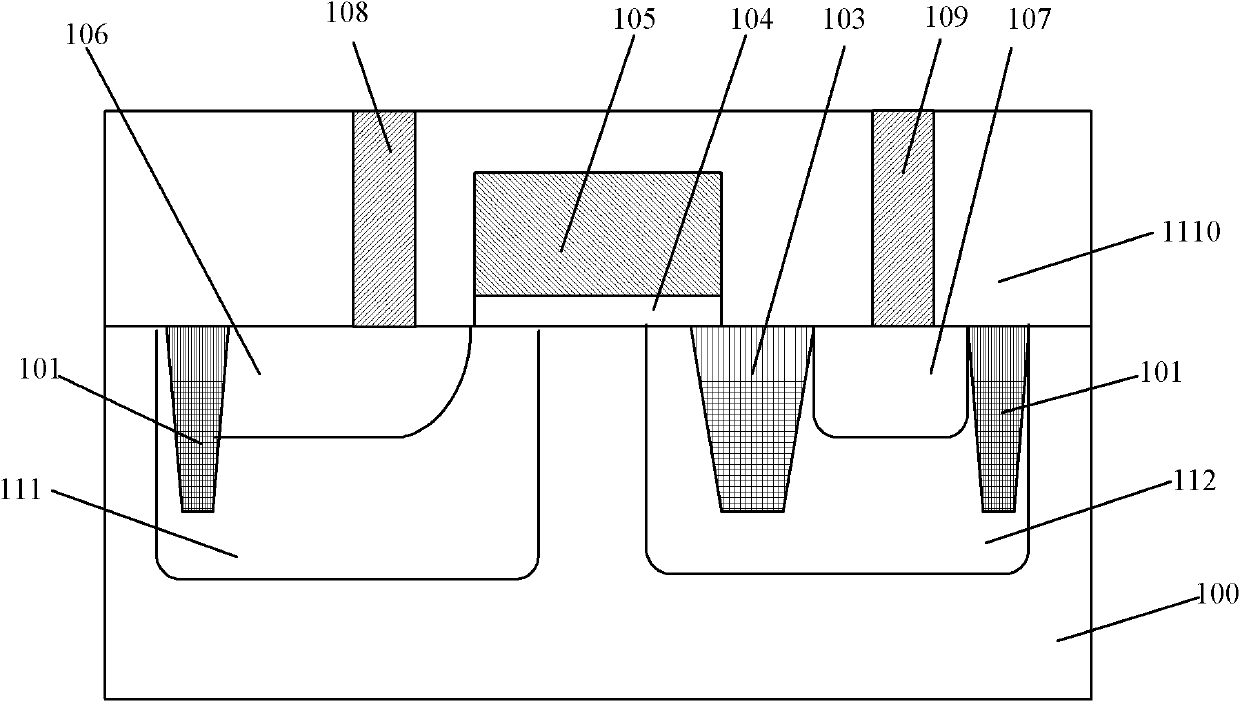

LDMOS-SCR device with source-end embedded finger NMOS

ActiveCN105390491AEnhanced ESD robustnessImprove discharge capacityTransistorSemiconductor/solid-state device detailsLDMOSResistance capacitance

The invention provides an LDMOS-SCR device with a source-end embedded finger NMOS, which can be applied to improving ESD protection reliability of an on-chip IC. The LDMOS-SCR device with the source-end embedded finger NMOS mainly comprises a P substrate, a P epitaxy, a P well, an N well, a first N+ injection region, a second N+ injection region, a first P+ injection region, a third N+ injection region, a fourth N+ injection region, a second P+ injection region, a fifth N+ injection region, a plurality of polysilicon gates, a plurality of thin gate oxides and a plurality of field oxide insulation regions. On one hand, the second P+ injection region, a third polysilicon gate, the fifth N+ injection region, the N well, the P well, the first P+ injection region, the first N+ injection region form a parasitical LDMOS-SCR current path, thereby reinforcing the ESD robustness of the LDMOS-SCR device; on the other hand, the first N+ injection region, a first polysilicon gate, a first thin gate oxide, the second N+ injection region, the first P+ injection region, the third N+ injection region, a second polysilicon gate, a second thin gate oxide and the fourth N+ injection region form the finger NMOS and a parasitic resistor, thereby forming a resistance-capacitance coupling effect; thereby, the maintaining voltage is increased.

Owner:JIANGNAN UNIV

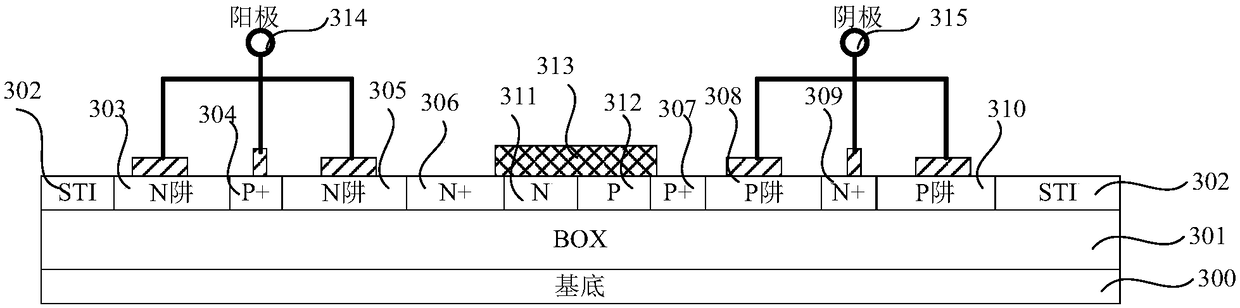

SCR electrostatic protection device and electrostatic protection circuit

InactiveCN108336082ALow spurious noiseLower the trigger voltageTransistorSolid-state devicesDevice formEngineering

The invention provides an SCR electrostatic protection device and an electrostatic protection circuit. The SCR electrostatic protection device formed in a continuous active region of a top semiconductor layer on an insulating layer includes two N wells encircling a P doping region of an SCR and two P wells encircling an N doping region of the SCR to form a finger type diode structure, so that a parasitic PNP transistor and a parasitic NPN transistor of the SCR are formed; an additional N doping region adjacent to one N well and an additional P doping region adjacent to one P well are added between each two adjacent N well and P well and thus a parasitic gate controlled diode or PN junction diode is generated between the N well and the P well, so that the base electrode of the parasitic PNPtriode is connected to the base electrode of the parasitic NPN triode by the parasitic gate controlled diode or PN junction diode. According to the SCR electrostatic protection device and the electrostatic protection circuit, the low SCR trigger voltage and high maintaining voltage are provided and electrostatic protection is provided for the integrated circuit formed by processes like an SOI.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

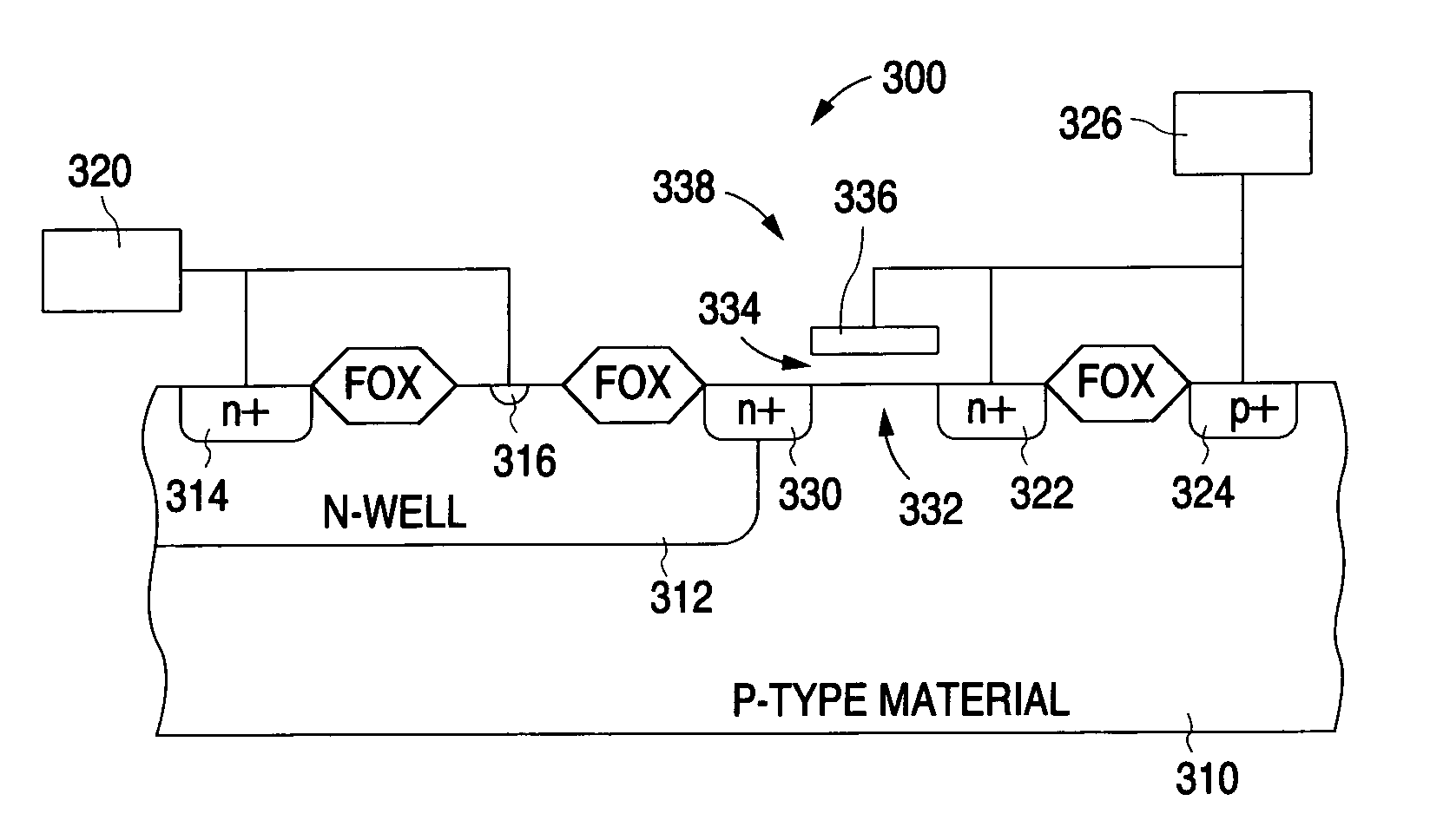

High holding voltage ESD protection structure and method

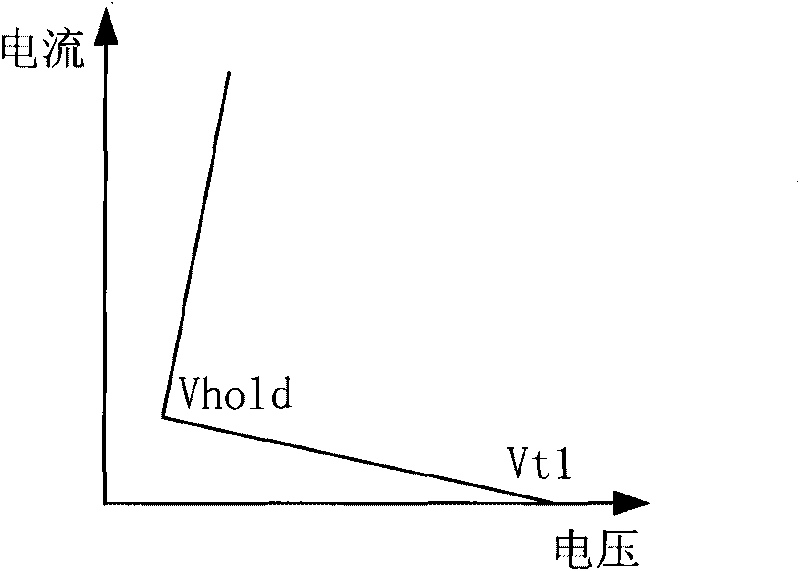

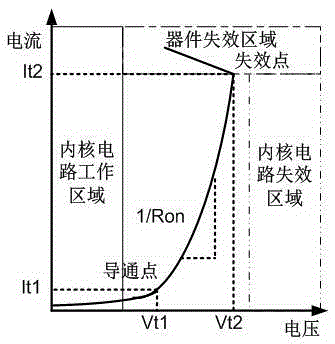

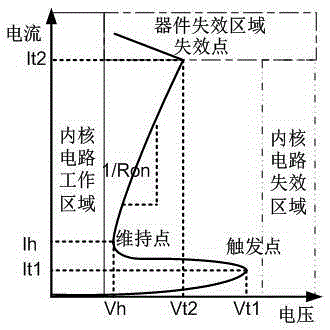

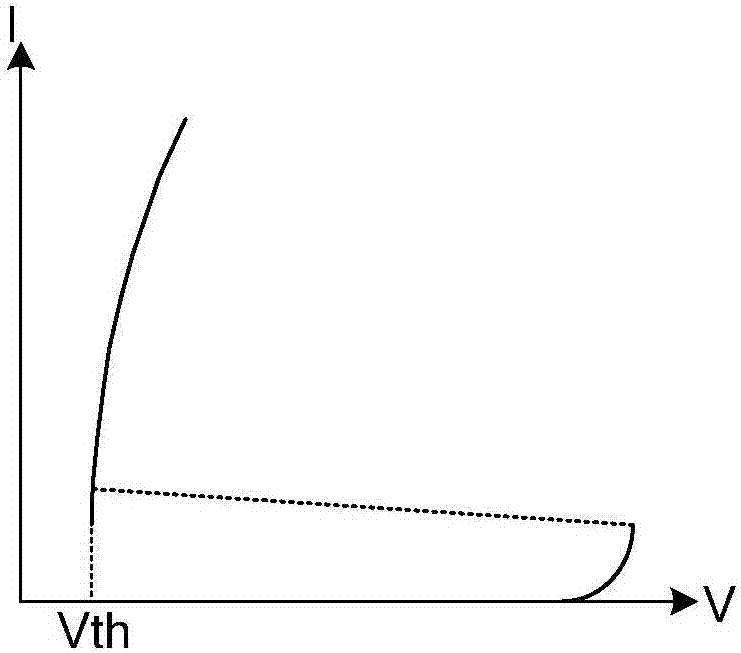

The holding voltage (the minimum voltage required for operation) of a LVTSCR-like device is increased to a value that is greater than a dc bias on a to-be-protected node. The holding voltage is increased by reducing the size of the p+ emitter defined by the LVTSCR-like device. As a result, the LVTSCR can be utilized to provide ESD protection to power supply pins, having better current capabilities than a GGNMOS and better holding voltage characteristics than a LVTSCR.

Owner:NAT SEMICON CORP

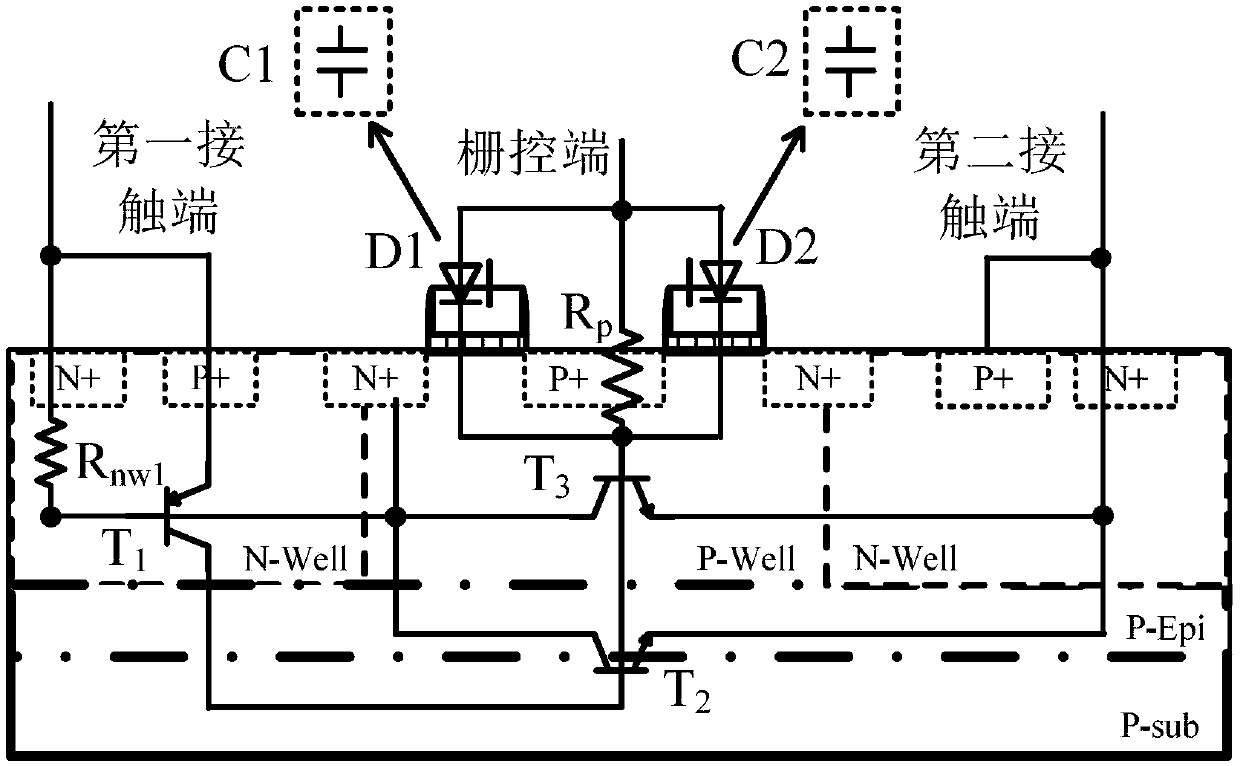

Bidirectional ESD protection anti-latch-up device of holosymmetric dual-grid-control-diode triggering SCR structure

ActiveCN107658295ALower the trigger voltageOpen fastSolid-state devicesDiodeCapacitanceHemt circuits

The invention discloses a bidirectional ESD protection anti-latch-up device of a holosymmetric dual-grid-control-diode triggering SCR structure, and the device can be used for improving the capabilityof an IC chip in resisting ESD. The device mainly consists of a P substrate, a P epitaxial part, a first N well, a P well, a second N well, a first N+ injection region, a first P+ injection region, asecond N+ injection region, a second P+ injection region, a third N+ injection region, a third P+ injection region, a fourth N+ injection region, a first polysilicon gate, a first thin gate oxide layer covering the first polysilicon gate, a second polysilicon gate, and a second thin gate oxide layer covering the second polysilicon gate. The device has a resistance-capacitance coupling auxiliary triggering path under the action of ESD stress, does not need an additional layout area, also can make the most of the advantages of low triggering voltage of a resistance-capacitance coupling circuitand the short start time, and shortens the voltage hysteresis amplitude of the device. In addition, the device also employs the conduction characteristics of the gate control diodes, improves the potential of a parasitic well resistor of the N well, and speeds up the starting of a current releasing path of the SCR structure. Moreover, the device has two ESD current releasing paths and a holosymmetric structure, facilitates the improvement of the ESD robustness of the device, and can achieve the bidirectional protection of ESD.

Owner:JIANGNAN UNIV

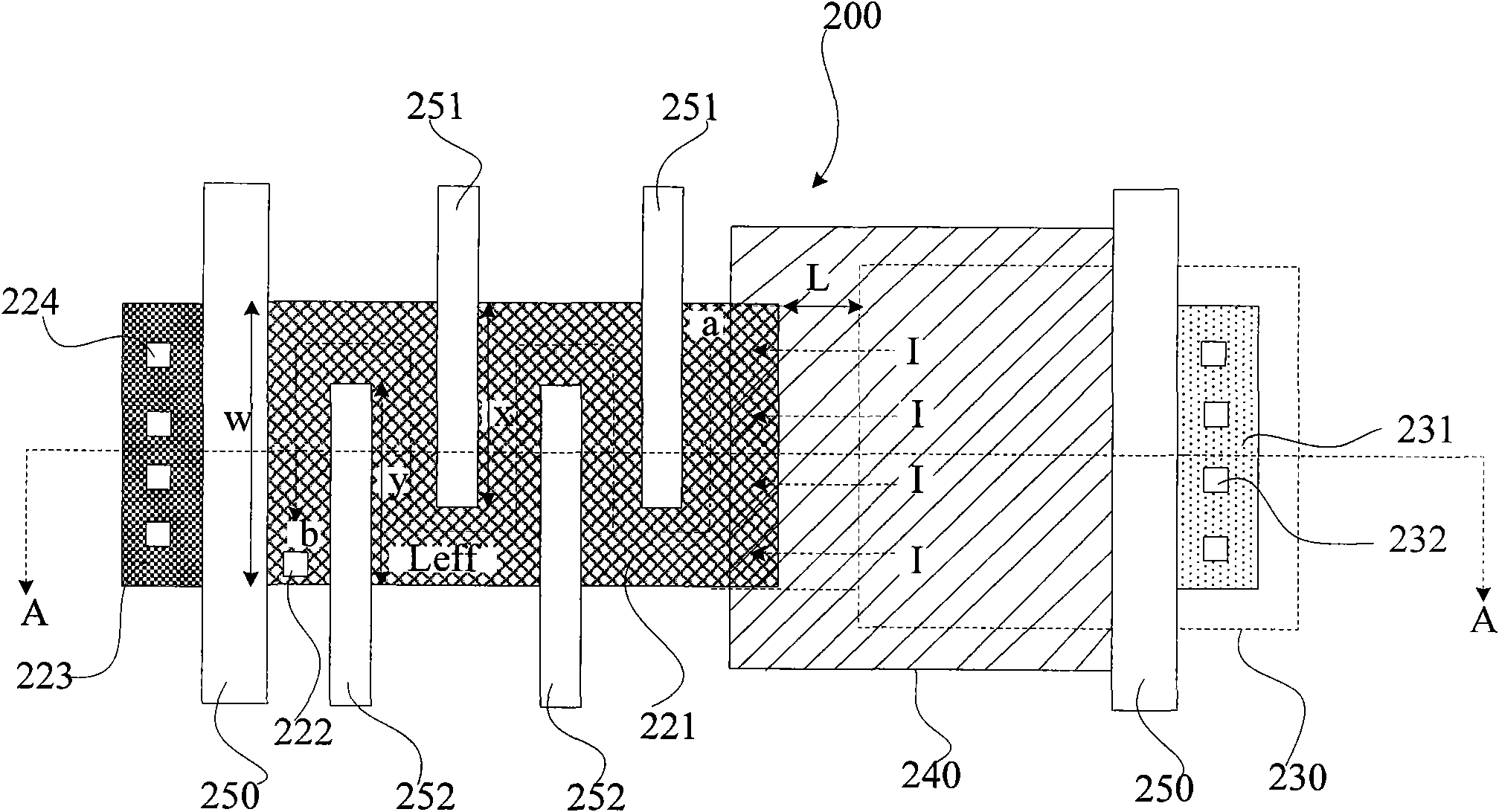

LDMOS ESD(Laterally Diffused Metal Oxide Semiconductor Electro-Static Discharge) structure

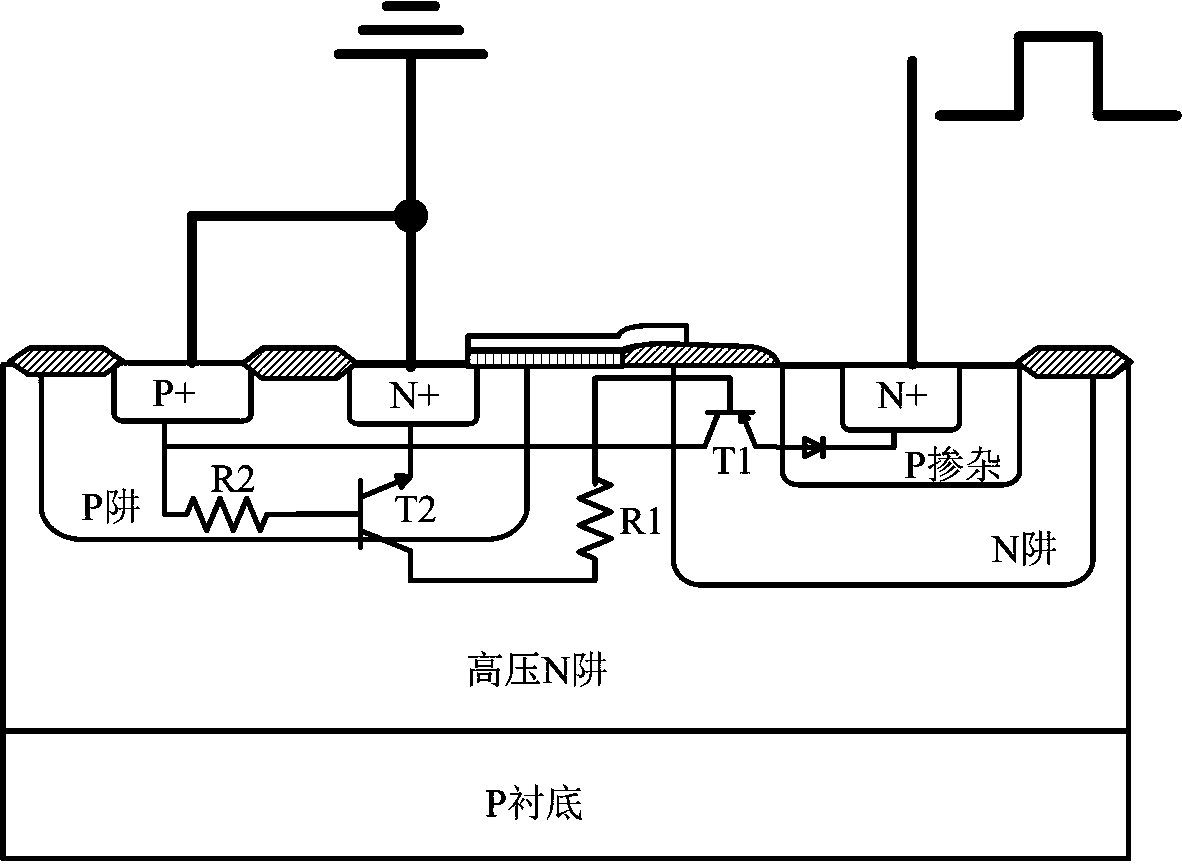

ActiveCN102376761AImprove antistatic performanceIncrease the lengthSemiconductor devicesLDMOSSquare waveform

The invention discloses an LDMOS ESD(Laterally Diffused Metal Oxide Semiconductor Electro-Static Discharge) structure comprising a gate region, a drain region and a source region, wherein an interdigitated STI(Shallow-Trench Isolation) structure is arranged in the source region, so that the flow direction of the electrostatic leakage current of the LDMOS ESD is of a square-wave form. Therefore, the effective channel length is increased while the actual channel length is not increased, and the effective channel resistance is increased, thereby further increasing the sustaining voltage and enhancing the antistatic effect of the LDMOS ESD.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP +1

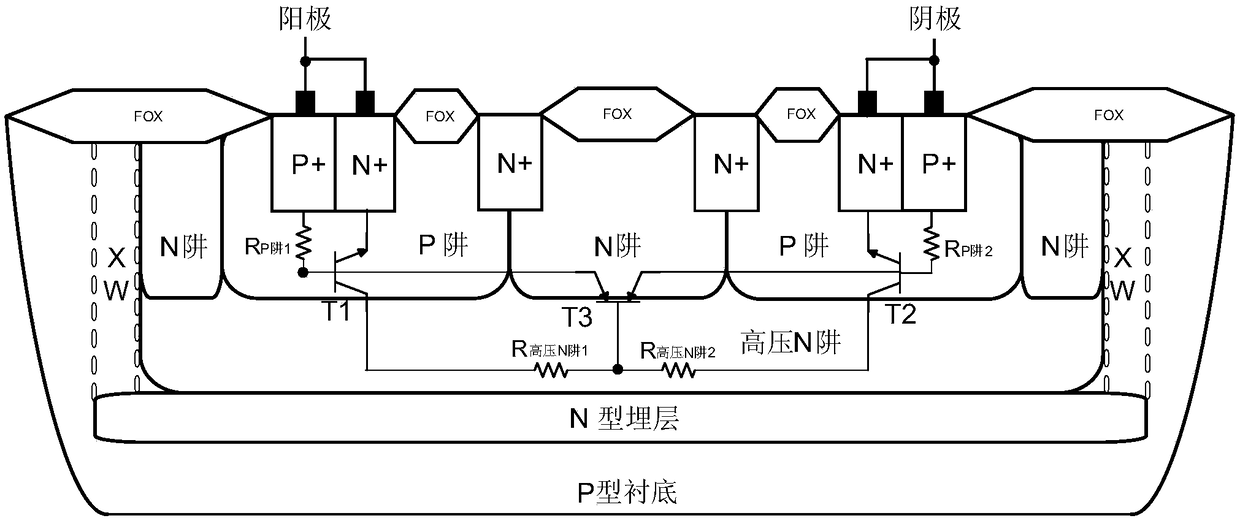

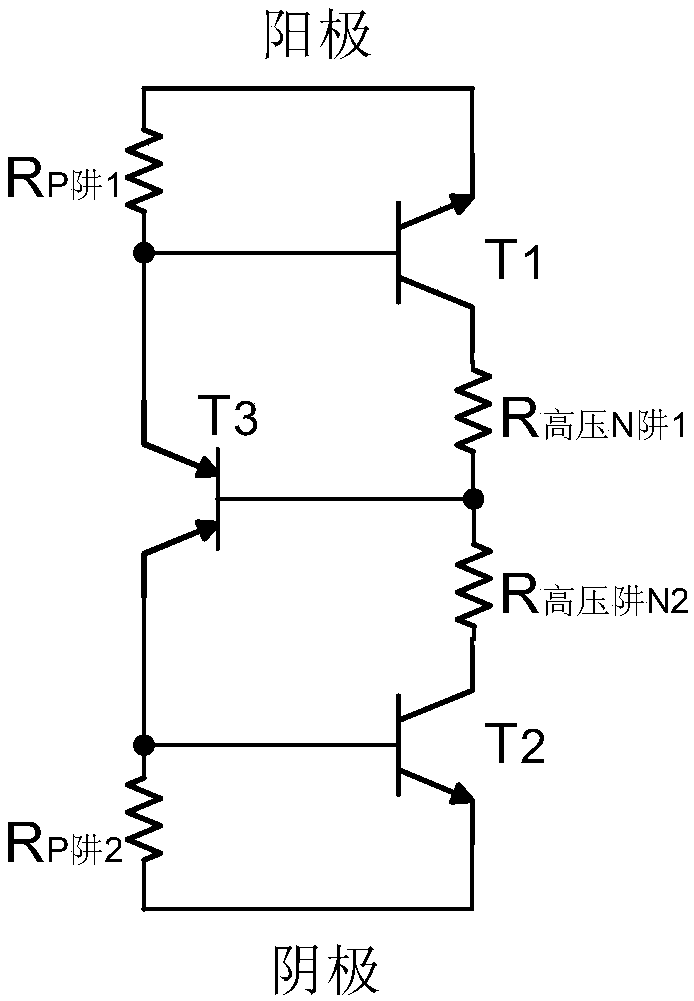

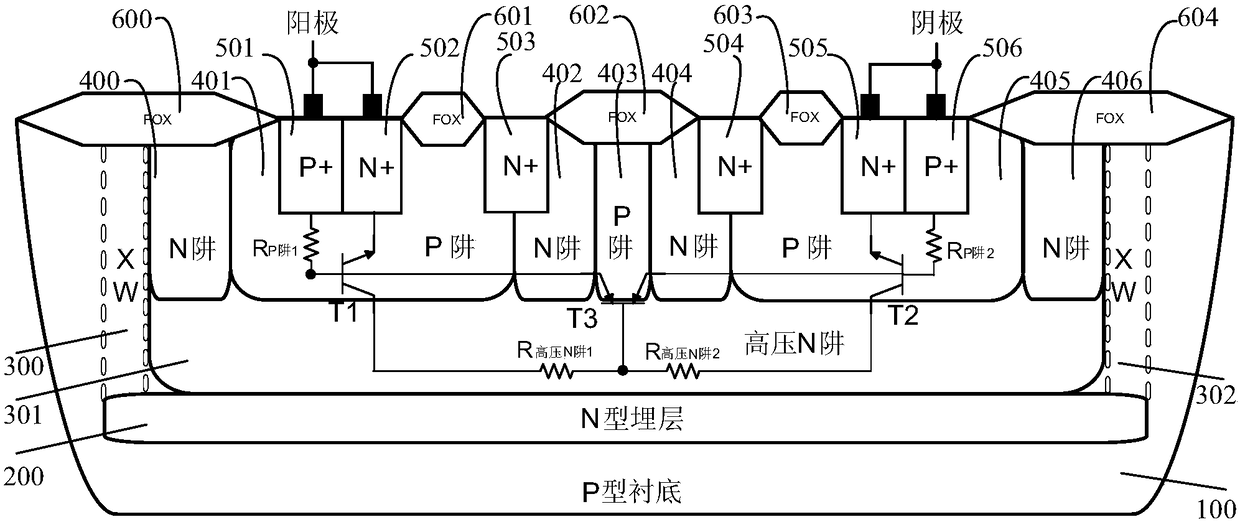

NPNPN type bidirectional silicon controlled rectifier electrostatic protection device with high maintaining voltage

ActiveCN108520875APrevent lock-up issuesIncrease holding voltageSemiconductor/solid-state device detailsSolid-state devicesElectrical resistance and conductanceSilicon-controlled rectifier

The invention discloses an NPNPN type bidirectional silicon controlled rectifier electrostatic protection device with high maintaining voltage. The NPNPN type bidirectional silicon controlled rectifier electrostatic protection device with high maintaining voltage comprises a P type substrate, wherein an N type buried layer is arranged in the P type substrate; a first N type deep trap, a high voltage N trap and a second N type deep trap are arranged on the N type buried layer; a first N trap, a first P trap, a second N trap, a second P trap, a third N trap, a third P trap and a fourth N trap are arranged on the high voltage N trap; a first P+ injection region, a first N+ injection region and a second N+ injection region are arranged in the first P trap; and a third N+ injection region, a fourth N+ injection region and a second P+ injection region are arranged in the third P trap. The NPNPN type bidirectional silicon controlled rectifier electrostatic protection device with high maintaining voltage has the advantages that one P trap is added between two N traps, the thickness of the P trap is just exhausted with the N traps at the left side and the right side, an access with a certain resistance is formed, a bidirectional SCR structure can have one relatively high maintaining voltage after avalanche breakdown and breakover, and the problem that an electrostatic discharge device is locked due to low maintaining voltage after breakover is effectively prevented.

Owner:SUPERESD MICROELECTRONICS TECH CO LTD

SCR for electrostatic protection, chip and system

InactiveCN107093596AImprove reliabilityImprove robustnessSemiconductor/solid-state device detailsSolid-state devicesEngineeringSemiconductor

The invention provides a semiconductor controlled rectifier (SCR) for electrostatic protection, a chip and a system, relates to the electronic technology field and can realize start voltage reduction and maintenance voltage improvement. The SCR comprises a semiconductor substrate, and a first well, a second well and a third well which are arranged on the semiconductor substrate, wherein conductive types of the first well and the third well are identical, the second well is in a different conductive type, the first well is internally provided with a first heavily doped region and a second heavily doped region, the first heavily doped region and the second heavily doped region are different in conductive types, the first heavily doped region and the first well are identical in conductive types, the third well is internally provided with a third heavily doped region, the third heavily doped region and the third well are identical in conductive types, the second well is internally provided with a fourth heavily doped region, the four heavily doped region and the second well are identical in conductive types, the fourth heavily doped region extends to the first well and the third well, a first gap is arranged between the fourth heavily doped region and the second heavily doped region, and a metal gate is arranged at the first gap.

Owner:HUAWEI TECH CO LTD

Thyristor device

The invention discloses a thyristor device, which comprises a P-type substrate, wherein a first N well and a second N well are arranged on the P-type substrate; the first N well is connected with an anode; the potential of the second N well suspends; and a third N+ injection region is bridged between the two N wells and the P-type substrate. A triggering voltage value is reduced by bridging the third N+ injection region between the first N well and the P-type substrate, and a maintaining voltage value is increased by adding the second N well which has the suspending potential into the P-type substrate, so that the aim of a low-triggering and high-maintaining voltage is achieved. Moreover, the thyristor device is simple in structure, high in layout efficiency of unit area, uniform in current, good in robustness, and stable and reliable.

Owner:ZHEJIANG UNIV

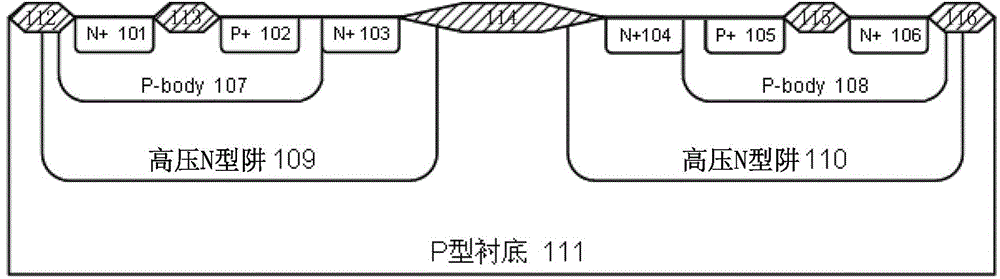

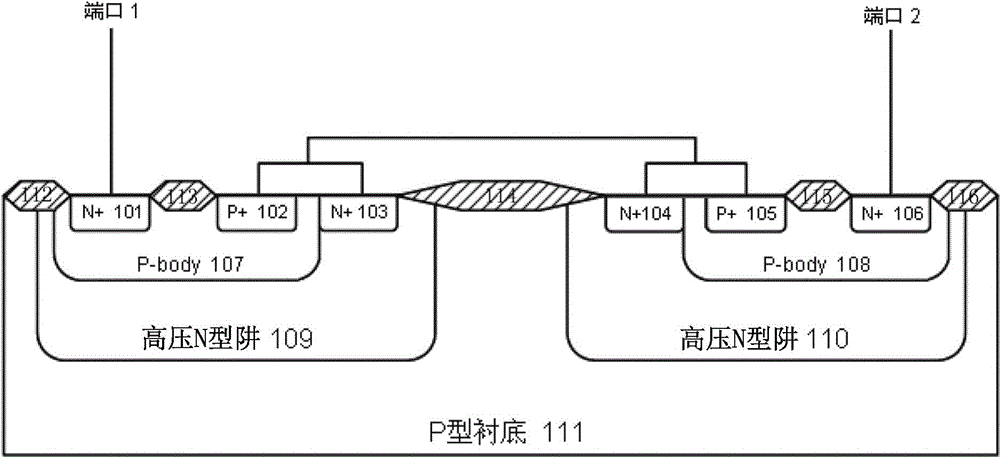

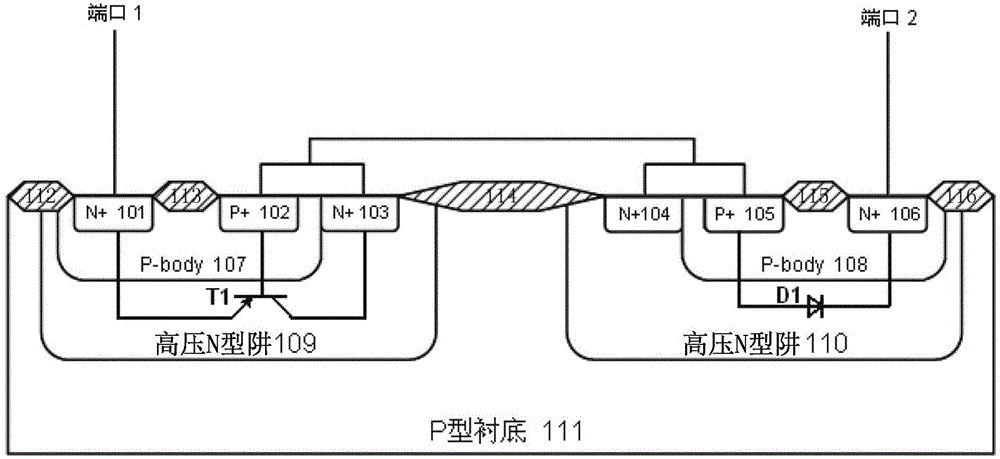

High-voltage bidirectional ESD protective device based on longitudinal NPN structure

ActiveCN104600068ASymmetrical ProtectionIncrease flexibilitySolid-state devicesSemiconductor devicesIsolation layerHigh pressure

The invention relates to a high-voltage bidirectional ESD protective device based on a longitudinal NPN structure. The high-voltage bidirectional ESD protective device based on the longitudinal NPN structure comprises a P type substrate, a first high-voltage N type trap, a second high-voltage N type trap, a first P-body injection region, a second P-body injection region, a first N+ injection region, a first P+ injection region, a second N+ injection region, a third N+ injection region, a second P+ injection region, a fourth N+ injection region and a plurality of oxide isolation layers. Compared with the prior art, the reverse PN junction of the inside longitudinal NPN structure is triggered to conduct under the forward or negative ESD pulse effect, and meanwhile, the positive PN junction in the other N trap is conducted, an ESD current discharge route composed of a longitudinal NPN transistor and a forward diode in a series mode would be generated, the voltage of the device can be kept temporarily through respectively stretching the emitting zone width of each of two NPNS and separately changing the forward or reverse ESD pulse, and the device use environment flexibility is improved.

Owner:武汉芯光虹创科技有限公司

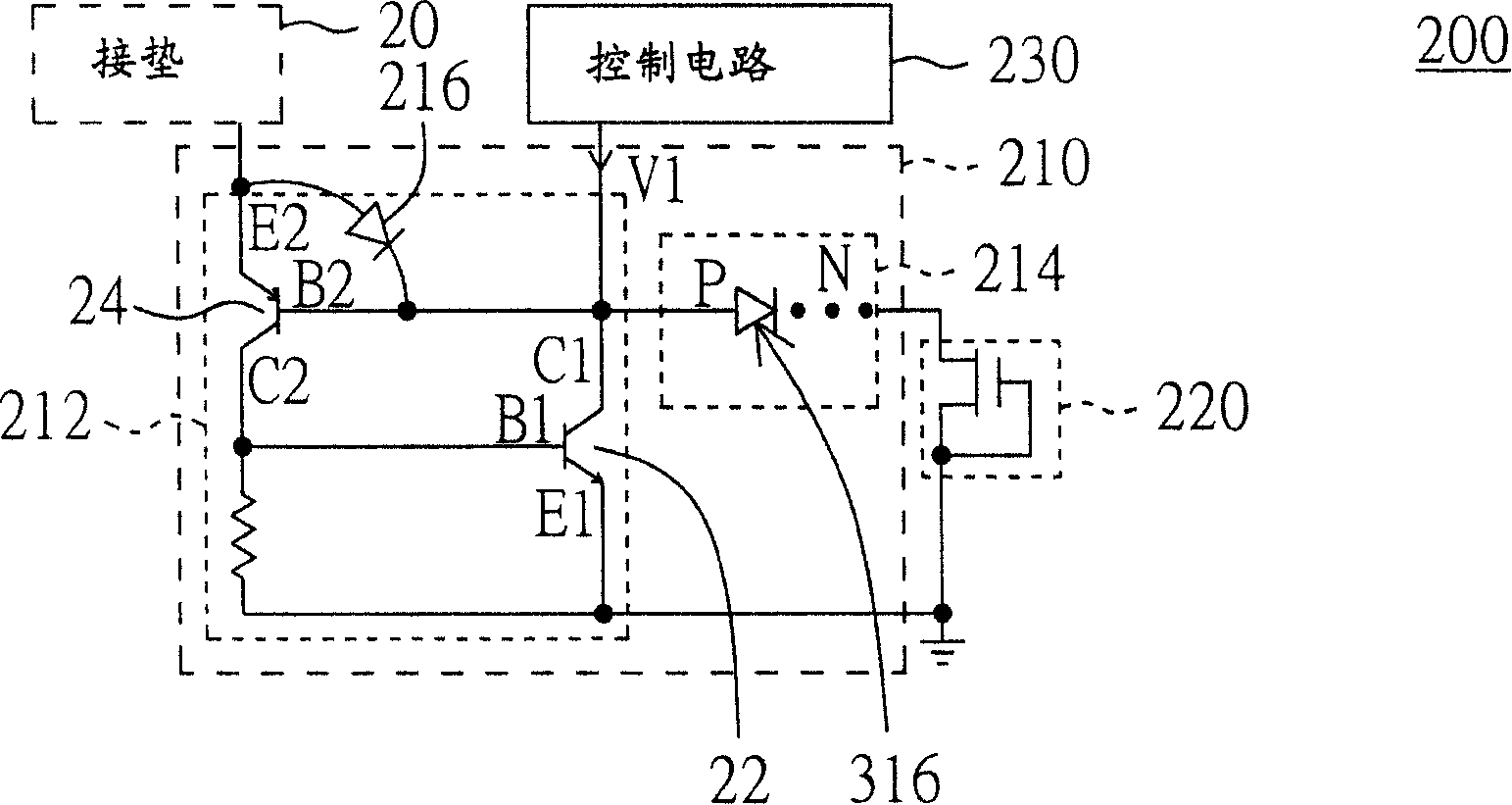

Electrostatic discharge protecting equipment of connection pad and its method and structure

ActiveCN101174622ADoes not increase the areaIncrease the trigger voltageSemiconductor/solid-state device detailsSolid-state devicesSilicon-controlled rectifierCharge carrier

An electrostatic discharge protection device for a contact pad includes a regulating circuit, a snapback component and a control circuit. The regulating circuit includes a silicon controlled rectifier coupled to the pad. The silicon controlled rectifier includes a first diode. The snapback component is coupled to the N pole of the first diode when the second diode is not used, and is coupled to the N pole of the second diode when the second diode is used. The control circuit is coupled to the N pole of the first diode. In normal operation mode, the control circuit is used to provide a first voltage to the N pole of the first diode, so that the N pole of the first diode Collect a plurality of charged carriers, and make the silicon controlled rectifier not be turned on. In the electrostatic discharge mode, the control circuit does not provide the first voltage to the N pole of the first diode, so that the N pole of the first diode Charge carriers are not collected.

Owner:MACRONIX INT CO LTD

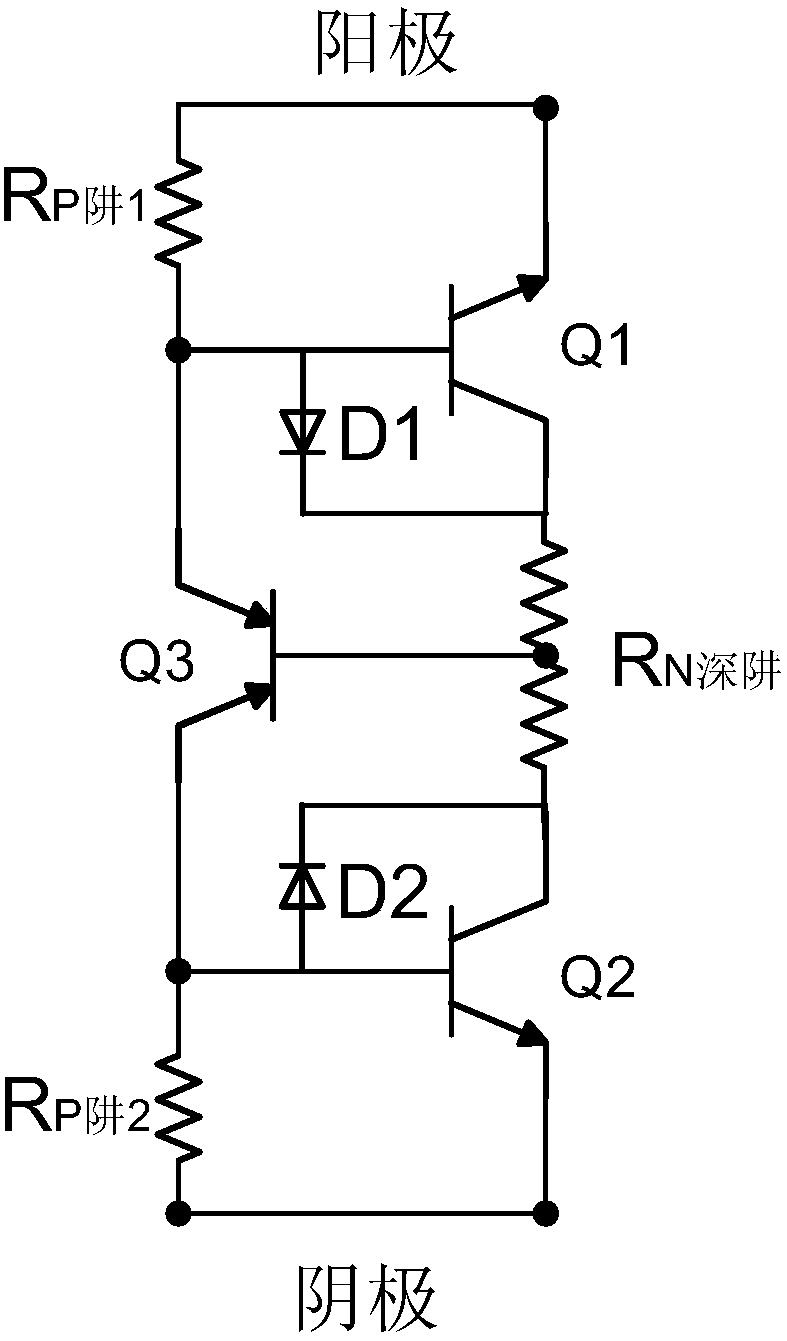

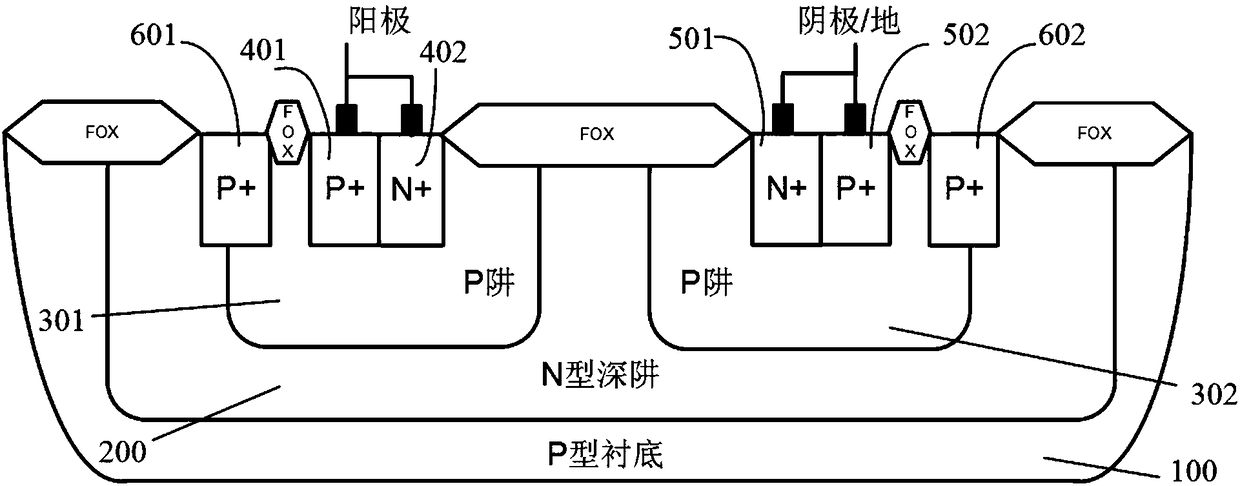

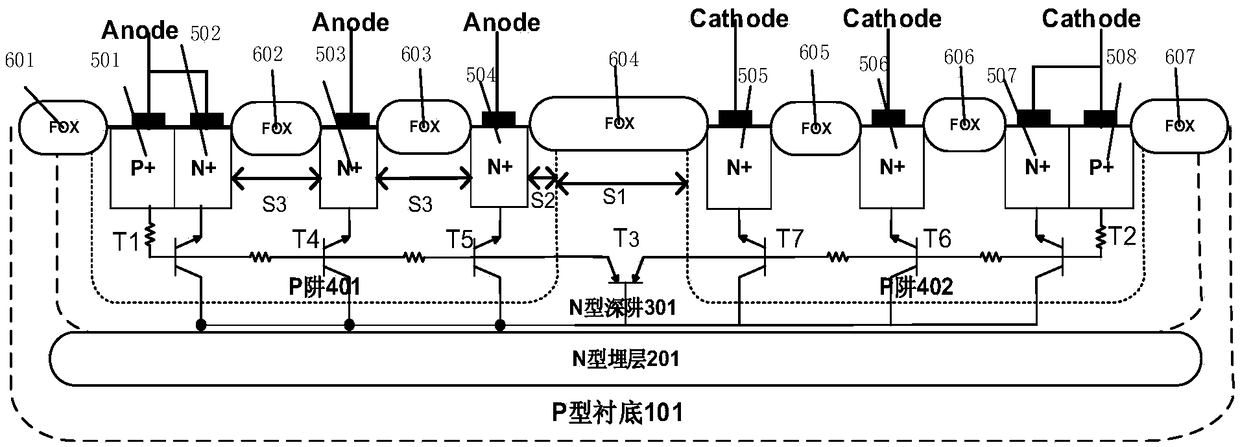

Low-trigger bidirectional silicon-controlled electrostatic protection device with high maintenance voltage

ActiveCN108461491AReduce conductivityLower the trigger voltageTransistorSolid-state devicesDIACSilicon

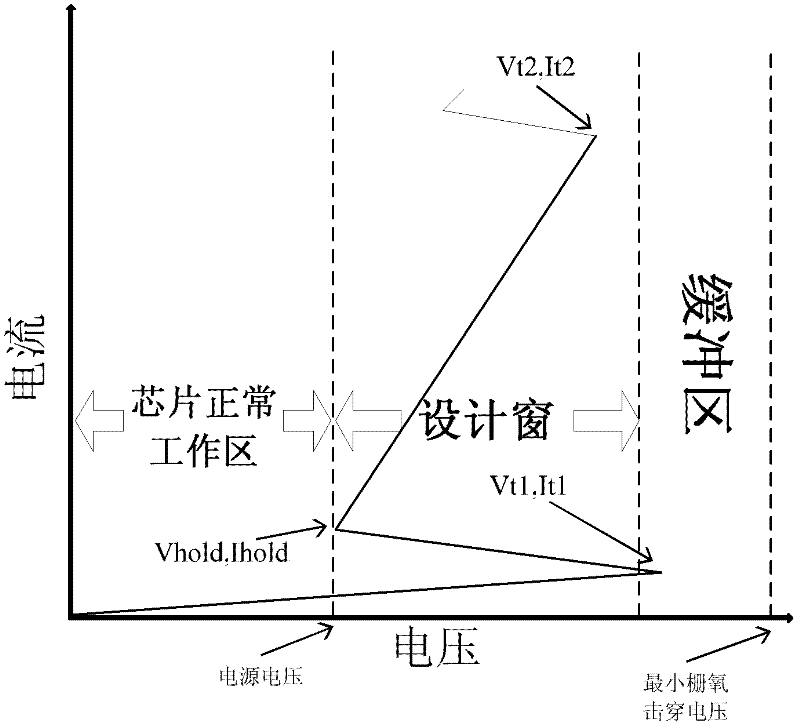

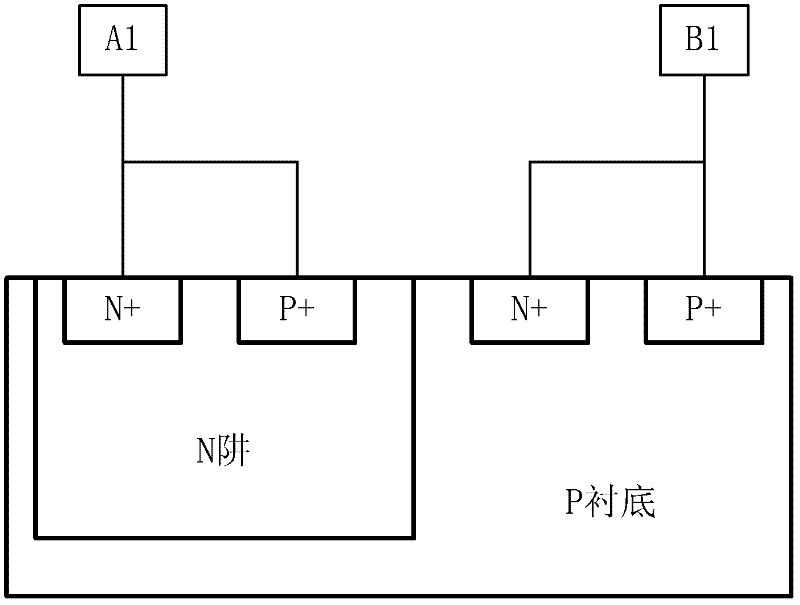

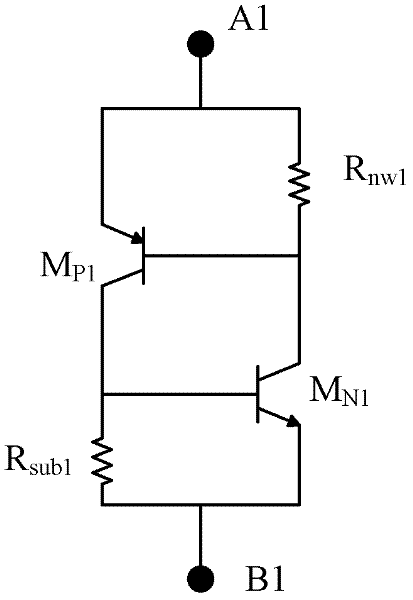

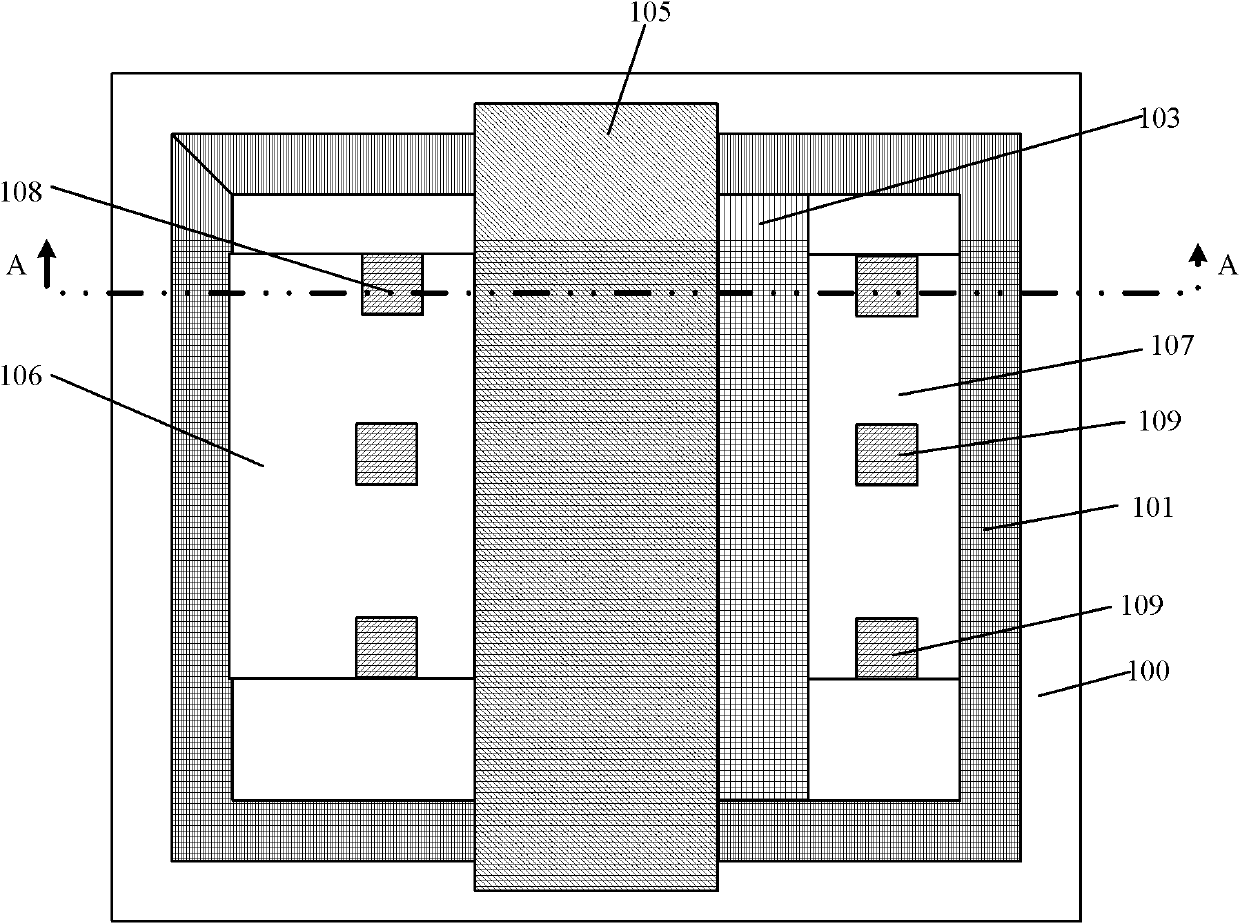

The invention discloses a low-trigger bidirectional silicon-controlled electrostatic protection device with a high maintenance voltage. The low-trigger bidirectional silicon-controlled electrostatic protection device comprises a P-type substrate, wherein an N deep pit is arranged is arranged in the P-type substrate, a first P well and a second P well are arranged in the N deep pit, a first P+ injection region, a second P+ injection region and a first N+ injection are arranged in the first P well, a second N+ injection region, a third P+ injection region and a fourth P+ injection region are arranged in the second P well, the second P+ injection region and the first N+ injection region are connected and are used as a positive electrode of the device, and the second N+ injection region and the third P+ injection region are connected and used as a negative electrode of the device. The low-trigger bidirectional silicon-controlled electrostatic protection device has the capability of bidirectional electrostatic discharging and can be simultaneously used for electrostatic protection of an input-output pin of an integrated circuit of which a signal level is lower than ground or higher thanthe ground, the device is enabled to have low trigger voltage and also has relatively high maintenance voltage on the premise that no extra area is expanded and the conduction capability of the device is not reduced, so that the device has favorable electrostatic discharge (ESD) window.

Owner:SUPERESD MICROELECTRONICS TECH CO LTD

ESD protection component of LDMOS structure and with high maintaining voltage

ActiveCN103715233AImprove high pressure performanceInhibition of the Kirk effectTransistorHemt circuitsPolysilicon gate

An ESD protection component of an LDMOS structure and with high maintaining voltage can be used for an on-chip IC high-voltage ESD protection circuit and mainly comprises a P substrate, a high-voltage N trap, an N trap, a P trap, a P sink doping, a P+ injection region, a first N+ injection region, a second N+ injection region, a meal anode, a metal cathode, a polysilicon gate, a thin gate oxide layer and a plurality of field oxide isolation regions. According to the ESD protection component of the LDMOS structure, under the action of an high-voltage ESD, on one hand, a parasitic SCR current discharging path is formed by the P sink doping, the N trap, the high-voltage N trap, the P trap and the first N+ injection region, idle currents of the component are increased, and ESD robustness of the component is improved; on the other hand, by means of a biasing reversal PN junction formed between the second N+ injection region and the P sink doping, maintaining voltage of the component is improved and the latch-up-resistant capacity of the component is improved.

Owner:扬州市冠科科技有限公司

Bidirectional silicon-controlled electrostatic protection device with high protection level and fabrication method thereof

ActiveCN108807371AReduce in quantityImprove even distributionTransistorSolid-state devicesDIACCurrent distribution

The invention discloses a bidirectional silicon-controlled electrostatic protection device with high protection level. The bidirectional silicon-controlled electrostatic protection device comprises aP-type substrate, wherein an N-type buried layer is arranged in the substrate, an N-type deep well is arranged on the N-type buried layer, a first P well and a second P well are arranged in the N-typedeep well, a first P+ injection region and a plurality of N+ injection regions I are arranged in the first P well, a second P+ injection region and a plurality of N+ injection regions II are arrangedin the second P well, the first P+ injection region and all N+ injection regions I are connected and used as a positive electrode of the device, and the second P+ injection region and all N+ injection regions II are connected and used as a negative electrode of the device. The numbers of the N+ injection regions I and the N+ injection regions II can be increased or reduced according to differentprotection levels, the numbers of the N+ injection regions I and the N+ injection regions II are increased if the protection level is high, the uniform current distribution of the device is improved,and the robustness of the device is improved; and if the protection level is low, the numbers of the N+ injection regions I and the N+ injection regions II are reduced, and the layout area is reduced.

Owner:XIANGTAN UNIV

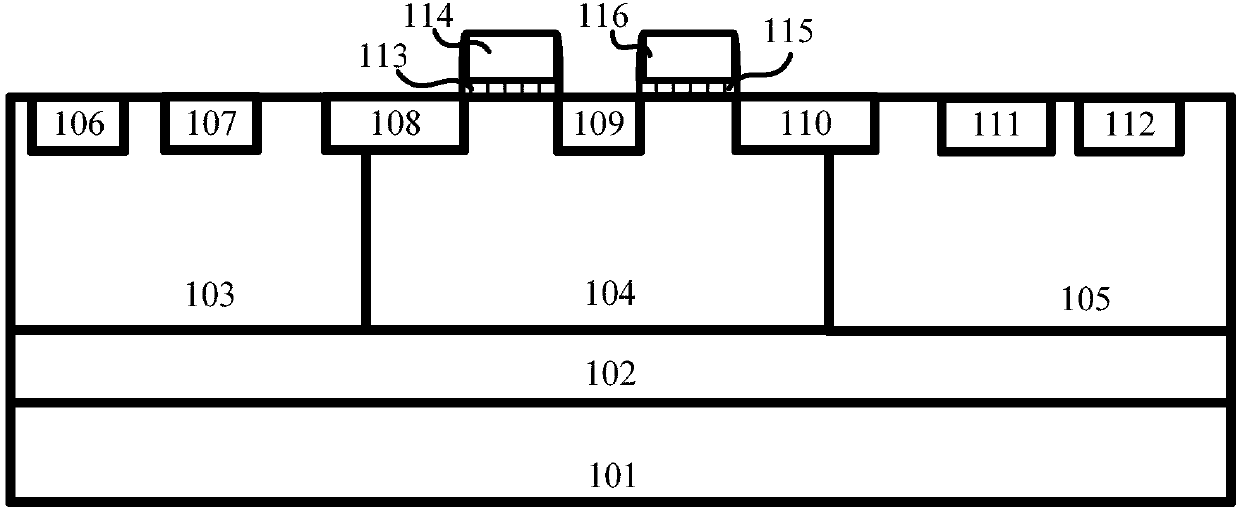

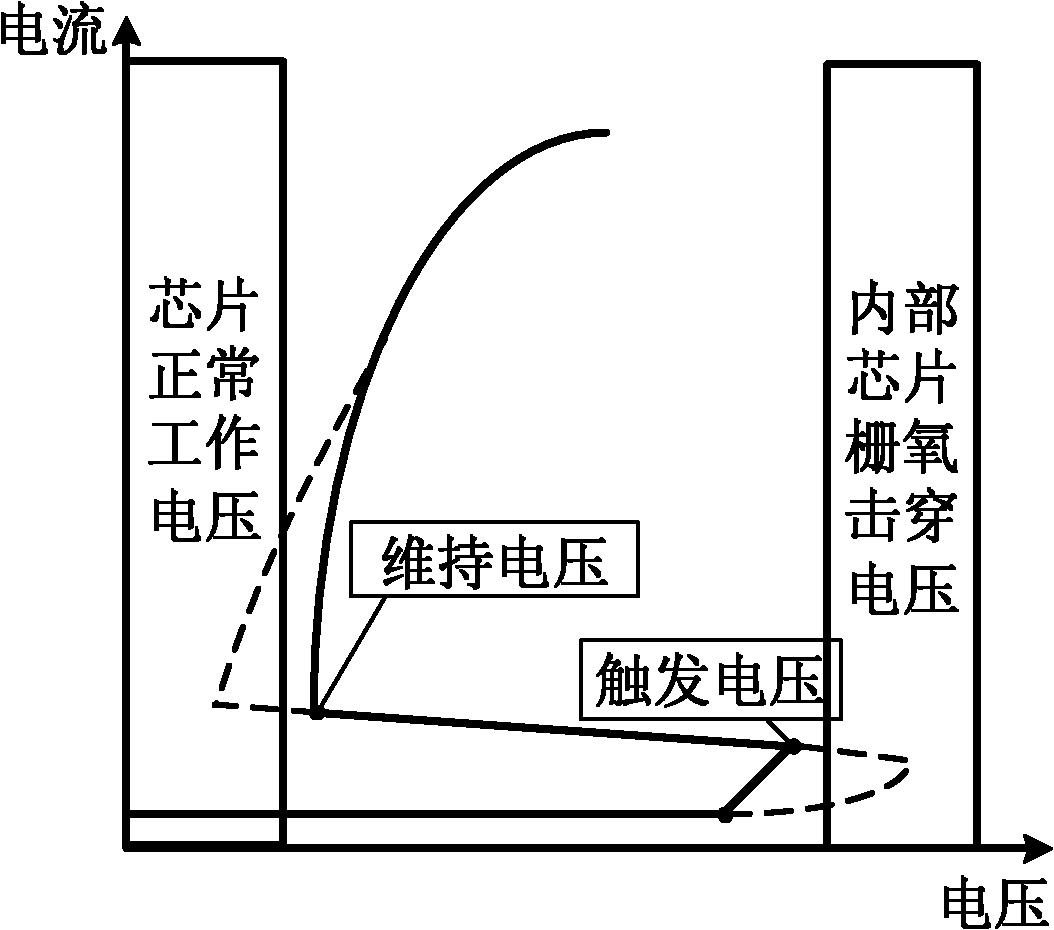

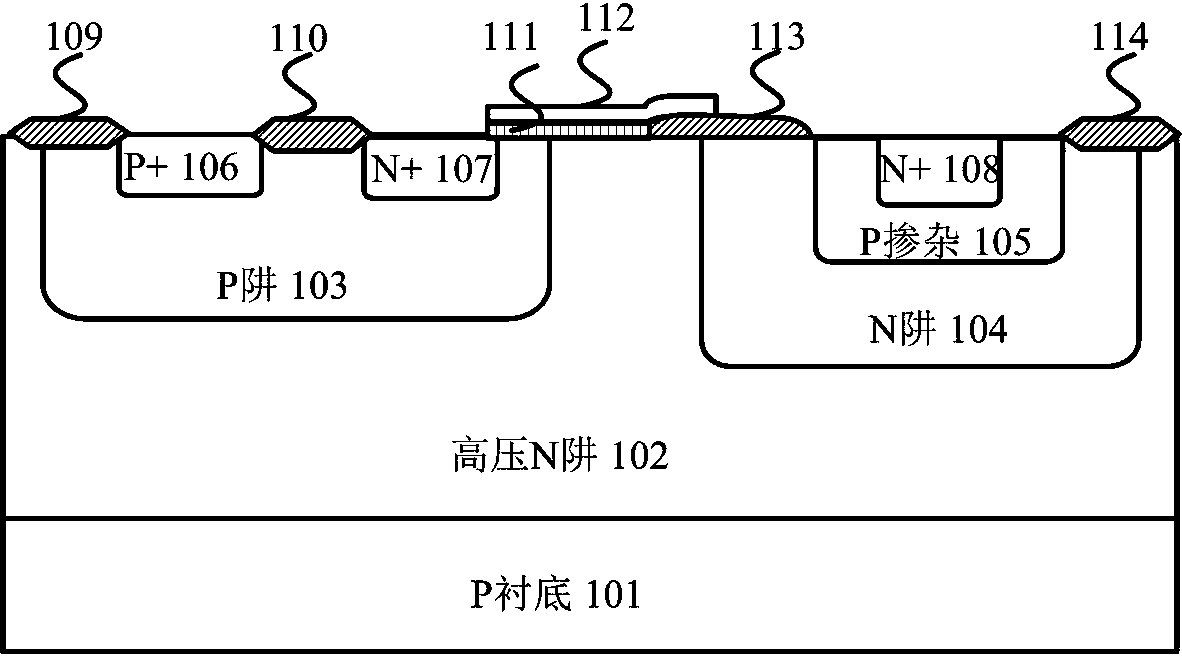

Thyristor with high hold voltage and low triggering voltage ESD (electronstatic discharge) characteristic

ActiveCN102244105ALower the trigger voltageIncrease holding voltageThyristorDiodeThyratronEngineering

The invention relates to the technical field of a protection circuit of a semiconductor integrated chip, and particularly relates to a thyristor with high hold voltage and low triggering voltage ESD (electronstatic discharge) characteristic. The thyristor comprises a substrate layer (311), a well region layer and a gate oxide layer sequentially from bottom to top, wherein the well region layer comprises an N well region (309) and a P well region (310); the N well region is adjacent to the P well region; the N well region and the P well region contact the substrate layer (311); a first N+ doping region (305) is arranged at the junction of the N well region (309) and the P well region (310); the N well region (309) is provided with a first P+ doping region (304); and the P well region (310)is provided with a second N+ doping region (306) and a second P+ doping region (307). According to the invention, through improving the original thyristor structure, the triggering voltage of the thyristor is reduced, and the hold voltage of the thyristor is improved, so that the thyristor can ideally act as an ESD clamping protection device.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP +1

Laterally diffused metal oxide semiconductor (LDMOS) transistor, layout method and manufacture method

ActiveCN102569392AIncrease holding voltageIncrease resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesLDMOSEngineering

The invention provides a structure of a laterally diffused metal oxide semiconductor (LDMOS) transistor, a manufacture method and a layout method of the structure. The structure comprises a substrate, a first mixing pit, a second mixing pit, a grid electrode structure, a first isolation structure, a second isolation structure, a source region, a drain region, an interlamination medium layer, a source region plug and a drain region plug. The first mixing pit and the second mixing pit are located in the substrate, the grid electrode structure is located above the first mixing pit and the second mixing pit, the isolation structure surrounds the first mixing pit and the second mixing pit, one side of the second isolation structure is adjacent to the grid electrode structure, the second isolation structure has two opposite ends and is connected with the first isolation structure, the source region is located in the first mixing pit, a third isolation structure is formed in the source region, and the source region is used for increasing resistance of the source region, the drain region is located in the second mixing pit between the first isolation structure and the second isolation structure, and the interlamination medium layer is located on the surface of the substrate, and the source region plug and the drain region plug are located in the interlamination medium layer. The structure guarantees that the LDMOS transistor can be normally opened.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP

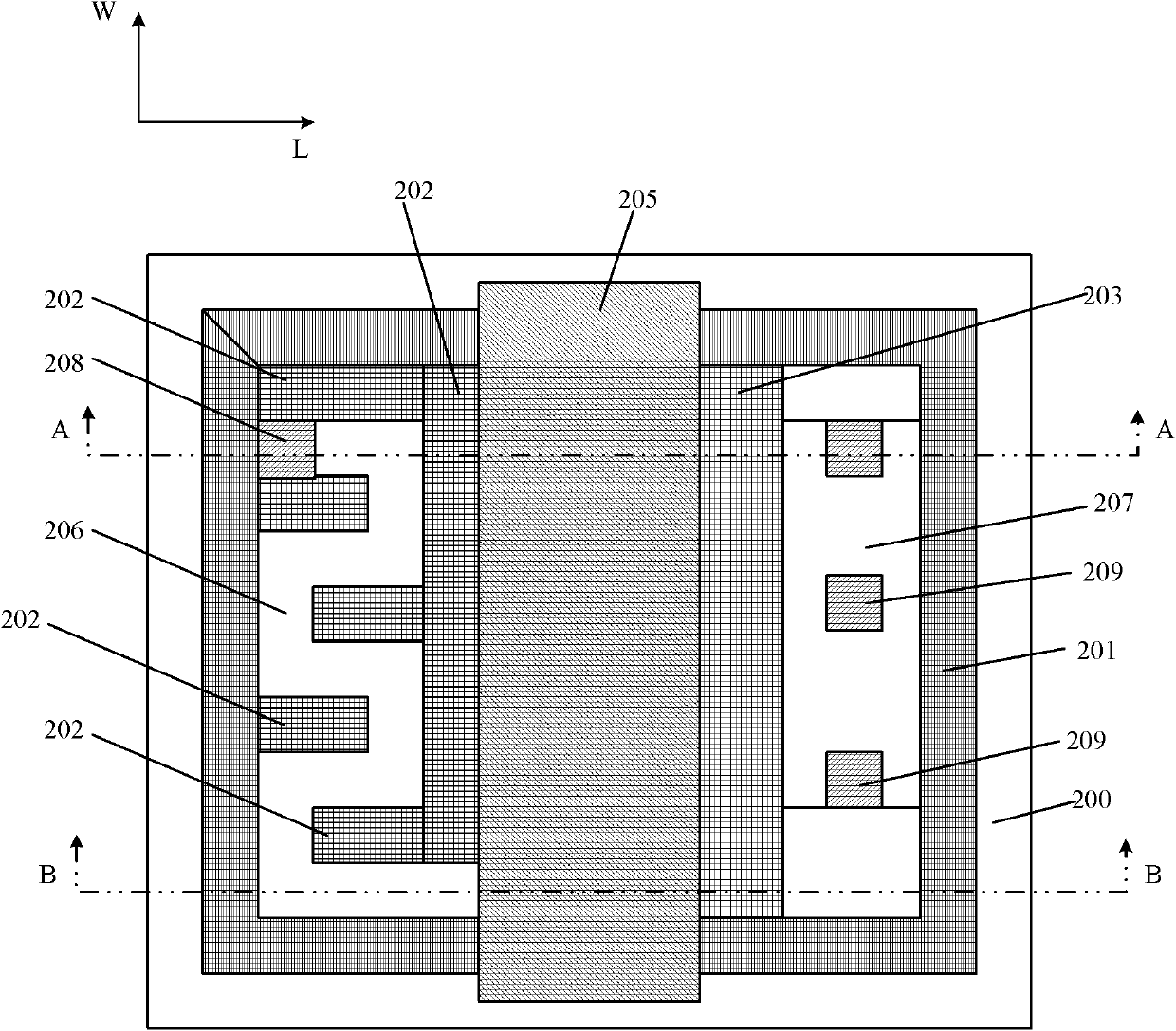

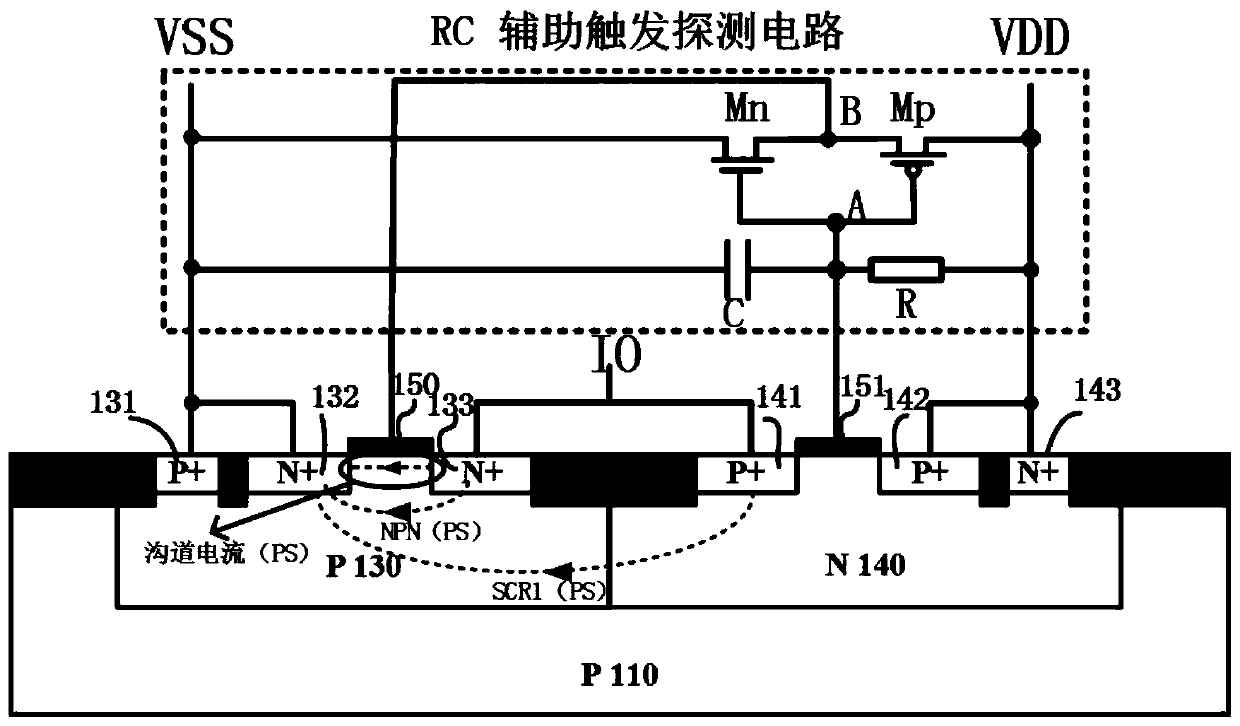

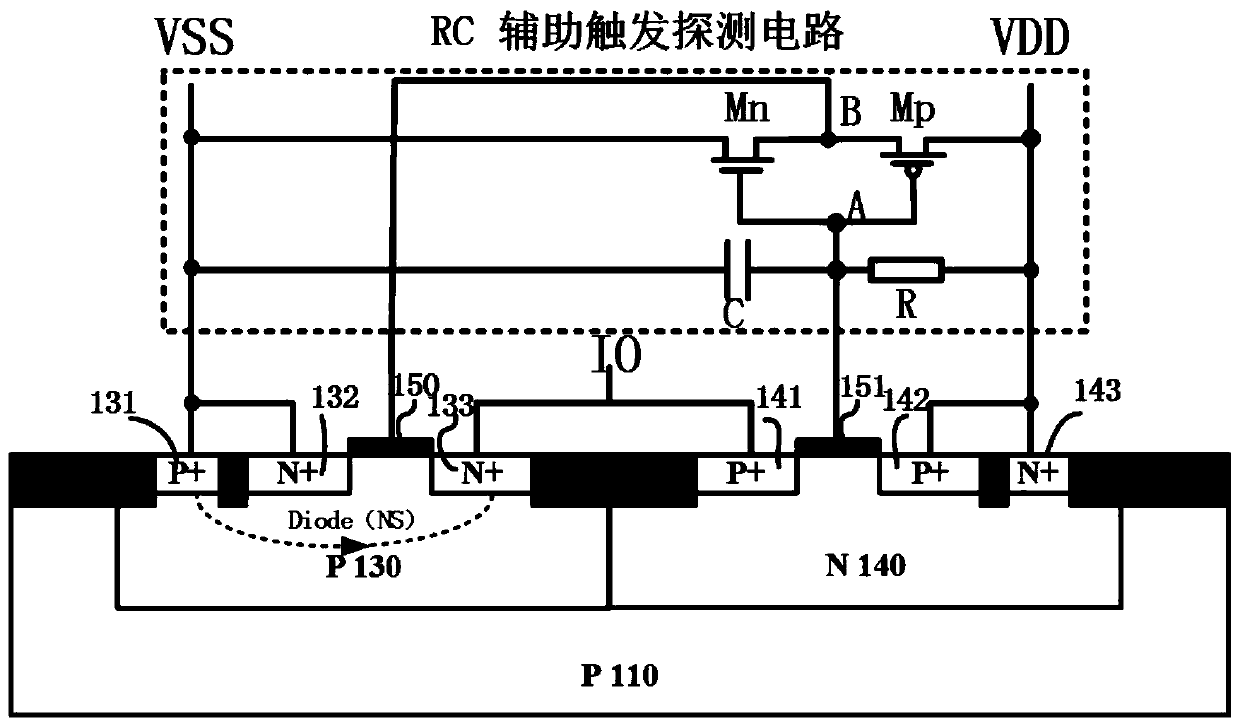

Three-end compact and compound SCR device for whole-chip ESD protection

ActiveCN110190052AReduce conductance modulation effectFulfill protection needsTransistorSolid-state devicesCMOSEngineering

The present invention belongs to the technical field of electrons, especially relates to the design of an ESD (Electro-Static discharge) protection circuit, and especially provides a three-end compactand compound SCR device (CCSCR) for whole-chip ESD protection. The three-end compact and compound SCR device comprises a main discharge CCSCR and a RC auxiliary trigger detection circuit; the main discharge CCSCR is a three-end device, three parasitic SCR pathways are introduced on the basis of the CMOS device structure so that the whole-chip ESD protection with high robustness is achieved in a smaller territory area; the RC auxiliary trigger detection circuit is introduced to further reduce the triggering voltage of the device; and besides, the CCSCR can be taken as a two-end device to supply ESD protection between any one IO port and a power supply.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

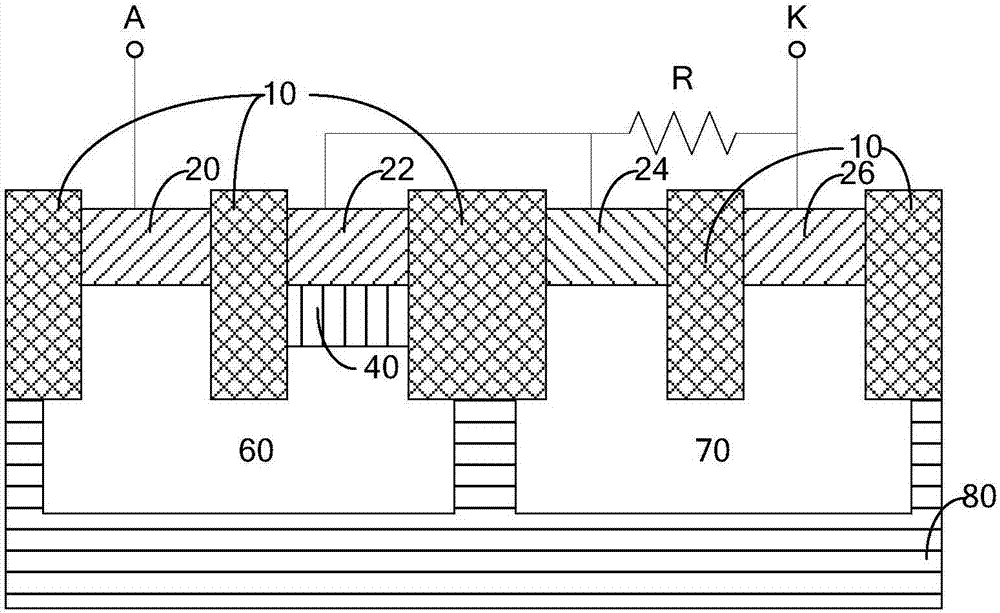

Novel ESD protection structure and realizing method thereof

ActiveCN107248514AIncrease holding voltageLower the trigger voltageSolid-state devicesDiodePhysicsP type doping

The invention discloses a novel ESD (Electro-Static Discharge) protection structure and a realizing method thereof. The ESD protection structure comprises a semiconductor base body; a first N well and a second N well generated in the semiconductor base body; a silicon controlled rectifier arranged in the first N well and a diode structure arranged in the second N well; a high-concentration P-type doping (28), a high-concentration N-type doping (20) and a high-concentration N-type doping (22) arranged at the upper part of the first N well; and a P-type ESD implanting layer (40) arranged below the high-concentration N-type doping (22). The high-concentration N-type doping (20) is connected in a floating manner and has a distance S to the high-concentration P-type doping (28); the high-concentration N-type doping (20) and the high-concentration N-type doping (22) are arranged in an isolated manner; and the high-concentration P-type doping (28), the first N well (60), the ESD implanting layer (40) and the high-concentration N-type doping (22) compose the silicon controlled rectifier. According to the novel ESD protection structure and the realizing method thereof, the maintaining voltage of the hysteresis effect of the ESD protection structure can be increased.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP