Three-end compact and compound SCR device for whole-chip ESD protection

A composite, full-chip technology, applied in the field of electronics, can solve the problems of large chip area, chip area loss, occupation, etc., and achieve the effect of reducing trigger voltage, reducing ESD current, and small area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] The present invention will be described in detail below in conjunction with the accompanying drawings and specific embodiments.

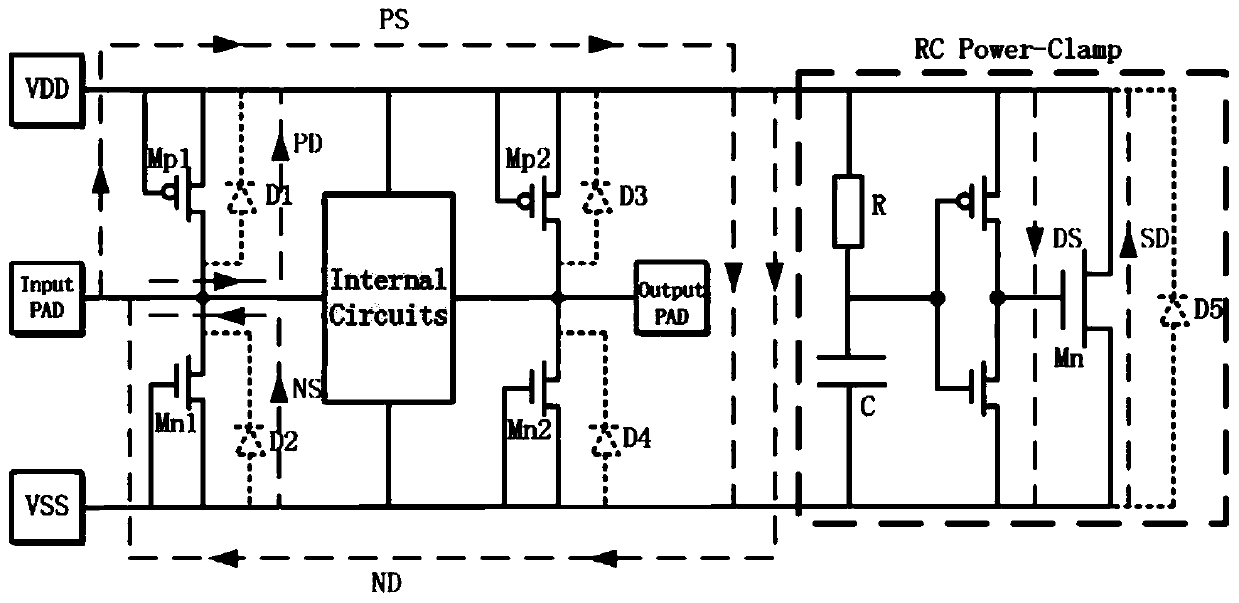

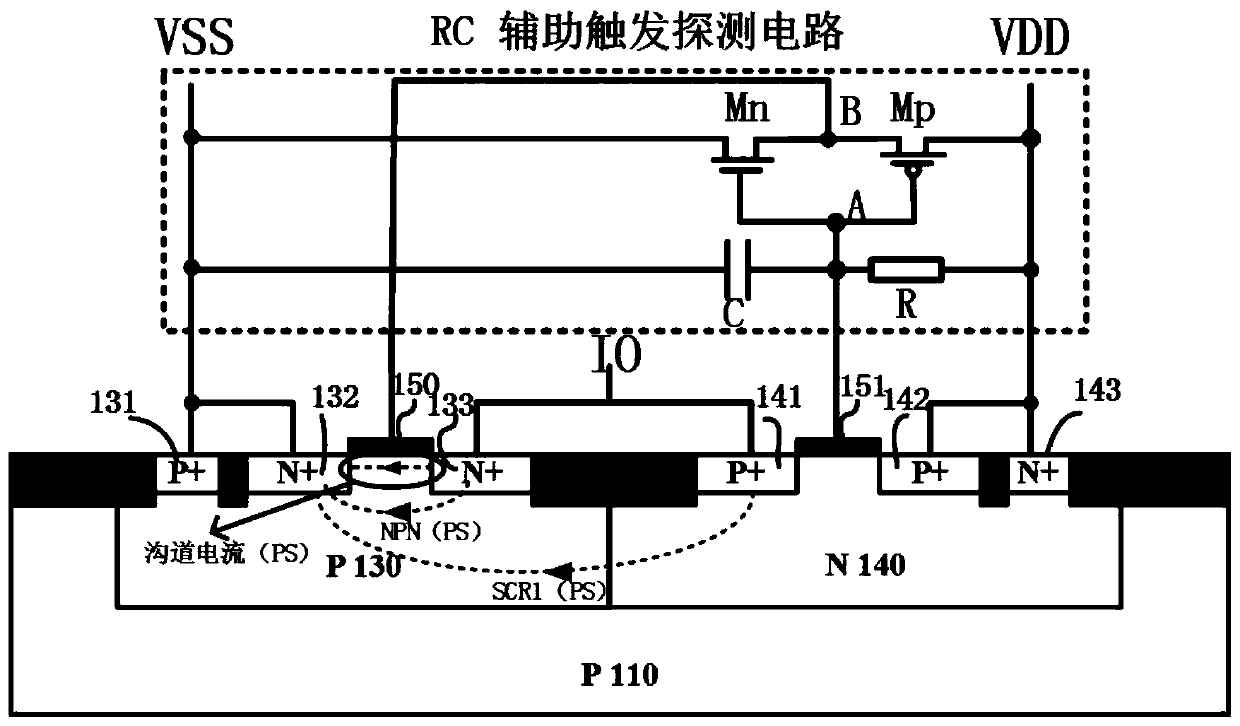

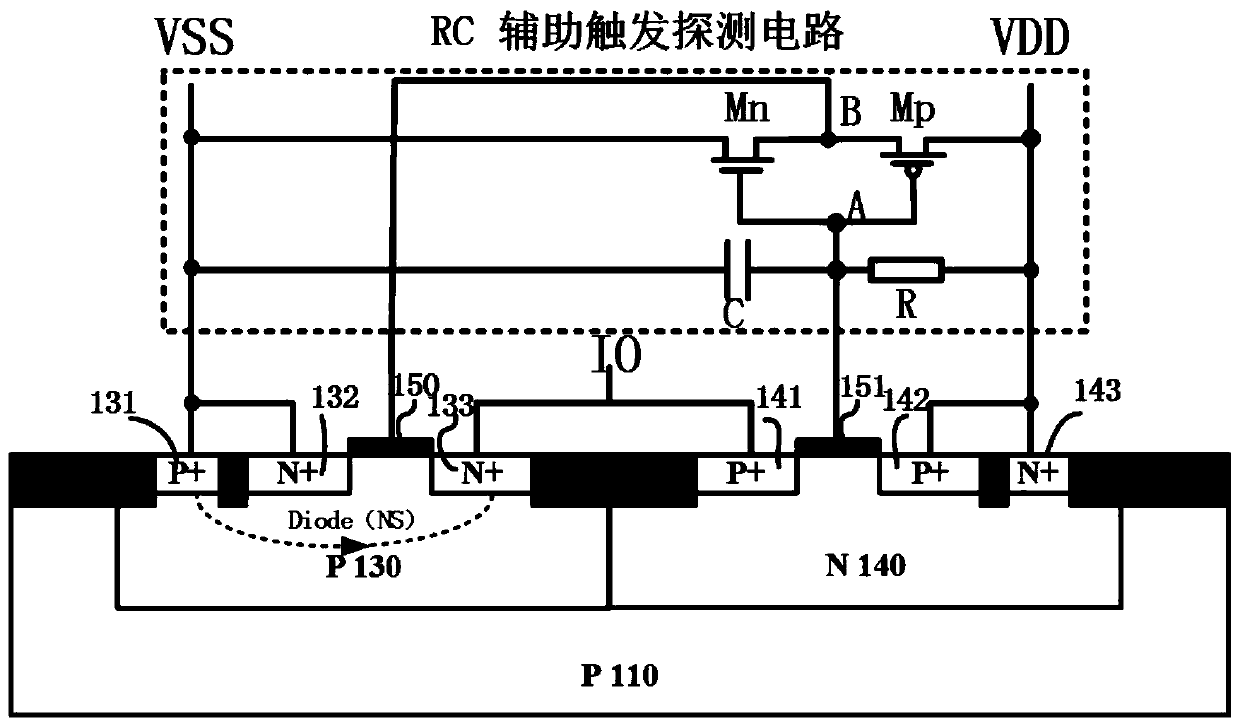

[0024] This embodiment provides a three-terminal compact composite SCR device for full-chip ESD protection, such as Figure 2 to Figure 7 shown; including: a main discharge CCSCR device and an RC auxiliary trigger detection circuit; where,

[0025] The main discharge CCSCR device includes:

[0026]p-type silicon substrate 110; the well region formed on the p-type substrate 110, the well region includes a p-type well region 130 and an n-type well region 140, the two well regions are adjacent; the p A p-type heavily doped region 131, an n-type heavily doped region 132, and an n-type heavily doped region 133 are provided in the well region 130; a p-type heavily doped region 140 is provided in the n-type well region region 141, a p-type heavily doped region 142 and an n-type heavily doped region 143; a gate oxide layer is arranged on the silico...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More