Low-voltage SCR (Silicon Controlled Rectifier) structure for ESD (Electronic Static Discharge) protection of integrated circuit chip

An ESD protection and integrated circuit technology, applied in the electronic field, can solve the problems of reduced ESD resistance, increased voltage drop, chip failure, etc., to achieve excellent ESD protection performance, low trigger voltage, and fast trigger speed.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach 1

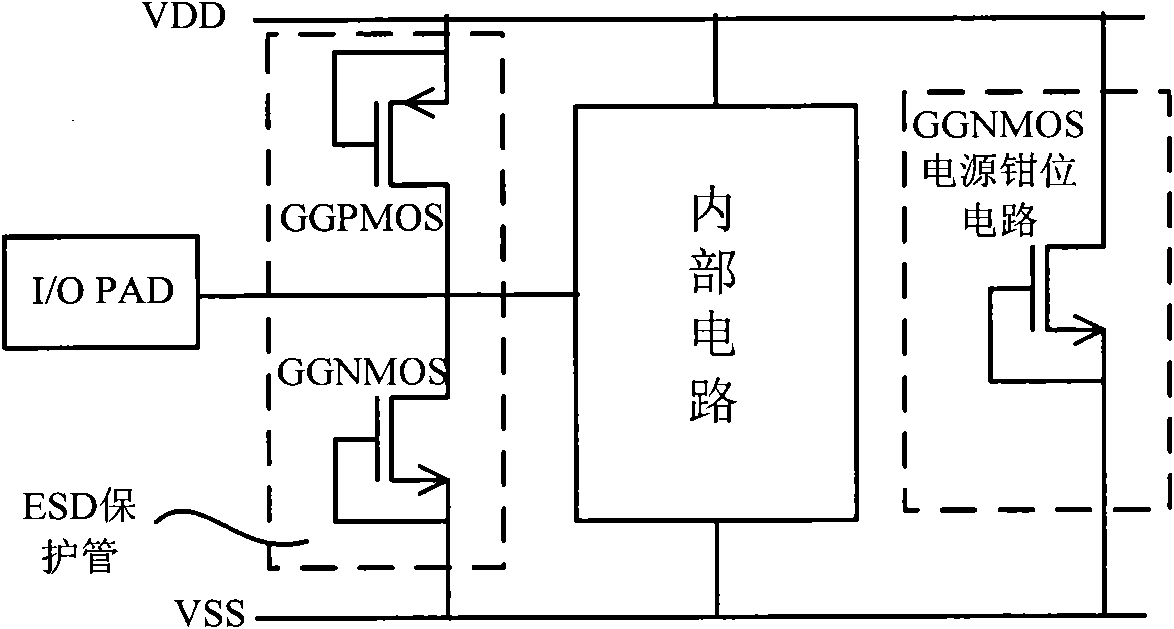

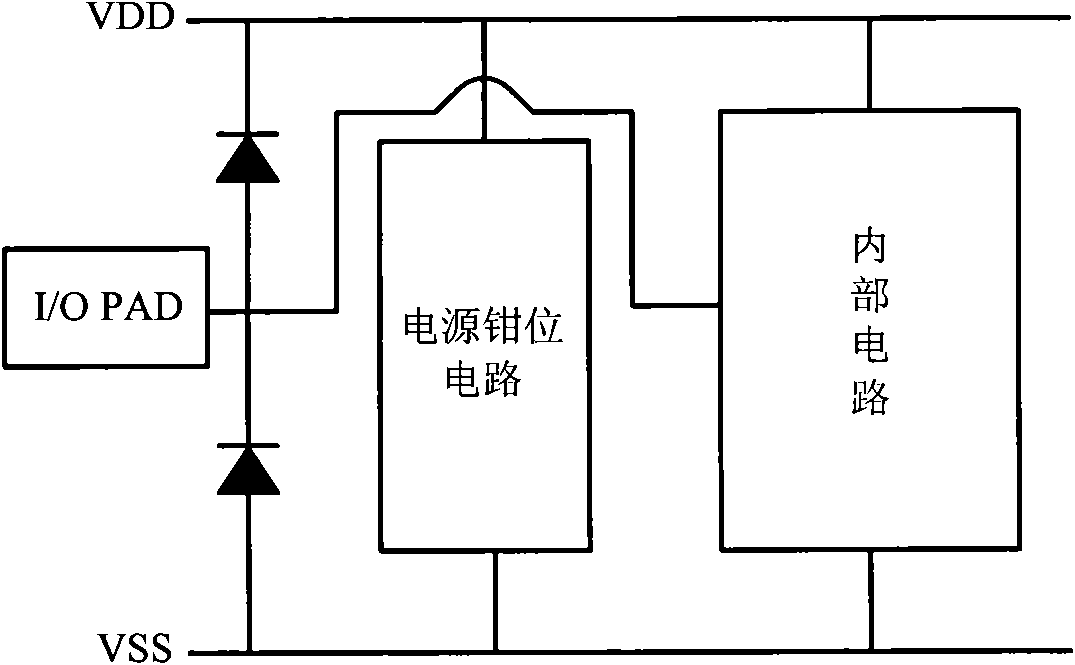

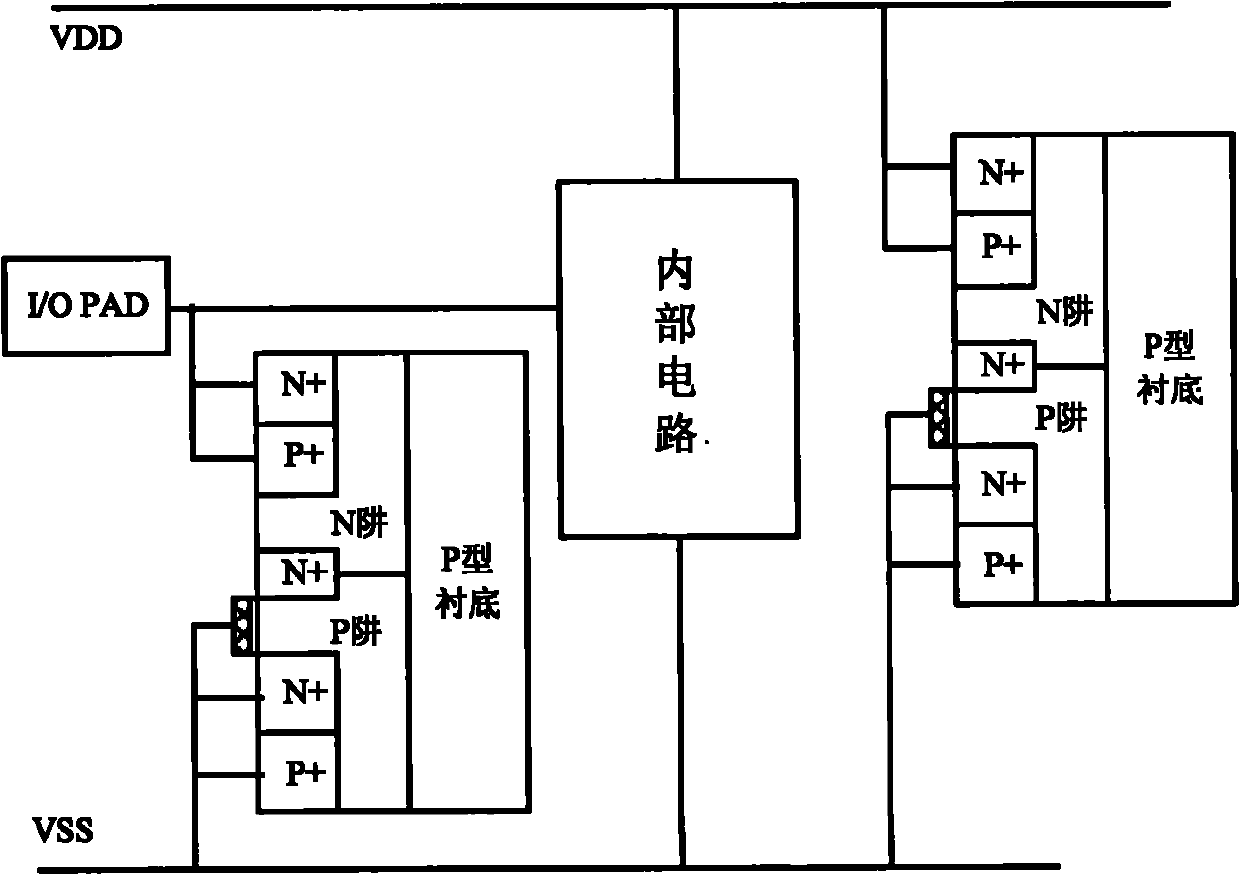

[0037] A low-voltage SCR structure used for ESD protection of integrated circuit chips, such as Figure 4 As shown, two types of low-voltage SCR ESD protection devices are included, and the two types of SCR ESD protection devices are integrated on the same chip substrate with the integrated circuit chips they protect.

[0038] The first type of low-voltage SCR ESD protection device includes an N well region, two P well regions, three P + area and the four N + region, the N well region is sandwiched between two P well regions; the middle of the top of the first P well region is the first N well region + region, the side of the top of the first P well region far away from the N well region is the first P + region; the middle of the top of the second P well region is the second N + region, the side of the top of the second P well region away from the N well region is the second P well region + region; the middle of the top of the N well region is the third P + District; Thir...

specific Embodiment approach 2

[0040] Such as Figure 5 shown in Figure 4 On the basis of the technical scheme shown, the third and fourth polysilicon regions are added above the N well region of the first type of low-voltage SCR ESD protection device; the third polysilicon region is located in the third N well region + District and Third P + above the N well region between regions, the fourth polysilicon region is located in the fourth N + District and Third P + Above the N well region between the regions, there is an insulating layer between the third and fourth polysilicon regions and the N well region; I / O ports are connected. The third and fourth polysilicon regions are added above the P well region of the second type of low-voltage SCR ESD protection device; the third polysilicon region is located in the third P + District and Third N + above the P well region between regions, the fourth polysilicon region is located in the fourth P + District and Third N + Above the P well region between the...

specific Embodiment approach 3

[0041] Such as Image 6 shown in Figure 4 On the basis of the technical scheme shown, the third and fourth polysilicon regions are added above the N well region of the first type of low-voltage SCR ESD protection device; the third polysilicon region is located in the third N well region + District and Third P + above the N well region between regions, the fourth polysilicon region is located in the fourth N + District and Third P + Above the N well region between the regions, there is an insulating layer between the third and fourth polysilicon regions and the N well region; The VDD rail of the power rails is connected. The third and fourth polysilicon regions are added above the P well region of the second type of low-voltage SCR ESD protection device; the third polysilicon region is located in the third P + District and Third N + above the P well region between regions, the fourth polysilicon region is located in the fourth P + District and Third N + Above the P wel...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More