LDMOS-SCR device with source-end embedded finger NMOS

A technology of LDMOS-SCR and devices, which is applied in the direction of electric solid-state devices, semiconductor devices, semiconductor/solid-state device components, etc., can solve the problems of insufficient anti-latch-up ability and low maintenance voltage, and increase the ESD current discharge capacity , enhance the resistance-capacitance coupling effect, and improve the effect of conduction uniformity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] Below in conjunction with accompanying drawing and specific embodiment the present invention will be described in further detail:

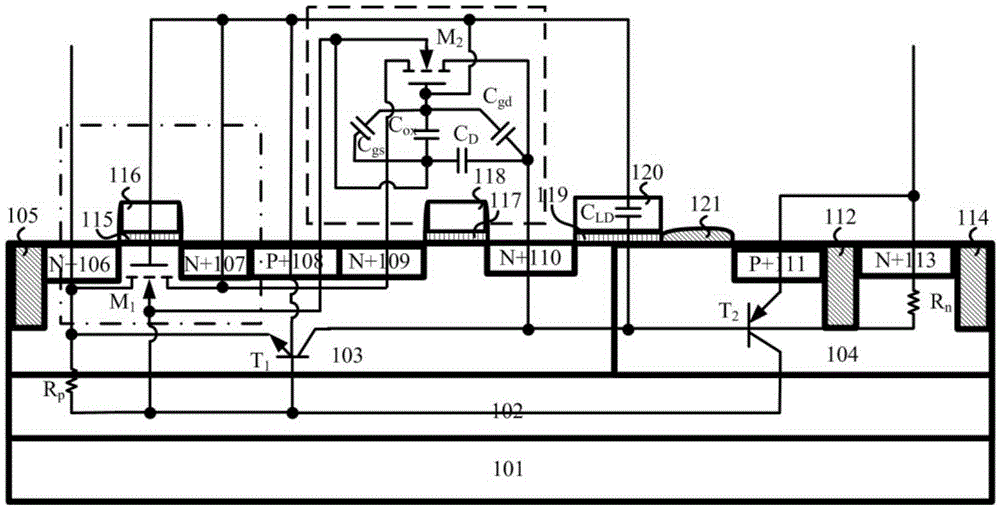

[0026] The example of the present invention designs an LDMOS-SCR device with interdigitated NMOS embedded in the source terminal, which not only utilizes the high-voltage resistance characteristics of LDMOS, but also utilizes the robustness of SCR strong ESD current. The interdigitated NMOS structure is embedded in the terminal design, and the resistance-capacitance coupling effect is formed by means of the source-side substrate parasitic resistance to improve the current conduction uniformity and turn-on speed of the device, enhance the ESD robustness of the device, and also increase the size of the device. the sustaining voltage.

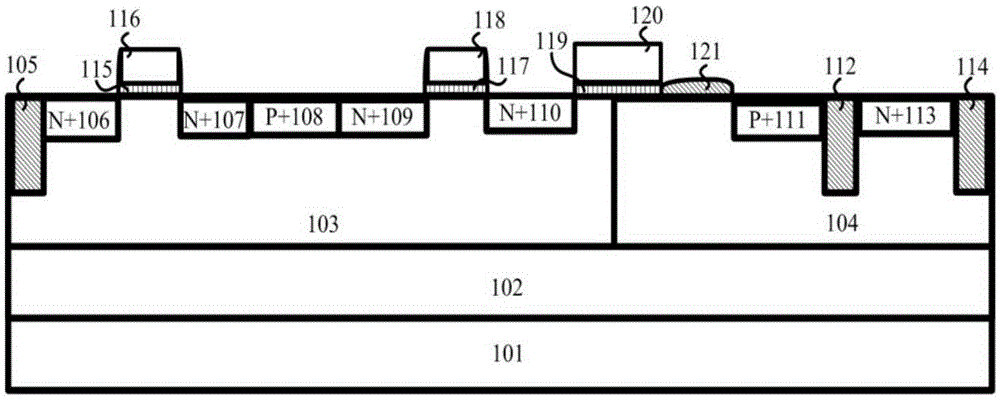

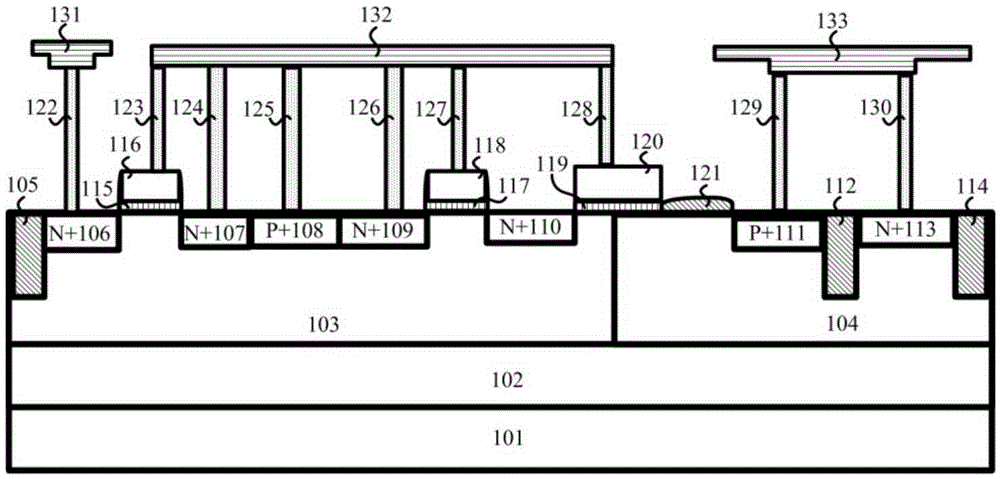

[0027] Such as figure 1 The sectional view of the internal structure of the example device of the present invention shown, its main feature is: mainly by P substrate 101, P epitaxy 102, P well 103, N well 104,...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More