ESD protection design with turn-on restraining method and structures

a protection circuit and turn-on technology, applied in the direction of semiconductor devices, electrical equipment, semiconductor/solid-state device details, etc., can solve the problems of high cost, increased cost, and serious degradation of cmos integrated circuits (ics), and achieve the reduction of the turn-on speed of the first mos transistor, improve the esd robustness of i/o cells, and increase the drain breakdown voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0054]The present invention will now be described by way of preferred embodiments with references to the accompanying drawings. Like numerals refer to corresponding parts of various drawings.

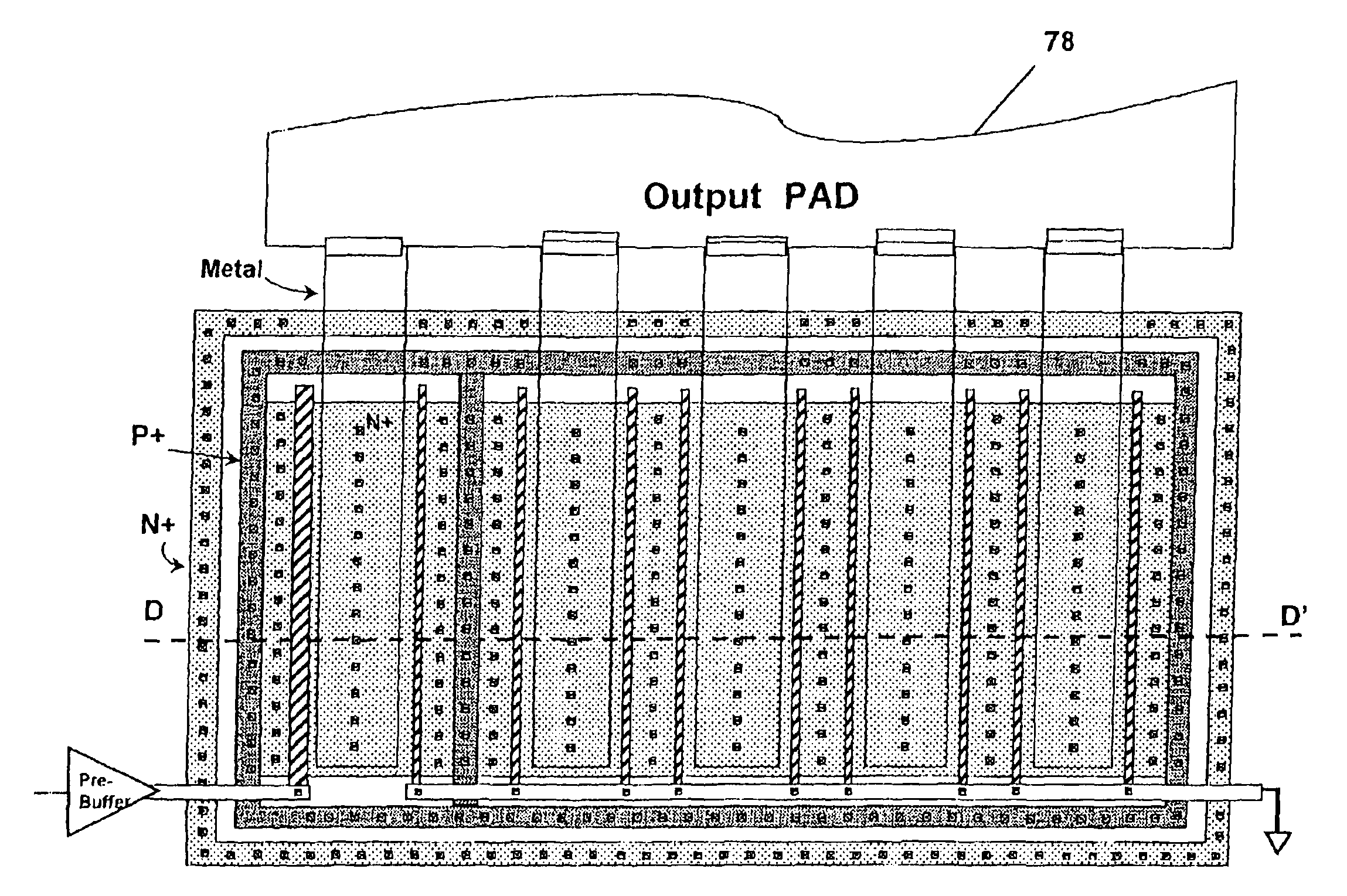

[0055]Referring now to FIGS. 7(a) and 7(b), one embodiment of the present invention is shown in which a simple layout is employed for drawing an additional P+ pick-up diffusion region 70, which surrounds one of the MOS transistors (Mn1 guarded device) 72 to reduce its parasitic base-emitter resistance. Therefore, the parasitic BJT in Mn1 has a slower turn-on speed than that of the other MOS transistor (Mn2 ESD protection device) 74. As shown in FIG. 7(b), a pre-buffer 76 with a core logic 77 is connected to the Mn1 device 72, a pad 78 is connected to the Mn1 device 72 and Mn2 device 74, and an ESD current discharging path is indicated by dash lines when the turn-on speed of Mn1 device 72 is slowed down. A corresponding top layout view is shown in FIG. 7(c) in which a cross-sectional view along t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More