Patents

Literature

70results about How to "Does not increase the area" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Image sensor

ActiveCN104735427ADoes not increase the areaReduce manufacturing difficultyPicture signal generatorsRadiation controlled devicesLight sensingLight filter

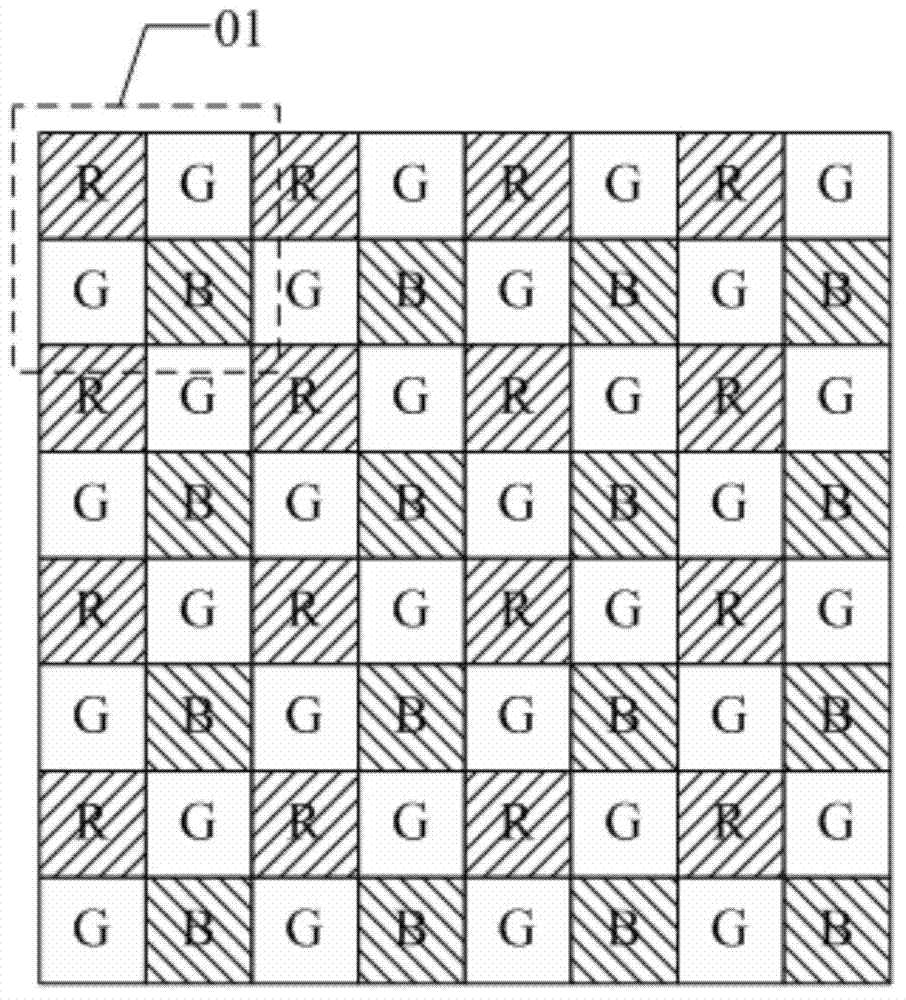

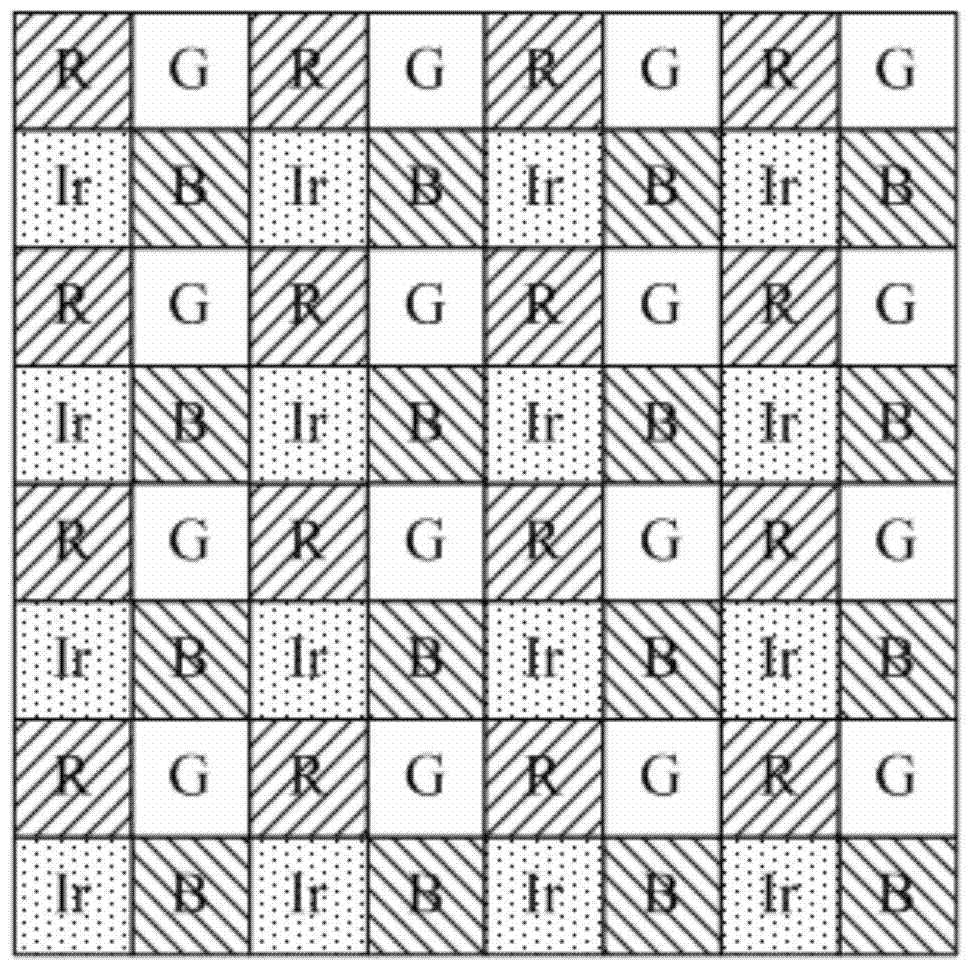

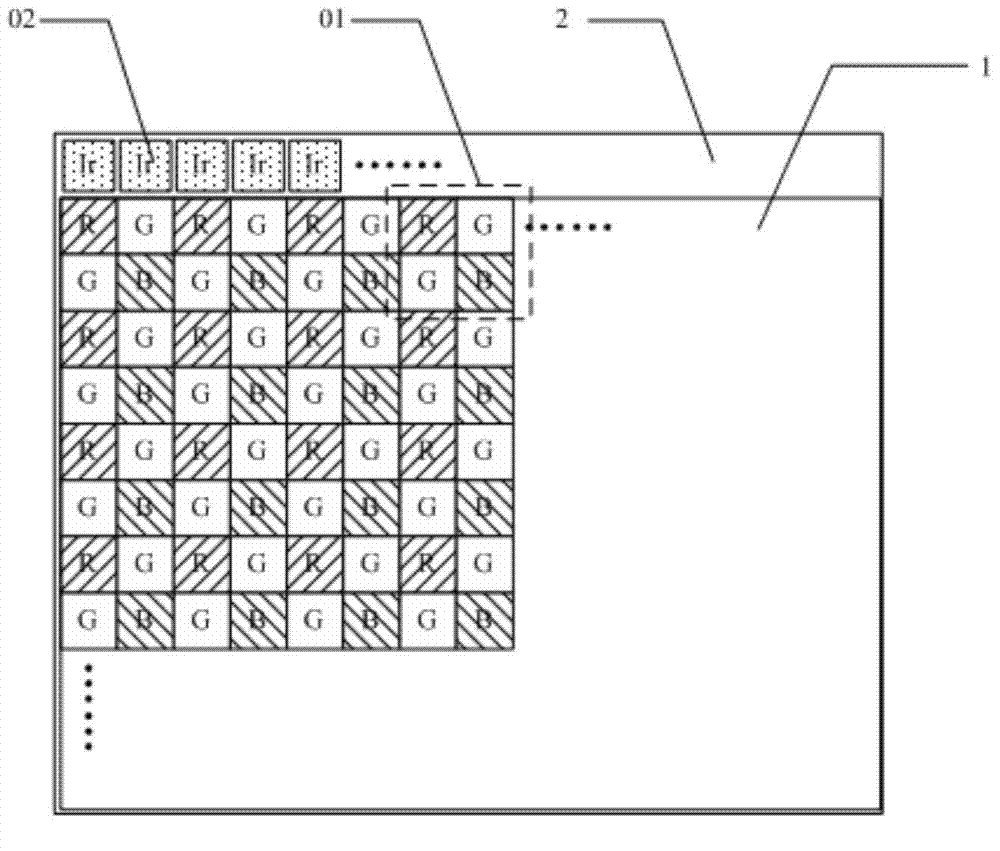

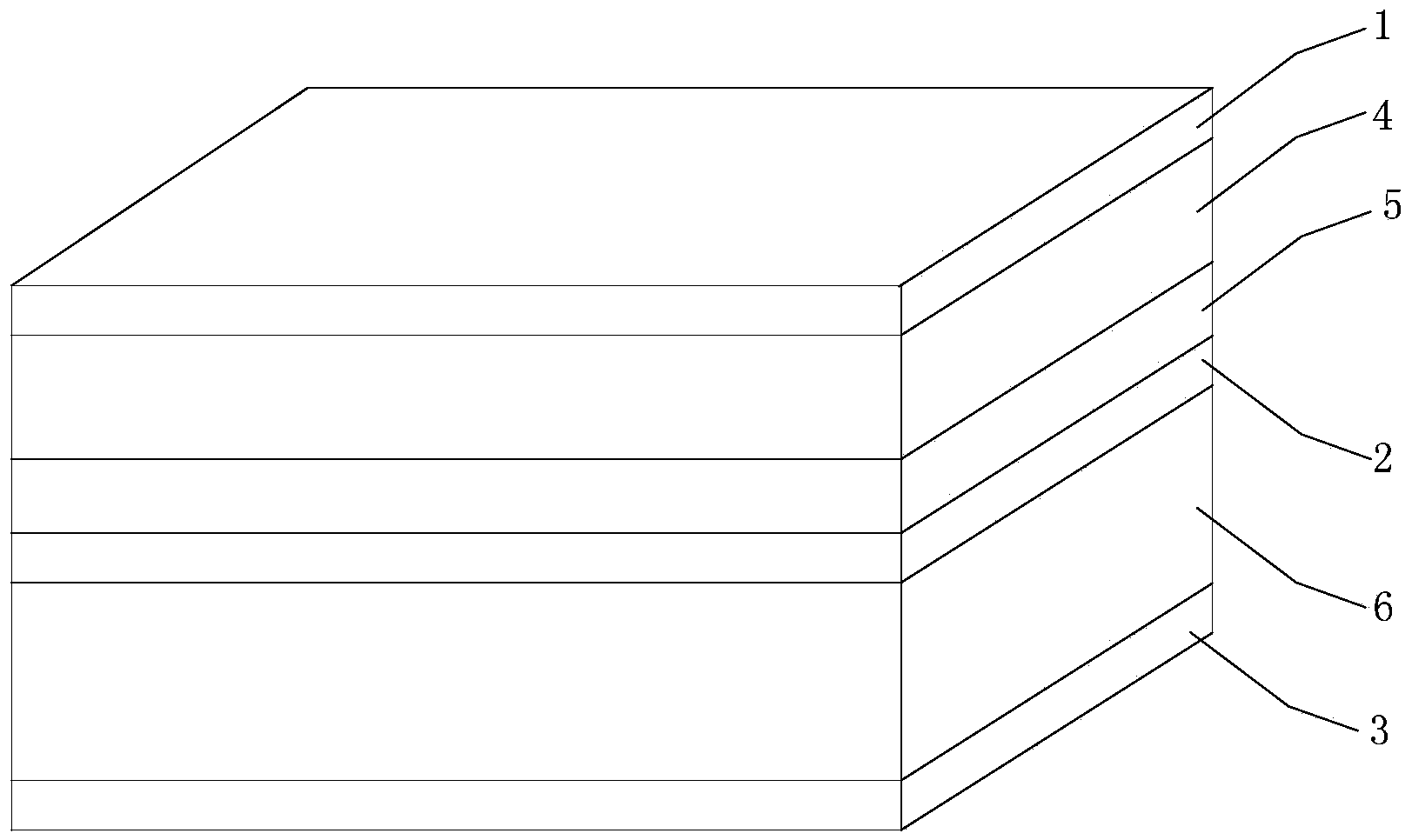

The invention discloses an image sensor. Compared with an existing image sensor, due to the fact that an existing visible light sensing unit in a Bayer format is reserved in a center area of a light sensing unit array and an infrared light sensing unit is added in the marginal area, the intensity of infrared light and the intensity of the visible light can be obtained through only one two-way light filter, and the cost of the light filter and a switching mechanism is reduced. In the daytime, the intensity of the visible light and the intensity of the infrared light can be worked out by means of the light sensing unit in the center area and the light sensing unit in the marginal area, so that the color accuracy of a daytime image is ensured; at night, the light sensing unit in the center area can receive the energy of the visible light and the energy of the infrared light at the same time, and the night image brightness is increased. In addition, due to the fact that the infrared light sensing unit is arranged on the marginal area of the light sensing unit array, compared with the existing image sensor, the positions of redundant light sensing units on the periphery of the image sensor are just utilized, and the area of the image sensor will not be increased.

Owner:ZHEJIANG DAHUA TECH CO LTD

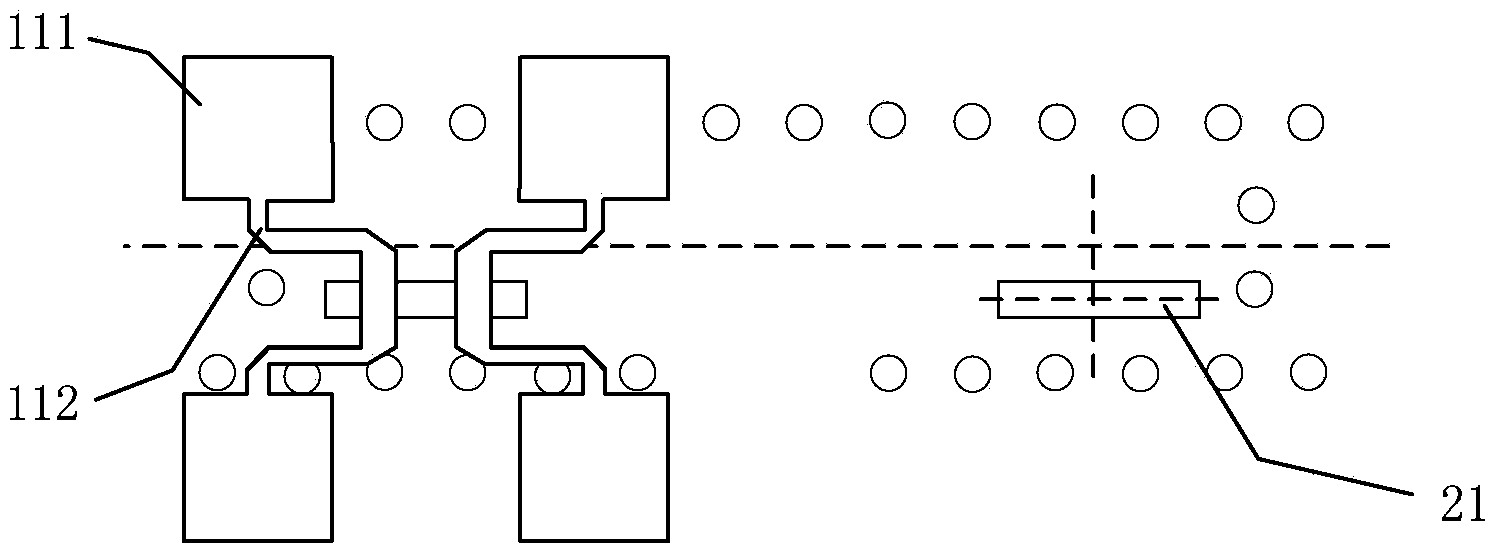

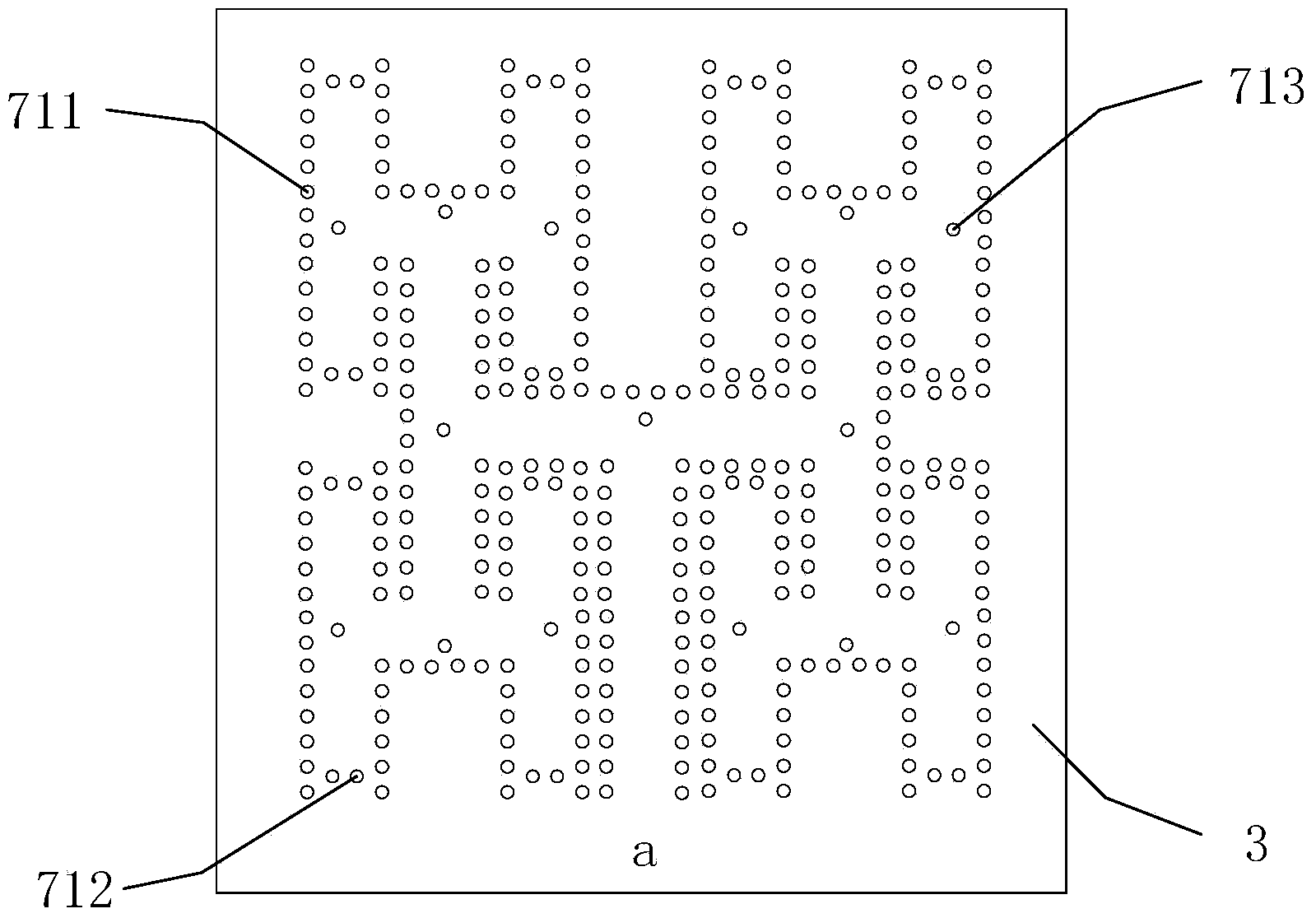

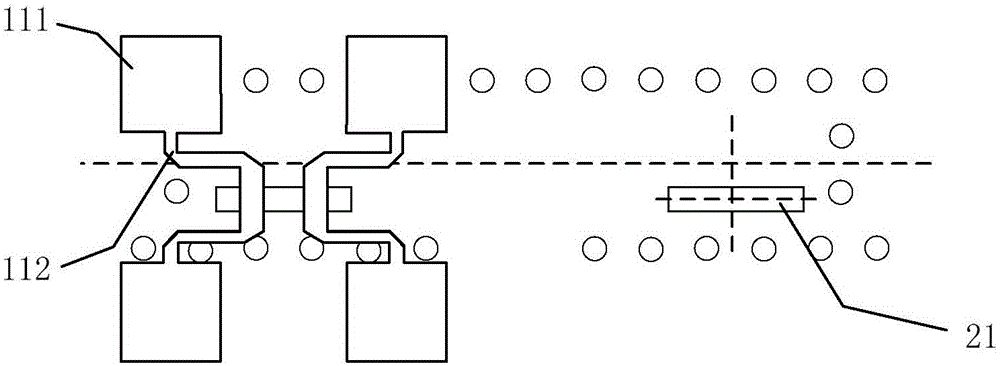

Broadband flat plate array antenna

ActiveCN103825101AWidening bandwidthHigh gainAntenna arraysResonant antennasHigh impedanceLarge array

The invention discloses a broadband flat plate array antenna, broadband can be achieved, and array antenna gain can be improved. According to the broadband flat plate array antenna, a coupling groove is used for stimulating two micro-strip subarrays, at the time, the impedance of a single micro-strip wire is high, a radiation paster can easily carry out high-impedance matching, accordingly the bandwidth of the micro-strip subarrays is widened, broadband is achieved, the relative bandwidth (Sll < -10 dB) of the feeding mode can reach 16%, 1 dB gain bandwidth can reach 14.6%, and common structure bandwidth is only about 6%. In addition, an H-shaped base chip is used for integrating a waveguide feeding network, the micro-strip subarrays are connected in parallel for feeding, along with increasing of array units, the bandwidth is hardly changed, broadband features can be kept in a large array, and array antenna gain can be improved gradually. In addition, the feeding network is placed below the micro-strip subarrays, extra circuit area cannot be increased, and array antenna miniaturization is promoted. The broadband flat plate array antenna is suitable for promotion and application in the technical field of microwave and millimeter wave antennas.

Owner:成都宁锦威通信技术有限公司

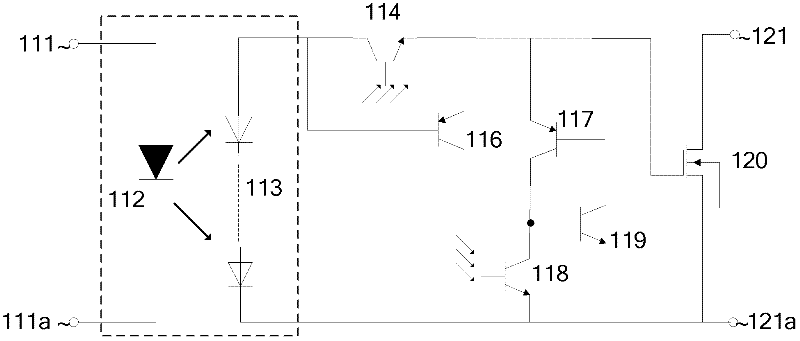

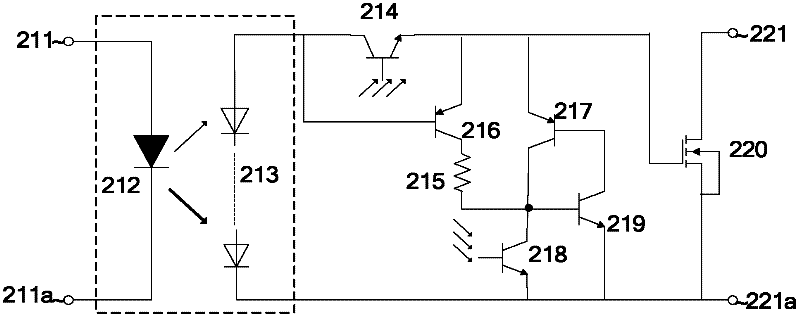

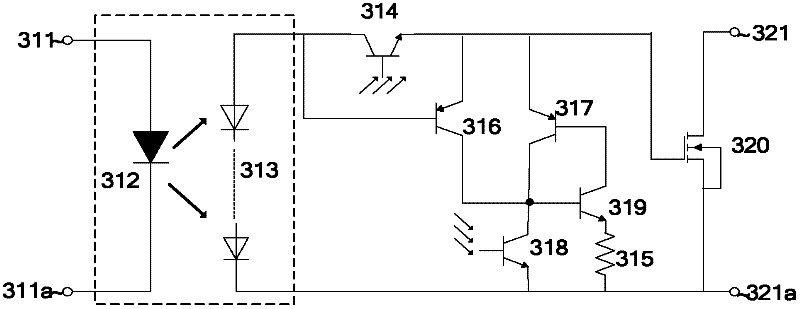

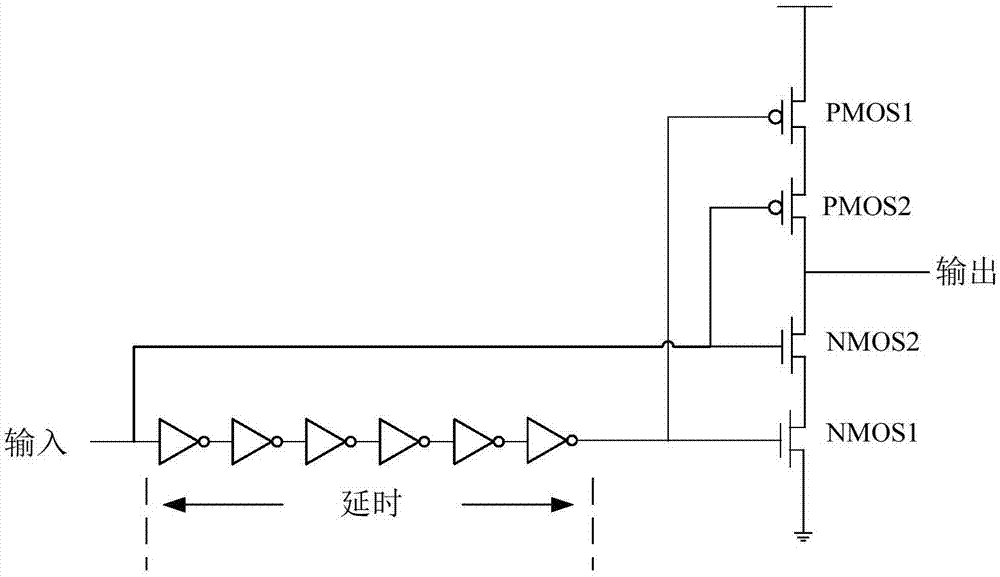

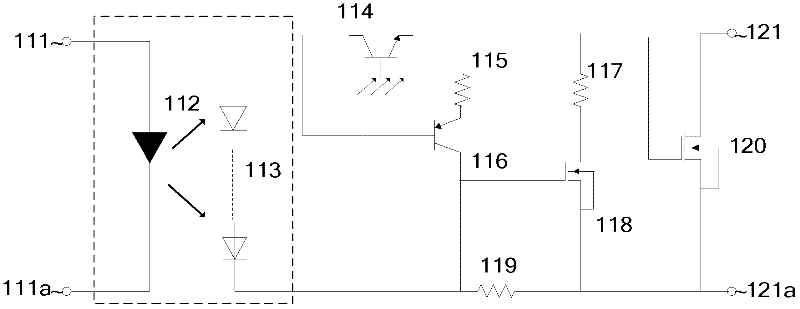

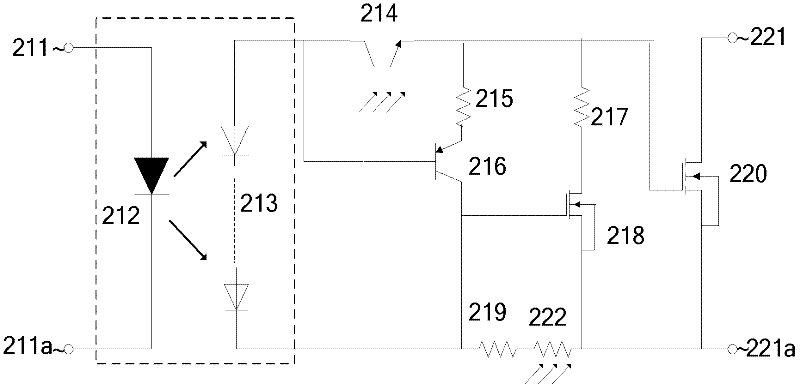

Solid-state relay

The invention discloses a solid-state relay which comprises a light-emitting element, a photovoltaic diode array, one or two normally open metallic oxide field effect transistors which are arranged between output terminals of the relay, an accelerated charging circuit formed by photoelectric triodes, and an accelerated leakage circuit formed by two PNP triodes, an NPN triode and a photoelectric triode. The solid-state relay can be realized in a way that the output metallic oxide field effect transistor gate capacitance is charged and discharged, the purpose of fast connection and disconnection on the relay can be achieved by using the circuit structure, the photoelectric triodes are led, the circuit is at a state of illumination when the output metallic oxide field effect transistor gate capacitance is charged, and the photoelectric triodes of the accelerated charging circuit are at a state of low resistivity. The relay is simple in structure, and improves the anti-interference capability when the connection time is not added.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

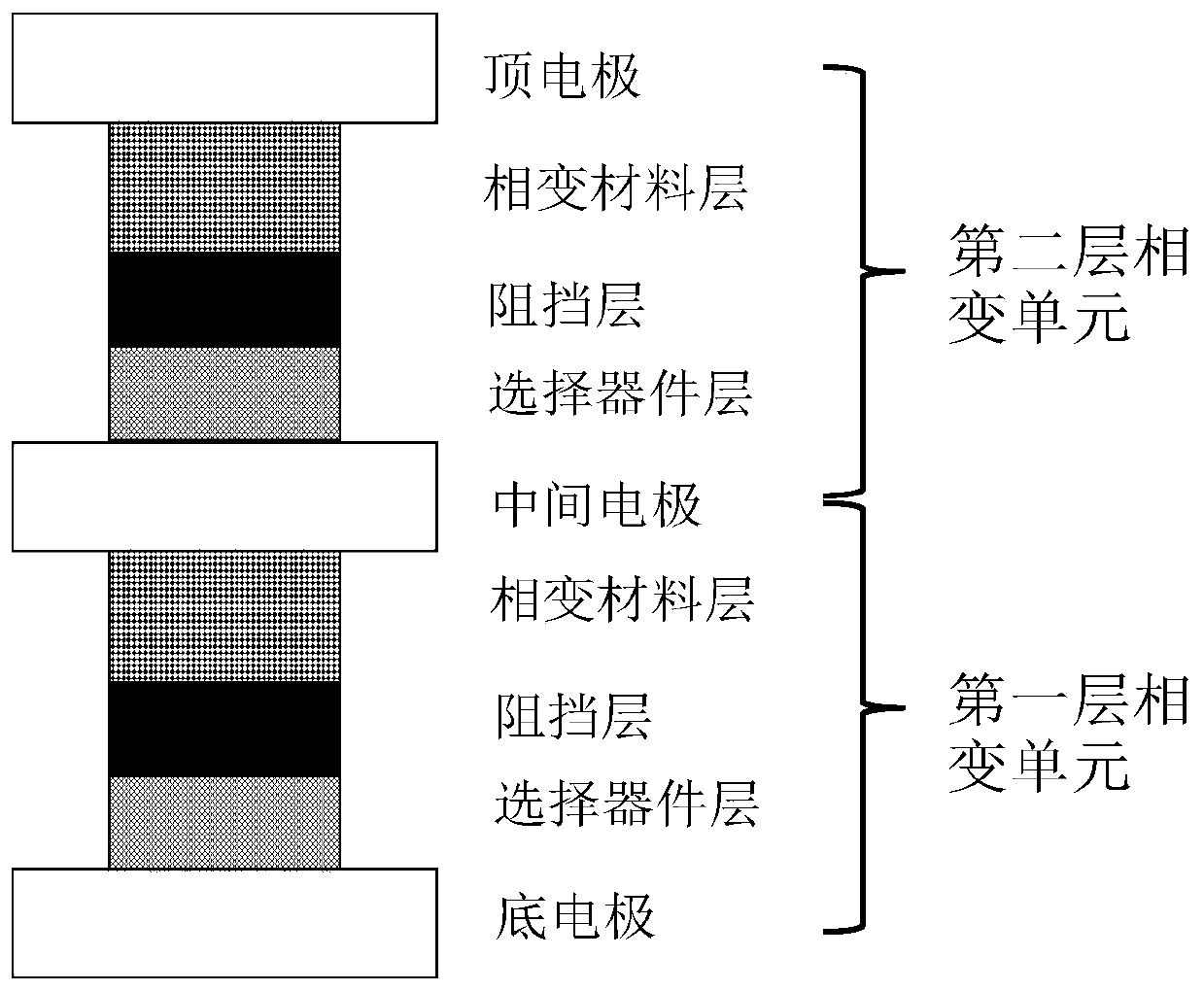

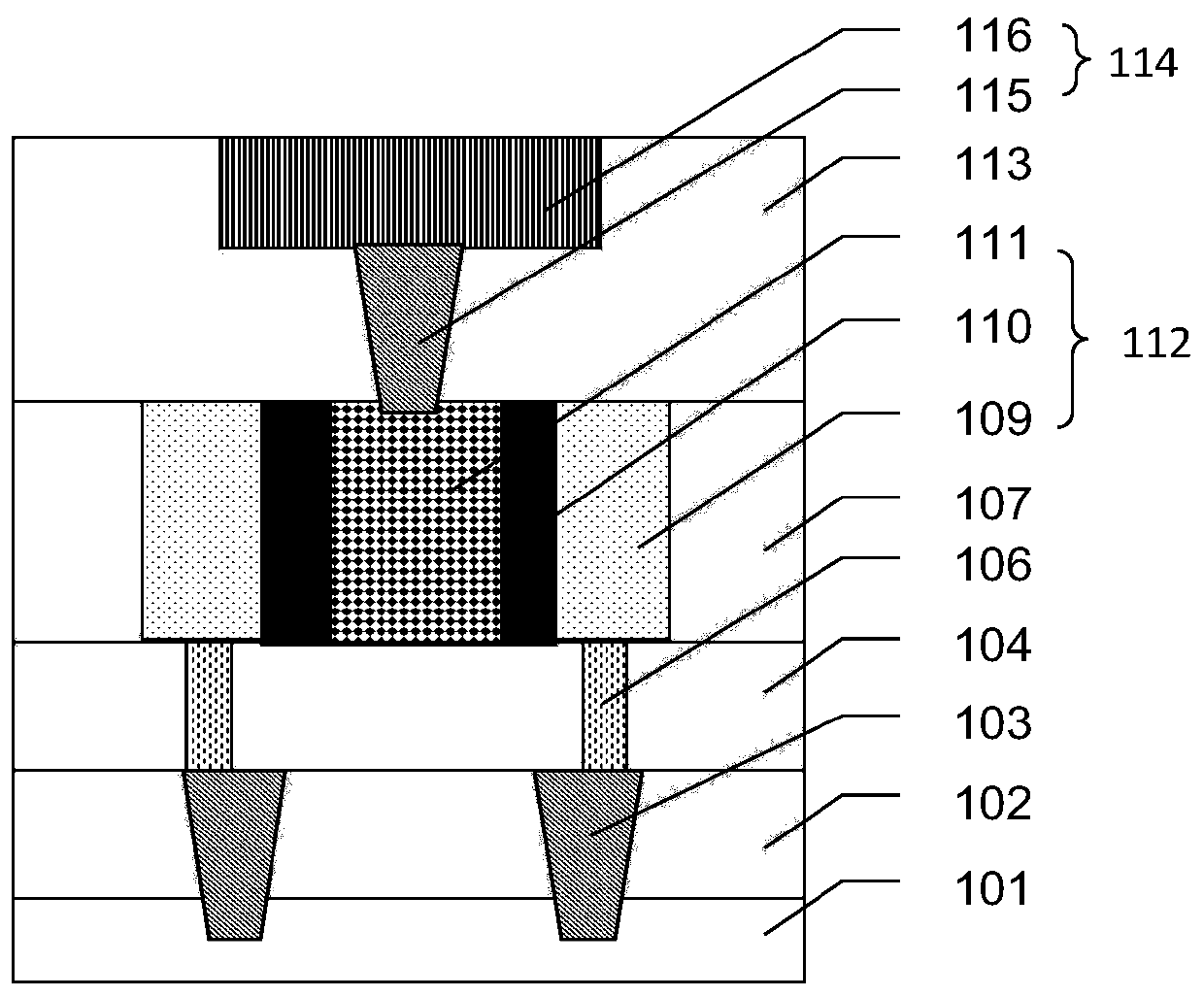

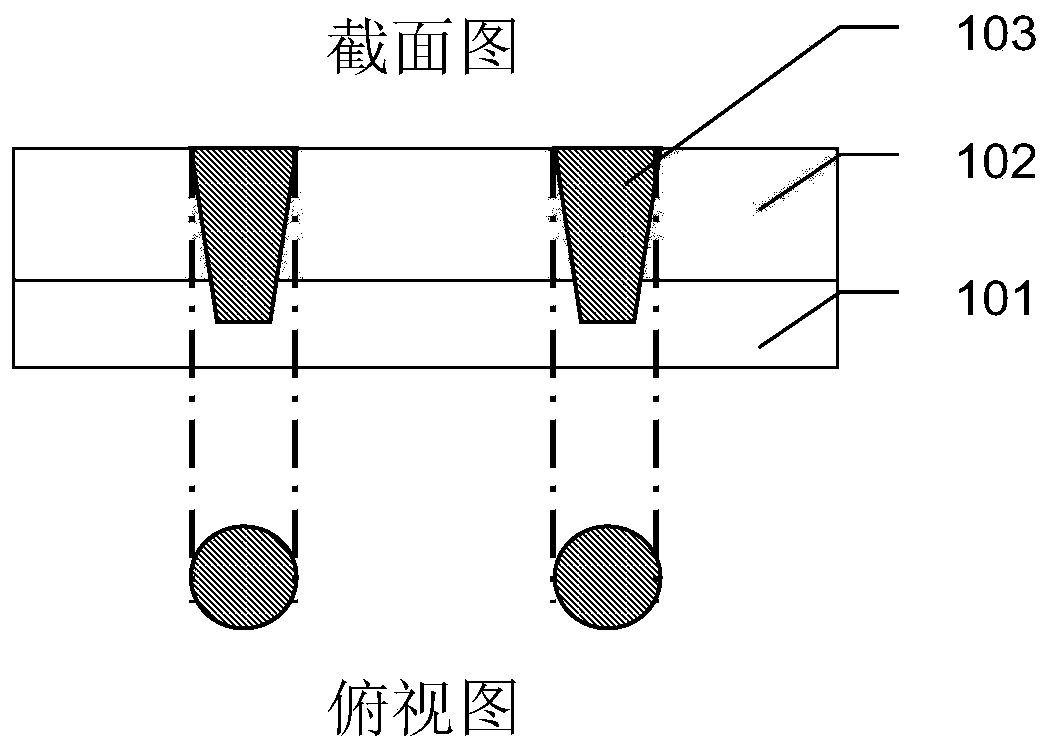

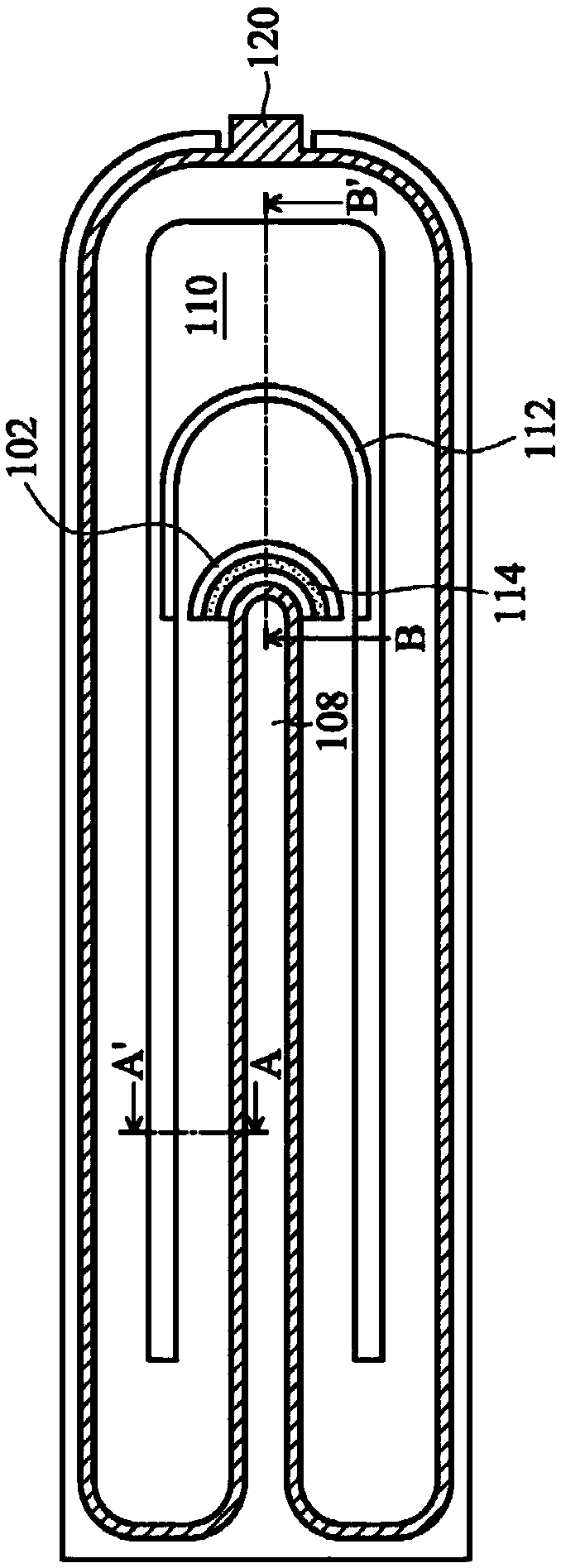

Phase change memory unit and preparation method thereof

ActiveCN111146339AReduce the volume of the phase change operation regionReduce device power consumptionSolid-state devicesSemiconductor devicesComposite materialMetal interconnect

The invention discloses a phase change memory unit. The phase change memory unit comprises bottom electrodes, heating electrodes, a phase change unit and a top electrode from bottom to top, and the phase change unit is of a longitudinally arranged cylinder structure and comprises a cylindrical selection device layer, an annular barrier layer and an annular phase change material layer from inside to outside; the plurality of bottom electrodes and the plurality of heating electrodes are in one-to-one correspondence, the bottom electrodes, the heating electrodes and the phase change material layer are sequentially connected, and the selection device layer is connected with the top electrode. According to the invention, the phase change unit and the plurality of heating electrodes are combinedtogether to form a structure that a plurality of phase change resistors share one selection device, and different phase change resistors can be connected with the bottom electrodes positioned on different metal interconnection layers through respective heating electrodes, so that the area of the chip in the horizontal direction is not increased, high-density storage is realized, the phase changematerial and the heating electrodes are very thin, and the power consumption of the device can be effectively reduced.

Owner:SHANGHAI INTEGRATED CIRCUIT RES & DEV CENT

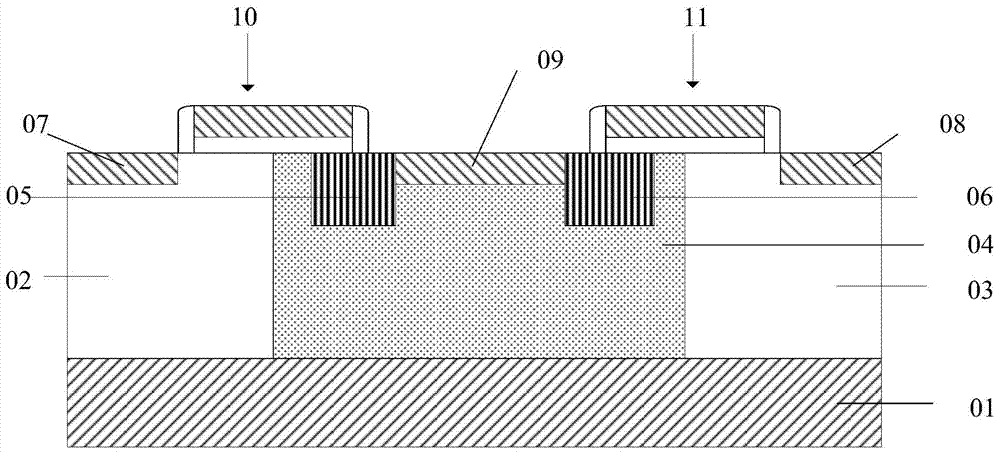

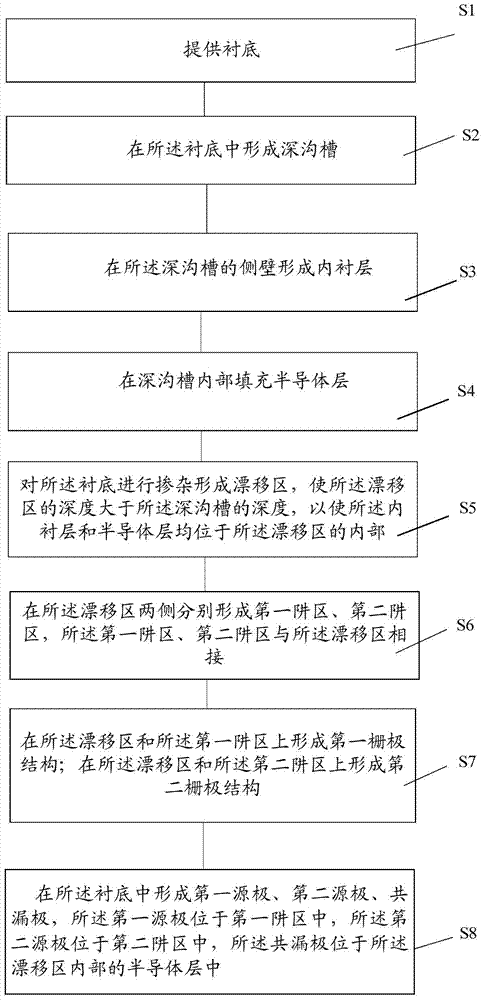

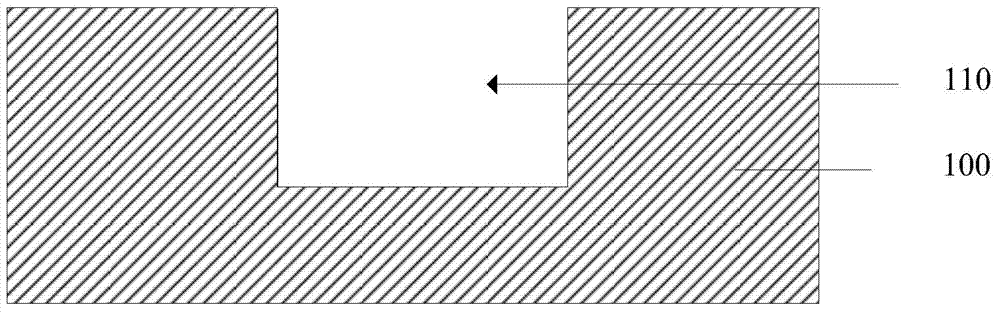

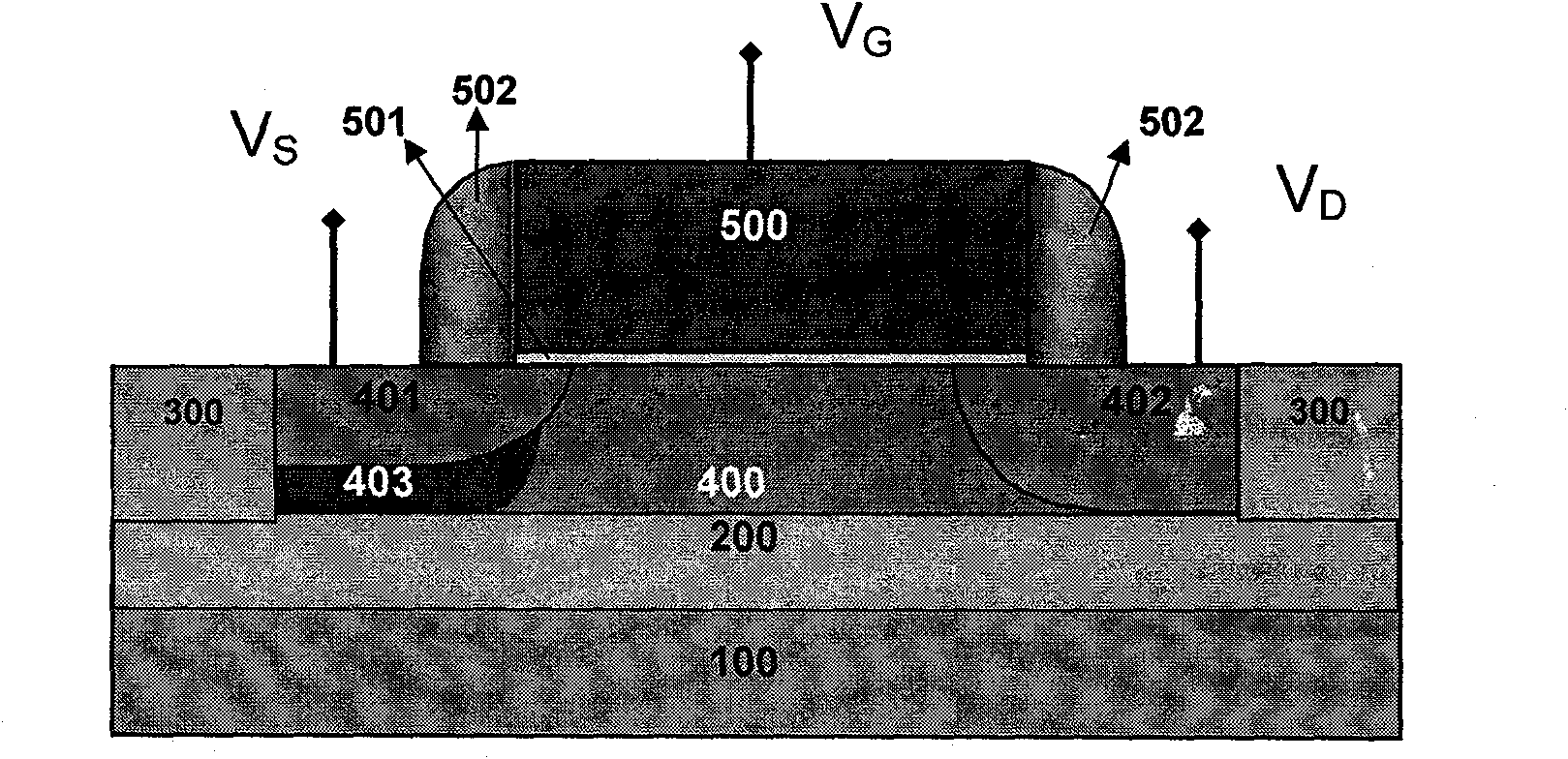

LDMOS (lateral double-diffused metal oxide semiconductor) transistor structure and formation method thereof

InactiveCN104517848AImprove breakdown voltageSmall sizeTransistorSemiconductor/solid-state device manufacturingLDMOSCommon drain

Disclosed are an LDMOS (lateral double-diffused metal oxide semiconductor) transistor structure and a formation method thereof. The formation method includes forming a deep groove in a substrate, forming a liner layer on the side wall of the deep groove, and filling a semiconductor layer in the deep groove; doping the substrate to form a drift area, and enabling the liner layer and the semiconductor layer within the drift area; forming a first trap and a second trap respectively in the substrate on two sides of the drift area, connecting the first trap and the second trap with the drift area; forming a first grid structure on the drift area and the first trap; forming a second grid structure on the drift area and the second trap; forming a common drain in the semiconductor layer exposed by the first grid structure and the second grid structure; forming a first source in the first trap exposed by the first grid structure, and forming a second source in the second trap exposed by the second grid structure. By the LDMOS transistor structure, breakdown voltage of the LDMOS transistor can be increased without increasing the area of the transistor.

Owner:SEMICON MFG INT (SHANGHAI) CORP

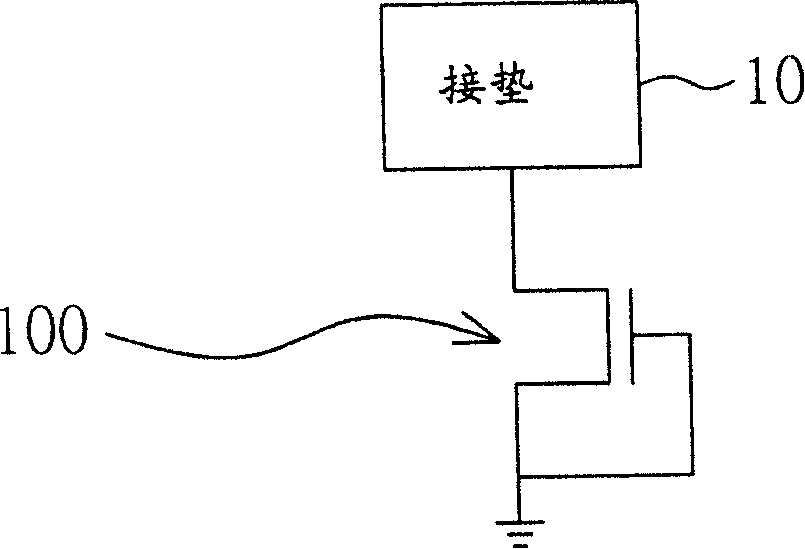

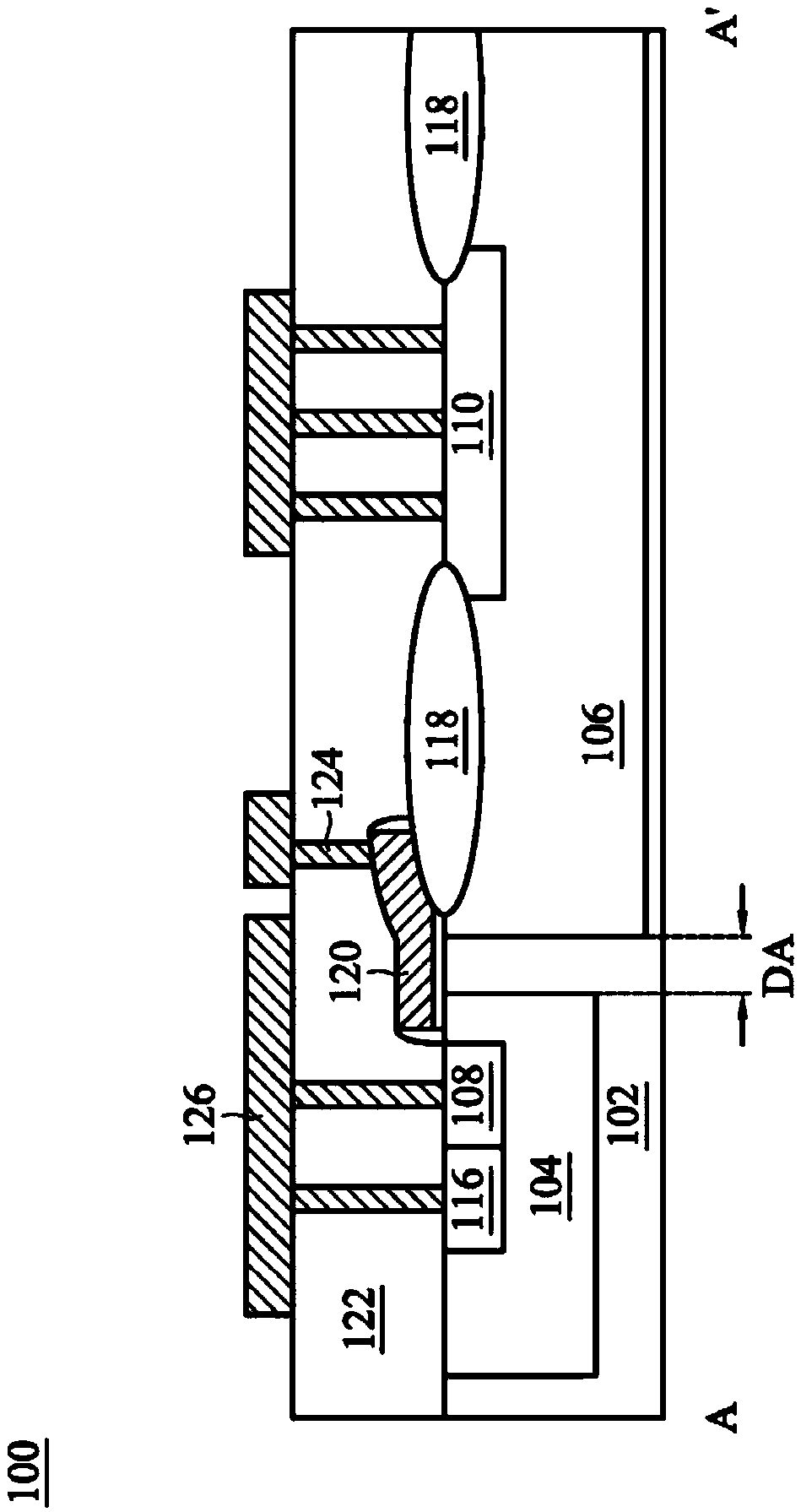

Electrostatic discharge protecting equipment of connection pad and its method and structure

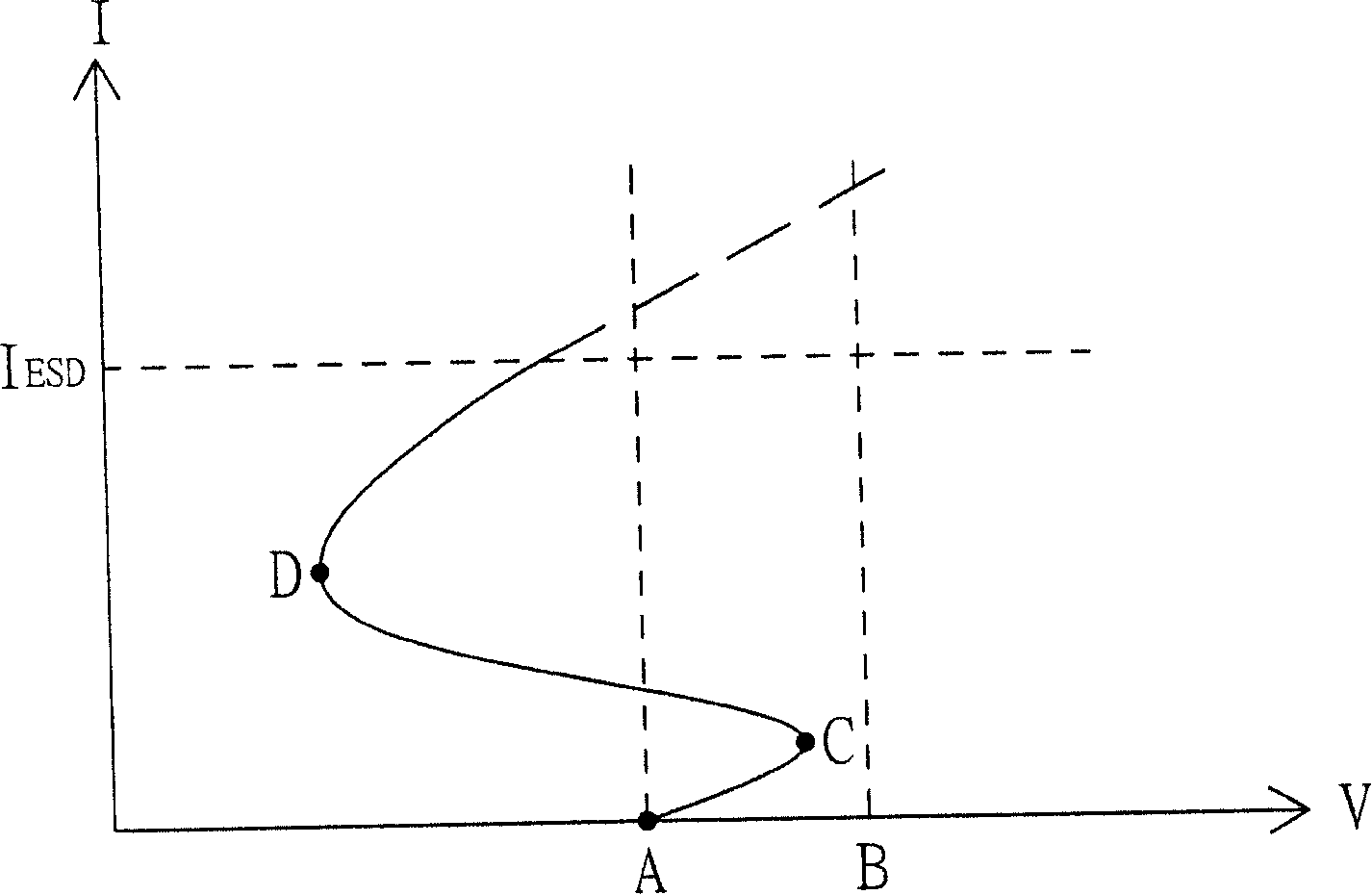

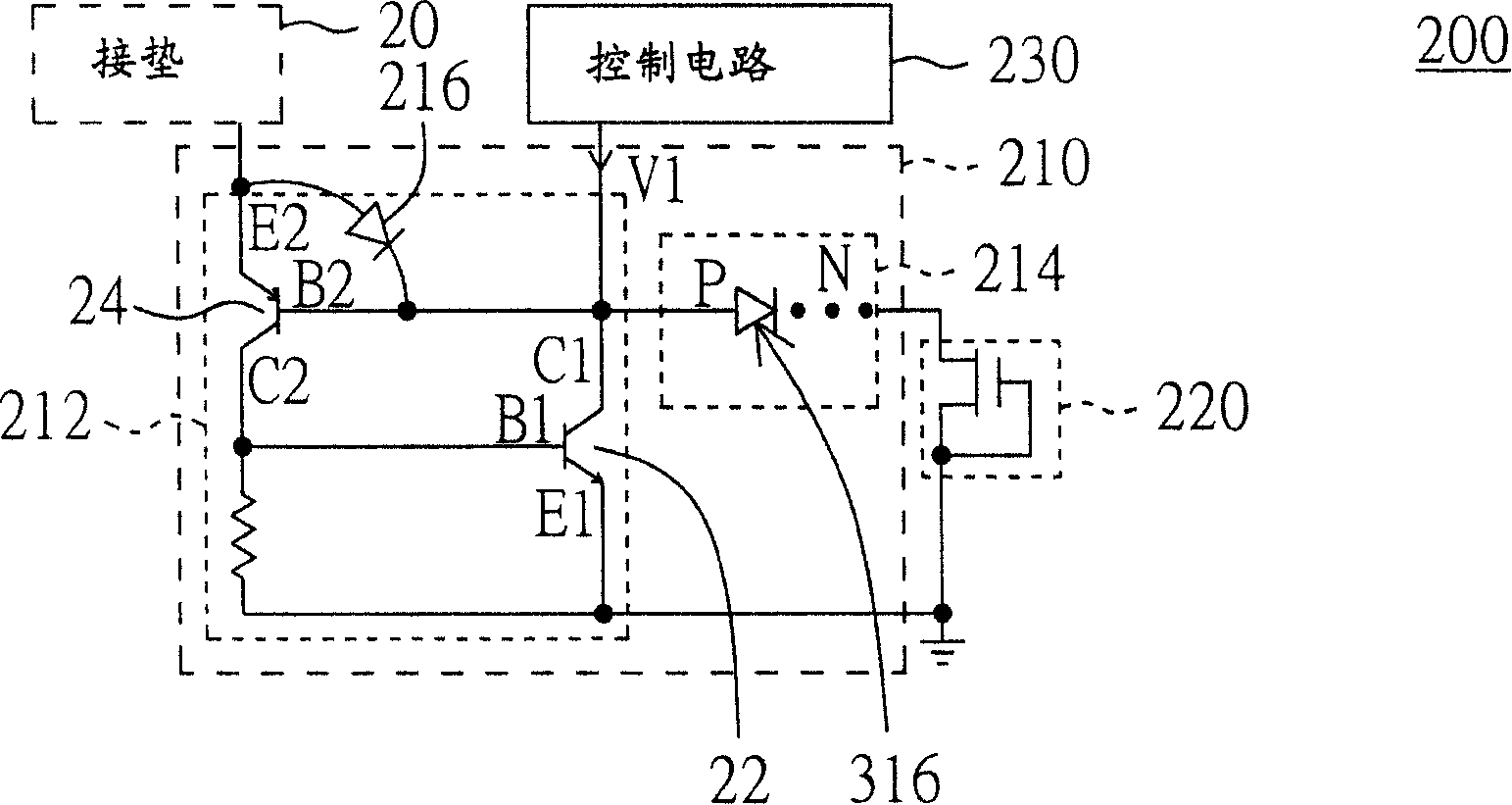

ActiveCN101174622ADoes not increase the areaIncrease the trigger voltageSemiconductor/solid-state device detailsSolid-state devicesSilicon-controlled rectifierCharge carrier

An electrostatic discharge protection device for a contact pad includes a regulating circuit, a snapback component and a control circuit. The regulating circuit includes a silicon controlled rectifier coupled to the pad. The silicon controlled rectifier includes a first diode. The snapback component is coupled to the N pole of the first diode when the second diode is not used, and is coupled to the N pole of the second diode when the second diode is used. The control circuit is coupled to the N pole of the first diode. In normal operation mode, the control circuit is used to provide a first voltage to the N pole of the first diode, so that the N pole of the first diode Collect a plurality of charged carriers, and make the silicon controlled rectifier not be turned on. In the electrostatic discharge mode, the control circuit does not provide the first voltage to the N pole of the first diode, so that the N pole of the first diode Charge carriers are not collected.

Owner:MACRONIX INT CO LTD

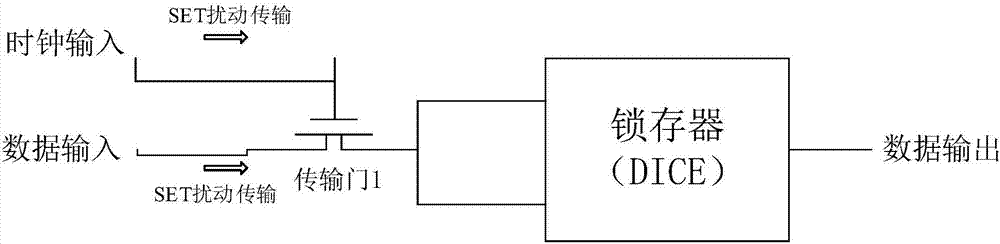

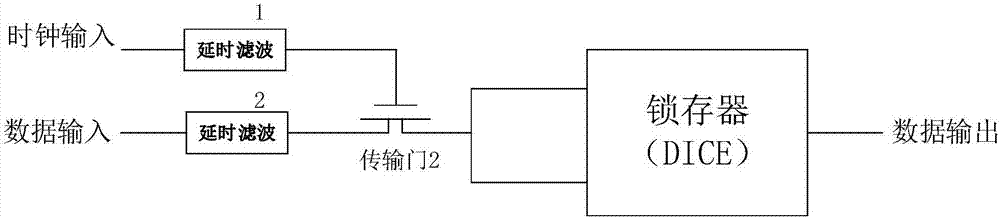

Single event transient disturbance reinforced latch circuit

InactiveCN107124176ADoes not affect the working frequencySimple structureReliability increase by circuit redundancyEngineeringOperating frequency

The invention relates to a single event transient disturbance reinforced latch circuit and belongs to the field of circuit design. The single event transient disturbance reinforced latch circuit comprises a first lowpass filter unit and a latch. First way data input of a data input end is connected with a first input end of the latch. Second data input of the data input end is connected with a second input end of the latch through the first lowpass filter unit. The first lowpass filter unit is a circuit unit which is composed of a passive device and is used for removing a high-frequency signal. The first lowpass filter unit for removing the high-frequency signal is composed of the passive device, the filter capacity only needs to be greater than the maximum pulse width produced by single event transient disturbance, the working frequency of the latch circuit is not influenced, and a circuit structure is simple. The passive device itself does not produce the single event transient disturbance and an area and the power consumption of a storage unit are not increased, so the single event effect resistance of logic circuits such as the latch and a trigger can be effectively improved.

Owner:58TH RES INST OF CETC

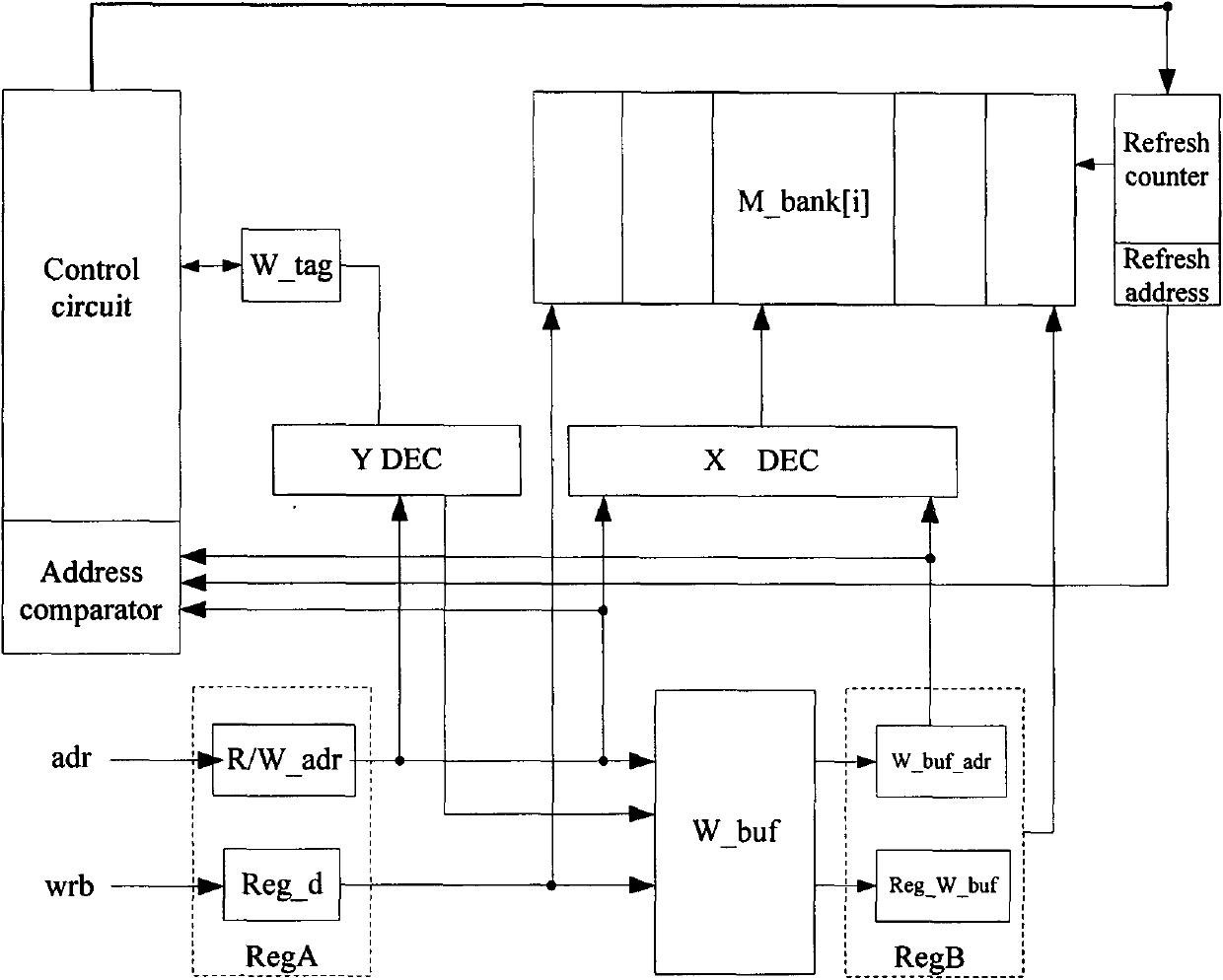

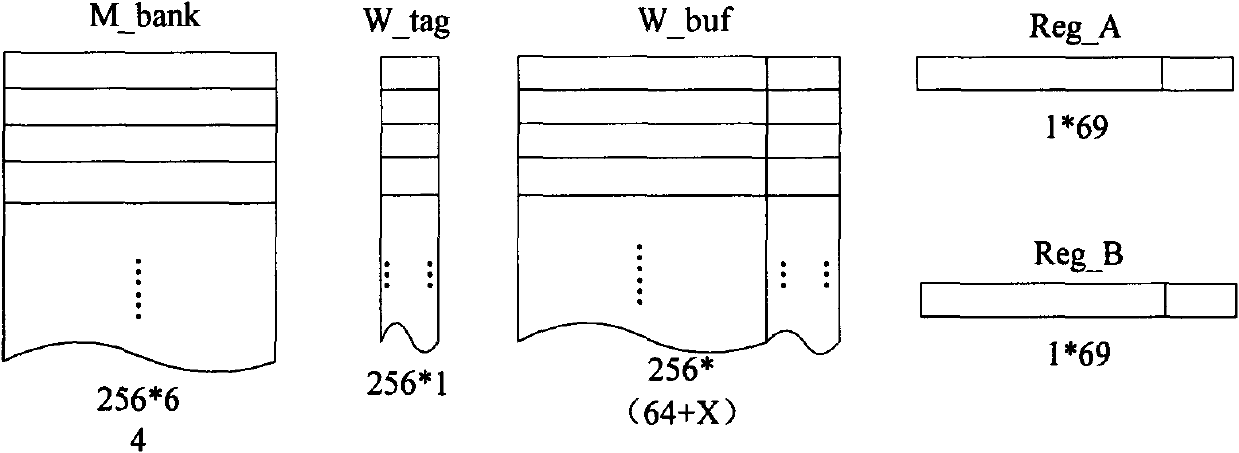

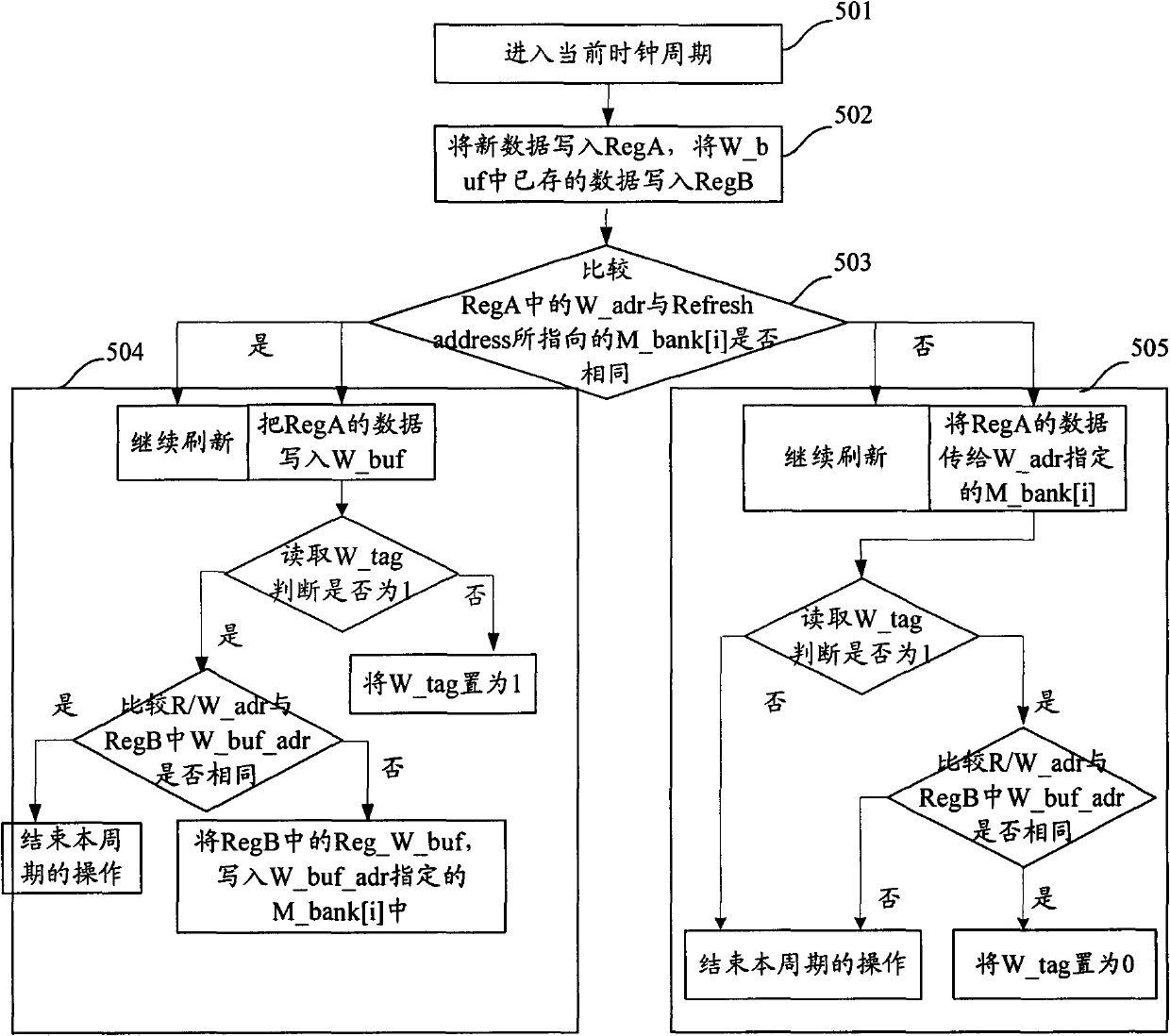

Pseudo-static memory and method for controlling write operation and refresh operation of pseudo-static memory

The invention provides a pseudo-static memory. The pseudo-static memory comprises a first register set, a second register set, a write operation buffer, a write operation flag register, a comparator and a control circuit, wherein the comparator is used for comparing a memory set address which the current write operation aims at with a memory set address in the second register set and outputting comparison result signals; the control circuit comprises a first control submodule; and the first control submodule is used for writing data in the first register set into the write operation buffer and executing the refresh operation when the write operation conflicts with the refresh operation in the current time period, setting a write state signal of the write operation flag register as a valid identification signal when the write state signal of the write operation flag register is an invalid identification signal, and writing data in the second register set into the appointed memory set when the write state signal of the write operation flag register is the valid identification signal and the comparator outputs the comparison result signals with different addresses. The pseudo-static memory can increase the access speed of a pseudo static random access memory (SRAM) so as to improve the working efficiency of the pseudo SRAM.

Owner:GIGADEVICE SEMICON (BEIJING) INC

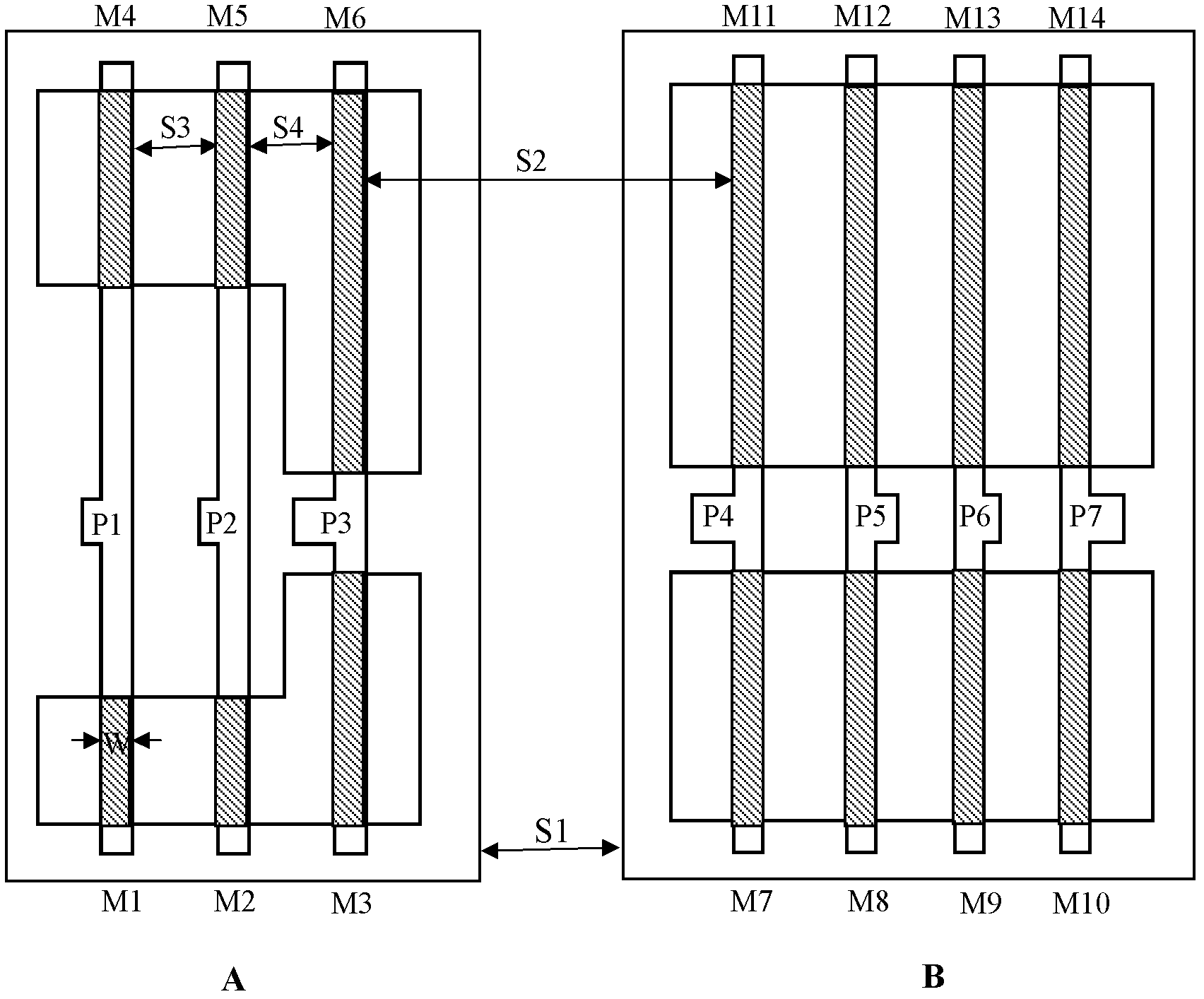

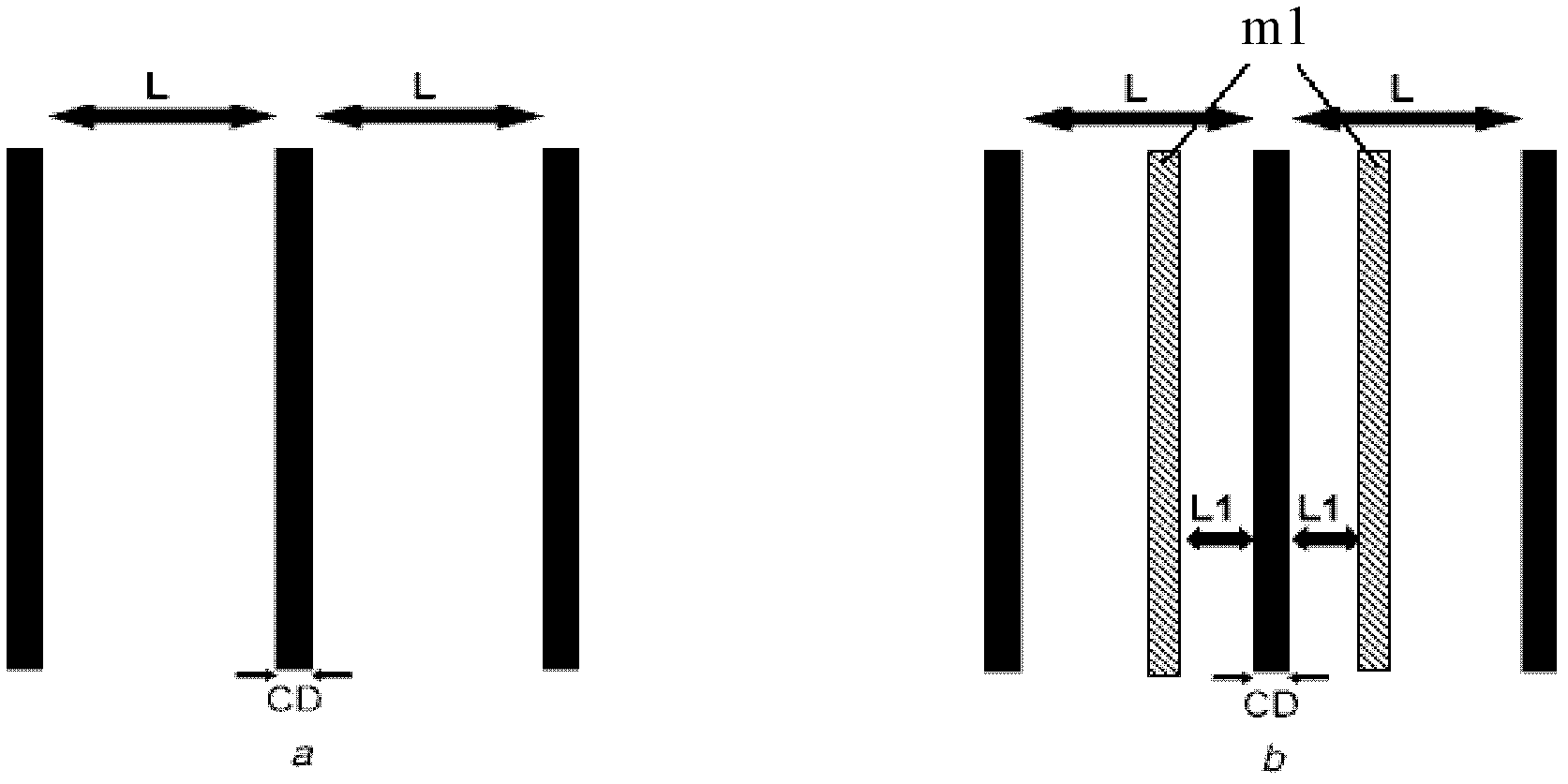

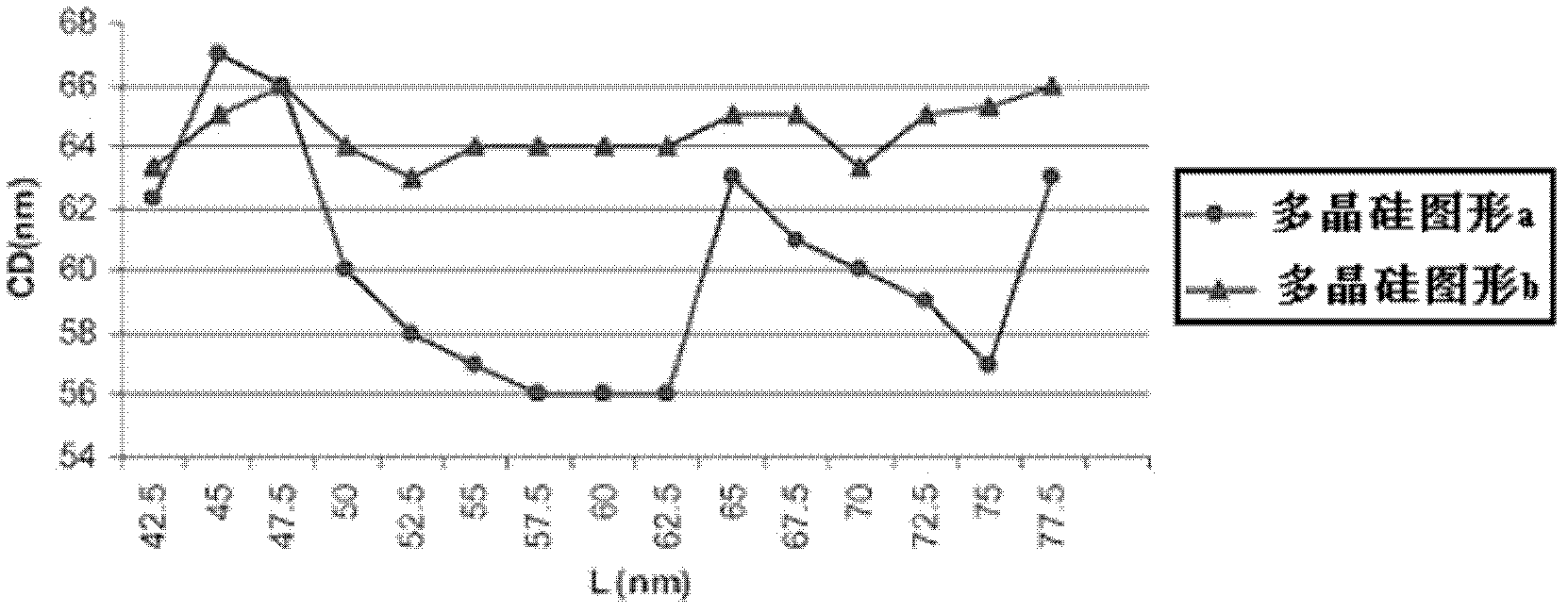

Insertion method for filling redundant polysilicon strip arrays in existing layout

InactiveCN102664142AEasy to operateLittle changeSemiconductor/solid-state device manufacturingSpecial data processing applicationsApplication-specific integrated circuitComputer science

The utility model discloses an insertion method for filling redundant polysilicon strip arrays in the existing layout. The insertion method comprises the following steps of: extracting the position information of standard cells; sequencing the position of the standard cells; judging whether distance exists between the adjacent standard cells or not; if the distance exists, respectively inserting the redundant polysilicon strip arrays into the opposite borders of the two adjacent standard cells; if the distance does not exist, inserting the redundant polysilicon strip arrays into the borders of the two adjacent standard cells in a shared mode; and moreover, checking layout design rules and the consistence of the layout and a schematic diagram to the layout where the redundant polysilicon strip arrays are inserted. Based on the current ASIC (Application Specific Integrated Circuit) design flow, the method optimizes the designed layout, and a standard cell library needs not to be modified, so that the operation is simple and is compatible with the current ASIC design flow. The method only finely adjusts the existing layout, the LVS (Low Velocity Scanning) and DRC (Data Record Control) check of the layout is not influenced, and the area of the layout cannot be increased.

Owner:ZHEJIANG UNIV

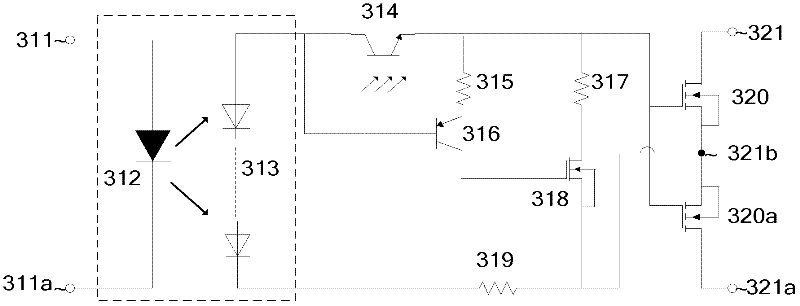

Solid state relay

InactiveCN102332900ALower latencyImprove anti-interference abilityElectronic switchingEngineeringTurn on time

The invention discloses a solid state relay, which comprises a photovoltaic diode array, one or two field effect transistors, a charging circuit and an acceleration discharge circuit, wherein the charging circuit consists of a photoelectric transistor and a resistor; an emitter of the photoelectric transistor is connected with a gate of the field effect transistor, a collector is connected to a first end of the photovoltaic diode array, and the resistor is connected between a source of the field effect transistor and a second end of the photovoltaic diode array; the acceleration discharge circuit consists of a triode, an N-channel field effect transistor and two resistors; the triode is connected with the gate of the field effect transistor through one resistor, the collector is connected to the second end of the photovoltaic diode array, and a base is connected to the first end of the photovoltaic diode array; and a drain of the N-channel field effect transistor is connected with the gate of the field effect transistor through one resistor, the source and a substrate are connected to the source of the field effect transistor, and the gate is connected to the second end of the photovoltaic diode array. The solid state relay is simple in structure; and when turning-on time is not increased, anti-interference capacity is improved.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

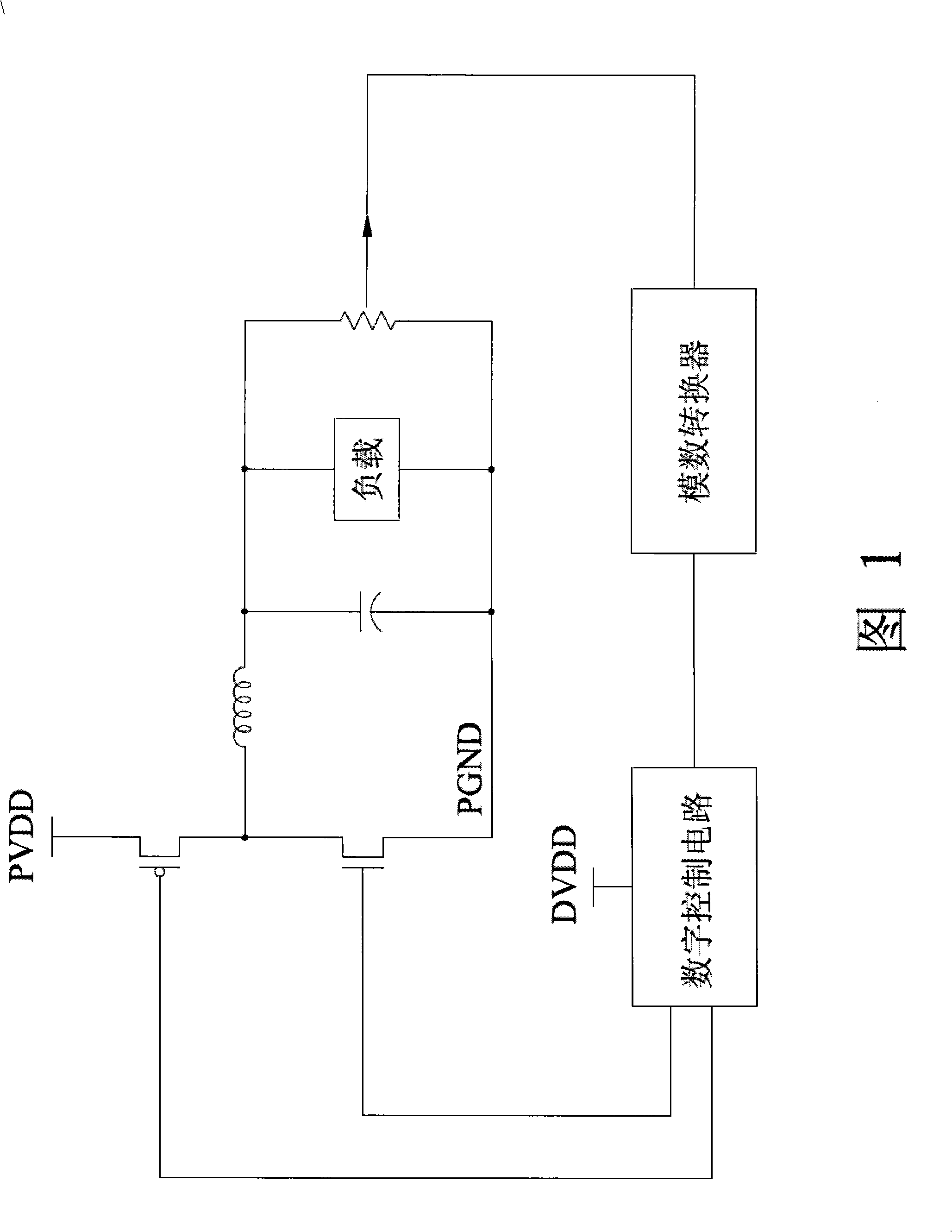

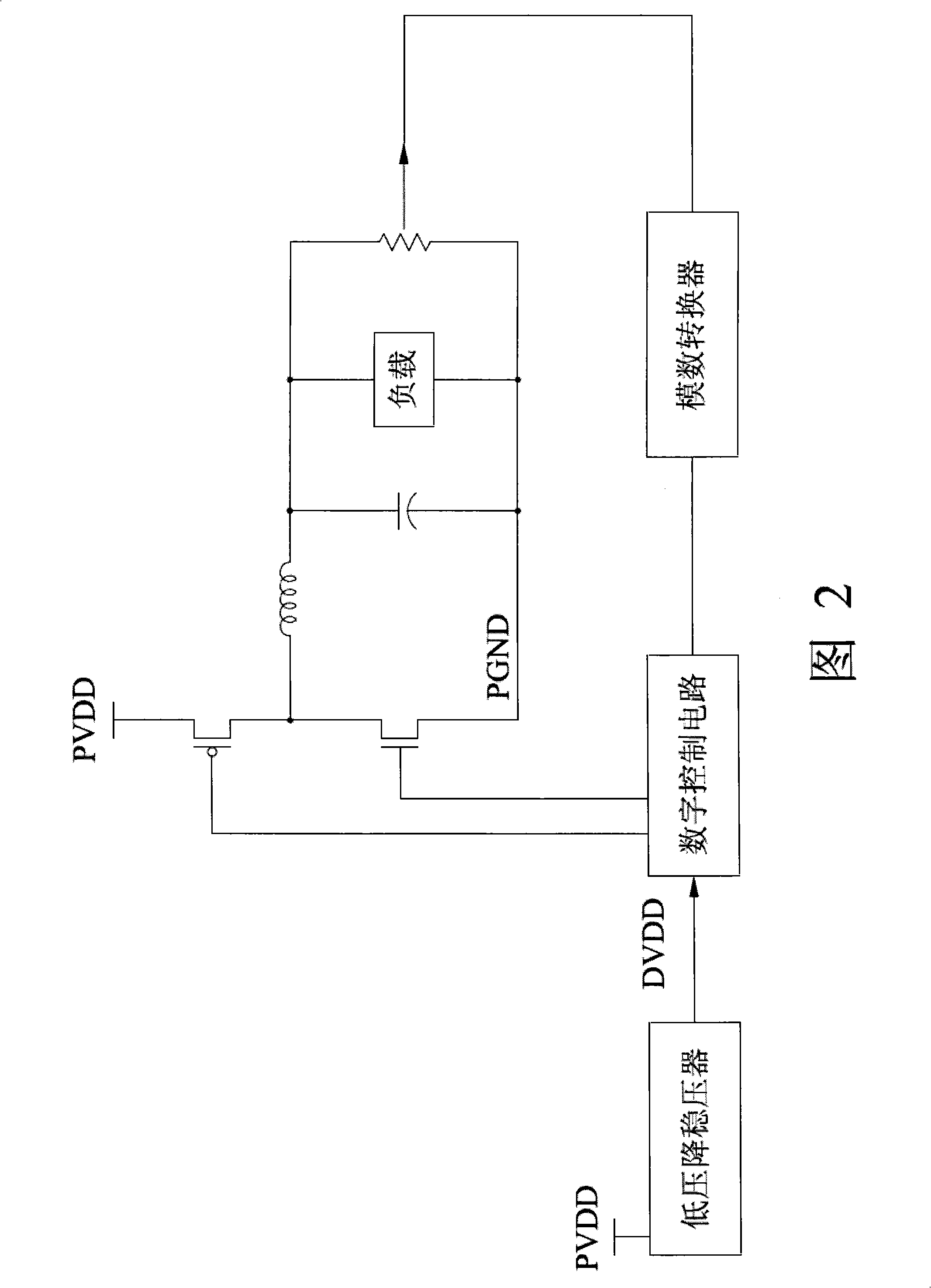

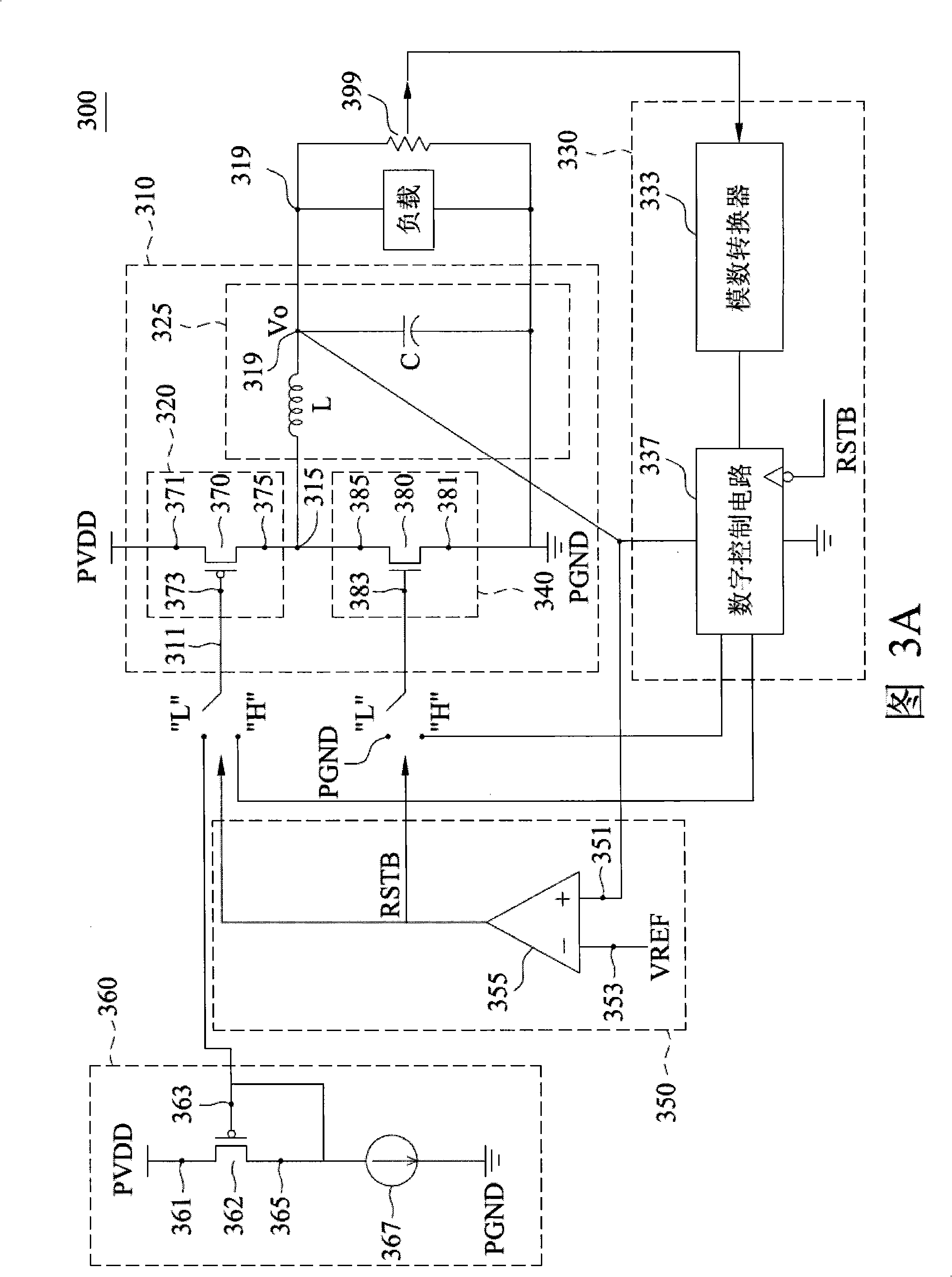

DC-DC converter

ActiveCN101404448ADoes not increase the areaDoes not affect conversion efficiencyEfficient power electronics conversionApparatus without intermediate ac conversionDc dc converterLow-pass filter

The present invention provides a DC-DC converter providing a DC output voltage at an output node. The DC-DC converter comprises an output stage, a digital controller, and a controller. The output stage comprises a pull-up circuit having a control terminal and coupled between a first fixed voltage and a internal node, a pull-down circuit coupled between the internal node and a second fixed voltage, and a low pass filter coupled between the internal node and the output node. The digital controller is powered by the DC output voltage and adjusts the DC output voltage by controlling the output stage. The controller controls a connection of a feedback path, comprising the digital controller, between the output node and the control terminal according to the DC output voltage.

Owner:MEDIATEK INC

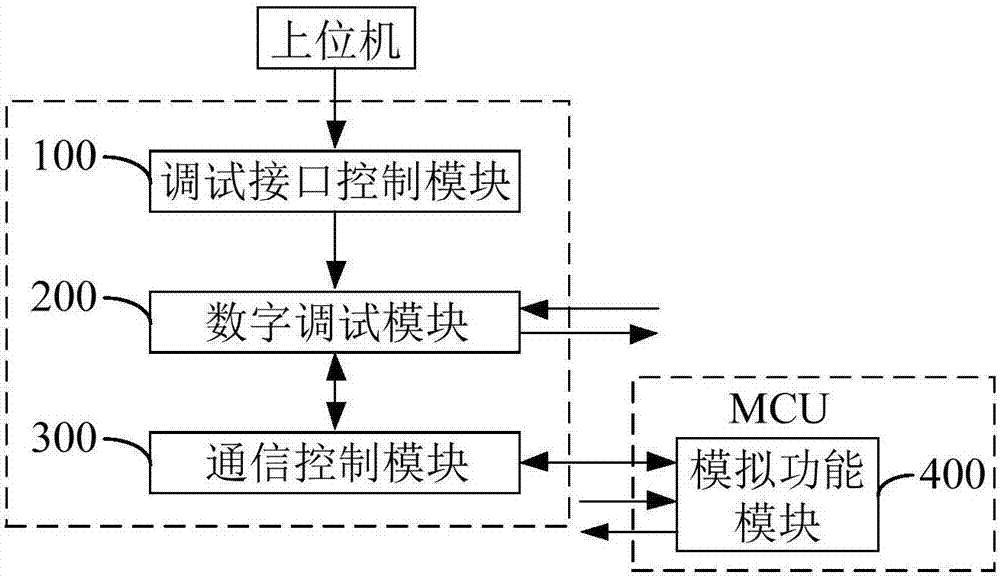

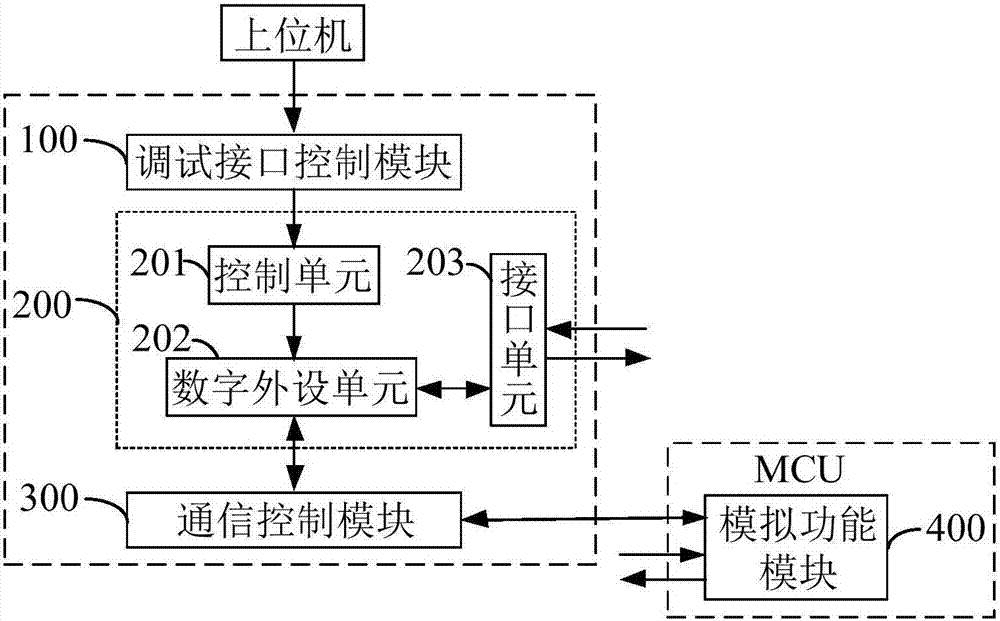

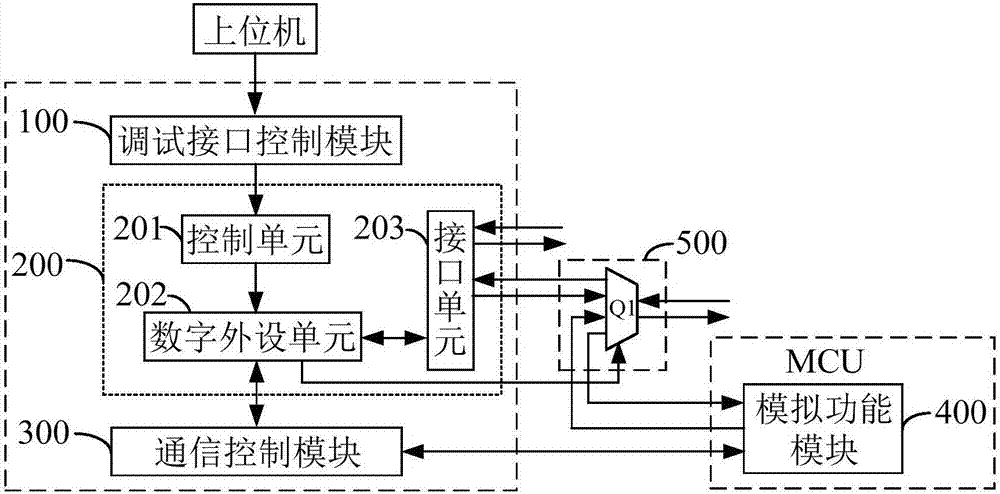

Debugger applied to microcontroller

ActiveCN107305526AImplement debuggingDoes not increase the areaSoftware testing/debuggingTotal factory controlMicrocontrollerComputer architecture

The invention belongs to the field of circuit technology and provides a debugger applied to a microcontroller. The debugger comprises a debugging interface control module, a digital debugging module and a communication control module, wherein the digital debugging module and a digital function module of the microcontroller have the same structure, a debugging result obtained after debugging is performed on the digital debugging module and a debugging result obtained after debugging is performed on the digital function module of the microcontroller are the same, the communication control module performs communication with an analog function module in the microcontroller, and debugging on the analog function module in the microcontroller can be realized. In this way, by use of the debugger, debugging on the digital function module and the analog function module in the microcontroller can be realized, and the area of a microcontroller chip cannot be enlarged due to the fact that the debugger is located outside the microcontroller. As a result, by the adoption of the debugger, debugging on the analog function module and the digital function module of the microcontroller on the premise of not enlarging the area of the microcontroller chip is realized.

Owner:SHENZHEN BOJUXING IND DEV

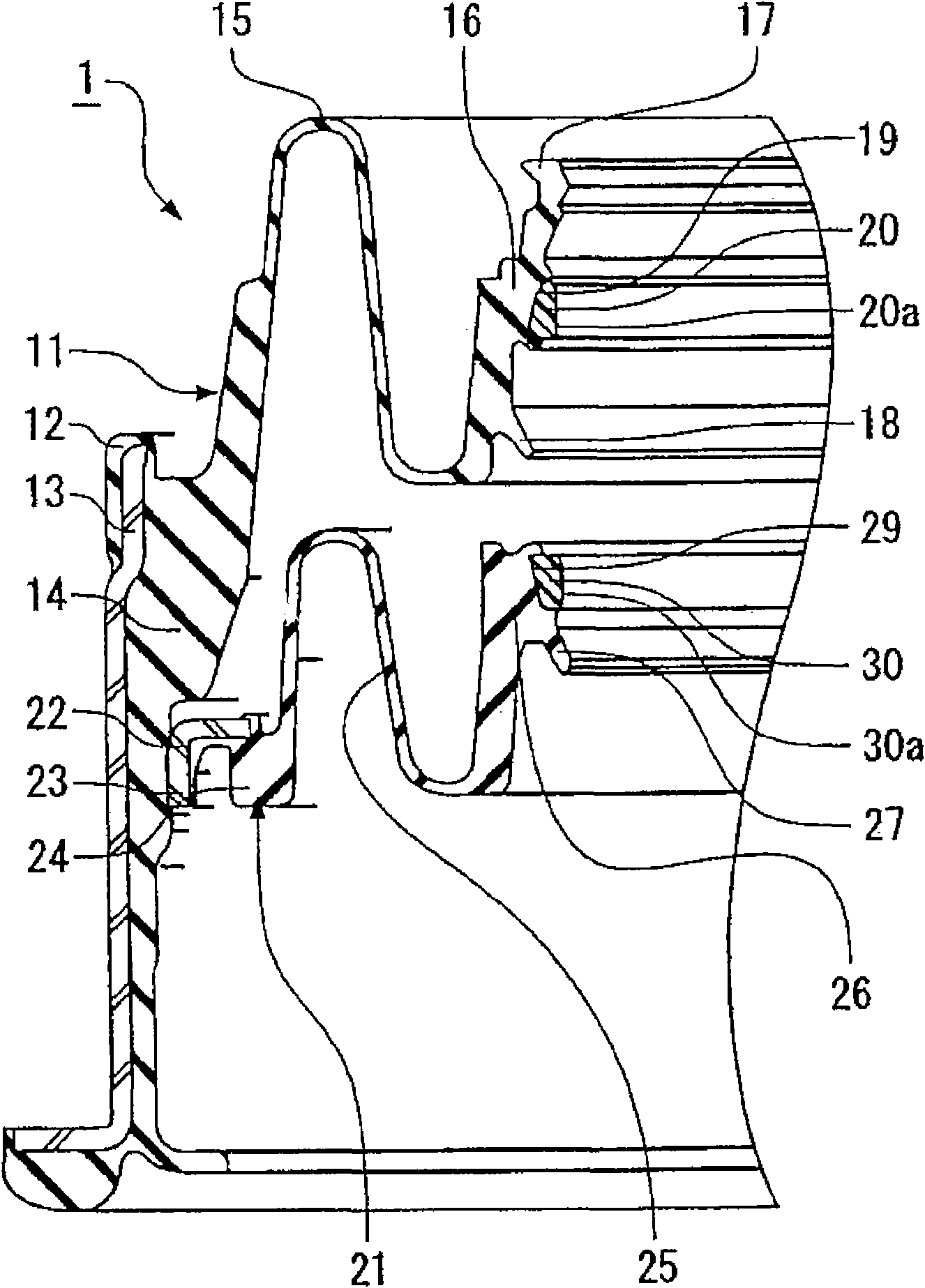

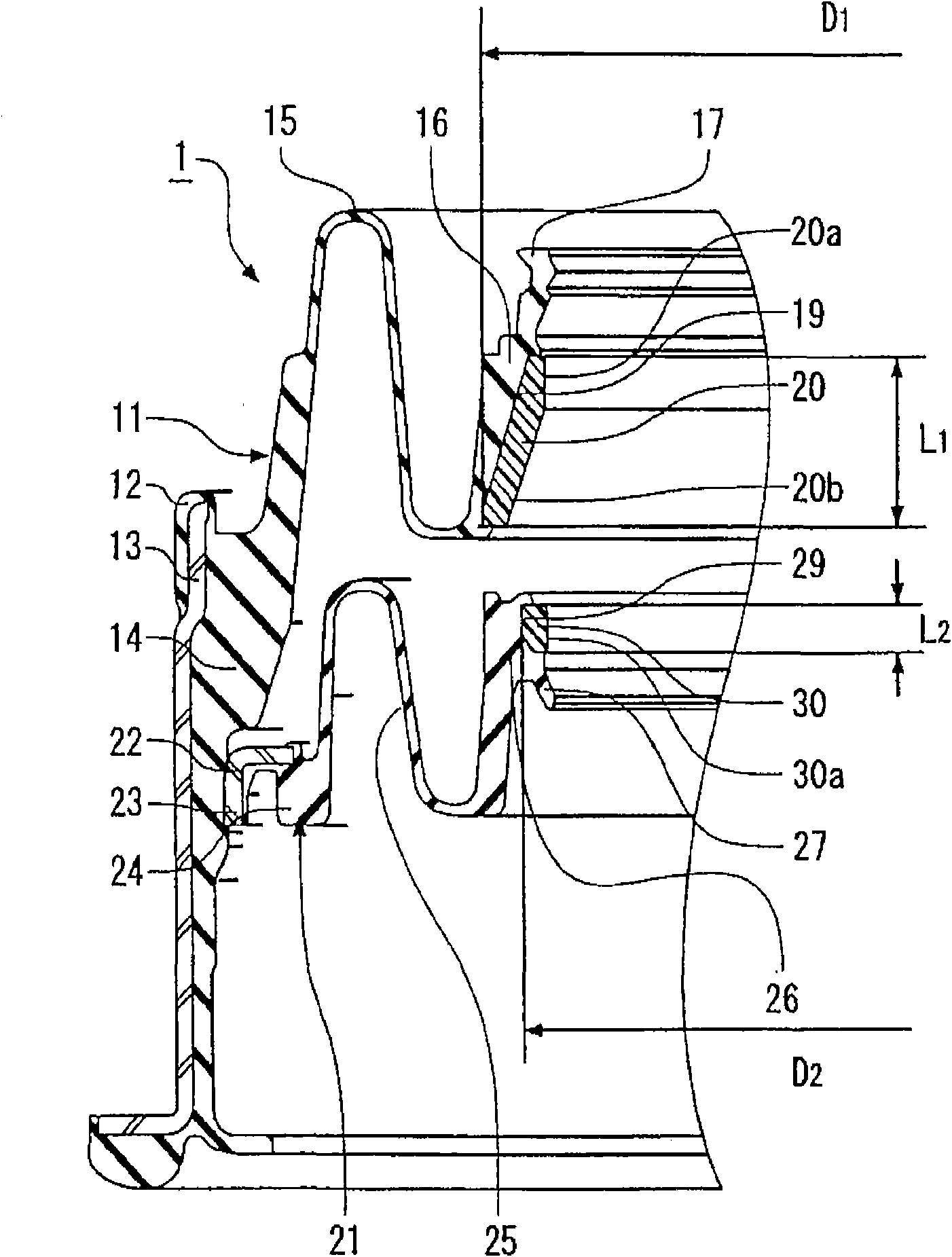

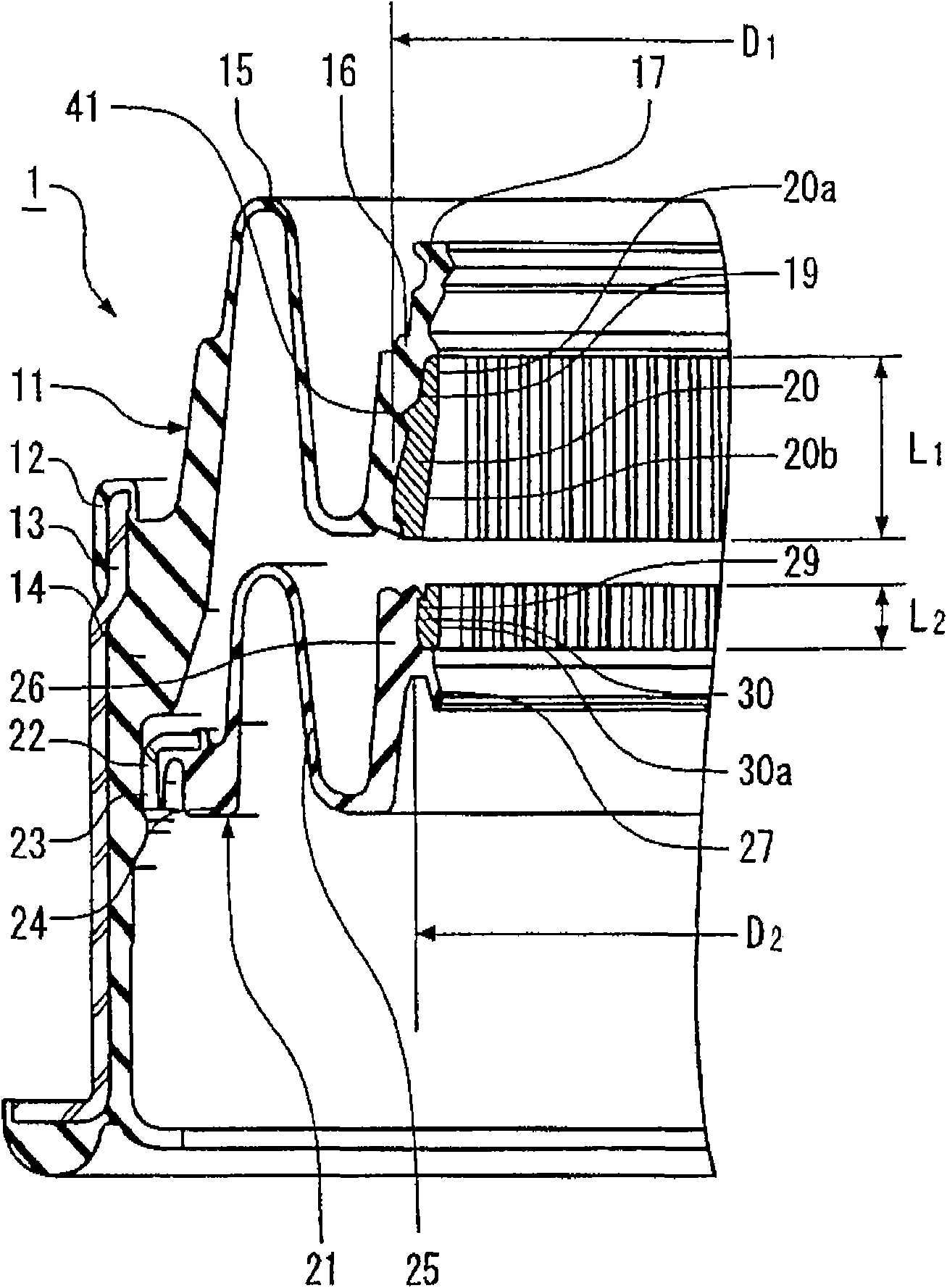

Sealing device

ActiveCN101583814AIncrease the cross-sectional shapeImprove sound insulationEngine sealsSteering columnsEngineeringBellows

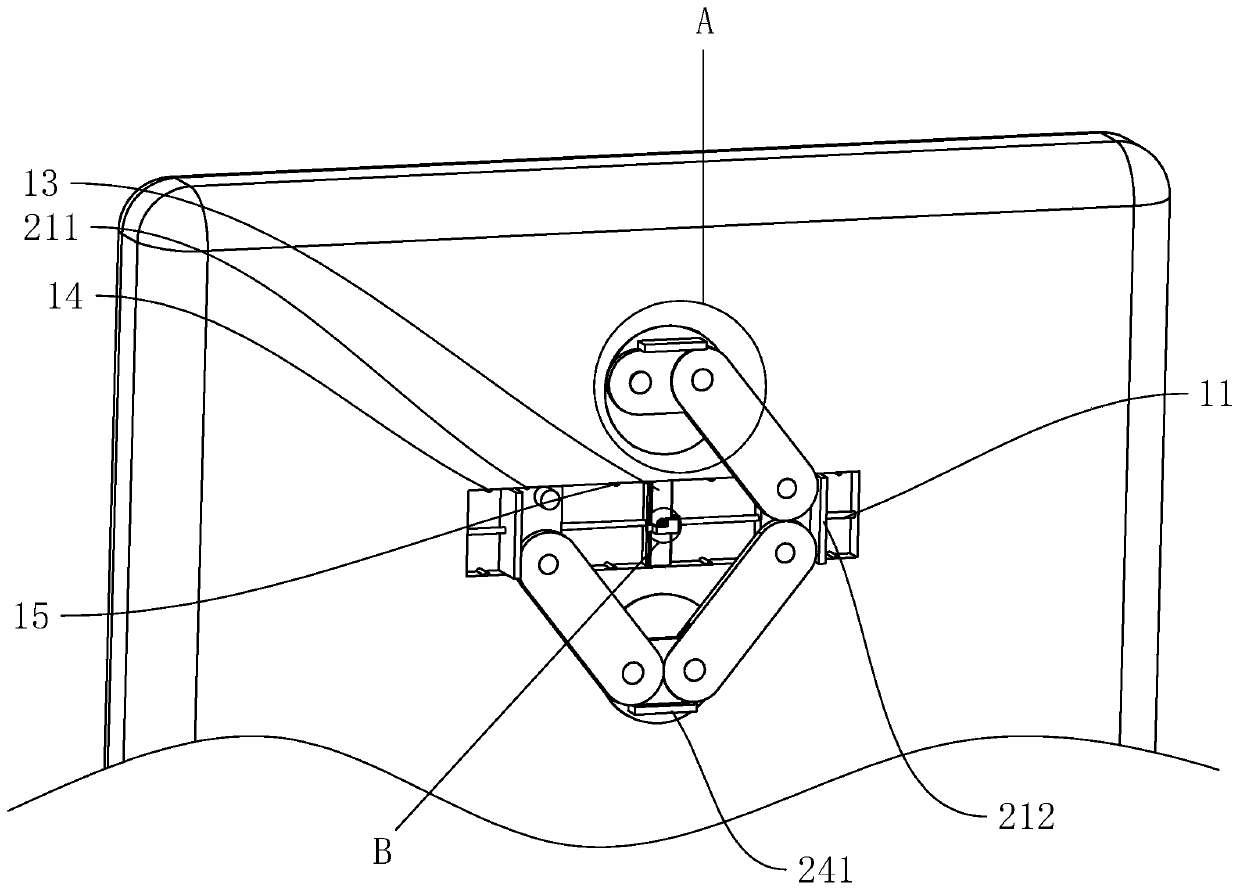

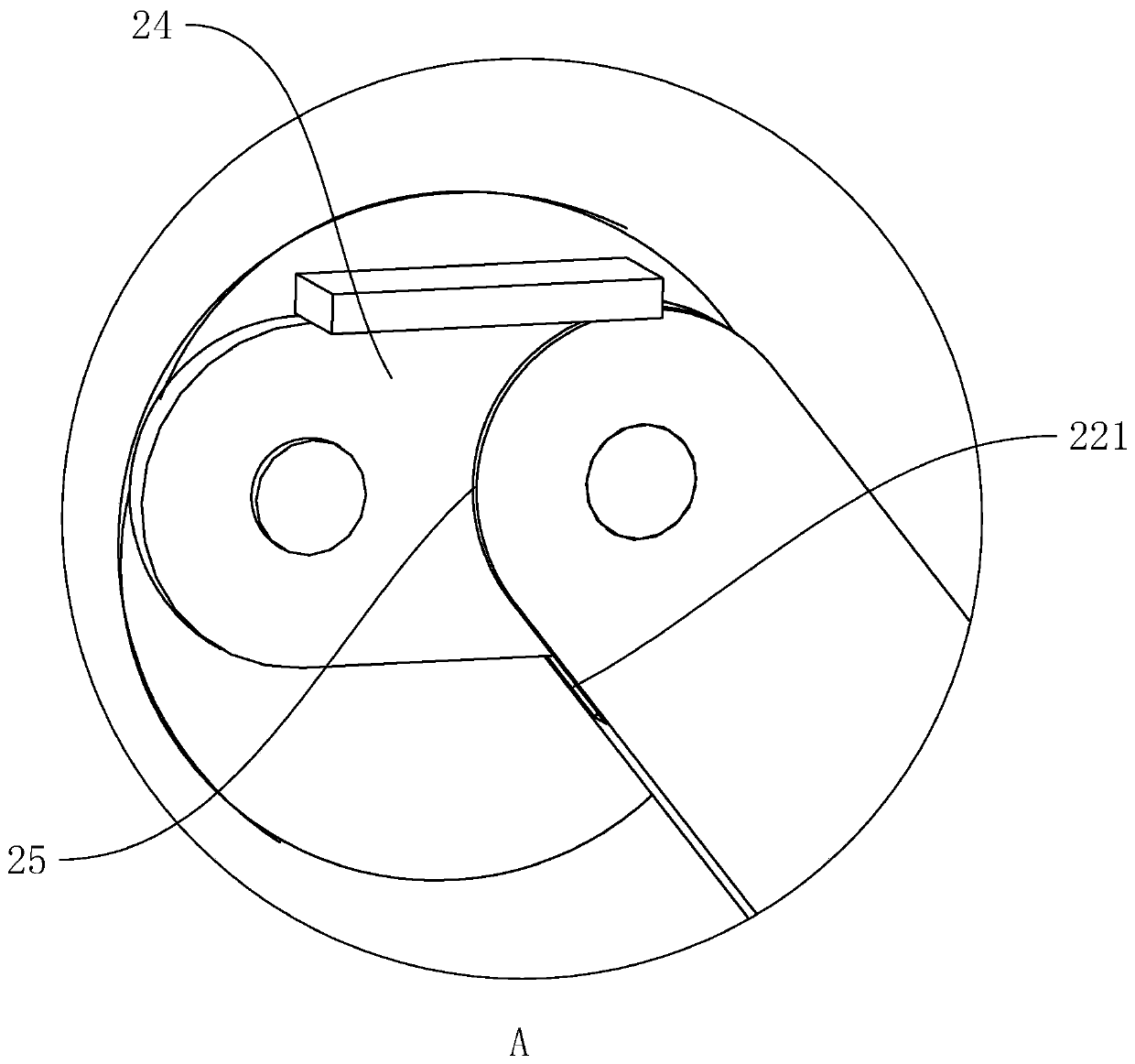

A sealing device in which squealing noise occurring when a steering shaft is in strong intimate contact with a bumper portion is effectively suppressed and in which a slide member for preventing squealing noise can be easily fixed to the bumper portion. The sealing device (1) for sealing between a housing and a shaft inserted into the housing has a first molding (11) in which the bumper portion (16) and a seal lip portion (17) are integrally molded, with a bellows-like flexible portion (15) in between, on the inner peripheral side of an outer peripheral fixing portion (12) secured to the housing. The sealing device (1) also has a second molding (21) in which a second bumper portion (26) is integrally molded, with a second flexible portion (25) in between, on the inner peripheral side of asecond fixing portion (22) secured to the outer peripheral fixing portion (12). Fall out prevention portions (19, 29) are respectively provided on the inner peripheral surfaces of the bumper portion (16) and second bumper portion (26), and resin slide members (20, 30) are fitted without bonding to the fall out prevention portions (19, 29), respectively.

Owner:NOK CORP

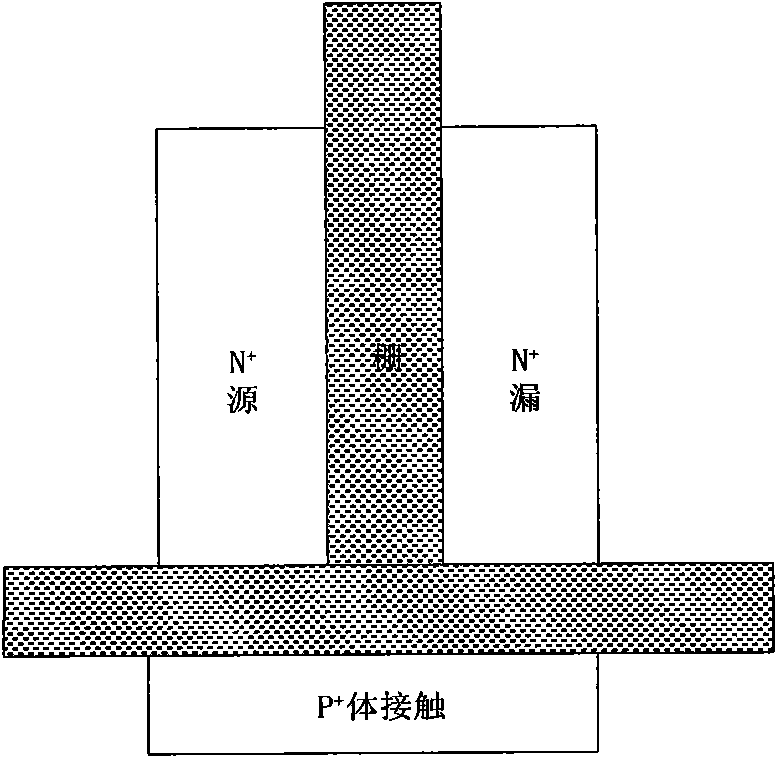

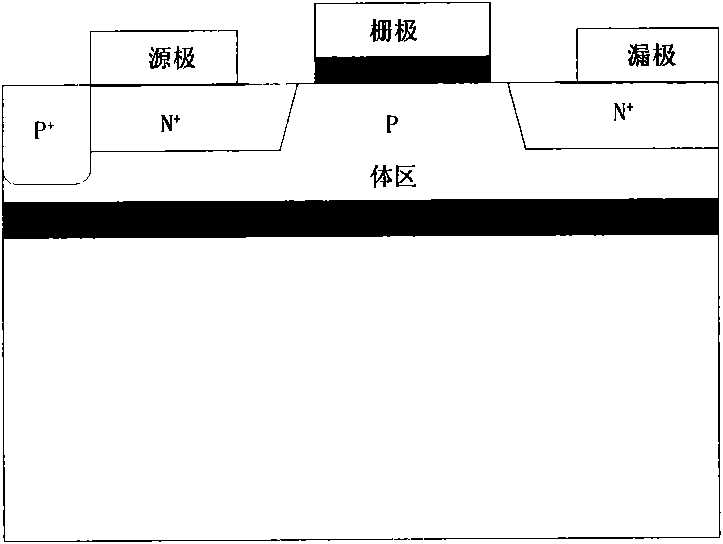

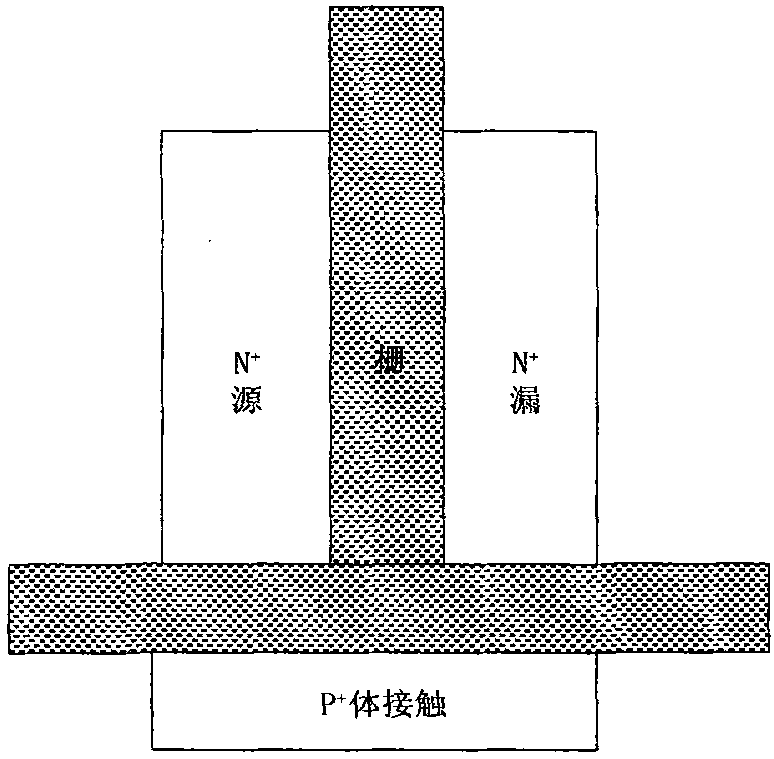

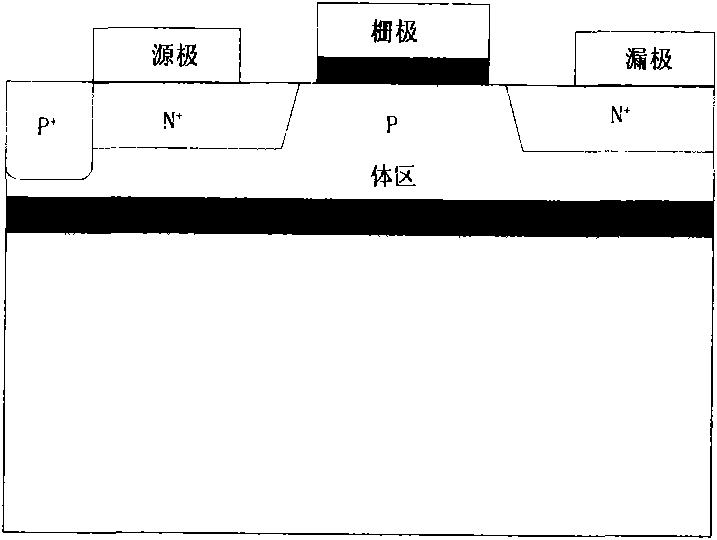

Method for manufacturing SOI MOS device capable of realizing ohmic contact with source body

InactiveCN101950723ASuppression of floating body effectSimple manufacturing processSemiconductor/solid-state device manufacturingSemiconductor devicesFloating body effectBody region

The invention discloses a method for manufacturing an SOI MOS device capable of realizing ohmic contact with a source body, comprising the following steps: firstly manufacturing a grid region; carrying out light dope on a high-dose source region and a high-dose drain region to form a high-concentration light-doped N-shaped source region and a light-doped N-doped drain region; manufacturing a side wall isolation structure around the grid region; carrying out the ion implantation on the source region and the drain region, carrying out heavy-doped P ion implantation obliquely through arranging a mask with an opening in the source region, so as to form a heave-doped P-shaped region between the source region and a body region, and finally forming a layer of metal on of the partial surfaces on the source region; and heating to lead the metal to react with the Si material below the metal to generate silicide. In the method of the invention, the silicide forms ohmic contact with the heavy-doped P-shaped region near the silicide, and releases the holes accumulated by the SOI MOS device in the body region, so as to inhibit the floating body effect of the SOIMOS device, and have the advantages of not increasing the chip area, possessing simple manufacturing process and being compatible with the conventional CMOS process and the like.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

A resistance random access memory and a preparation method thereof

InactiveCN102694118AWith low resistance state rectification functionRealize low-impedance state rectification functionSolid-state devicesSemiconductor devicesStatic random-access memoryRandom access memory

The embodiment of the invention discloses a resistance random access memory and a preparation method thereof. The access memory comprises a bottom electrode, a first resistance random function layer above the bottom electrode, a second resistance random function layer above the first resistance random function layer, and a top electrode above the second resistance random function layer, wherein the first resistance random function layer has an majority carrier type opposite to that of the second resistance random function layer. Through the first resistance random function layer and the second resistance random function layer with opposite majority carrier types, pn junction is formed in the resistance random function layers of the access memory. Without an external rectified diode or triode, resistance random is realized, crosstalk is curbed and a memory cell is not expanded. Therefore memory density is effectively improved and integrated level of the memory is enhanced.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Solar cell

InactiveCN102664207AImprove photoelectric conversion efficiencyDoes not increase movement distancePhotovoltaic energy generationSemiconductor devicesCharge carrierEngineering

The invention relates to a solar cell which comprises a main body, a plurality of first finger electrodes, a first solder strip and a second solder strip, wherein the main body is provided with a first surface and a second surface which are positioned on two opposite sides; the first finger electrodes are positioned on the first surface, and each first finger electrode is provided with an end which is bent and extends onto the second surface; the first solder strip is positioned on the first surface, and electrically connected with the first finger electrodes; and the second solder strip is positioned on the second surface, and electrically connected with the first finger electrodes. The solar cell provided by the invention can not increase the migration distance of the current carrier on the first finger electrodes, and can increase the area of the first surface of the solar cell irradiated by light rays, thereby enhancing the photoelectric conversion efficiency of the solar cell.

Owner:AU OPTRONICS CORP

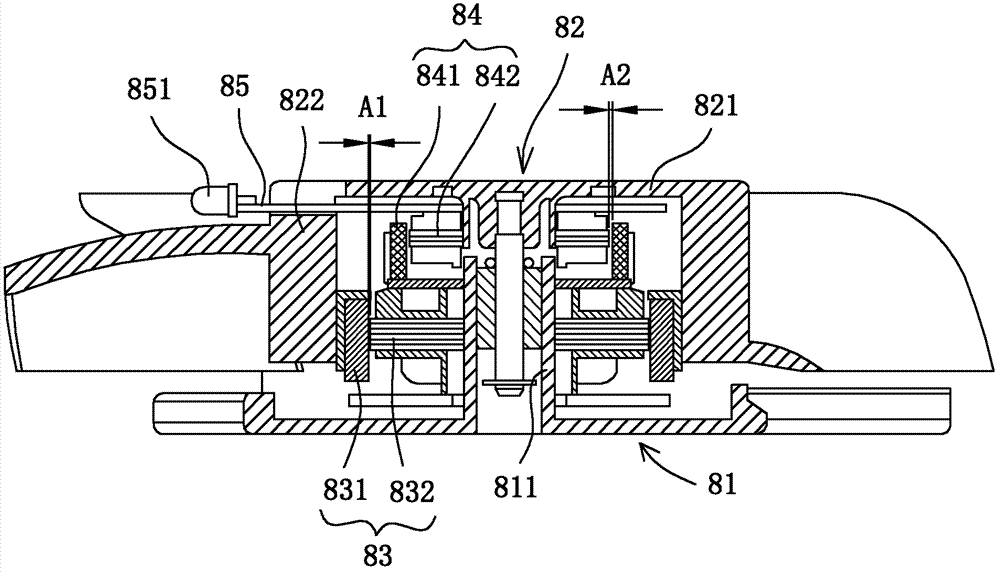

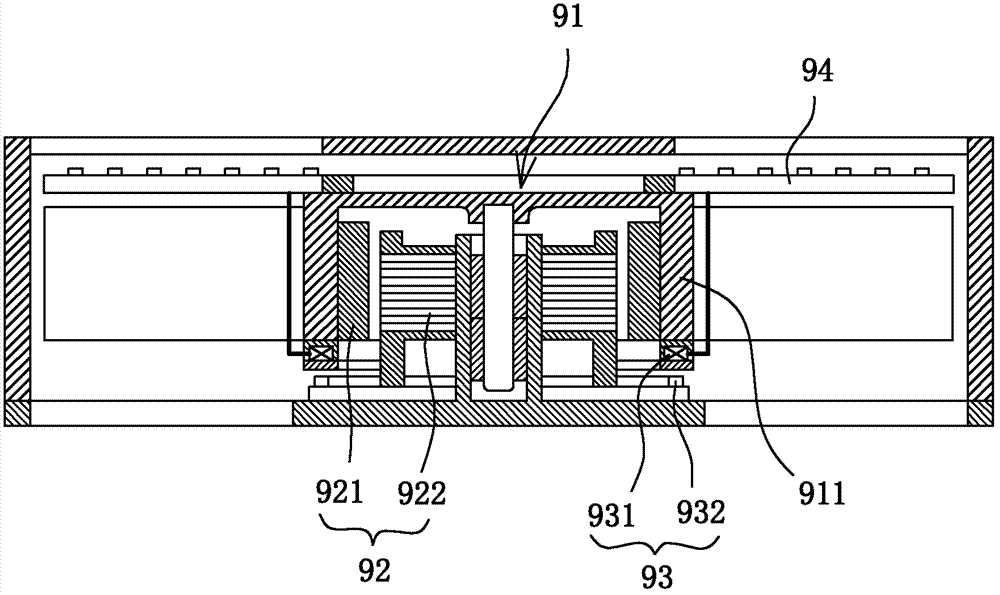

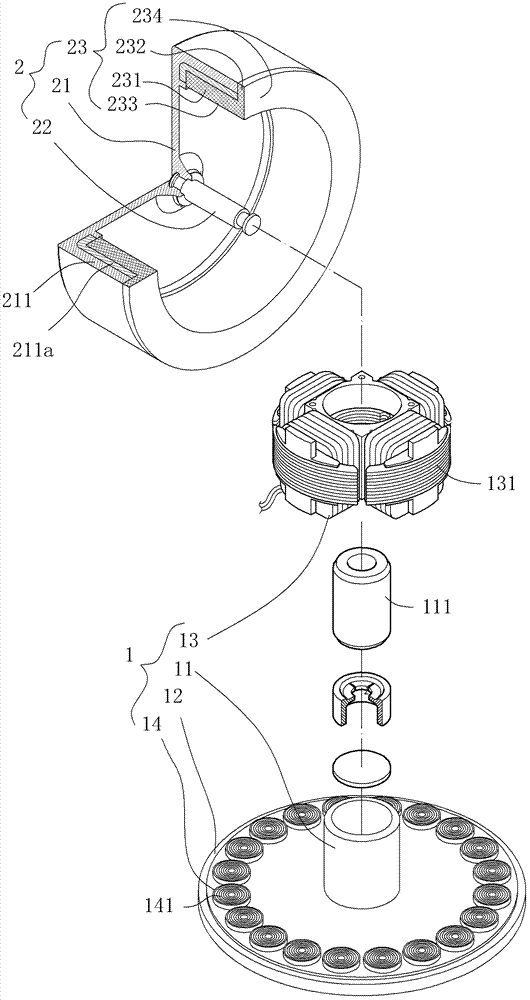

Motor capable of generating electricity

ActiveCN103248186AReduce manufacturing costNo increase in axial heightMagnetic circuit rotating partsStructural associationElectricityDriving circuit

A motor with power-generating coil module includes: a base that has a shaft tube, a supporting surface surrounding the shaft tube, a first coil module mounted on an outer circumferential surface of the shaft tube, and a second coil module disposed above the supporting surface; a rotor that has a carrier extending a lateral wall toward the base, a shaft rotatably coupling with the shaft tube, and a magnetic member mounted on the lateral wall and having an axial extension and a radial extension, with a first magnetic face on the axial extension and facing the first coil module and a second magnetic face on the radial extension and facing the second coil module; a driving circuit electrically connecting with one of the first and second coil modules; and a power-storing unit electrically connecting with the other one of the first and second coil modules.

Owner:SUNONWEALTH ELECTRIC MACHINE IND

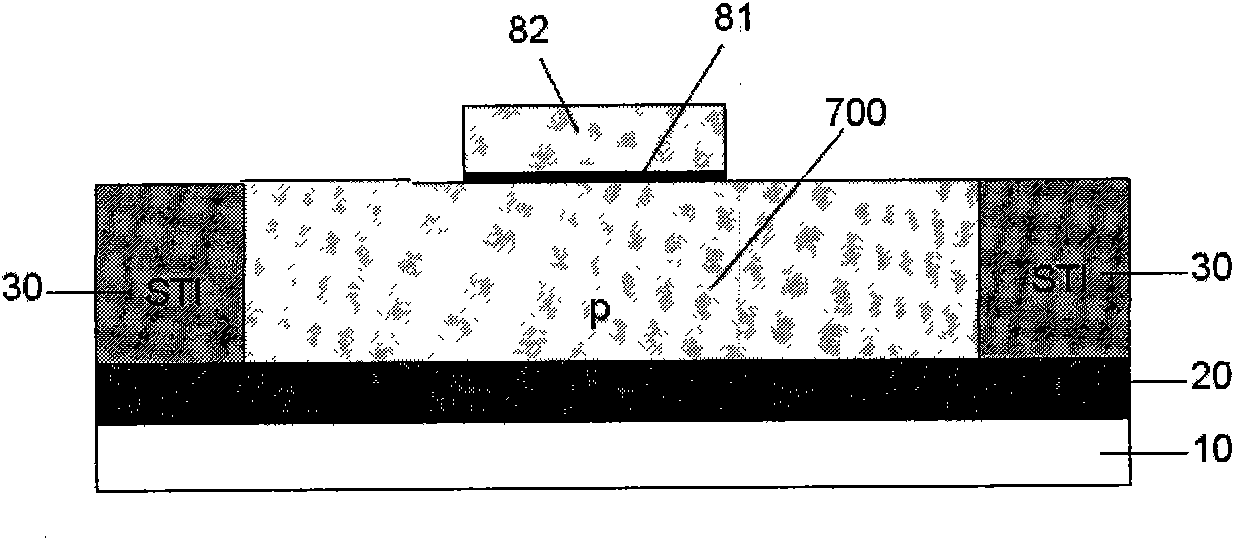

MOS structure for inhibiting SOI floating-body effect and manufacturing method thereof

InactiveCN101872737AWork will not affectDoes not increase the areaSemiconductor/solid-state device manufacturingSemiconductor devicesFloating body effectEngineering

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

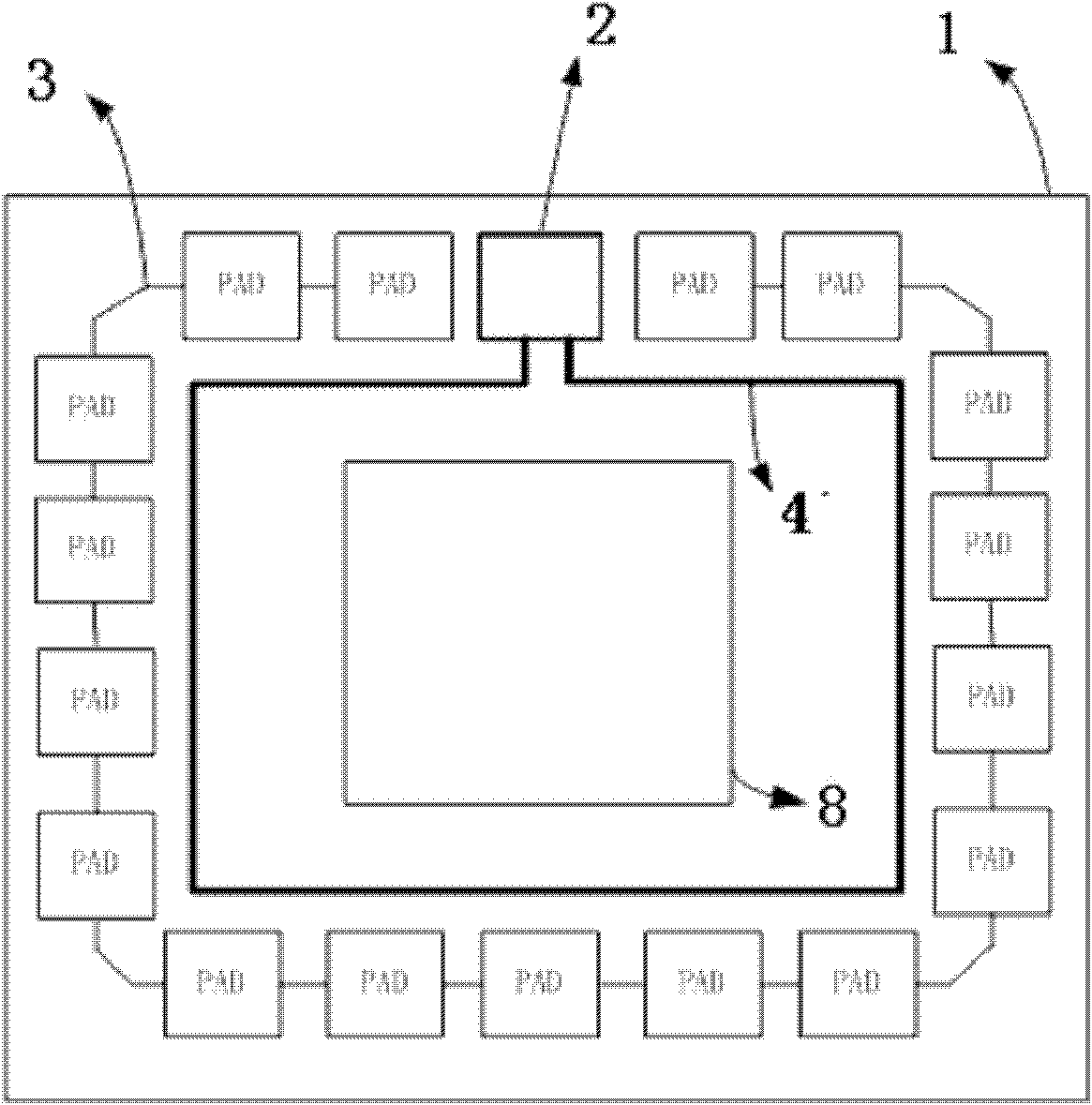

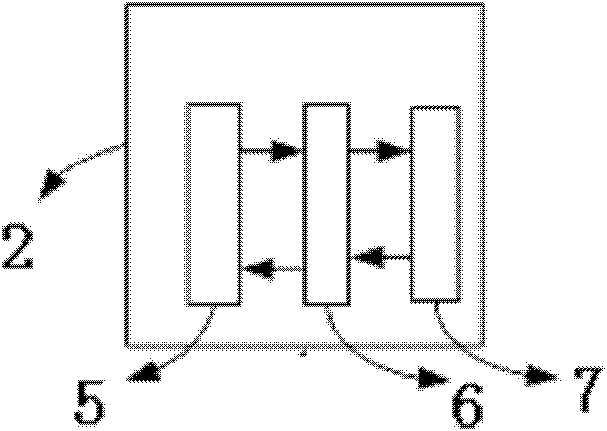

Chip with information identification and preparation method of chip

ActiveCN102156898ADoes not increase the areaLow costRecord carriers used with machinesRadio frequencyAnalogue circuits

The invention provides a chip with information identification, wherein the chip comprises a label circuit, a chip antenna, a chip core and a pad ring; the label circuit comprises a radio frequency analogue circuit, a digital circuit module and a memory; the chip antenna is connected to the radio frequency analogue circuit, the radio frequency analogue circuit is connected to the digital circuit module, the digital circuit module is connected to the memory, the chip core is arranged on the centre of the pad ring and is connected to the pad of the pad ring; the preparation method comprises the following steps of: forming a FRID (Radio Frequency Identification) label circuit into a module which is the same with the width of the chip pad, then directly placing the layout of a FRID module in the position of the chip pad, placing a FRID chip antenna inside or outside the pad ring in the chip layout, and then making plate and processing to produce a chip with embedded electric identificationinformation, wherein the identification information in the chip is written into or read from the chip through a card reader. The chip with information identification and the preparation method of thechip have the advantages that the reliability for the method of embedding the identification information of the chip is high, the cost is prevented from increasing, and the chip has great applicationvalues in anti-fake, management and identification field of the chip.

Owner:TSINGHUA UNIV

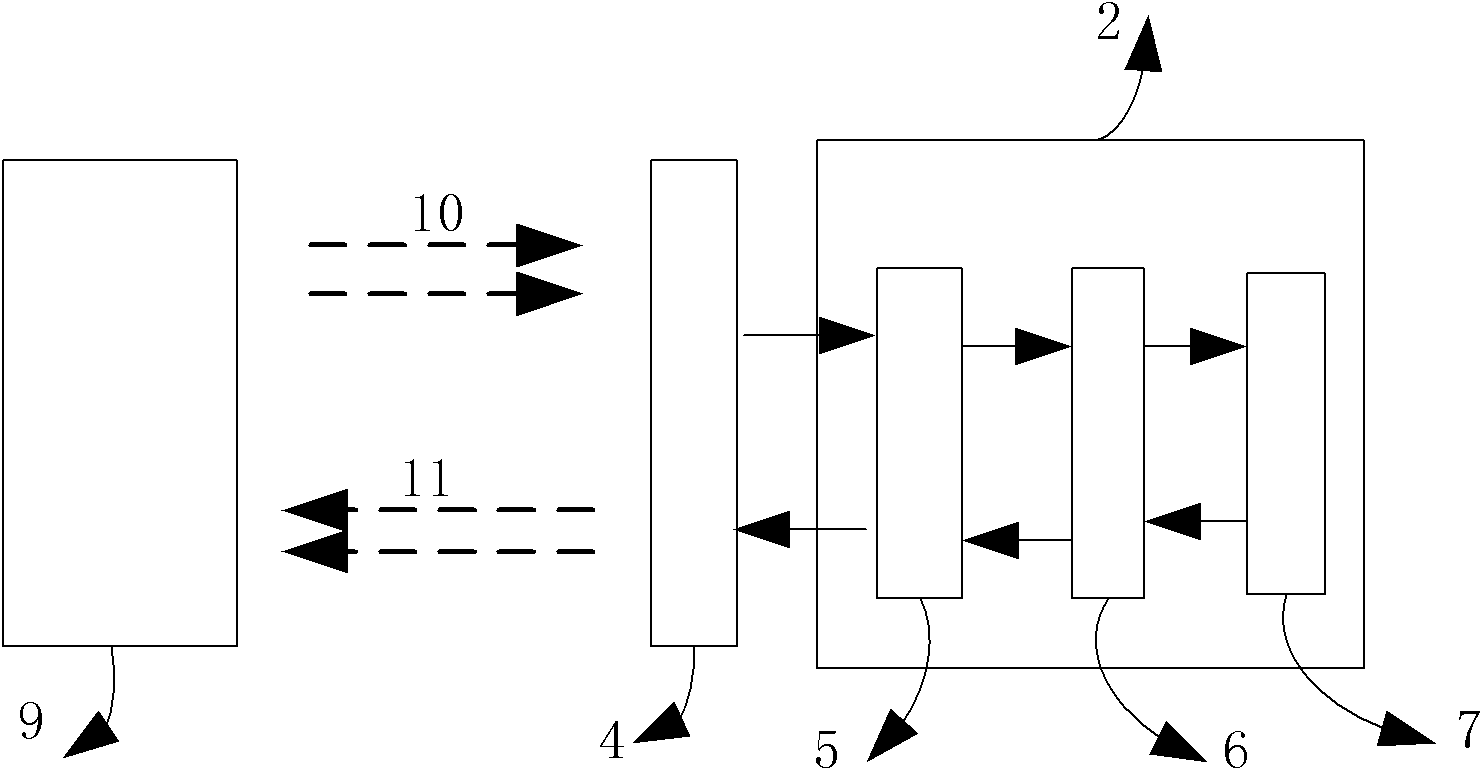

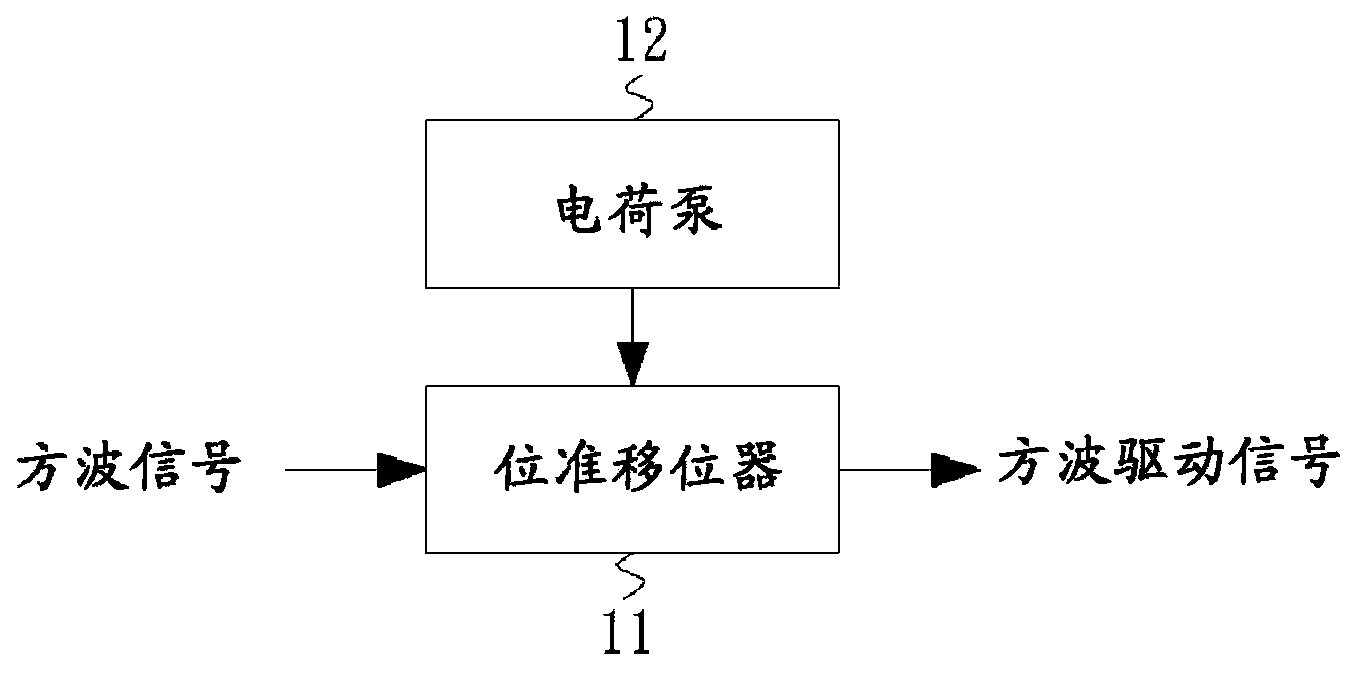

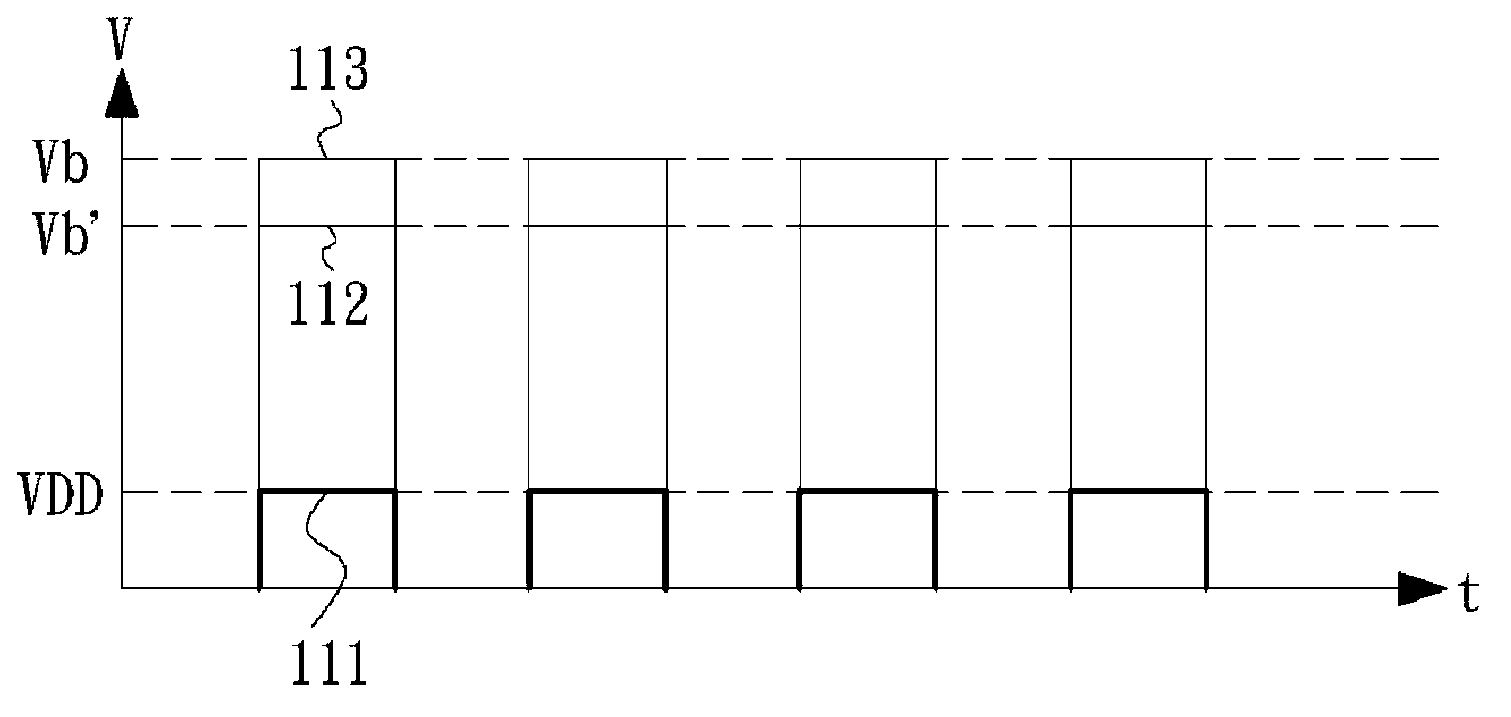

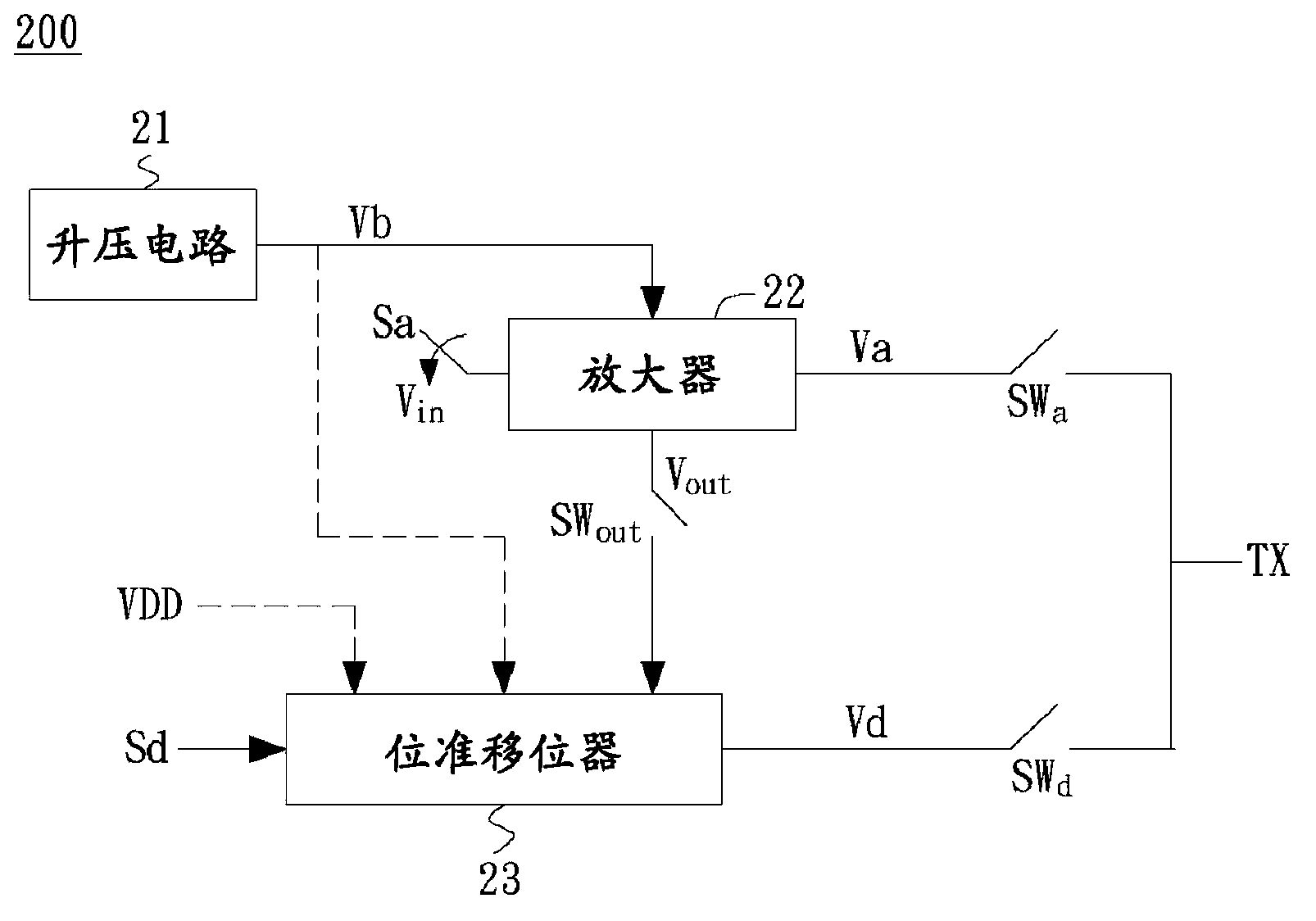

Drive signal generation system

ActiveCN103576953ADoes not increase the areaWidely used valueInput/output processes for data processingAudio power amplifierEngineering

The invention relates to a drive signal generation system. According to the drive signal generation system, a booster circuit provides a supply voltage, an amplifier provides analog waveform driving signals, a level shifter provides digital waveform drive signals, and a selecting unit selects the analog waveform drive signals as the drive signals in an analog waveform mode to a touch panel and selects the digital waveform drive signals as the drive signals in a digital waveform mode to the touch panel, wherein the booster circuit provides the supply voltage to the amplifier, and in the digital waveform mode, the amplifier generates and provides an output voltage for at least the last circuit of the level shifter as the power source.

Owner:EGALAX EMPIA TECH INC

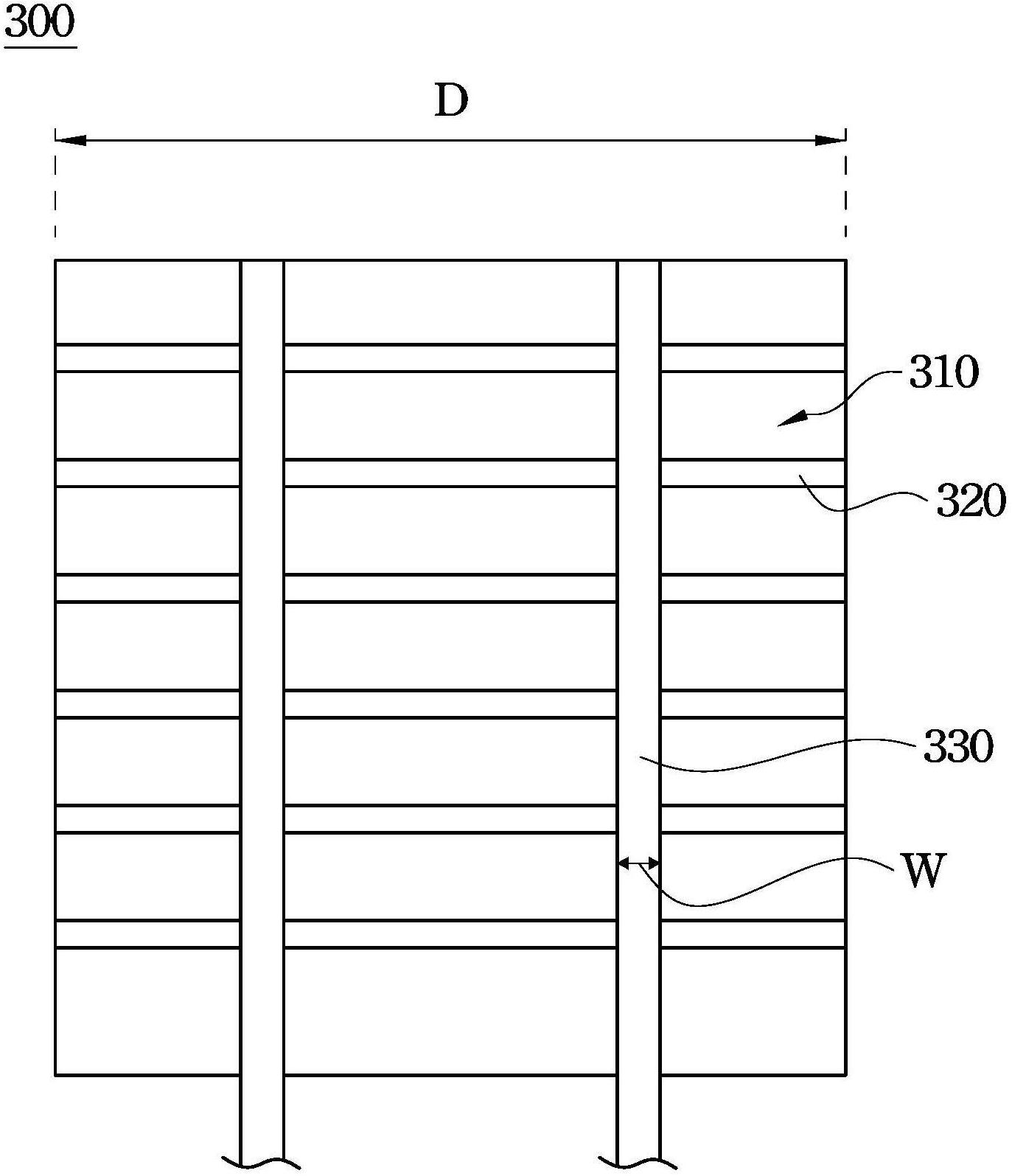

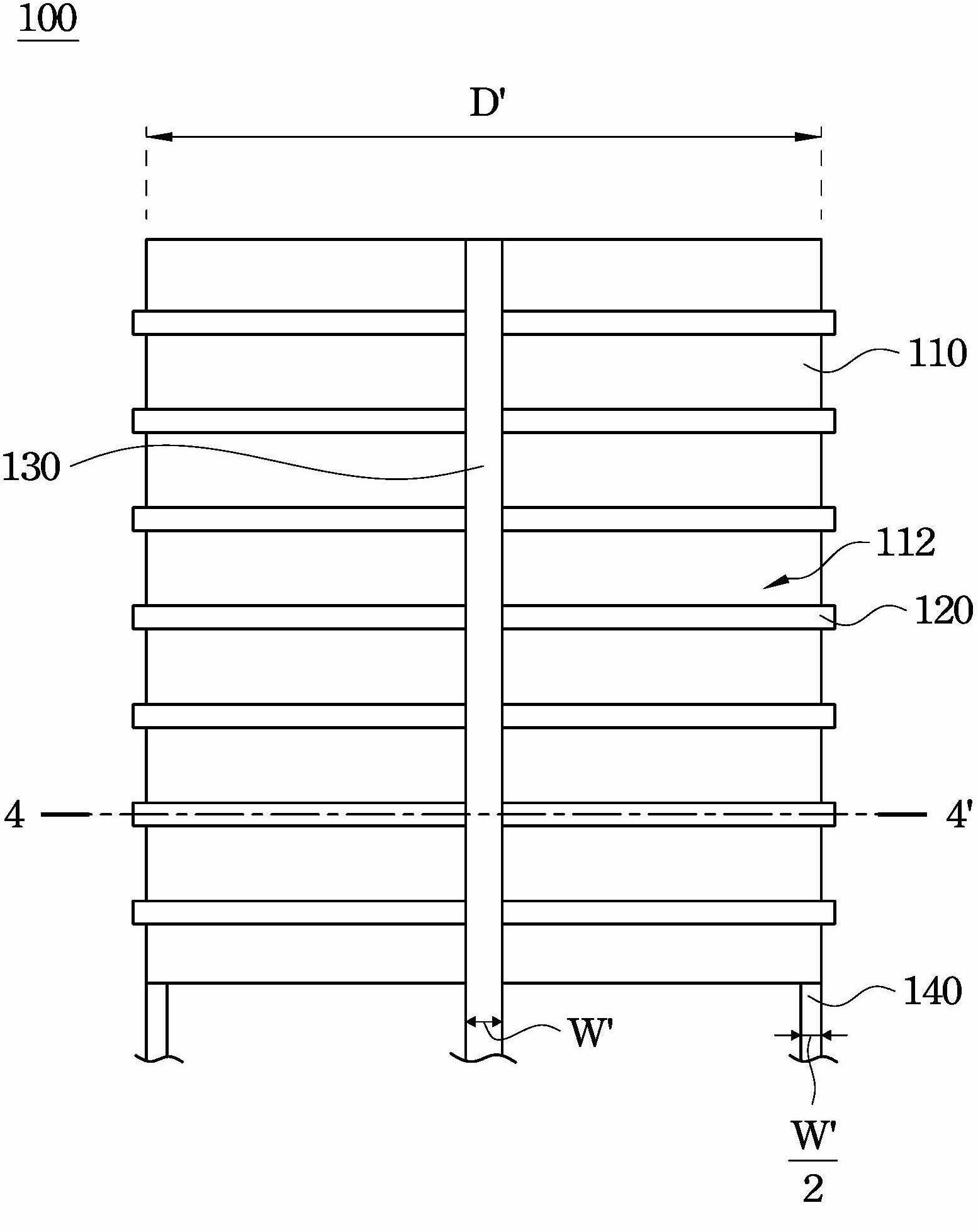

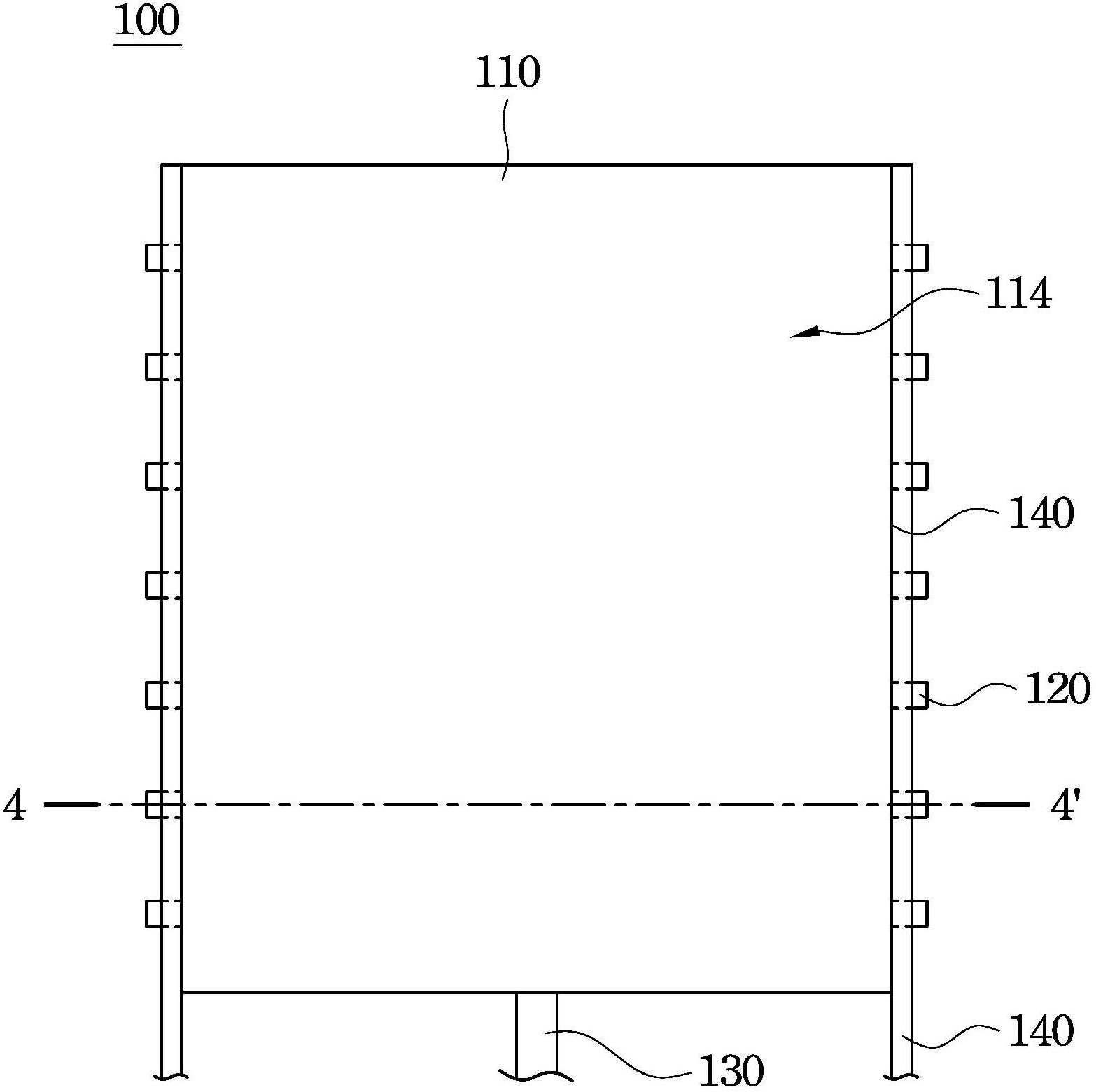

Broadband Panel Array Antenna

ActiveCN103825101BMiniaturizationHigh impedanceAntenna arraysResonant antennasAntenna gainImpedance matching

The invention discloses a broadband flat plate array antenna, broadband can be achieved, and array antenna gain can be improved. According to the broadband flat plate array antenna, a coupling groove is used for stimulating two micro-strip subarrays, at the time, the impedance of a single micro-strip wire is high, a radiation paster can easily carry out high-impedance matching, accordingly the bandwidth of the micro-strip subarrays is widened, broadband is achieved, the relative bandwidth (Sll < -10 dB) of the feeding mode can reach 16%, 1 dB gain bandwidth can reach 14.6%, and common structure bandwidth is only about 6%. In addition, an H-shaped base chip is used for integrating a waveguide feeding network, the micro-strip subarrays are connected in parallel for feeding, along with increasing of array units, the bandwidth is hardly changed, broadband features can be kept in a large array, and array antenna gain can be improved gradually. In addition, the feeding network is placed below the micro-strip subarrays, extra circuit area cannot be increased, and array antenna miniaturization is promoted. The broadband flat plate array antenna is suitable for promotion and application in the technical field of microwave and millimeter wave antennas.

Owner:成都宁锦威通信技术有限公司

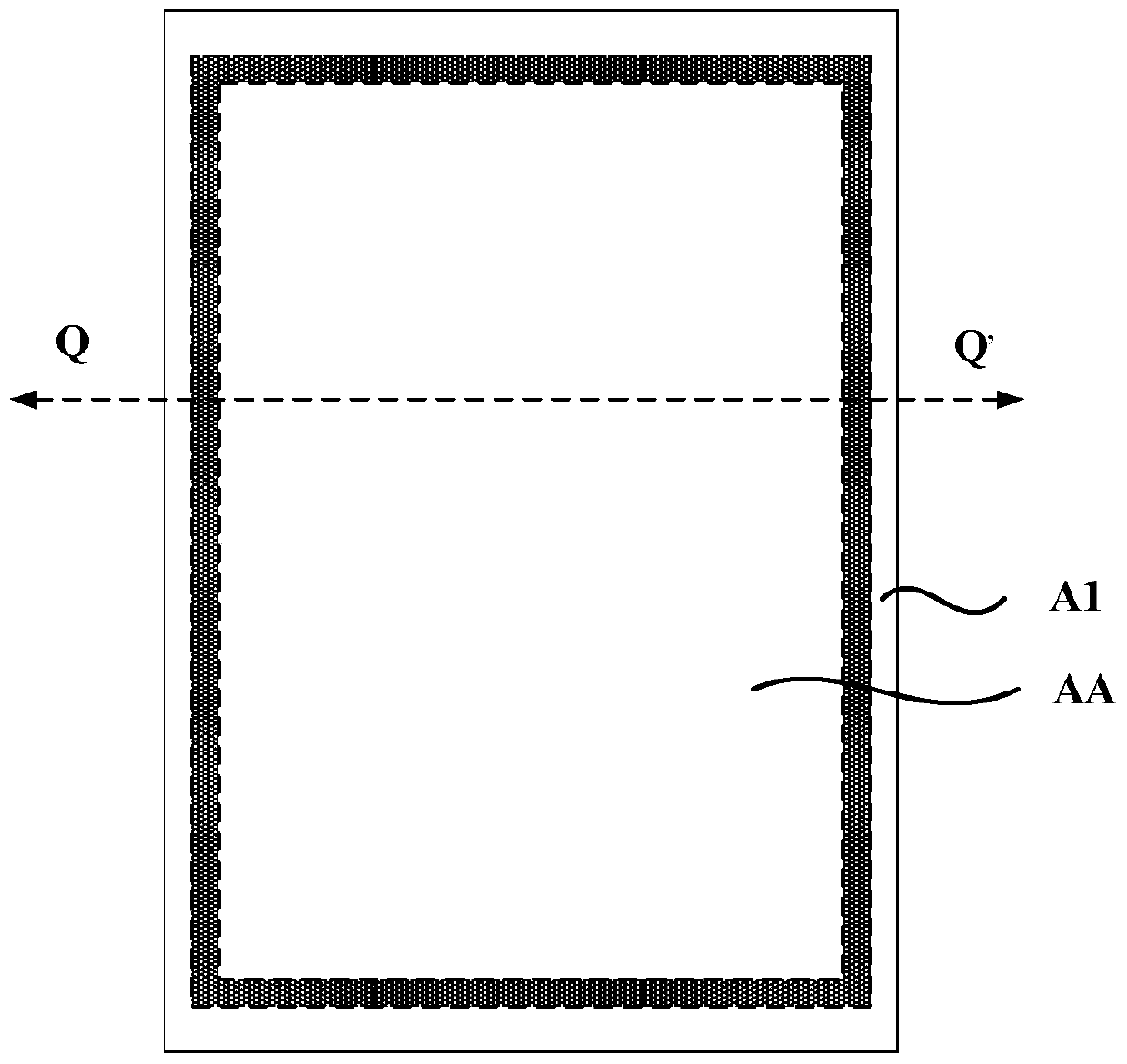

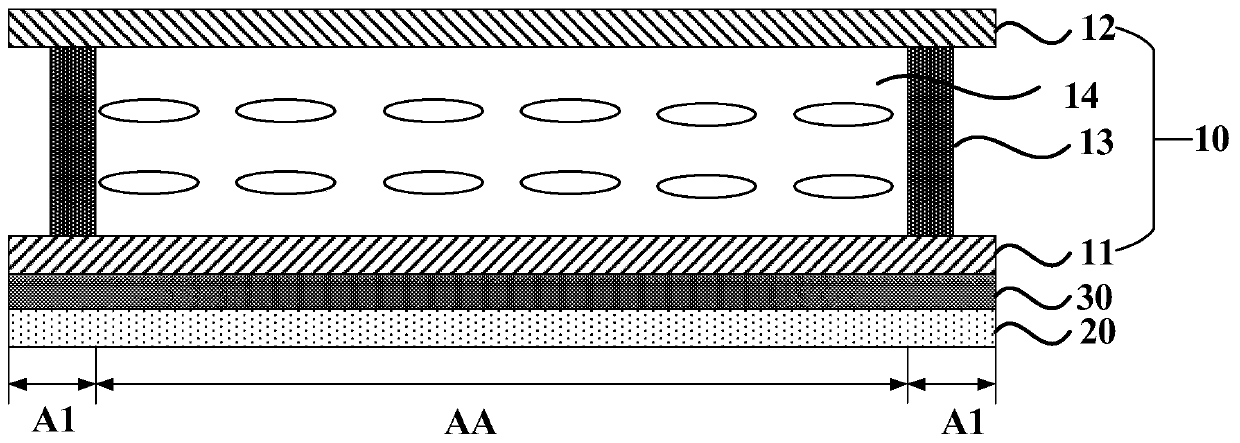

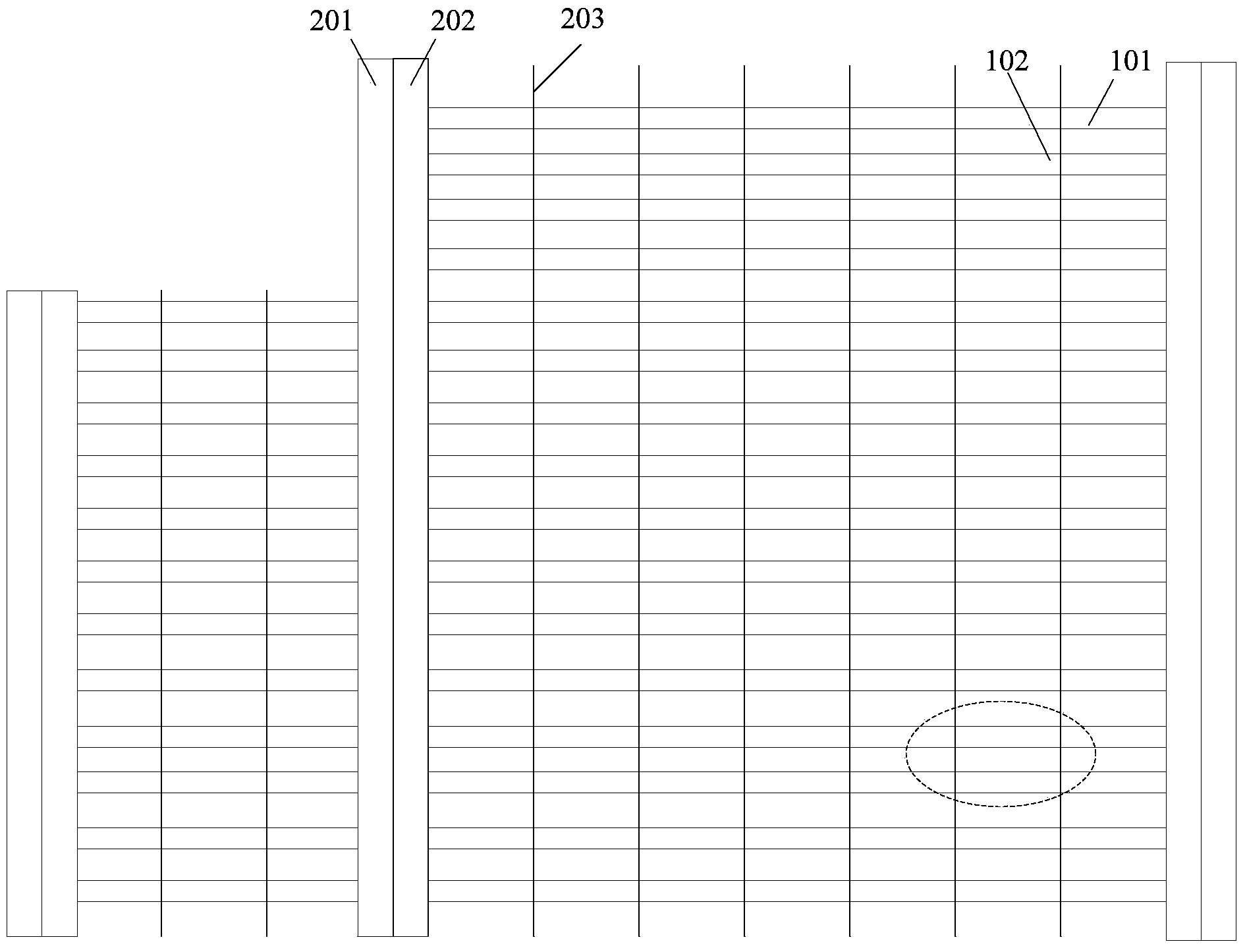

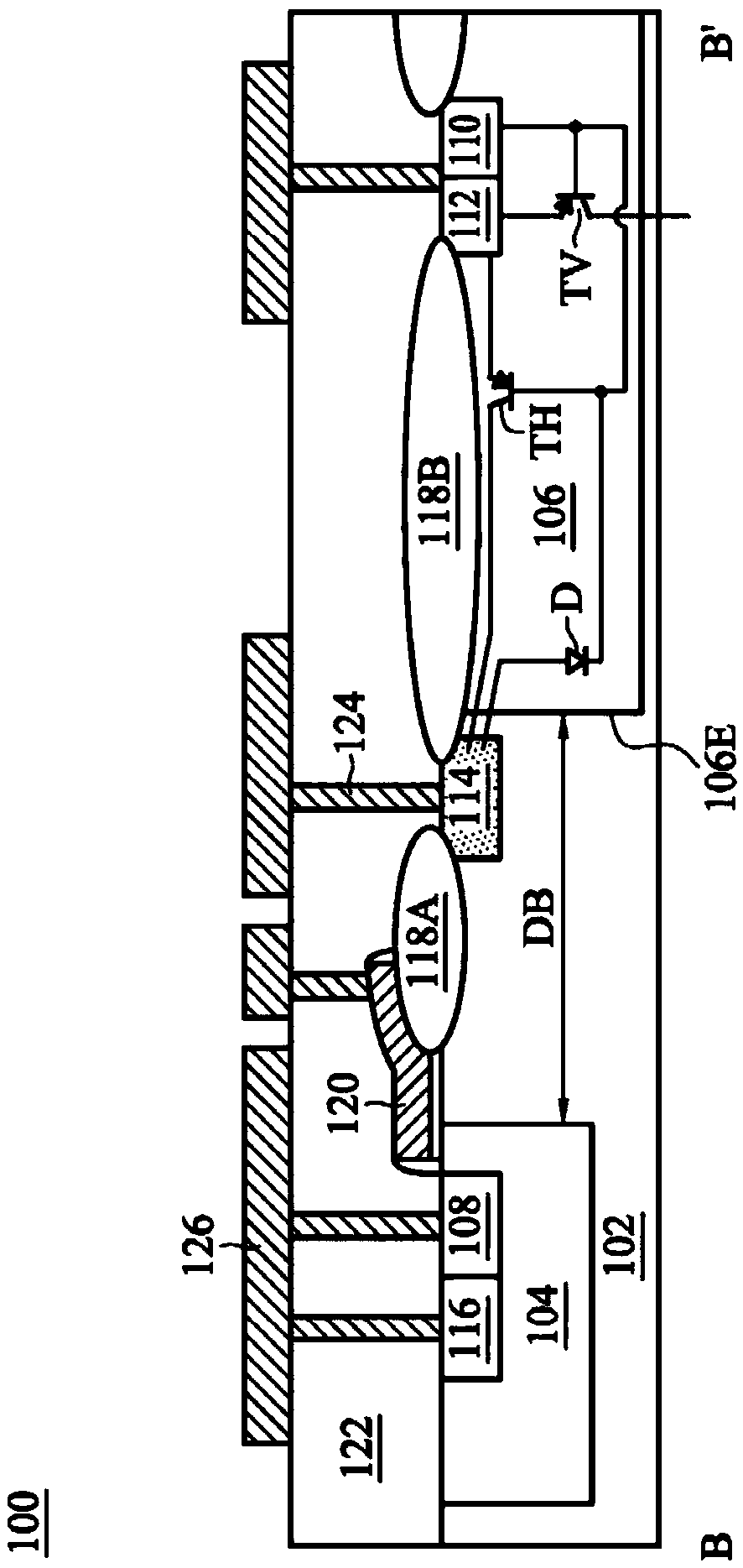

Display device

ActiveCN110007537AImprove electrostatic protection abilityReduce screen ratioNon-linear opticsDisplay deviceComputer science

The invention discloses a display device which comprises a display area and a first non-display area surrounding the display area. The display device further comprises a display panel comprising an array substrate and an opposite substrate; a backlight module arranged on one side, deviating from the opposite substrate, of the array substrate; and a first conductive structure arranged on one side,close to the backlight module, of the array substrate, and the first conductive structure is electrically connected with the backlight module. A first conductive structure is arranged on one side, close to the backlight module, of the array substrate; due to the fact that the first conductive structure can guide electrostatic charges on the periphery of the display device into the backlight module, static electricity is dissipated through the backlight module, the problem that static electricity is left in the liquid crystal layer due to the fact that the electrostatic charges on the peripheryof the display device enter the display panel is effectively avoided, and normal display of the display device is guaranteed.

Owner:XIAMEN TIANMA MICRO ELECTRONICS

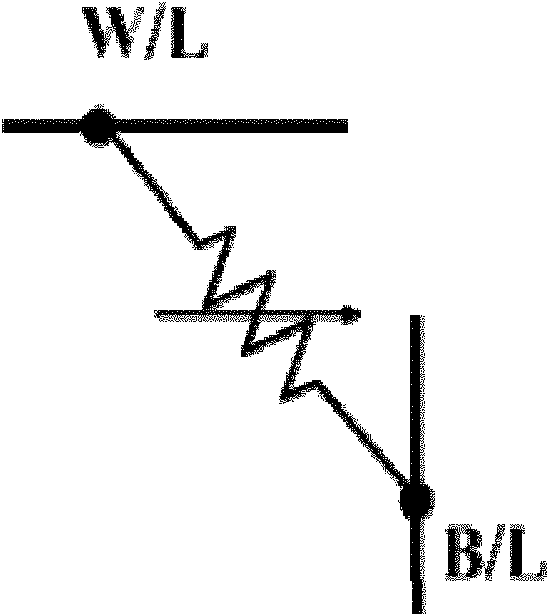

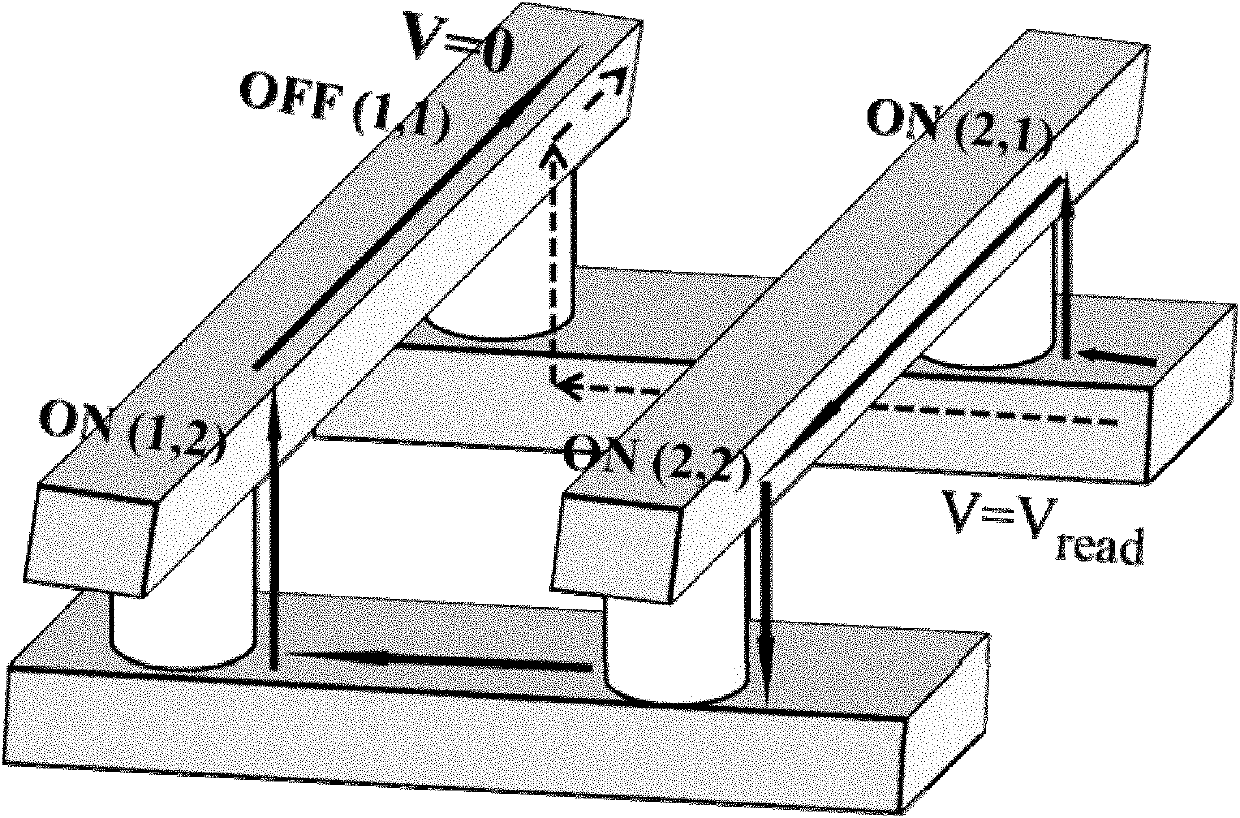

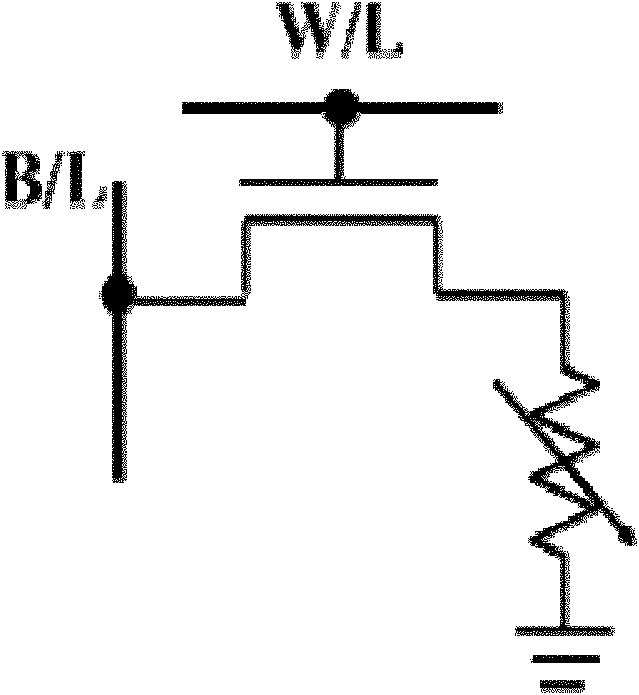

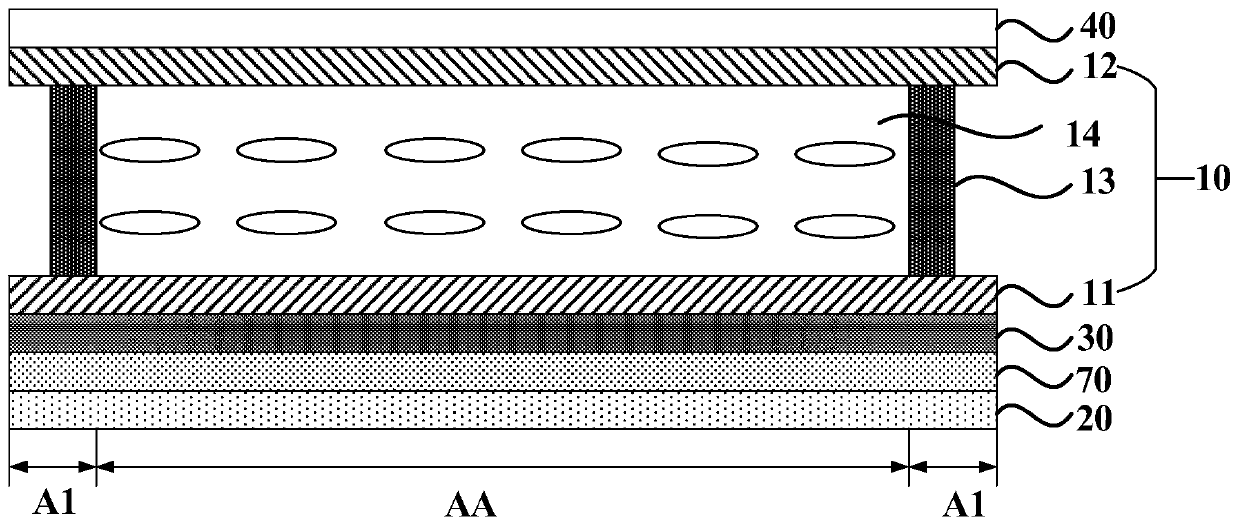

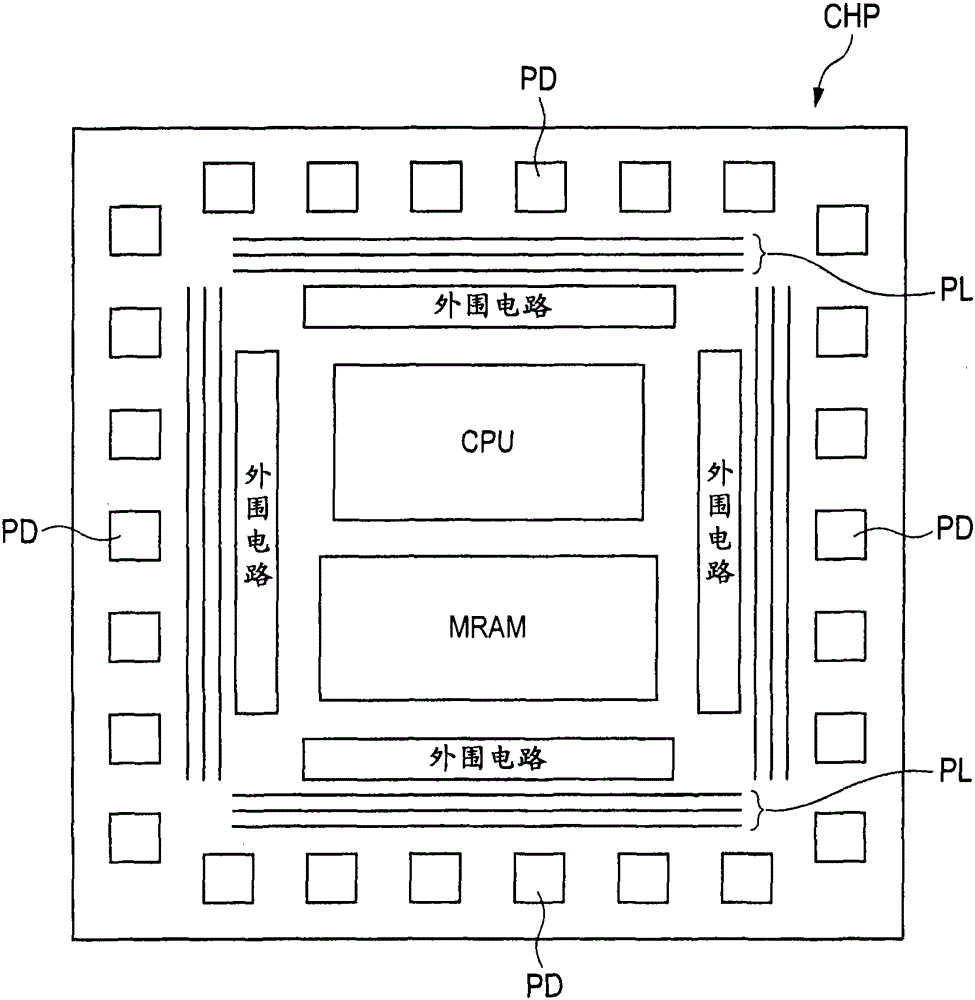

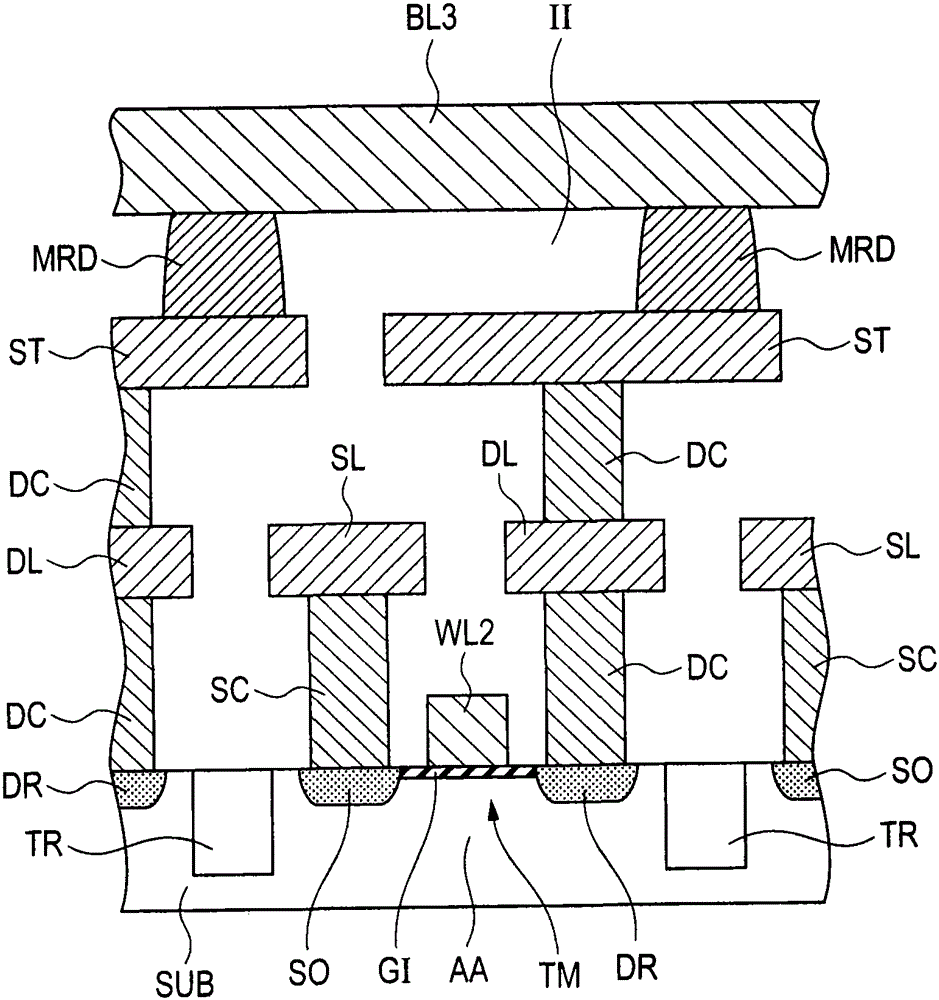

Semiconductor device

InactiveCN102629659BEasy to handleDoes not increase the areaNanoinformaticsMagnetic-field-controlled resistorsIn planeMagnetization

A semiconductor device comprising: a spin moment written in-plane magnetized magnetoresistive element placed on a main surface of a semiconductor substrate, the magnetization state of which can be changed according to a current flow direction; and a first wiring, and the magnetoresistive element Electrically coupled and extending toward a direction along the major surface. The width-to-length ratio of the magnetoresistive element as seen in a plane is a value other than 1. In a memory cell region where a plurality of memory cells in which a magnetoresistive element and a switching element are electrically coupled to each other are arranged, measures are taken: a plurality of memory cells adjacent to each other in the length direction of each magnetoresistive element as seen in a plane The magnetoresistive elements are arranged such that they are not placed on the same straight line extending in the length direction.

Owner:RENESAS ELECTRONICS CORP

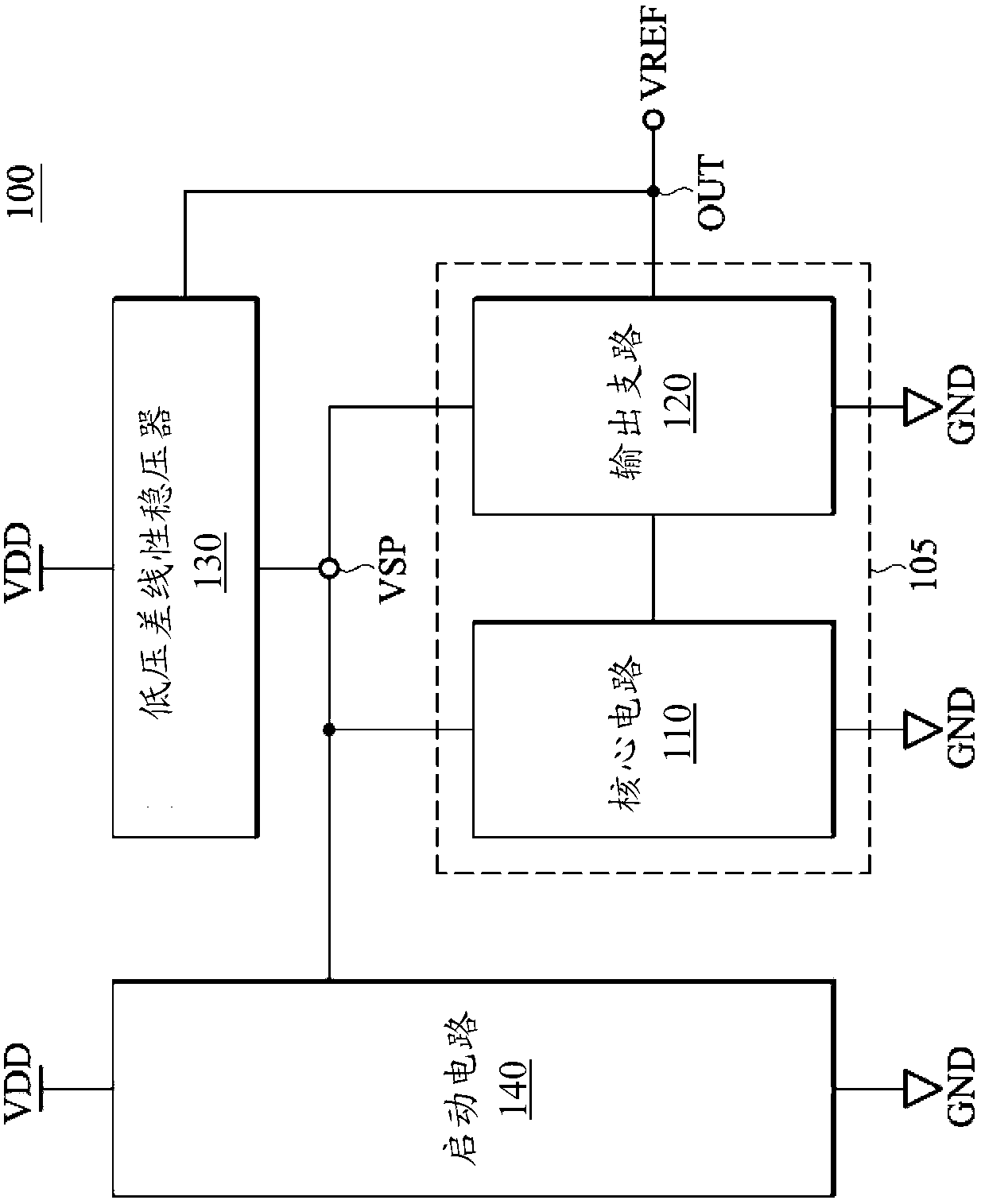

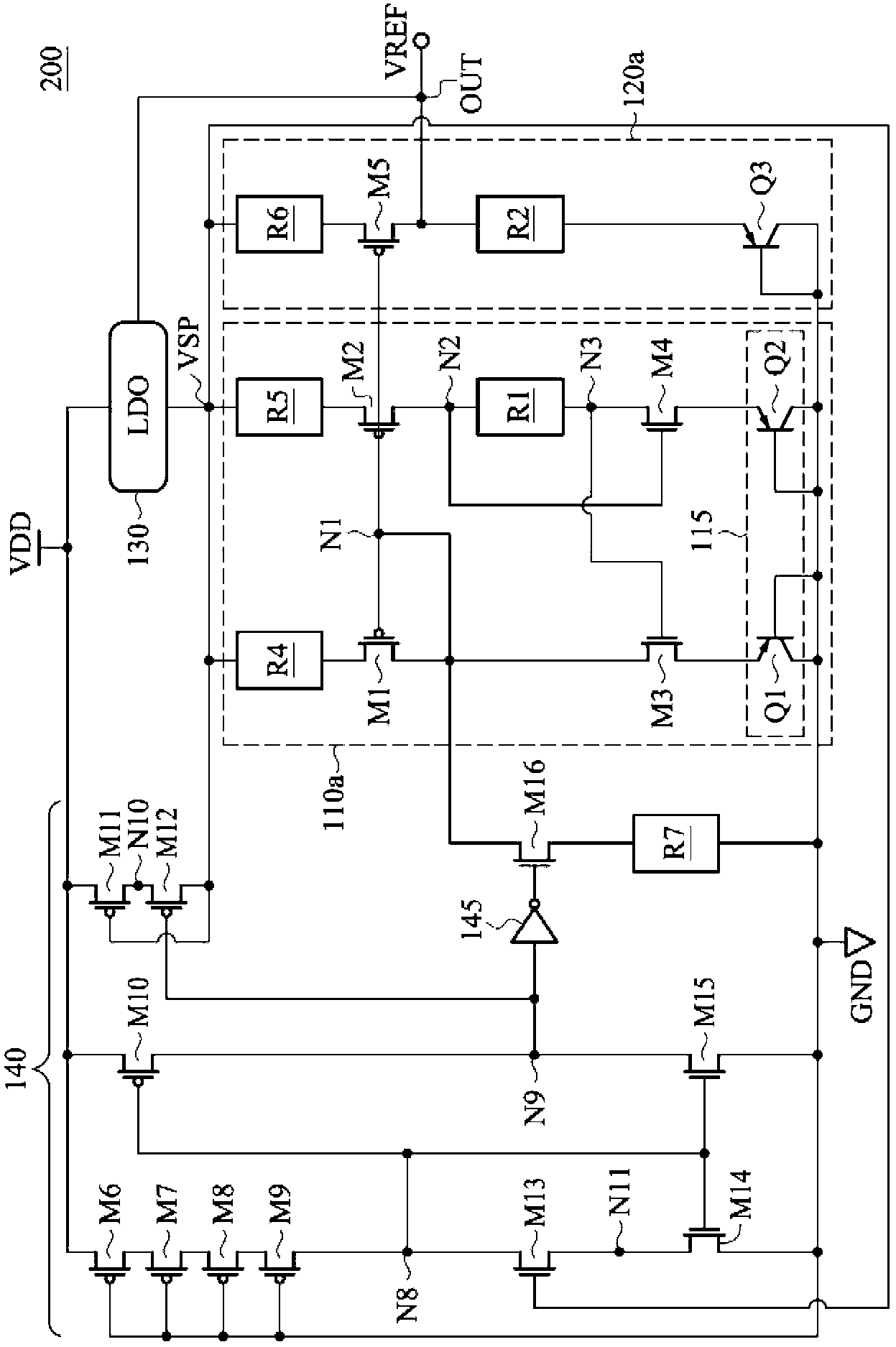

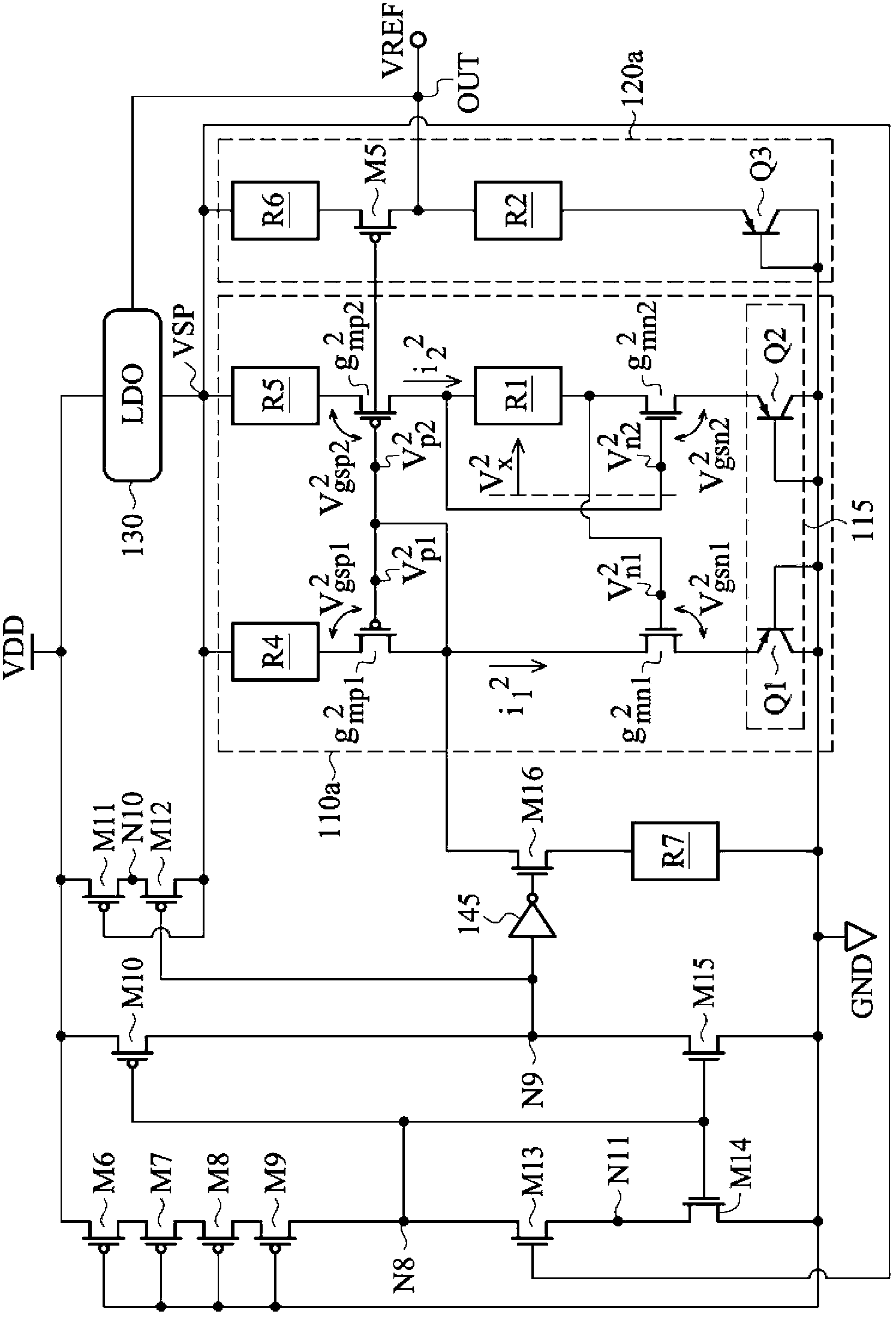

Bandgap circuit

InactiveCN102915062ADoes not increase the areaGood Noise Cancellation PerformanceElectric variable regulationVoltage referenceTransistor

Owner:MEDIATEK SINGAPORE PTE LTD SINGAPORE

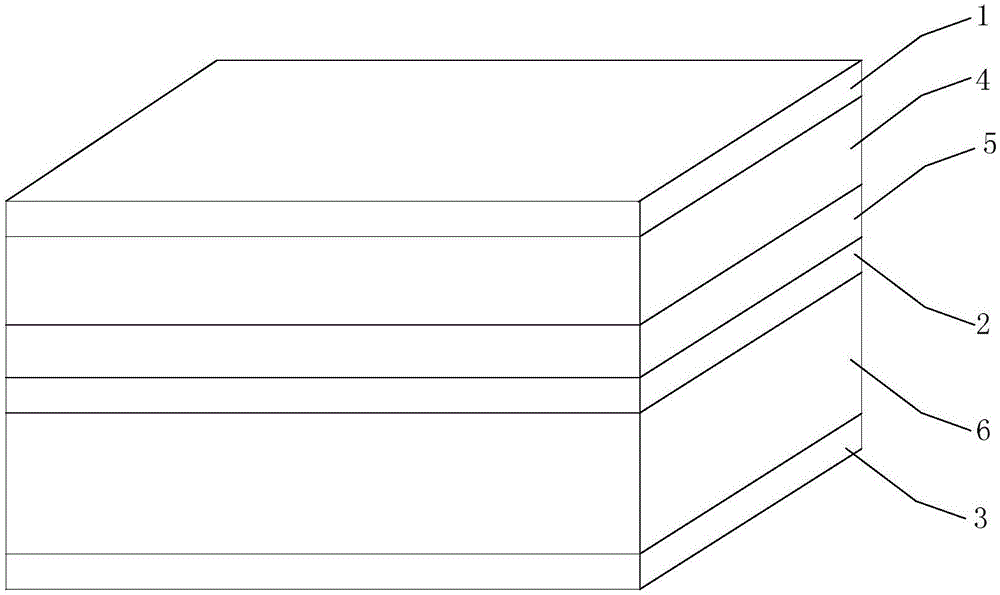

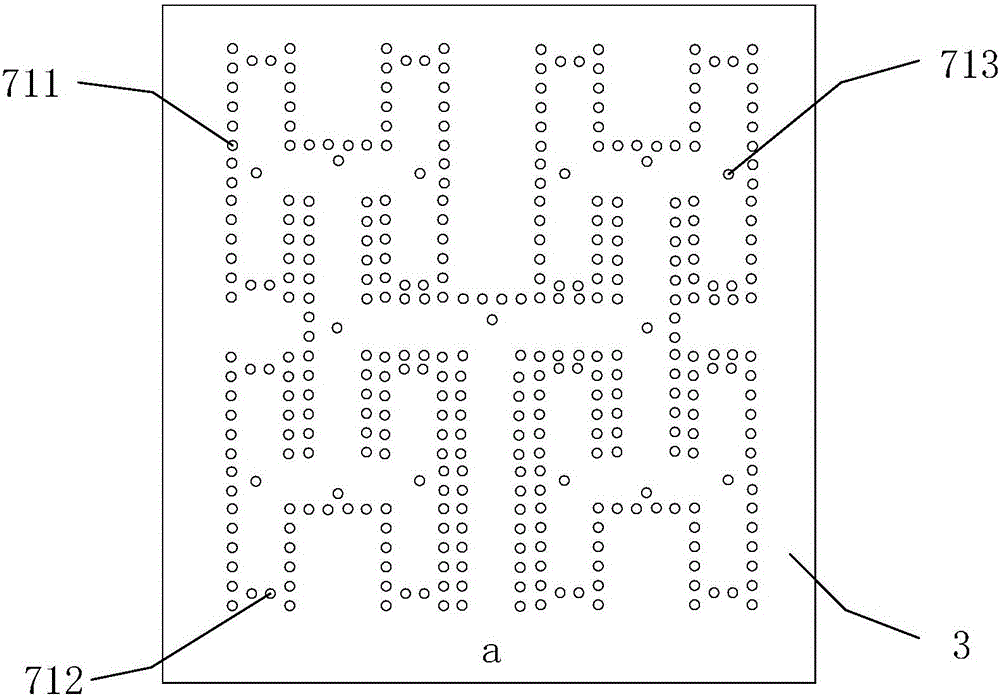

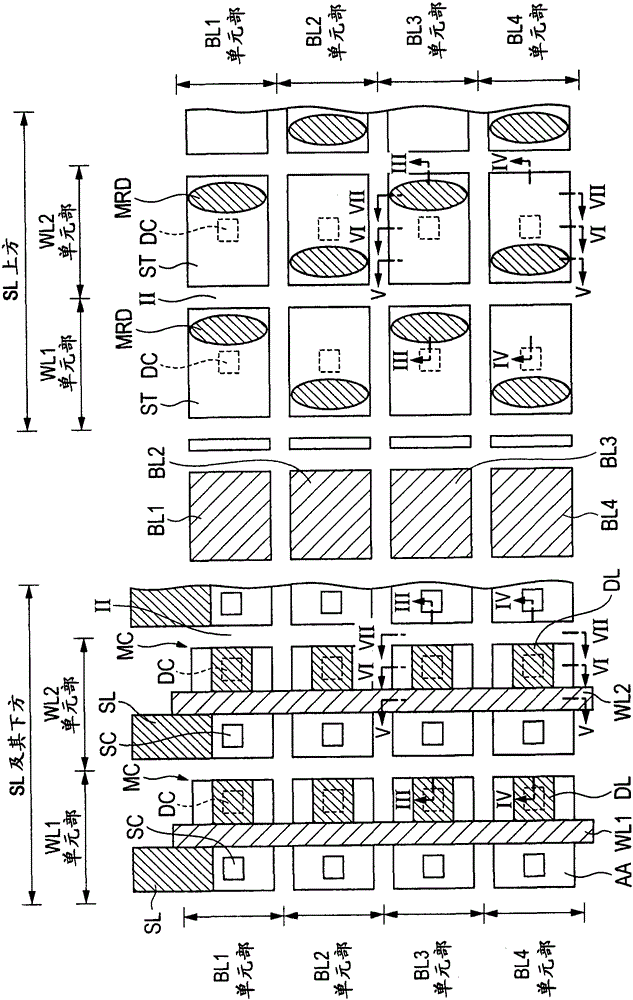

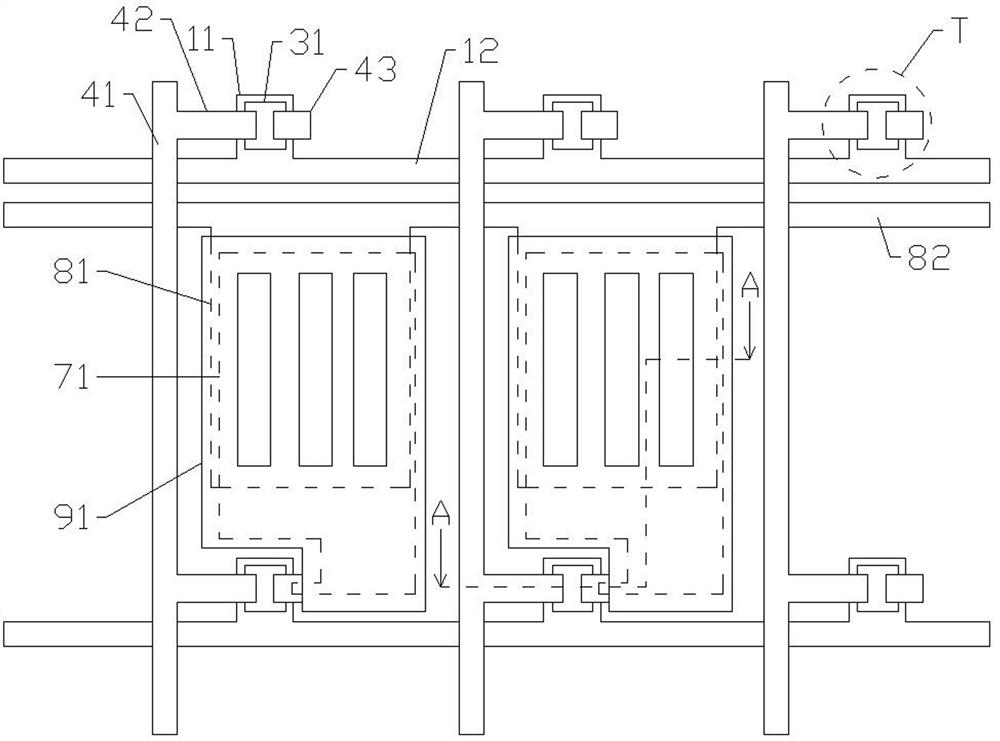

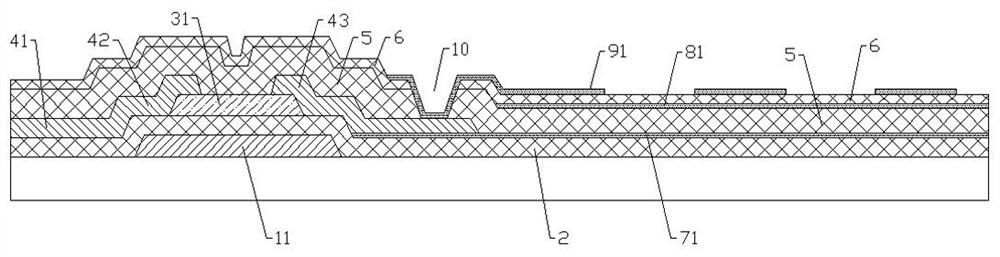

Low-frequency low-power-consumption array substrate and manufacturing method thereof

InactiveCN112363353AGuaranteed resolutionDoes not increase footprintSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringLow power dissipation

The invention discloses a low-frequency low-power-consumption array substrate which comprises a pixel area; the pixel area comprises a first electrode layer, a first insulating layer, a second electrode layer, a second insulating layer and a third electrode layer which are stacked up and down, the first electrode layer comprises a first electrode, and the second electrode layer comprises a secondelectrode; the third electrode layer comprises a third electrode; the first electrode and the second electrode are at least partially overlapped up and down, so that a first storage capacitor is formed by the upper and lower overlapped parts of the first electrode and the second electrode; and the second electrode and the third electrode are at least partially overlapped up and down, so that a second storage capacitor is formed by the upper and lower overlapped parts of the second electrode and the third electrode. According to the low-frequency low-power-consumption array substrate, the voltage maintaining time of the pixel electrode can be prolonged under the condition that the resolution is not reduced, so that the pixel electrode still has sufficient voltage maintaining time in a low-frequency and low-power-consumption working state. The invention further discloses a manufacturing method of the low-frequency low-power-consumption array substrate.

Owner:信利(仁寿)高端显示科技有限公司

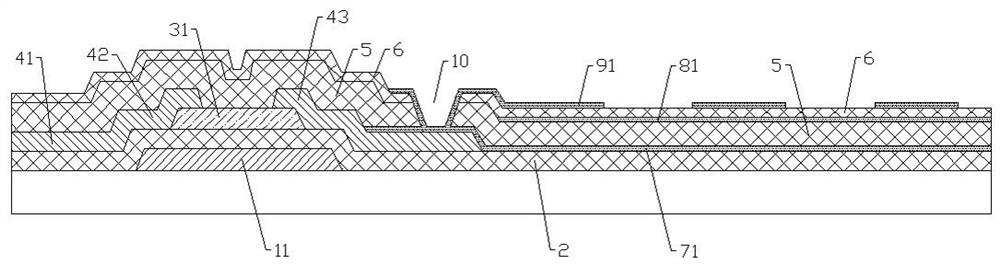

Power source ground network and wire arrangement method thereof

ActiveCN104241247AIncrease the number of gridsIncrease mesh densitySemiconductor/solid-state device detailsSolid-state devicesGrid densityVoltage drop

The invention discloses a power source ground network and a wire arrangement method of the power source ground network. The power source ground network comprises a plurality of first power wires, first ground wires, a plurality of first vertical metal wires and a plurality of second vertical metal wires, wherein the first power wires and the first ground wires are located in a first metal layer and arranged in parallel at intervals, the first vertical metal wires are located in a second metal layer, the arrangement direction of the first vertical metal wires is perpendicular to the arrangement direction of the first power wires and the first ground wires, and every two adjacent first vertical metal wires are in one group. In each group, one is a second power wire, and the other is a second ground wire. The second power wires are connected with the first power wires, the second ground wires are connected with the first ground wires, and first intervals exist between the different groups. The second vertical metal wires are located in the second metal layer and among the first vertical metal wires in the different groups and are parallel with the first vertical metal wires, second intervals exist between the adjacent second vertical metal wires, and the second vertical metal wires are connected with the first power wires or the first ground wires. The grid density of the power source ground network is improved, and the voltage drop is reduced.

Owner:GALAXYCORE SHANGHAI

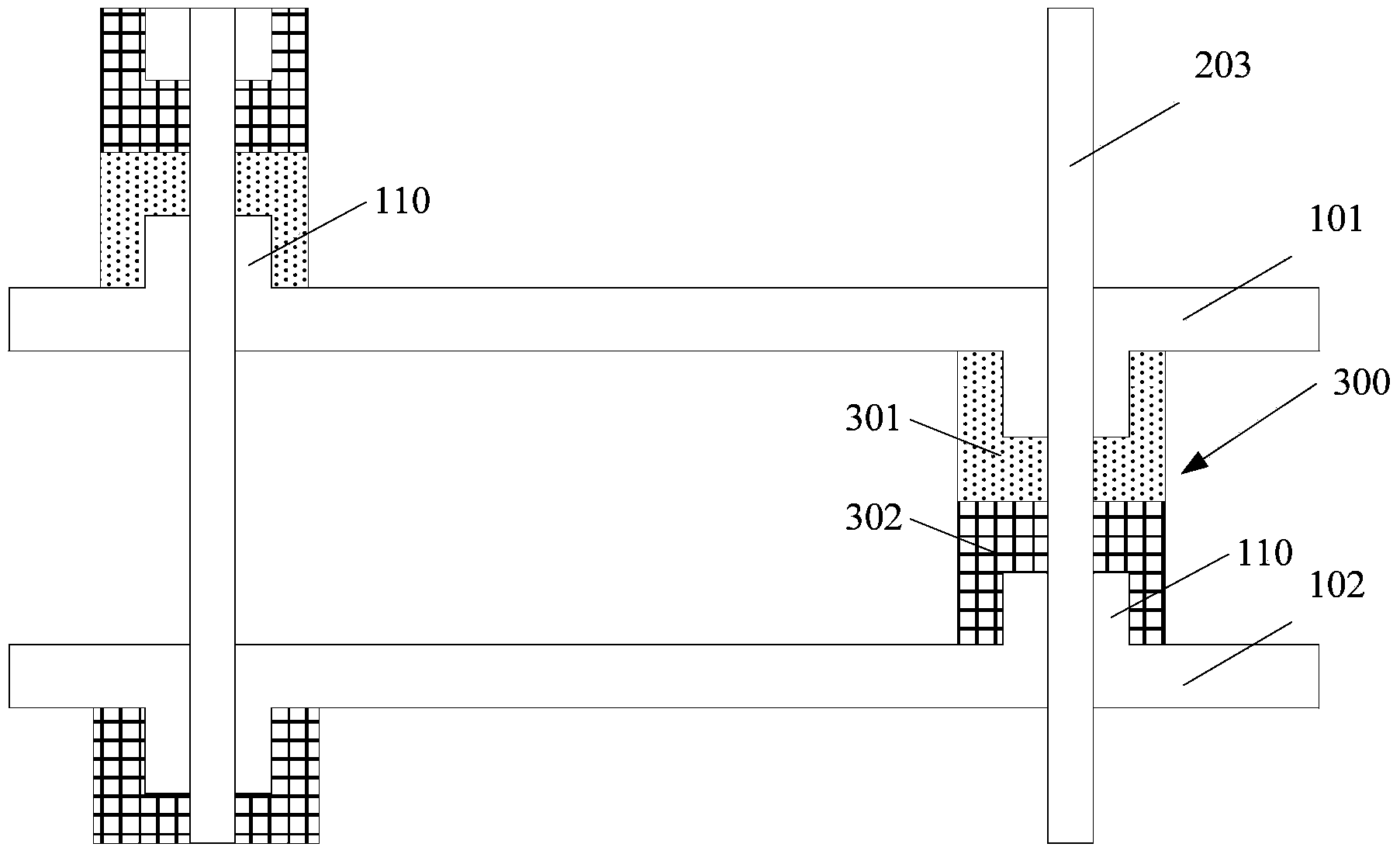

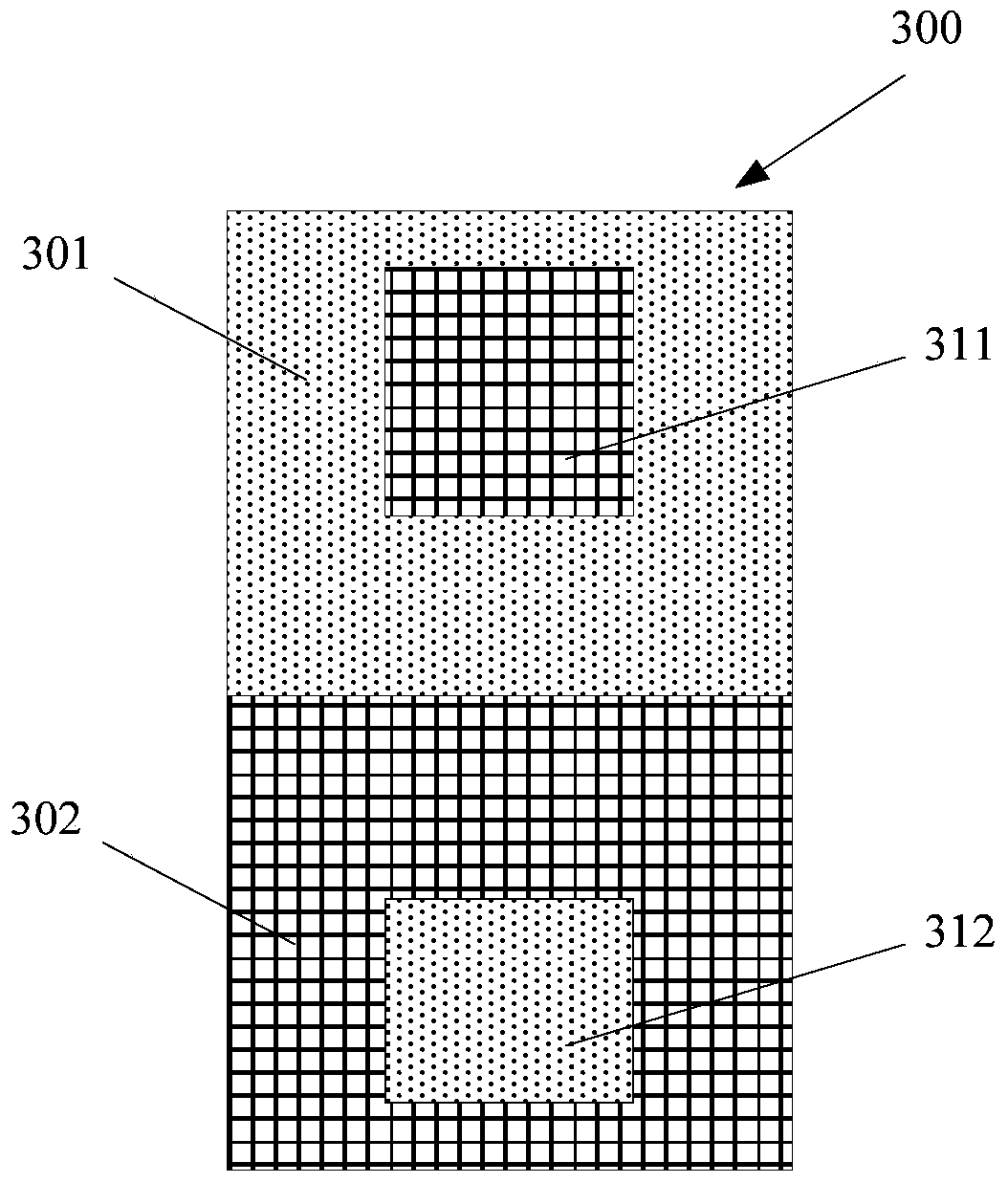

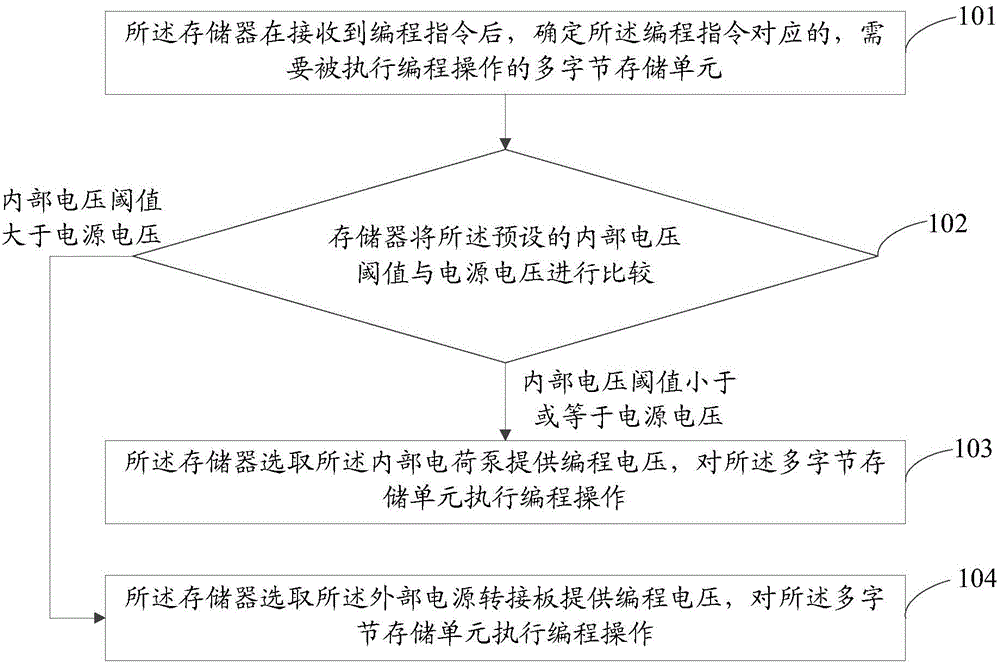

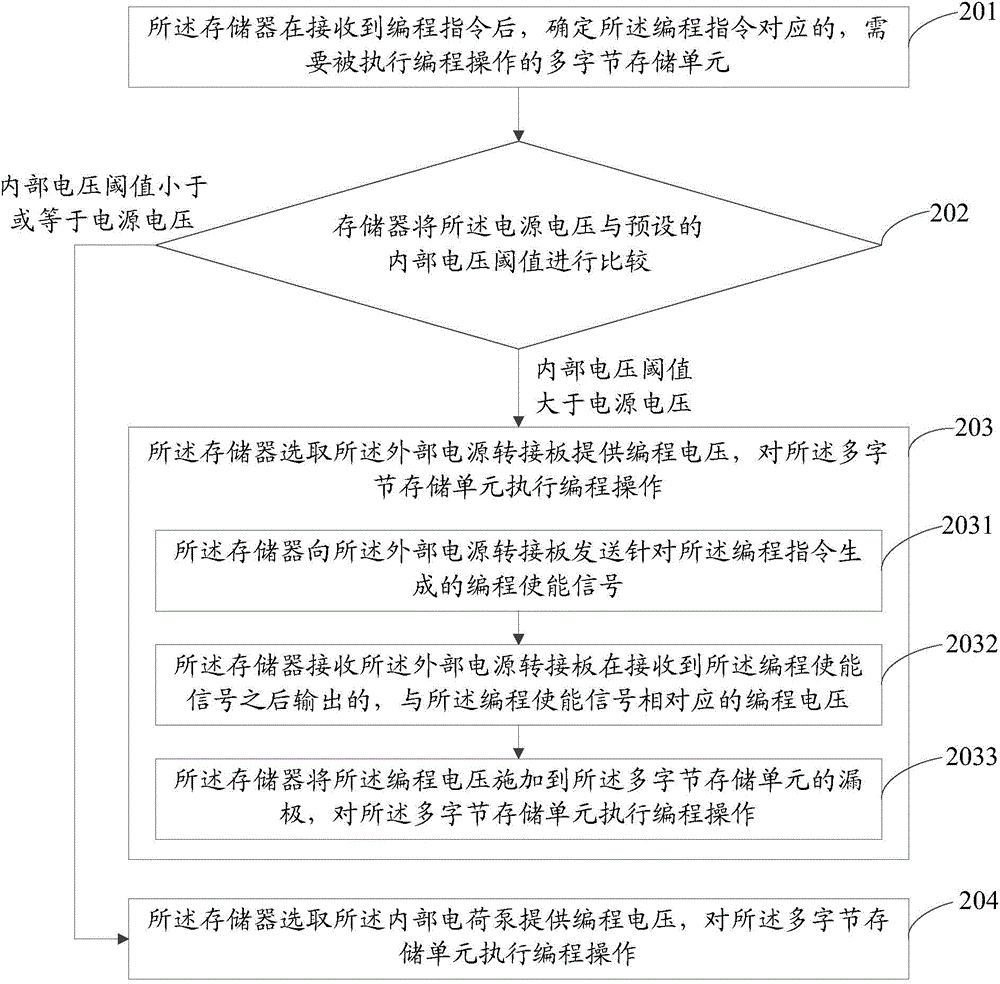

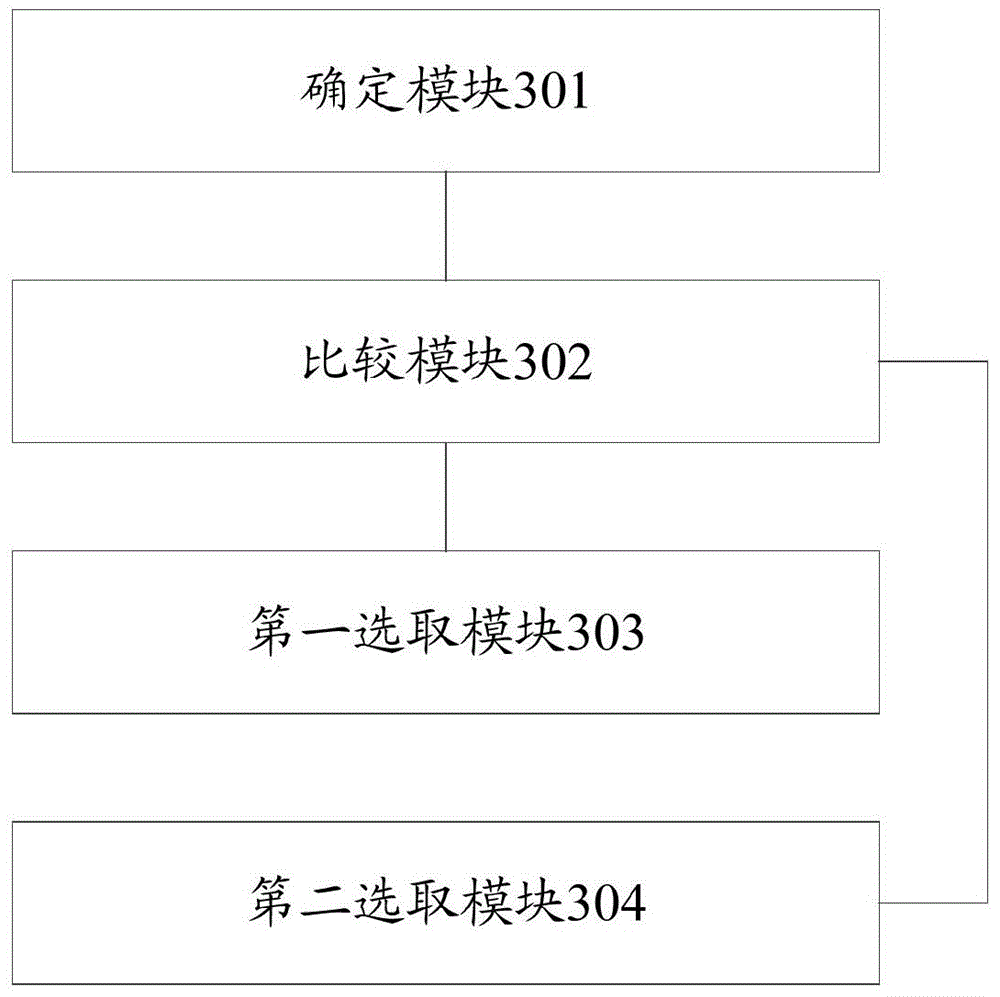

Memory programming method and system

The invention discloses a memory programming method and system to solve the problems that larger memory areas are occupied, the costs of memories are increased and use of other devices in the memories is affected by increasing the quantities of capacitors and diodes in charge pumps. The method comprises the steps that after receiving a programming instruction, a memory determines a multi-byte memory cell which corresponds to the programming instruction and needs to undergo programming operation; the memory compares power supply voltage with a preset internal voltage threshold; if the internal voltage threshold is less than or equal to the power supply voltage, an internal charge pump is selected to provide programming voltage to carry out programming operation on the multi-byte memory cell; if the internal voltage threshold is more than the power supply voltage, an external power supply transfer board is selected to provide programming voltage to carry out programming operation on the multi-byte memory cell. The method has the advantages that the area of the memory can not be increased; the cost of the memory is lower; use of other devices in the memory can not be affected; the external power supply transfer board is more flexible to use.

Owner:GIGADEVICE SEMICON (BEIJING) INC

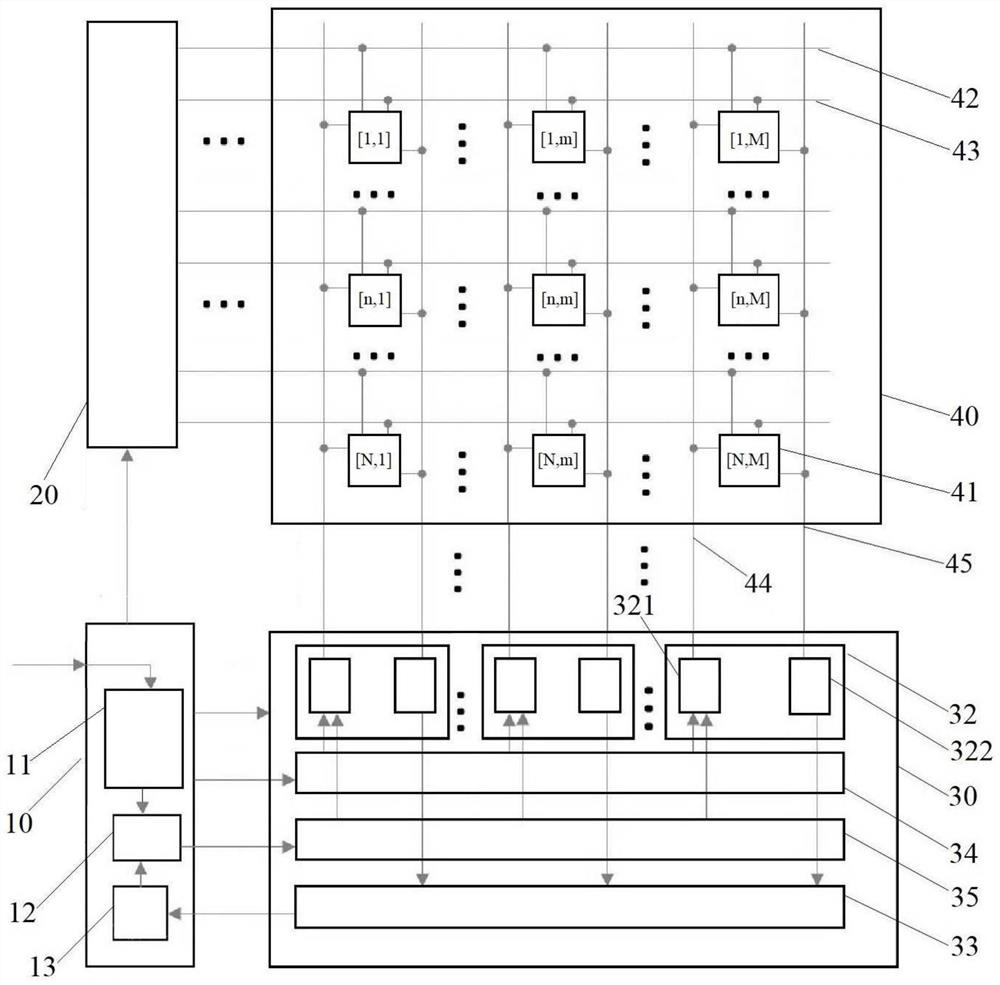

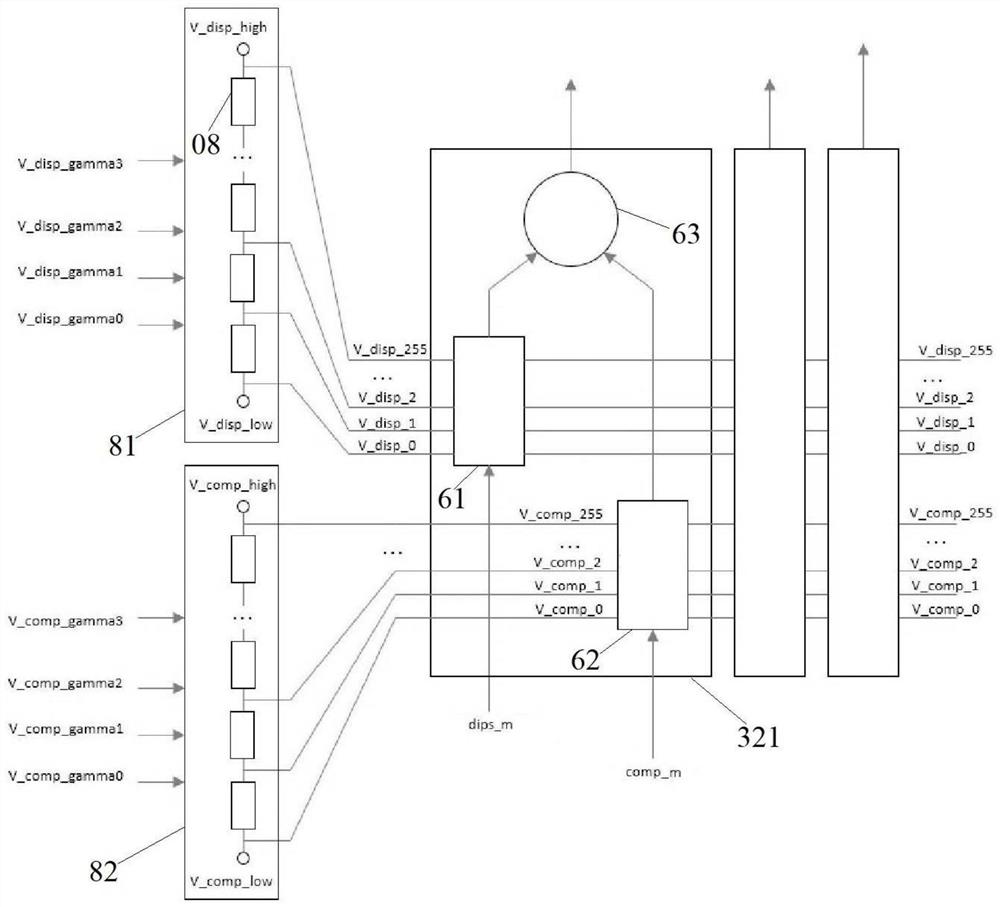

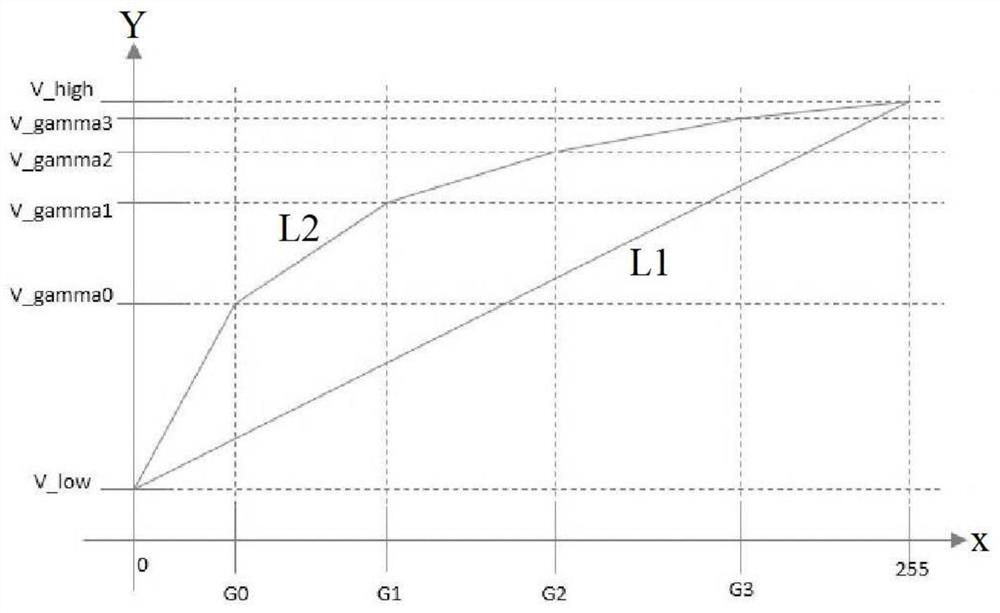

Feedback signal detection method and pixel external analog domain compensation display system

ActiveCN112164358ASimple designDoes not increase the areaStatic indicating devicesDigital-to-analog converterConverters

The invention provides a feedback signal detection method and a pixel external analog domain compensation display system. The system comprises M columns of driving channels, each column of which comprises a pixel unit and a detection unit; the detection unit comprises a source driving module and a detection module; and the detection module comprises a comparator. A first digital-to-analog converter and a second digital-to-analog converter are arranged in the source driving module. The source driving module is connected to the pixel unit through a display signal line. A first input end of the comparator is connected to the pixel unit through a feedback signal line, a second input end of the comparator is connected to the second digital-to-analog converter, and the output end of the comparator is used for outputting a detection result. The digital-to-analog converter and the comparator are matched to detect aging information fed back by a target pixel unit, devices like a TFT, an OLED and a QLED can be detected, existing modules in the display system are further utilized, the area of a chip cannot be increased, and the overall design of the display system is optimized.

Owner:PEKING UNIV SHENZHEN GRADUATE SCHOOL

Lateral diffused metal oxide semiconductor field effect transistor

ActiveCN109599439ADoes not affect DC performanceDoes not increase the areaTransistorSolid-state devicesMOSFETLDMOS

Embodiments of the present invention provide a lateral diffused metal oxide semiconductor field effect transistor. The metal oxide semiconductor field effect transistor (MOSFET) comprises: a body region located on an upper portion of a substrate and having a first conductivity type; a drift region located at the upper part of the substrate and having a second conductivity type, wherein a first isolation region os arranged between the body region and the drift region; a grid positioned above the substrate; a source region located in the body region; a drain region in the drift region, comprising a first drain region and a second drain region disposed adjacent to each other, wherein the first drain region has a second conductivity type, and the second drain region having a first conductivitytype; a second isolation region disposed in a drift region between the first isolation region and the drain region; and a first doped region having a first conductivity type in the substrate betweenthe first isolation region and the second isolation region. The first doped region and the drift region form a first diode.

Owner:NUVOTON

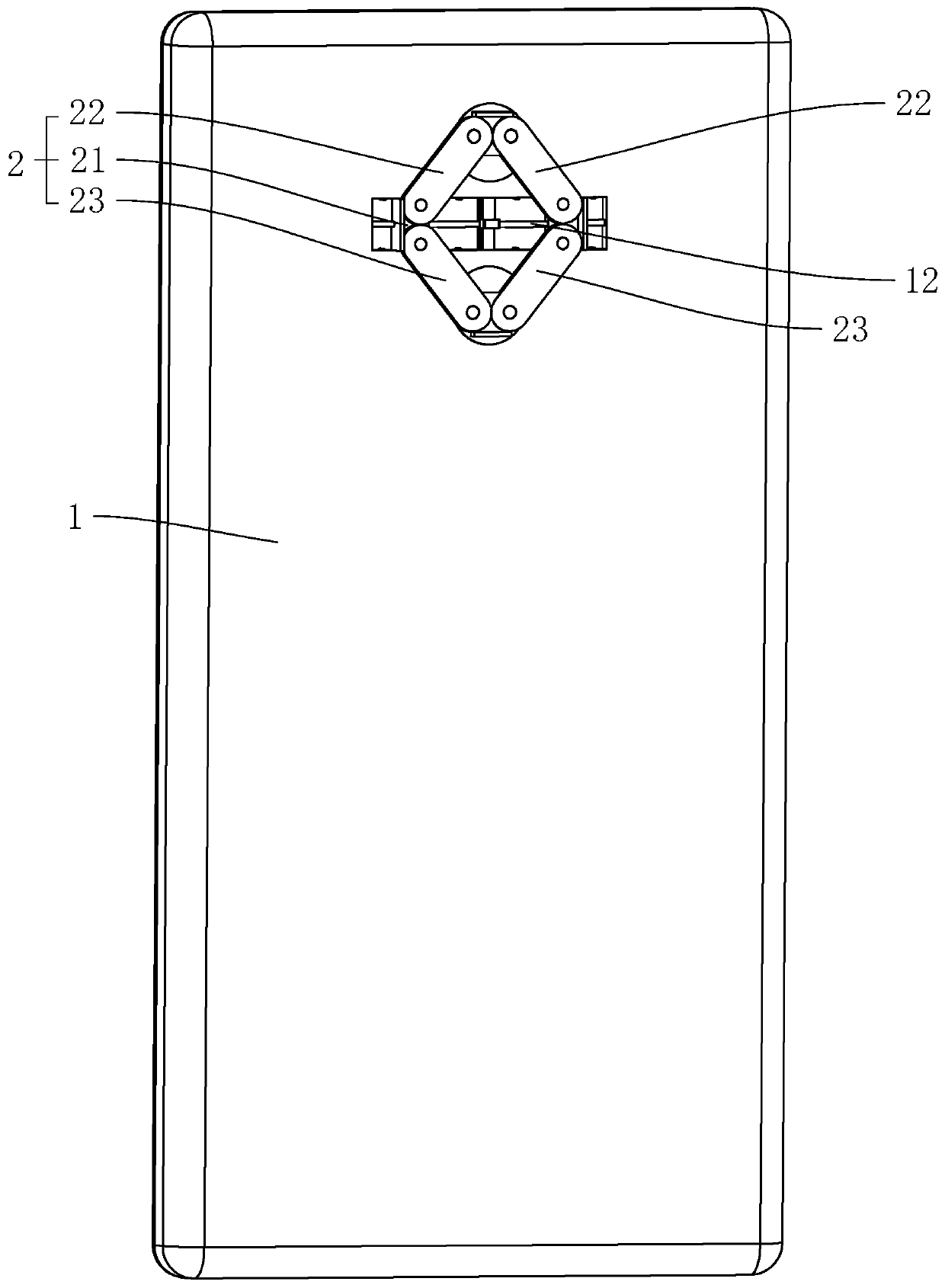

Mobile phone lens cone with protection function

ActiveCN110830621ADoes not increase the areaUse impactTelephone set constructionsDevices with fuctional cameraEngineeringComputer science

The invention discloses a mobile phone lens cone with a protection function. Key points of the technical scheme are as follows: the key points are as follows; protective mechanism, the protection mechanism comprises a plurality of sliding blocks sliding on the back surface of the machine body, a plurality of upper protection sheets for covering the upper camera and a plurality of lower protectionsheets for covering the lower camera; a sliding groove is formed between the two cameras of the machine body, the sliding block is arranged in the sliding groove to slide, the upper protection parts are connected to the upper ends of the side walls, away from the machine body, of the sliding block, the lower protection parts are connected to the lower ends of the side walls, away from the mobile phone, of the sliding block, the adjacent upper protection parts abut against each other, and the adjacent lower protection parts abut against each other. The upper protection sheet and the lower protection sheet arranged between the two cameras are used for shielding the cameras. When the mobile phone is not needed, the upper protection sheet and the lower protection sheet are accommodated betweenthe two cameras, so that the area of the protection mechanism required for shielding the cameras is not increased while the two cameras are shielded, and the use of the mobile phone is not influenced.

Owner:深圳纳百鑫光学有限公司