Pseudo-static memory and method for controlling write operation and refresh operation of pseudo-static memory

A write operation and memory technology, applied in static memory, digital memory information, information storage, etc., can solve the problems of slower access speed and faster SRAM, and achieve the effect of improving access speed and work efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

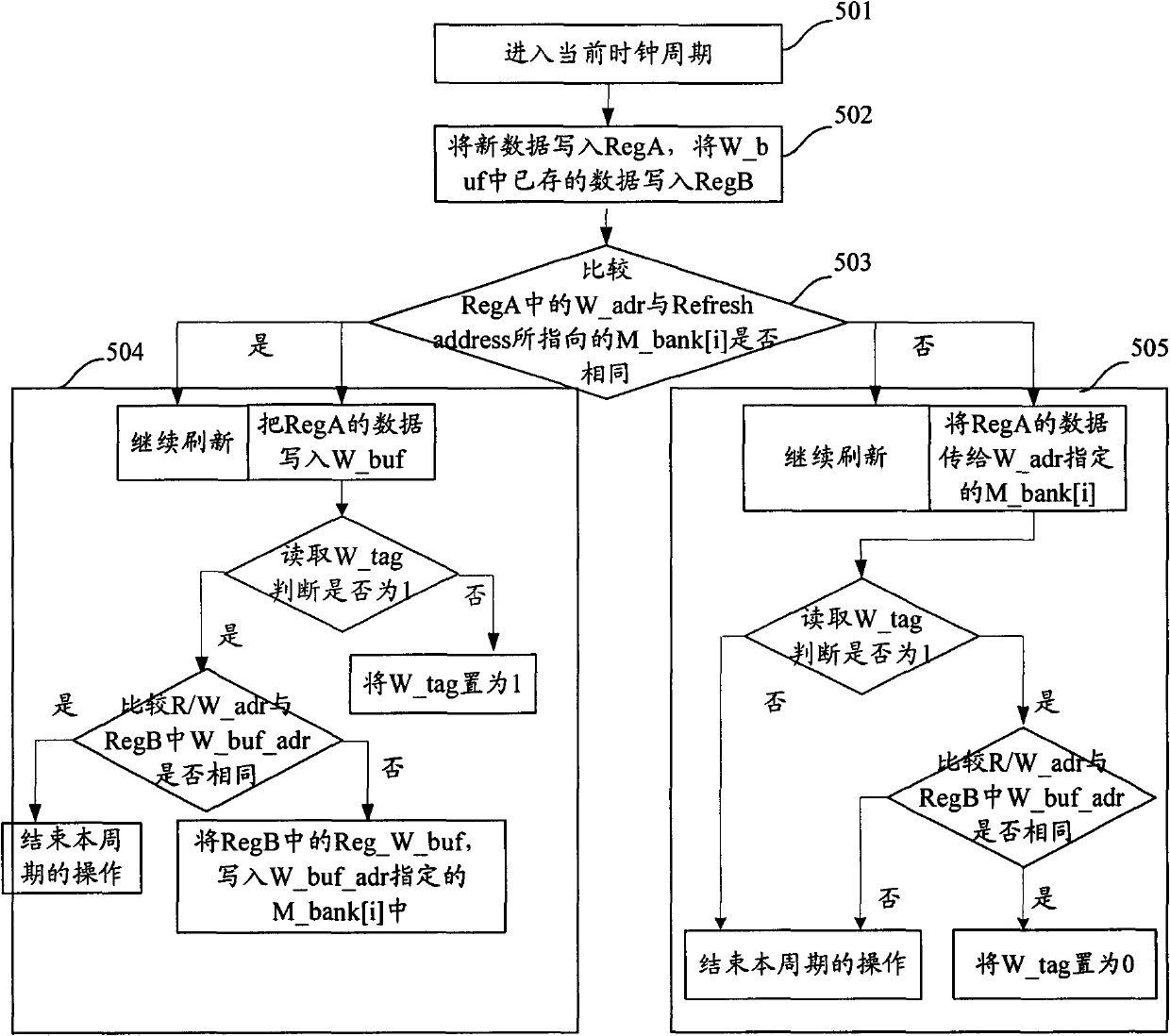

[0048] In order to make the above objects, features and advantages of the present invention more comprehensible, the present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

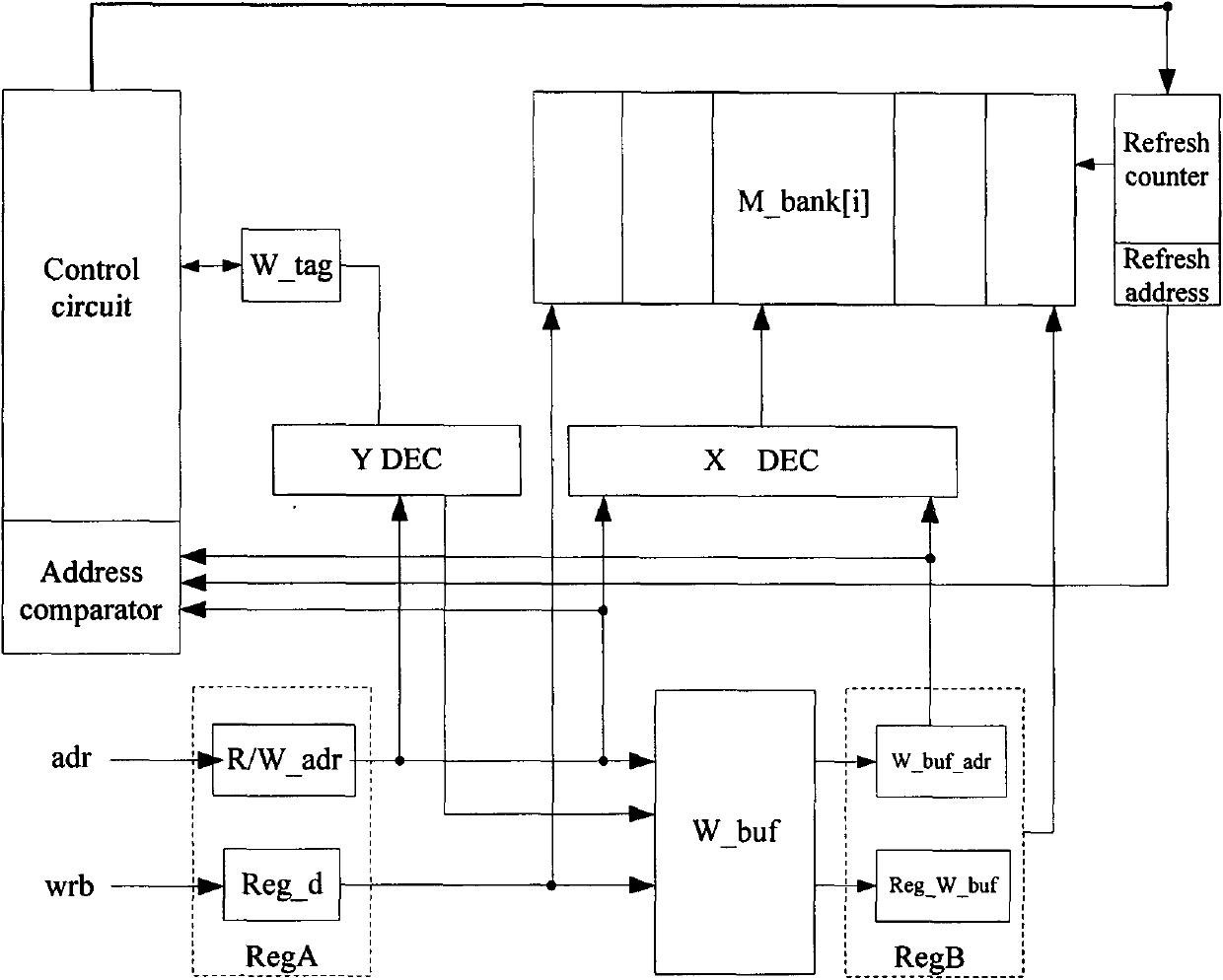

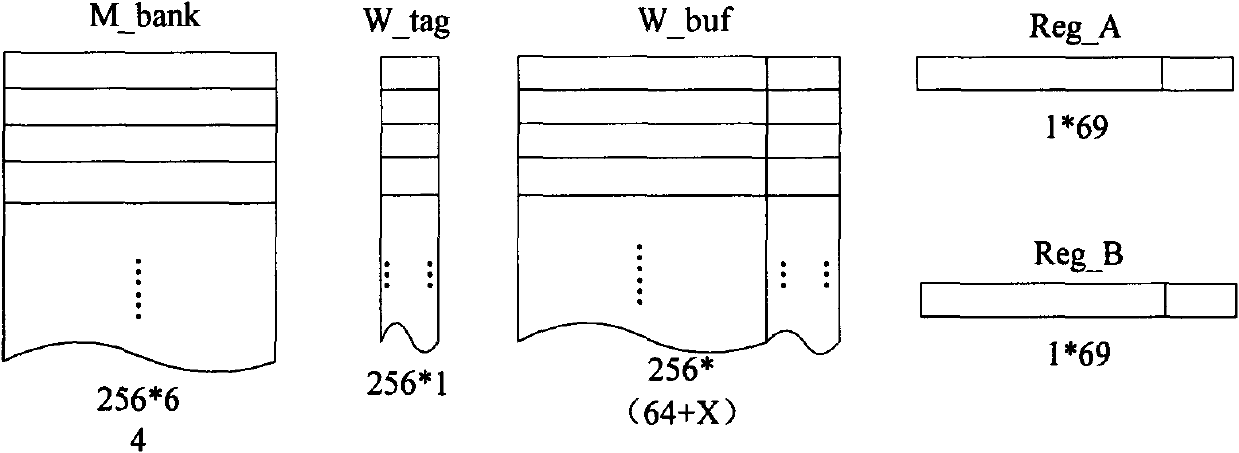

[0049] The inventor of this patent creatively proposed the idea of improving the access speed by parallelizing the write operation and the refresh operation, and proposed a brand-new design of a pseudo-SRAM, which may specifically include:

[0050] The first register group RegA;

[0051] The second register group RegB;

[0052] Write operation buffer W_buf;

[0053] Write operation flag register W_tag;

[0054] Write the new data and the corresponding memory bank address that need to be written into the memory group M_bank[i] into the first register group RegA, and write the data stored in the write operation buffer W_buf and the corresponding memory group address into the second Register group RegB; in practice, this module ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More