Insertion method for filling redundant polysilicon strip arrays in existing layout

A technology of polysilicon strips and polysilicon, applied in special data processing applications, instruments, electrical digital data processing, etc., to achieve the effect of increasing layout area and simple operation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

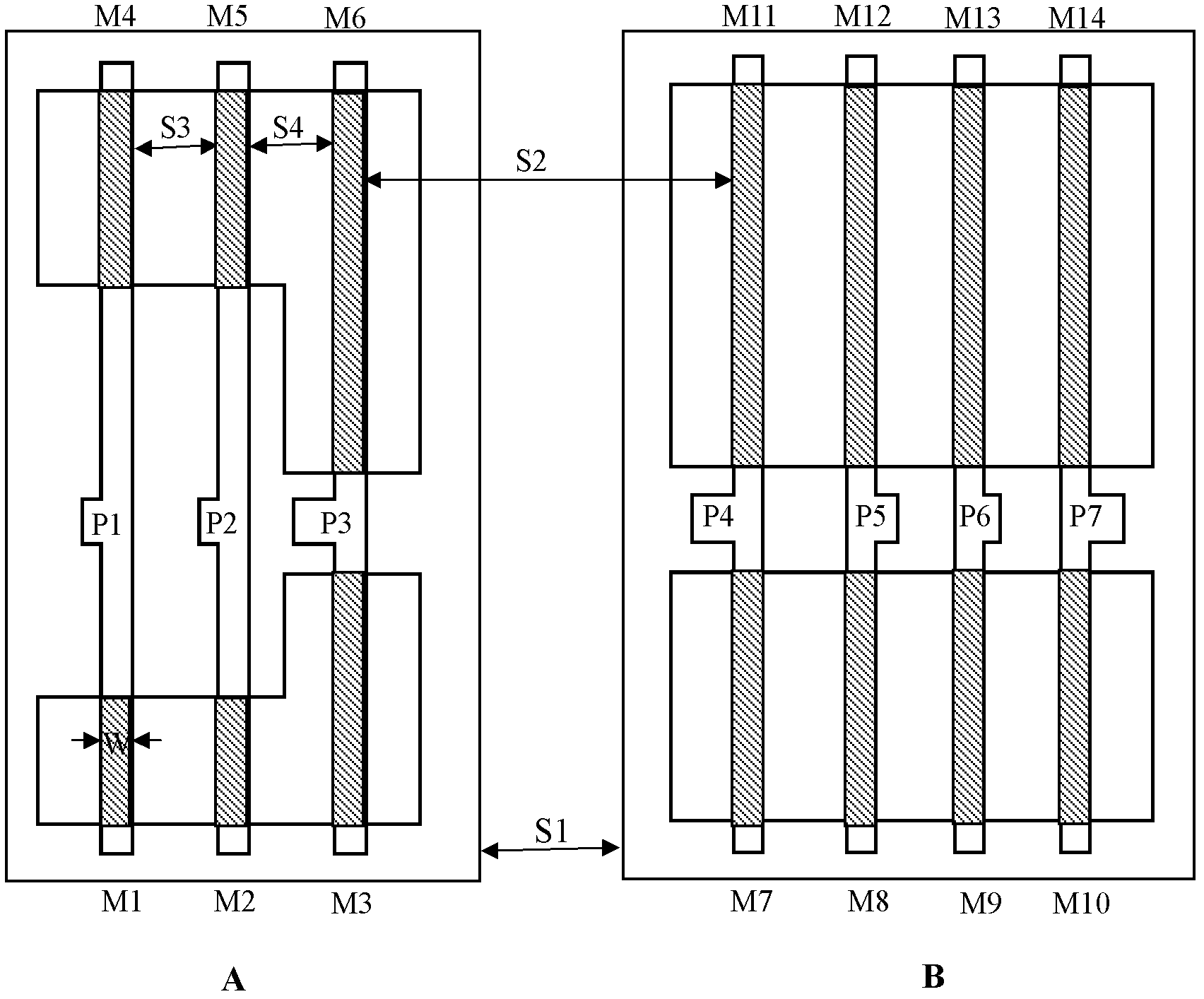

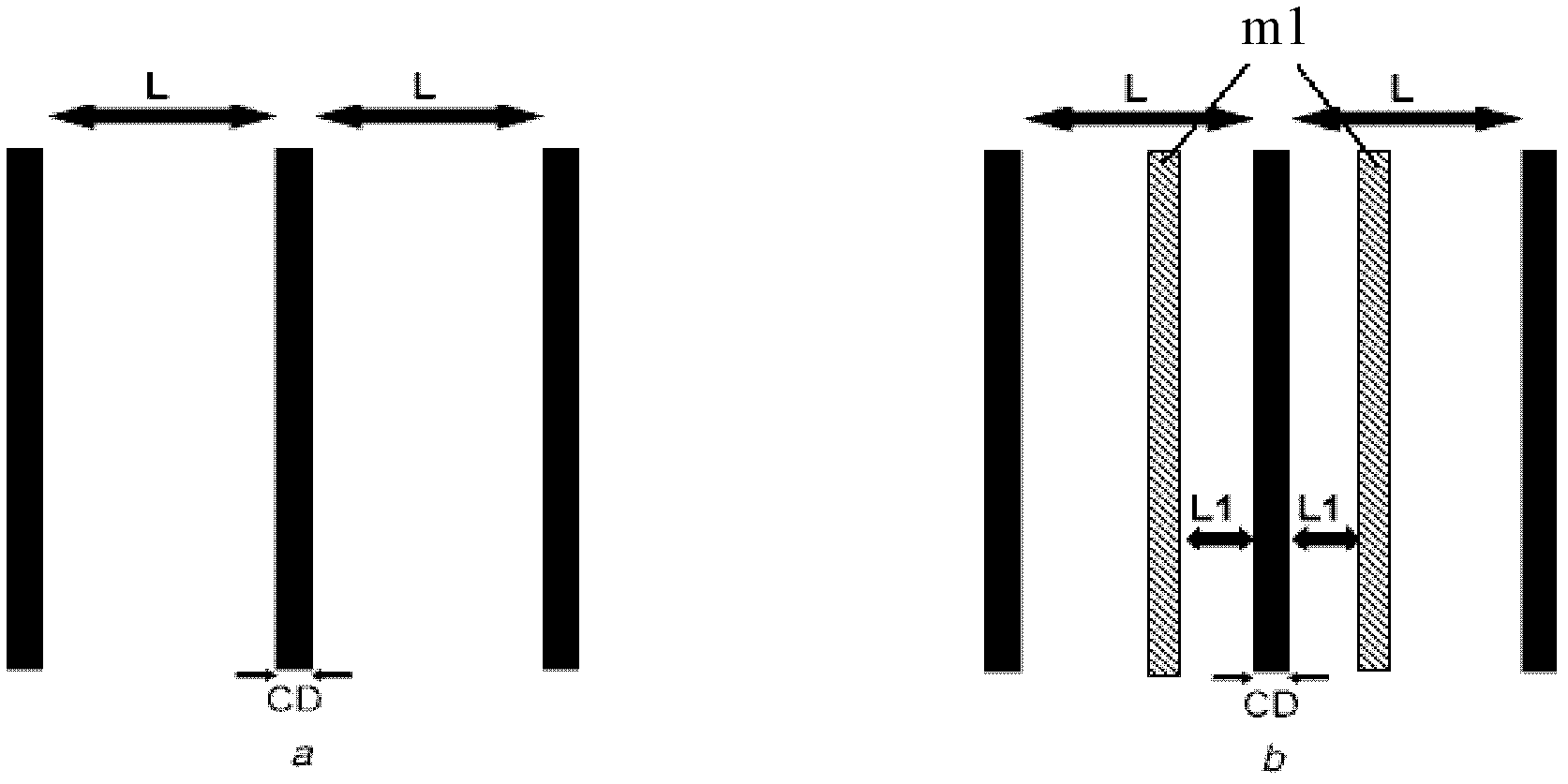

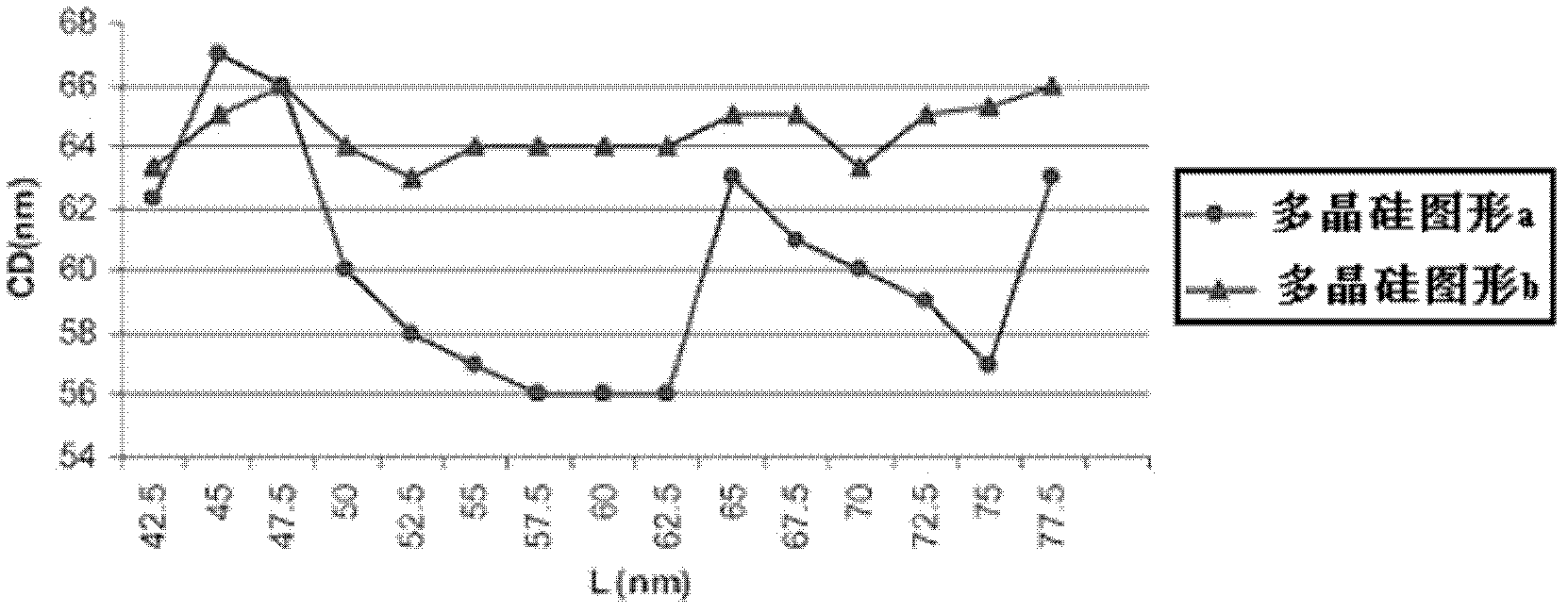

[0042] The specific implementation manner of the present invention will be described in detail below in conjunction with the accompanying drawings.

[0043] An insertion method for filling an array of redundant polysilicon strips into an existing layout, such as Figure 8 shown, including steps:

[0044] (1) Extract the location information of the standard unit.

[0045] The relative position coordinates X and Y of each standard cell in the layout can be obtained in the layout design tool, and the position information of the standard cells is the relative position coordinates X and Y of the standard cells in the layout.

[0046] (2) Based on the extracted position information, sort the positions of the standard units.

[0047] The sorting process of the position of the standard unit is specifically: the standard unit with the same Y coordinate value of the standard unit is represented in the same row, and the standard units in the same row are sorted according to the size of...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More