Method for manufacturing SOI MOS device capable of realizing ohmic contact with source body

A technology of ohmic contact and manufacturing method, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of increased parasitic effect, inconspicuous Kink effect, depletion, etc., and achieves simple manufacturing process and suppression of floating body effect Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

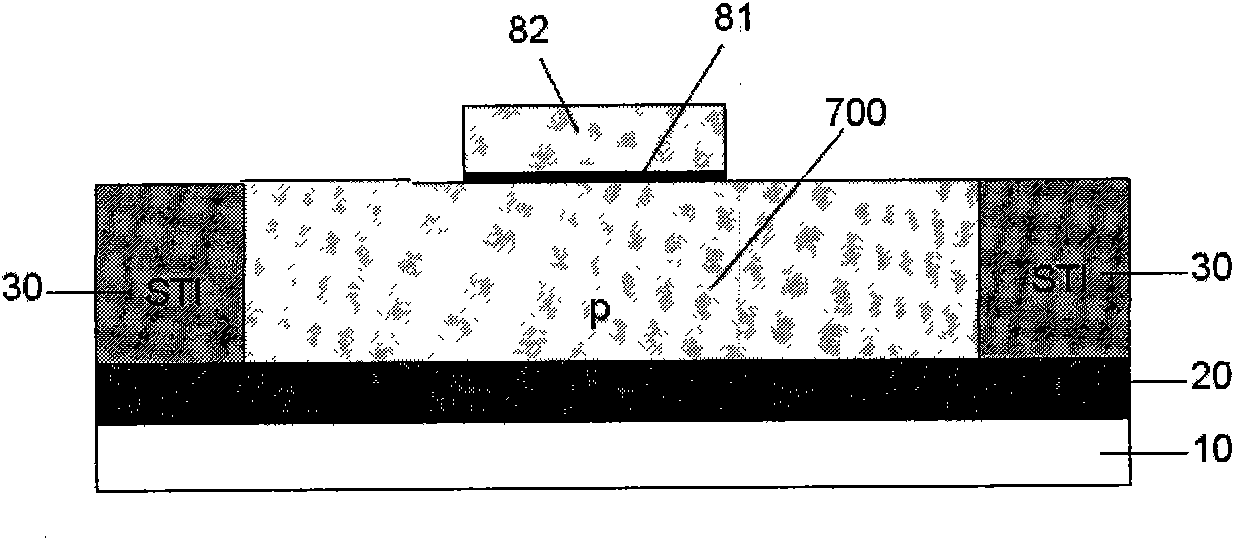

[0020] The present invention is further described below with reference to the accompanying drawings, which are not drawn to scale for the convenience of illustration.

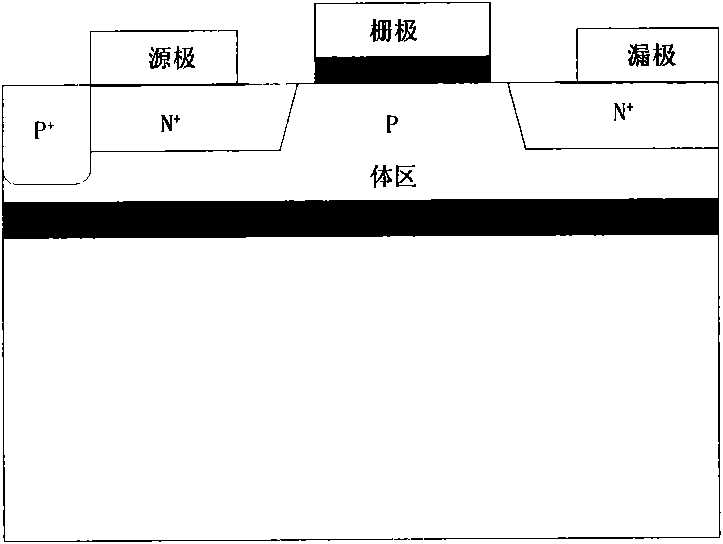

[0021] like Figure 2e As shown, a MOS device structure for suppressing SOI floating body effect includes: a substrate 10, an insulating buried layer 20 on the substrate 10, an active region on the insulating buried layer 20, and the active region on the The upper gate region and the Shallow Trench Isolation (STI) structure 30 around the active region.

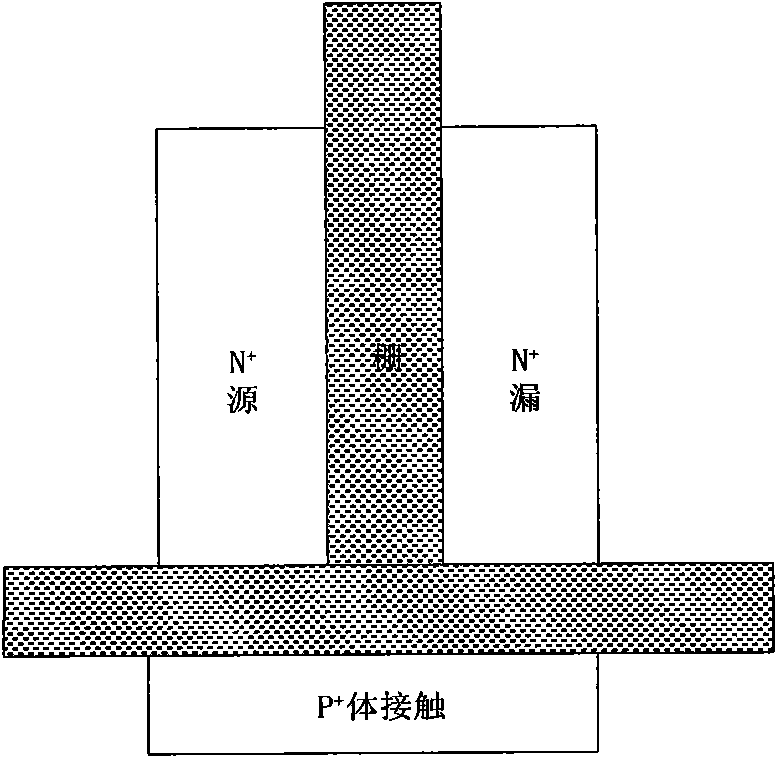

[0022] The active region includes: a body region 70, an N-type source region, an N-type drain region 40, and a heavily doped P-type region 60; the N-type source region is composed of a silicide 51 and an N-type Si region 52 connected thereto. The N-type source region and the N-type drain region 40 are located at both ends of the body region 70 respectively; the heavily doped P-type region 60 is located under the N-type Si region 52 of the N-type source region,...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More