Patents

Literature

804 results about "Analogue circuits" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

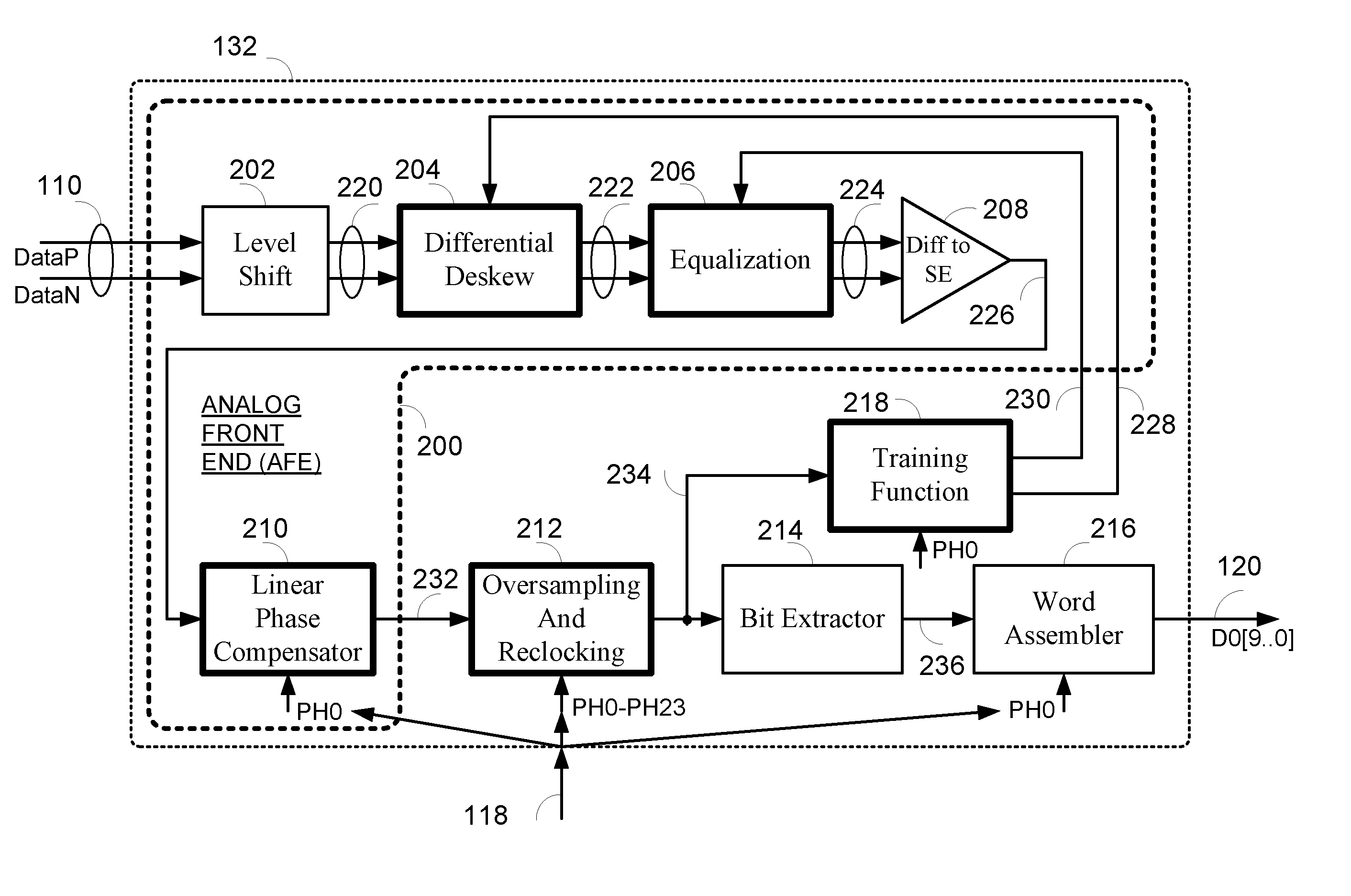

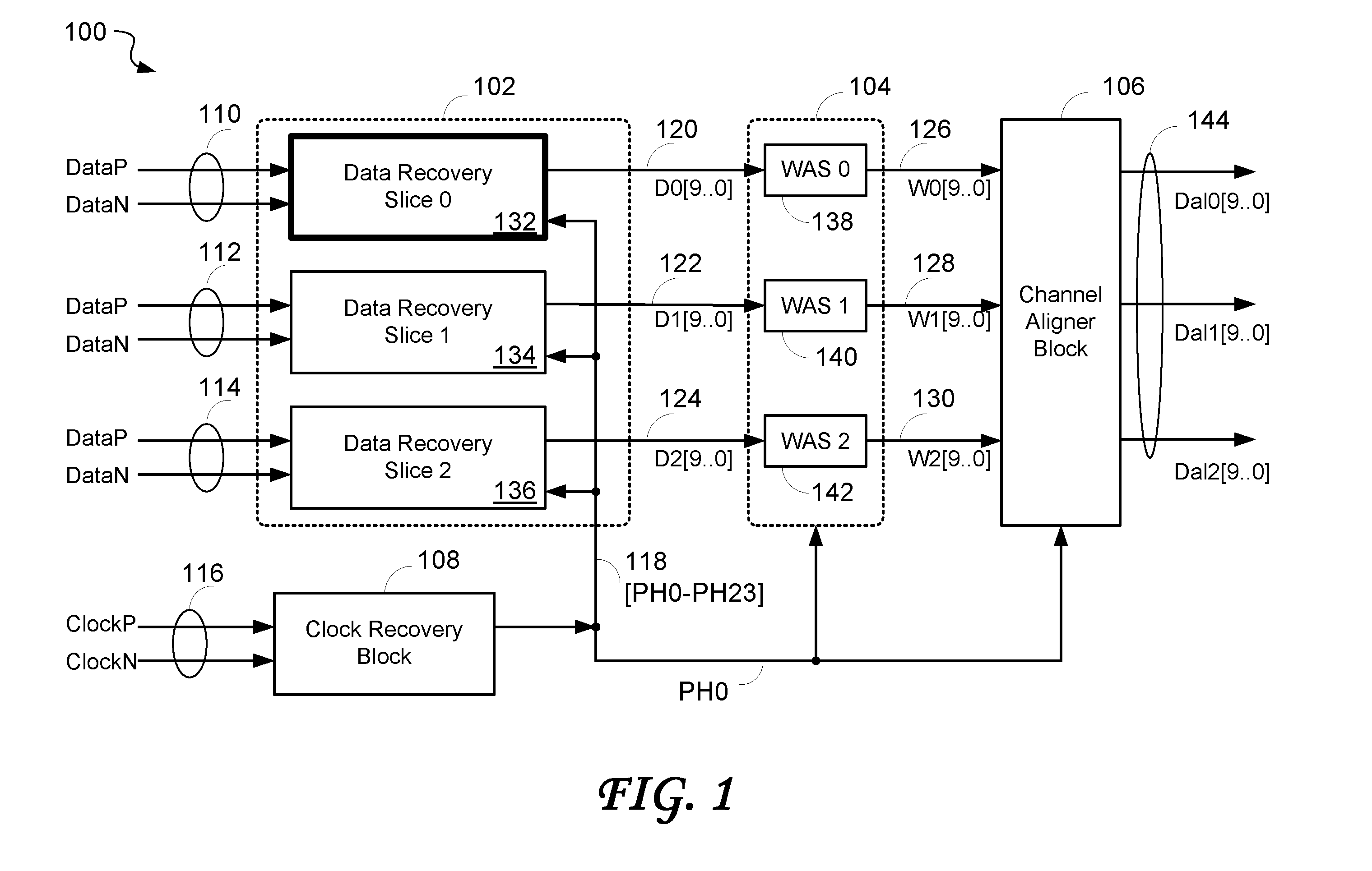

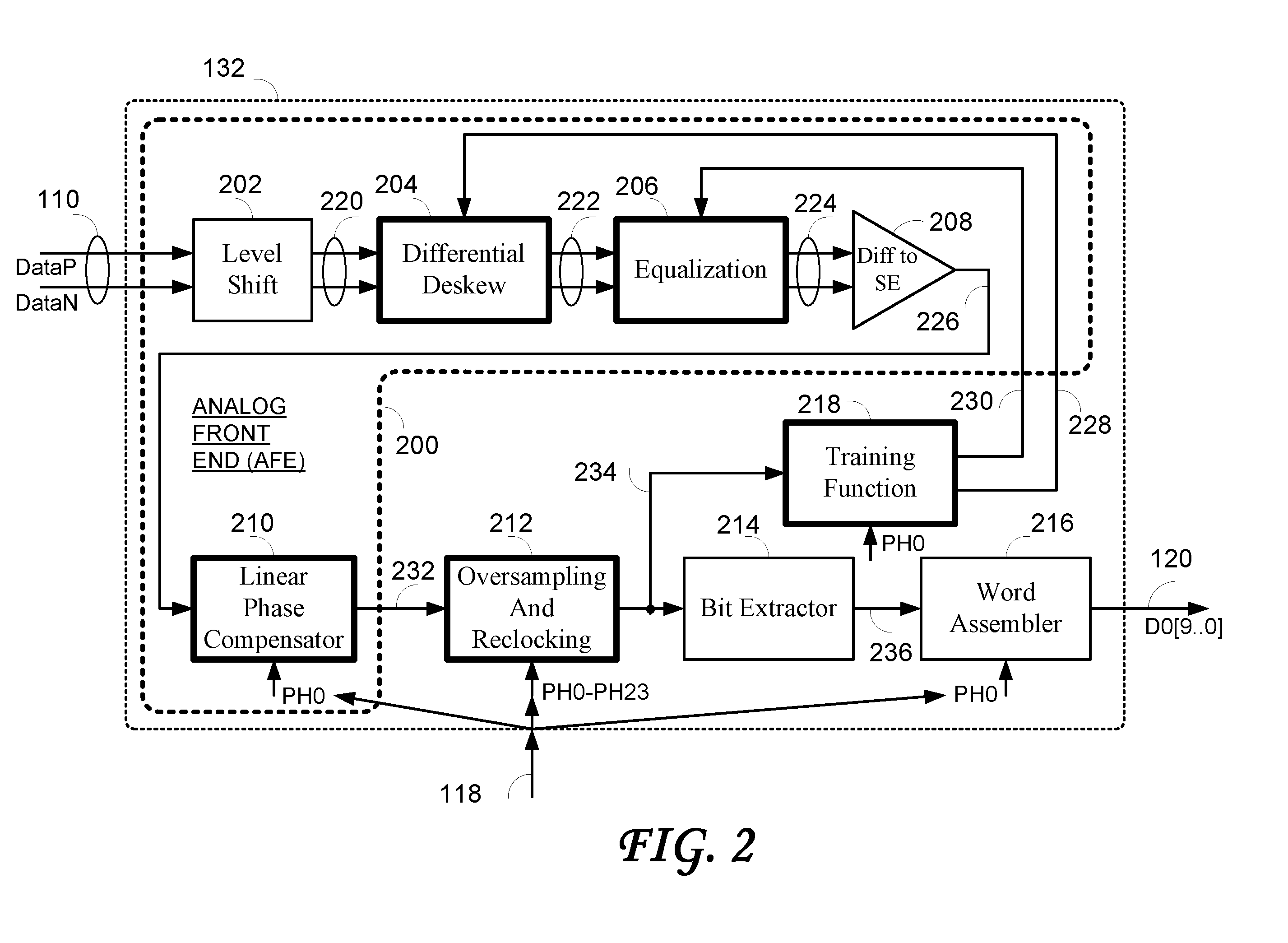

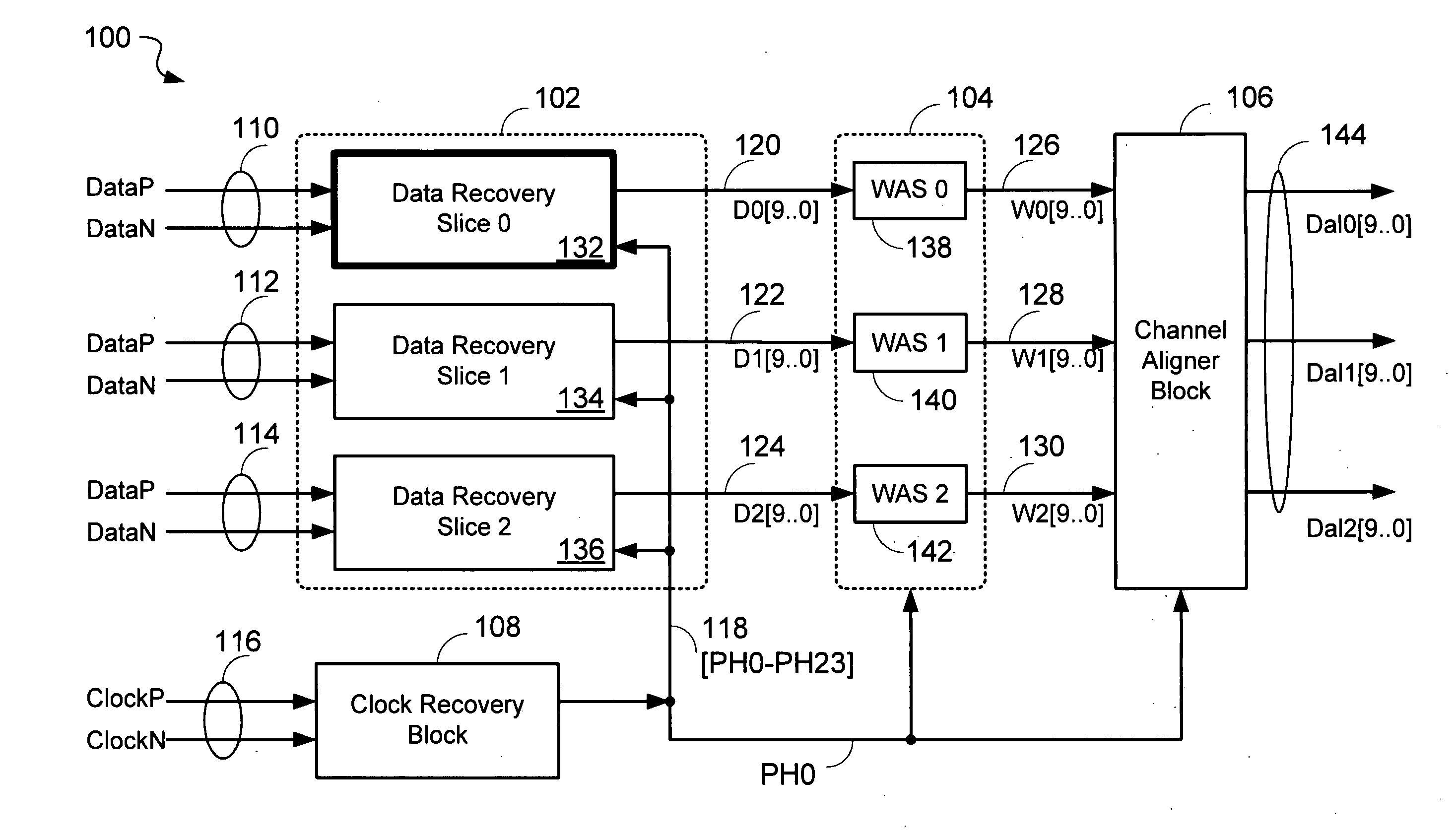

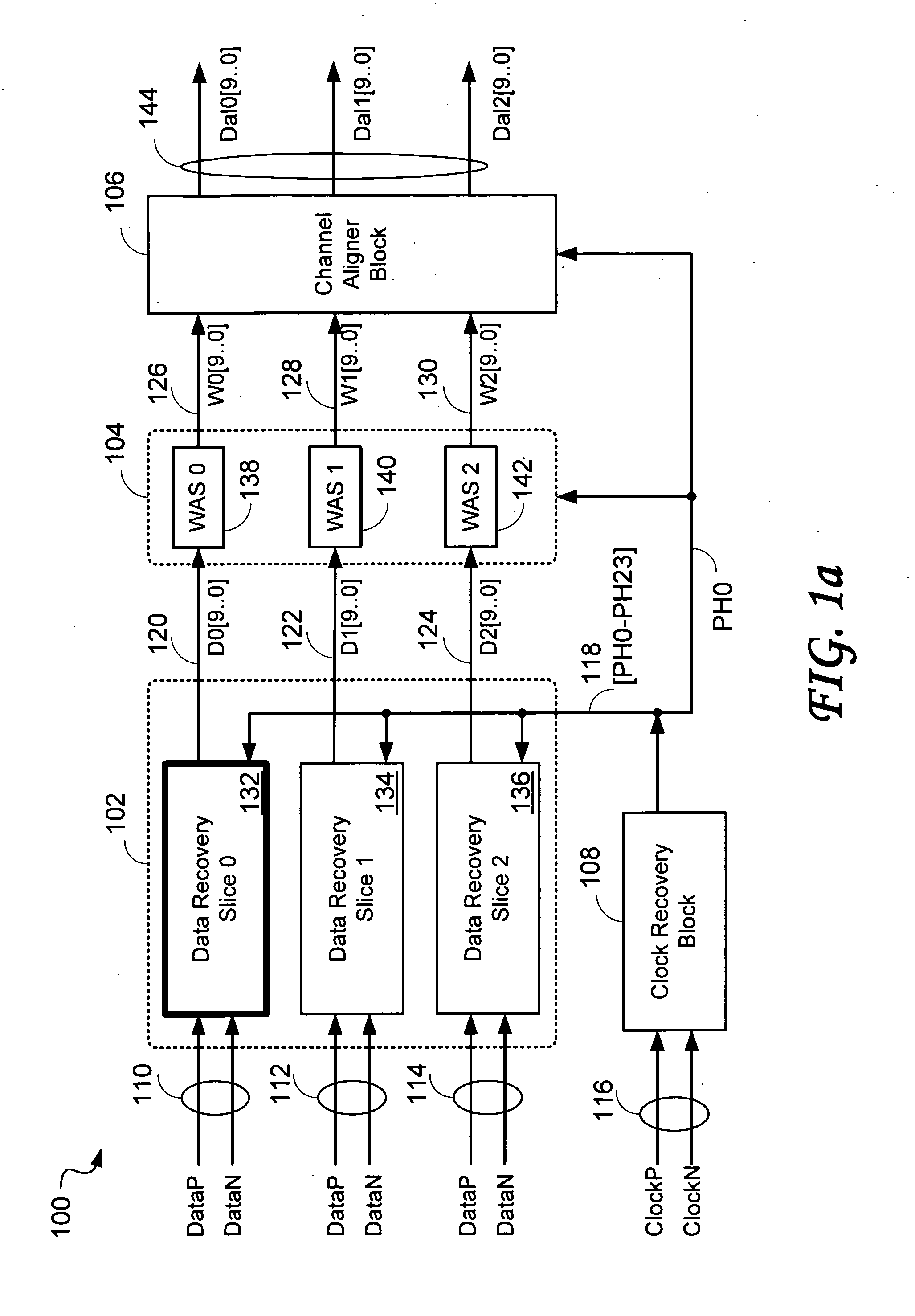

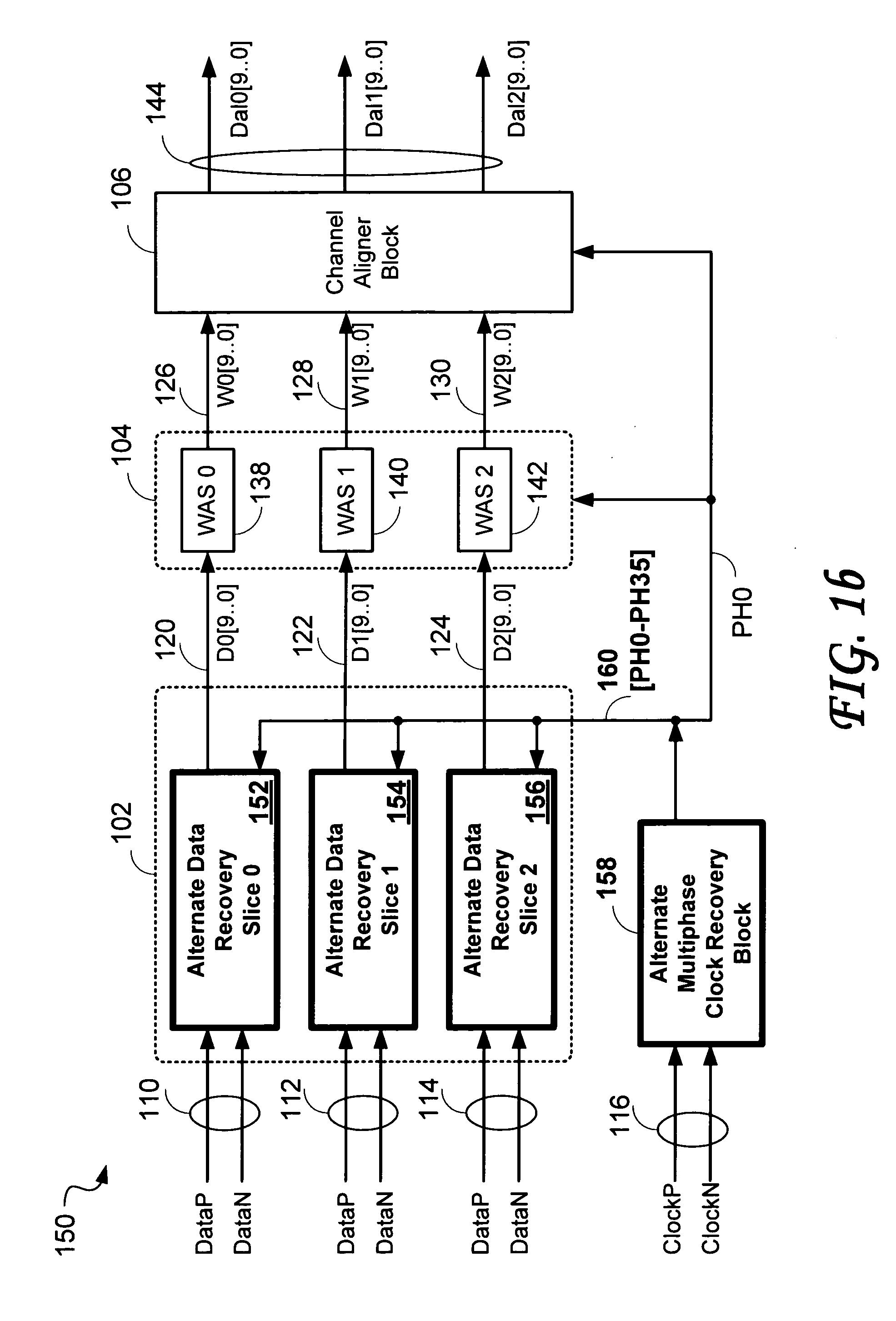

Data recovery system for source synchronous data channels

ActiveUS20070164802A1Easy Data RecoveryReduce distortion problemsModulated-carrier systemsPulse demodulator24-bitAnalog signal

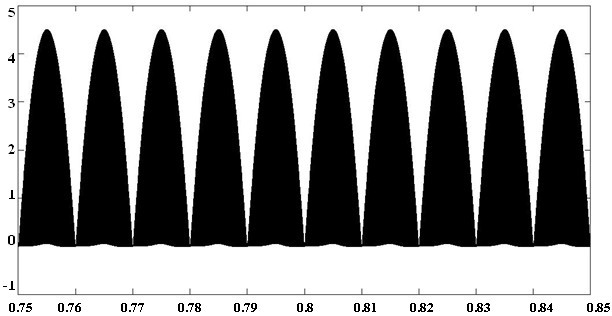

A high-definition multimedia interface (HDMI) receiver recovers high speed encoded data which are transmitted differentially over data channels of a lossy cable, along with a clock. Inter symbol interference, high-frequency loss, skew between the clock and data channels, and differential skew within a differential signal are compensated by analog circuits which are automatically tuned for best performance by observing the quality of the recovered analog signal. Oversampling is used to provide a 24-bit digital representation of the analog signal for determining the quality of the signal. A corresponding method of deskewing a differential signal and a system and circuit therefor are also provided.

Owner:REDMERE TECH

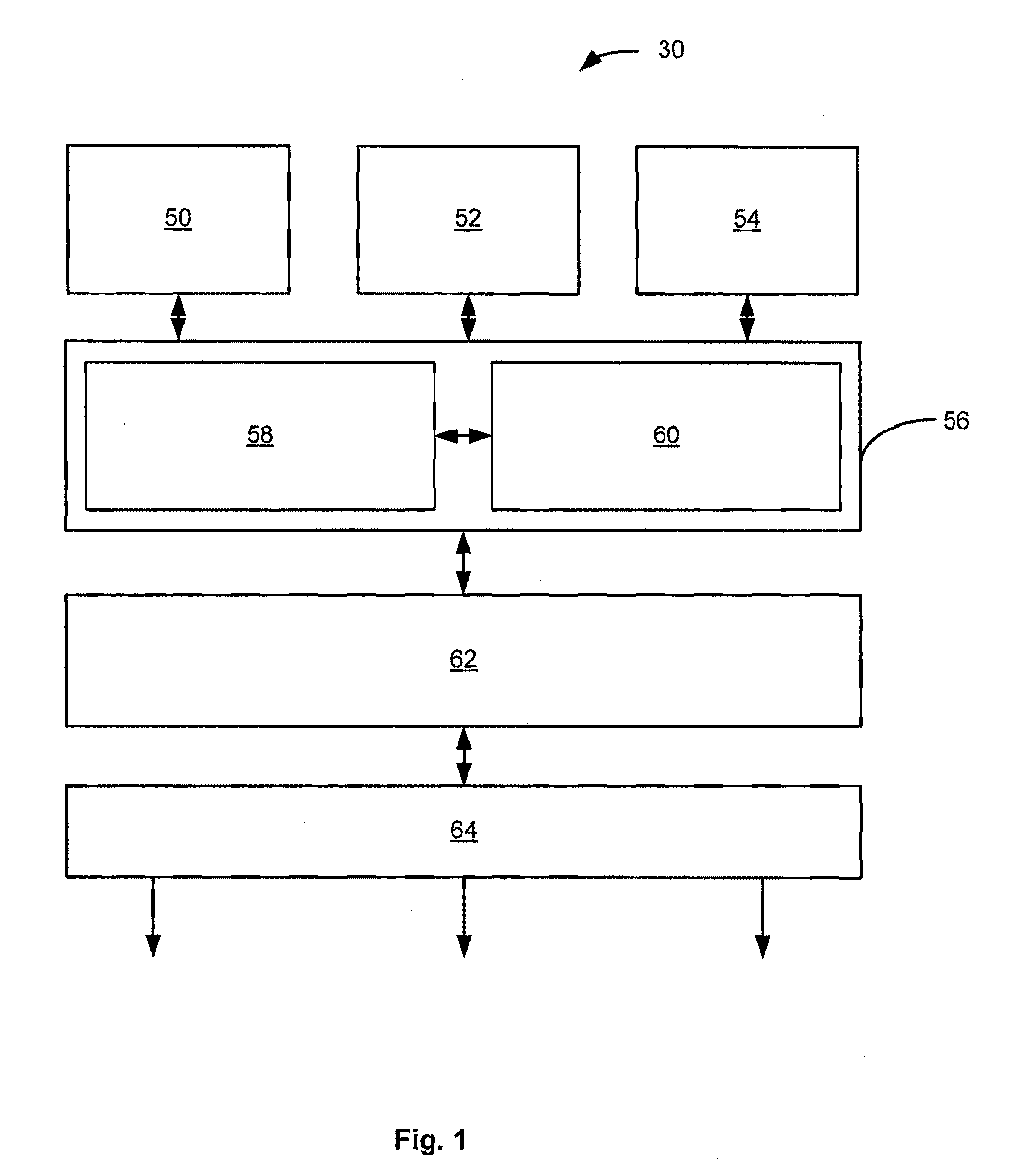

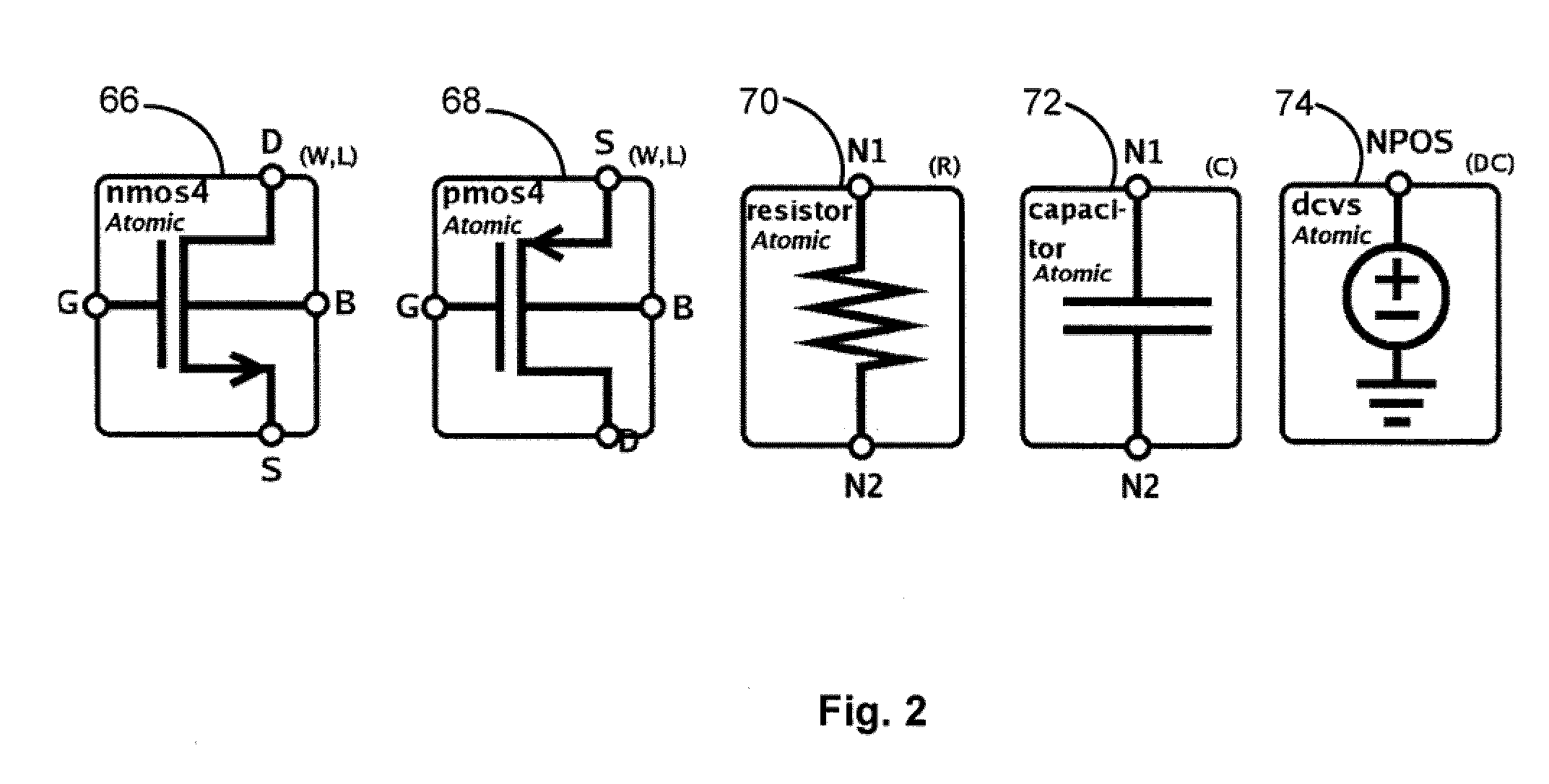

Trustworthy structural synthesis and expert knowledge extraction with application to analog circuit design

ActiveUS20090307638A1Detecting faulty computer hardwareCAD circuit designAnalog circuit designAnalytic model

A system and method that does trustworthy multi-objective structural synthesis of analog circuits, and extracts expert analog circuit knowledge from the resulting tradeoffs. The system defines a space of thousands of possible topologies via a hierarchically organized combination of designer-trusted analog building blocks, the resulting topologies are guaranteed trustworthy. The system can perform a search based on a multi-objective evolutionary algorithm that uses an age-layered population structure to balance exploration vs. exploitation, with operators that make the search space a hybrid between vector-based and tree-based representations. A scheme employing average ranking on Pareto fronts is used to handle a high number of objectives. Good initial topology sizings are quickly generated via multi-gate constraint satisfaction. To explicitly capture expert analog design knowledge, data mining is employed on the sized circuits to: automatically generate a decision tree for navigating from performance specifications to topology choice, to do global nonlinear sensitivity analysis, and to generate analytical models of performance tradeoffs.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

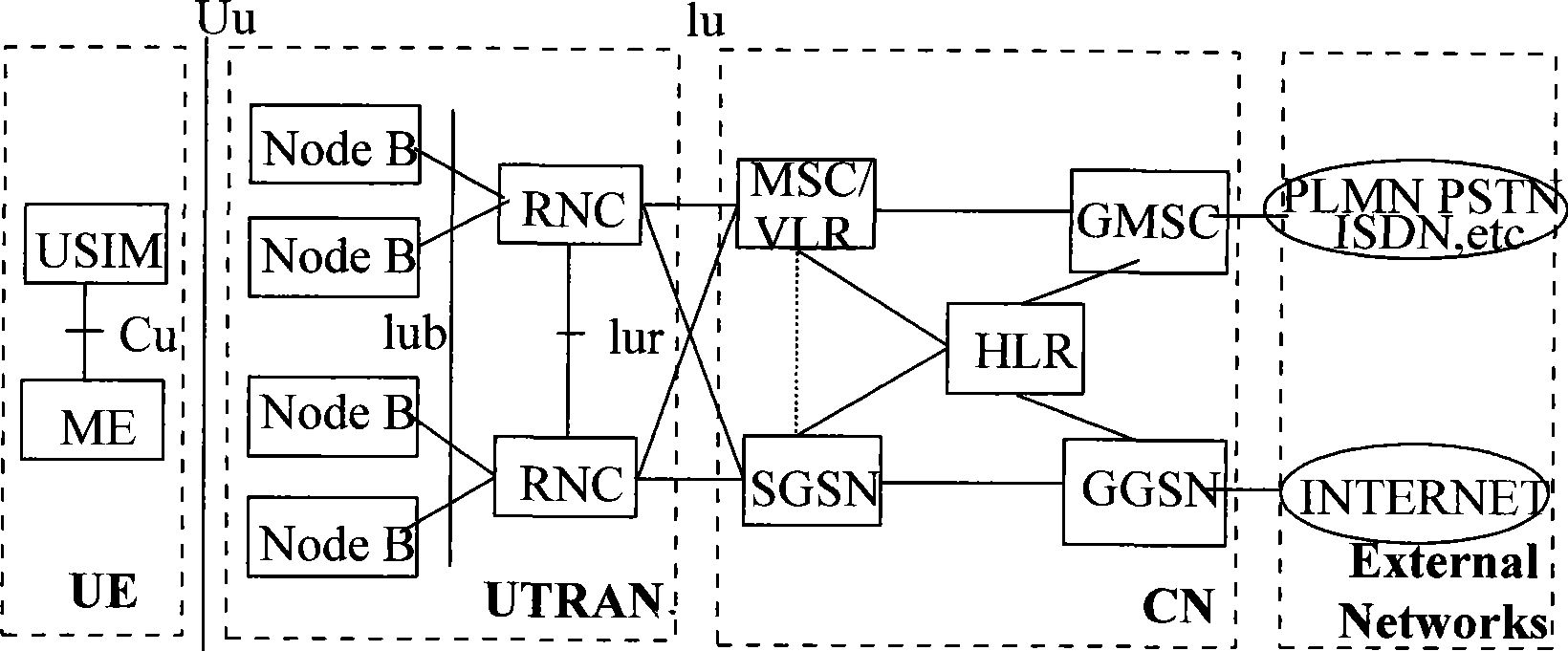

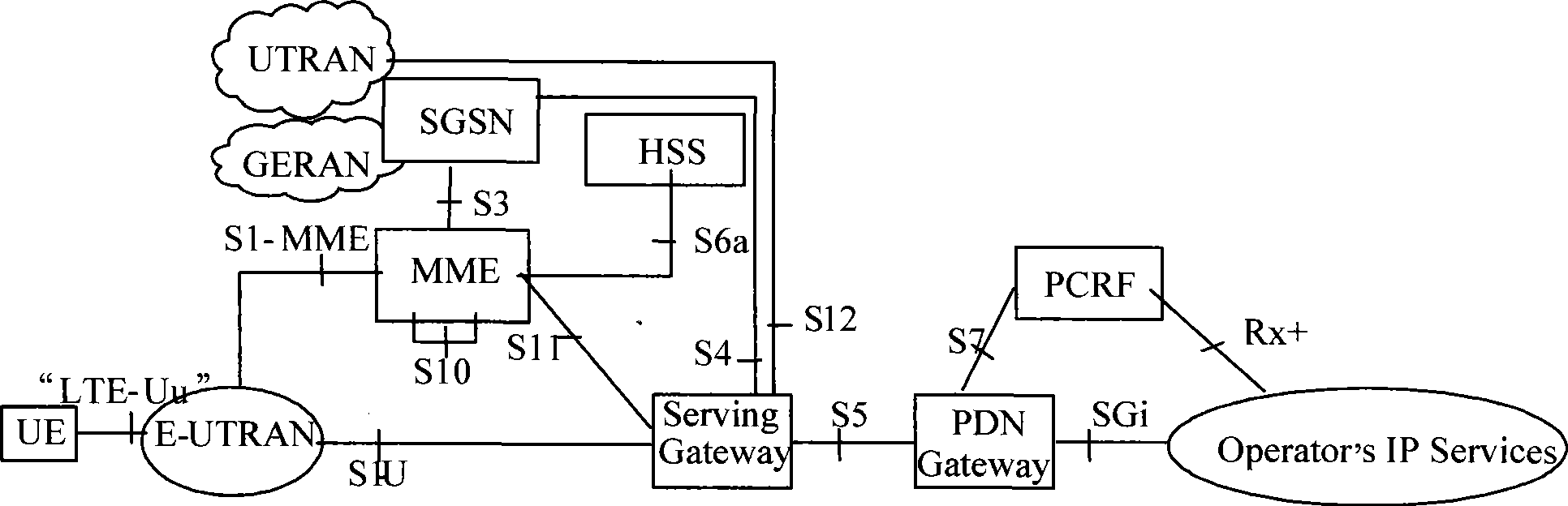

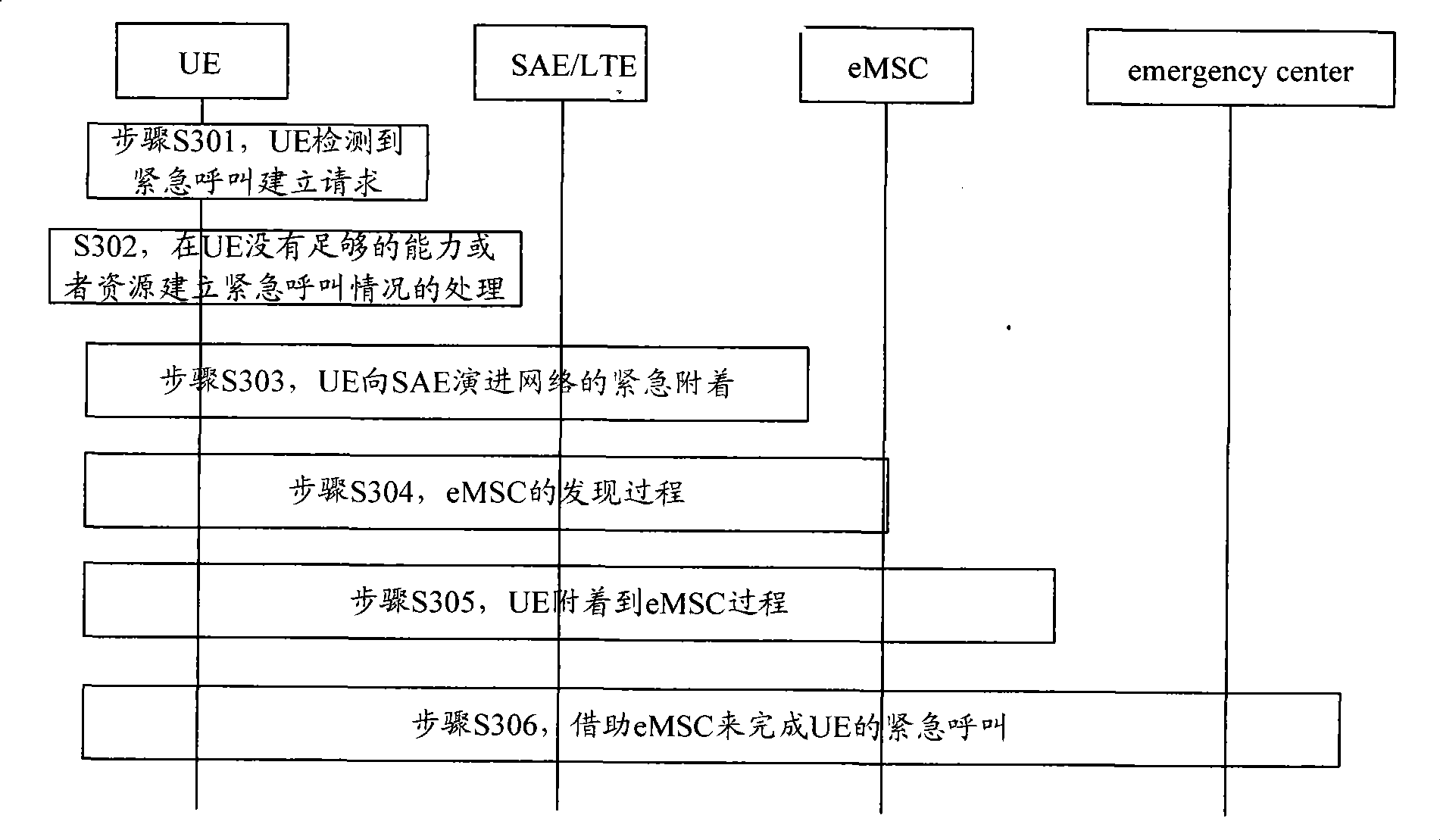

Emergency call method and apparatus

ActiveCN101466083AEmergency connection handlingConnection managementTelecommunicationsUser equipment

The invention discloses an emergency call method, which particularly includes that: user equipment (UE) can send an emergency attachment request to an SAE network in evolution network; the emergency attachment request includes an emergency indication; the SAE network receives the emergency indication, and then selects an emergency call service entity for the UE; the UE can send out an emergency call request to the emergency call service entity after being emergently attached onto the SAE network; the emergency call service entity can establish the emergency voice carrying; and the UE can execute the emergency call according to the established emergency voice carrying. The embodiment of the invention provides the method which can finish the emergency call of the analogue circuit area with the help of the emergency call service entity in the evolution network, so as to realize the emergence call service in the SAE / LTE packet networks.

Owner:HUAWEI TECH CO LTD

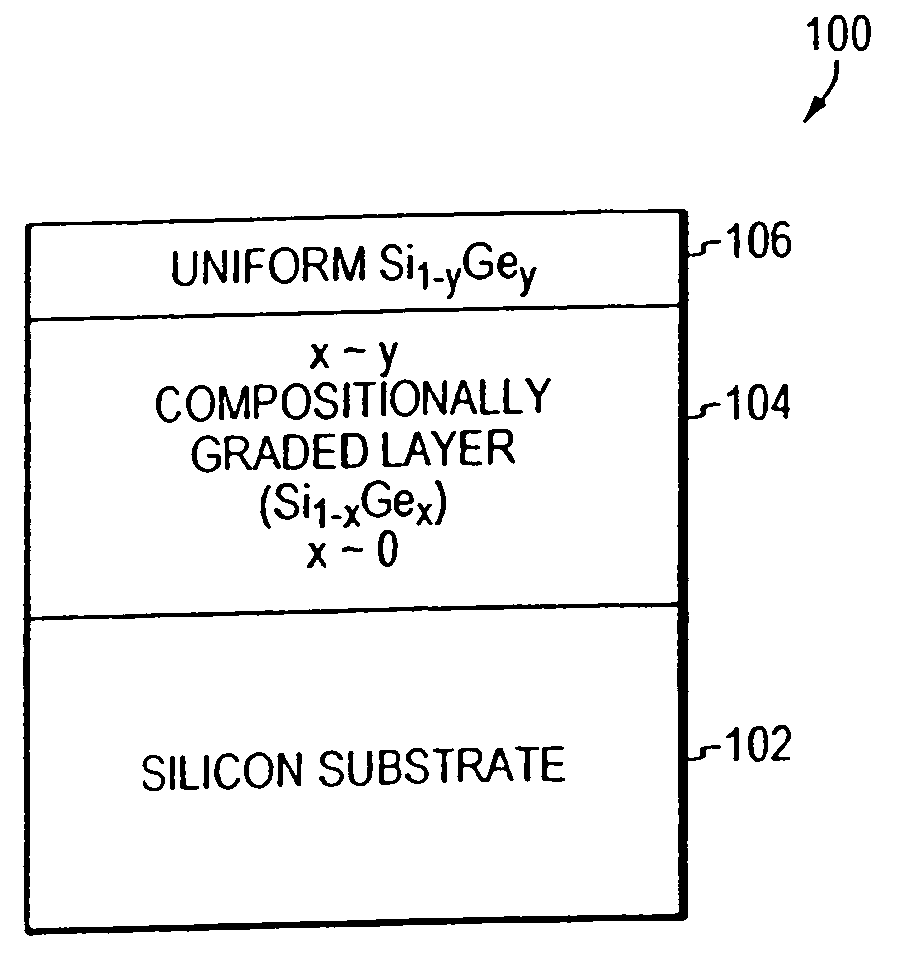

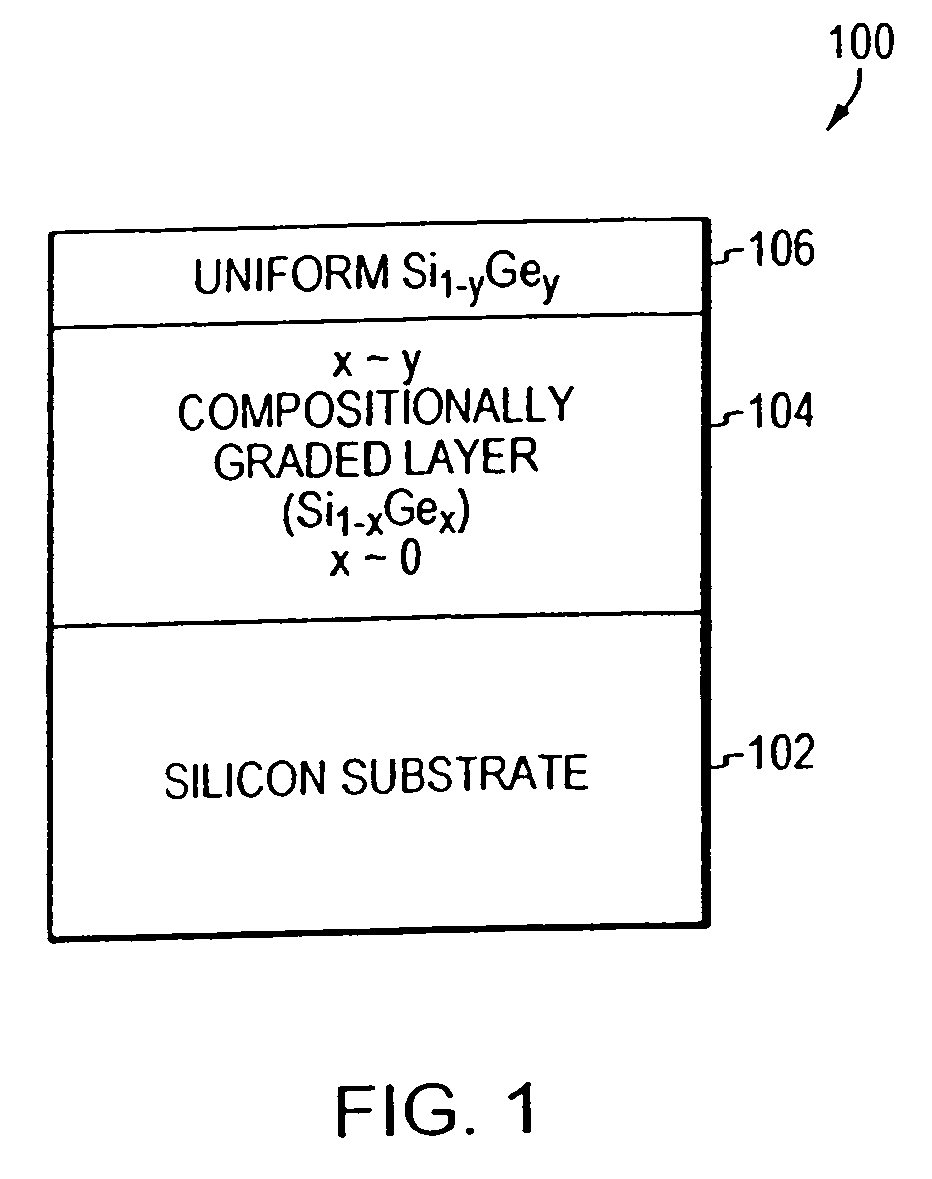

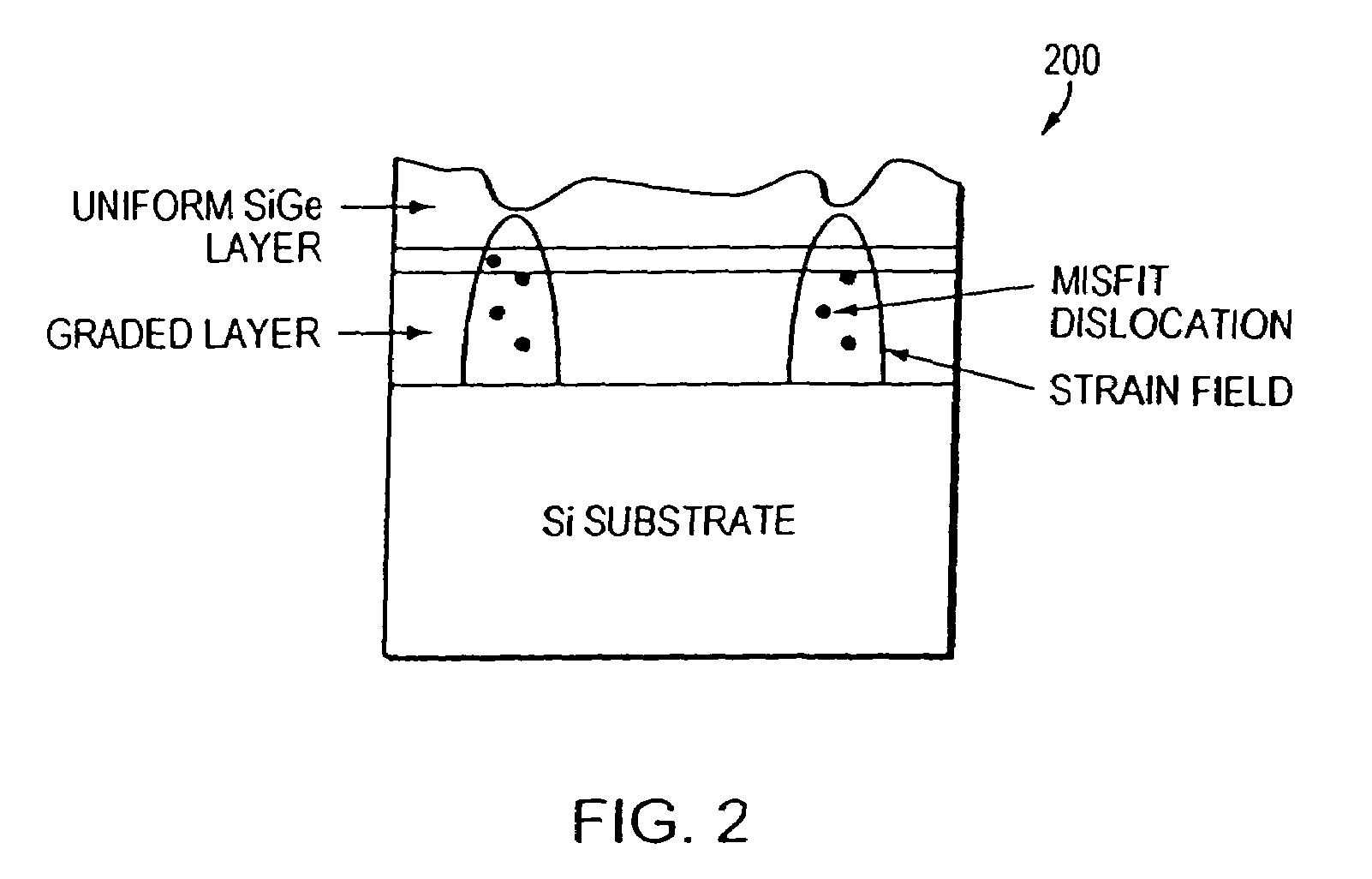

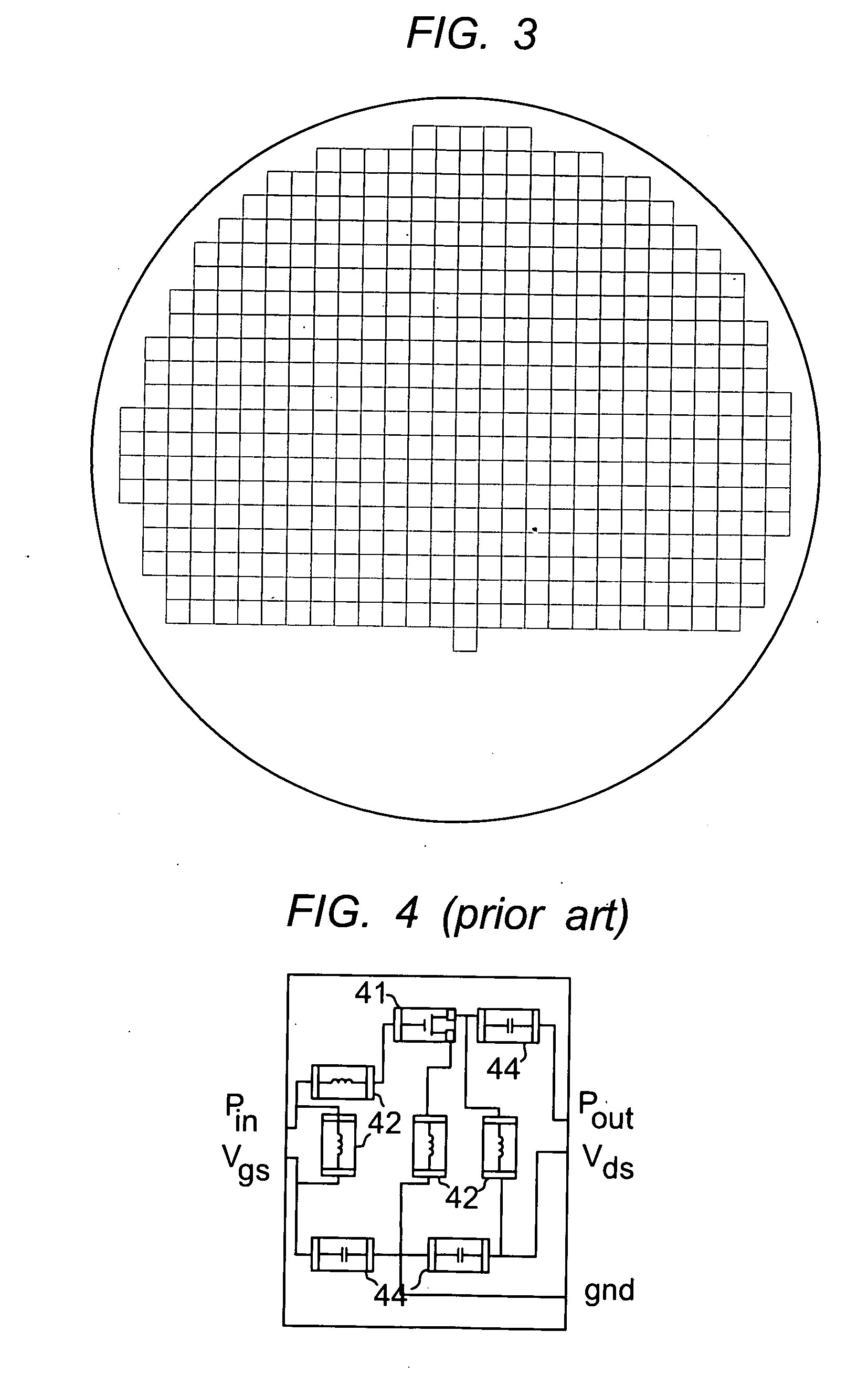

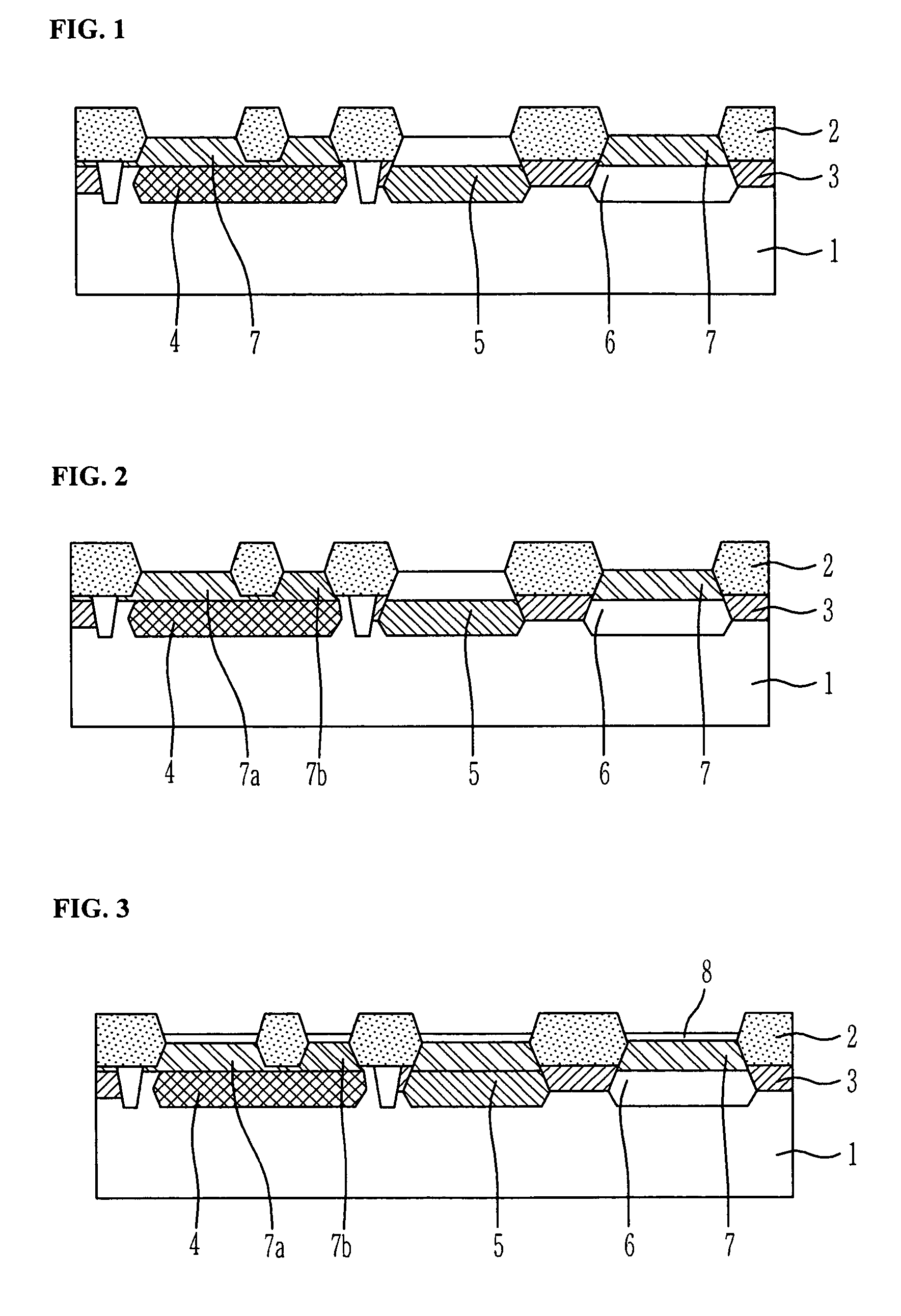

Relaxed SiGe platform for high speed CMOS electronics and high speed analog circuits

InactiveUS7256142B2Minimal surface roughnessImprove featuresTransistorSemiconductor/solid-state device manufacturingMOSFETCmos electronics

Structures and methods for fabricating high speed digital, analog, and combined digital / analog systems using planarized relaxed SiGe as the materials platform. The relaxed SiGe allows for a plethora of strained Si layers that possess enhanced electronic properties. By allowing the MOSFET channel to be either at the surface or buried, one can create high-speed digital and / or analog circuits. The planarization before the device epitaxial layers are deposited ensures a flat surface for state-of-the-art lithography.

Owner:TAIWAN SEMICON MFG CO LTD

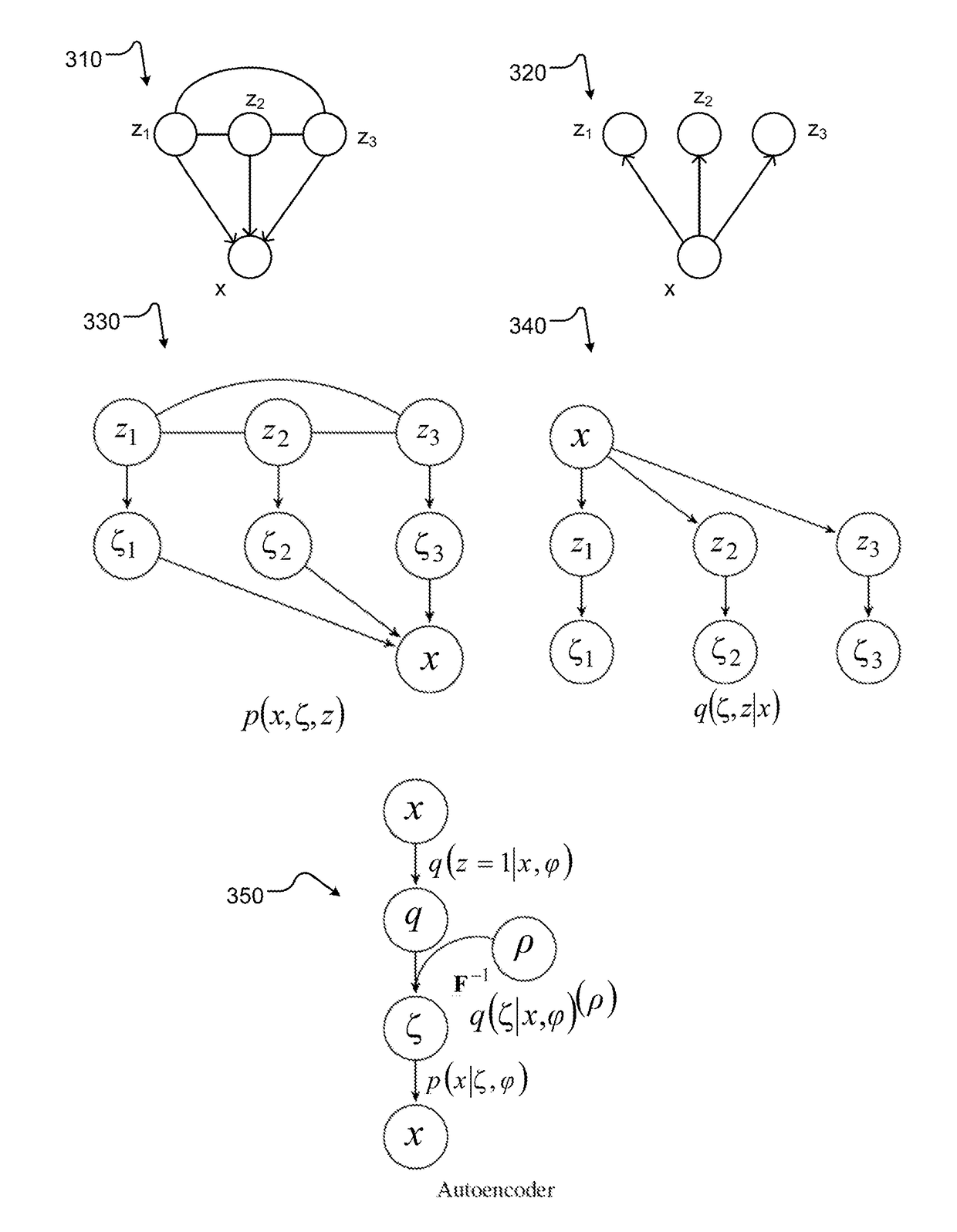

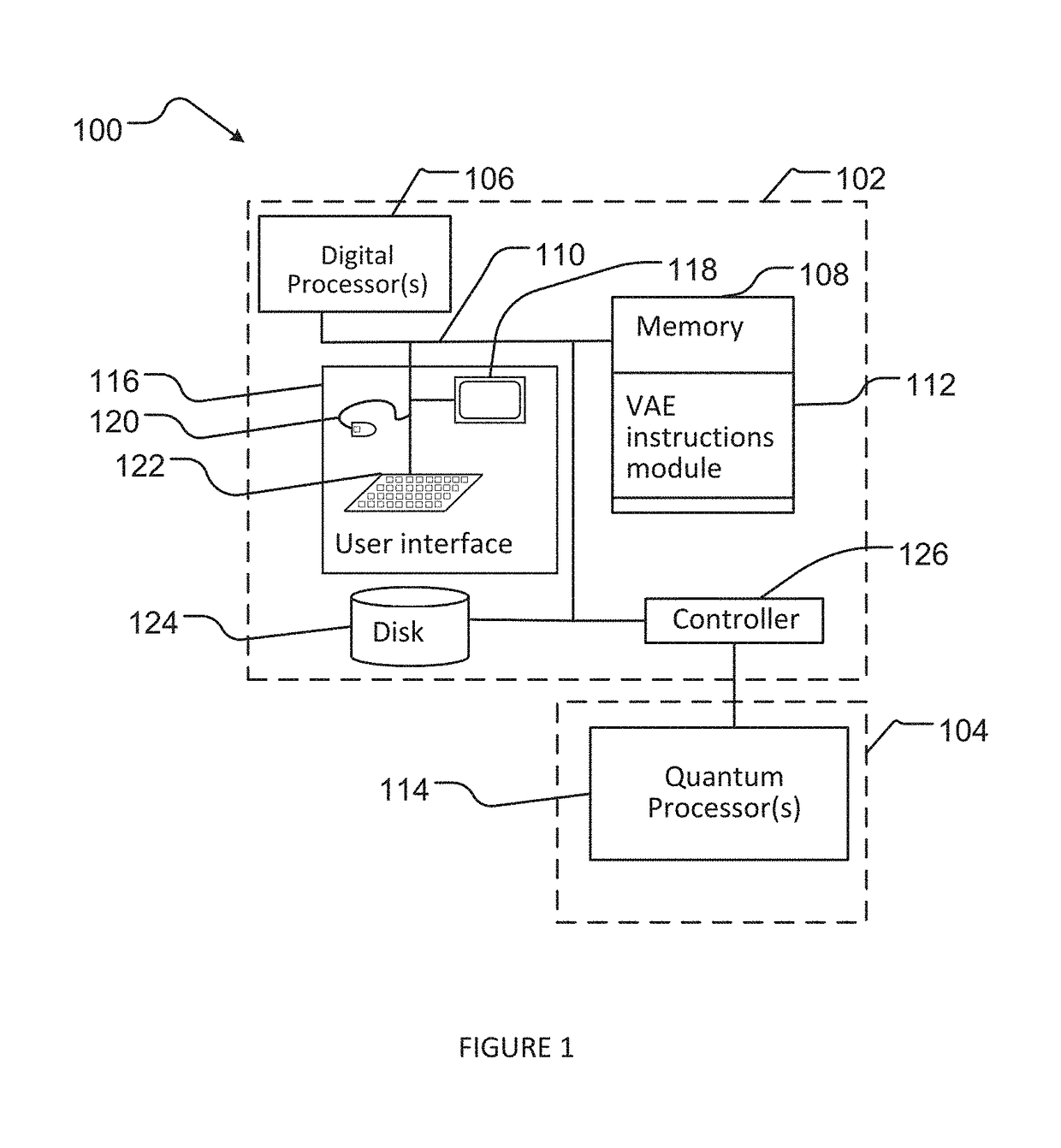

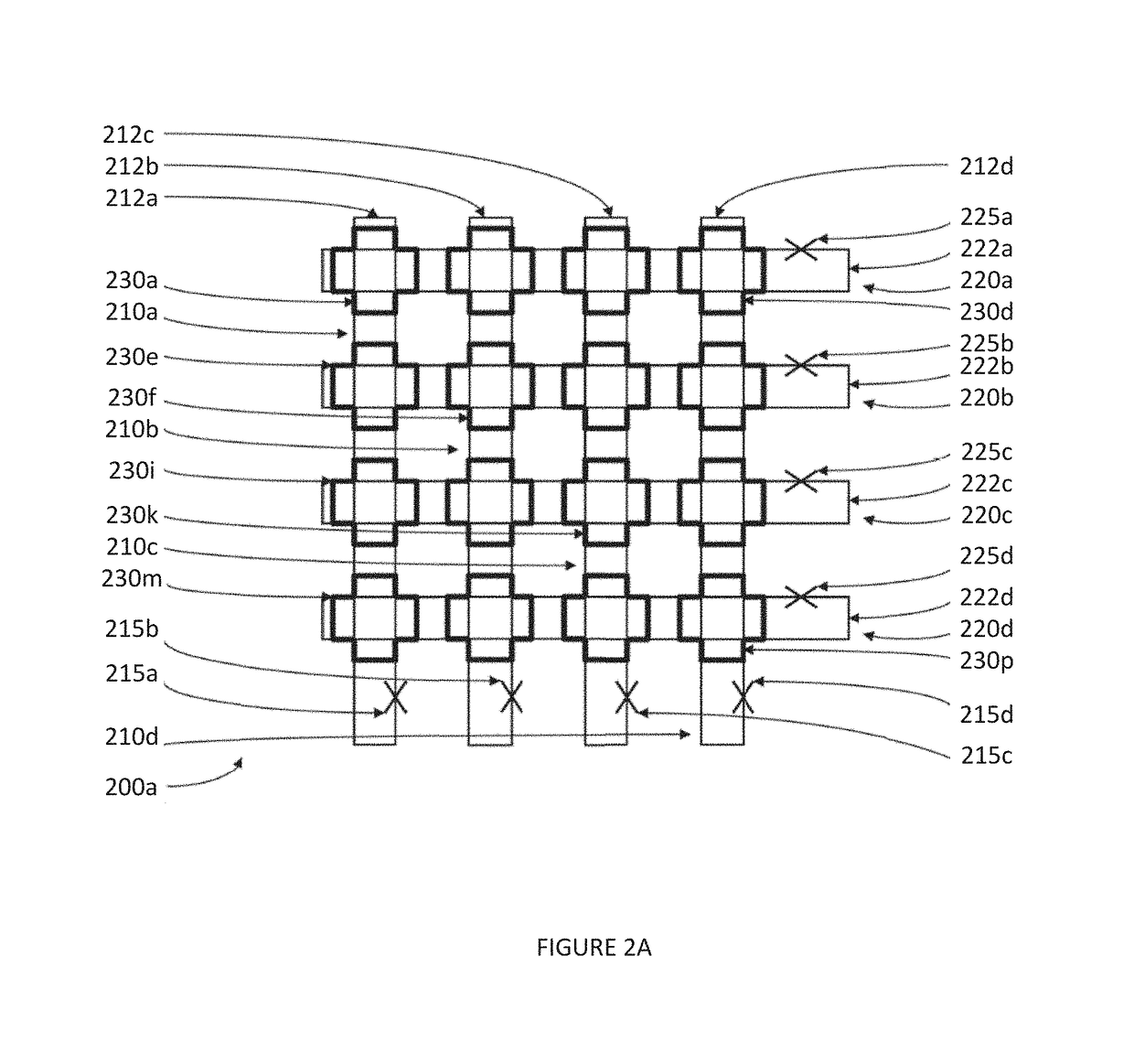

Discrete variational auto-encoder systems and methods for machine learning using adiabatic quantum computers

A computational system can include digital circuitry and analog circuitry, for instance a digital processor and a quantum processor. The quantum processor can operate as a sample generator providing samples. Samples can be employed by the digital processing in implementing various machine learning techniques. For example, the computational system can perform unsupervised learning over an input space, for example via a discrete variational auto-encoder, and attempting to maximize the log-likelihood of an observed dataset. Maximizing the log-likelihood of the observed dataset can include generating a hierarchical approximating posterior. Unsupervised learning can include generating samples of a prior distribution using the quantum processor. Generating samples using the quantum processor can include forming chains of qubits and representing discrete variables by chains.

Owner:D WAVE SYSTEMS INC

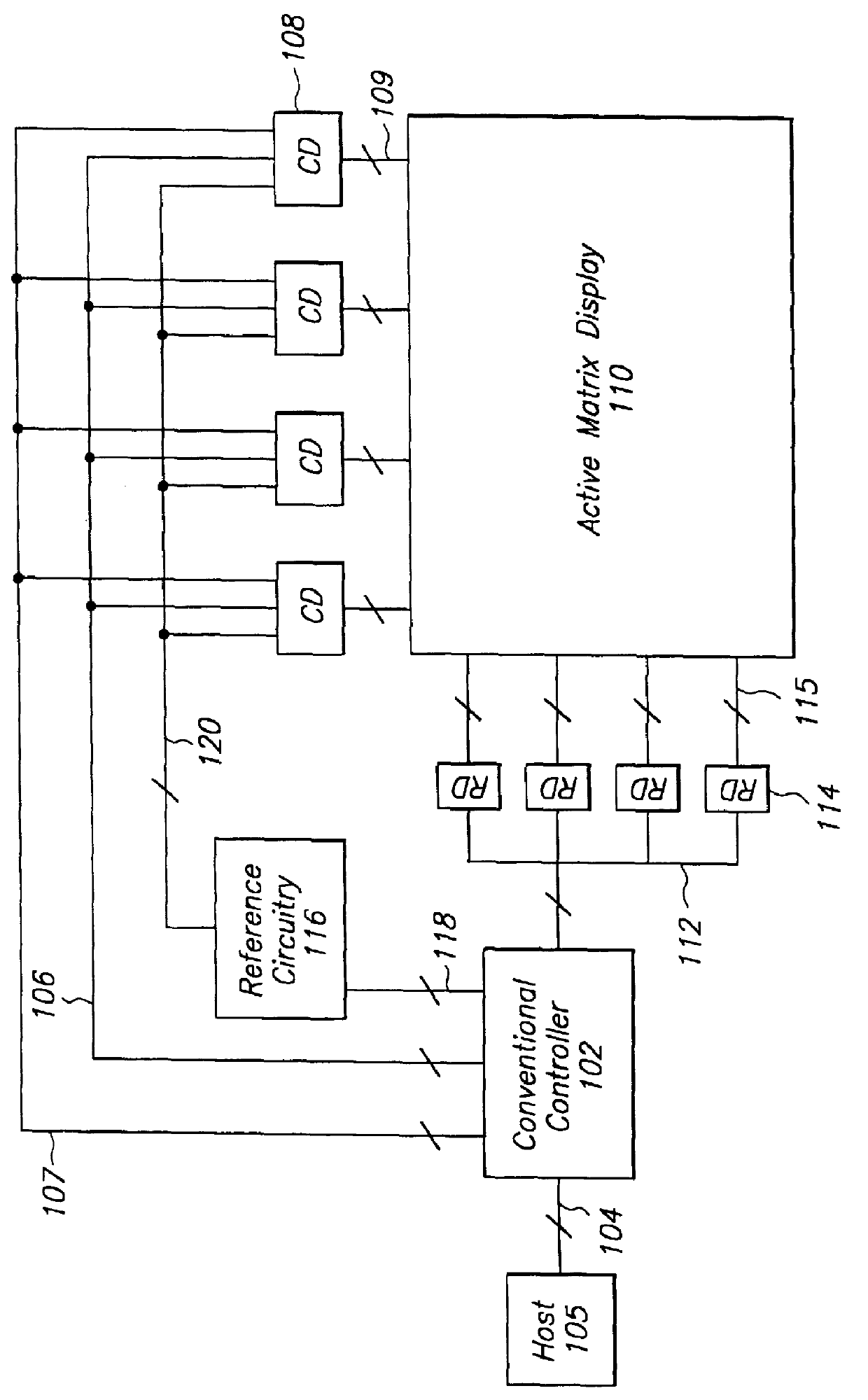

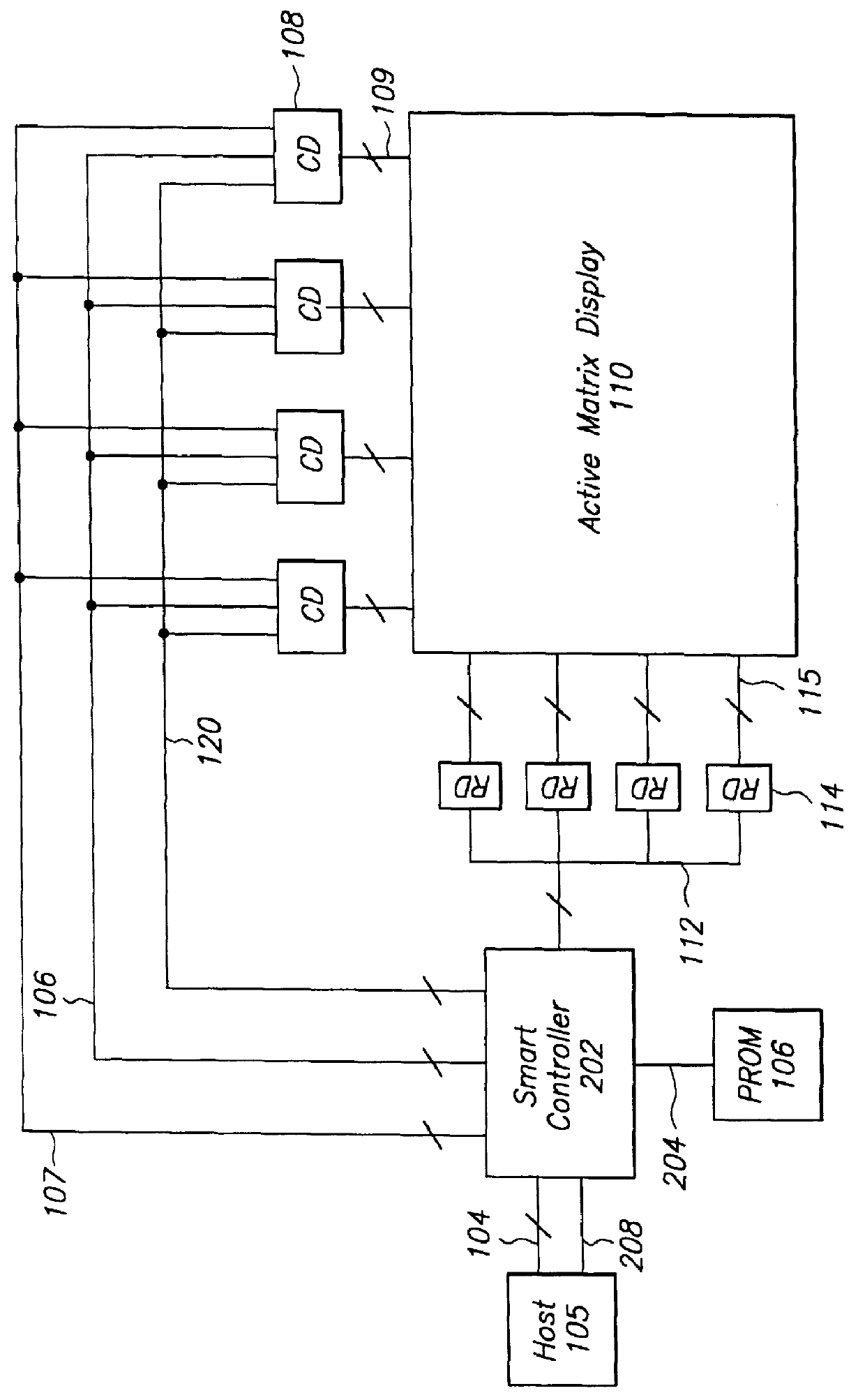

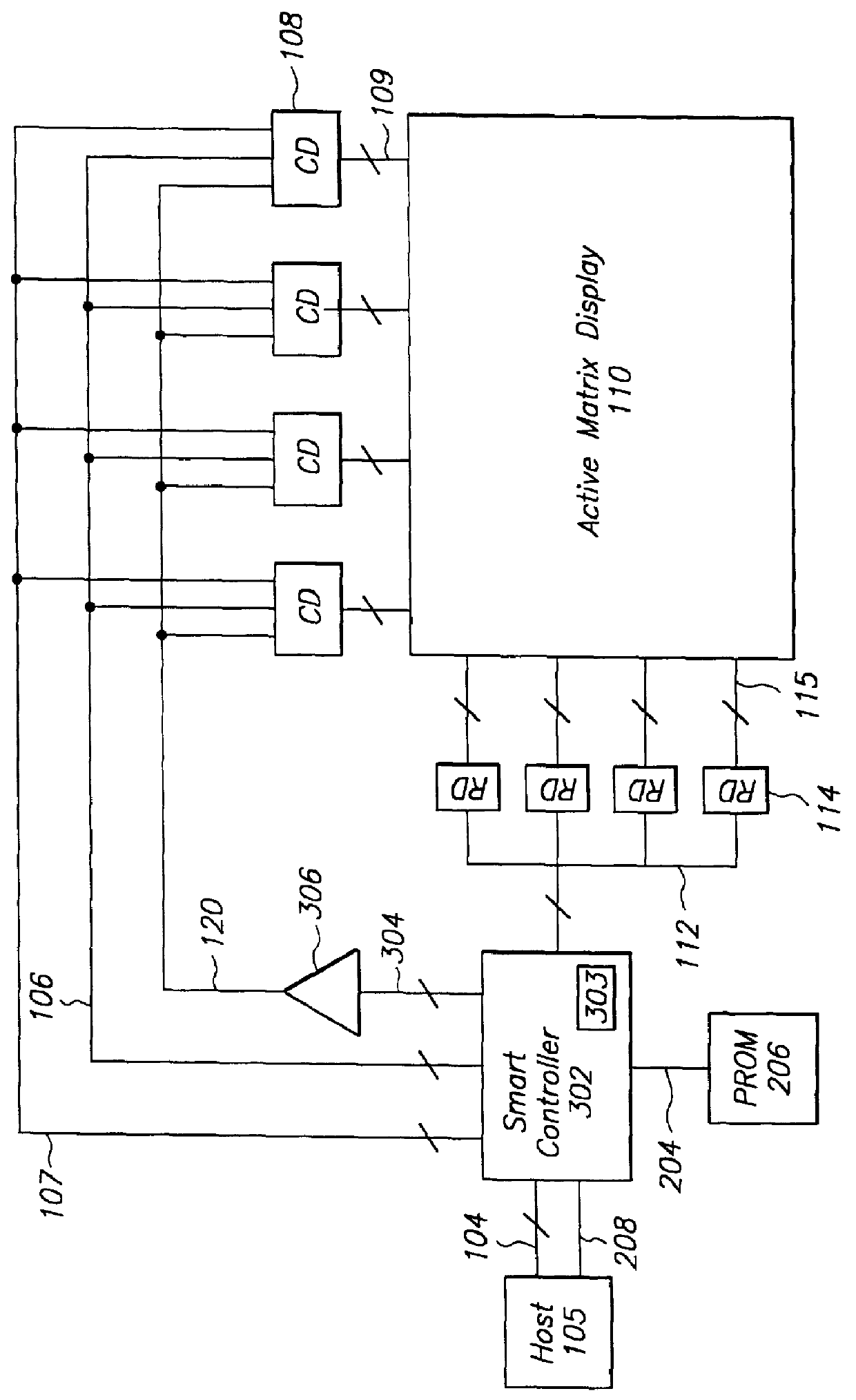

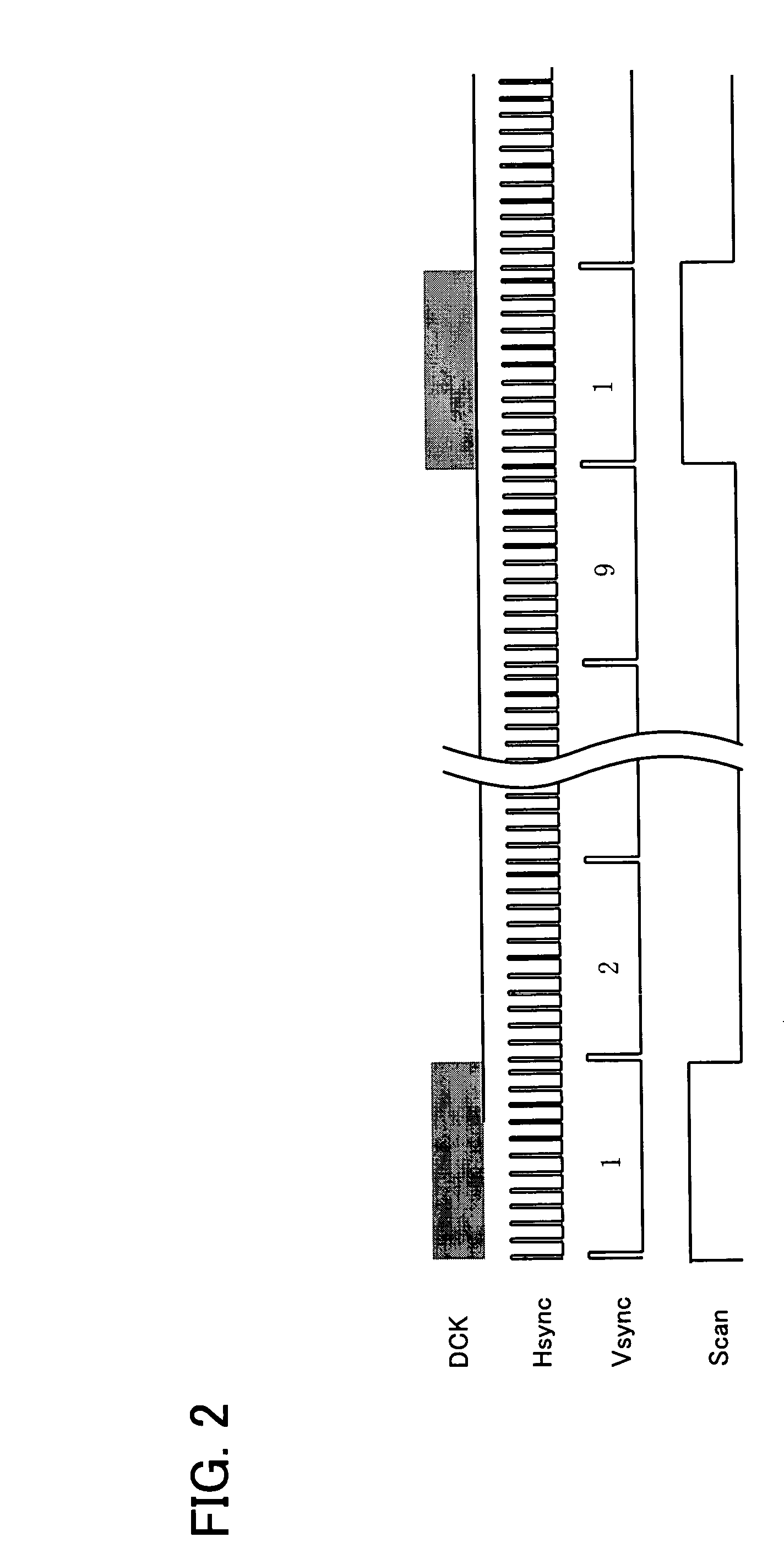

System and method for controlling an active matrix display

InactiveUS6100879AReduce complexityCathode-ray tube indicatorsInput/output processes for data processingActive matrixProcessor register

A smart controller chip for controlling an active matrix display. Within the controller chip, circuitry for generating analog reference levels is incorporated alongside circuitry for generating digital timing and control signals. The combination of D / A analog circuitry and standard digital logic makes the controller uniquely suited for addressing all the panel control needs both for the normal digital functions but also for control of the analog aspects of the panel, like display gamma. The analog reference levels and the digital signals are made programmable using registers internal to the controller chip. The contents of these registers are programmed initially by digital values stored in an external PROM or in flash memory integrated into the controller chip. In addition, software in a host system is able to program these registers via an interface between the host system and the controller chip.

Owner:SUPER INTERCONNECT TECH

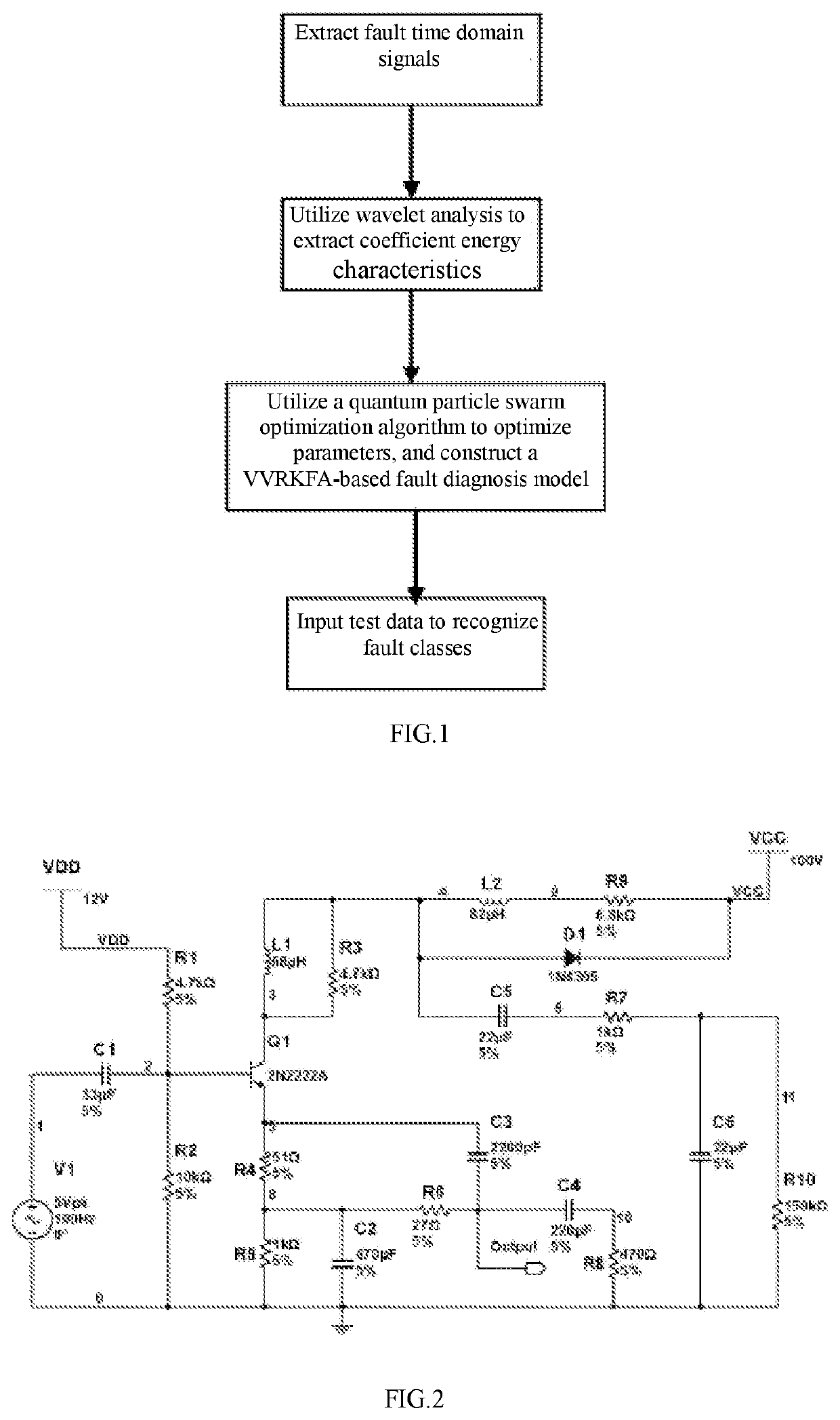

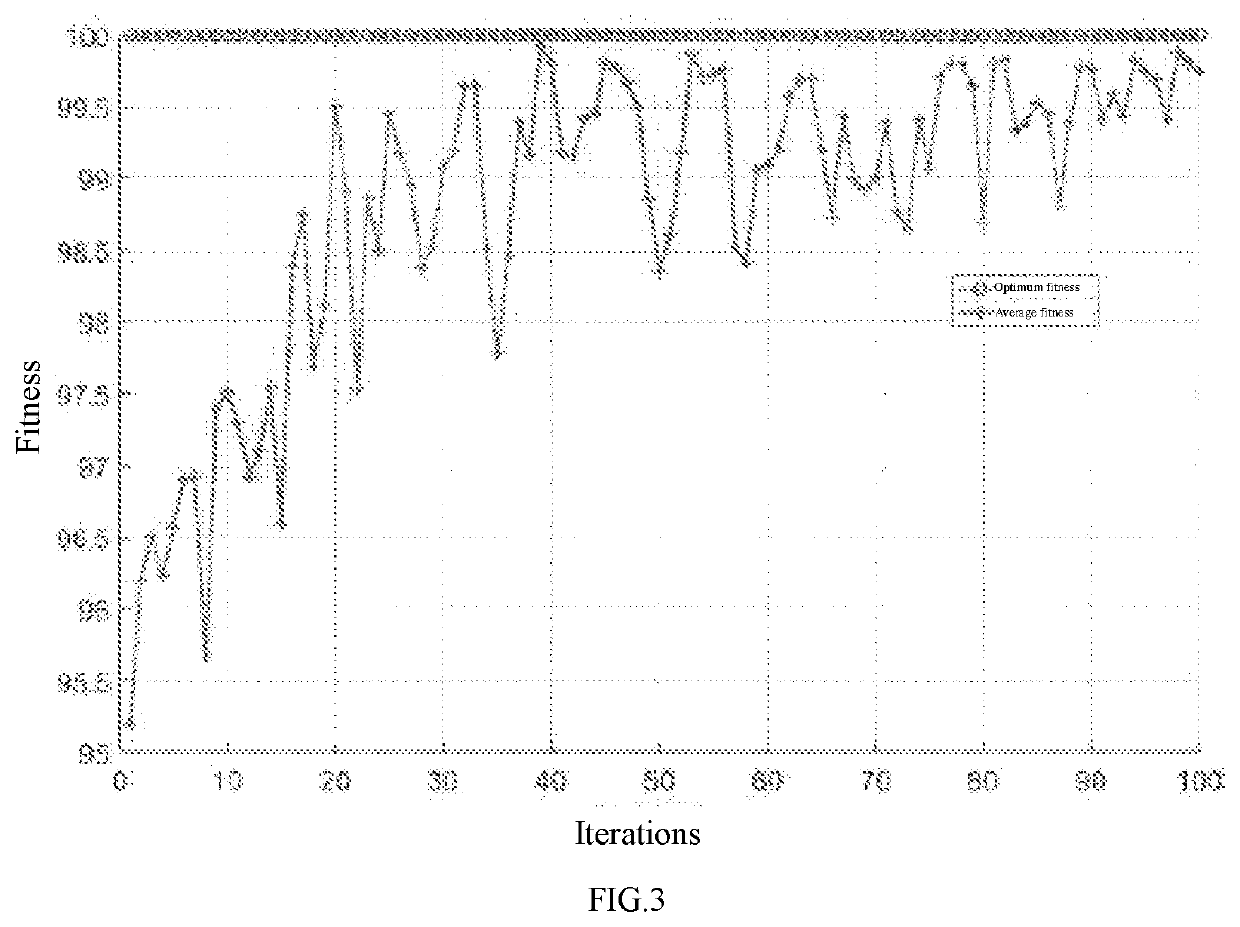

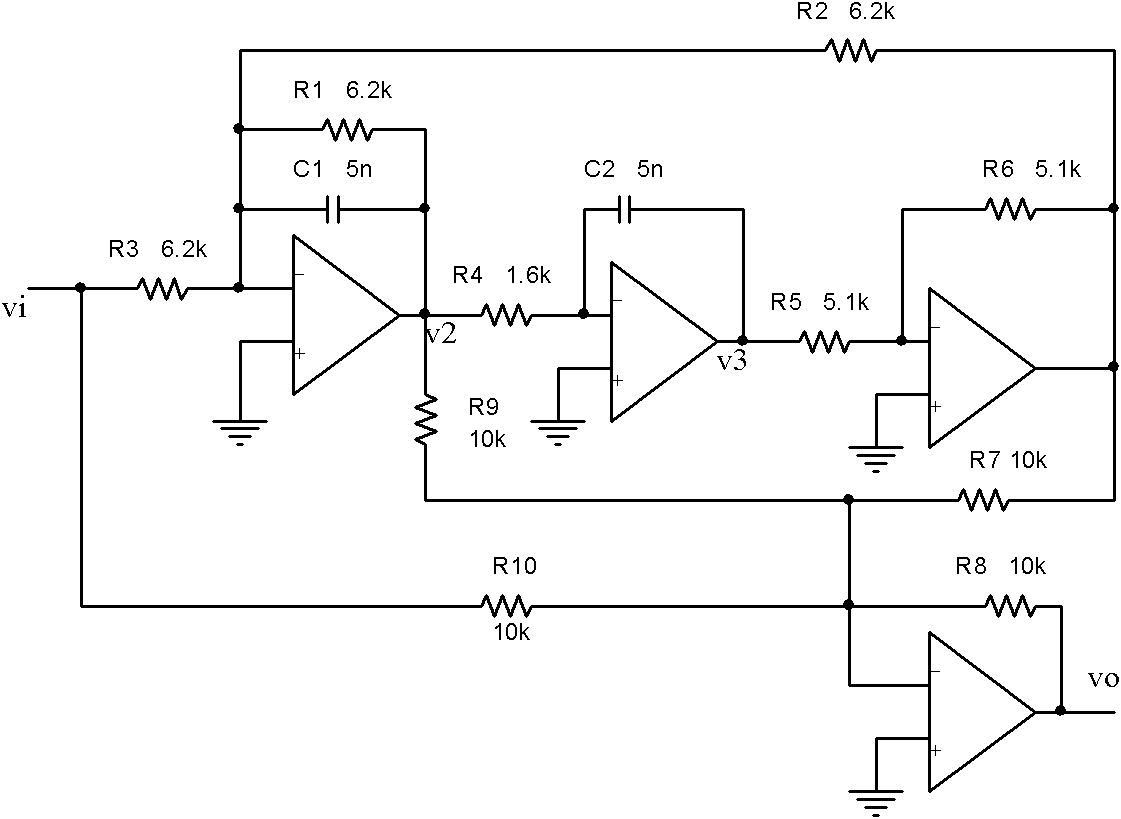

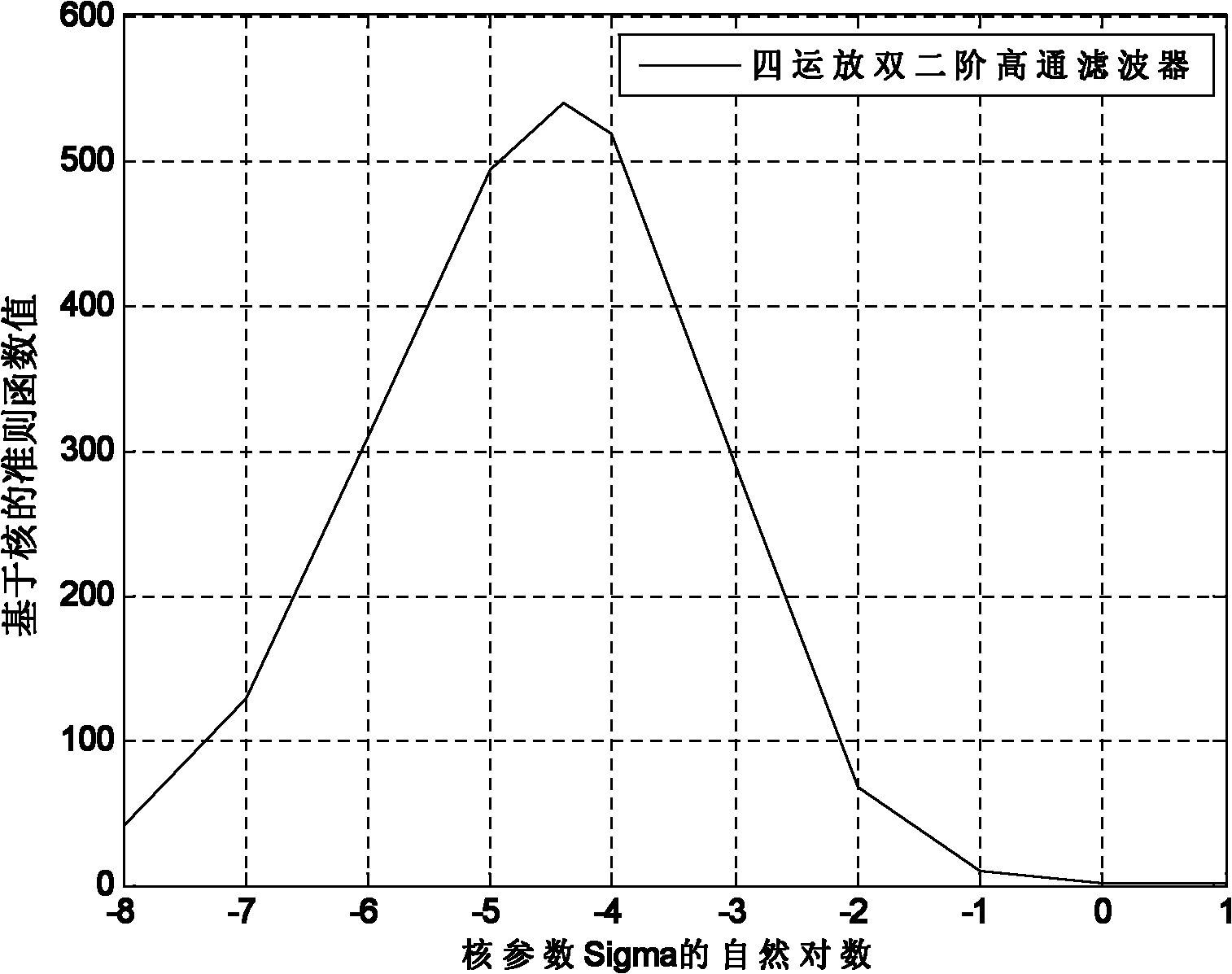

Method for diagnosing analog circuit fault based on vector-valued regularized kernel function approximation

ActiveUS20200271720A1Improve accuracyIncrease speedKernel methodsElectrical testingAlgorithmWavelet packet transformation

A method for diagnosing analog circuit fault based on vector-valued regularized kernel function approximation, includes steps of: step (1) acquiring a fault response voltage signal of an analog circuit; step (2) carrying out wavelet packet transform on the collected signal, and calculating a wavelet packet coefficient energy value as a characteristic parameter; step (3) utilizing a quantum particle swarm optimization algorithm to optimize a regularization parameter and kernel parameter of vector-valued regularized kernel function approximation, and training a fault diagnosis model; and step (4) utilizing the trained diagnosis model to recognize circuit faults.

Owner:HEFEI UNIV OF TECH

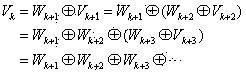

Novel analog circuit early fault diagnosis method

InactiveCN104198924AFacilitates early fault diagnosisImprove feature extractionAnalog circuit testingSpecial data processing applicationsFeature vectorLeast squares support vector machine

A novel analog circuit early fault diagnosis method includes the steps of (1) acquiring time domain response signals of an analog circuit and taking the time domain response signals as output voltage signals of the analog circuit; (2) performing wavelet transform to the acquired voltage signals; (3) performing fractal analysis to original signal patterns and wavelet sub patterns to generate wavelet fractal dimensions of different patterns; (4) performing kernel entropy component analysis to candidate feature vector data composed of the wavelet fractal dimensions to acquire low-dimension feature vector data; (5) creating a multi-class classifier of a least squares support vector machine, and optimally selecting penalty factor and width factor of the least squares support vector machine, which are used for distinguishing overlapped early fault categories, by a quantum-behaved particle swarm optimization algorithm; and (6) sending the low-dimension feature vector data into the multi-class classifier of the least squares support vector machine and then outputting early fault diagnosis results. The novel analog circuit early fault diagnosis method can effectively detect early faults of analog circuits.

Owner:HEFEI UNIV OF TECH

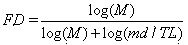

PFC (power factor correction) control method with high input power factor and control circuit thereof

ActiveCN101986542AEasy to implementSmall rippleEfficient power electronics conversionPower conversion systemsCapacitanceActive power factor correction

The invention provides a PFC (power factor correction) control method with high input power factor and a control circuit thereof. The method comprises the steps of controlling a switching tube to be switched on and switched off according to the principle of leading impulse area to be equivalent, and leading input inductive current and sinusoidal half-wave current to have the equivalent impulse area in each switching period, thereby realizing the high power factor (PF); furthermore, the higher the switching frequency, the closer to 1 the PF value is. In the control circuit, a circuit topological structure of a Boost converter and a control circuit for realizing a variable duty ratio sequence jointly constitute a PFC stage of a commonly used LED (light-emitting diode) driving power supply, the front stage of the PFC stage is connected with the output end of a non-controllable rectifier bridge of a single-phase diode via an input filter capacitor, the back stage of the PFC stage is connected with a DC / DC (direct current / direct current) stage of the commonly used LED driving power supply via an output filter inductor and an output filter capacitor. By adopting the PFC control method, not only the very high input power factor can be realized, but also output voltage ripple can be reduced; furthermore, the control circuit is simple and easy to realize an analog circuit, thereby being conductive to large-scale integration.

Owner:SOUTH CHINA UNIV OF TECH

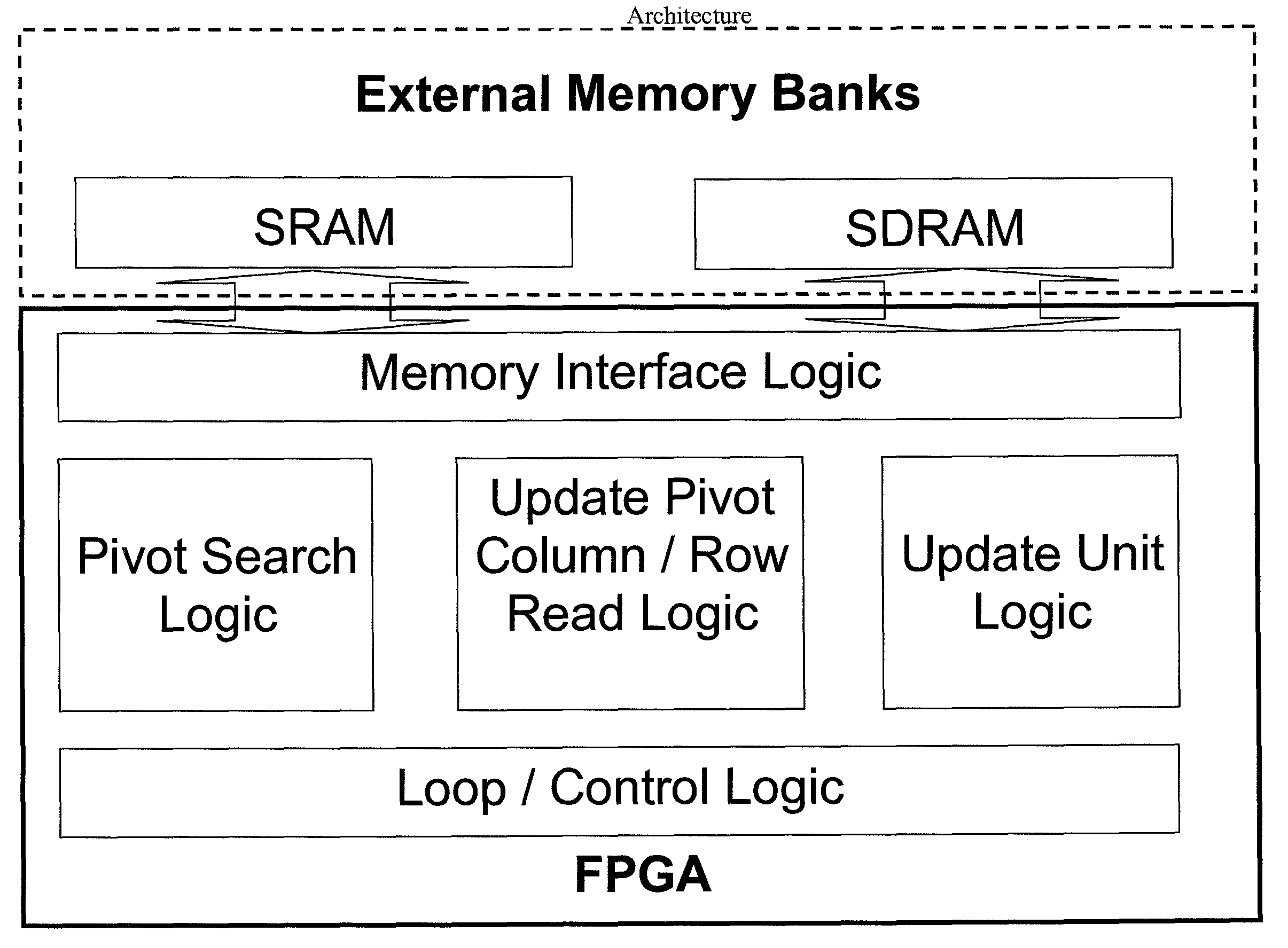

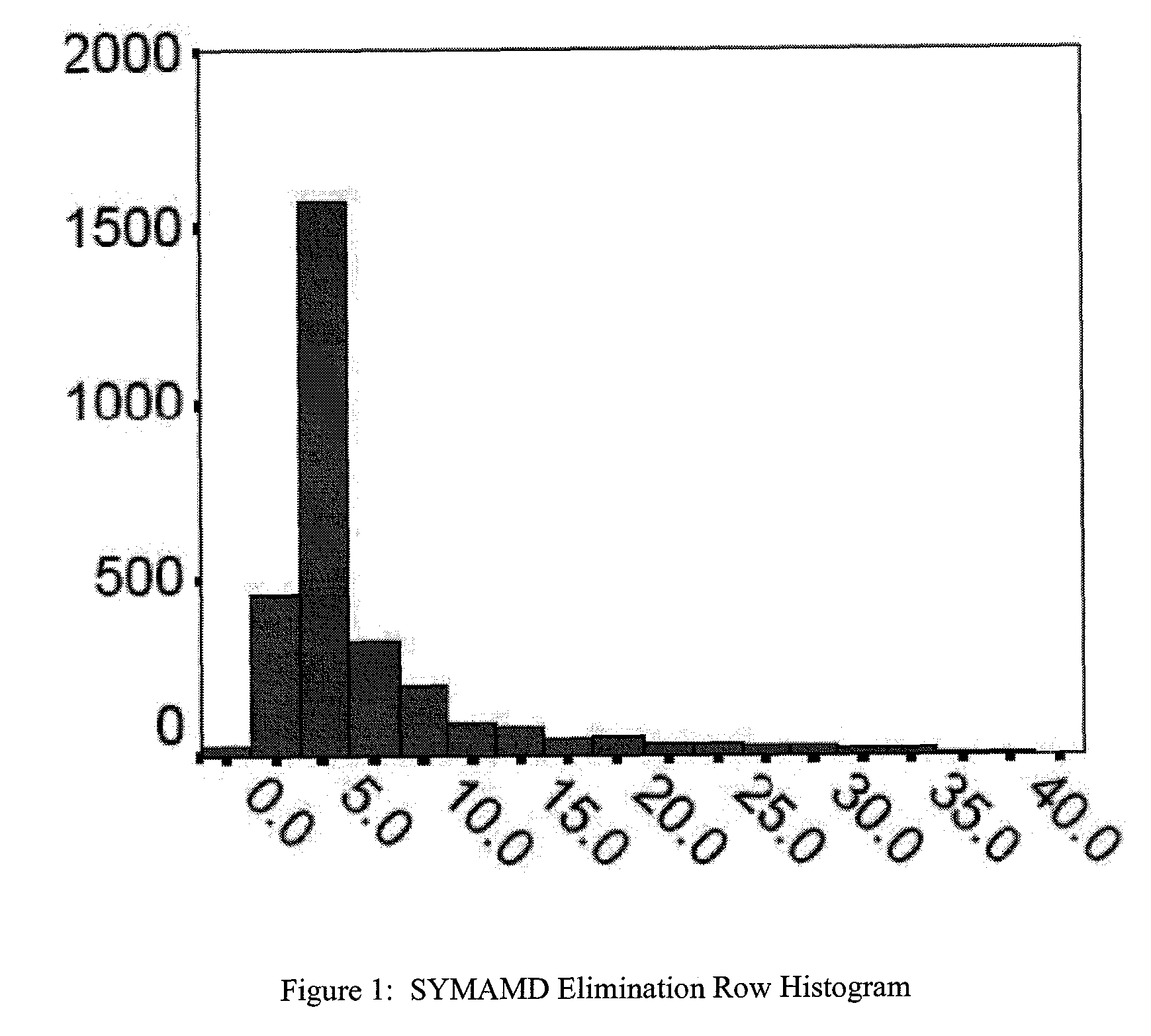

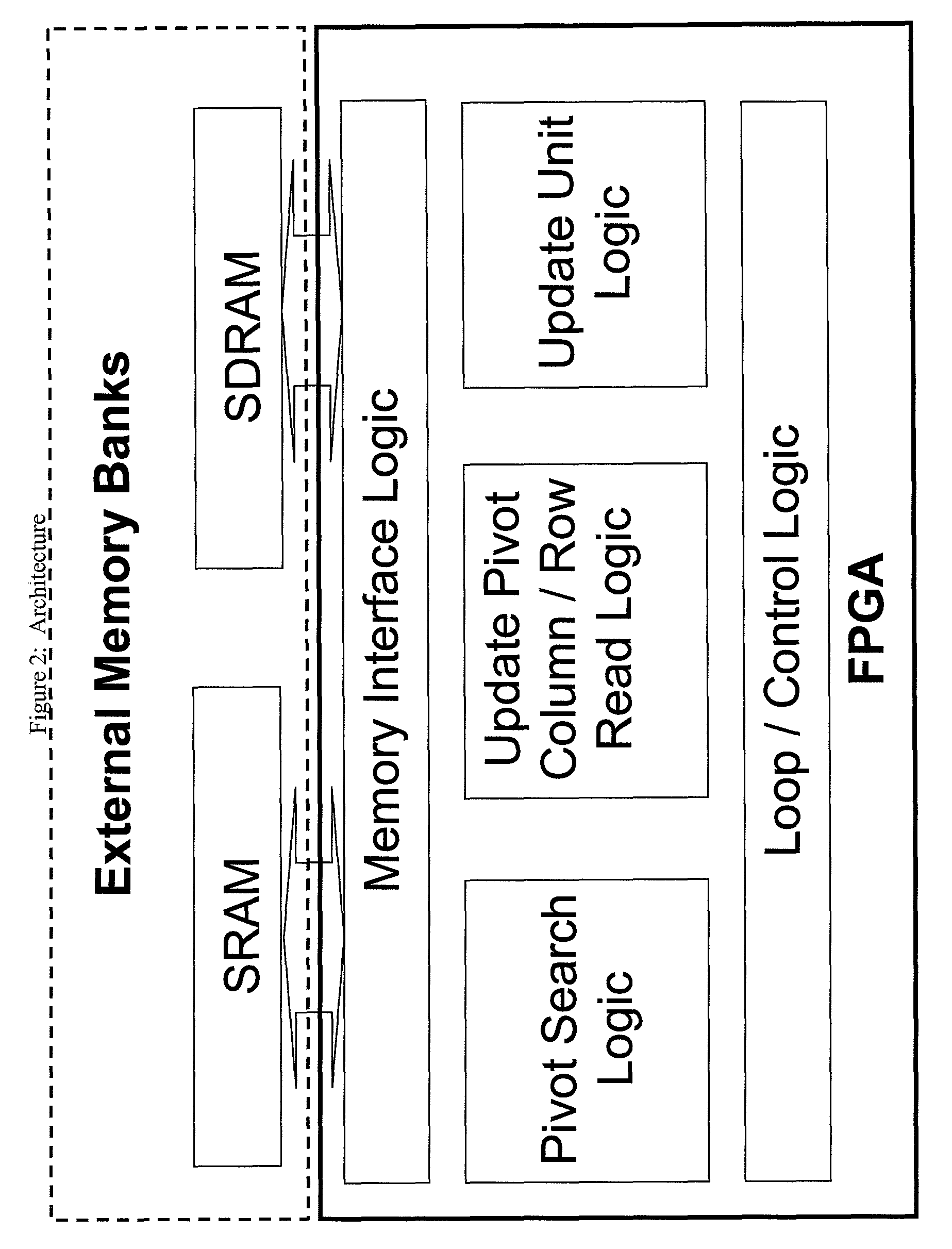

Solver for hardware based computing

InactiveUS20090292520A1Reduce computing timeComputation using non-contact making devicesAnalogue computers for nuclear physicsOperational transconductance amplifierDynamo

Full-AC load flow constitutes a core computation in power system analysis. The present invention provides a performance gain with a hardware implementation of a sparse-linear solver using a Field Programmable Gate Array (FPGA). The invention also relates to the design, simulation, and hardware verification of a static transmission line model for analog power flow computation. Operational transconductance amplifiers are employed in the model based on a previously proposed DC emulation technique of power flow computation, and provide reconfigurability of transmission line parameters via transconductance gain. The invention also uses Analog Behavioral Models (ABMs) in an efficient strategy for designing analog emulation engines for large-scale power system computation. Results of PSpice simulations of these emulation circuits are compared with industrial grade numerical simulations for validation. The application is also concerned with the development of a generator model using analog circuits for load flow emulation for power system analysis to reduce computation time. The generator model includes reconfigurable parameters using operational transconductance amplifiers (OTAs). The circuit module is used with other reconfigurable circuits, i.e., transmission lines and loads.

Owner:DREXEL UNIV

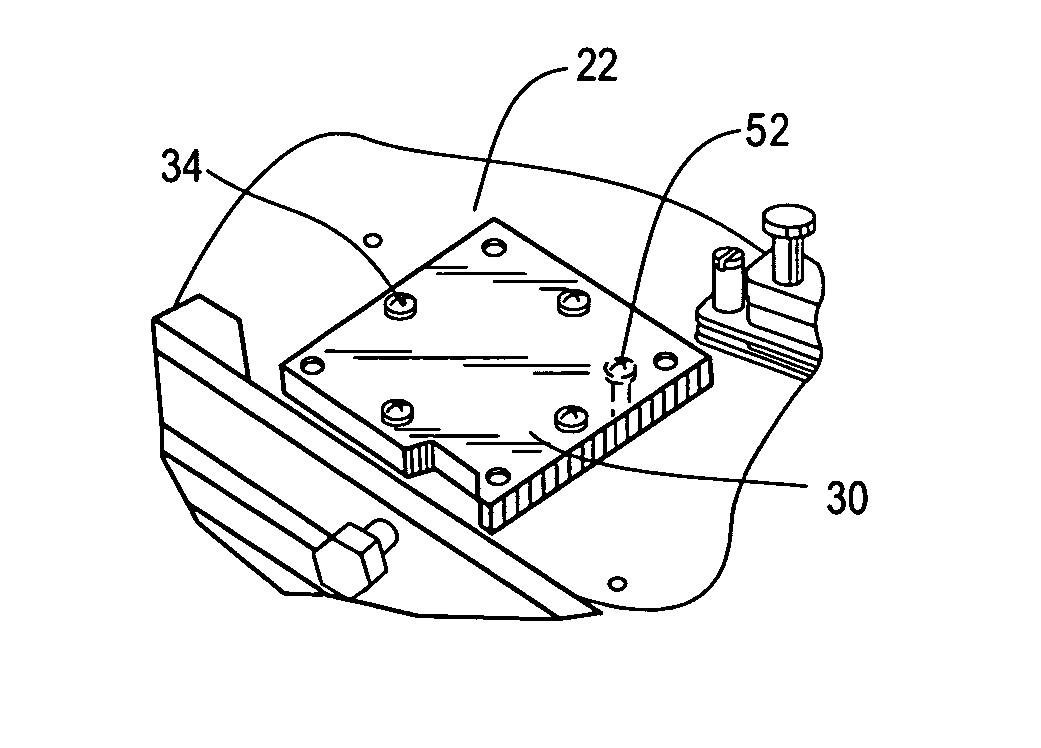

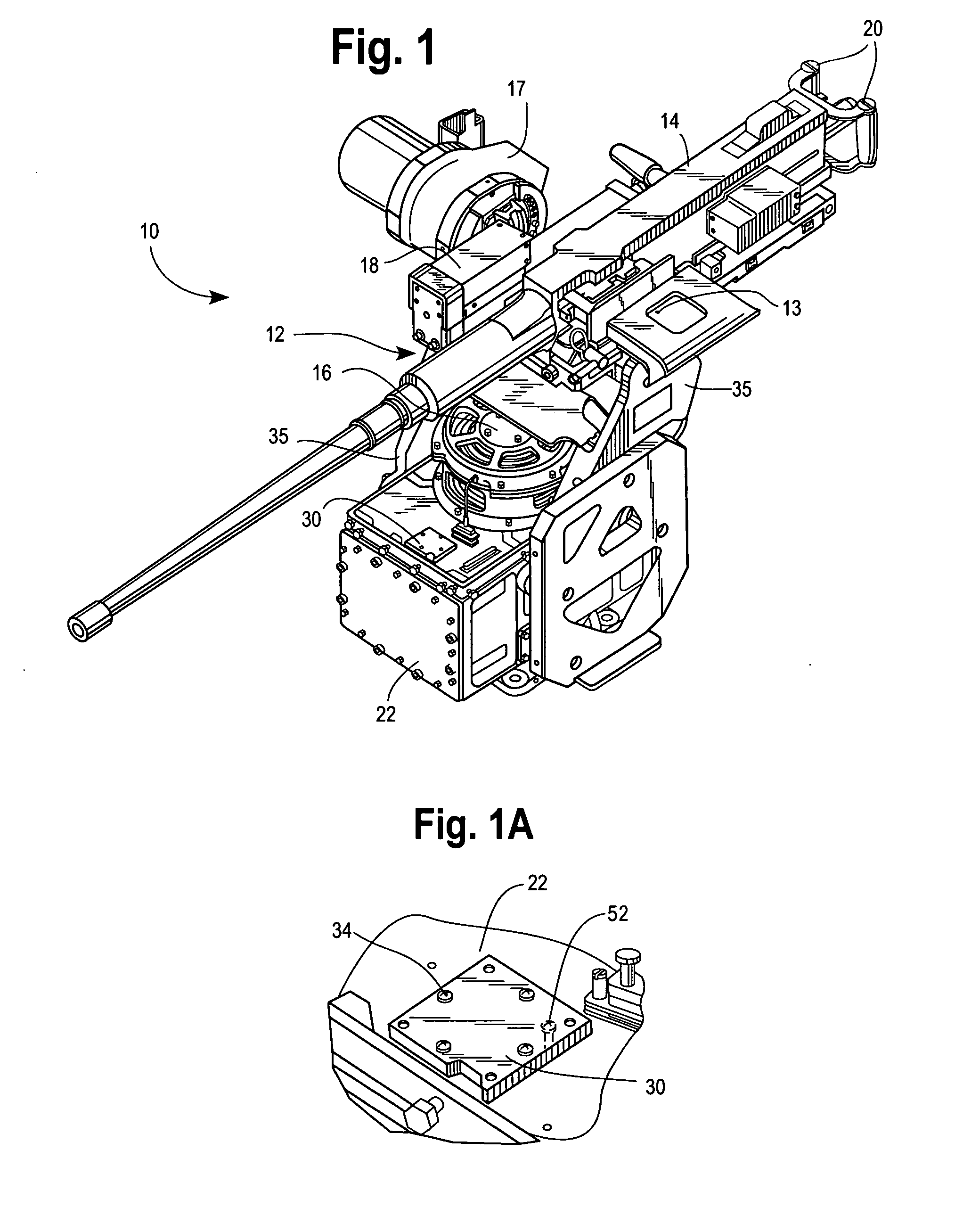

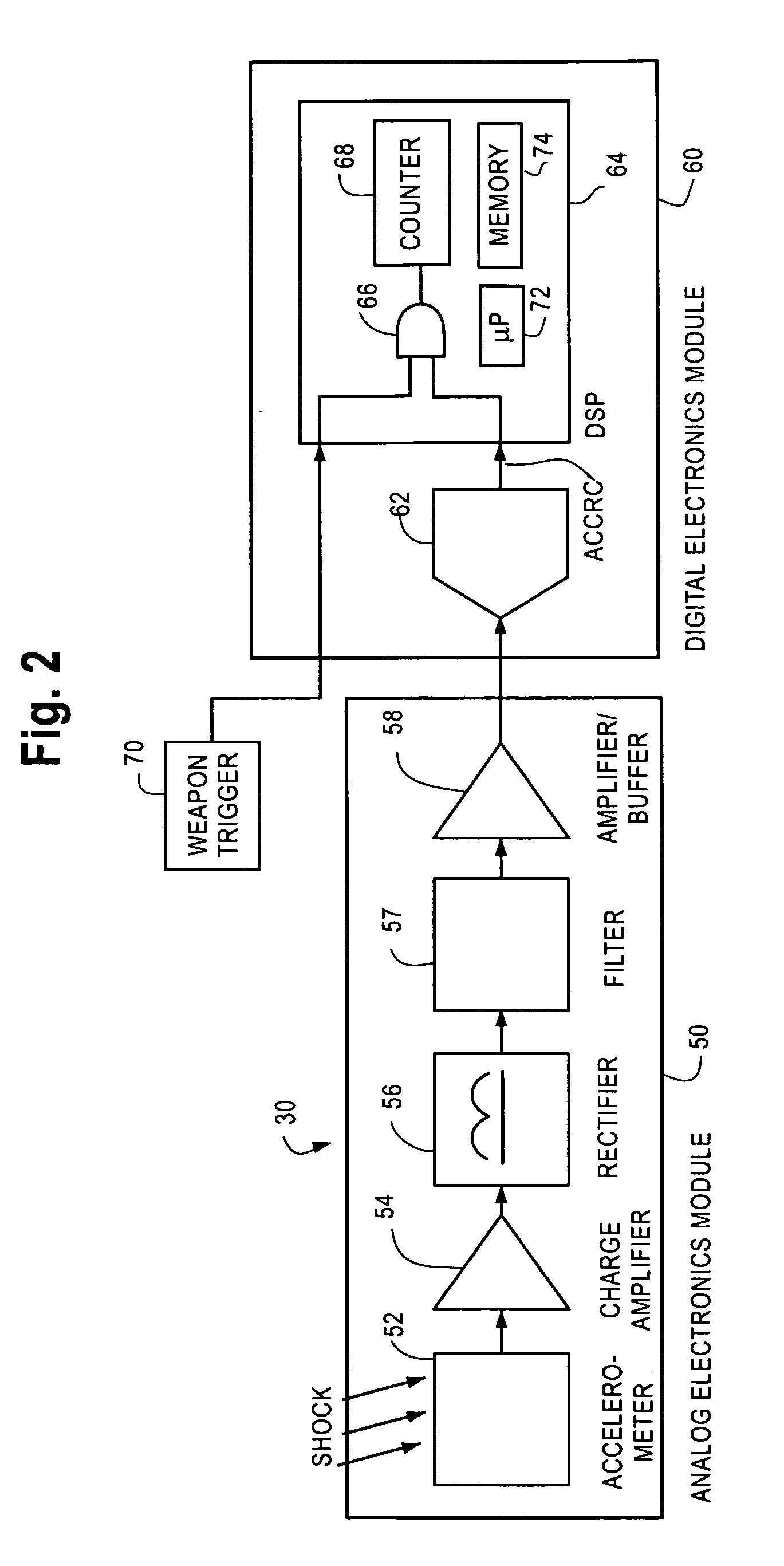

Rounds counter remotely located from gun

A rounds counter for a weapon mount is disclosed. The rounds counter is mounted on the mount in a remote location from the weapon itself, such as to a pedestal supporting a gimbal rotating the weapon mount in azimuth, inside an elevation drive housing, or to other structure. The mounting location is selected to be one where shock loads are relatively high, as compared to other locations on the mount. The rounds counter includes a sensor which senses shock due to the firing of the weapon, such as an accelerometer or strain gauge. The sensor could also be an acoustic transducer. Analog and digital circuitry for processing the sensor signal and to count the firing of the gun is also disclosed. The rounds counter is particularly useful as a common, single rounds counter unit for a weapon mount is adapted to receive and fire a variety of weapons, such as remotely operated weapon mounts mounted to military vehicles and patrol watercraft adapted to receive and fire four different types of guns.

Owner:EOS DEFENSE SYST

Data recovery system for source synchronous data channels

ActiveUS20090290671A1Easy Data RecoveryReduce distortion problemsModulated-carrier systemsFrequency/rate-modulated pulse demodulationSignal quality24-bit

A high-definition multimedia interface (HDMI) receiver recovers high speed encoded data which are transmitted differentially over data channels of a lossy cable, along with a clock. Inter symbol interference, high-frequency loss, skew between the clock and data channels, and differential skew within a differential signal are compensated by analog circuits which are automatically tuned for best performance by observing the quality of the recovered analog signal. Oversampling is used to provide a 24-bit digital representation of the analog signal for determining the quality of the signal.

Owner:REDMERE TECH

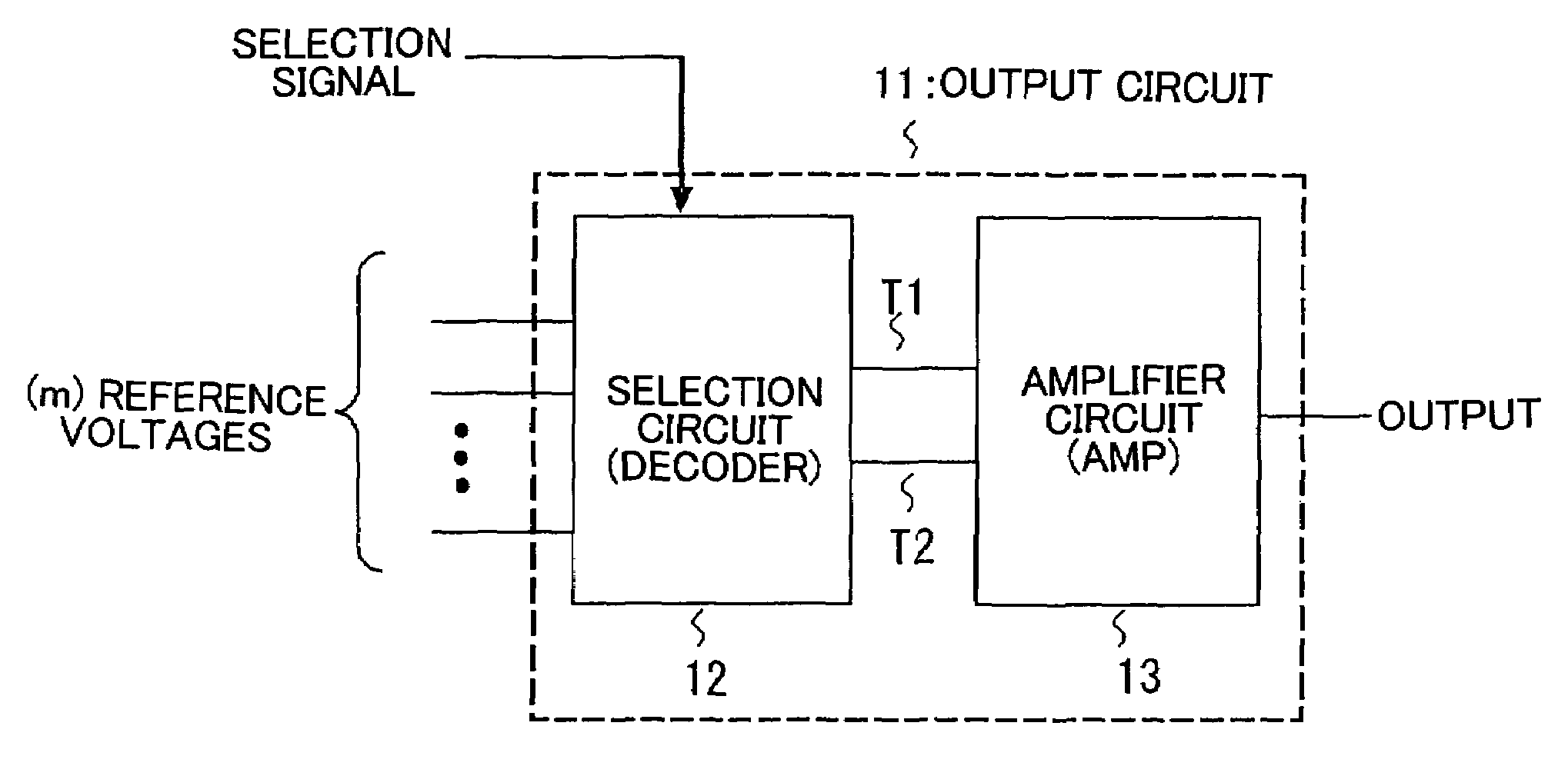

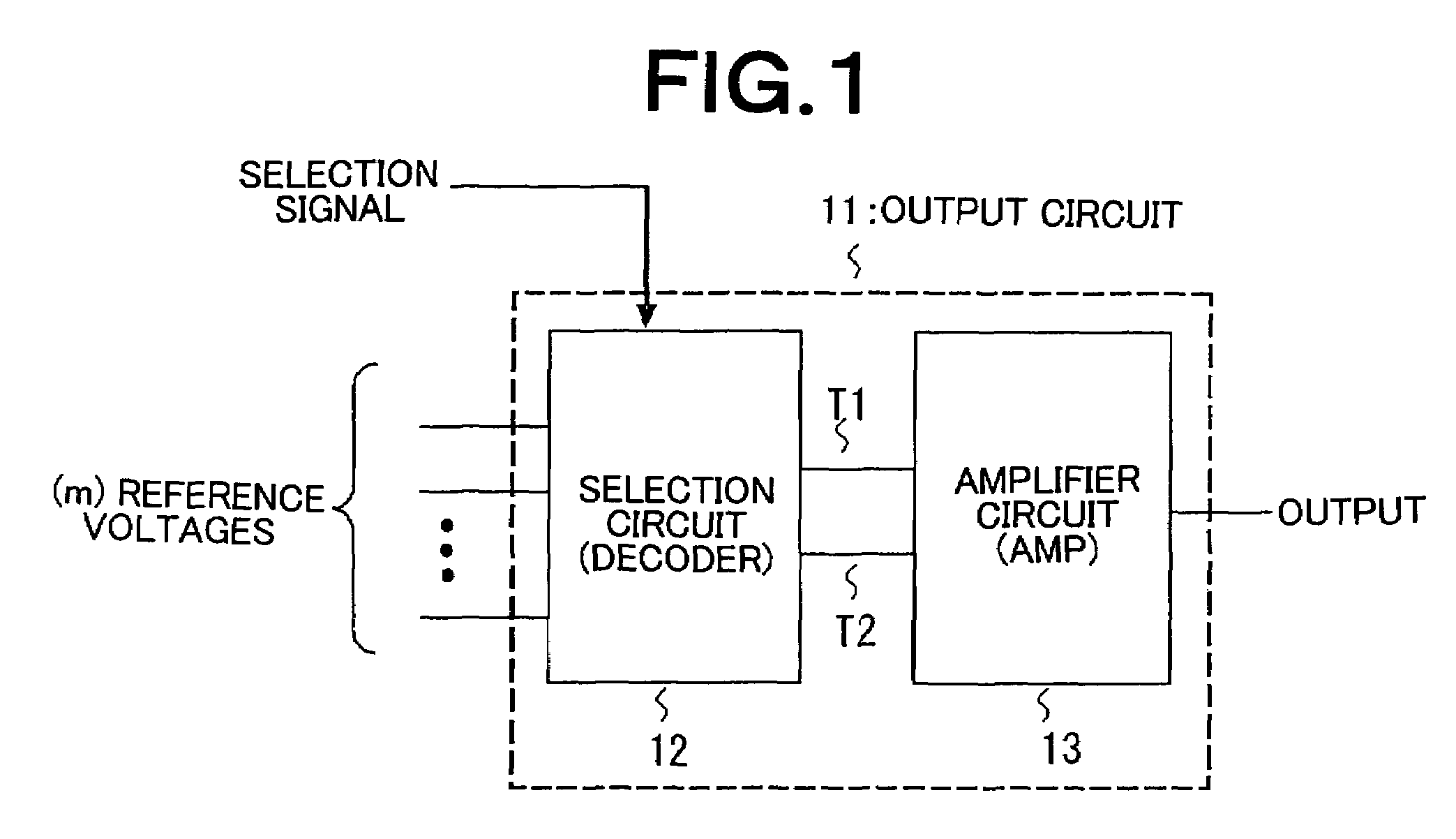

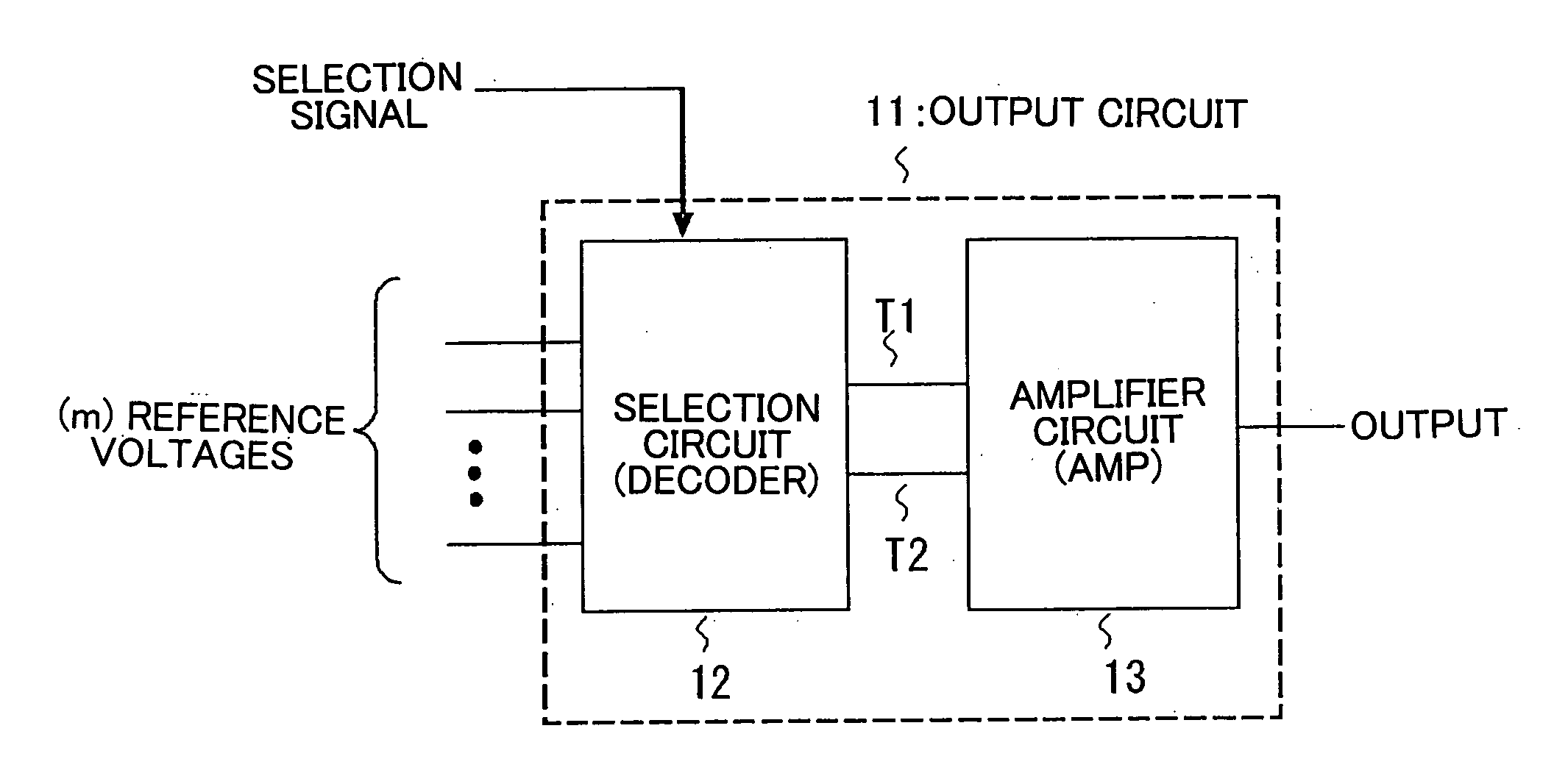

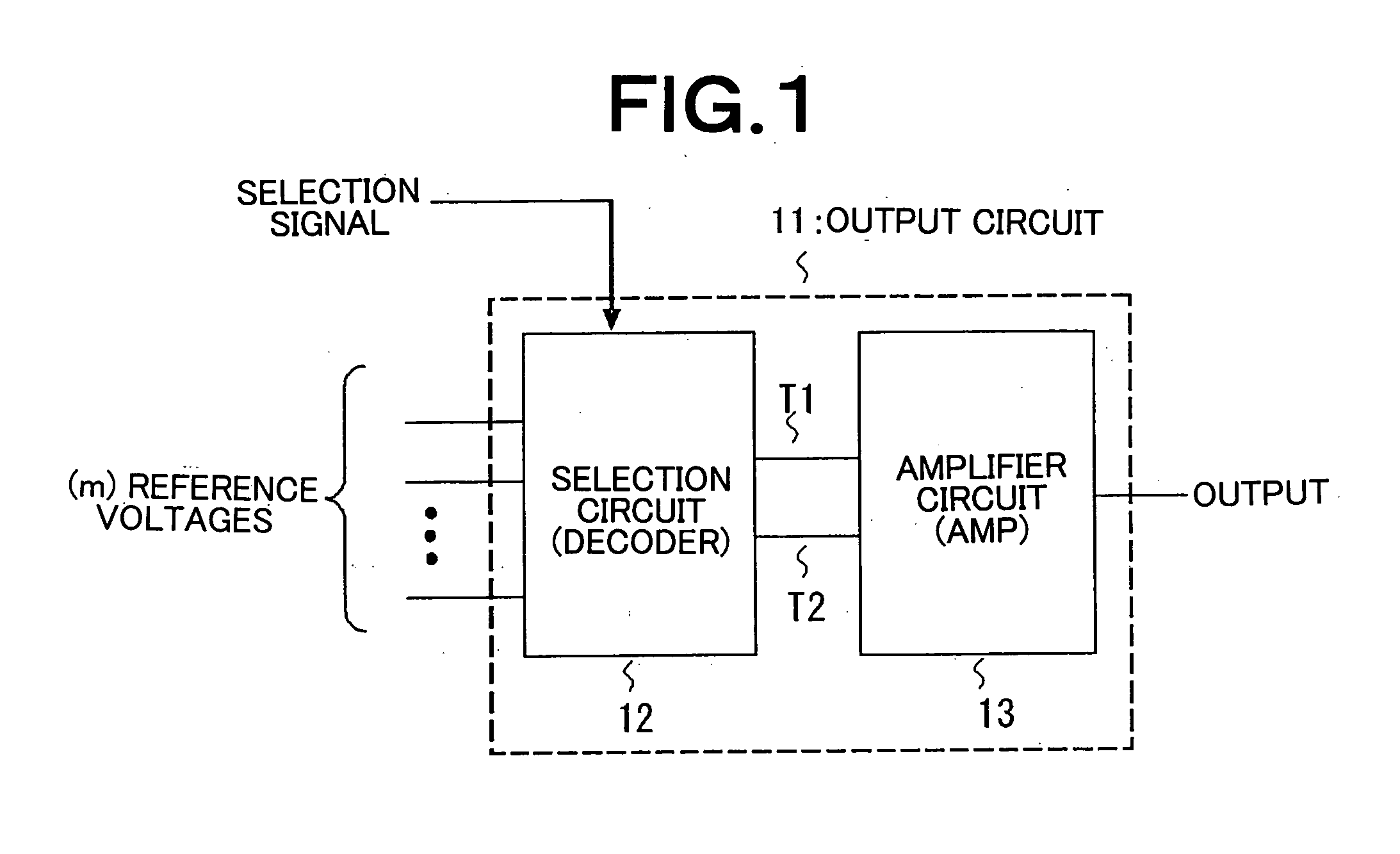

Output circuit, digital/analog circuit and display apparatus

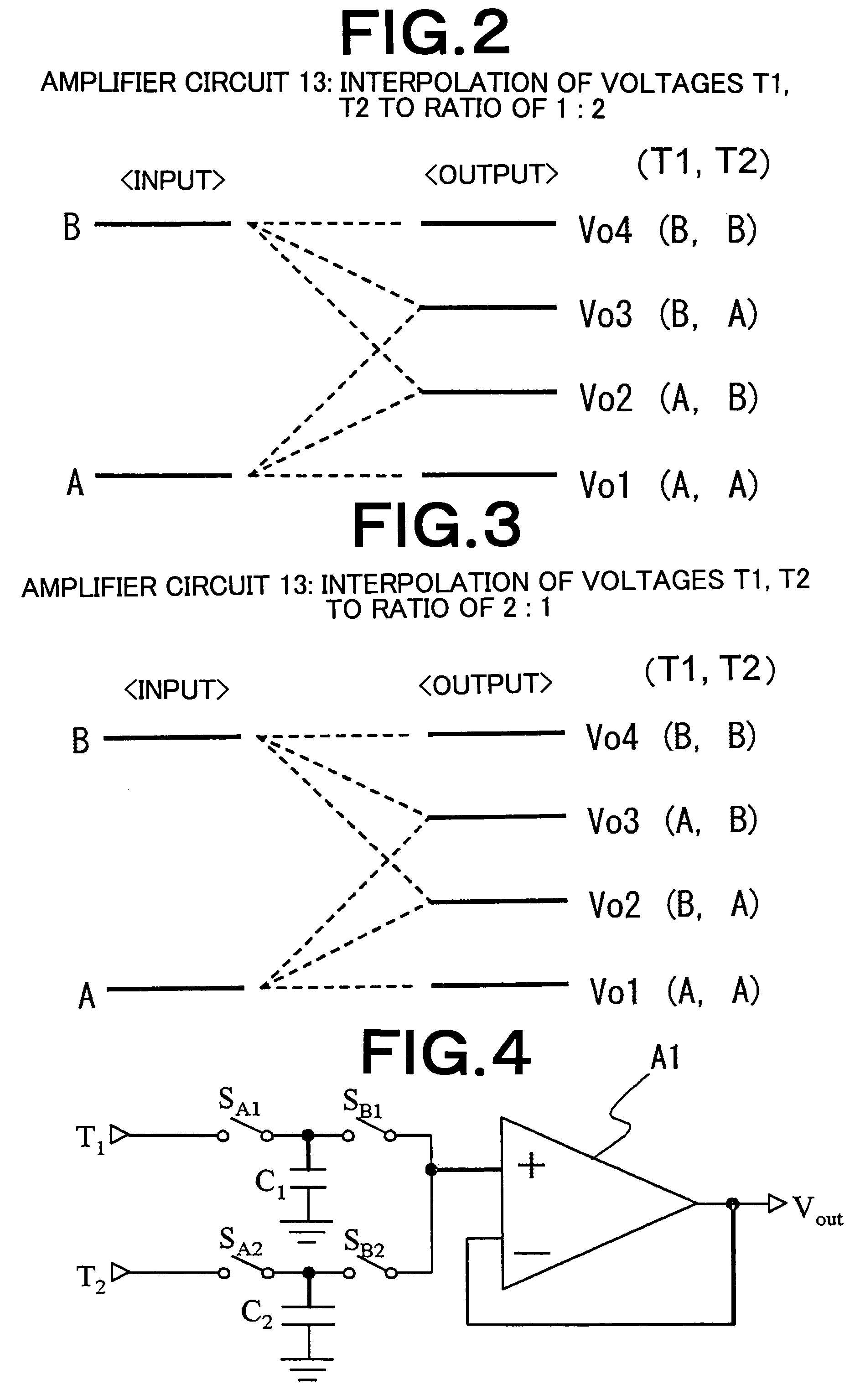

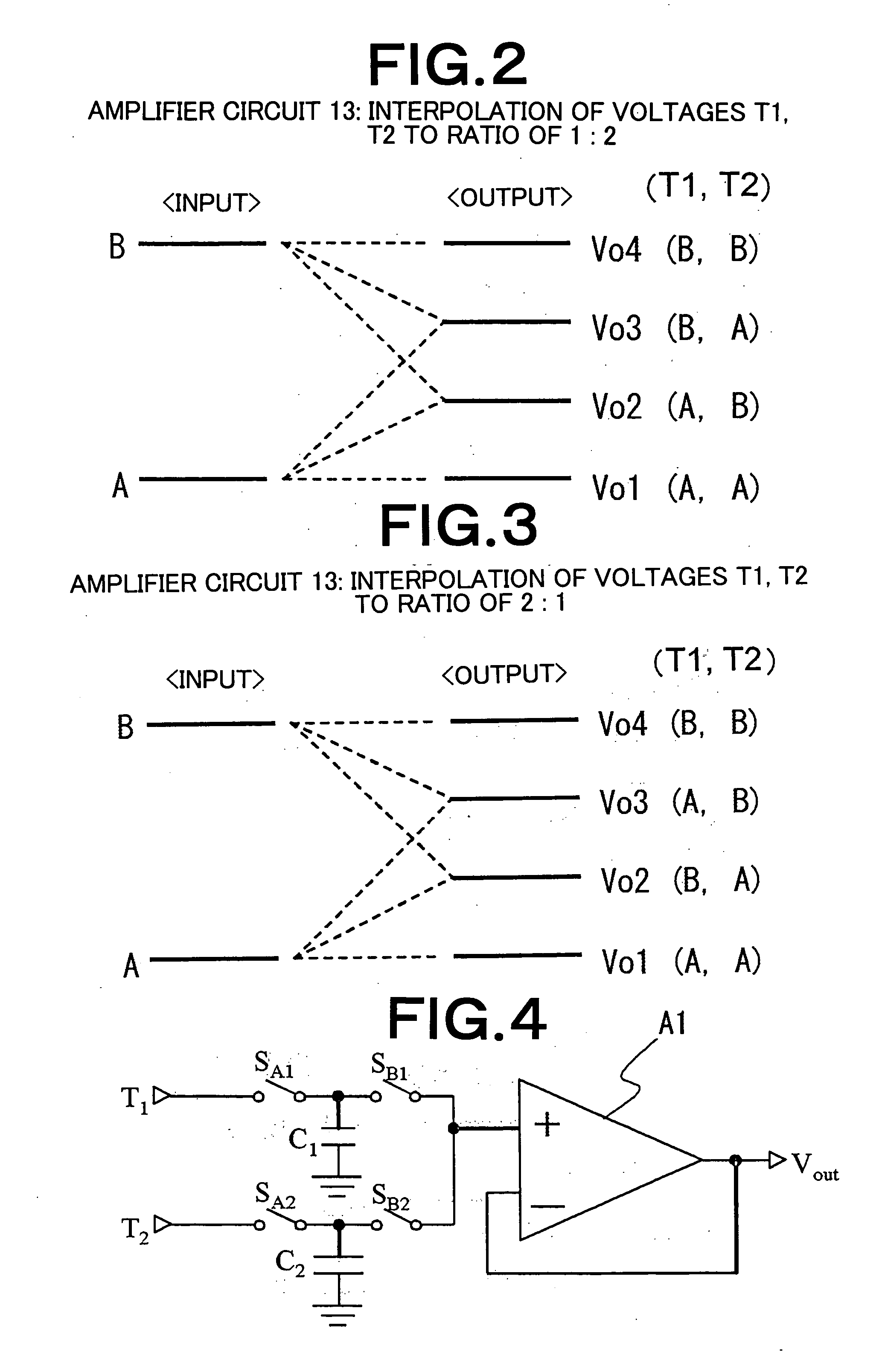

InactiveUS7369075B2Reduce in quantityIncrease the number ofTelevision system detailsElectric signal transmission systemsAudio power amplifierTerminal voltage

An output circuit, a digital / analog conversion circuit and a display apparatus can reduce the number of required input voltages and the number of transistors to save the necessary area. The output circuit and the digital / analog conversion circuit comprise a selection circuit for receiving as input a plurality of (m) reference voltages having mutually different respective voltage values, selecting two of the voltages according to a selection signal and outputting them and an amplifier circuit for receiving as input the voltages output from the selection circuit at two input terminals T1, T2 and outputting the voltage obtained by interpolating the voltage difference of the two input terminal voltages V(T1), V(T2) to a predetermined ratio. It may alternatively be so arranged that the selection circuit sequentially outputs the selected two voltages and the amplifier circuit sequentially receives as two input the two voltages and outputs the output voltage obtained by interpolation.

Owner:NEC CORP

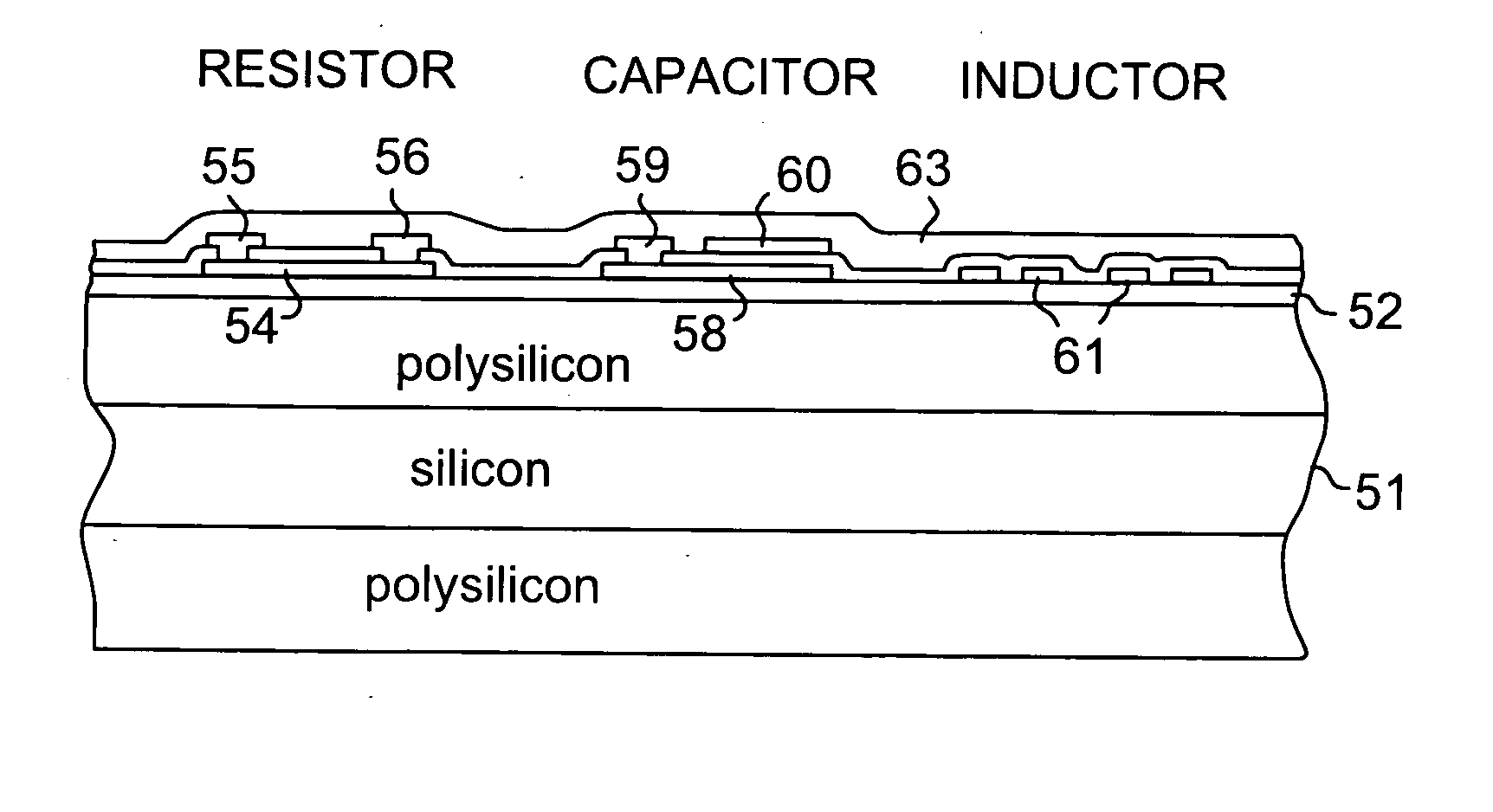

Integrated passive devices

InactiveUS20050253257A1Reduce interactionReduces rf interactionSemiconductor/solid-state device detailsSolid-state devicesElectrical interactionInductor

The specification describes a multi-chip module (MCM) that contains an integrated passive device (IPD) as the carrier substrate (IPD MCM). Parasitic electrical interactions are controlled at one or both interfaces of the IPD either by eliminating metal from the interfaces, or by selective use of metal in parts of the MCM that are remote from the sensitive device components. The sensitive device components are primarily analog circuit components, especially RF inductor elements. In the IPD layout, the sensitive components are segregated from other components. This allows implementation of the selective metal approach. It also allows parasitic interactions on top of the IPD substrate to be reduced by selective placement of IC semiconductor chips and IC chip ground planes. In preferred embodiments of the IPD MCM of the invention, the IPD substrate is polysilicon, to further minimize RF interactions. The various methods of assembling the module may be adapted to keep the overall thickness within 1.0 mm.

Owner:SYCHIP

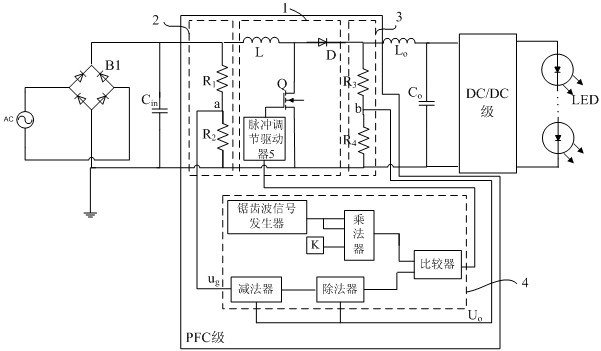

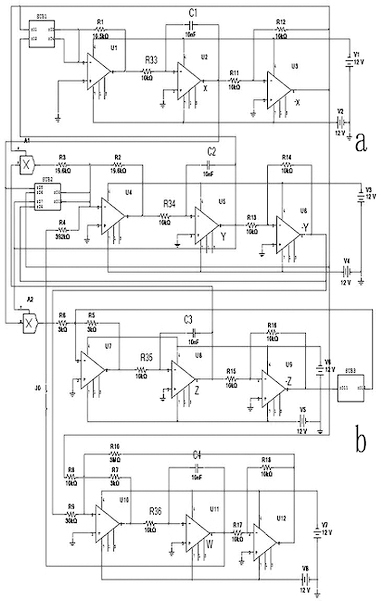

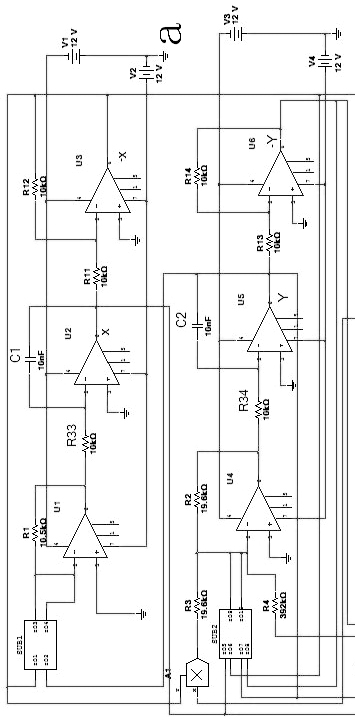

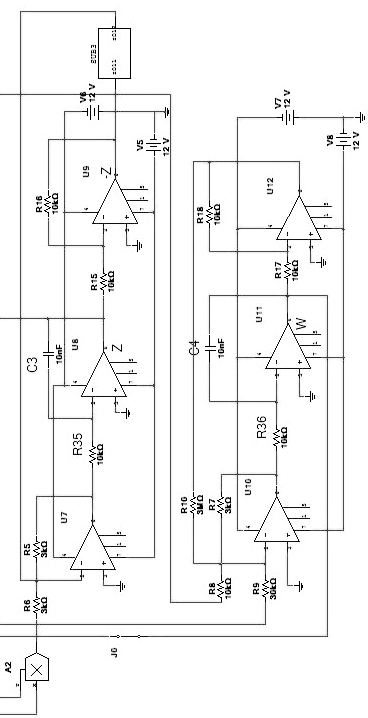

Different-dimensional switchable chaotic system design method and circuit

The invention relates to a different-dimensional switchable chaotic system design method and a circuit; a four-dimensional hyper-chaos system is constructed by adding variables and feeding back control items based on a three-dimensional generalized Lorenz system family; and a switchable different-dimensional chaotic circuit is designed through a plurality of switch controllers in Multisim software. An analog circuit constructed by the invention is convenient to use and easy to realize by hardware, and has relatively lower cost; the designed switchable circuit not only can flexibly realize the switching between a three-dimensional chaotic system and the four-dimensional hyper-chaos system, but also can return to realize the switch among three chaotic systems in the same dimension; and the systems can serve as practical chaotic modulation and chaotic encryption signals, and can be widely applied to the field of information security cryptography with higher requirements on confidentiality and reliability.

Owner:JIANGXI UNIV OF SCI & TECH

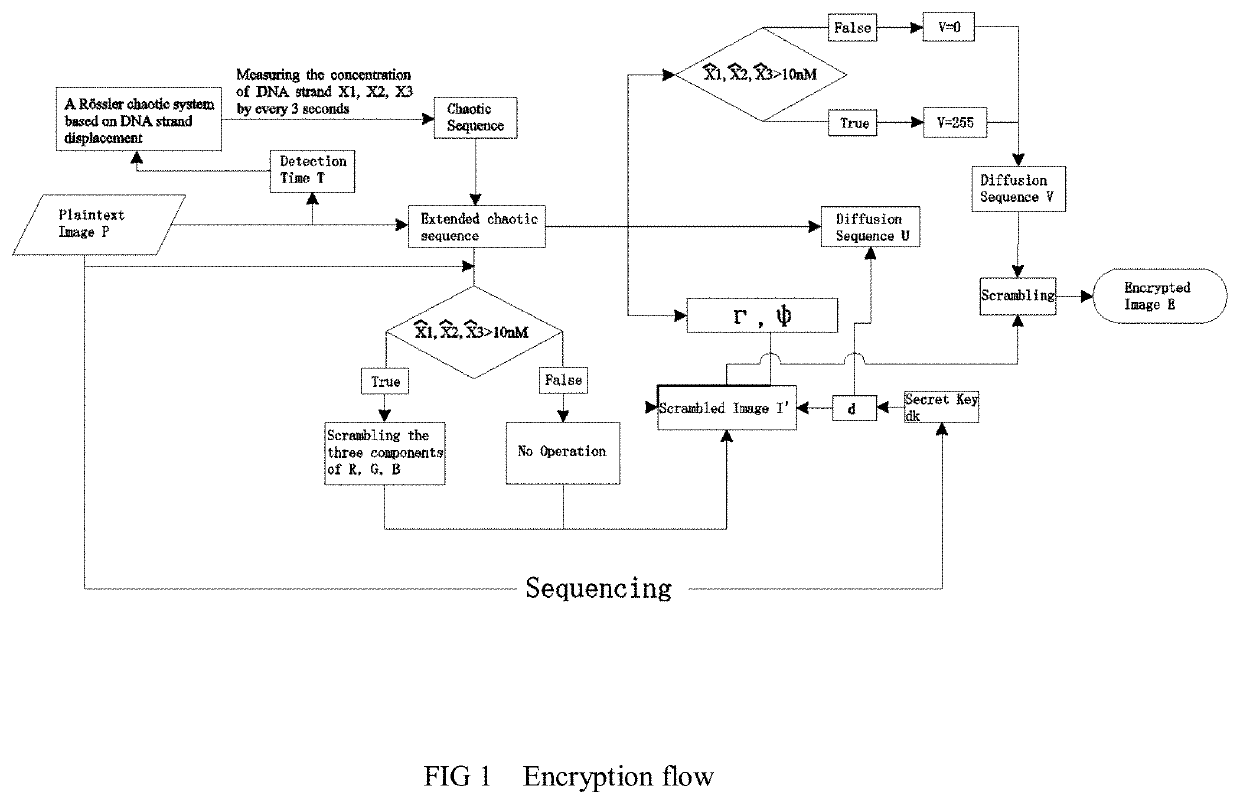

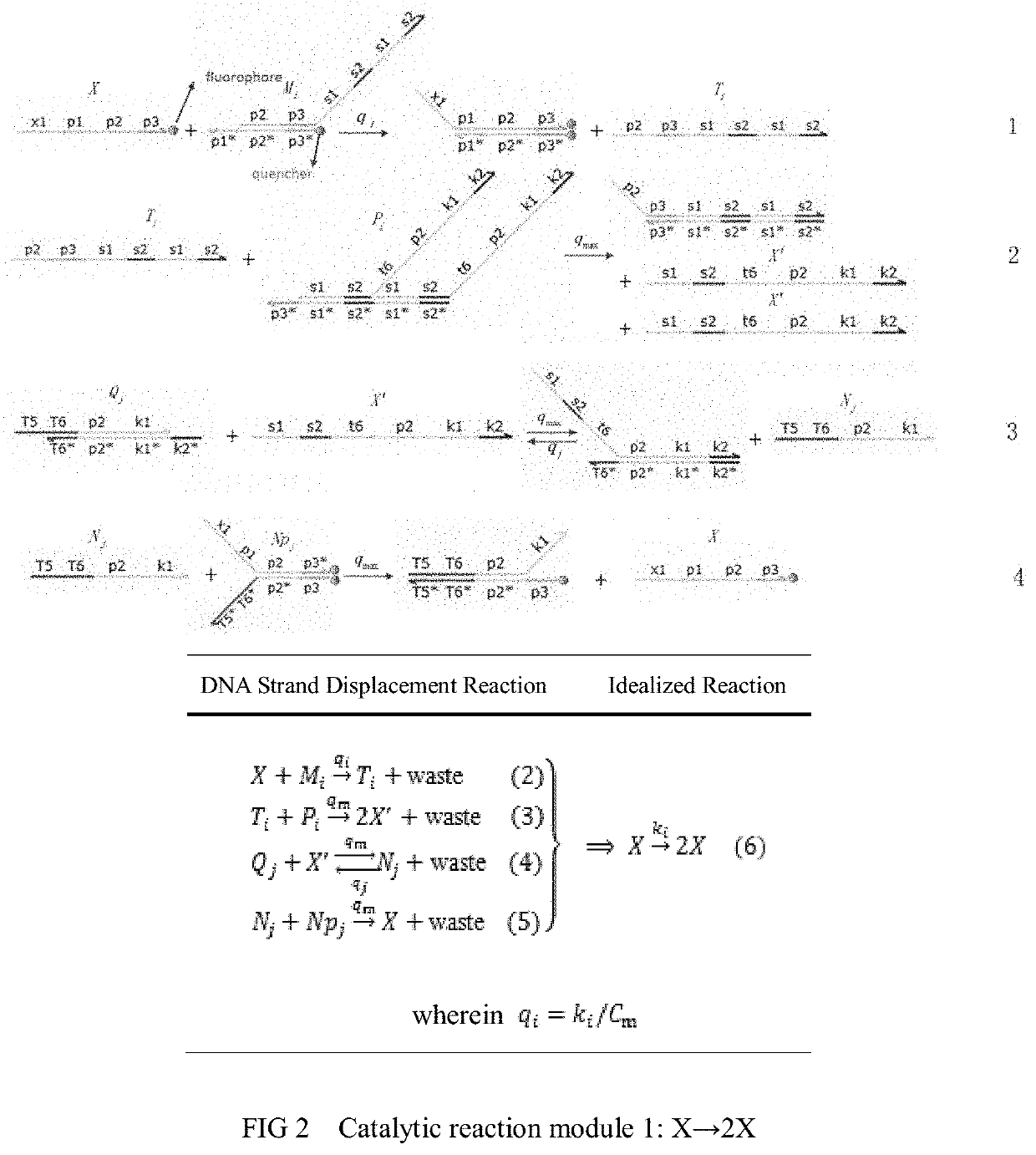

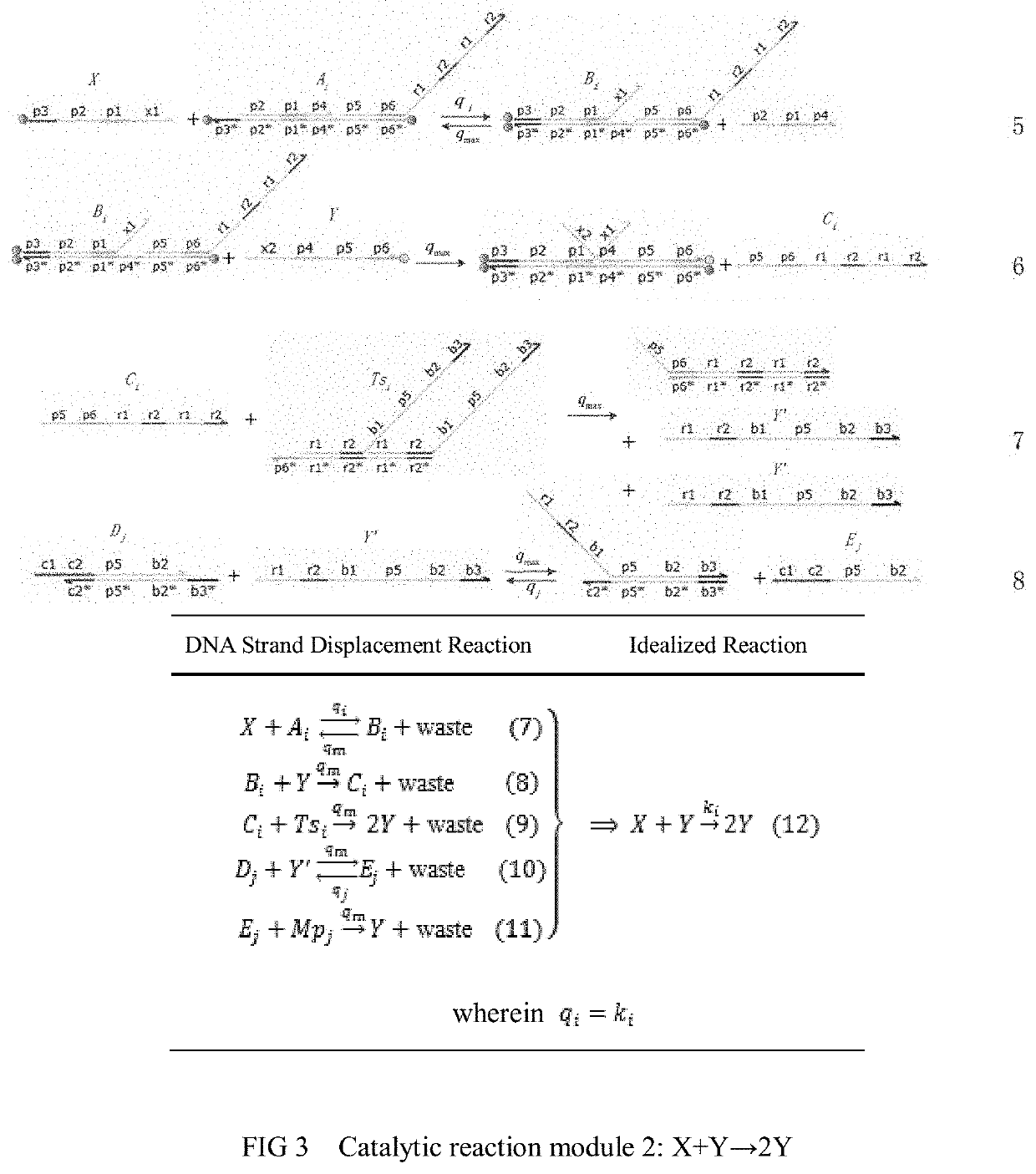

Color Image Encryption Method Based on DNA Strand Displacement Analog Circuit

InactiveUS20200287704A1A large amountShorten the timeKey distribution for secure communicationSecuring communication by chaotic signalsDna strand displacementA-DNA

The invention relates to the field of strand displacement, and provides a color image encryption method based on a DNA strand displacement analog circuit. Firstly, a reaction module with a light-emitting group and a quenching group is designed through Visual DSD software, and by utilizing the equivalence of a DNA strand displacement reaction module and an ideal reaction module, an analog circuit formed by the DNA strand displacement reaction module can perform analog on the dynamics characteristics of an ideal reaction network formed by the ideal reaction module, wherein the Rössler chaotic system can be described by the idealized reaction network. Secondly, data generated by the DNA strand displacement analog circuit is converted into a chaotic sequence matched with a plaintext image in size after being extended, and finally, the color image encryption effect is achieved through scrambling and diffusion operations.

Owner:ZHANG QIANG +3

Output circuit, digital/analog circuit and display apparatus

InactiveUS20060132344A1Reduce in quantityIncrease the number ofTelevision system detailsElectric signal transmission systemsAudio power amplifierTerminal voltage

An output circuit, a digital / analog conversion circuit and a display apparatus can reduce the number of required input voltages and the number of transistors to save the necessary area. The output circuit and the digital / analog conversion circuit comprise a selection circuit for receiving as input a plurality of (m) reference voltages having mutually different respective voltage values, selecting two of the voltages according to a selection signal and outputting them and an amplifier circuit for receiving as input the voltages output from the selection circuit at two input terminals T1, T2 and outputting the voltage obtained by interpolating the voltage difference of the two input terminal voltages V(T1), V(T2) to a predetermined ratio. It may alternatively be so arranged that the selection circuit sequentially outputs the selected two voltages and the amplifier circuit sequentially receives as two input the two voltages and outputs the output voltage obtained by interpolation.

Owner:NEC CORP

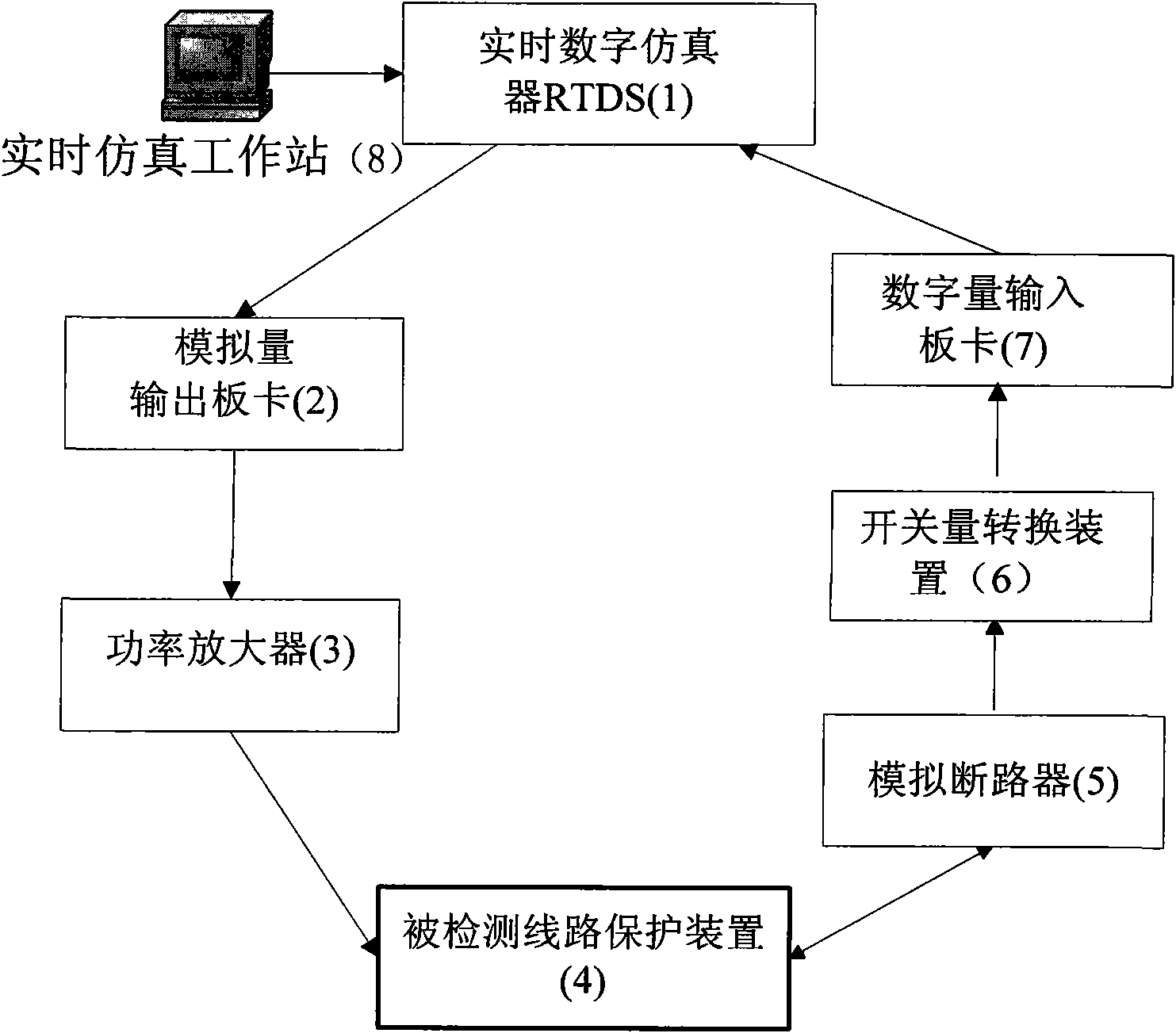

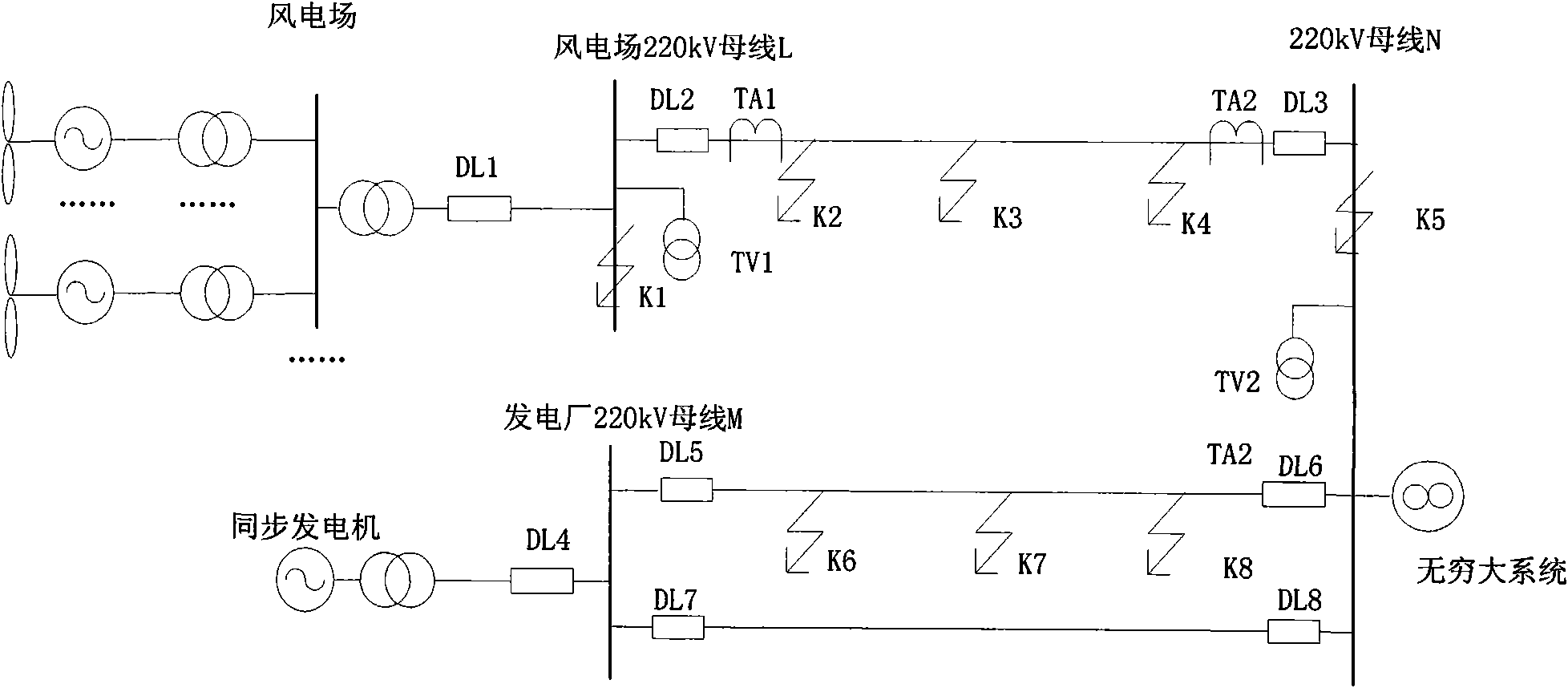

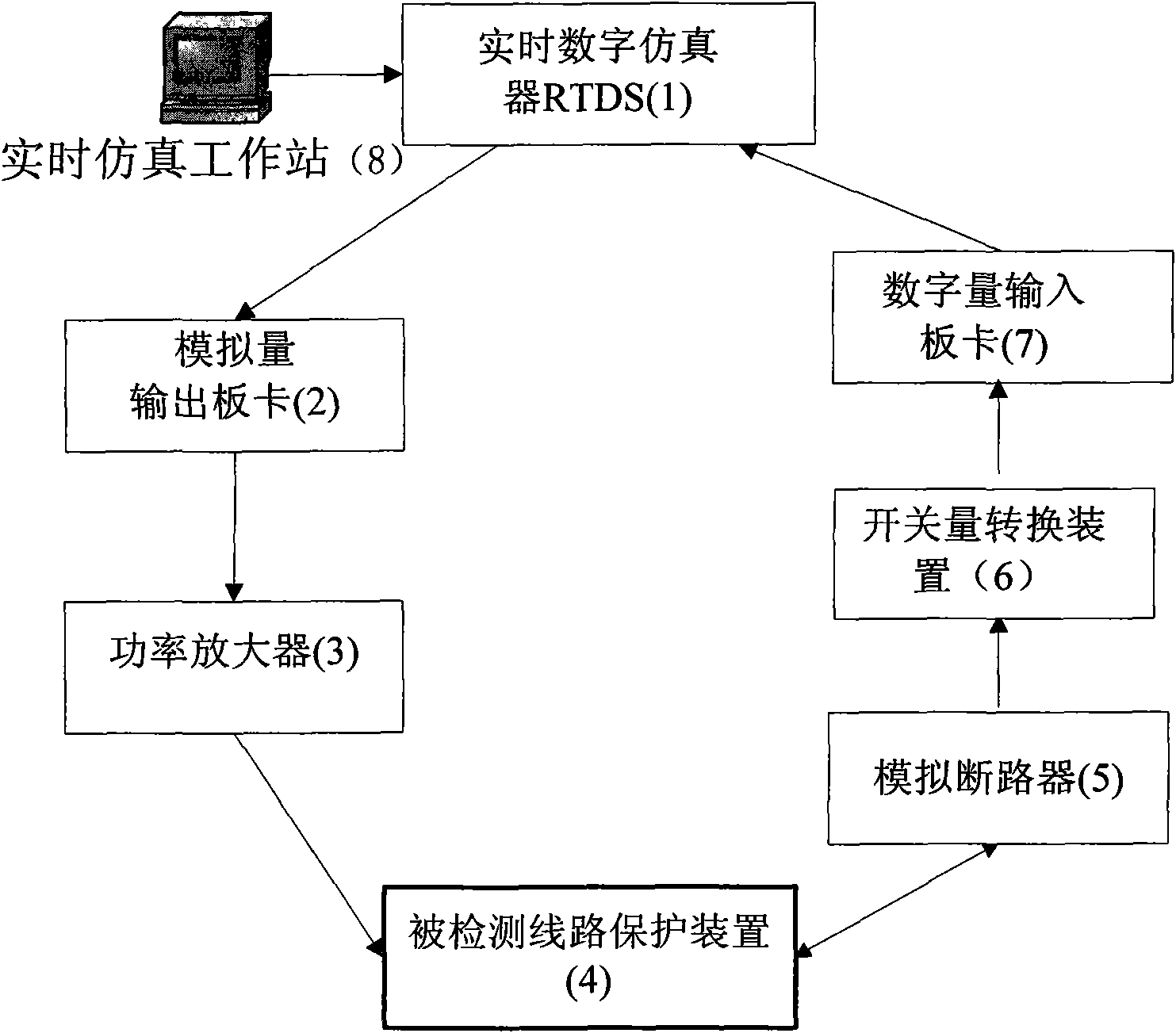

Operation method for safely applying line protection device to wind power station

InactiveCN102208801AAvoid disconnection issuesExtended power generation timeEmergency protective circuit arrangementsElectrical testingEngineeringWorkstation

The invention discloses an operation method for safely applying a line protection device to a wind power station, which relates to the relay protection of a power plant and is provided aiming at solving the problem that the line protection device in the current system cannot meet the protective requirements of the wind power station very well. The operation method comprises the following steps of: firstly, establishing a real-time simulation model which is a virtual power grid environment, including fault points in a wind power station, a bus and transmission lines, a main transformer unit of a power generator, a current and voltage mutual inductor, an equivalent system and a simulation system; secondly; establishing an experimental detection platform including a real-time digital simulation work station, an RTDS (Real Time Digital System) real-time digital simulator, an analogue quantity output board card, a power amplifier, a line protection device, an analogue circuit breaker, a switch conversion device and a digital quantity input board card; and thirdly, accessing the line protection device to be detected to the power amplifier of the detection system, then connecting the line protection device with the analogue circuit breaker and carrying out various kinds of experiments. The experiment implemented by using the wind power station model and an onsite oscillograph of the wind power station can provide a real and accurate simulation environment so that validation possibility is improved, and therefore the line protection device to be detected can be safely used for the wind power station after detected.

Owner:内蒙古自治区电力科学研究院

Circuit arrangement, in particular phase-locked loop, as well as corresponding method

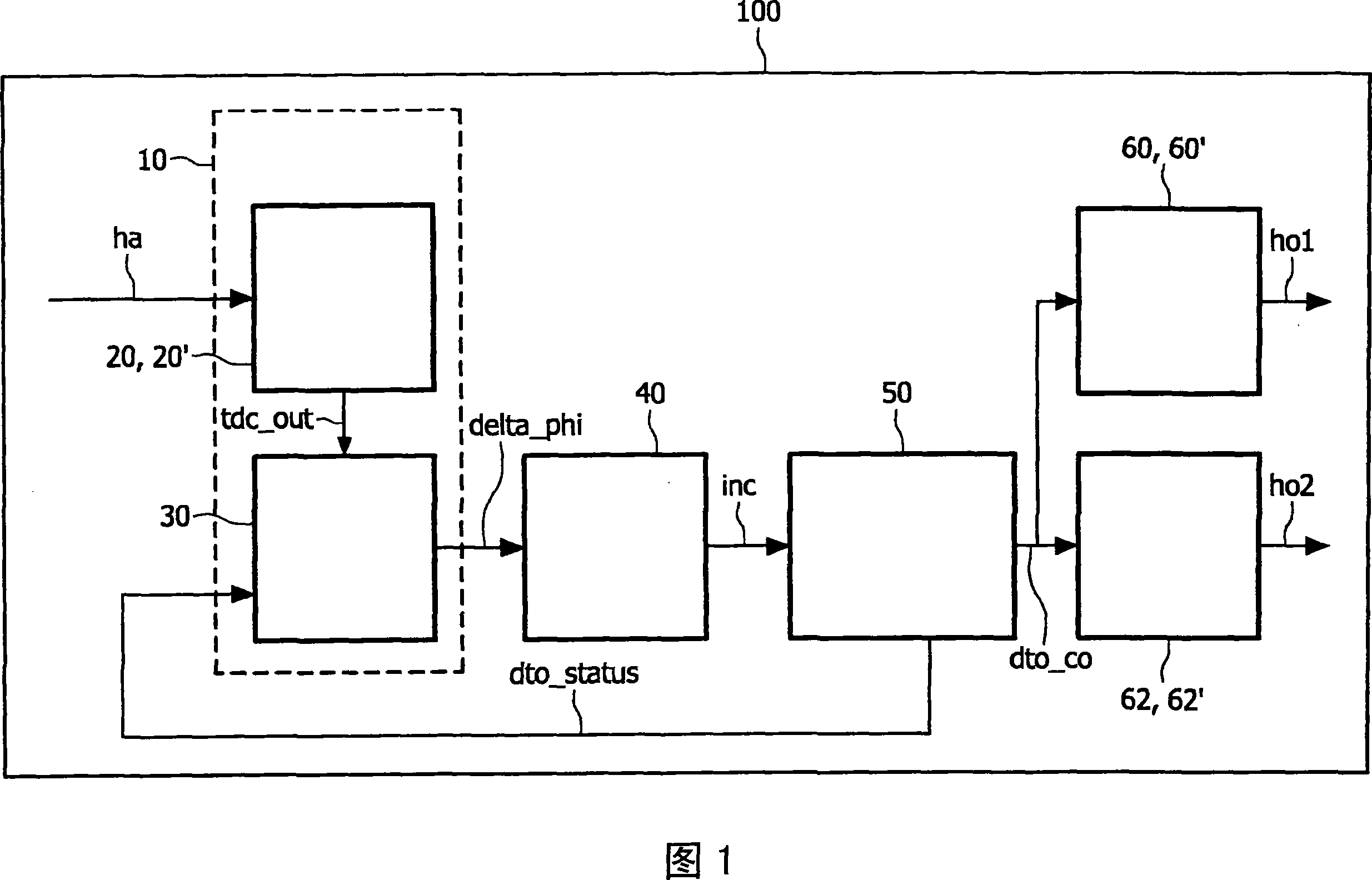

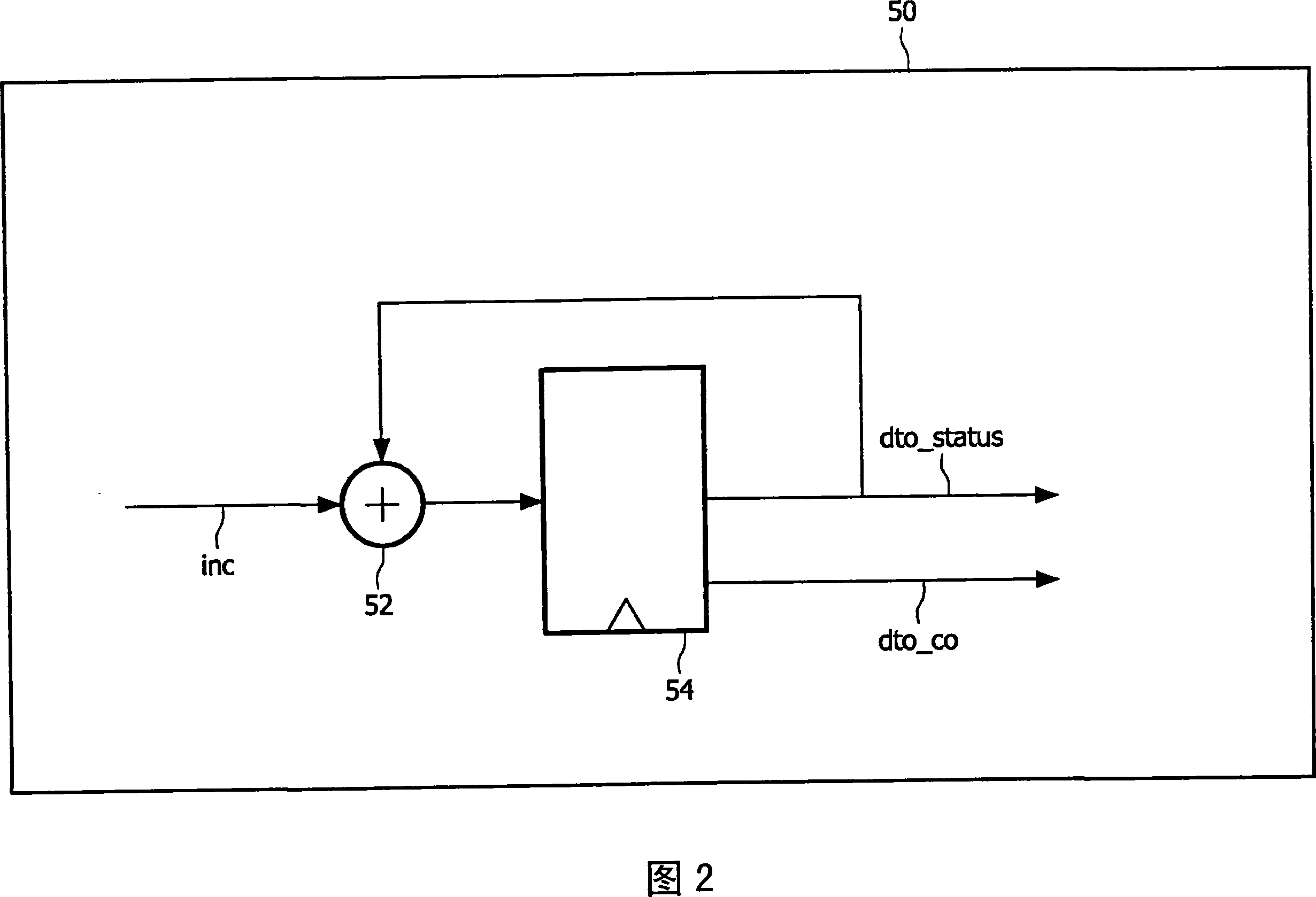

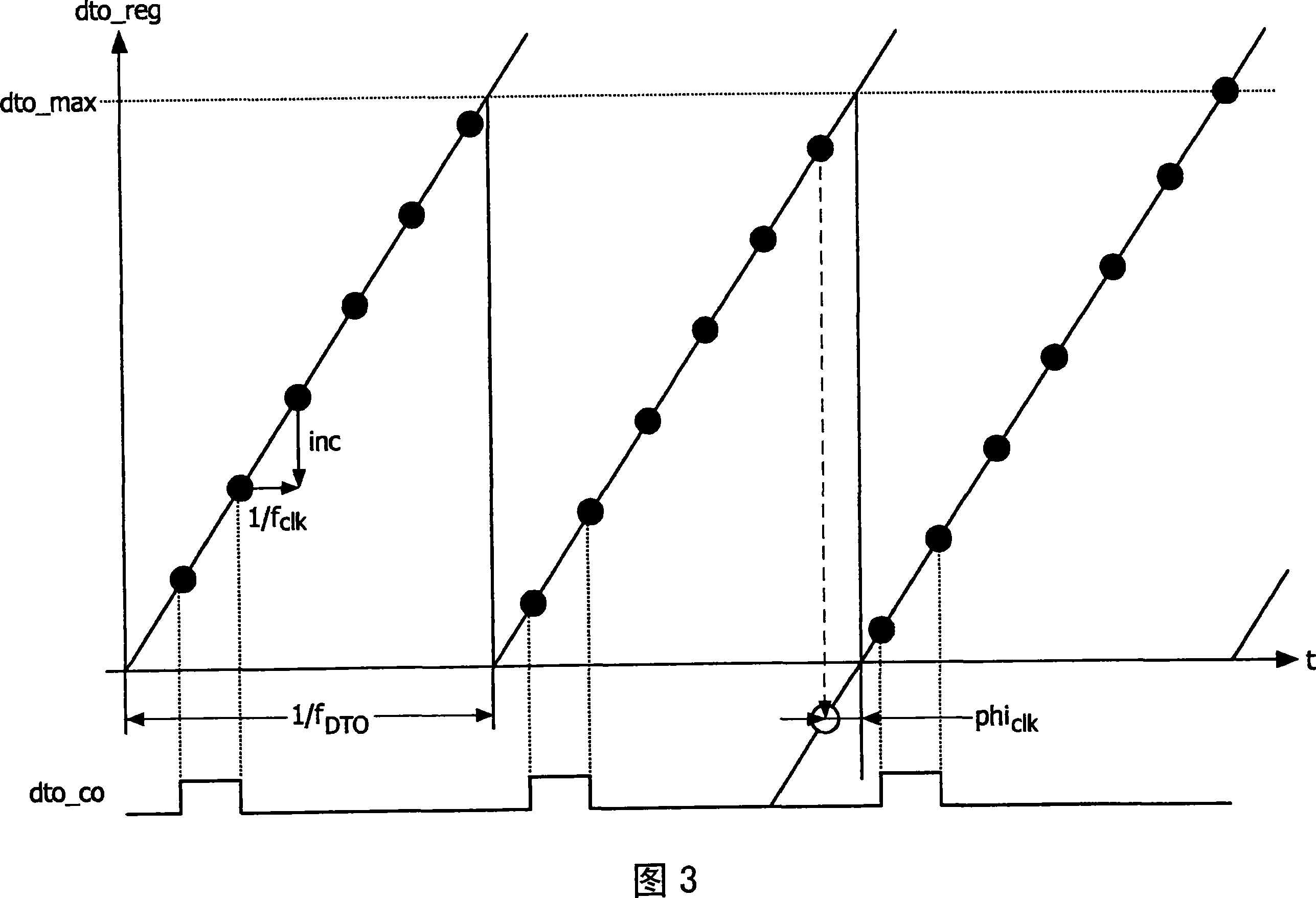

In order to further develop a circuit arrangement (100), in particular to a phase-locked loop for sub-clock or sub-pixel accurate phase-measurement and phase-generation, as well as a corresponding method in such way that no clock multiplier phase-locked loop is to be provided behind the time-to-digital converter and that neither an analog delay line nor a signal divider unit is to be provided between the digital ramp oscillator or discrete time oscillator and the digital-to-time converter, wherein less analog circuitry is susceptible for noise and for ground bounce in the digital environment, it is proposed to provide at least one phase measurement unit (10); - at least one loop filter unit (40; 40') being provided with at least one output signal (delta-phi) of at least one phase detector unit (30); at least one digital ramp oscillator unit or discrete time oscillator unit (50; 50') being provided with at least one output signal, in particular with at least one increment (inc), of the loop filter unit (40; 40'), the status signal (dto-status) of at least one register unit (54; 54') of the digital ramp oscillator unit or discrete time oscillator unit (50; 50') being fed back as input signal to the phase detector unit (30); and at least one digital-to-time converter unit (60, 62; 60', 62') being provided with at least one output signal (dto-co) of the digital ramp oscillator unit or discrete time oscillator unit (50; 50') and generating at least one output signal (hoi, ho2).

Owner:NXP BV

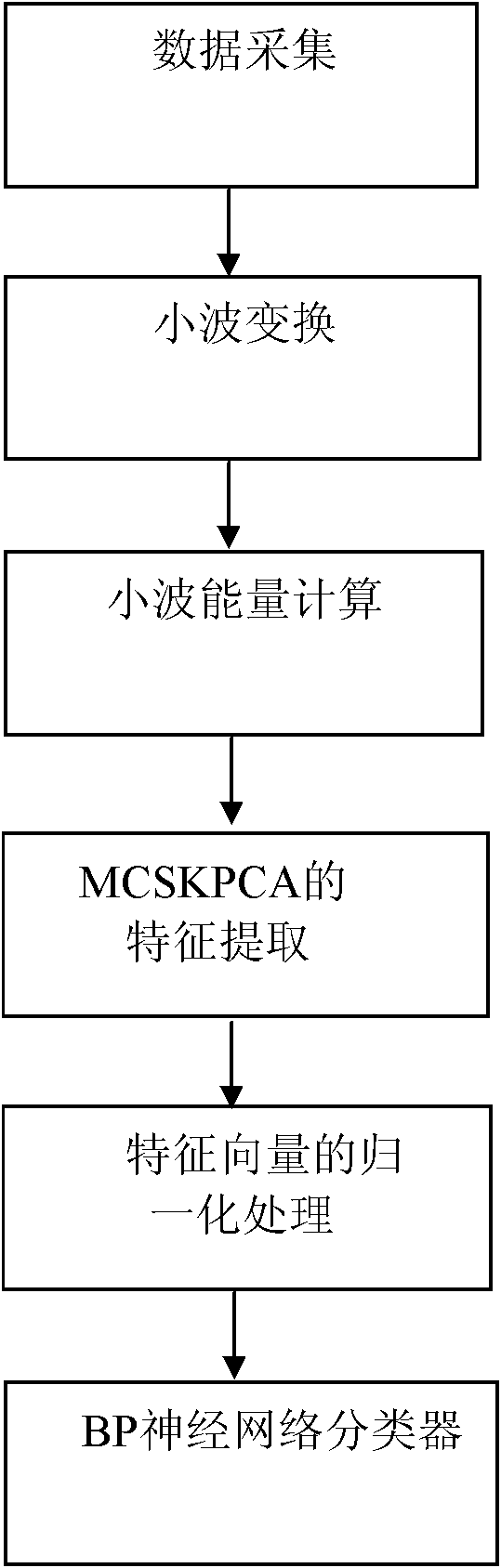

MCSKPCA based neural network fault diagnosis method for analog circuits

ActiveCN102279358ASimple calculationApplicable to real-time environmentAnalog circuit testingNeural learning methodsFeature vectorFeature extraction

Disclosed is an MCSKPCA based neural network fault diagnosis method for analog circuits, comprising acquiring the output voltage signal of an analog circuit to be diagnosed; performing wavelet transformation on the acquired output voltage signal; calculating the energy eigenvalues of the wavelet coefficients of the output voltage signal, obtained through the wavelet transformation; performing MCSKPCA feature extraction and dimensionality reduction on the energy eigenvalues, and obtaining an optical eigenvector; and sending the optical eigenvector to a BP neural network separator, and outputting a fault diagnosis result by the BP neural network separator. The method can be used for not only diagnosis of linear or nonlinear circuits and systems thereof, but also diagnosis of hard fault and soft fault in the linear or nonlinear circuits.

Owner:HUNAN UNIV

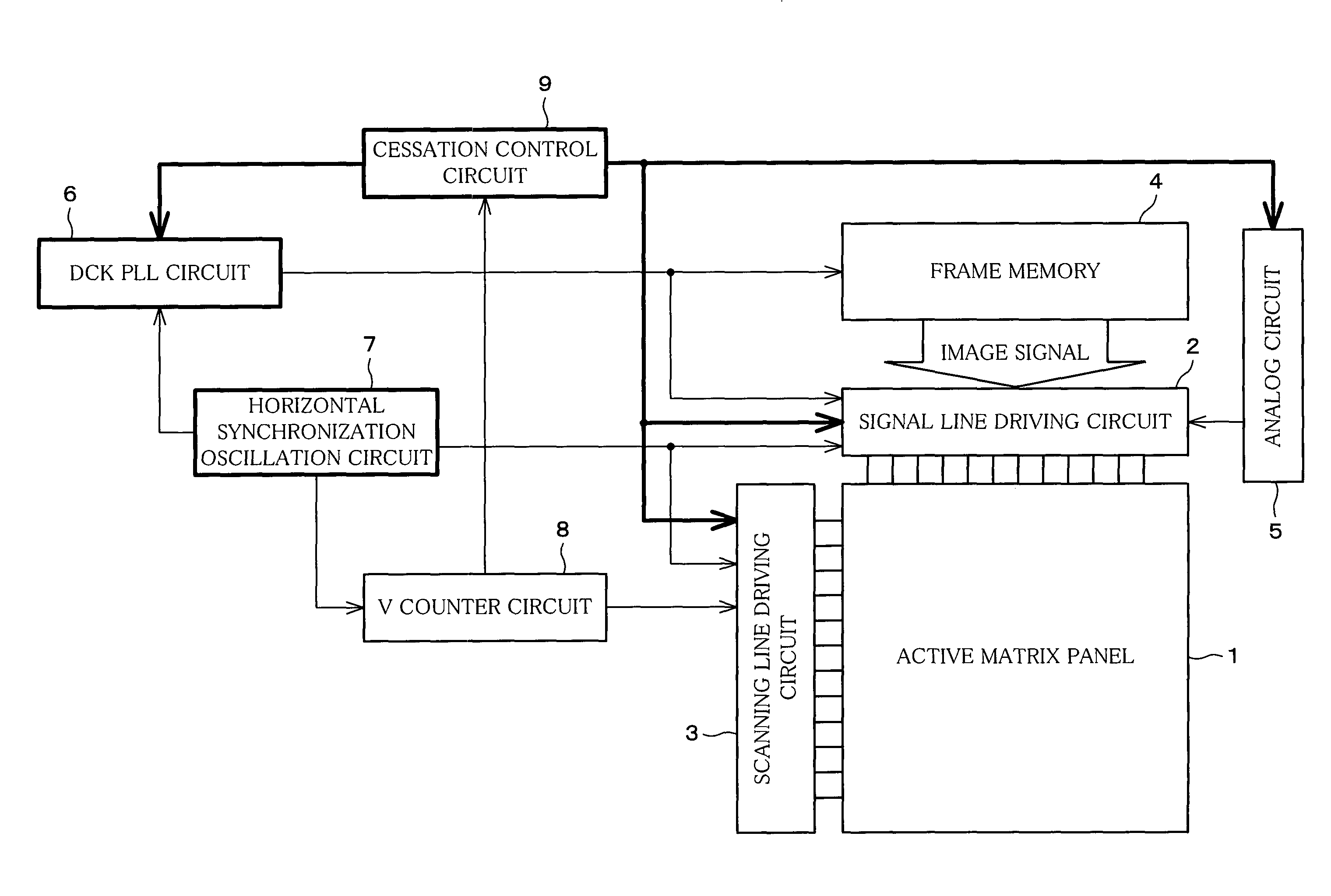

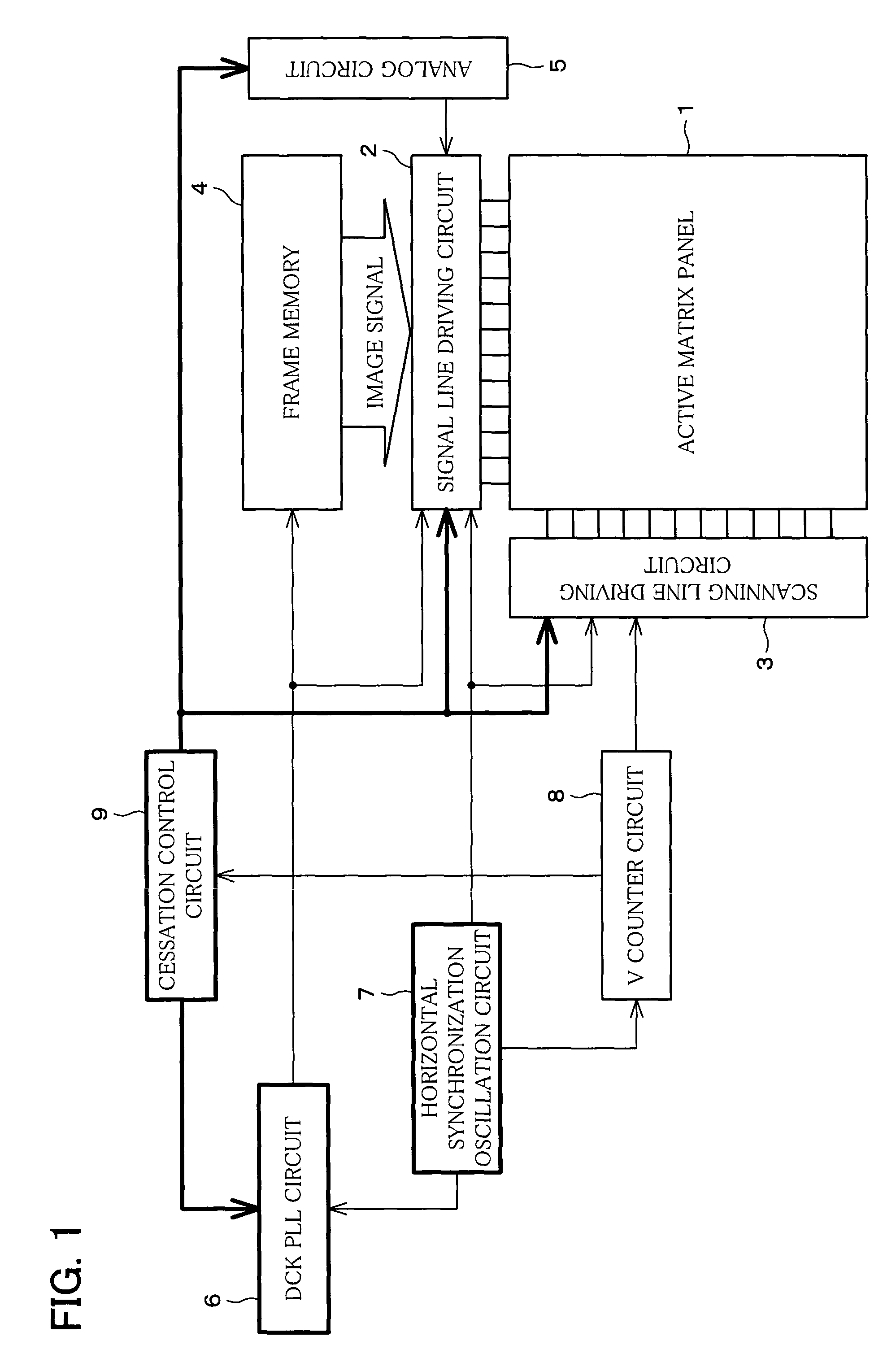

Display device and driving method thereof

ActiveUS7212185B2Reduce power consumptionEnergy efficient ICTCathode-ray tube indicatorsRefresh cycleActive matrix

A display device includes an inaction control circuit and a DCK-PLL circuit. The inaction control circuit stops driving of driving circuits, such as a signal line driving circuit, a scanning line driving circuit, analog circuit and the like, which are provided for driving an active matrix panel. The inaction control circuit stops the control circuits in a non-refresh period where all scanning lines become non-scanning state and provided between refresh periods for scanning a screen of the active matrix panel. The inaction control circuit also stops driving of the DCK-PLL circuit in the non-refresh period, in addition to stopping driving of the driving circuits.

Owner:SHARP KK

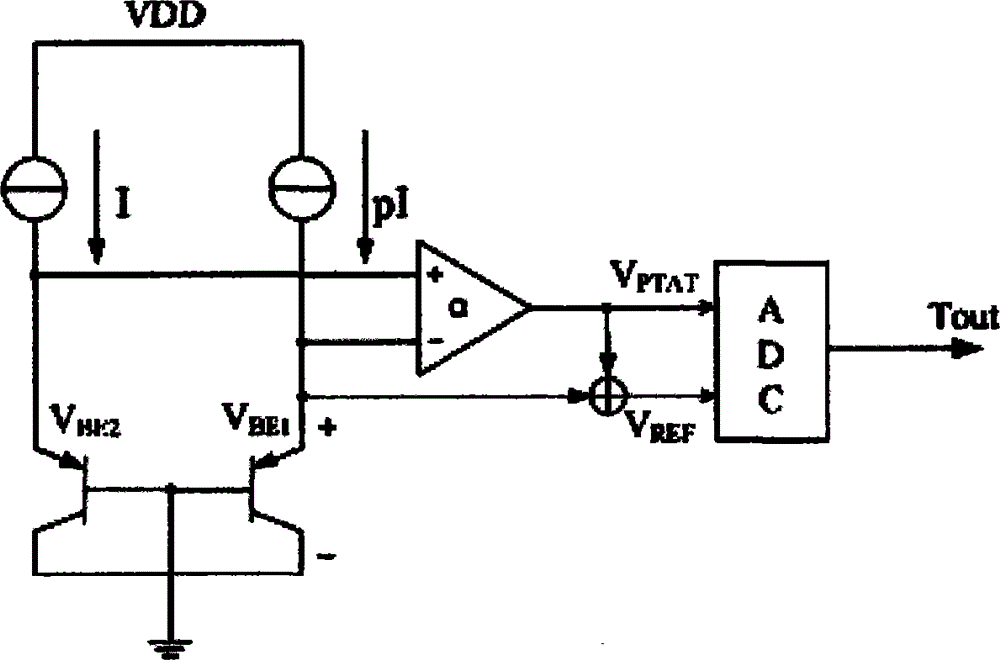

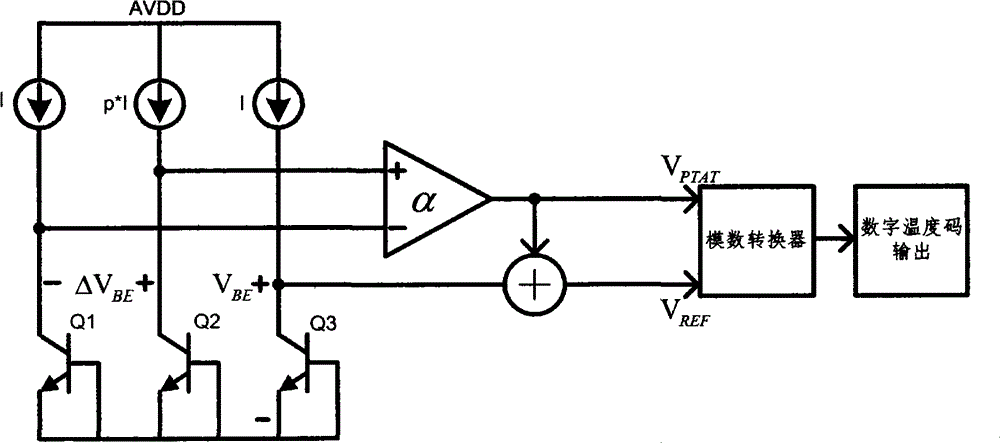

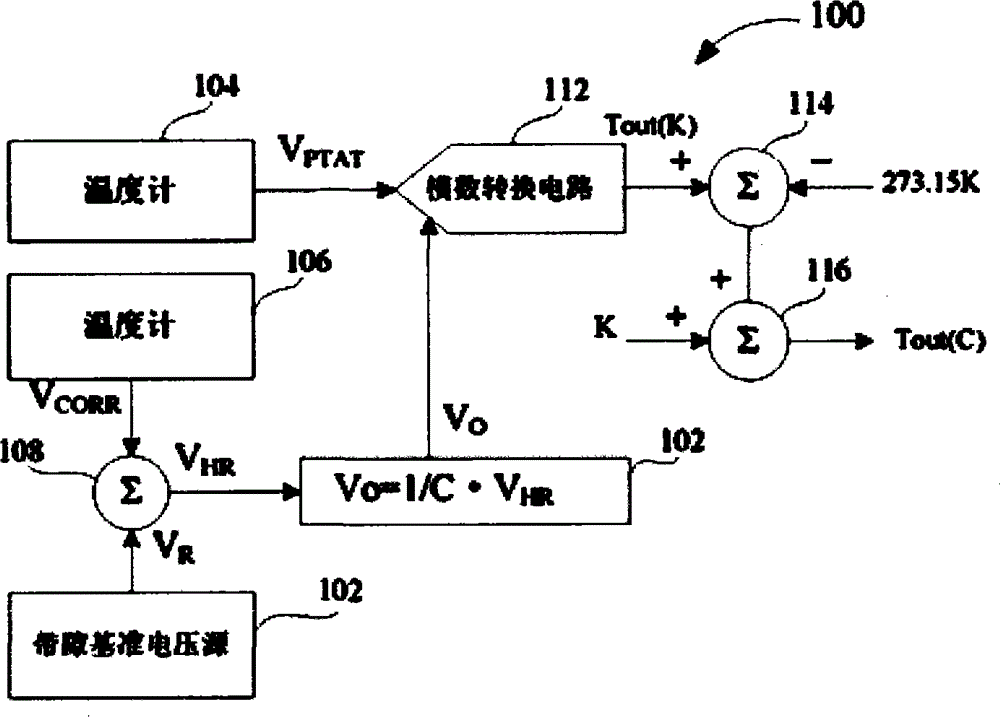

Temperature sensor applied to metering ammeter and temperature trimming method thereof

ActiveCN104807551AHigh precisionReduce design costThermometer detailsThermometers using electric/magnetic elementsShift registerCapacitance

The invention provides a temperature sensor applied to a metering ammeter. The temperature sensor comprises an analog circuit portion, a digital circuit portion and a user ARM portion. The analog circuit portion comprises a positive temperature coefficient current generator in direct-proportion current bias with an absolute temperature, a bias current mirror array, a low-temperature drift coefficient reference current source, a temperature-sensitive transistor and an analog-to-digital conversion integrator. The digital circuit portion comprises a switch control logic, a digital code output, a digital counter and a shift register. The analog-to-digital conversion integrator has a sampling capacitor and an integrating capacitor, of which the capacitance is same; and bias current of the temperature-sensitive transistor is biased by six unit current mirrors in turns in a proportion of 5:1. According to a temperature trimming method for the temperature sensor, the number of the bias current mirrors is 6, wherein 5 paths of currents are used for coarse tuning, and the other one path of current is used for fine tuning; when the output bias of the counter is relatively large, the 5 paths of coarse-tuning currents are used; and when the output of the counter is between the two paths of unit currents, fine tuning is used.

Owner:BEIJING XIAOCHENG TECH CO LTD

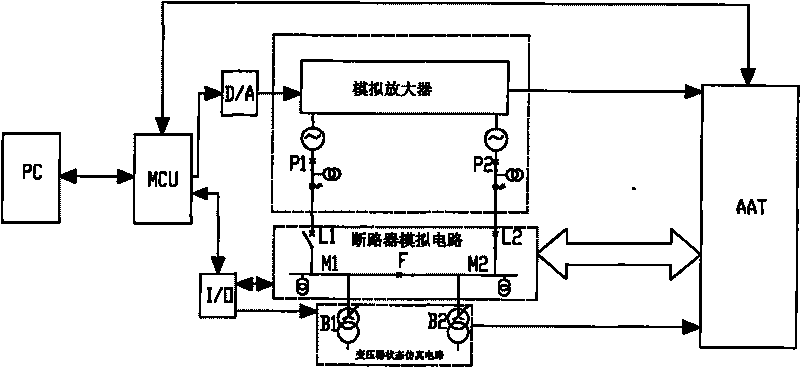

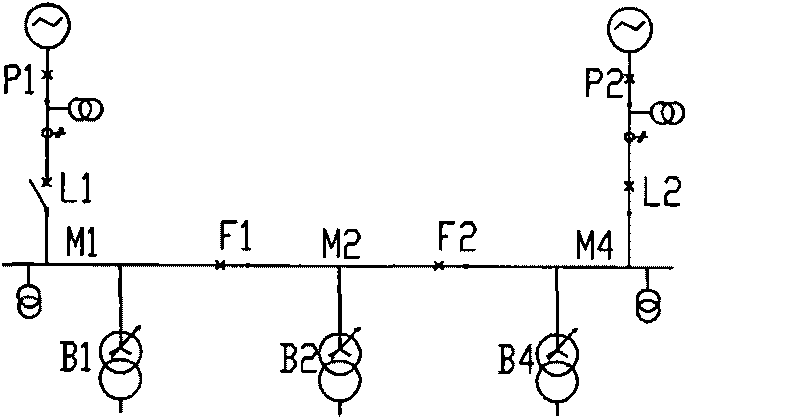

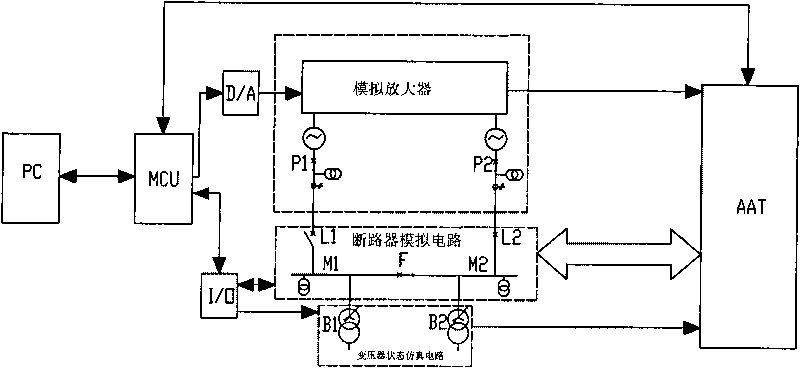

Spare automatic switching comprehensive tester

InactiveCN101750555AComprehensive and Accurate JudgmentComprehensive and accurate identificationElectrical testingCombined testDigital analog converter

The invention discloses a spare automatic switching comprehensive tester, and relates to a comprehensive tester of a spare automatic switching device in the field of an electrical power system and a power supply system. The spare automatic switching comprehensive tester can simulate a primary system operation state and a main transformation fault state and implement state detection on a detected spare automatic switching device comprehensively and intuitively on the premise of meeting the requirements of the prior art, and comprises an upper computer, a lower computer, an analogue amplifier, a circuit-breaker analogue circuit and a transformer state simulation circuit. The lower computer is connected with the analogue amplifier through a digital-to-analog converter and is connected with the circuit-breaker analogue circuit and the transformer state simulation circuit; the lower computer and the circuit-breaker analogue circuit are provided with a data interface which exchanges data with the detected spare automatic switching device bidirectionally; the analogue amplifier is provided with a voltage / current output port connected with the detected spare automatic switching device, and output ports P1 and P2 connected with the circuit-breaker analogue circuit; and the transformer state simulation circuit is provided with an interface through which a transformer state signal is transmitted to the detected spare automatic switching device unidirectionally, and output ports B1 and B2 connected with the circuit-breaker analogue circuit.

Owner:JIANGSU ELECTRIC POWER COMPANY YANGZHOU POWER

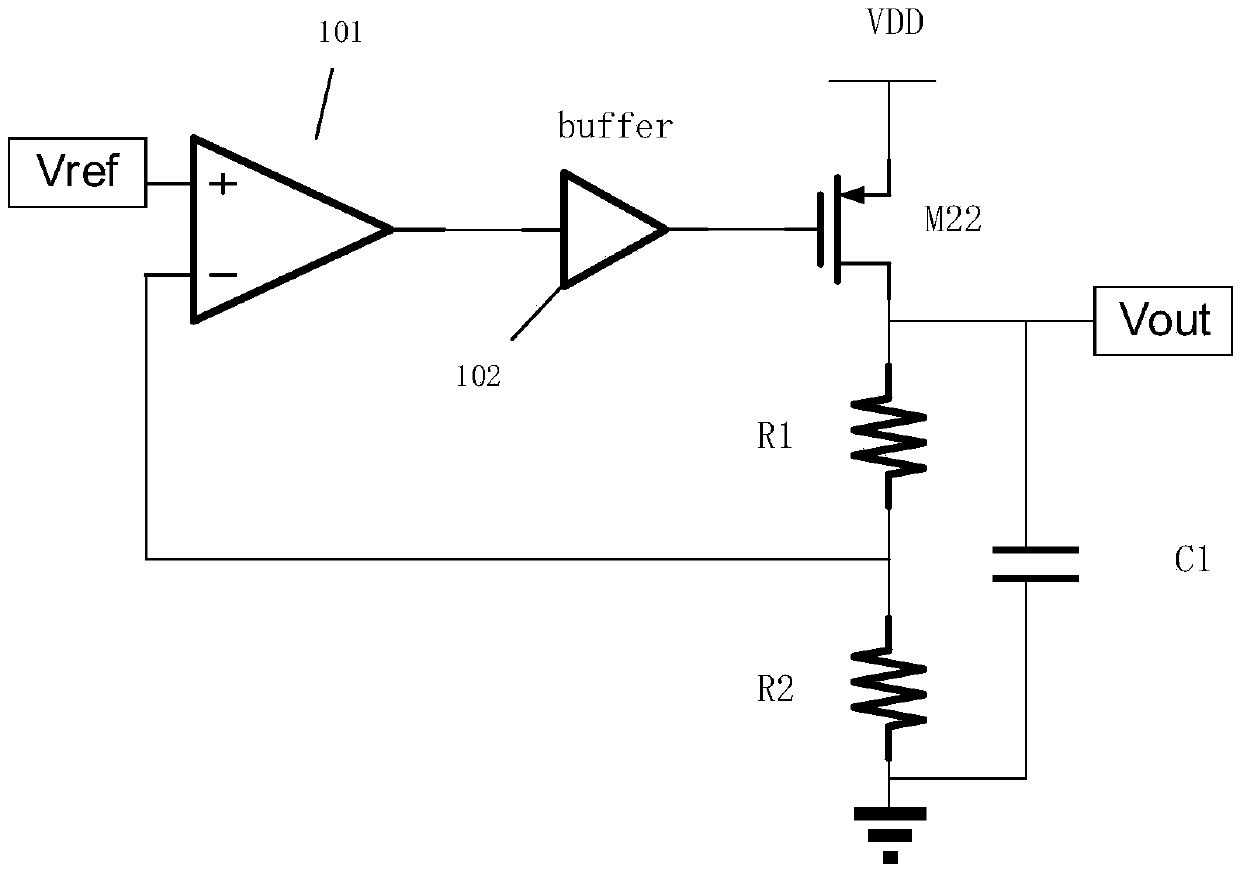

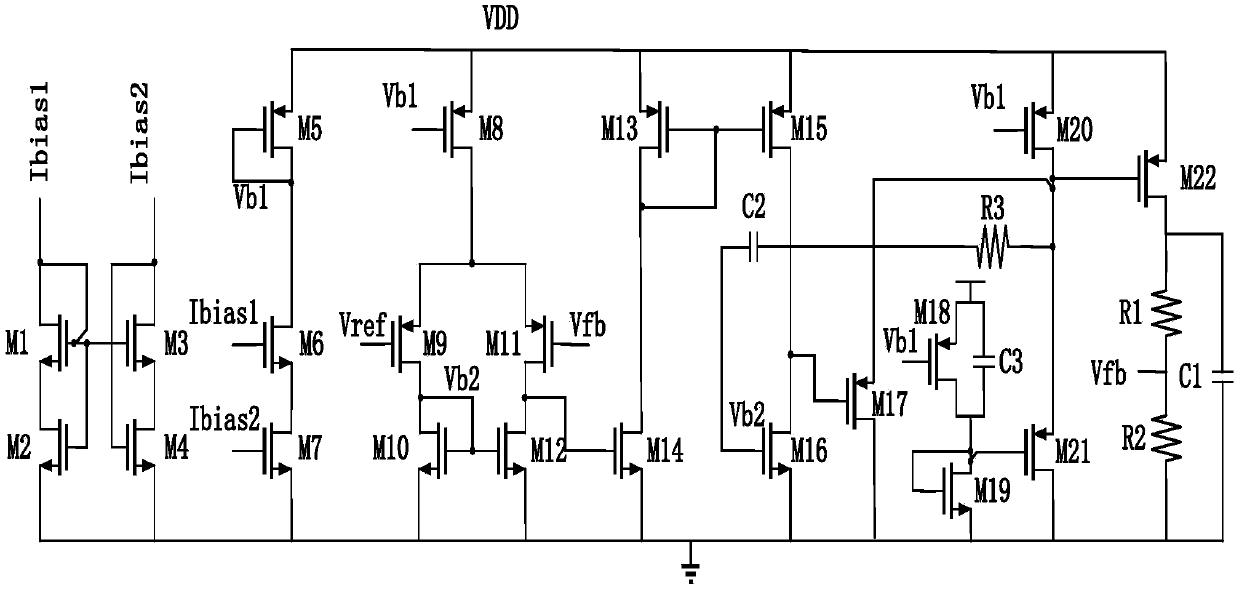

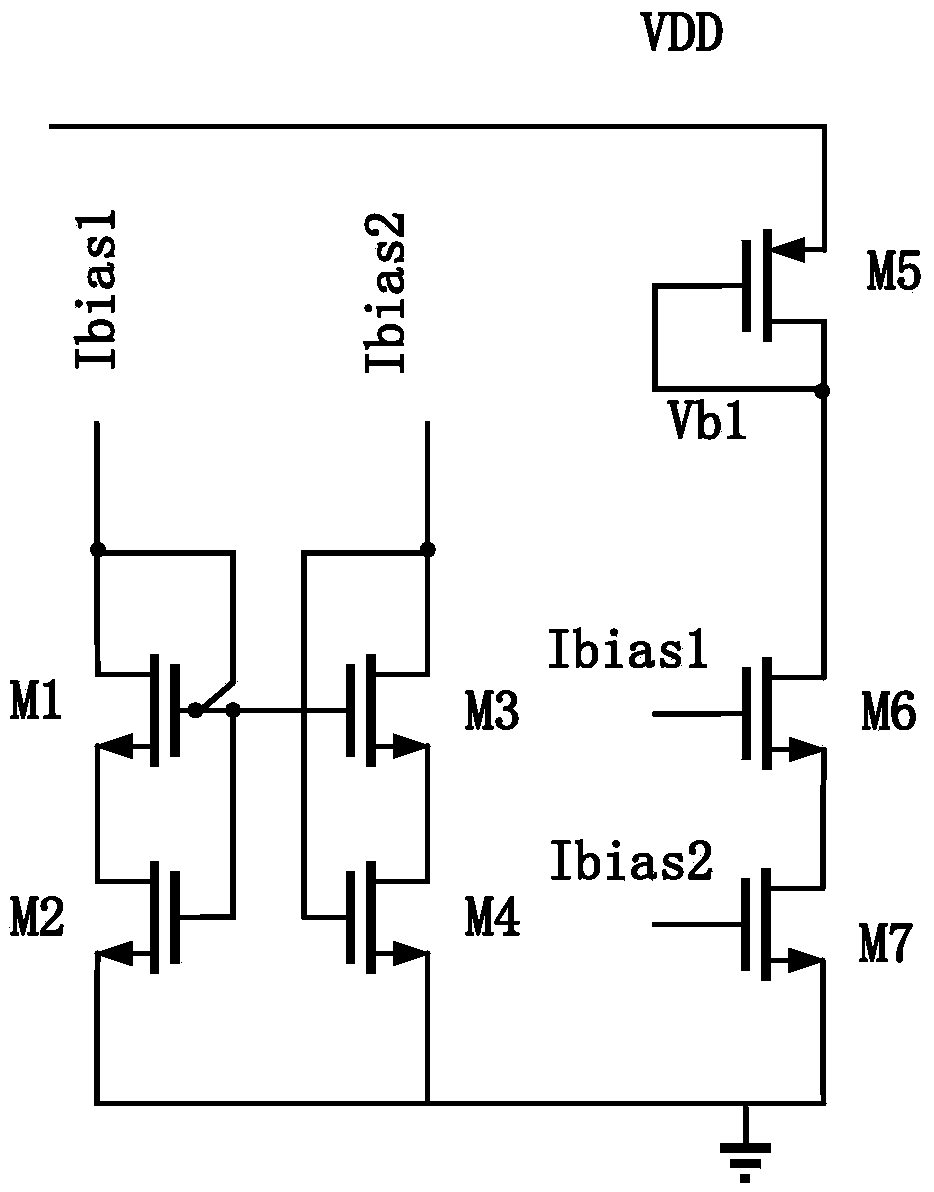

Low-dropout linear regulator circuit with high power supply rejection ratio

InactiveCN109683651AImprove power supply rejection ratioSimple structureElectric variable regulationLinear regulatorCapacitance

The invention provides a low-dropout linear regulator circuit with a high power supply rejection ratio, and belongs to the field of analog circuit integration. The low-dropout linear regulator circuitcomprises a bias module, an error amplifier, a buffer and an output stage, wherein the bias module provides bias voltage; a positive input end of the error amplifier is connected to reference voltage, a negative input end of the error amplifier is connected to feedback voltage, and an output end of the error amplifier passes through the buffer and the output stage to be connected to an output endof an LDO; the buffer comprises an amplification stage, a high-pass filter and a current source, and the amplification stage is connected between an input end and output end of the buffer; the current source is connected between power supply voltage and the output end of the buffer; the high-pass filter comprises a first NMOS transistor, a first PMOS transistor, a second PMOS transistor and a first capacitor, a grid electrode of the first PMOS transistor is connected with the bias voltage, a source electrode of the first PMOS transistor is connected with power supply voltage and is connectedto a drain electrode of the first PMOS transistor, a grid electrode of the second PMOS transistor and a grid electrode and drain electrode of the first NMOS transistor after passing through the firstcapacitor; a source electrode of the second PMOS transistor is connected with the output end of the buffer, and a drain electrode of the second PMOS transistor is connected with a source electrode ofthe first NMOS transistor and is grounded. The low-dropout linear regulator circuit with the high power supply rejection ratio improves the power supply rejection ratio.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

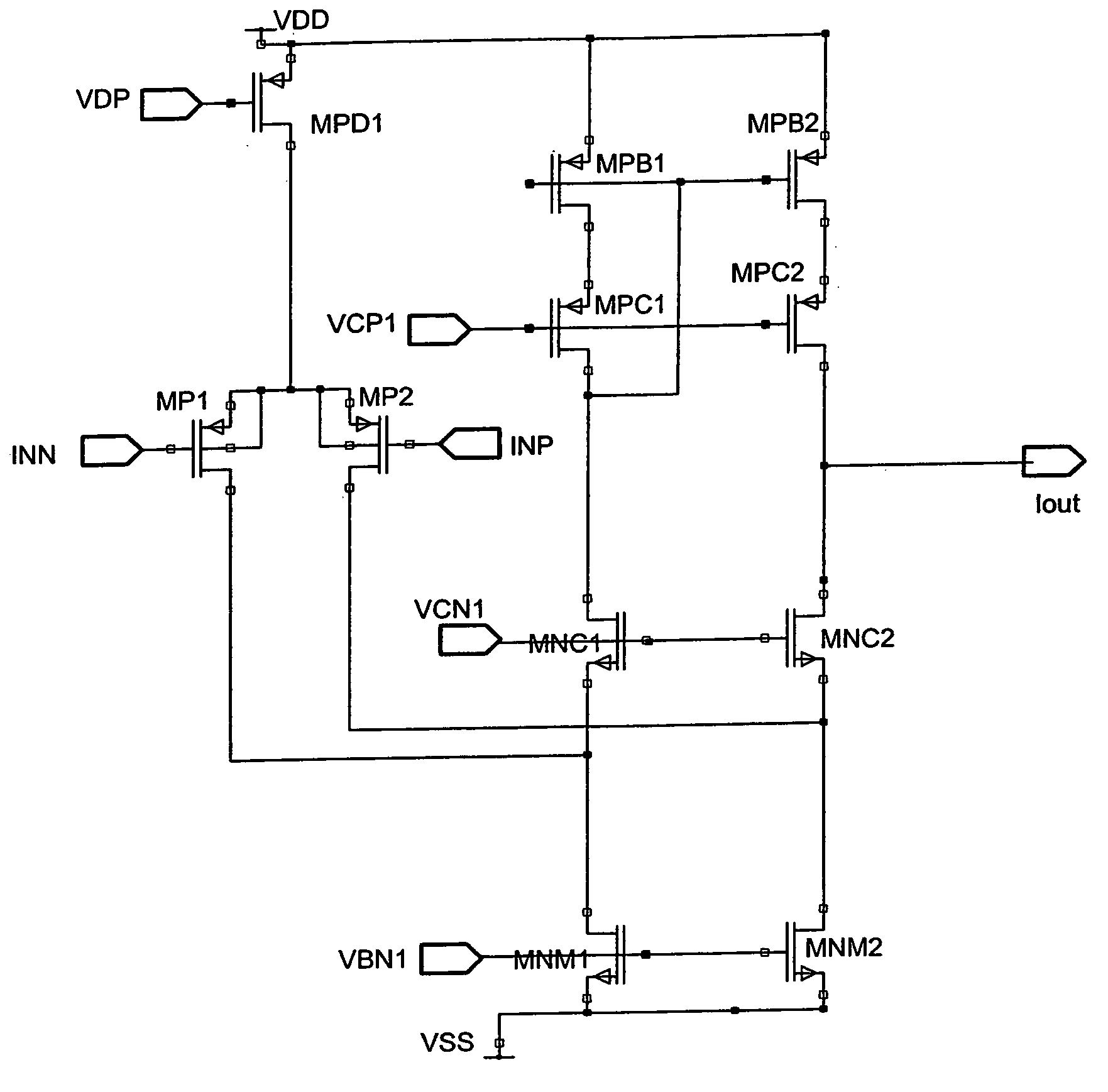

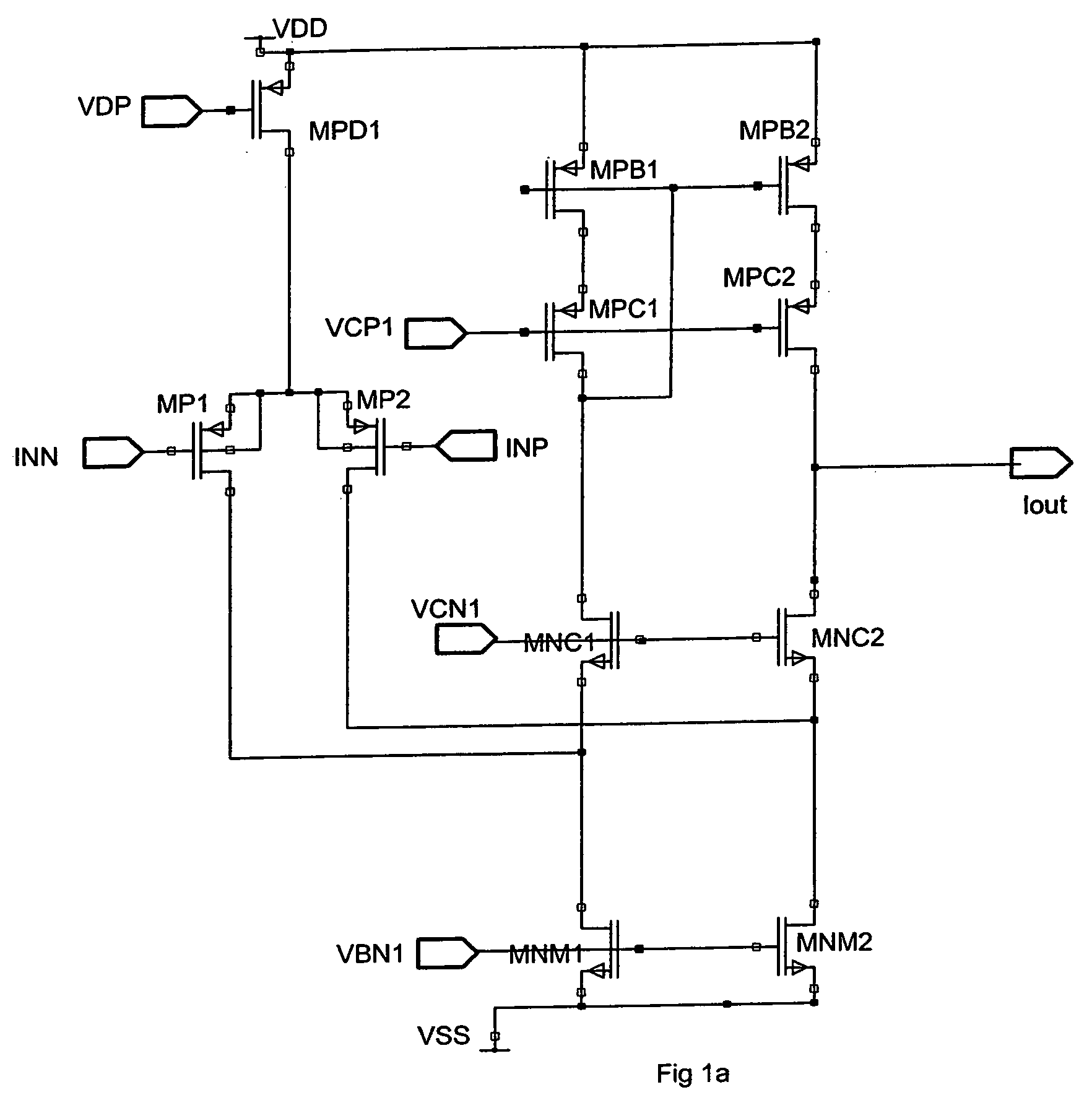

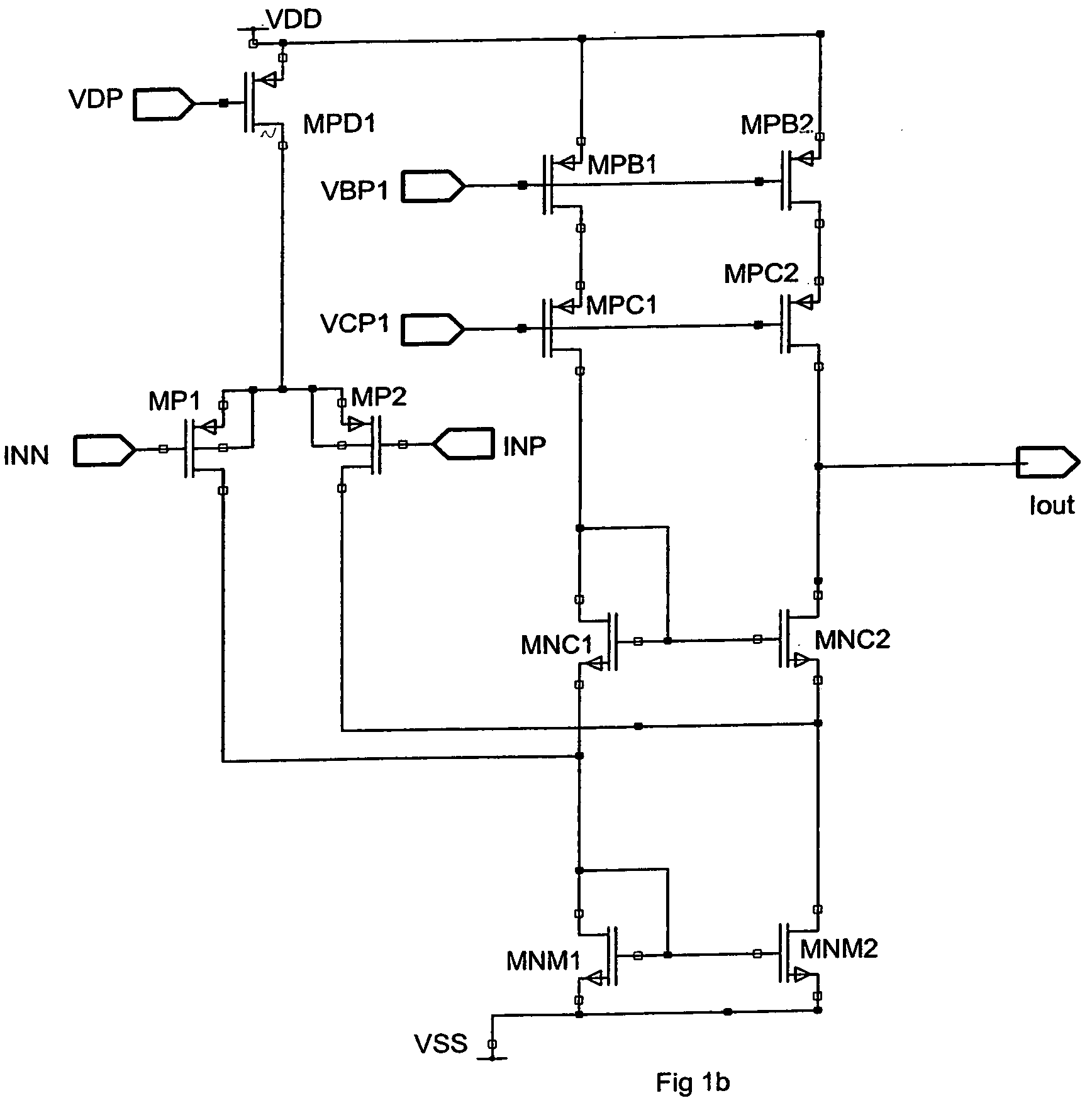

Low noise op amp

ActiveUS20050206454A1Reduce flicker noiseReduce thicknessAmplifier modifications to reduce noise influenceEmergency protective circuit arrangementsLow noiseAudio power amplifier

The present invention relates amplifiers using metal oxide semiconductor based integrated circuits. The present invention is particularly but not exclusively related to audio application mixed signal chips. The present invention provides an analogue circuit for processing analogue signals in an integrated circuit comprising a number of metal oxide semiconductor transistor devices, the circuit stage comprising a first said transistor device having a first oxide thickness, and a second said transistor device having a second and different oxide thickness. Preferably a cascode based op amp structure is implemented.

Owner:CIRRUS LOGIC INC

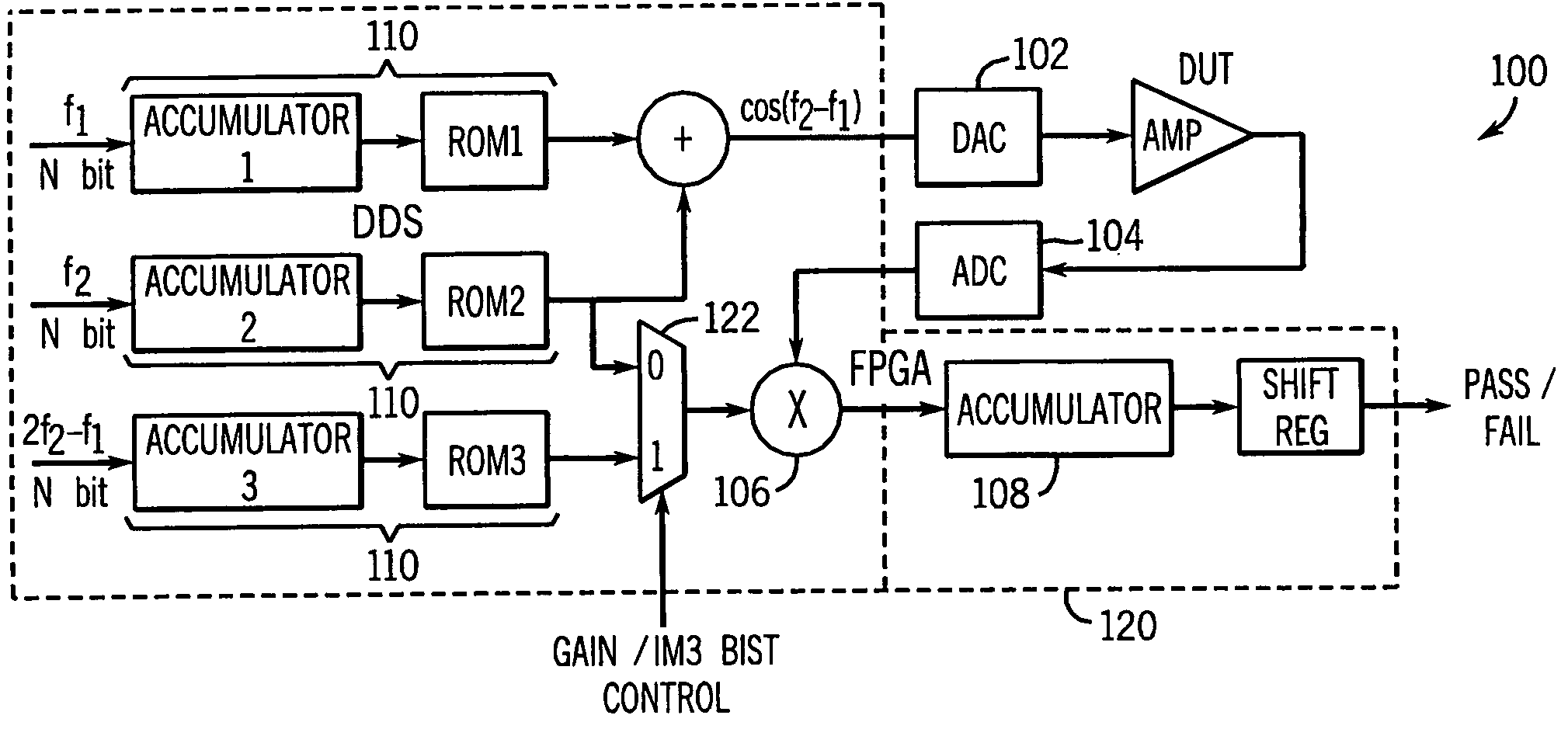

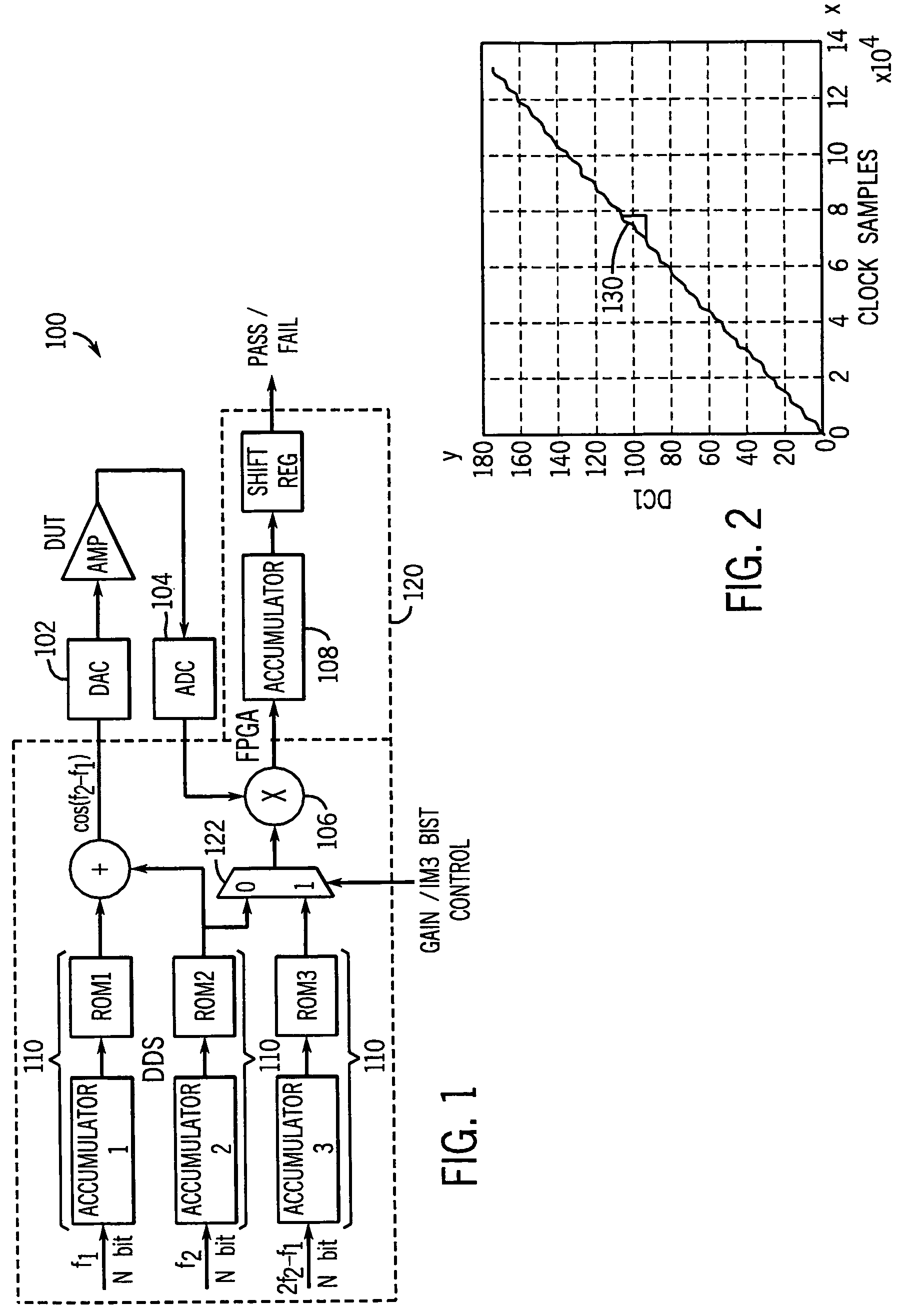

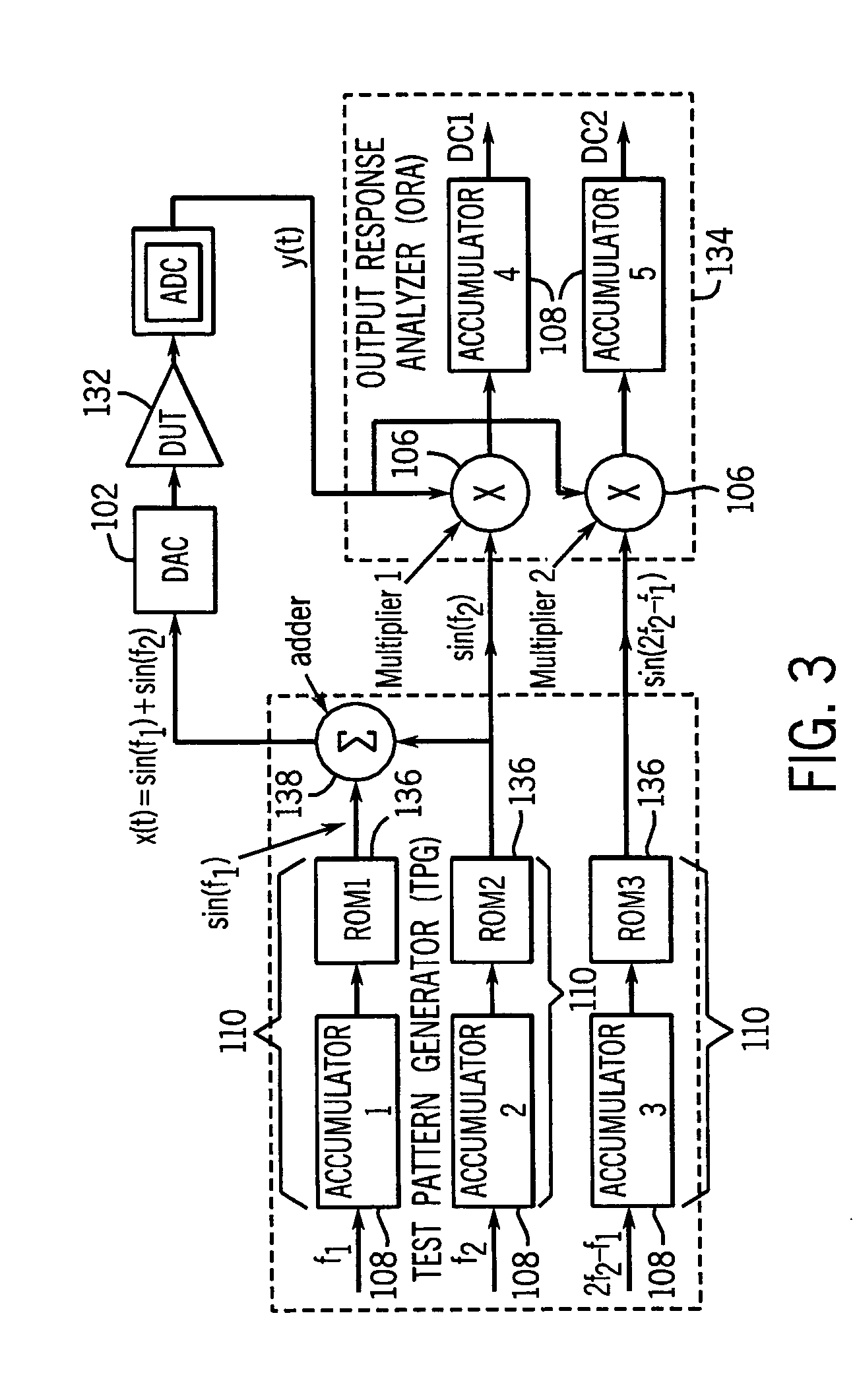

Automatic analog test and compensation with built-in pattern generator and analyzer

A built-in-self test (BIST) scheme for analog circuitry functionality tests such as frequency response, gain, cut-off frequency, signal-to-noise ratio, and linearity measurement. The BIST scheme utilizes a built-in direct digital synthesizer (DDS) as the test pattern generator that can generate various test waveforms such as chirp, ramp, step frequency, two-tone frequencies, sweep frequencies, MSK, phase modulation, amplitude modulation, QAM and other hybrid modulations. The BIST scheme utilizes a multiplier followed by an accumulator as the output response analyzer (ORA). The multiplier extracts the spectrum information at the desired frequency without using Fast Fourier Transform (FFT) and the accumulator picks up the DC component by averaging the multiplier output.

Owner:AUBURN UNIV

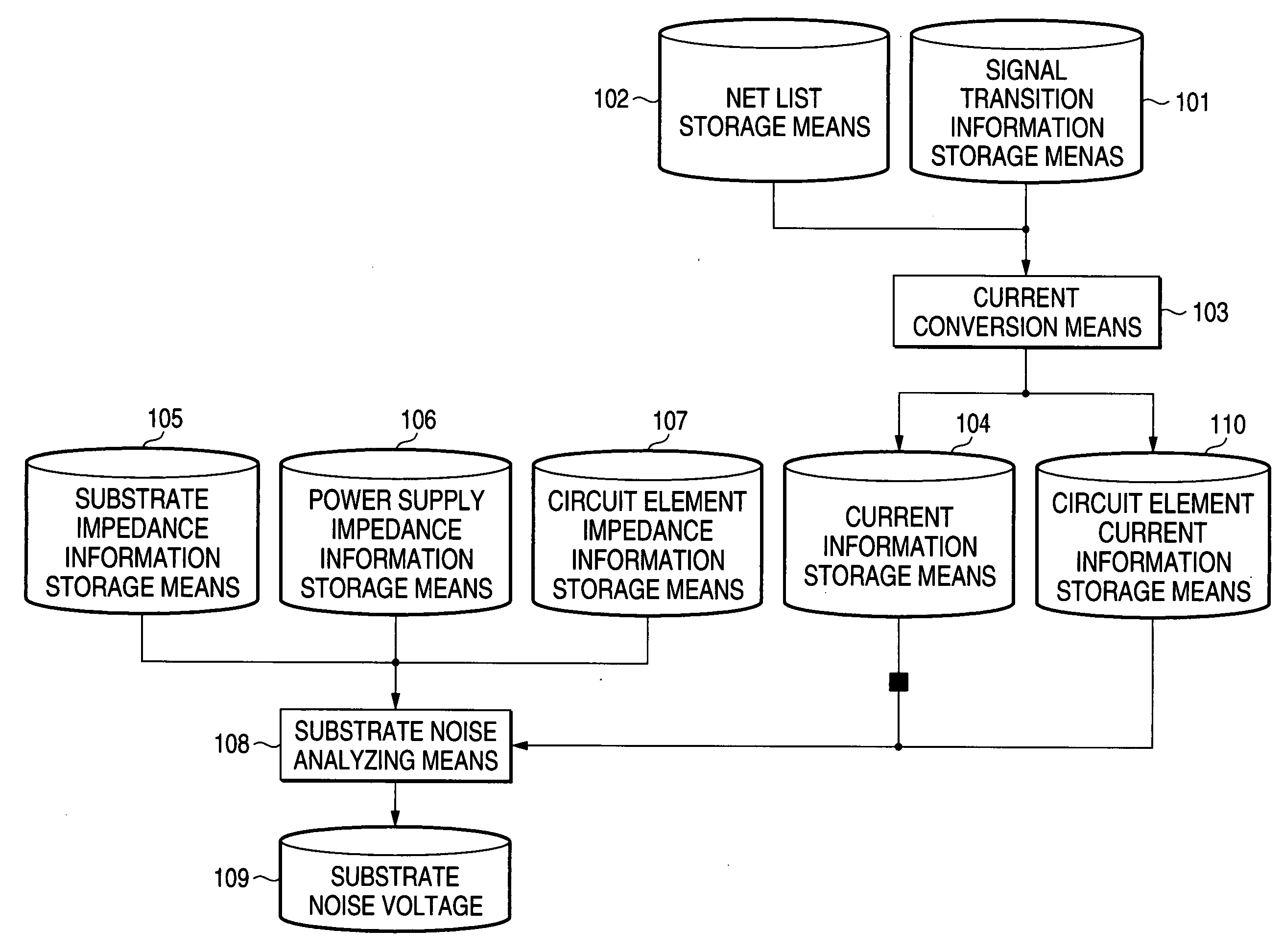

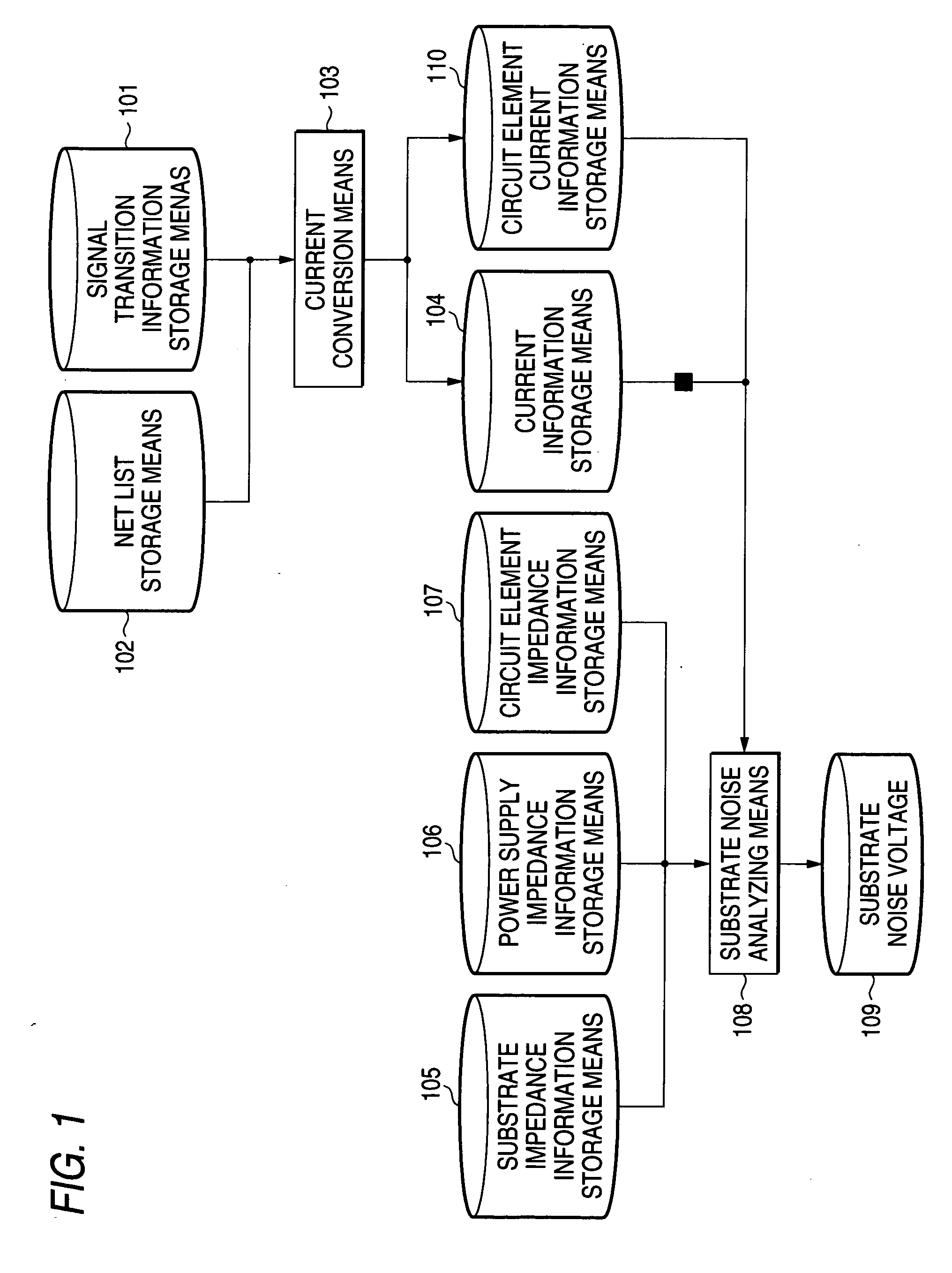

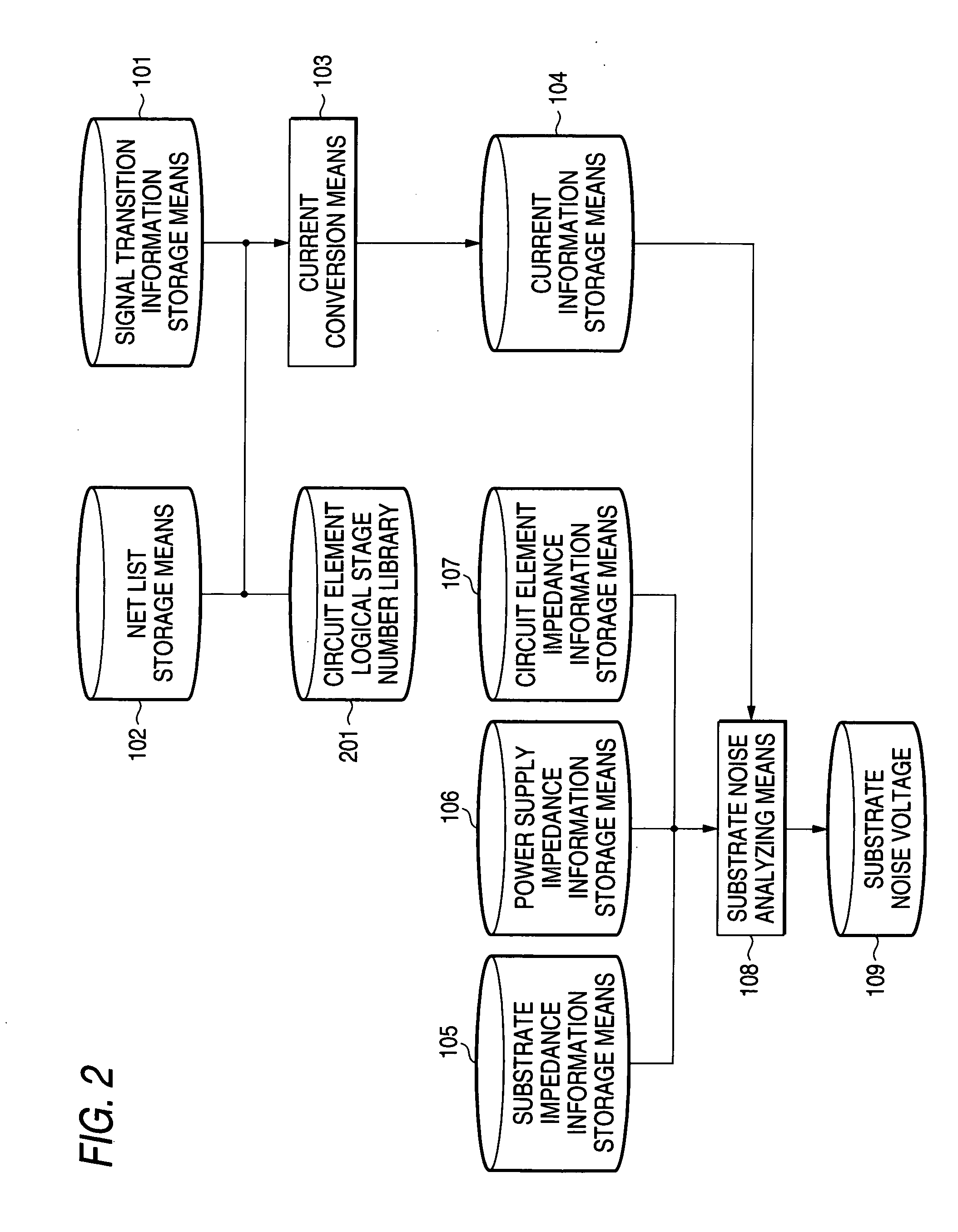

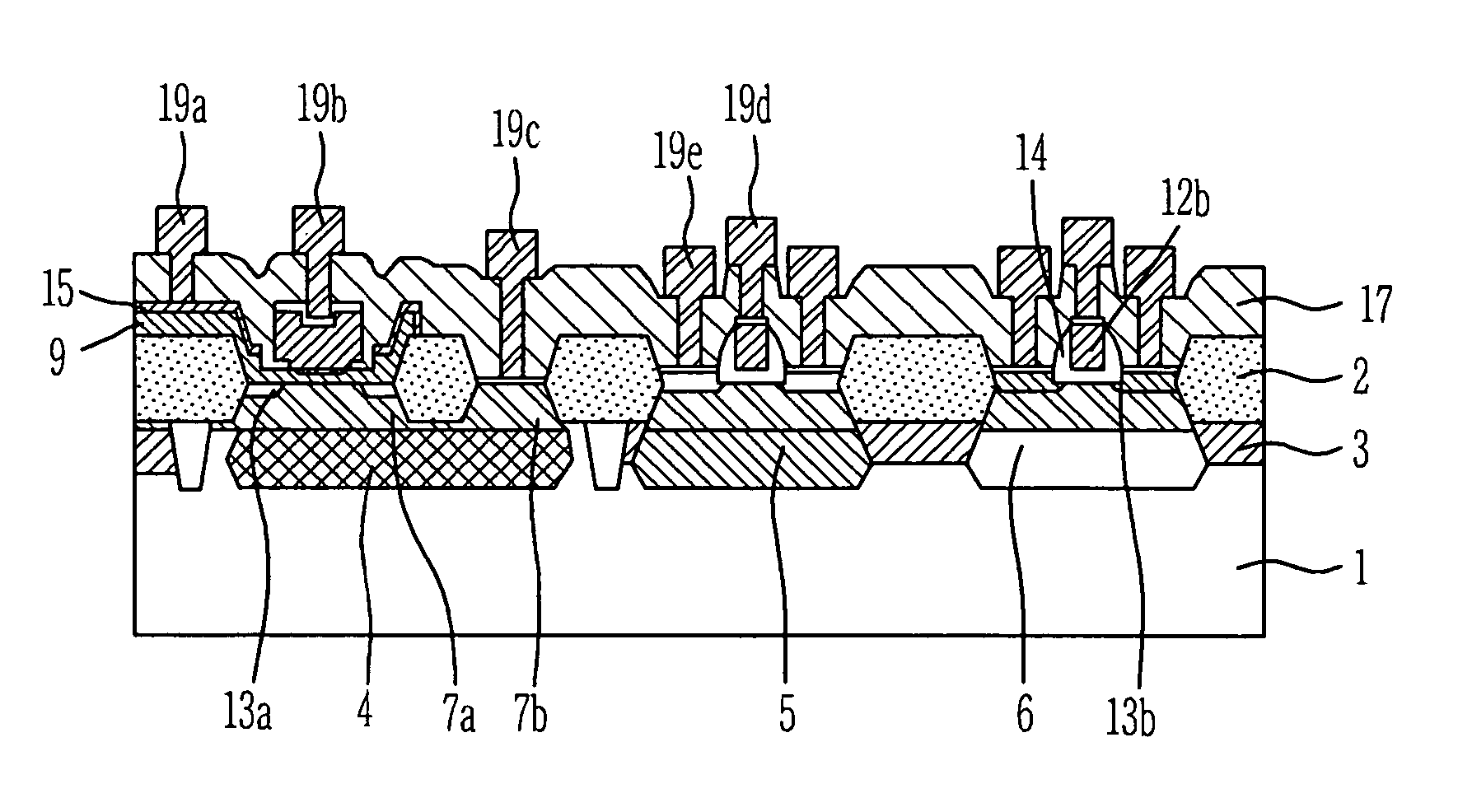

Substrate noise analyzing method for semiconductor integrated circuit, semiconductor integrated circuit, and substrate noise analyzing device for semiconductor integrated circuit

InactiveUS20050005254A1High-speed analysisDetecting faulty computer hardwareSemiconductor/solid-state device manufacturingCapacitanceEngineering

In substrate noise analysis for a semiconductor integrated circuit, it takes long to calculate the amount of current input to the substrate and substrate potential fluctuations in an analog circuit to which the current is propagated in combination with impedance / power supply resistance of the substrate including a large scale RC circuit network. The amount of calculation is reduced in calculating current passed to power supply / ground by adding triangles having areas corresponding to power consumption separately for rising / falling in logical changes in gate level simulation. The amount of calculation is reduced by summing current, interface capacitance, interface resistance, power supply resistance, ground resistance, power supply voltage fluctuations, and ground voltage fluctuations on a basis of block, instance or simultaneous operation. Since the calculation amount is reduced, it takes a shorter period to apply substrate noise analysis. In addition, the elements for calculation are also reduced, and therefore substrate noise analysis can be applied to a large scale semiconductor integrated circuit.

Owner:PANASONIC CORP

Method of fabricating SiGe Bi-CMOS device

InactiveUS7115459B2High frequencyIncrease contactSolid-state devicesSemiconductor/solid-state device manufacturingHeterojunctionElectrical resistance and conductance

Provided is a method of fabricating a silicon germanium (SiGe) Bi-CMOS device. In the fabrication method, the source and drain of the CMOS device is formed using a silicon germanium (SiGe) heterojunction, instead of silicon, thereby preventing a leakage current resulting from a parasitic bipolar operation. Further, since the source and drain is connected with an external interconnection through the nickel (Ni) silicide layer, the contact resistance is reduced, thereby preventing loss of a necessary voltage for a device operation and accordingly, making it possible to enable a low voltage and low power operation and securing a broad operation region even in a low voltage operation of an analogue circuit.

Owner:ELECTRONICS & TELECOMM RES INST

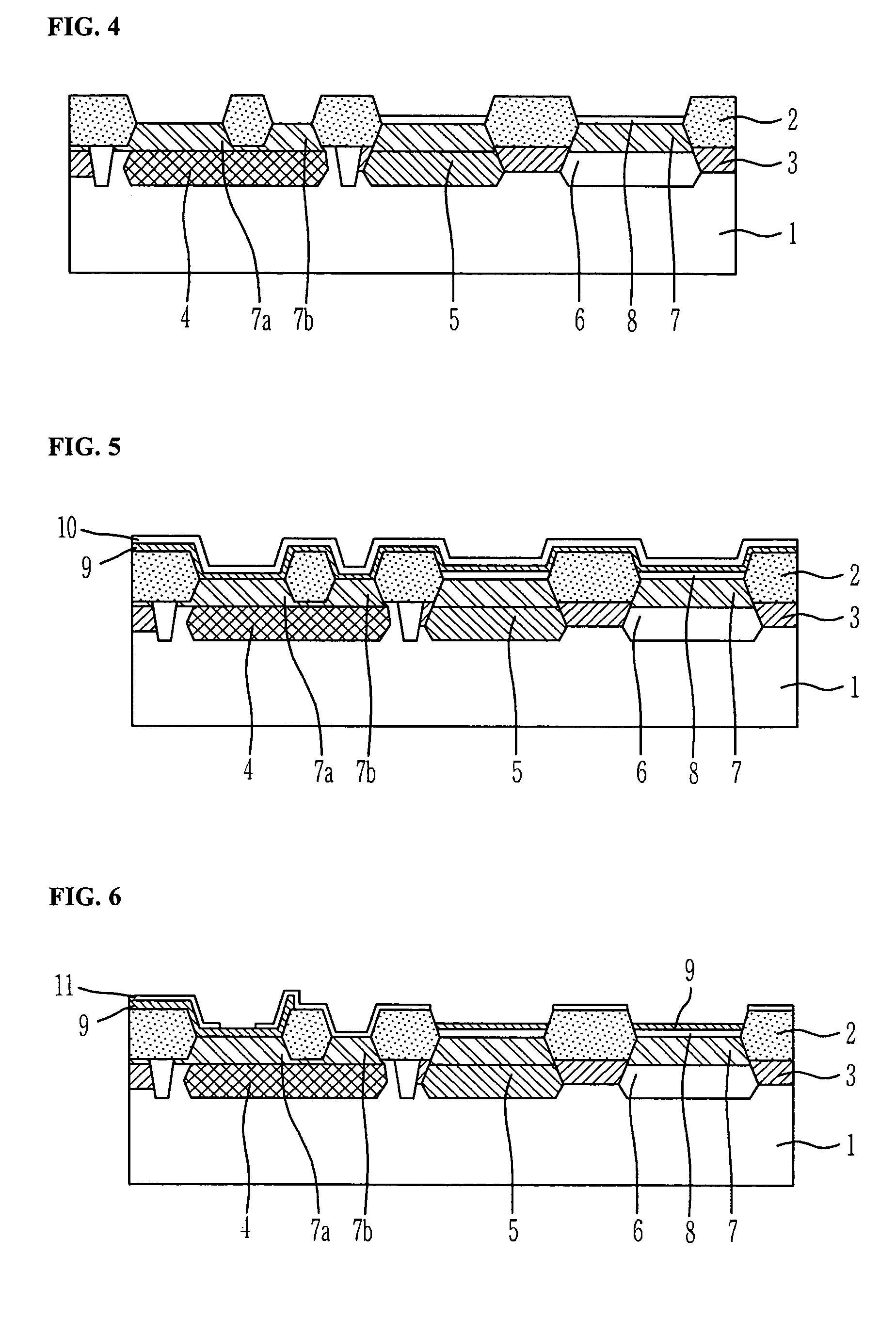

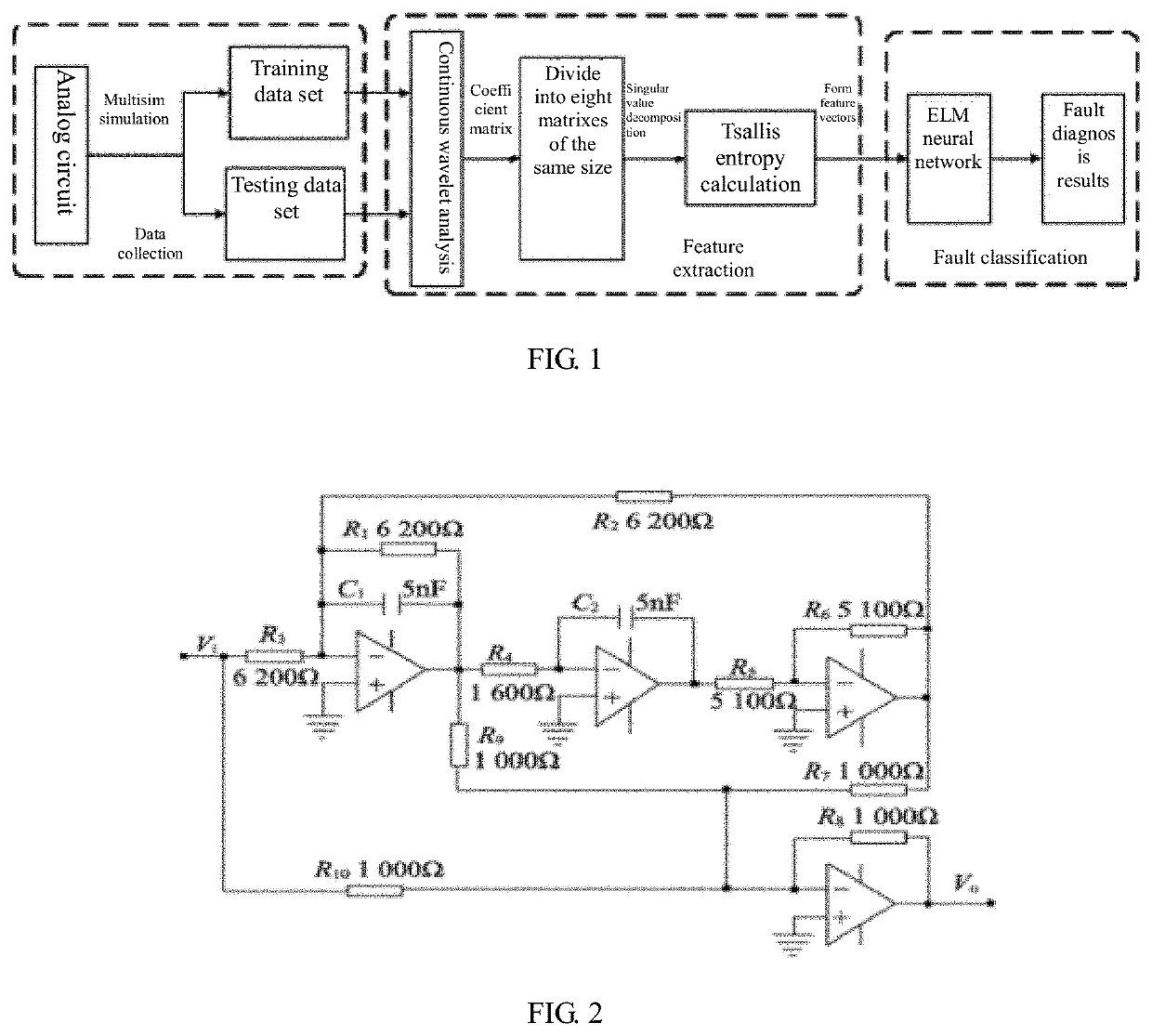

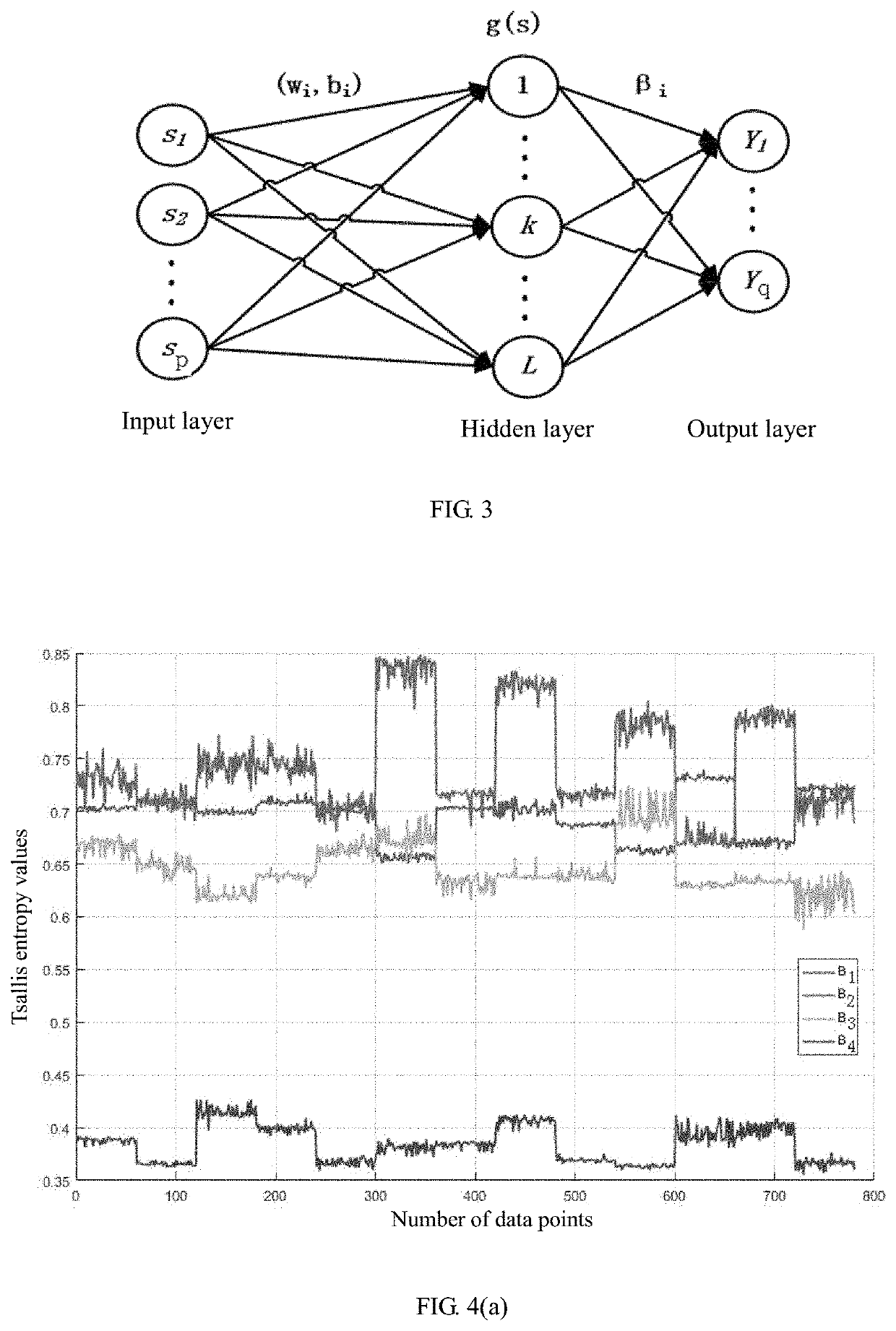

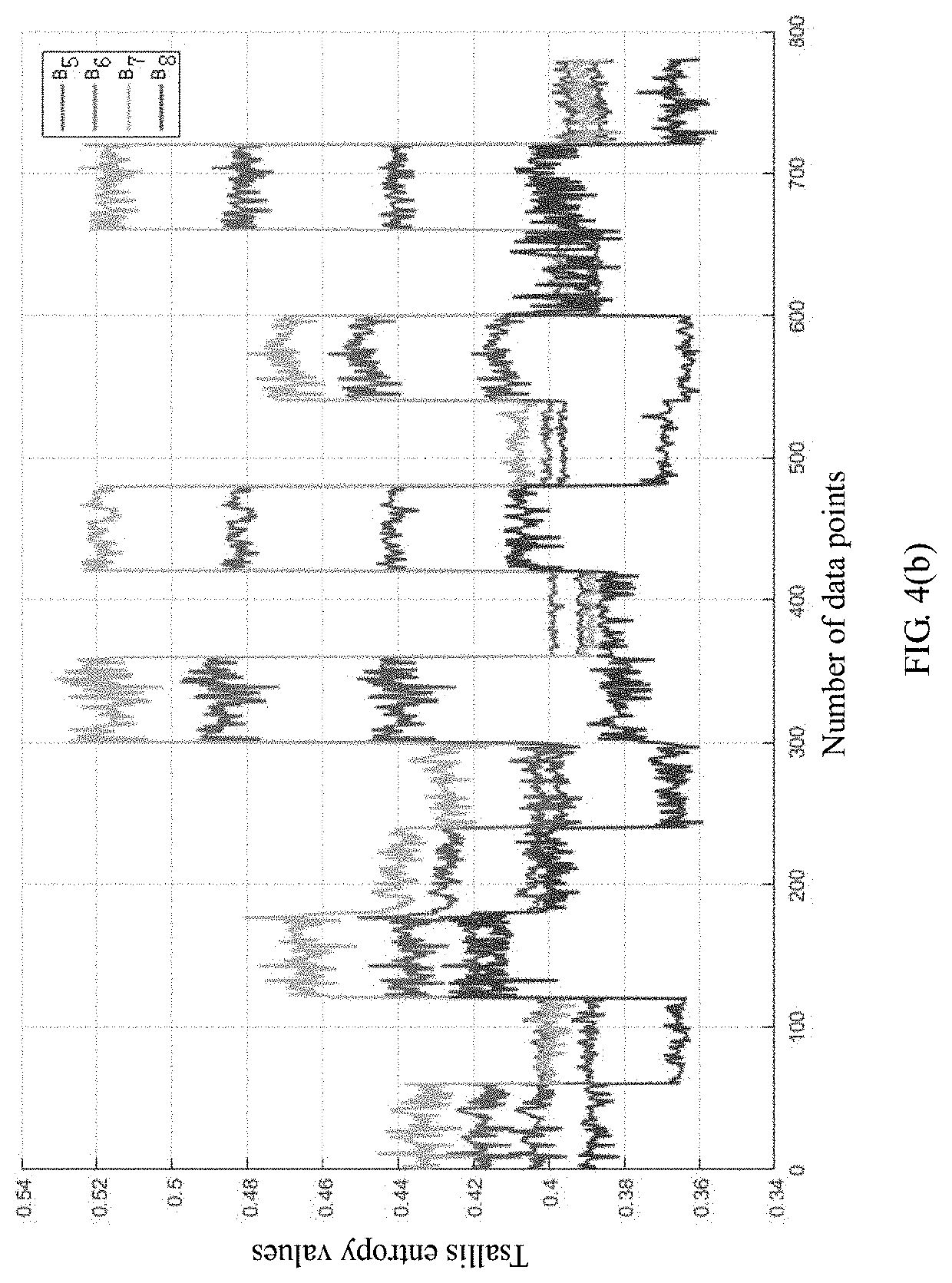

Analog-circuit fault diagnosis method based on continuous wavelet analysis and elm network

ActiveUS20200300907A1Fault classificationEfficiently and quickly with networkAnalog circuit testingSingular value decompositionData set

An analog-circuit fault diagnosis method based on continuous wavelet analysis and an ELM network comprises: data acquisition: performing data sampling on output responses of an analog circuit respectively through Multisim simulation to obtain an output response data set; feature extraction: performing continuous wavelet analysis by taking the output response data set of the circuit as training and testing data sets respectively to obtain a wavelet time-frequency coefficient matrix, dividing the coefficient matrix into eight sub-matrixes of the same size, and performing singular value decomposition on the sub-matrixes to calculate a Tsallis entropy for each sub-matrix to form feature vectors of corresponding faults; and fault classification: submitting the feature vector of each sample to the ELM network to implement accurate and quick fault classification. The method of the invention has a better effect on extracting the circuit fault features and can be used to implement circuit fault classification accurately and efficiently.

Owner:HEFEI UNIV OF TECH

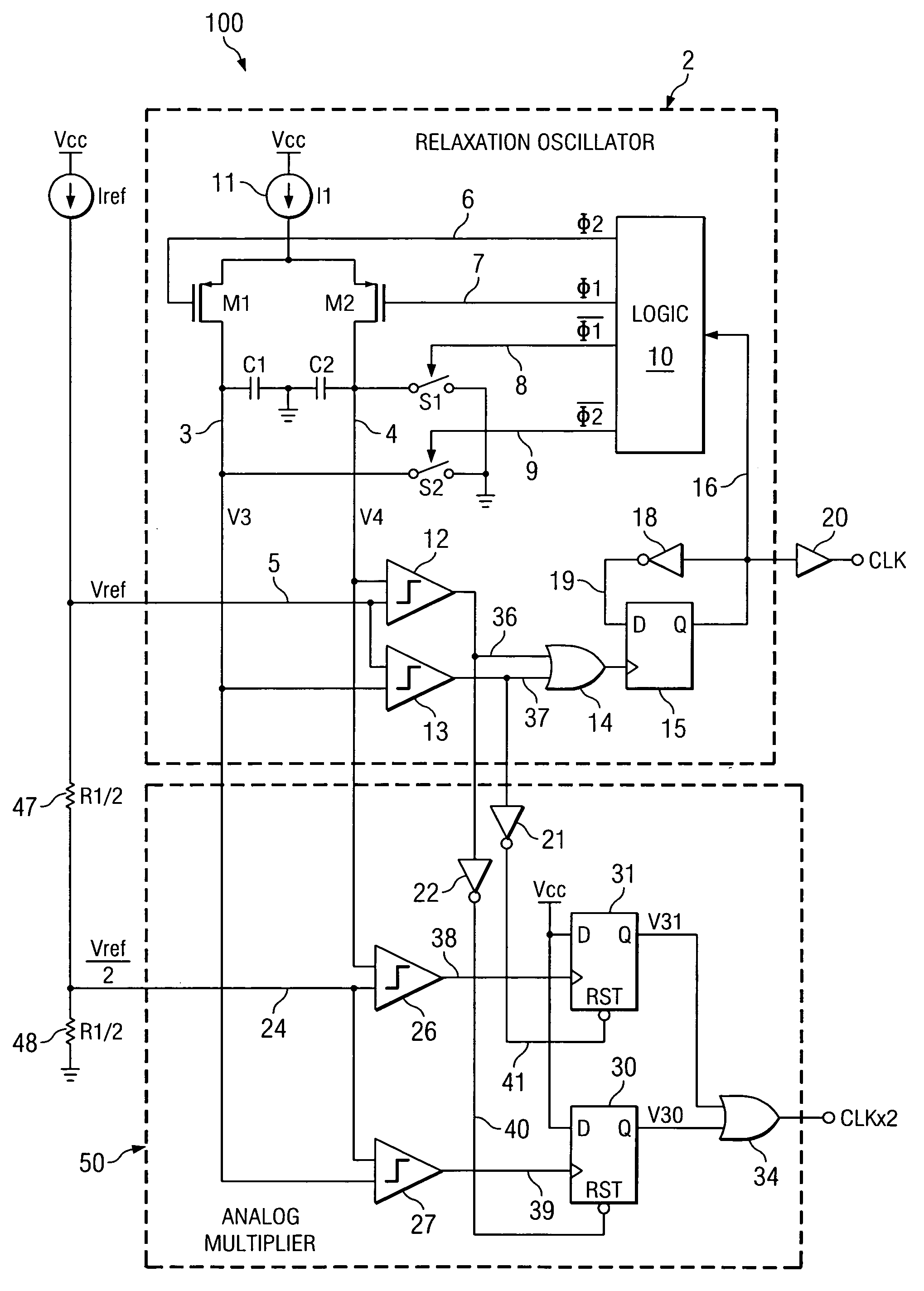

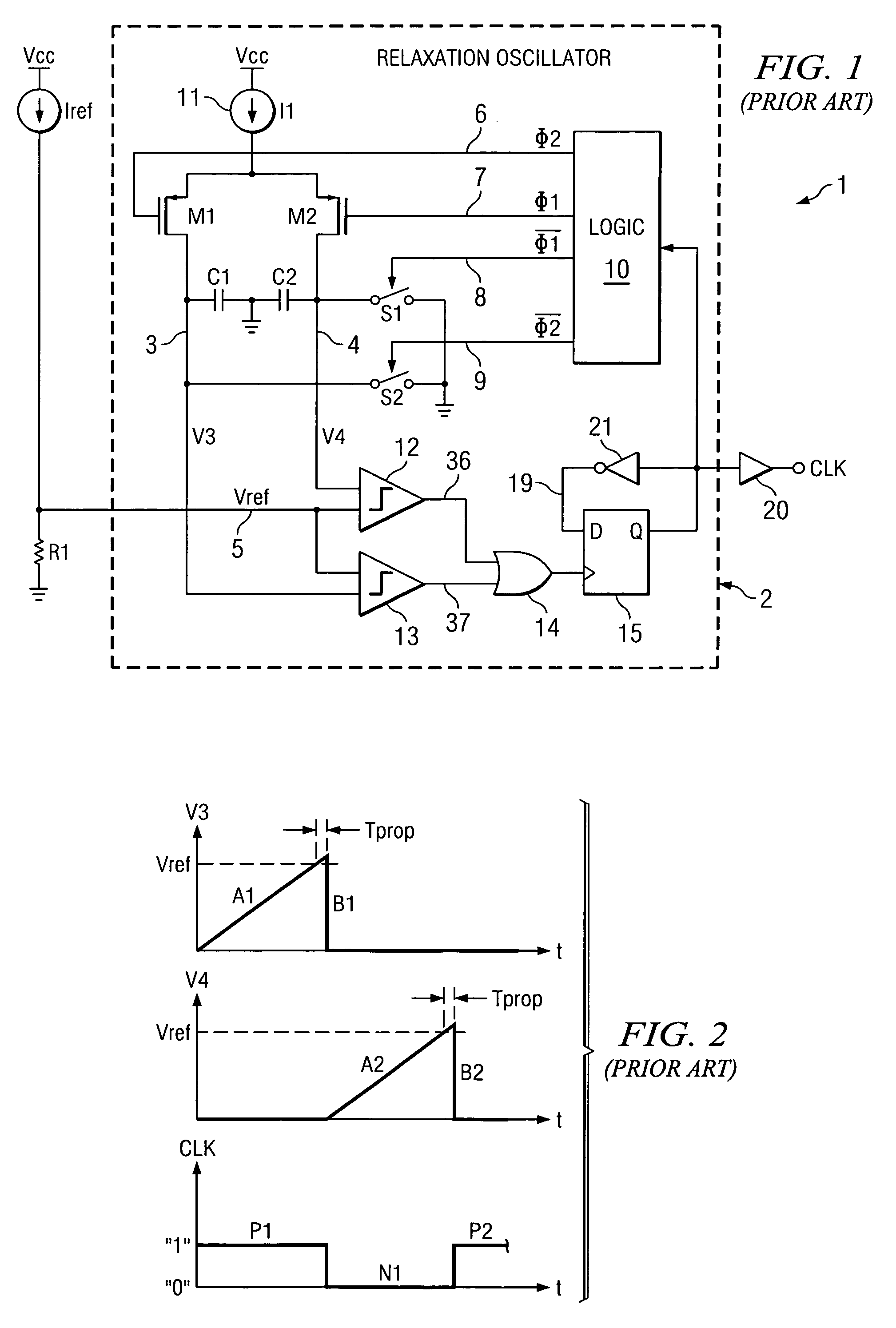

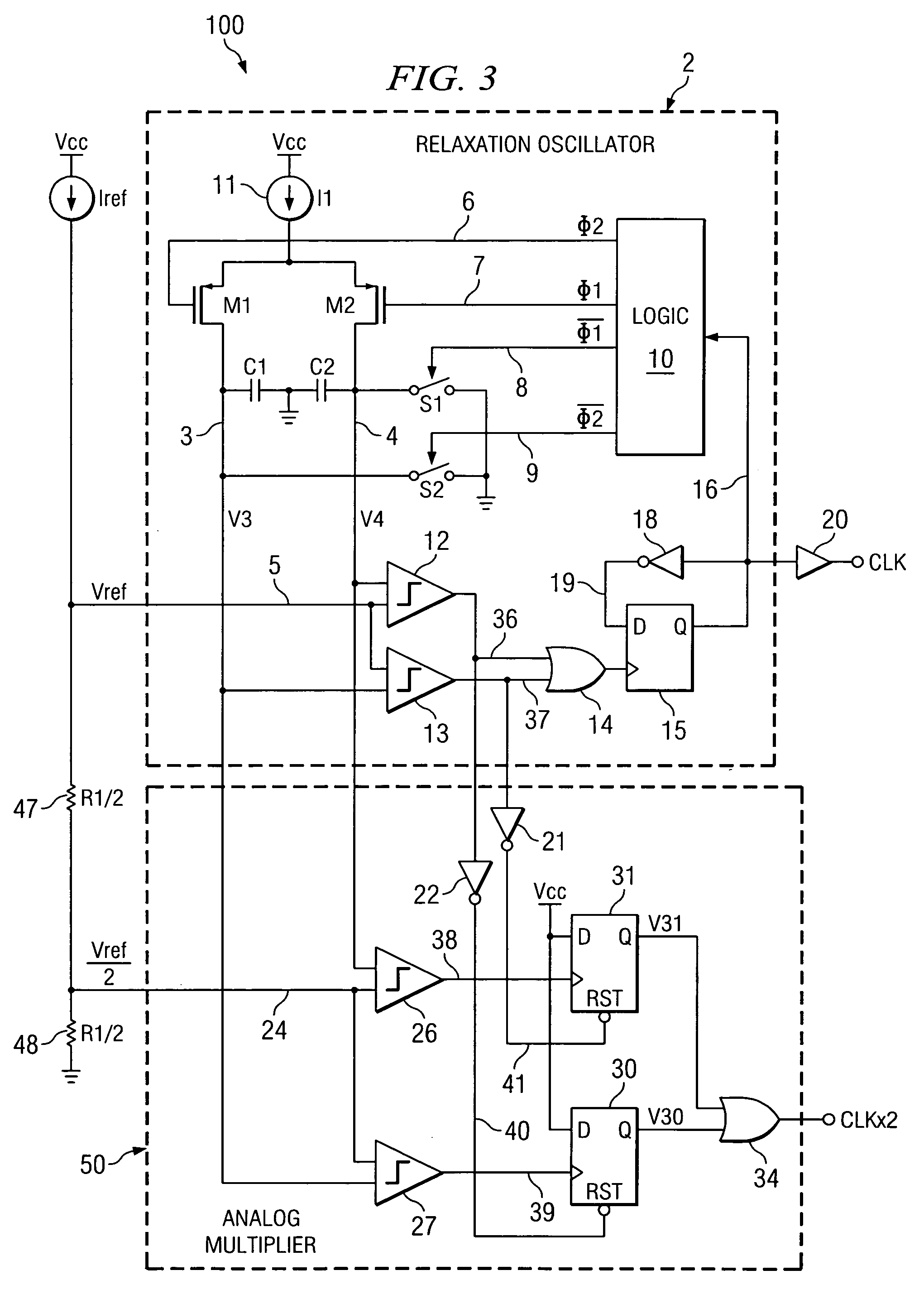

Analog circuit and method for multiplying clock frequency

ActiveUS20070279137A1Improve accuracyPulse generation by bipolar transistorsOscillations generatorsClock rateVoltage reference

A signal generating circuit includes a relaxation oscillator operating to alternately generate a first ramp signal that is periodic at a frequency of the relaxation oscillator and a second ramp signal that is periodic at the frequency of the relaxation oscillator and is out of phase with respect to the first ramp signal The first ramp signal is compared to a first reference voltage and the state of a first flip-flop is changed if the first ramp signal exceeds the first reference voltage. The second ramp signal is compared to the first reference voltage and the state of a second flip-flop is changed if the second ramp signal exceeds the first reference voltage. The first flip-flop is reset in response to a first level of the first ramp signal and the second flip-flop is reset in response to a second level of the second ramp signal. A logical ORing function is performed on an output of the first flip-flop and an output of the second flip-flop to produce an output signal having a frequency that is a multiple of the relaxation oscillator frequency.

Owner:TEXAS INSTR INC