Patents

Literature

112 results about "Nonlinear circuits" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

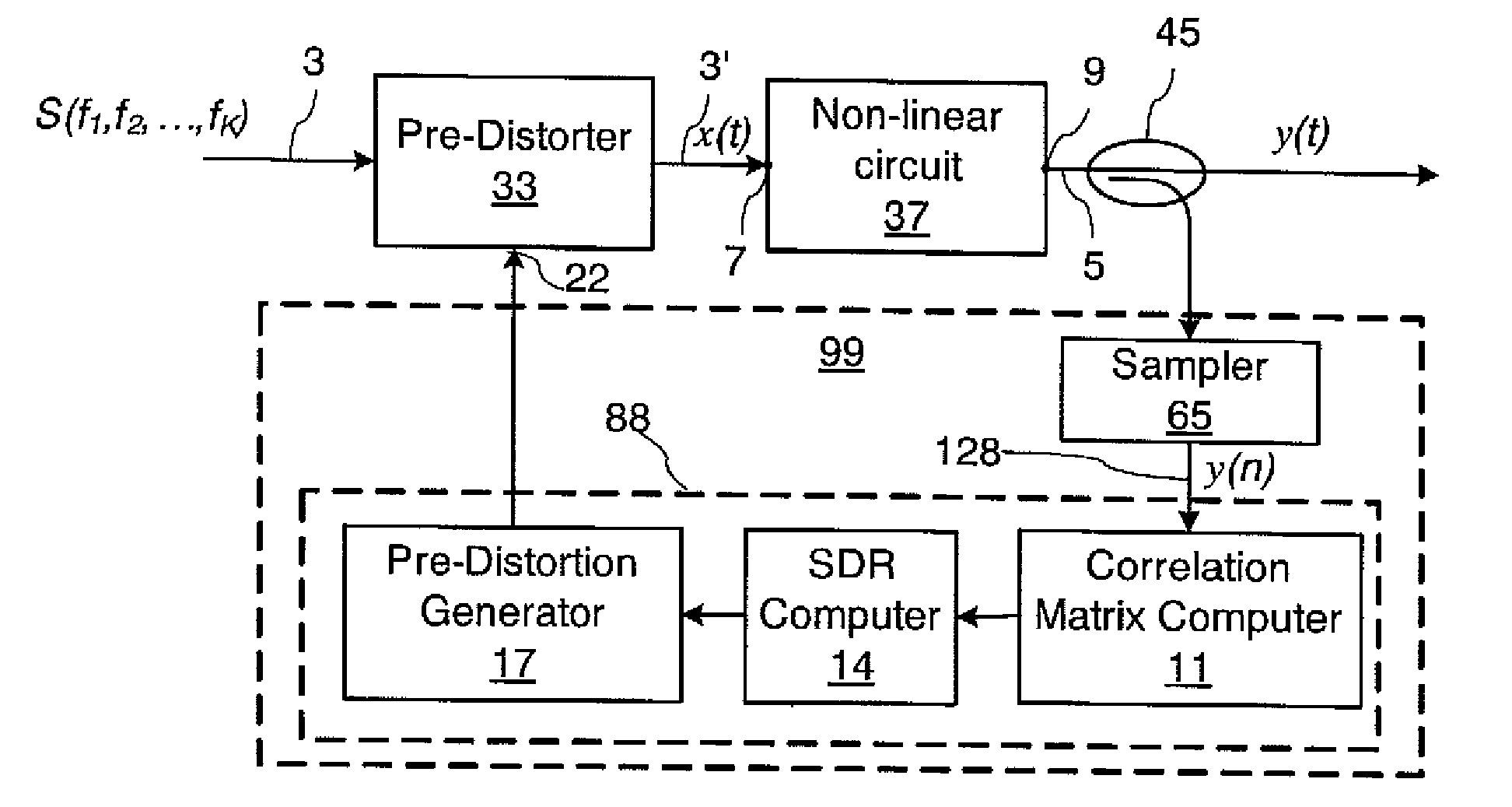

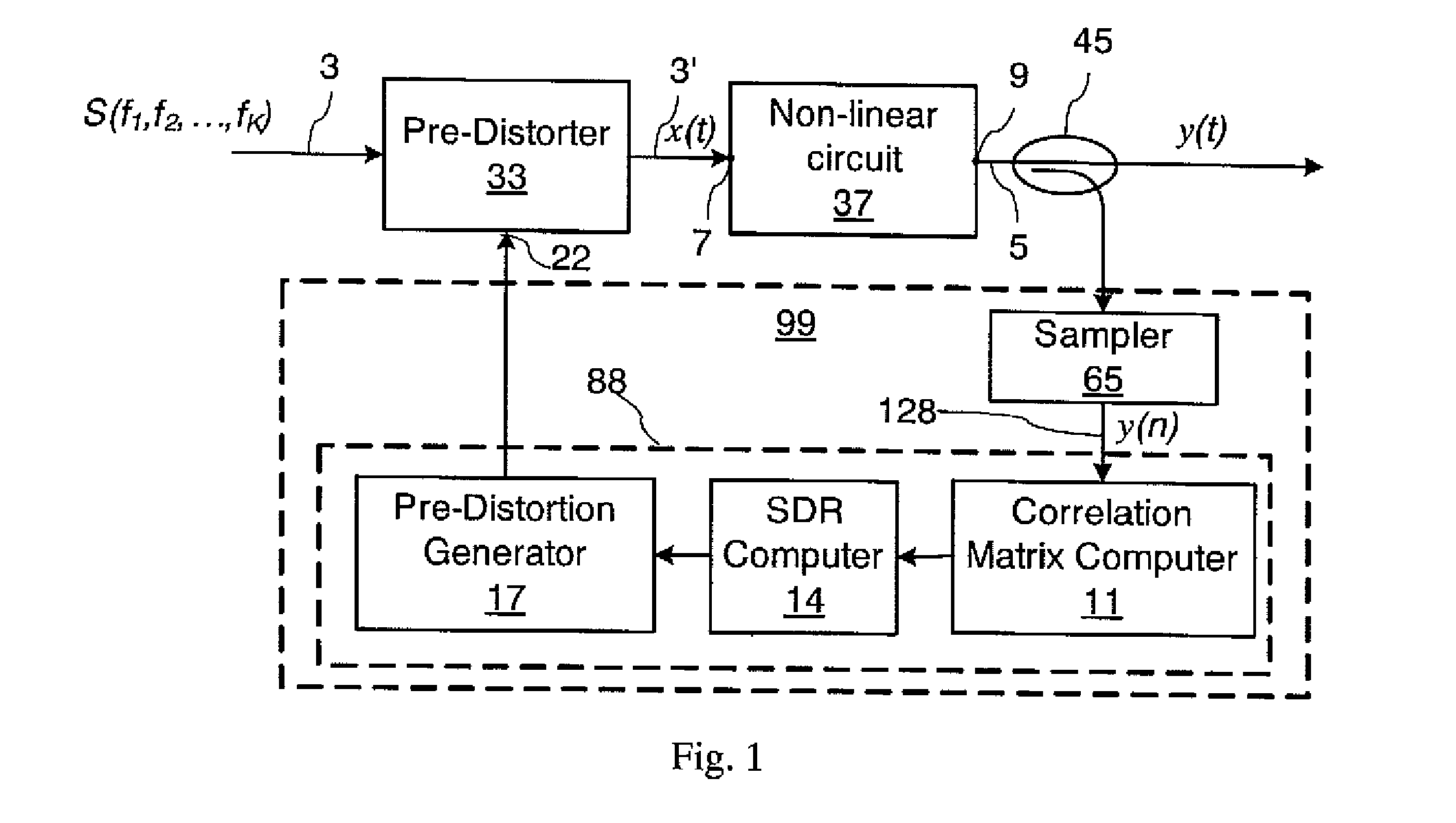

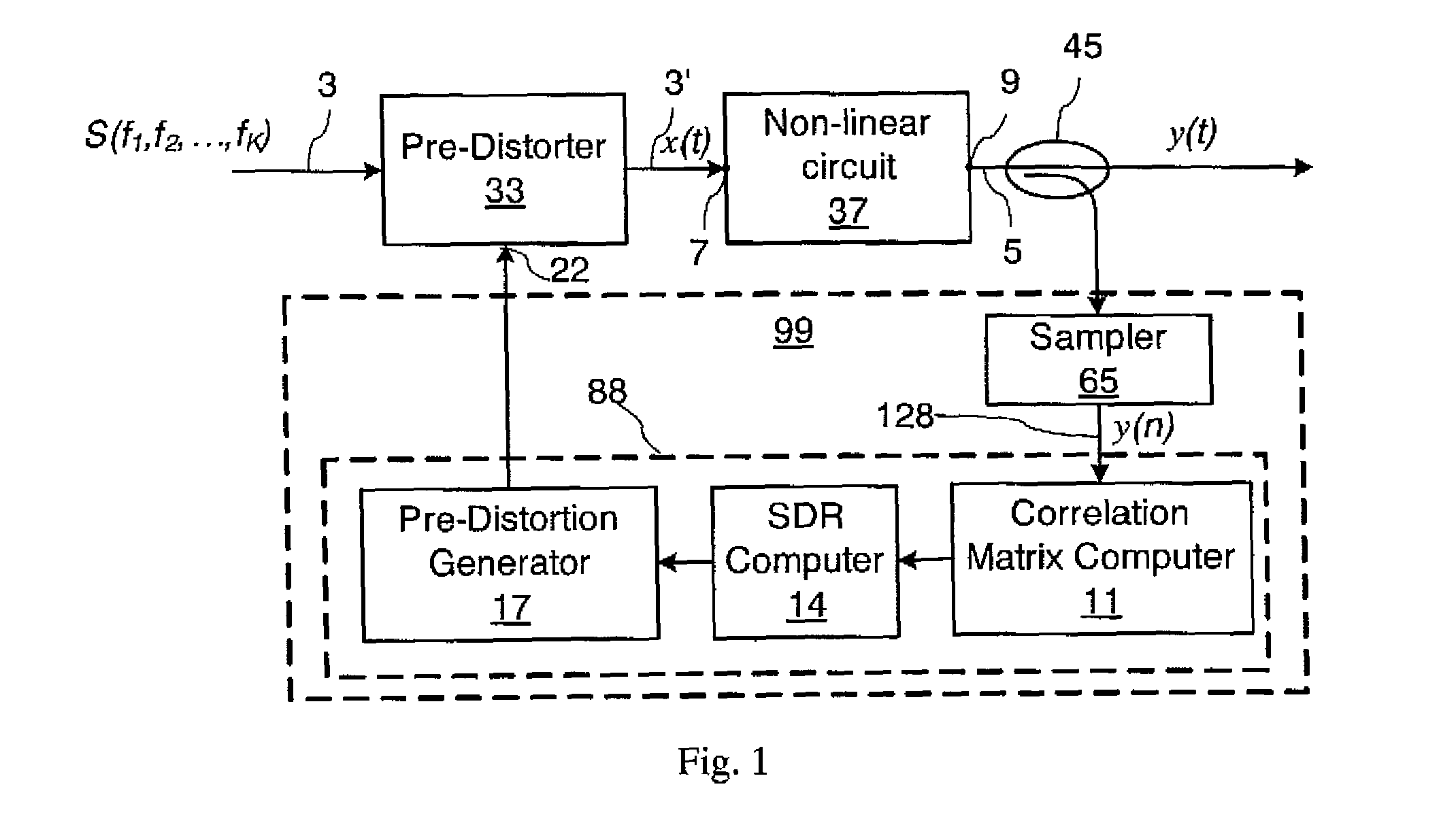

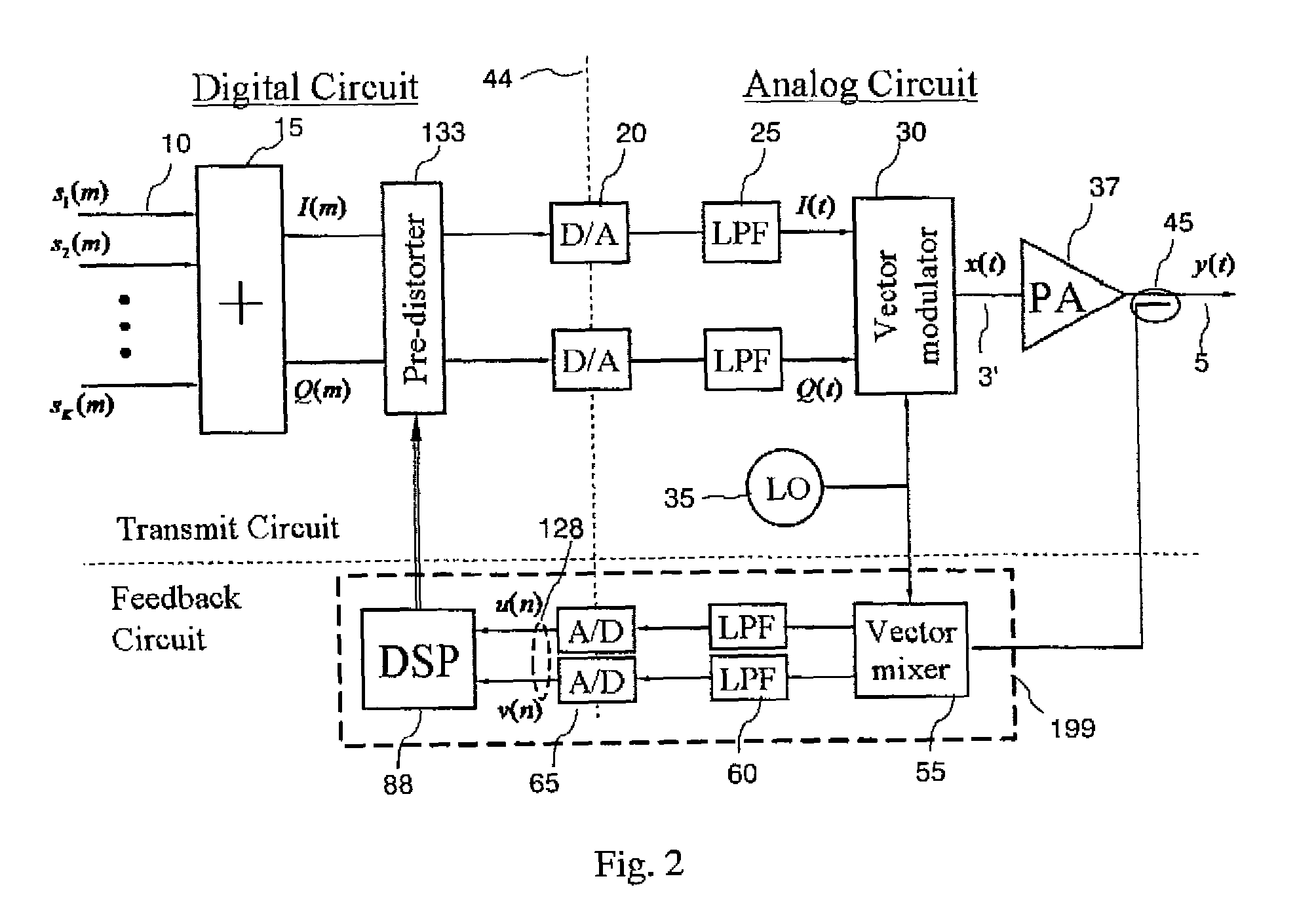

Multi-carrier amplifier linearization system and method

InactiveUS20110064171A1Increase SDRNonlinear distortion can be introducedModulated-carrier systemsLine-faulsts/interference reductionAudio power amplifierCarrier signal

Owner:HER MAJESTY THE QUEEN & RIGHT OF CANADA REPRESENTED BY THE MIN OF IND THROUGH THE COMM RES CENT

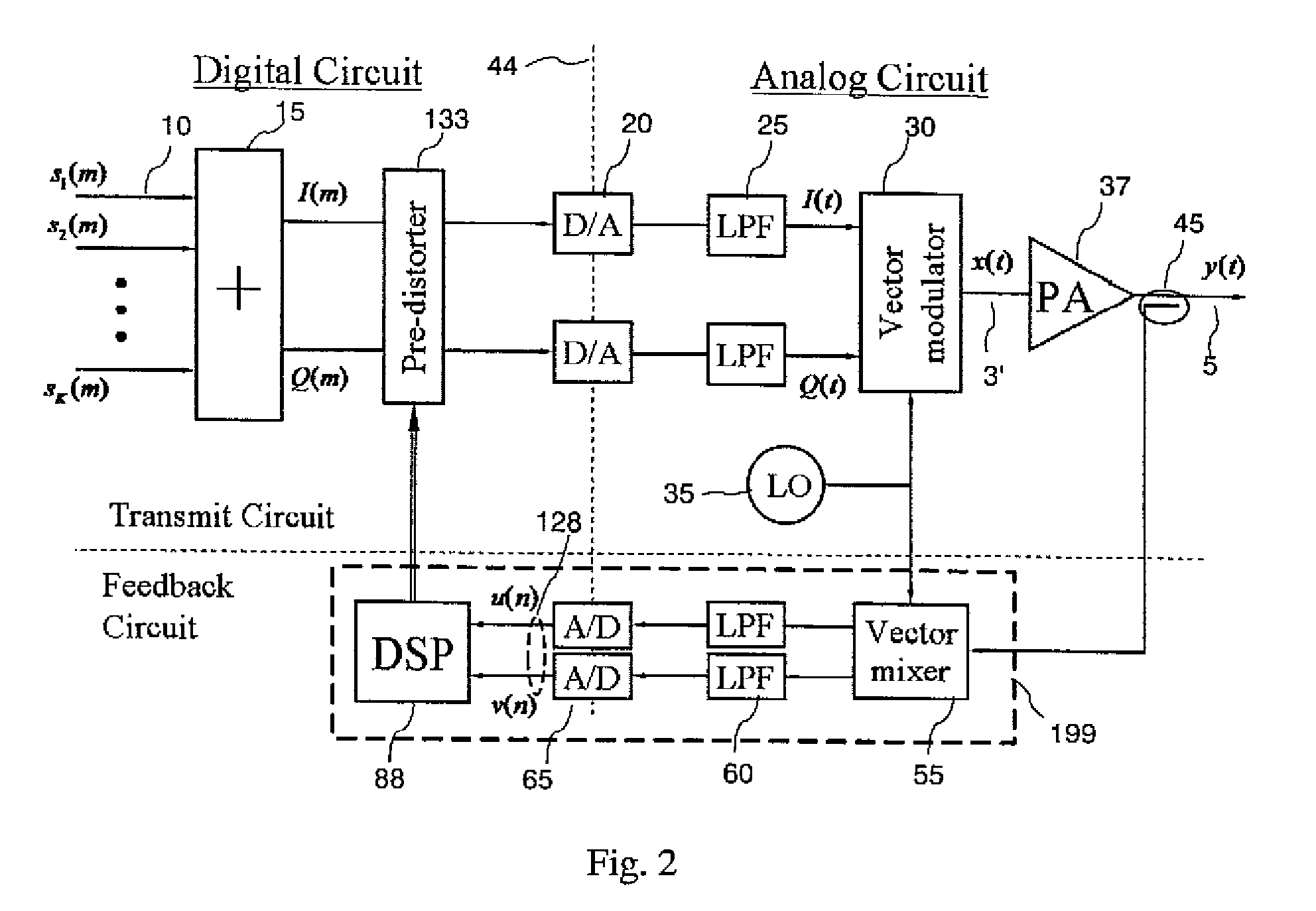

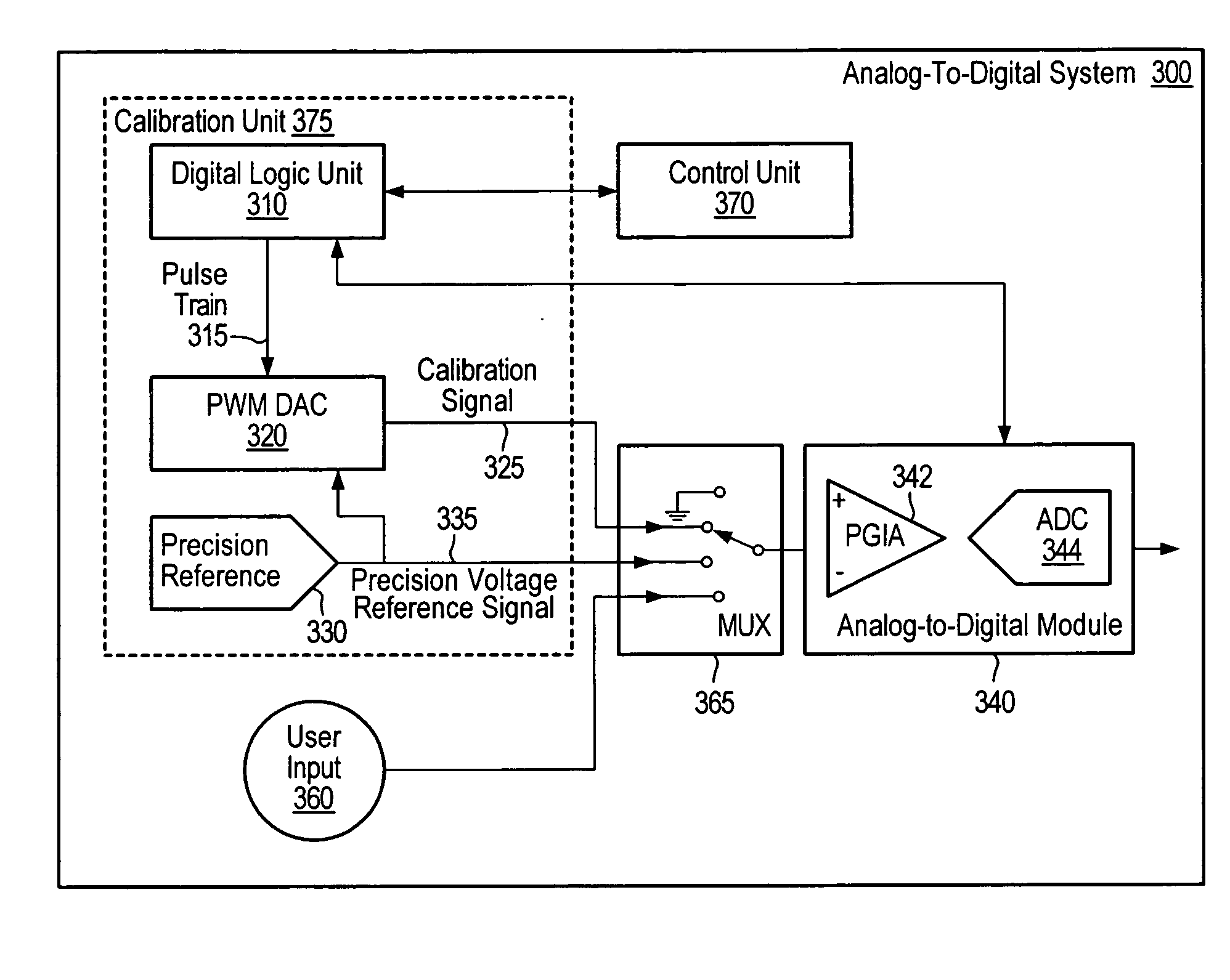

Calibrating analog-to-digital systems using a precision reference and a pulse-width modulation circuit to reduce local and large signal nonlinearities

ActiveUS20050197796A1Reduce measurementReduce large signal nonlinearitiesElectric signal transmission systemsVoltage-current phase angleElectrical resistance and conductanceData acquisition

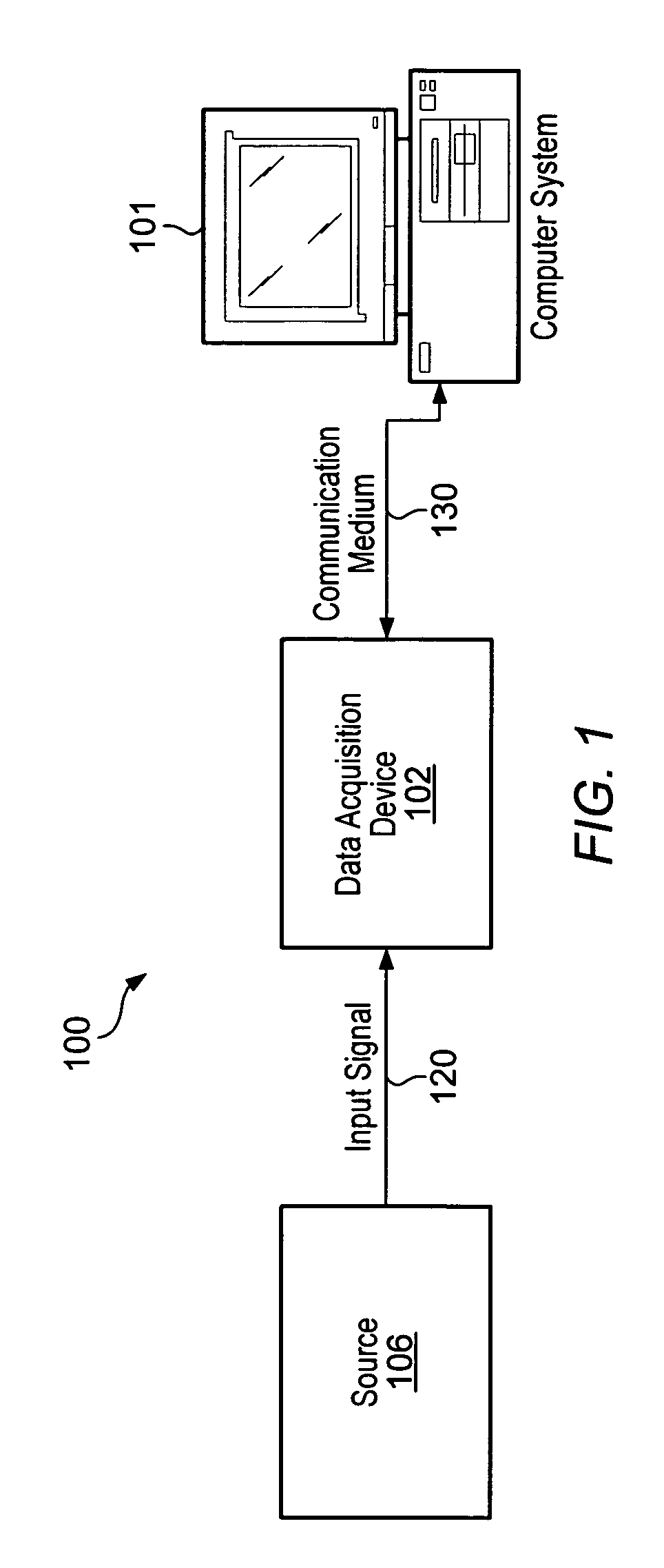

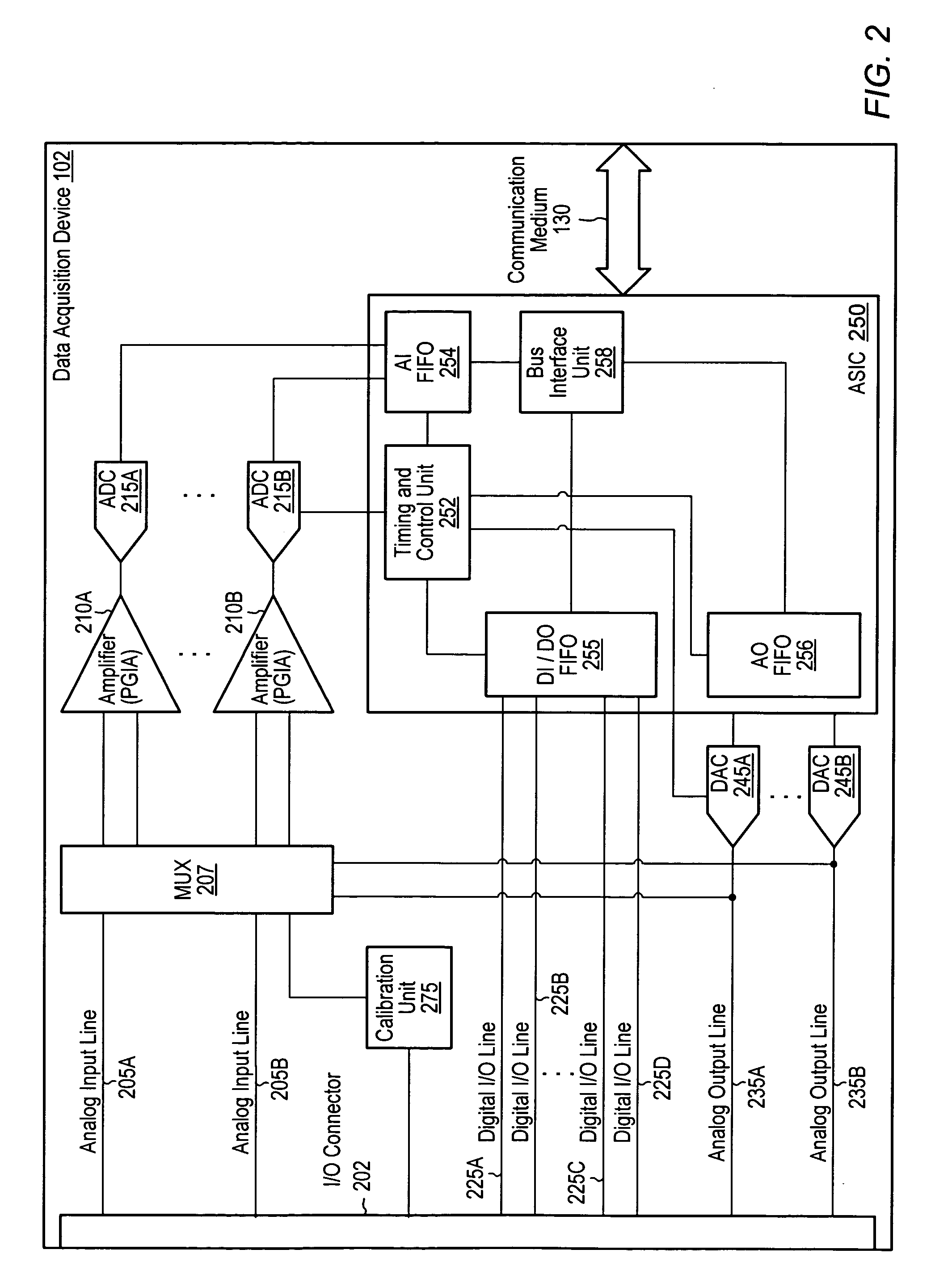

A calibration unit and technique for calibrating A / D systems (e.g., data acquisition devices) using a pulse-width modulation (PWM) circuit to reduce nonlinearity. The calibration unit may be coupled to an analog-to-digital module (ADM) of the A / D system. The PWM circuit may generate a calibration signal with intentional ripple, which may exercise a region of a transfer curve of the ADM to reduce local nonlinearities in measurements associated with the calibration of the system. Pulse trains of varying frequency and duty cycle may be generated to sweep the PWM circuit through an ADM range and to calculate an ADM linearity correction function, which may be used to perform gain and offset correction with respect to a best-fit line through an ADM transfer curve to reduce large signal nonlinearities. The PWM circuit may include a resistor divider circuit including a plurality of taps to improve the ability to calibrate small input ranges.

Owner:NATIONAL INSTRUMENTS

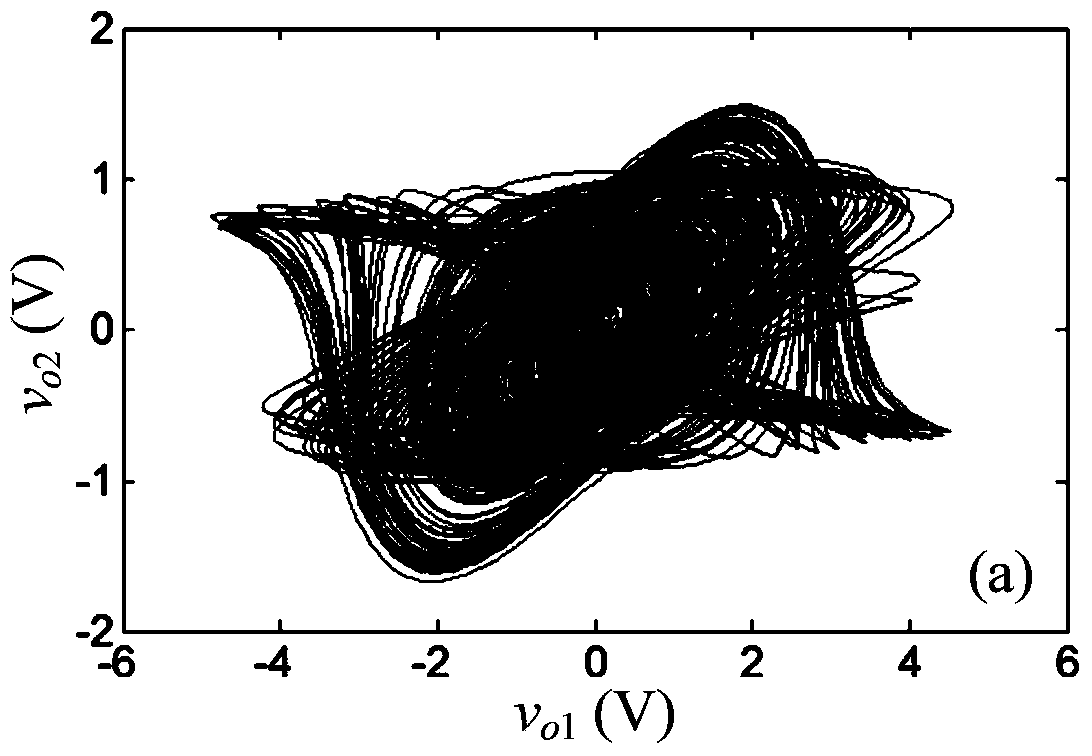

Switchable chaotic signal source by memristor circuit and nonlinear circuit

The invention relates to a switchable chaotic analog circuit based on a Chua chaotic circuit system. The switchable chaotic signal source by a memristor circuit and a nonlinear circuit comprises a Chua chaotic circuit post-stage switchable-mode main circuit which is composed of an integrating circuit, a control switch circuit (S) arranged at the post stage of the integrating circuit, an absolute value function circuit (H(.)) disposed at the post stage of the control switch circuit (S), a first multiplying circuit (M1) mounted at the post stage of the absolute value function circuit (H(.)) and a negative resistance circuit arranged at the post stage of the first multiplying circuit (M1). The chaotic analog circuit has characteristics of simple circuit structure and strong implementability. In addition, switching of chaotic signals can be realized by the memristor circuit and the nonlinear circuit. Meanwhile, chaotic systems capable of generating two types of different charotic attractors and complex chaotic scrolls both show complex dynamic characteristics and become a novel chaotic signal source.

Owner:溧阳常大技术转移中心有限公司

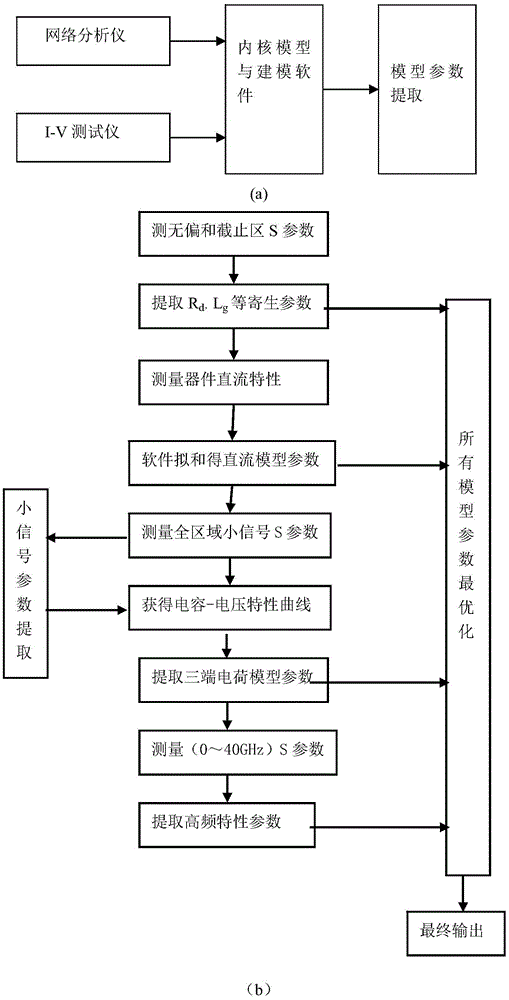

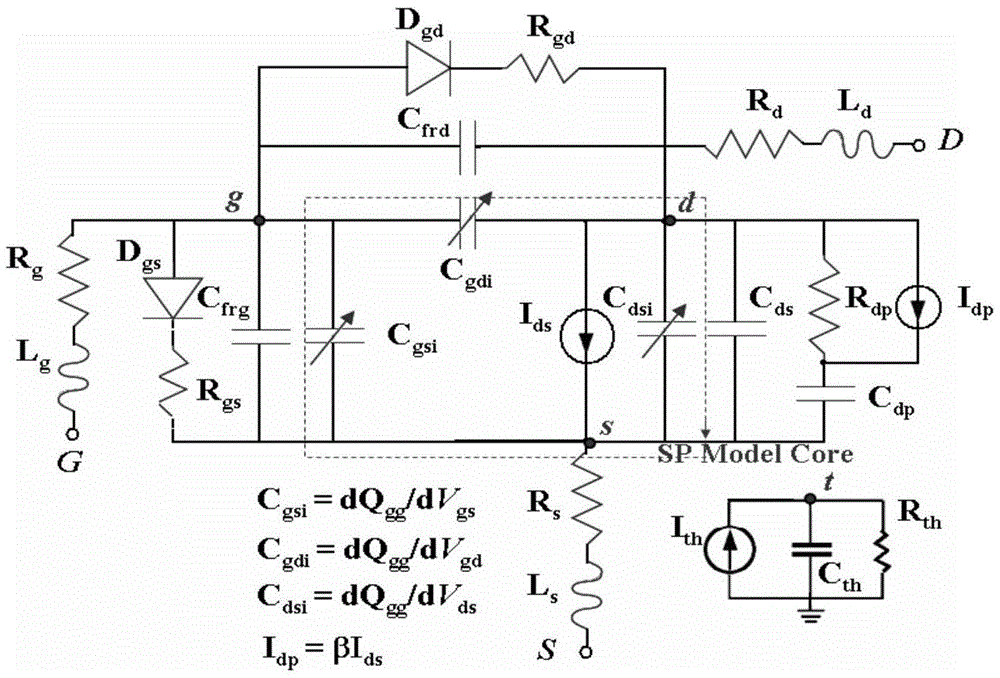

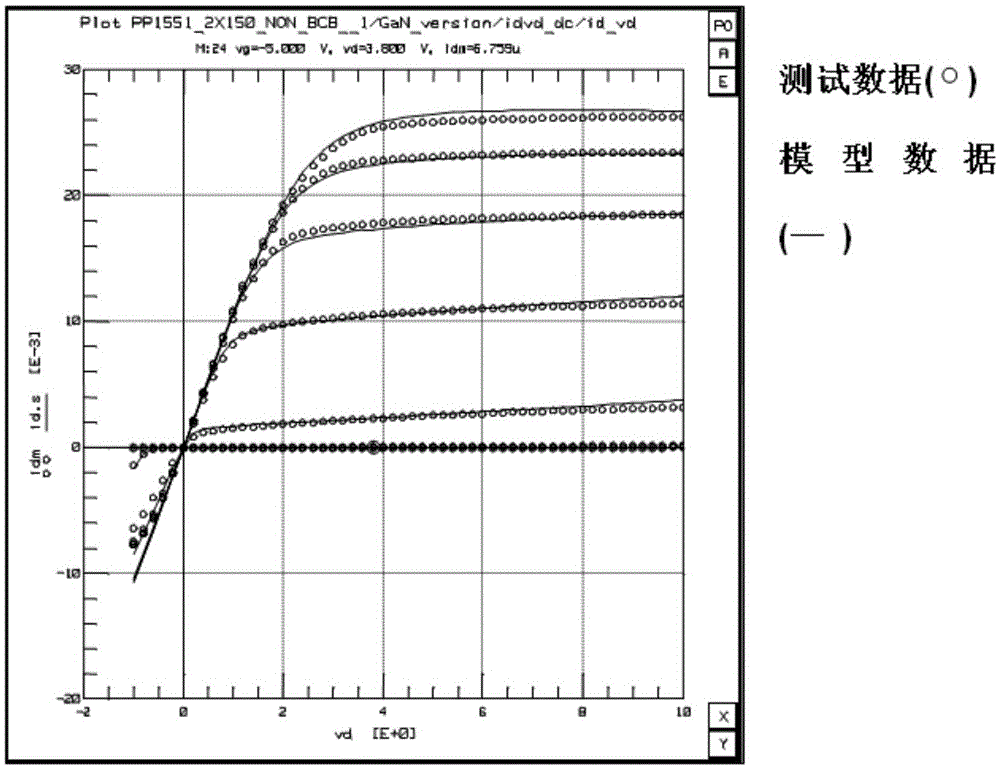

Modelling method for surface potential basis intensive model of III-V group HEMT (High Electron Mobility Transistor)

ActiveCN105468828ASolve the physics problem of quantum effect processingSolve the problem of difficult glueCAD circuit designSpecial data processing applicationsCapacitancePhysical model

The invention discloses a modelling method for a surface potential basis intensive model of an III-V group HEMT (High Electron Mobility Transistor). The method comprises the following steps of firstly, establishing an intrinsic structure model and an extrinsic structure model of the III-V group HEMT, combining a physical structure and a behavior mechanism of a device to construct a topological structure, and then embedding the established models into a commercial EDA (Electronic Design Automation) tool; secondly, carrying out on-wafer testing on an actual depletion device to obtain various performance test data of the device; and lastly, verifying the intensive model. The model solves the problems that the existing current and charge equations of the device cannot integrate, the segment points are discontinuous and the equations cannot be used for nonlinear circuit simulation; through a method for solving a surface potential source equation to deduce model current and charge / capacitance equations, a physical problem for quantum effect processing and a numerical algorithm problem caused by simultaneous self-consistent solution of a classic carrier transport equation and a new effect in the existing physical model are solved; and furthermore, a computational formula for volume charge density is deducted again, so that a problem of difficulty in gluing in a charge model is solved.

Owner:HANGZHOU DIANZI UNIV

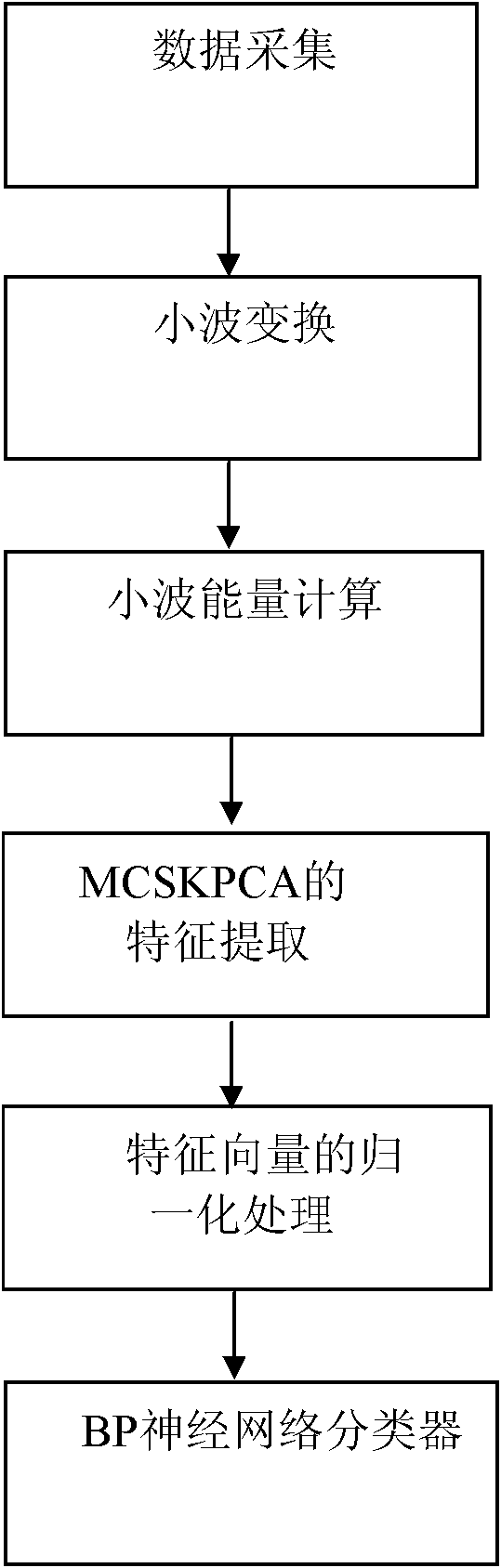

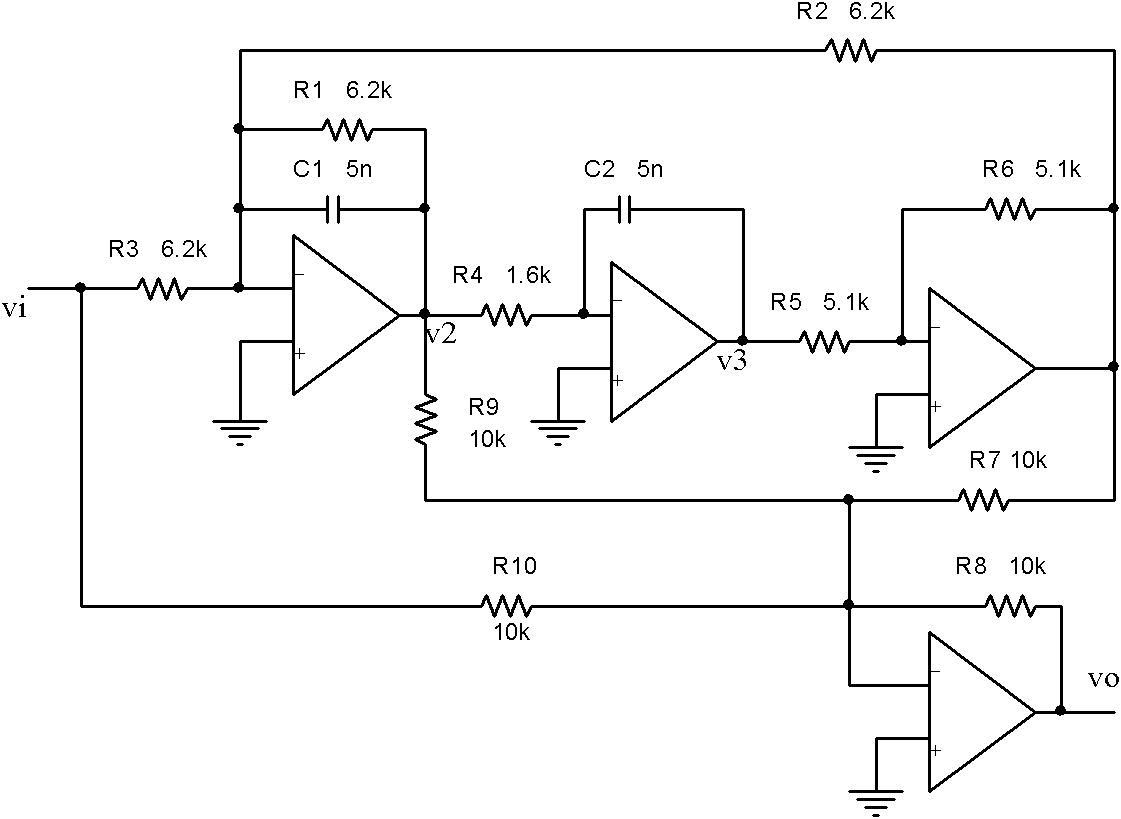

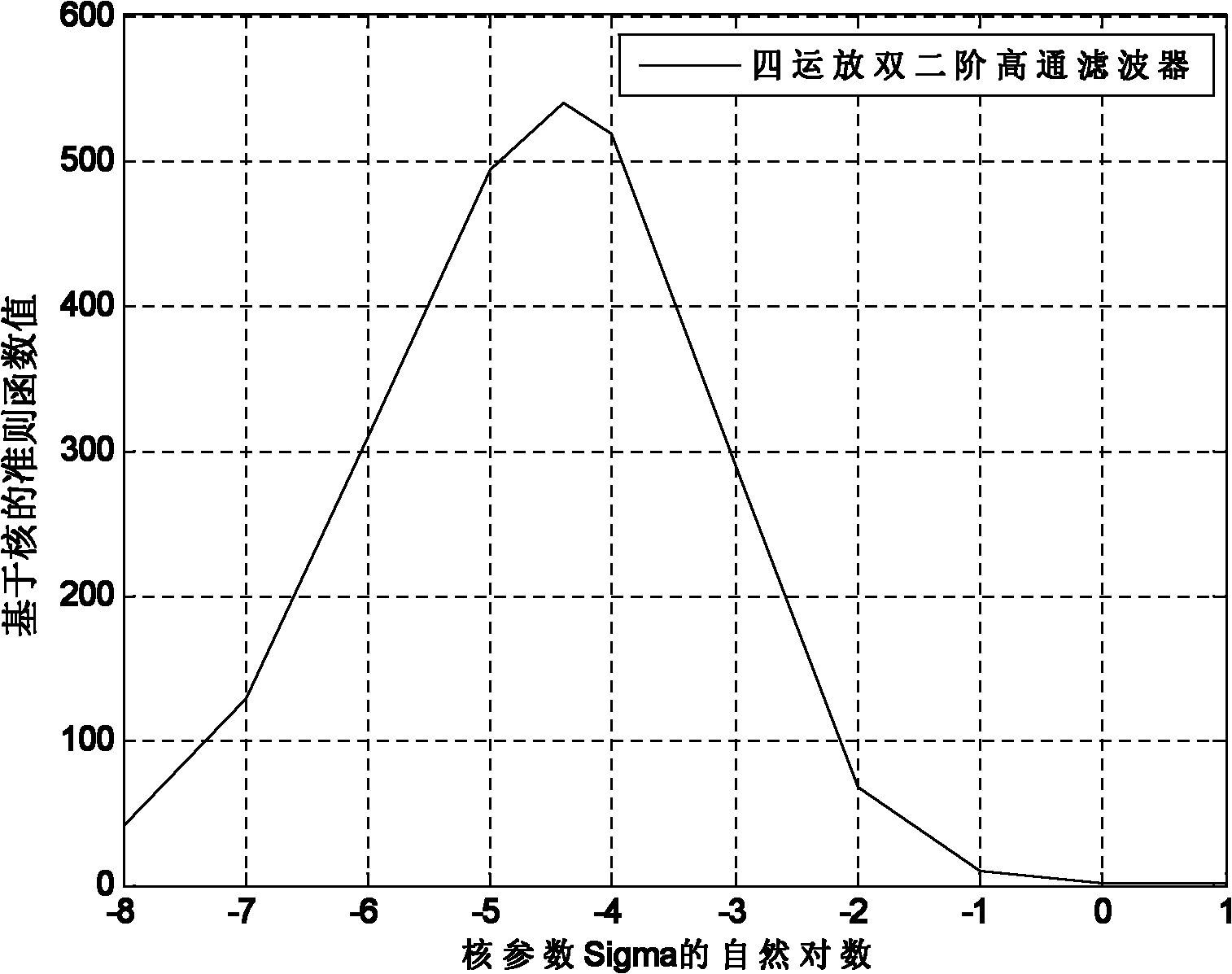

MCSKPCA based neural network fault diagnosis method for analog circuits

ActiveCN102279358ASimple calculationApplicable to real-time environmentAnalog circuit testingNeural learning methodsFeature vectorFeature extraction

Disclosed is an MCSKPCA based neural network fault diagnosis method for analog circuits, comprising acquiring the output voltage signal of an analog circuit to be diagnosed; performing wavelet transformation on the acquired output voltage signal; calculating the energy eigenvalues of the wavelet coefficients of the output voltage signal, obtained through the wavelet transformation; performing MCSKPCA feature extraction and dimensionality reduction on the energy eigenvalues, and obtaining an optical eigenvector; and sending the optical eigenvector to a BP neural network separator, and outputting a fault diagnosis result by the BP neural network separator. The method can be used for not only diagnosis of linear or nonlinear circuits and systems thereof, but also diagnosis of hard fault and soft fault in the linear or nonlinear circuits.

Owner:HUNAN UNIV

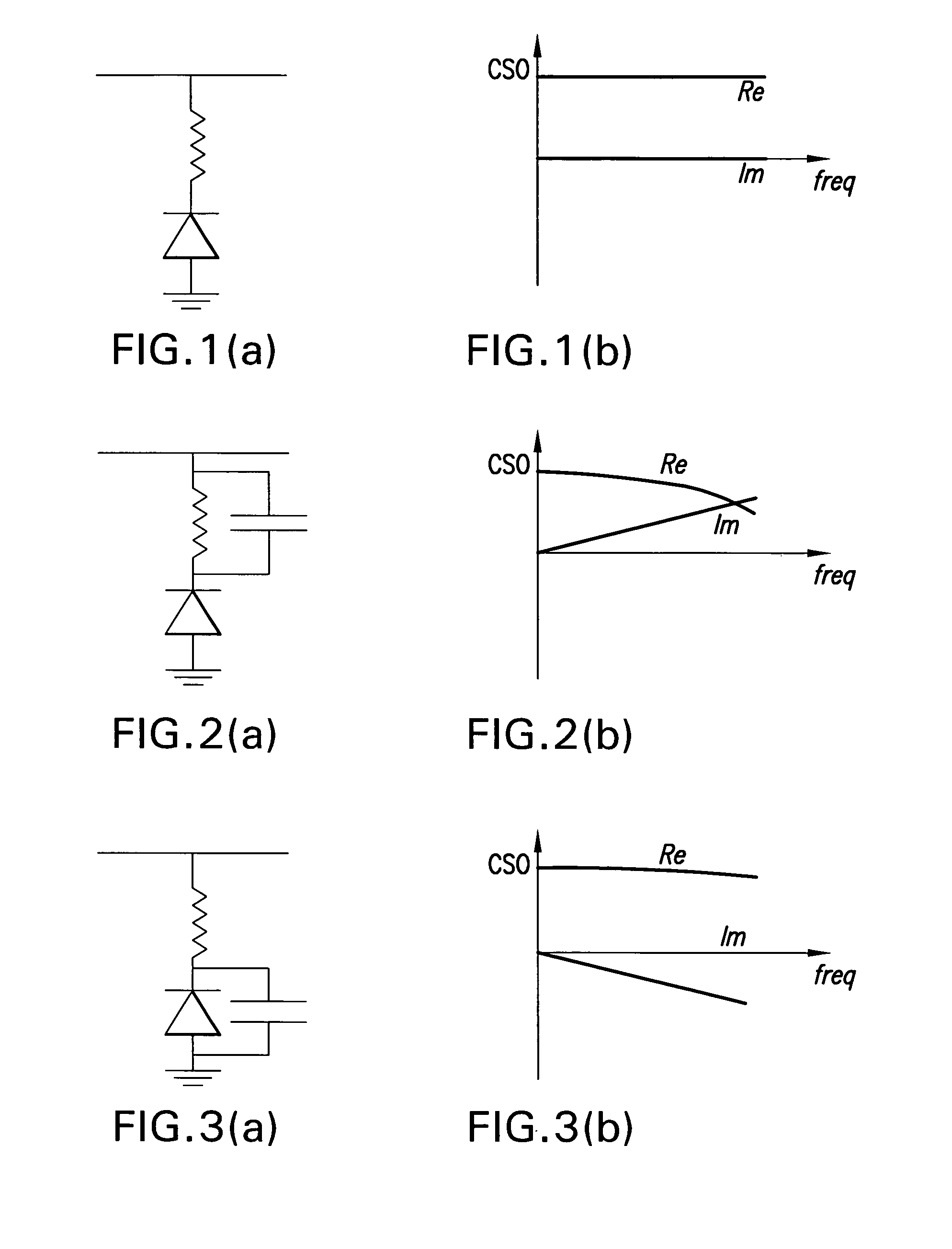

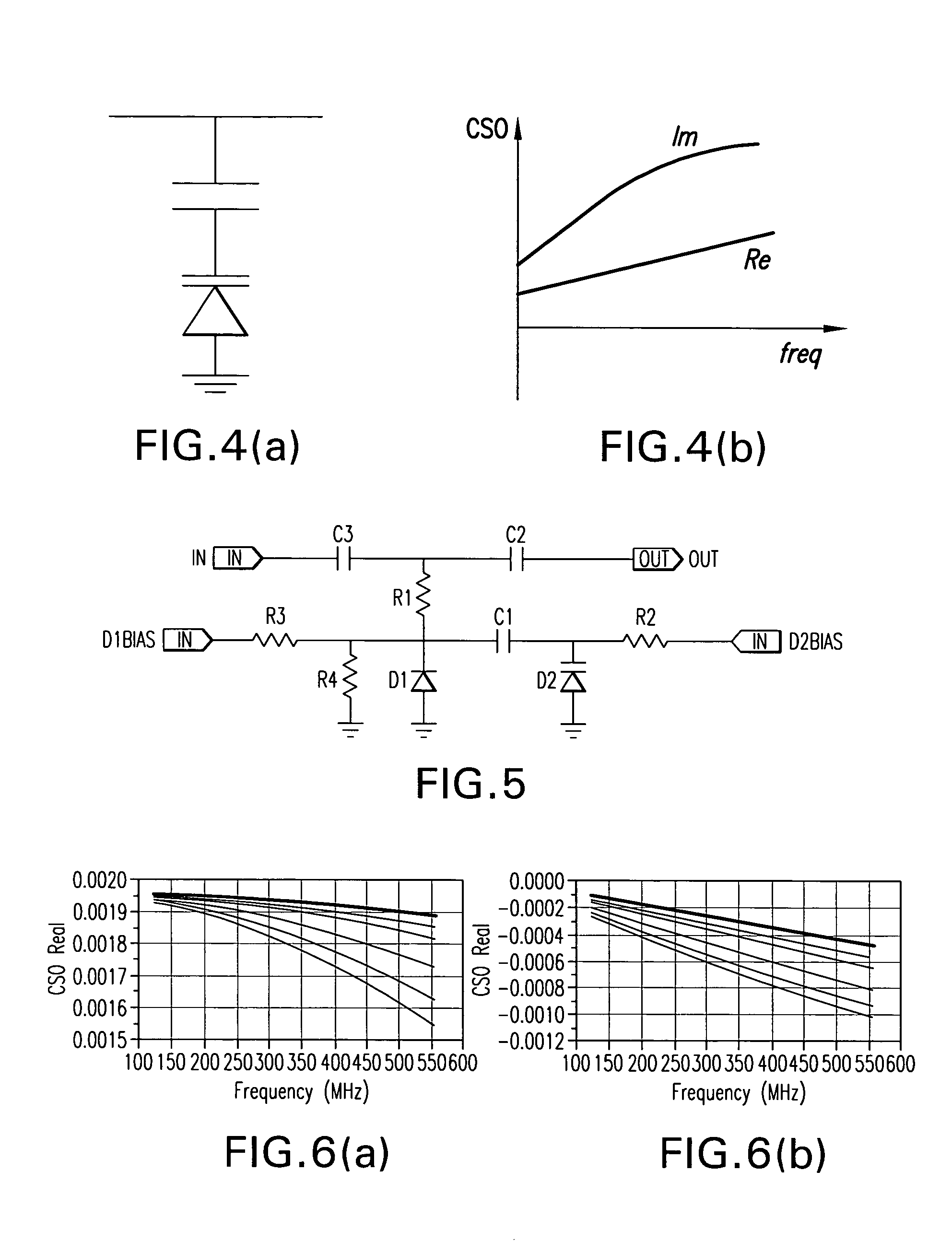

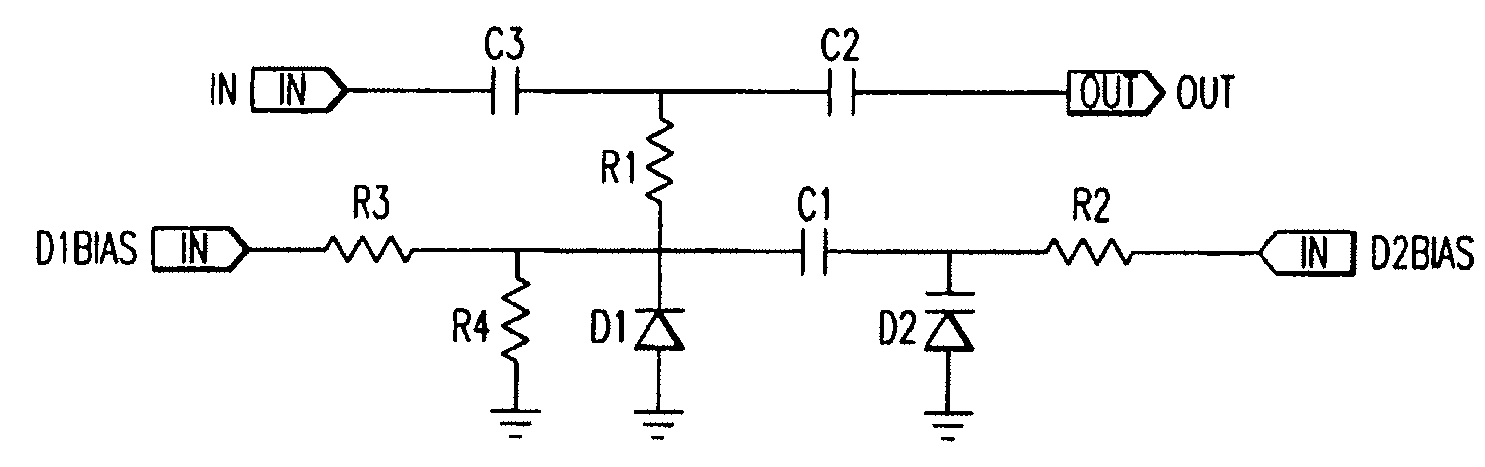

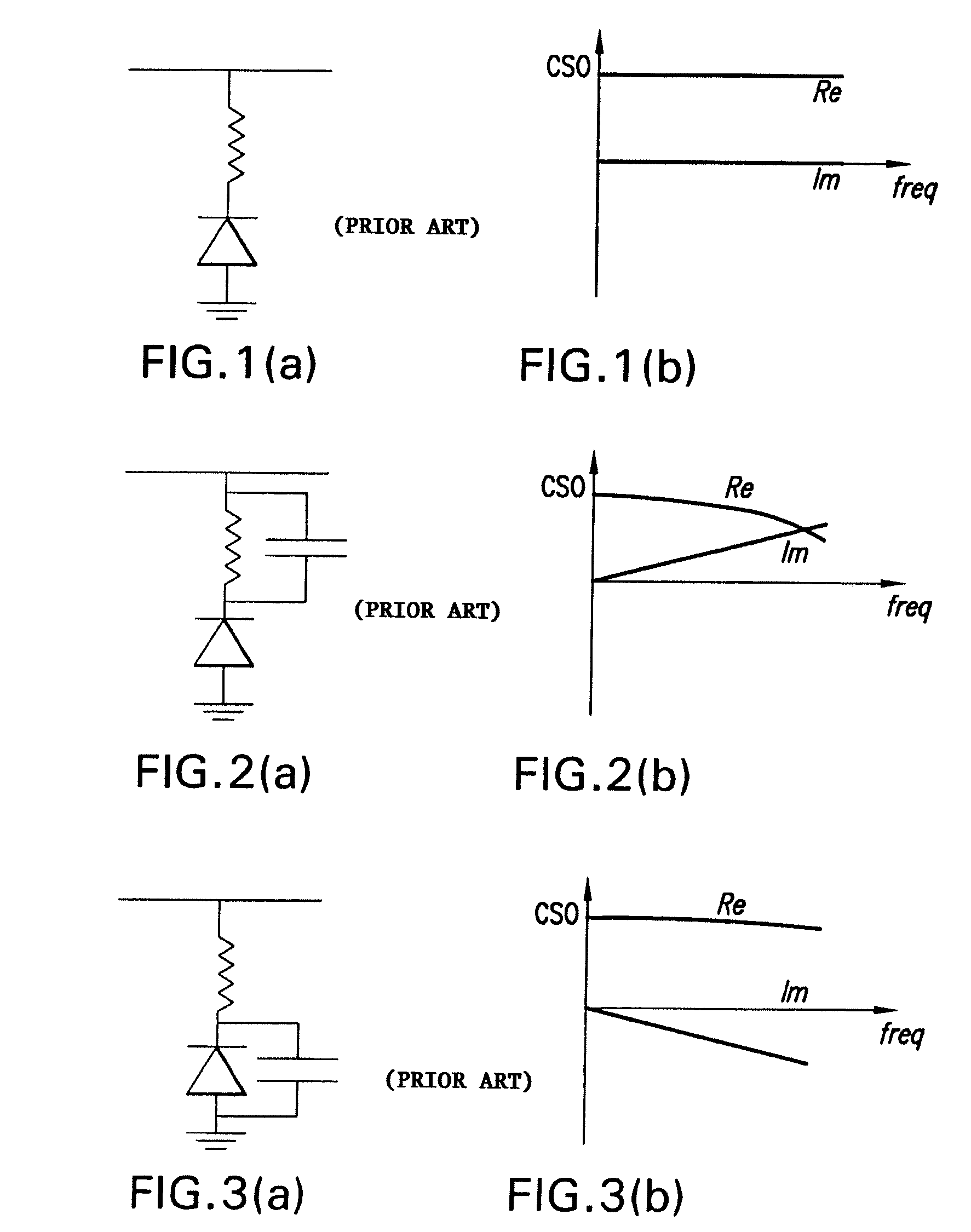

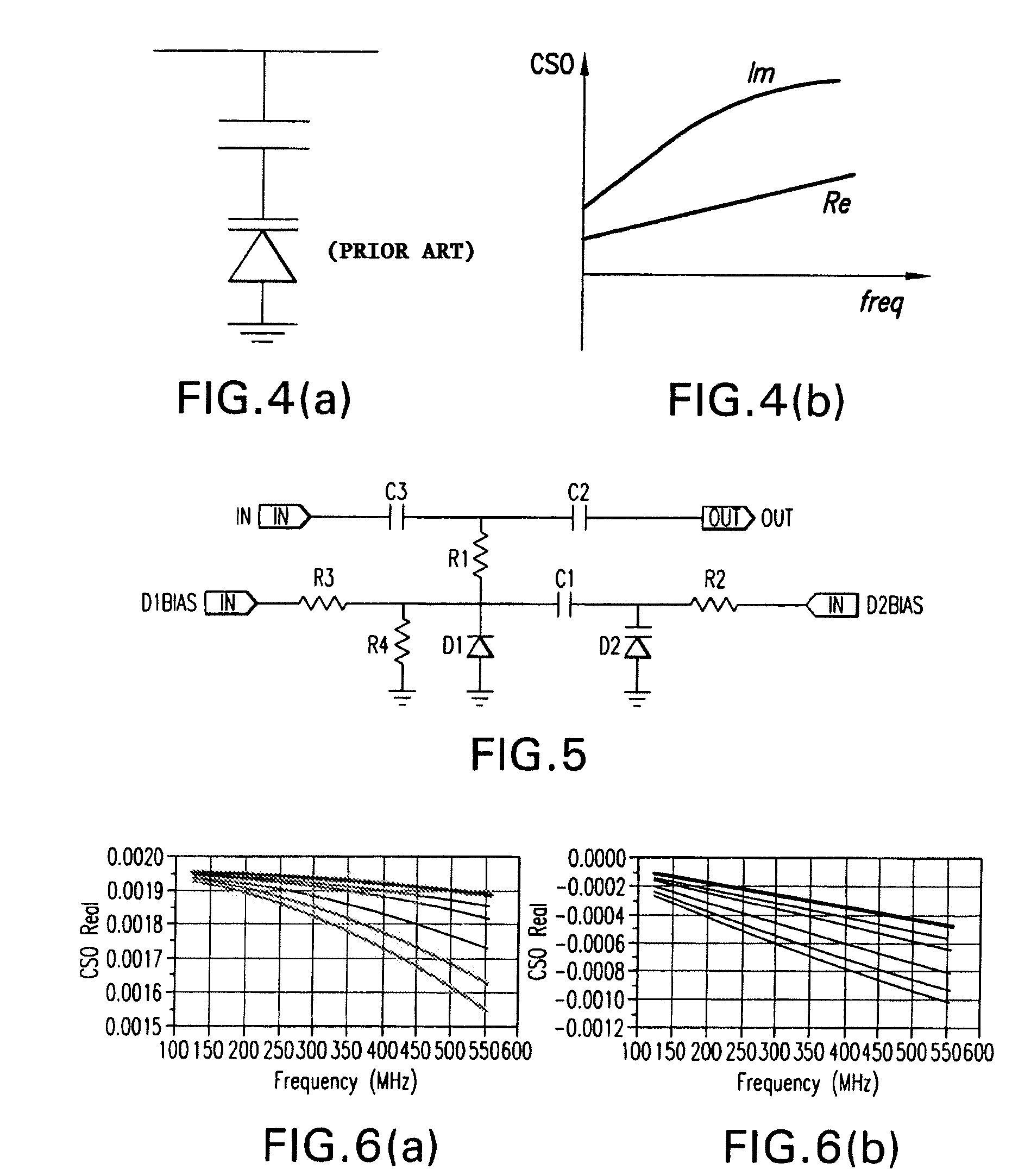

In-line distortion cancellation circuits for linearization of electronic and optical signals with phase and frequency adjustment

ActiveUS20070297803A1Reduce the amount of solutionLow insertion lossAmplifier modifications to reduce non-linear distortionPulse automatic controlNonlinear circuit elementsLinear circuit

A distortion circuit is provided for correcting the distortion from a nonlinear circuit element by generating a frequency dependent signal having a sign opposite to the distortion signal produced by the nonlinear circuit and substantially the same magnitude. The distortion circuit includes an input signal and a first nonlinear device coupled to the input signal for generating a first signal and where the first nonlinear device has a first bias level. Also included is a second nonlinear device different from same first nonlinear device and coupled to the first nonlinear device for modifying the first signal to produce an output second signal, the second nonlinear device having a second bias level. A bias control means is provided for adjusting the first and said second bias levels so that the magnitude, phase and frequency of the output second signal can be adjusted.

Owner:EMCORE INC

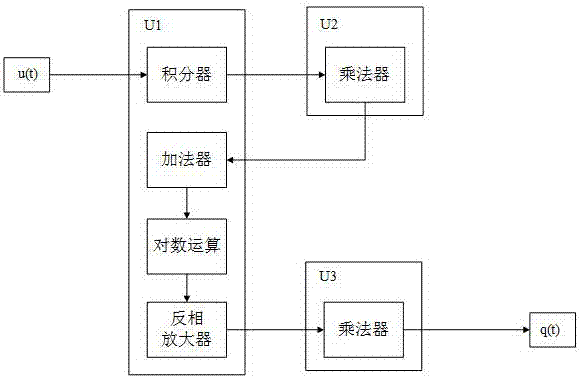

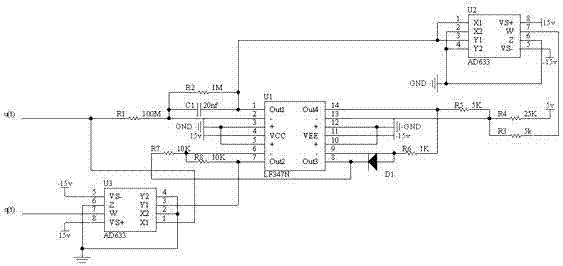

Equivalent simulation circuit of logarithmic memory capacitor

ActiveCN107169253AClear structureReduce areaCAD circuit designEnergy efficient computingIntegratorEngineering

The invention discloses an equivalent simulation circuit of a logarithmic memory capacitor. A circuit model meeting the characteristics of an exponential magnetic control memory capacitor is built by utilizing devices such as an operational amplifier, a multiplier and the like; and the circuit model can be applied to the research of the characteristics of a basic circuit of the memory capacitor and the research of a nonlinear circuit of the memory capacitor. Specifically, the functions of an integrator, an inverse summation operation circuit, a logarithmic operation circuit, an inverting amplifier and the like are realized by adopting an integrated circuit U1; the function of the multiplier is realized by integrated circuits U2 and U3; when a sine excitation signal is input, the characteristics of the signal can be observed by using an oscilloscope; voltage values of a voltage signal and a charge signal meet the characteristics of a 8-shaped compact hysteretic curve; and the hysteretic sidelobe area is reduced with the increment of a signal frequency. The circuit is simple and clear in structure; and as an emulator of an actual memory capacitor, the circuit is of important significance for characteristic and application research of a memory inductor.

Owner:HANGZHOU DIANZI UNIV

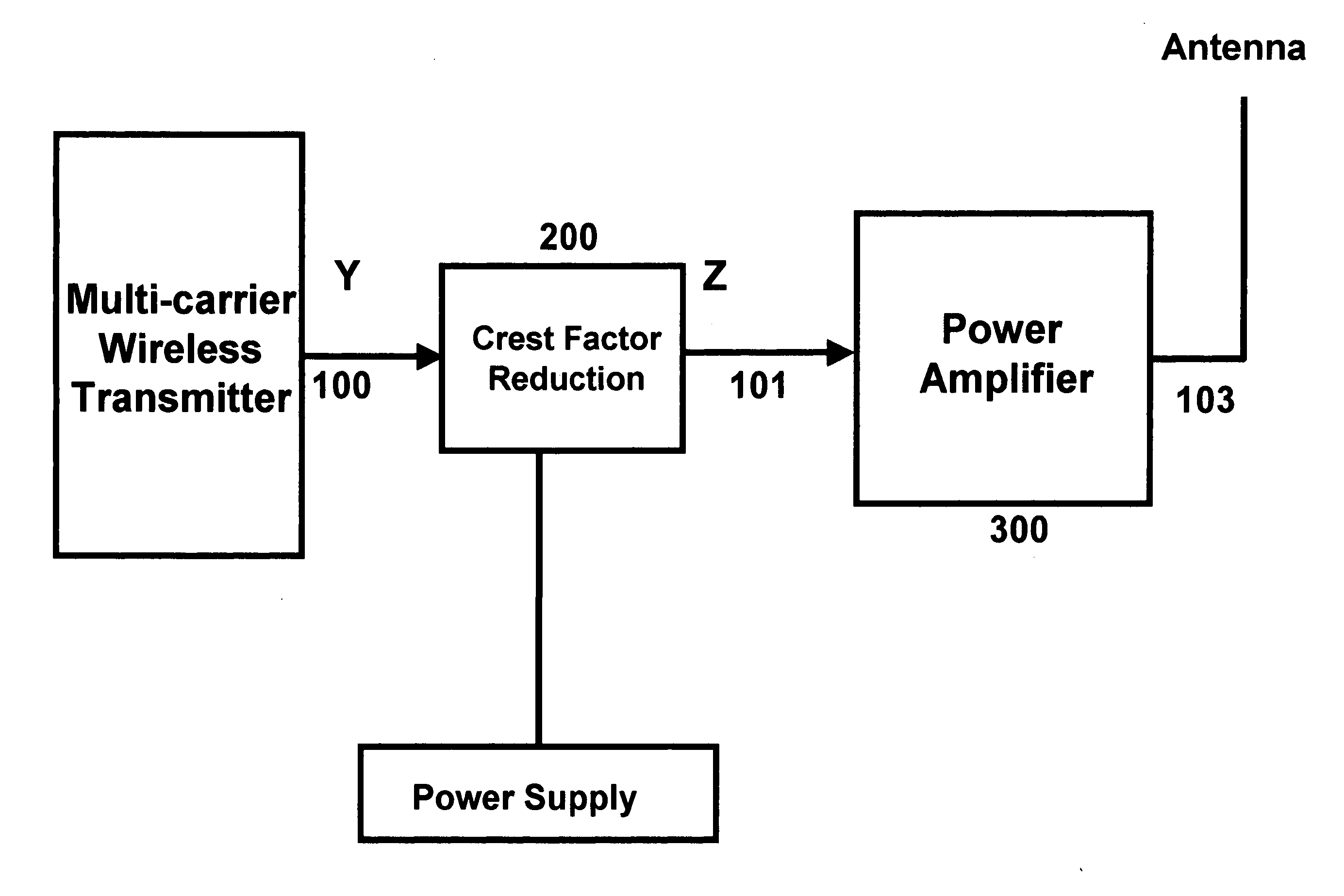

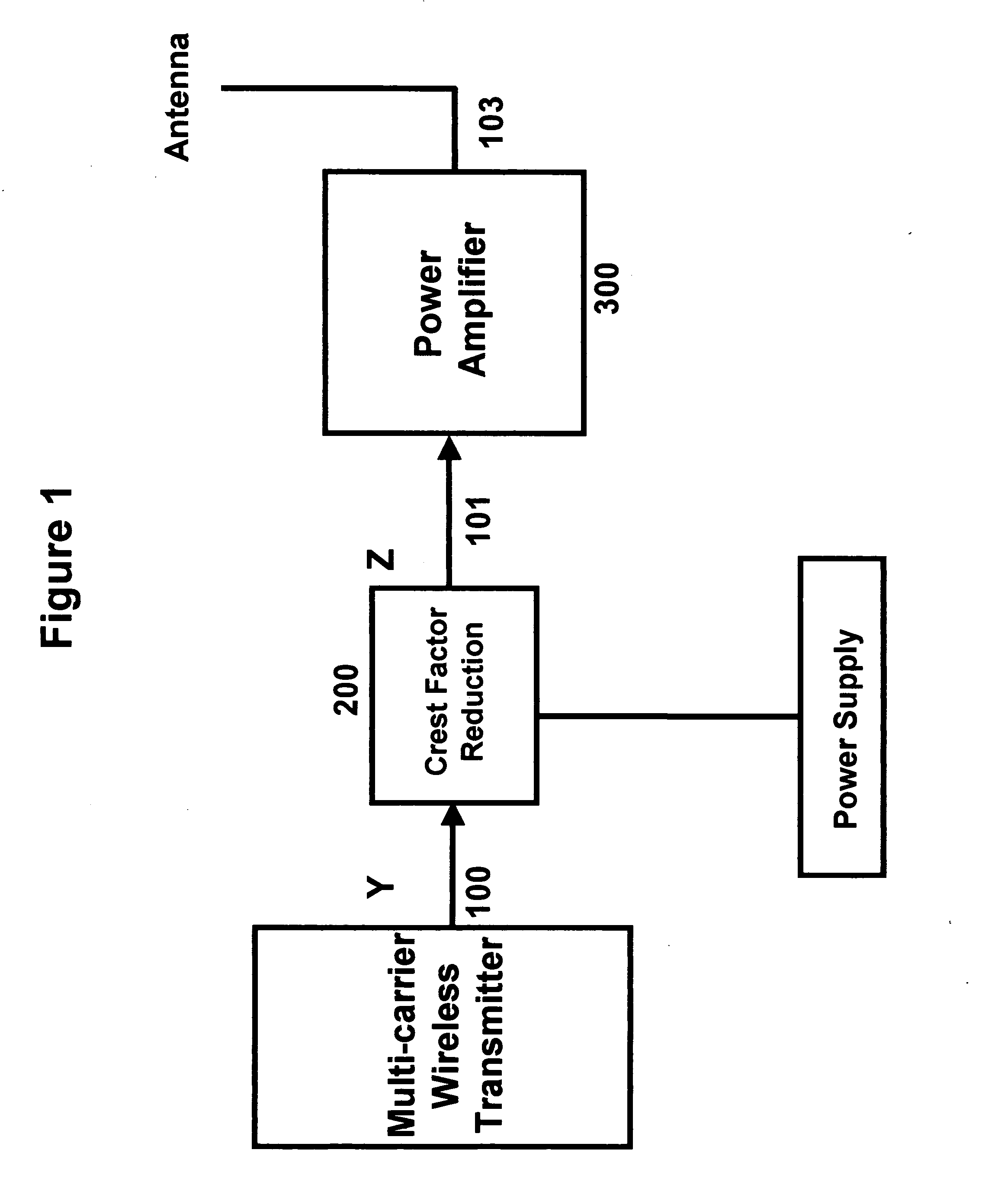

Simple crest factor reduction technique for non-constant envelope signals

A technique for Crest Factor reduction of non-constant envelope signals is described. The input to any nonlinear circuit is modified by a Crest Factor reduction circuit, prior to being applied to the nonlinear circuit. The Crest Factor reduction circuit can either be performed at baseband or RF / IF frequencies. When performed at baseband the real and imaginary components of the baseband signal individually are applied to the Crest Factor reduction circuit. When performed at RF / IF the real signal is directly applied to the Crest Factor reduction circuit. The Crest Factor reduction divides the signal in two equal components one in-phase and one quadrature phase. Each component is then individually clipped based on magnitude of the real or complex signal and then filtered before being combined again by a combiner that 90 degree phase shifts the in-phase component before combining . In the case of RF / IF the clipped signal is bandpass filtered. The Crest Factor reduction could be performed in digital or analog domain.

Owner:ANVARI KIOMARS

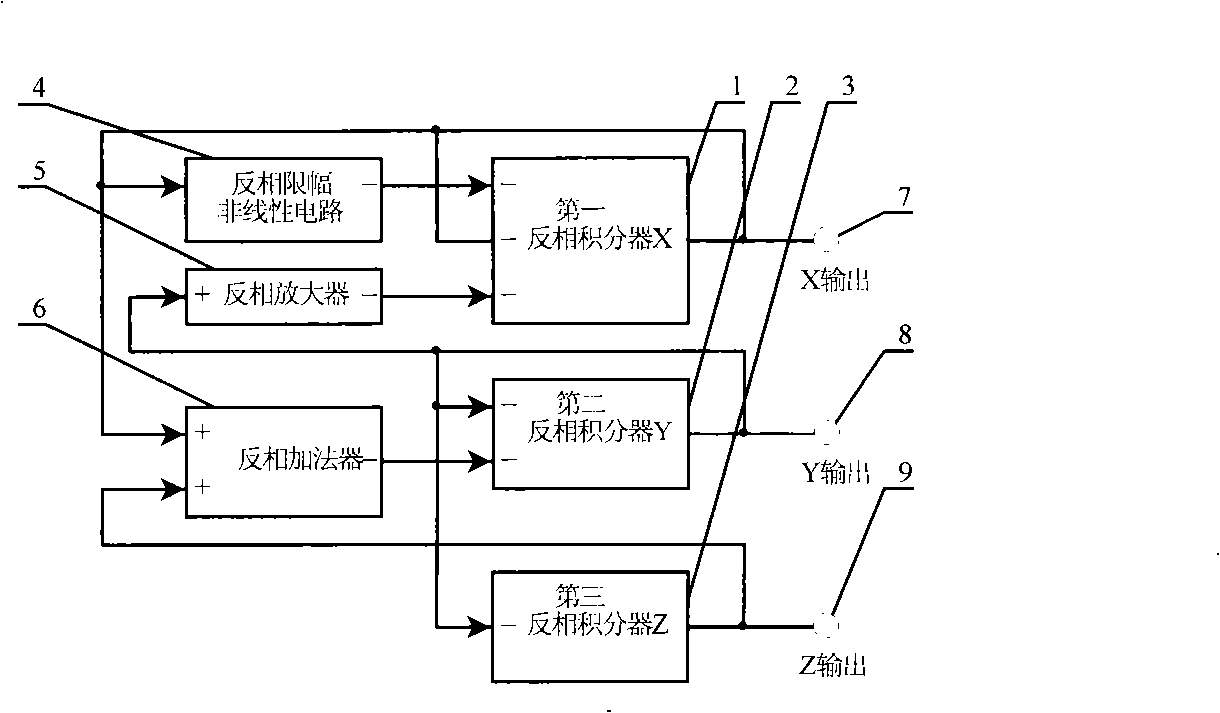

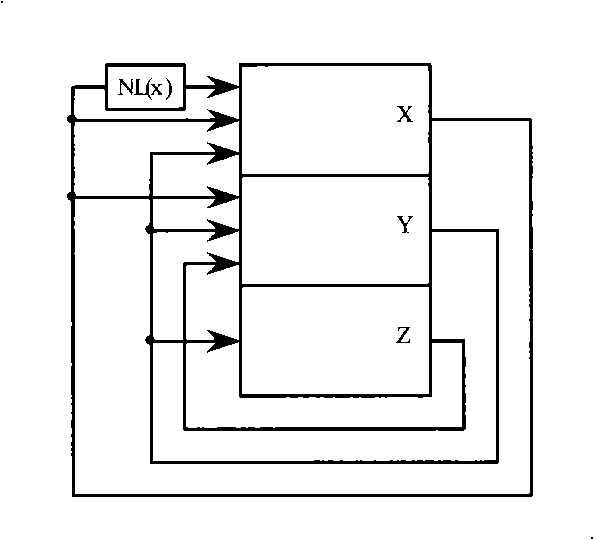

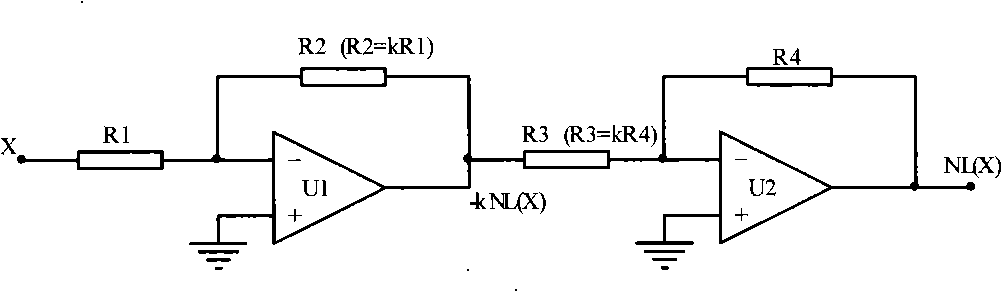

Non-inductor Chua's circuit

The invention discloses a noninductive Cai's circuit, comprising three anti-phase integrators, an anti-phase limiting nonlinear circuit, an anti-phase amplifier and an anti-phase adder. An output terminal X of a first anti-phase integrator is respectively connected with one input terminal itself, an input terminal of the anti-phase limiting nonlinear circuit and an input terminal of the anti-phase adder; an output terminal Y of a second anti-phase integrator is respectively connected with one input terminal itself, an input terminal of a third anti-phase integrator and the input terminal of the anti-phase amplifier; an output terminal Z of a third anti-phase integrator is connected with one input terminal of the anti-phase adder, and the output terminal of the anti-phase limiting nonlinear circuit is connected with one input terminal of the first anti-phase integrator, and the output terminal of the anti-phase amplifier is connected with one input terminal of the first anti-phase integrator, and the output terminal of the anti-phase adder is connected with one input terminal of the second anti-phase integrator. The noninductive Cai's circuit has simple structure, high accuracy and better stability, and can provide waveforms corresponding to each algebraic item of the mathematic expression of the Cai's circuit.

Owner:STATE GRID CORP OF CHINA +2

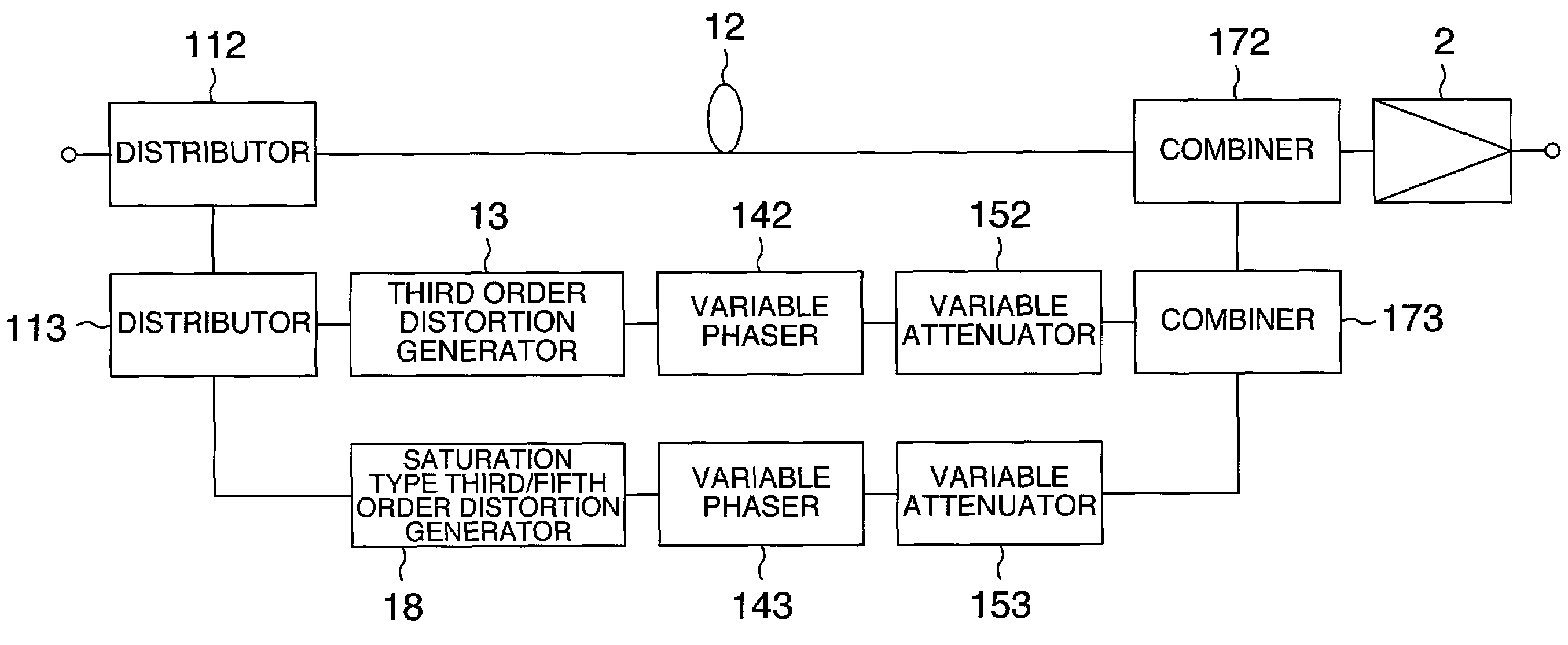

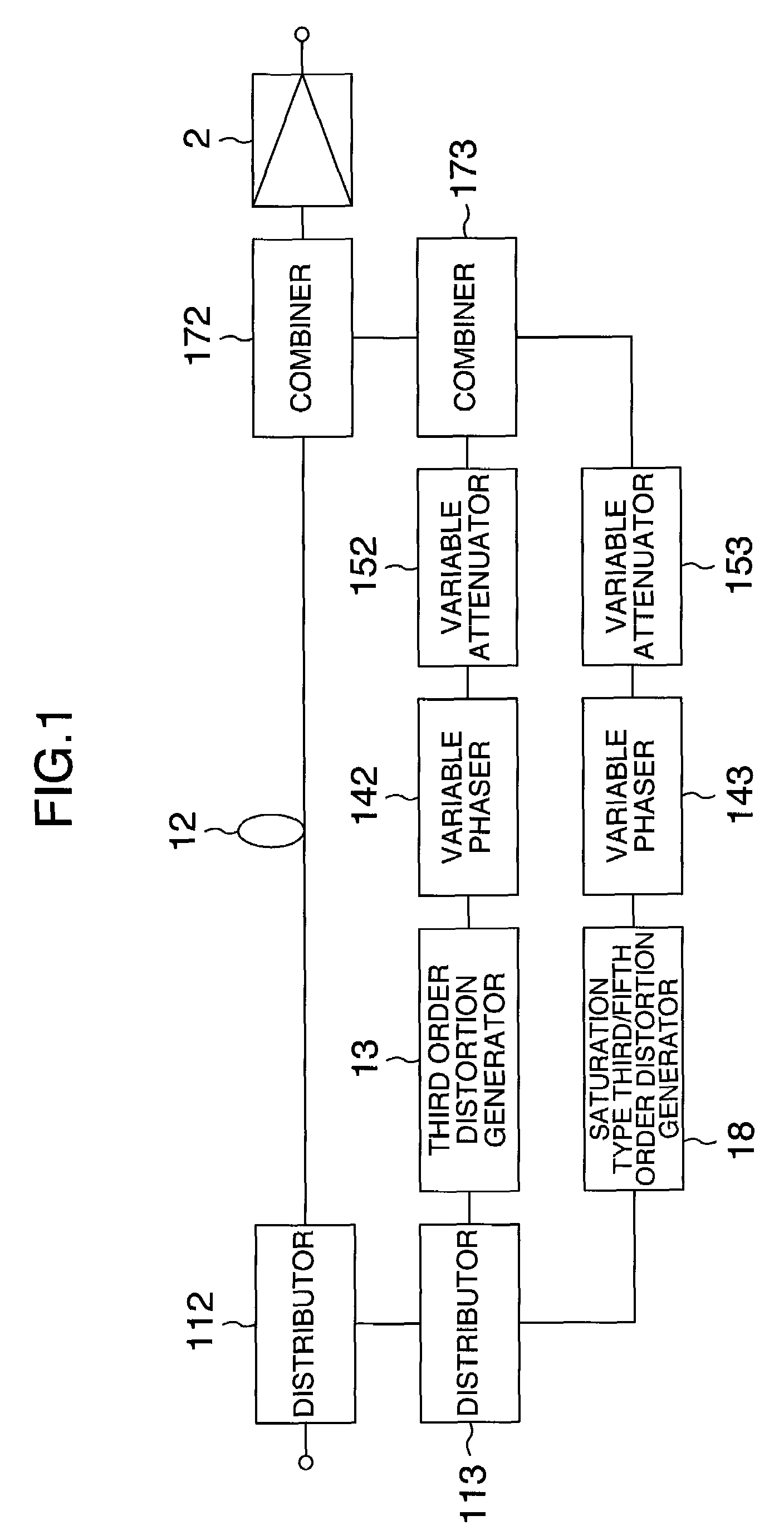

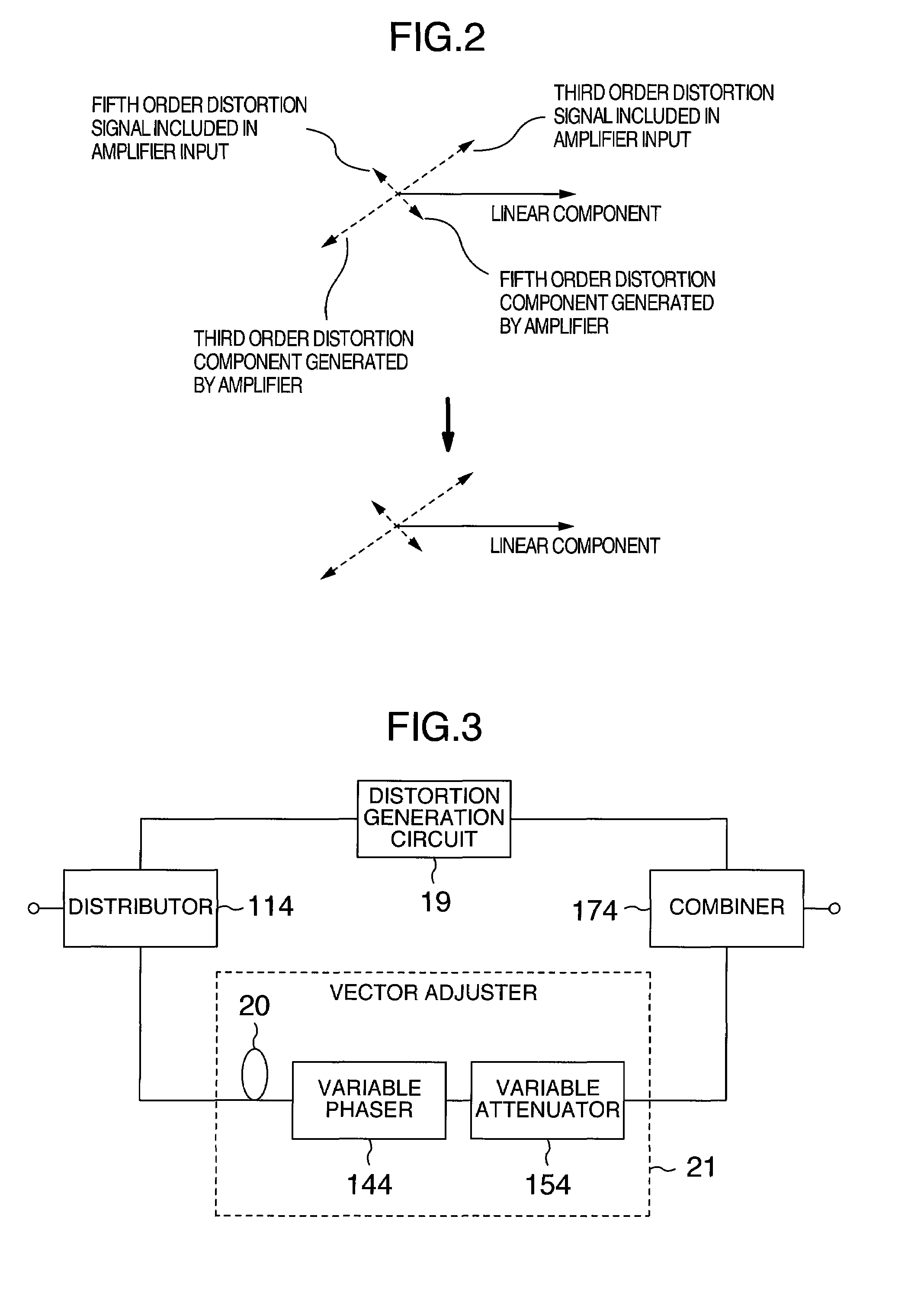

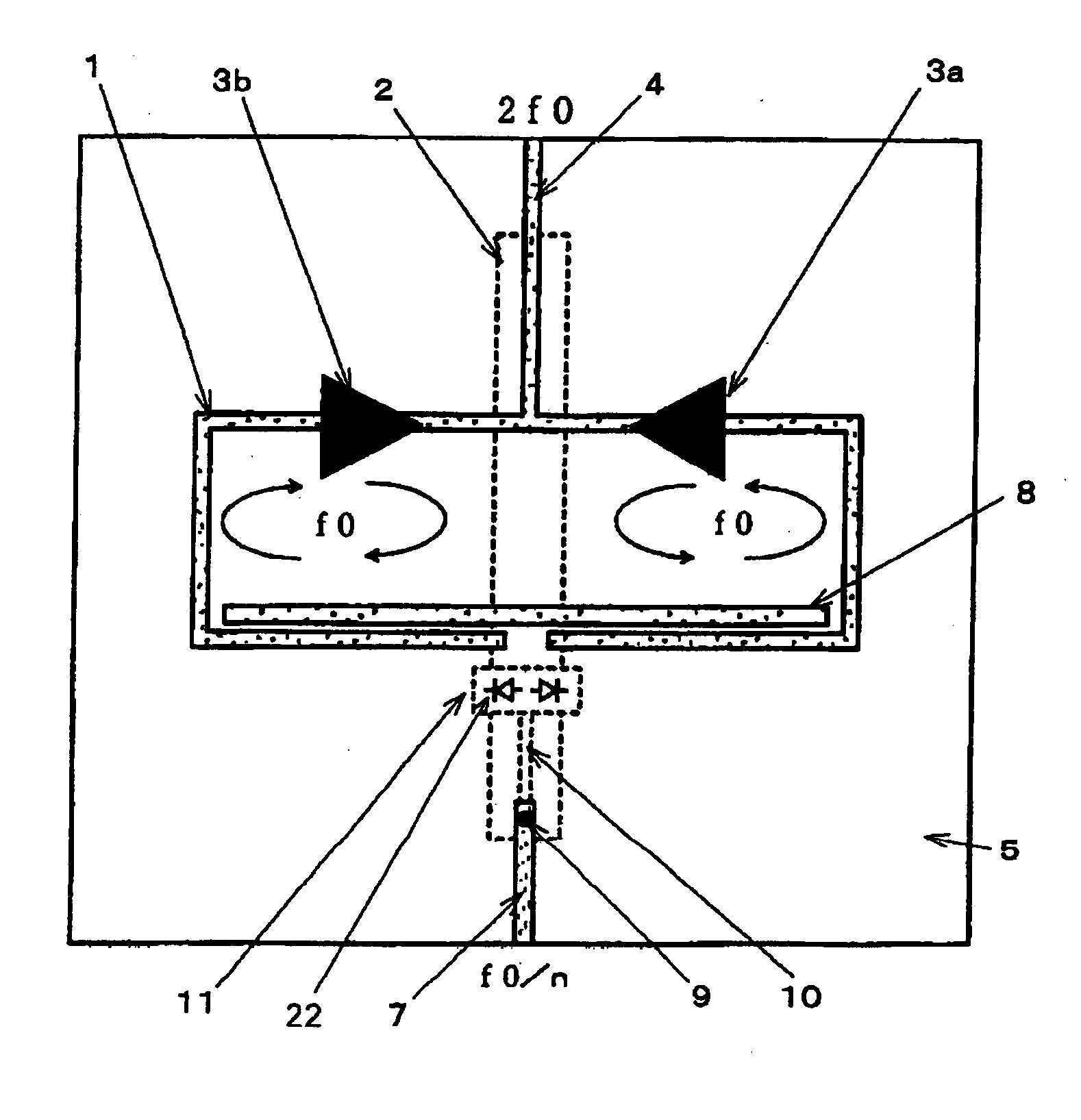

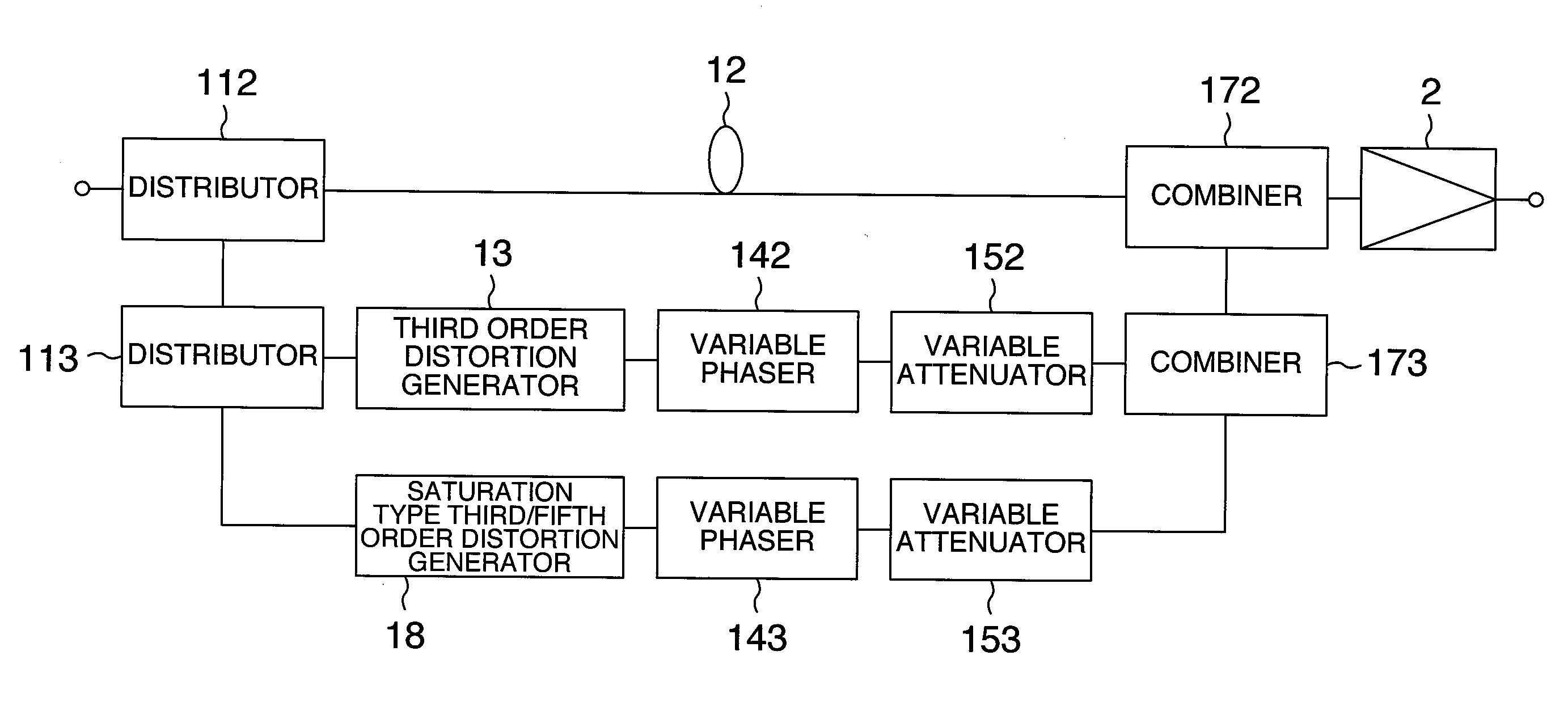

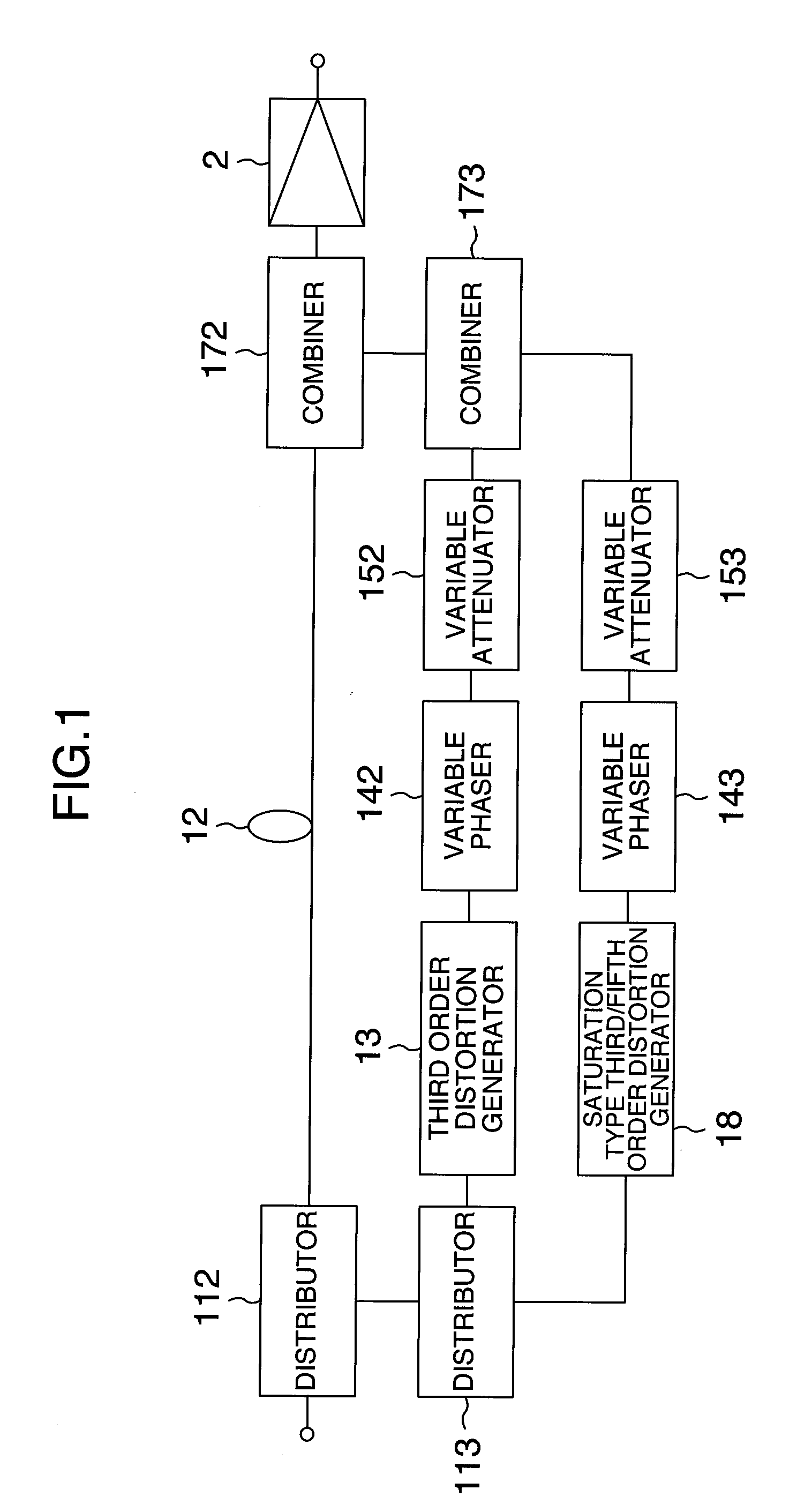

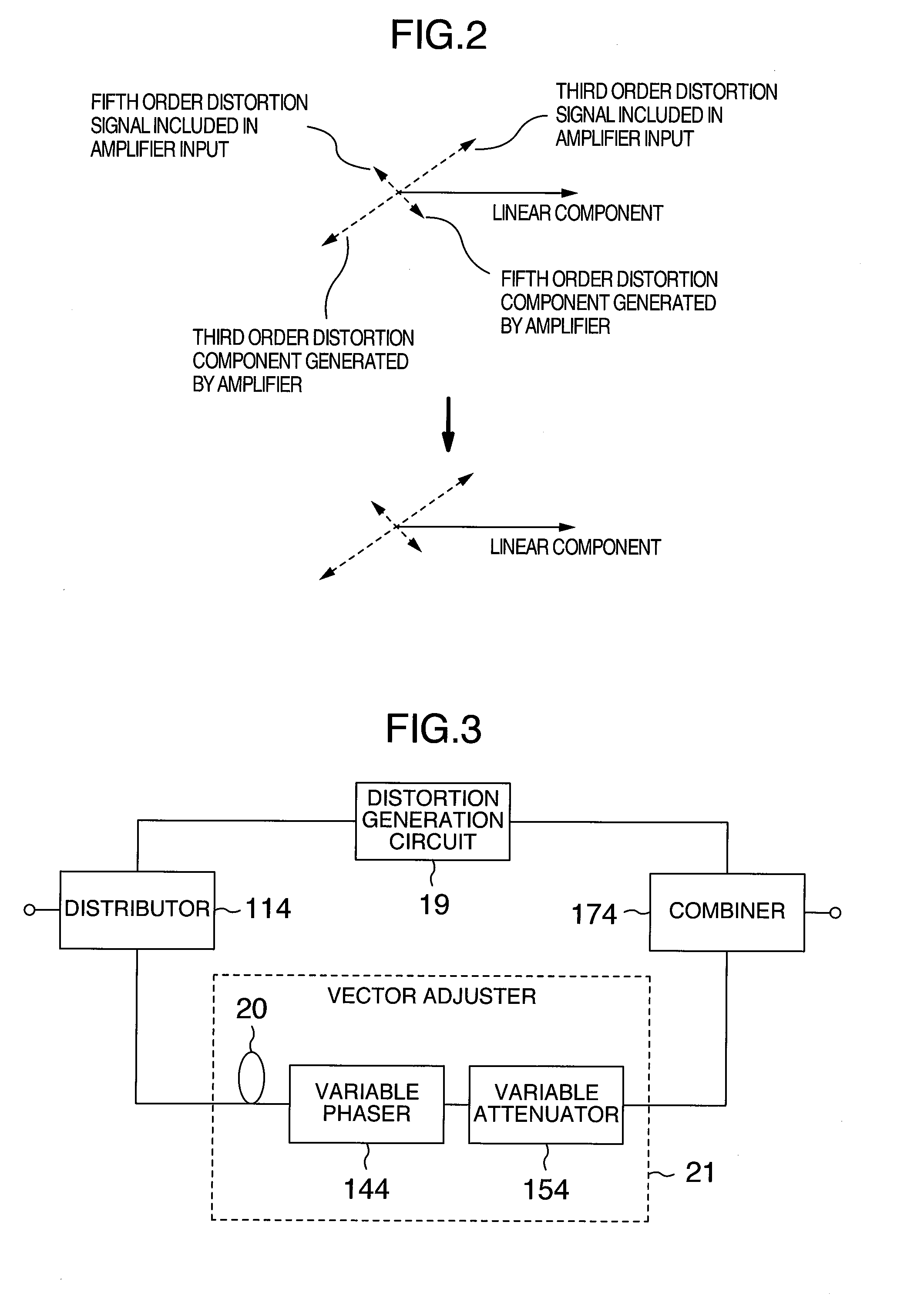

Distortion compensation apparatus

InactiveUS7626455B2Effective compensationAmplifier modifications to reduce noise influenceAmplifier modifications to reduce temperature/voltage variationAudio power amplifierDistortion

A distortion compensation apparatus includes distortion generating means for generating distortions to compensate for a distortion generated in an amplifier 2. The distortion generating means includes a nonlinear circuit 13 having an input / output expansion characteristic as a circuit which generates a distortion of the lowest odd order as a compensation target and also includes a nonlinear circuit 18 having an input / output saturation characteristic as a circuit which generates a distortion of another odd order as a compensation target.

Owner:KOKUSA ELECTRIC CO LTD

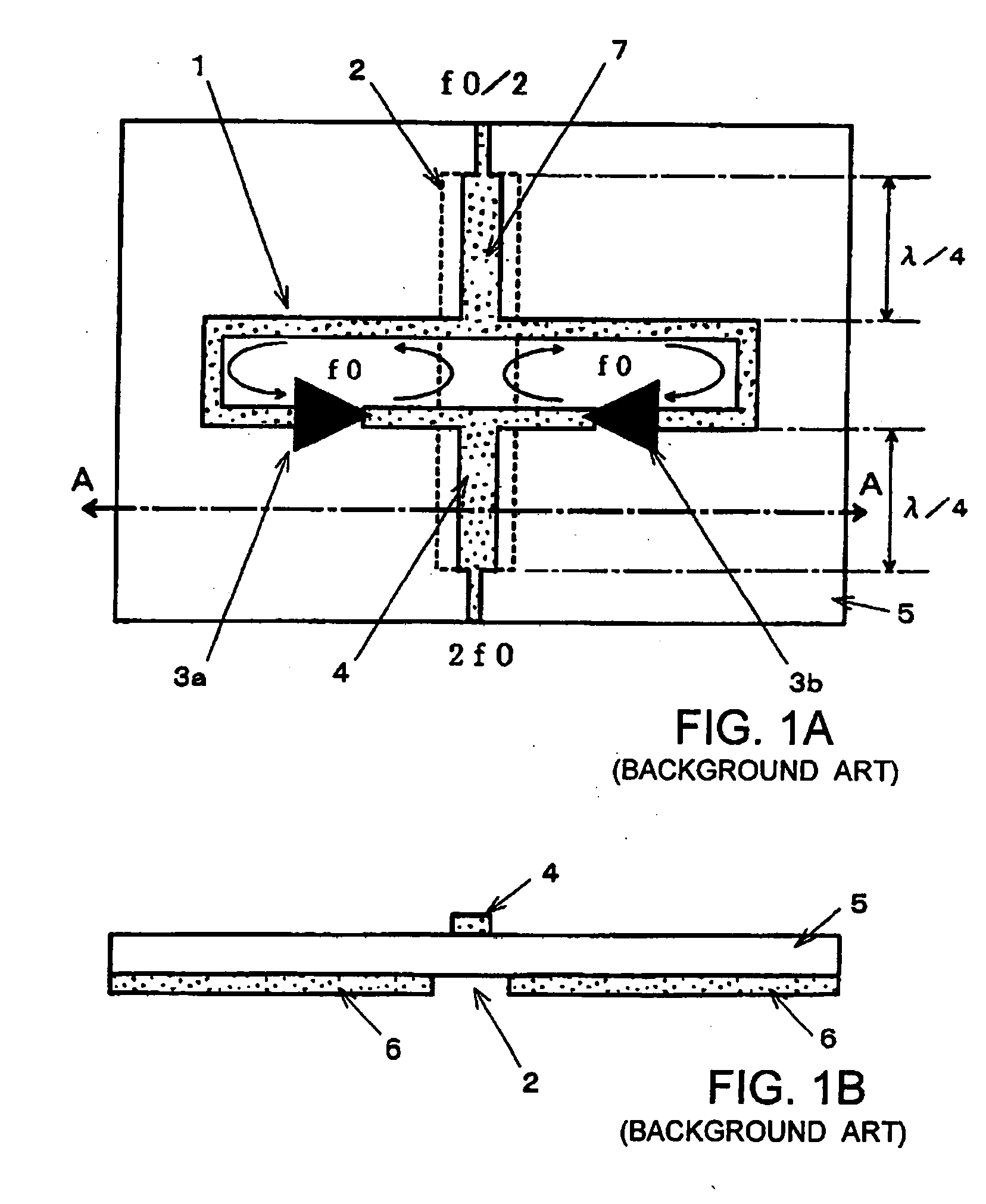

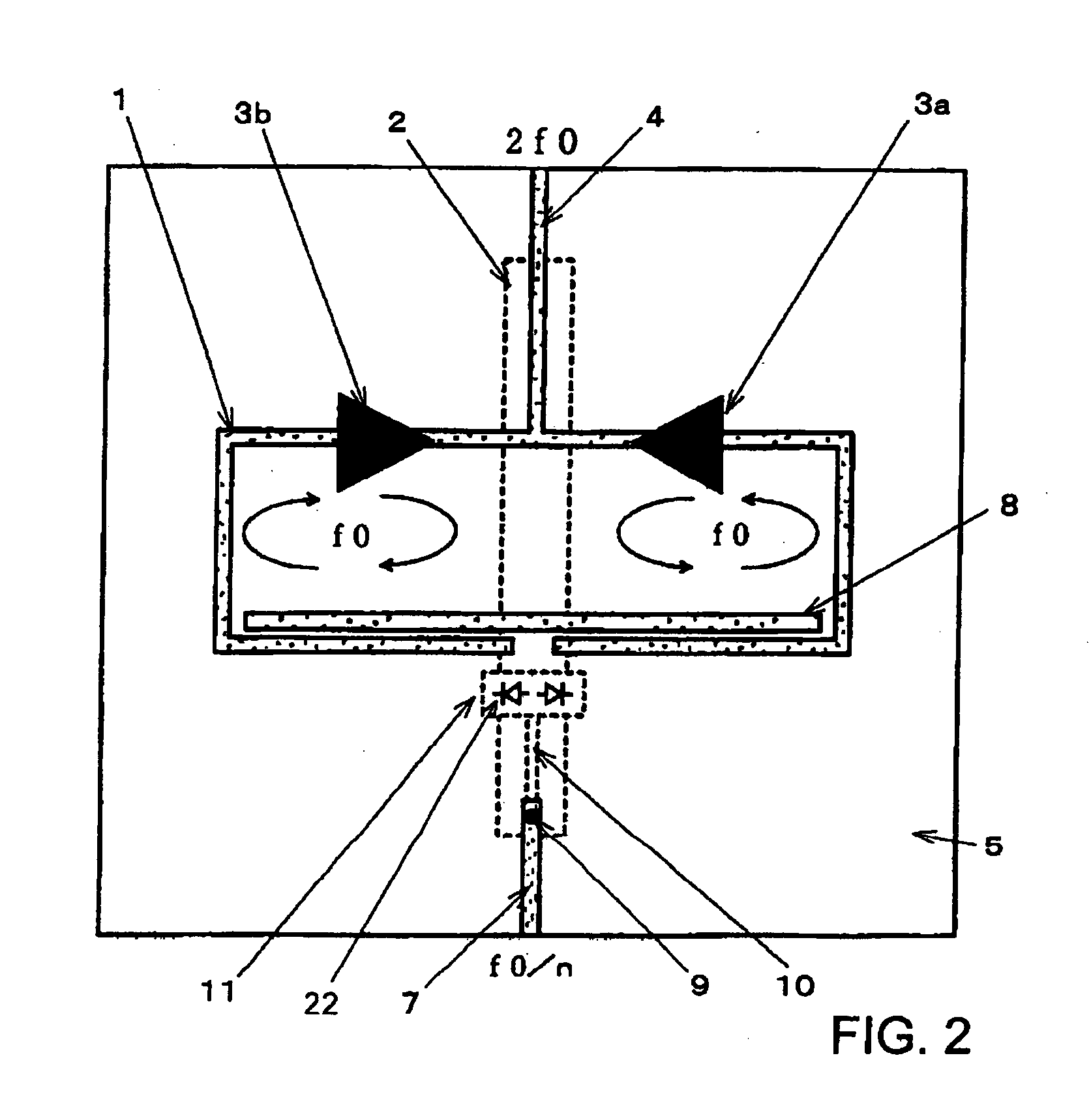

Injection locked high frequency oscillator

InactiveUS20050184816A1Improve frequency stabilityReduce phase noisePulse automatic controlSemiconductor/solid-state device detailsInjection lockedAudio power amplifier

A push-push high frequency oscillator comprises a pair of amplifiers for oscillation, a loop-shaped microstrip line for connecting inputs of the pair of amplifiers to each other and connecting outputs of the pair of amplifiers to each other, a slot line disposed between the inputs and the outputs of the pair of amplifiers for electromagnetically coupling with the microstrip line, a nonlinear circuit for enhancing the level of harmonic components in an applied synchronization signal, a coupler circuit for electromagnetically coupling the output of the nonlinear circuit to the microstrip line, and a filter circuit disposed at the output of the nonlinear circuit. The filter circuit filters harmonic components of the synchronization signal such that the two oscillation systems are injected with the same frequency components as the fundamental wave or frequency components twice as high as the fundamental wave to increase frequency stability.

Owner:NIHON DEMPA KOGYO CO LTD +1

In-line distortion cancellation circuits for linearization of electronic and optical signals with phase and frequency adjustment

ActiveUS7634198B2Reduce the amount of solutionLow insertion lossAmplifier modifications to reduce non-linear distortionNegative-feedback-circuit arrangementsNonlinear circuit elementsEngineering

A distortion circuit is provided for correcting the distortion from a nonlinear circuit element by generating a frequency dependent signal having a sign opposite to the distortion signal produced by the nonlinear circuit and substantially the same magnitude. The distortion circuit includes an input signal and a first nonlinear device coupled to the input signal for generating a first signal and where the first nonlinear device has a first bias level. Also included is a second nonlinear device different from same first nonlinear device and coupled to the first nonlinear device for modifying the first signal to produce an output second signal, the second nonlinear device having a second bias level. A bias control means is provided for adjusting the first and said second bias levels so that the magnitude, phase and frequency of the output second signal can be adjusted.

Owner:EMCORE INC

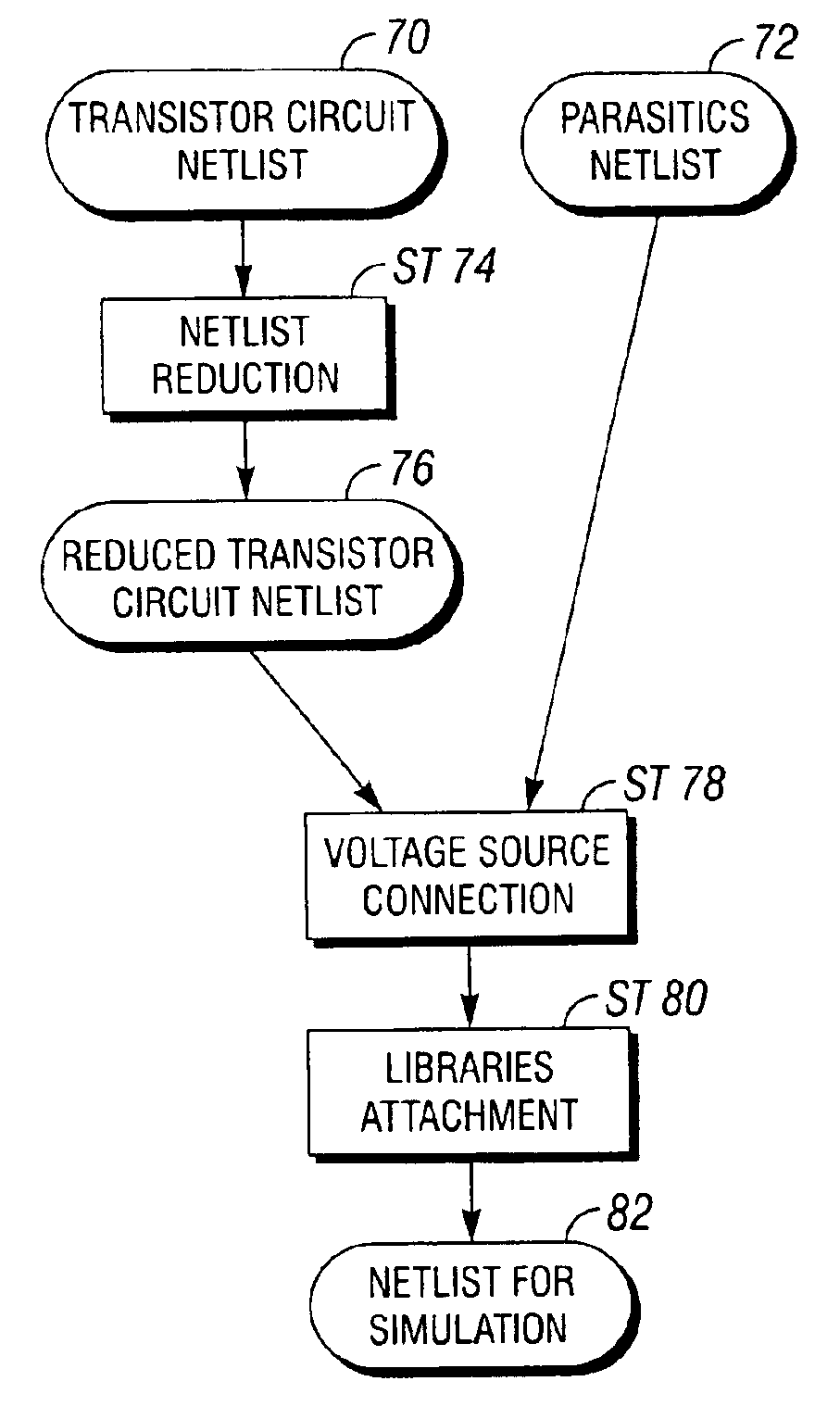

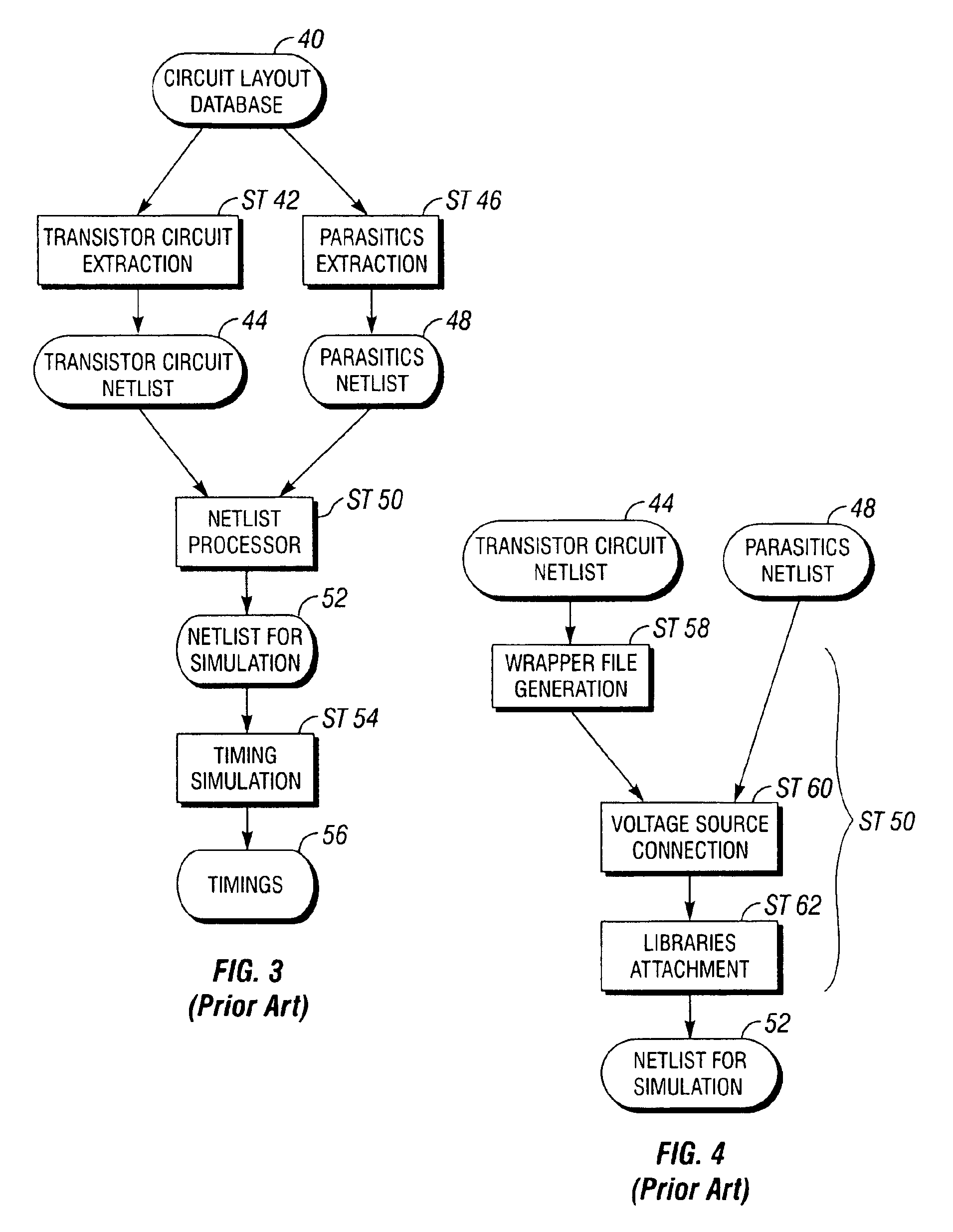

Circuit reduction technique for improving clock net analysis performance

InactiveUS6895524B2CAD circuit designGenerating/distributing signalsComputerized systemClock network

A method for reducing a transistor circuit netlist for clock network timing verification is provided. Further, a simulation tool that reduces a transistor circuit netlist such that nonlinear circuit properties are preserved is provided. Further, a computer system that improves clock network performance by simulating a netlist that is generated from a reduced transistor circuit netlist is provided.

Owner:ORACLE INT CORP

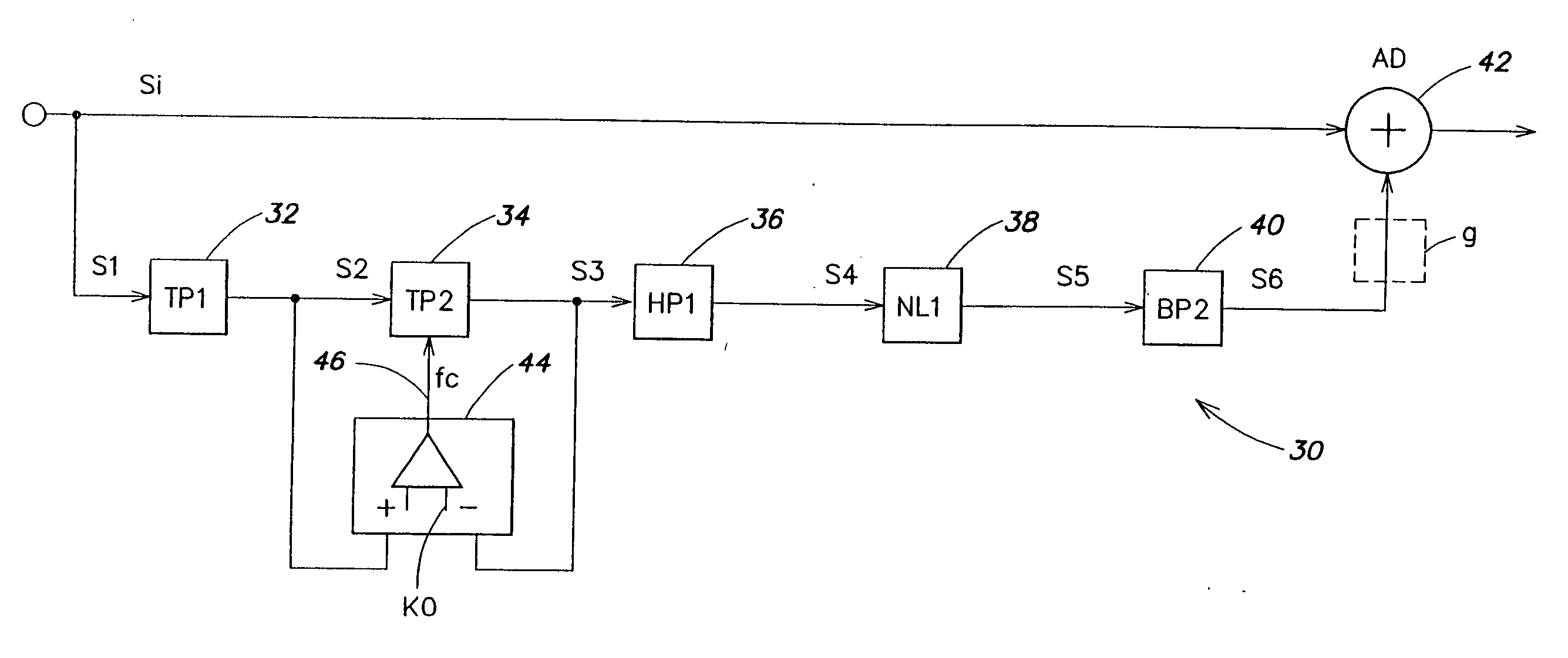

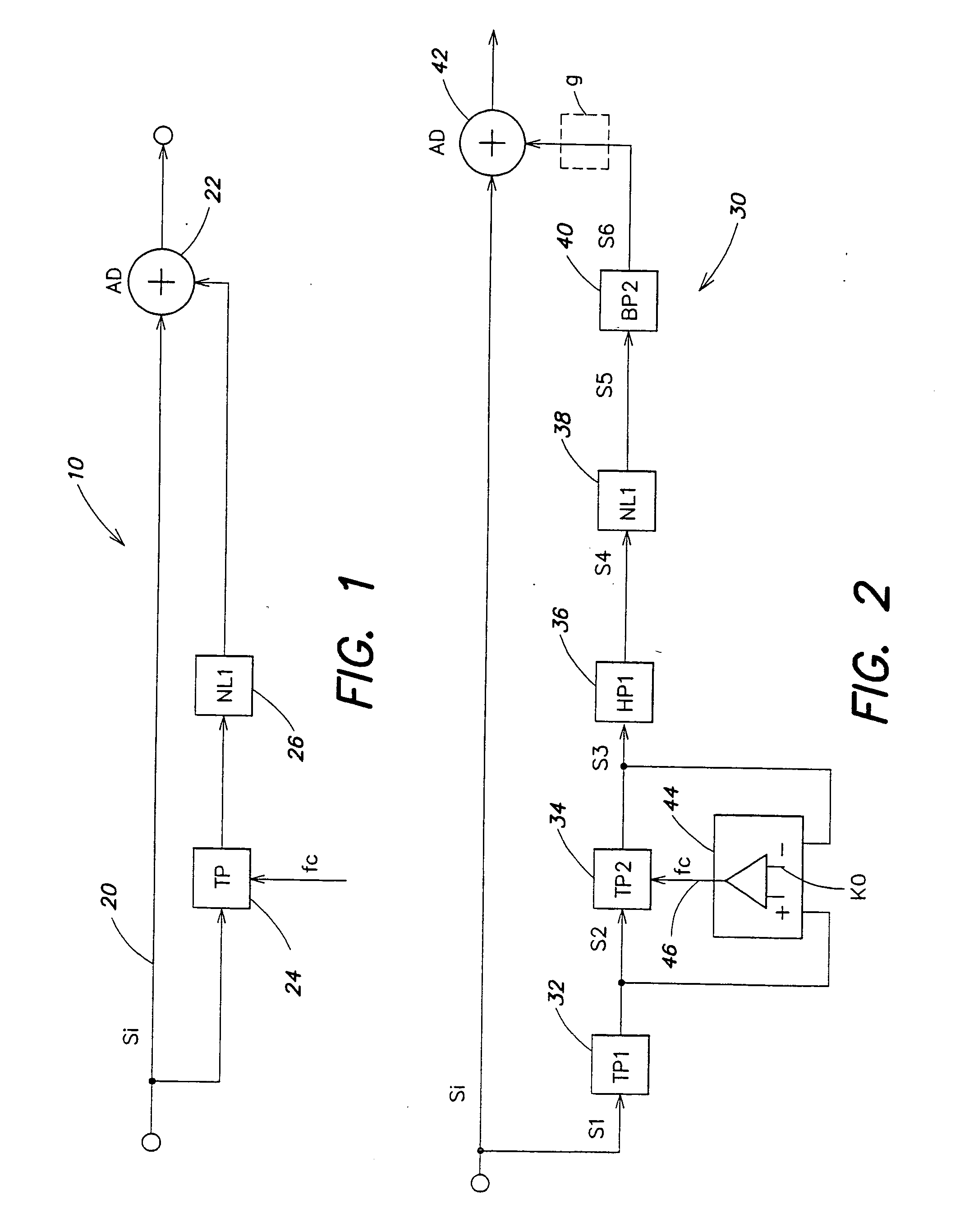

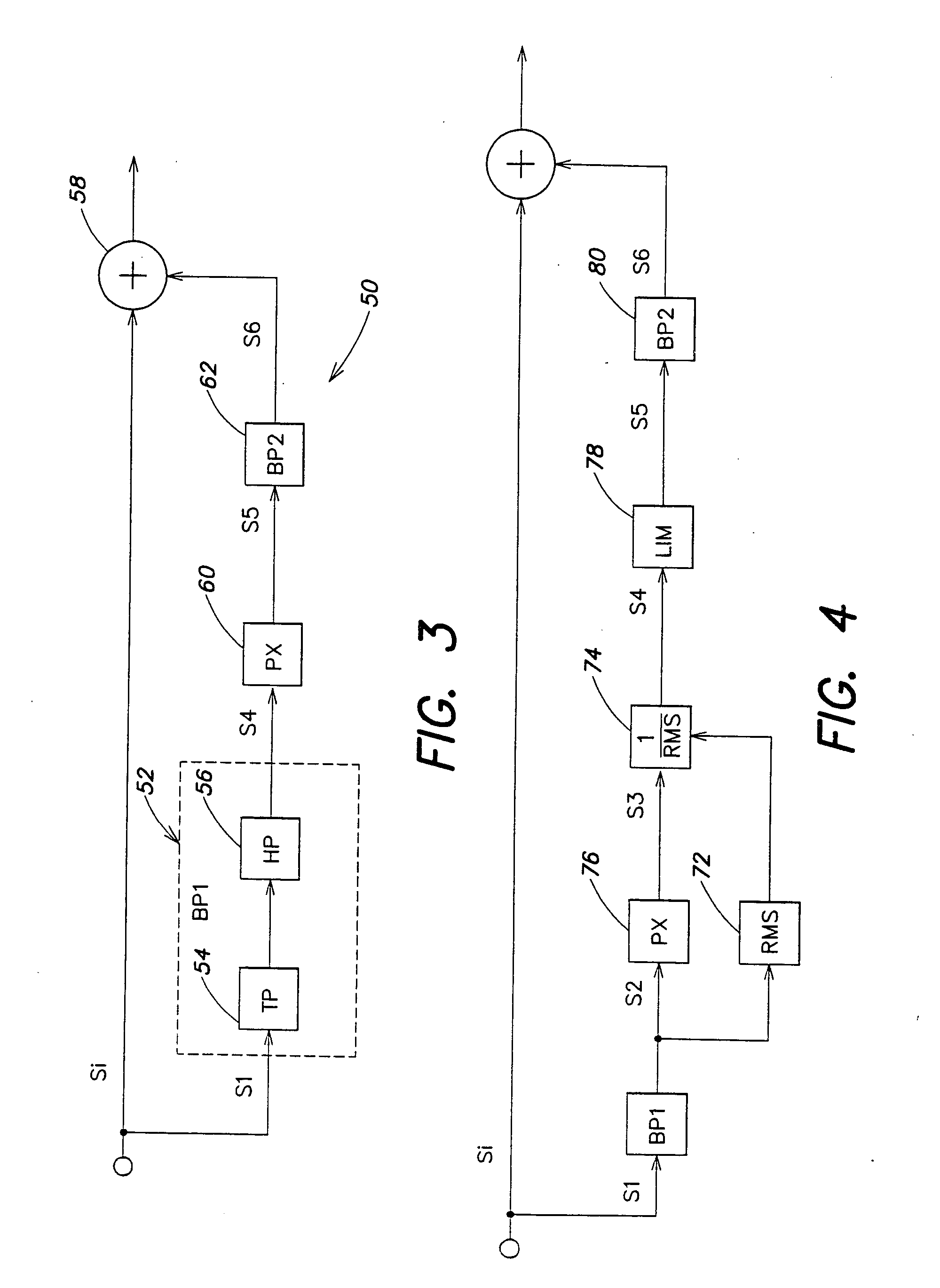

Apparatus for generating harmonics in an audio signal

InactiveUS20050141727A1Increase impressionGain controlAutomatic tone/bandwidth controlHarmonicEngineering

An apparatus for generating harmonics in an audio signal with an adder stage, which can add signals from a first signal line and a second signal line, such that an audio signal with harmonics can be tested at the output of the adder stage and such that a filter device and a nonlinear circuit device are situated in the second signal line, characterized in that a corner frequency of the filter device is adjustable

Owner:VIERTHALER MATTHIAS

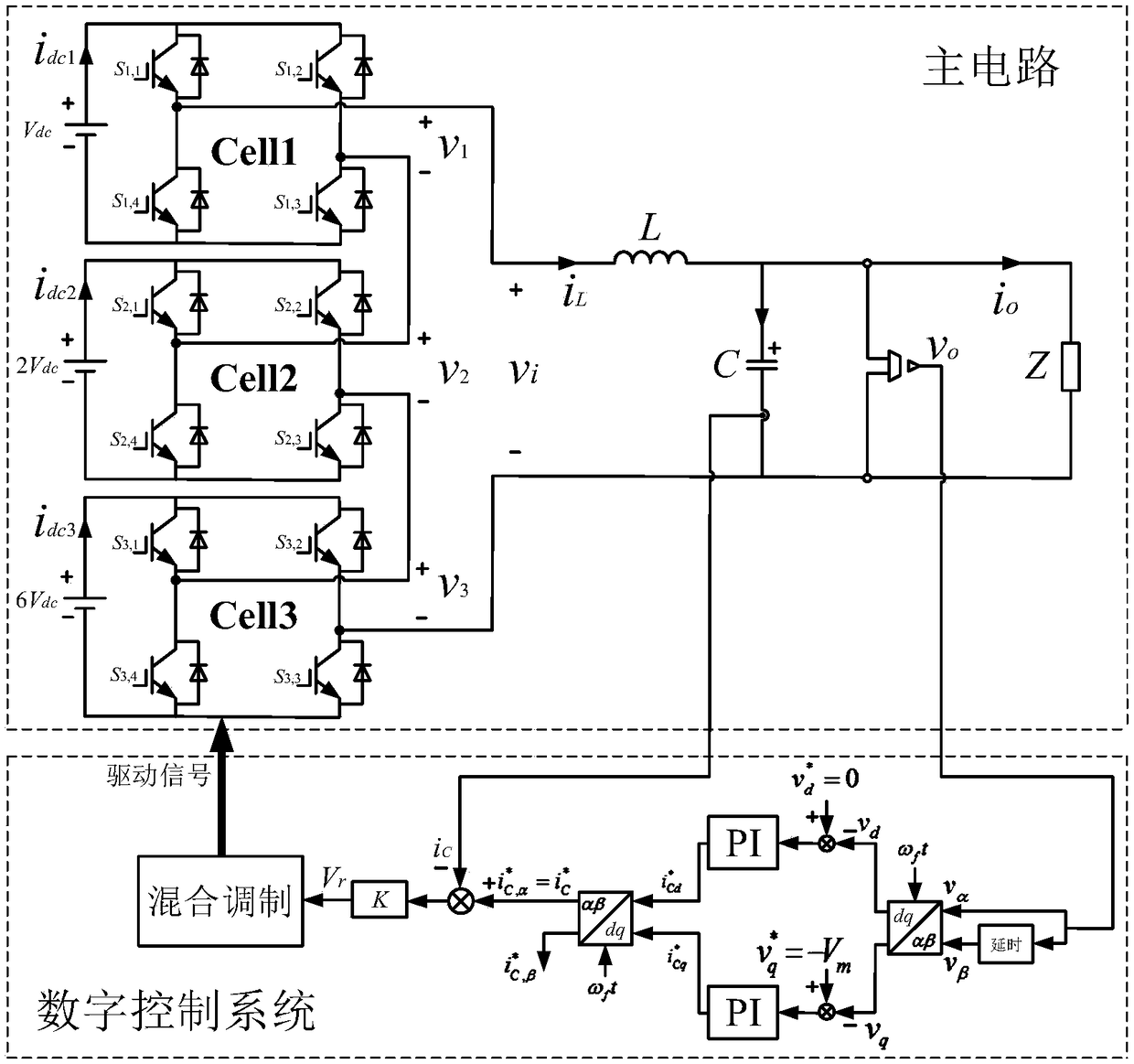

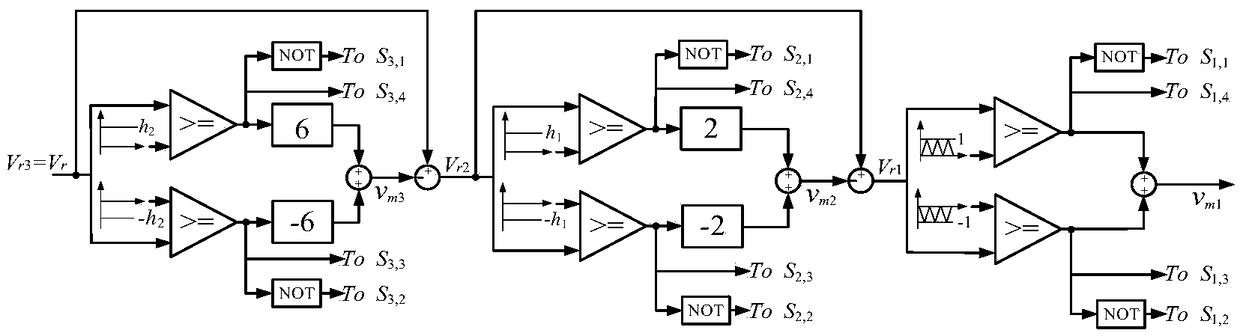

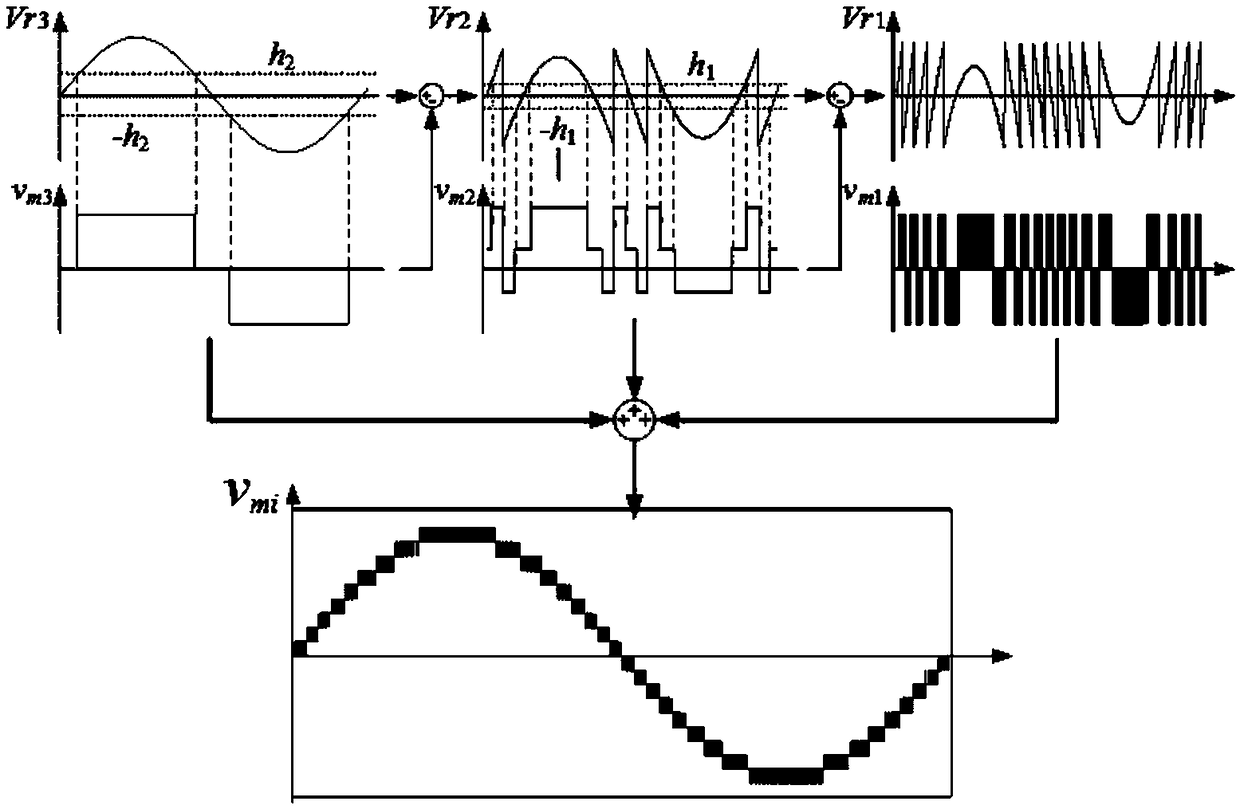

Small signal modeling and stability analysis method of single-phase cascaded island inverter system

InactiveCN109378989AReduce harmonic contentReduce voltage stressAc-dc conversionCapacitanceLow voltage

A small signal model based on a single-phase cascaded island ACHB inverter system and a stability analysis method based on a floquet theory are provided. The single-phase cascaded island ACHB invertersystem includes a digital controller with double closed loop control, an LC filter, a load and three single-phase H-bridge inverters operating at low voltage, medium voltage and high voltage respectively. The digital controller is connected to a filter capacitor. The small signal model based on the single-phase cascaded island ACHB inverter system, in consideration of a linear resistive load withsmall signal disturbance, separates a disturbance component, obtains a modulation signal expression by coordinate transformation, and analyzes the system stability by using the floquet theory. The beneficial effect is that a multi-level inverter reduces the harmonic components in the output voltage due to the increase of the output level of a main circuit, and the stability analysis of the smallsignal model solves the difficulty of modeling the nonlinear circuit of a converter, the dynamic characteristics of steady-state operating point of the converter are described by unified differentialequations, the stability domain of the system is accurately verified by the floquet theory, and a reliable criterion is provided for the stable operation of the whole single-phase cascaded island inverter system.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

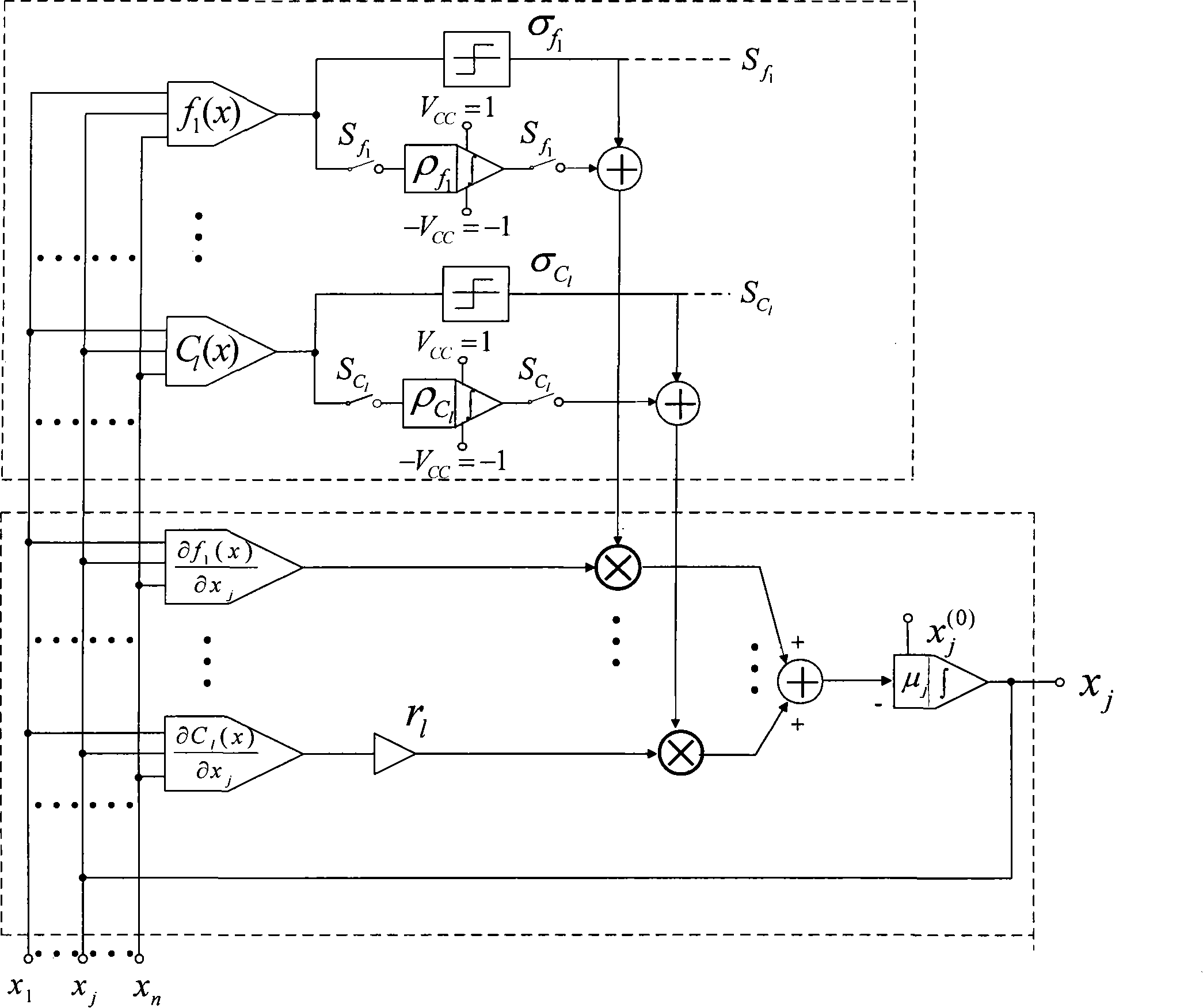

Circuit failure diagnosis method based on neural network

InactiveCN101251576AAvoid errorsImprove the accuracy of fault diagnosisElectronic circuit testingPhysical realisationNonlinear circuitsDevice parameters

The invention discloses a circuit fault diagnosis method based on a neural network, wherein current excitation or voltage excitation is exerted on a to-be-tested circuit; the voltage of a testable junction is measured and is compared with that of a normal condition to obtain voltage increment; according to the Kirchhoff theorem of circuit, the relation equation of circuit device parameters and excitation and response is obtained; then, element parameter increment is taken as an optimization variable; the relation equation is solved through adopting a constraint nonlinearity noncontinuous optimization method to obtain element parameter increment; finally, the increment is compared with a normal parameter to determine a fault element. The circuit fault diagnosis method has the characteristics of strong anti-interference capability, fast location and high accuracy, etc.; moreover, the method has wide application range and is suitable for the test and the diagnosis of a linear circuit, a nonlinear circuit and a mixed signal circuit.

Owner:HUNAN UNIV

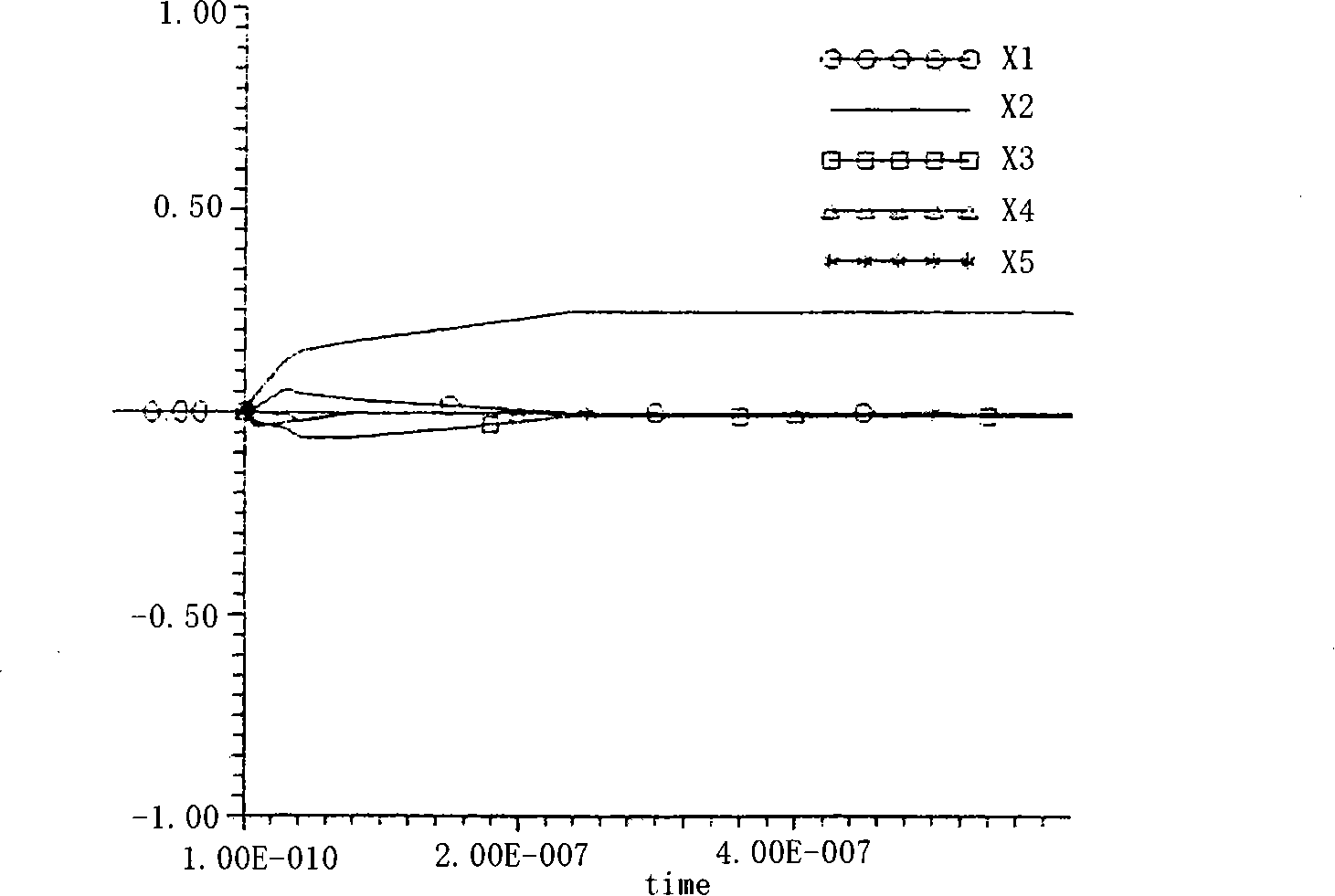

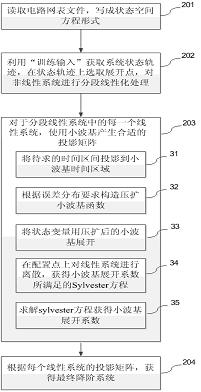

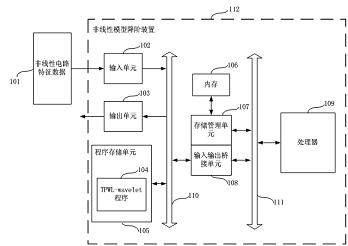

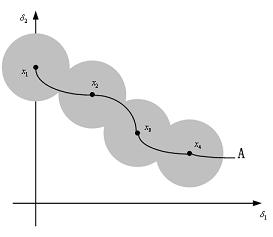

Nonlinear circuit time domain model reduction method and device

ActiveCN102467593AHigh precisionEasy to controlSpecial data processing applicationsTerm memoryLinear circuit

The invention belongs to the field of design of an integrated circuit and relates to a nonlinear circuit time domain model reduction method and a nonlinear circuit time domain model reduction device. The method comprises the following steps of: forming a track in a state space through a 'training signal', and selecting an expansion point on the track to approach a nonlinear circuit through a segmented linear method; and obtaining a final reduction model through a time domain model reduction method based on wavelet collocation. The device comprises an input unit, an output unit, a program storage unit, an external bus, a memory, a storage management unit, an input / output bridging unit, a system bus and a processor. A nonlinear system is directly subjected to model reduction in a time domain, the time domain reduction accuracy of the nonlinear system can be guaranteed, and a time domain error can be controlled; therefore, an accurate and compact reduction model can be acquired, and the simulation accuracy and efficiency are improved.

Owner:FUDAN UNIV

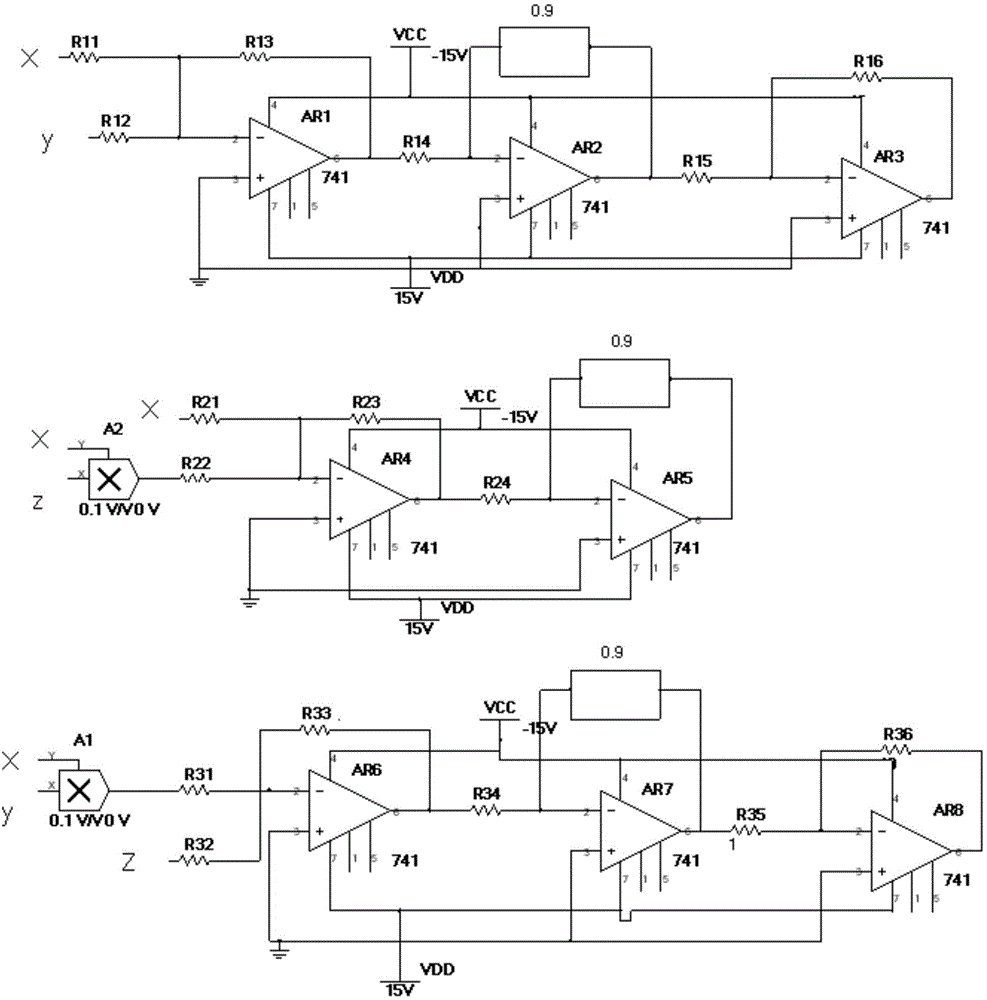

Fractional order T chaotic circuit

InactiveCN104144050AImprove performanceSimple structureSecuring communicationBinary multiplierChaotic

A fractional order T chaotic circuit is composed of three channels. The fractional order T chaotic circuit is characterized in that an output signal of the first channel is fed back to an input end to serve as a first path of input signal connected with an input pin of a multiplying unit A2, last-level output of the first channel is connected with the input of a multiplying unit A1 and the input of the second channel, the output of the second channel is connected with the input, namely the multiplying unit A1, of the third channel, the output of the third channel is fed back to the input, and a last-level output signal is connected with the second channel and the multiplying units. The fractional order T chaotic circuit is simple in structure and reliable in performance and has an extremely important application value in image encryption and secret communication. The fractional order T chaotic circuit is suitable for university chaos science and chaotic circuit demonstration, a nonlinear circuit box and the like.

Owner:XIJING UNIV

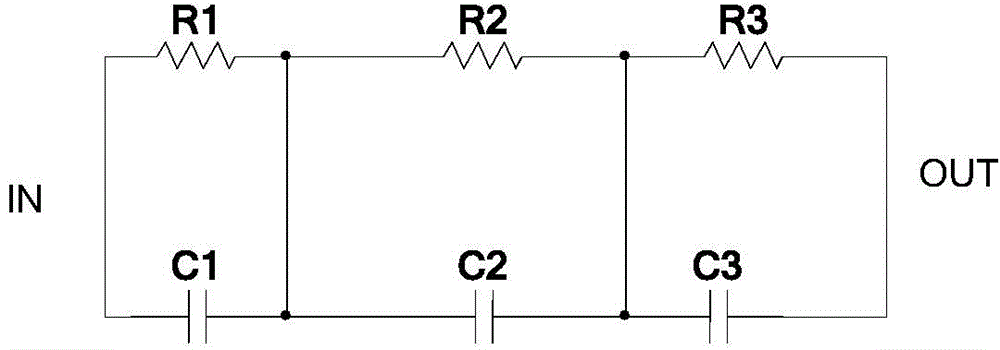

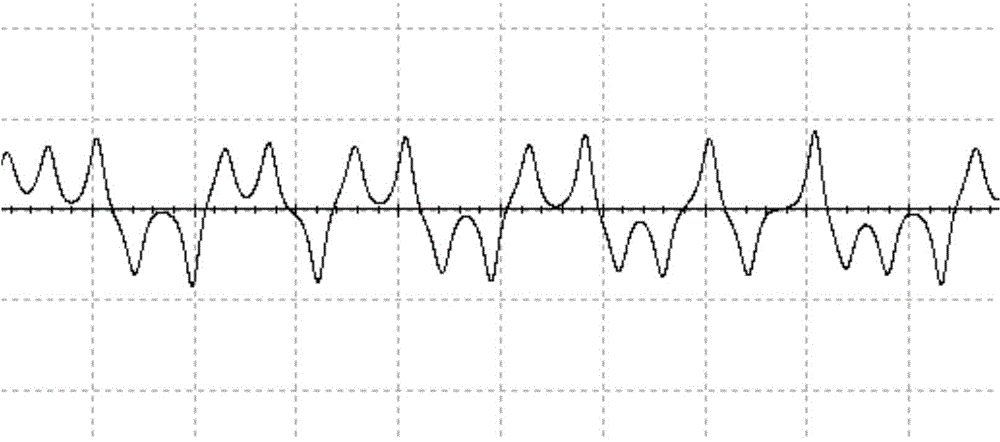

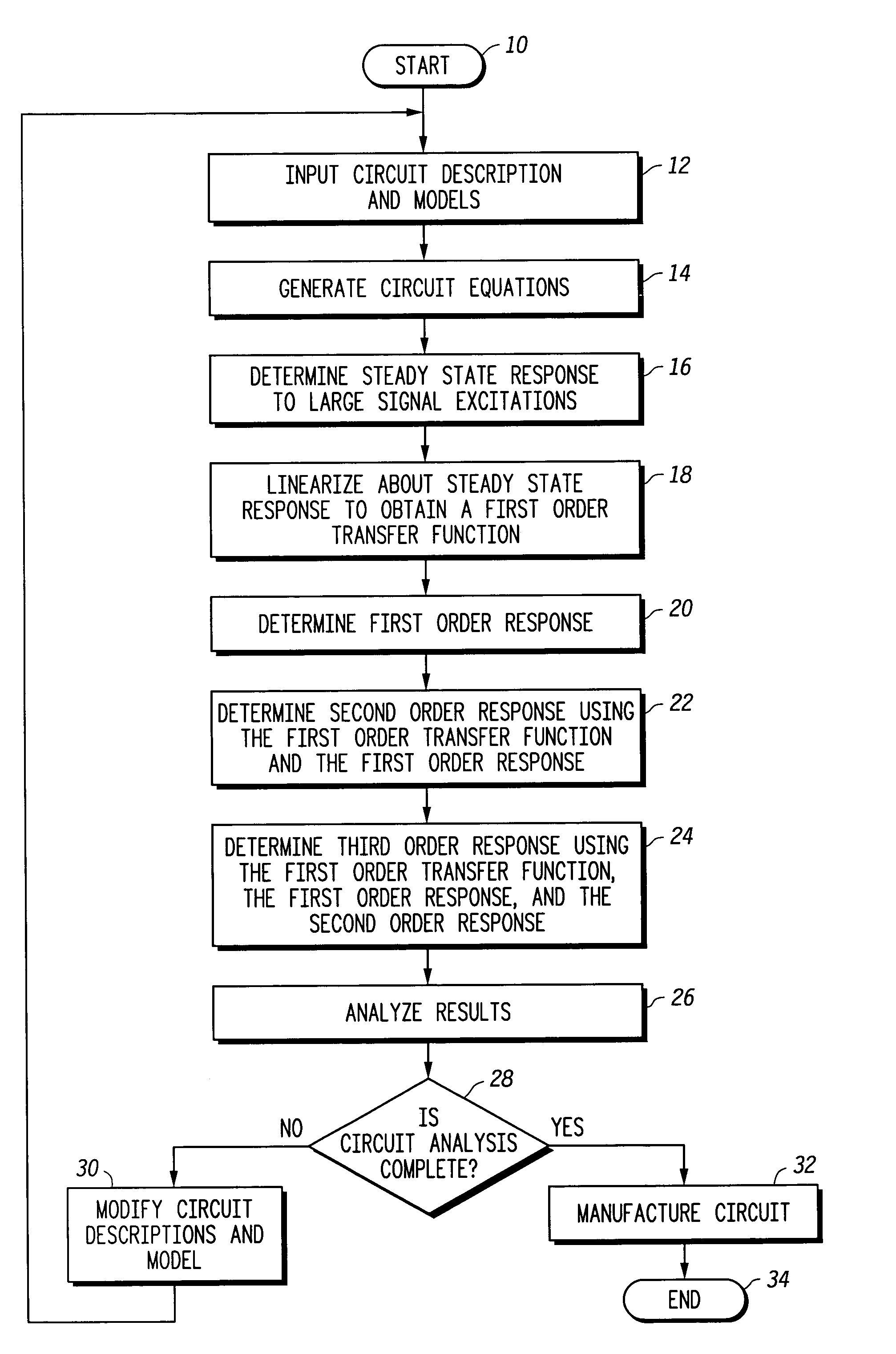

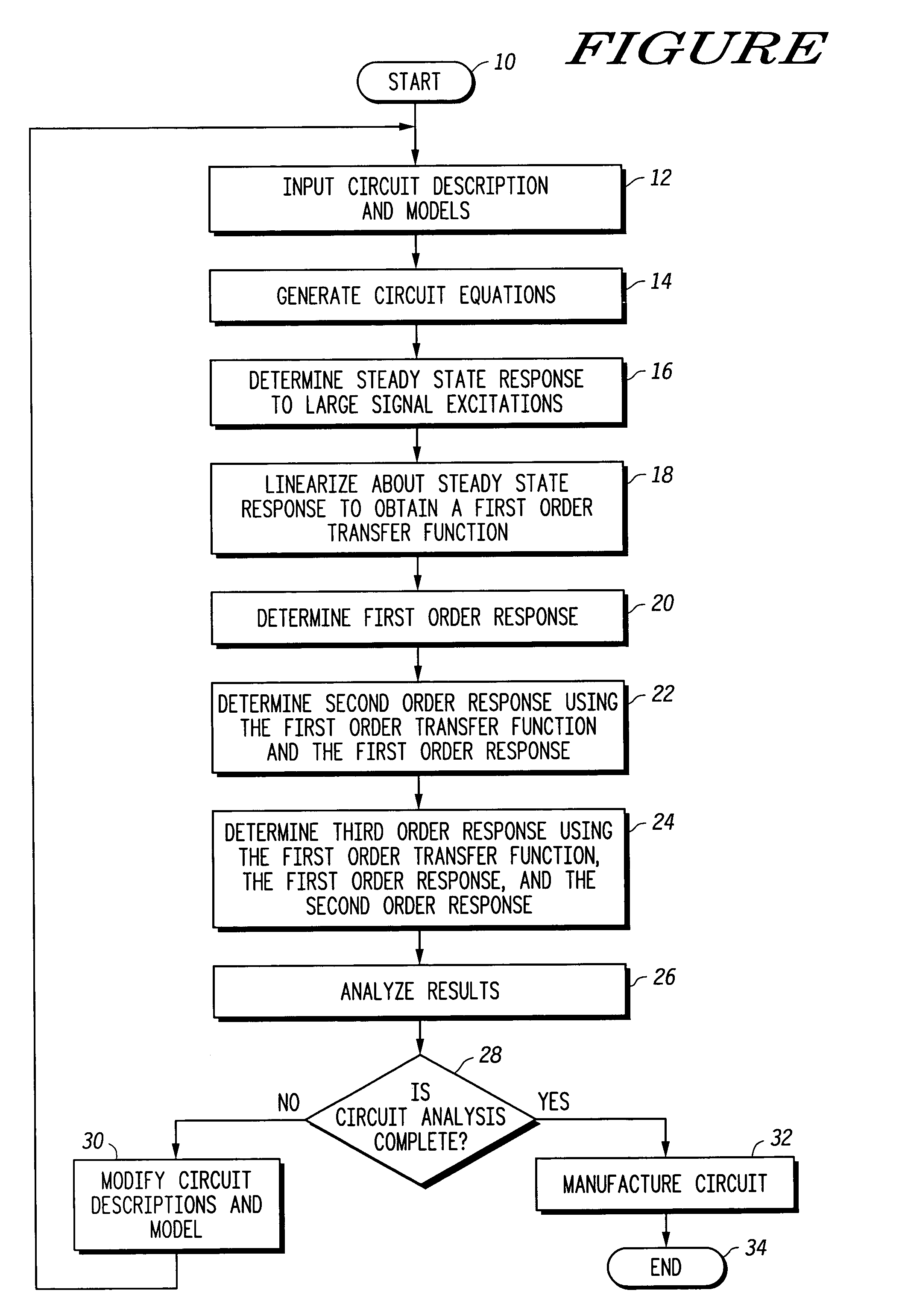

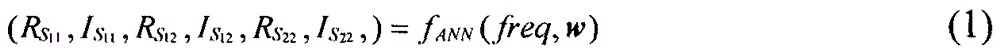

Method and apparatus for distortion analysis in nonlinear circuits

A circuit on an integrated circuit is made from a design that is verified using a design tool. The design tool takes a model of the circuit and generates equations with respect to nodes on the circuit. The time consuming task of completely determining the voltage at each node is performed for a predetermined input. To determine the node voltages for other signals, the first order transfer function of the equations is taken and then calculated for the predetermined input. A first order estimate of the node voltages is achieved using this first order transfer function and the node voltages determined from the predetermined input. A second order estimate is achieved using the first order transfer function and the first order estimate. A third order estimate is achieved using the first order transfer function and the second order estimate. The circuit design is verified for manufacturabiltity then manufactured.

Owner:APPLE INC

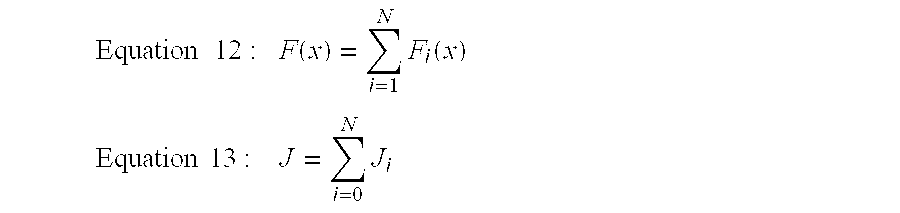

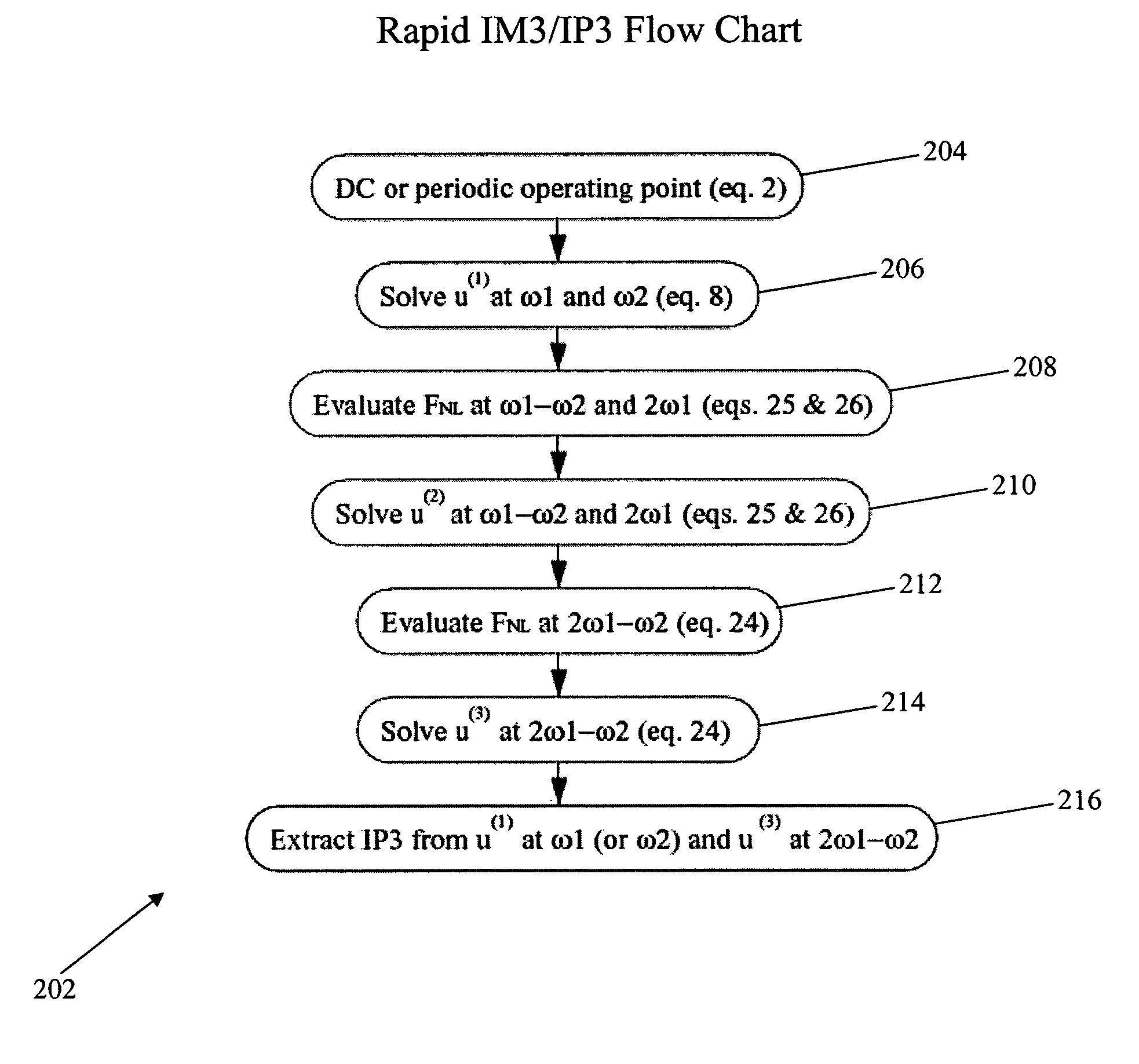

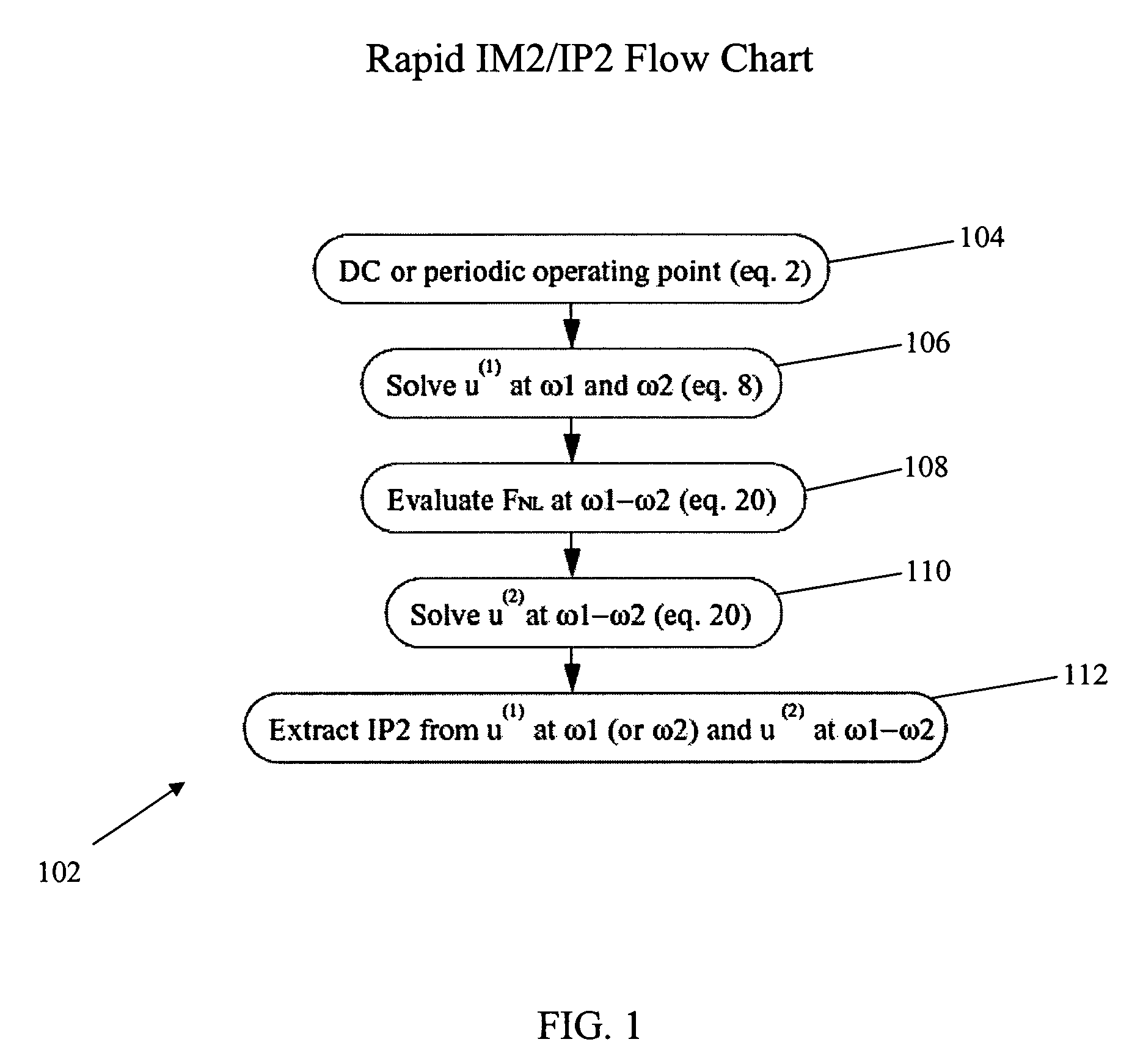

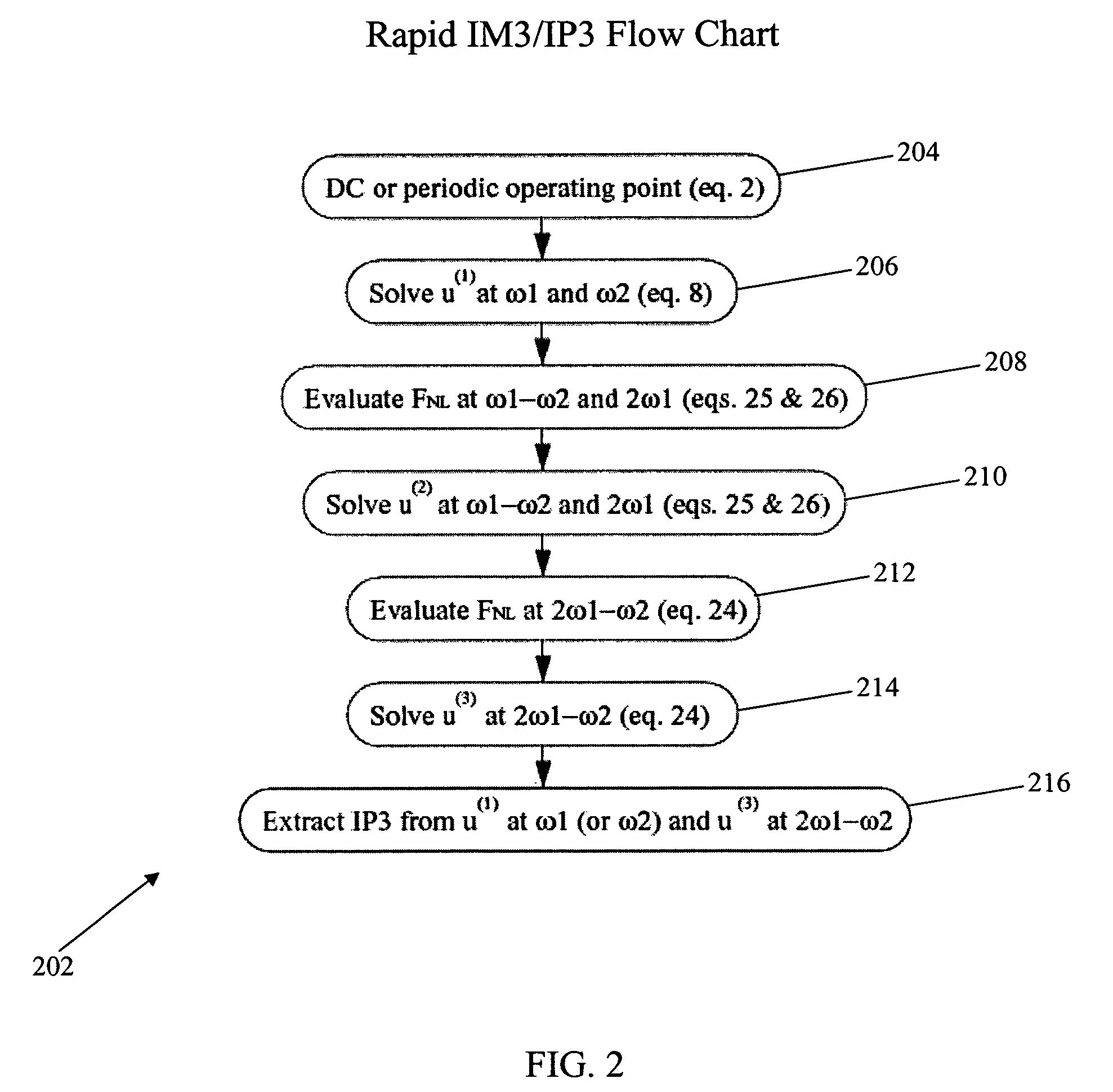

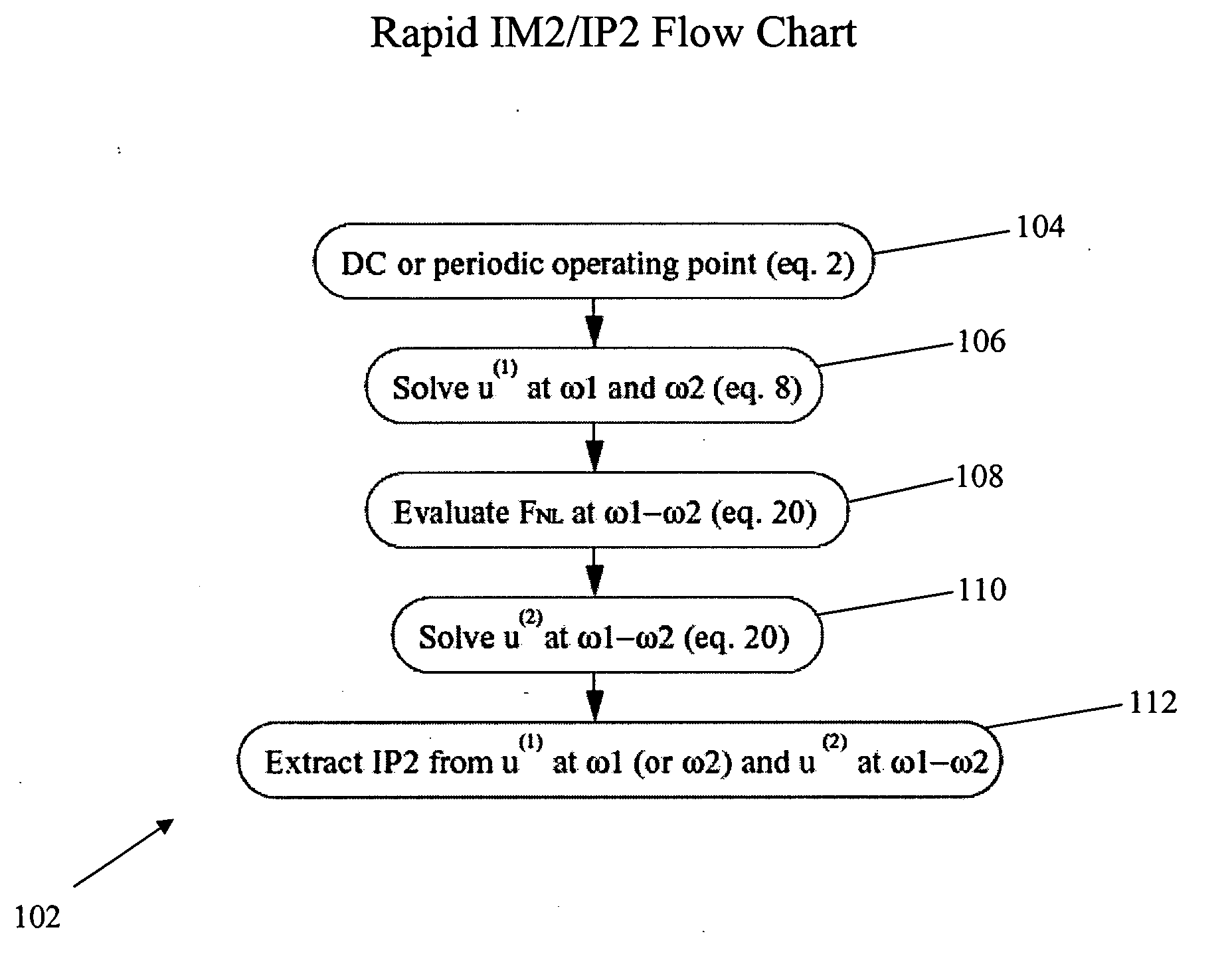

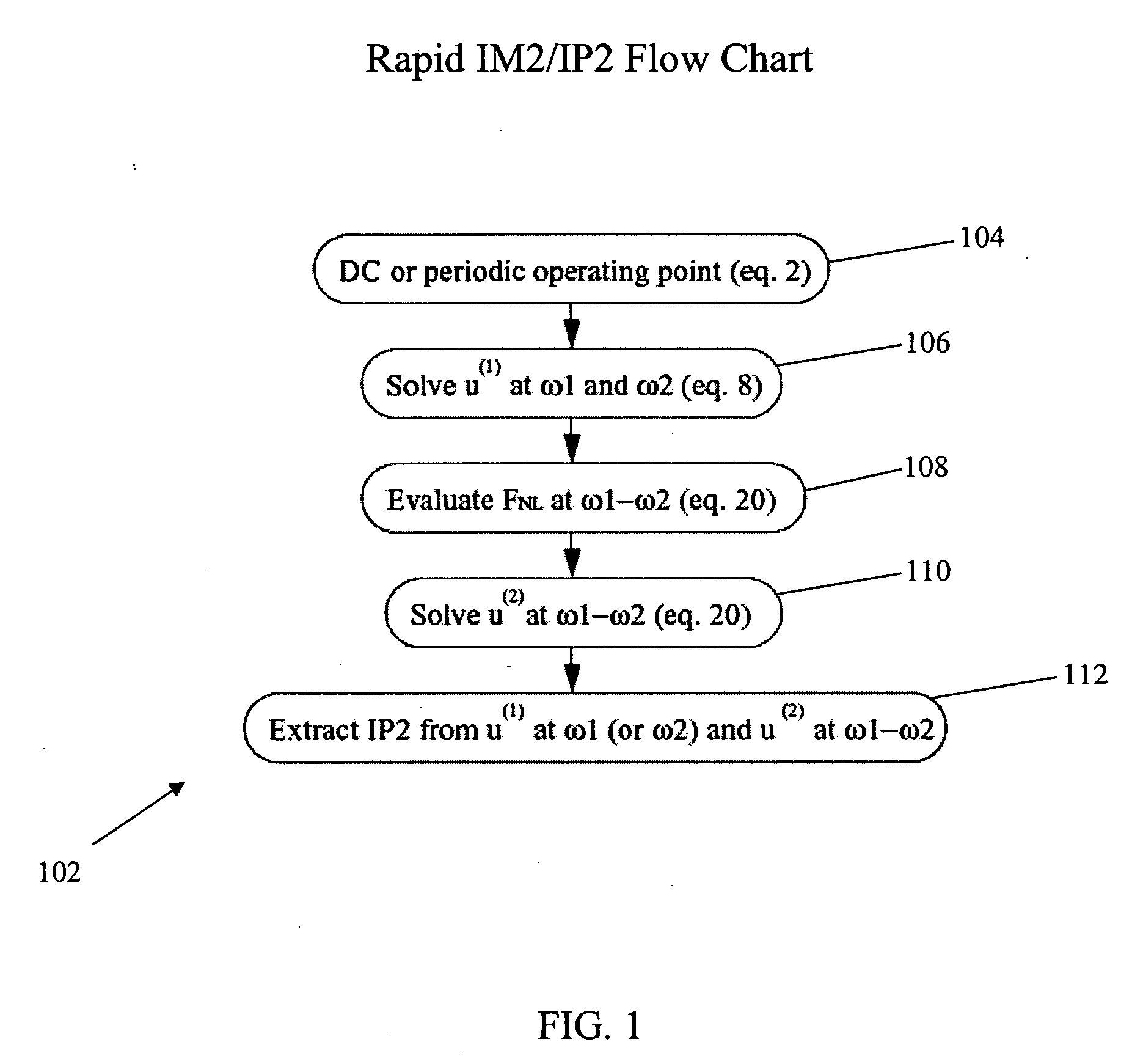

Calculating intermodulation products and intercept points for circuit distortion analysis

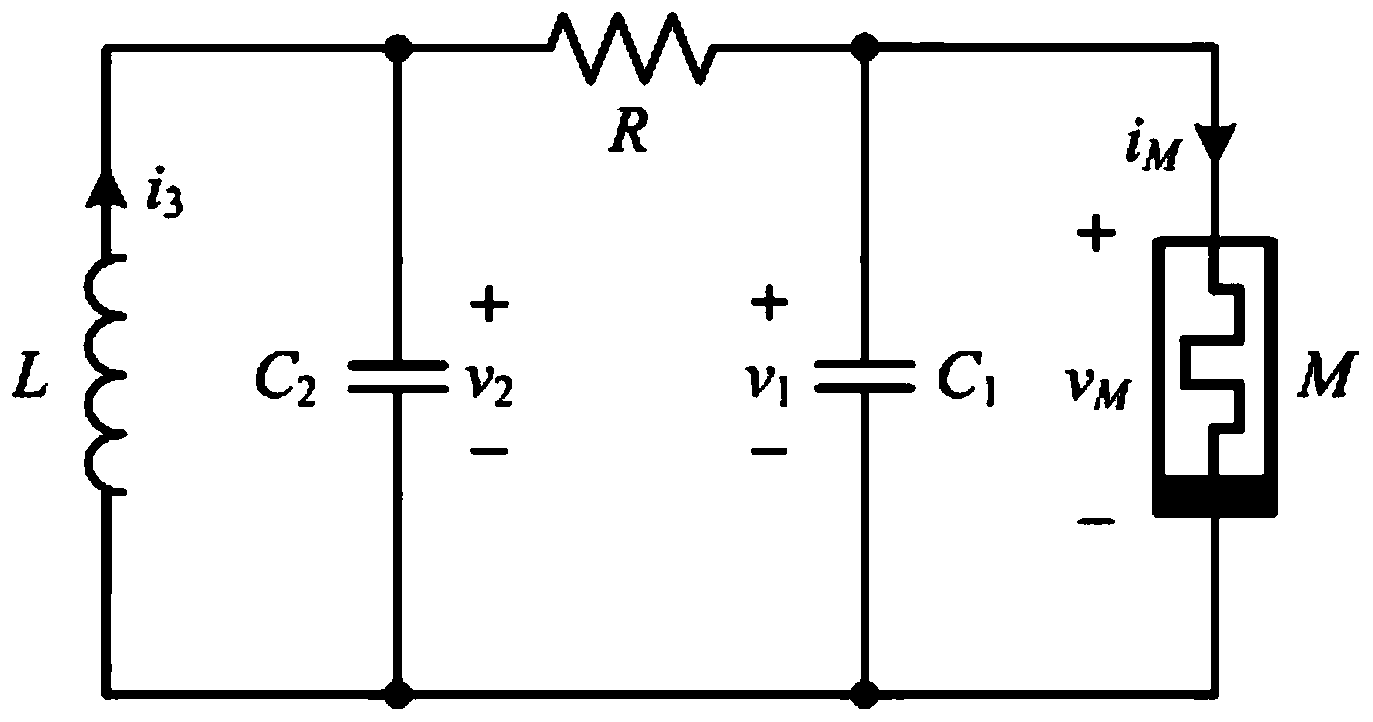

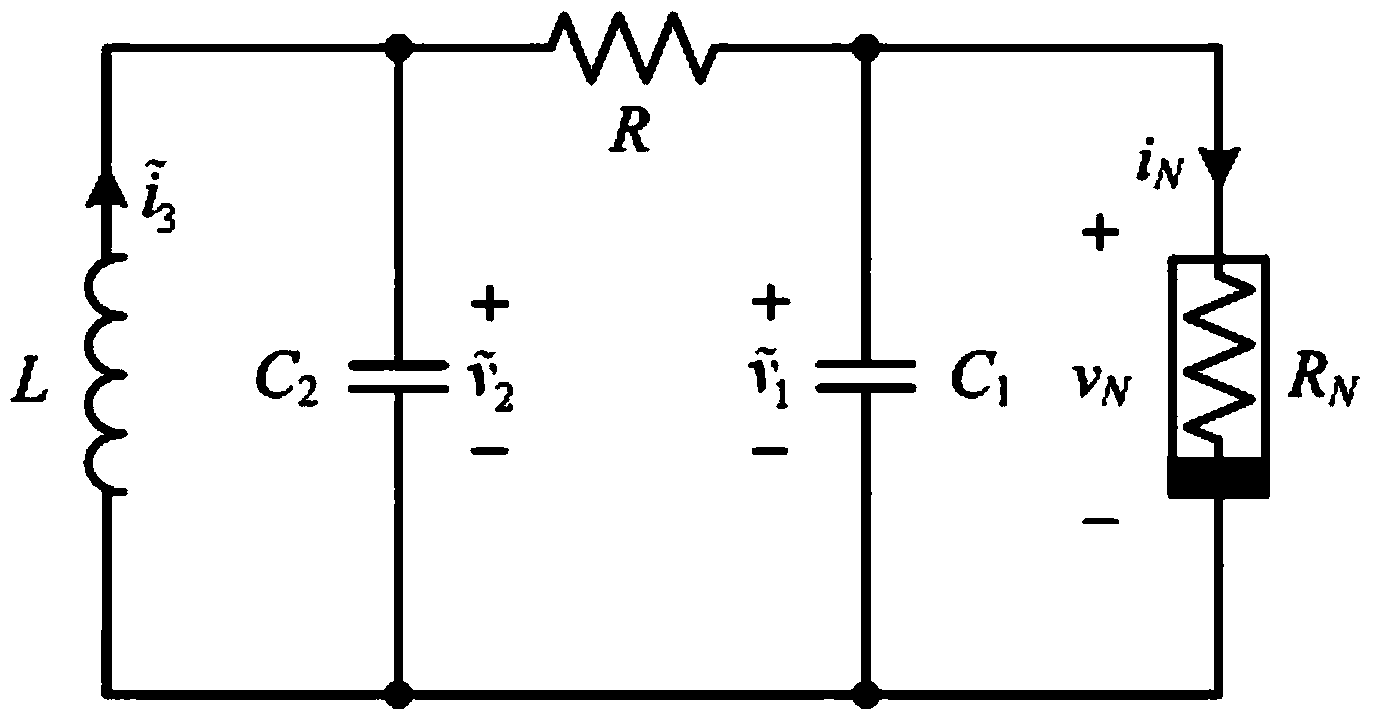

ActiveUS7774176B2Easy to calculateAnalogue computers for electric apparatusComputation using non-denominational number representationTime domainHarmonic

A pertubative approach based on the Born approximation resolves weakly nonlinear circuit models without requiring explicit high-order device derivatives. Convergence properties and the relation to Volterra series are discussed. According to the disclosed methods, second and third order intermodulation products (IM2, IM3) and intercept points (IP2, IP3) can be calculated by second and third order Born approximations under weakly nonlinear conditions. A diagrammatic representation of nonlinear interactions is presented. Using this diagrammatic technique, both Volterra series and Born approximations can be constructed in a systematic way. The method is generalized to calculate other high-order nonlinear effects such as IMn (nth order intermodulation product) and IPn (nth order intermodulation intercept point). In general, the equations are developed in harmonic form and can be implemented in both time and frequency domains for analog and RF circuits.

Owner:CADENCE DESIGN SYST INC

Calculating intermodulation products and intercept points for circuit distortion analysis

ActiveUS20070136045A1Easy to calculateAnalogue computers for electric apparatusComputation using non-denominational number representationTime domainHarmonic

A pertubative approach based on the Born approximation resolves weakly nonlinear circuit models without requiring explicit high-order device derivatives. Convergence properties and the relation to Volterra series are discussed. According to the disclosed methods, second and third order intermodulation products (IM2, IM3) and intercept points (IP2, IP3) can be calculated by second and third order Born approximations under weakly nonlinear conditions. A diagrammatic representation of nonlinear interactions is presented. Using this diagrammatic technique, both Volterra series and Born approximations can be constructed in a systematic way. The method is generalized to calculate other high-order nonlinear effects such as IMn (nth order intermodulation product) and IPn (nth order intermodulation intercept point). In general, the equations are developed in harmonic form and can be implemented in both time and frequency domains for analog and RF circuits.

Owner:CADENCE DESIGN SYST INC

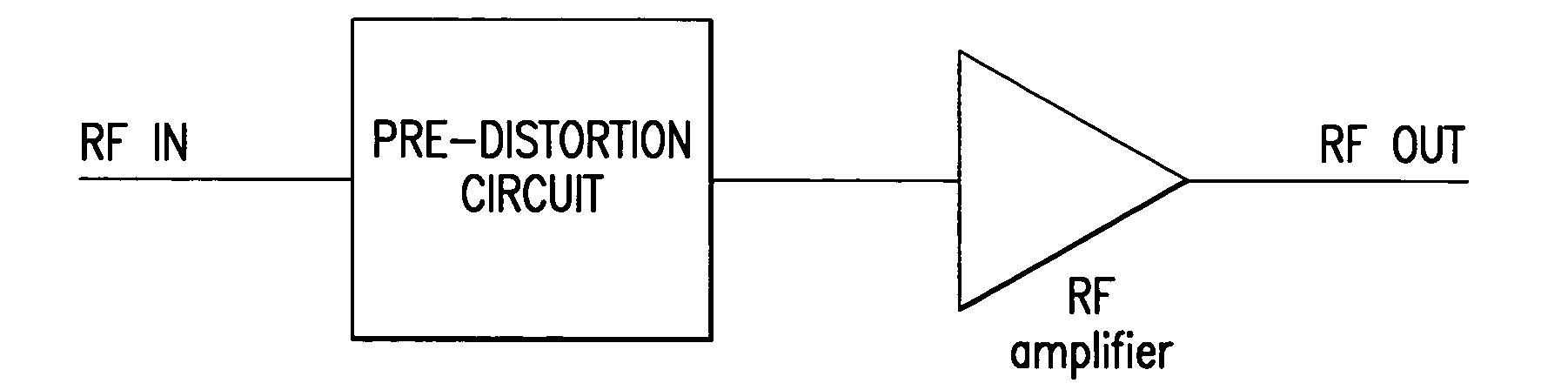

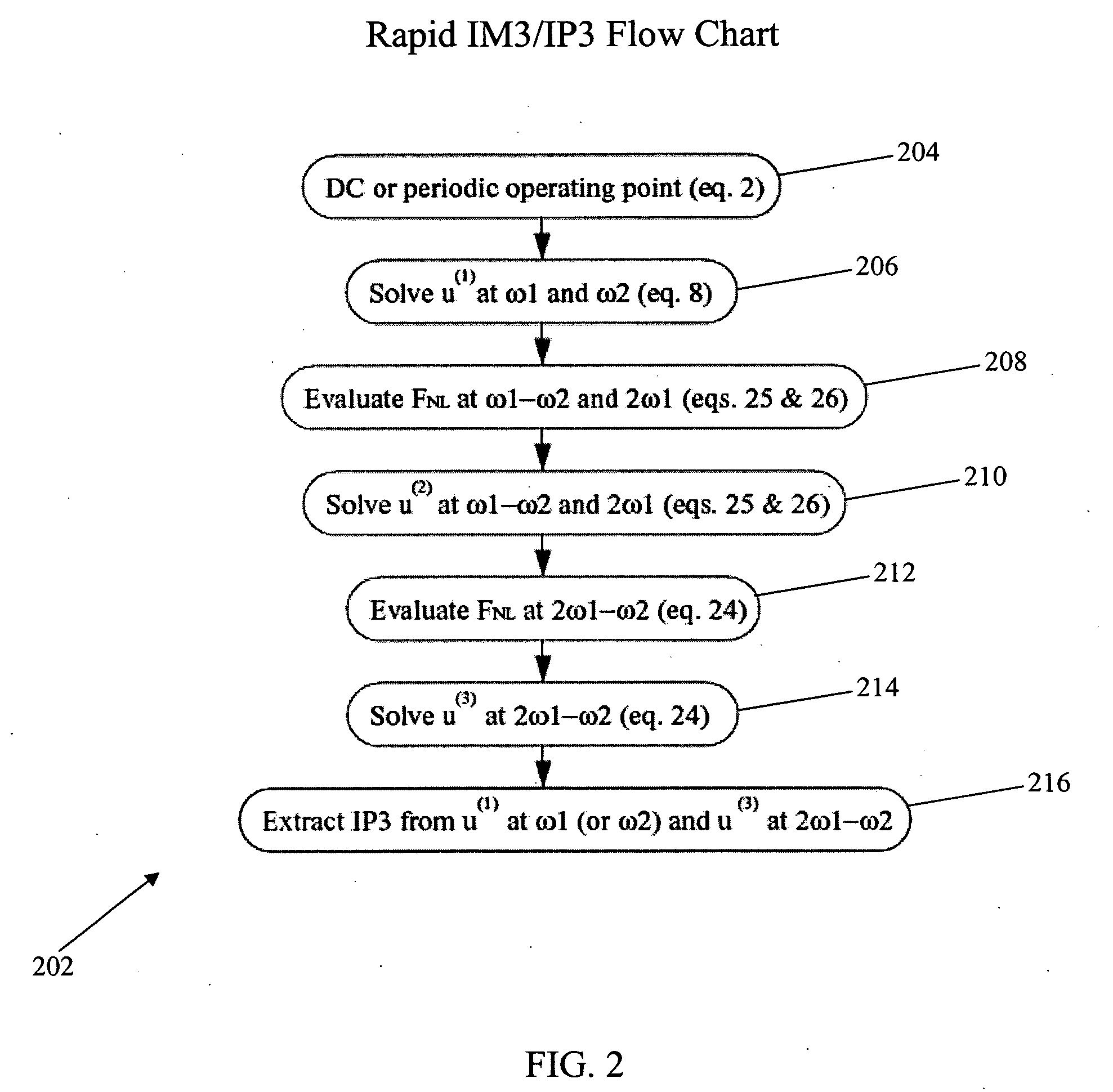

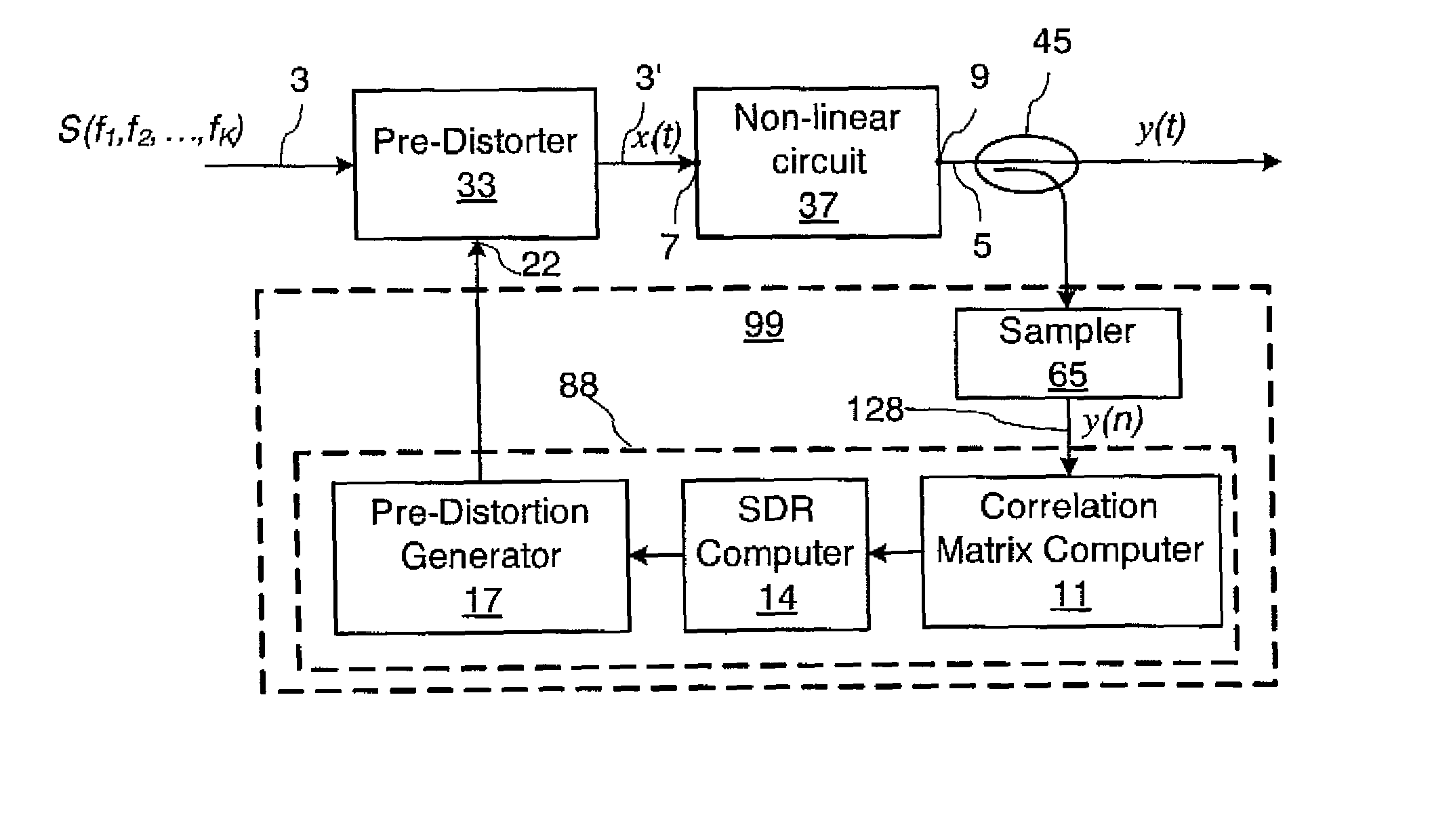

Multi-carrier amplifier linearization system and method

InactiveUS8532215B2Modulated-carrier systemsLine-faulsts/interference reductionAudio power amplifierCarrier signal

The invention relates to a method and circuit for linearizing amplifiers and other nonlinear circuits for multi-carrier signals. An output signal from the amplifier is sampled, and a correlation matrix of size N×N is computed from the sampled signal, wherein N exceeds the number of multiplexed carriers in the signal. A signal-to-distortion ratio (SDR) is then estimated based on a ratio of one or more largest to one or more smallest eigenvalues of the correlation matrix, and the signal into the amplifier is pre-distorted so as to maximize the SDR.

Owner:HER MAJESTY THE QUEEN & RIGHT OF CANADA REPRESENTED BY THE MIN OF IND THROUGH THE COMM RES CENT

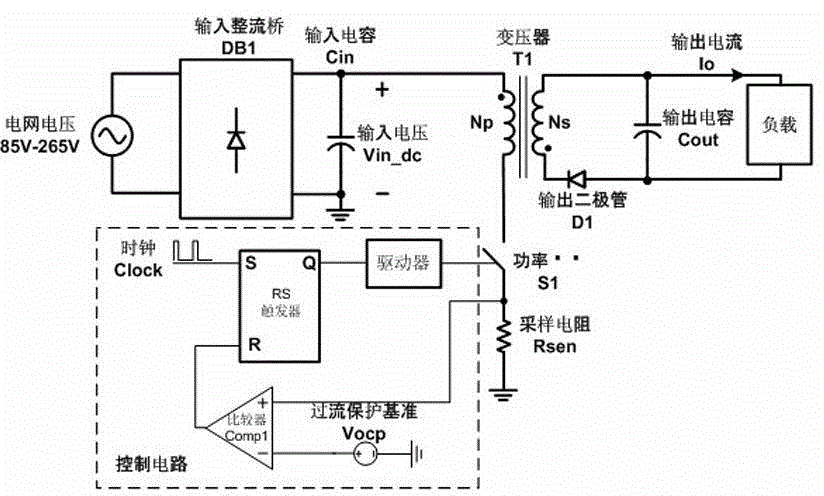

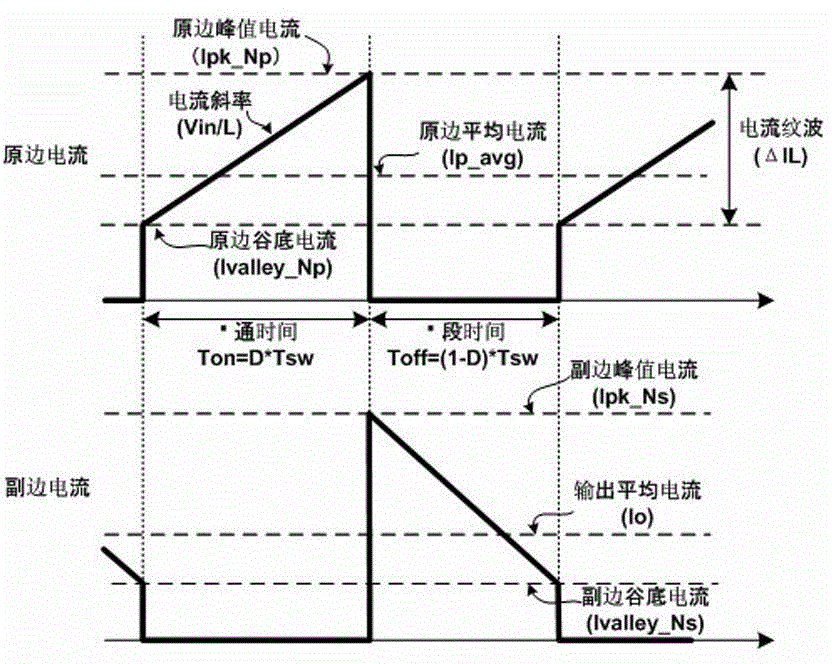

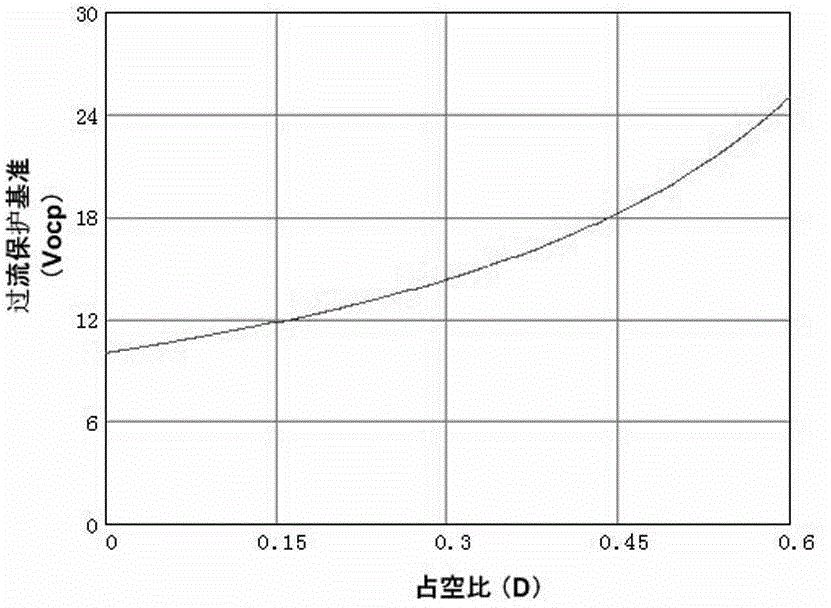

Flyback converter overcurrent protection achieving method for nonlinear circuit

InactiveCN104104063AGood overcurrent protection functionEmergency protective circuit arrangementsLoad circuitCapacitance

The invention relates to a flyback converter overcurrent protection achieving method for a nonlinear circuit. A flyback converter is arranged and comprises an input rectifier bridge, an input capacitor, a transformer, a power switch, an output diode, an output capacitor and a load circuit. A control circuit is arranged and electrically connected with the flyback converter. The control circuit comprises a sampling resistor, an overcurrent comparator, a nonlinear overcurrent reference circuit, an RS trigger and a driver, wherein the nonlinear overcurrent reference circuit provides overcurrent protection reference voltage, and the overcurrent protection reference voltage is a voltage reference nonlinearly varying with a duty ratio of the transformer.

Owner:AQUIL STAR PRECISION IND SHENZHEN

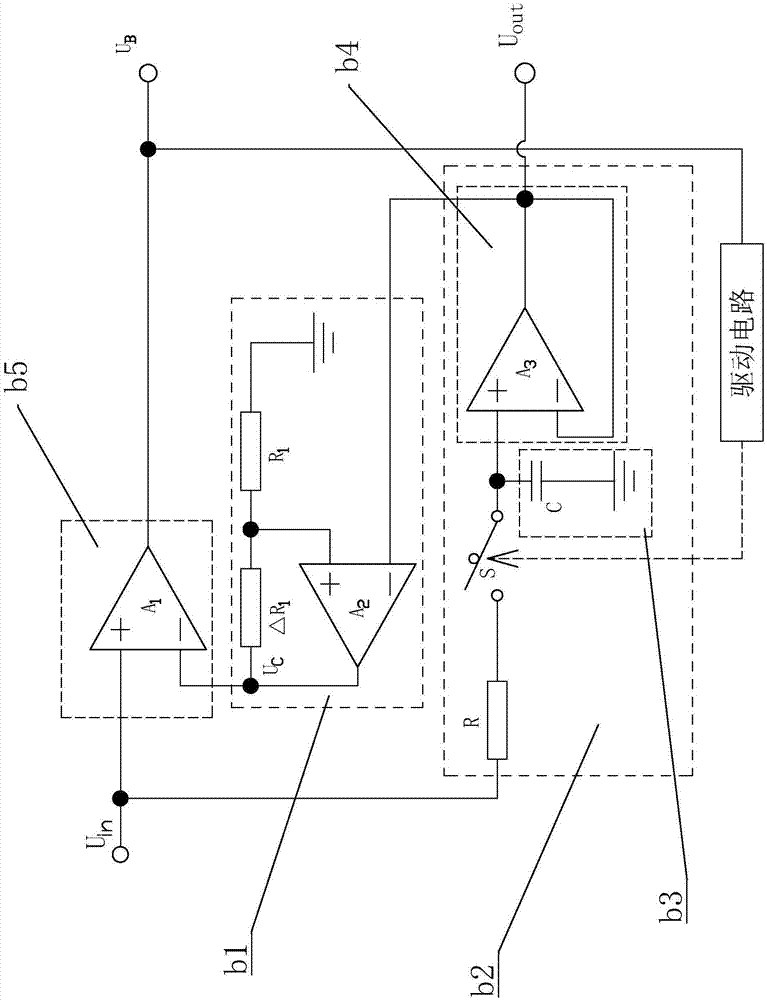

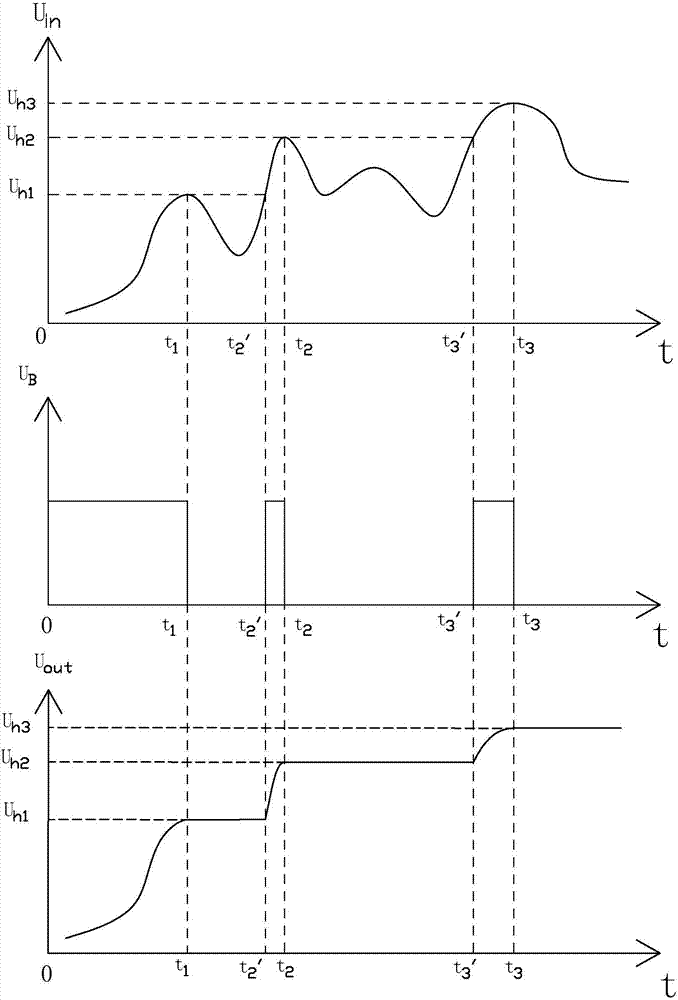

Peak value and over-peak moment tracking detection circuit

ActiveCN107121587AAvoid introducingHigh precisionAc/pulses peak value measurementsHemt circuitsClassical mechanics

The invention discloses a peak value and over-peak moment tracking detection circuit which comprises a voltage comparator, a noninverting amplifier, a sampling retention circuit and a driving circuit, wherein the sampling retention circuit comprises a resistor, a voltage follower, a controlled switch and a retention circuit; the voltage follower follows voltage of the retention circuit, namely output voltage of the voltage follower is equal to that of the retention circuit; the voltage comparator compares an output voltage signal of the noninverting amplifier with a voltage signal Uin input by a tracking detection circuit; a comparison result is output through the voltage comparator to control the driving circuit; the driving circuit controls turning on or turning off of the controlled switch. The circuit directly detects and compares a voltage value of the voltage signal Uin instead of processing a waveform of the voltage signal Uin, so that the circuit is in no relation to the waveform of the voltage signal Uin; therefore, introduction of a nonlinear circuit such as a differential circuit is avoided, and the precision and the reliability of the tracking detection circuit are improved.

Owner:FOSHAN UNIVERSITY

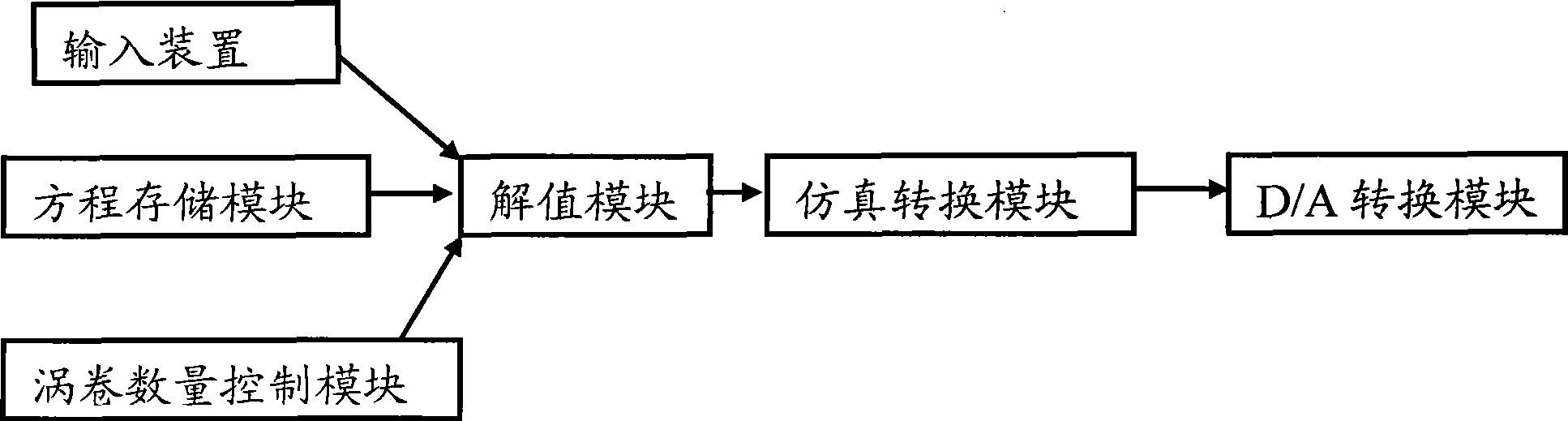

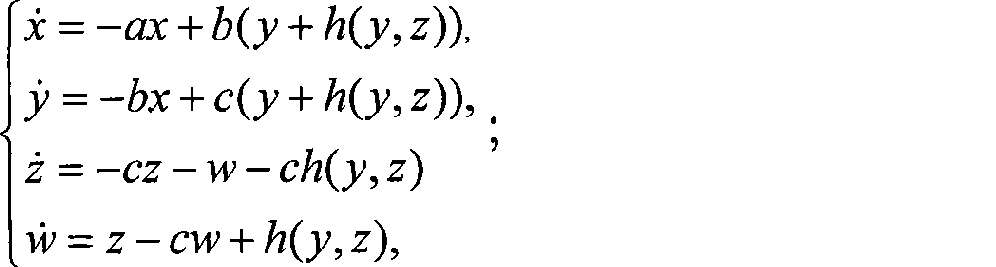

Producing device and producing method of multi-scroll chaotic signals

InactiveCN101447863ASimple structureEasy to implementSecuring communicationEngineeringSignal transition

The invention provides a producing device of multi-scroll chaotic signals, which can produce multi-scroll chaotic signals without nonlinear circuit. The device comprises a chaotic producing equation storage module, a numerical solution module, a simulation converting module and a D / A converting module, wherein one or a plurality of differential equations are stored in the chaotic producing equation storage module; the numerical solution module is used for performing numerical solution on the differential equation capable of producing the multi-scroll chaotic signals; the simulation converting module is used for converting the numerical value obtained through the numerical solution module, so as to obtain simulation chaotic signals; and the simulation chaotic signals obtained by the simulation converting module are converted into electrical signals through the D / A converting module. The invention further discloses a method for producing the multi-scroll chaotic signal; the invention ensures that the solving of the differential equation capable of producing the multi-scroll chaotic signal though soft wares is achieved through software and the obtained value is finally converted into the electrical signal, and has the advantages of simple structure and easy implementation.

Owner:CHONGQING UNIV OF POSTS & TELECOMM

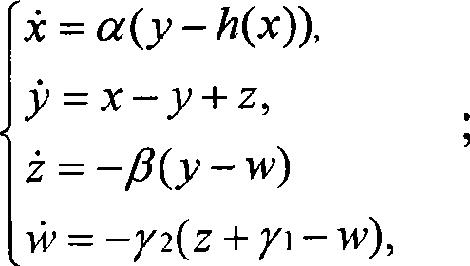

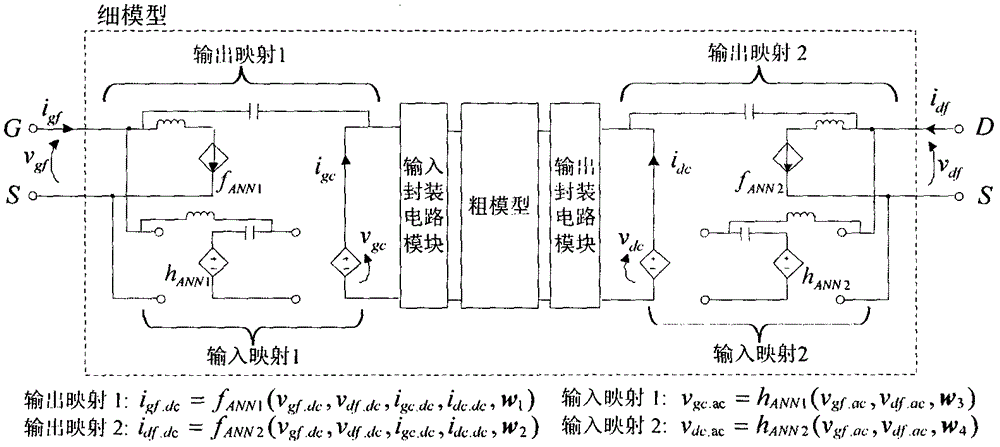

Neural network space mapping modeling method for packaged transistors

InactiveCN106777621ASimple structureFeatures accurately reflectCAD circuit designSpecial data processing applicationsCommunications systemNerve network

The invention provides a neural network space mapping modeling method for packaged transistors. Building of accurate packaged transistor models is of vital importance on improving the precision of wireless communication system circuits. The neural network space mapping modeling method aims to overcome the shortcomings of requirements on internal structure information and high computational complexity of existing modeling methods for packaged transistors. The neural network space mapping modeling method for the packaged transistors includes dividing each packaged transistor model into an input packaged circuit module, a nonlinear circuit module and an output packaged circuit module; respectively constructing structures of the input packaged circuit modules, the nonlinear circuit modules and the output packaged circuit modules. The neural network space mapping modeling method has the advantages that characteristics of the packaged transistors can be accurately reflected by trained models, the neural network space mapping modeling method is high in simulation speed, the design cycle can be greatly shortened, and large-scale circuits can be possibly further designed.

Owner:TIANJIN POLYTECHNIC UNIV +1

Distortion compensation apparatus

InactiveUS20090015326A1Effective compensationAmplifier modifications to reduce non-linear distortionAmplifier modifications to reduce noise influenceAudio power amplifierEngineering

A distortion compensation apparatus includes distortion generating means for generating distortions to compensate for a distortion generated in an amplifier 2. The distortion generating means includes a nonlinear circuit 13 having an input / output expansion characteristic as a circuit which generates a distortion of the lowest odd order as a compensation target and also includes a nonlinear circuit 18 having an input / output saturation characteristic as a circuit which generates a distortion of another odd order as a compensation target.

Owner:KOKUSA ELECTRIC CO LTD

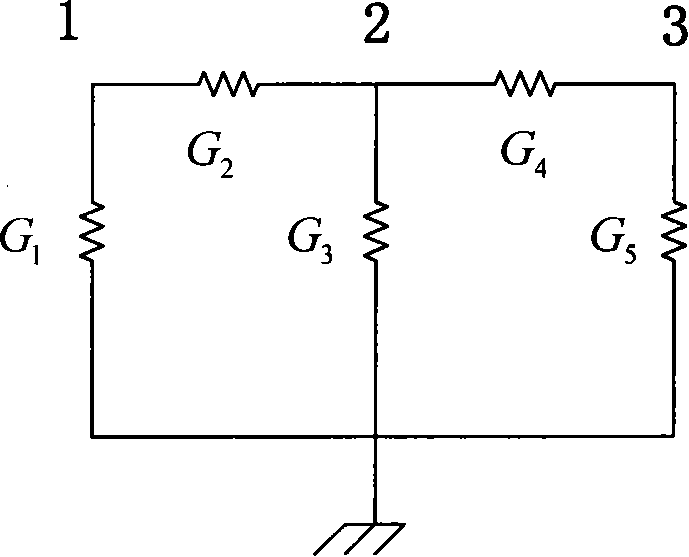

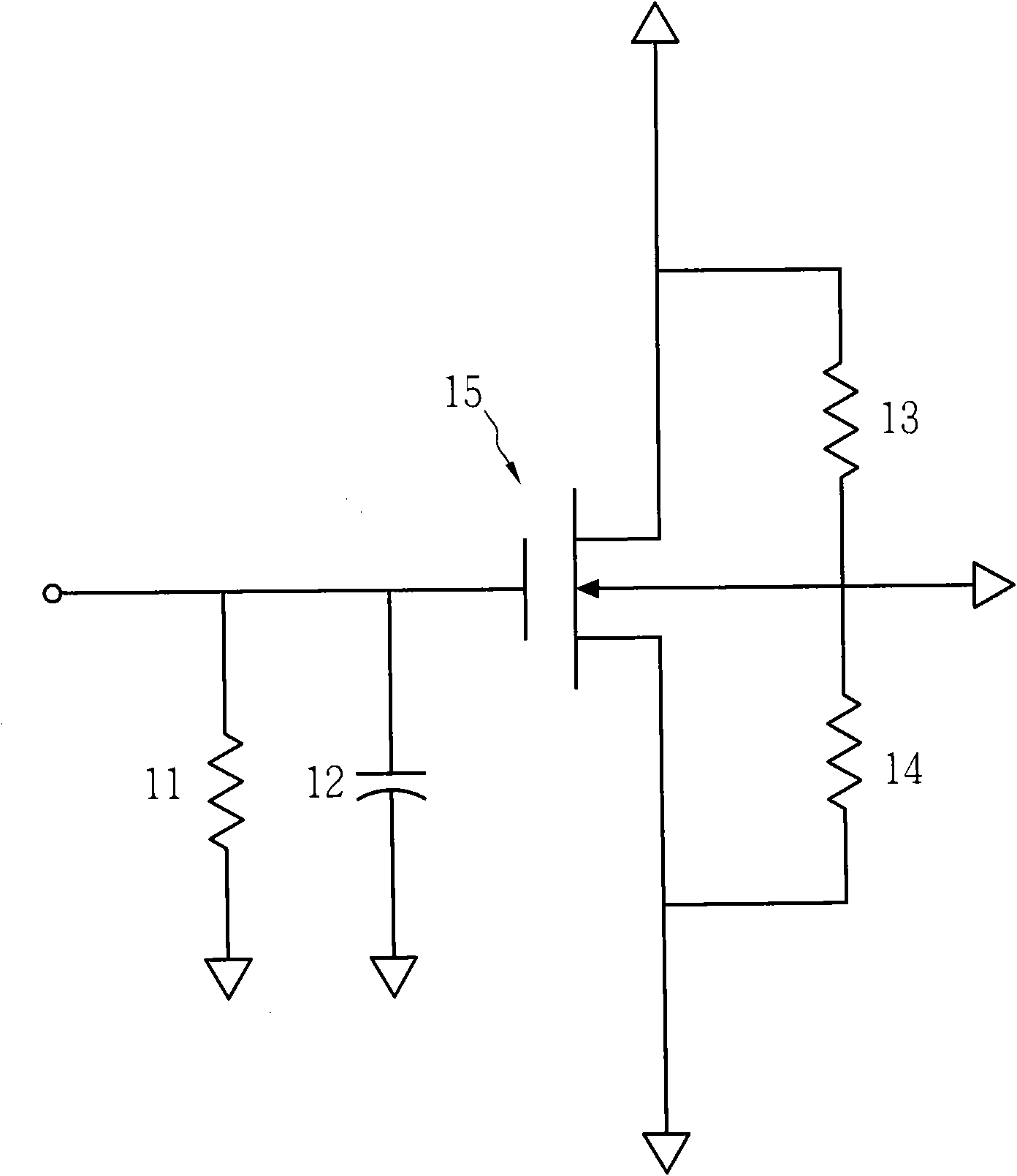

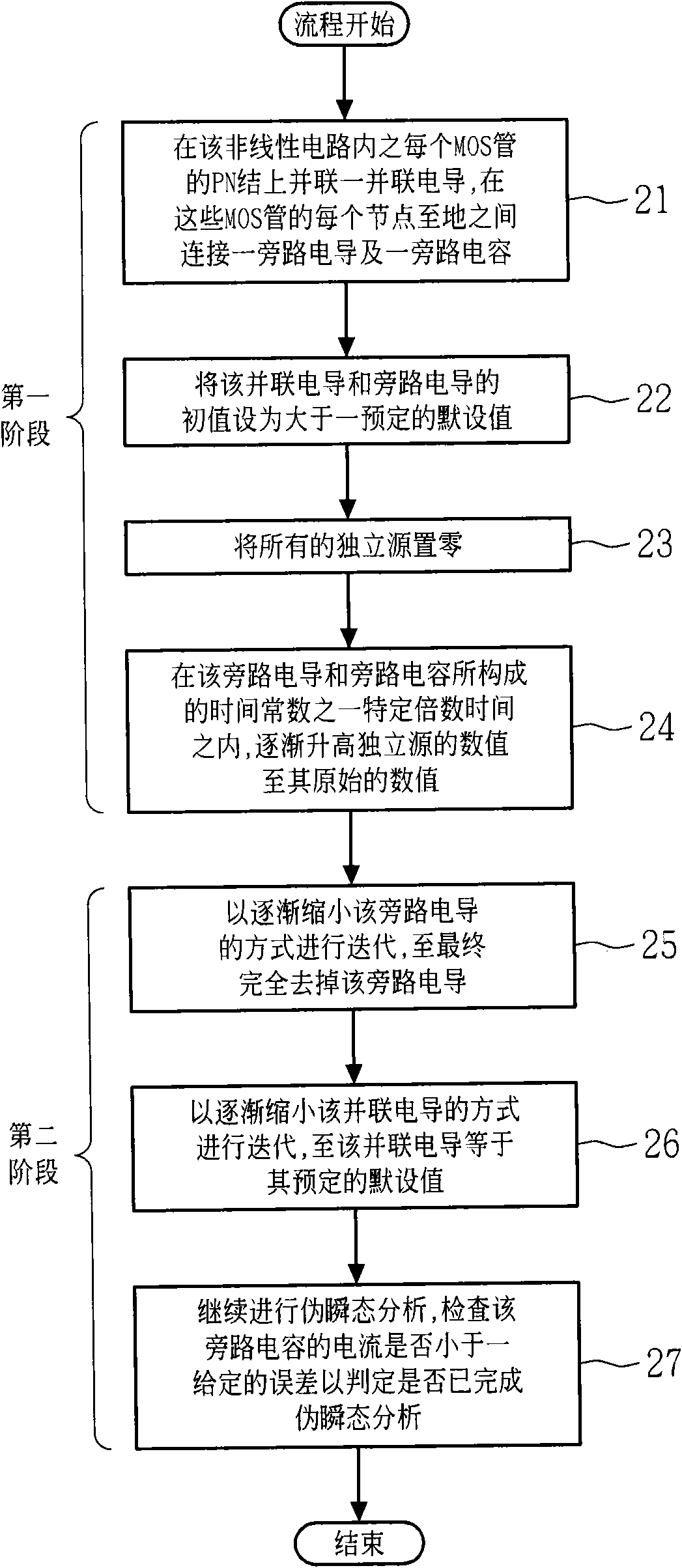

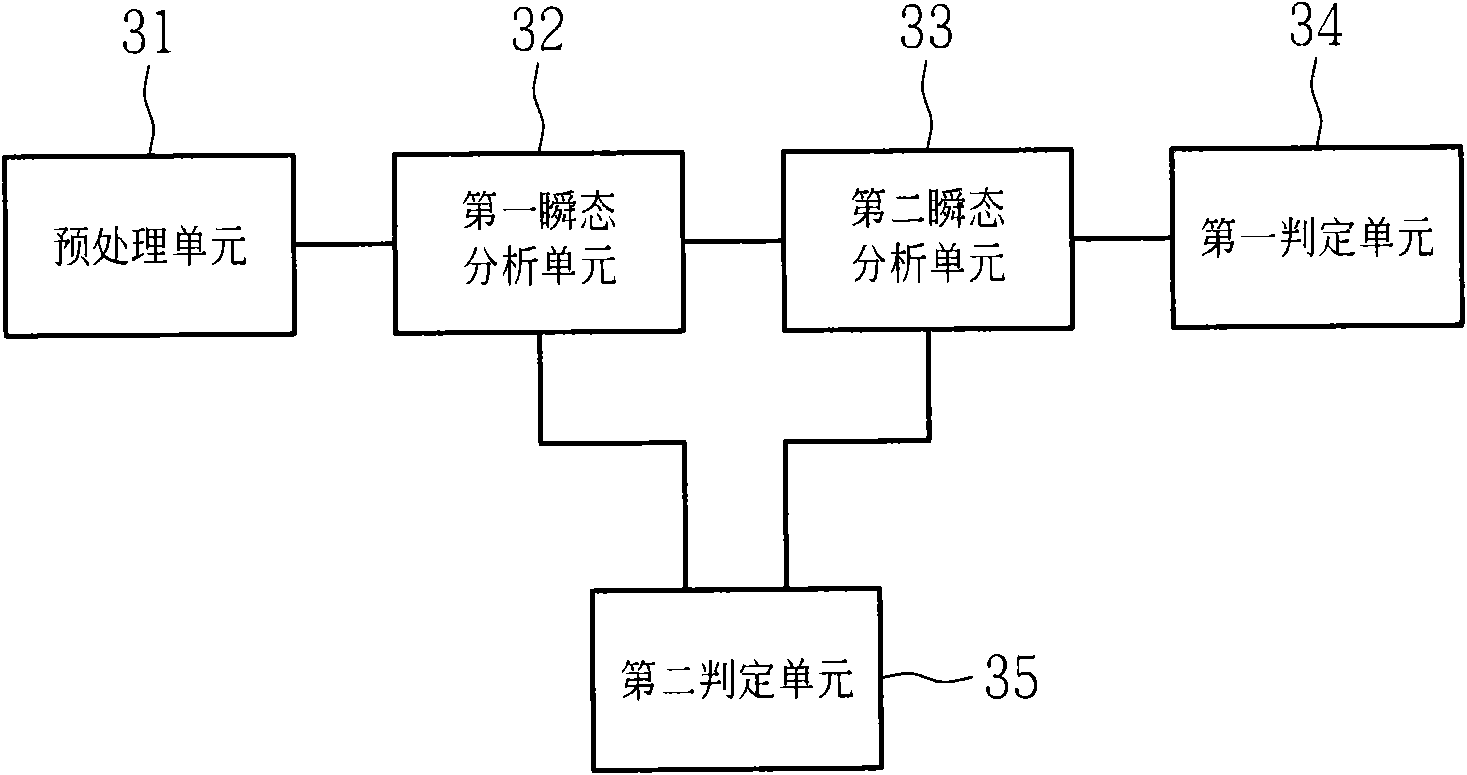

Pseudo transient analysis method of direct current operating point of nonlinear circuit and device

The invention relates to a pseudo transient analysis method of a direct current operating point of a nonlinear circuit and a device. The analysis method comprises the following steps: a PN node of each MOS pipe in the nonlinear circuit is connected with a parallel conductance in parallel, and a bypass conductance and a bypass capacitance are connected between each node of the MOS pipe and the ground; the initial values of the parallel conductance and the bypass conductance are set to be more than a predetermined default value; zero setting is carried out to all independent sources; the values of the independent sources are gradually rose to the original value of the independent sources within a specific multiple time of a time constant formed by the bypass conductance and the bypass capacitance; the iteration is carried out in a manner of gradually reducing the bypass conductance until the bypass conductance is finally and completely eliminated; the iteration is carried out in a manner of gradually reducing the parallel conductance until the parallel conductance is equal to the default value predetermined by the parallel conductance; the transient analysis is continuously carried out, and whether the current of the bypass capacitance is smaller than a given error is checked to judge whether the pseudo transient analysis is finished.

Owner:SYNOPSYS SHANGHAI

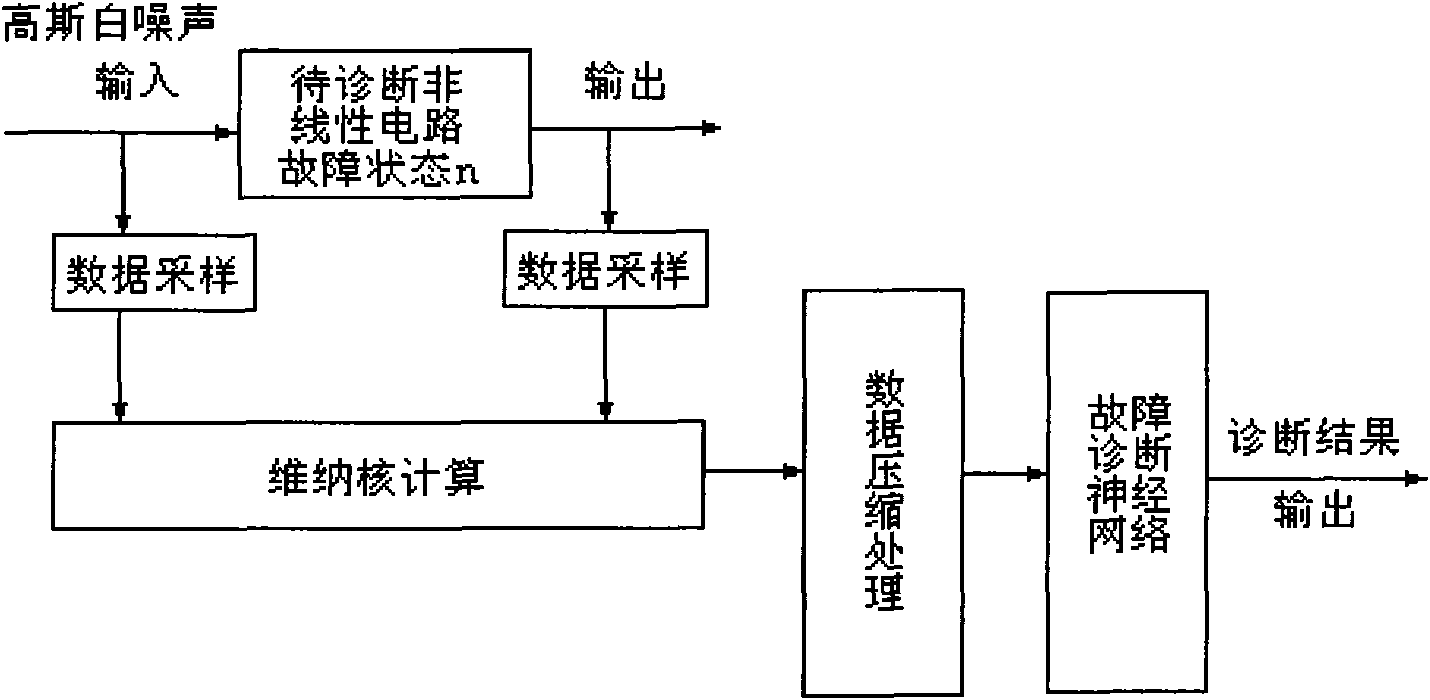

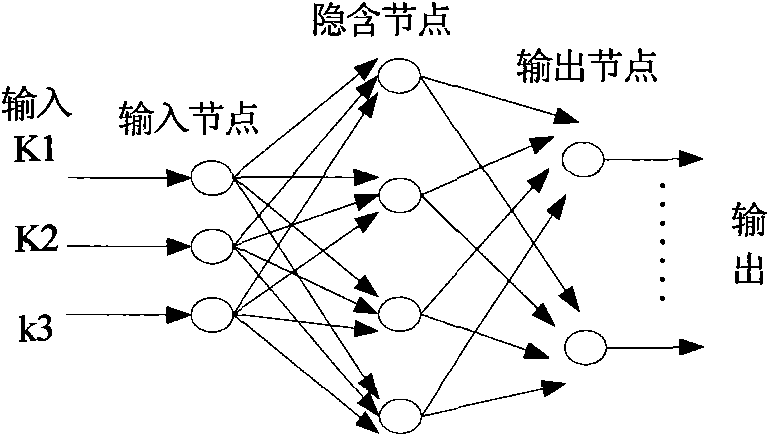

Method for diagnosing faults of nonlinear analog circuit based on Wiener kernels and neural network

InactiveCN101813747AImprove diagnostic efficiencyPractical and reliableAnalog circuit testingNeural learning methodsNerve networkFeature extraction

The invention provides a method for diagnosing faults of a nonlinear analog circuit based on Wiener kernels and a neural network. The existing nonlinear systems are difficult to describe mathematically and lack uniform description method. The invention relates to feature extraction, mode recognition and fault diagnosis technology of the nonlinear analog circuit and is characterized by determining a fault state set of the nonlinear analog circuit to be tested; obtaining the first n-order Wiener kernel of each fault state in sequence; establishing a BP neural network and training the neural network with each state code and the corresponding n-order Wiener kernel of the state code; and obtaining the first n-order Wiener kernel of the circuit to be diagnosed and using the kernel as input of the neural network and output of the neural network as the result of diagnosis. By the method, the features of part of nonlinear circuits with Volterra series unable to be described can be extracted, the terms of output and expanded series are orthogonal, feature extraction and data processing are simpler, the diagnostic system has strong generalization capability, and the method is high in accuracy and strong in practicability. The method is used for diagnosing the faults of electronic circuits.

Owner:哈尔滨海恒博涵科技发展有限公司

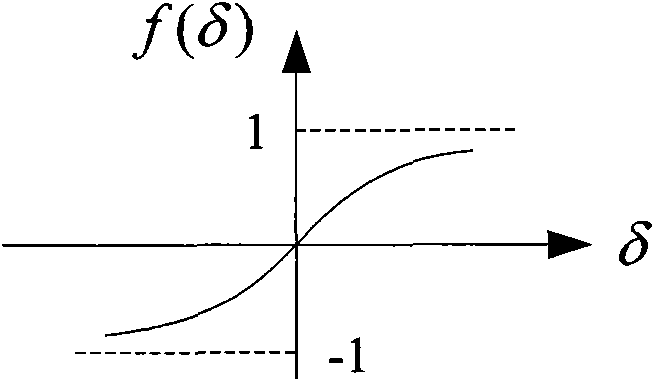

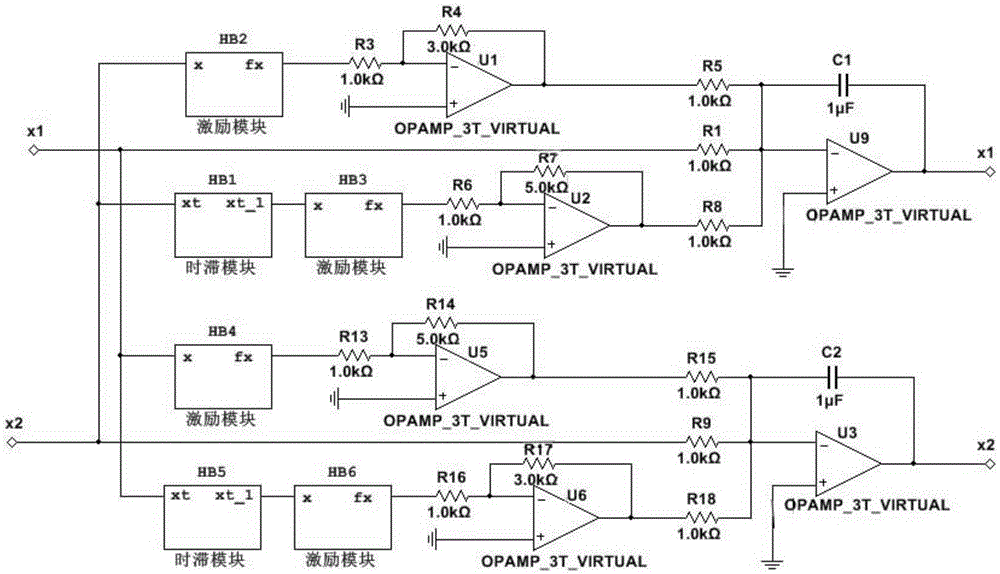

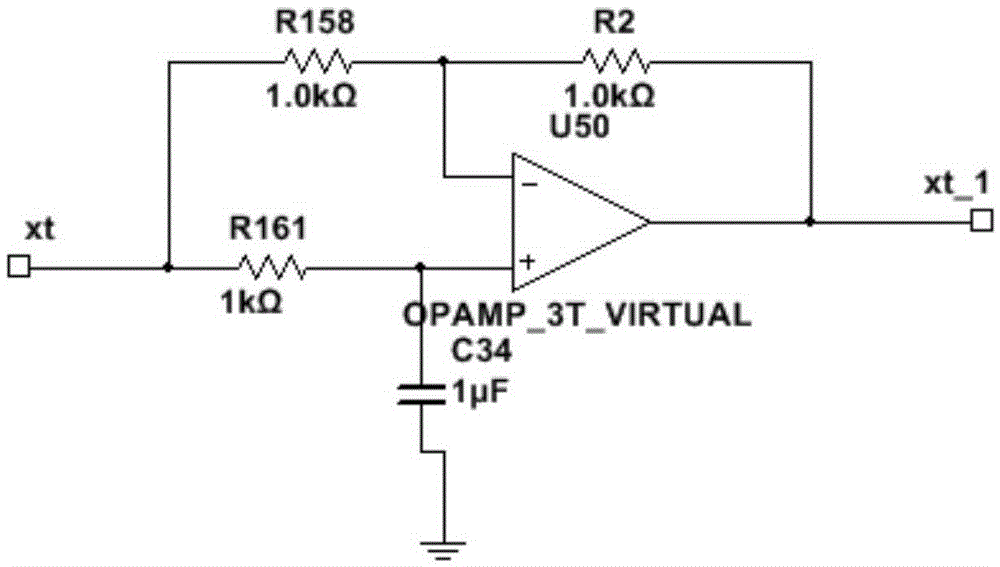

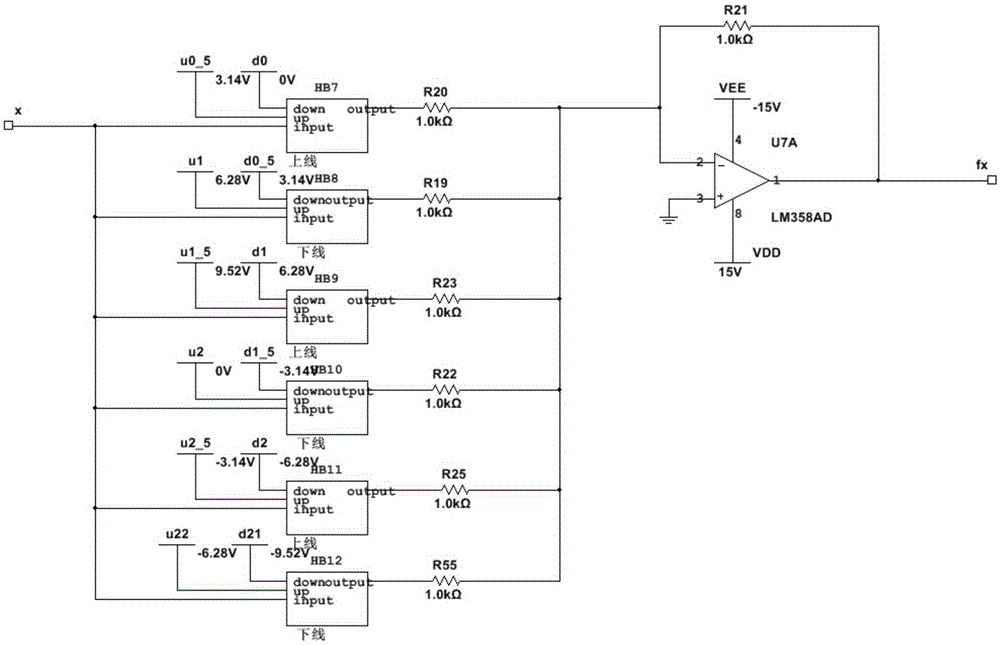

Time-lag neural network hyperchaos circuit

The invention discloses a time-lag neural network hyperchaos circuit which belongs to the field of nonlinear circuits. The circuit comprises an integration circuit, a time lag module and an excitation module, and can generate a chaotic signal under the interference of a pulse signal. The integration circuit consists of an operational amplifier U1, an operational amplifier U2, an operational amplifier U5, an operational amplifier U6, an operational amplifier U3, and an operational amplifier U9. The time lag module comprises a first time lag module HB1 and a second time lag module HB5. The excitation module comprises a first excitation module HB2, a second excitation module HB3, a third excitation module HB4, and a fourth excitation module HB6. Compared with the prior art, the circuit has the improvement that a time-lag hyperchaos neural network phase diagram is represented under different interferences through adjusting a pulse voltage value.

Owner:CHINA UNIV OF PETROLEUM (EAST CHINA)