Neural network space mapping modeling method for packaged transistors

A neural network and modeling method technology, applied in the field of microwave circuit and device modeling, can solve problems such as the inability to reflect the impact of packaged circuits on transistor performance, and achieve the effect of accurate reflection and simple neural network structure

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] In order to make the object, technical solution and advantages of the present invention clearer, the embodiments of the present invention will be described in detail below with reference to the accompanying drawings.

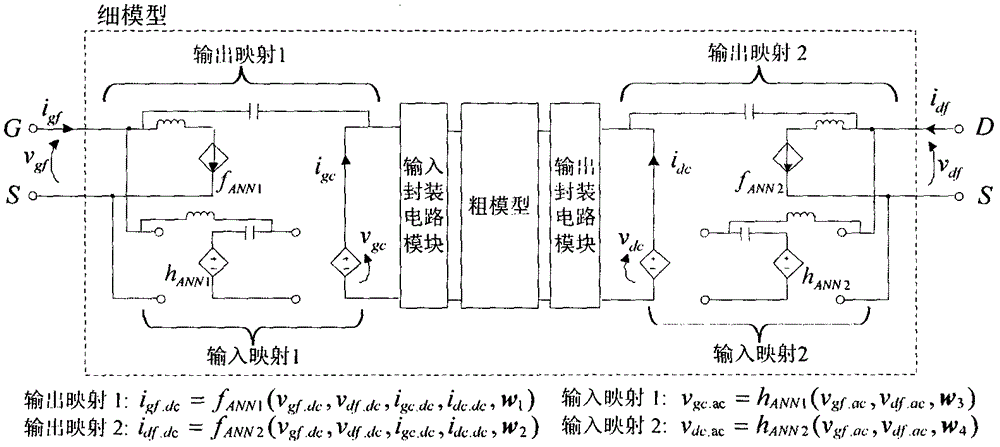

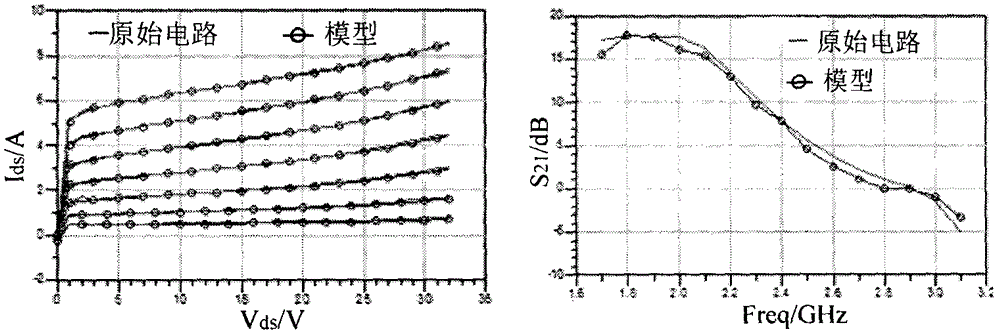

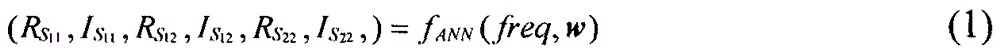

[0034] When adopting the modeling method proposed by the present invention to model the packaged transistor, its model structure is as follows figure 1 shown. The model is mainly divided into four parts: the input package circuit module, the rough model module, the output package circuit module and the mapping circuit. Simulate the non-linear characteristics of packaged transistor dies, using mapping circuits to tune the characteristics of the entire model.

[0035] The existing model is selected as the rough model module of the package transistor model. If the transistor model researched by the device manufacturer is selected as the rough model, its performance should be as close as possible to the performance of the packaged transistor being modeled; ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More