Patents

Literature

265 results about "Scaling circuits" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Transmit/receive switch

ActiveUS20090036065A1Reduce noiseMultiple-port networksResonant long antennasEngineeringImpedance matching

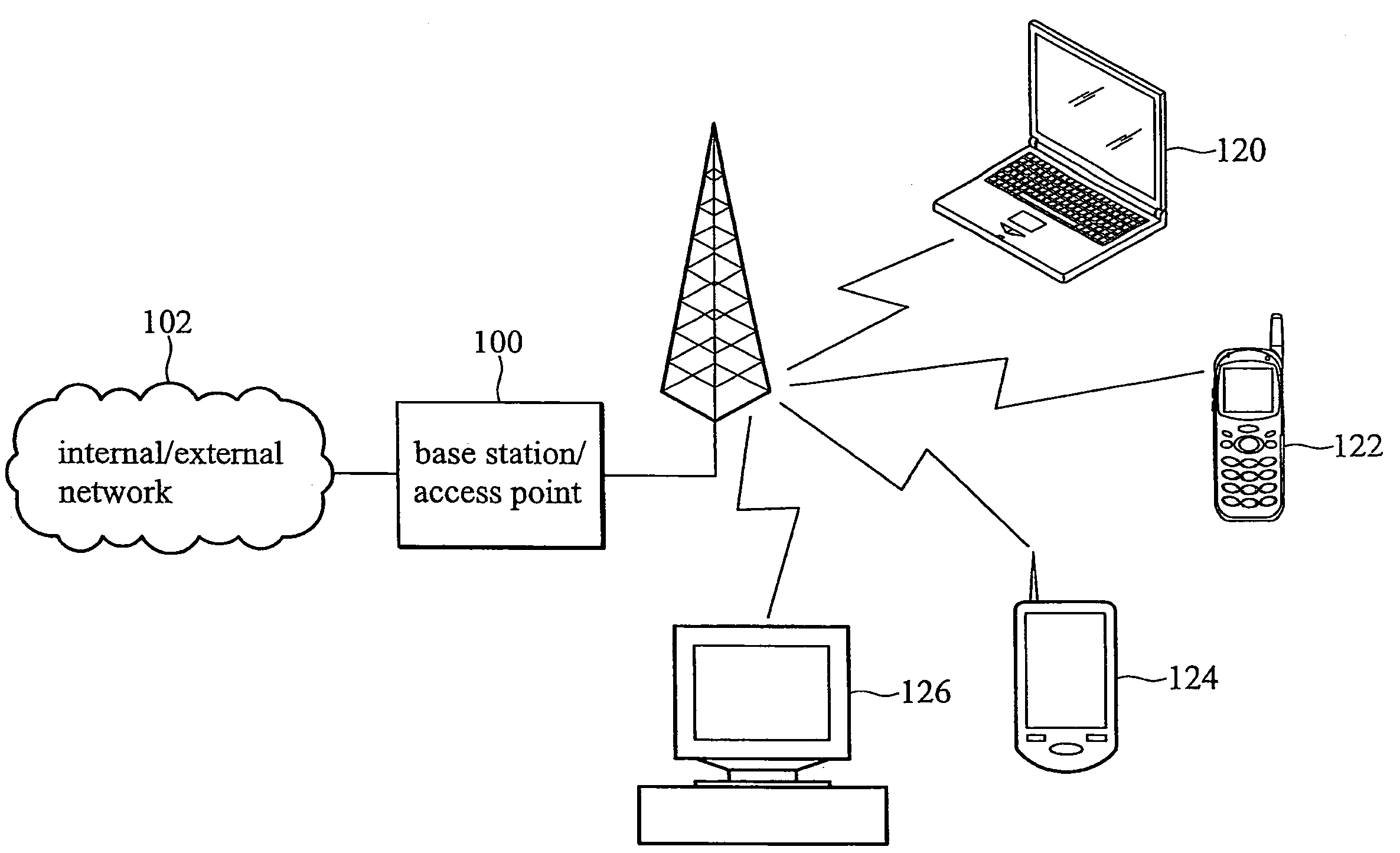

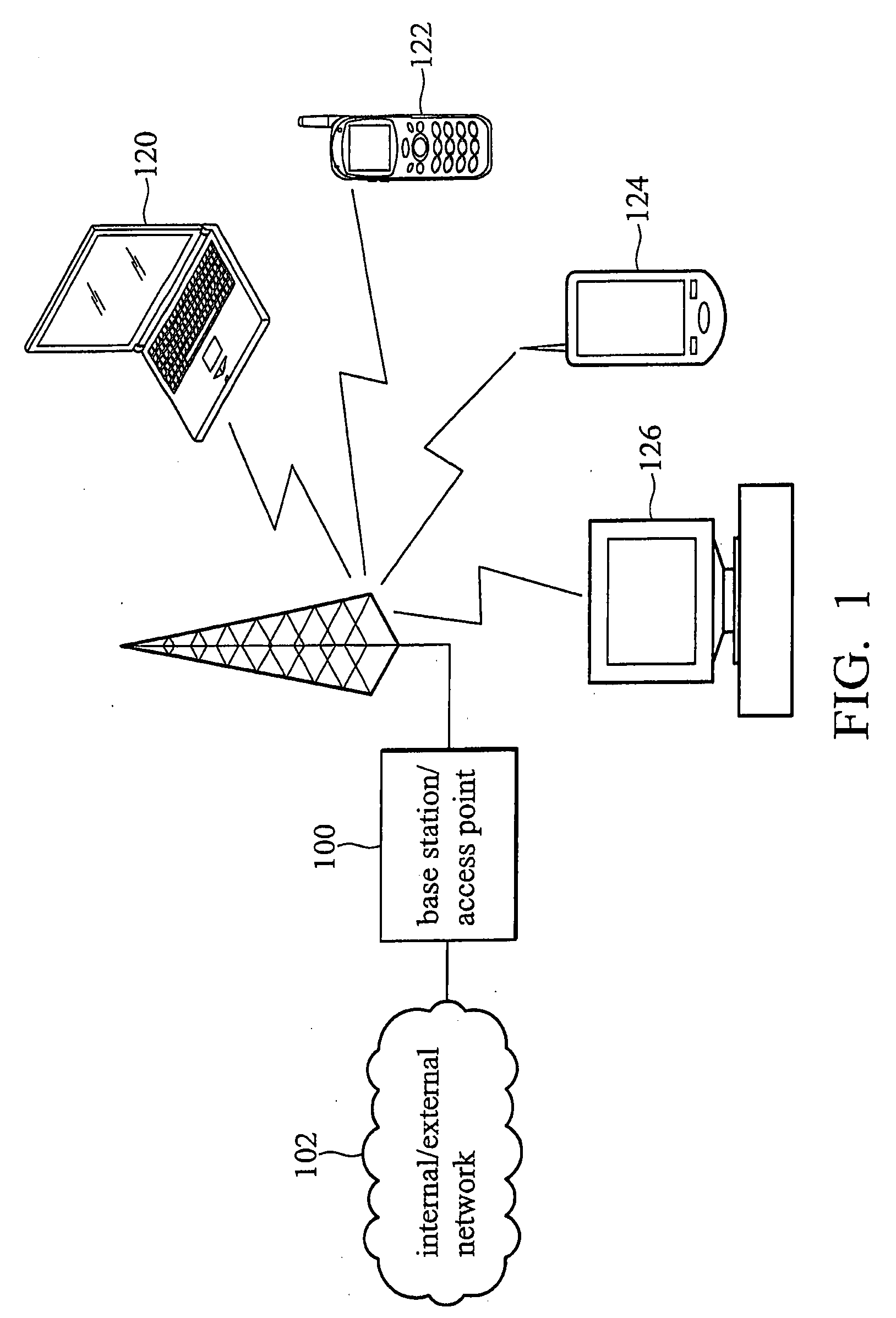

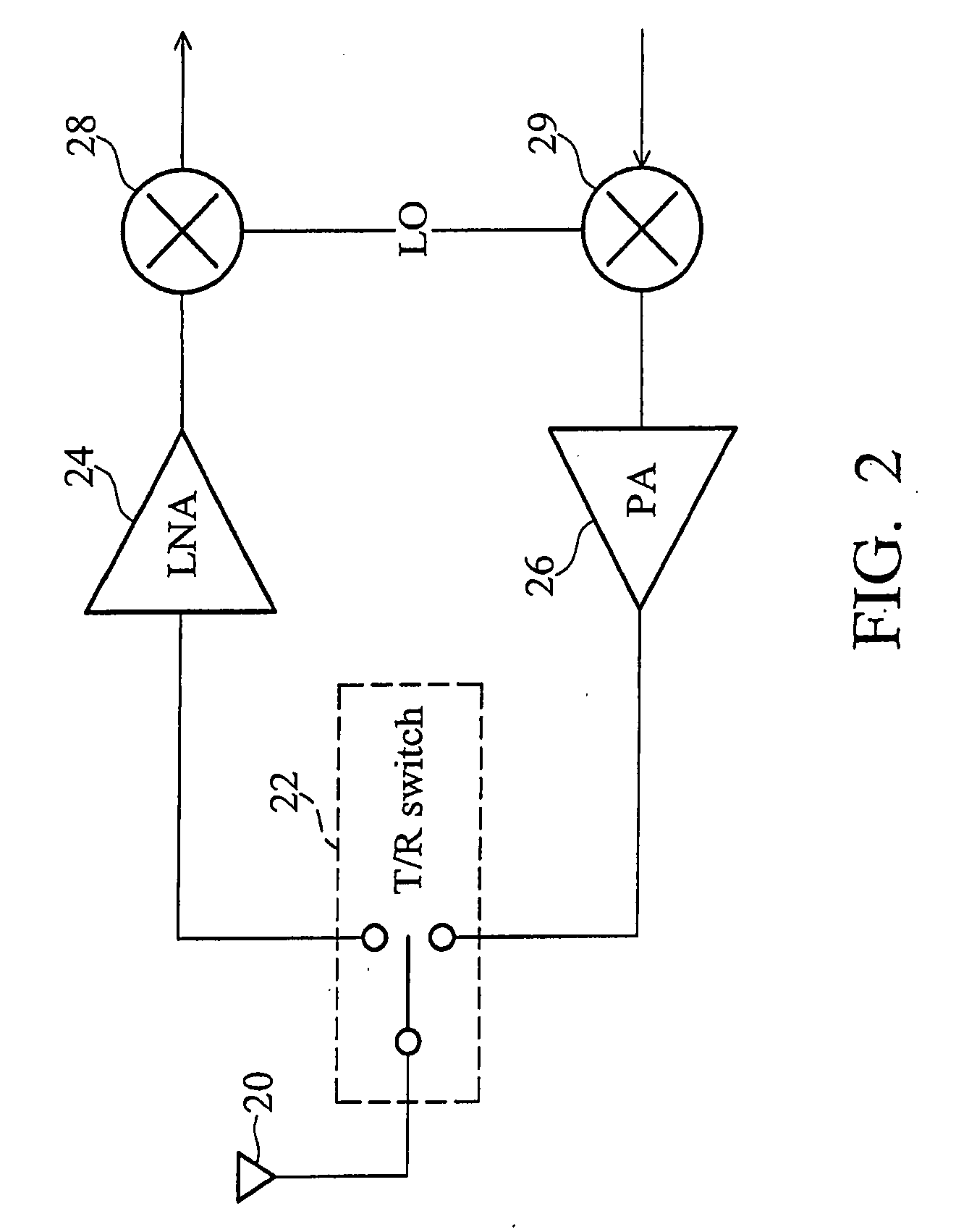

A radio frequency (RF) transmit / receive switch. The transmit / receive switch comprises an impedance matching circuit and a voltage scaling circuit. The impedance matching circuit matches an incoming RF signal to a low noise amplifier and an outgoing RF signal from a power amplifier. The voltage scaling circuit, coupled to the impedance matching circuit, the power amplifier, and the low noise amplifier, attenuates the outgoing RF signal to a scaled signal within a breakdown voltage of a transistor device in the low noise amplifier during transmission of the outgoing RF signal.

Owner:MEDIATEK USA INC

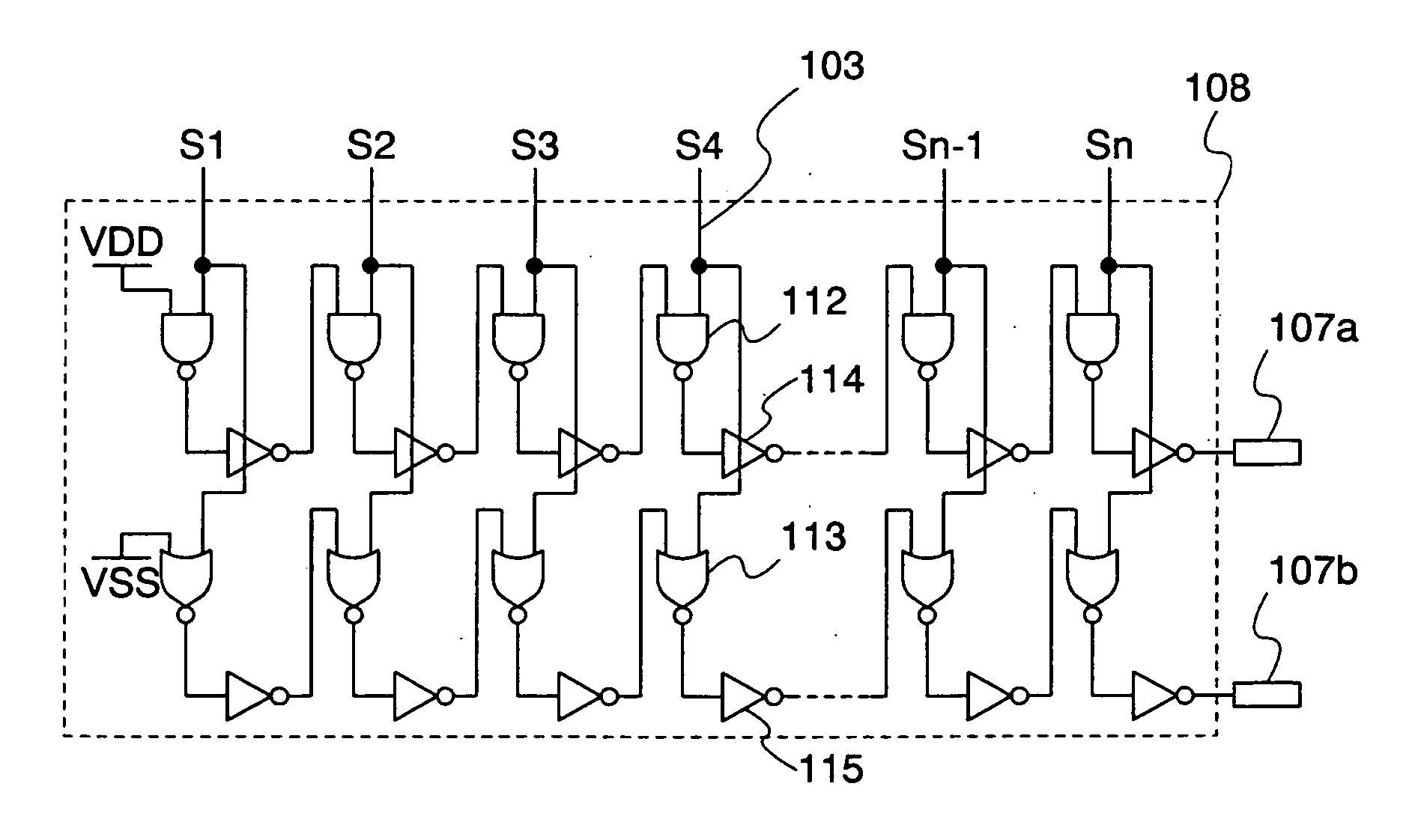

Semiconductor device

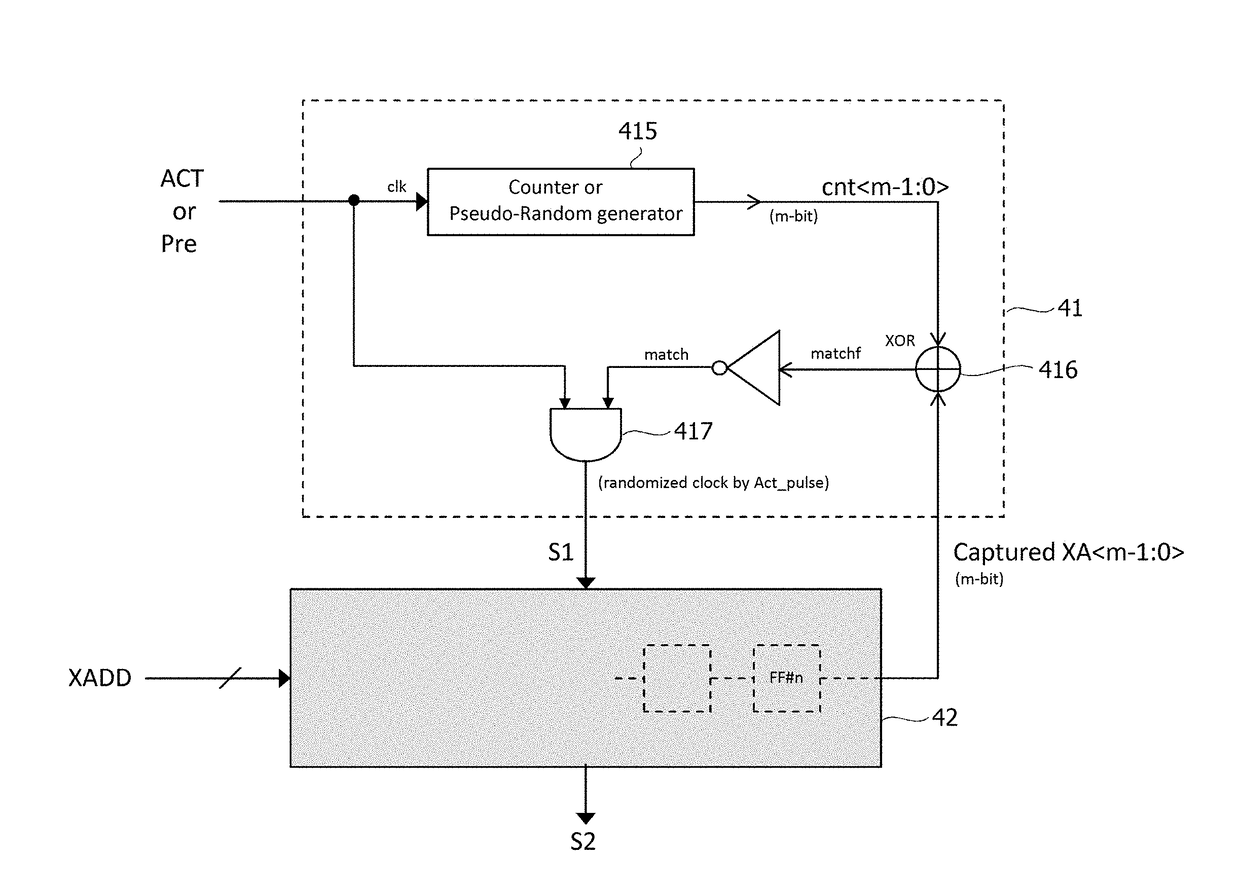

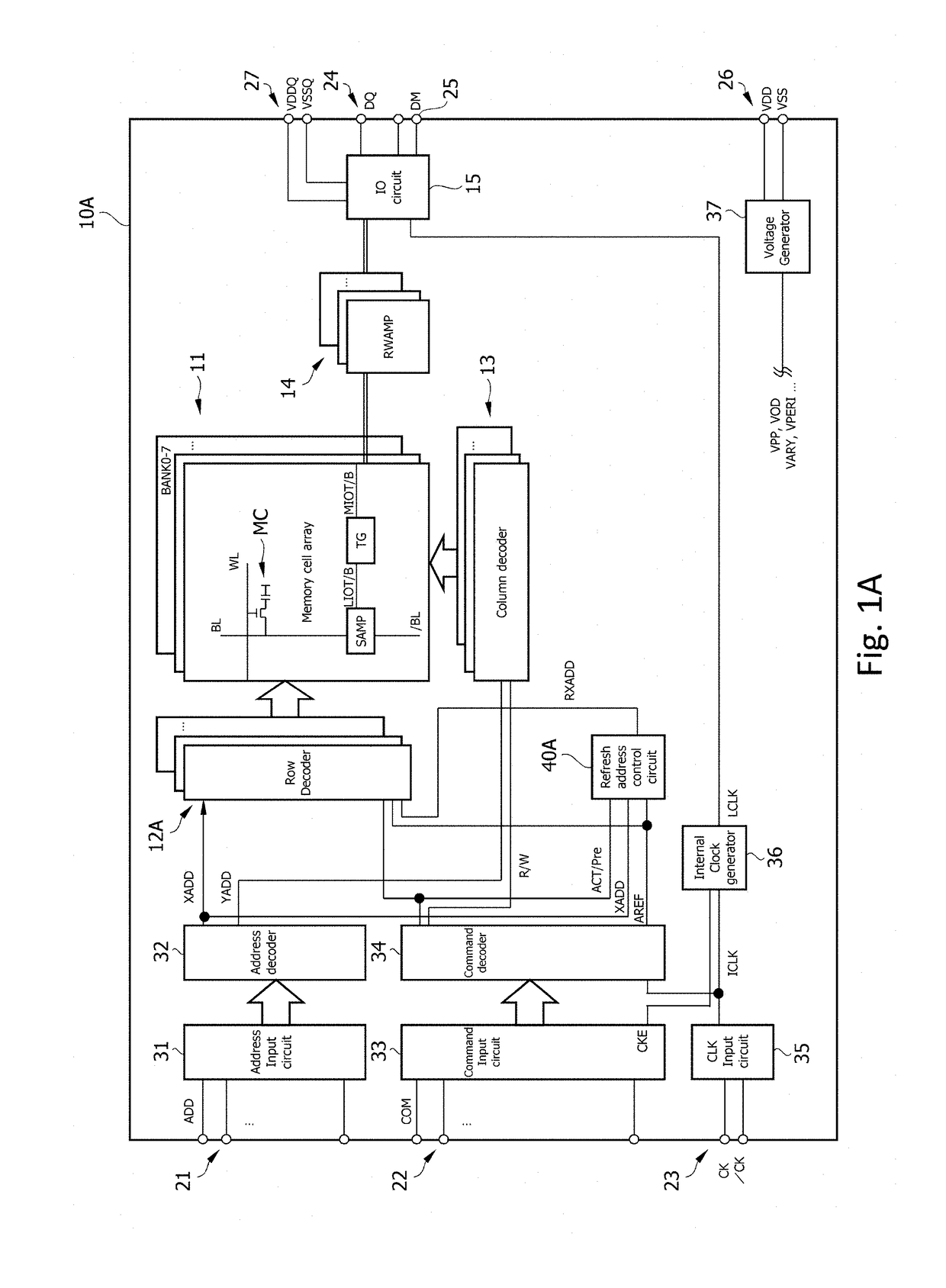

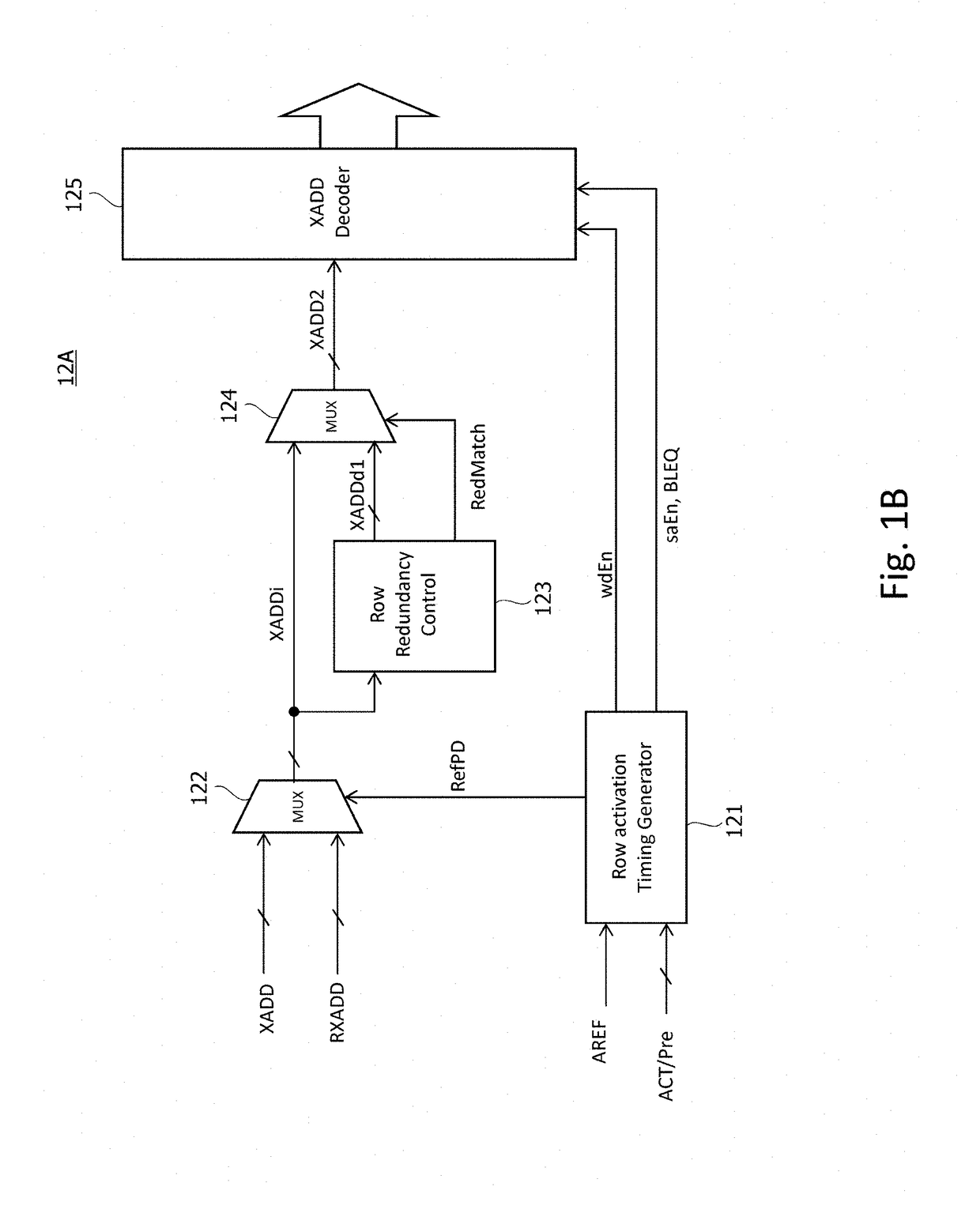

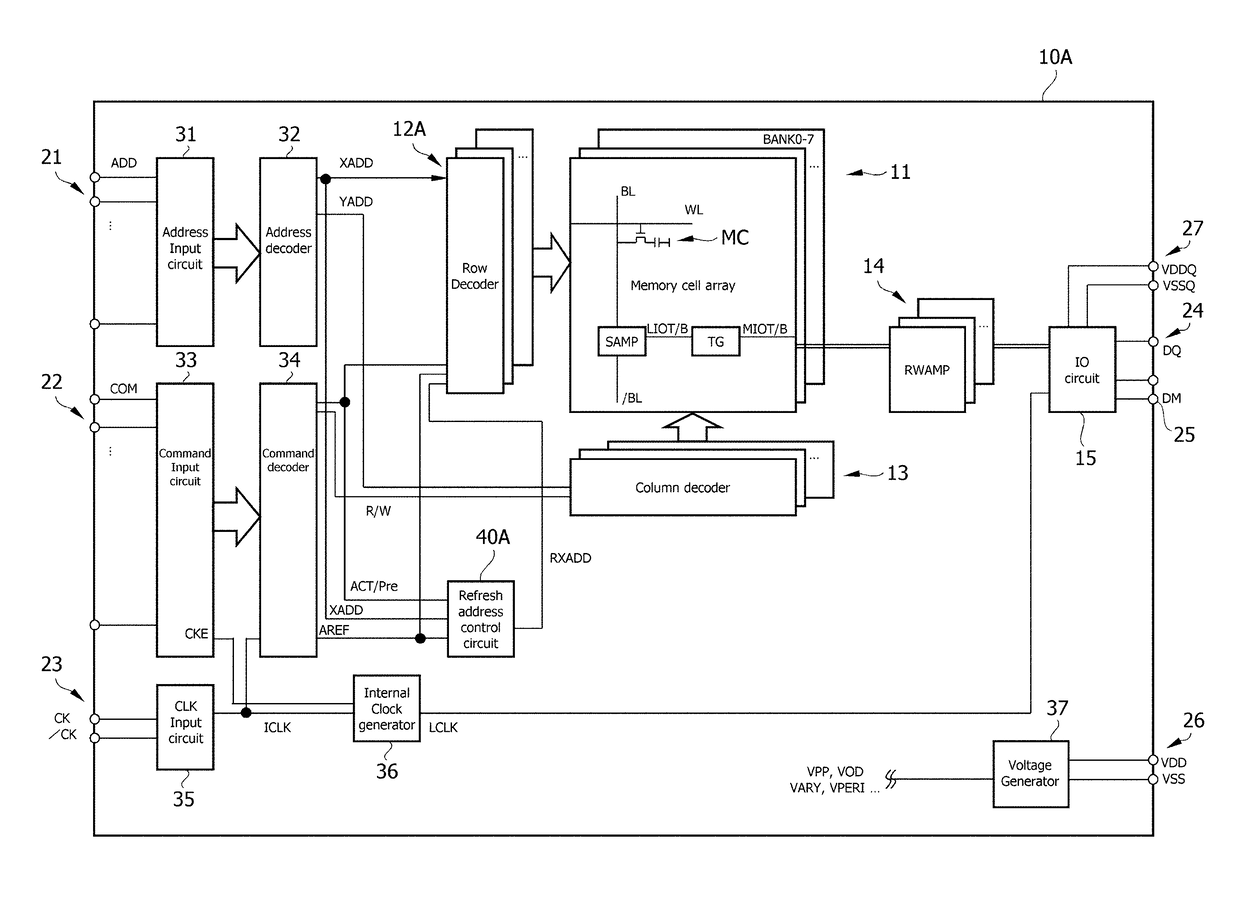

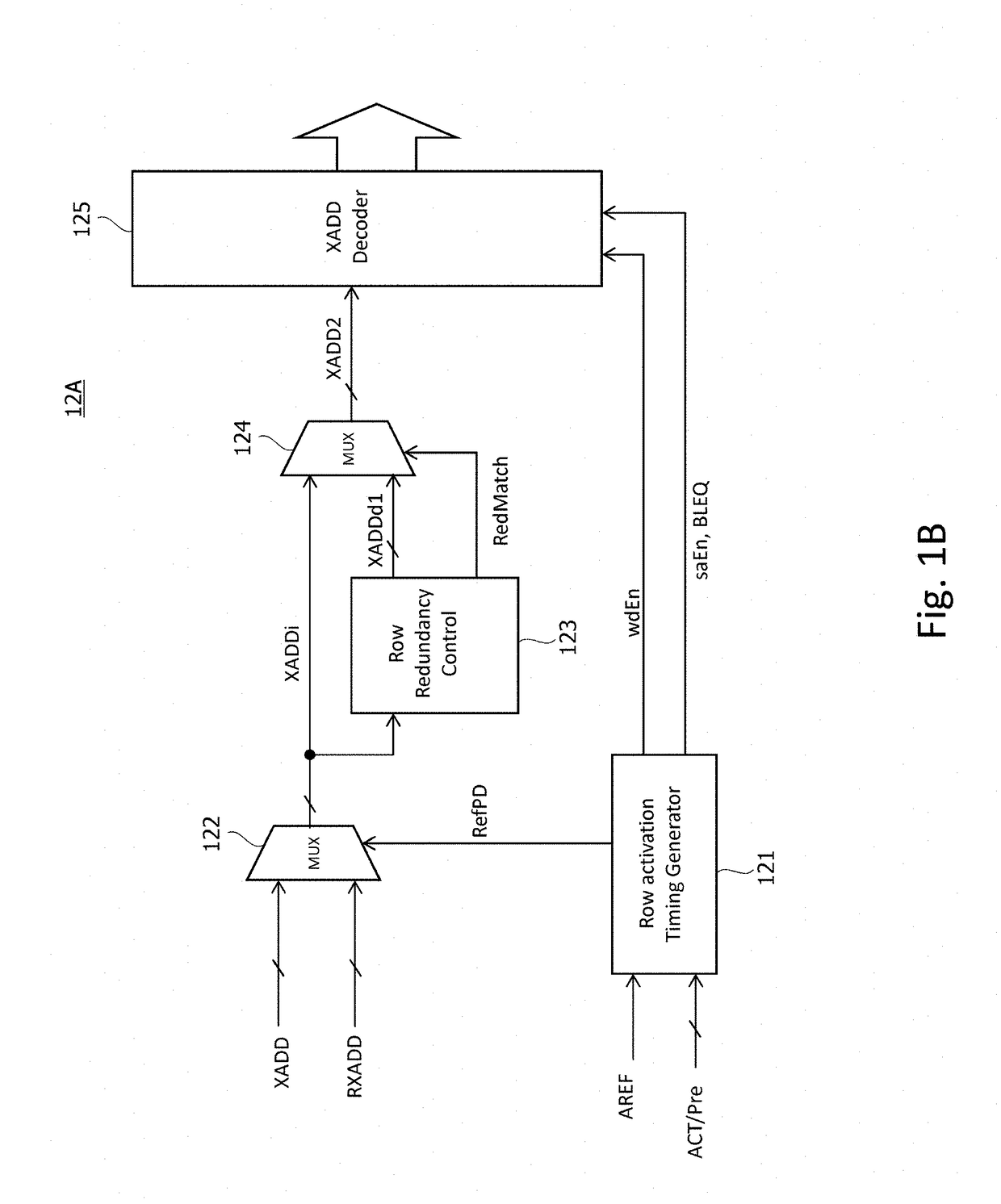

A semiconductor device according to an aspect of the present invention has: a plurality of memory cells MC; a plurality of word lines WL each coupled to a corresponding one of the plurality of memory cells MC; and a control circuit that intermittently monitors accesses to the plurality of word lines WL, stores / erases some captured row-addresses in a first number of registers, and detects, by comparison with stored addresses, in response to a first number of accesses to one of the word lines WL in a first period of time. According to the present invention, access histories can be precisely analyzed by a small-scale circuit configuration, and measures against, for example, the Row Hammer problem, etc. can be taken.

Owner:MICRON TECH INC

Semiconductor device

A semiconductor device according to an aspect of the present invention has: a plurality of memory cells MC; a plurality of word lines WL each coupled to a corresponding one of the plurality of memory cells MC; and a control circuit that intermittently monitors accesses to the plurality of word lines WL, stores / erases some captured row-addresses in a first number of registers, and detects, by comparison with stored addresses, in response to a first number of accesses to one of the word lines WL in a first period of time. According to the present invention, access histories can be precisely analyzed by a small-scale circuit configuration, and measures against, for example, the Row Hammer problem, etc. can be taken.

Owner:MICRON TECH INC

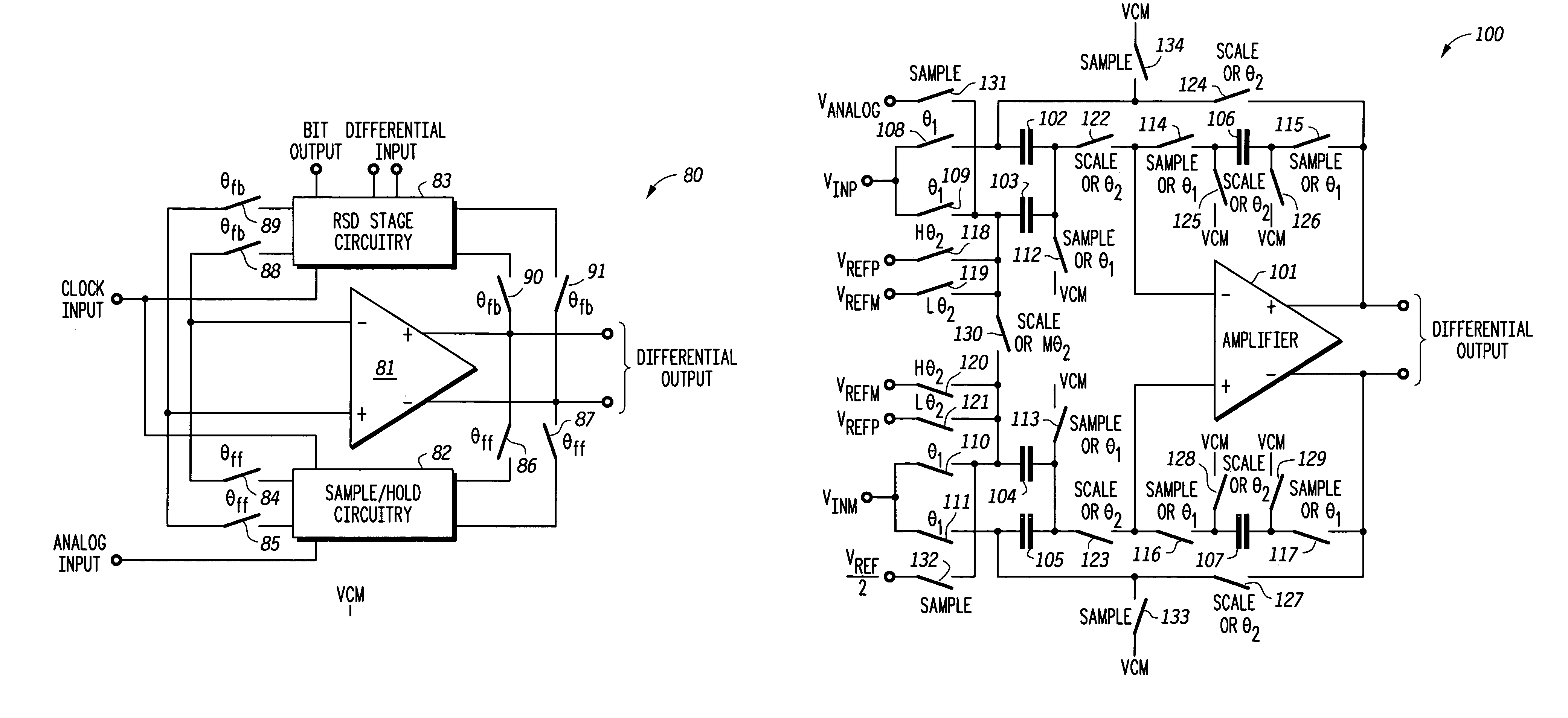

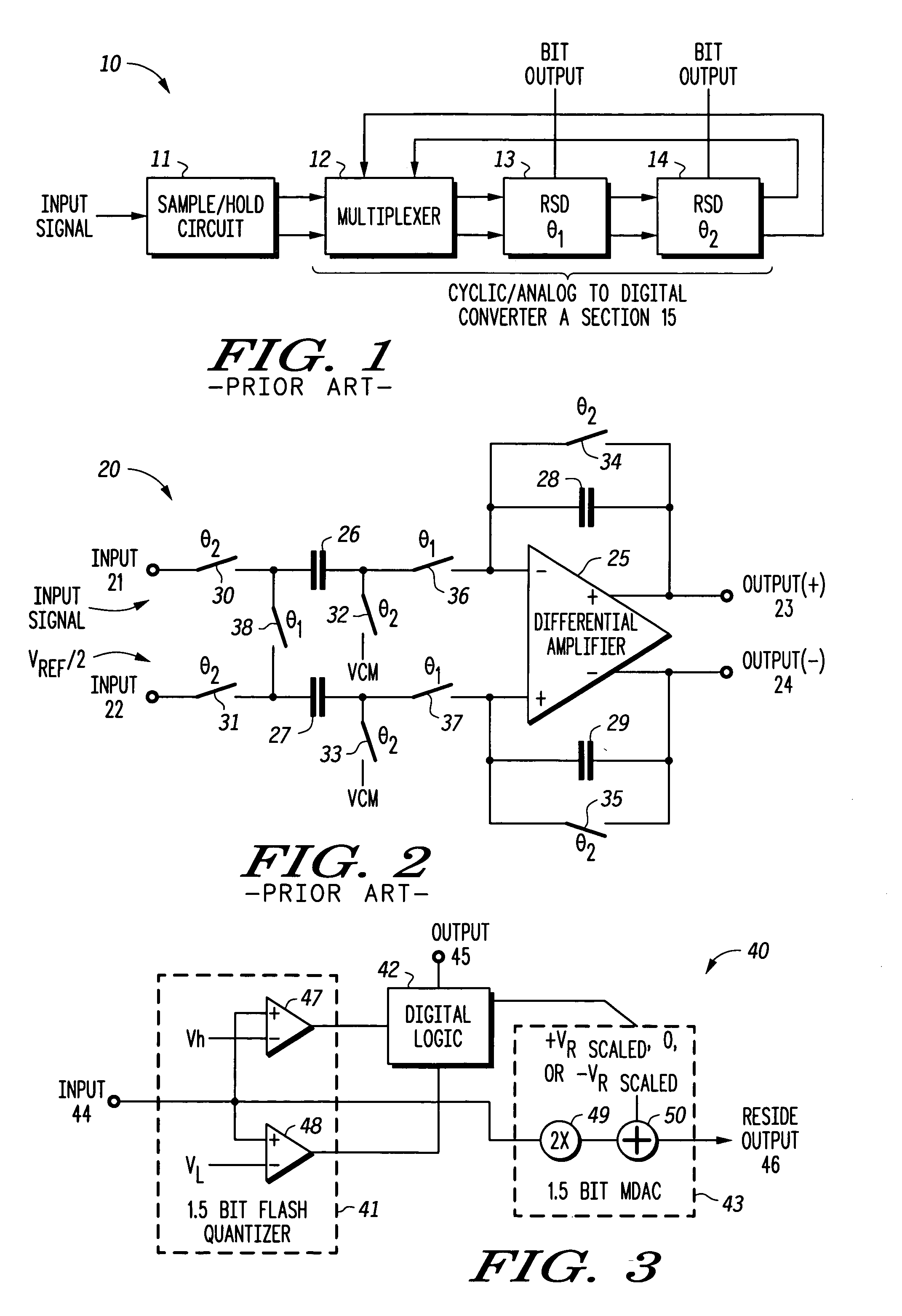

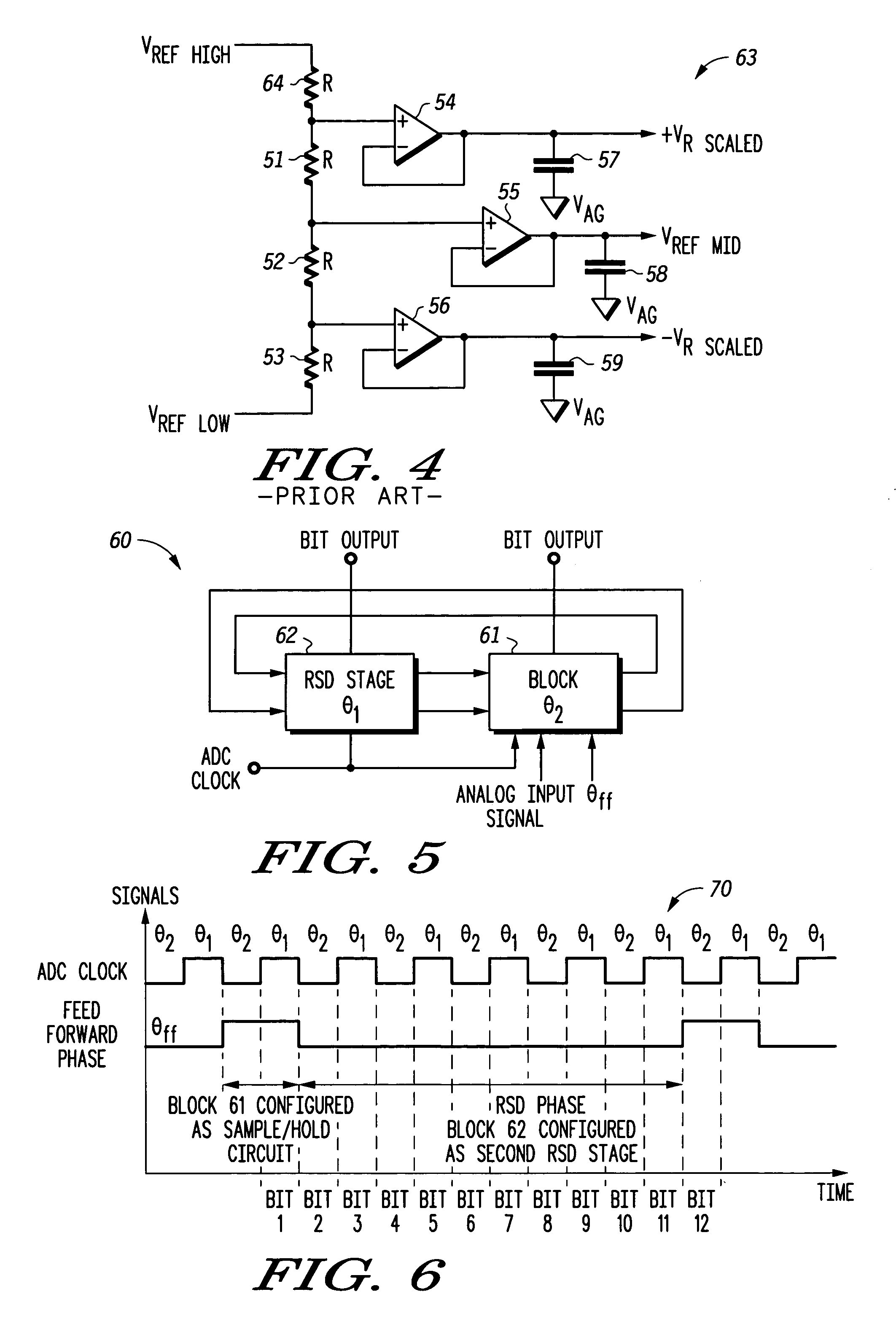

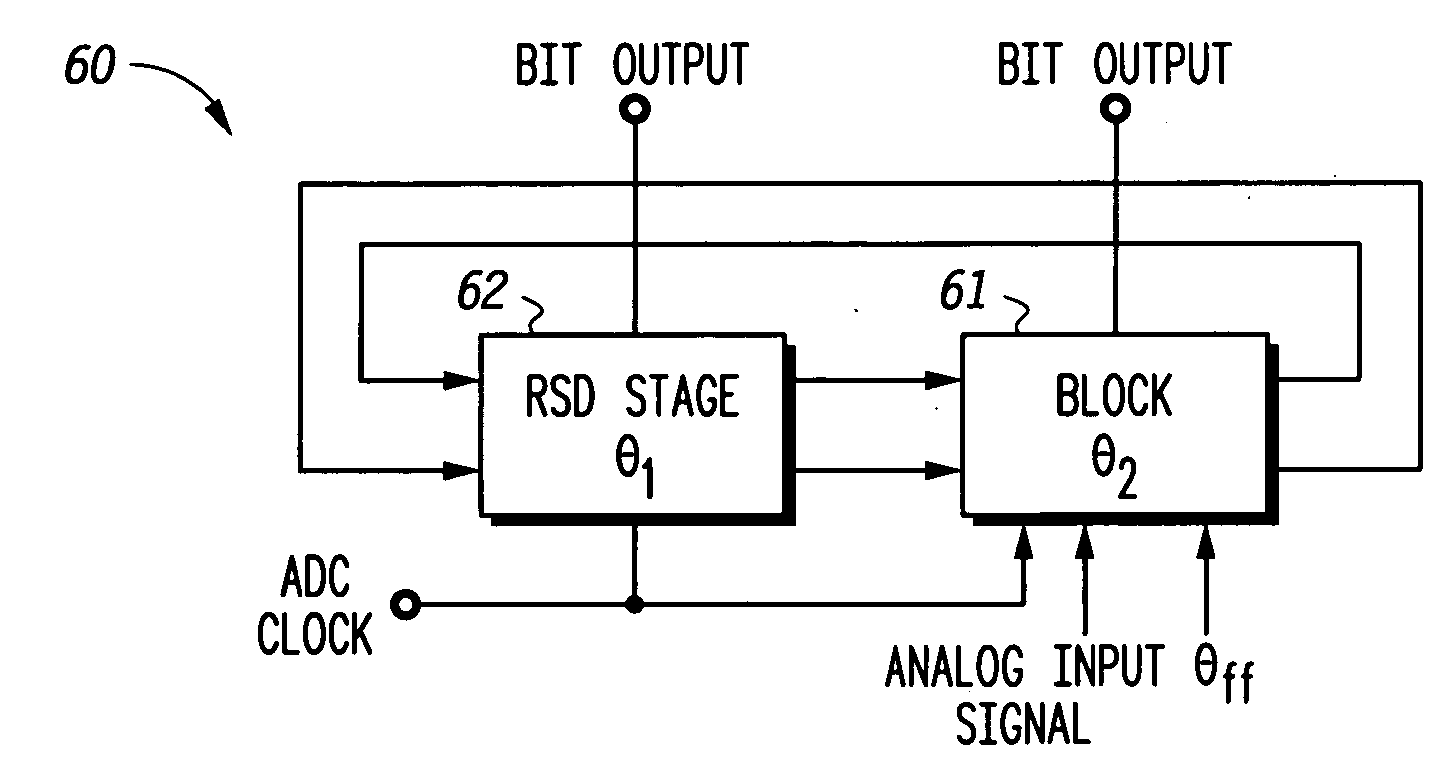

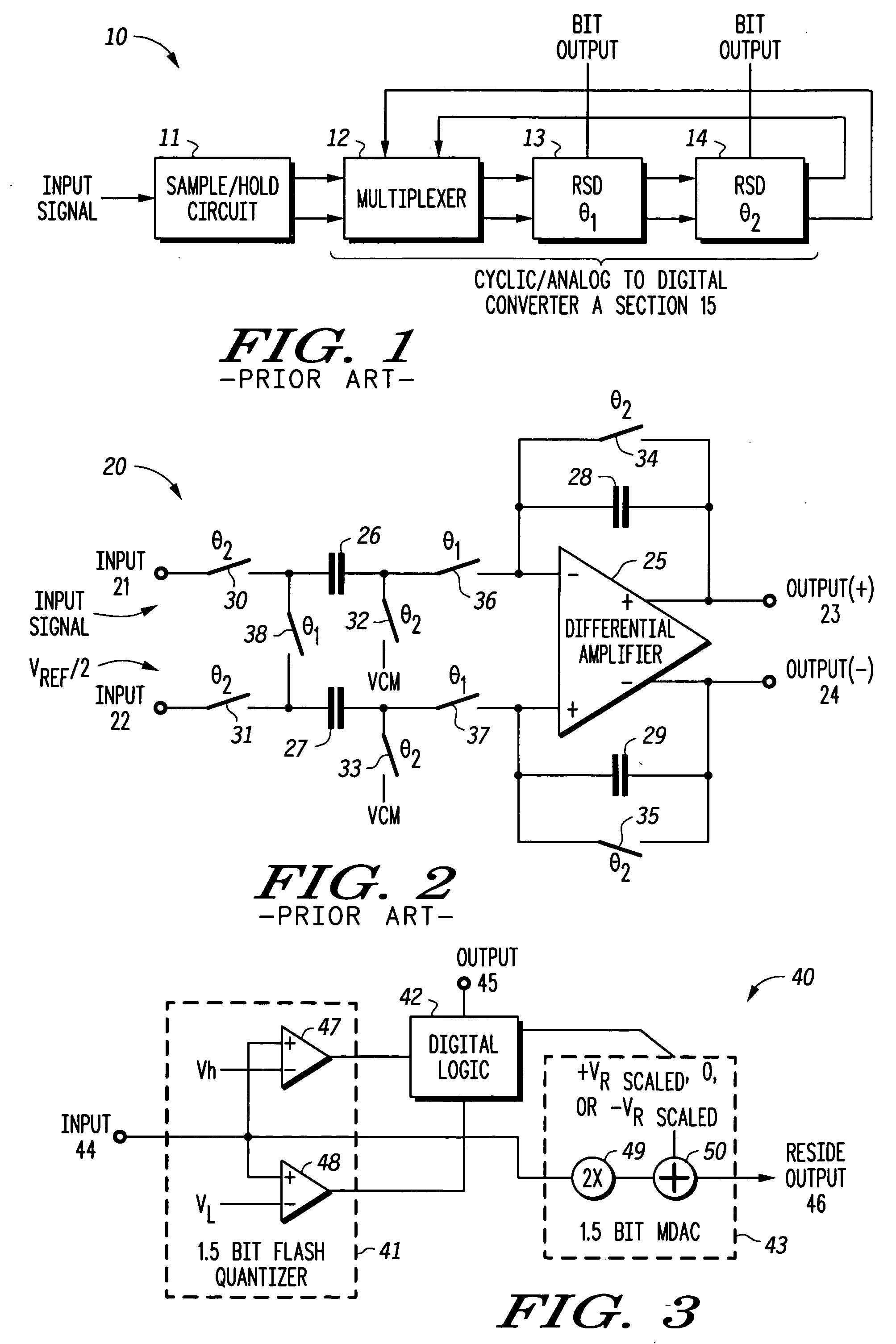

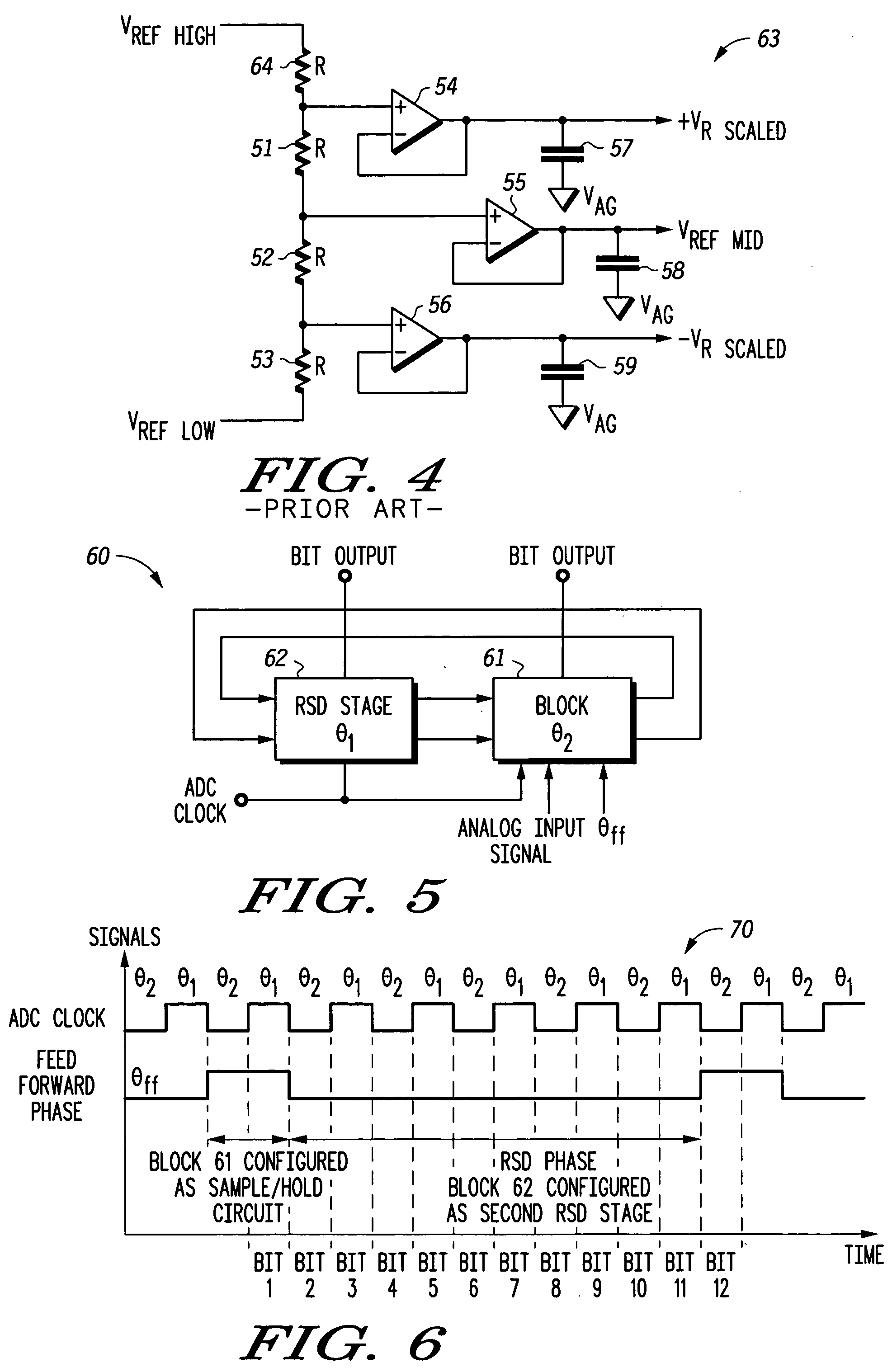

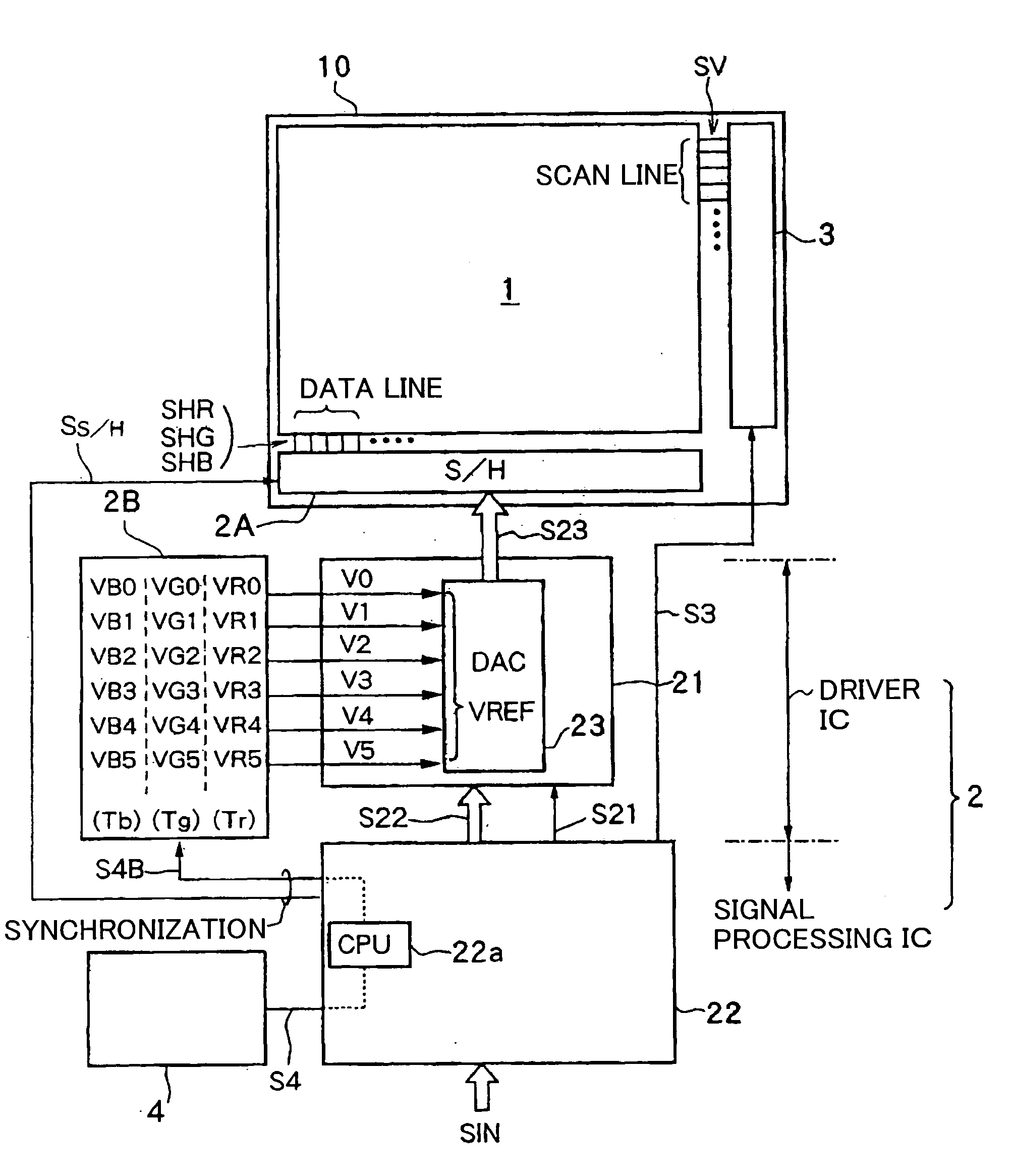

Optimized reference voltage generation using switched capacitor scaling for data converters

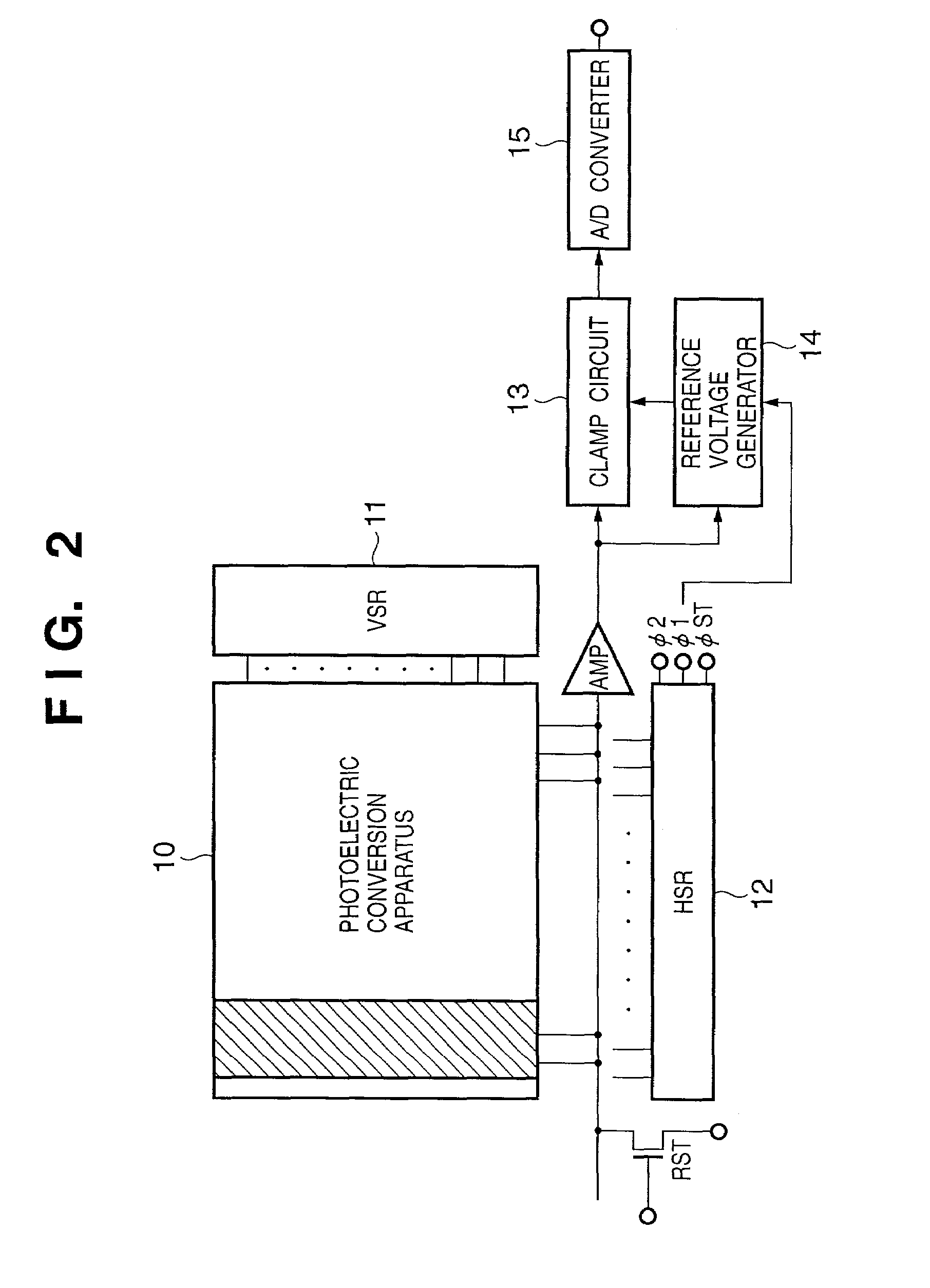

InactiveUS6967611B2Electric signal transmission systemsAnalogue-digital convertersCapacitanceA d converter

An algorithmic or cyclic data converter uses an RSD stage having a switched capacitor network for efficiently scaling at least one externally supplied reference voltage. A reference voltage is scaled by using capacitor ratios that also function to provide an output voltage used as a residue output of the RSD A / D converter. The residue is used to generate a bit value corresponding to the magnitude of the residue. Two RSD stages cycle back and forth generating a logic value each half clock cycle until the desired bit resolution is achieved. In one form, the RSD stage scales the externally supplied reference voltage only by factors of less than one. In another form, the RSD stage scales the reference voltage by any scaling factor. A reference voltage scaling circuit separate from the RSD stage is avoided.

Owner:NORTH STAR INNOVATIONS

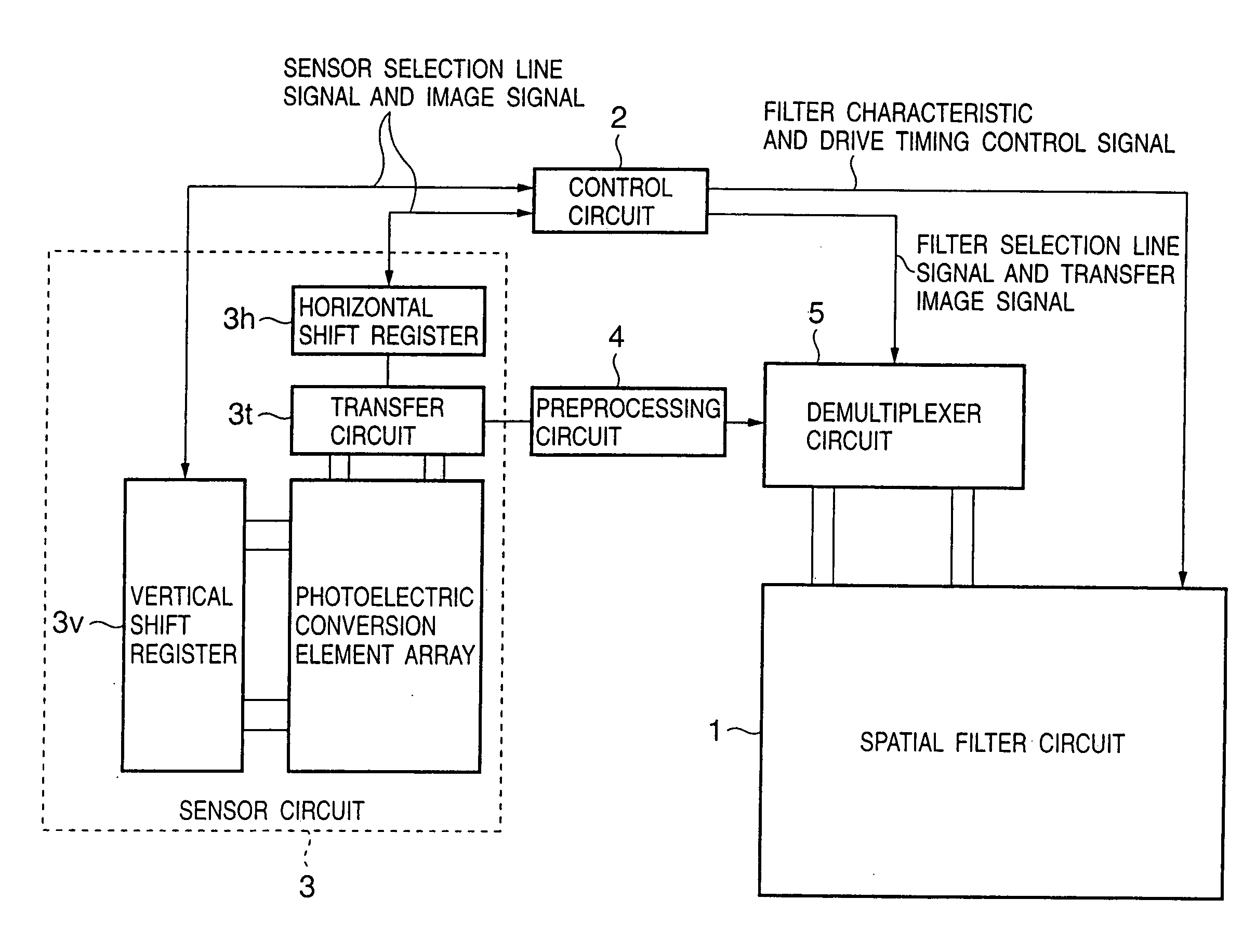

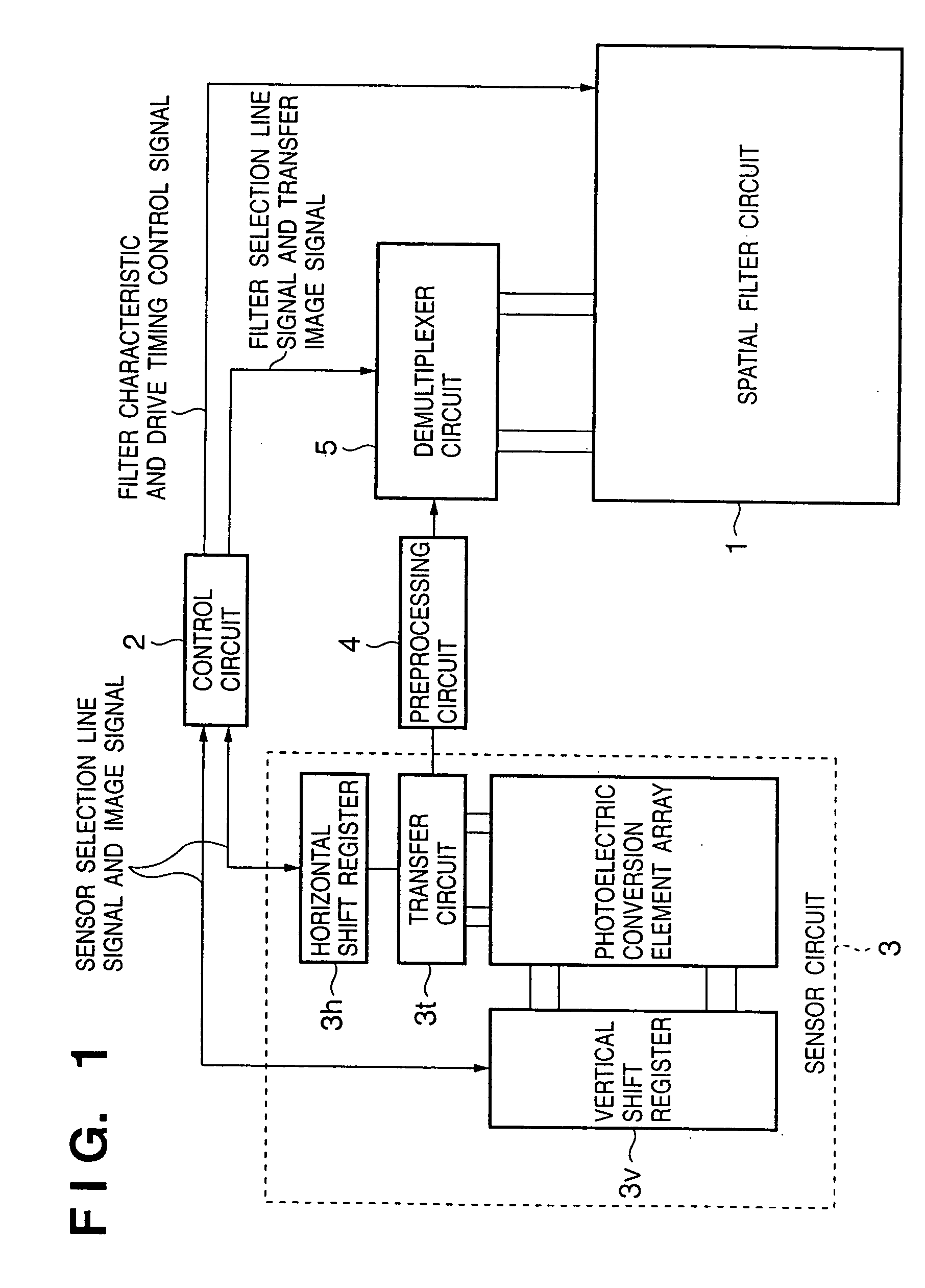

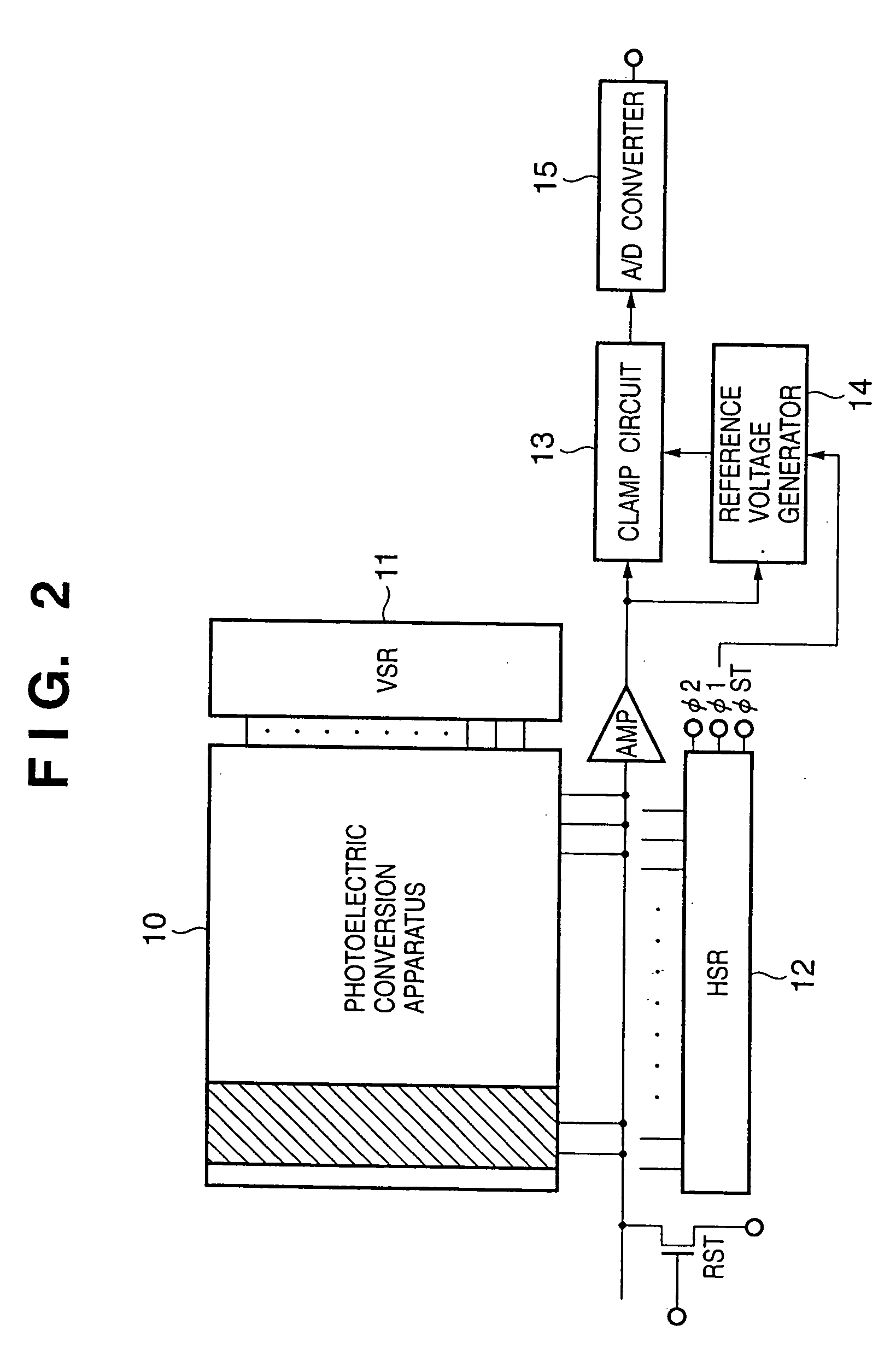

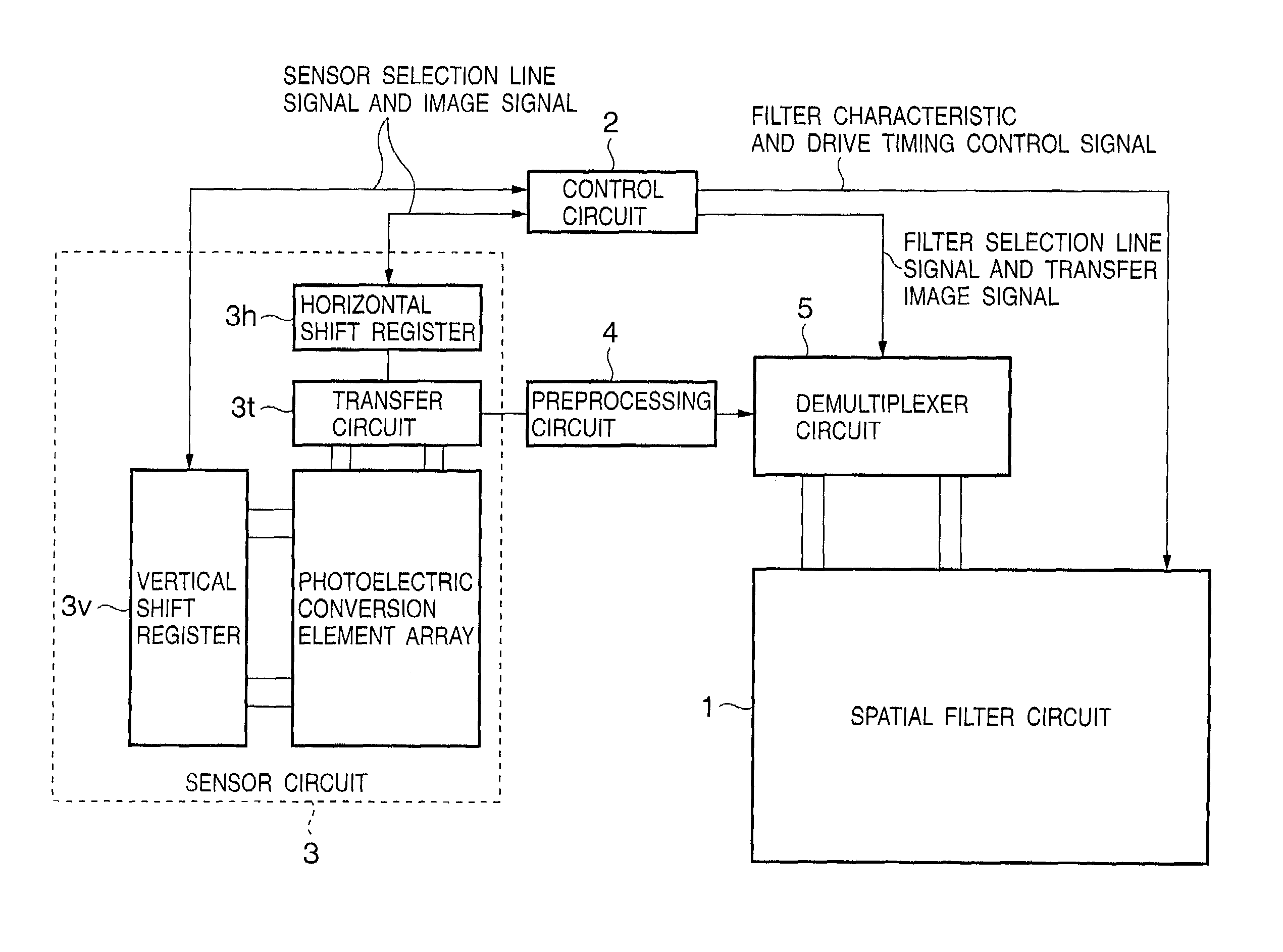

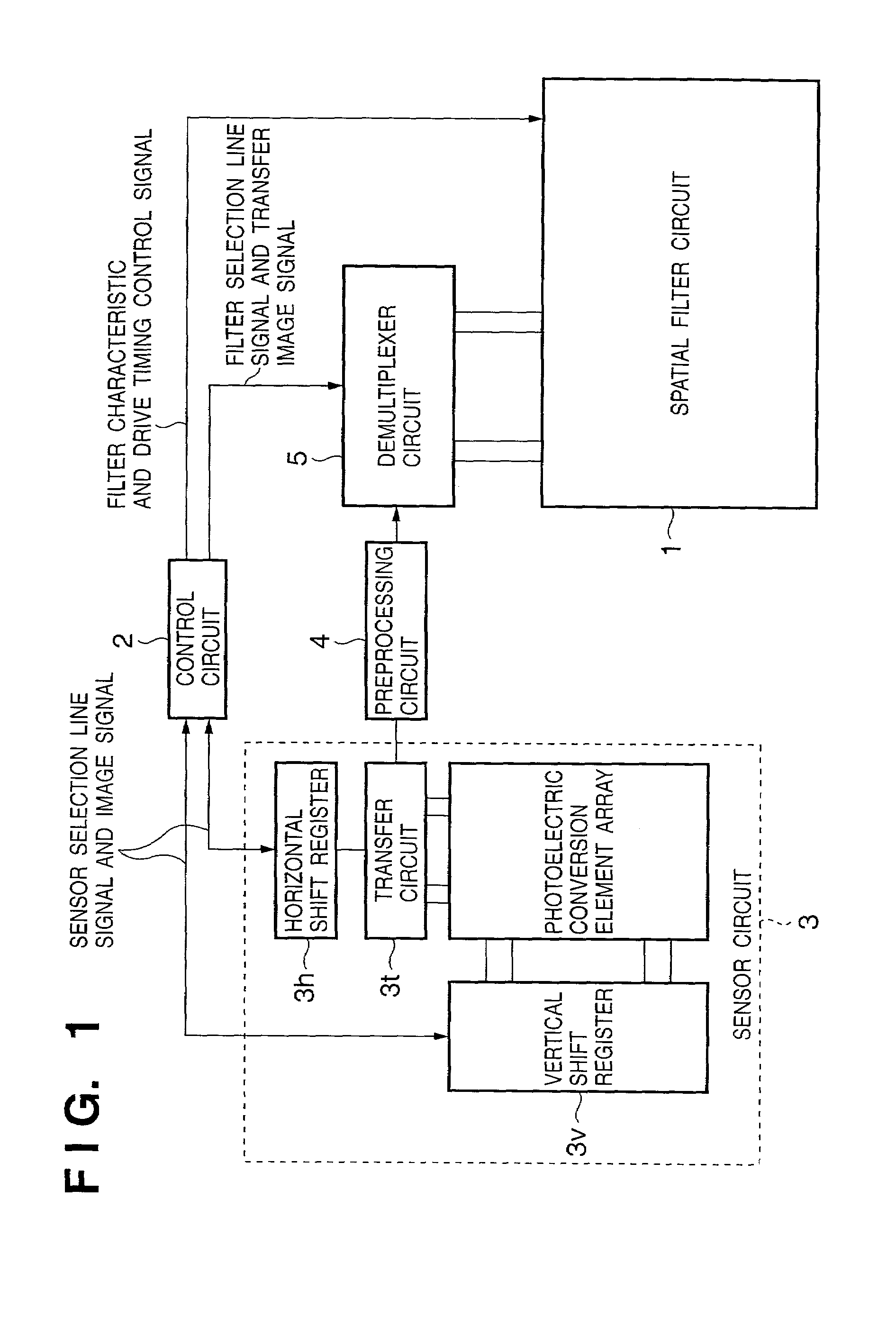

Dynamically reconfigurable signal processing circuit, pattern recognition apparatus, and image processing apparatus

InactiveUS20060228027A1Efficiently sequentially extract a pluralityEfficiently and stably executeCharacter and pattern recognitionNeural architecturesImaging processingSignal processing circuits

A plurality of signal processing functions are achieved with the same arithmetic processing circuit by controlling wiring arrangements or signal modulation in accordance with a predetermined arrangement control signal that is output based on circuit arrangement information read from a circuit arrangement information storage unit. Hierarchical parallel processing is realized with small-scale circuit configuration. Further, detection of a predetermined feature and integration of the detection results can be efficiently performed.

Owner:CANON KK

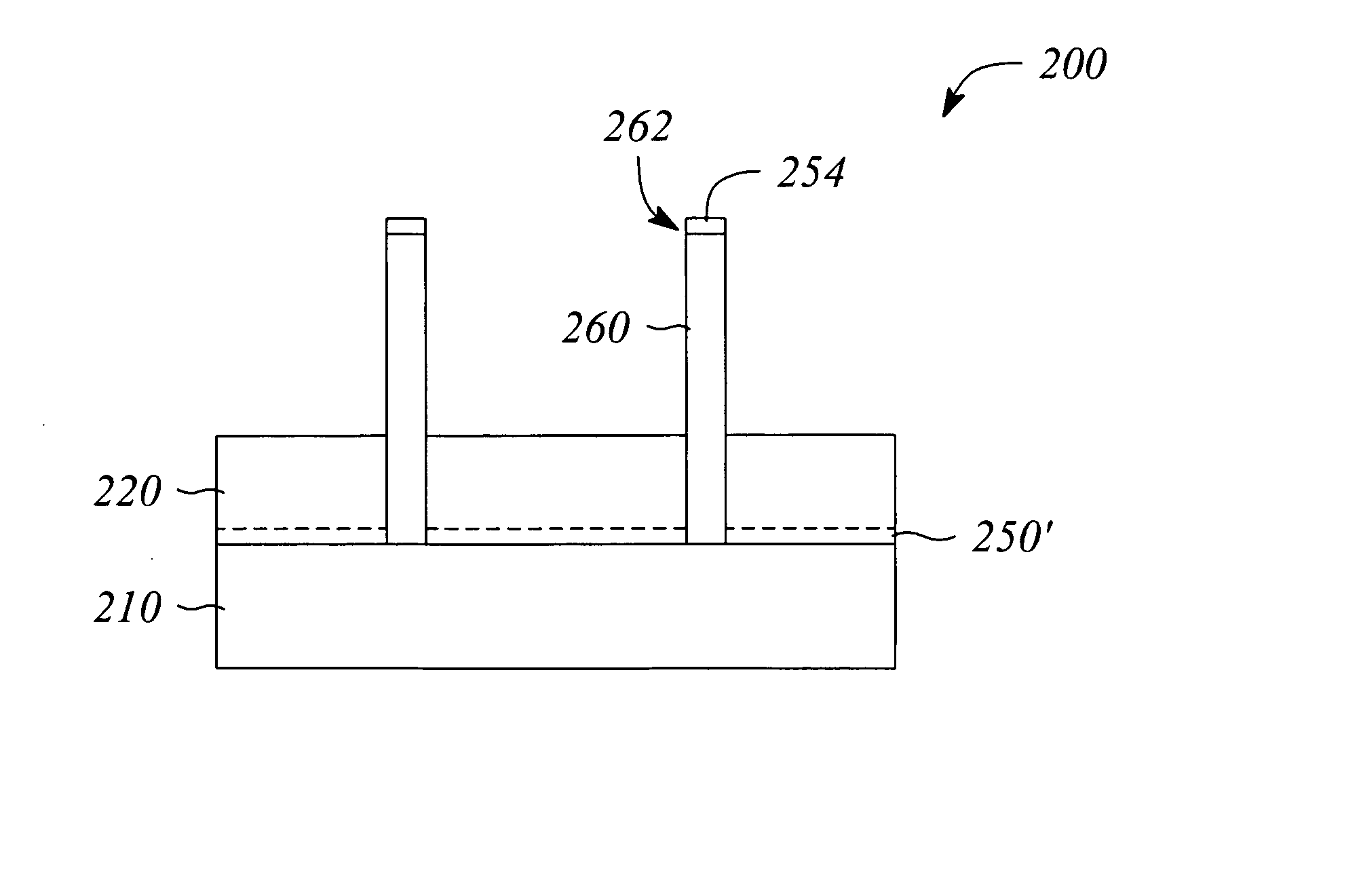

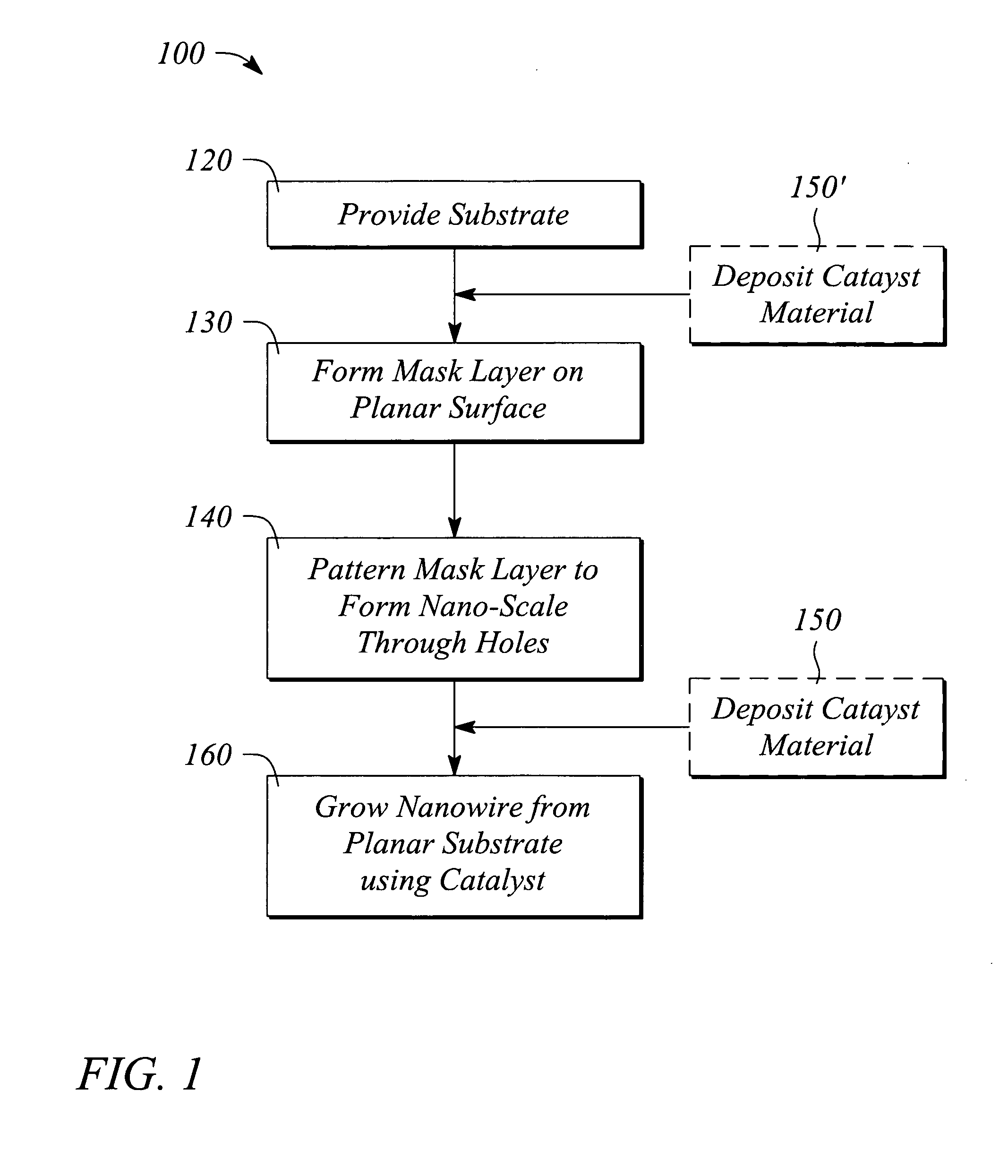

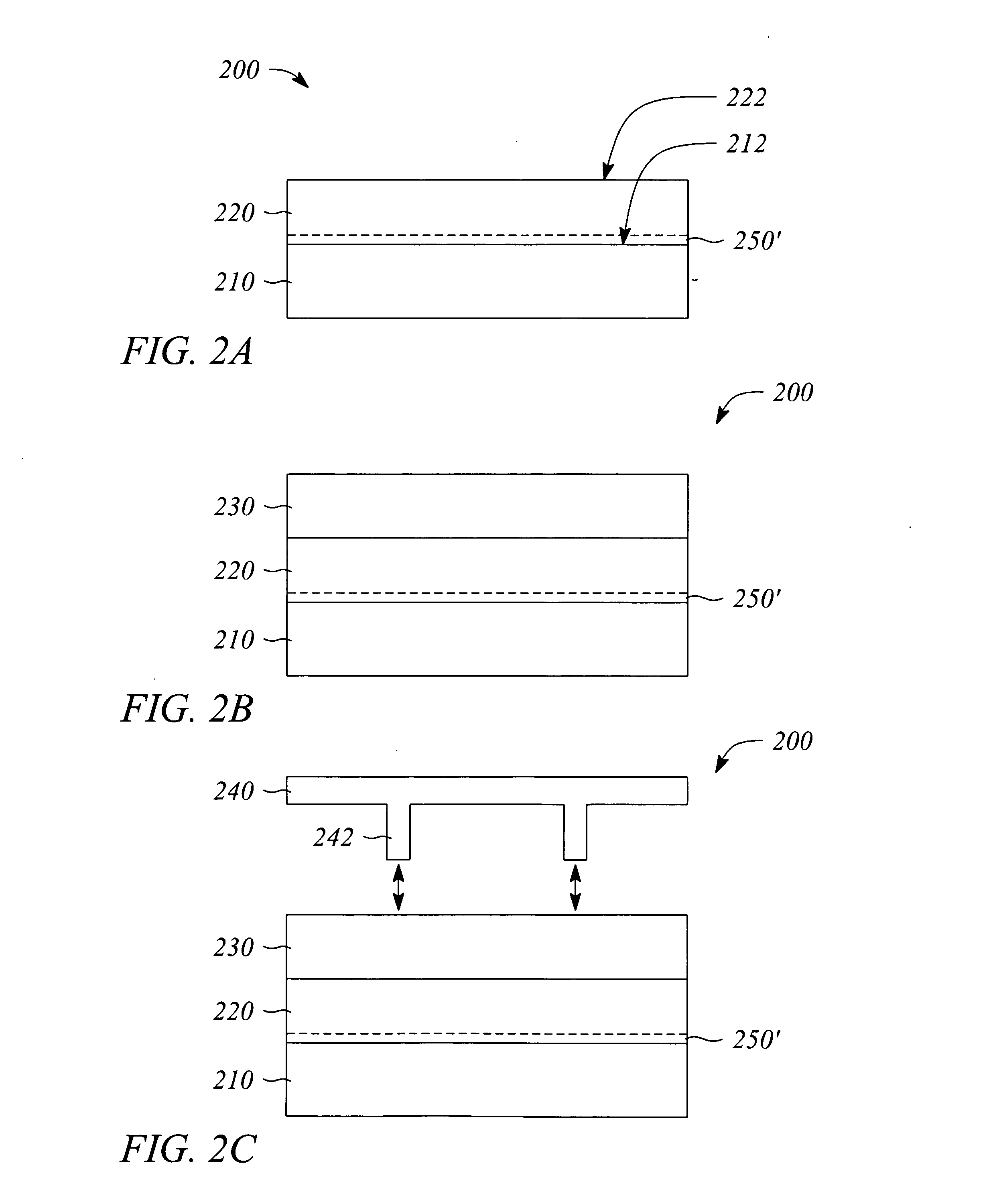

Method of controlling nanowire growth and device with controlled-growth nanowire

InactiveUS20070105356A1Semiconductor/solid-state device detailsSolid-state devicesNanowireCrystal orientation

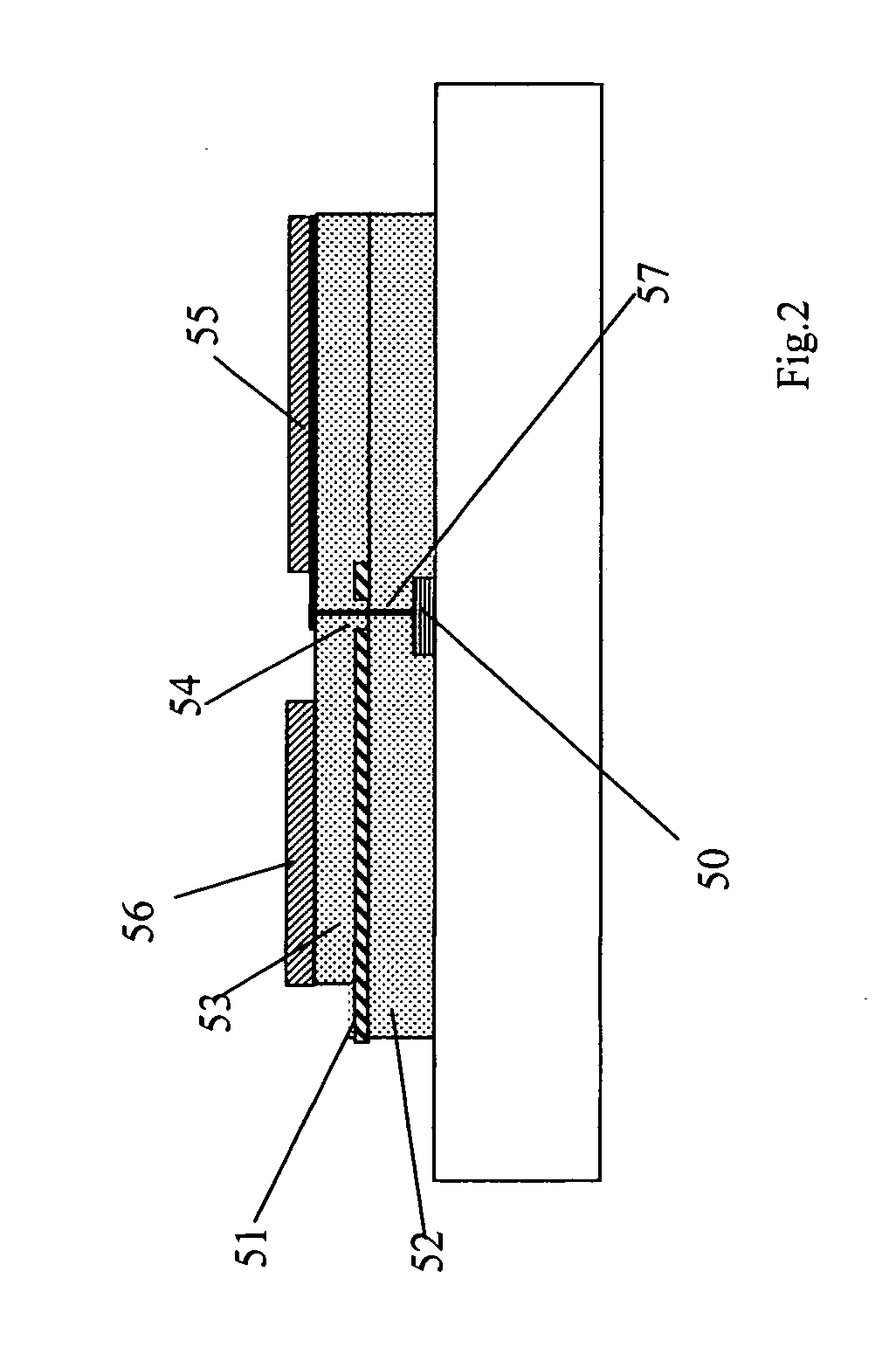

Nanowire growth in situ on a planar surface, which is one of a crystalline surface having any crystal orientation, a polycrystalline surface and a non-crystalline surface, is controlled by guiding catalyzed growth of the nanowire from the planar surface in a nano-throughhole of a patterned layer formed on the planar surface, such that the nanowire grows in situ perpendicular to the planar surface. An electronic device includes first and second regions of electronic circuitry vertically spaced by the patterned layer. The nano-throughhole of the patterned layer extends perpendicularly between the regions. The first region has the planar surface. The device further includes a nanowire extending perpendicular from a catalyst location on the planar surface of the first region in the nano-throughhole. The nanowire forms a component of a nano-scale circuit that connects the regions.

Owner:HEWLETT PACKARD DEV CO LP

Optimized reference voltage generation using switched capacitor scaling for data converters

InactiveUS20050219097A1Electric signal transmission systemsAnalogue-digital convertersEngineeringVoltage reference

An algorithmic or cyclic data converter uses an RSD stage having a switched capacitor network for efficiently scaling at least one externally supplied reference voltage. A reference voltage is scaled by using capacitor ratios that also function to provide an output voltage used as a residue output of the RSD A / D converter. The residue is used to generate a bit value corresponding to the magnitude of the residue. Two RSD stages cycle back and forth generating a logic value each half clock cycle until the desired bit resolution is achieved. In one form, the RSD stage scales the externally supplied reference voltage only by factors of less than one. In another form, the RSD stage scales the reference voltage by any scaling factor. A reference voltage scaling circuit separate from the RSD stage is avoided.

Owner:NORTH STAR INNOVATIONS

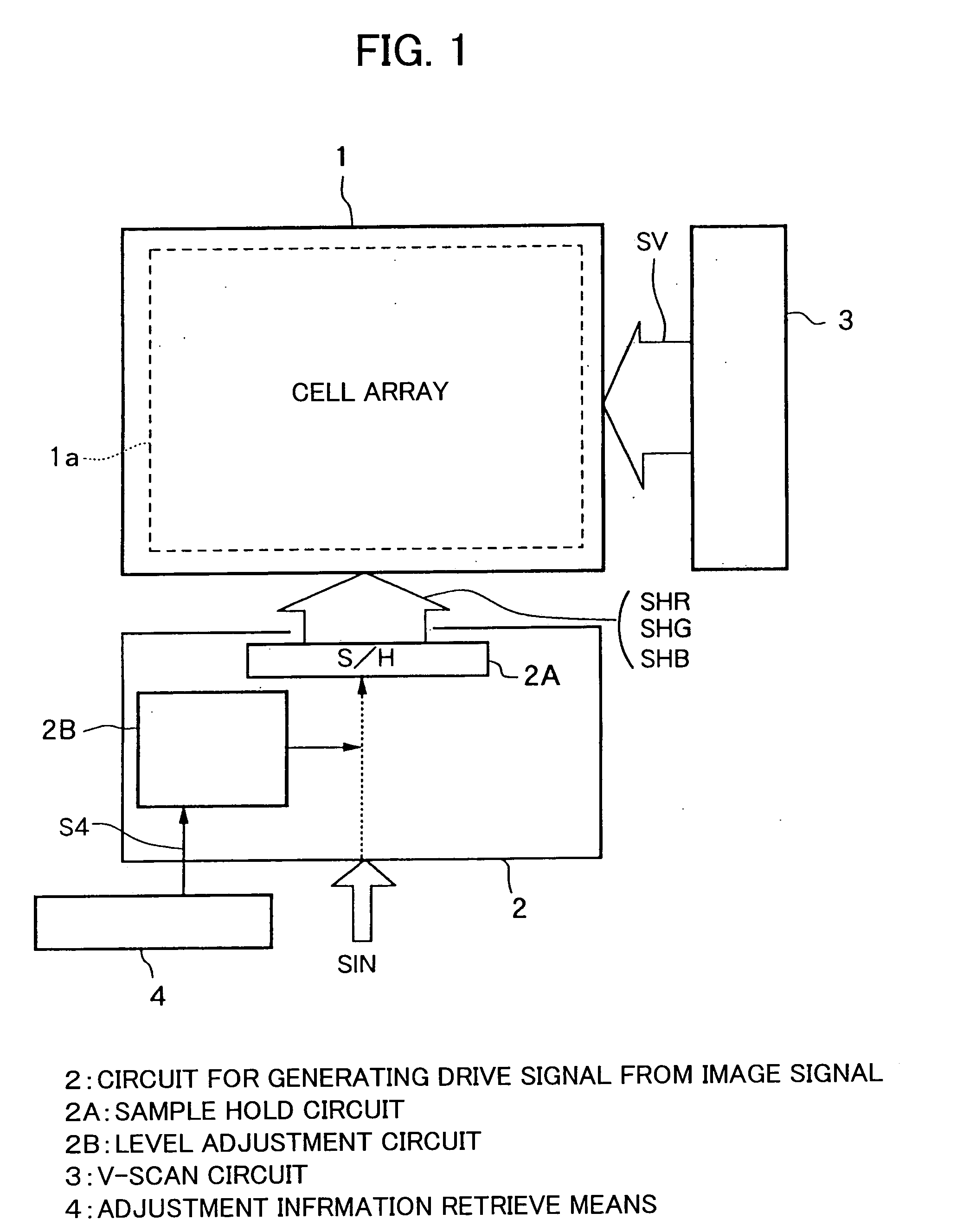

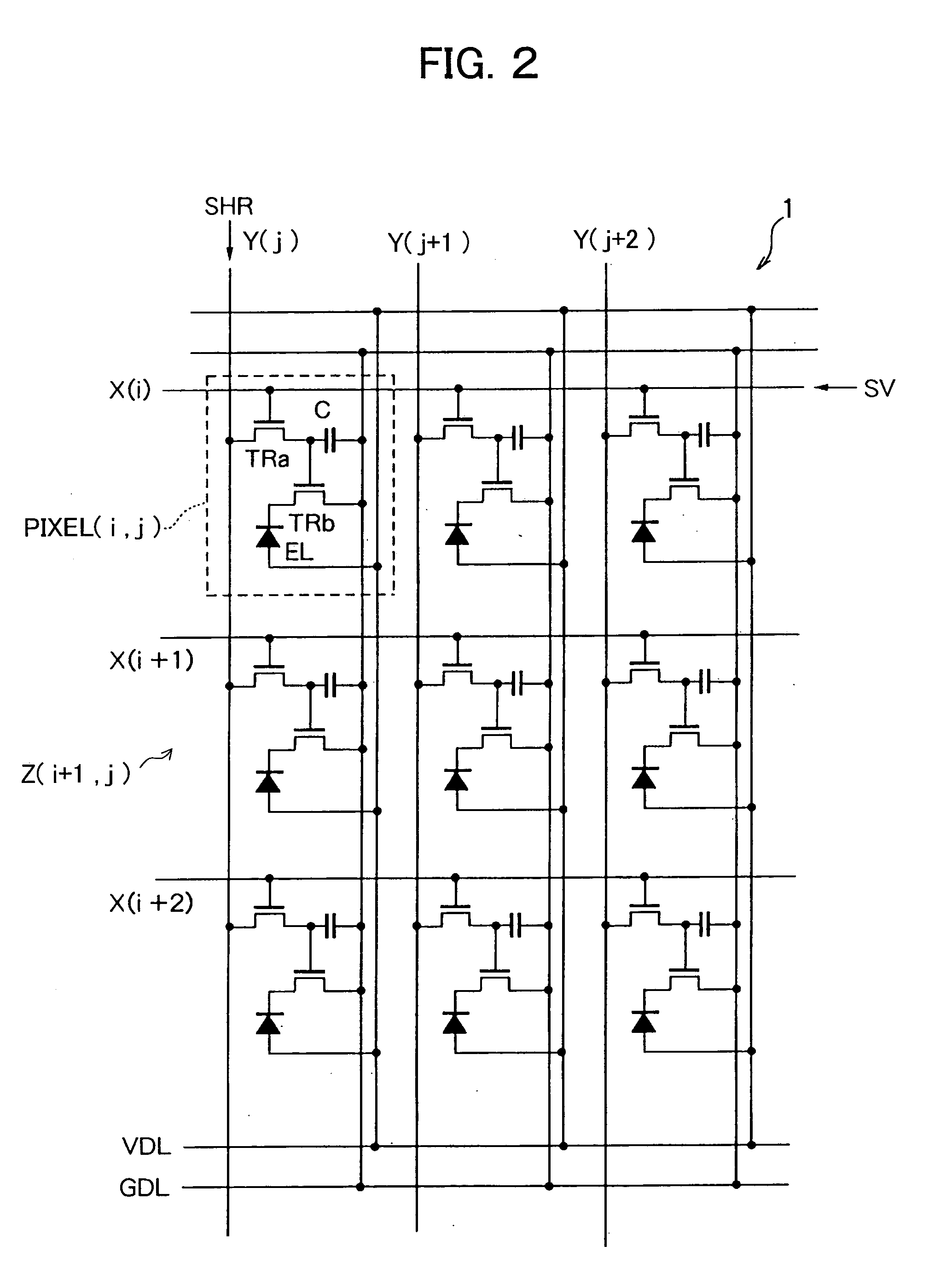

Image display device and the color balance adjustment method

InactiveUS20050062691A1Easily adjusting color balanceElectroluminescent light sourcesSolid-state devicesEngineeringLight emission

A circuit for generating drive signals (SHR, SHG and SHB) from an input image signal (SIN), a cell array (1) including a light emitting element (EL) for emitting light of a predetermined color of red (R), green (G) or blue (B) by being applied with a drive signal (SHR, SHG and SHB) supplied for each color from the circuit (2), an adjustment information retrieve means (4) for obtaining information relating light emission adjustment of the light emitting element (EL), and a level adjustment circuit (2B) provided in the circuit (2) for changing a level of an RGB signal (S22) before divided to drive signals (SHR, SHG and SHB) for the respective RGB colors based on the information obtained by the adjustment information retrieve means (4) are provided. In the present invention, color balance adjustment can be performed by the above small scale circuit.

Owner:JOLED INC

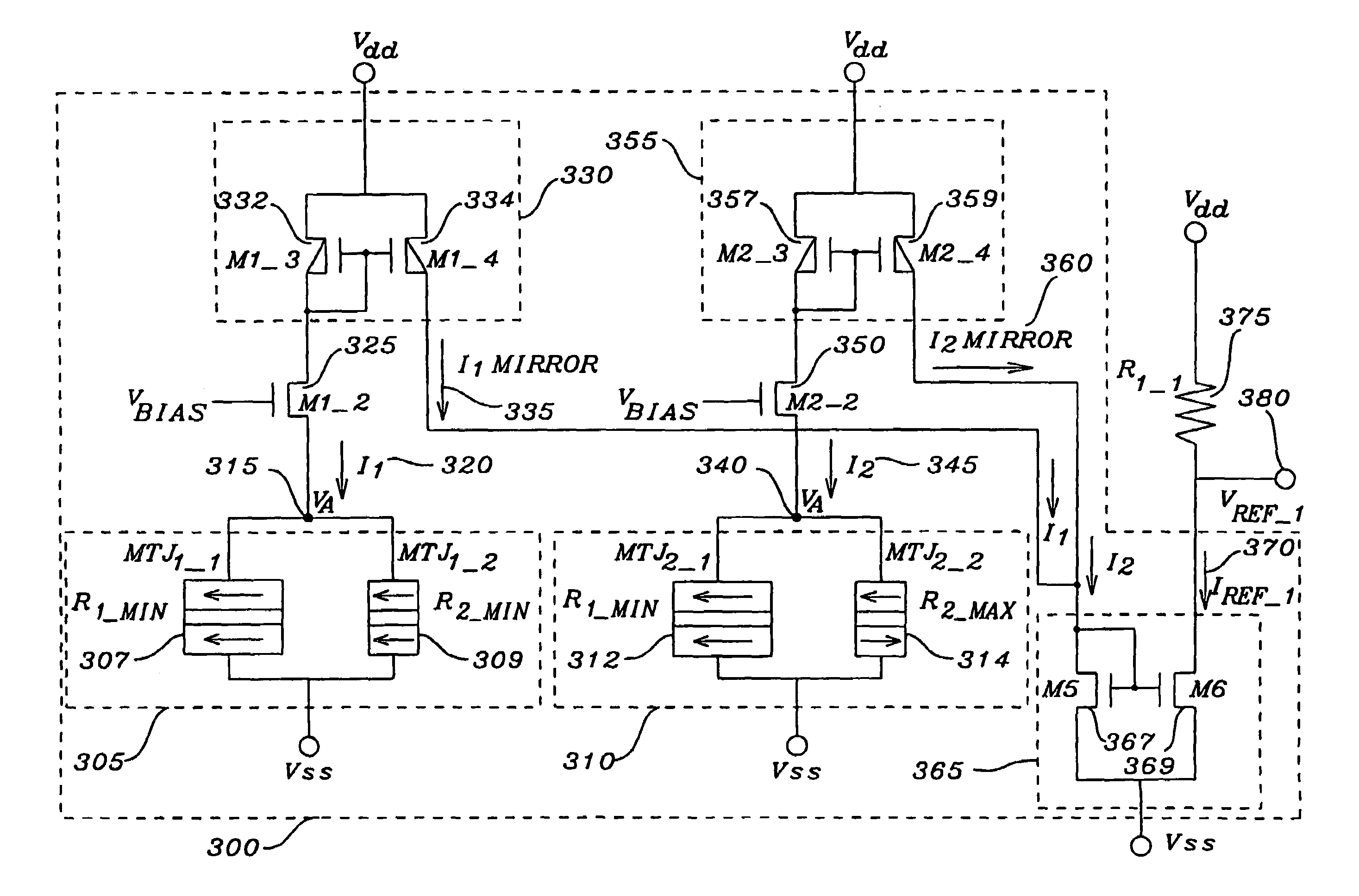

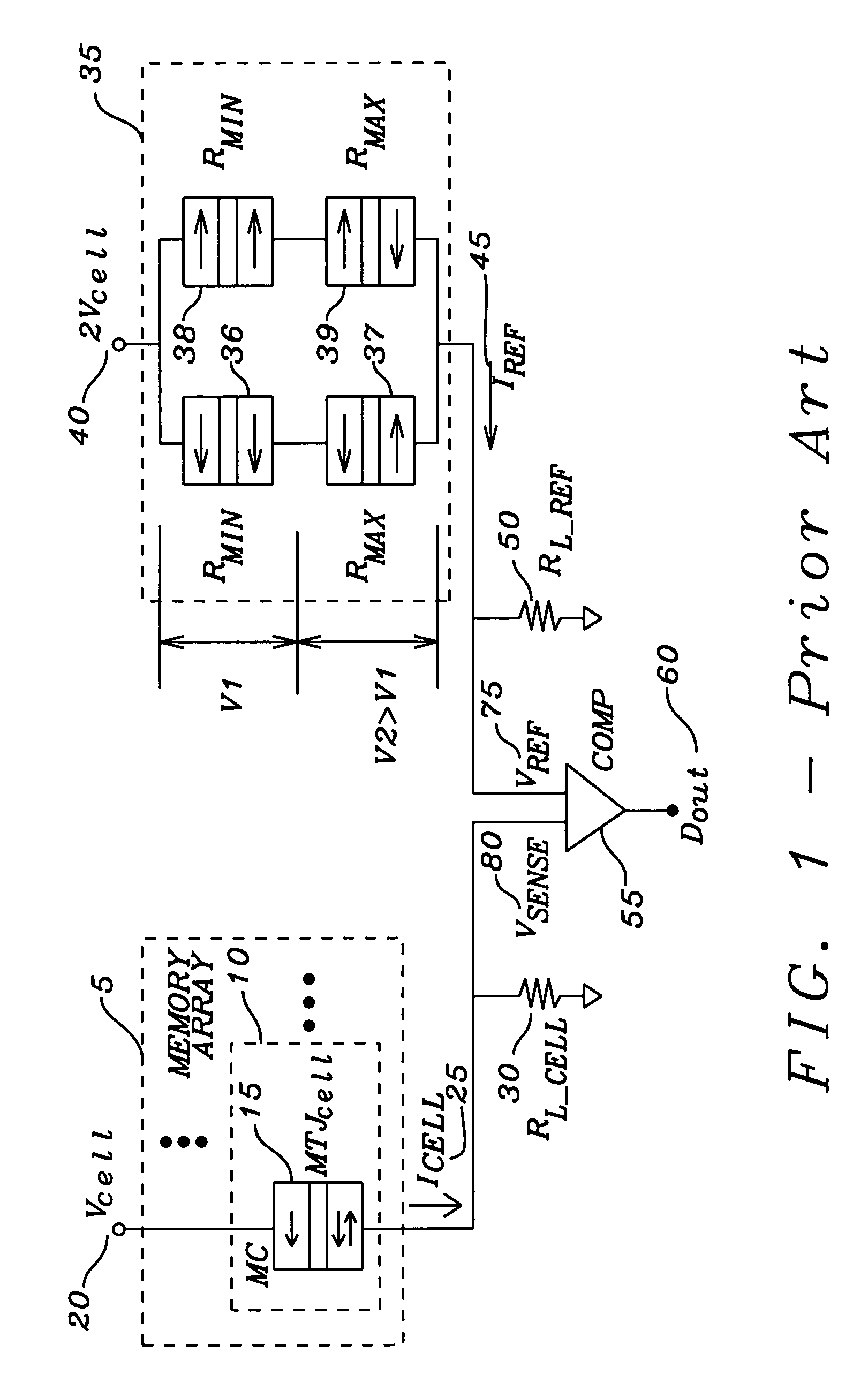

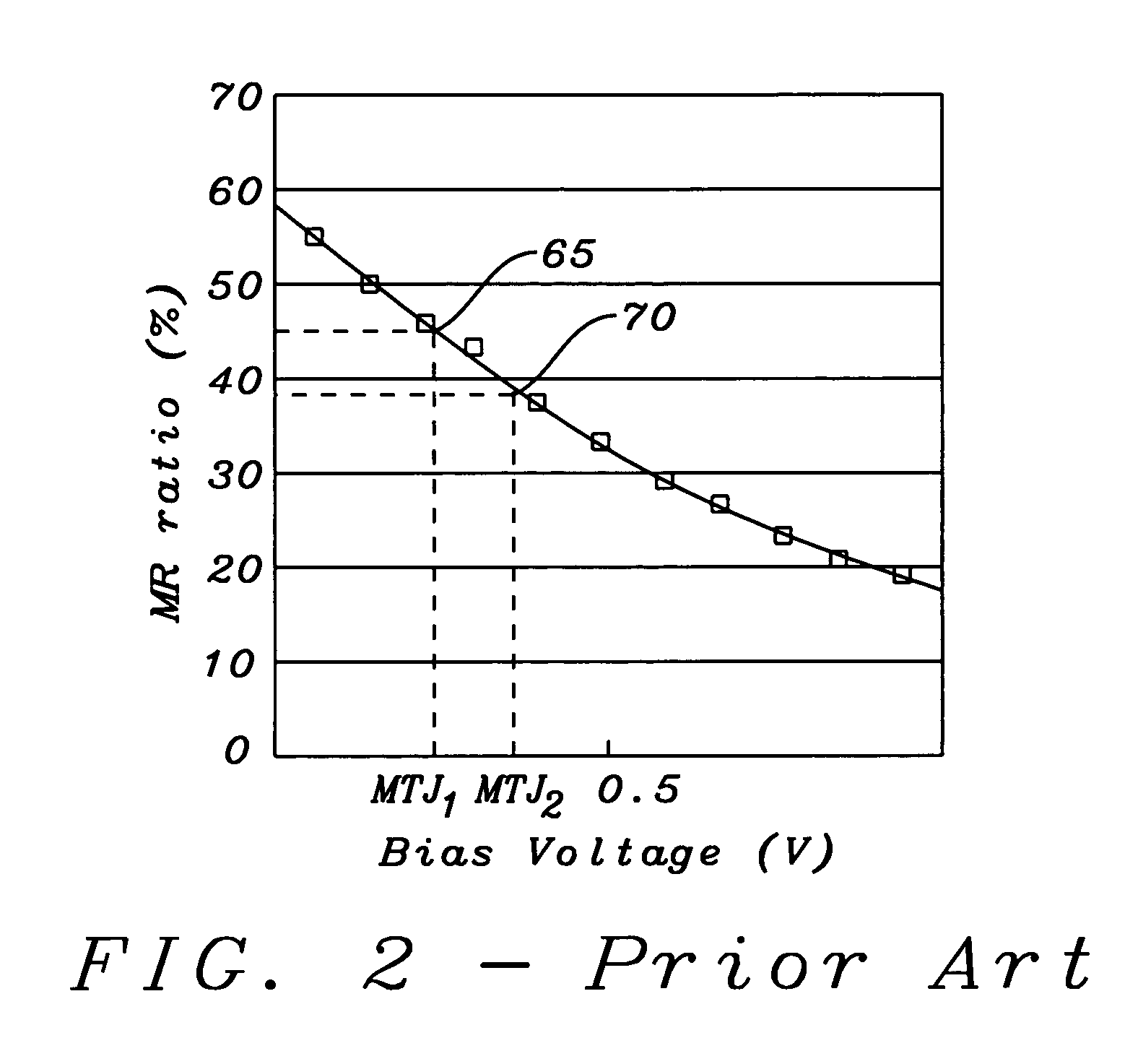

Reference generator for multilevel nonlinear resistivity memory storage elements

A multilevel reference generator has a plurality of nonlinear standard resistive elements where each resistive element is biased at a constant level to develop a resultant level. The multilevel reference generator has a plurality of mirror sources. Each mirror source is in communication with the one of the plurality of resistive elements such that each mirror source receives the resultant level from the one standard resistive element and provides a mirrored replication of the resultant level. The multilevel reference generator has a plurality of reference level combining circuits. The reference level combining circuit includes a resultant level summing circuit that additively combines the first and second mirrored replication level and a level scaling circuit to create a scaling of the combined first and second mirrored replication levels to create the reference level.

Owner:TAIWAN SEMICON MFG CO LTD

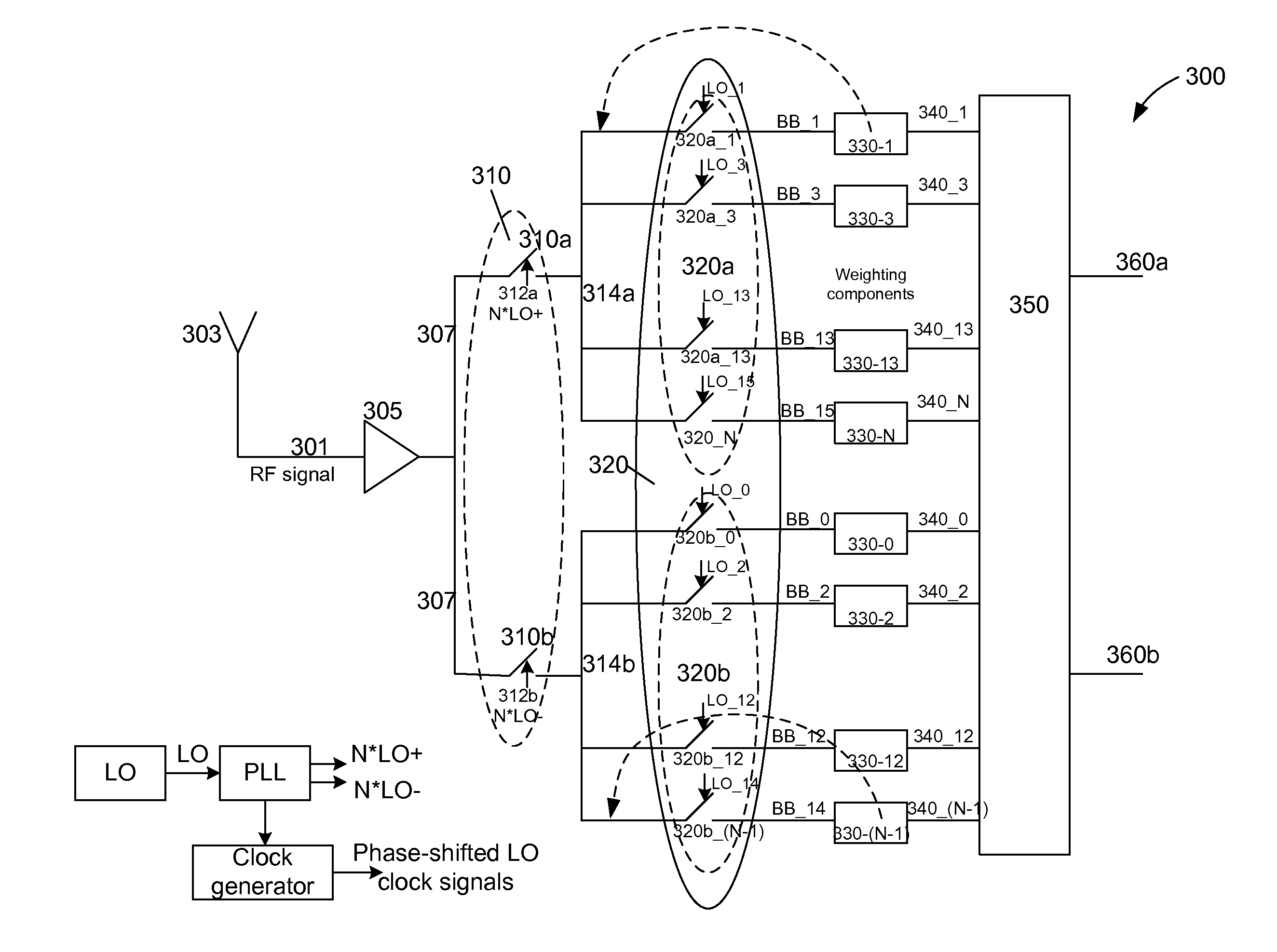

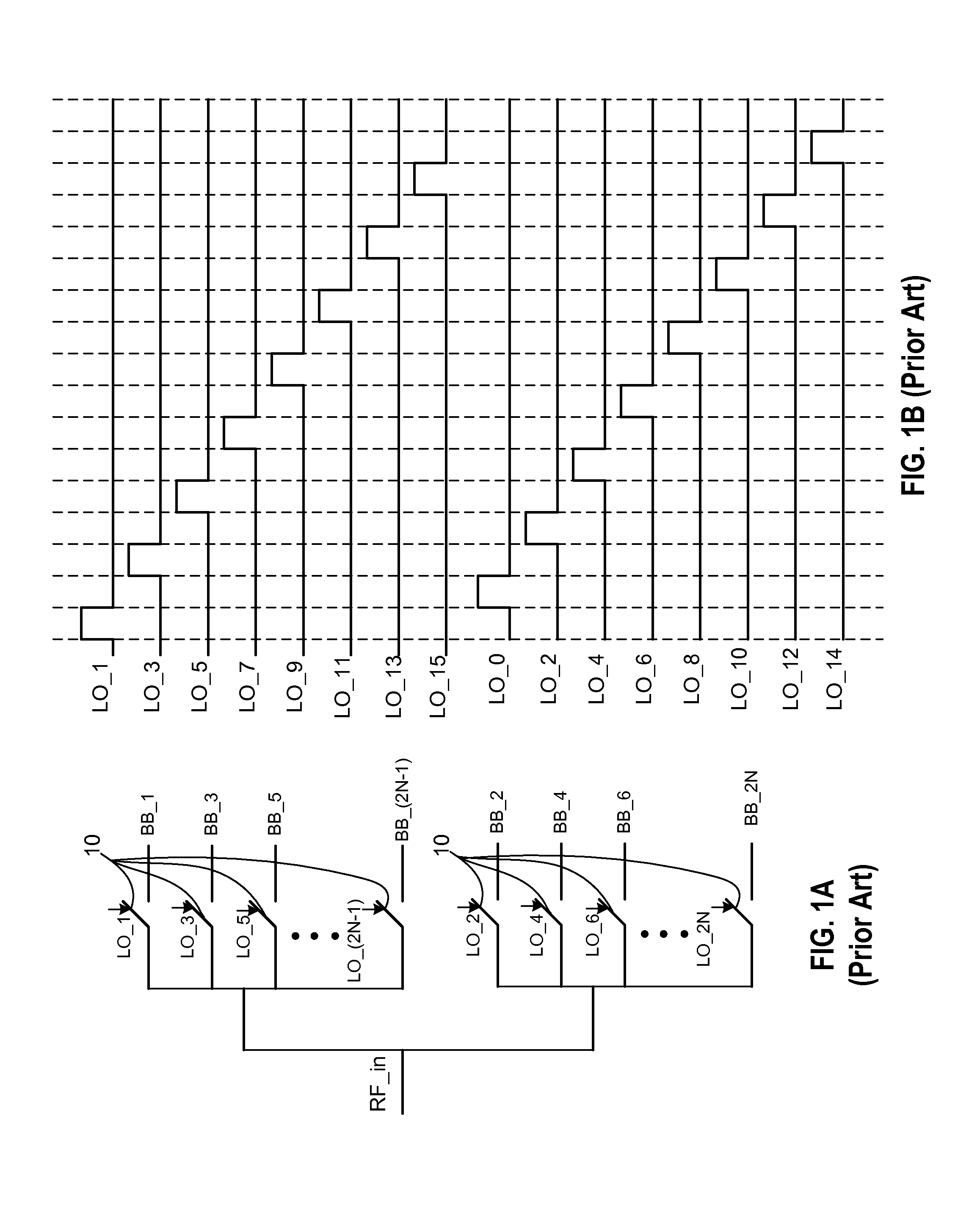

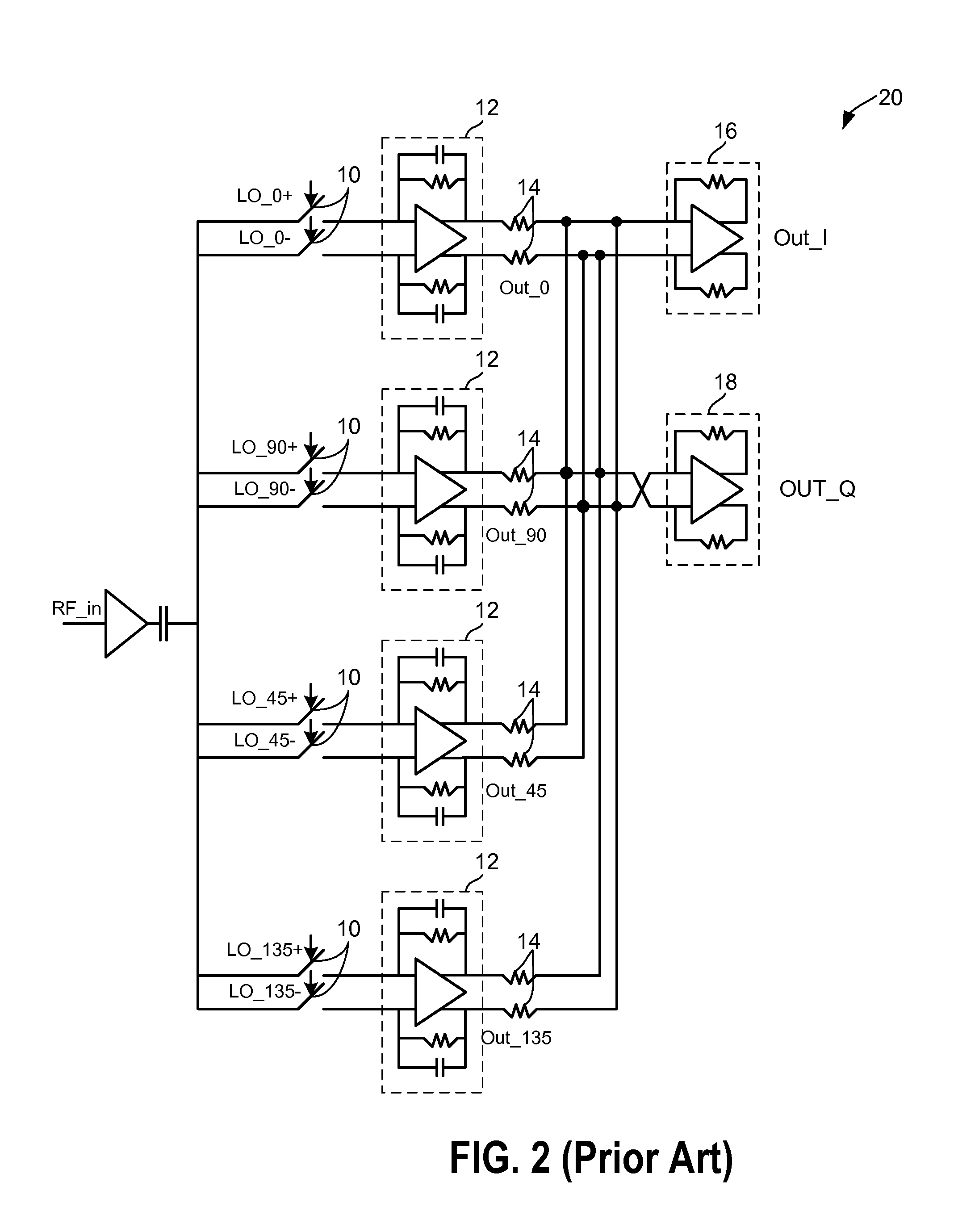

Harmonic Rejection Mixer Architecture with Reduced Sensitivity to Gain and Phase Mismatches

A harmonic rejection mixer includes a first scaling circuit for scaling an RF signal to generate a plurality of scaled RF signals, a first switching stage for sampling the scaled RF signals using a first plurality of switching signals, and a second mixing stage for mixing the sampled RF signals with a second plurality of switching signals to generate a plurality of frequency translated signals having different phases. A combiner adds the frequency translated signals together to generate a first plurality of baseband versions of the RF signal. A first amplifier stage processes the first plurality of baseband versions to generate a second plurality of baseband versions. The mixer further includes a second scaling circuit for scaling the second plurality of baseband versions and a second amplifier stage to generate an in-phase baseband signal and a quadrature baseband signal from the scaled second plurality of baseband versions.

Owner:MAXLINEAR INC

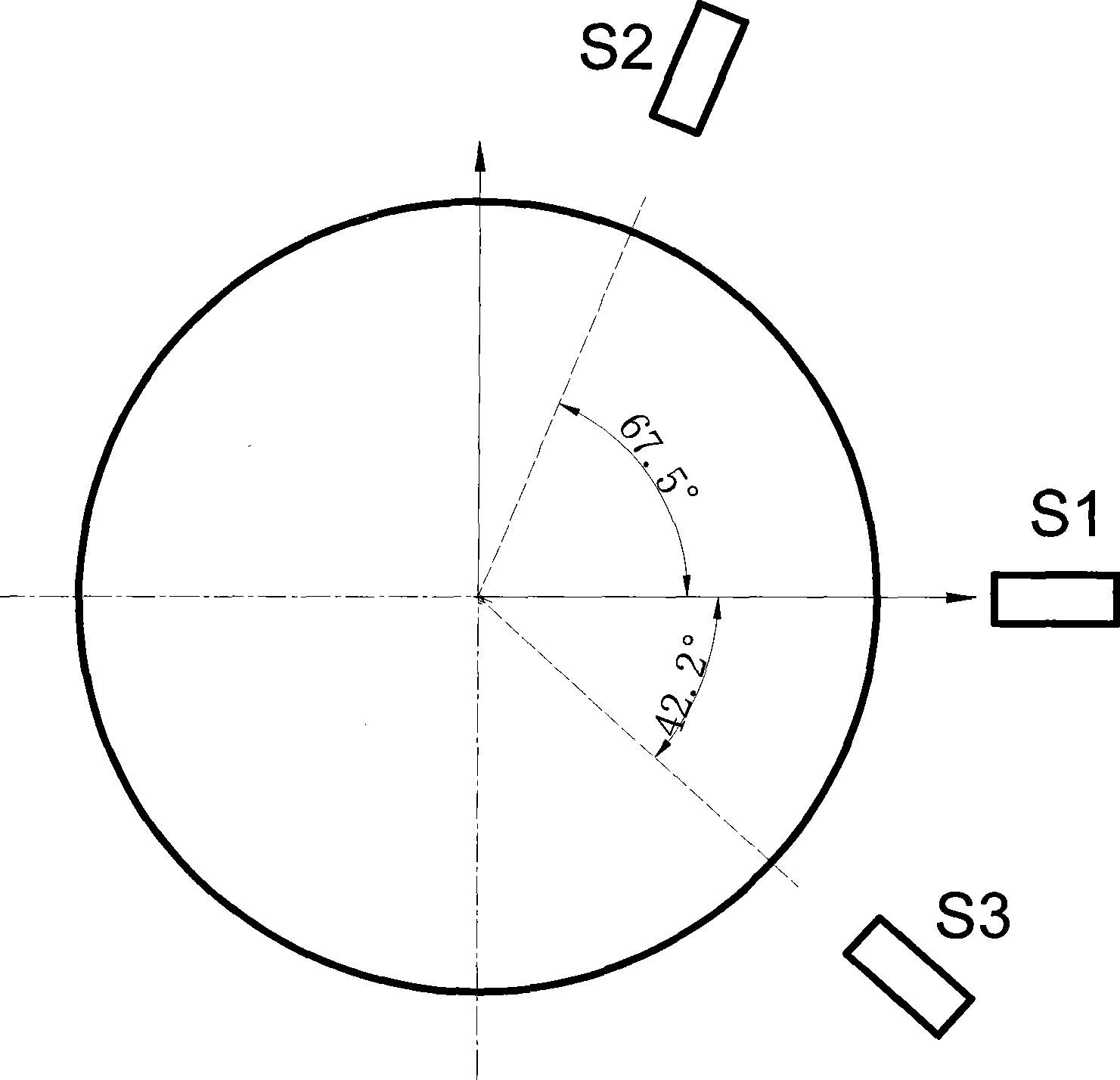

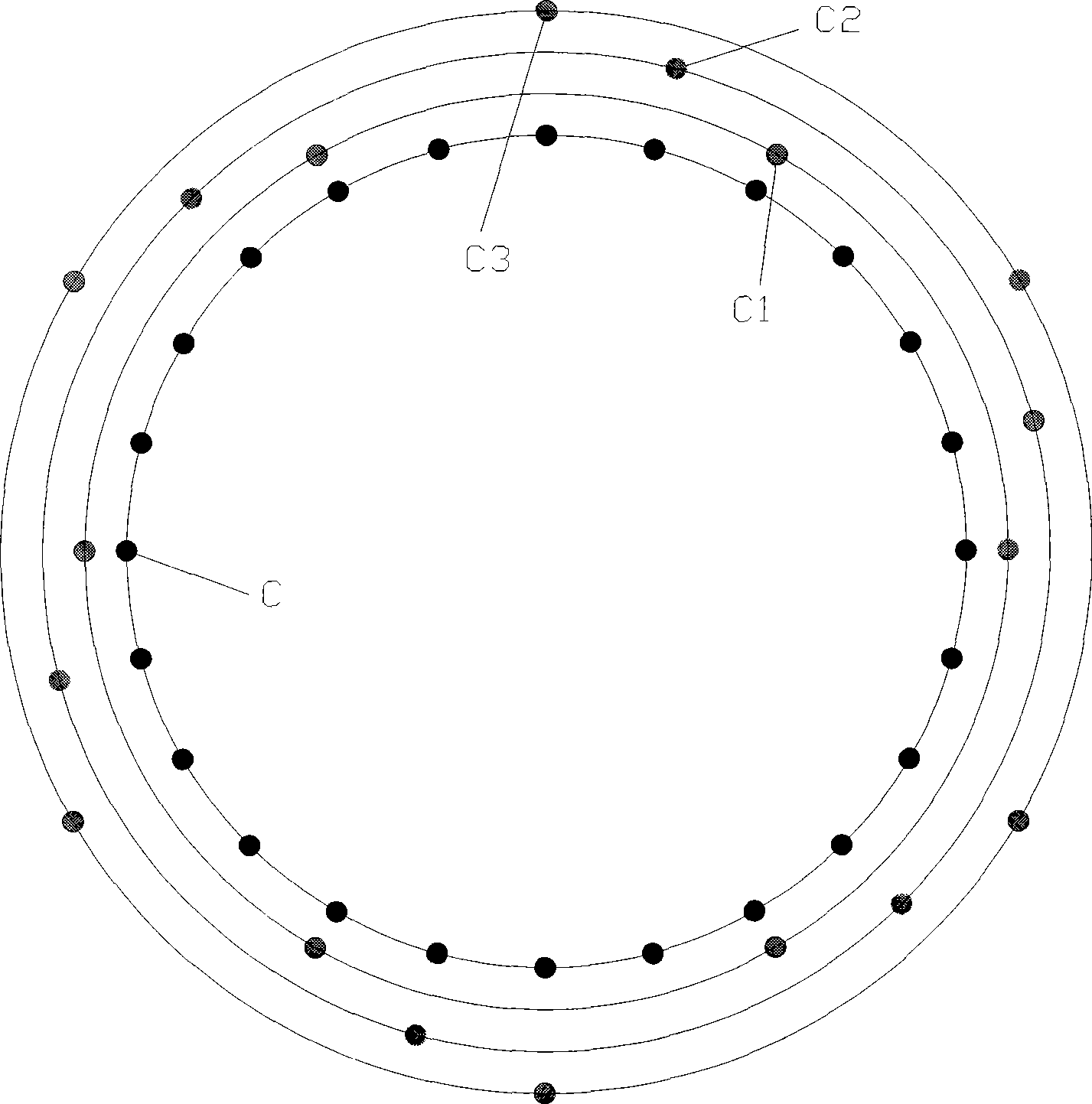

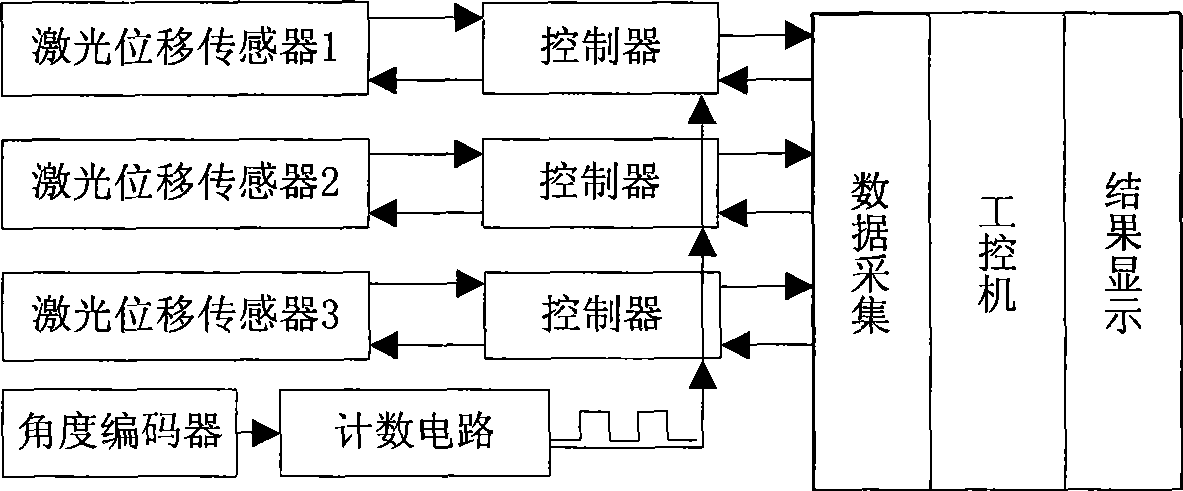

Method for detecting radial motion error of high speed principal axis by multi-ring coincidence three-point method

InactiveCN101424512ALower resolution requirementsMeasurement/indication equipmentsUsing optical meansRadial motionUSB

The invention discloses a method for detecting radial motion error of a high-speed principal axis by adopting a multi-circle superposition three-point method. Three laser displacement sensors are distributed around the high-speed principal axis which is provided with an angle encoder that has N lines and is connected with a scaling circuit; when the scaling circuit counts for Z times in an accumulating way and Z can not be divided exactly by N, the scaling circuit outputs sampled signals, and a trigger sensor implements sampling once; by repeating in this way, the principal axis is evenly distributed with n points for sampling by rotating the principal axis for a plurality of times to complete a sampling period; after every time of sampling, the sampling value is transmitted to an industrial computer through a USB interface and is then recorded; according to the requirements of detection accuracy, the sampling work having a plurality of sampling periods is carried out, the average sampling value of n points of every laser displacement sensor is calculated, and the deviation from circular form, the eccentric error and radial turning error of the principal axis which are obtained by separation are calculated. The method is not sensitive to the performance of the laser displacement sensor and is suitable for detecting radial motion error of the high-speed principal axis.

Owner:ZHEJIANG UNIV

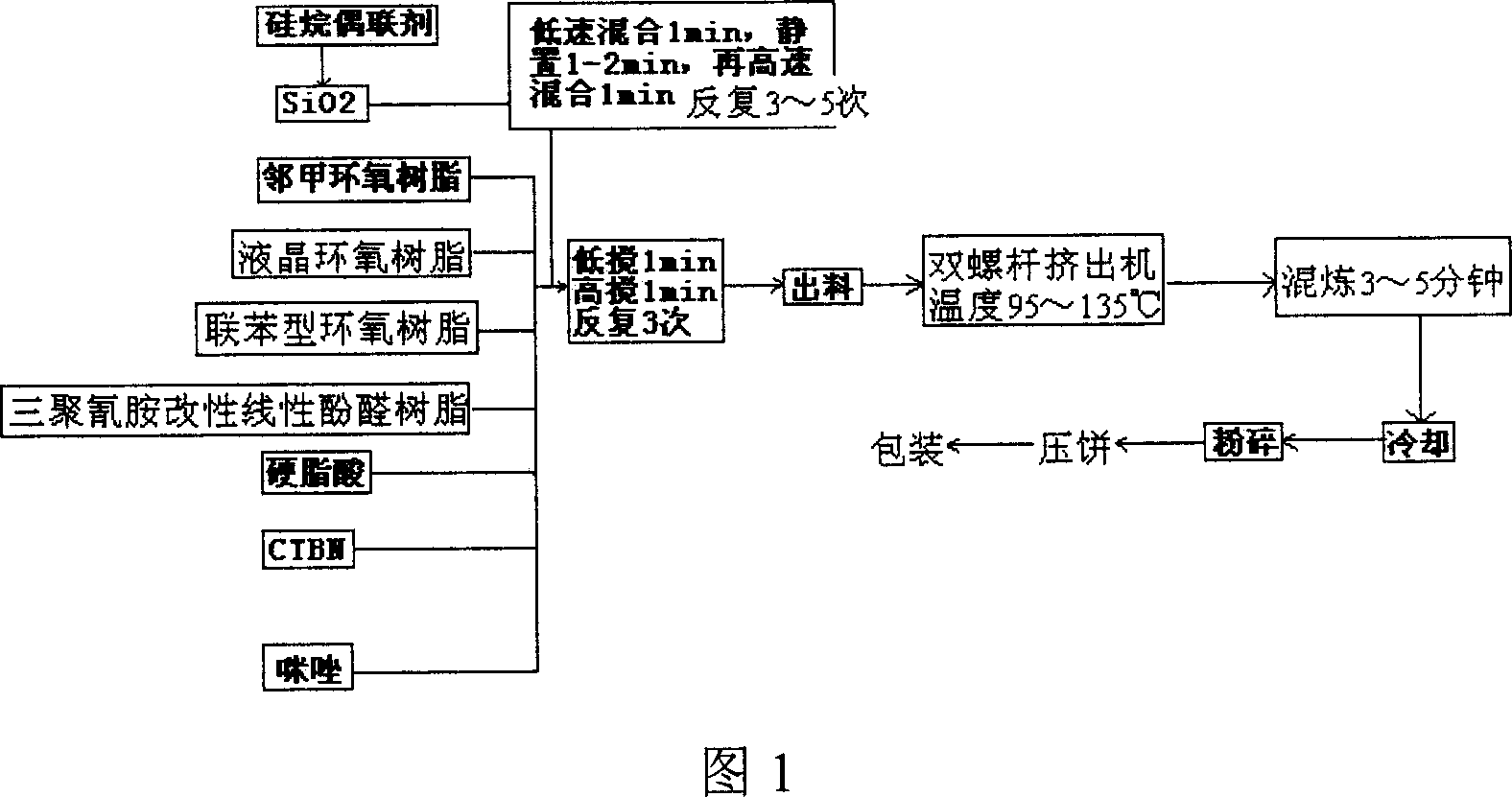

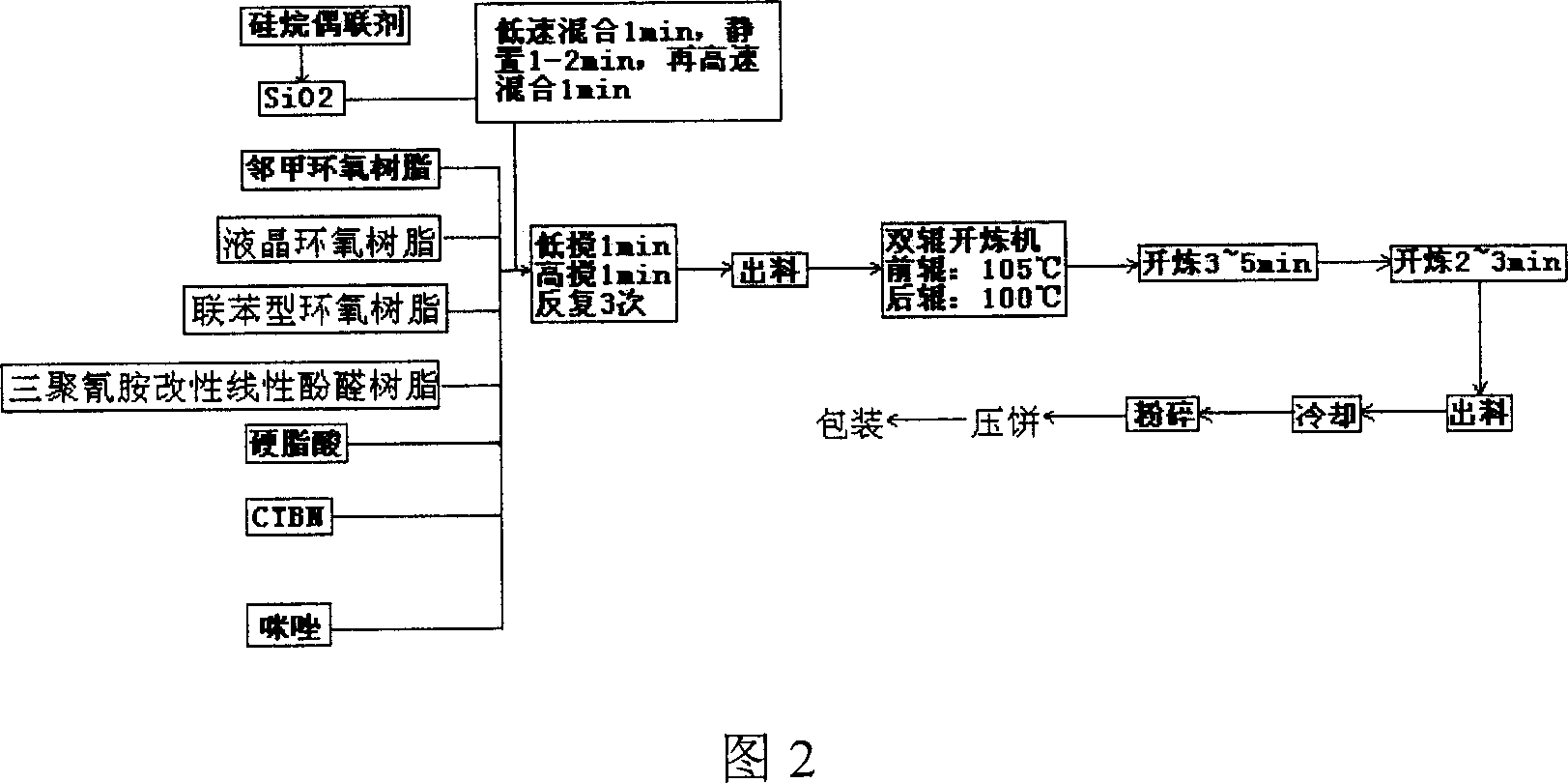

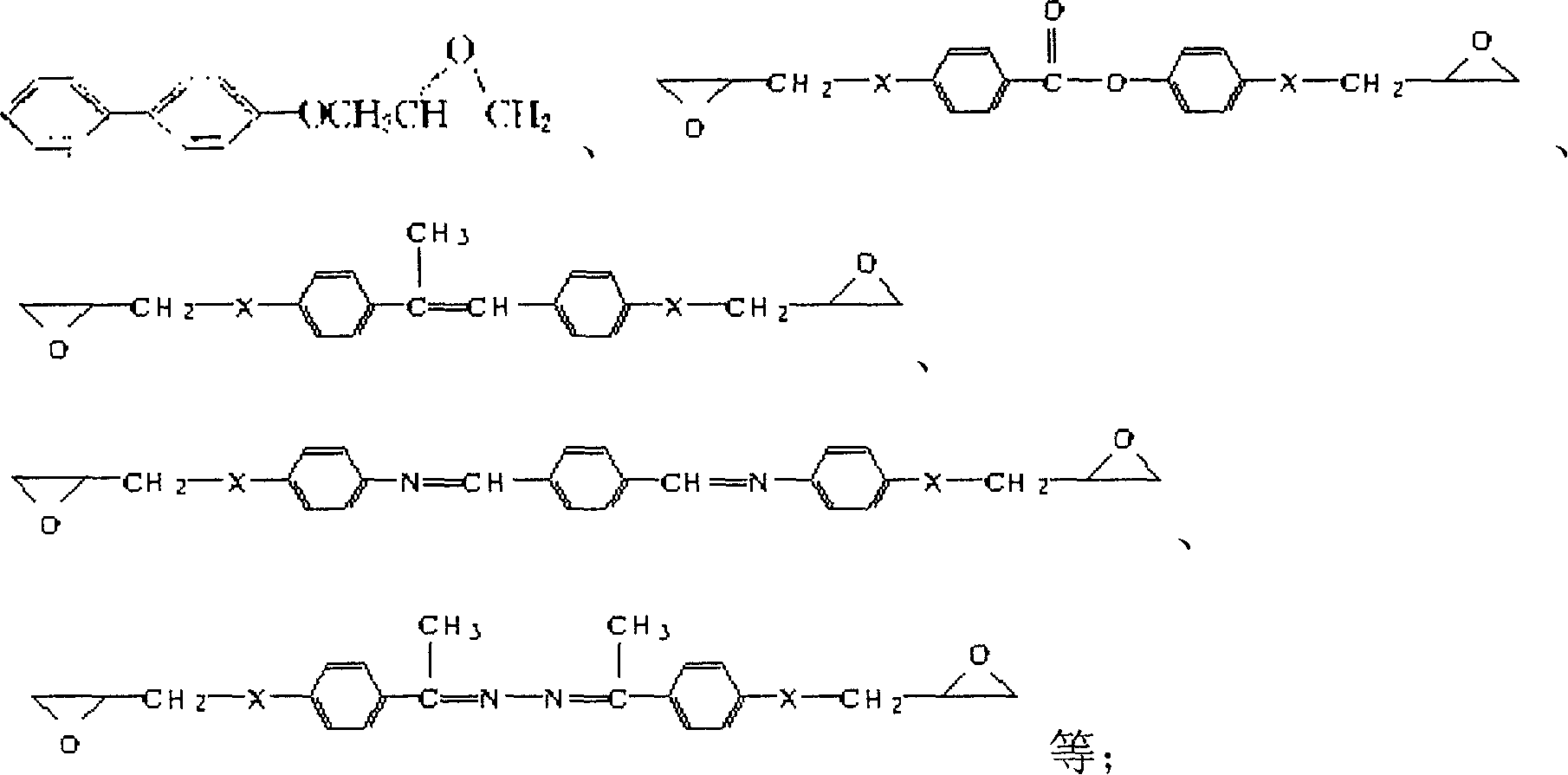

Epoxy-resin mould plastic for packing IC circuit and its production

InactiveCN101029165AHigh glass transition temperatureReduce melt viscositySemiconductor/solid-state device detailsSolid-state devicesEpoxyThermal expansion

An epoxy resin mold plastic and its production are disclosed. The mold plastic consists of liquid-crystal epoxy resin, methyl-phenolic epoxy resin, epoxy resin containing biphenyl unit structure, melamine modified linear phenolic resin, silicone micro-powder, imidazo curing improver, toughening agent and silane coupling agent. The process is carried out by treating silicone micro-powder in mixer by coupling agent for 2-5mins, adding into other components, mixing for 3-5mins, melt milling at 95-135 degree for 3-5mins, cooling, crushing, mesh screening, pressing into material cake and storing below 6degree. Its advantages include low thermal expansion coefficient, excellent heat and fire resistances, better toughness and fluidity, no phosphor, no antimony and environmental pollution. It can be used to pack large-scale circuit and electronic devices.

Owner:GUANGDONG RONGTAI IND

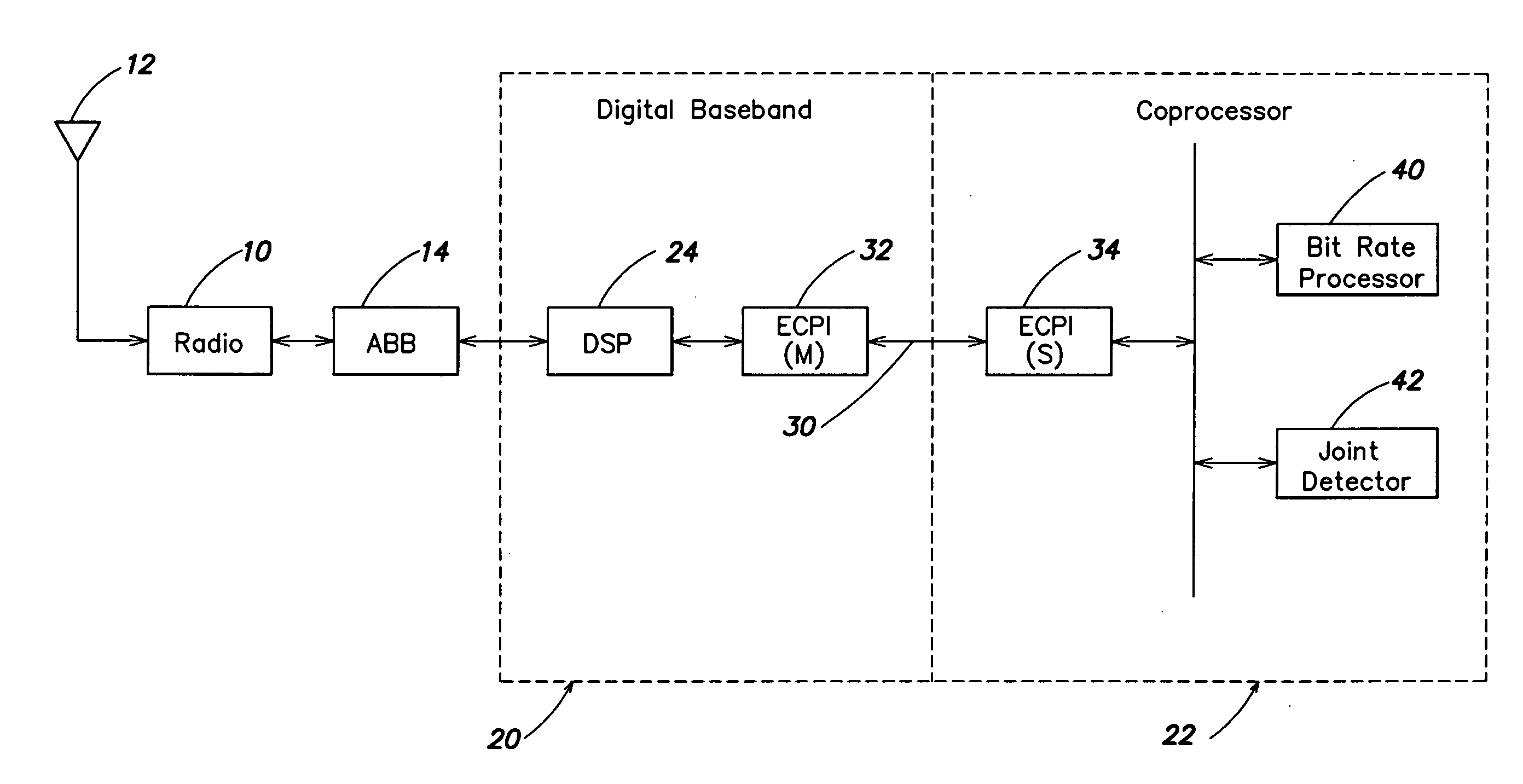

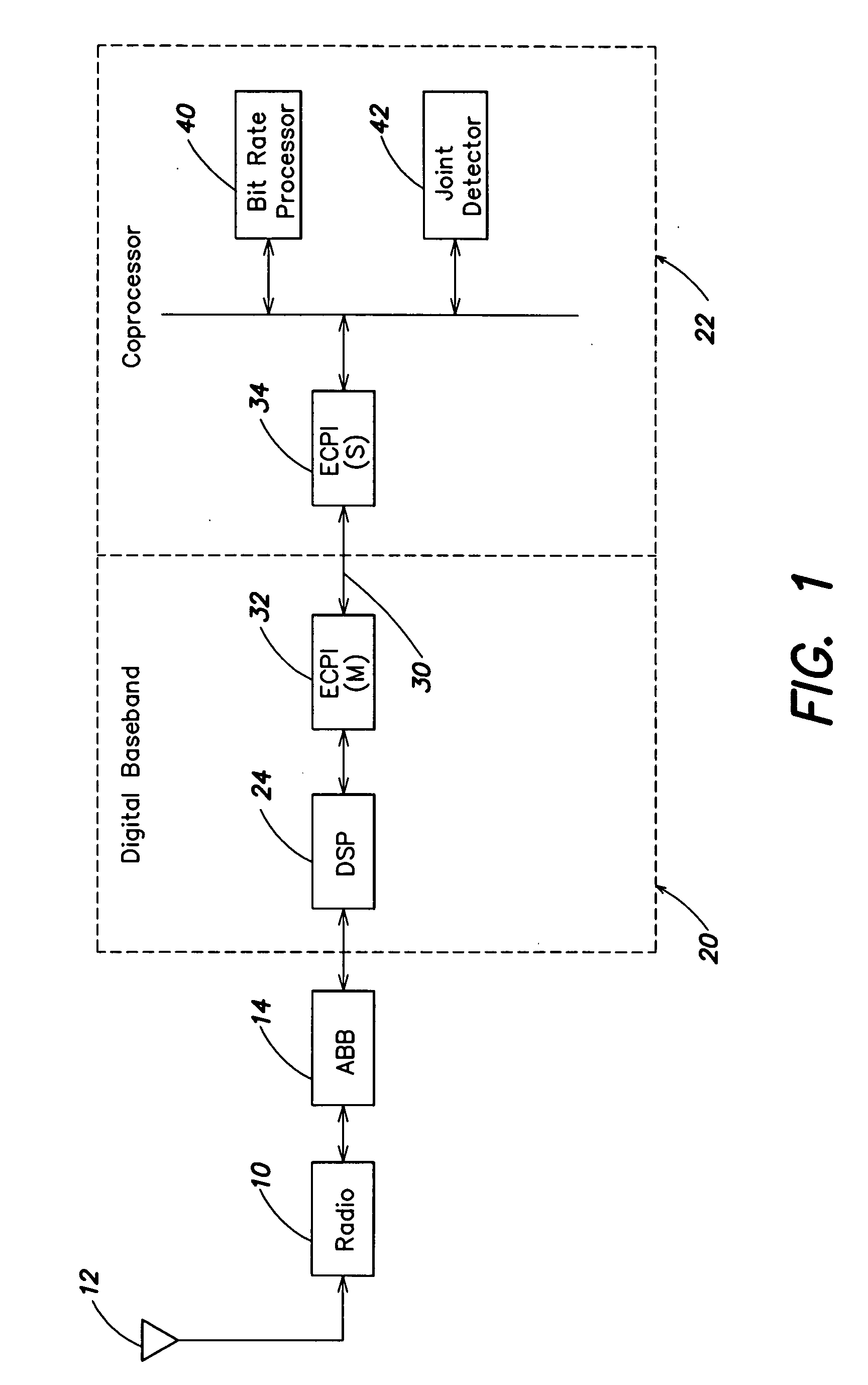

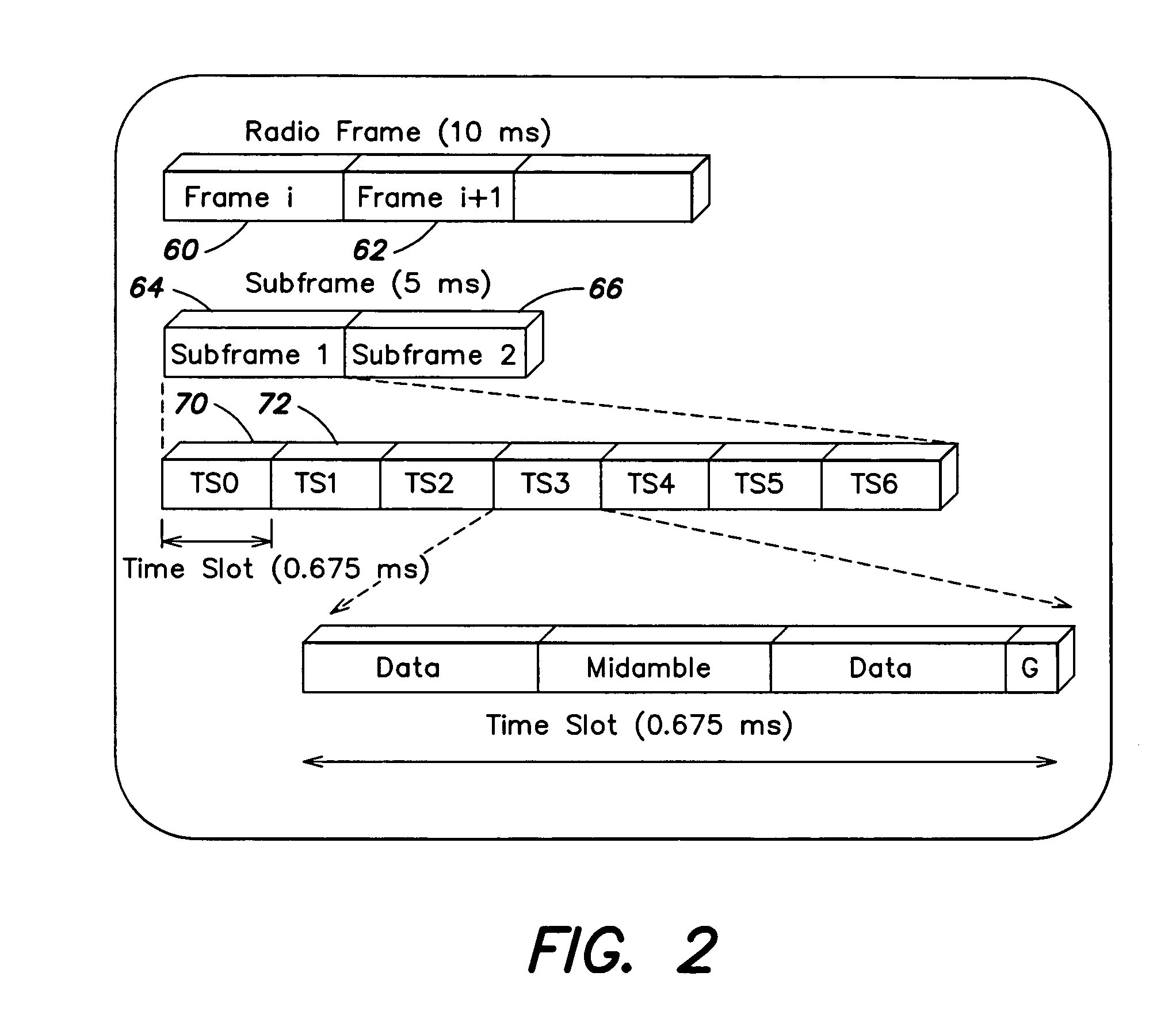

Re-Quantization in downlink receiver bit rate processor

ActiveUS20080081575A1Transmission systemsFrequency-division multiplex detailsChannel dataComputer science

A bit rate processor in a wireless system includes a front end processor to process physical channel data and to generate encoded transport channel data, a transport channel buffer to hold the encoded transport channel data, and a back end processor to process the encoded transport channel data from the transport channel buffer and to generate decoded transport channel bits. The front end process may include a frame buffer that receives the physical channel data, a first stage to de-map the physical channel data from the frame buffer, an intermediate frame buffer that receives the de-mapped physical channel data from the first stage, and a second stage to process the de-mapped physical channel data and to provide the encoded transport channel data. The back end processor may include a third stage, including a scaling circuit to scale the encoded transport channel data, a decoder to decode the scaled transport channel data and a CRC checker to provide the decoded transport channel bits, and an output buffer to receive the decoded transport channel bits.

Owner:MEDIATEK INC

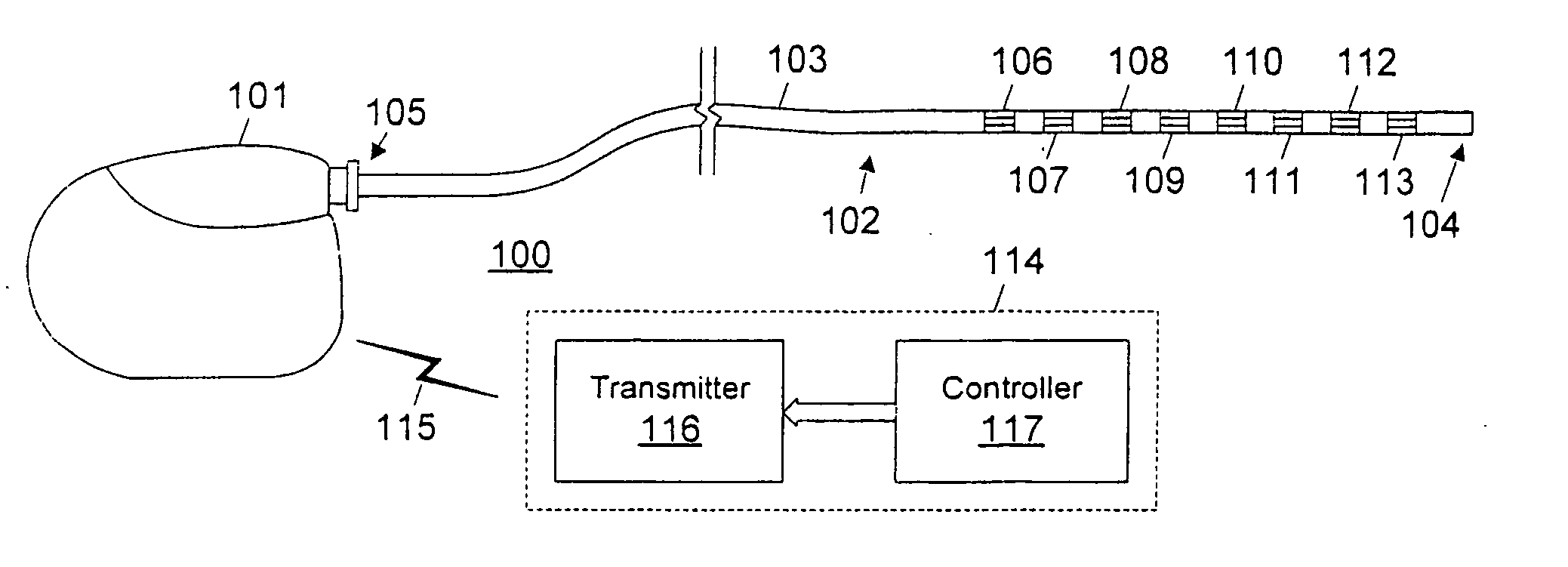

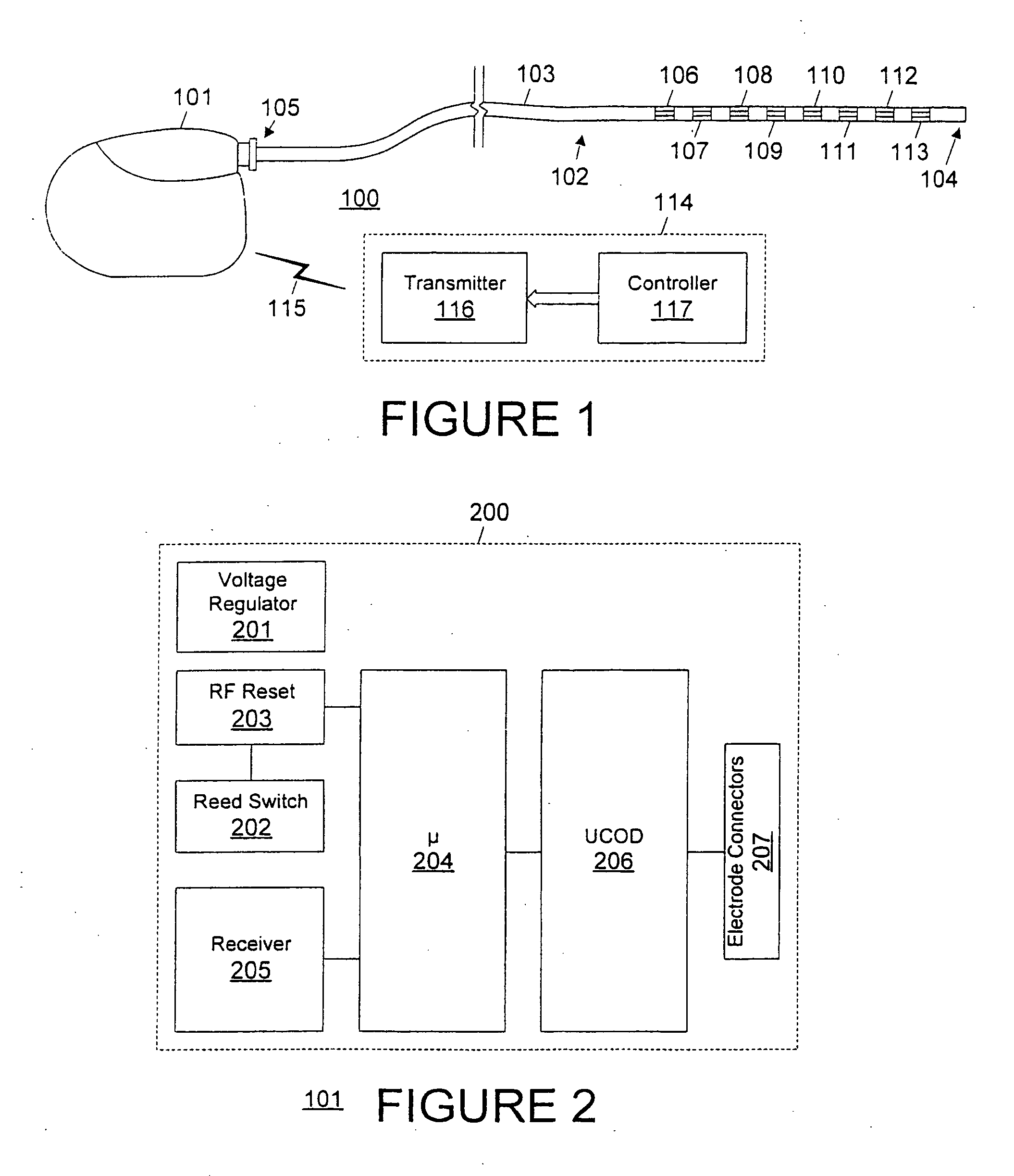

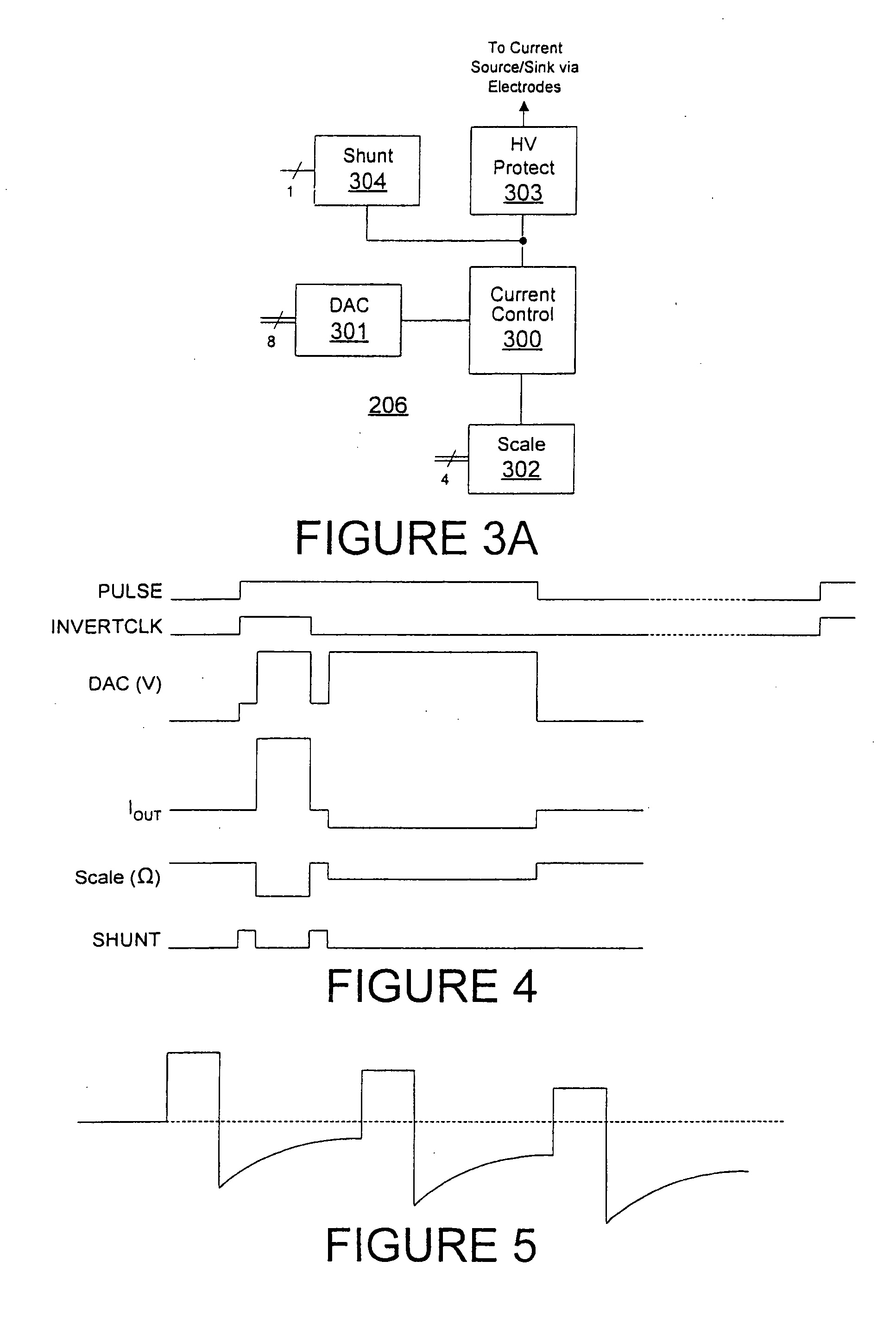

Systems and methods for providing amplitude selection for pulse generation

Owner:ADVANCED NEUROMODULATION SYST INC

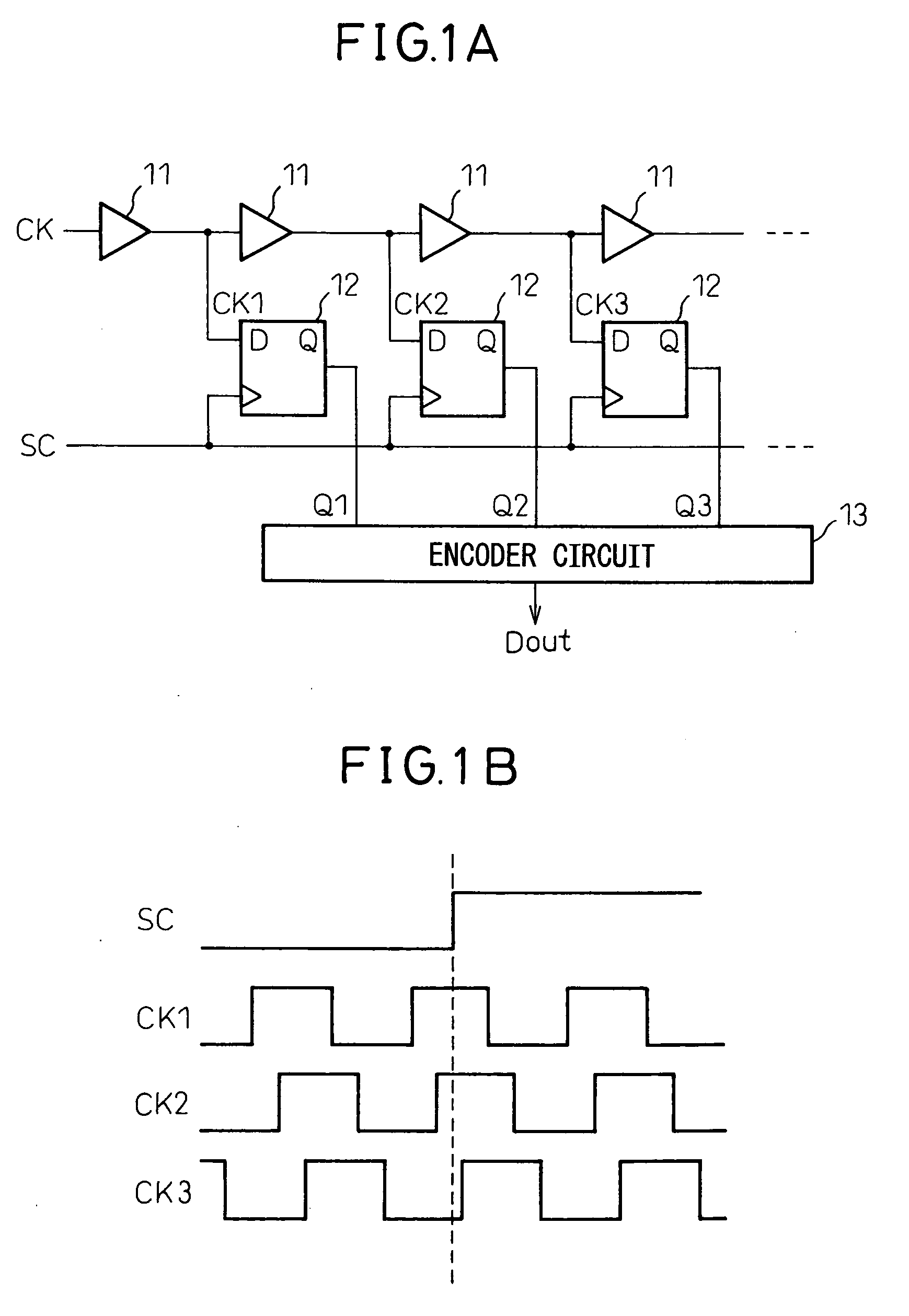

Time-to-digital converter

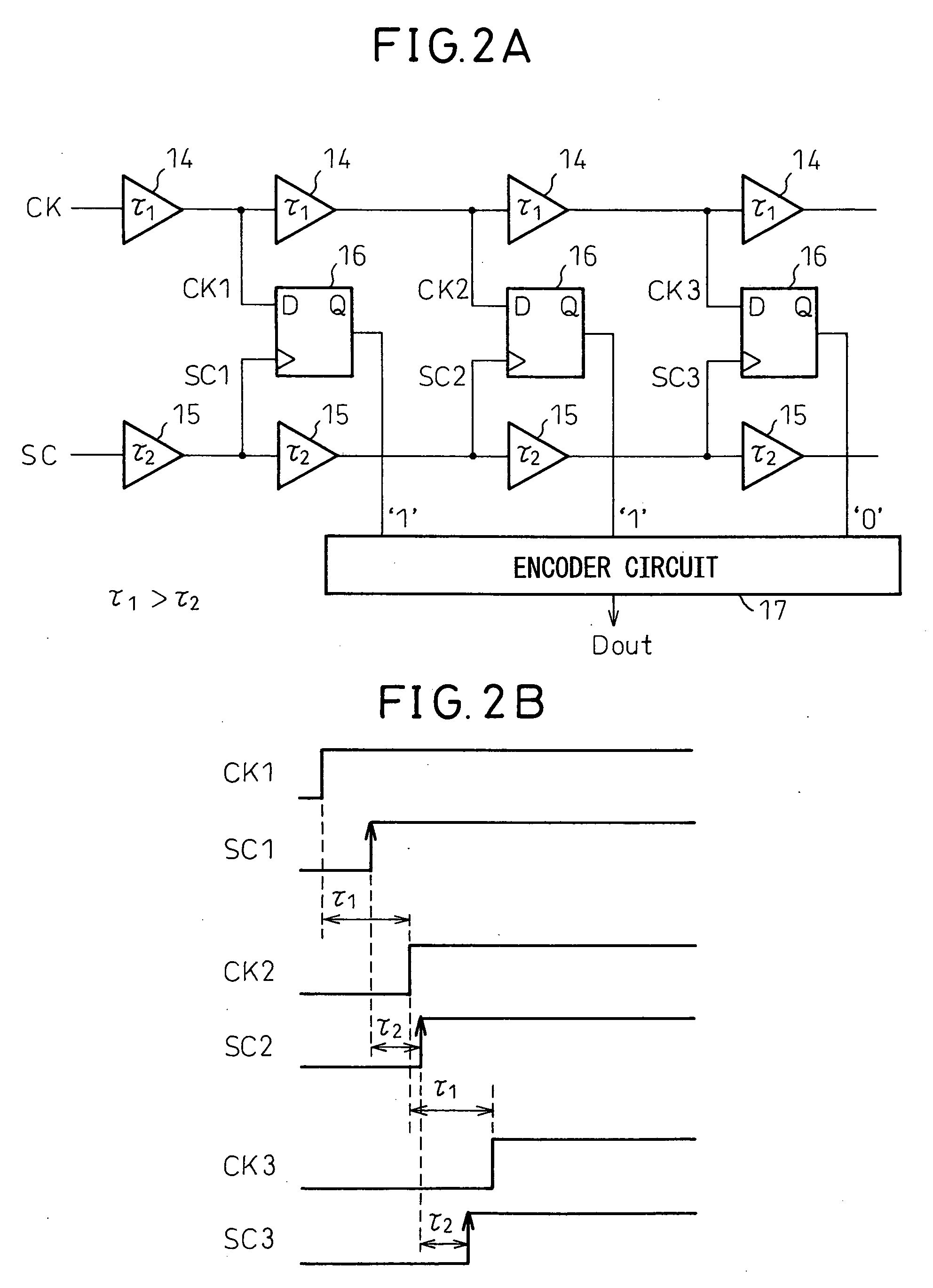

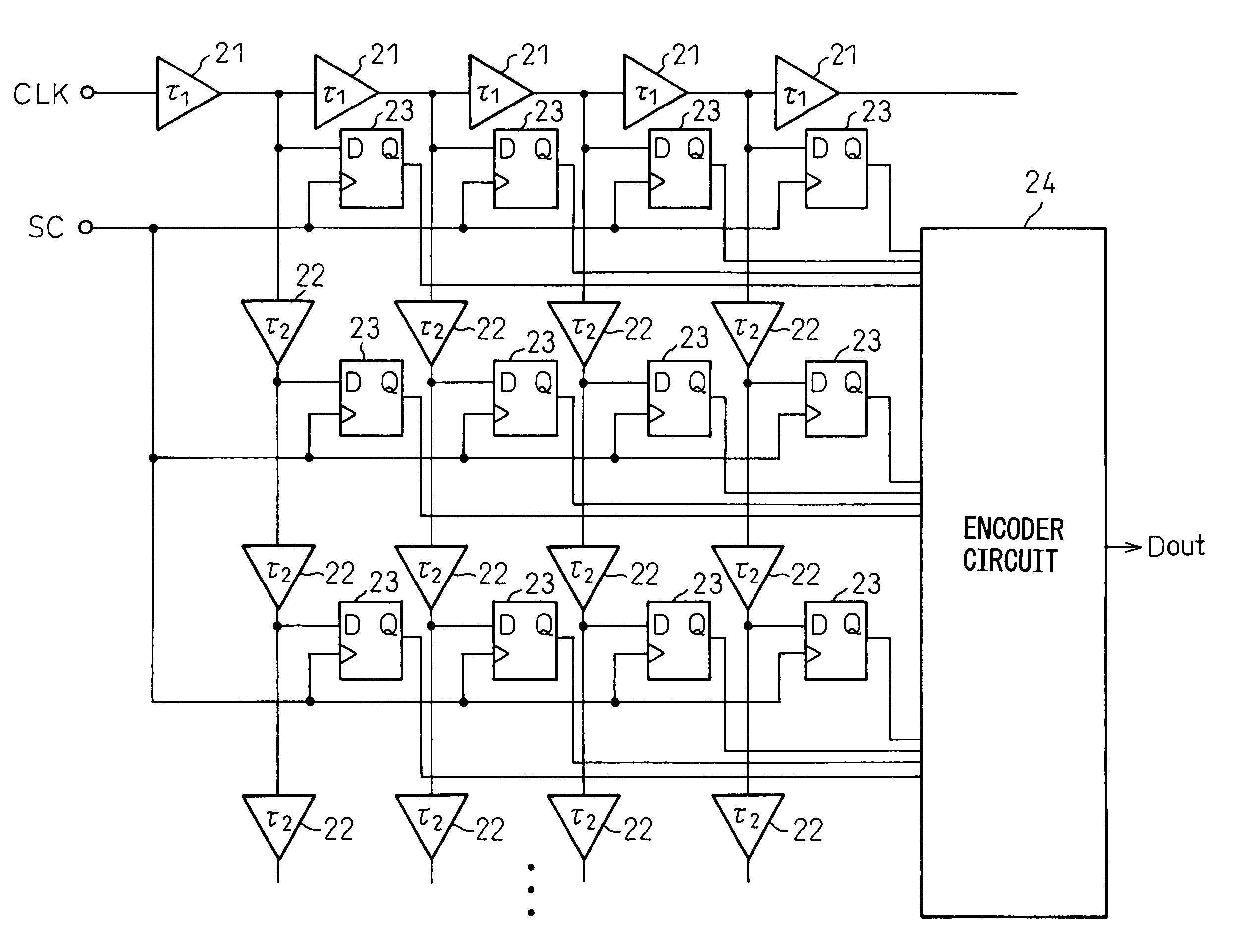

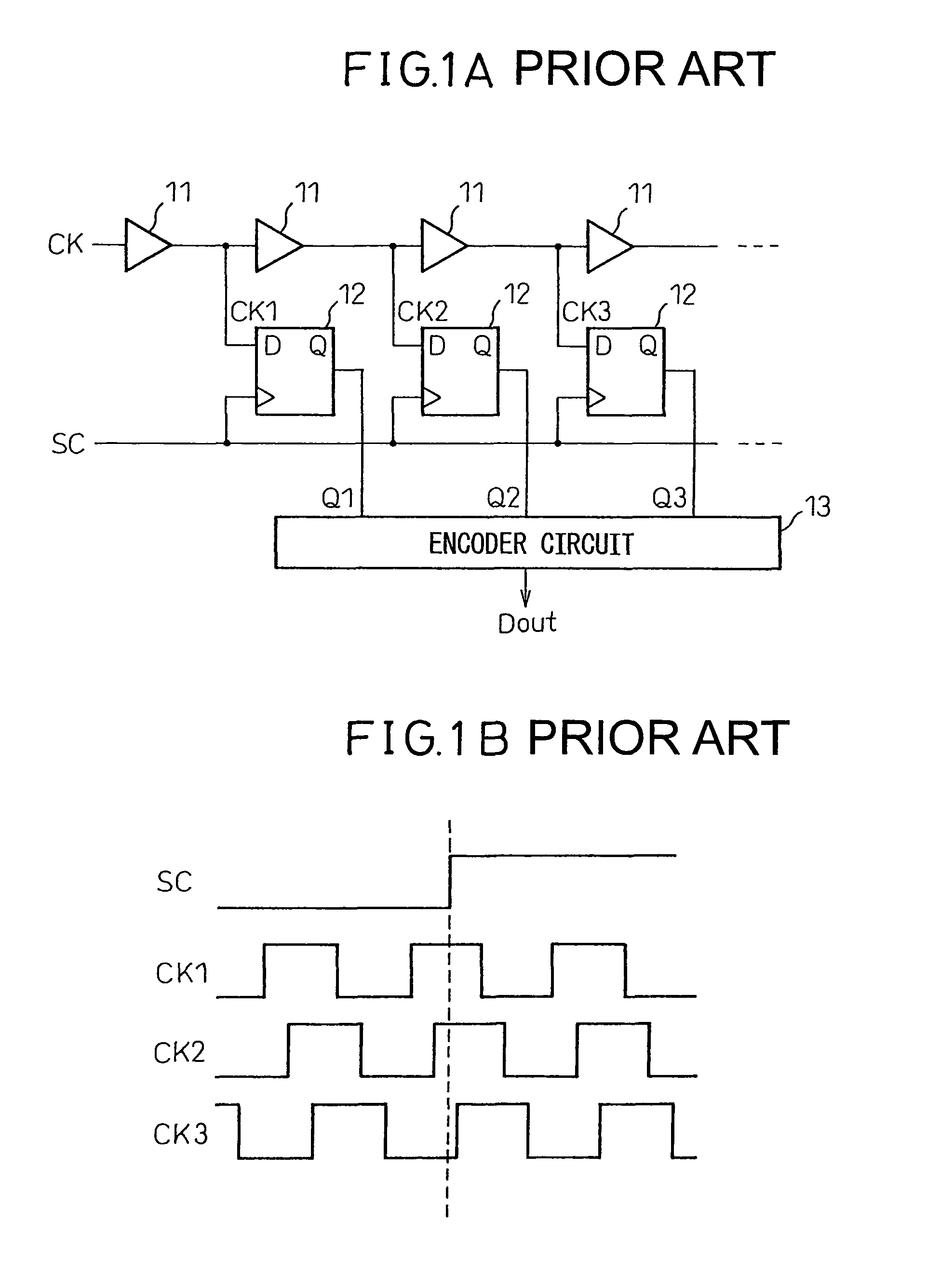

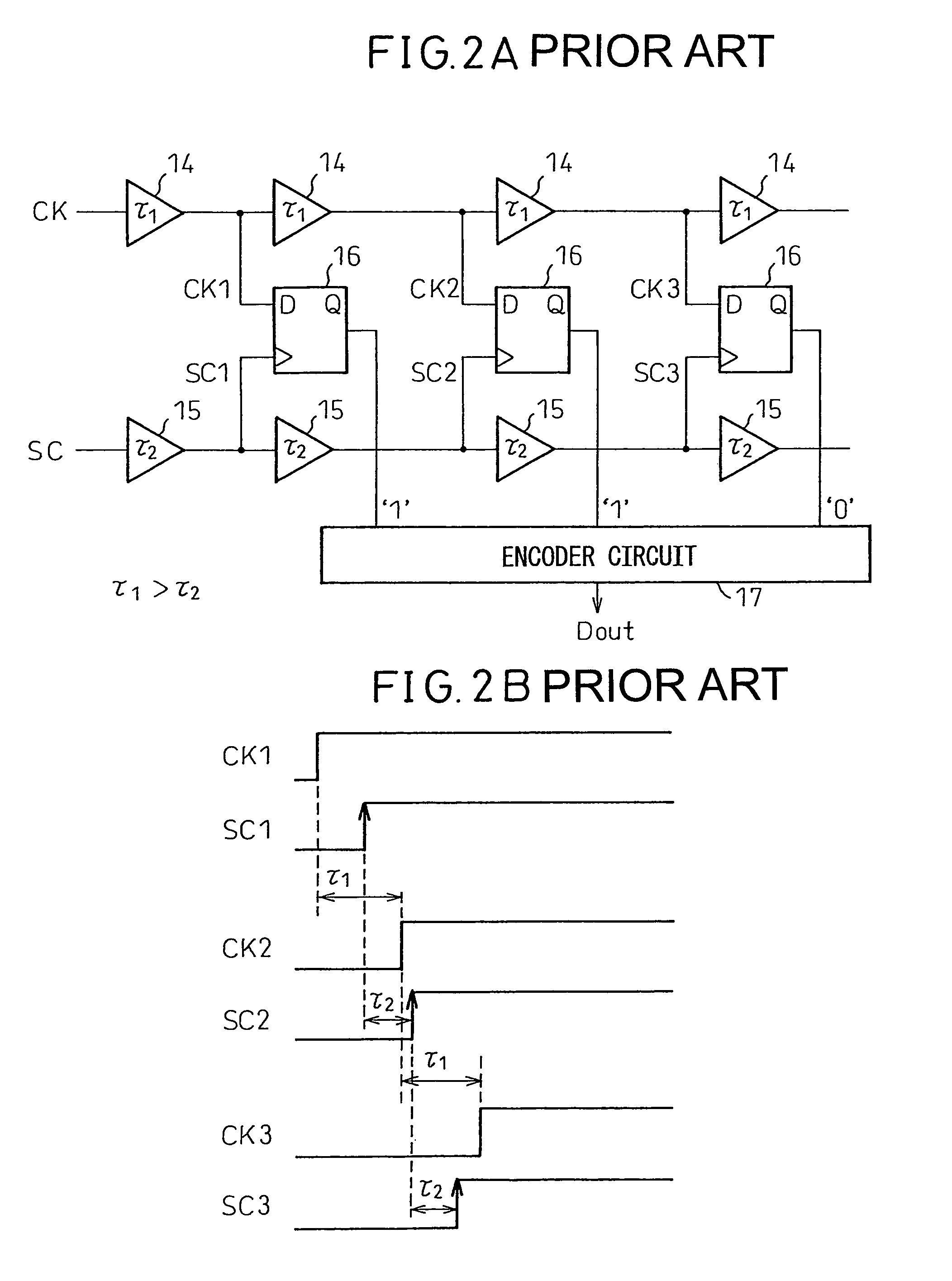

InactiveUS20090225631A1Reduce circuit sizeHigh resolutionAnalogue/digital conversionElectric signal transmission systemsDigital down converterEngineering

A TDC circuit having a small scale circuit and high resolution is disclosed, which is a time-to-digital converter that detects a phase with respect to a reference clock of a signal to be measured, comprising a first delay line in which a plurality of first delay elements with a first delay amount is connected in series, a second delay line group that is connected to a plurality of connection nodes of the first delay line or an input node in the first stage and in which at least one or more second delay elements with a second delay amount different from the first delay amount are connected in series, a plurality of judgment circuits that judge whether the changing edge of the signal to be measured is advanced or delayed with respect to the changing edges of a delayed clock output from the first delay element and the second delay element, and an operation circuit that calculates a phase with respect to the reference clock of the changing edge of the signal to be measured from the judgment results, wherein a difference between the first delay amount and the second delay amount is smaller than the first delay amount and the second delay amount.

Owner:SEMICON TECH ACADEMIC RES CENT

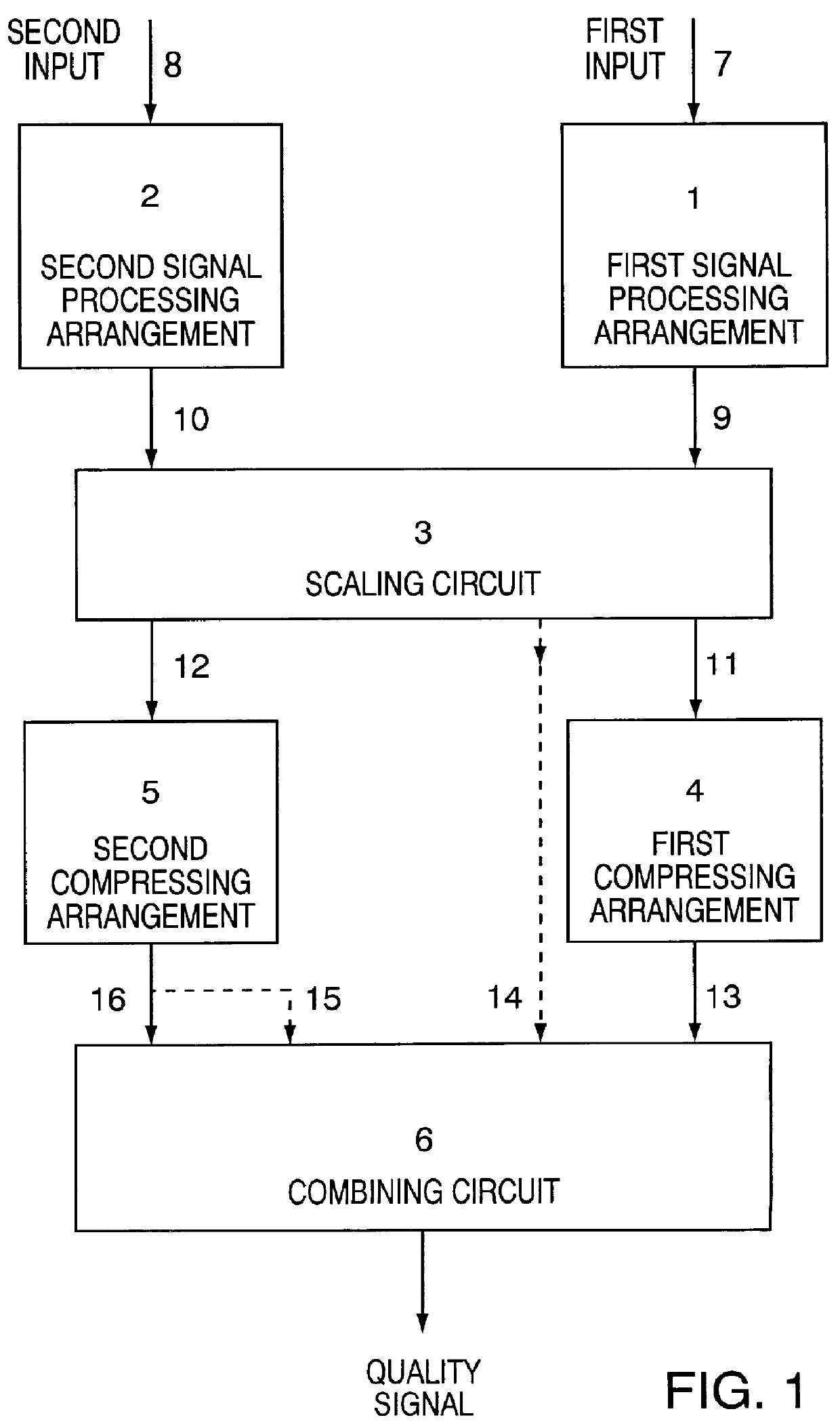

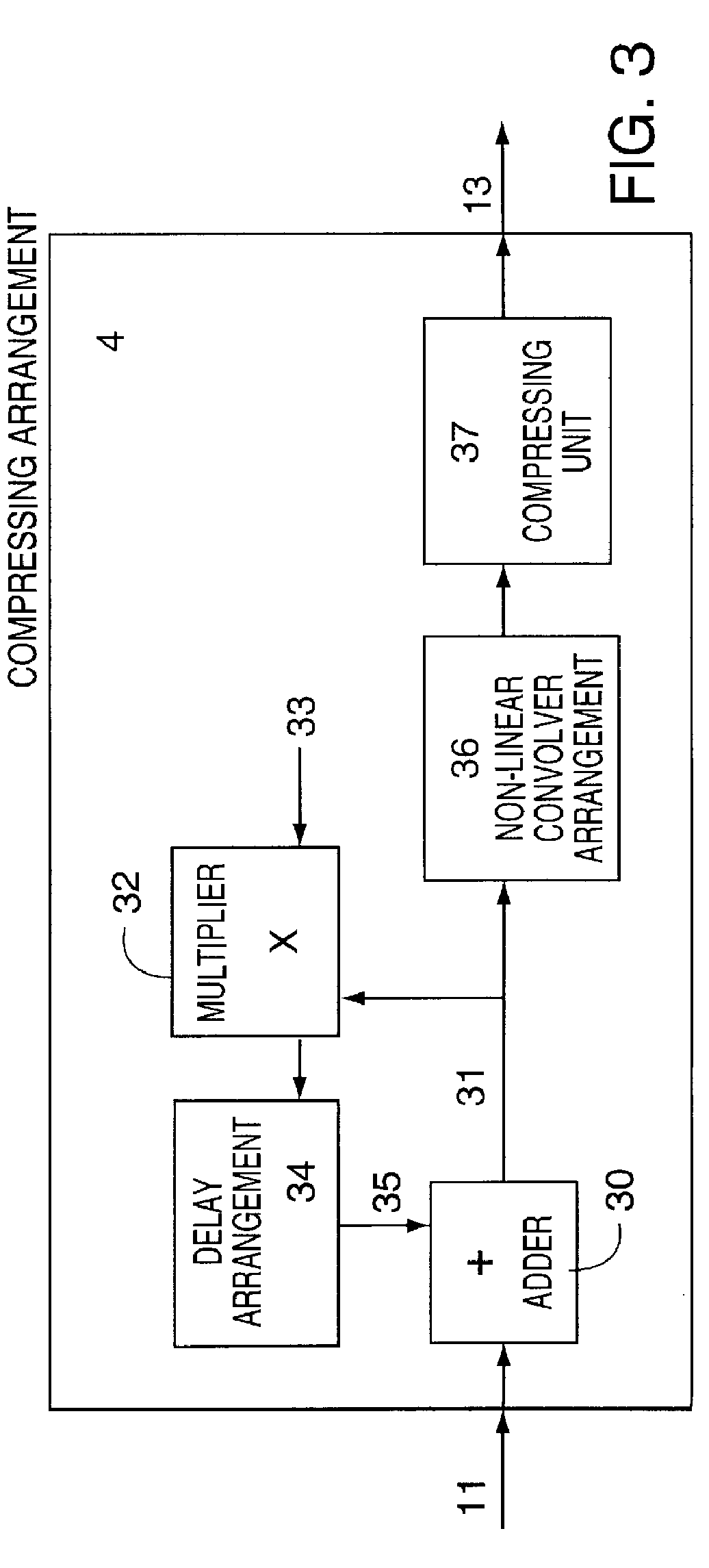

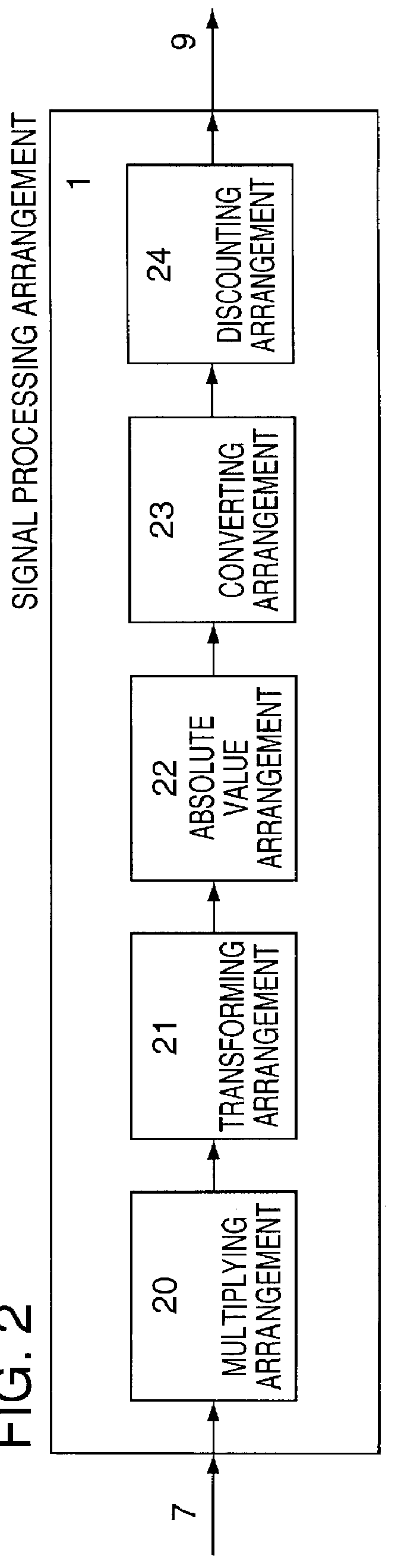

Signal quality determining device and method

InactiveUS6041294AReduce the amplitudeGood correlationNoise figure or signal-to-noise ratio measurementDigital technique networkObjective qualitySignal quality

PCT No. PCT / EP96 / 01143 Sec. 371 Date Sep. 5, 1997 Sec. 102(e) Date Sep. 5, 1997 PCT Filed Mar. 13, 1996 PCT Pub. No. WO96 / 28950 PCT Pub. Date Sep. 19, 1996A device for determining the quality of an output signal to be generated by a signal processing circuit with respect to a reference signal. The device is provided with a first series circuit for receiving the output signal and a second series circuit for receiving the reference signal. The device generates an objective quality signal through a combining circuit which is coupled to the two series circuits. Poor correlation between the objective quality and subjective quality signals, the latter which will be assessed by human observers, can be considerably improved by a differential arrangement present in the combining circuit. This arrangement determines a difference between the two series circuit signals and reduces this difference by a certain value, preferably one that is a function of a series circuit signal. Poor correlation can be improved further by disposing a scaling circuit, between the two series circuits, for scaling at least one series circuit signal. Furthermore, the quality signal can also be scaled as a function of the scaling circuit.

Owner:KONINK KPN NV

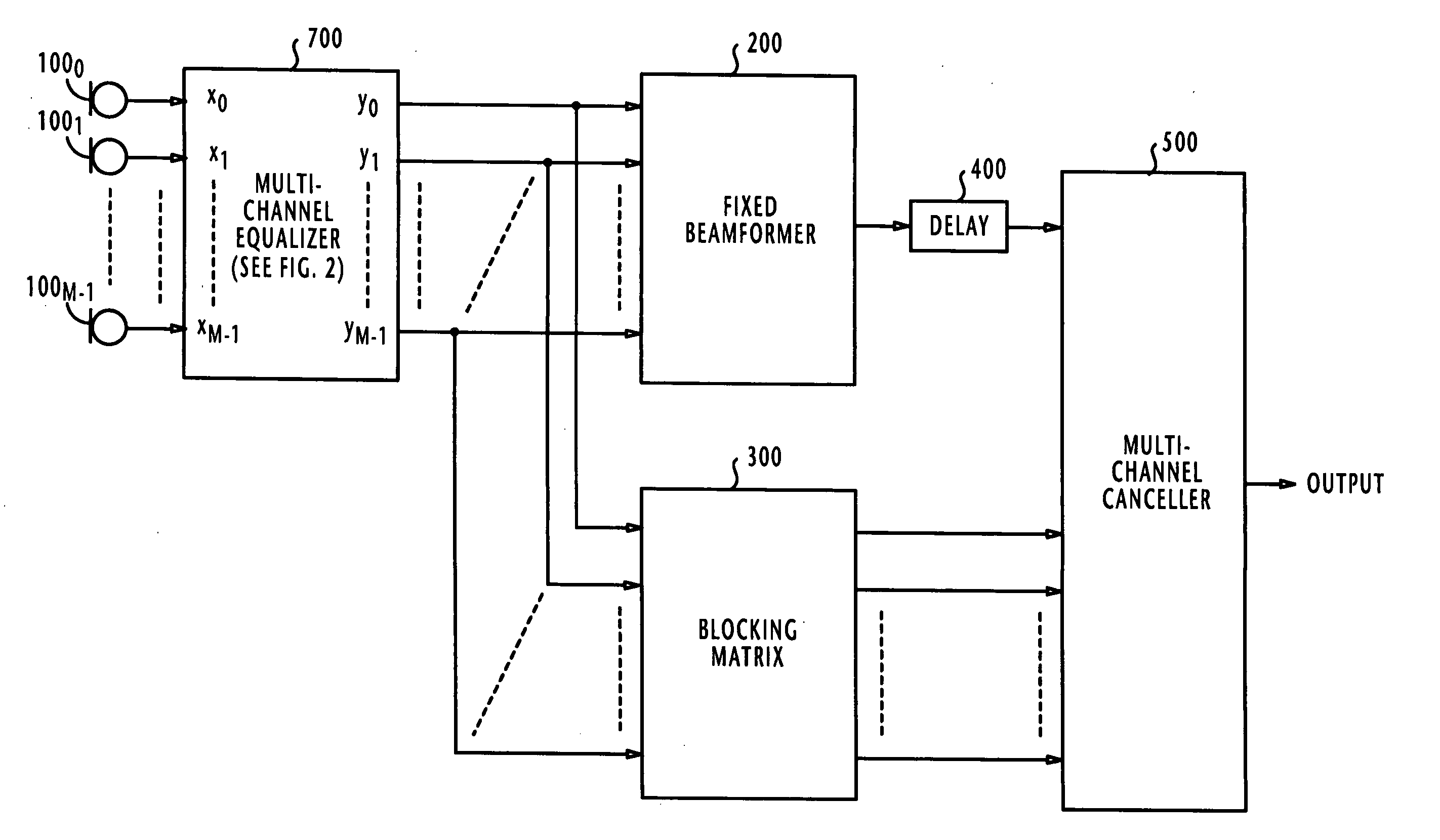

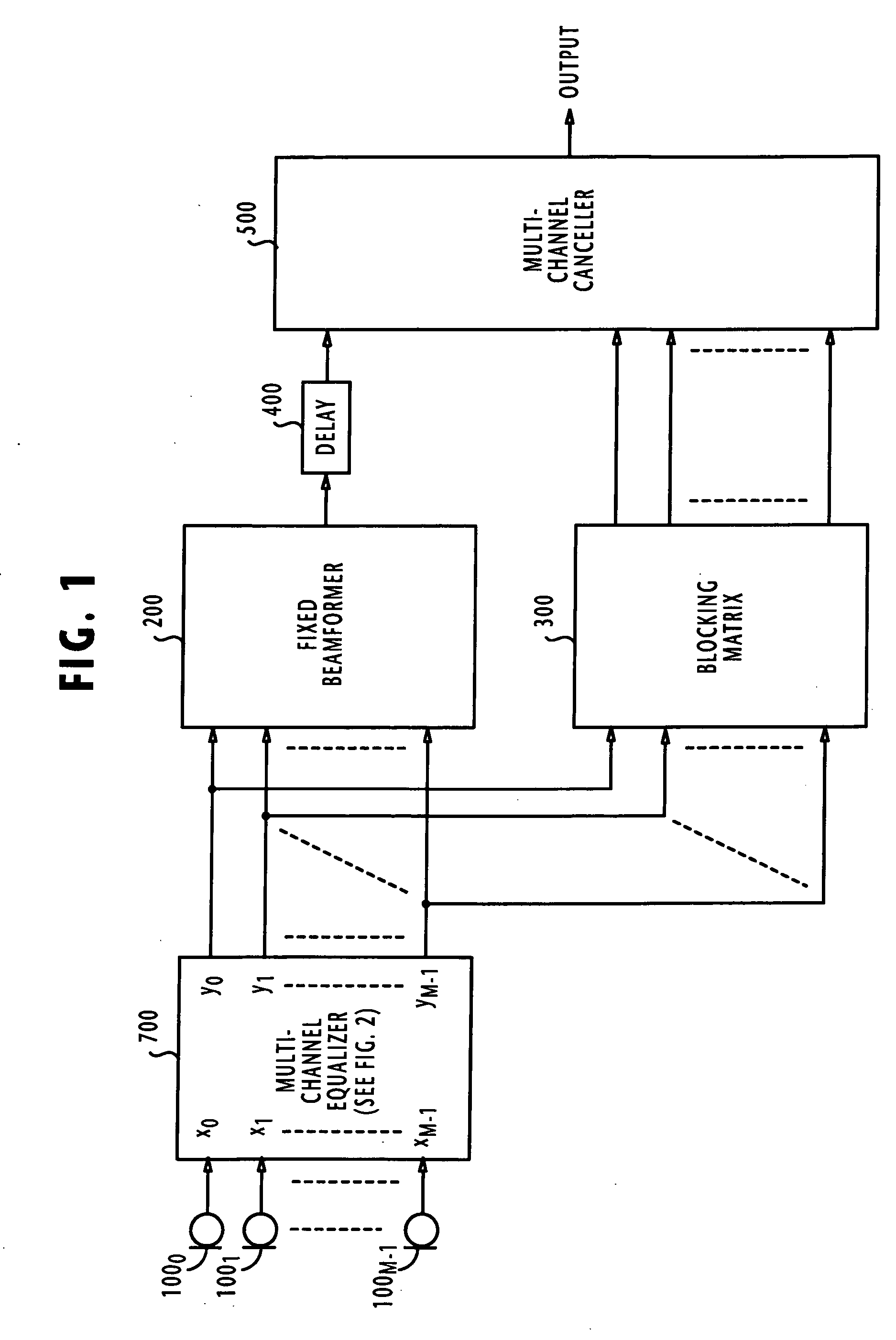

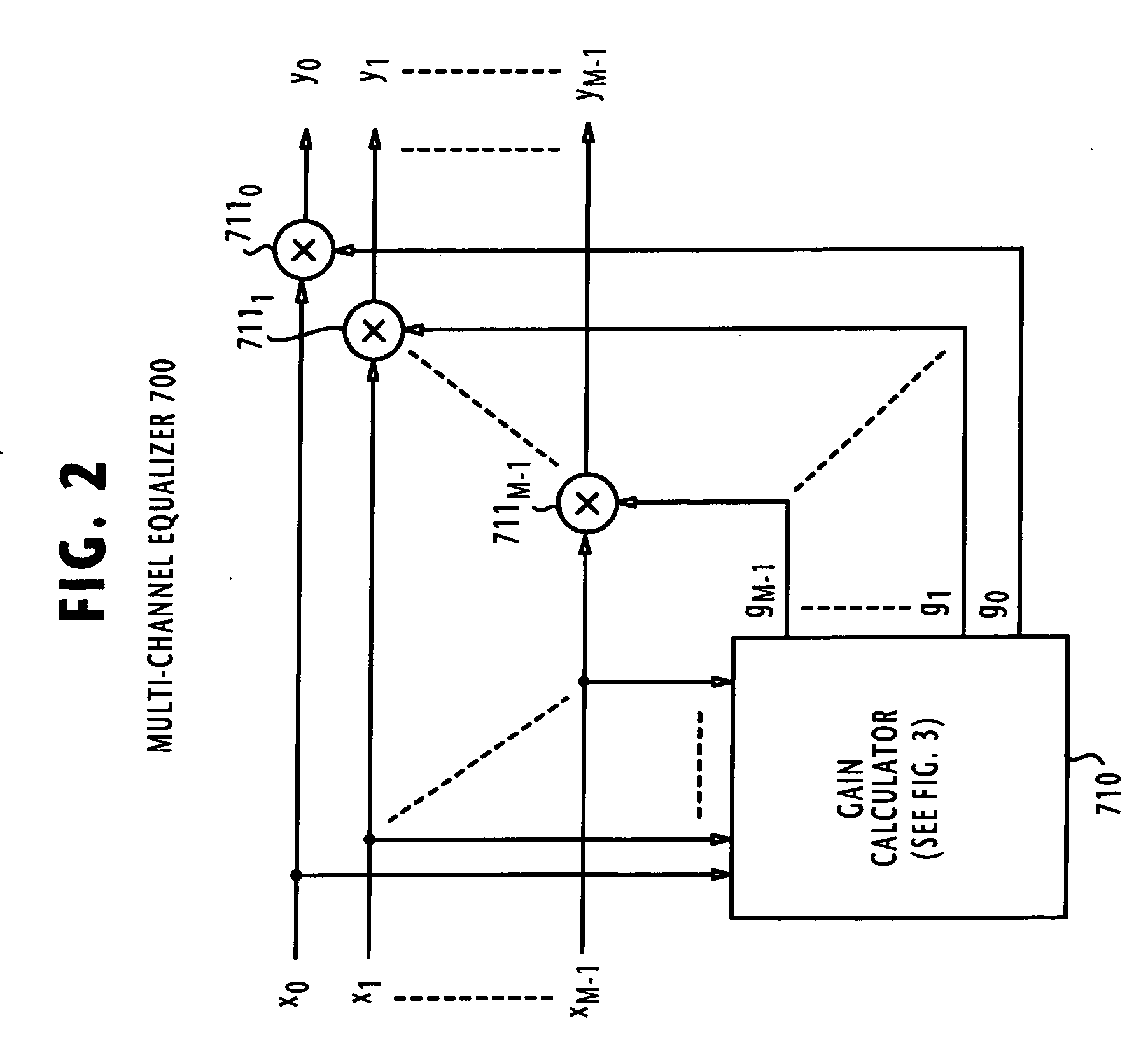

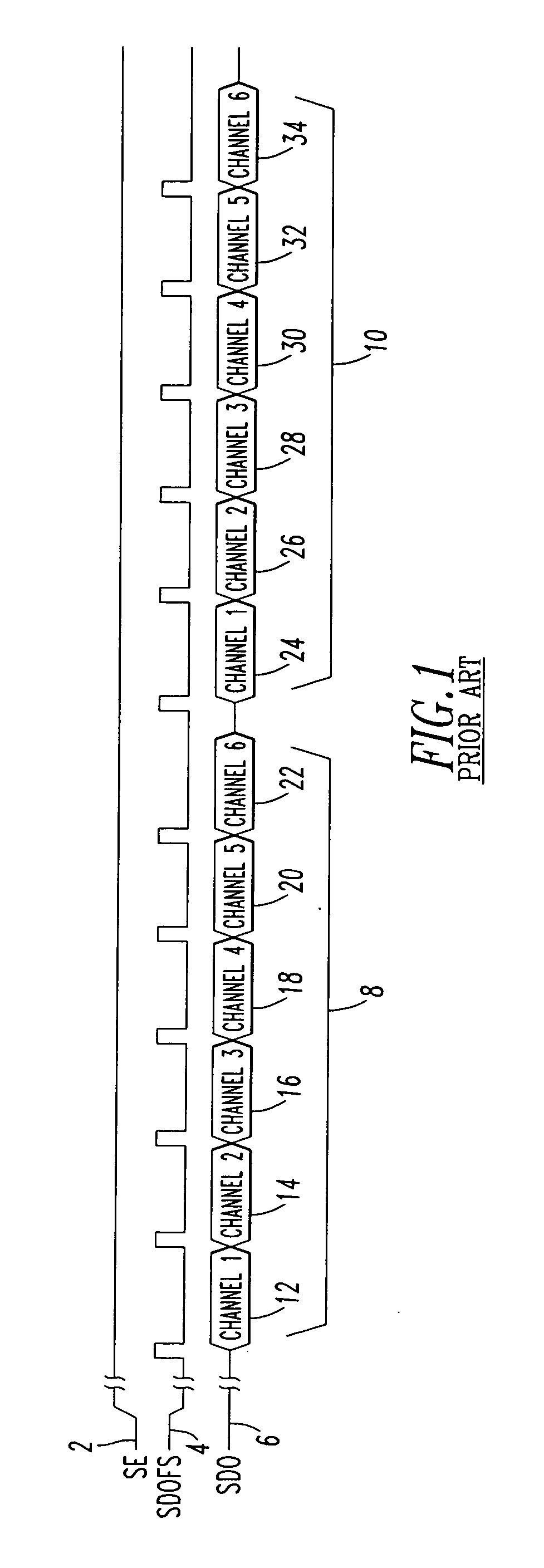

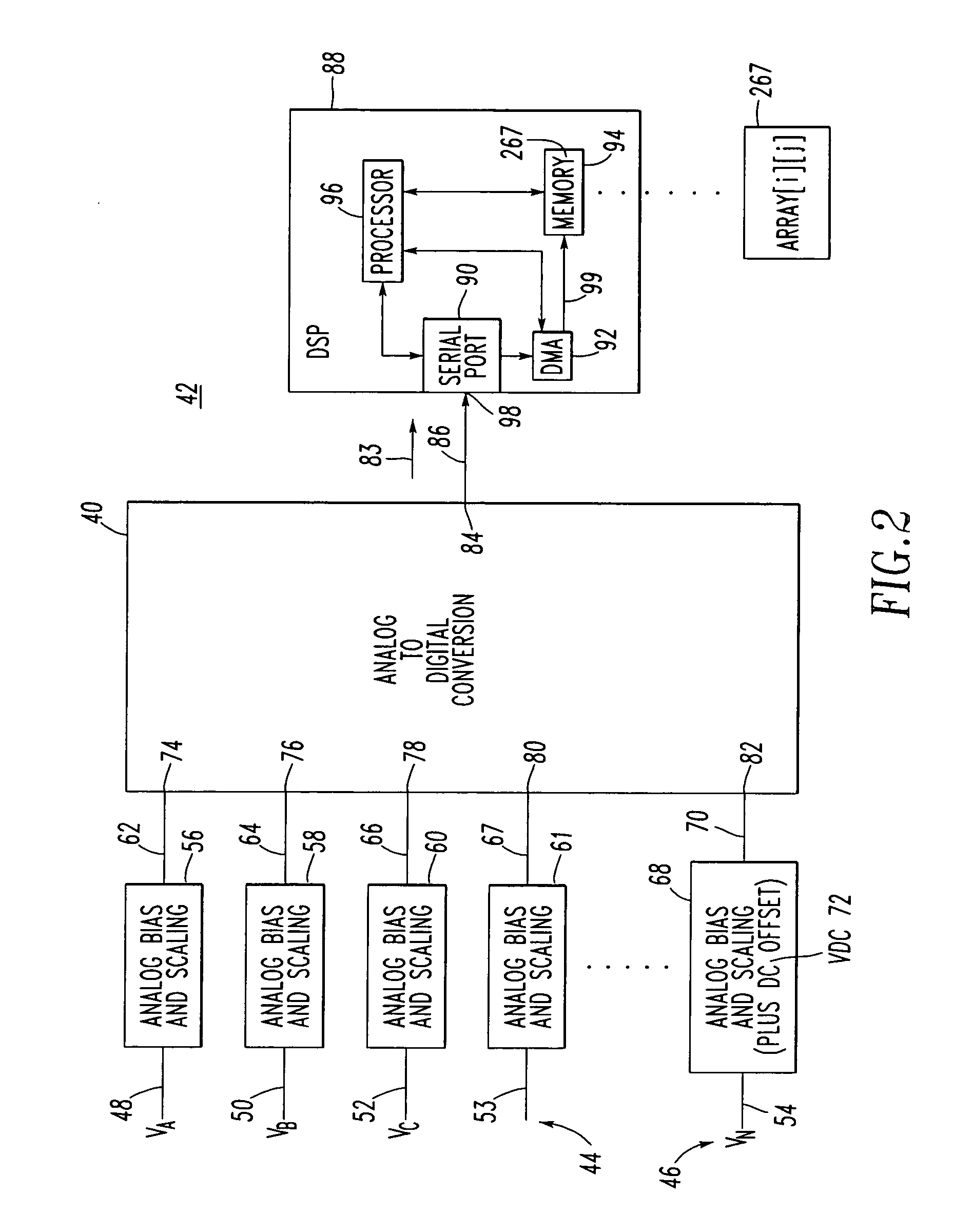

Signal processing system and method for calibrating channel signals supplied from an array of sensors having different operating characteristics

In a signal processing system, a set of channel signals from an array of sensors of different operating characteristics are processed in calibration circuitry that calculates individual average values of the channel signals and calculates an average of the individual average values of channel signals as a reference value. Reciprocal calculators calculate reciprocal values of the individual average values of the channel signals. Scaling circuitry scales the reciprocal values by the reference value to produce a set of amplitude calibration signals and scales the channel signals by the calibration signals respectively. As a result, the channel signals are normalized by their own average values and scaled by the reference value to produce a set of calibrated channel signals.

Owner:NEC CORP

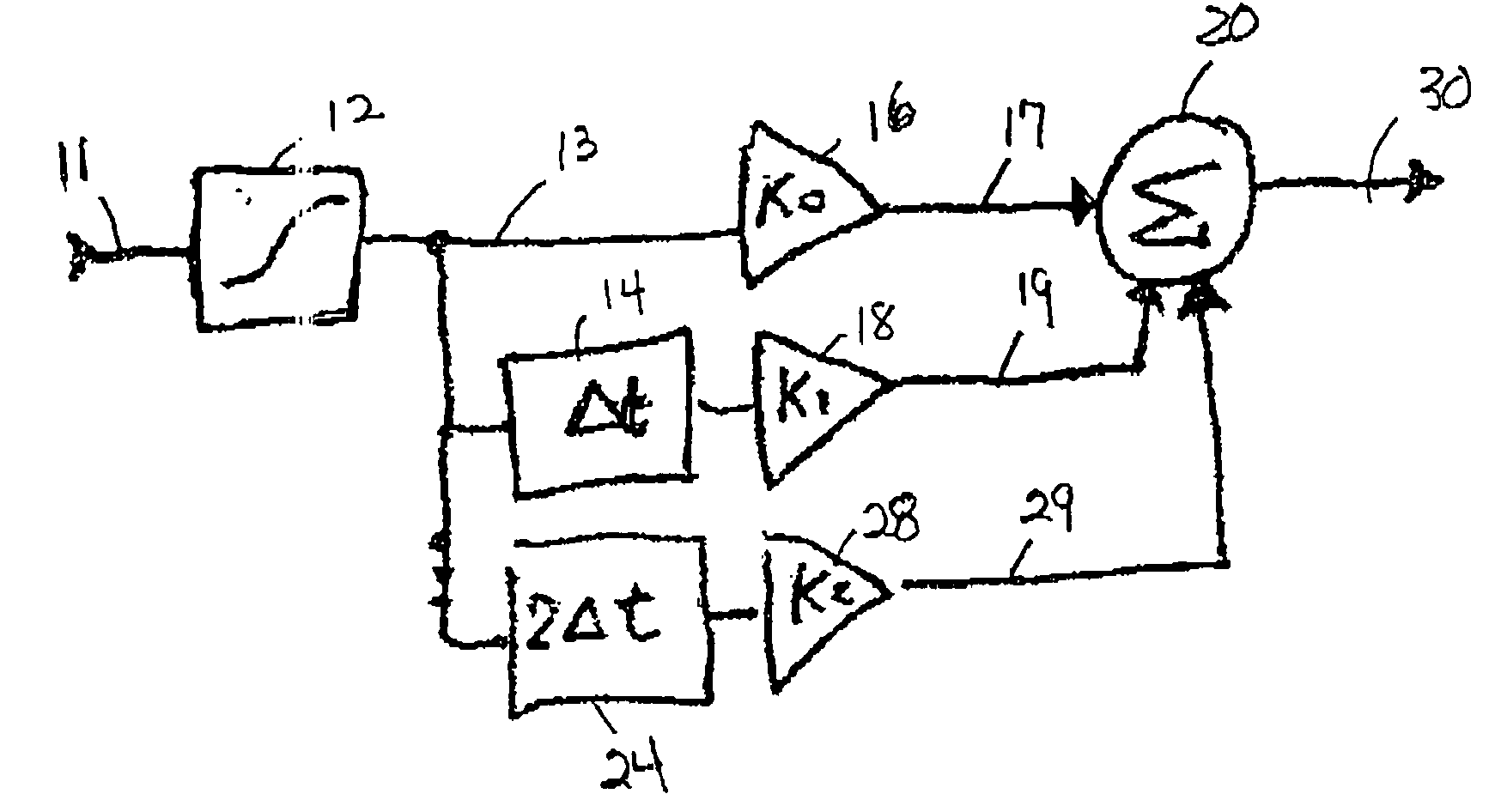

Method and apparatus for creating variable delay

InactiveUS20050168258A1Large delay rangeSingle output arrangementsTime-delay networksFall timeImage resolution

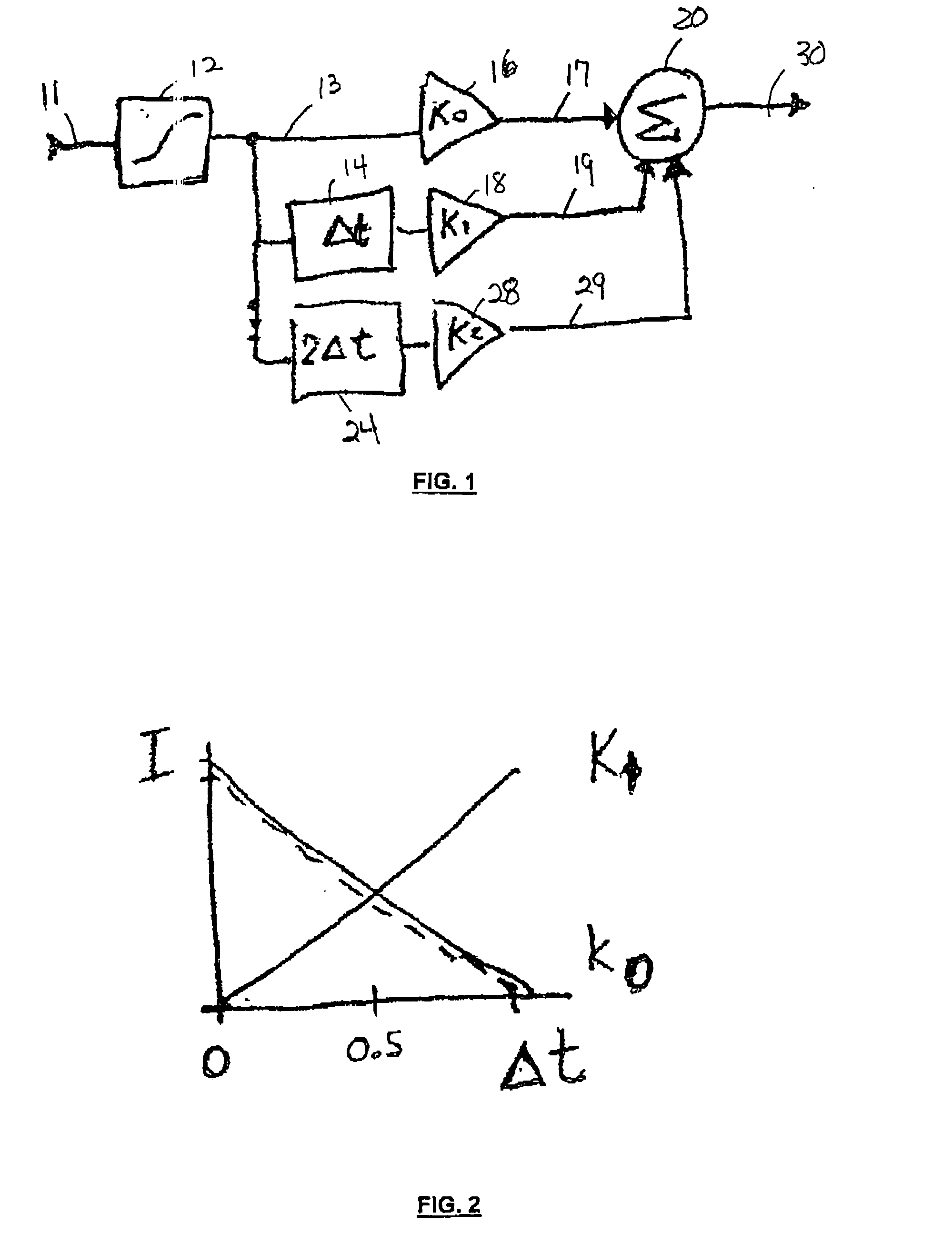

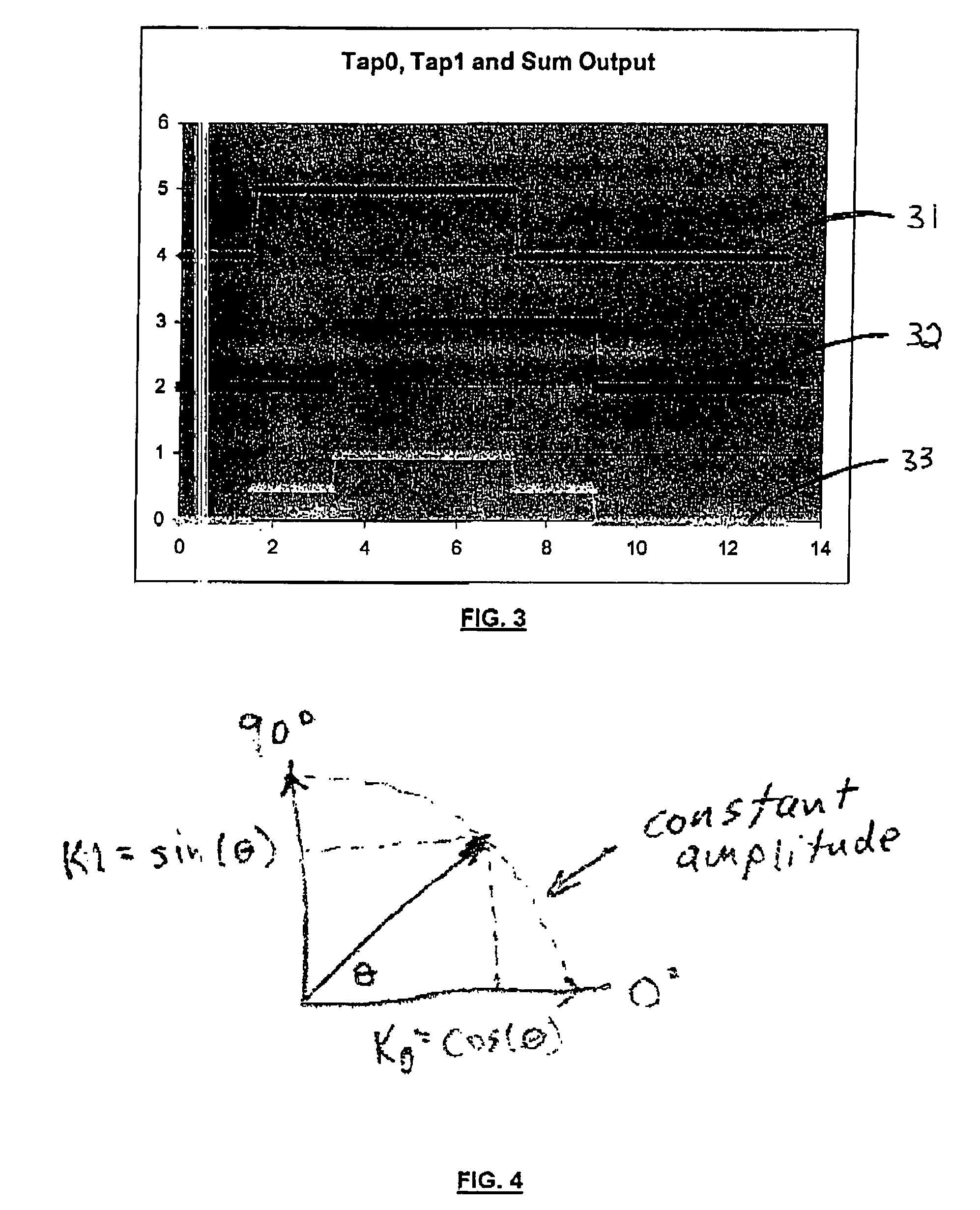

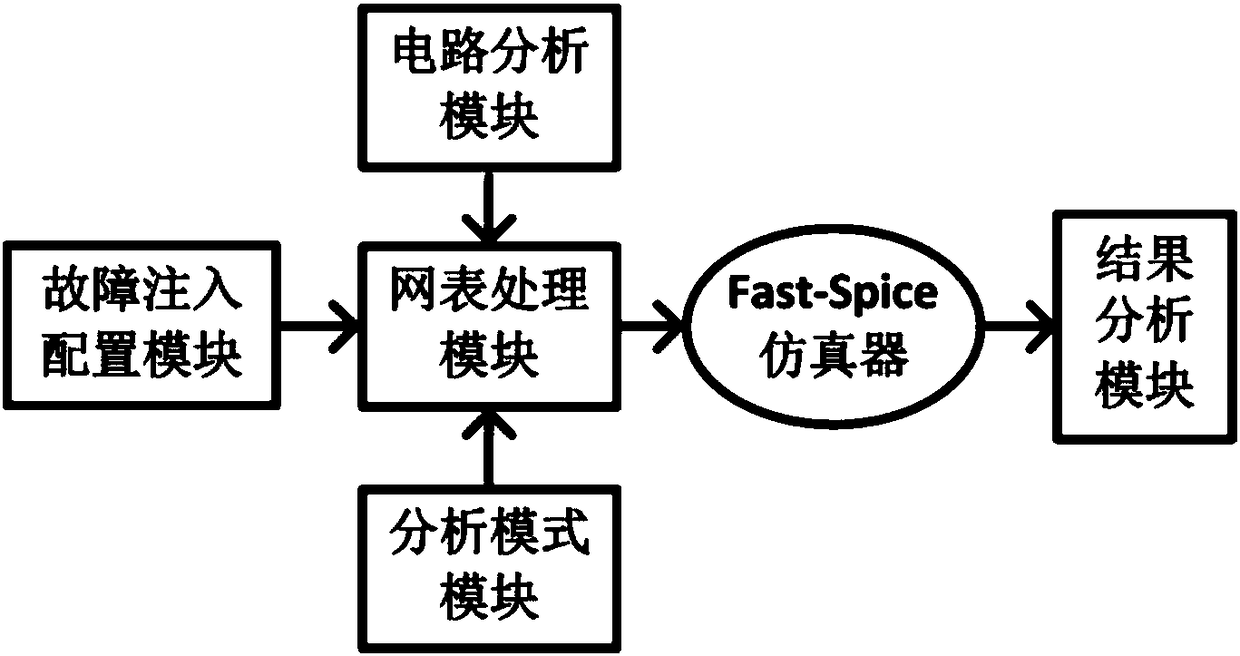

Disclosed herein is a method and apparatus used to create variable delay output from a high-speed trigger input signal. A variable delay generation circuit includes a preconditioning circuit, operative to provide a preconditioned signal in response to an input signal. At least one delay tap path is coupled to the preconditioned signal, and is operative to provide a delayed version of the preconditioned signal. The delay path includes a delay element and a scaling circuit. A summing circuit is coupled to the at least one delay tap path and preconditioned signal, and is operative to provide an output signal exhibiting variable delay characteristics in response to the preconditioned signal and the delayed version of the preconditioned signal. The delayed version of the preconditioned signal may be provided by an elongated signal trace between the preconditioning circuit and the delay tap path. Through the combination of summing delayed and scaled versions of the input signal and the preconditioning of the input signal to have required rise / fall times and shapes, high-frequency variable delay is implemented that provides for fast, stable settings with consistent delay range and resolution.

Owner:SYNTHESYS

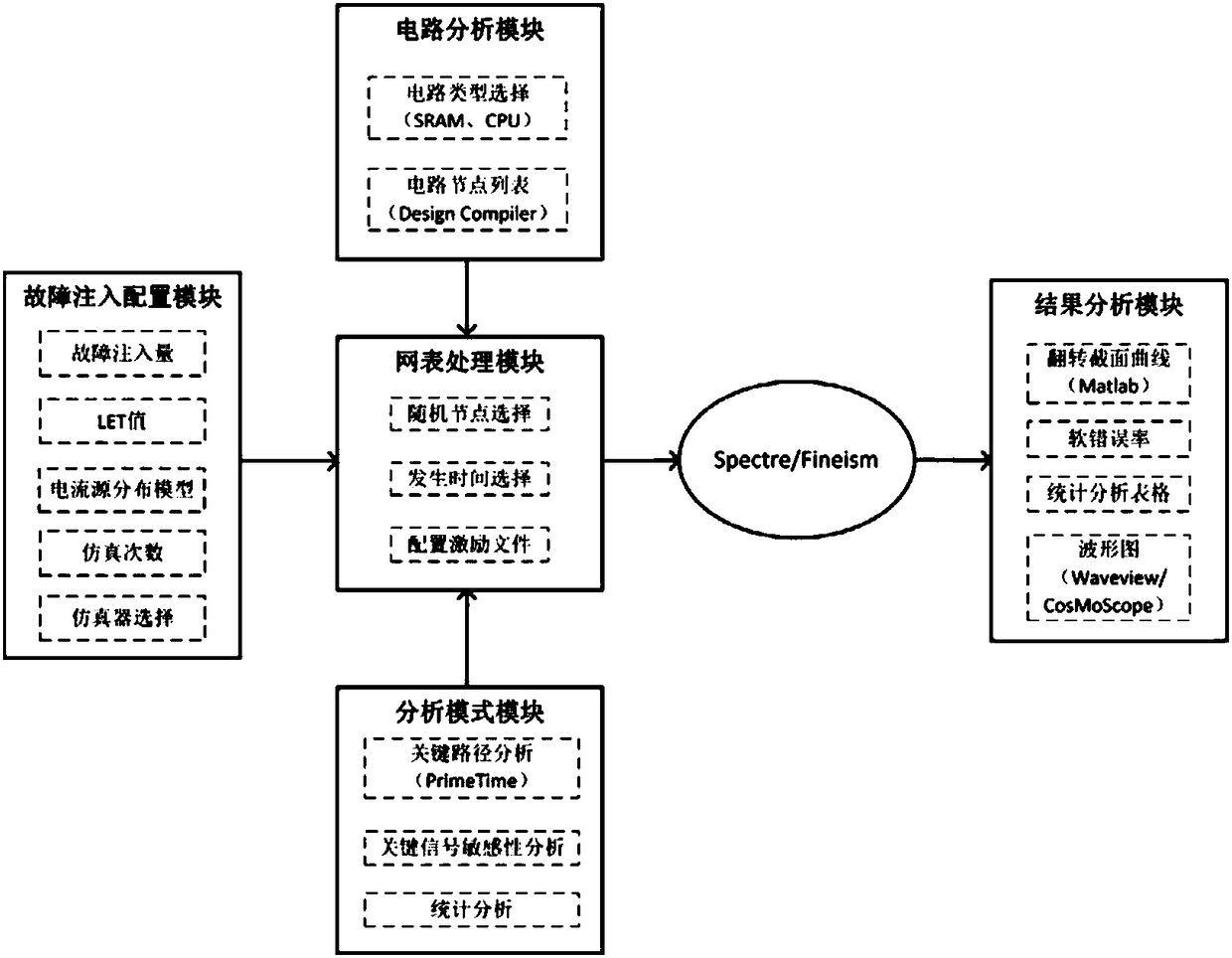

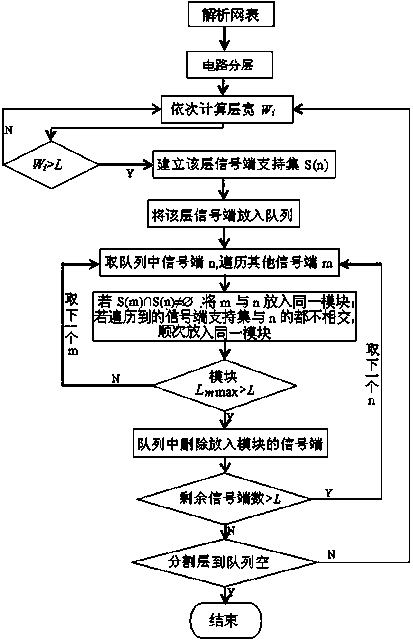

Circuit level single event effect simulation platform

ActiveCN108363894APrecise positioningLow costDesign optimisation/simulationCAD circuit designComputer architectureUser input

The invention provides a circuit level single event effect simulation platform. The simulation platform can support single event effect simulation analysis of large-scale circuits of 10,000 gate levels or above. The simulation platform comprises a circuit analysis module, a fault injection configuration module, an analysis mode module, a netlist processing module and a result analysis module, wherein the circuit analysis module extracts all sensitive nodes in circuits to generate a circuit node list file; the fault injection configuration module combines the circuit node list file and fault current source-related parameters which are input by a user and need to be injected into the circuits to write a script and randomly select circuit nodes and fault injection time to generate a fault injection file; the netlist processing module writes a script to obtain a result detection file, and combines analysis modes and the fault injection file to generate a stimulus file to be sent to a Fast-Spice simulator; the result analysis module saves and extracts simulation results, and forms different result icons according to different analysis modes.

Owner:陕西欣微绘通科技有限公司

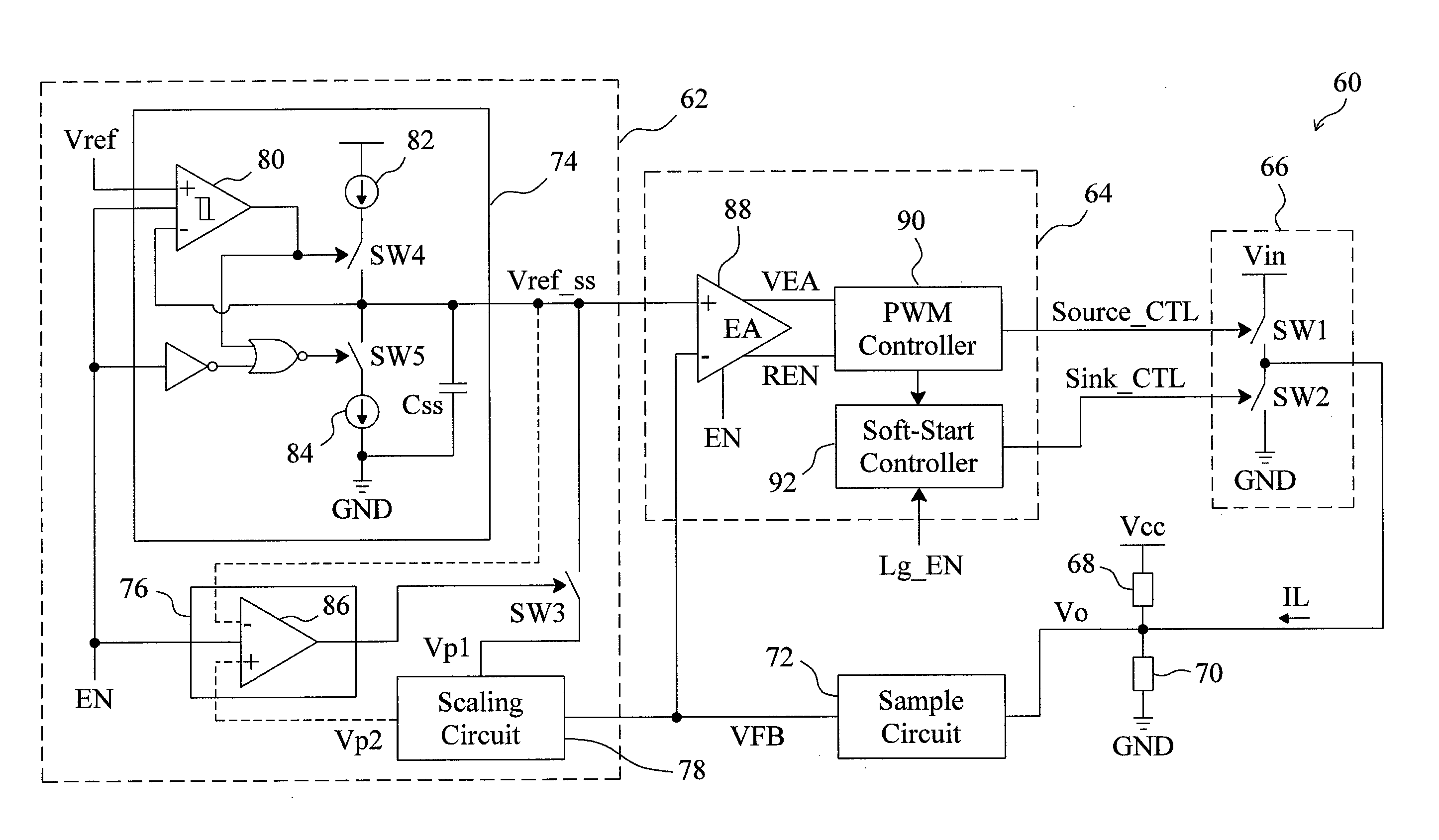

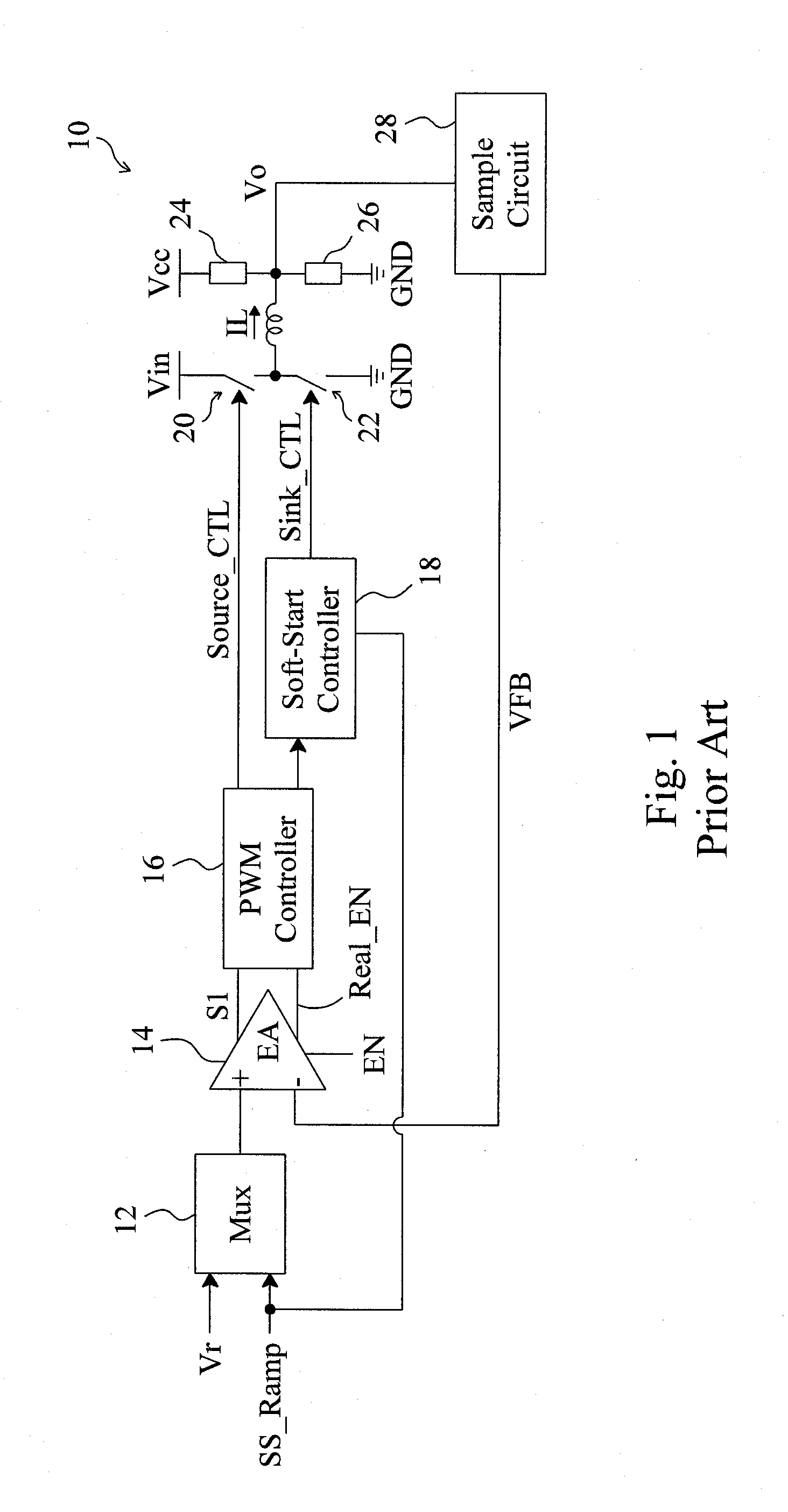

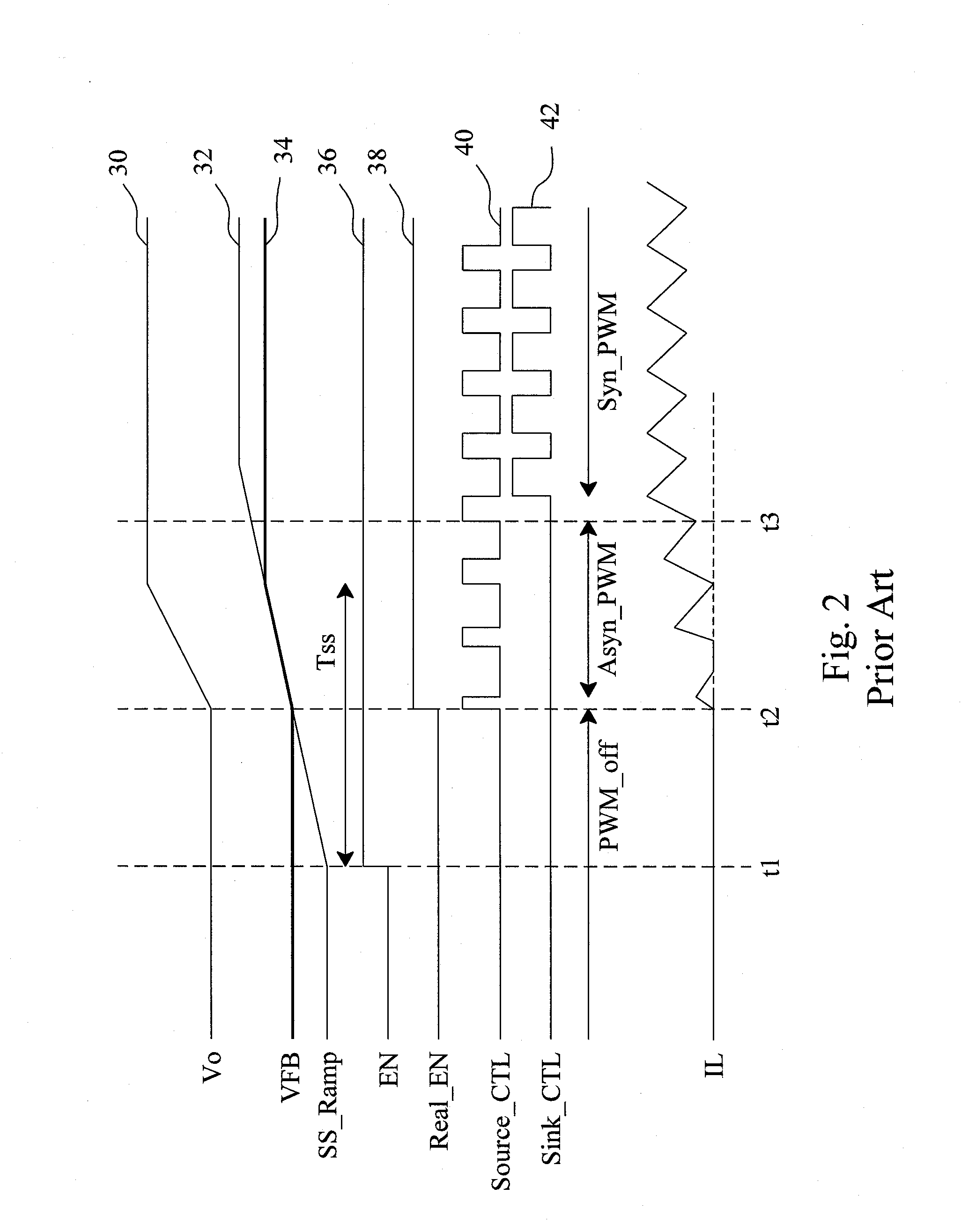

Soft-start circuit and method for a switching regulator

InactiveUS20110006746A1Reduce soft-start timeShorten the switching timeElectric variable regulationPower conversion systemsStart timeEngineering

A soft-start circuit for a switching regulator includes a signal generator and a scaling circuit coupled to the signal generator. During soft-start, the signal generator provides a ramp signal for the switching regulator such that the output voltage of the switching regulator changes from a residual voltage toward a target level. When soft-start is triggered, the scaling circuit provides a scaling voltage depending on the residual voltage, to shift the level of the ramp signal and consequently shorten the soft-start time of the switching regulator.

Owner:RICHTEK TECH

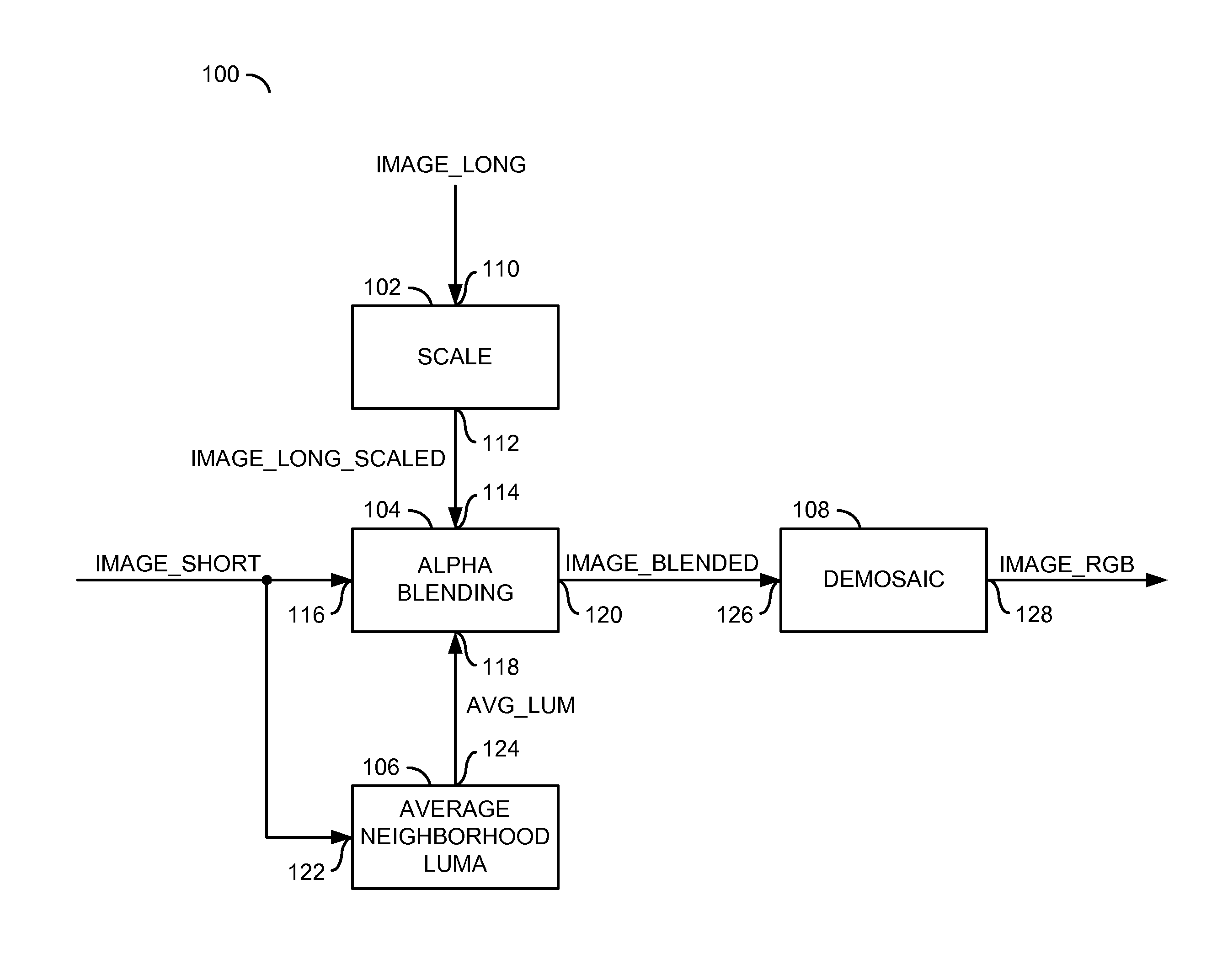

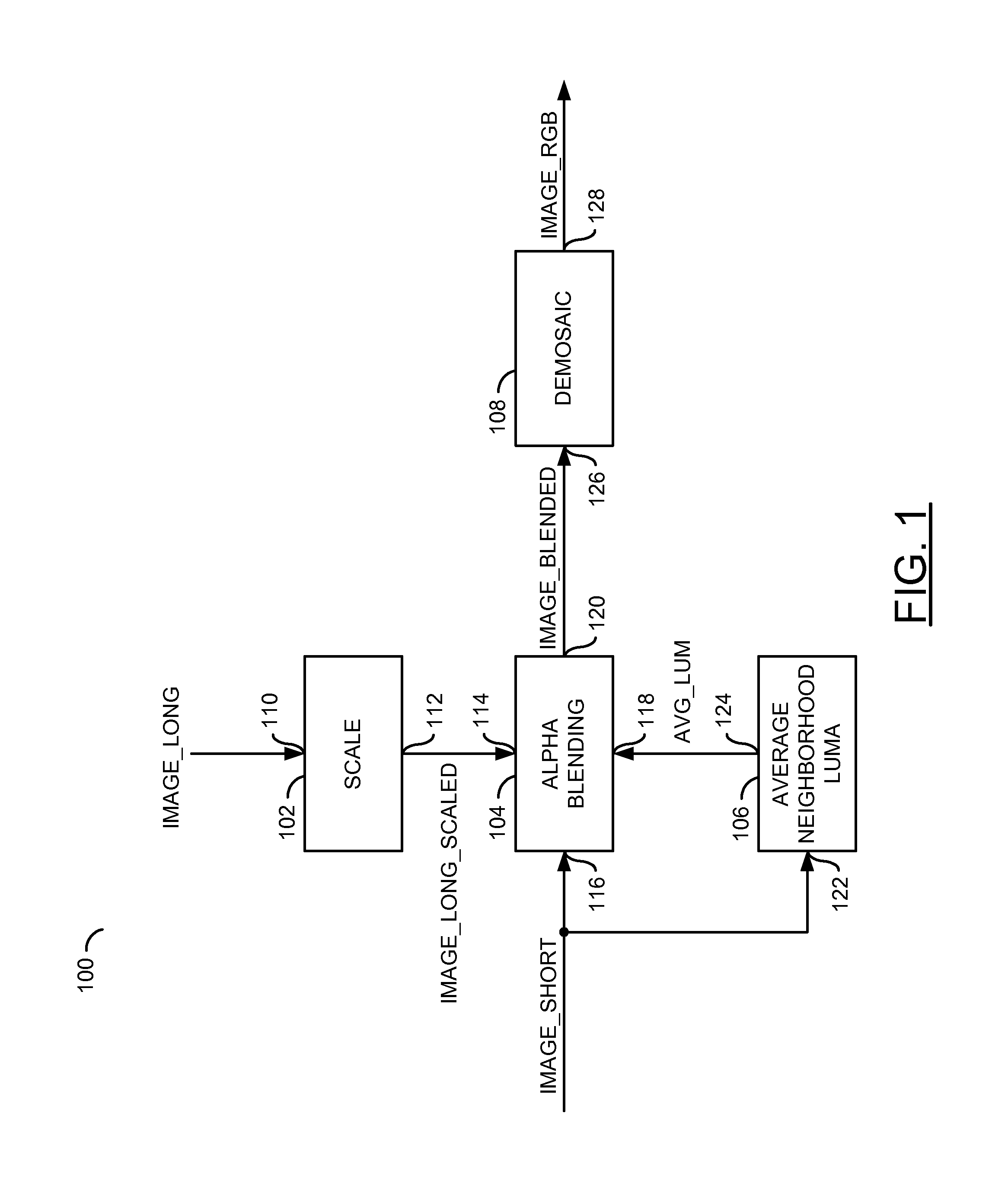

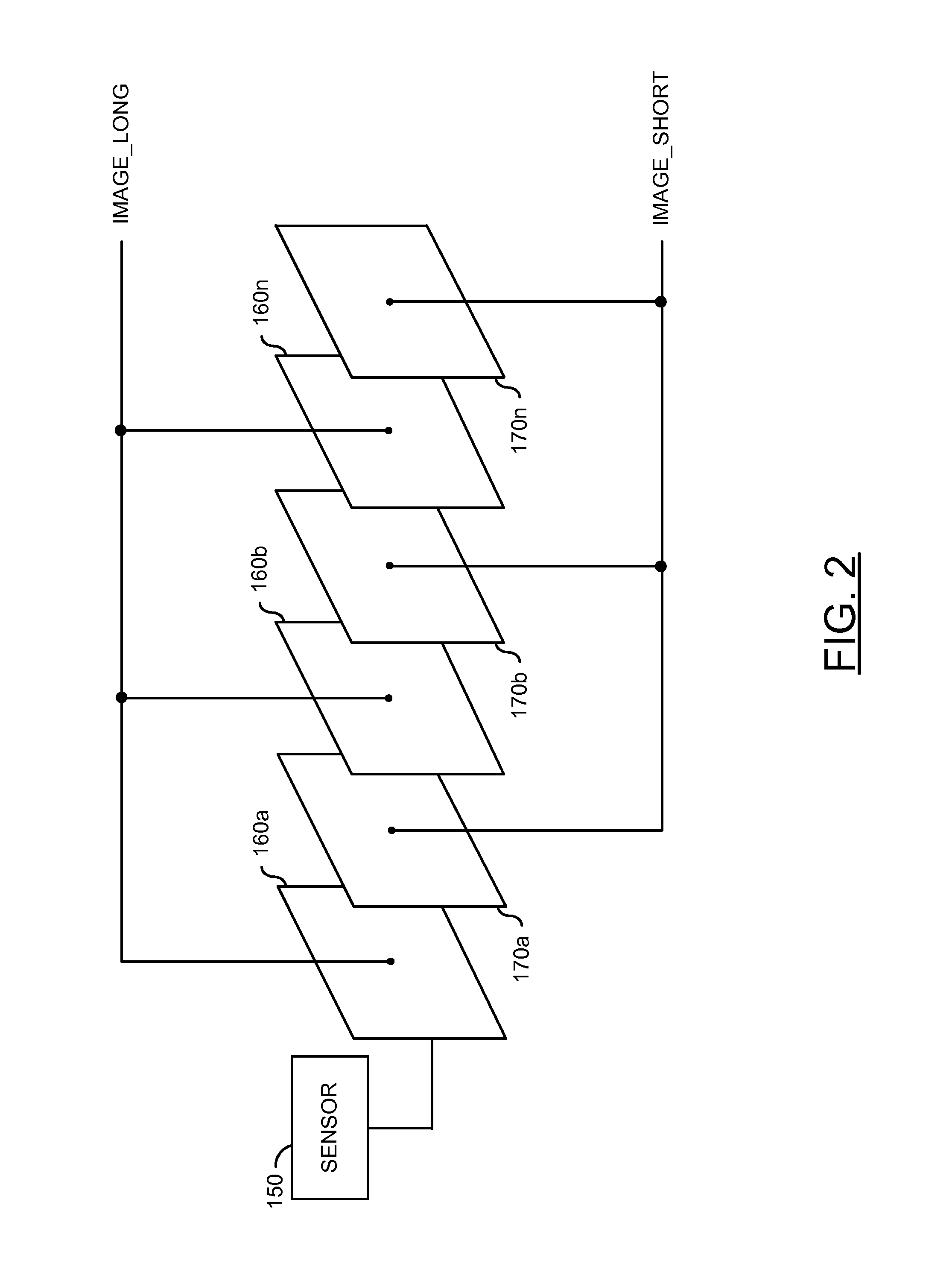

Method and/or apparatus for implementing high dynamic range image processing in a video processing system

ActiveUS9204113B1Low implementation costTelevision system detailsPulse modulation television signal transmissionImaging processingVideo processing

An apparatus comprising a scaling circuit, a luma circuit and a blending circuit. The scaling circuit may generate a plurality of scaled frames in response to a first plurality of frames generated by a sensor. The first plurality of frames may have a first exposure. The luma circuit may generate an average luminance value for each of a plurality of processed pixels in each of a second of the plurality of frames generated by the sensor. The second of the plurality of frames may have a second exposure and each of the average luminance values is calculated based on a plurality of neighboring pixels in a neighborhood of the processed pixel.

Owner:AMBARELLA INT LP

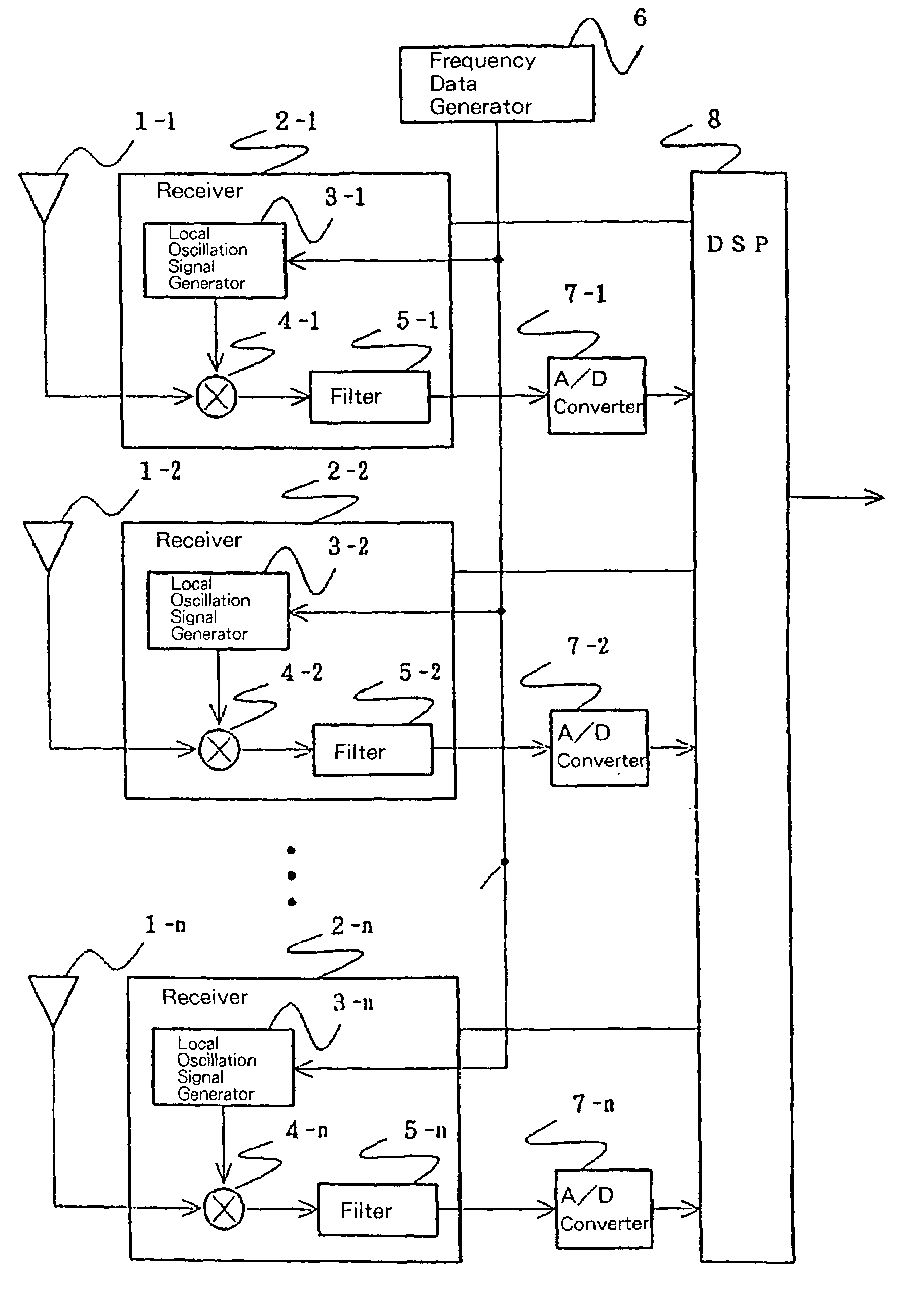

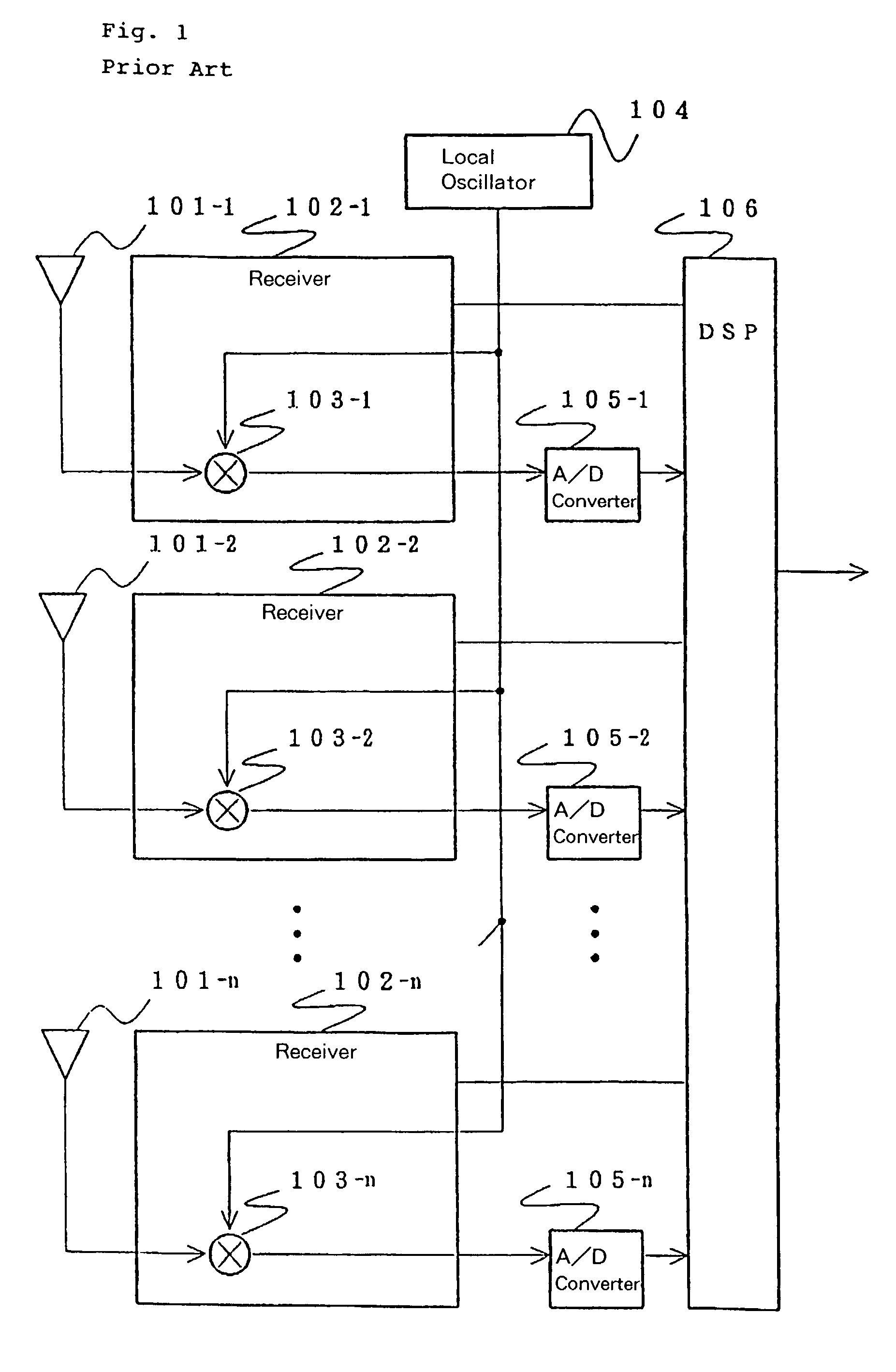

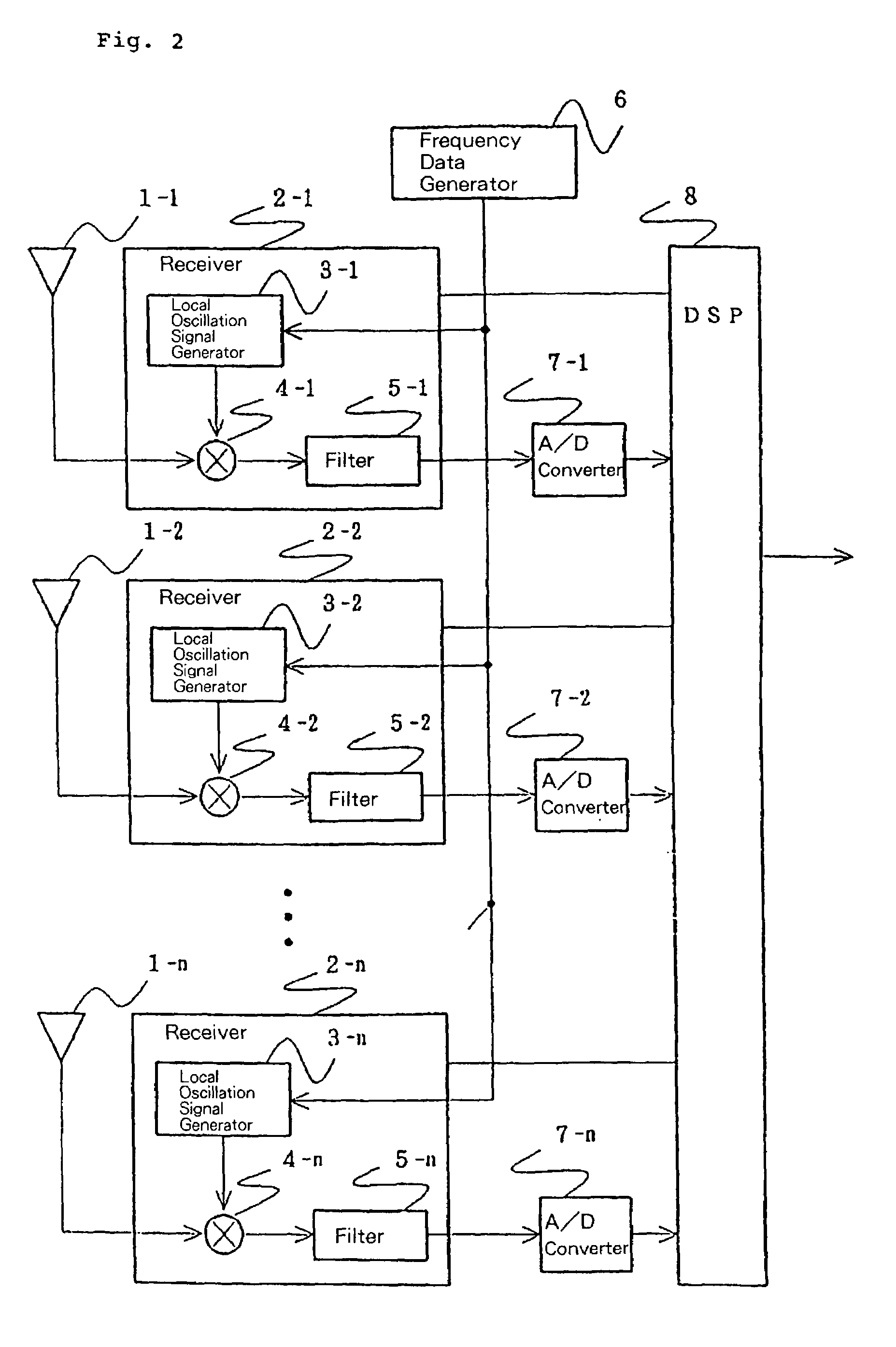

Local oscillation signal supply method and circuit therefor

InactiveUS7187723B1Exact reproductionSpatial transmit diversityRadio wave direction/deviation determination systemsPropagation delayQuadrature modulation

With the object of accurately reproducing, by means of a small-scale circuit, differences in propagation delay at antennas of received signals that are received as input by way of each of a plurality of receivers, frequency data generator 6 supplies frequency data that contain a frequency component that is synchronized in common to the plurality of receivers 2-1 to 2-n. At receiver 2-n, local oscillation signal generator 3-n, which is represented by a D / A converter, generates a local oscillation signal from frequency data that have been synchronized in common. The passing phase of a received signal that is outputted from antenna 1-n by way of receiver 1-n is thus fixed, and as a result, the phase difference of received signals that are received by DSP 8 by way of the plurality of receivers 2-1 to 2-n becomes the propagation delay difference of the received signals. As frequency data, frequency data that contain a plurality of frequency components are supplied to each receiver 2-n, and the frequency data are selected inside receiver 2-n and subjected to quadrature modulation to enable generation of local oscillation signals of differing intermediate frequencies.

Owner:NEC CORP

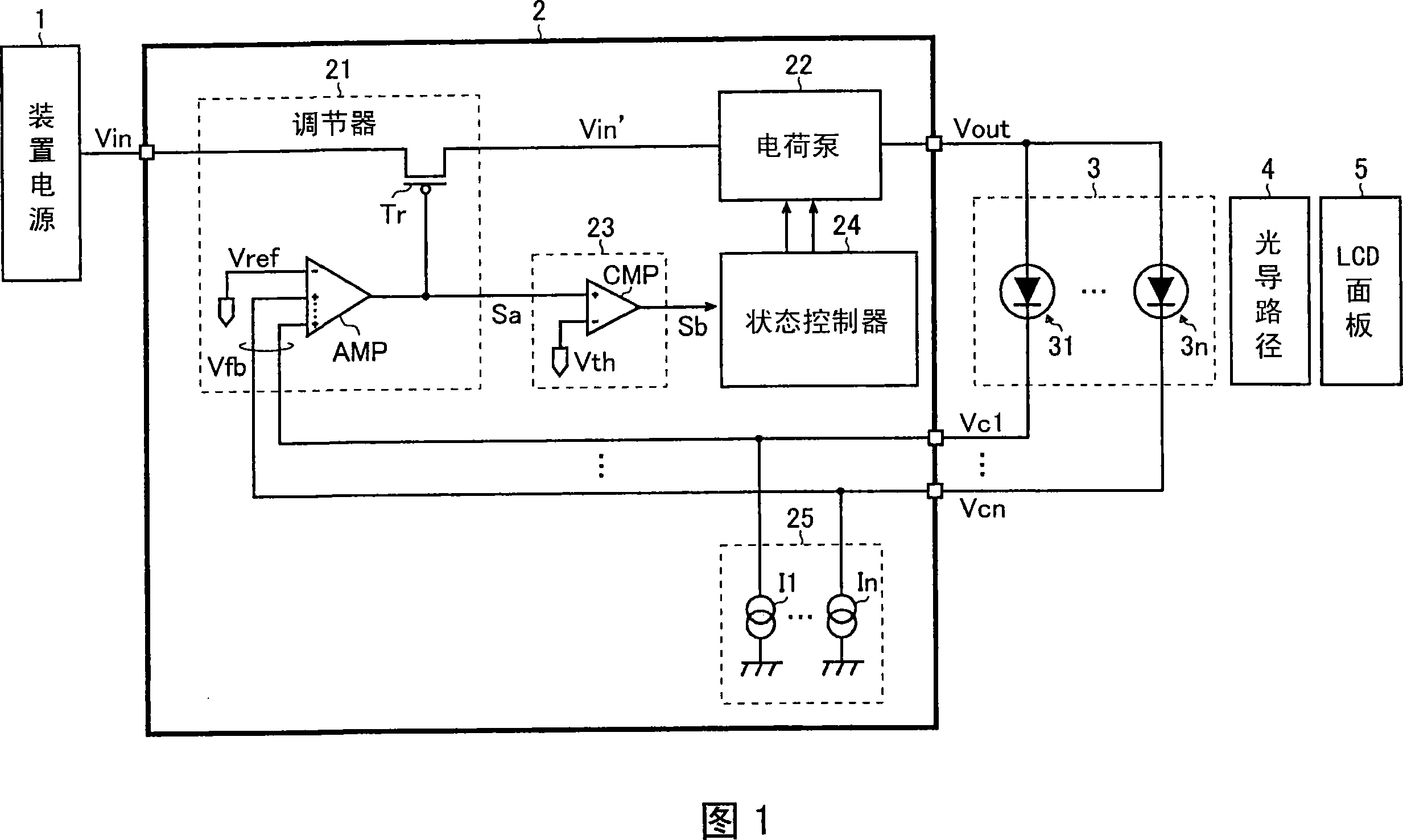

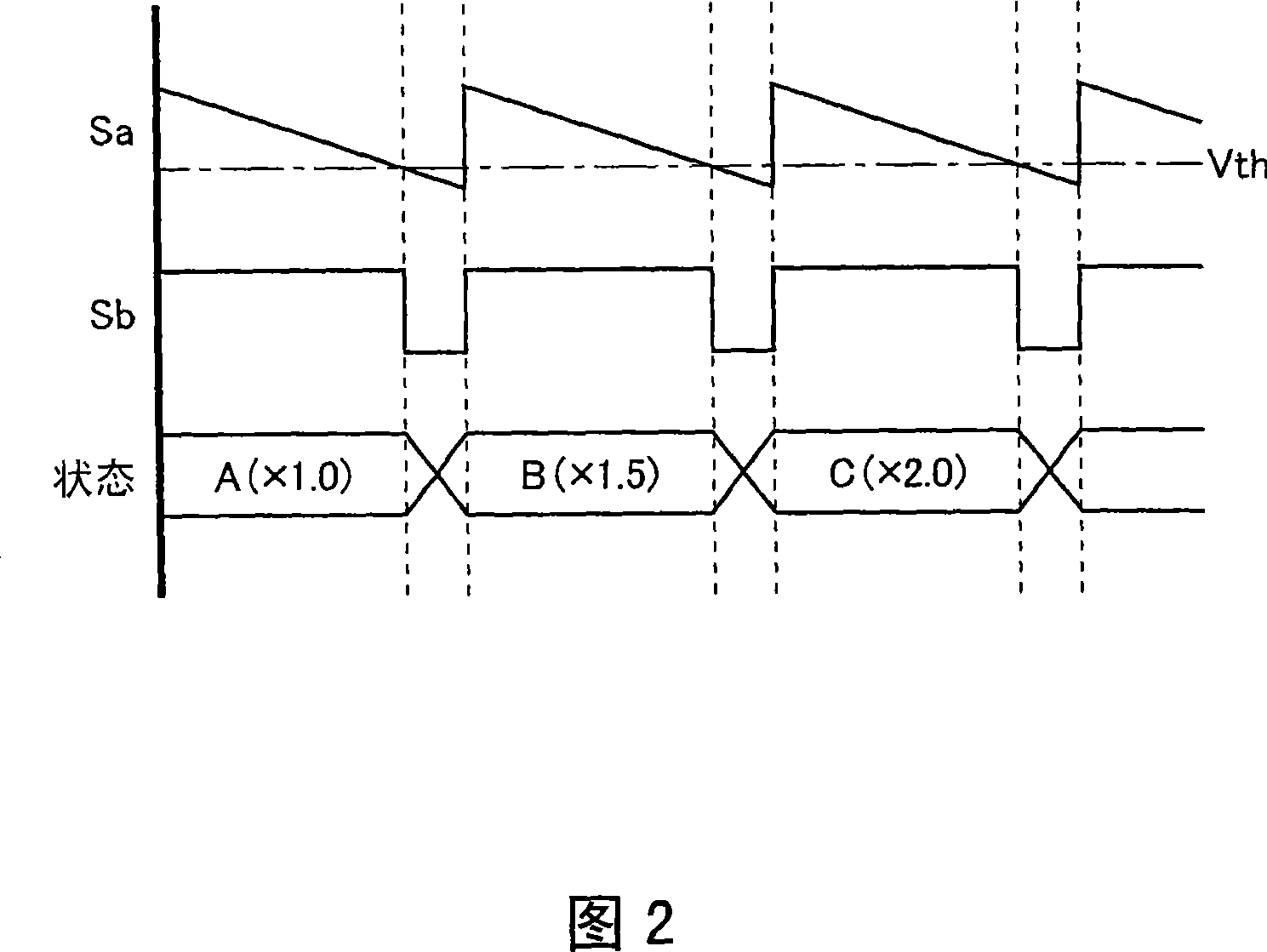

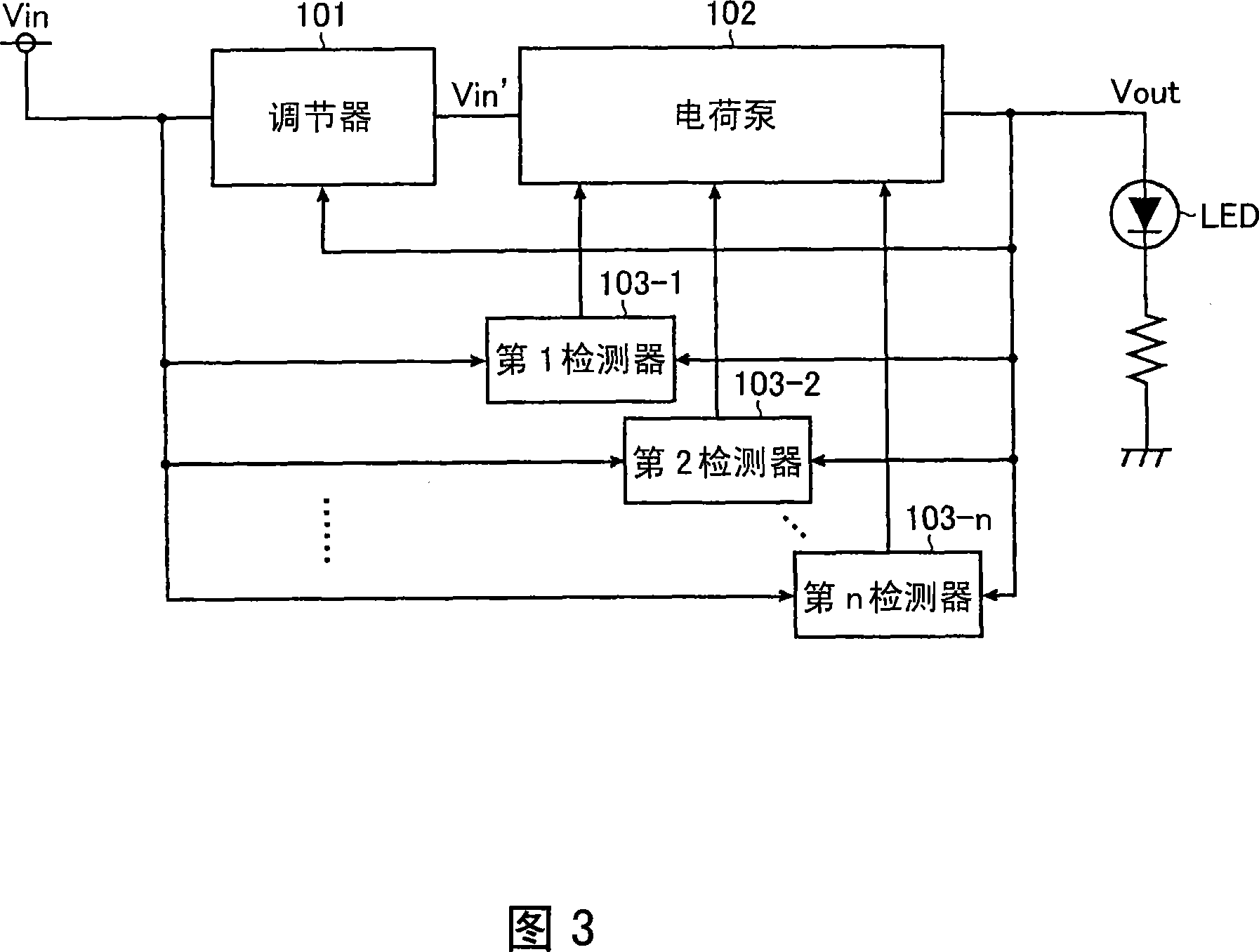

Power supply device, led driver, illumination device, and display device

InactiveCN101064467AStatic indicating devicesElectroluminescent light sourcesDisplay deviceEngineering

Owner:ROHM CO LTD

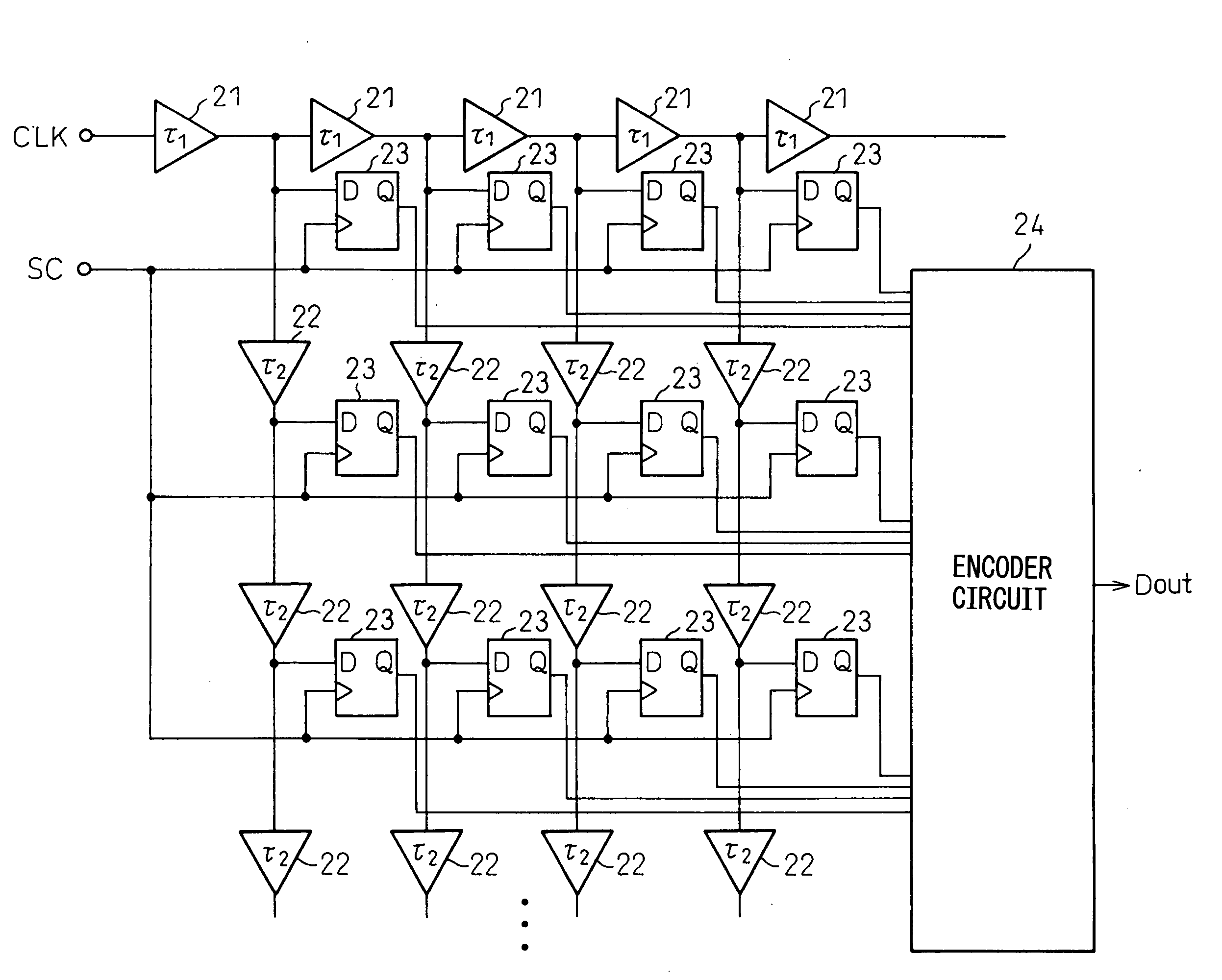

Time-to-digital converter

InactiveUS7884751B2Reduce circuit sizeHigh resolutionAnalogue/digital conversionElectric signal transmission systemsDigital down converterEngineering

A TDC circuit having a small scale circuit and high resolution is disclosed, which is a time-to-digital converter that detects a phase with respect to a reference clock of a signal to be measured, comprising a first delay line in which a plurality of first delay elements with a first delay amount is connected in series, a second delay line group that is connected to a plurality of connection nodes of the first delay line or an input node in the first stage and in which at least one or more second delay elements with a second delay amount different from the first delay amount are connected in series, a plurality of judgment circuits that judge whether the changing edge of the signal to be measured is advanced or delayed with respect to the changing edges of a delayed clock output from the first delay element and the second delay element, and an operation circuit that calculates a phase with respect to the reference clock of the changing edge of the signal to be measured from the judgment results, wherein a difference between the first delay amount and the second delay amount is smaller than the first delay amount and the second delay amount.

Owner:SEMICON TECH ACADEMIC RES CENT

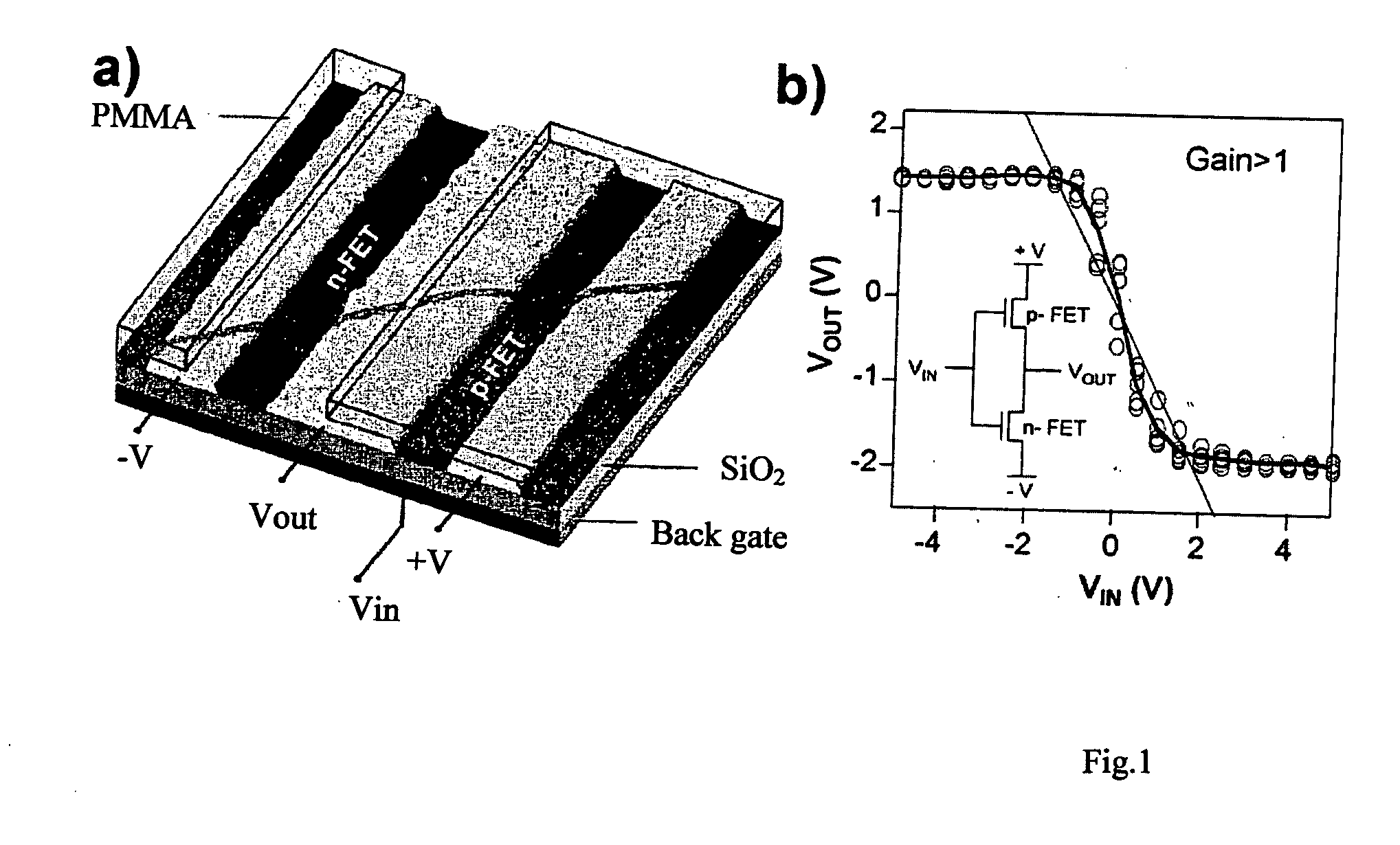

Nanotube array electronic and opto-electronic devices

InactiveUS20090189143A1Reduce contact resistanceMinimized contact resistanceNanoinformaticsSolid-state devicesManufacturing technologyPhotonics

Carbon nanotube (CNT)-based devices and technology for their fabrication are disclosed. The discussed electronic and photonic devices and circuits rely on the nanotube arrays grown on a variety of substrates, such as glass or Si wafer. The planar, multiple layer deposition technique and simple methods of change of the nanotube conductivity type during the device processing are utilized to provide a simple and cost effective technology for a large scale circuit integration. Such devices as p-n diode, CMOS-like circuit, bipolar transistor, light emitting diode and laser are disclosed, all of them are expected to have superior performance then their semiconductor-based counterparts due to excellent CNT electrical and optical properties. When fabricated on Si-wafers, the CNT-based devices can be combined with the Si circuit elements, thus producing hybrid Si-CNT devices and circuits.

Owner:NANO ELECTRONICS & PHOTONIC DEVICES & CIRCUITS

Dynamically reconfigurable signal processing circuit, pattern recognition apparatus, and image processing apparatus

ActiveUS7088860B2Efficiently sequentially extract a pluralityEfficiently and stably executeTelevision system detailsColor signal processing circuitsImaging processingSignal processing circuits

A plurality of signal processing functions are achieved with the same arithmetic processing circuit by controlling wiring arrangements or signal modulation in accordance with a predetermined arrangement control signal that is output based on circuit arrangement information read from a circuit arrangement information storage unit. Hierarchical parallel processing is realized with small-scale circuit configuration. Further, detection of a predetermined feature and integration of the detection results can be efficiently performed.

Owner:CANON KK

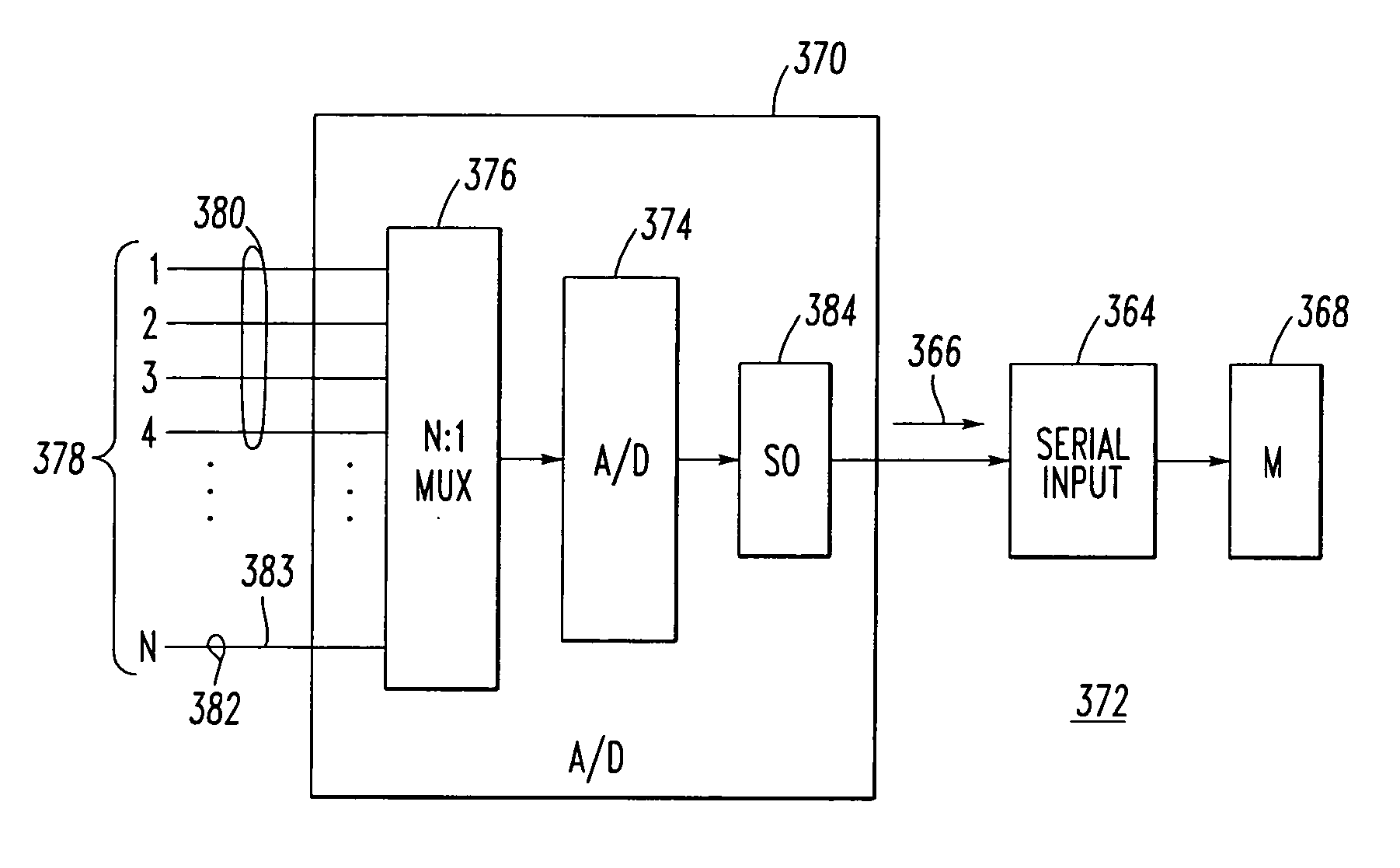

Plural channel analog-to-digital converter, method and meter employing an input channel with a predetermined direct current bias

ActiveUS20050134490A1Data can be lostElectric signal transmission systemsSpecial tariff metersA d converterEngineering

Owner:EATON INTELLIGENT POWER LTD

Circuit reliability evaluating method based on signal probability

The invention relates to a circuit reliability evaluating method based on the signal probability. The method includes reading an integrated circuit gate level netlist, analyzing the netlist to acquire connection structures of gate nodes, and providing a segmentation algorithm to segment the circuit into a plurality of modules; allowing each module to be one sub circuit, utilizing the PTM method onto the sub circuits, and calculating the reliability of each module sequentially; evaluating the reliability of the entire circuit according to the principle of calculating the independent event joint probability through the module reliability product. By the aid of the segmentation algorithm, the majority of modules are guaranteed being free of redundancy on functions and overlap on structures. The problem that only small-scale circuits can be evaluated by a PTM method is optimized, and the evaluating method can be applied to large-scale circuits; in addition, the TP method, the EPP method and the optimized PTM method are integrated to develop a circuit reliability evaluating platform which can be applied to the circuit designing step to calculate the reliability, and the designed structure can be adjusted conveniently and timely.

Owner:SHANGHAI UNIVERSITY OF ELECTRIC POWER

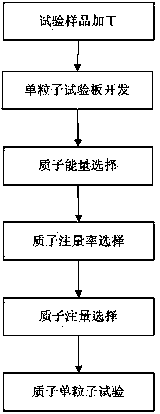

Method for conducting device proton signal-event test through accelerator high-energy proton

A method for conducting a device proton signal-event test through an accelerator high-energy proton comprises the steps that test samples are processed and the requirements of a signal-event test board and the requirements for selection of high-energy proton energy, the fluence rate and the fluence are satisfied. Single event upset of a large-scale circuit tends to be sensitive along with the increase of the integration degree and the reduction of the feature size. Single event upset can be generated through the method that a nuclear reaction of the proton occurs or the proton is directly ionized. An electronic system fault probably caused by single event upset happens to an on-orbit satellite. The method is used for conducting the device proton single event upset test on the ground. According to the method, the proton single event upset sensitivity of a key device for the satellite can be evaluated, proton single event upset sensitive parameters of the device can be obtained, a basis is provided for anti-radiation reinforcing design of the satellite, and the method for conducting the device proton signal-event test through the accelerator high-energy proton has important significance in the guarantee of the reliability of the new-generation satellite.

Owner:CHINA ACADEMY OF SPACE TECHNOLOGY

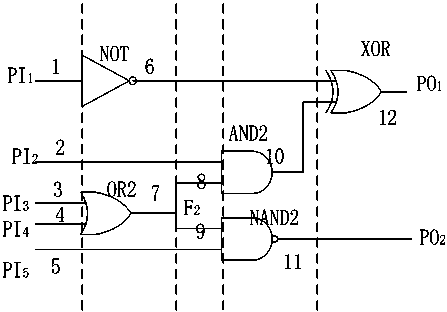

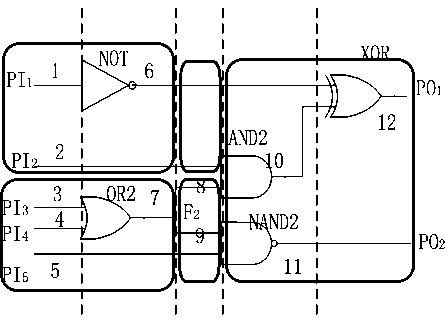

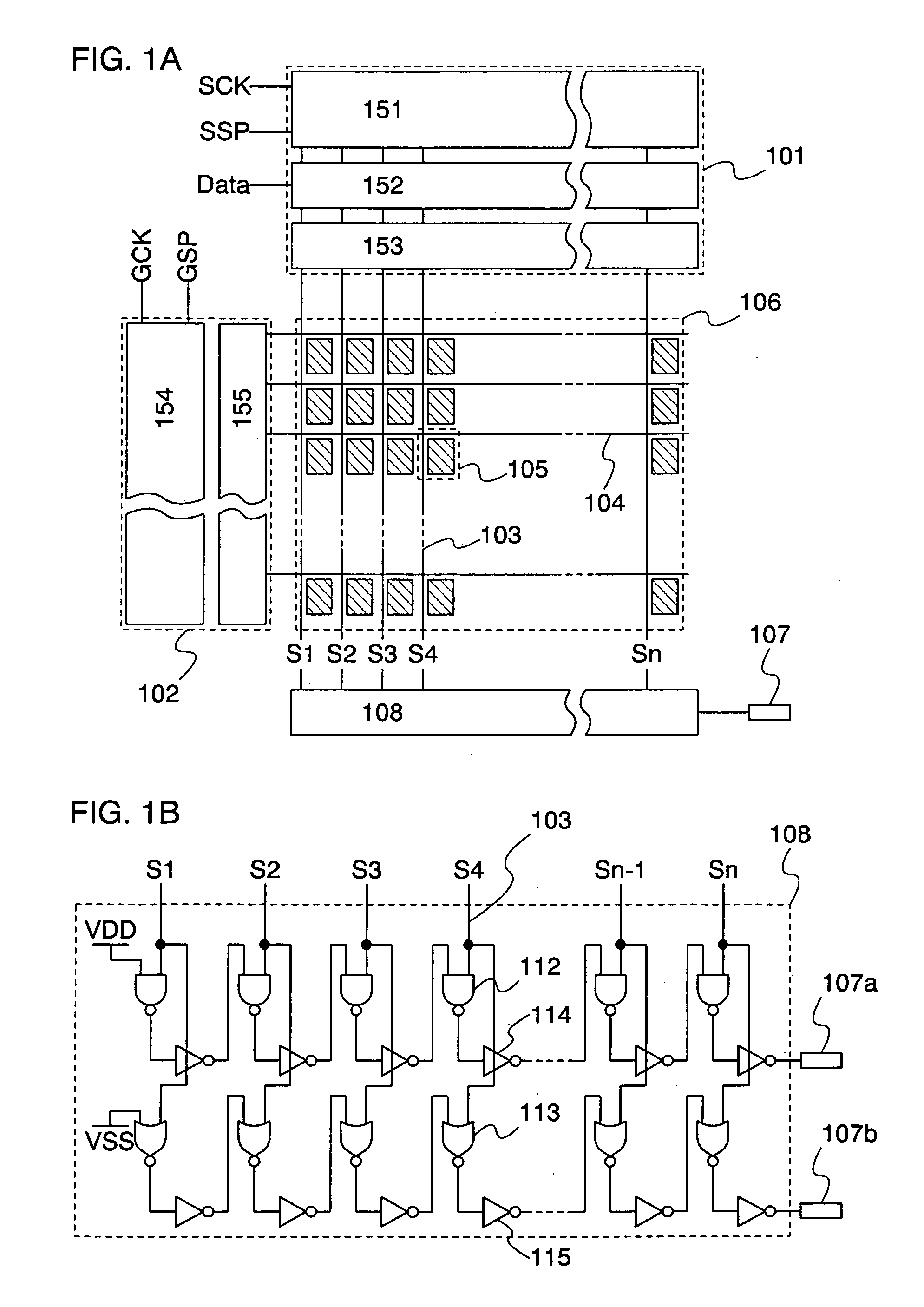

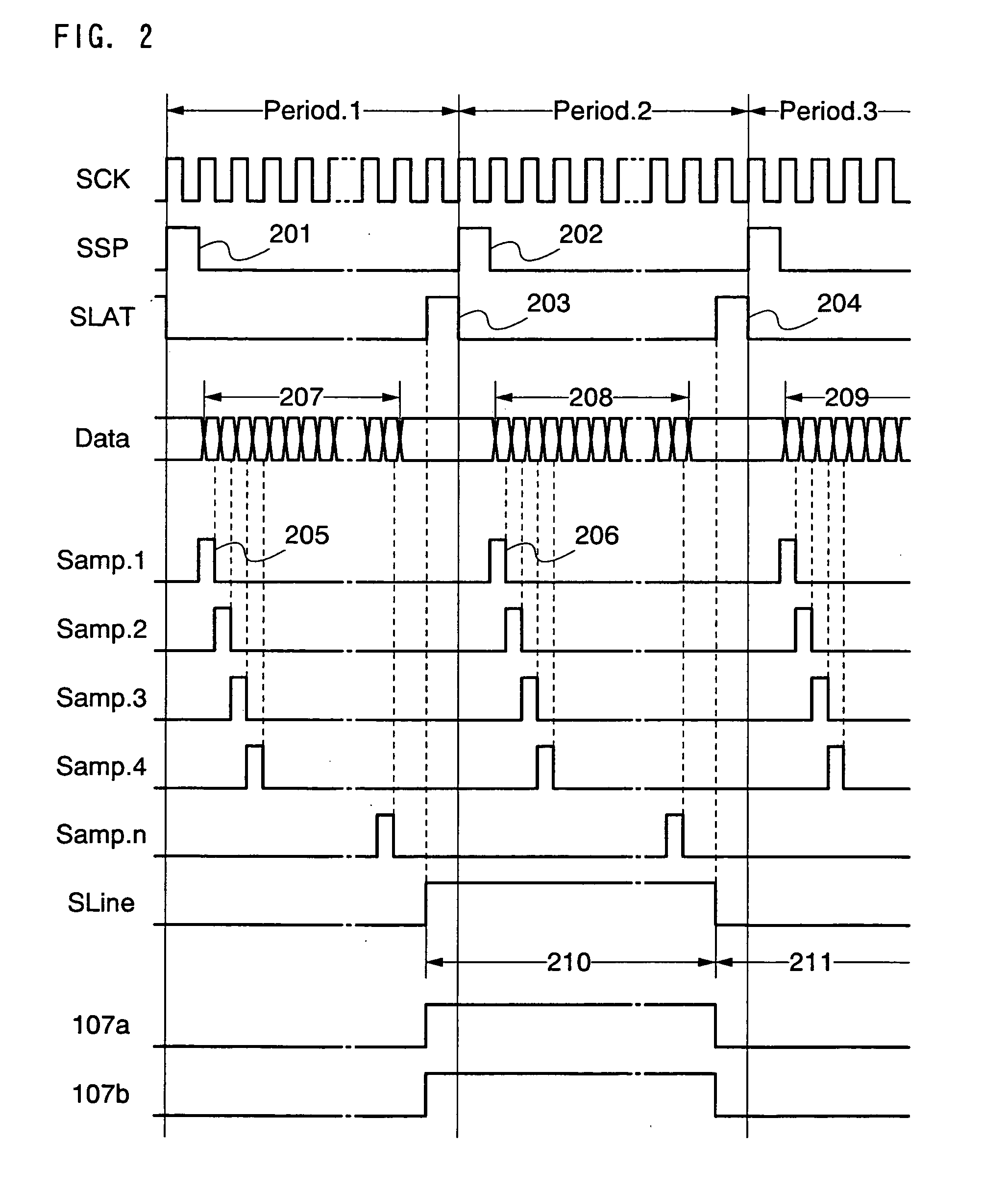

Circuit for inspecting semiconductor device and inspecting method

InactiveUS20050035805A1Effective Quality InspectionEfficient for of display deviceReliability increasing modificationsExclusive-OR circuitsDevice materialEngineering

It is configured by plurality of NAND circuits connected in series through a plurality of inverters, and a plurality of NOR circuits connected in series through the plurality of inverters. Each of a plurality of source signal lines provided in a pixel portion is connected to one input terminal of a NAND circuit and a NOR circuit, and an output of an inspection is obtained from final lines of the NAND circuit and the NOR circuit connected in series. In this manner, an inspecting circuit which is capable of determining a defect simply and accurately by using a small-scale circuit, and a method thereof are provided.

Owner:SEMICON ENERGY LAB CO LTD