Patents

Literature

82 results about "Row hammer" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

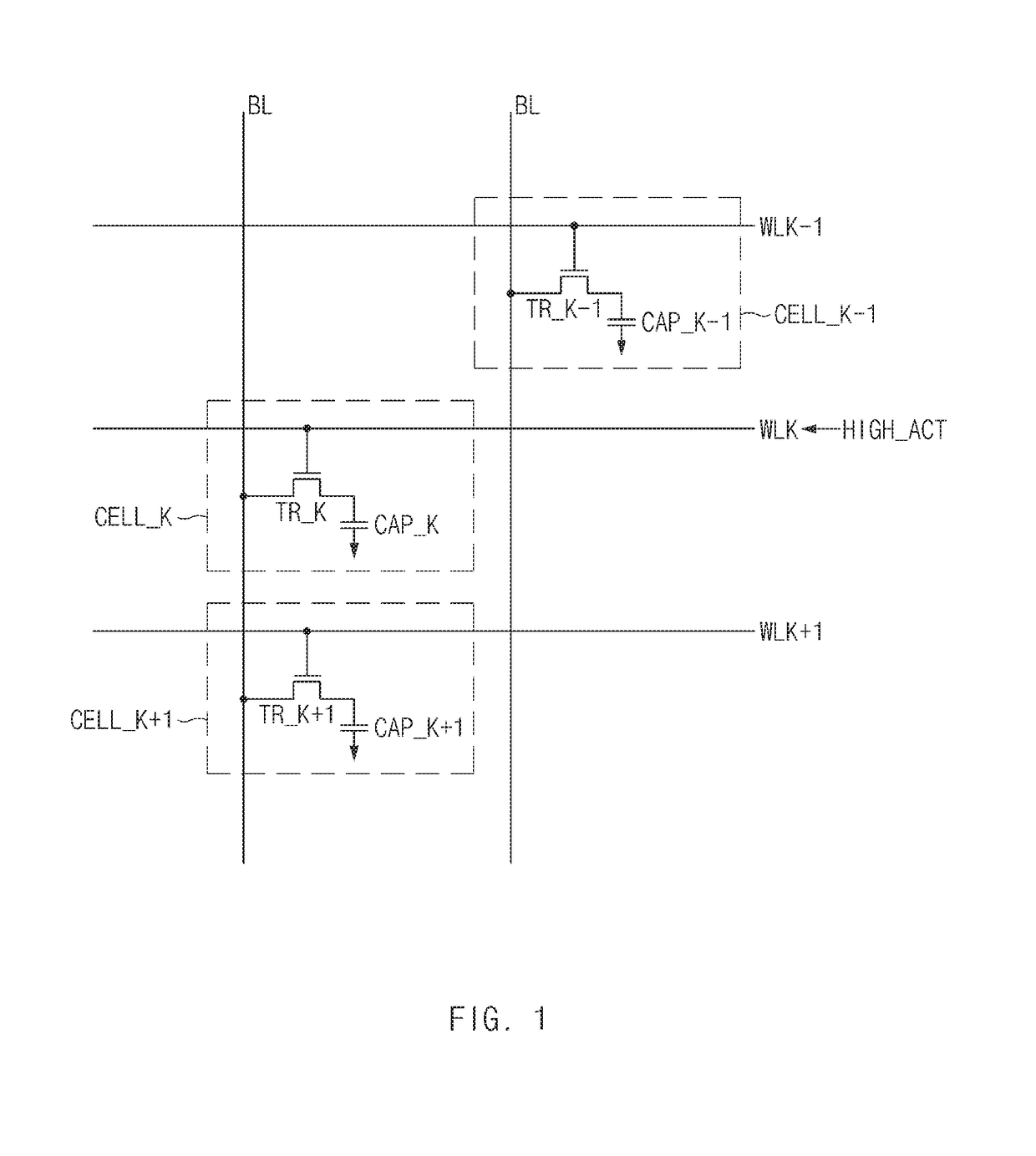

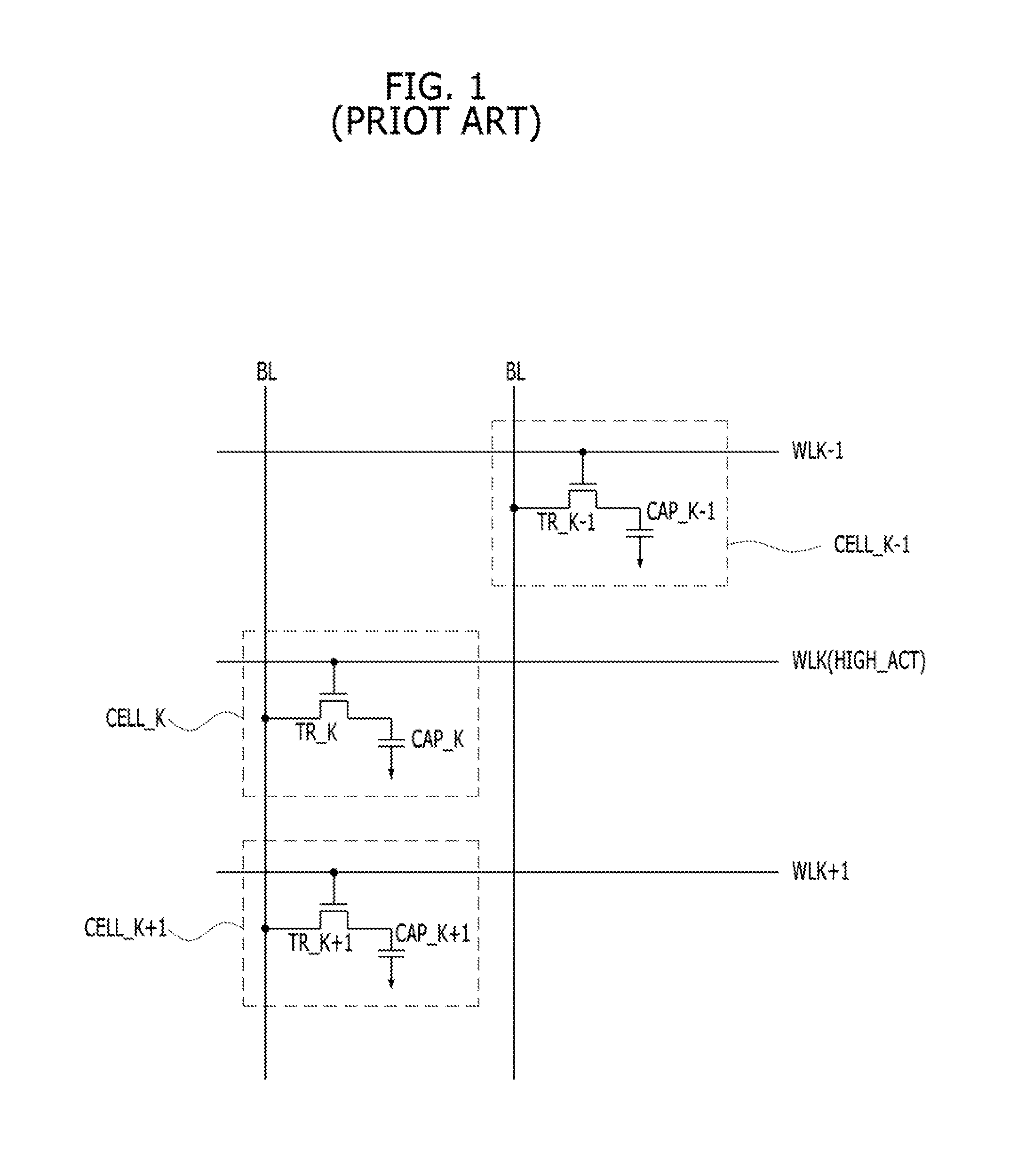

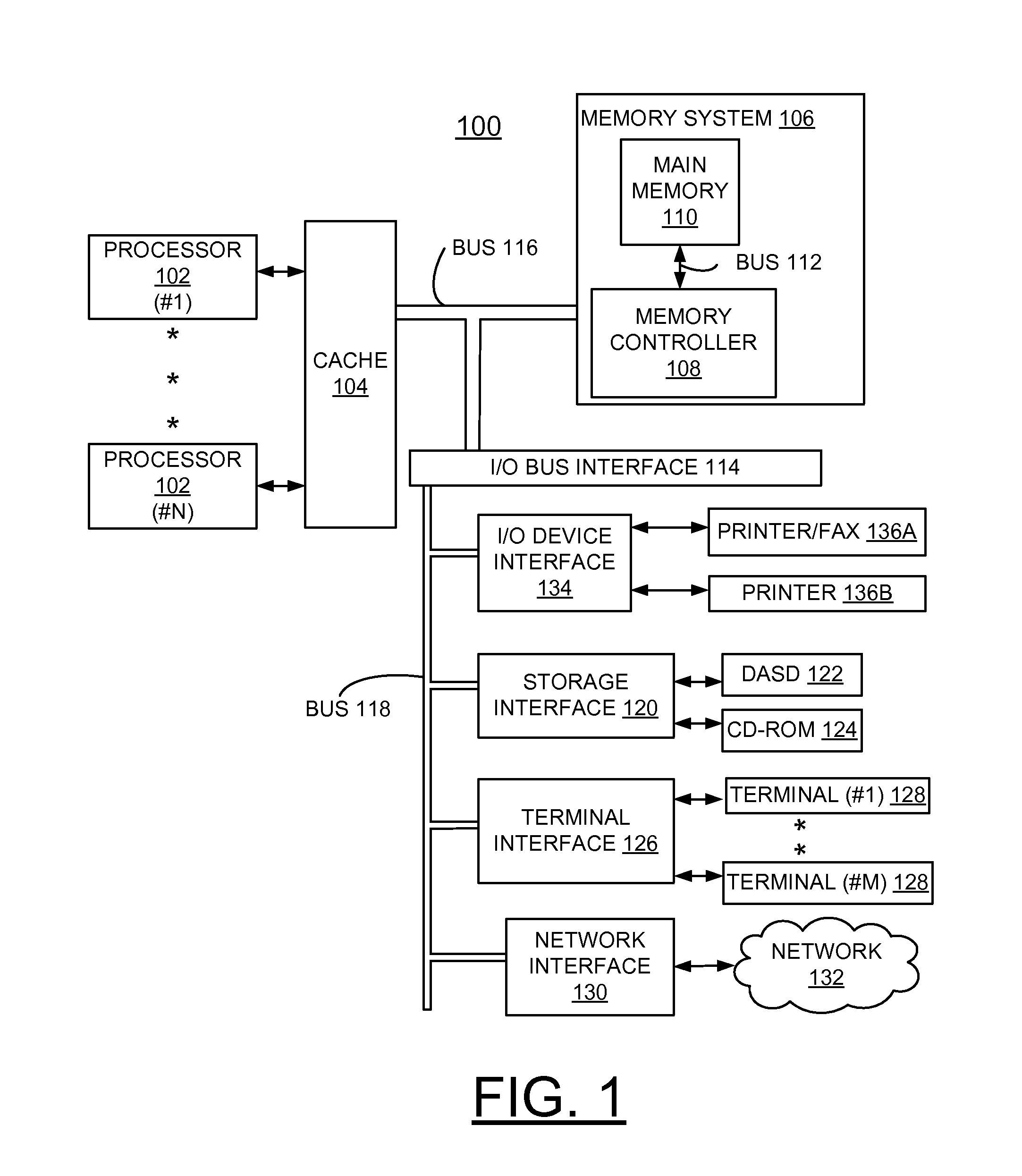

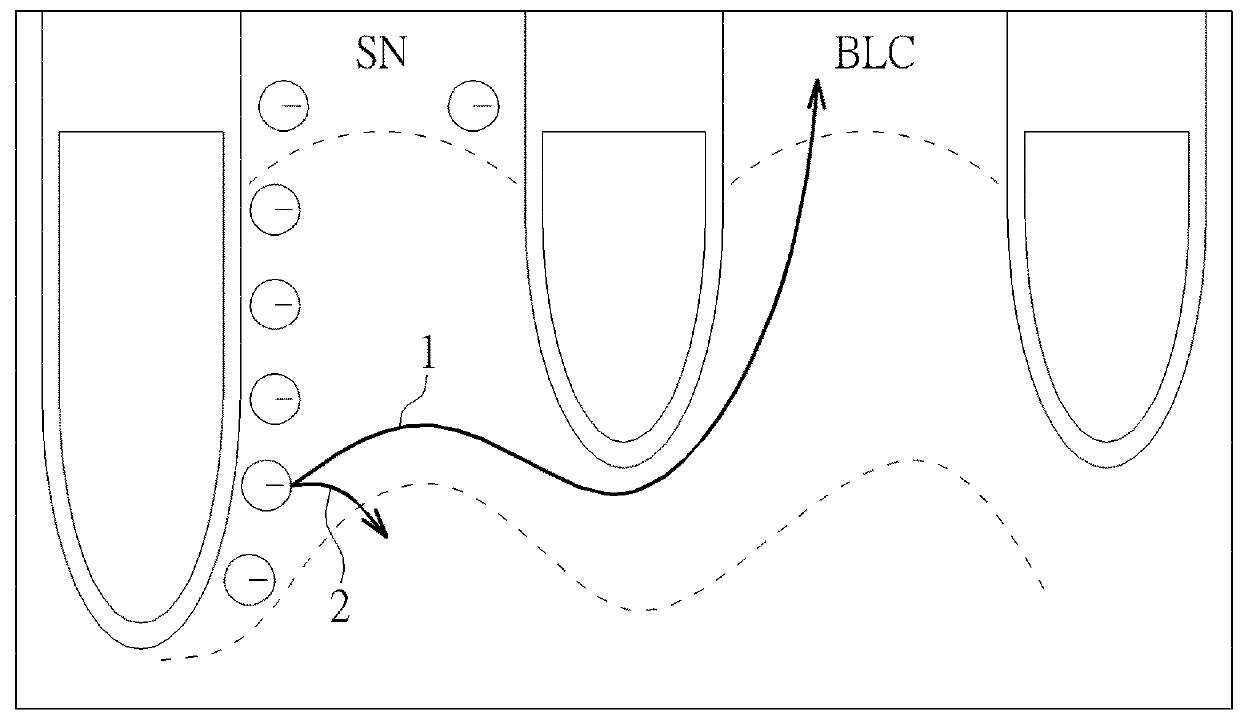

Row hammer (also written as rowhammer) is an unintended and undesirable side effect in dynamic random-access memory (DRAM) in which memory cells leak their charges and interact electrically between themselves, possibly leaking or changing the contents of nearby memory rows that were not addressed in the original memory access. This bypass of the isolation between DRAM memory cells results from the high cell density in modern DRAM, and can be triggered by specially crafted memory access patterns that rapidly activate the same memory rows numerous times.

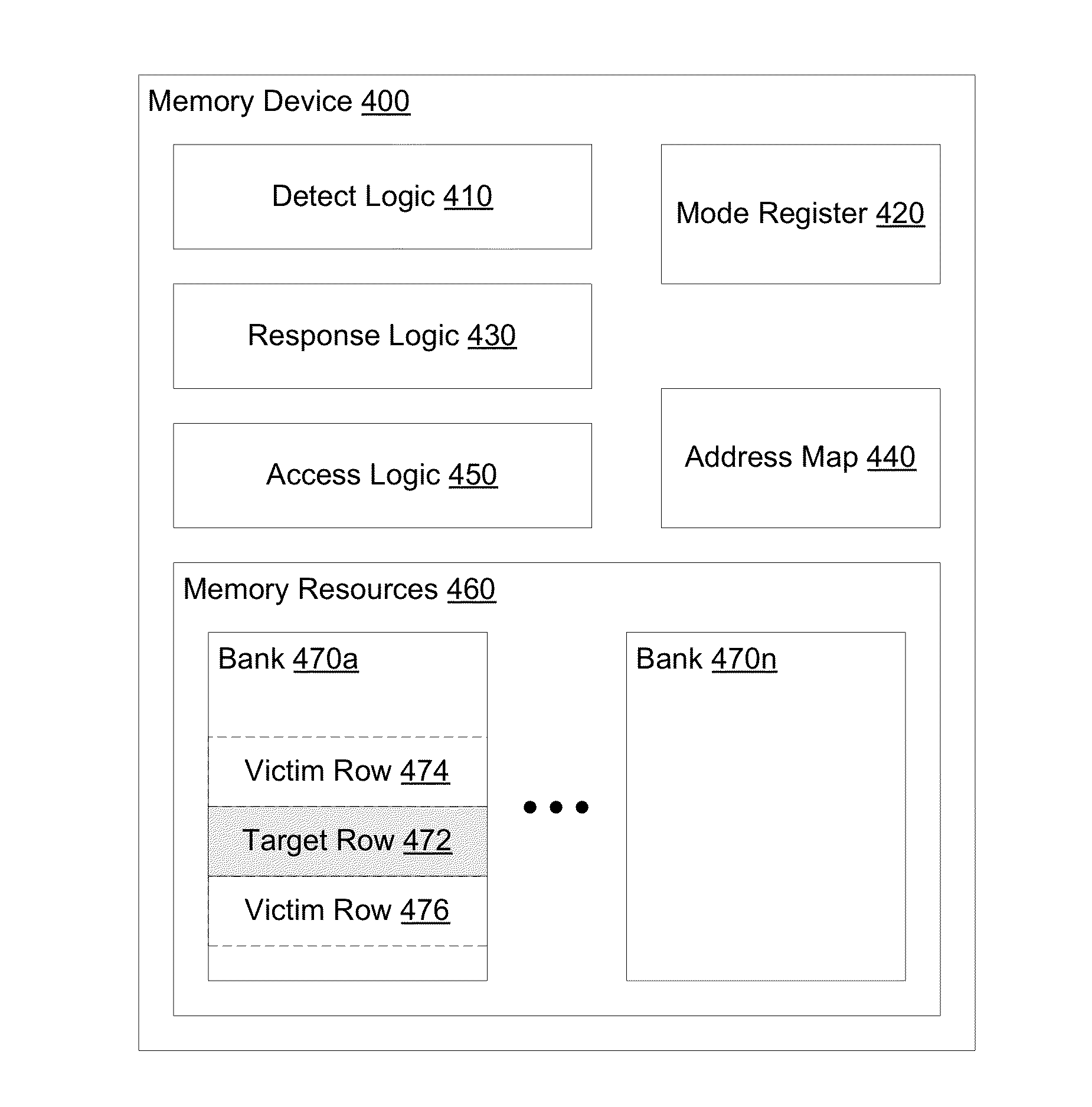

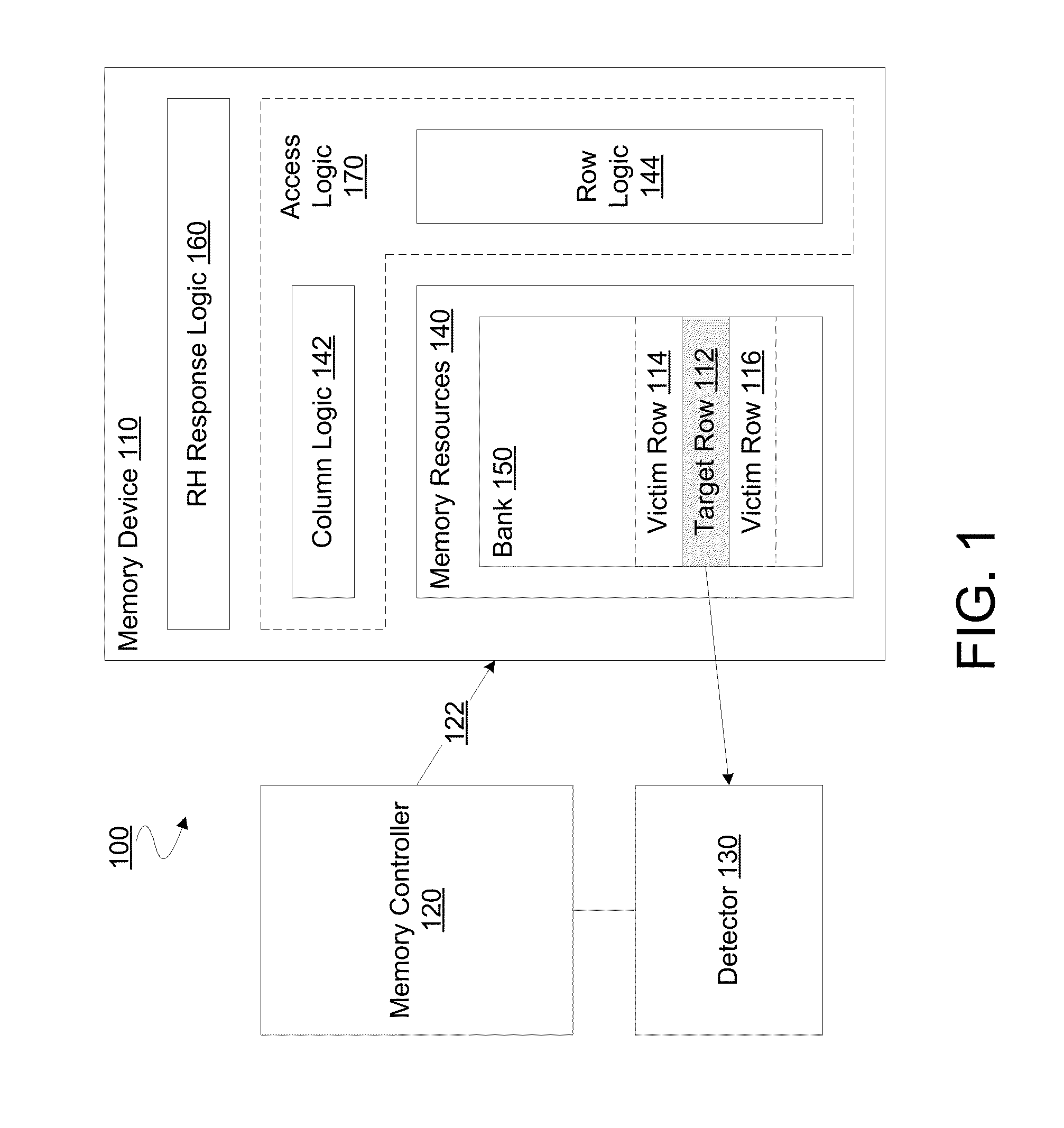

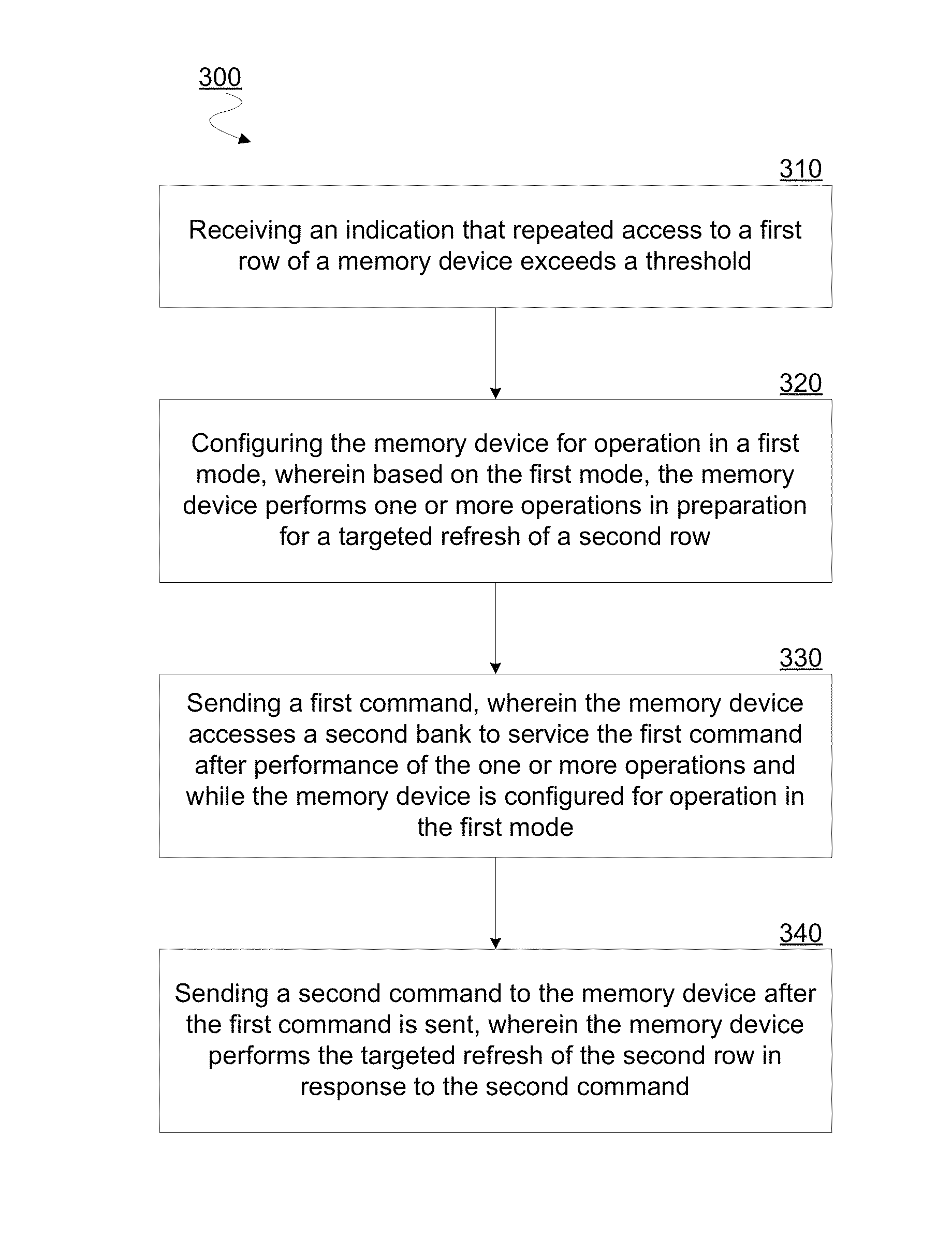

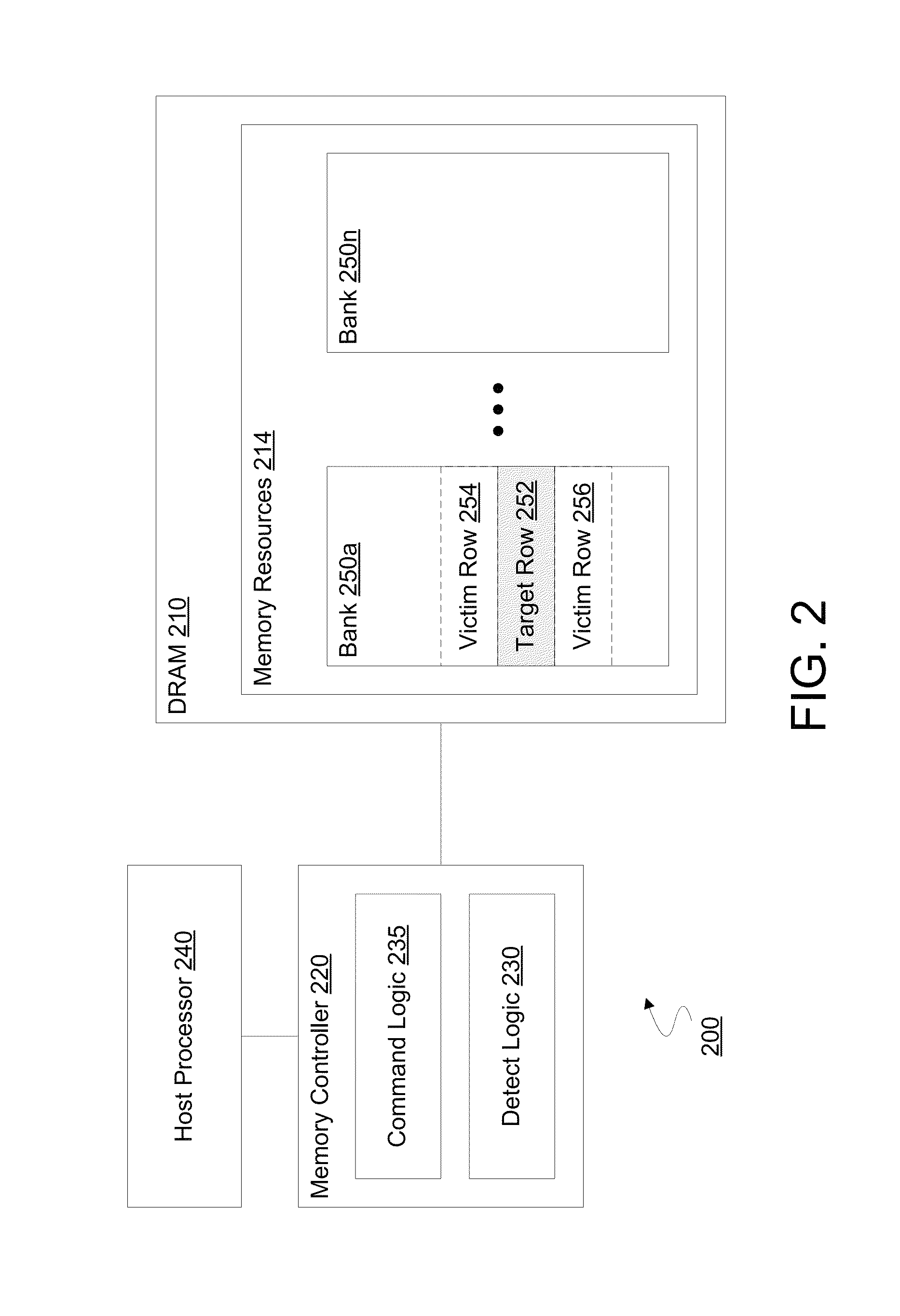

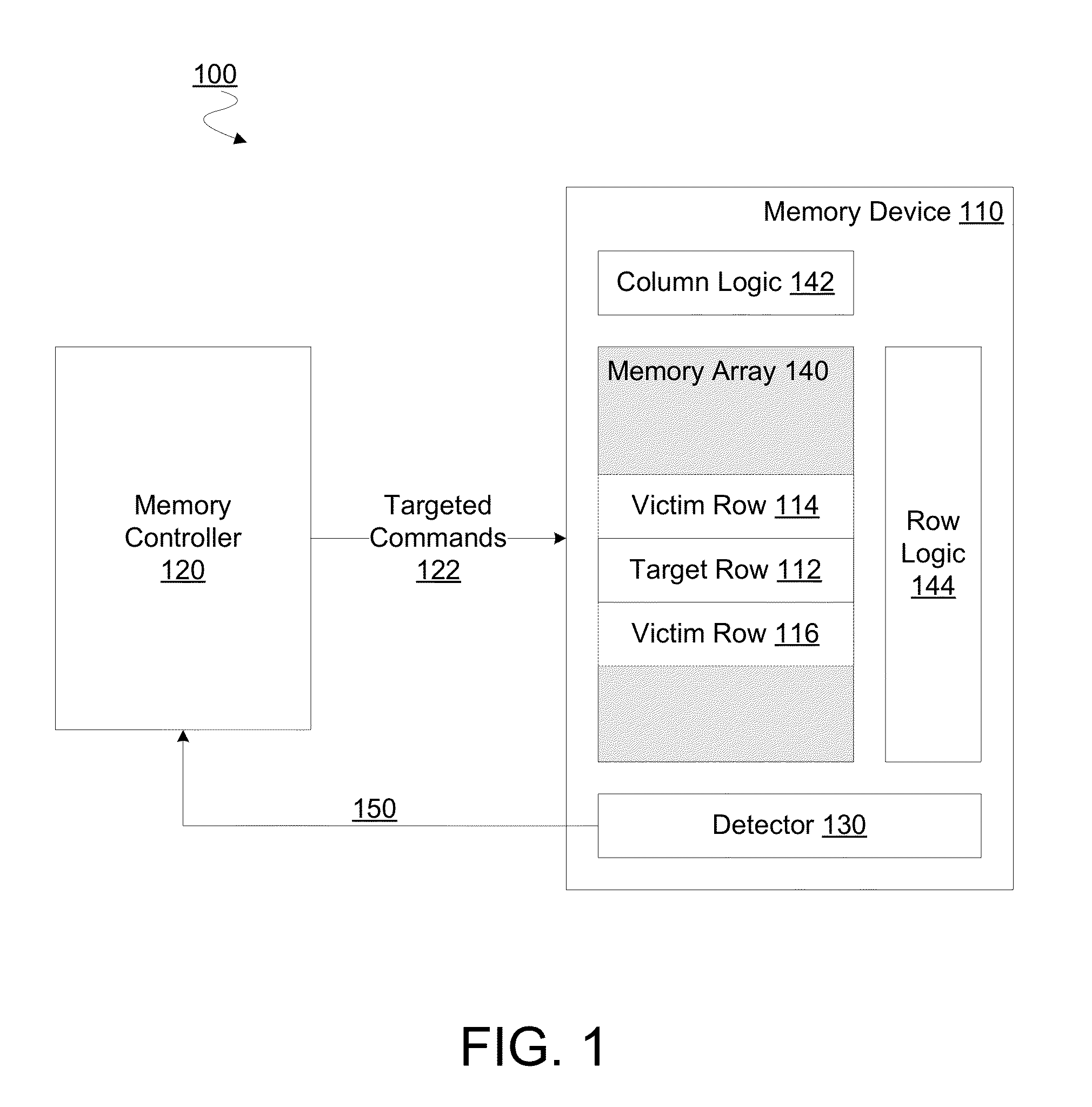

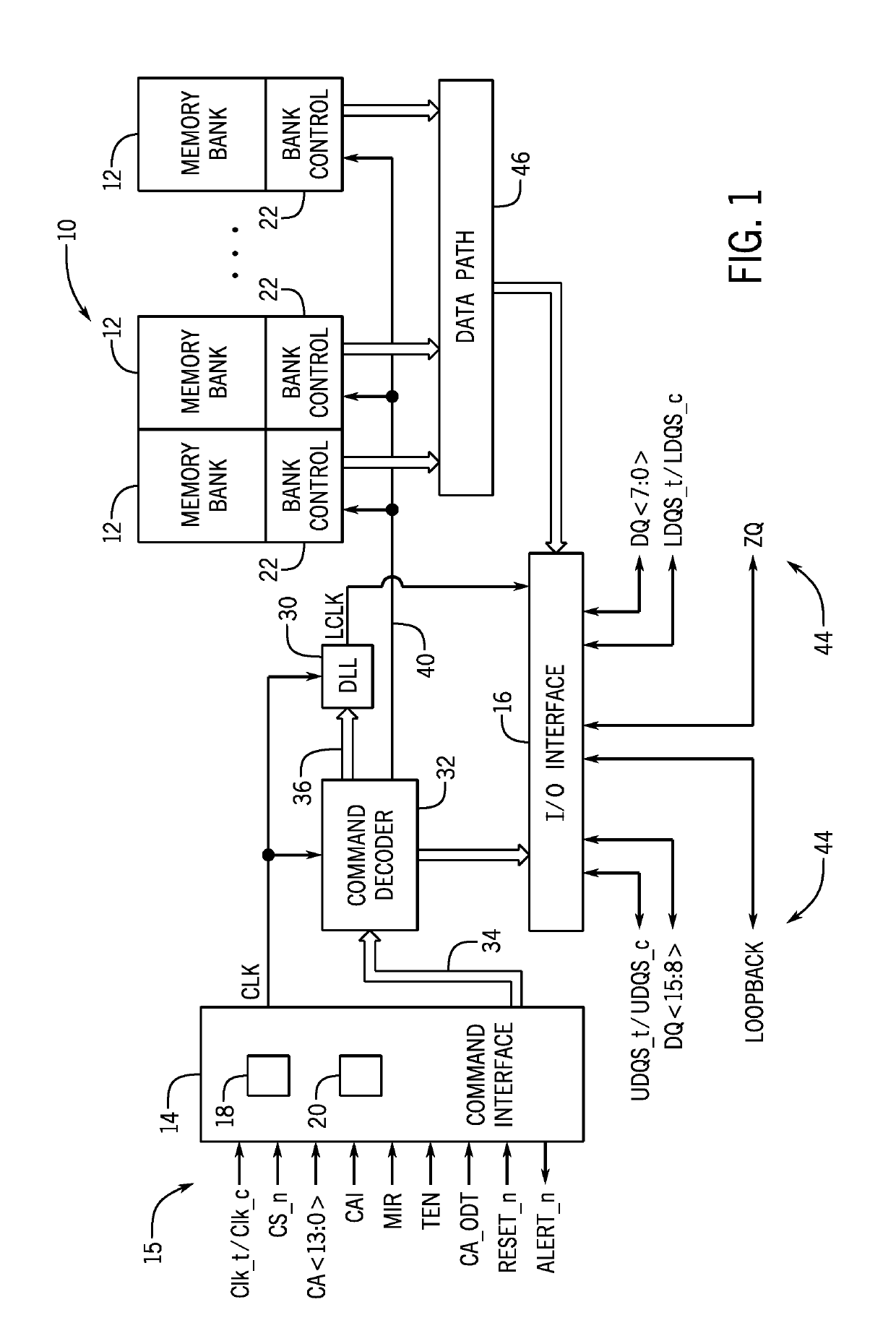

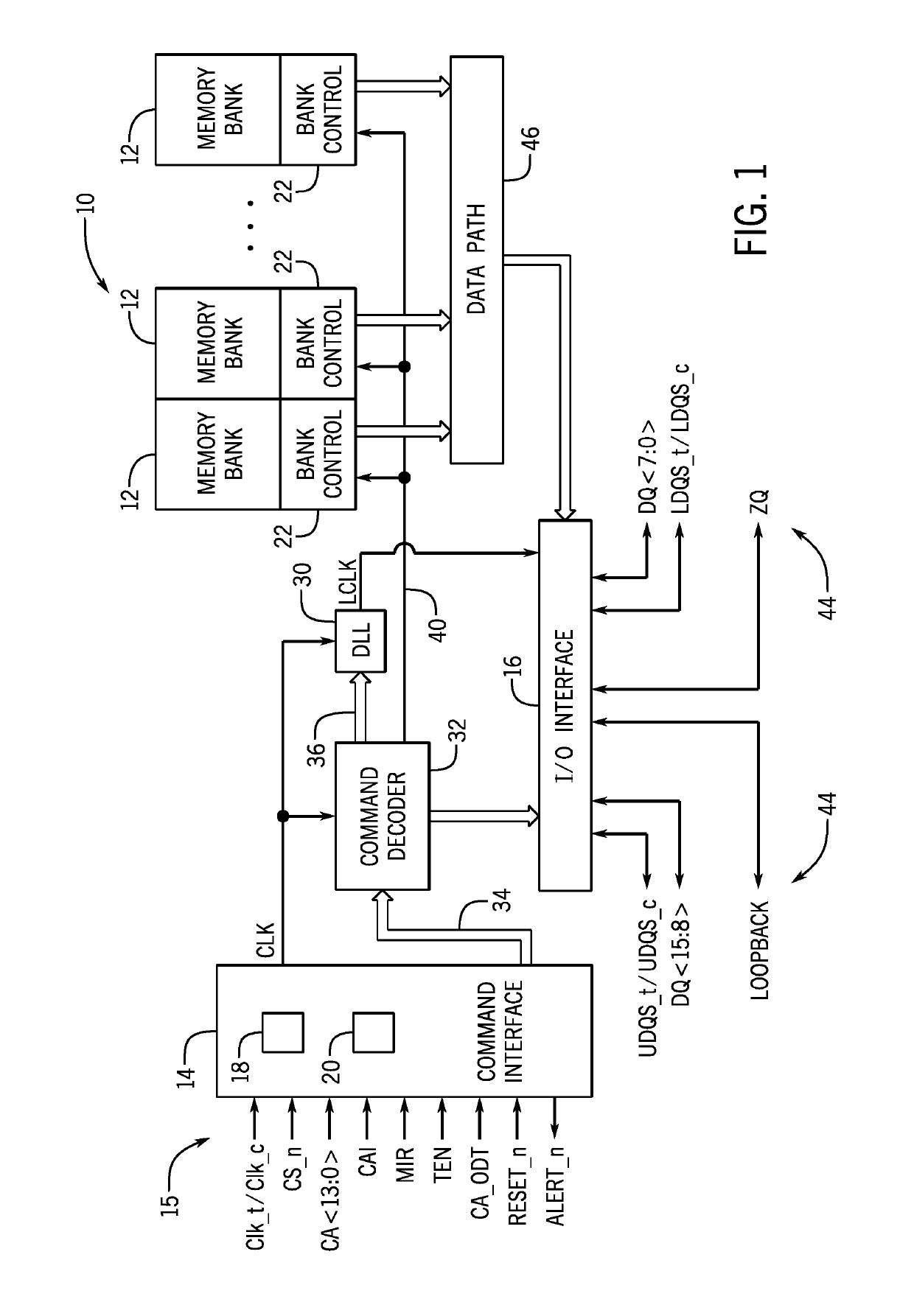

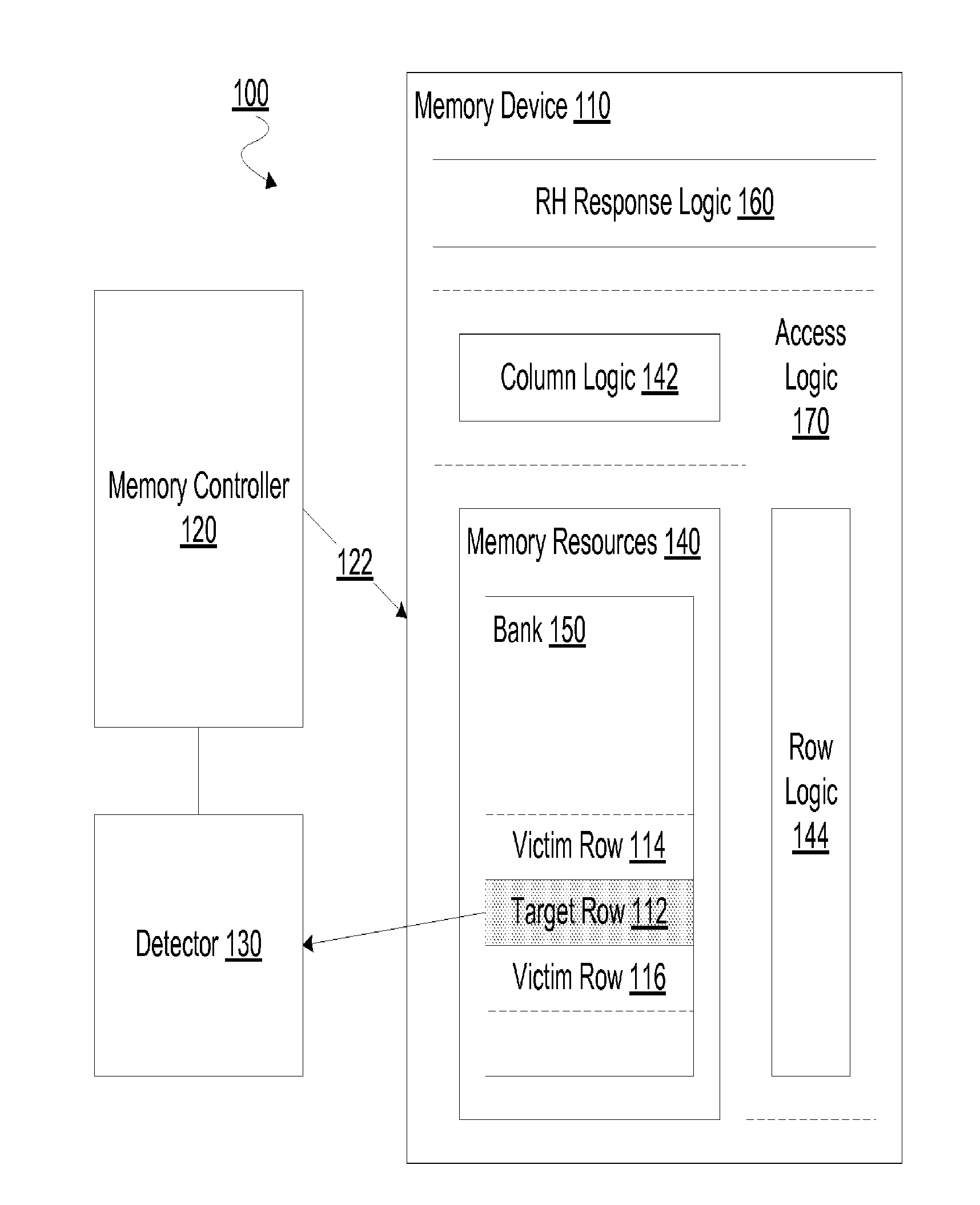

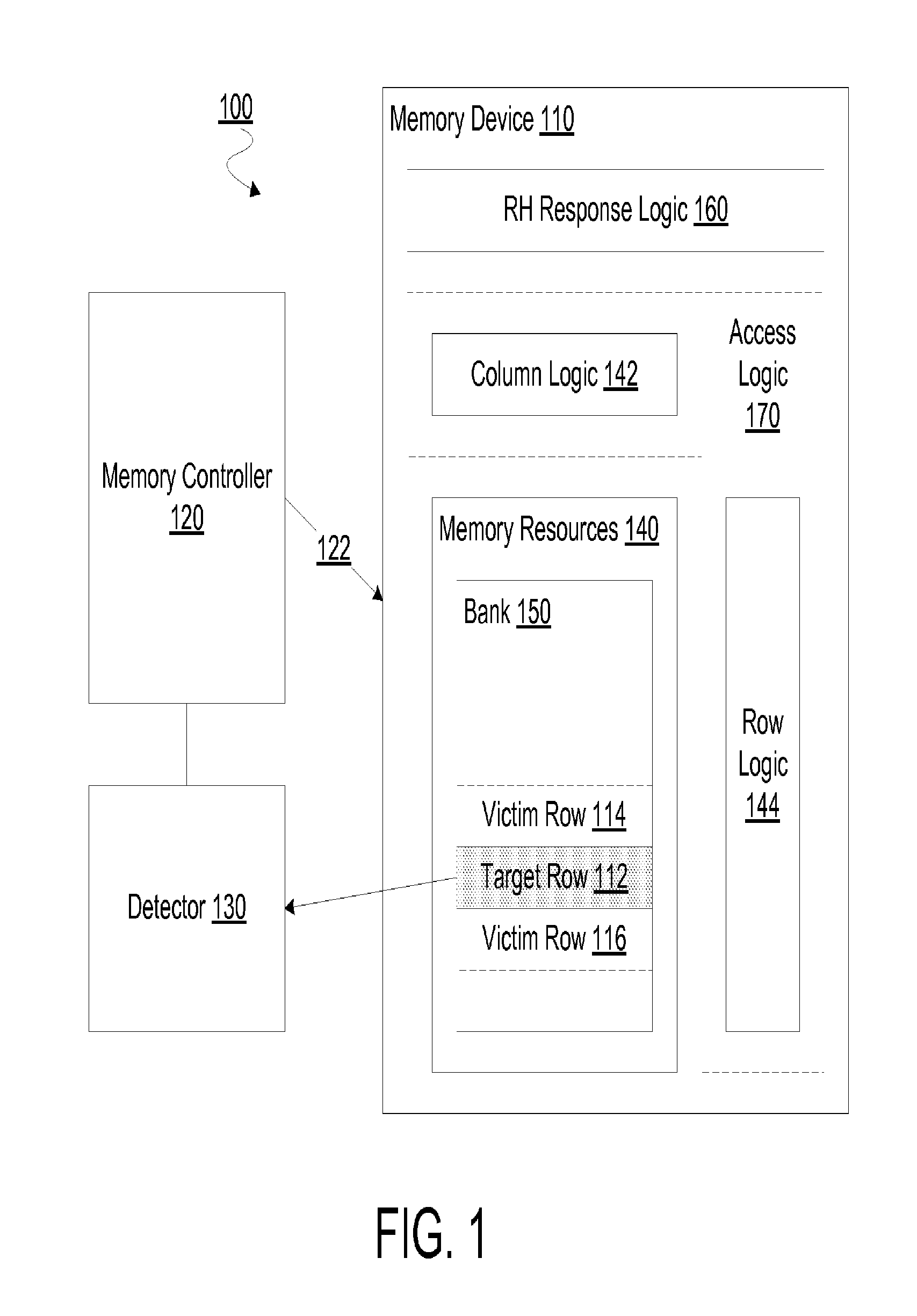

Method, apparatus and system for responding to a row hammer event

Techniques and mechanisms to facilitate an operational mode of a memory device to prepare for a targeted refresh of a row in memory. In an embodiment, the memory device performs one or more operations while in the mode to prepare for a future command from a memory controller, the command to implement, at least in part, a targeted refresh of a row in a first bank of the memory device. Prior to such a command, the memory device services another command from the memory controller. In another embodiment, servicing the other command includes the memory device accessing a second bank of the memory device while the memory device operates in the mode, and before completion of an expected future targeted row refresh.

Owner:INTEL CORP

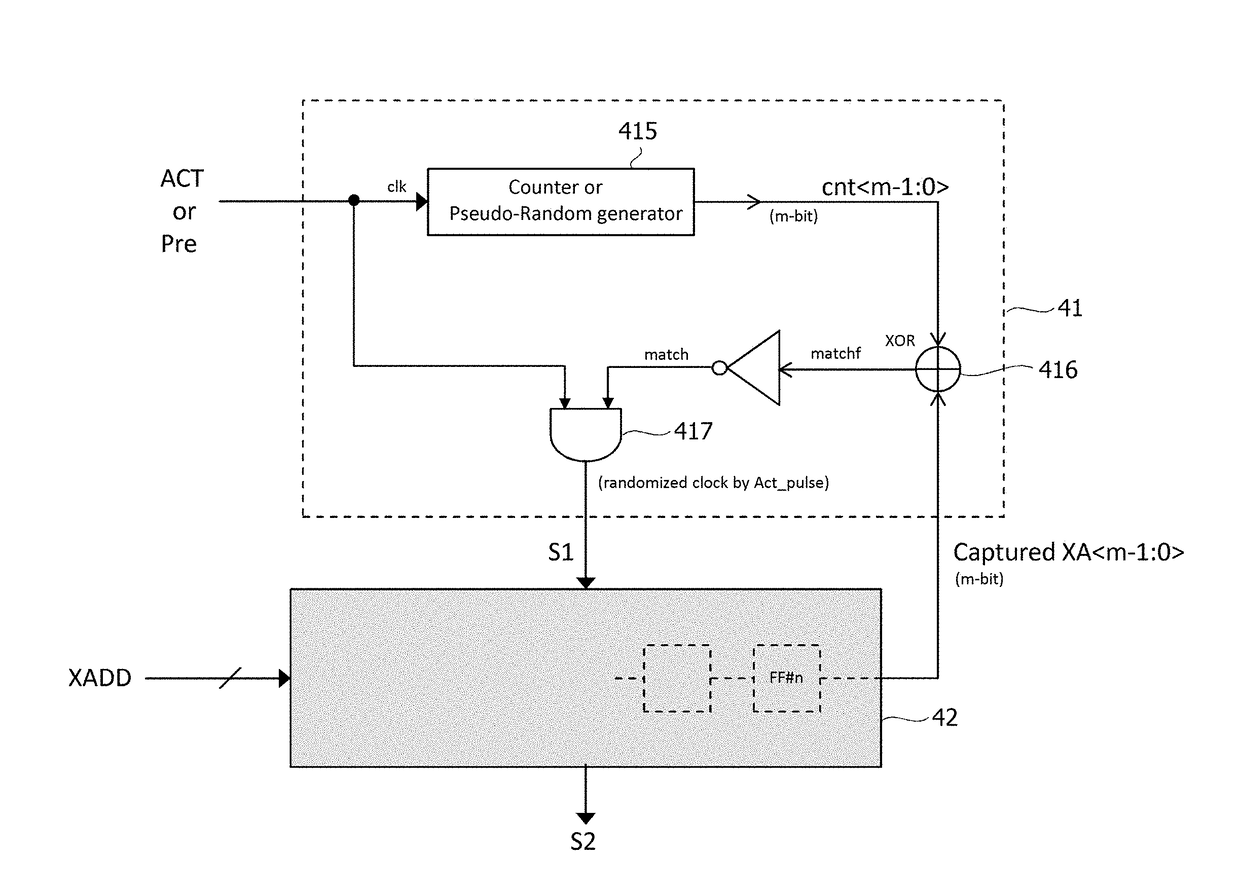

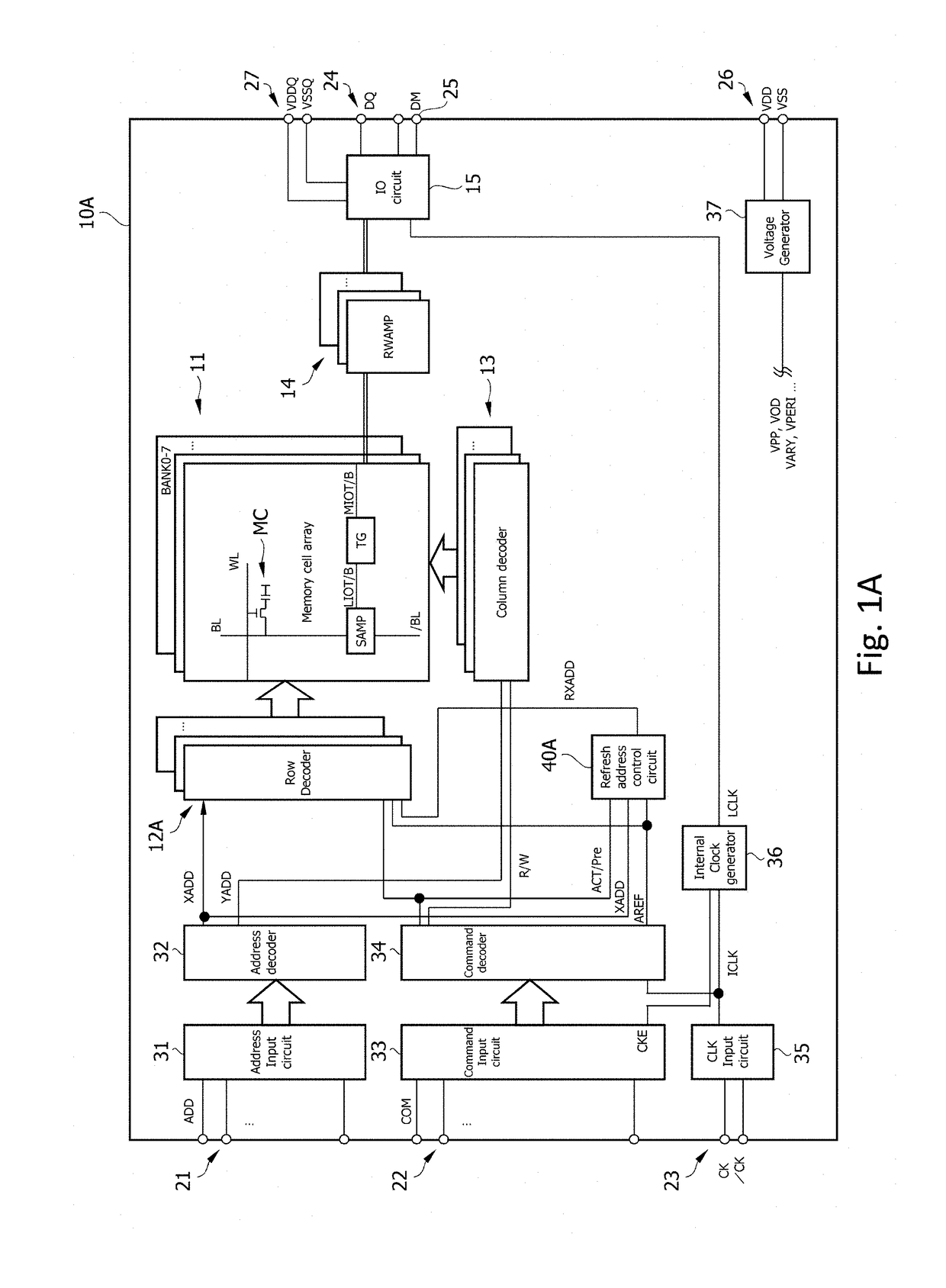

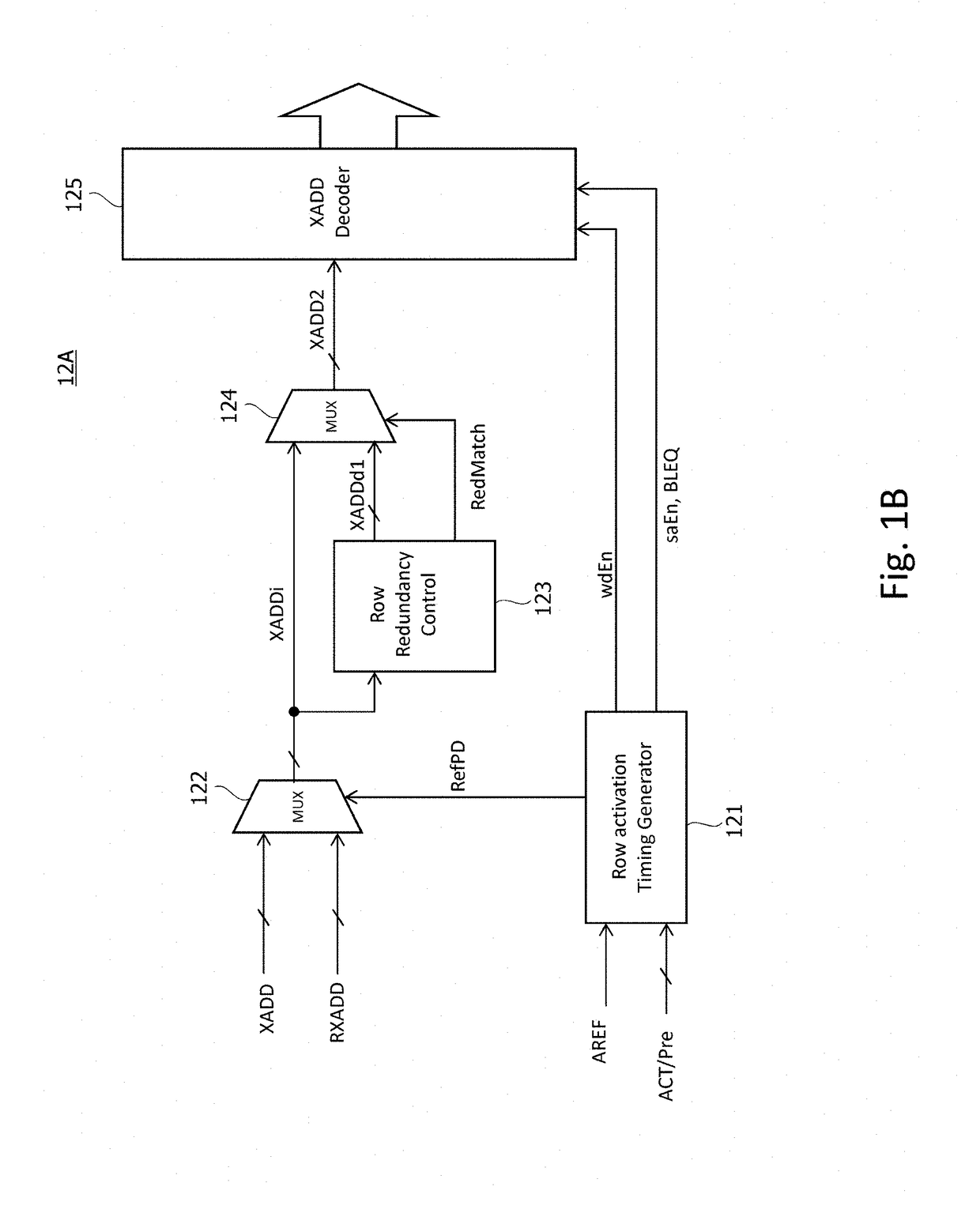

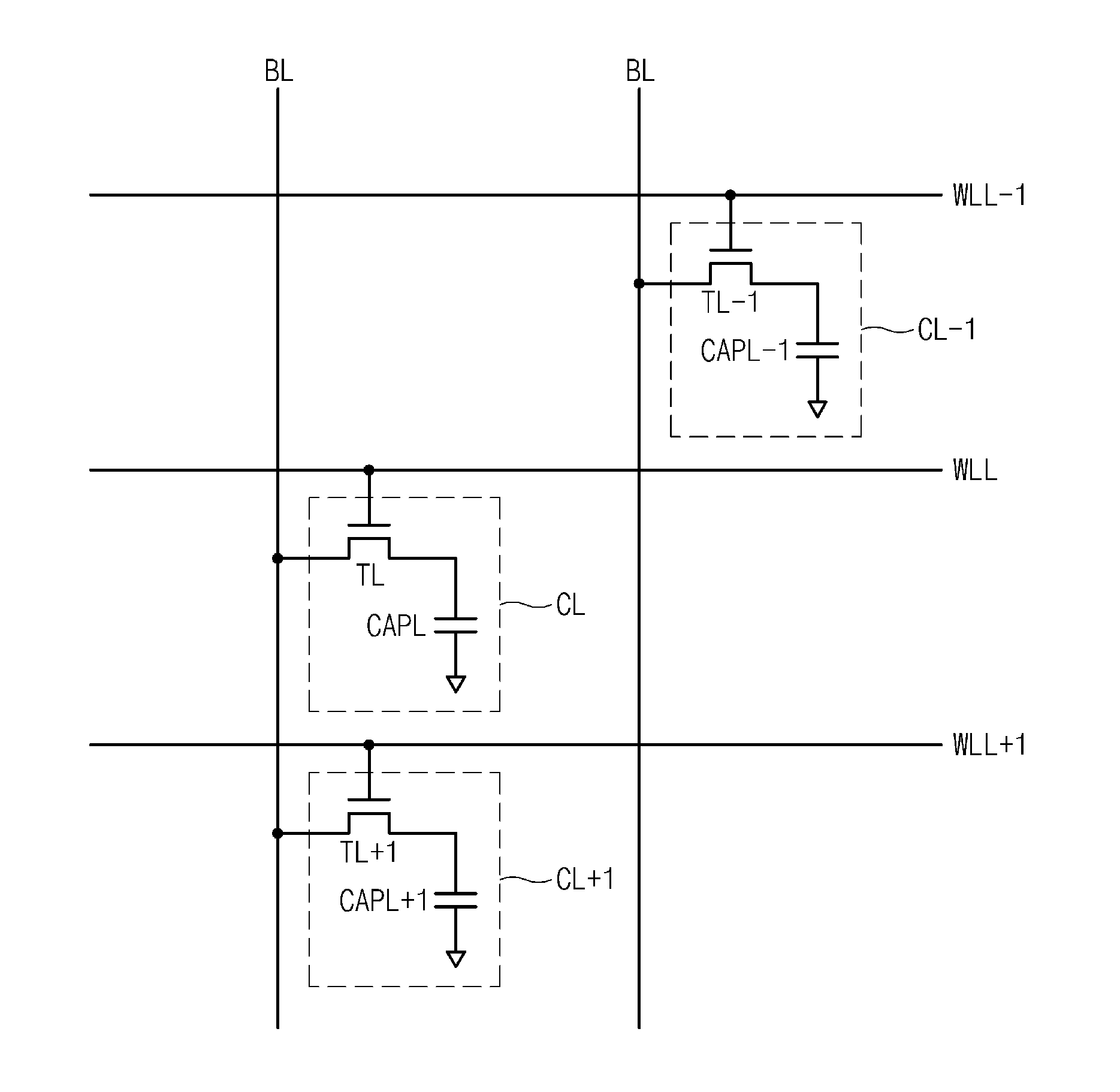

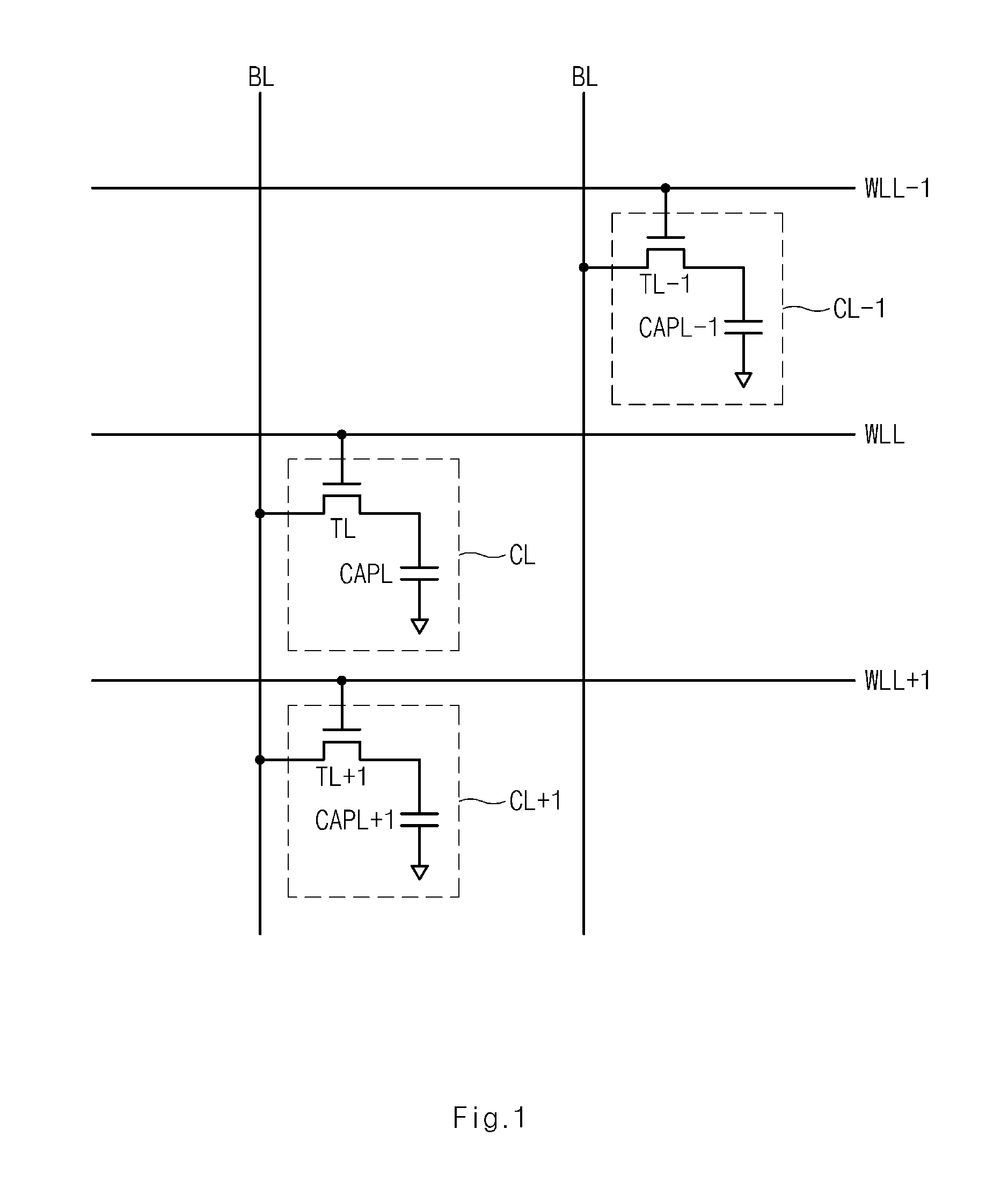

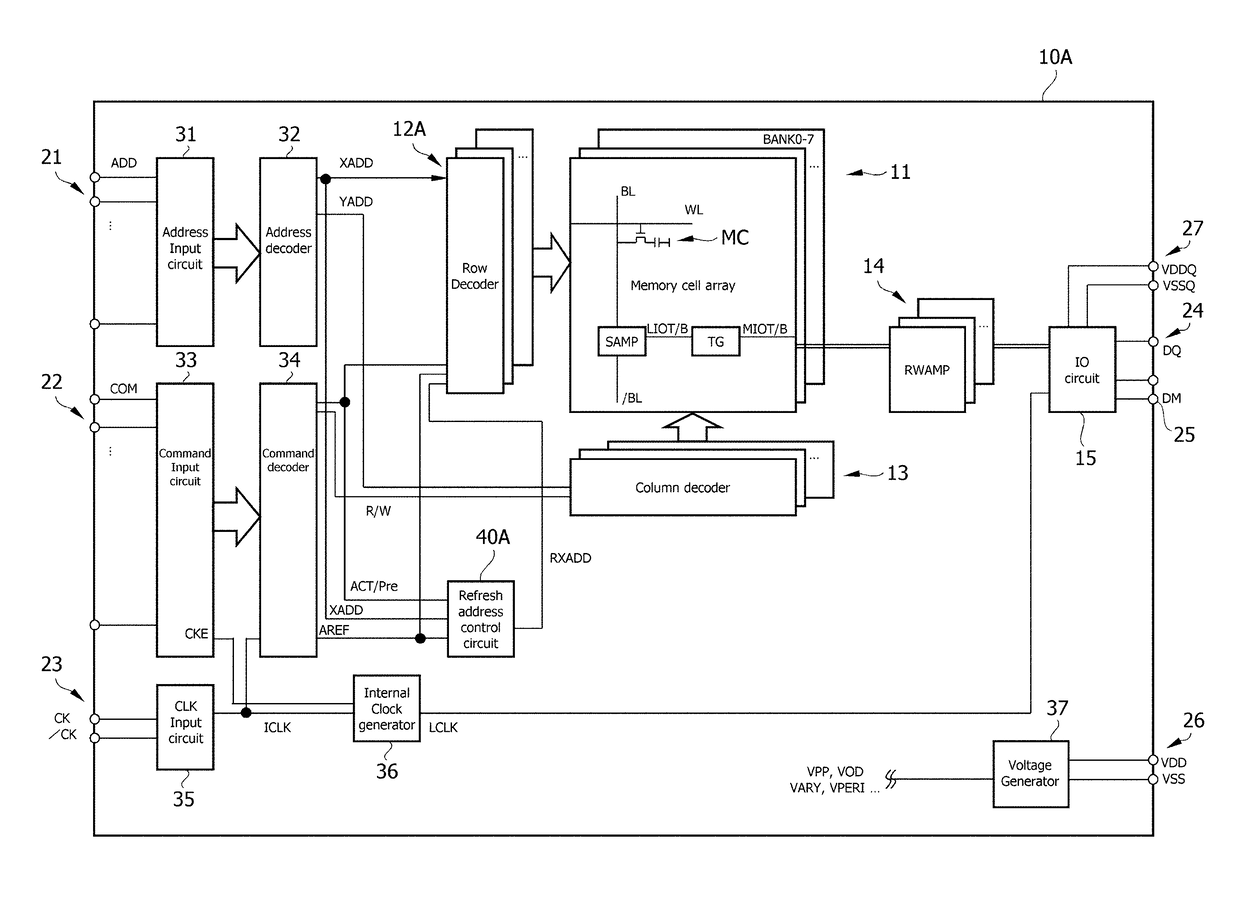

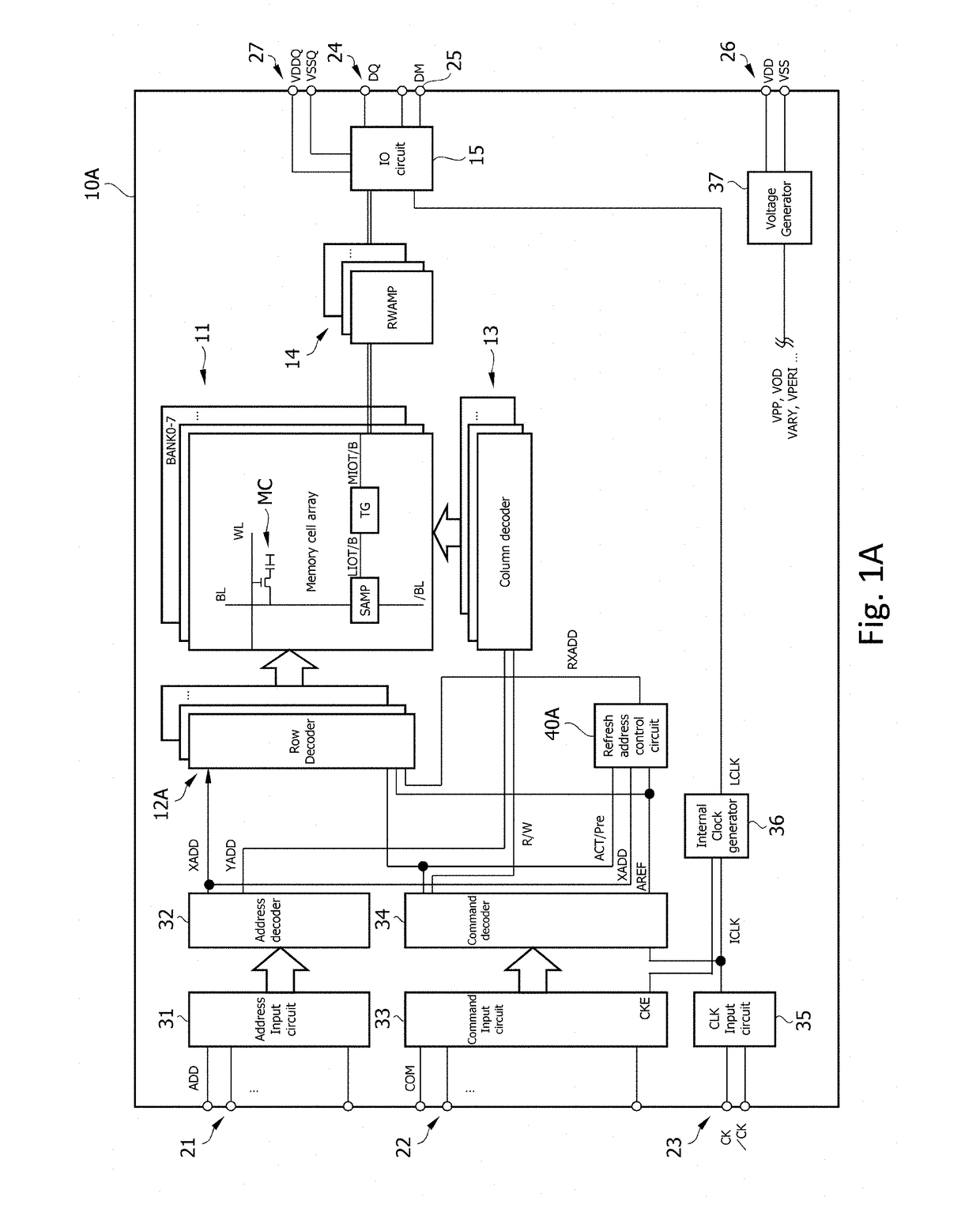

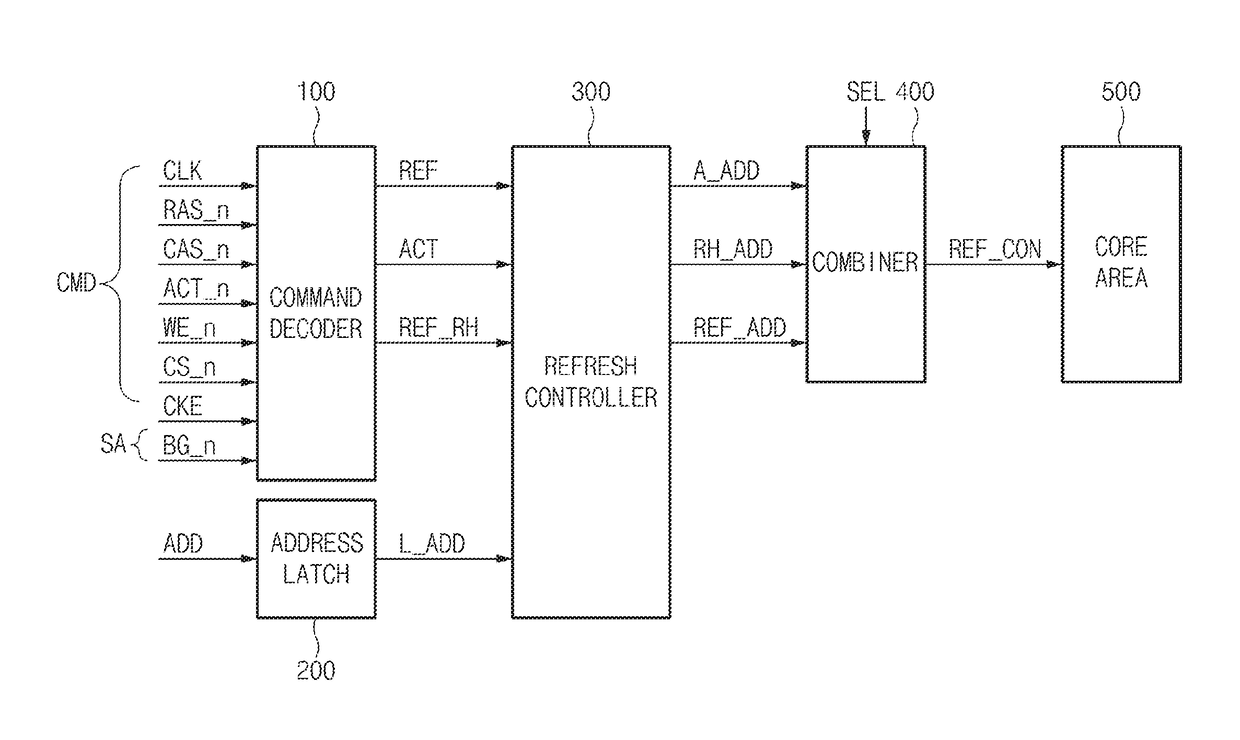

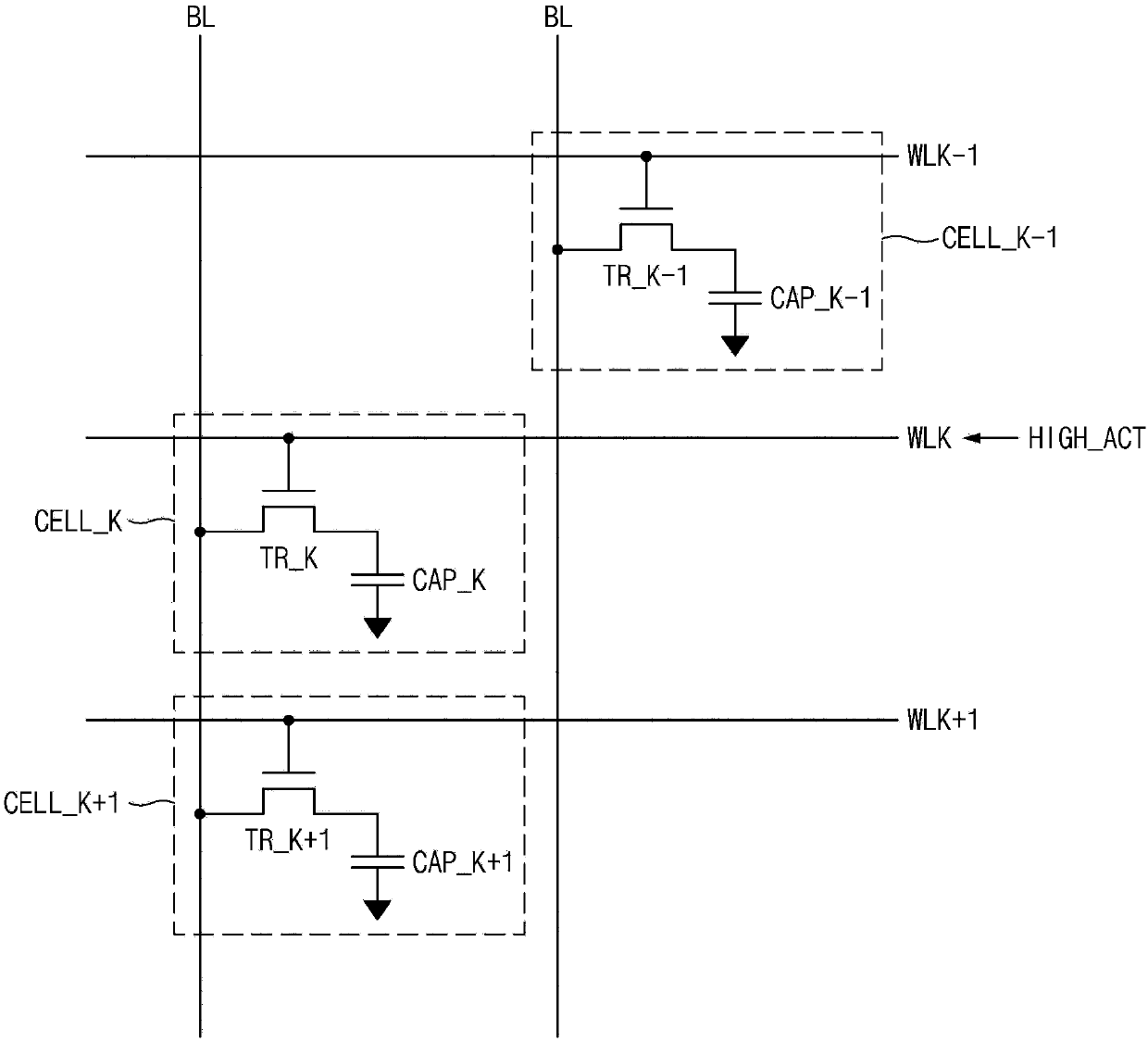

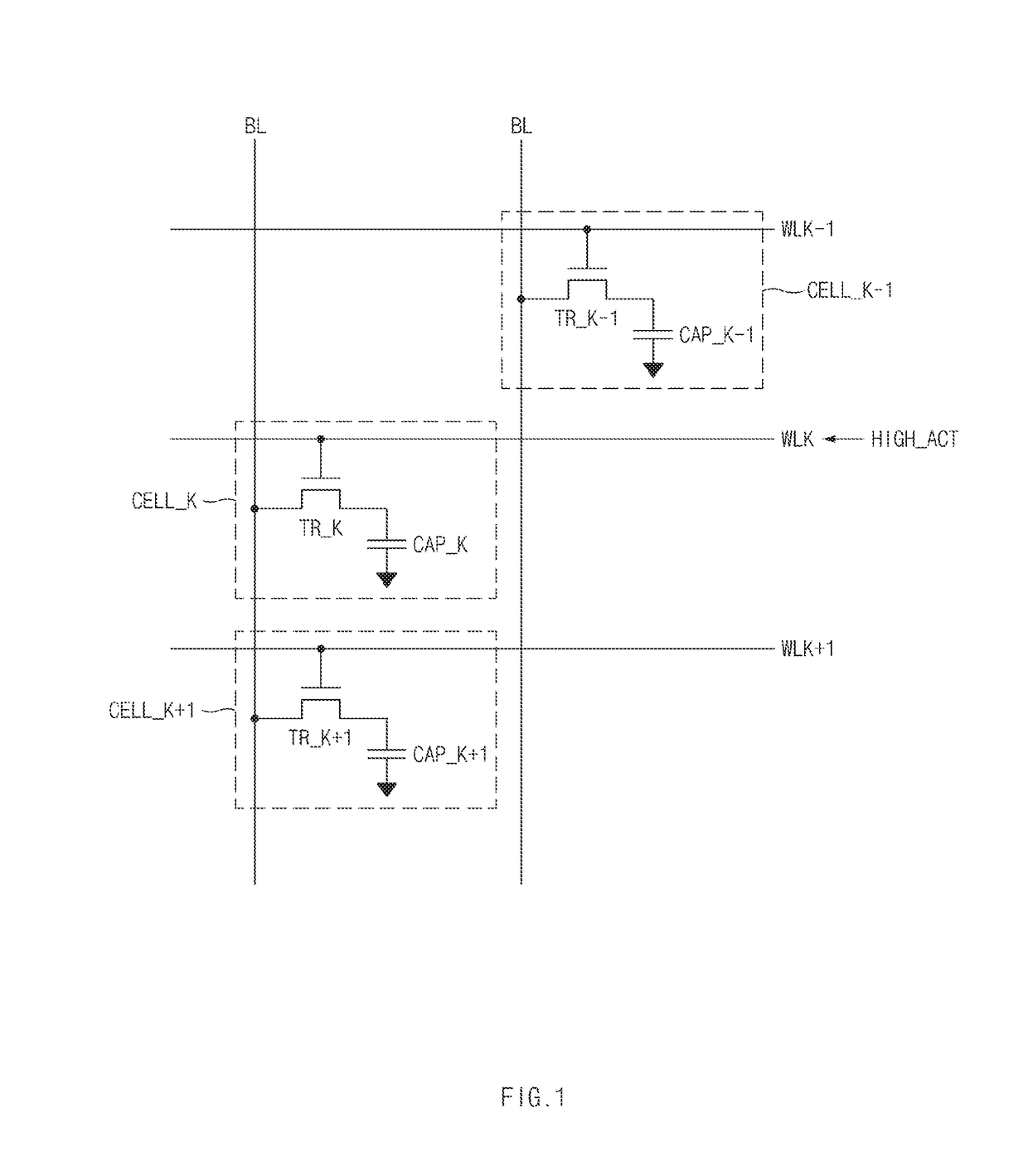

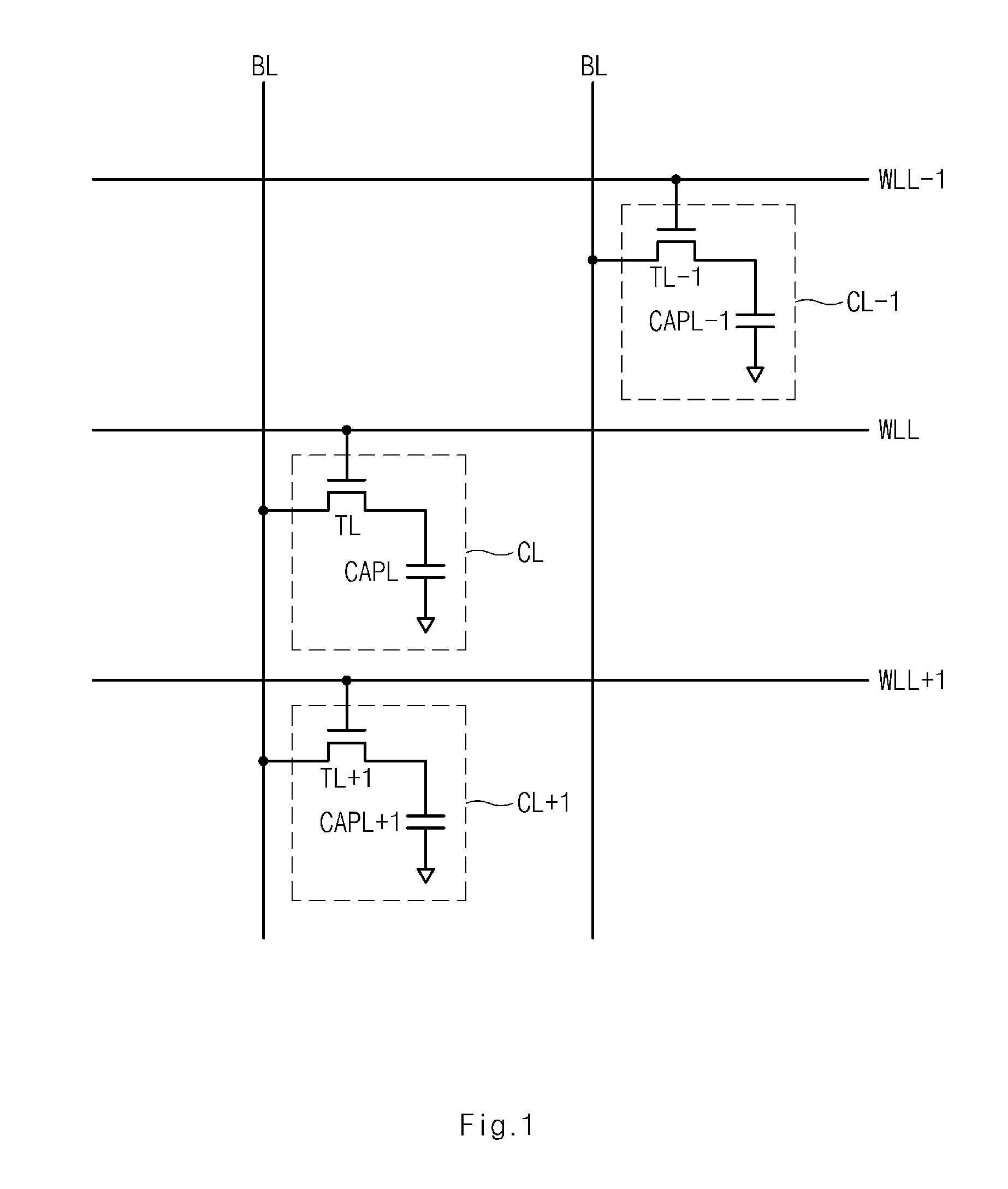

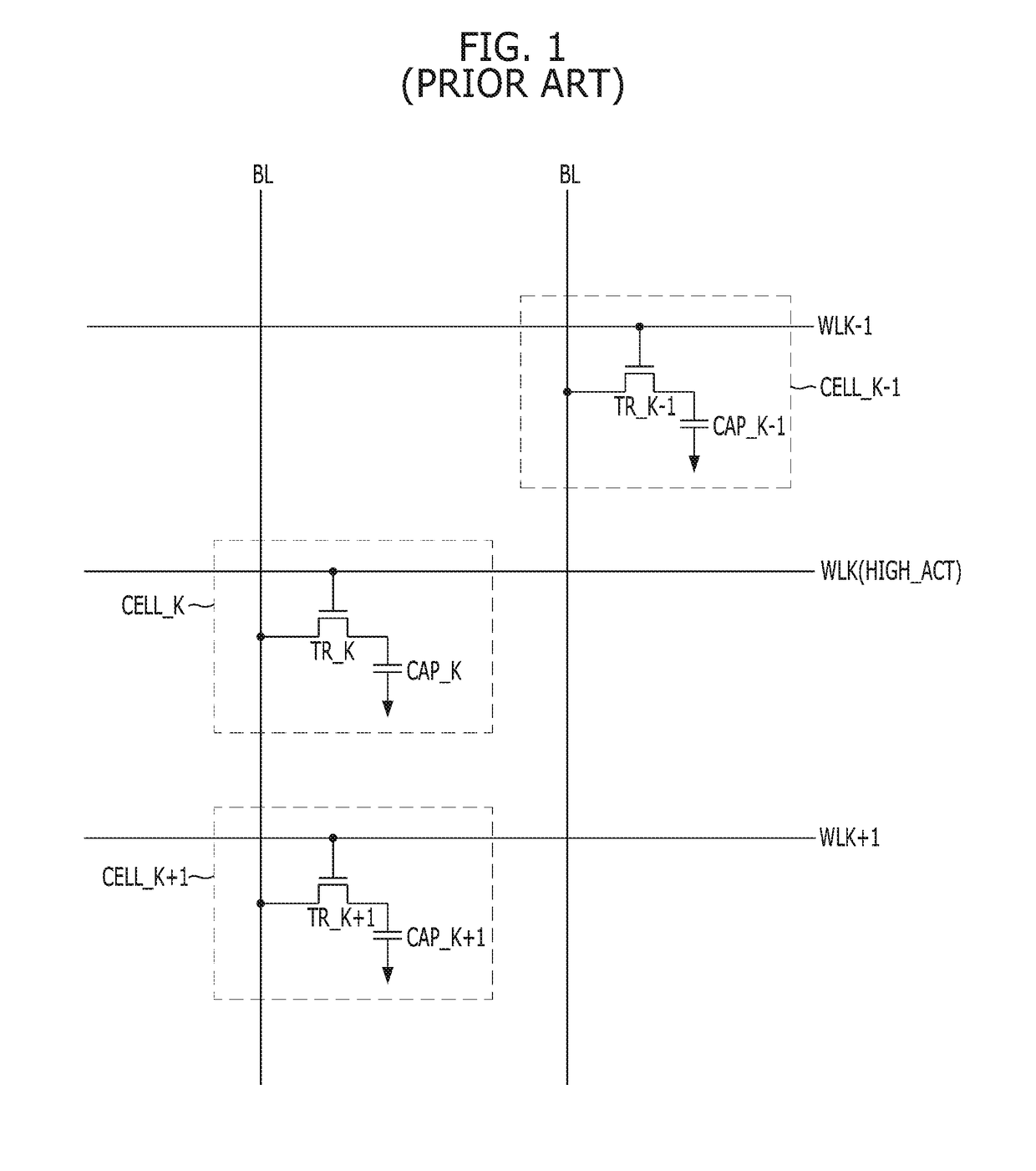

Semiconductor device

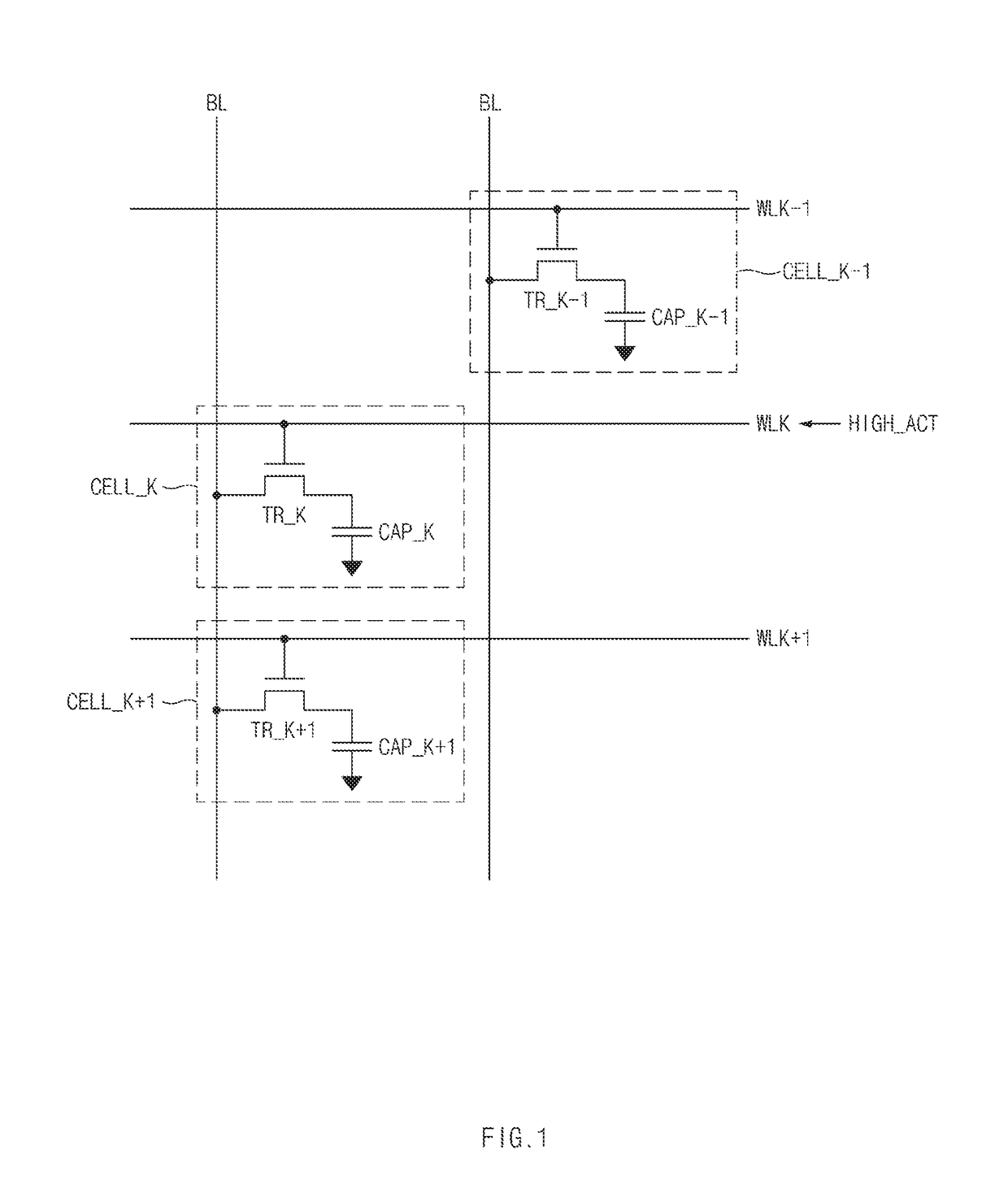

A semiconductor device according to an aspect of the present invention has: a plurality of memory cells MC; a plurality of word lines WL each coupled to a corresponding one of the plurality of memory cells MC; and a control circuit that intermittently monitors accesses to the plurality of word lines WL, stores / erases some captured row-addresses in a first number of registers, and detects, by comparison with stored addresses, in response to a first number of accesses to one of the word lines WL in a first period of time. According to the present invention, access histories can be precisely analyzed by a small-scale circuit configuration, and measures against, for example, the Row Hammer problem, etc. can be taken.

Owner:MICRON TECH INC

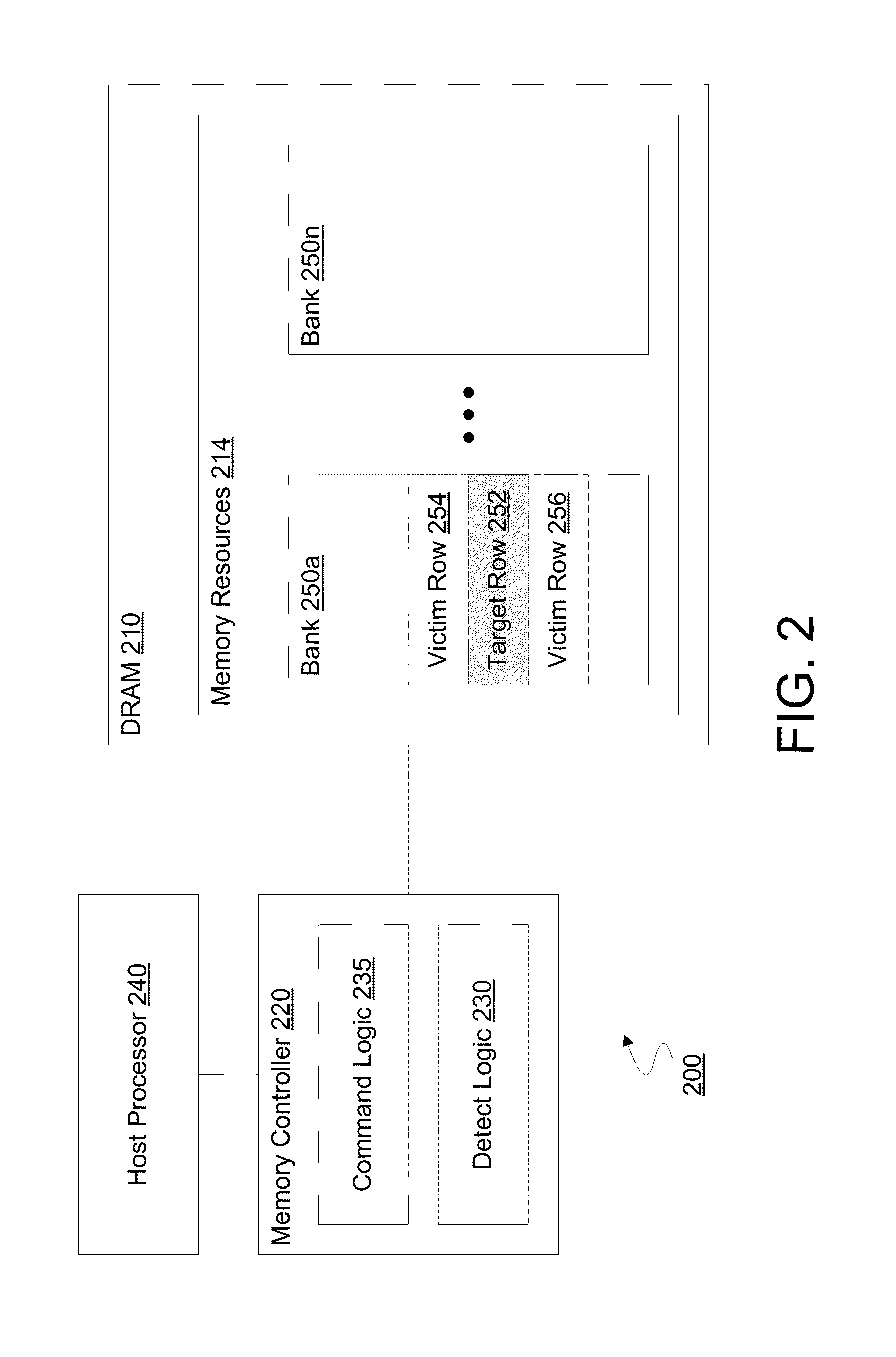

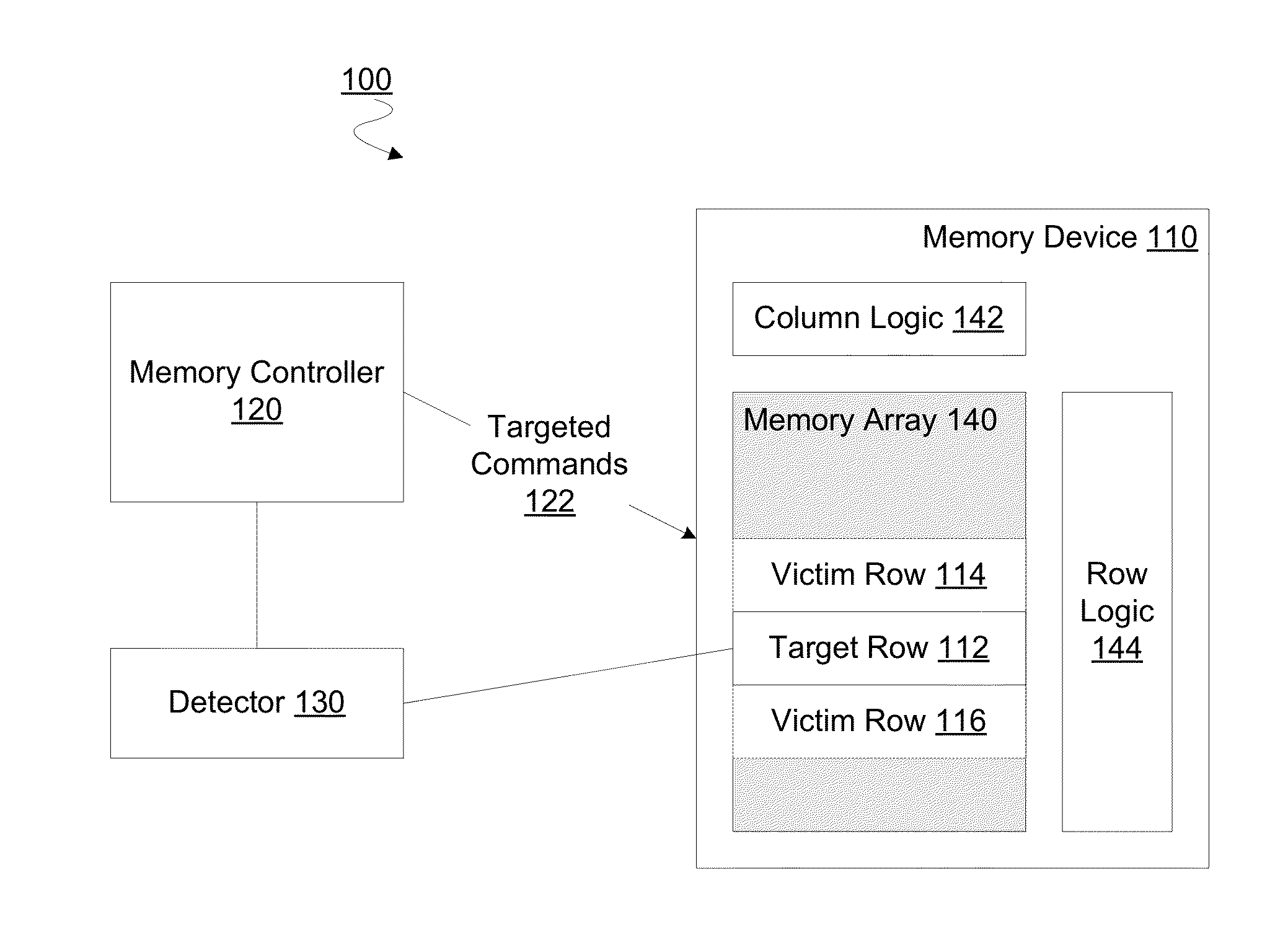

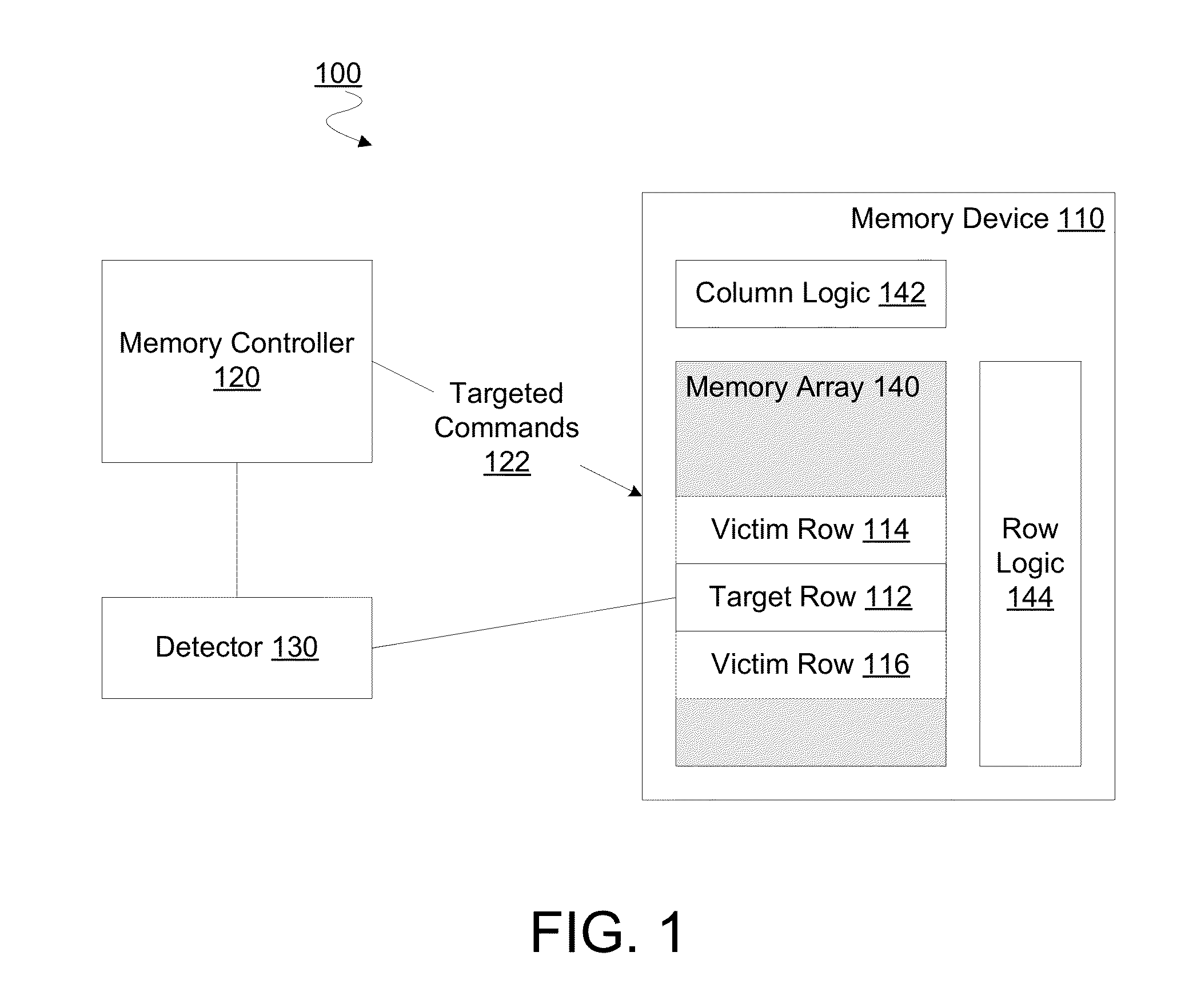

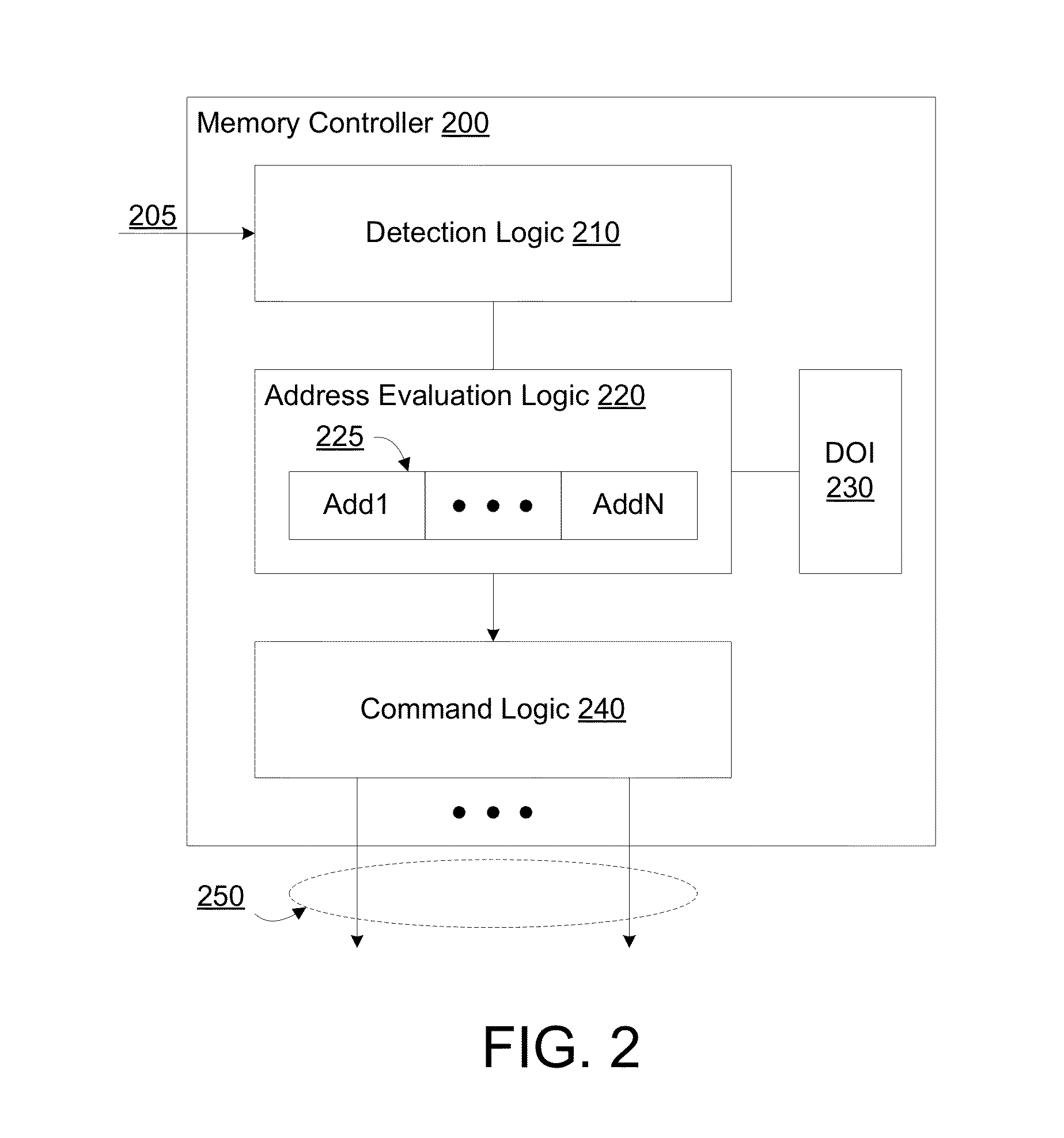

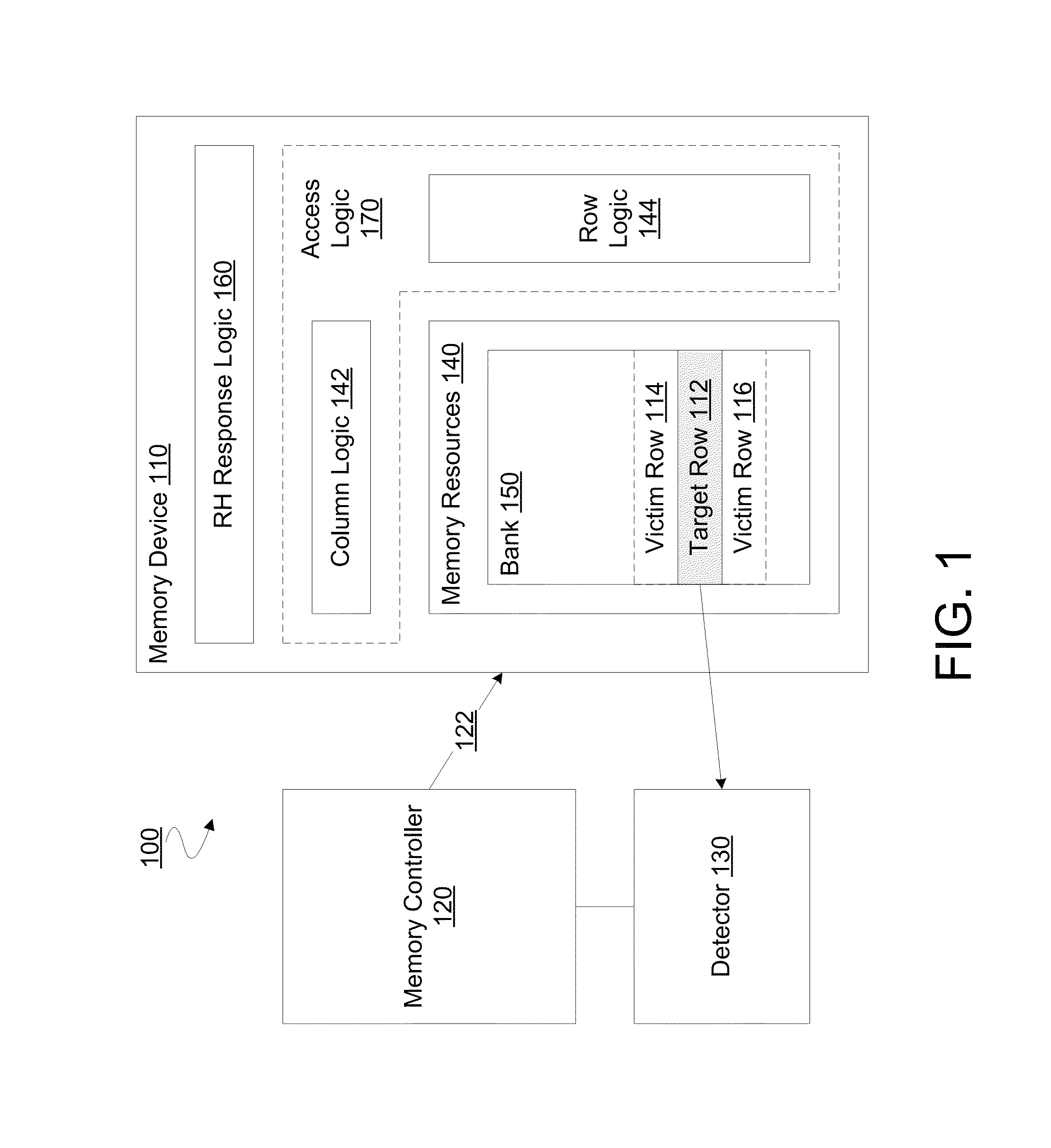

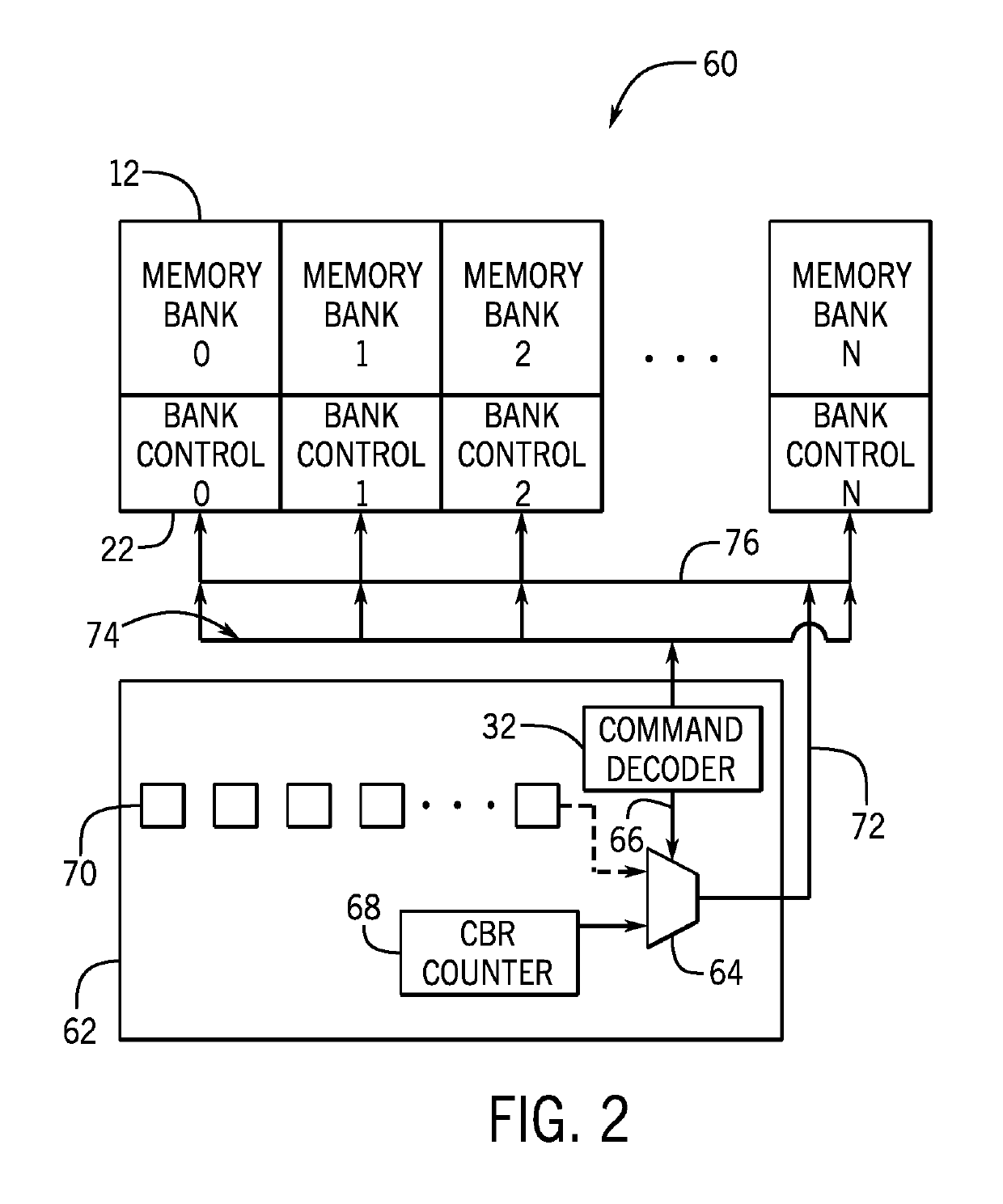

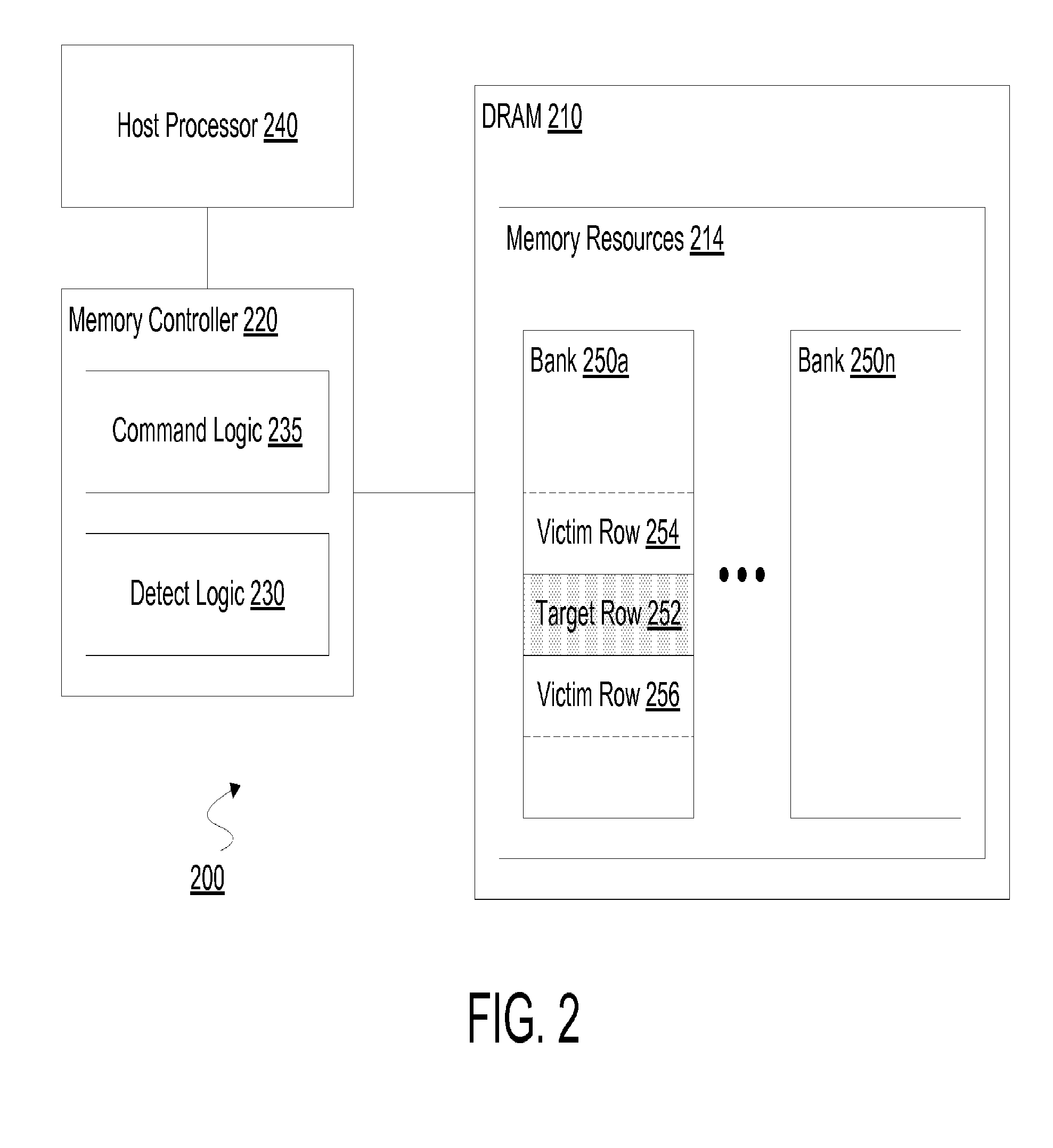

Method, apparatus and system for providing a memory refresh

A memory controller to implement targeted refreshes of potential victim rows of a row hammer event. In an embodiment, the memory controller receives an indication that a specific row of a memory device is experiencing repeated accesses which threaten the integrity of data in one or more victim rows physically adjacent to the specific row. The memory controller accesses default offset information in the absence of address map information which specifies an offset between physically adjacent rows of the memory device. In another embodiment, the memory controller determines addresses for potential victim rows based on the default offset information. In response to the received indication of the row hammer event, the memory controller sends for each of the determined plurality of addresses a respective command to the memory device, where the commands are for the memory device to perform targeted refreshes of potential victim rows.

Owner:INTEL CORP

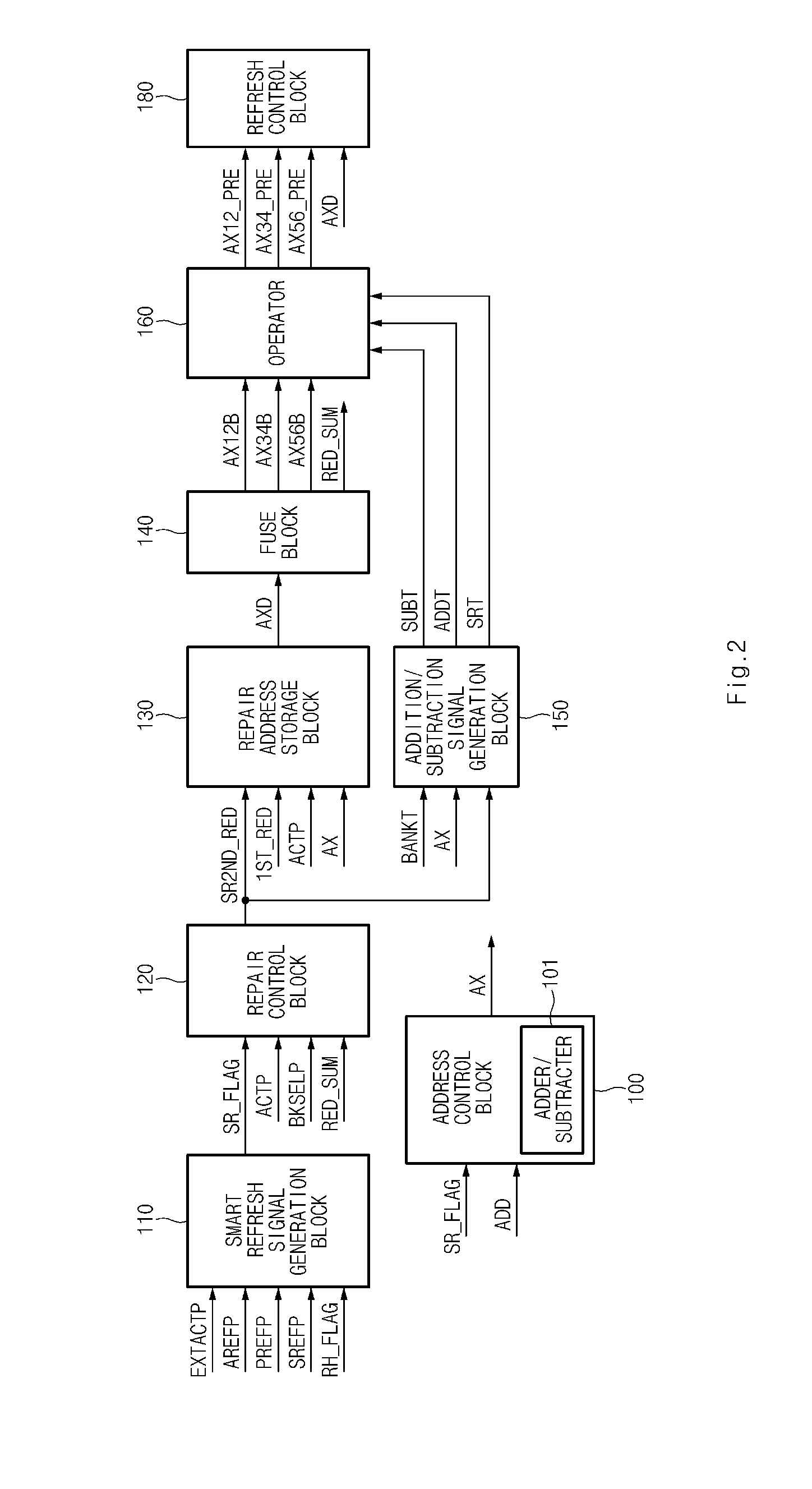

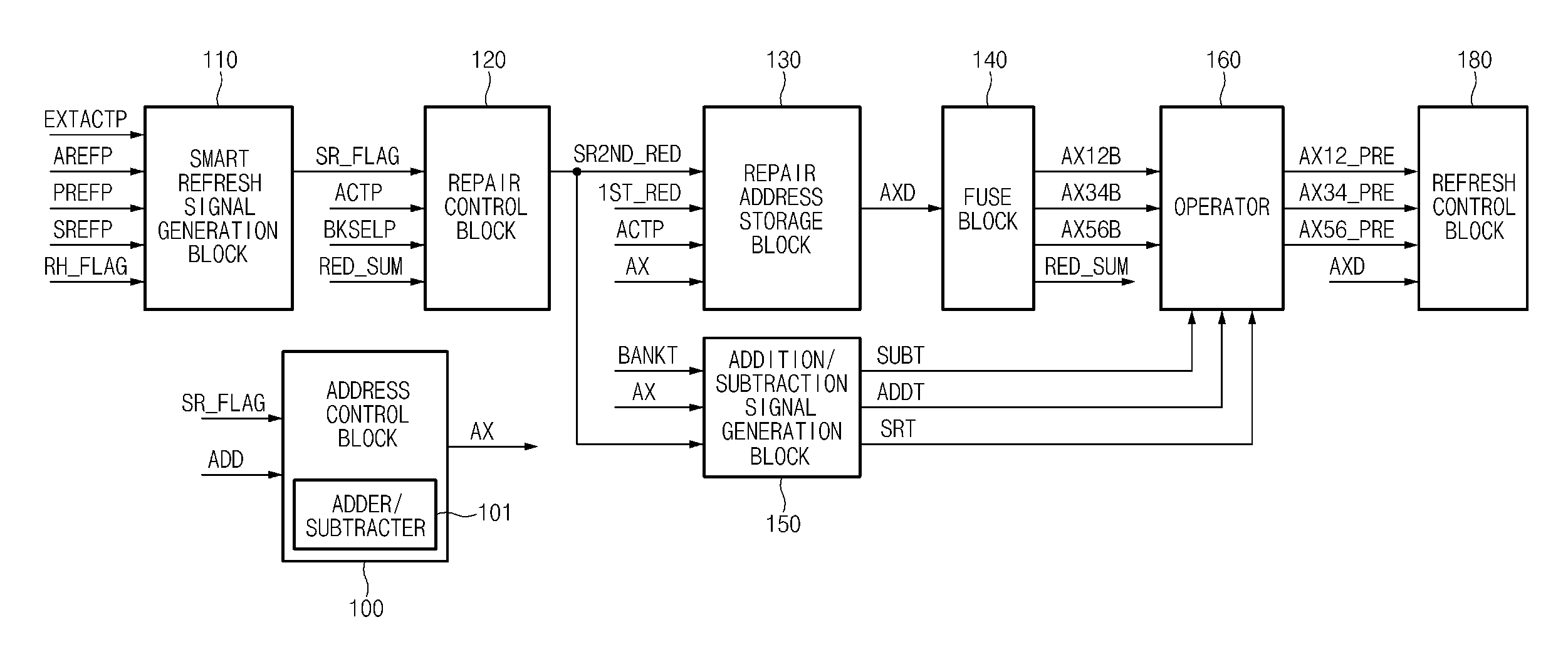

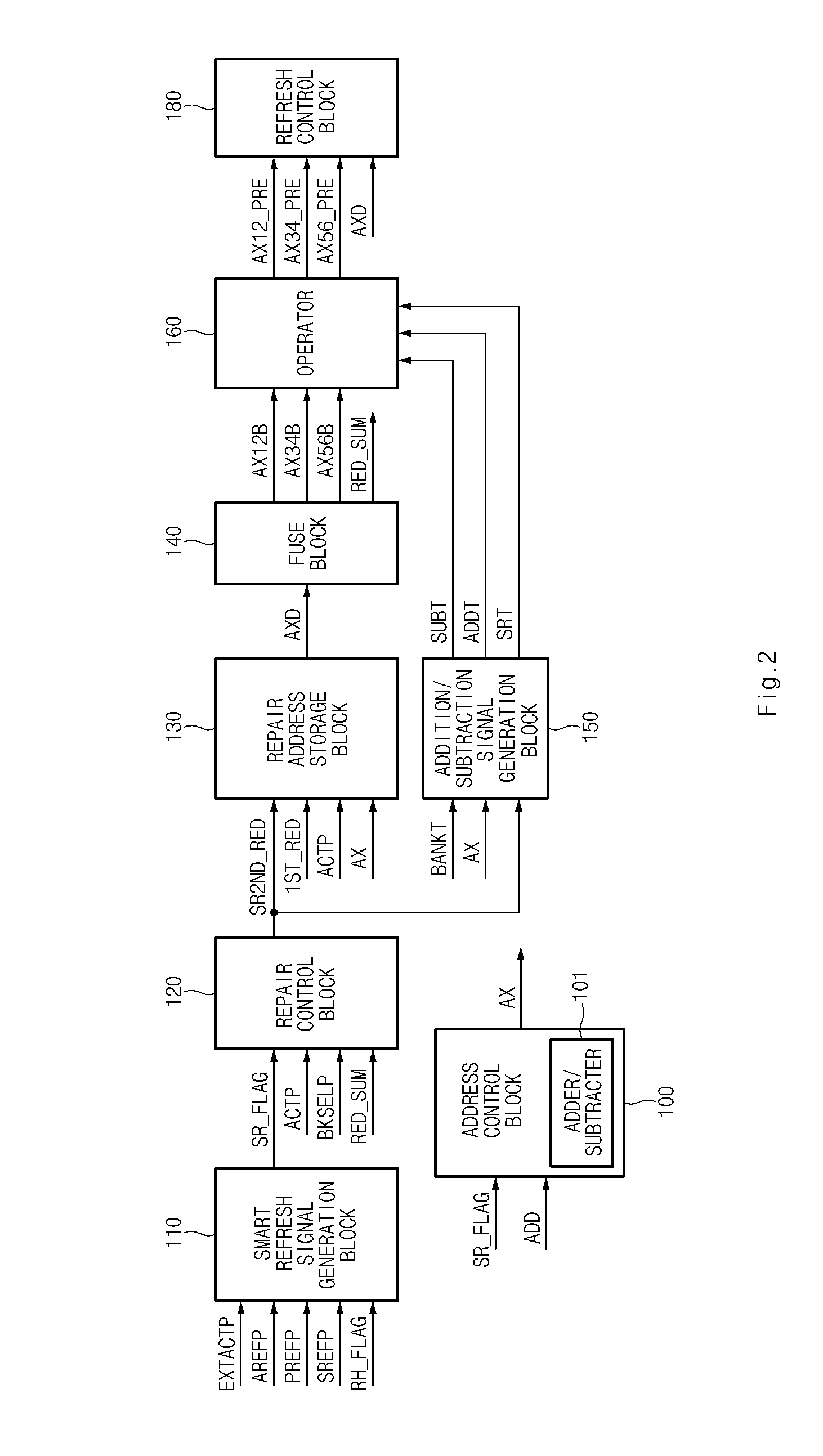

Smart refresh device

A smart refresh device includes an address control block configured to determine whether a specific row address is a row hammer address, and invert a first row hammer address and perform an addition / subtraction of an address; a repair control block configured to determine whether the row hammer address is a repaired address and output a stored repair address as a second repair control signal; a repair address storage block configured to store an output address of the address control block and output a stored address as a latch address; a fuse block configured to output a repair signal representing information on a repair address to the repair control block, and output a decoding signal according to the latch address; and an operator configured to add and subtract the decoding signal according to an addition signal and a subtraction signal.

Owner:SK HYNIX INC

Semiconductor device

A semiconductor device according to an aspect of the present invention has: a plurality of memory cells MC; a plurality of word lines WL each coupled to a corresponding one of the plurality of memory cells MC; and a control circuit that intermittently monitors accesses to the plurality of word lines WL, stores / erases some captured row-addresses in a first number of registers, and detects, by comparison with stored addresses, in response to a first number of accesses to one of the word lines WL in a first period of time. According to the present invention, access histories can be precisely analyzed by a small-scale circuit configuration, and measures against, for example, the Row Hammer problem, etc. can be taken.

Owner:MICRON TECH INC

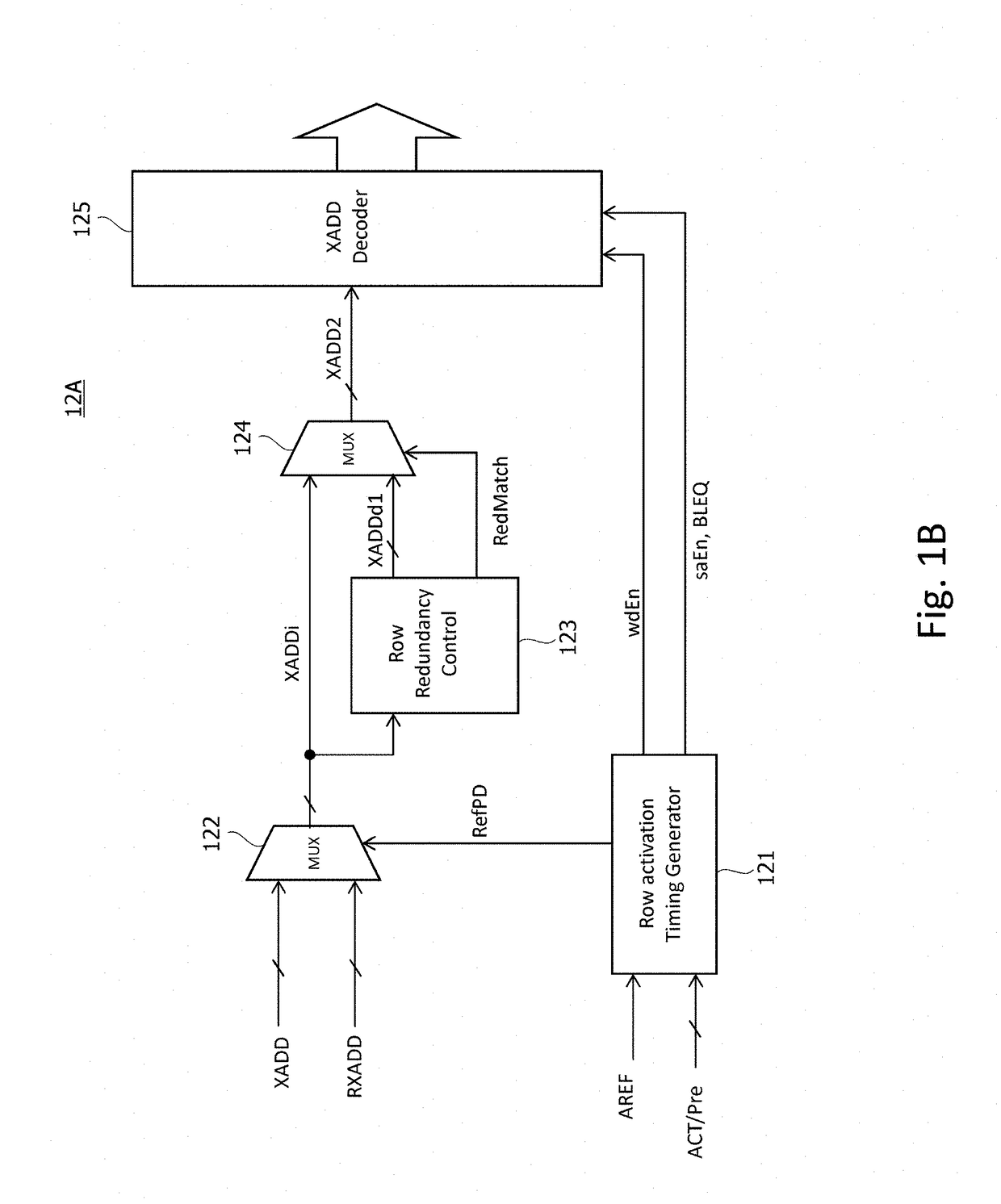

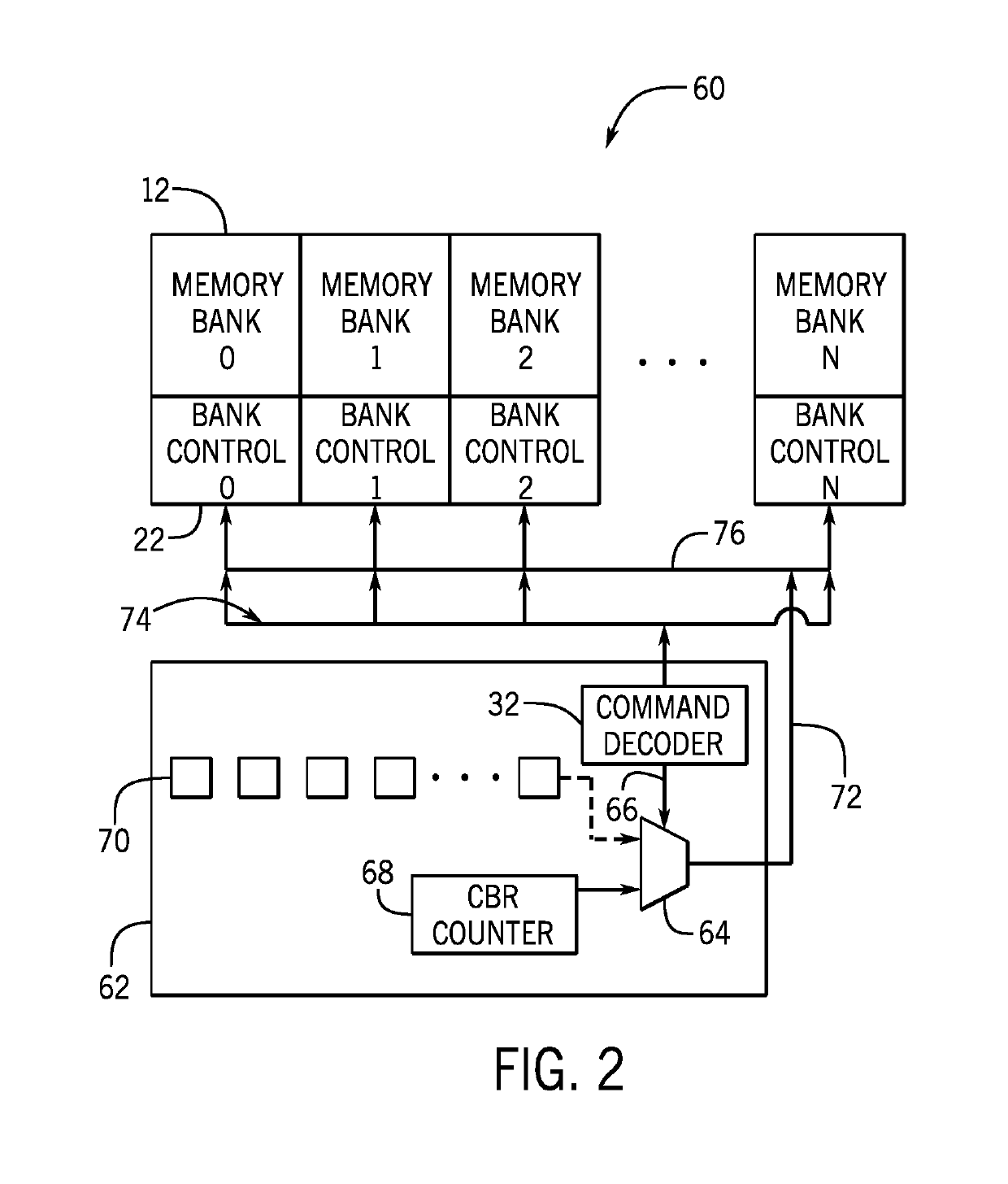

Refresh control device and semiconductor device including the same

ActiveUS9818469B1Memory architecture accessing/allocationInput/output to record carriersPower semiconductor deviceComputer hardware

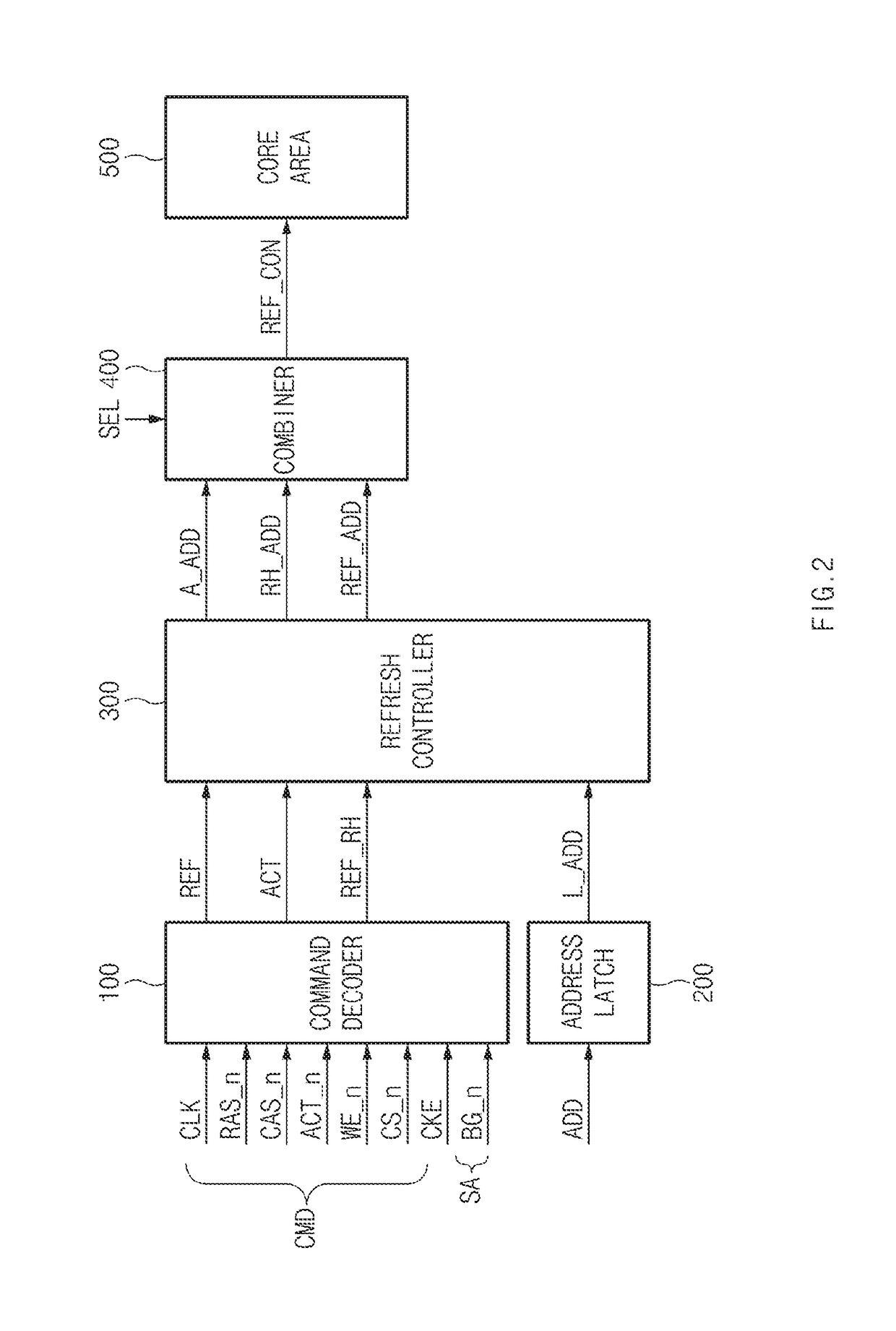

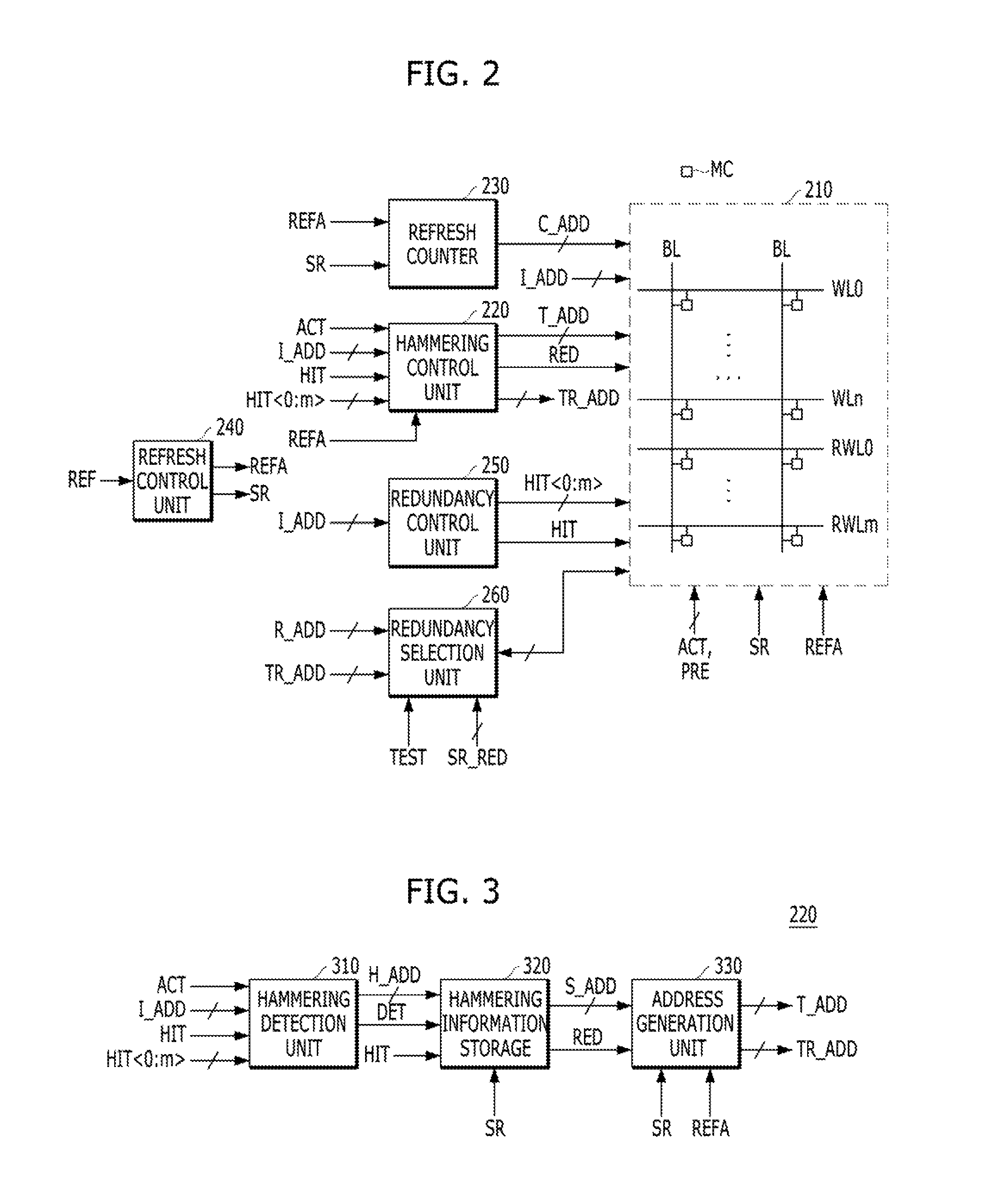

A refresh control device may include a command decoder configured to decode a command signal and a specific address, and output a refresh signal, an active signal and a row hammer refresh signal. The refresh control device may include a refresh controller configured to output an active address, a row hammer address and a refresh address based on the refresh signal, the active signal, the row hammer refresh signal and a latch address. The refresh control device may include a combiner configured to combine the active address, the row hammer address and the refresh address, and output a refresh control signal.

Owner:SK HYNIX INC

Method, apparatus and system for responding to a row hammer event

Techniques and mechanisms to facilitate an operational mode of a memory device to prepare for a targeted refresh of a row in memory. In an embodiment, the memory device performs one or more operations while in the mode to prepare for a future command from a memory controller, the command to implement, at least in part, a targeted refresh of a row in a first bank of the memory device. Prior to such a command, the memory device services another command from the memory controller. In another embodiment, servicing the other command includes the memory device accessing a second bank of the memory device while the memory device operates in the mode, and before completion of an expected future targeted row refresh.

Owner:INTEL CORP

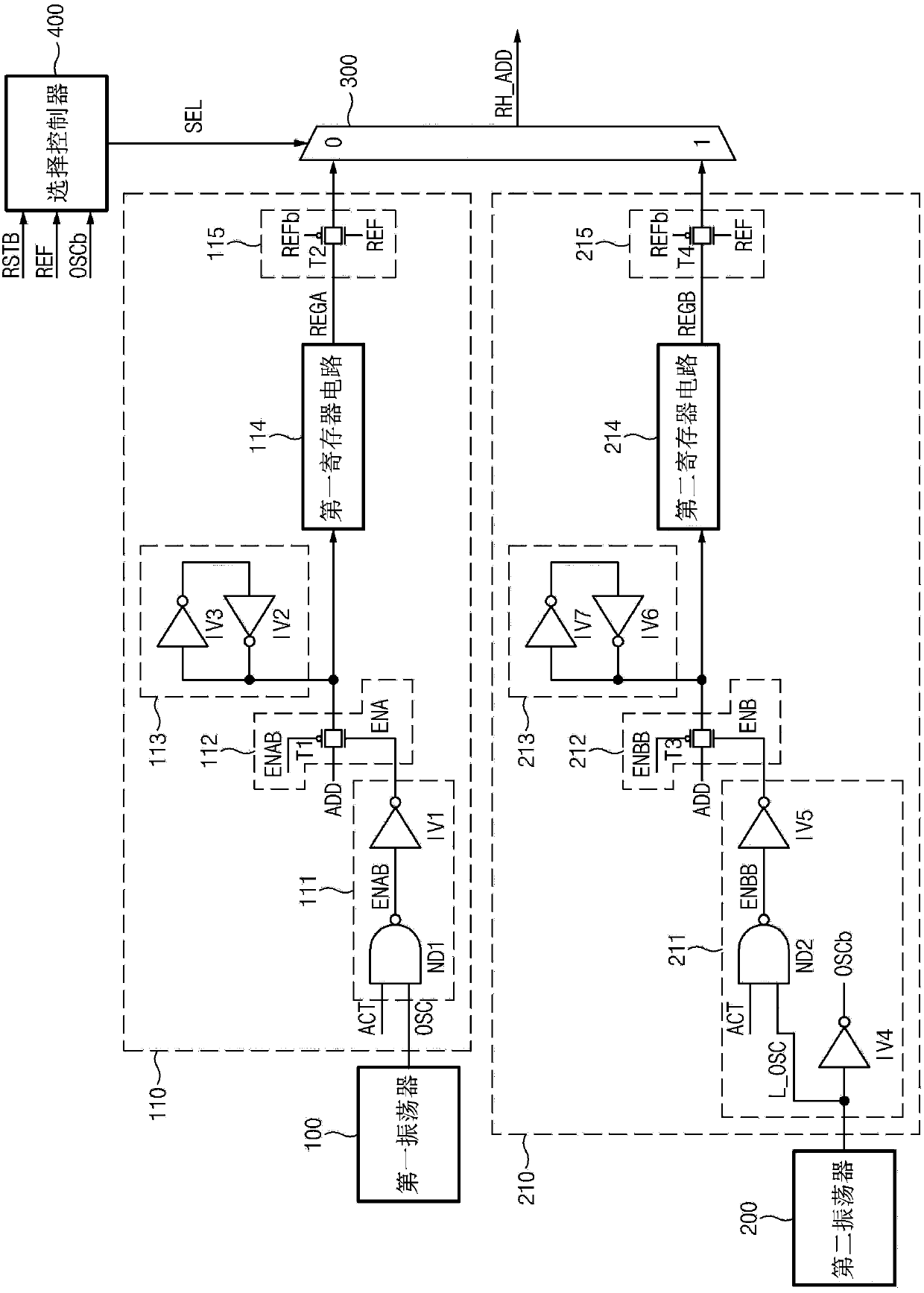

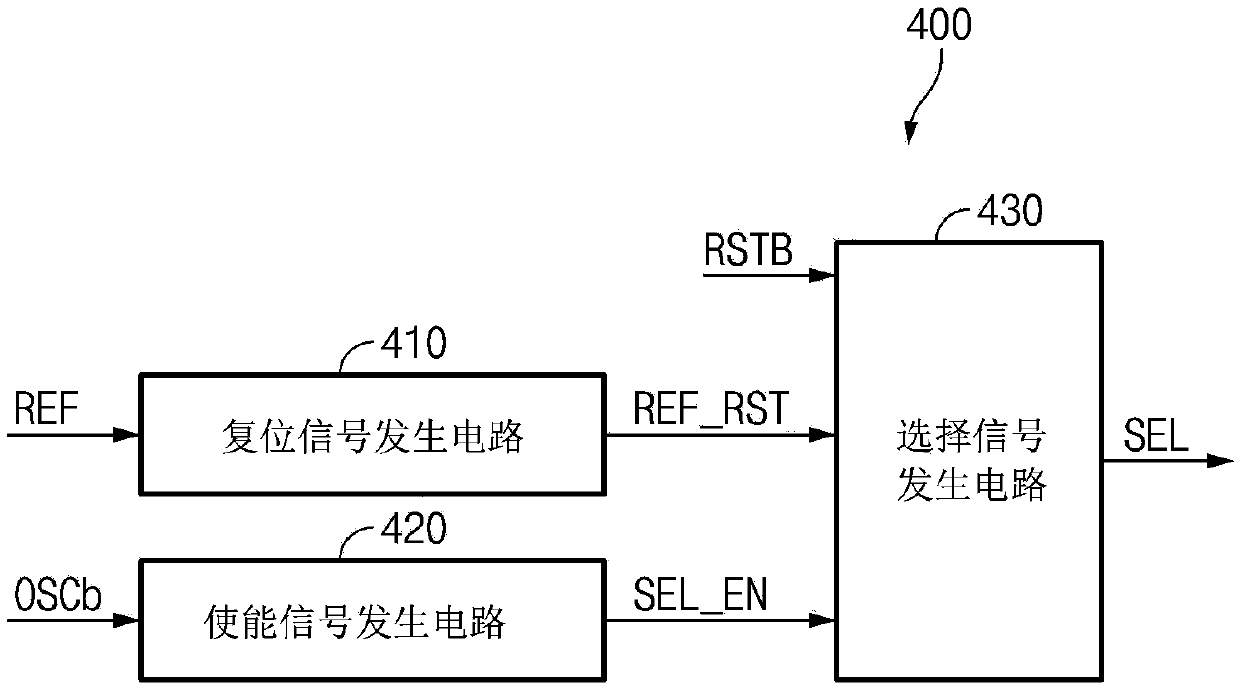

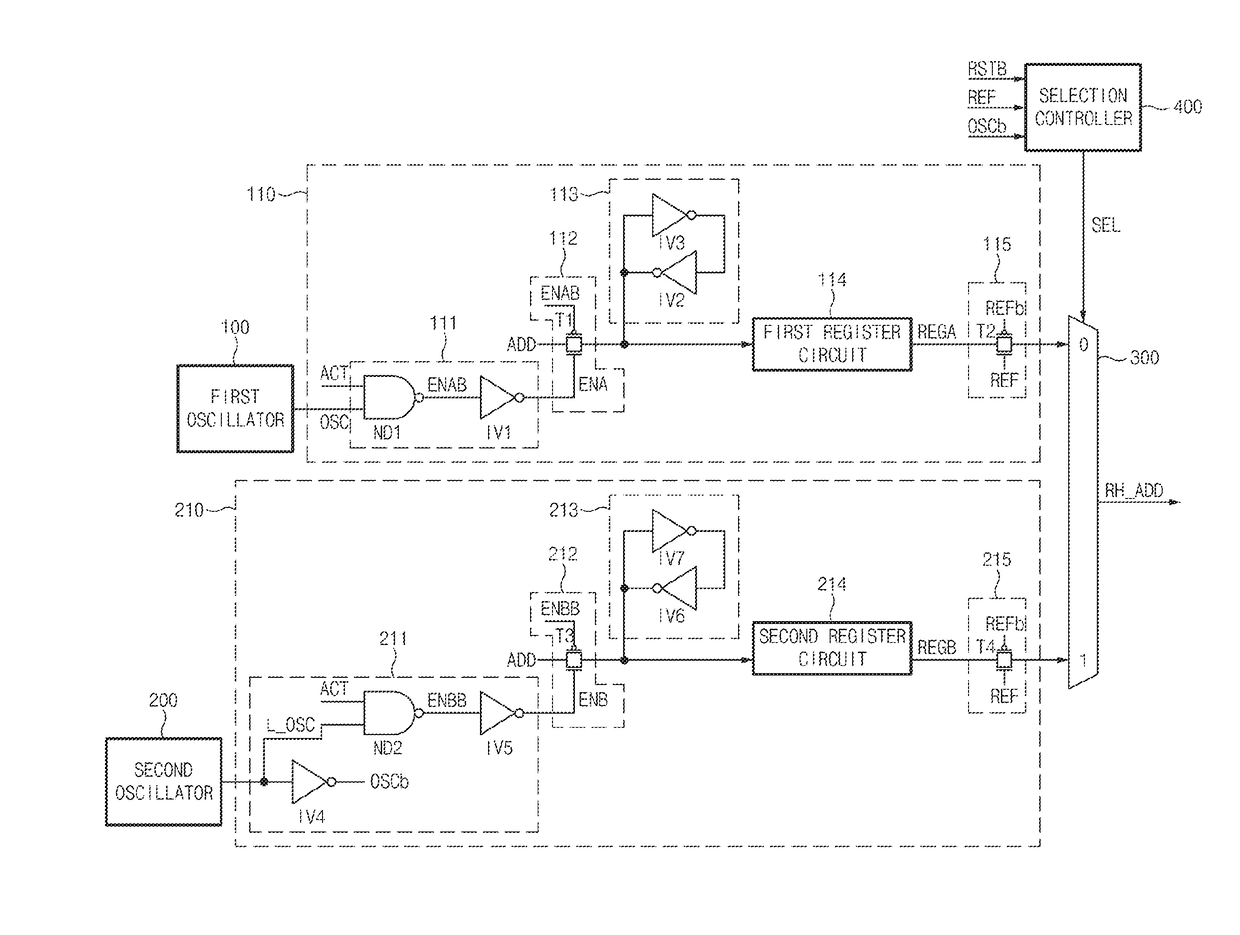

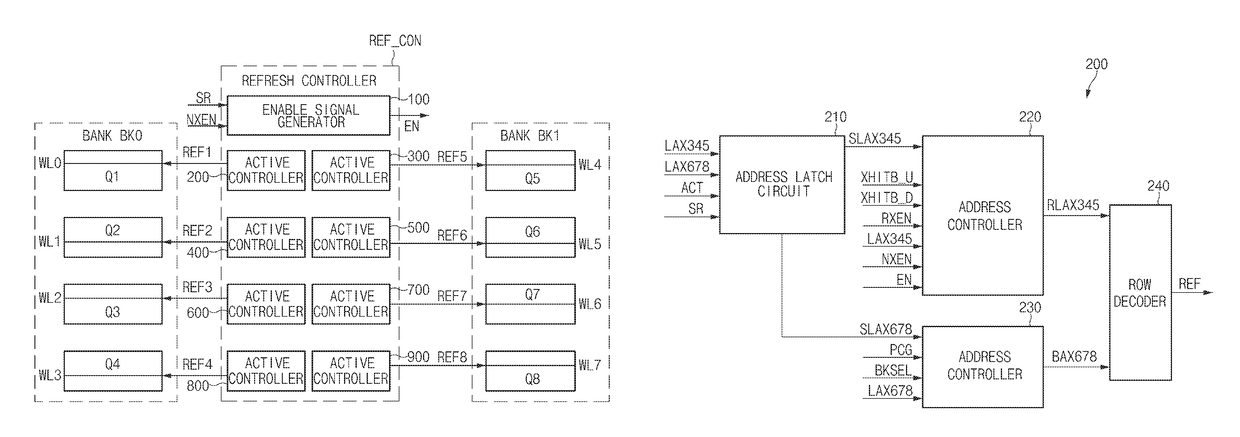

Refresh control device

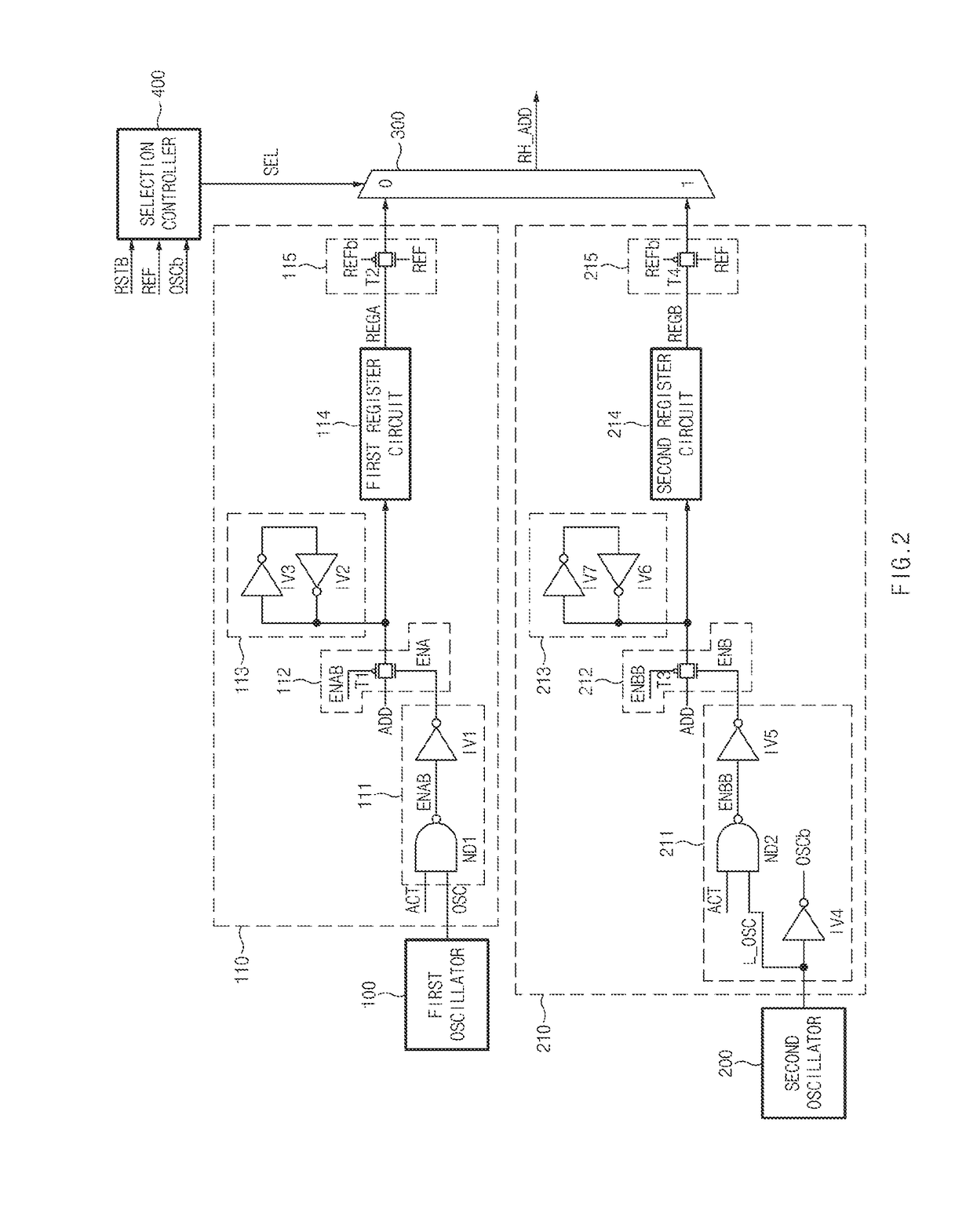

A refresh control device may include a first oscillator configured to generate a first oscillation signal, a second oscillator configured to generate a second oscillation signal having a different cycle from the first oscillation signal, a first address controller configured to latch an address in response to the first oscillation signal, and output the latched address when a refresh signal is enabled. The refresh control device may also include a second address controller configured to latch the address in response to the second oscillation signal, and output the latched address when the refresh signal is enabled. Further included may be a selector configured to select any one of the output of the first address controller and the output of the second address controller in response to a selection signal, and output the selected output as a row hammer address.

Owner:SK HYNIX INC

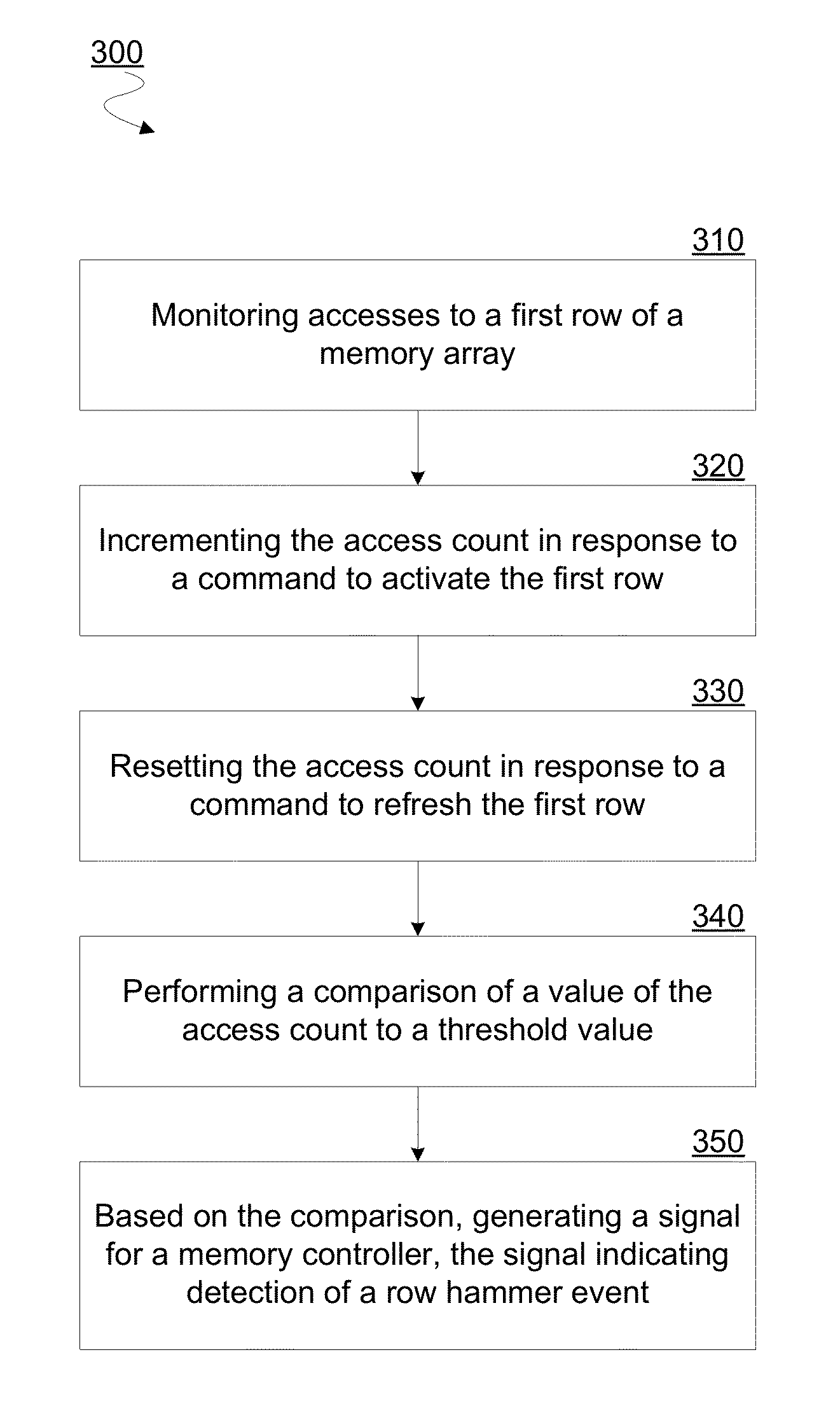

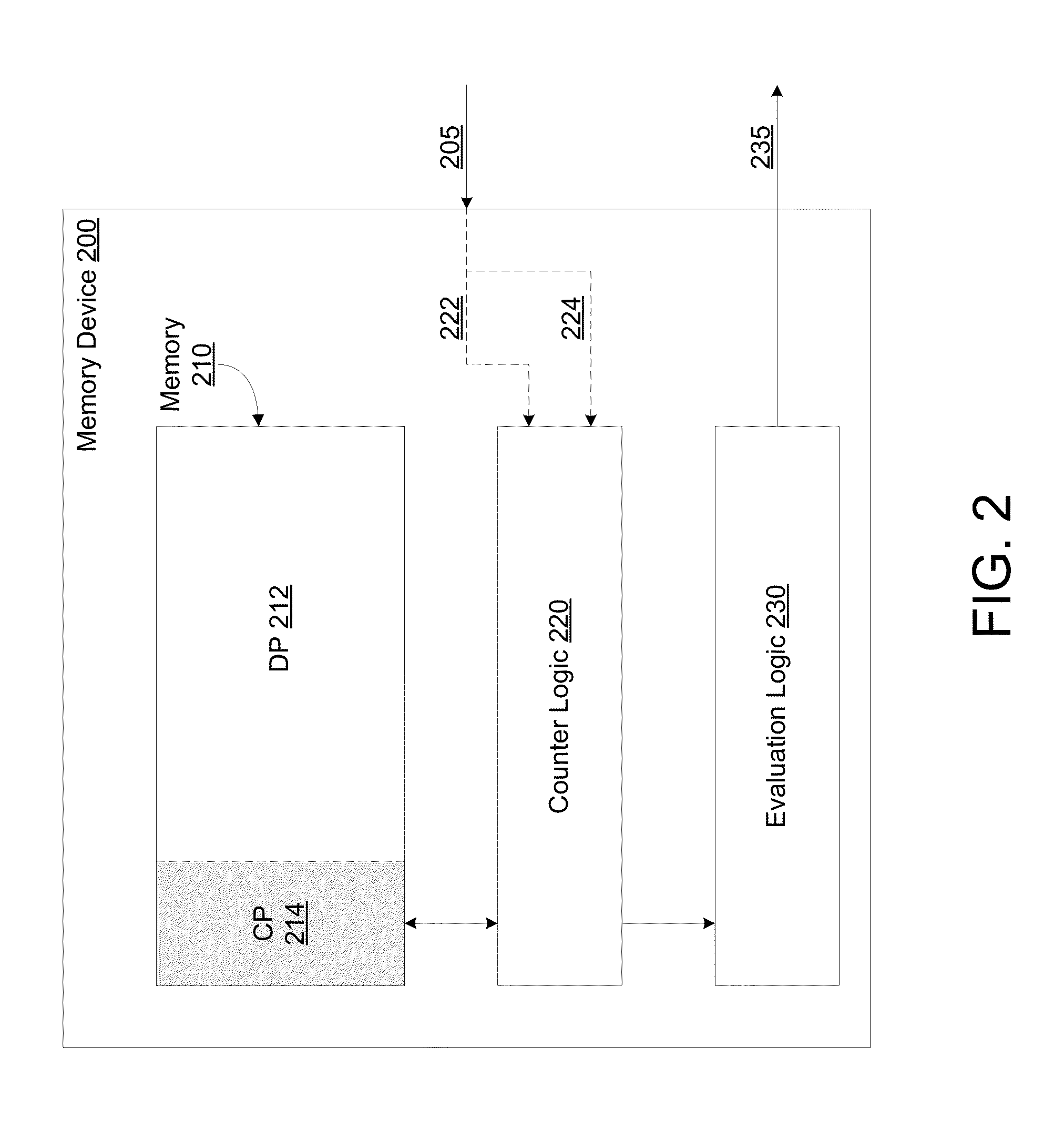

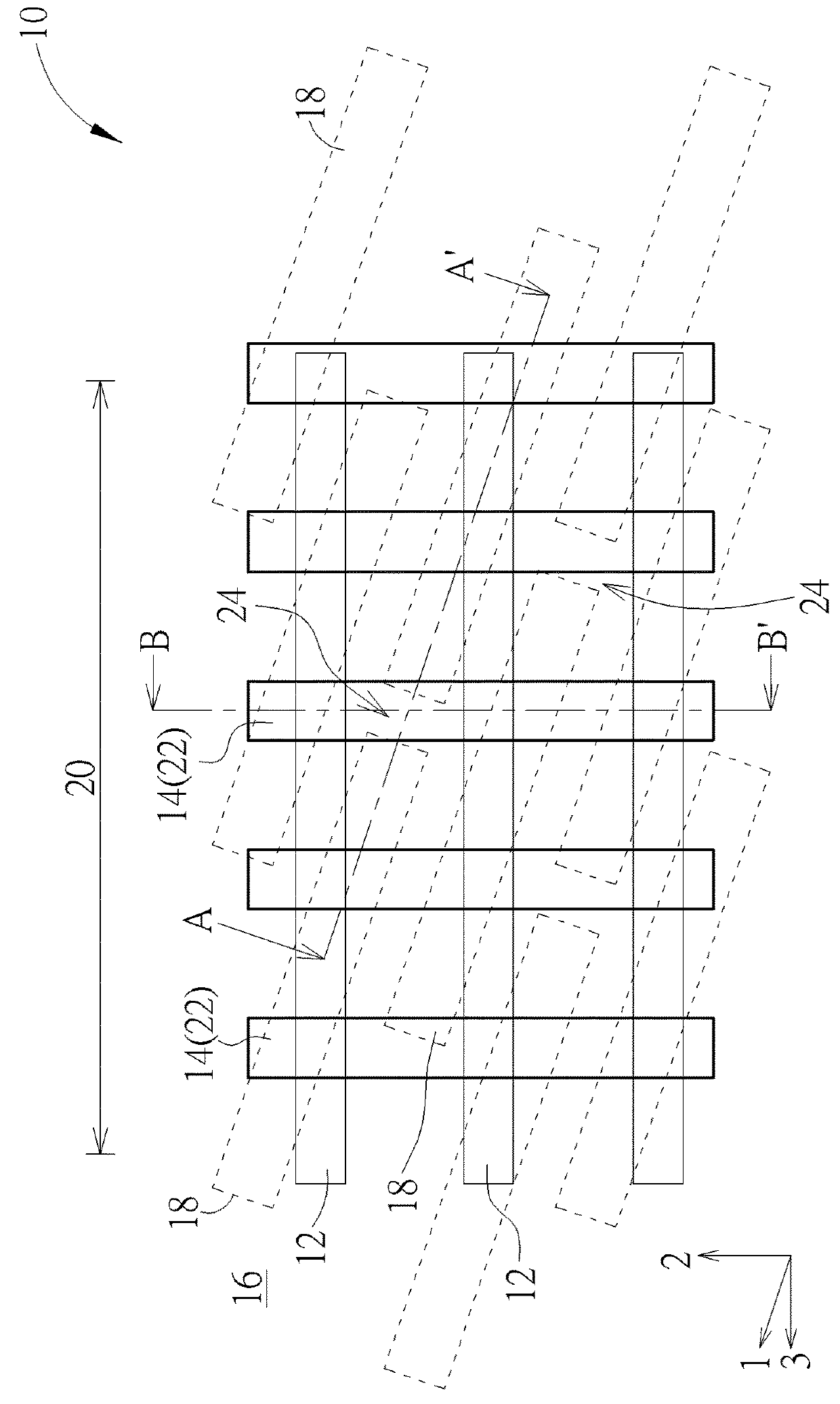

Method, apparatus and system for determining a count of accesses to a row of memory

Techniques and mechanisms for determining a count of accesses to a row of a memory device. In an embodiment, the memory device includes a counter comprising circuitry to increment a value of the count in response to detecting a command to activate the row. Circuitry of counter may further set a value of the count to a baseline value in response to detecting a command to refresh the row. In another embodiment, the memory device includes evaluation logic to compare a value of the count to a threshold value. A signal is generated based on the comparison to indicate whether a row hammer event for the row is indicated.

Owner:INTEL CORP

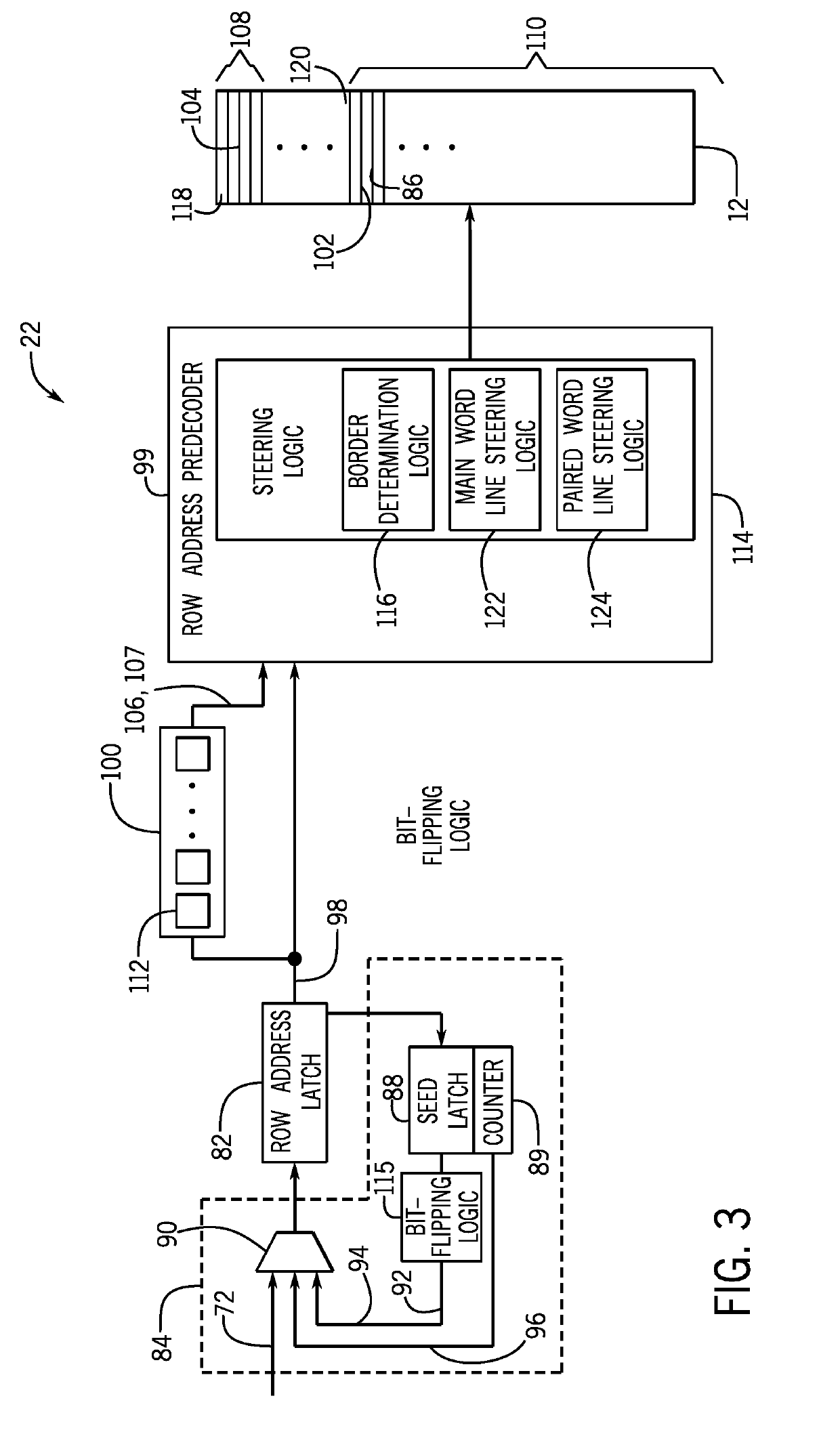

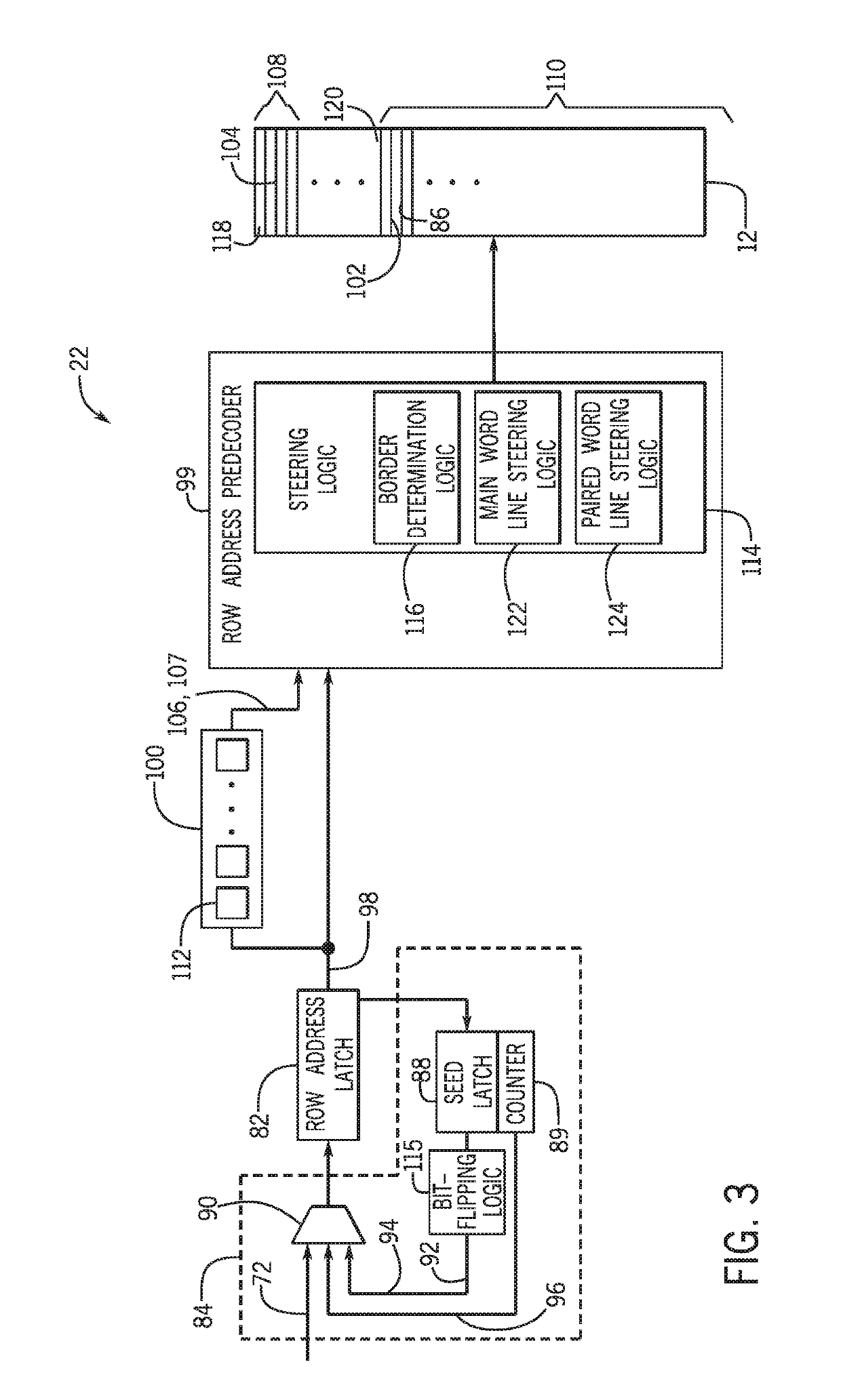

Systems and methods for performing row hammer refresh operations in redundant memory

Steering logic circuitry includes bit-flipping logic that determines a first neighboring redundant word line adjacent to a redundant word line of a memory bank, which also includes normal word lines. Redundant word lines include main word lines, each of which includes paired word lines. Each paired word line includes two redundant word lines. The steering logic circuitry also includes border determination logic that determines whether the redundant word line is on a border between the redundant word lines and an end of the memory bank or the normal word lines. The steering logic circuitry further includes main word line steering logic that determines a neighboring main word line that a second neighboring redundant word line adjacent to the redundant word line is disposed in, and paired word line steering logic that determines a neighboring paired word line that the second neighboring redundant word line is disposed in.

Owner:MICRON TECH INC

Refresh control device

ActiveUS20180090199A1Reducing a refresh failMemory architecture accessing/allocationData resettingRow hammerAddress control

A refresh control device may include a first oscillator configured to generate a first oscillation signal, a second oscillator configured to generate a second oscillation signal having a different cycle from the first oscillation signal, a first address controller configured to latch an address in response to the first oscillation signal, and output the latched address when a refresh signal is enabled. The refresh control device may also include a second address controller configured to latch the address in response to the second oscillation signal, and output the latched address when the refresh signal is enabled. Further included may be a selector configured to select any one of the output of the first address controller and the output of the second address controller in response to a select signal, and output the selected output as a row hammer address.

Owner:SK HYNIX INC

Smart refresh device

Owner:SK HYNIX INC

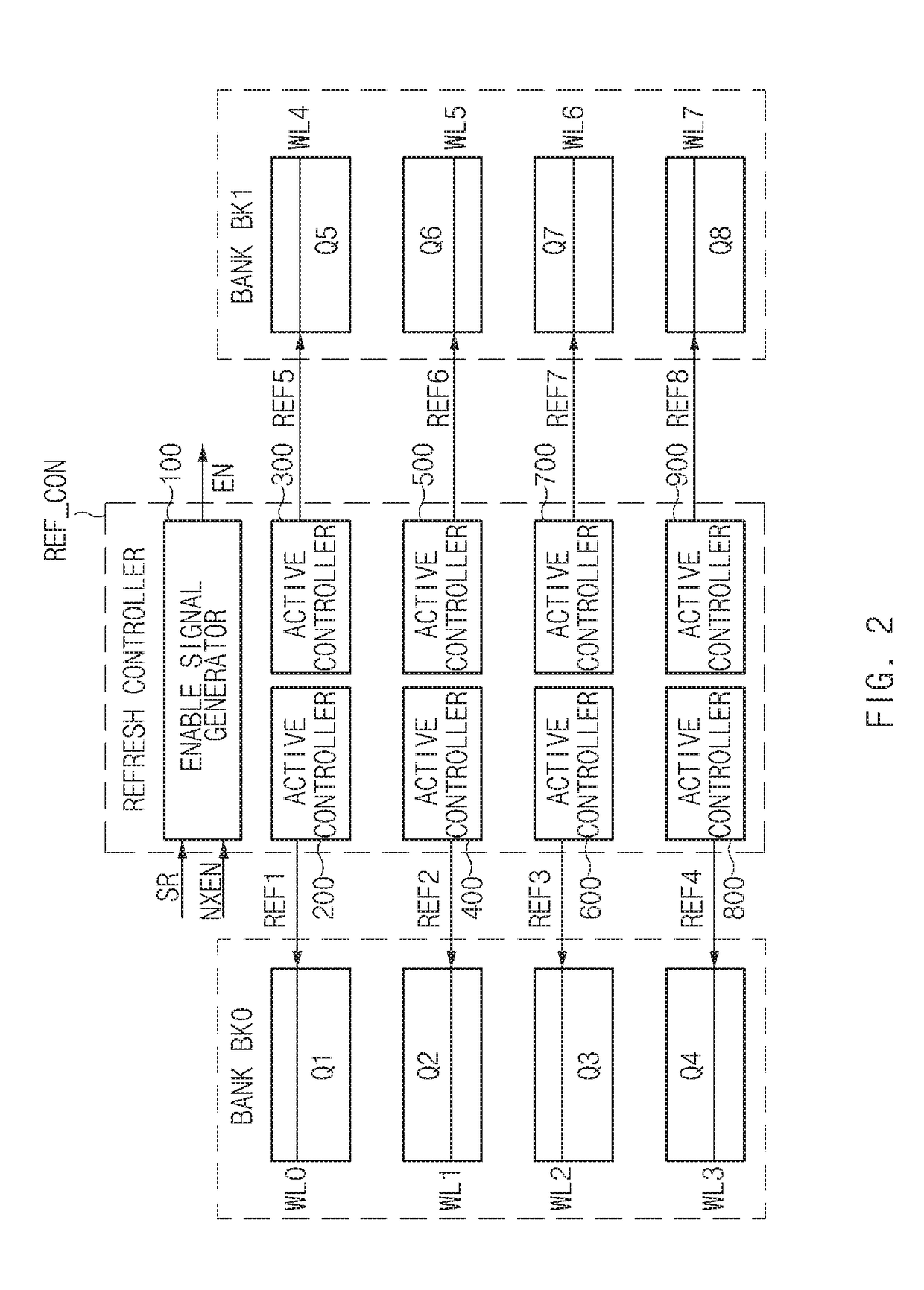

Simultaneous plural wordline within a bank refreshing control device and memory device including the same

A refresh control device and a semiconductor device including the same, for preventing a row hammer failure from occurring, may include an enable signal generator configured to generate an enable signal for performing a smart refresh operation and a plurality of active controllers configured to generate a plurality of refresh signals for refreshing word lines located at different positions within one bank, based on receiving the enable signal.

Owner:SK HYNIX INC

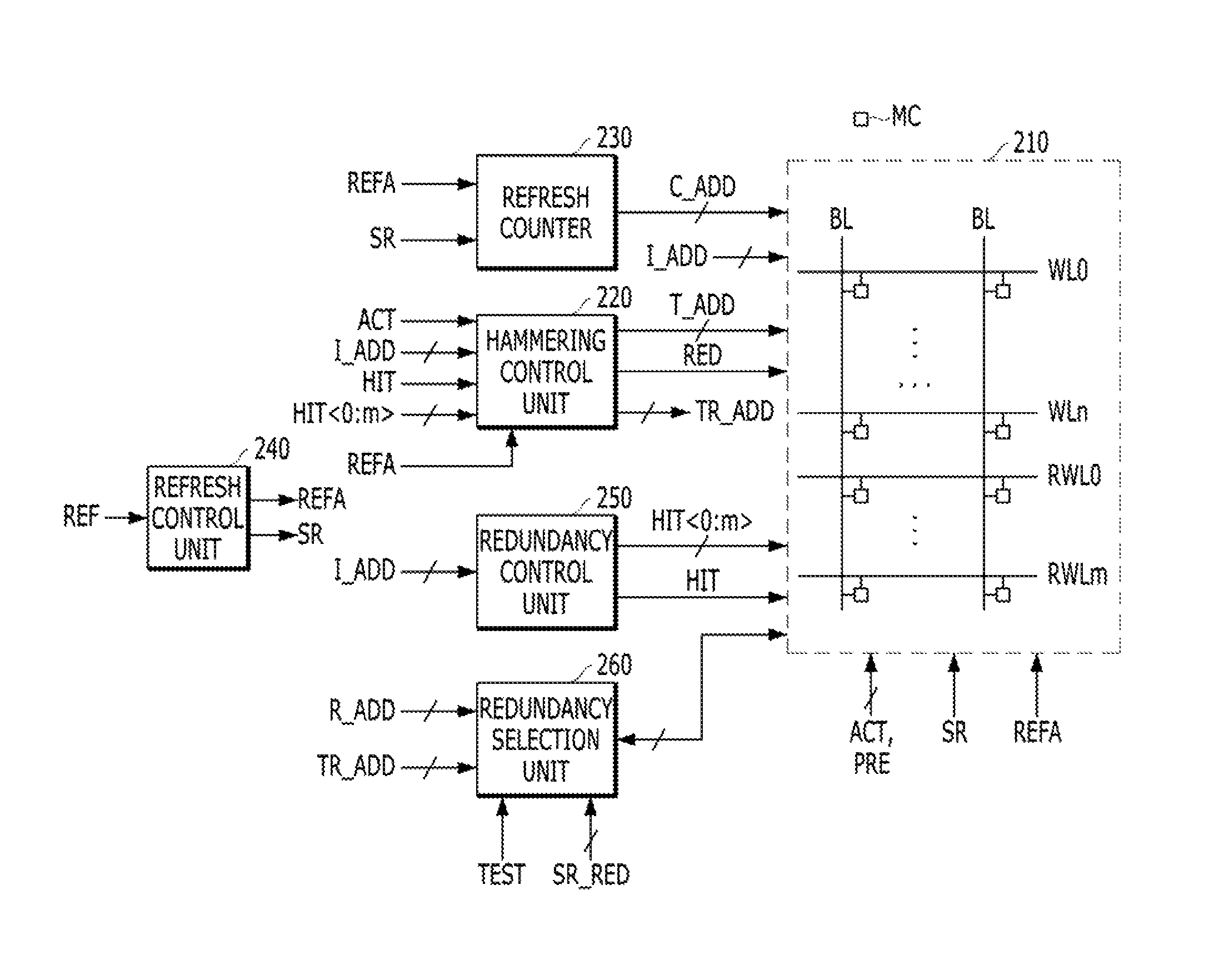

Memory device

A memory device may include a plurality of normal word lines; a plurality of redundancy word lines capable of replacing the word lines; a hammering information storage unit capable of storing an address of a row hammering word line of the normal word lines and the redundancy word lines; an address generation unit capable of generating an address of a normal word line or redundancy word line adjacent to a normal word line or redundancy word line corresponding to the address stored in the hammering information storage unit; and a refresh control unit capable of selecting the normal word line or redundancy word line corresponding to the address generated by the address generation unit for performing an additional refresh operation.

Owner:SK HYNIX INC

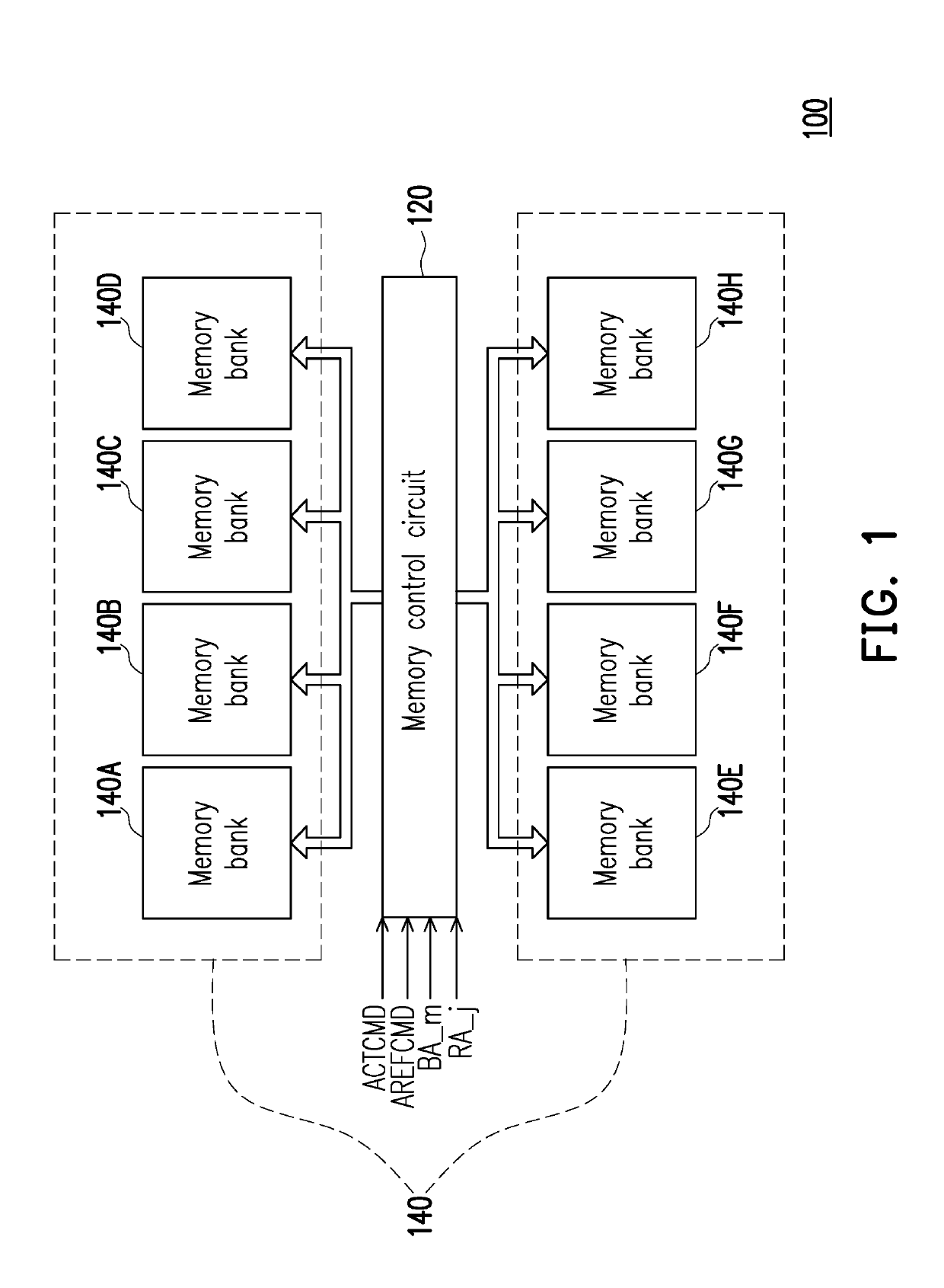

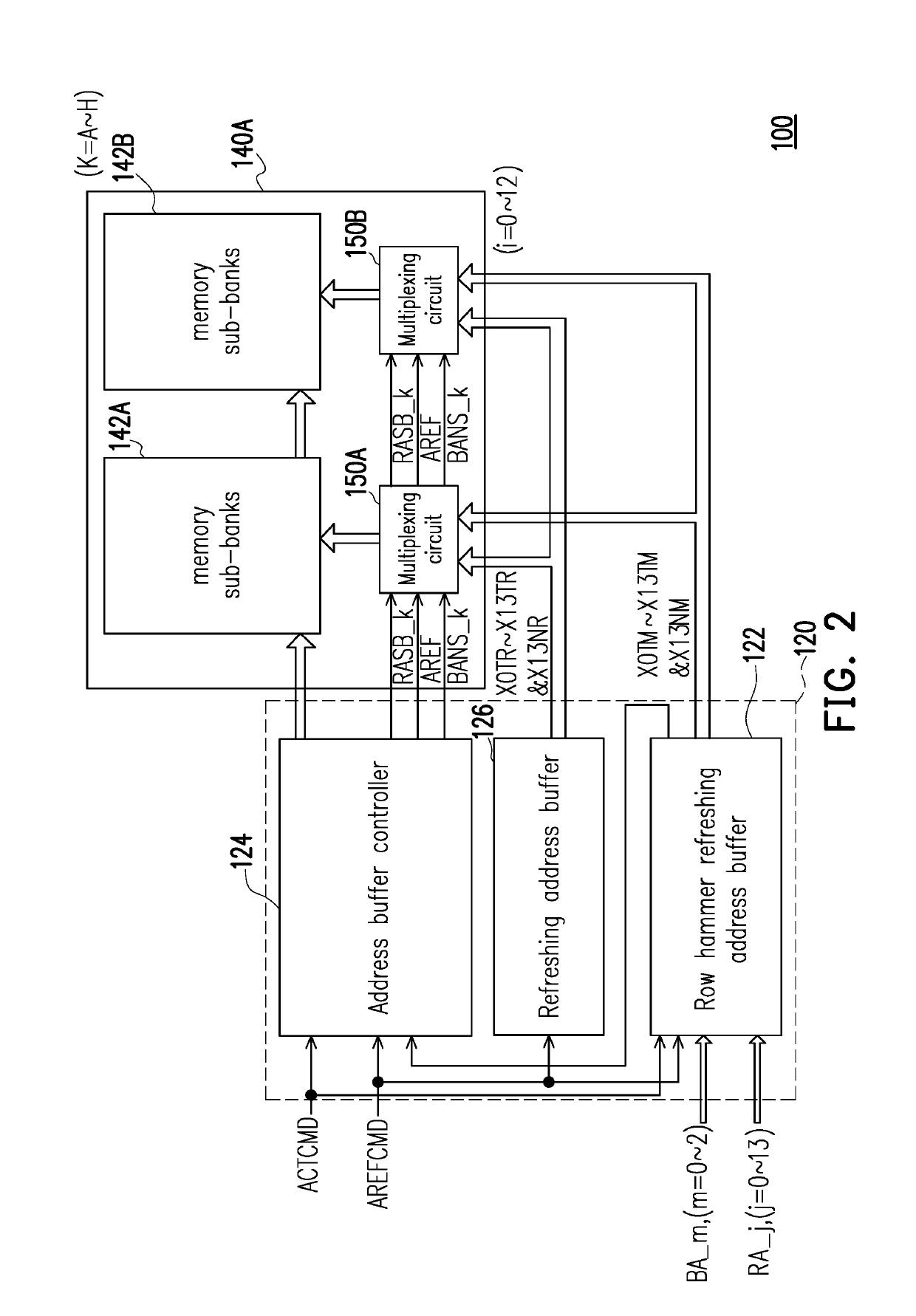

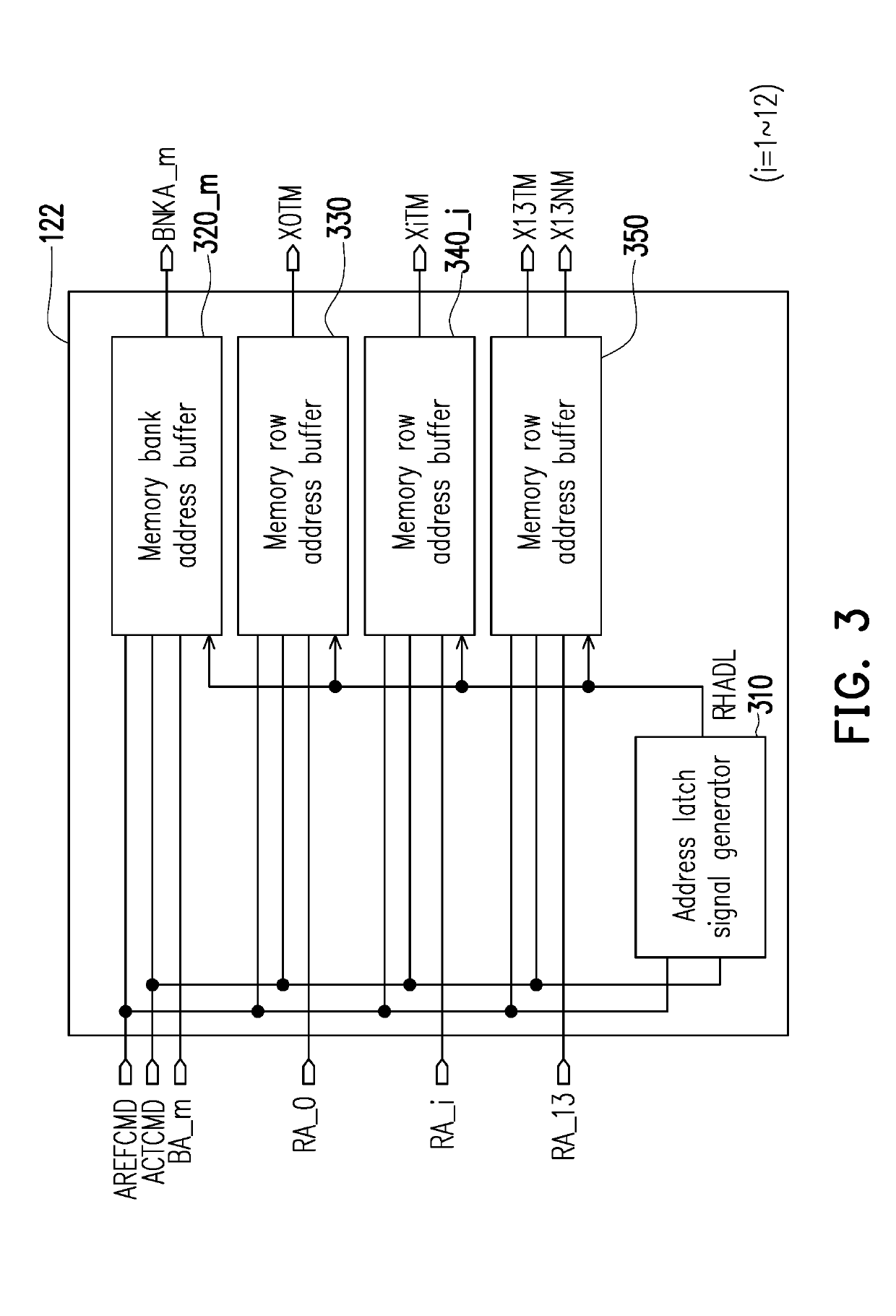

Memory device and refreshing method thereof

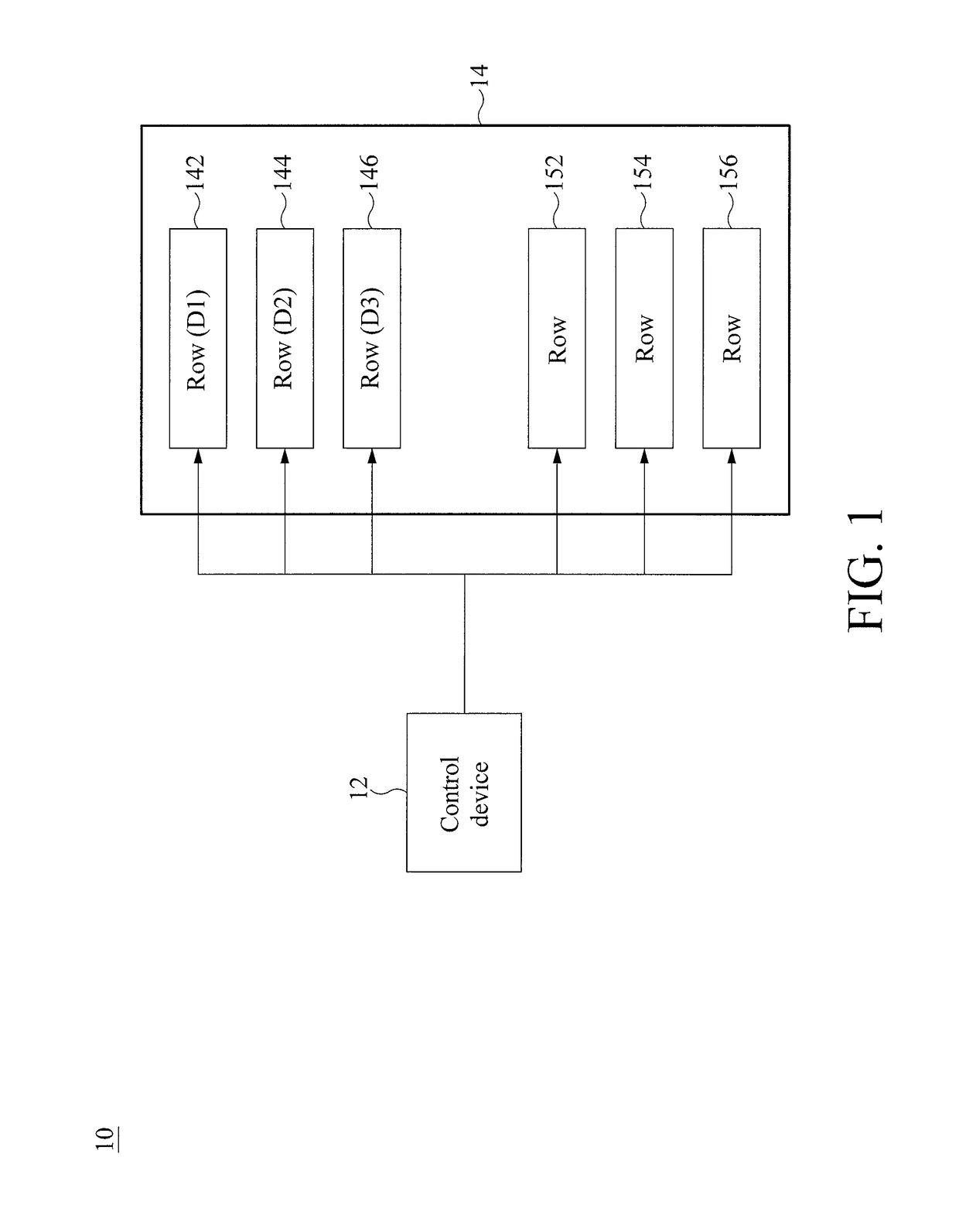

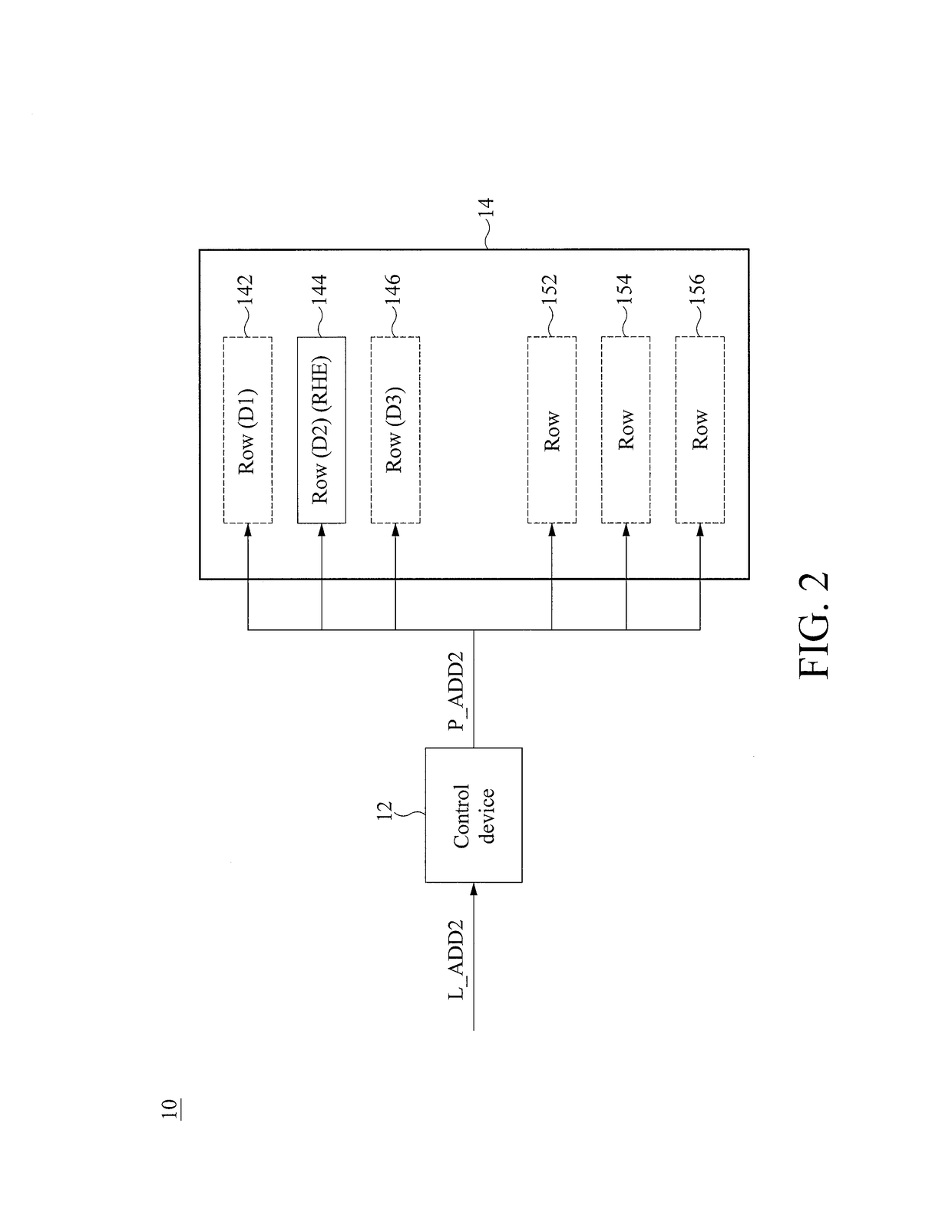

ActiveUS10607679B2Reduce stepsAvoid lossInput/output to record carriersDigital storageMemory bankRow hammer

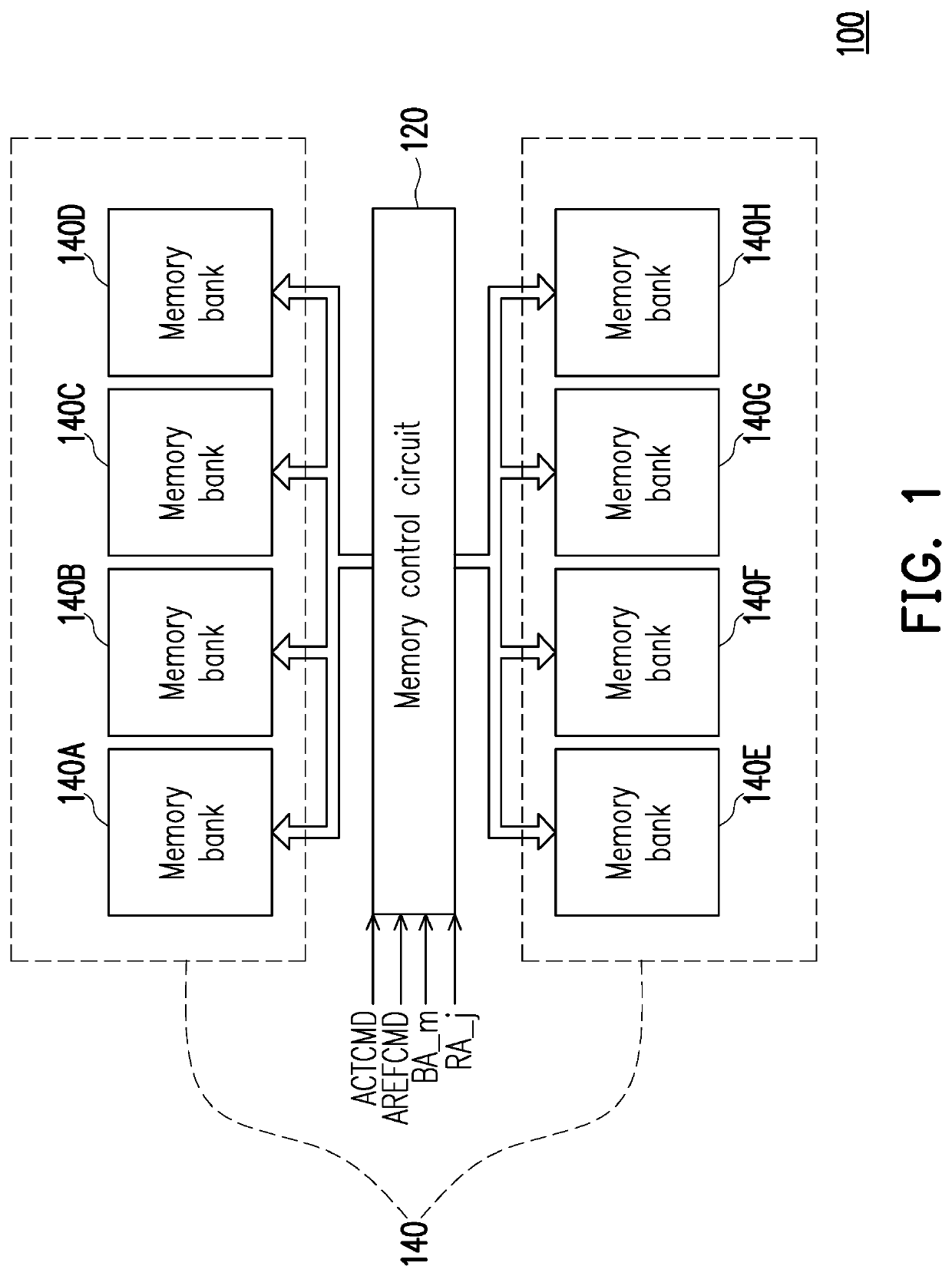

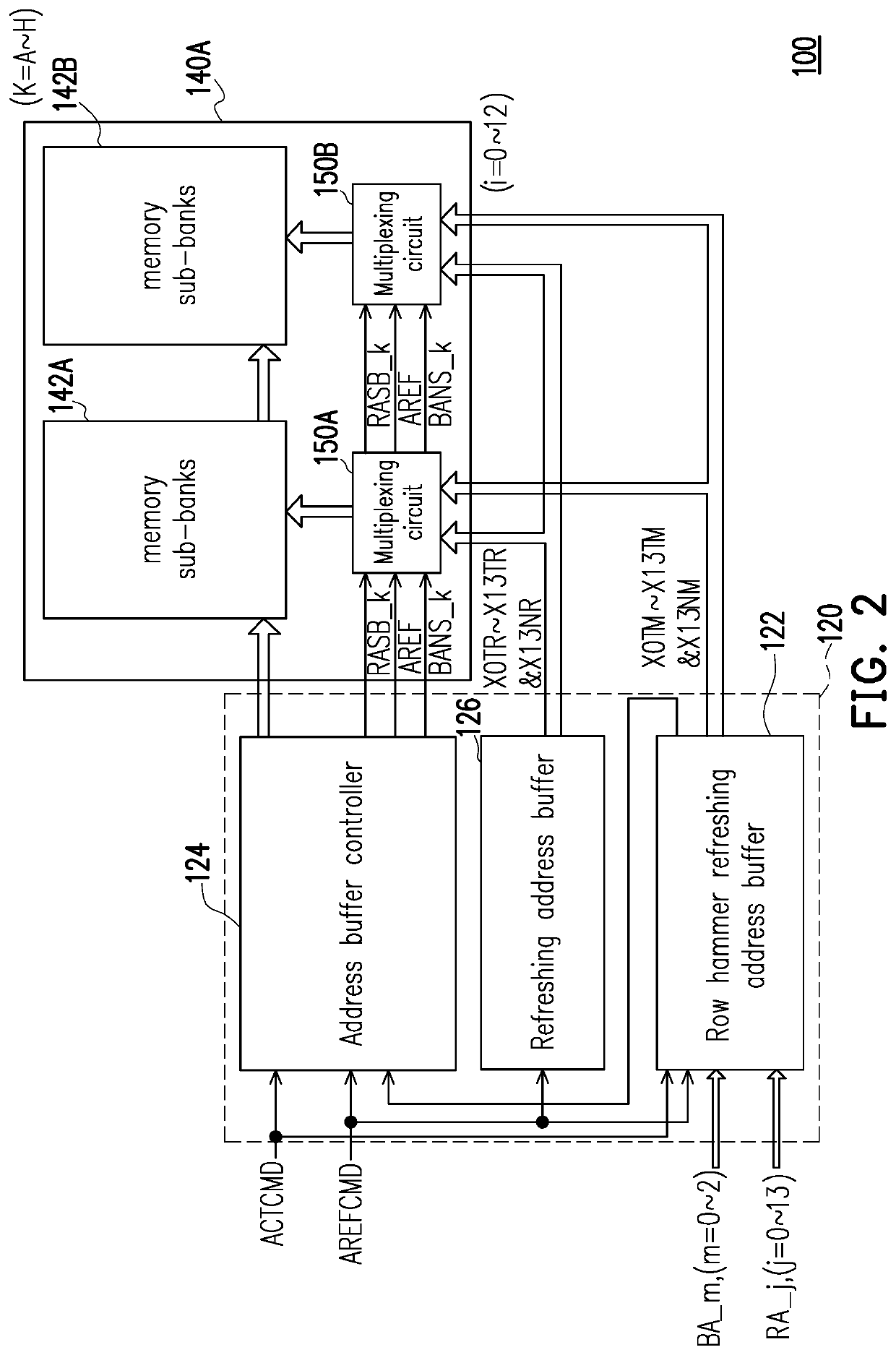

A memory device and a data refreshing method of the memory device are provided. The memory device includes a memory array and a memory control circuit. The memory control circuit counts the number of access commands to generate a first count value and counts the number of refreshing commands to generate a second count value. If the first count value is equal to the second count value, the memory control circuit latches a memory bank address and a memory row address corresponding to the access commands to obtain a row hammer refreshing bank address and a row hammer refreshing row address. The memory control circuit performs a row hammer refreshing operation on a memory bank according to the row hammer refreshing bank address and the row hammer refreshing row address.

Owner:WINBOND ELECTRONICS CORP

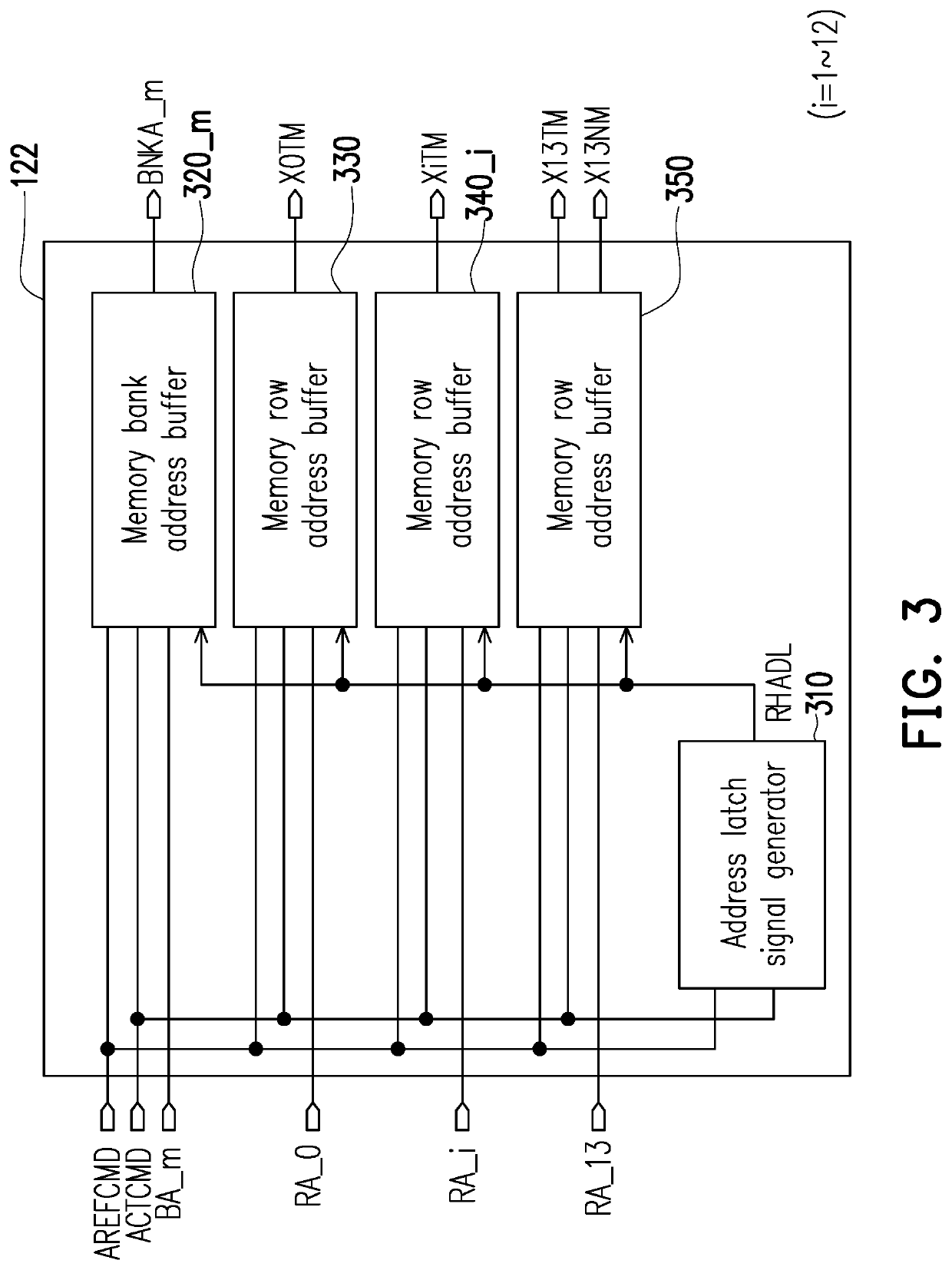

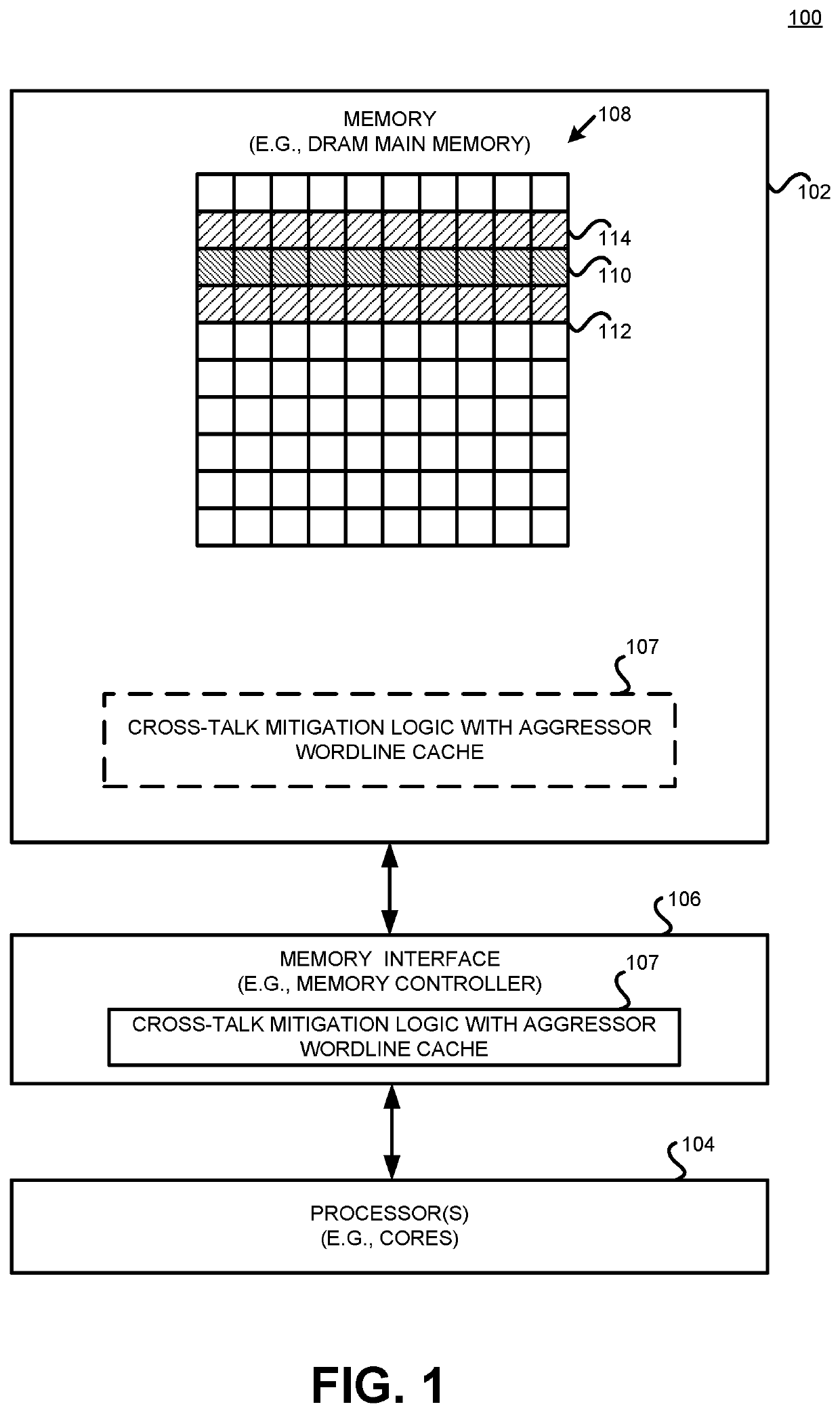

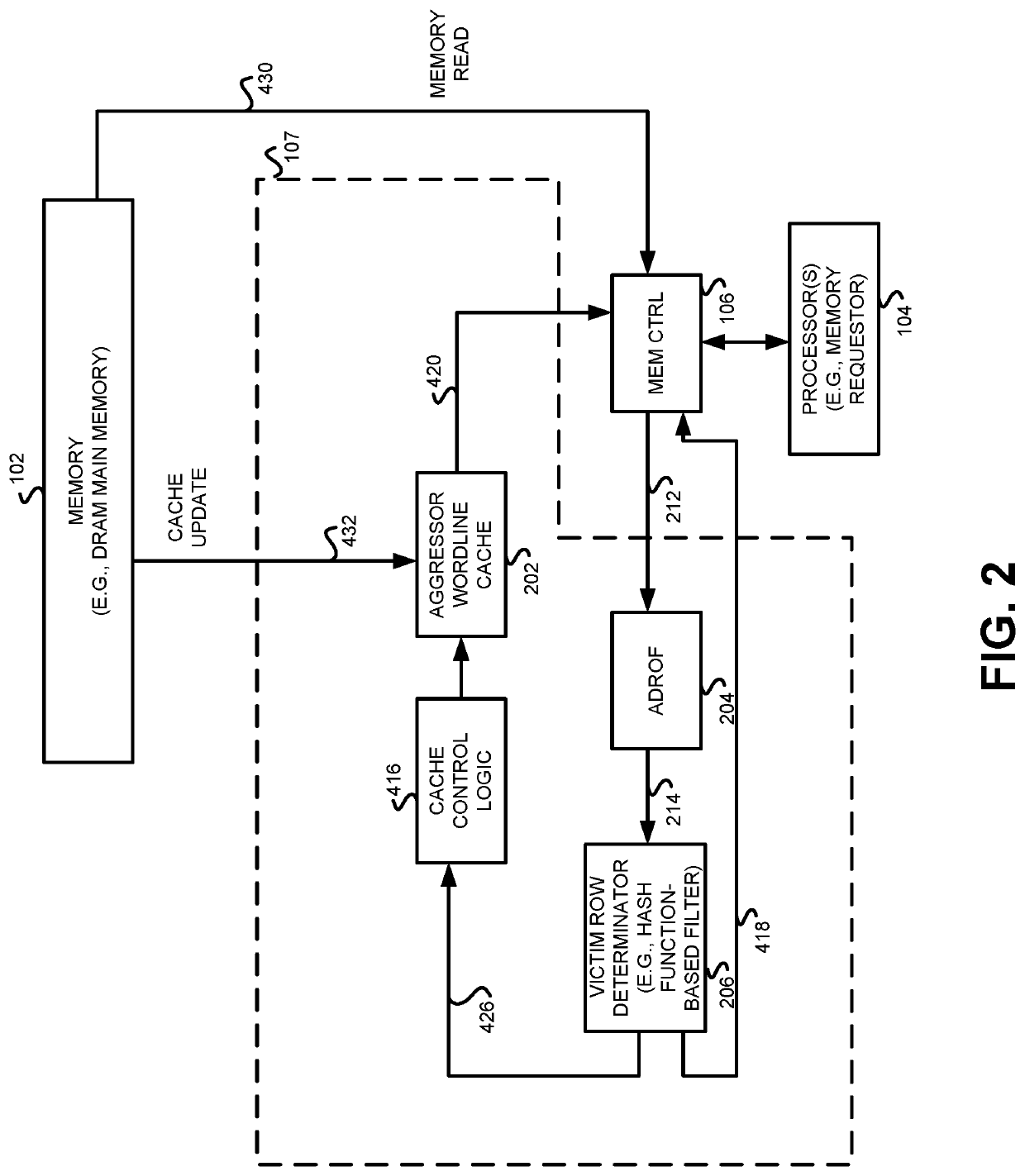

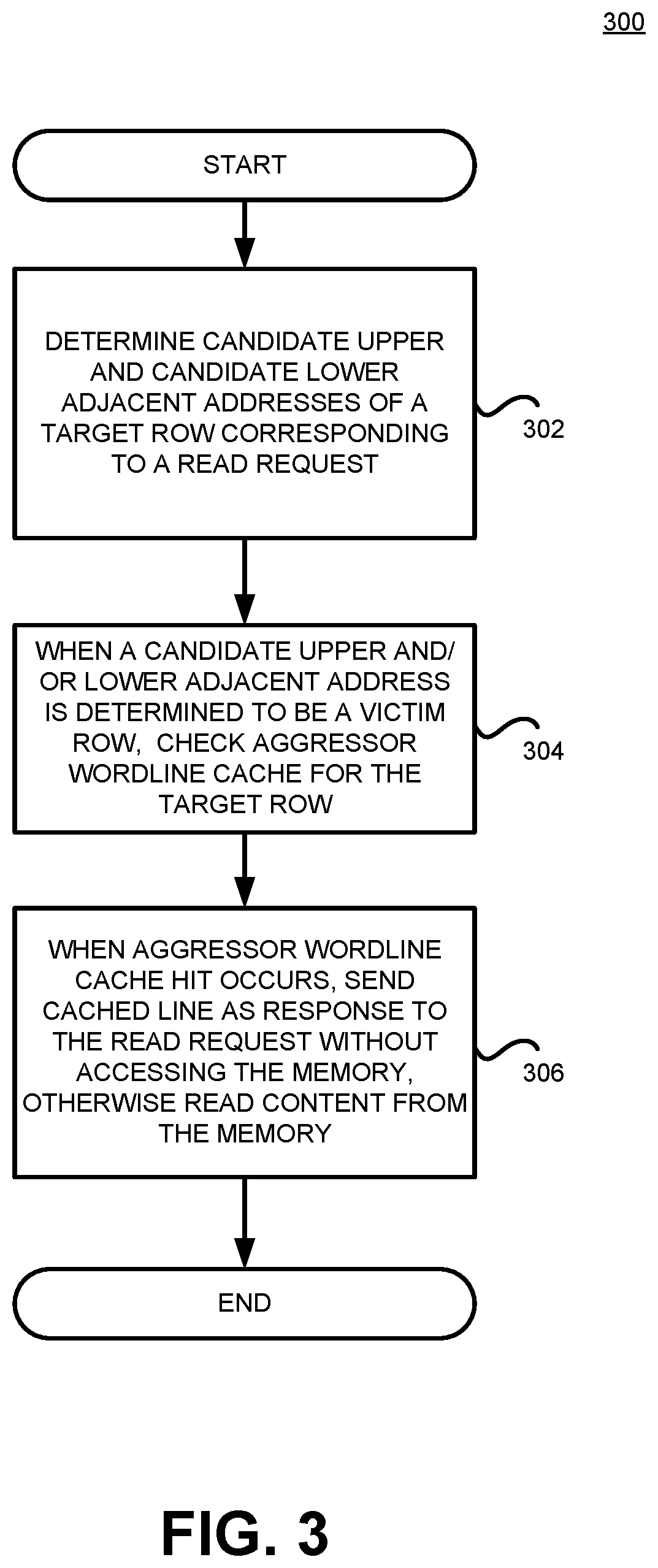

Method and apparatus for mitigating row hammer attacks

An integrated circuit includes an aggressor wordline cache and logic that determines a candidate upper adjacent address and a candidate lower adjacent address of a target memory row corresponding to a read request to memory. When at least one of the candidate upper adjacent address or the candidate lower adjacent address are determined to be a victim row, the logic checks the aggressor wordline cache for a cache hit for the target memory row. When there is a cache hit in the aggressor wordline cache, the logic sends a corresponding cache line as a response to the read request, otherwise the logic causes a read of content from the memory. In certain examples, the logic includes a stored bit array and a hash function-based filter, which determines whether any of the candidate upper adjacent address and the candidate lower adjacent address are victim rows represented in the stored bit array.

Owner:ADVANCED MICRO DEVICES INC

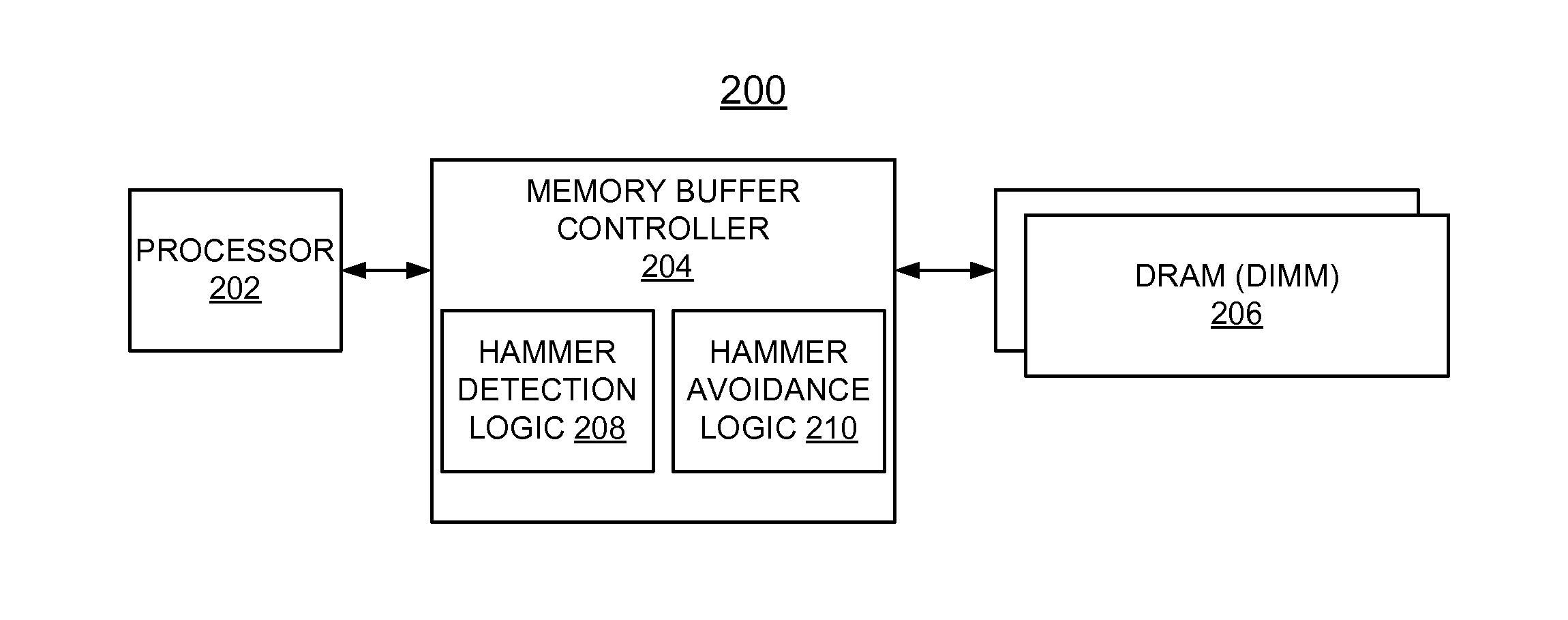

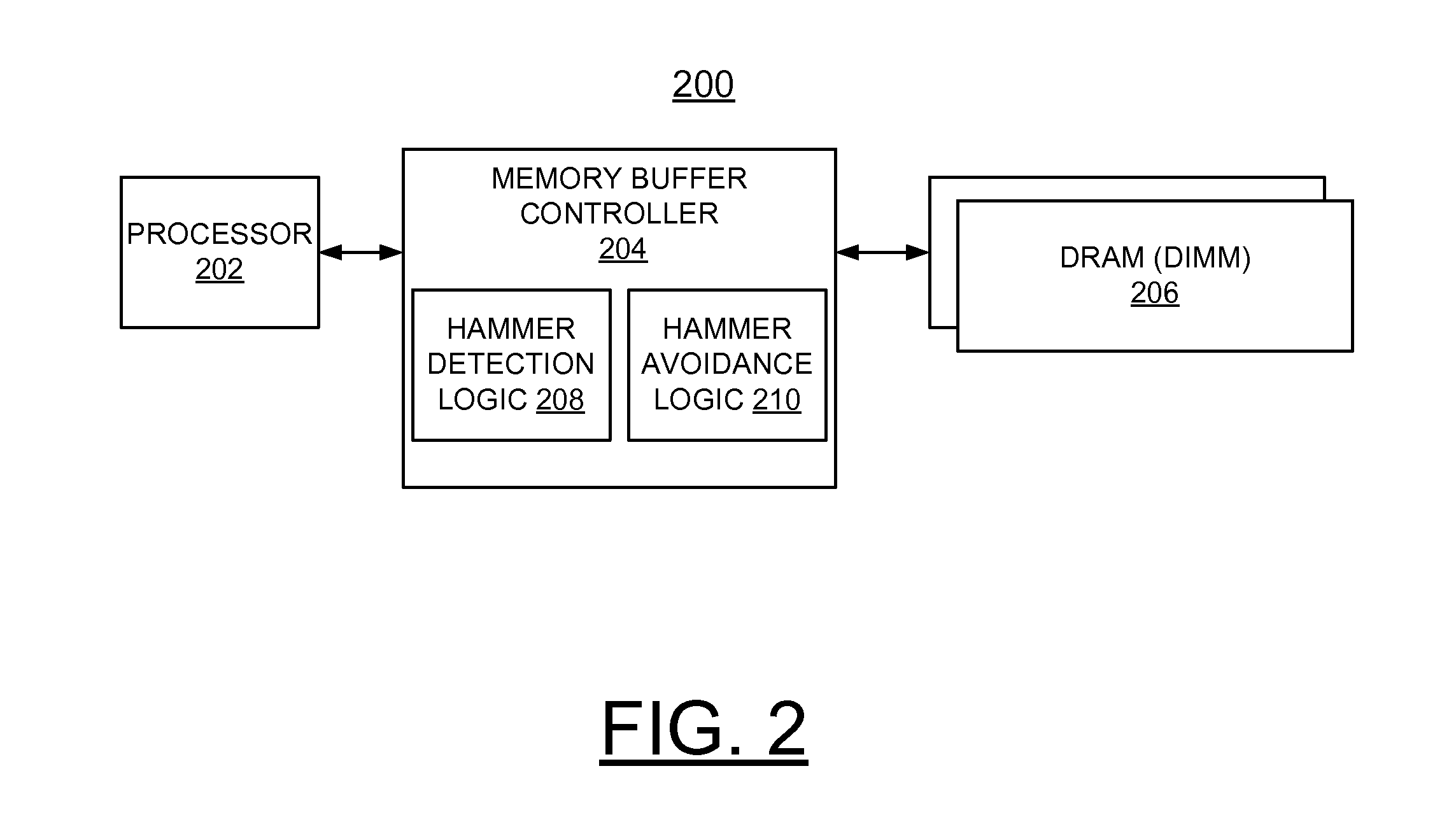

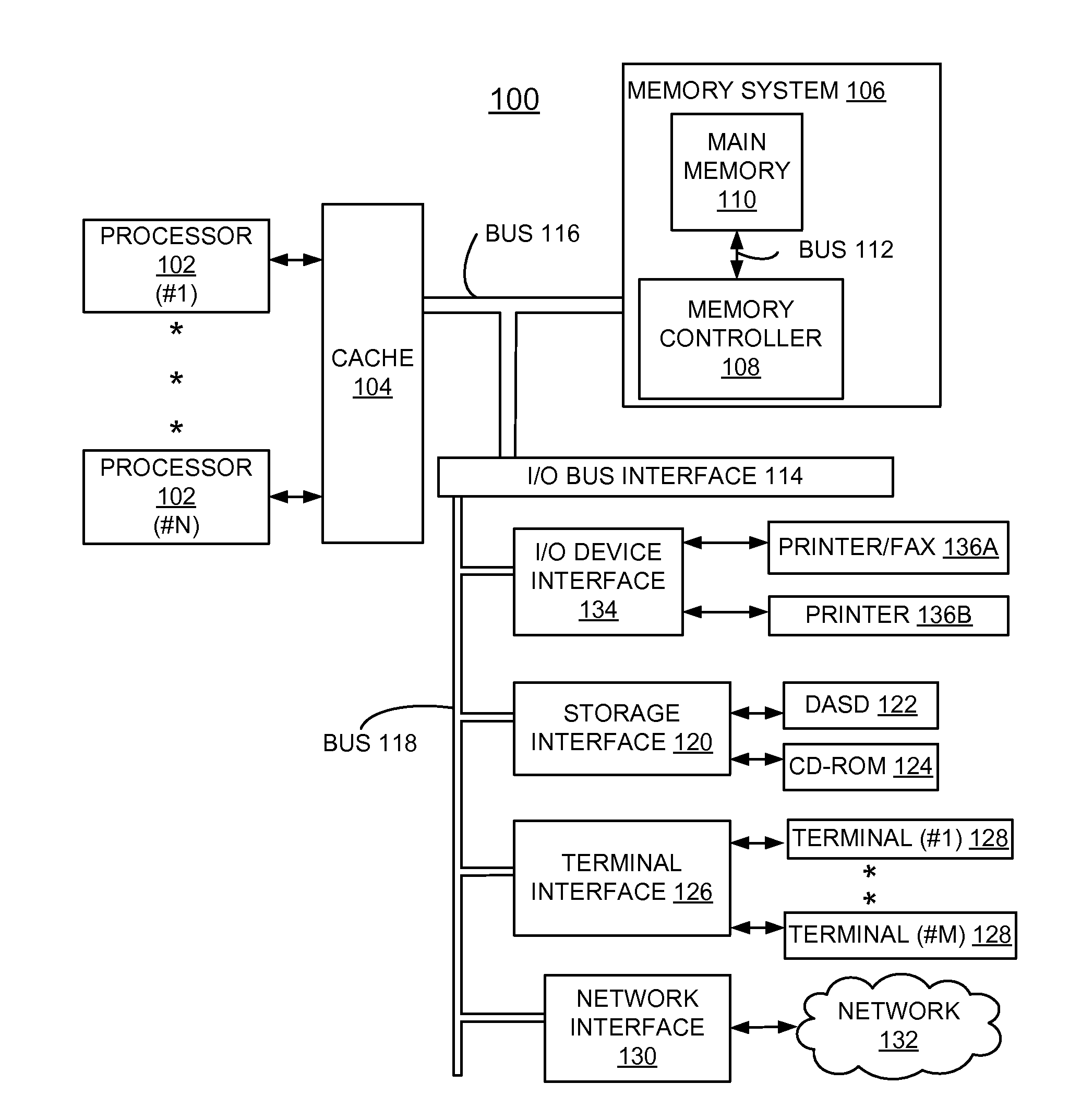

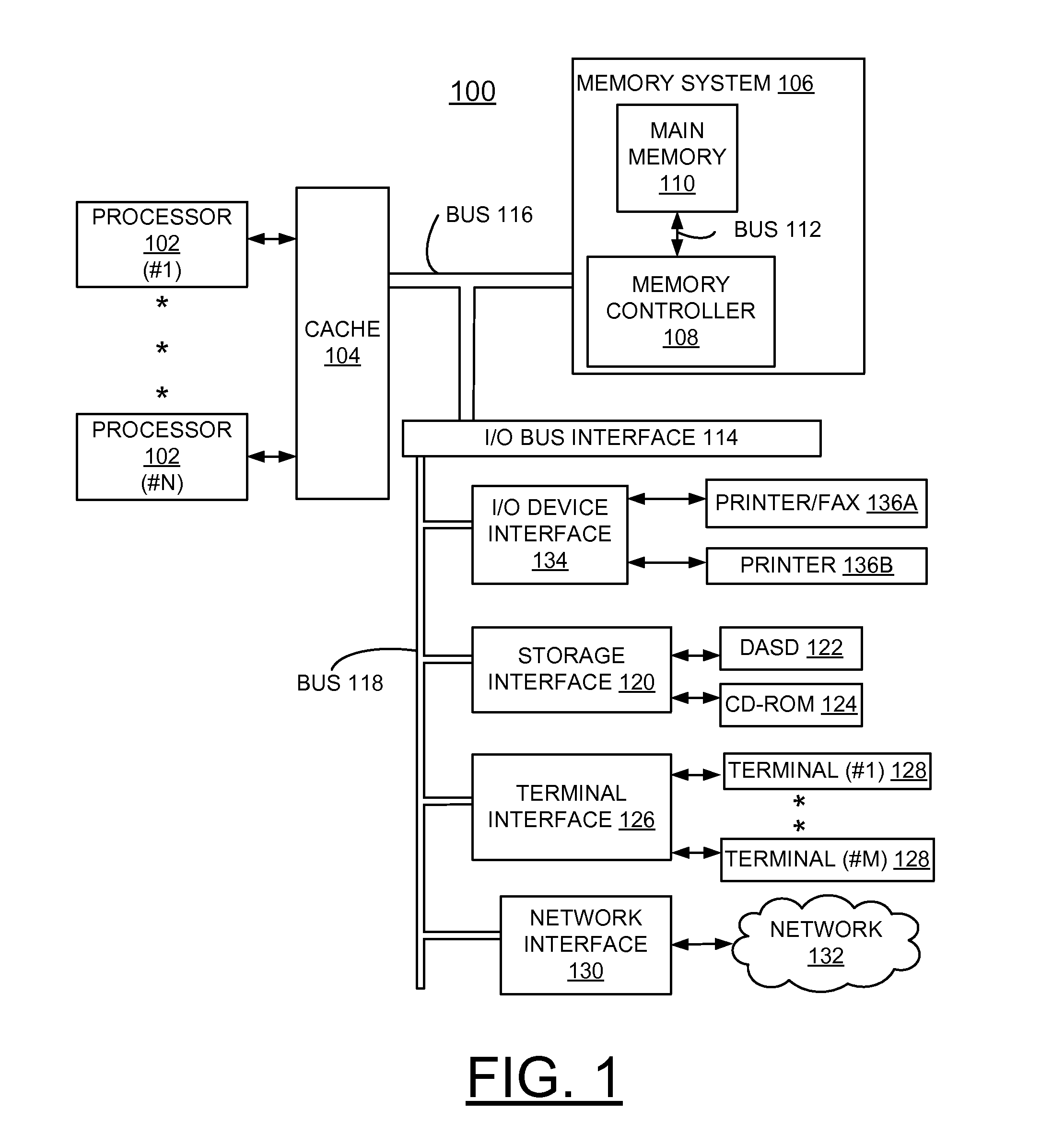

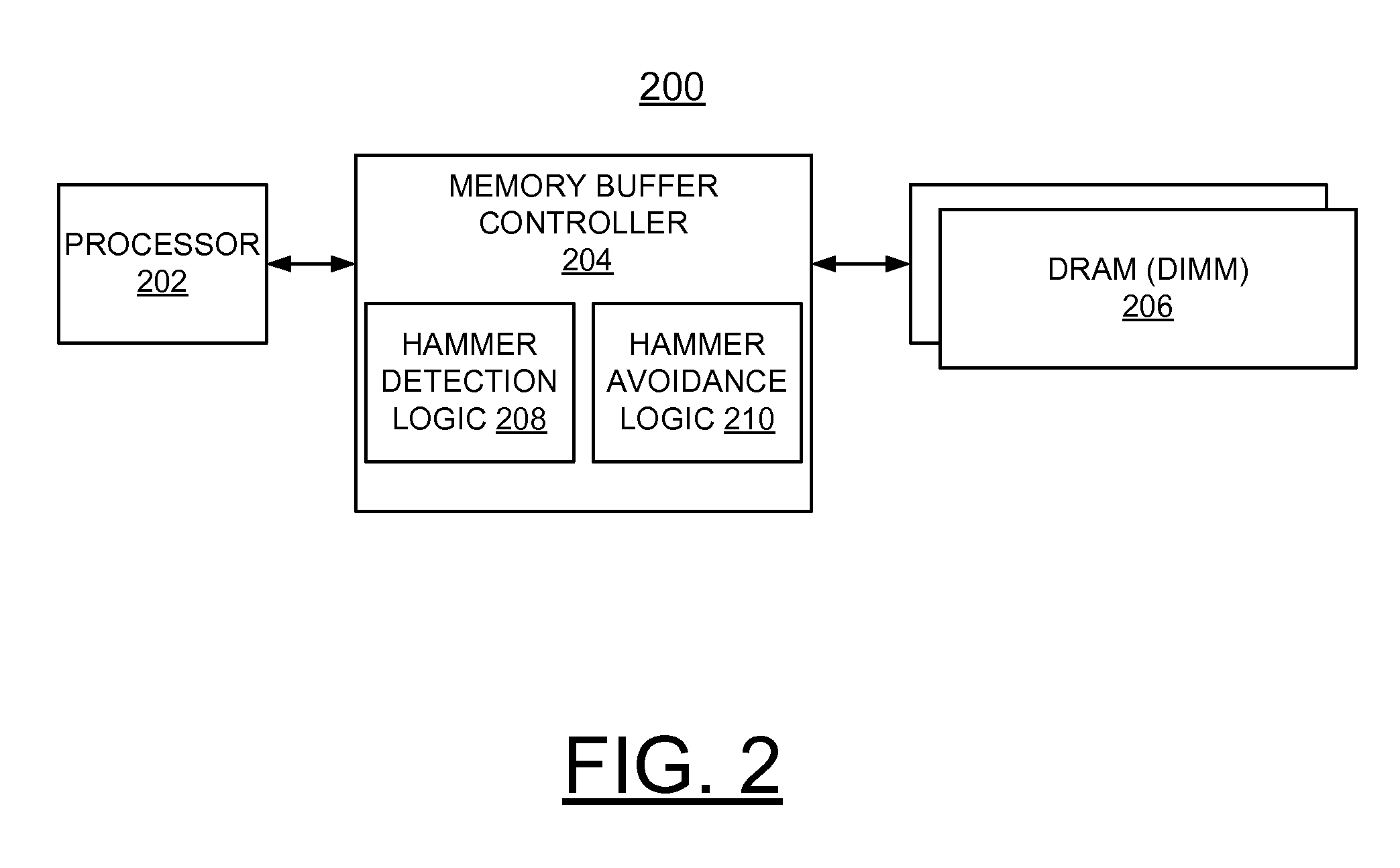

Implementing dram row hammer avoidance

ActiveUS20160180899A1Negative effectOvercome disadvantagesDigital storageMemory systemsStatic random-access memoryRandom access memory

A method and apparatus for implementing row hammer avoidance in a dynamic random access memory (DRAM) in a computer system. Hammer detection logic identifies a hit count of repeated activations at a specific row in the DRAM. Monitor and control logic receiving an output of the hammer detection logic compares the identified hit count with a programmable threshold value. Responsive to a specific count as determined by the programmable threshold value, the monitor and control logic captures the address where a selected row hammer avoidance action is provided.

Owner:IBM CORP

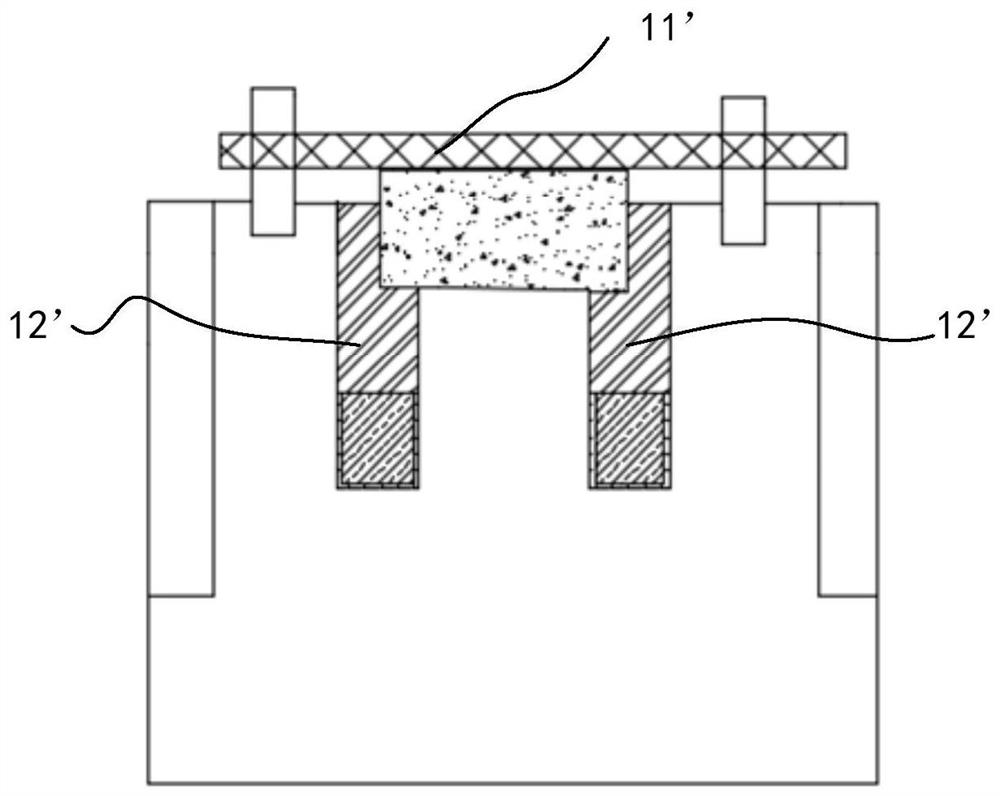

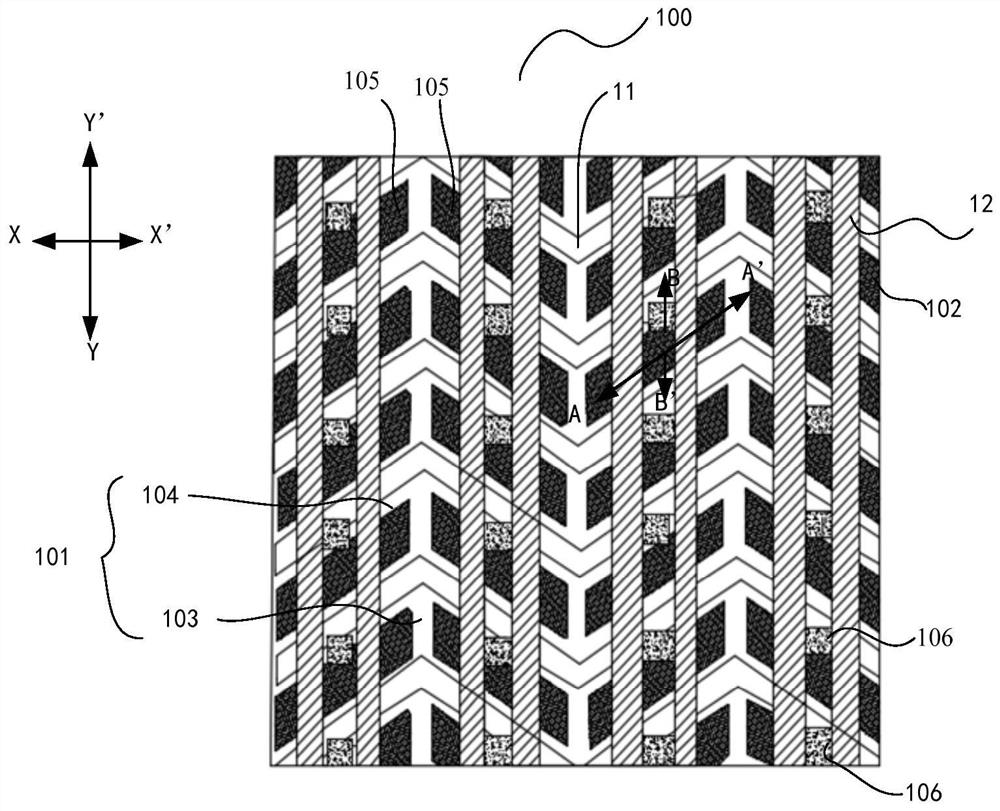

Semiconductor structure and preparation method

The invention relates to the technical field of semiconductors, in particular to a semiconductor structure. The semiconductor structure comprises a substrate having an active region defined by an isolation structure, embedded word lines extending in a first direction across the active region, an embedded bit line extending along at least part of the isolation structure with the extending directionintersected with the first direction, and an air gap positioned between the two adjacent embedded word lines. An embedded bit line is formed in an isolation structure, the bit line-unit coupling effect is reduced, the data sensing margin is improved, and moreover, an air gap is formed between the adjacent embedded word lines, and the dielectric constant of air is relatively small, so that the coupling effect of the adjacent embedded word lines can be reduced, the row hammering effect between the adjacent active regions is reduced, and the reliability of the semiconductor device is improved.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI +1

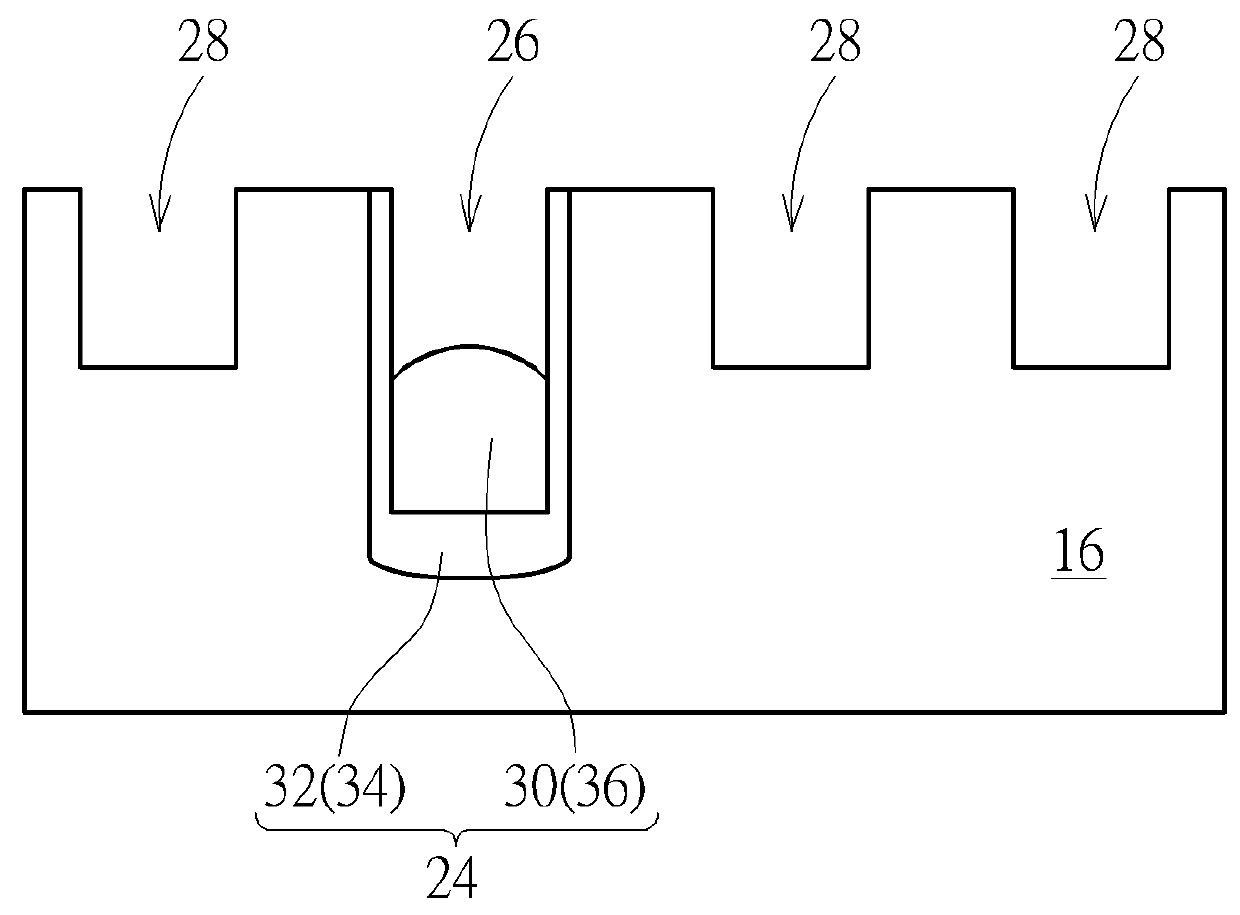

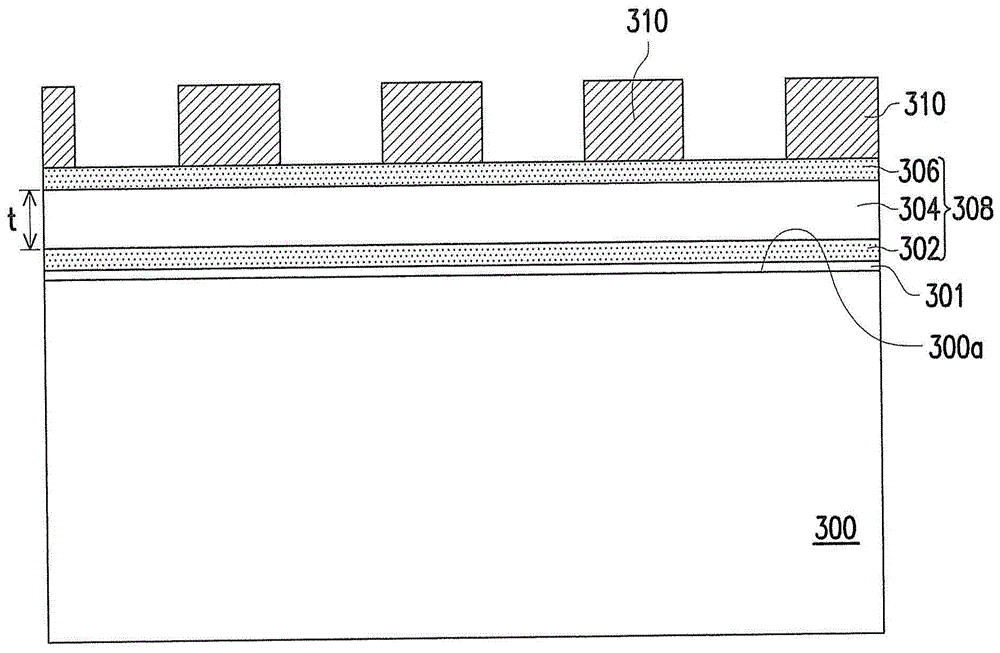

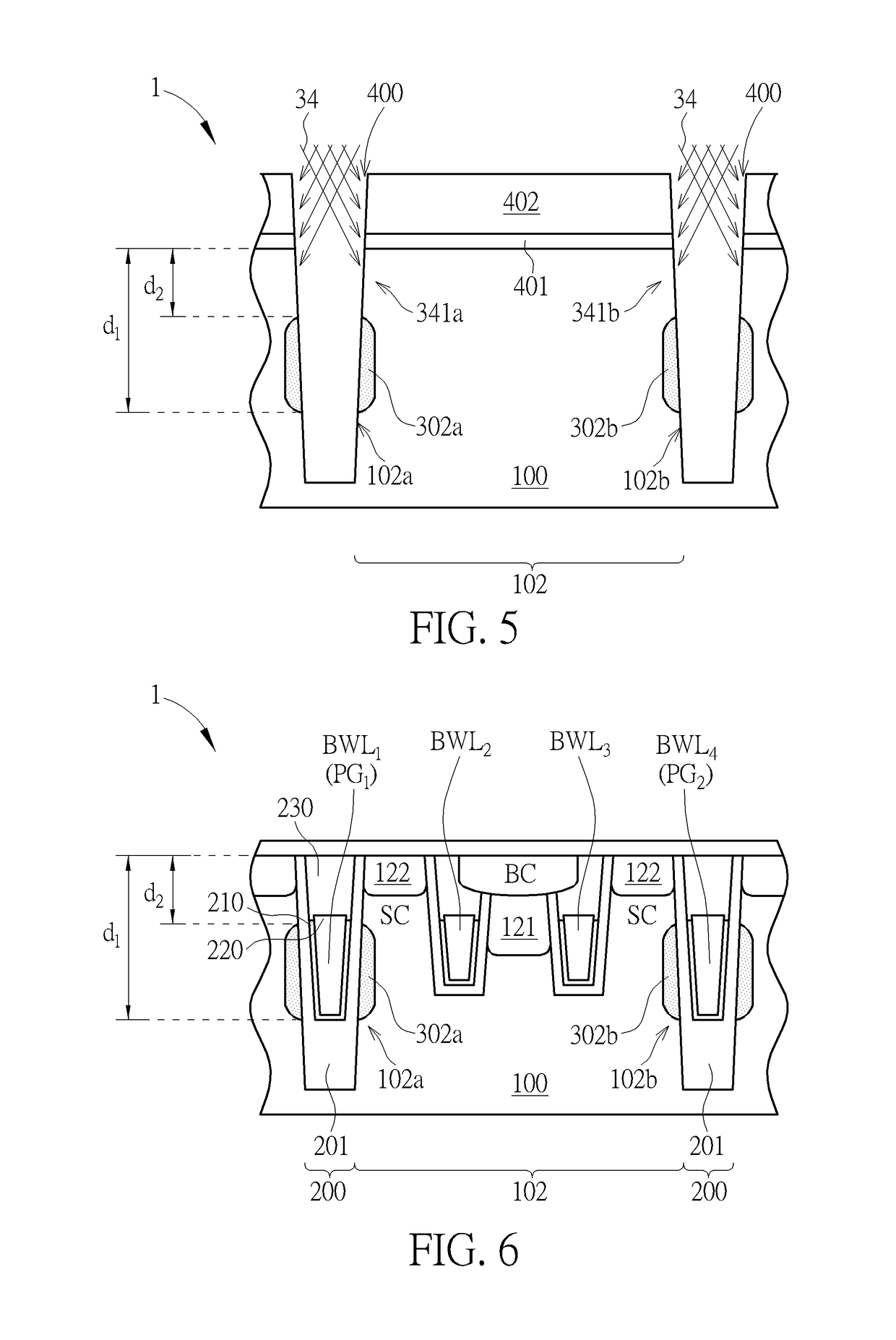

Semiconductor structure for preventing row hammering issue in DRAM cell and method for manufacturing the same

ActiveUS10043811B1Preventing row hammering issuePreventing the row hammering issueTransistorSolid-state devicesGate dielectricSemiconductor structure

A semiconductor structure for preventing row hammering issue in DRAM cell is provided in the present invention. The structure includes a trench with a gate dielectric, an n-type work function metal layer, a TiN layer conformally formed within, and a buried word line filled in the trench.

Owner:FUJIAN JINHUA INTEGRATED CIRCUIT CO LTD +1

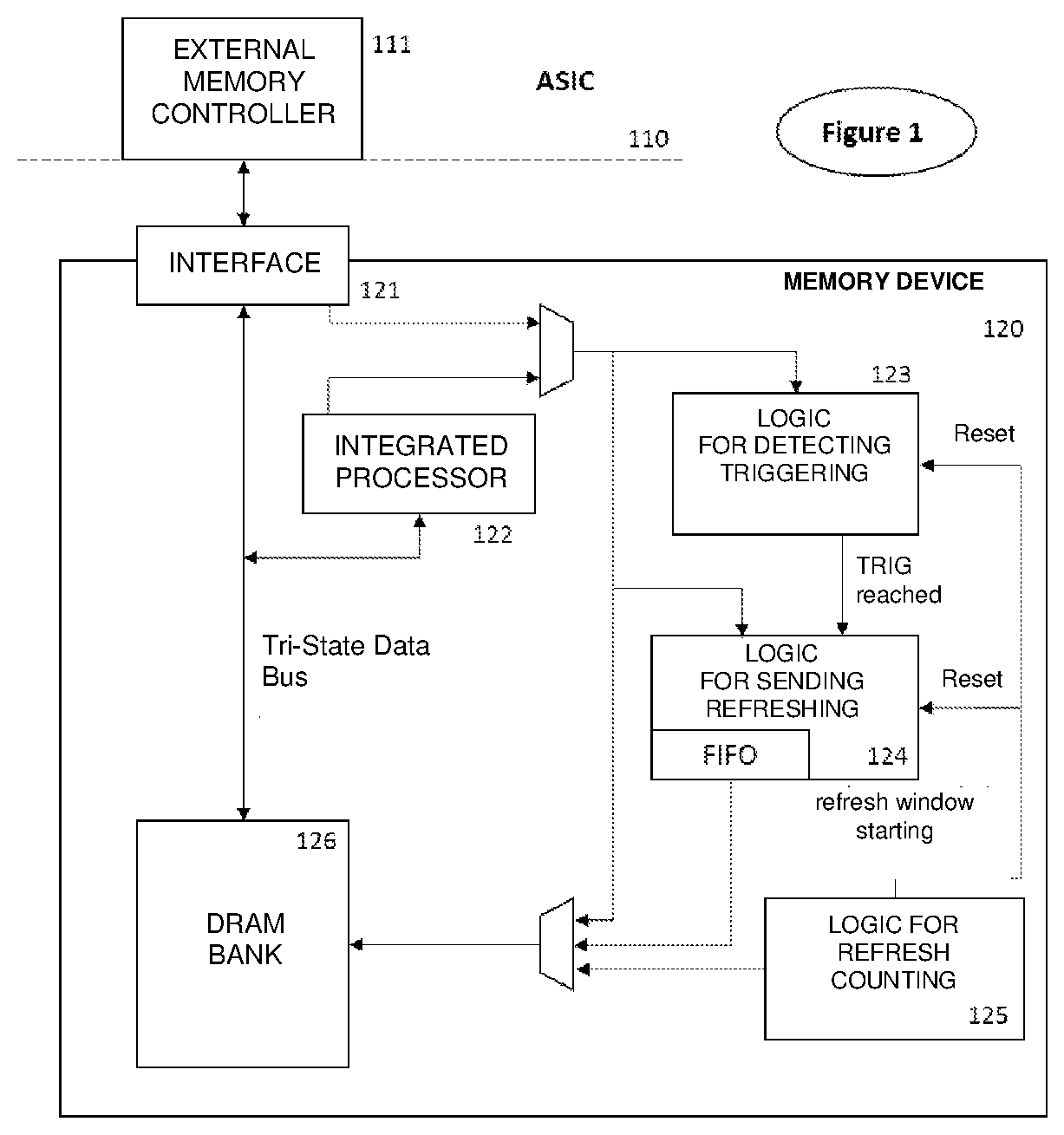

Row hammer correction logic for dram with integrated processor

A memory device comprises one or more bank(s), each bank comprising a plurality of DRAM memory rows, the memory device further comprising: an external access port configured to allow an external memory controller to activate and then access the memory rows of each bank; one or more internal processor(s) capable of activating and then accessing the memory rows of each bank; a logic for detecting triggering of the Row Hammer configured to monitor, for each bank, the activation commands from the external memory controller and from one or more internal processor(s), the logic for detecting triggering including memory storage and a logic for sending preventive refresh configured to implement a refresh operation for one or more of the adjacent rows of each identified row by emitting refresh requests instead of the periodic refresh requests generated by the external memory controller, delaying one or more of said periodic refresh requests.

Owner:UPMEM

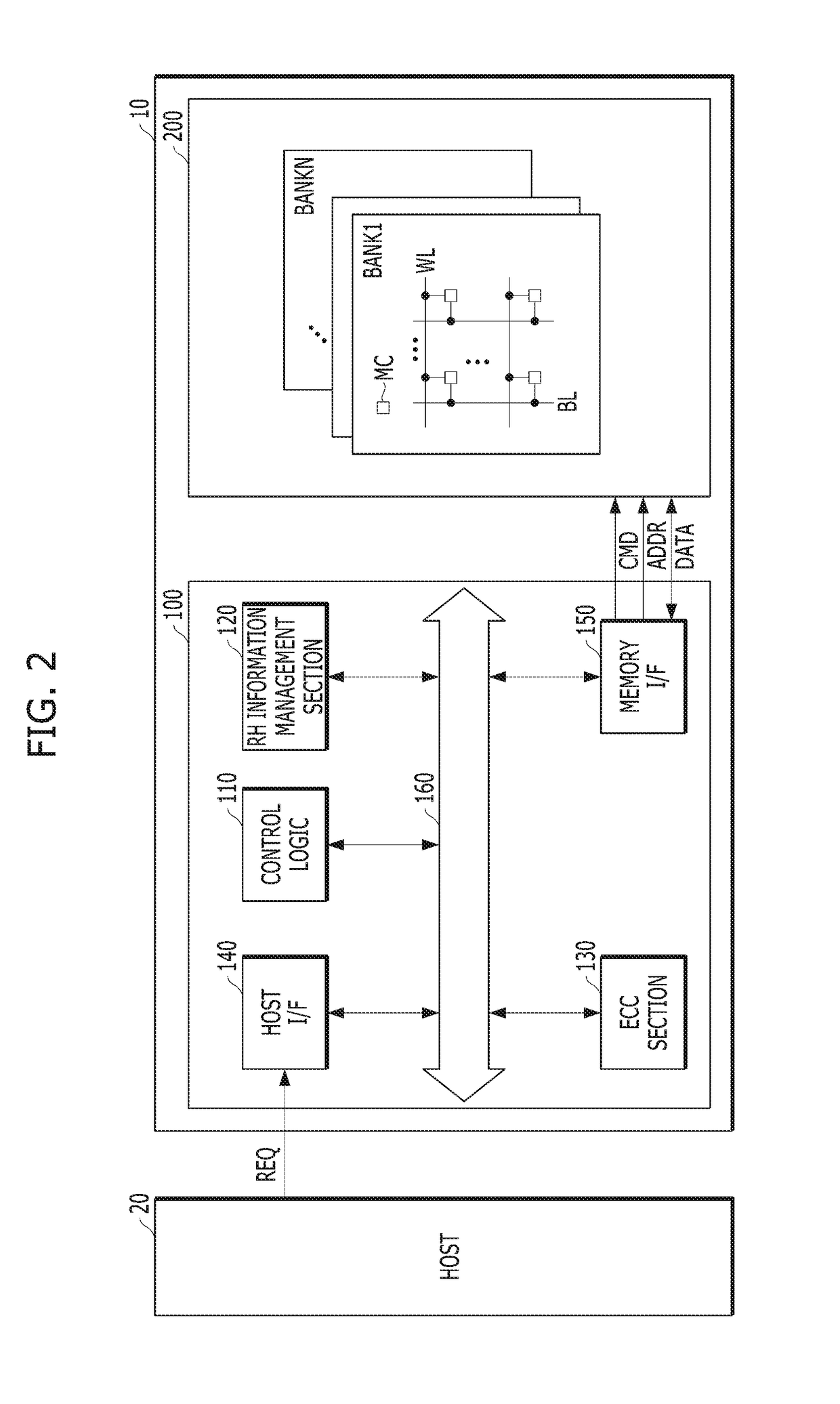

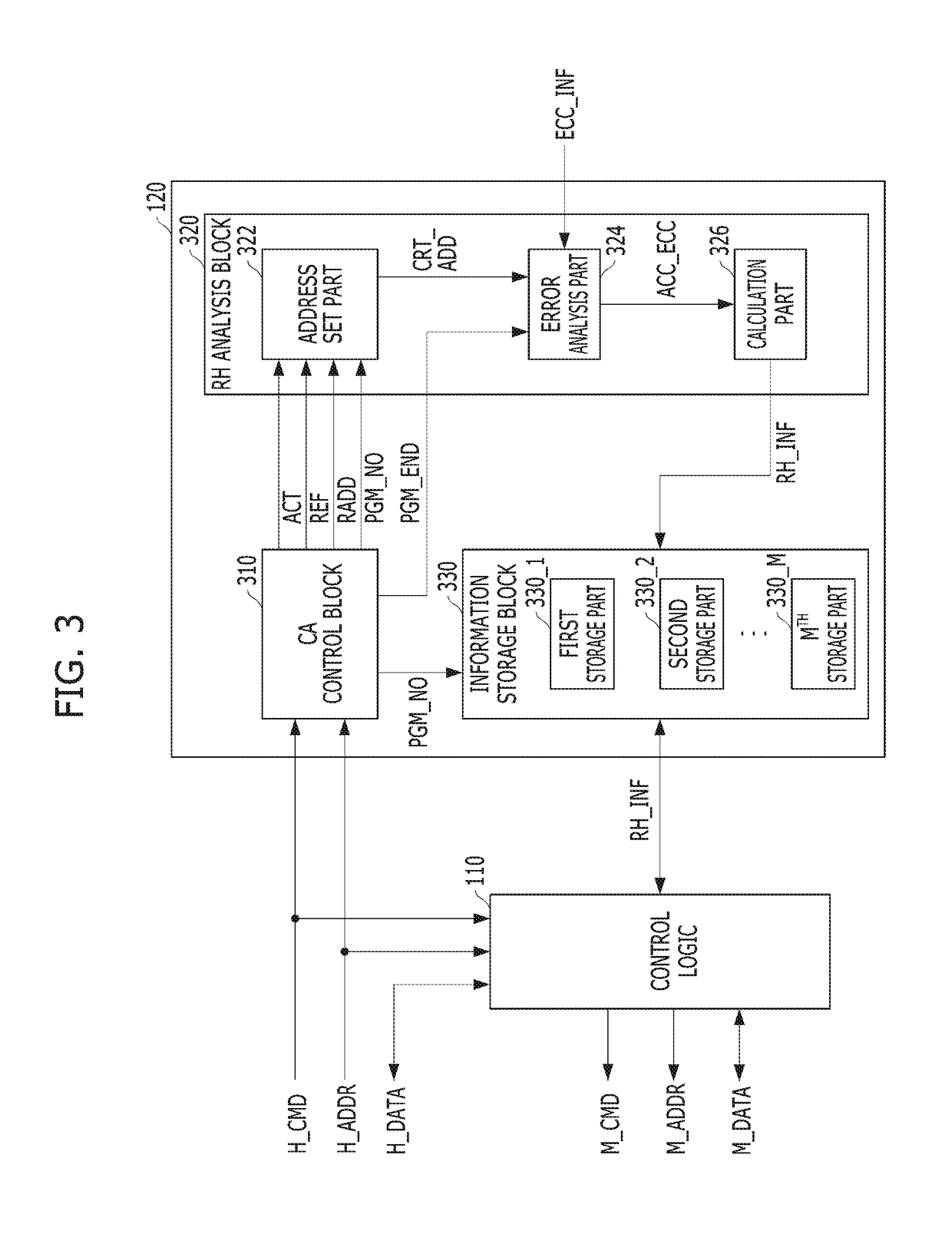

Memory system and operating method thereof

ActiveUS20190087127A1Use minimizedInput/output to record carriersDigital storageRow hammerMemory controller

A memory system includes: a memory device including a plurality of banks; and a memory controller suitable for: controlling an operation of the memory device, calculating row hammer information for each of the banks for each program having a command set requested from a host, and scheduling the banks based on the row hammer information for each of the banks corresponding to a specific program when the specific program is requested from the host.

Owner:SK HYNIX INC

Systems and methods for performing row hammer refresh operations in redundant memory

Steering logic circuitry includes bit-flipping logic that determines a first neighboring redundant word line adjacent to a redundant word line of a memory bank, which also includes normal word lines. Redundant word lines include main word lines, each of which includes paired word lines. Each paired word line includes two redundant word lines. The steering logic circuitry also includes border determination logic that determines whether the redundant word line is on a border between the redundant word lines and an end of the memory bank or the normal word lines. The steering logic circuitry further includes main word line steering logic that determines a neighboring main word line that a second neighboring redundant word line adjacent to the redundant word line is disposed in, and paired word line steering logic that determines a neighboring paired word line that the second neighboring redundant word line is disposed in.

Owner:MICRON TECH INC

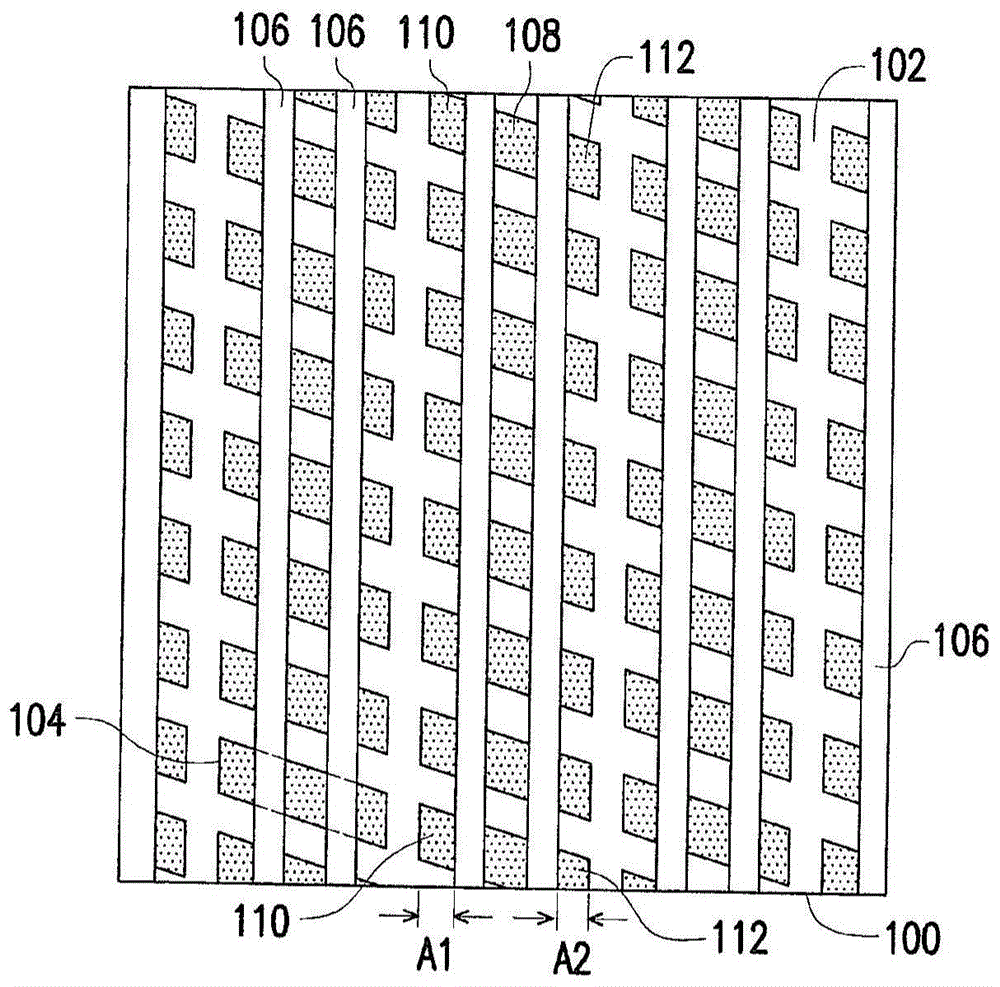

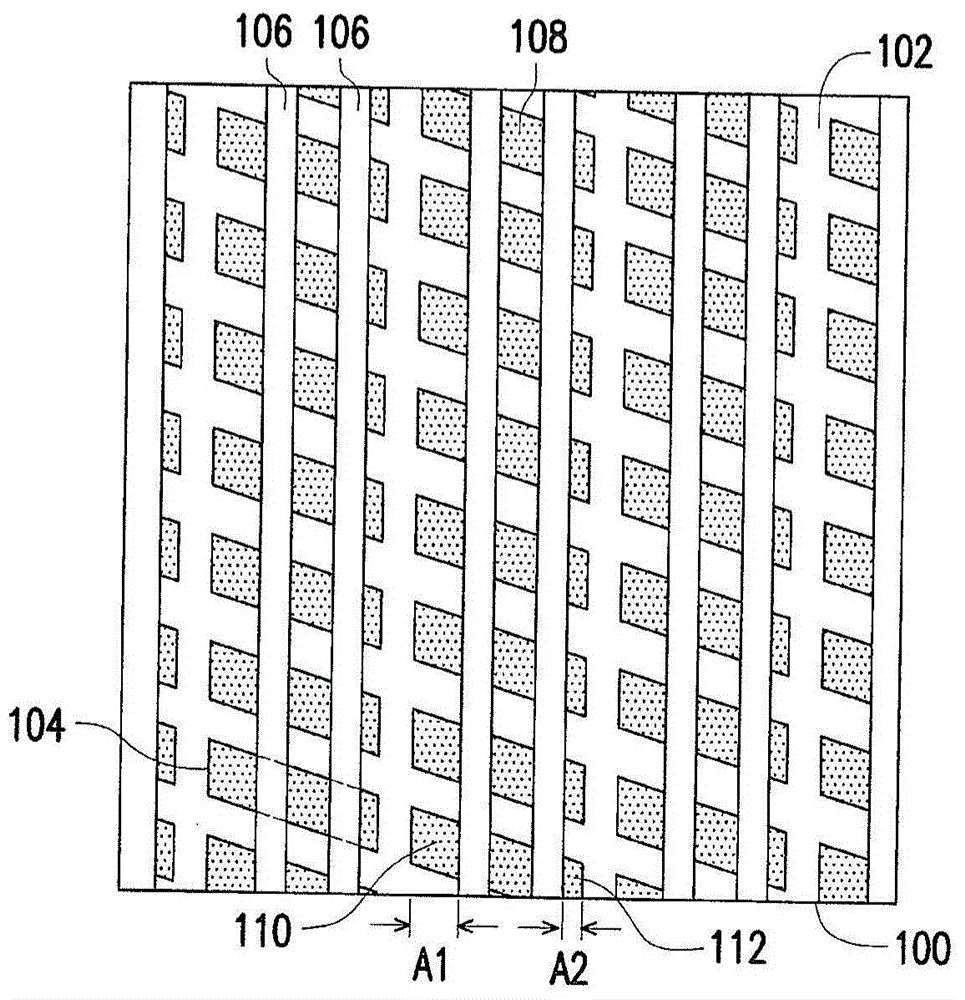

Method of manufacturing buried word lines and isolating structures thereof

ActiveCN105097641AReduce distractionsGuaranteed areaSemiconductor/solid-state device manufacturingRow hammerEngineering

A method of manufacturing buried word lines and isolating structures thereof comprises the following steps of forming a plurality of buried word lines inside a substrate, wherein the top of each buried word line is lower than the surface of the substrate; forming a mask structural layer inside a groove on each buried word line, making the mask structural layer protrude by removing a part of the structure so that side walls of the mask structural layer form distance pieces and a plurality of self-aligned grooves are further formed; removing substrate parts under the grooves in an etching way with the distance pieces and the mask structural layers as the etching masks so as to form a plurality of isolating structure grooves; and further forming isolating structures inside the isolating structure grooves. By means of the manufacturing method, interference (Row Hammer) among word lines can be effectively alleviated. Furthermore, the area of a contact zone inside an active region can be kept.

Owner:WINBOND ELECTRONICS CORP

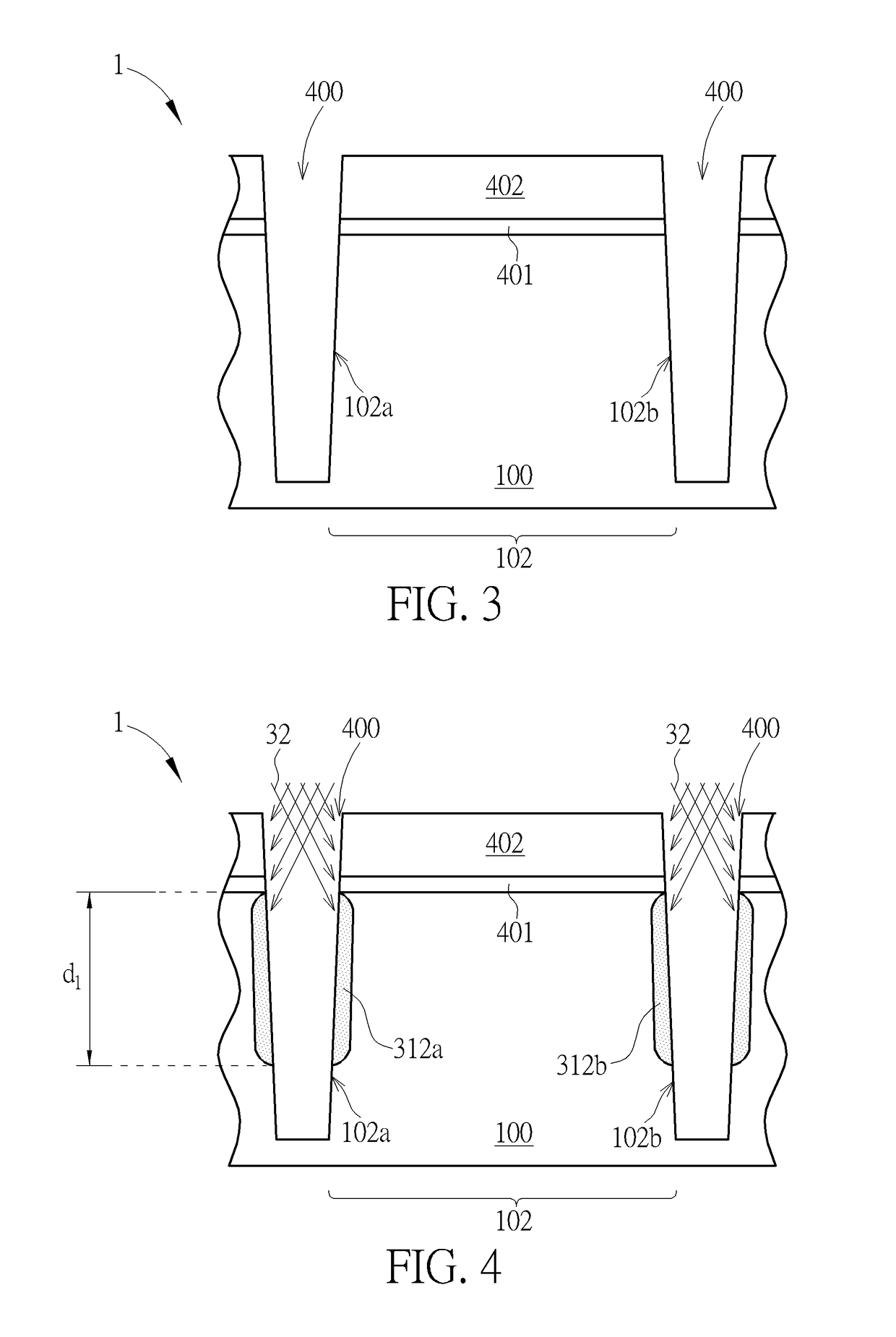

Semiconductor structure capable of improving row hammer effect in dynamic random access memory and fabrication method thereof

ActiveUS10211086B2Simple structureTransistorSolid-state devicesStatic random-access memoryRandom access memory

A semiconductor structure includes a substrate with a first conductivity type and a first doping concentration, an active area with its longitudinal axis extending along a first direction, a trench isolation structure contiguous with an end surface of the active area, a passing gate in the trench isolation structure and extending along a second direction that is not parallel with the first direction, and a localized doping region with a second conductivity type and a second doping concentration that is located on the end surface.

Owner:UNITED MICROELECTRONICS CORP +1

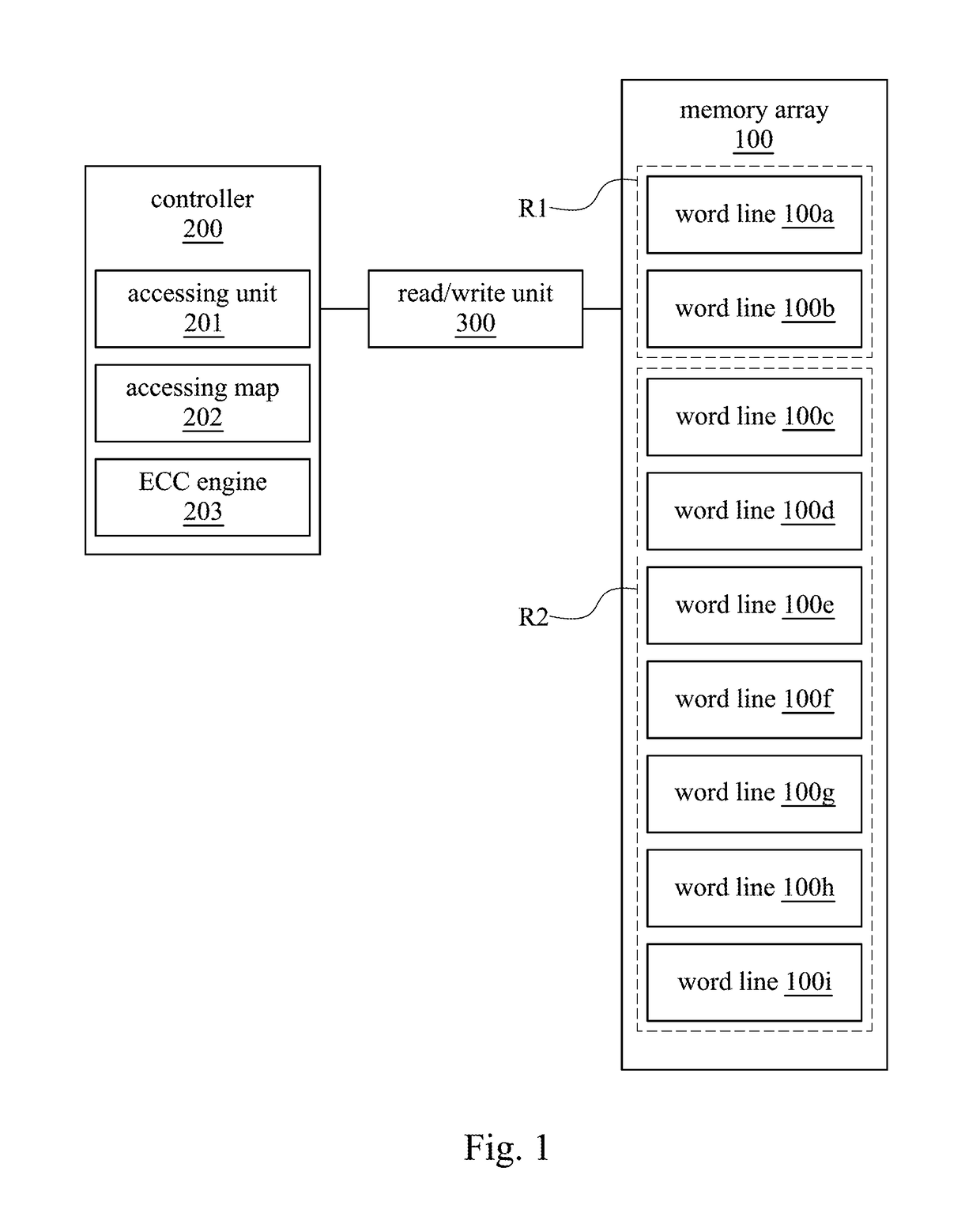

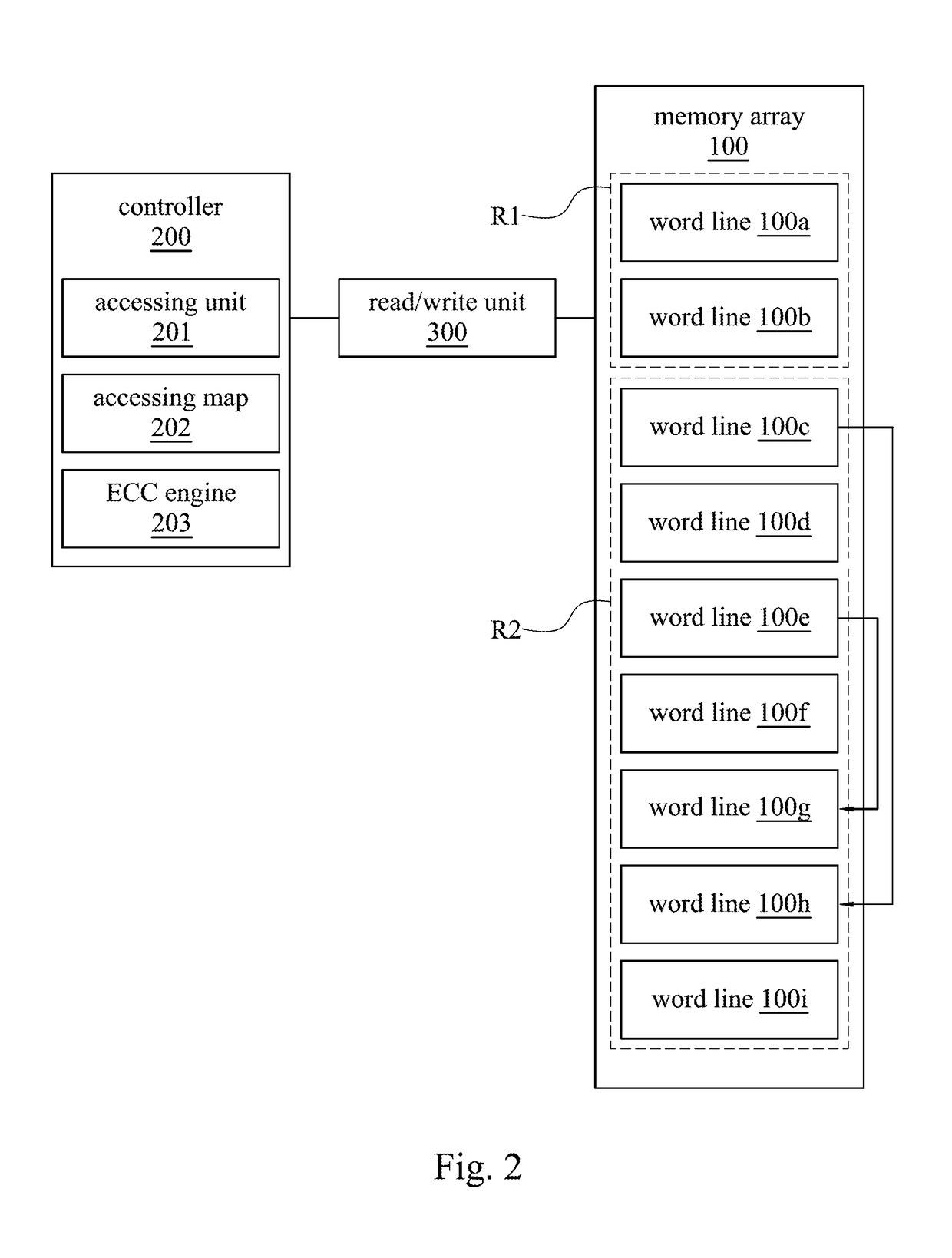

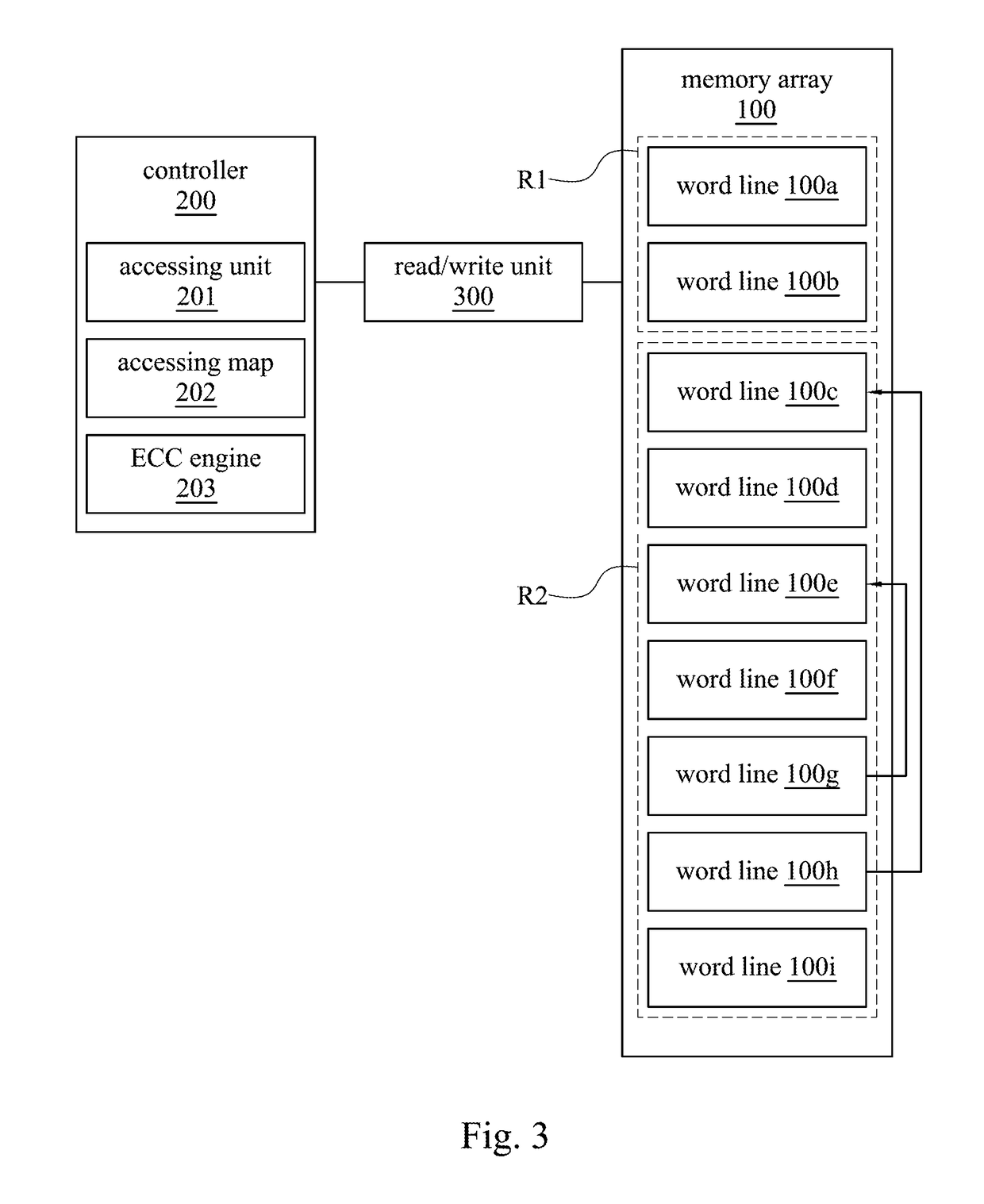

System and method for preserving data in volatile memory

Present disclosure includes a system for preserving data in a volatile memory and a method thereof. The volatile memory comprises a plurality of refreshing units, and each of the refreshing units comprises a plurality of word lines for storing data. The system comprises an accessing unit. The accessing unit is configured to detect a row-hammer indication indicating a first word line is frequently accessed, wherein the accessing unit is configured to copy data stored in the first word line to a second word line when the row-hammer indication is detected on the first word line, wherein the data stored in the first and the second word lines are available to be selectively accessed.

Owner:NAN YA TECH

Memory device and data refreshing method thereof

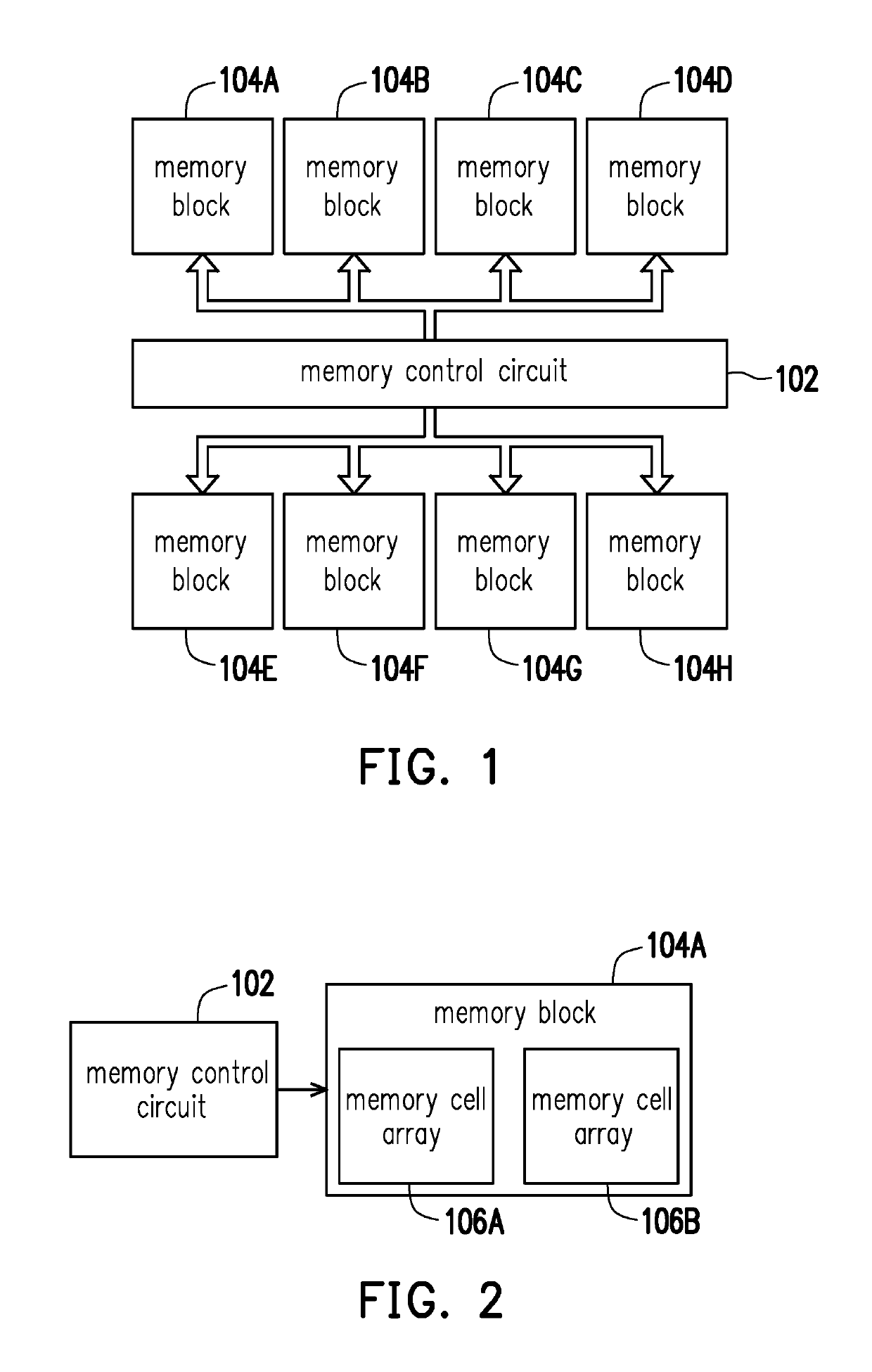

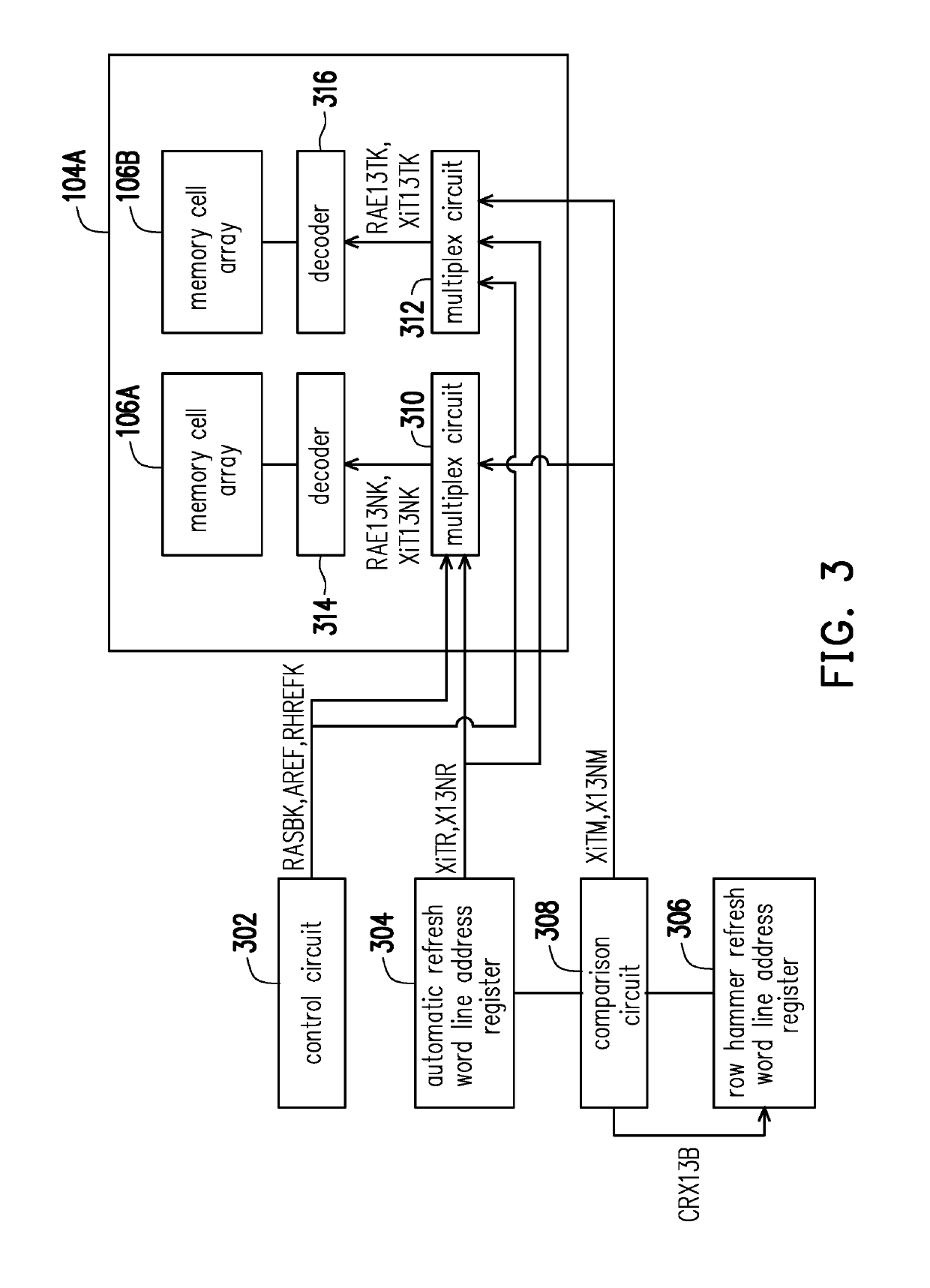

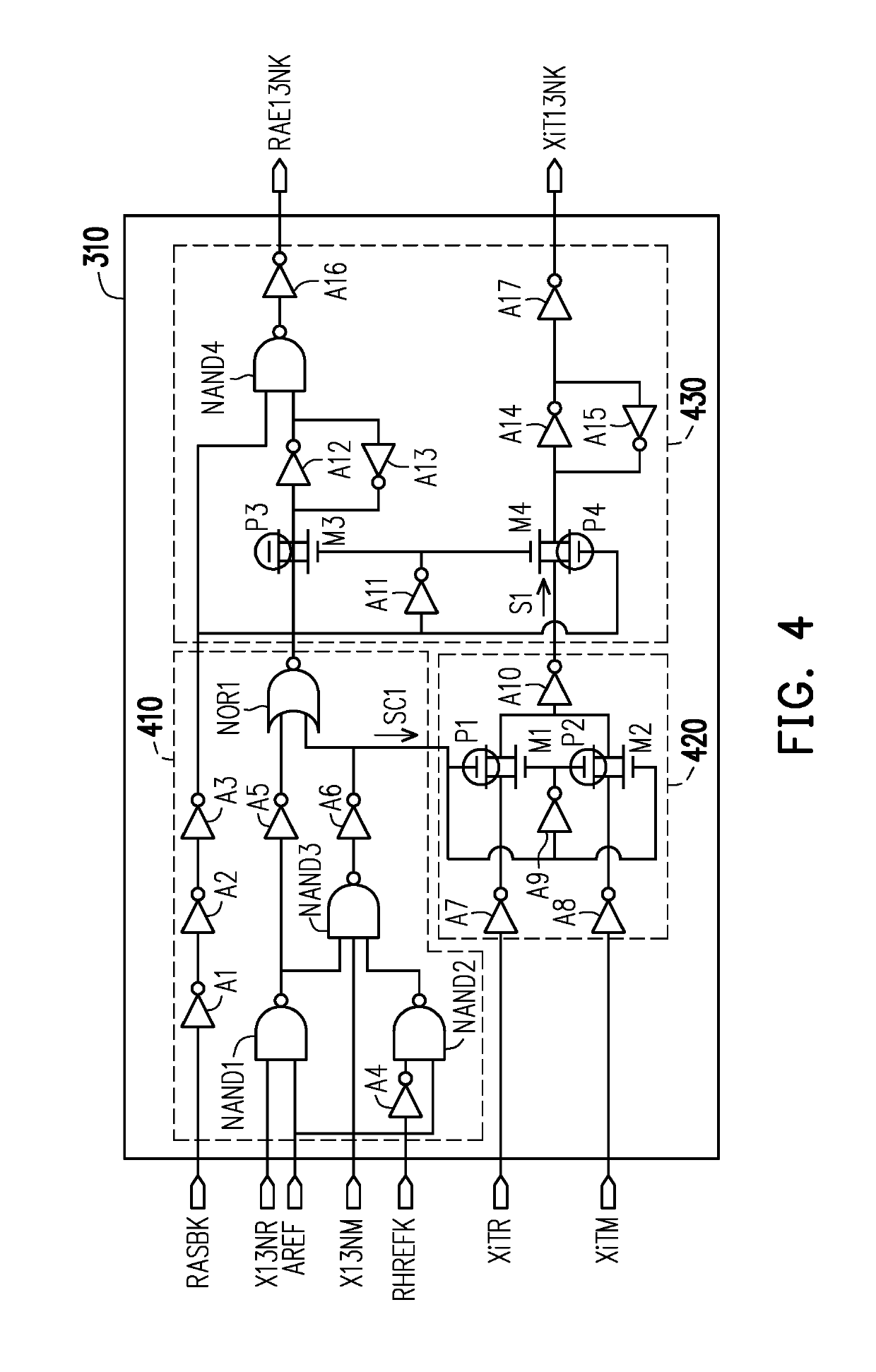

A memory device and a data refreshing method thereof are provided. When an automatic refresh word line address and a row hammer refresh word line address belong to the same memory cell array, memory cells corresponding to the automatic refresh word line address are refreshed, and a time to refresh memory cells corresponding to the row hammer refresh word line address is postponed.

Owner:WINBOND ELECTRONICS CORP

Dram and method for accessing a dram

ActiveUS10019350B1Row hammerReduce performanceMemory architecture accessing/allocationMemory adressing/allocation/relocationAlgorithmAccess frequency

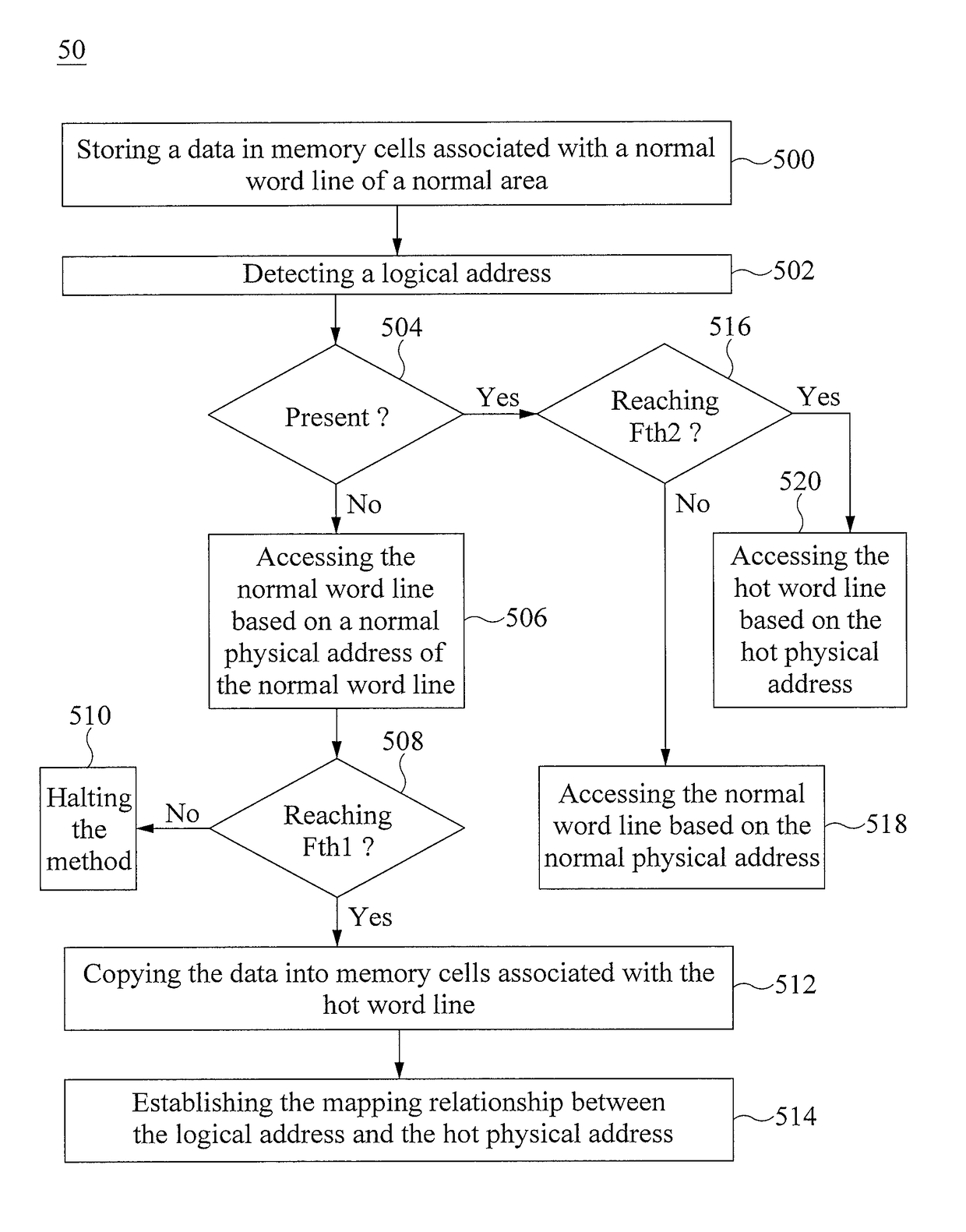

The present disclosure provides a method. The method includes copying a data stored in memory cells associated with a normal word line subject to a row hammer effect into memory cells associated with a hot word line before a condition is satisfied, wherein the condition includes an access frequency of the normal word line reaching a threshold frequency; accessing, based on a logical address, the normal word line before the condition is satisfied; accessing, based on the logical address, the hot word line associated with the copied data only if the condition is satisfied; and accessing the data no longer from the normal word line only if the condition is satisfied.

Owner:NAN YA TECH

Implementing dram row hammer avoidance

ActiveUS20160180900A1Negative effectOvercome disadvantagesDigital storageMemory systemsStatic random-access memoryRandom access memory

A method and apparatus for implementing row hammer avoidance in a dynamic random access memory (DRAM) in a computer system. Hammer detection logic identifies a hit count of repeated activations at a specific row in the DRAM. Monitor and control logic receiving an output of the hammer detection logic compares the identified hit count with a programmable threshold value. Responsive to a specific count as determined by the programmable threshold value, the monitor and control logic captures the address where a selected row hammer avoidance action is provided.

Owner:IBM CORP

Method, apparatus and system for responding to a row hammer event

ActiveUS20160225434A1Memory adressing/allocation/relocationDigital storageRow hammerMemory controller

Techniques and mechanisms to facilitate an operational mode of a memory device to prepare for a targeted refresh of a row in memory. In an embodiment, the memory device performs one or more operations while in the mode to prepare for a future command from a memory controller, the command to implement, at least in part, a targeted refresh of a row in a first bank of the memory device. Prior to such a command, the memory device services another command from the memory controller. In another embodiment, servicing the other command includes the memory device accessing a second bank of the memory device while the memory device operates in the mode, and before completion of an expected future targeted row refresh.

Owner:INTEL CORP

Memory device and refreshing method thereof

ActiveUS20190325944A1Reduce redundant refreshing operationAvoid lossInput/output to record carriersDigital storageMemory bankRow hammer

A memory device and a data refreshing method of the memory device are provided. The memory device includes a memory array and a memory control circuit. The memory control circuit counts the number of access commands to generate a first count value and counts the number of refreshing commands to generate a second count value. If the first count value is equal to the second count value, the memory control circuit latches a memory bank address and a memory row address corresponding to the access commands to obtain a row hammer refreshing bank address and a row hammer refreshing row address. The memory control circuit performs a row hammer refreshing operation on a memory bank according to the row hammer refreshing bank address and the row hammer refreshing row address.

Owner:WINBOND ELECTRONICS CORP