Patents

Literature

38 results about "Cmos electronics" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

CMOS: Front-End Electronics for Radiation Sensors provides specialized knowledge previously obtained only through the study of multiple technical and scientific papers.

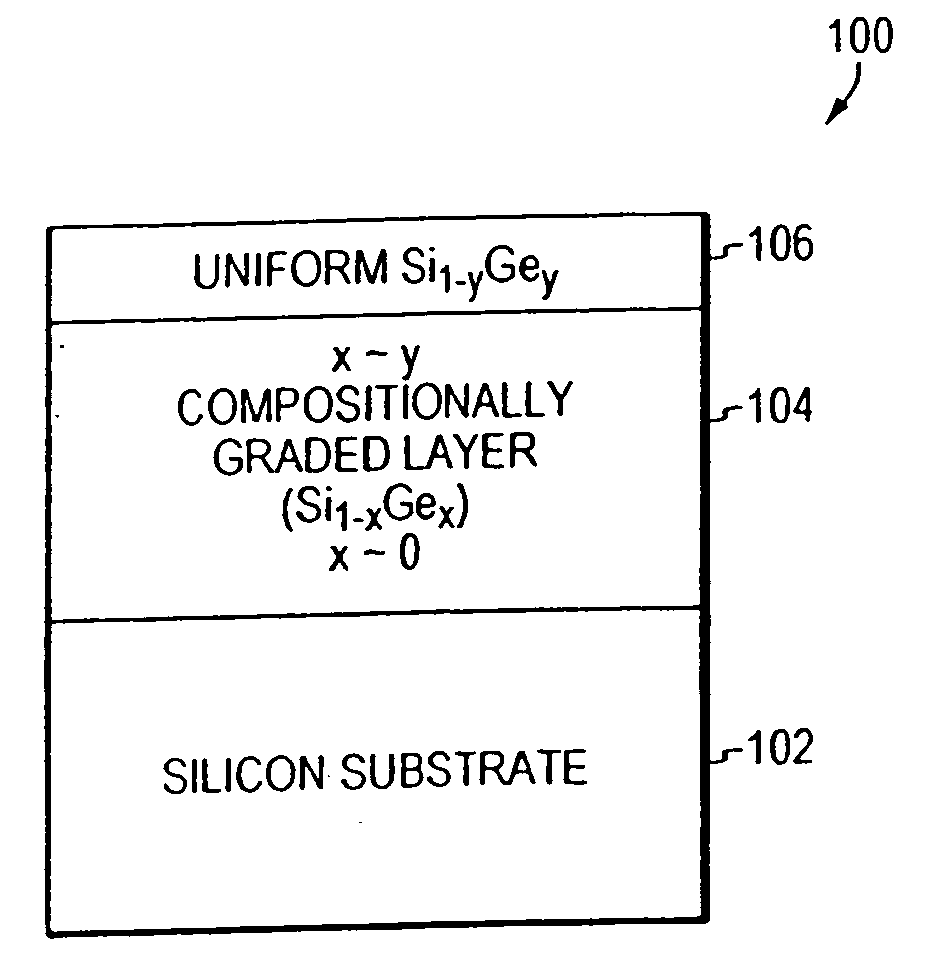

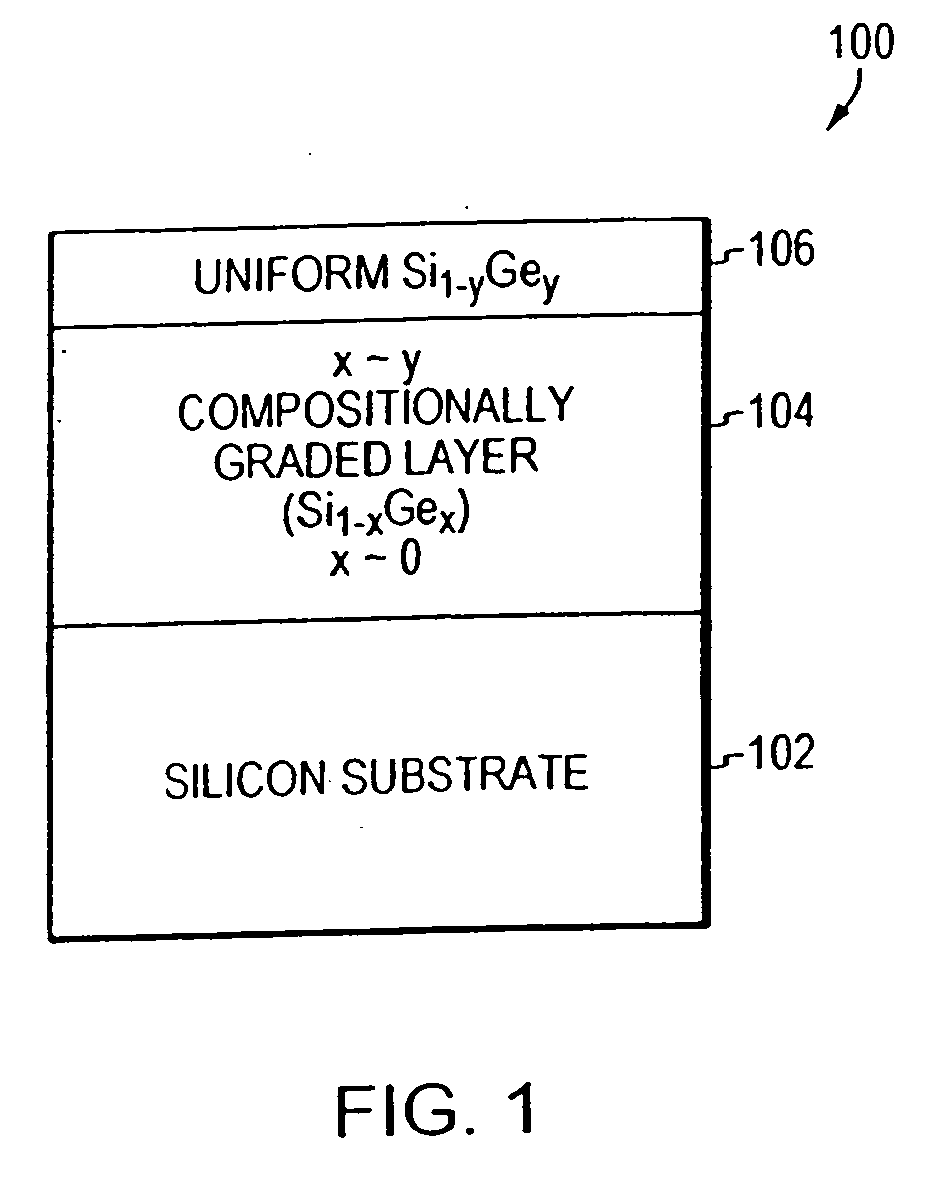

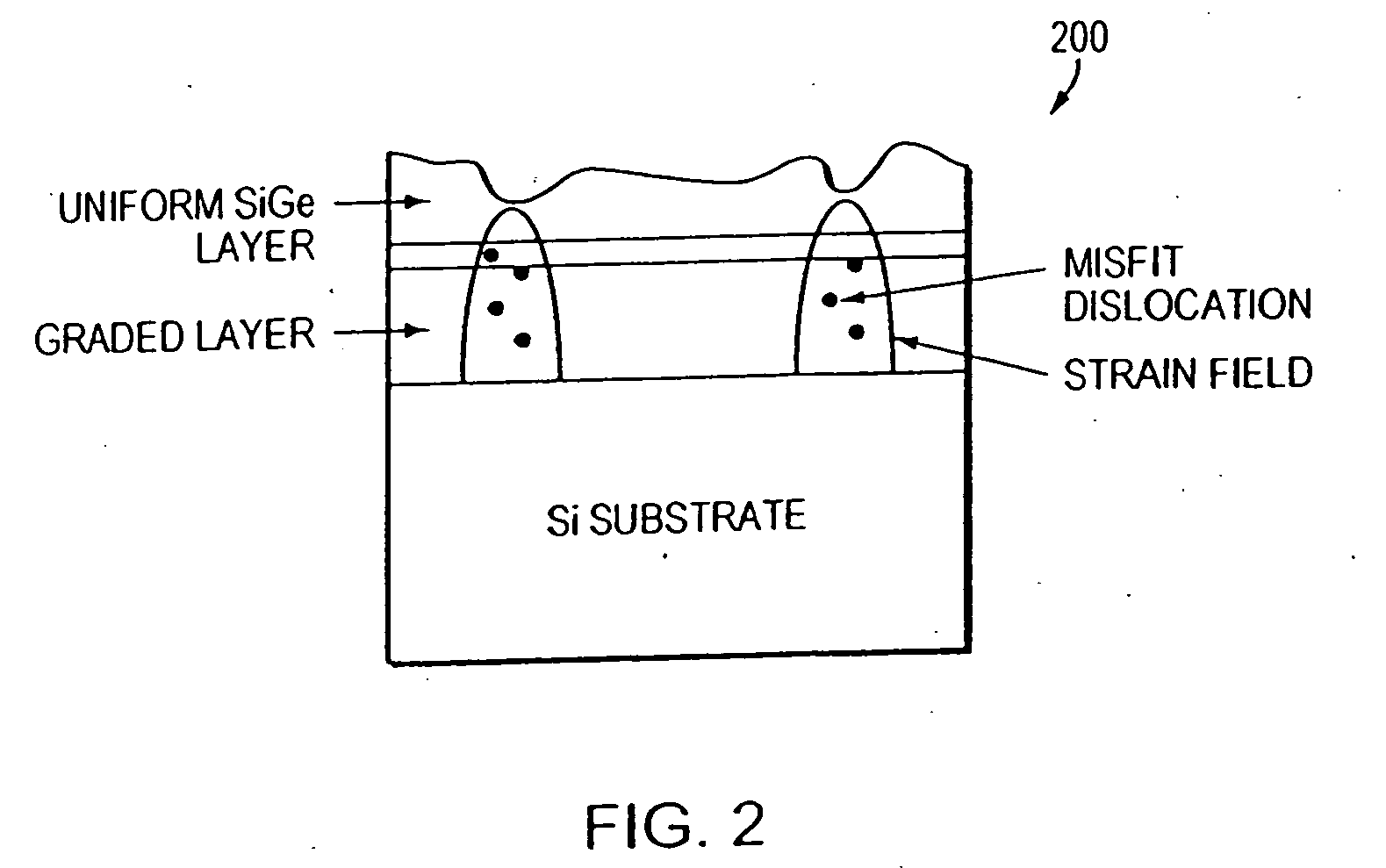

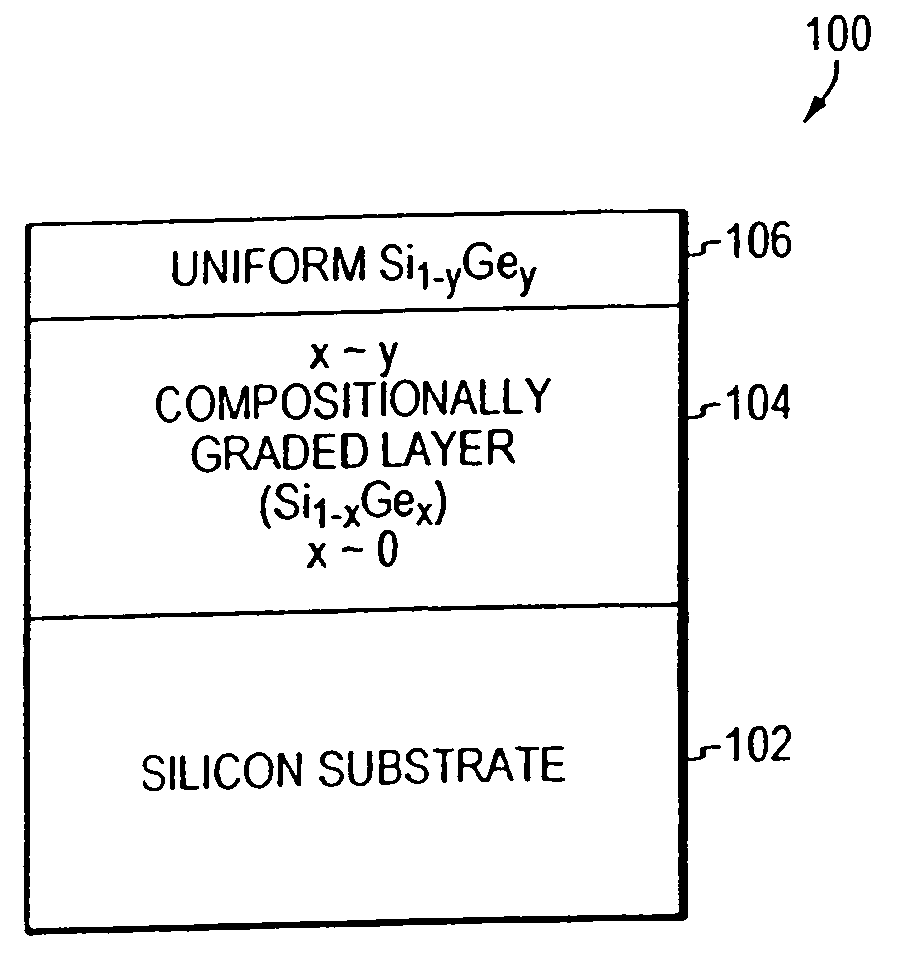

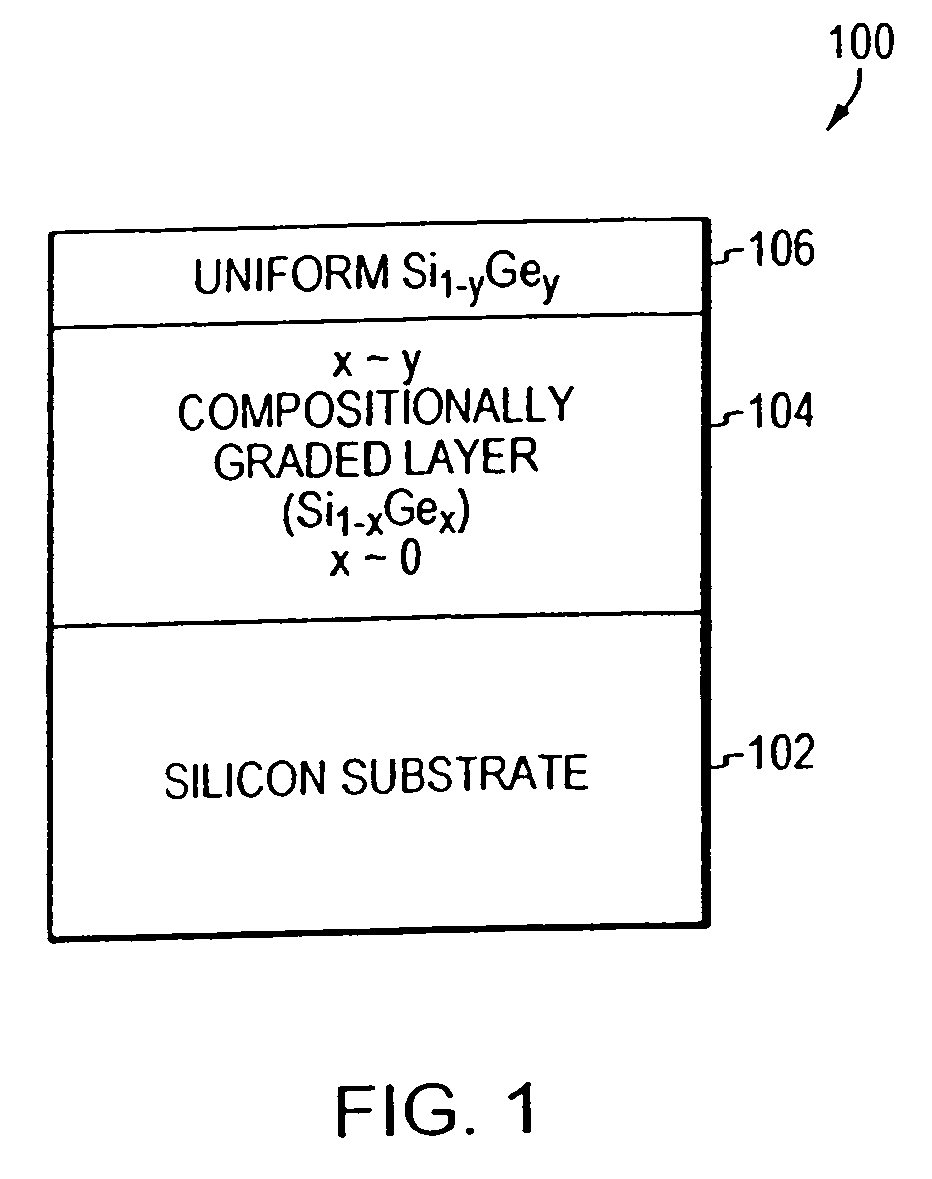

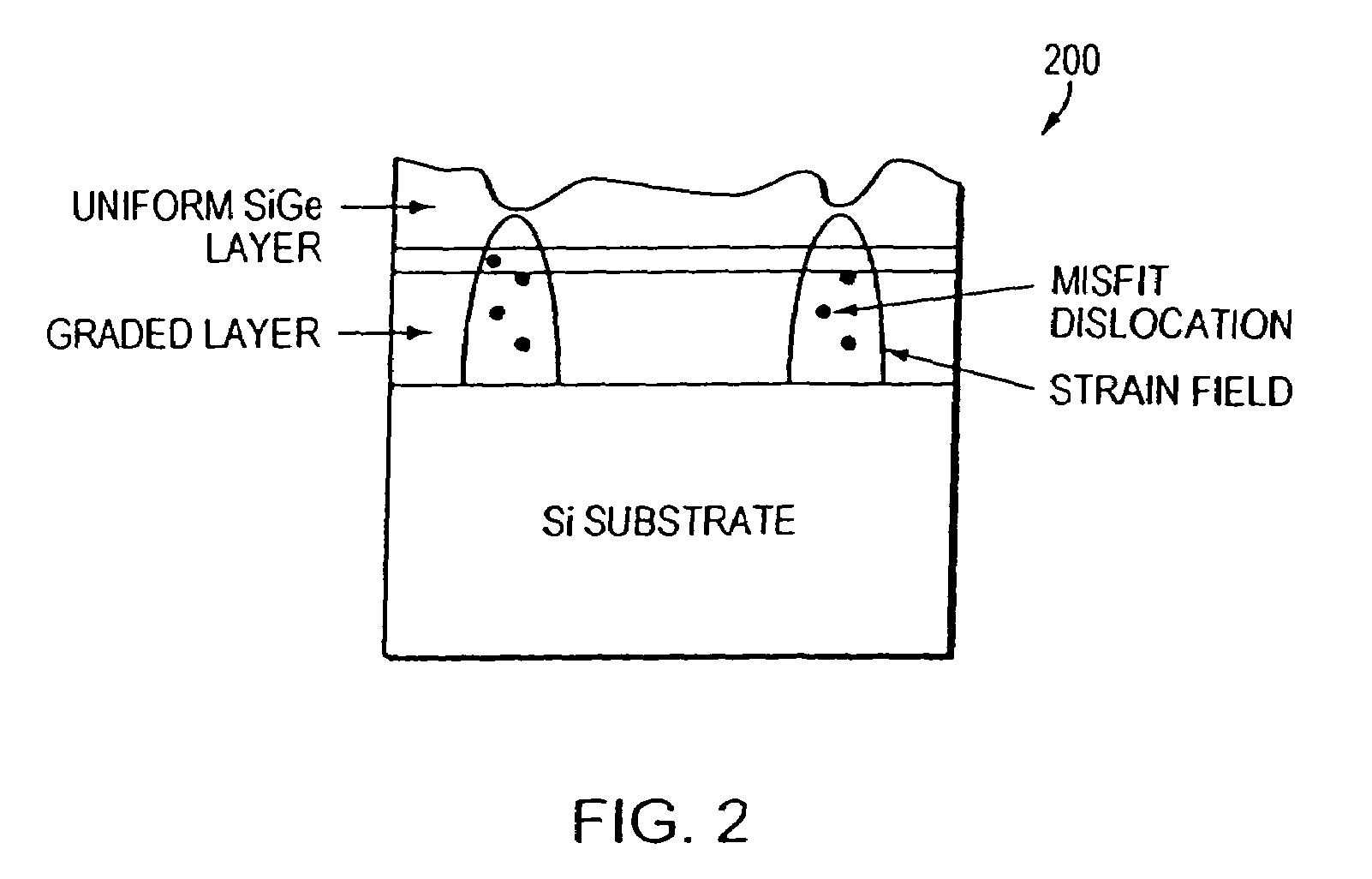

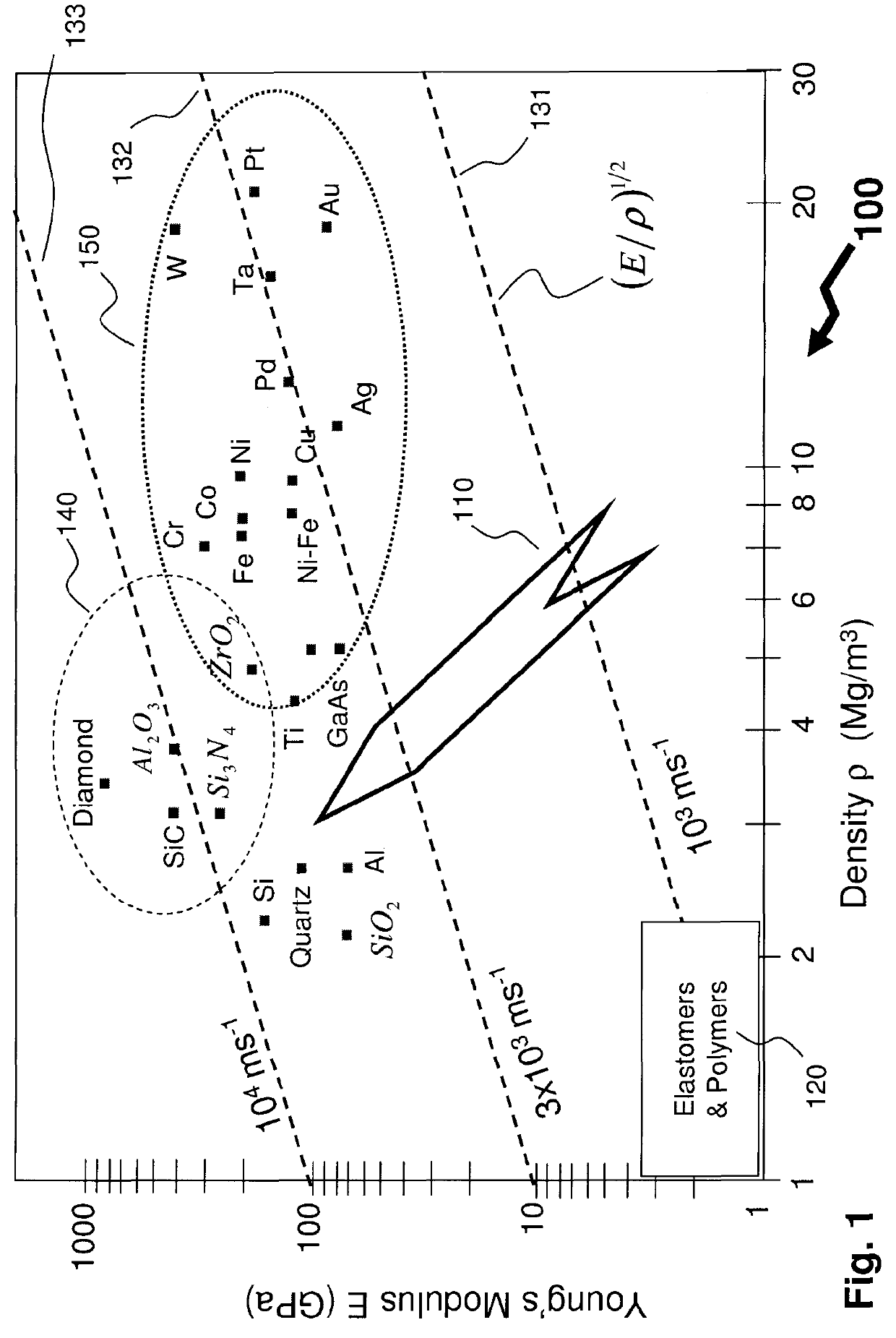

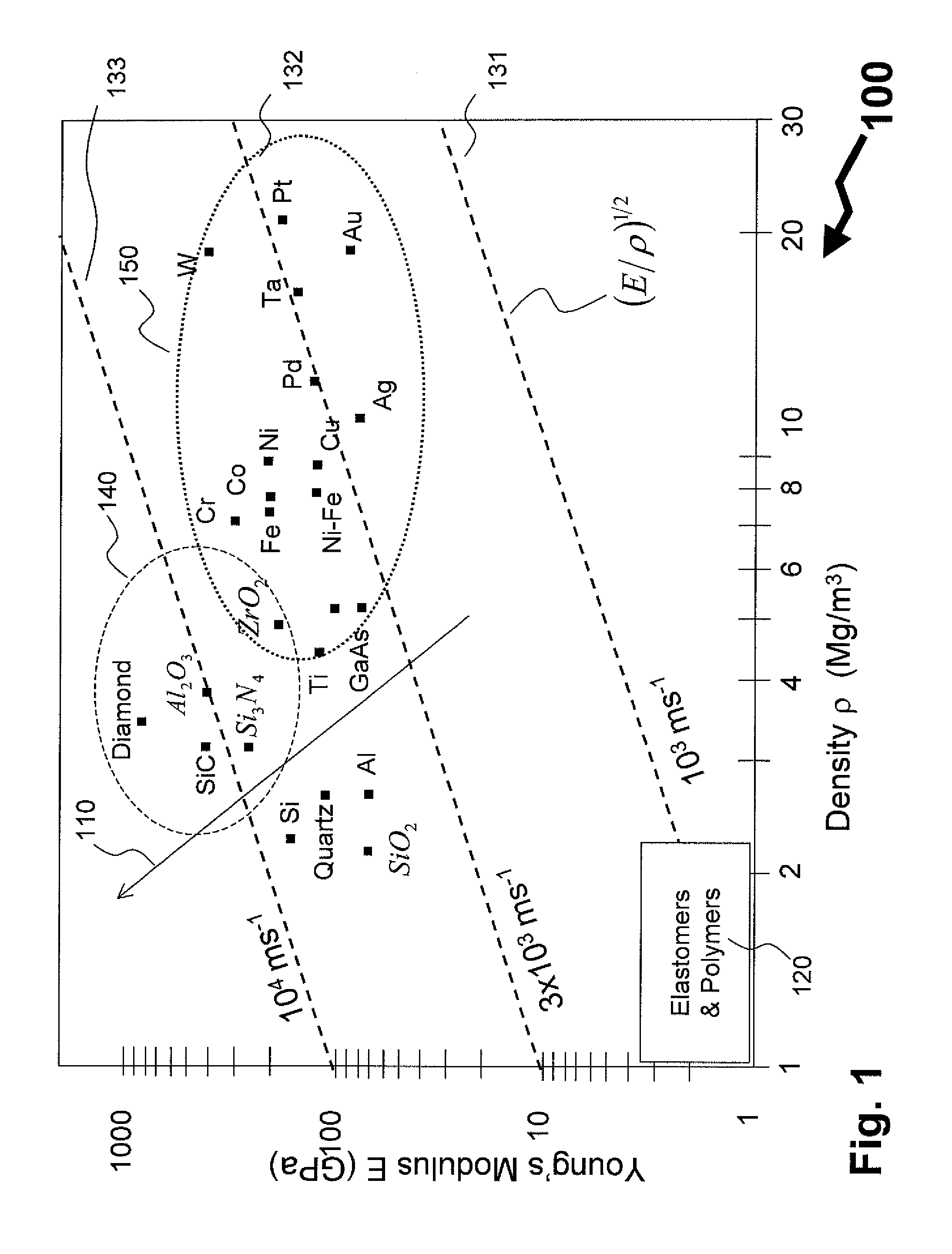

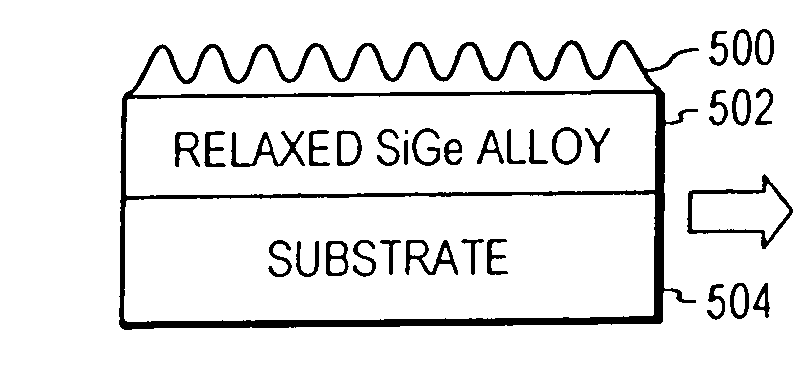

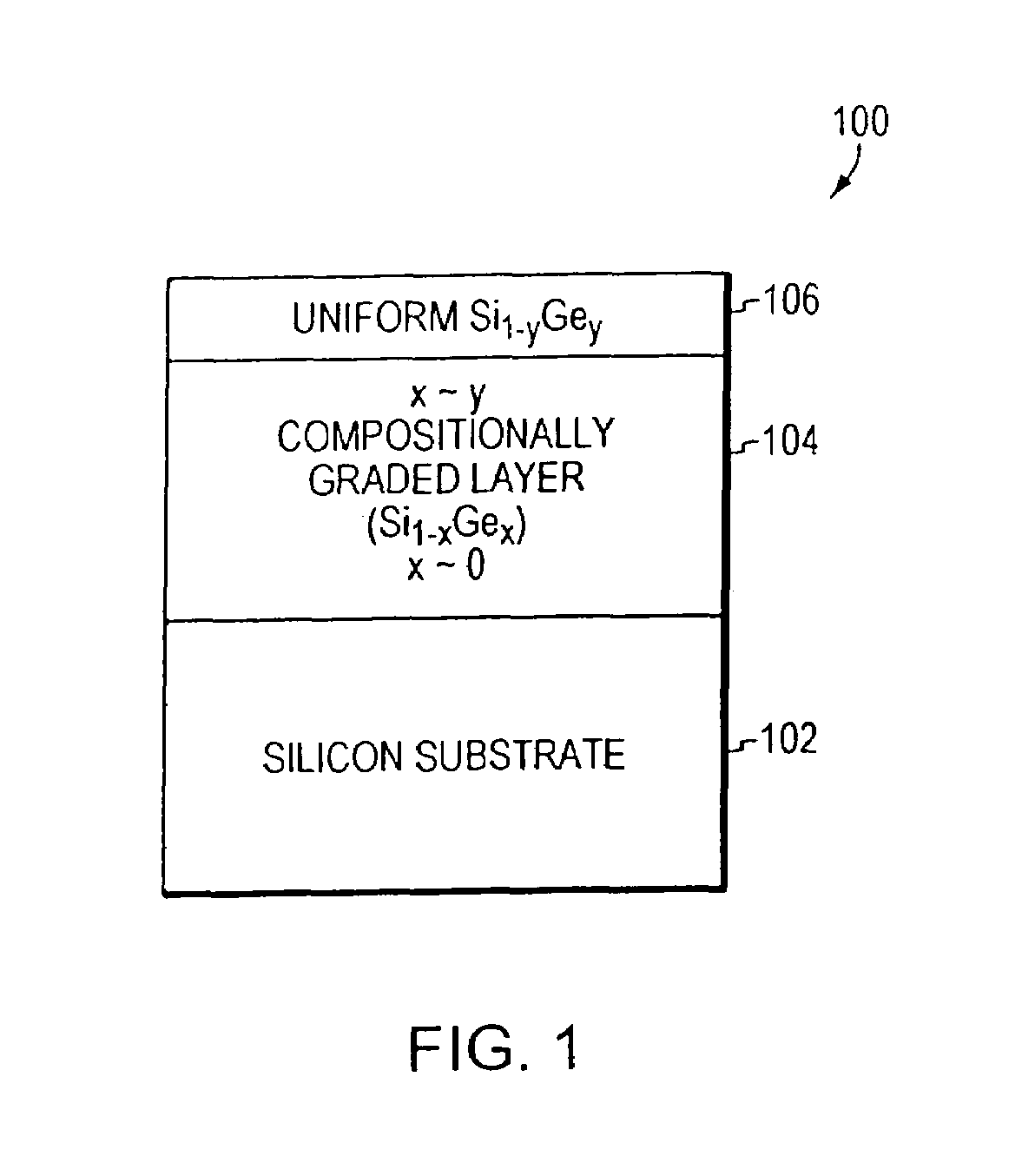

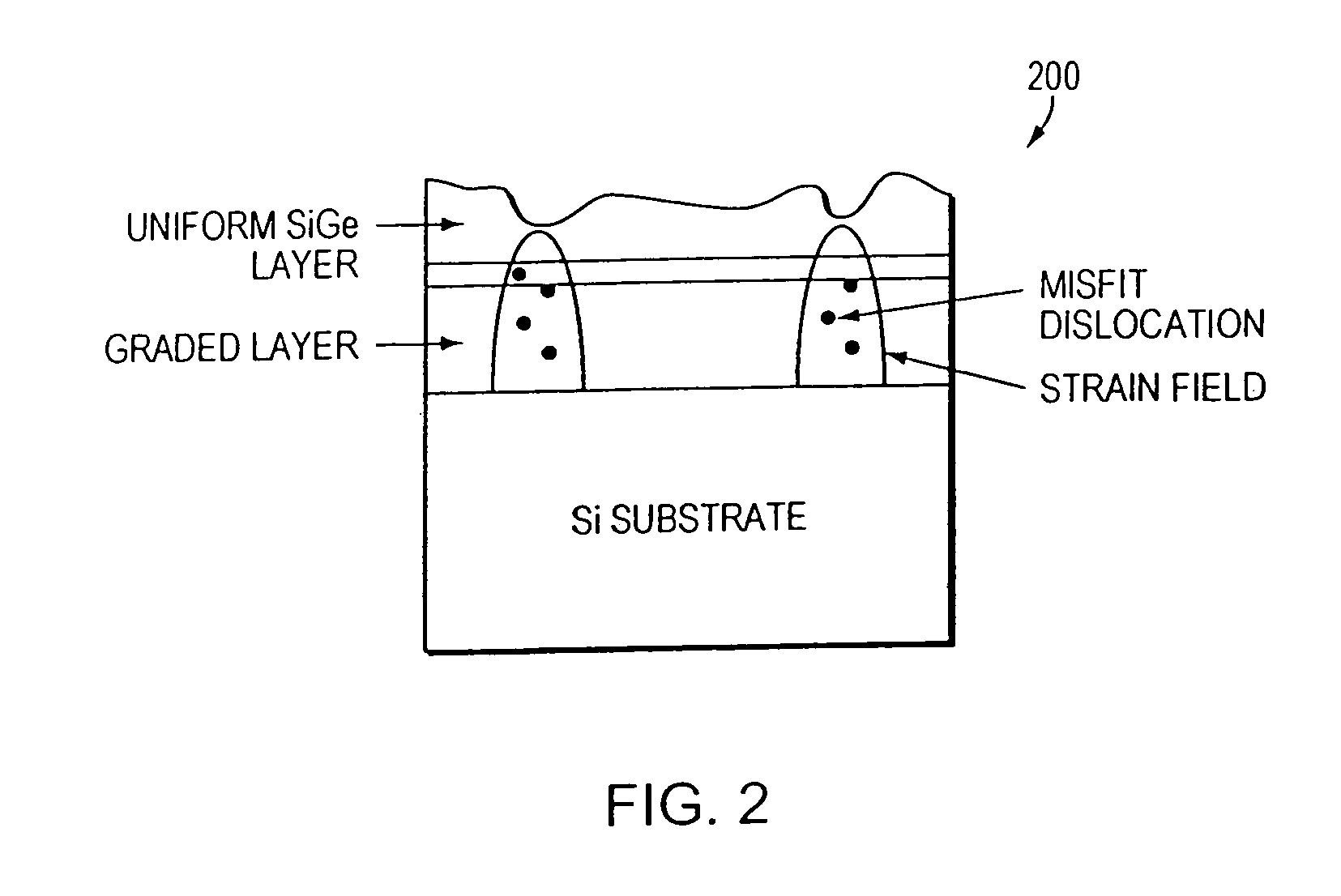

Relaxed SiGe platform for high speed CMOS electronics and high speed analog circuits

InactiveUS20050077511A1Minimal surface roughnessImprove featuresTransistorSemiconductor/solid-state device manufacturingMOSFETLithographic artist

Structures and methods for fabricating high speed digital, analog, and combined digital / analog systems using planarized relaxed SiGe as the materials platform. The relaxed SiGe allows for a plethora of strained Si layers that possess enhanced electronic properties. By allowing the MOSFET channel to be either at the surface or buried, one can create high-speed digital and / or analog circuits. The planarization before the device epitaxial layers are deposited ensures a flat surface for state-of-the-art lithography.

Owner:TAIWAN SEMICON MFG CO LTD

Relaxed SiGe platform for high speed CMOS electronics and high speed analog circuits

InactiveUS7256142B2Minimal surface roughnessImprove featuresTransistorSemiconductor/solid-state device manufacturingMOSFETCmos electronics

Structures and methods for fabricating high speed digital, analog, and combined digital / analog systems using planarized relaxed SiGe as the materials platform. The relaxed SiGe allows for a plethora of strained Si layers that possess enhanced electronic properties. By allowing the MOSFET channel to be either at the surface or buried, one can create high-speed digital and / or analog circuits. The planarization before the device epitaxial layers are deposited ensures a flat surface for state-of-the-art lithography.

Owner:TAIWAN SEMICON MFG CO LTD

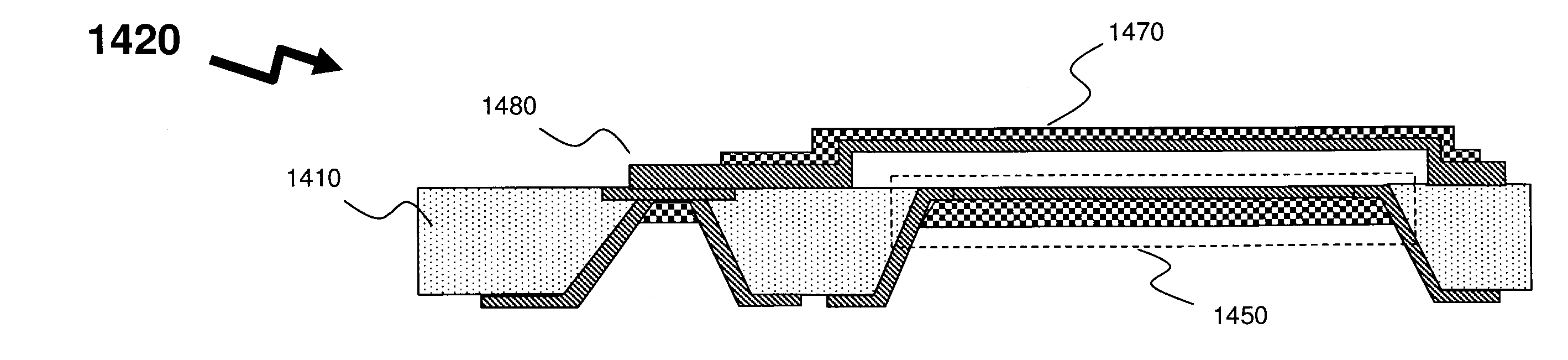

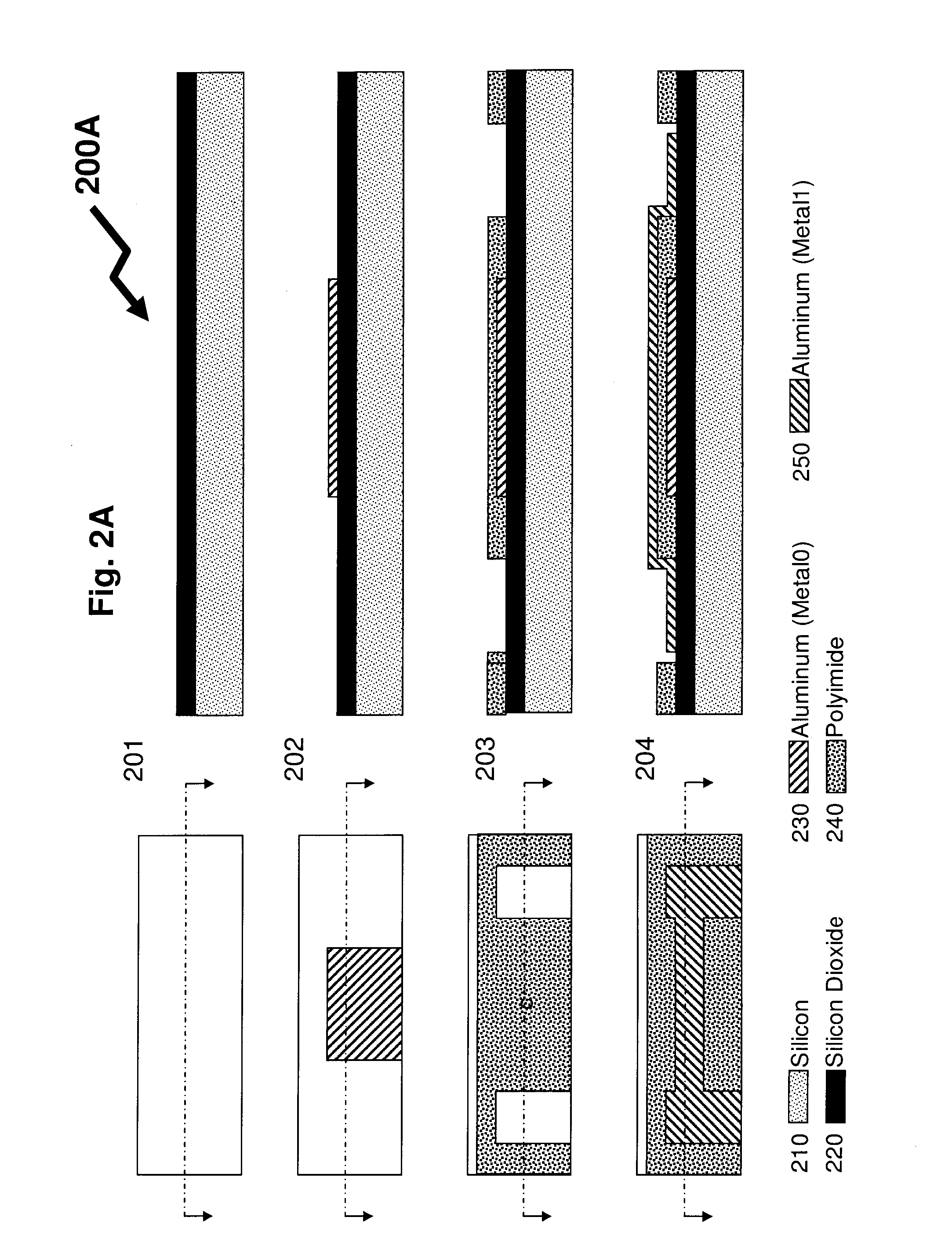

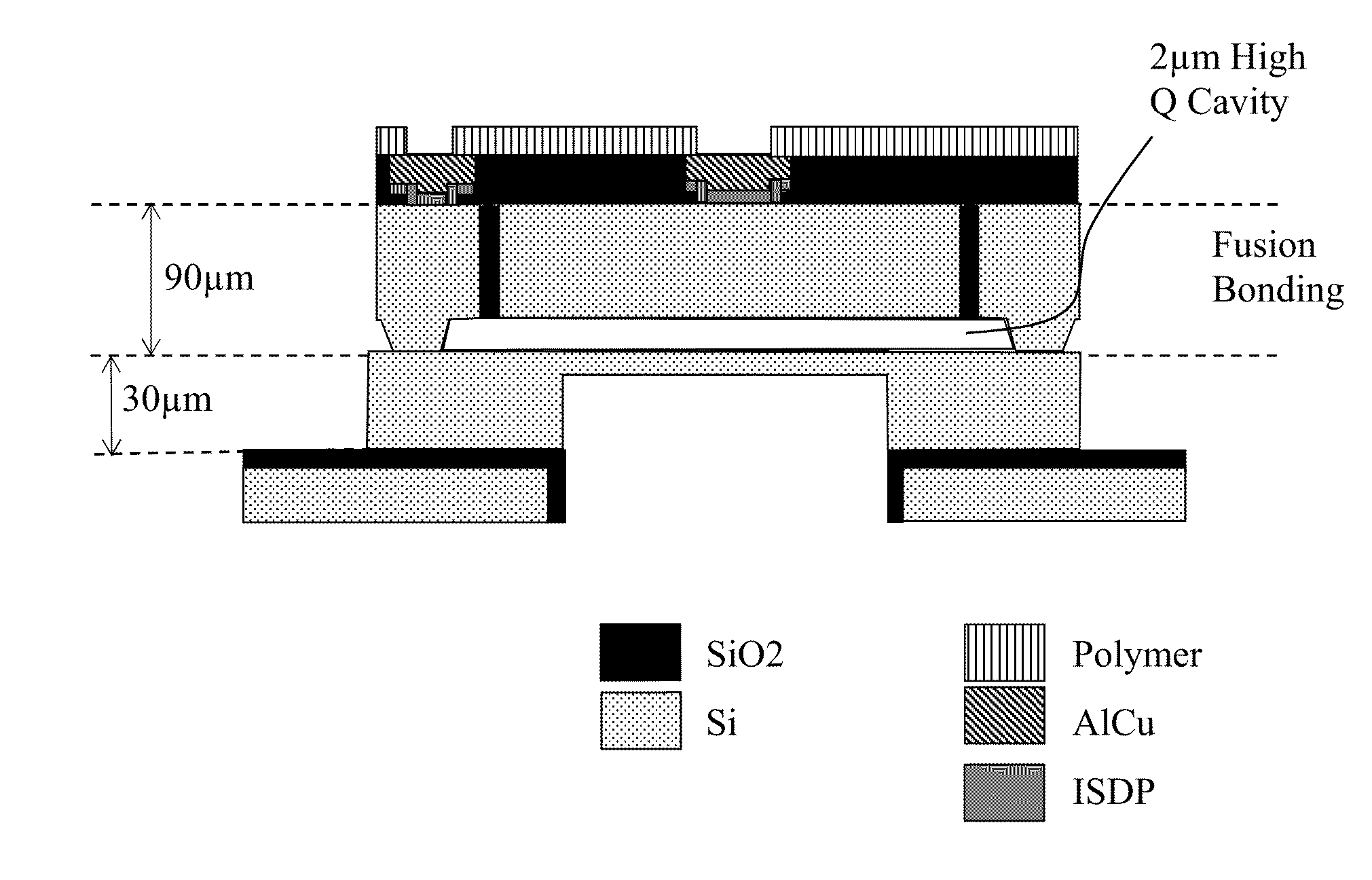

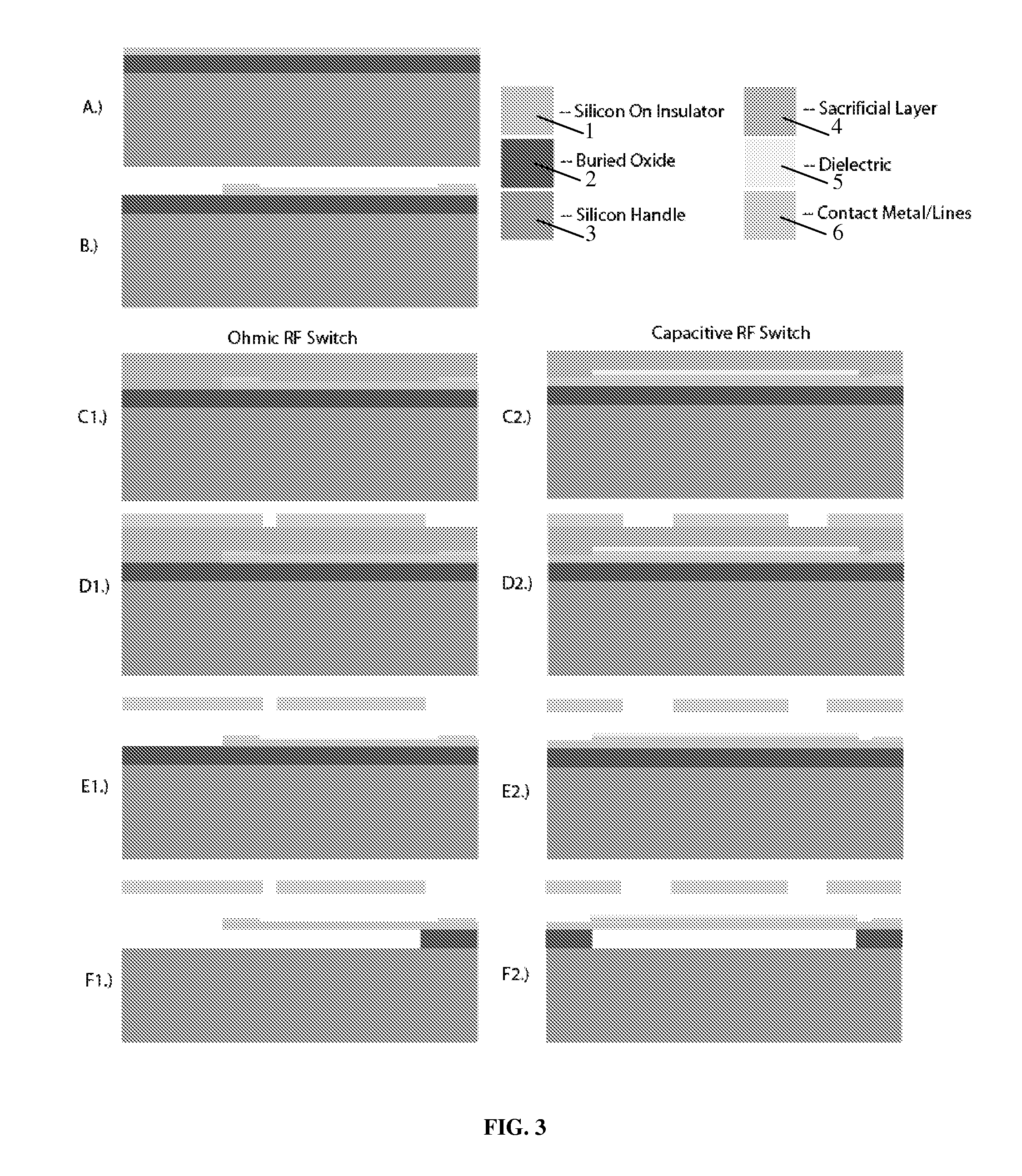

Low Temperature Wafer Level Processing for MEMS Devices

ActiveUS20110027930A1Impedence networksSemiconductor/solid-state device detailsLow temperature depositionEngineering

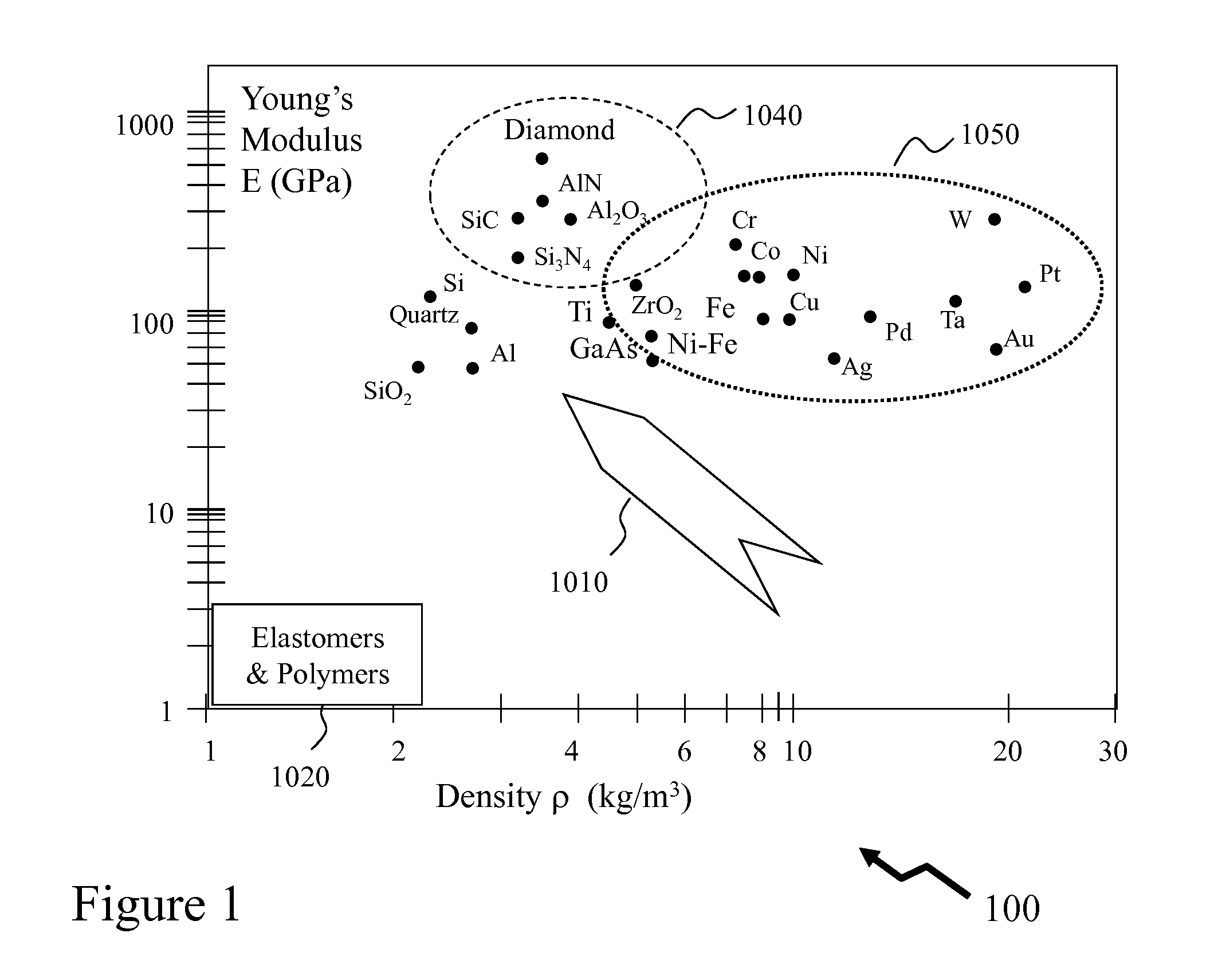

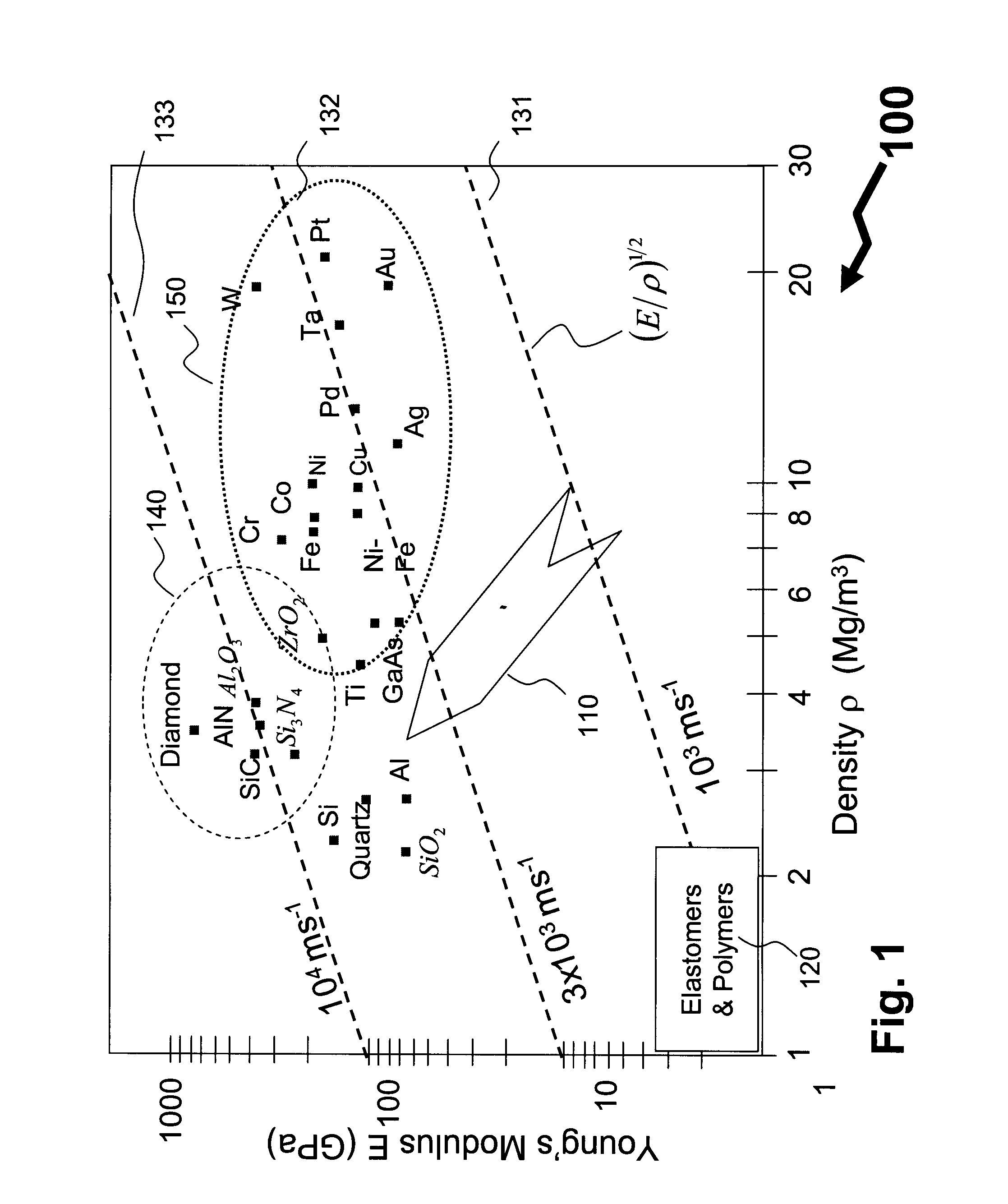

Microelectromechanical systems (MEMS) are small integrated devices or systems that combine electrical and mechanical components. It would be beneficial for such MEMS devices to be integrated with silicon CMOS electronics and packaged in controlled environments and support industry standard mounting interconnections such as solder bump through the provisioning of through-wafer via-based electrical interconnections. However, the fragile nature of the MEMS devices, the requirement for vacuum, hermetic sealing, and stresses placed on metallization membranes are not present in packaging conventional CMOS electronics. Accordingly there is provided a means of reinforcing the through-wafer vias for such integrated MEMS-CMOS circuits by in filling a predetermined portion of the through-wafer electrical vias with low temperature deposited ceramic materials which are deposited at temperatures below 350° C., and potentially to below 250° C., thereby allowing the re-inforcing ceramic to be deposited after fabrication of the CMOS electronics.

Owner:MCGILL UNIV

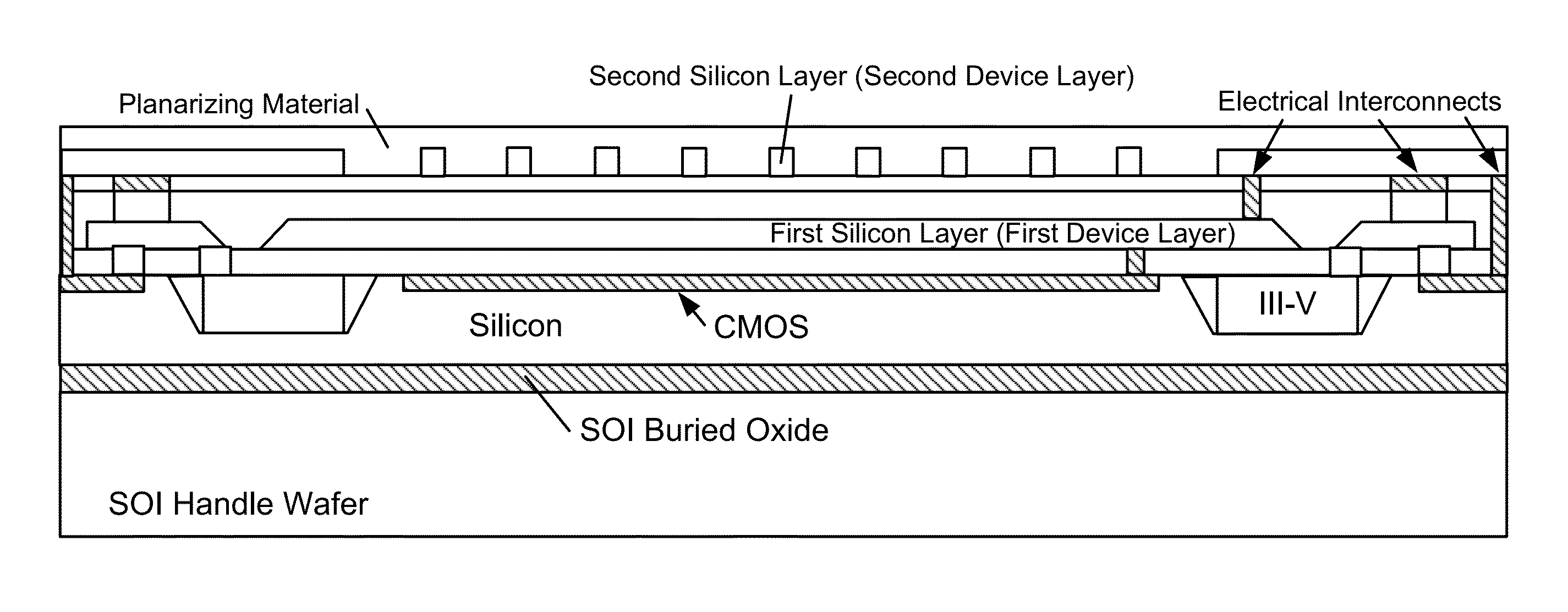

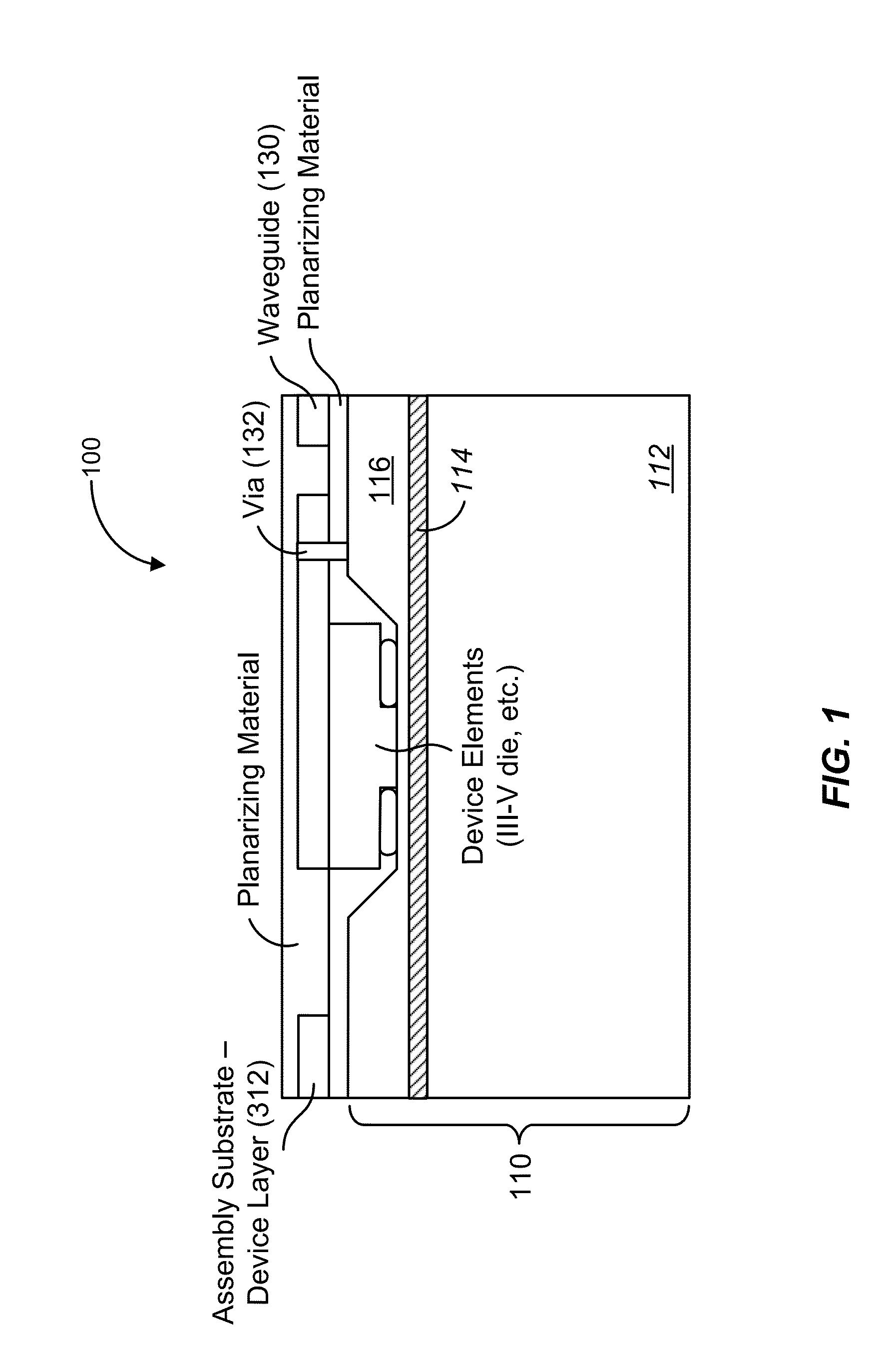

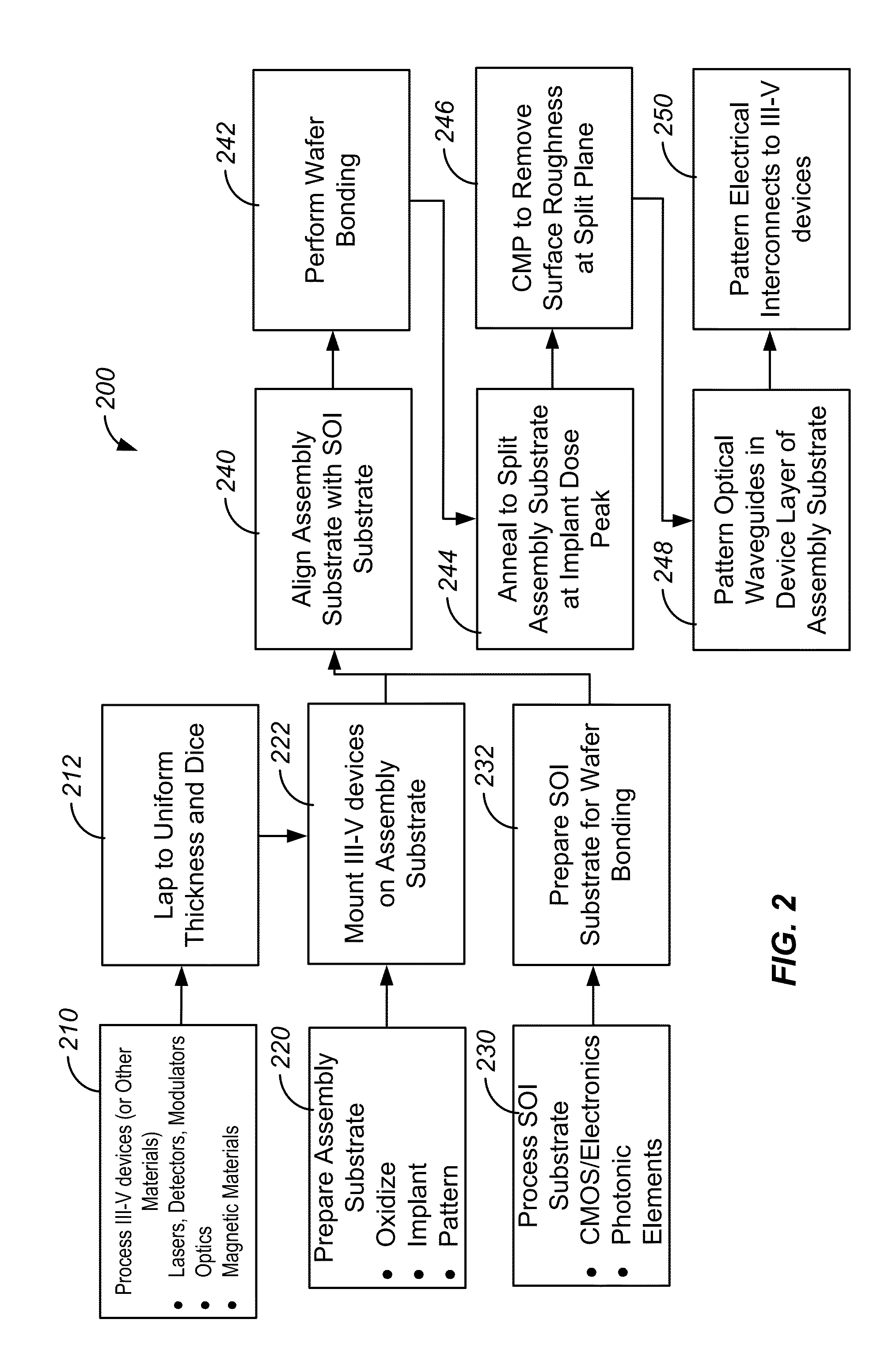

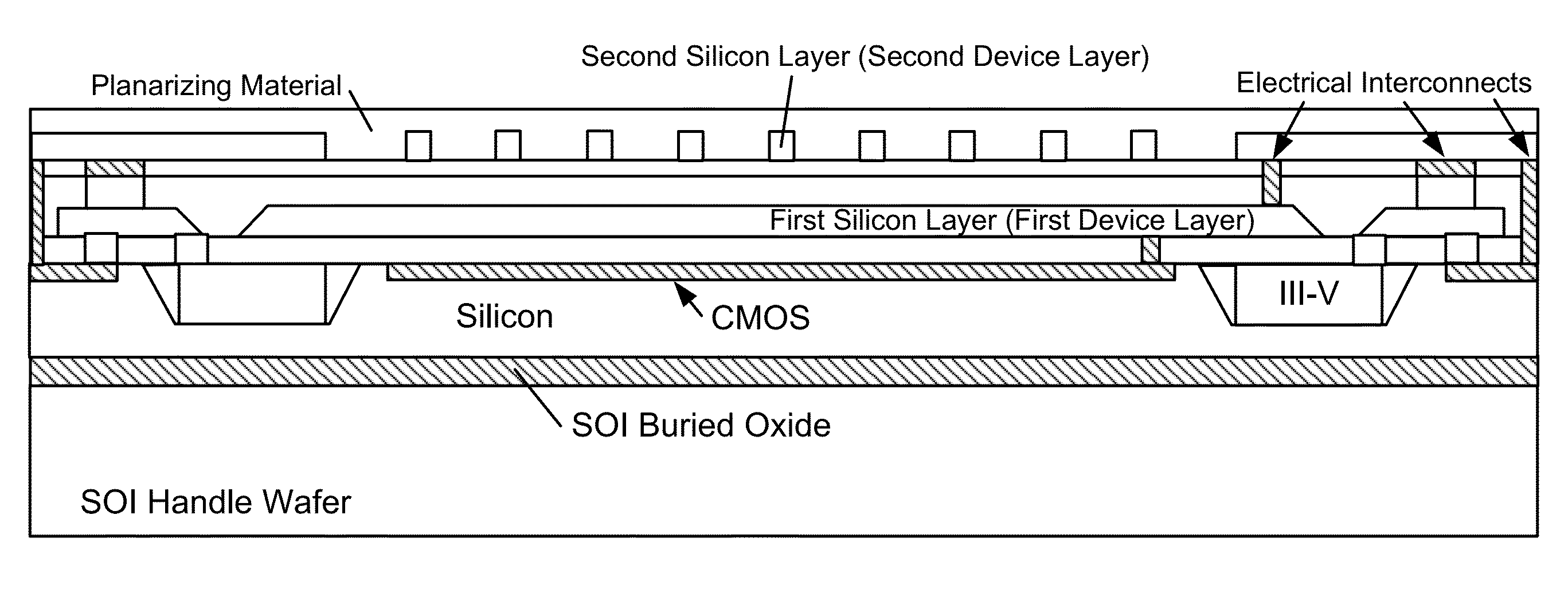

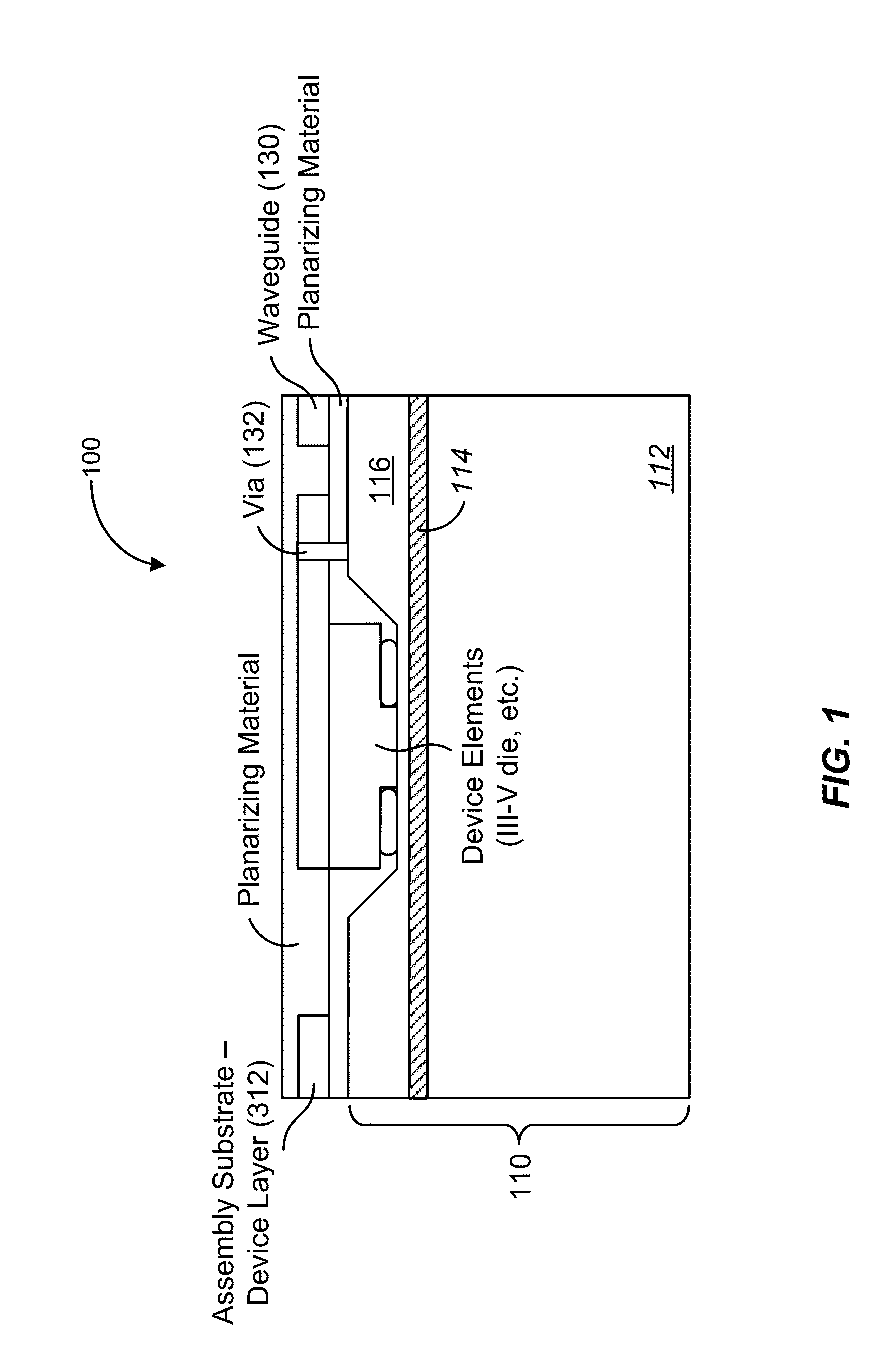

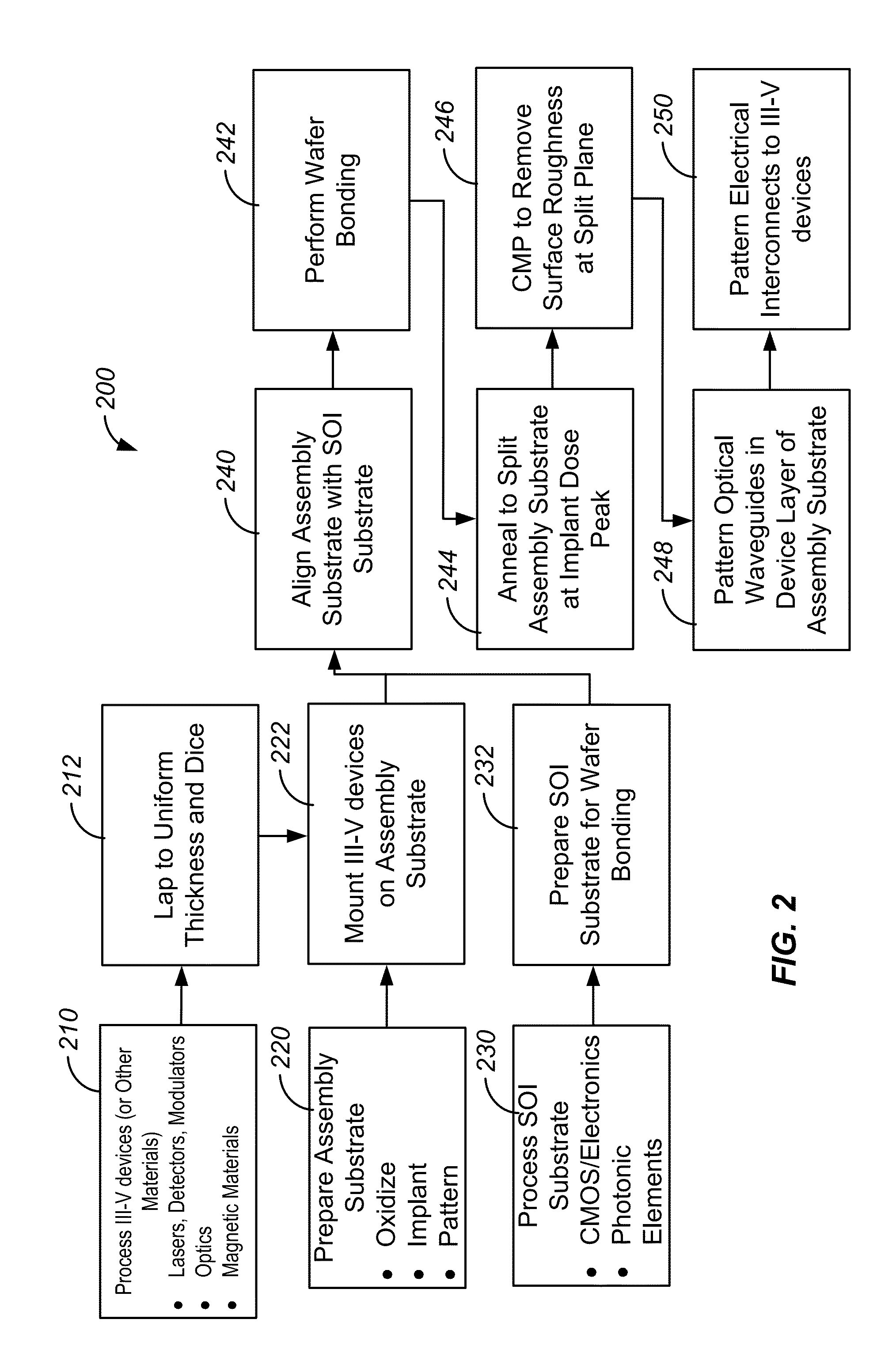

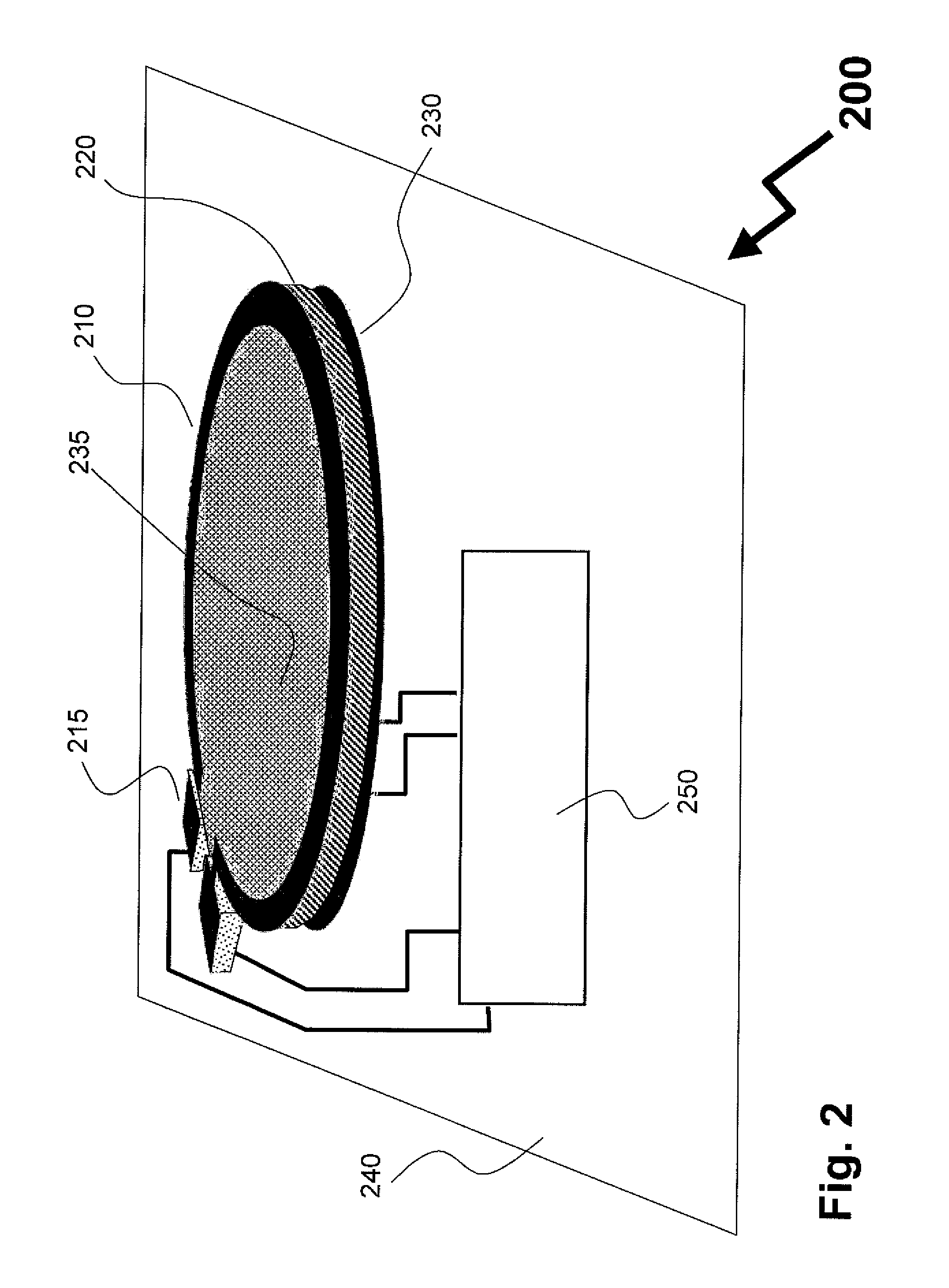

Vertical integration of CMOS electronics with photonic devices

ActiveUS20130210214A1Increase costRelaxing alignment toleranceSolid-state devicesSemiconductor/solid-state device manufacturingSemiconductor structureCmos electronics

A method of fabricating a composite semiconductor structure includes providing an SOI substrate including a plurality of silicon-based devices, providing a compound semiconductor substrate including a plurality of photonic devices, and dicing the compound semiconductor substrate to provide a plurality of photonic dies. Each die includes one or more of the plurality of photonics devices. The method also includes providing an assembly substrate having a base layer and a device layer including a plurality of CMOS devices, mounting the plurality of photonic dies on predetermined portions of the assembly substrate, and aligning the SOI substrate and the assembly substrate. The method further includes joining the SOI substrate and the assembly substrate to form a composite substrate structure and removing at least the base layer of the assembly substrate from the composite substrate structure.

Owner:SKORPIOS TECH

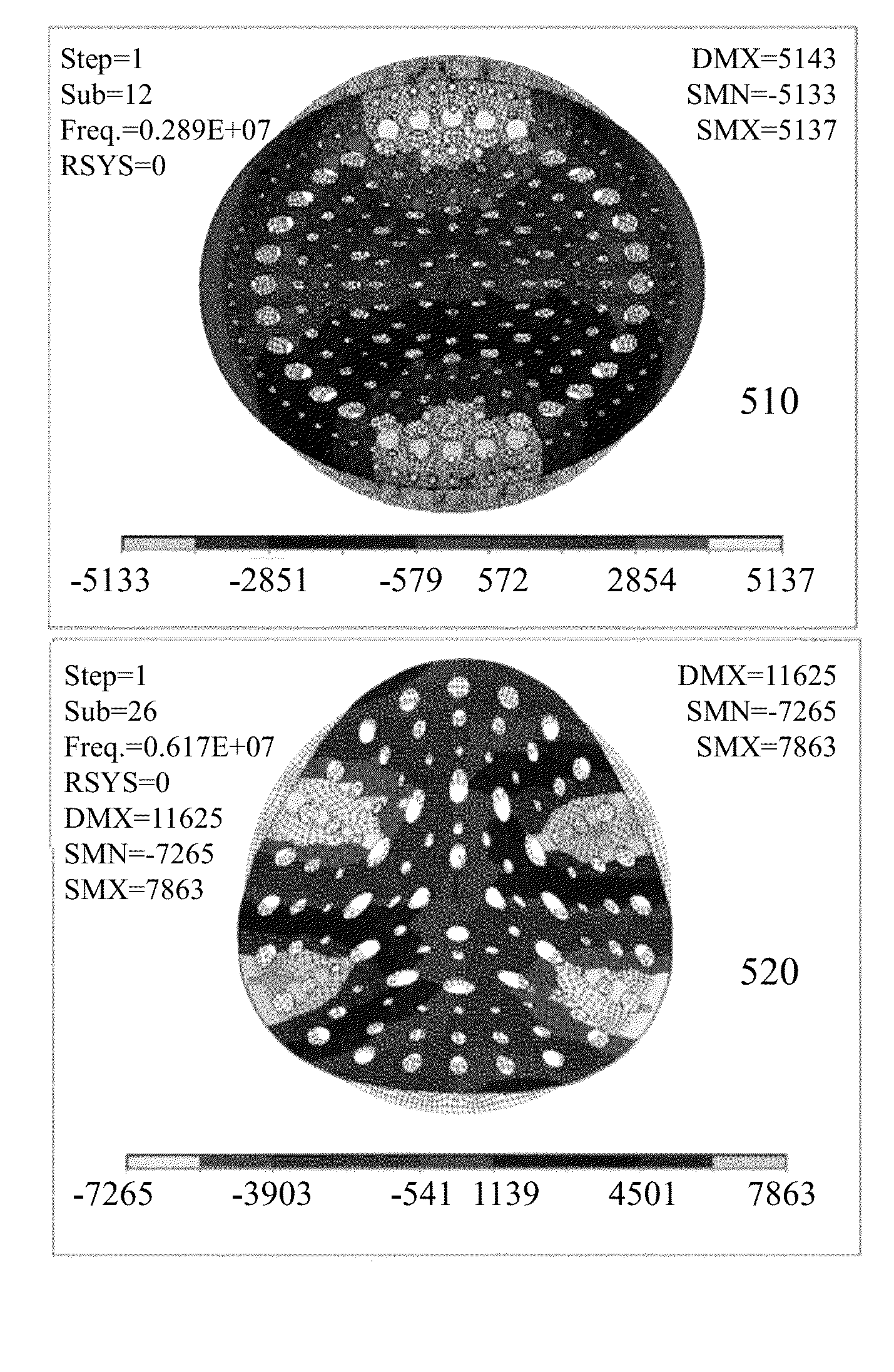

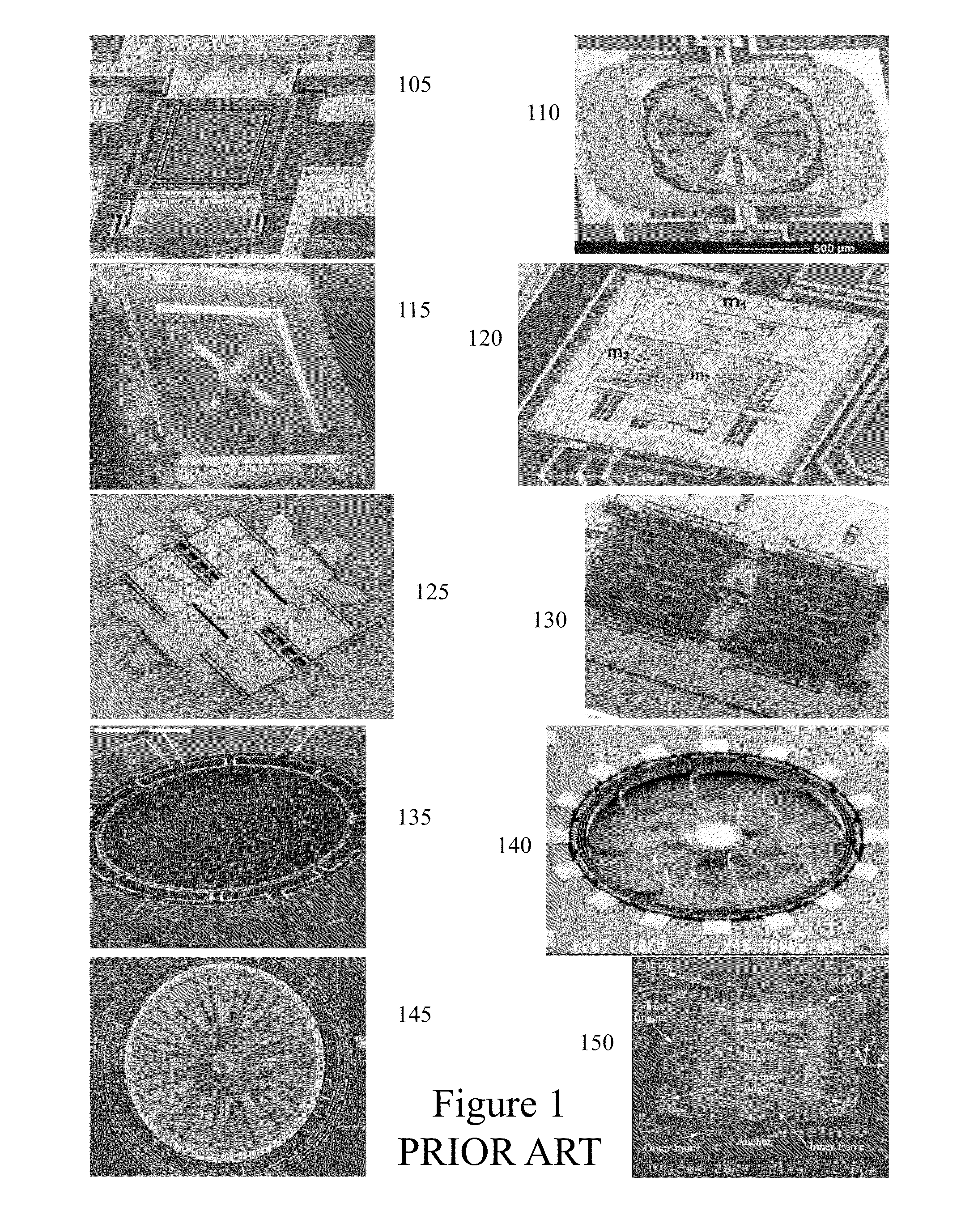

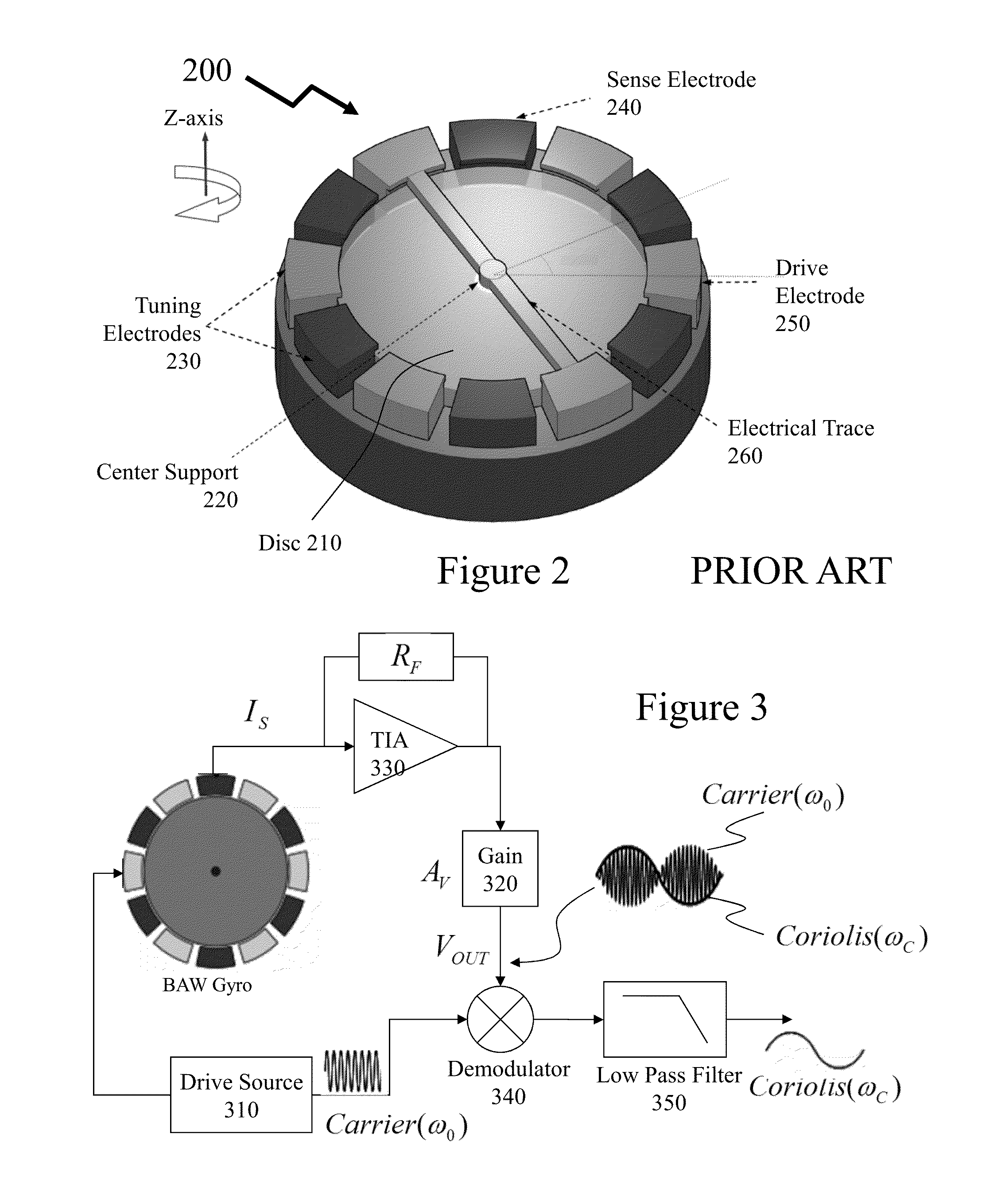

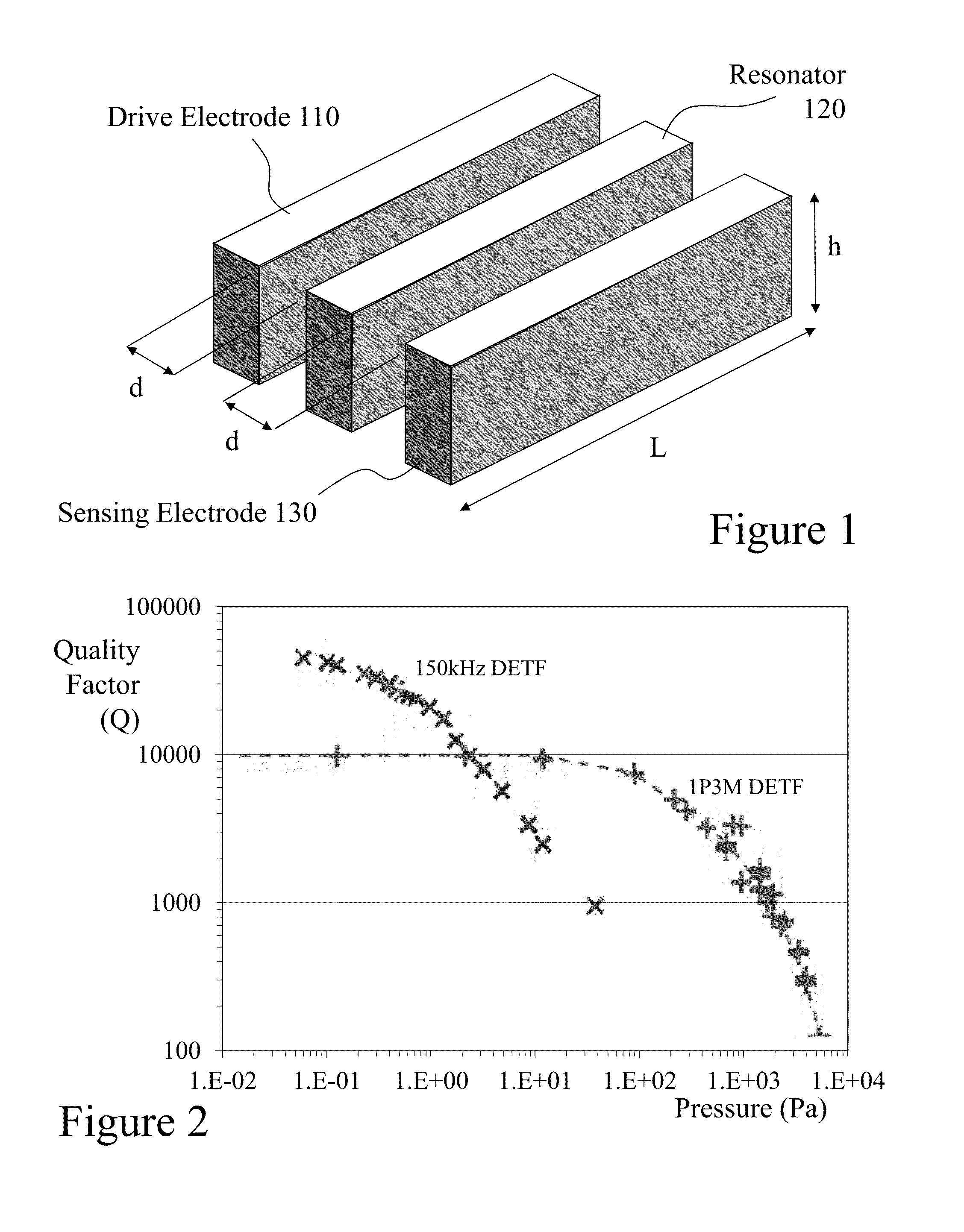

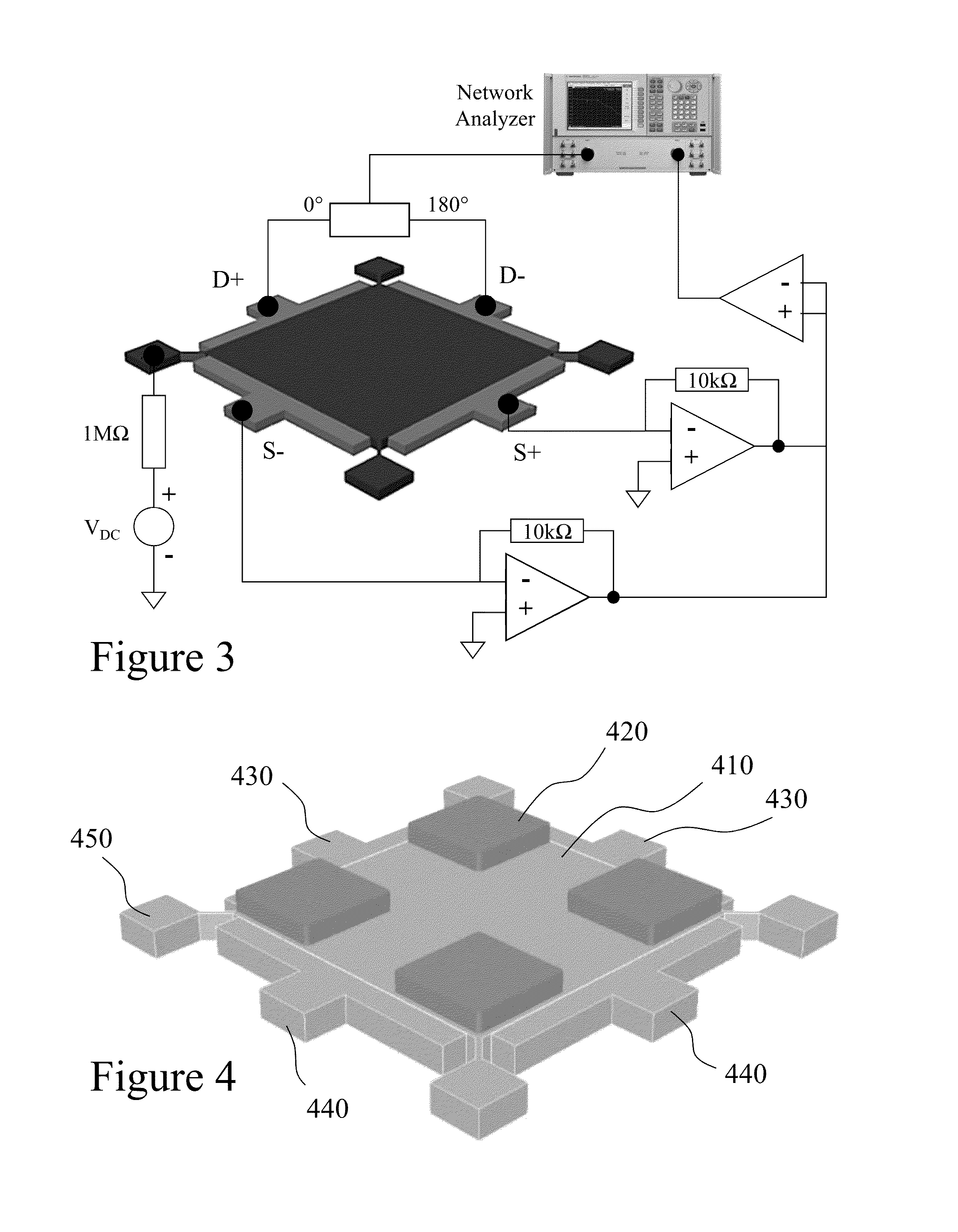

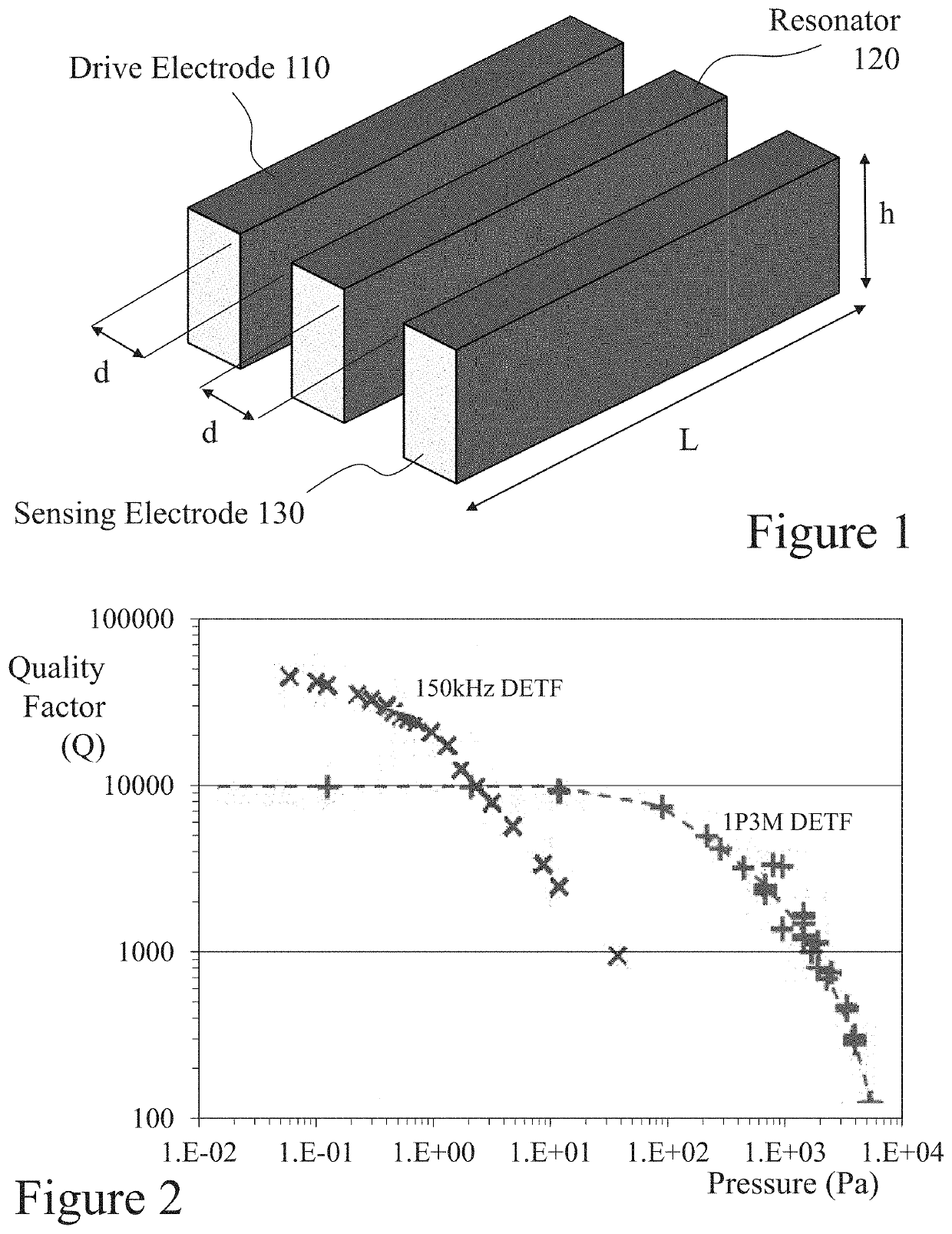

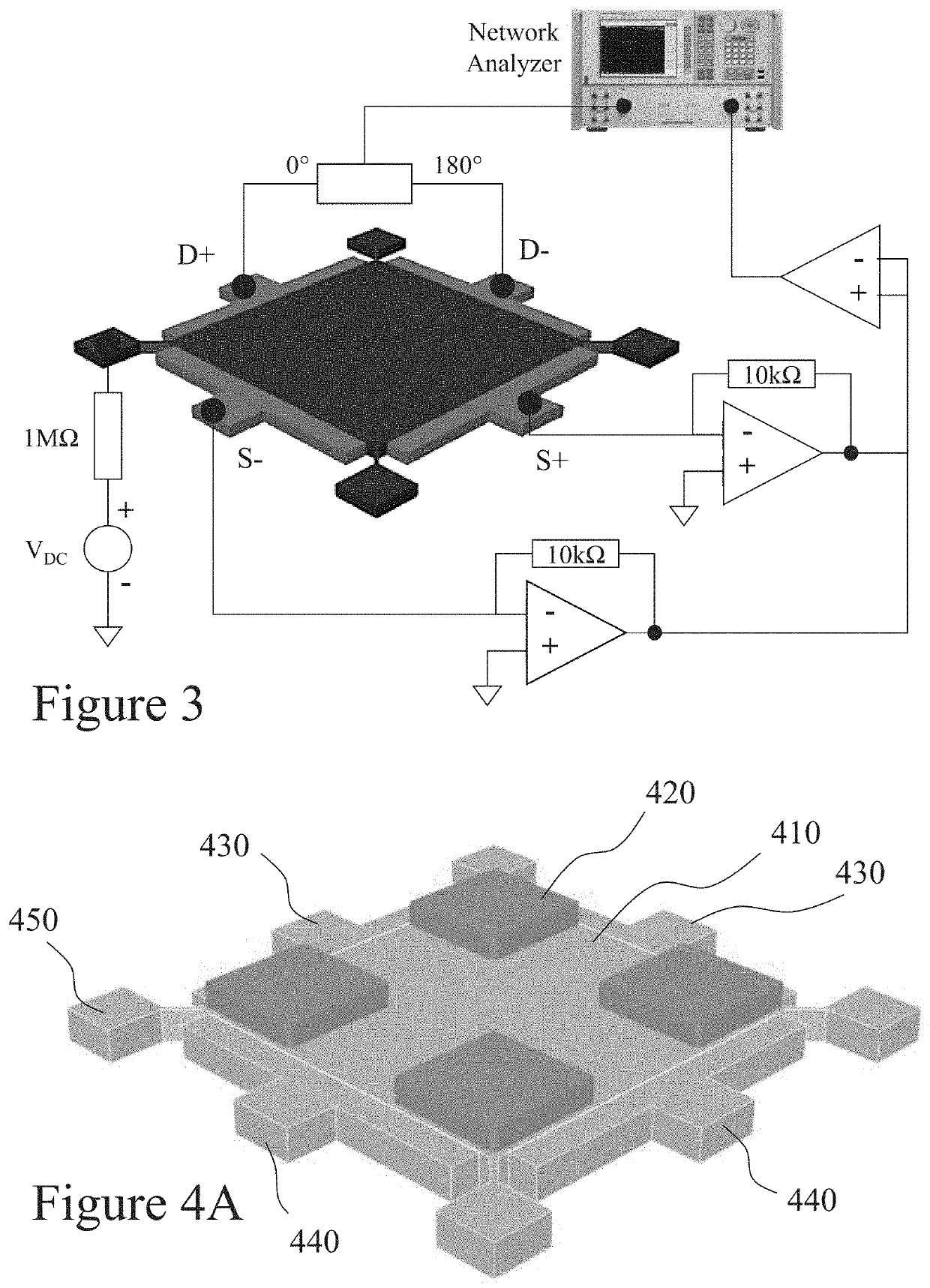

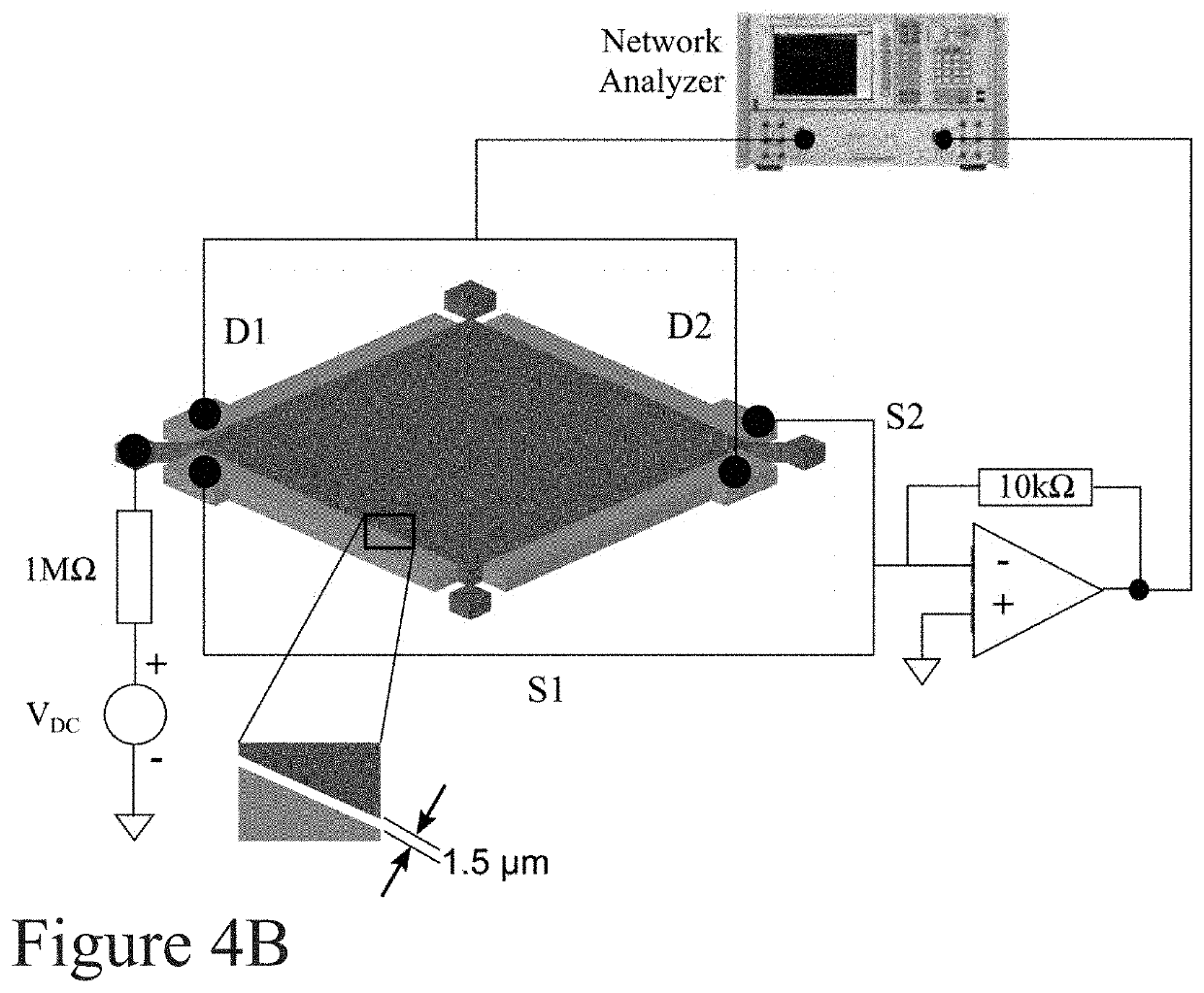

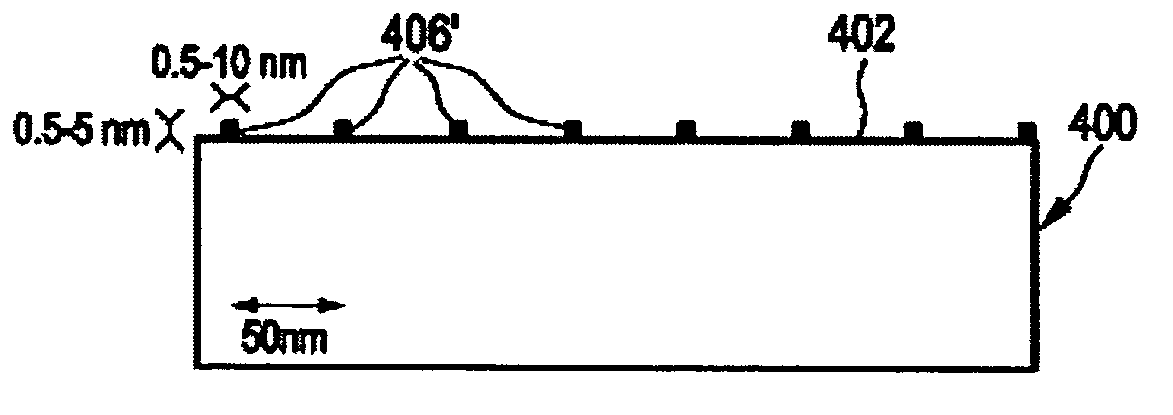

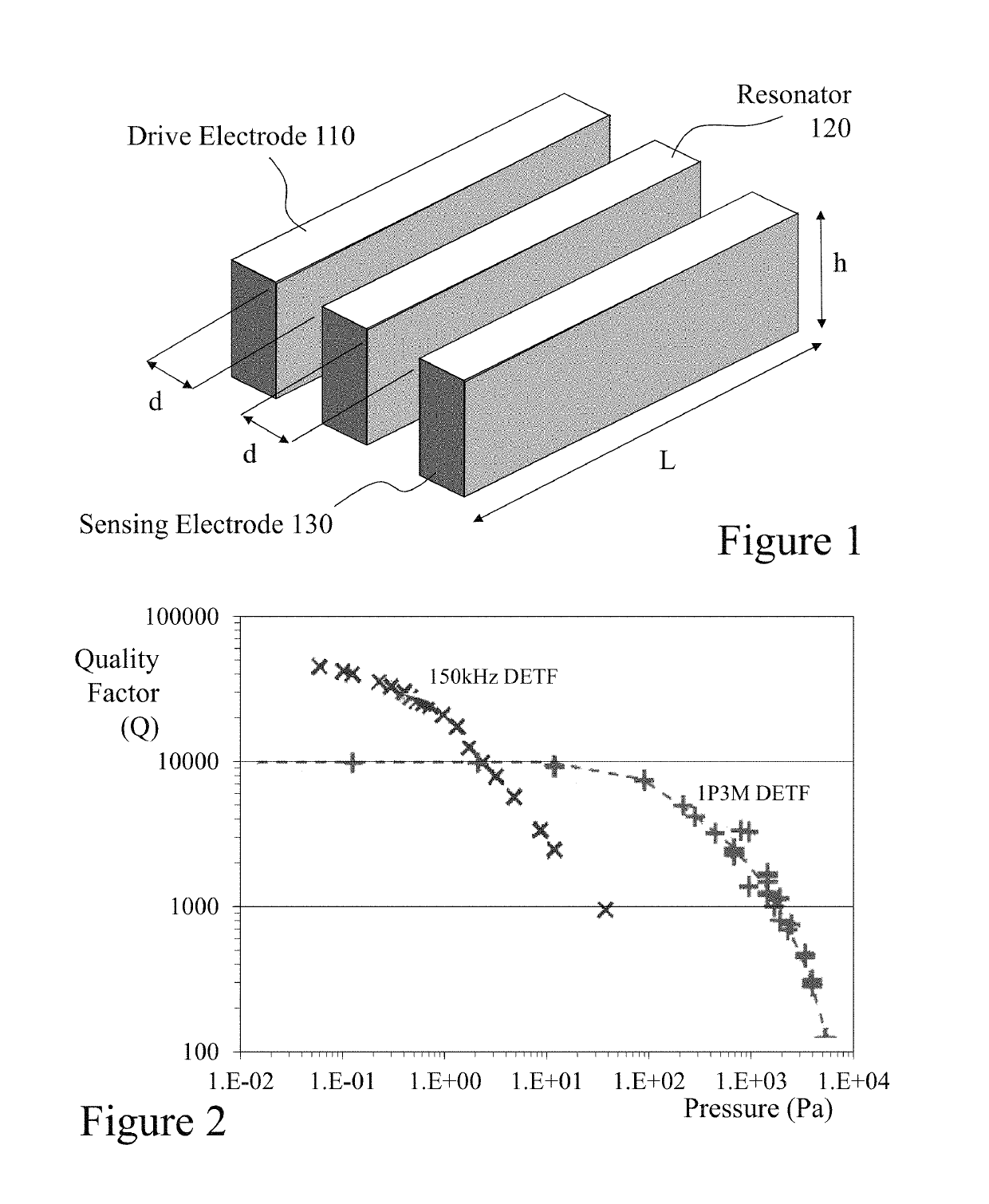

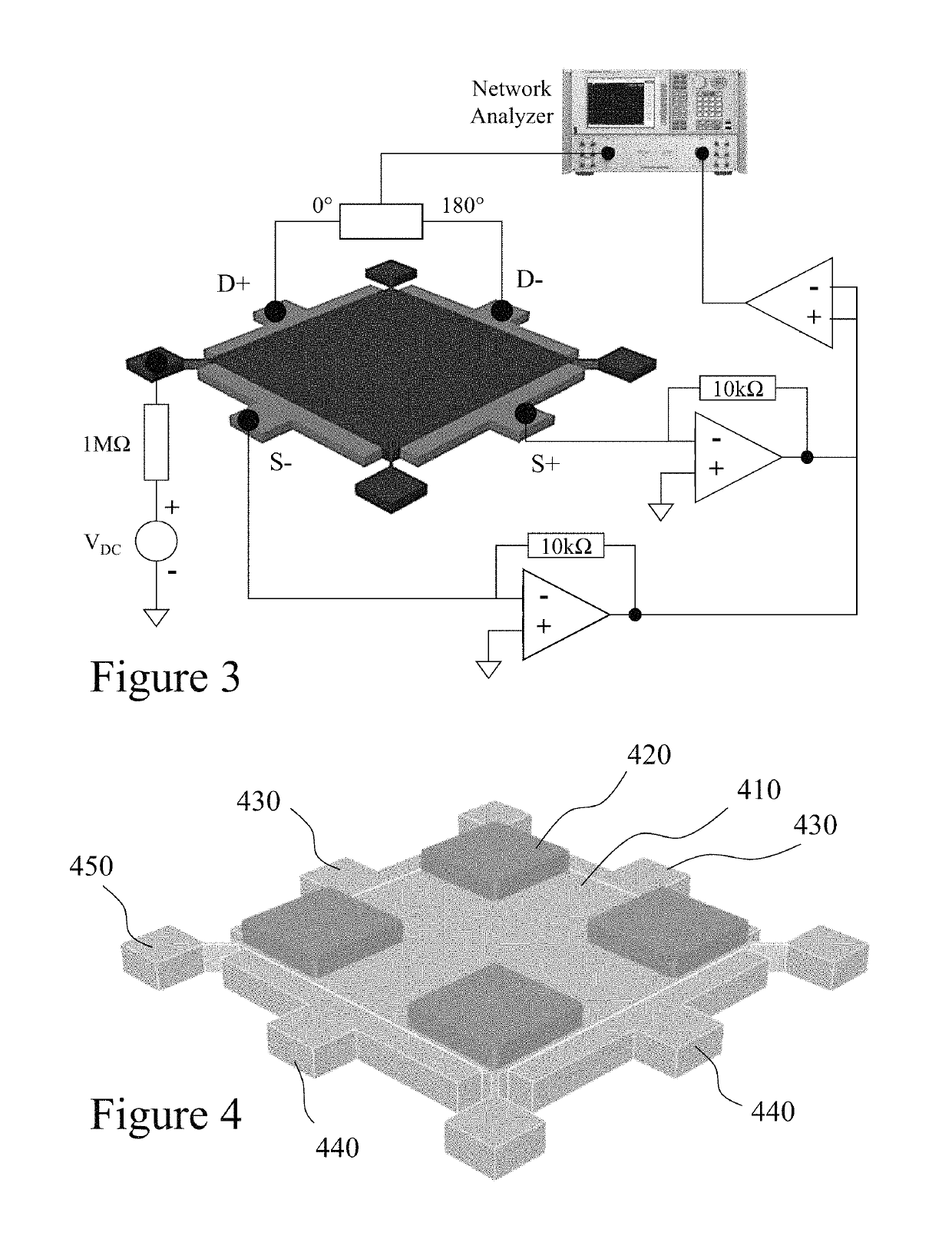

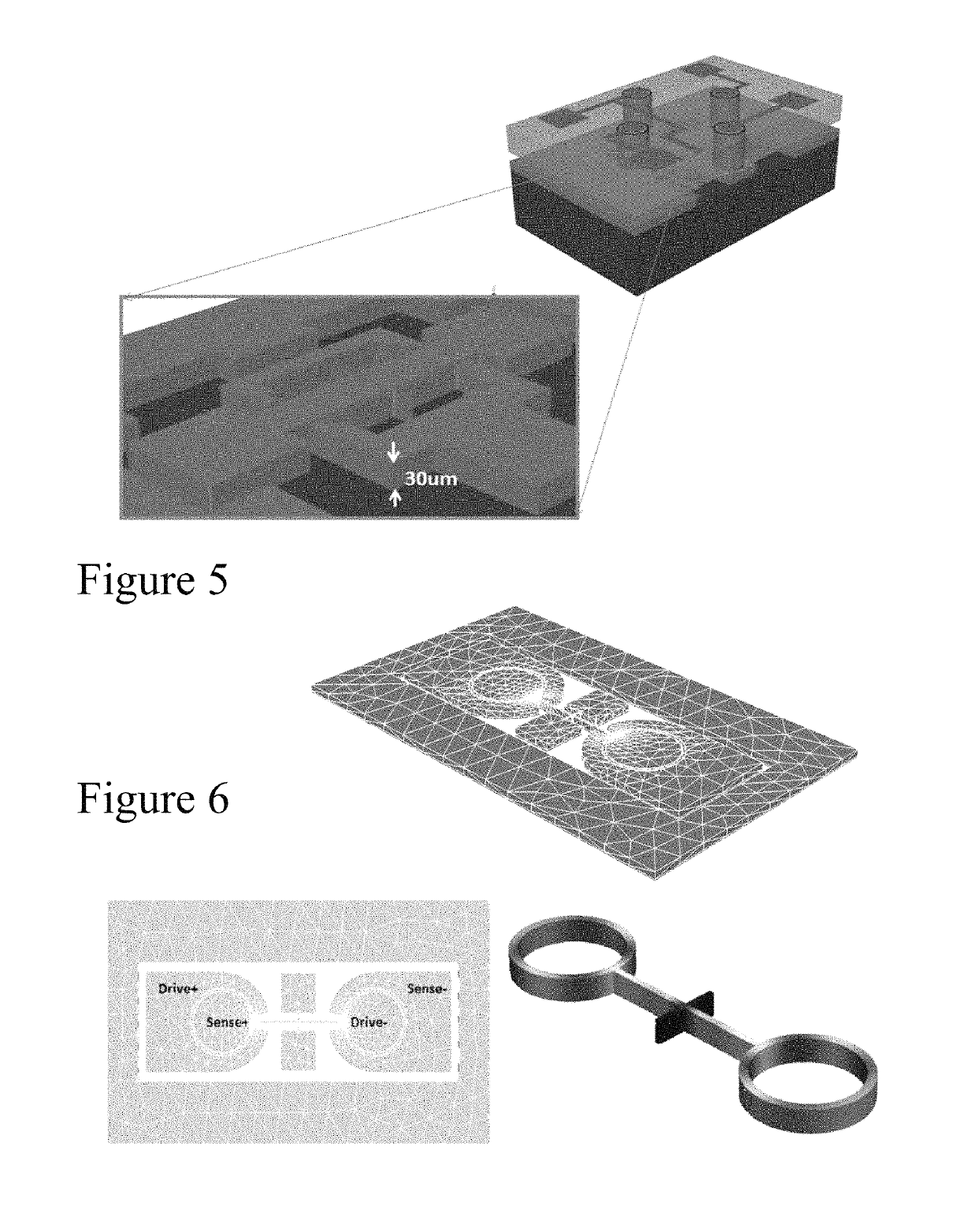

Microelectromechanical Bulk Acoustic Wave Devices and Methods

ActiveUS20140230547A1Acceleration measurement using interia forcesSpeed measurement using gyroscopic effectsGyroscopeEngineering

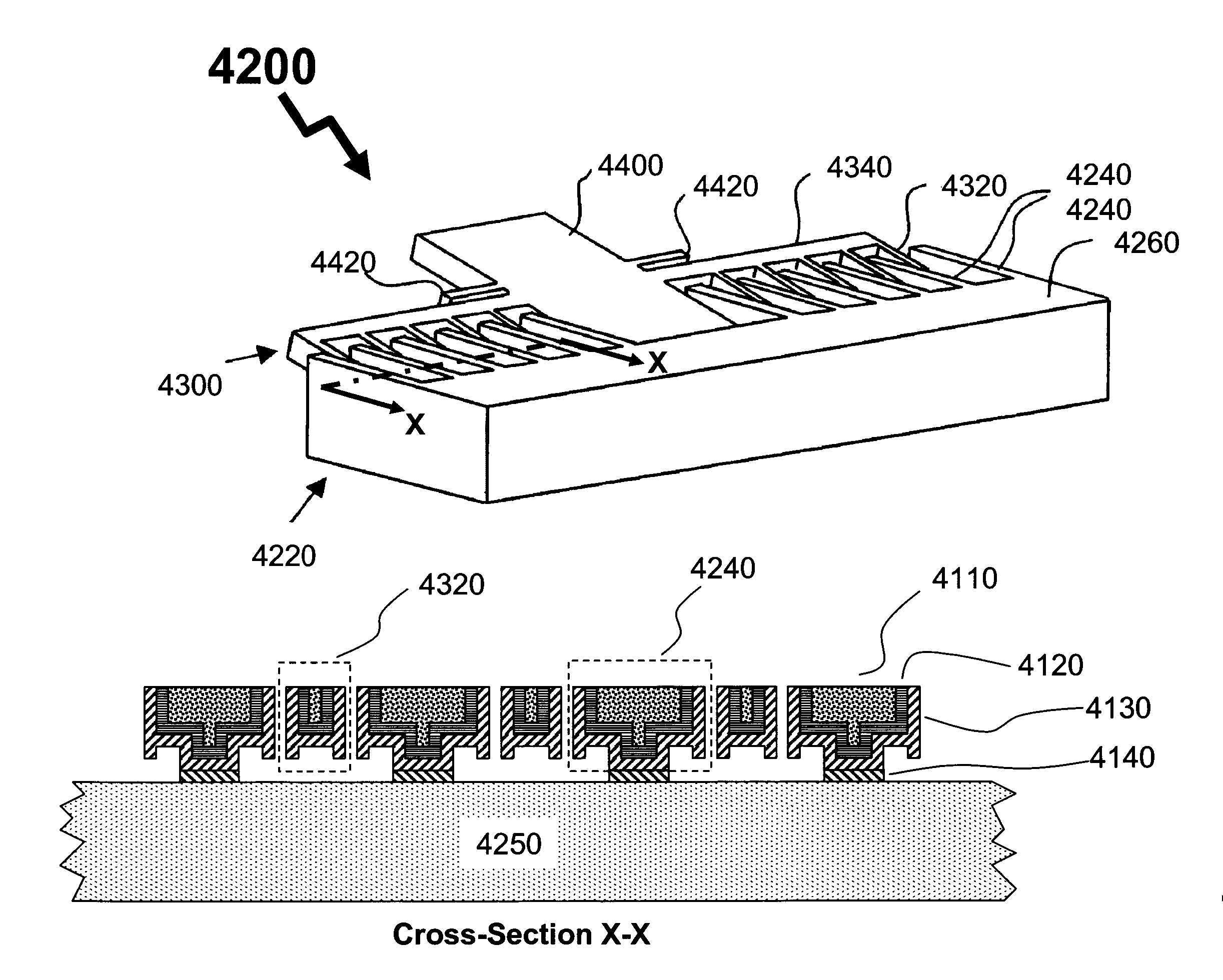

Micromachined gyroscopes, such as those based upon microelectromechanical systems (MEMS) have the potential to dominate the rate-sensor market mainly due to their small size, low power and low cost. As MEMS gyroscopes are resonant devices requiring active excitation it would be beneficial to improve the resonator Q-factor reducing the electrical drive power requirements for the excitation circuitry. Further, many prior art MEMS gyroscope designs have multiple resonances arising from design and manufacturing considerations which require additional frequency tuning and control circuitry together with the excitation / sense circuitry. It would therefore be beneficial to enhance the bandwidth of the resonators to remove the requirement for such circuitry. Further, to address the relatively large dimensions of MEMS gyroscopes it would be beneficial for the MEMS gyroscopes to be fabricated directly above the CMOS electronics thereby reducing the die dimensions and lowering per die cost.

Owner:MCGILL UNIV

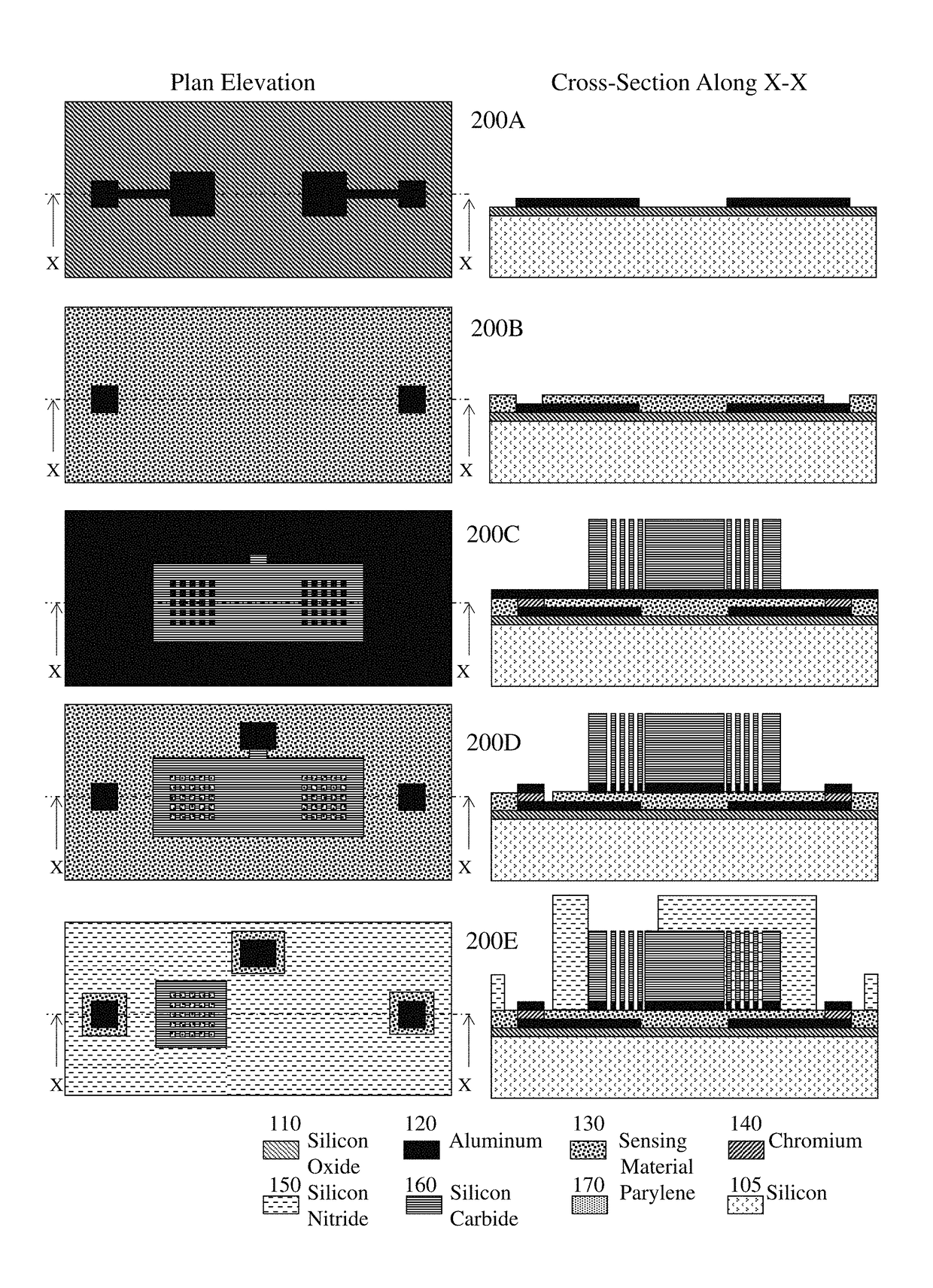

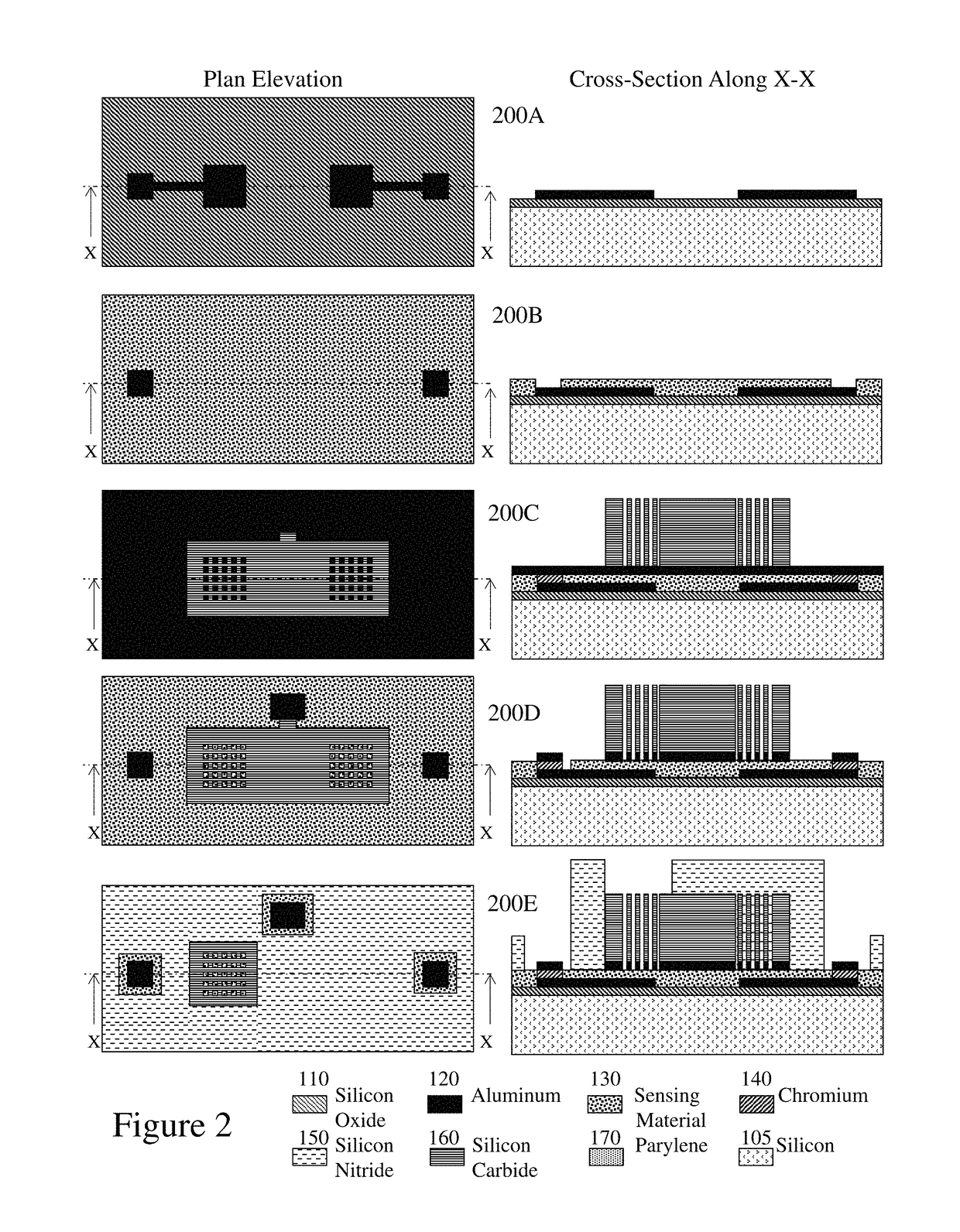

Methods and systems for humidity and pressure sensor overlay integration with electronics

ActiveUS20140125359A1Resistance/reactance/impedenceSemiconductor/solid-state device manufacturingCmos electronicsEngineering

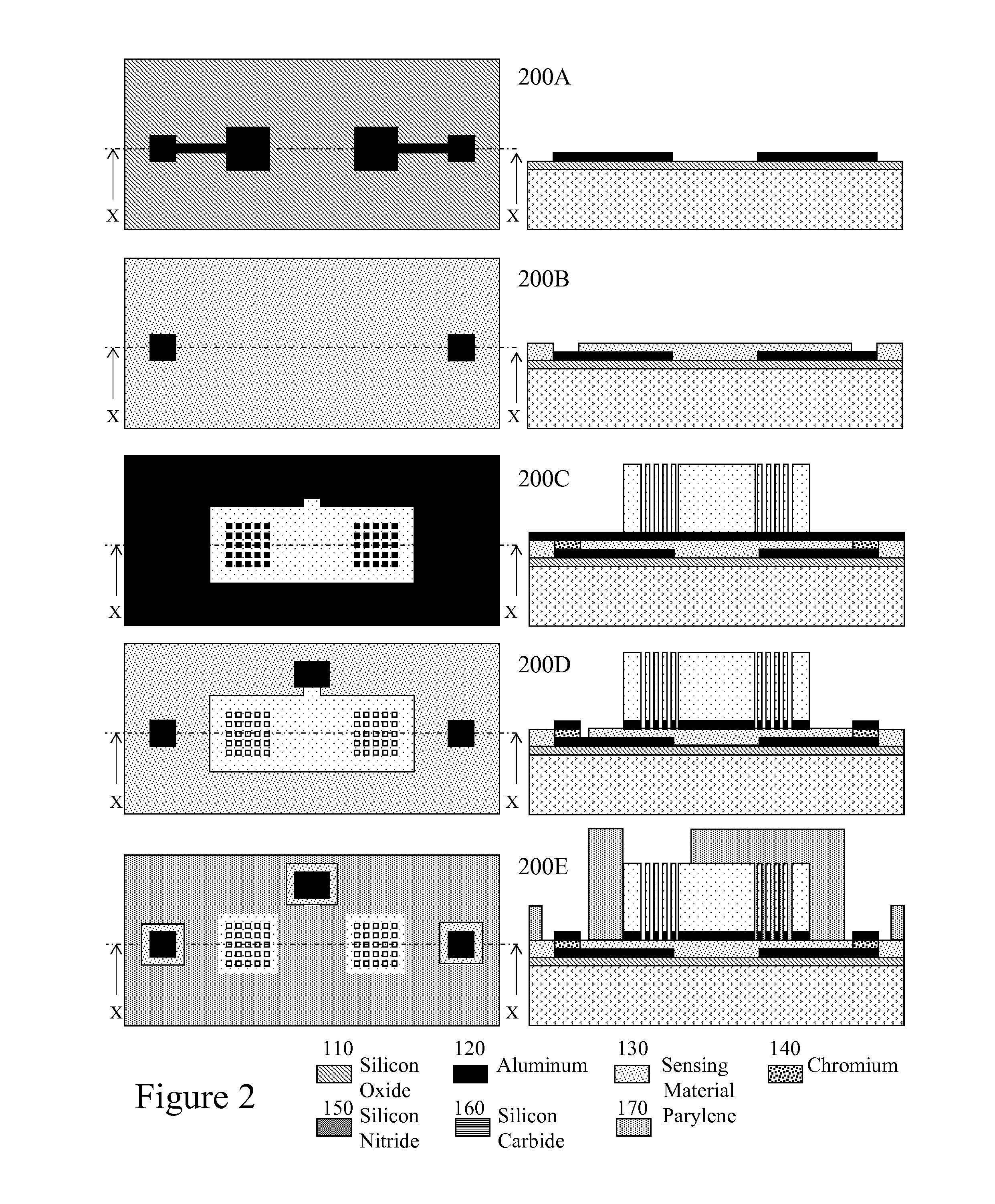

Capacitive sensors and MEMS elements that can be implemented directly above silicon CMOS electronics are disclosed. A capacitive based sensor is disposed over a first predetermined portion of a wafer that includes at least a first ceramic element providing protection for the final capacitive based sensor and self-aligned processing during its manufacturing.

Owner:MEMS VISION INT

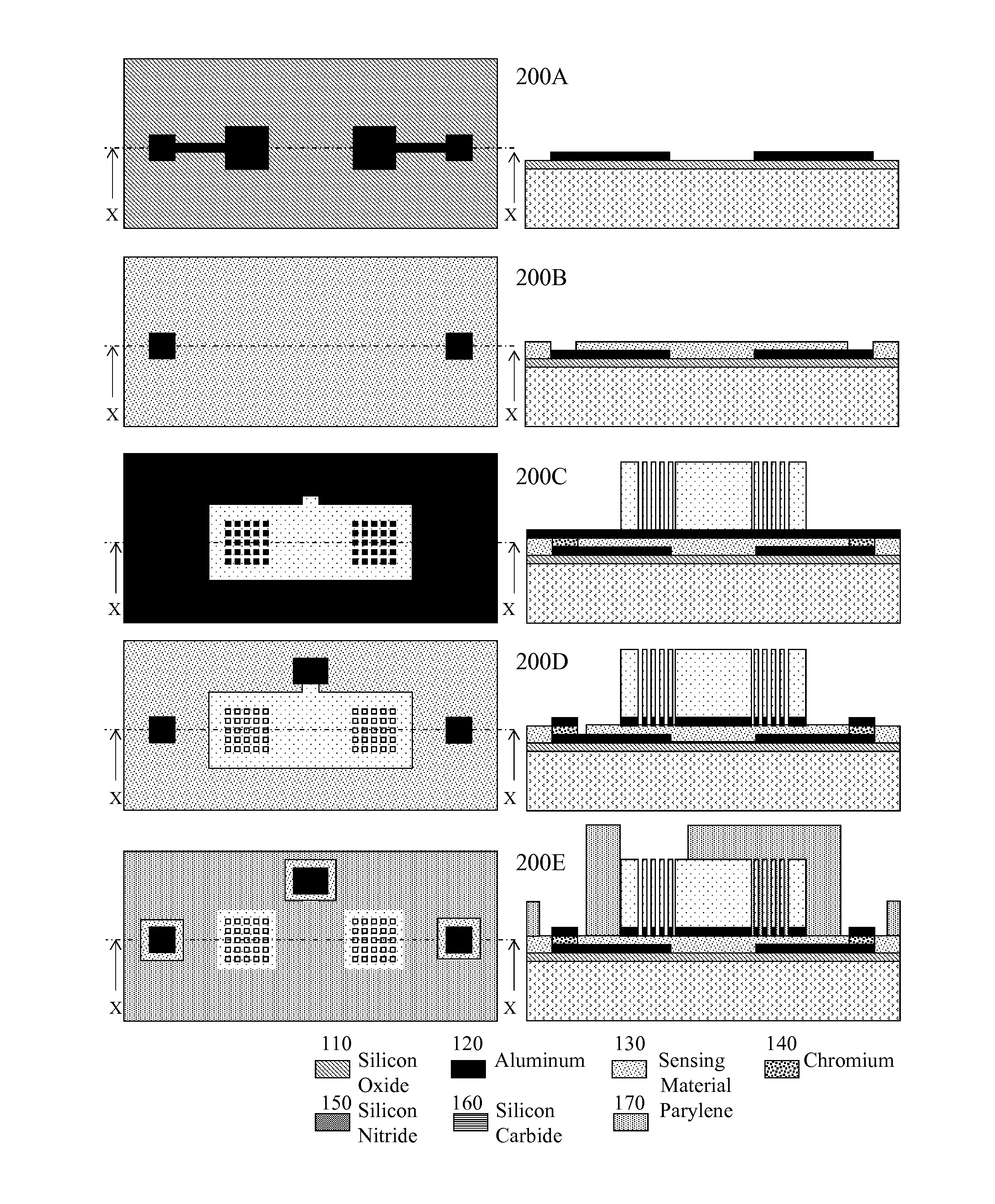

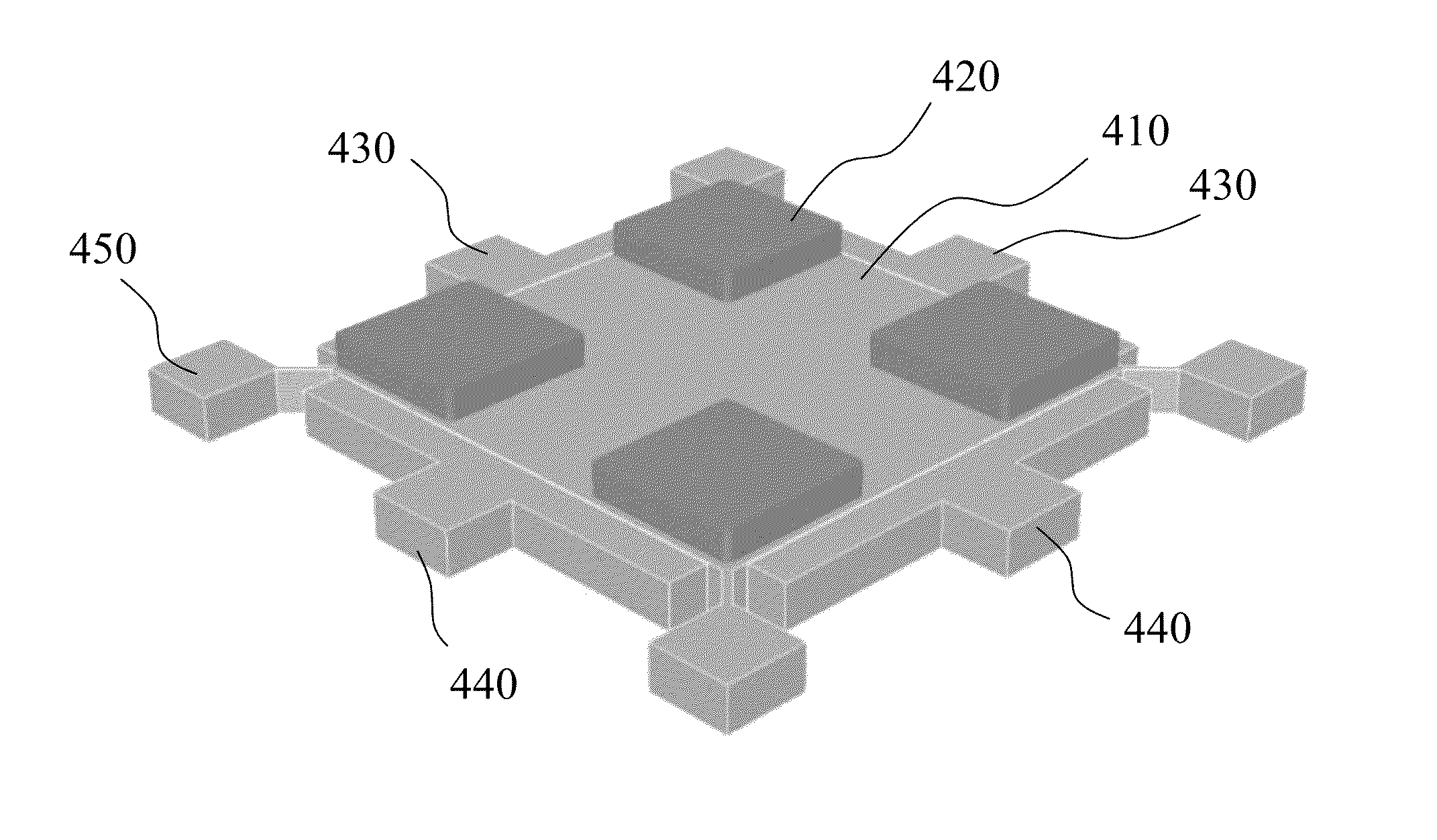

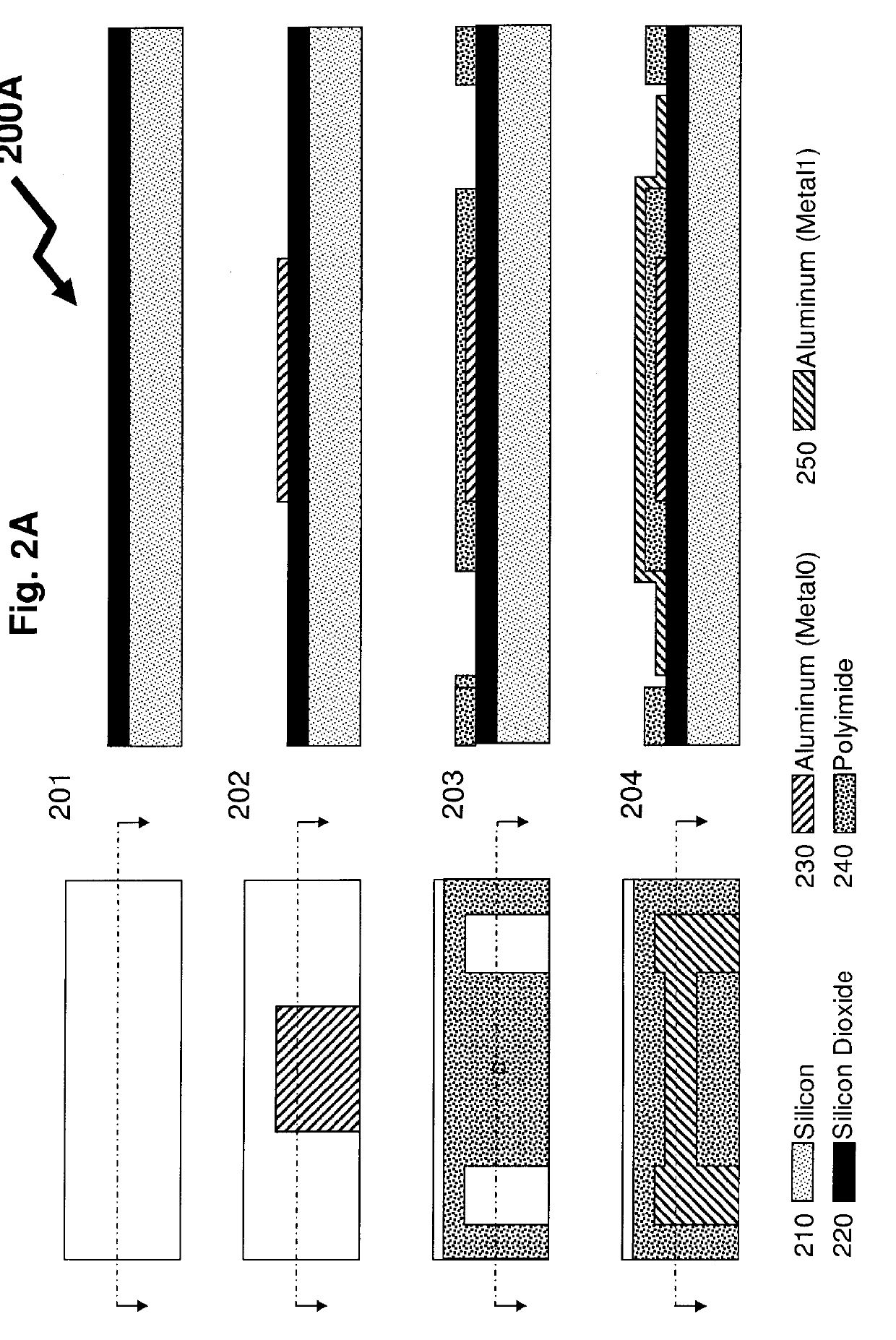

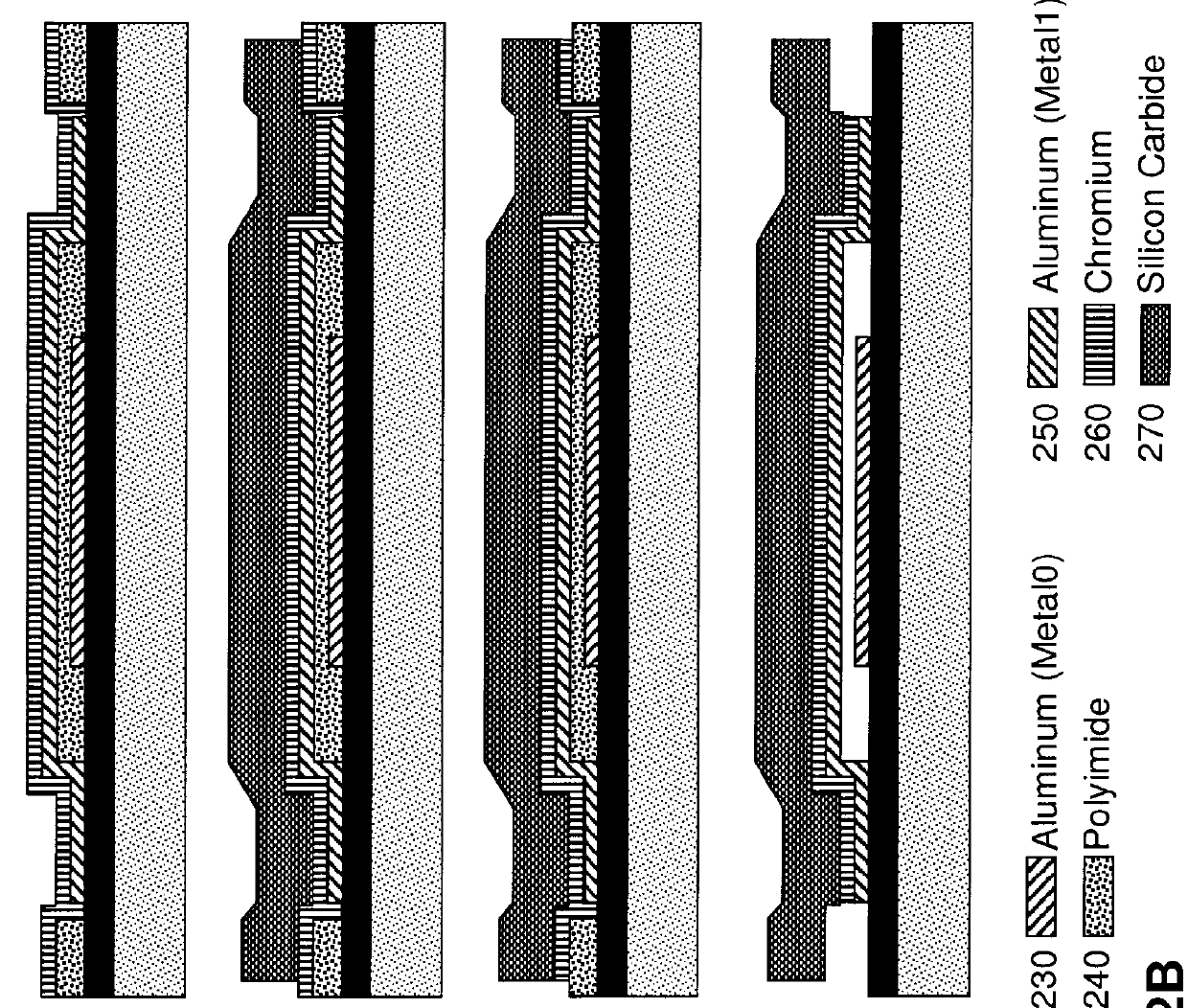

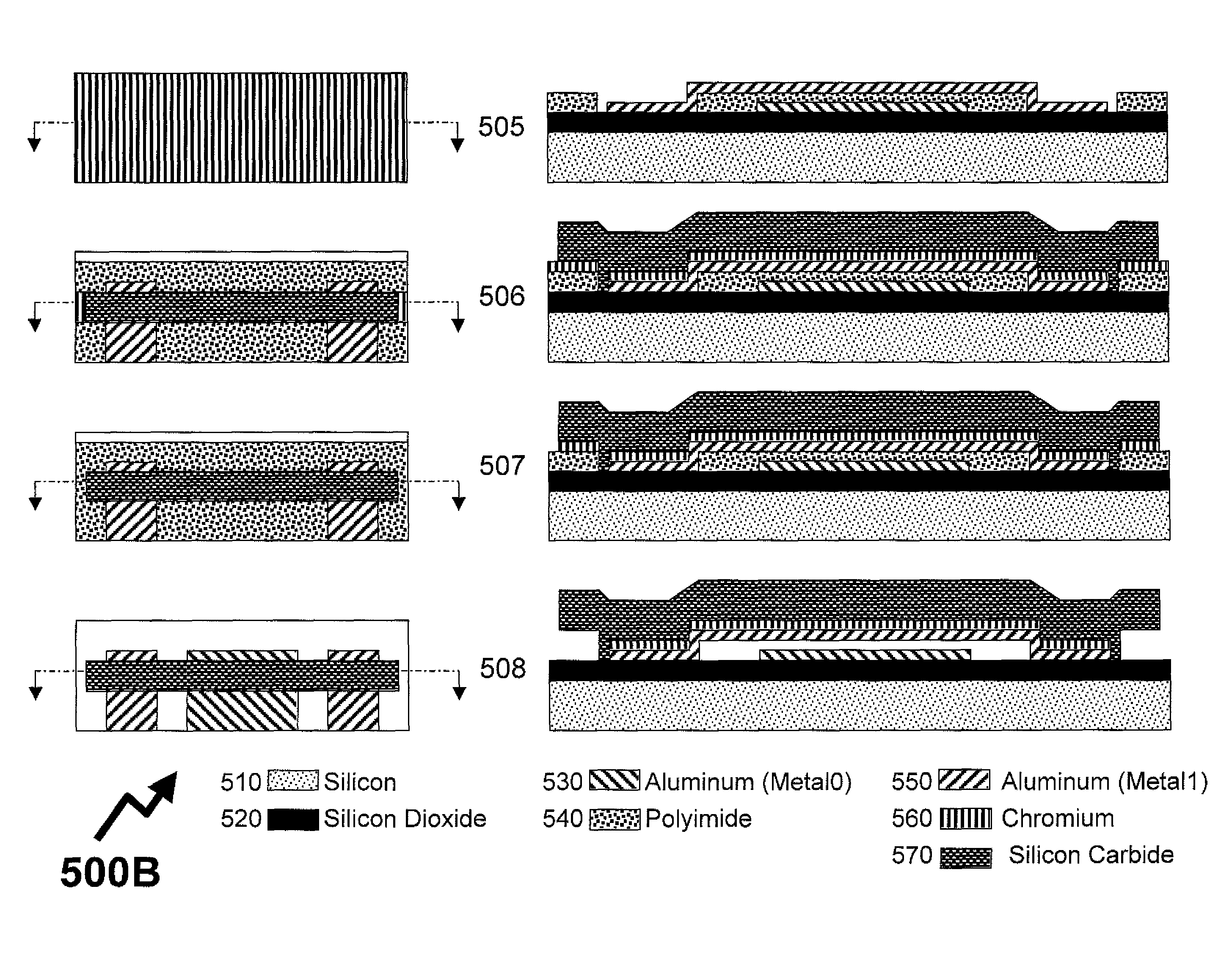

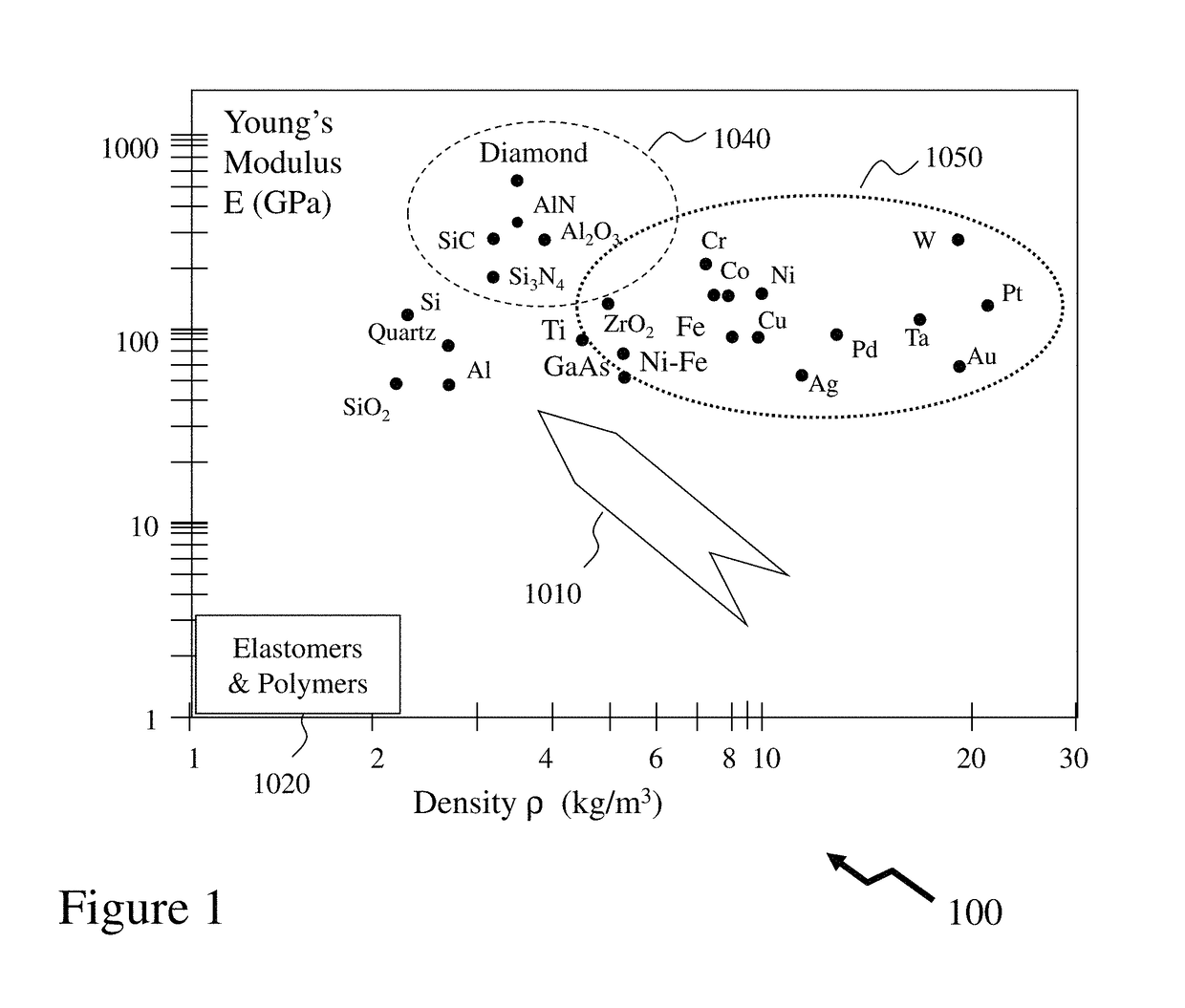

Low temperature ceramic microelectromechanical structures

ActiveUS20110111545A1Semiconductor/solid-state device manufacturingForming microstructural systemsCmos electronicsConductive materials

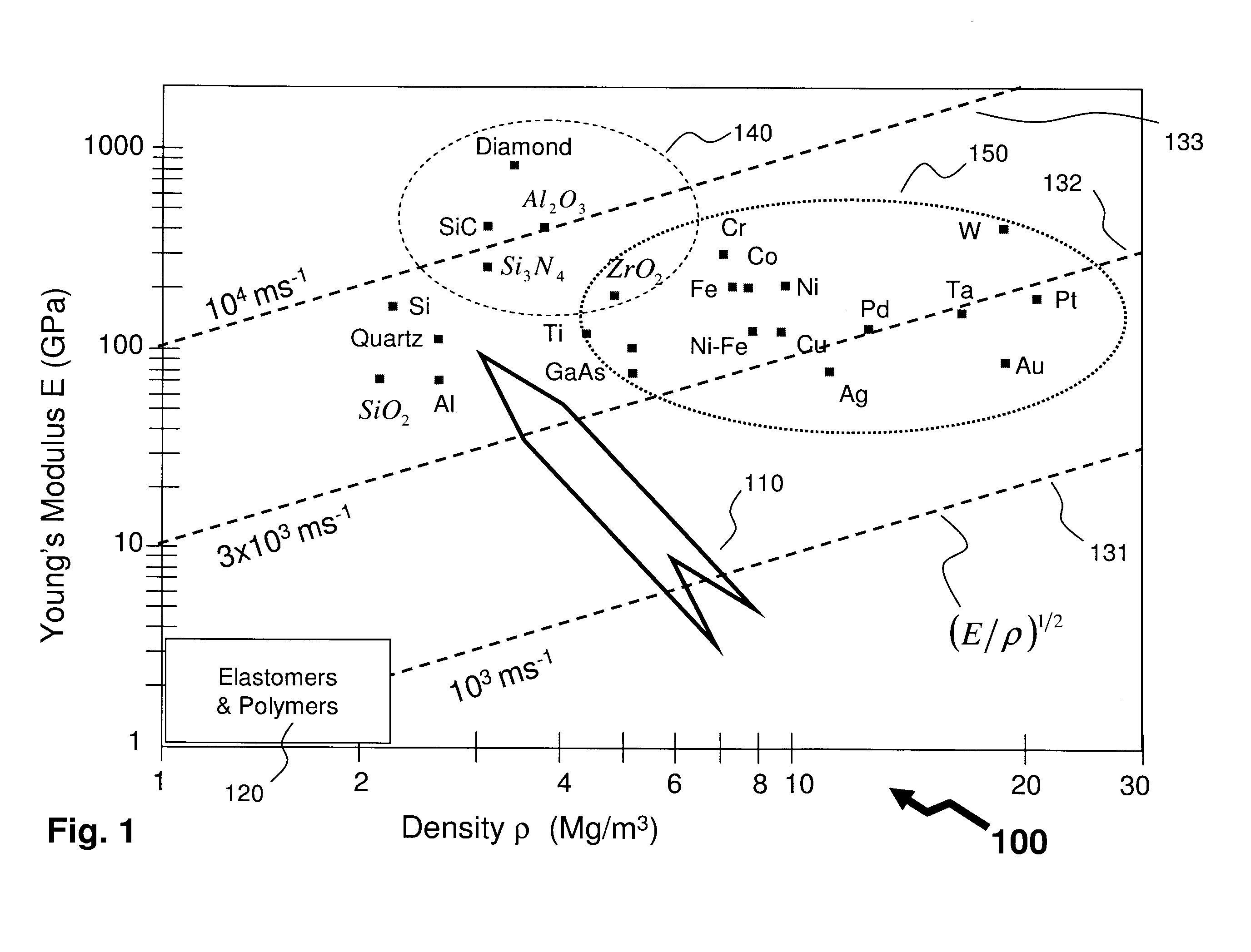

A method of providing microelectromechanical structures (MEMS) that are compatible with silicon CMOS electronics is provided. The method providing for processes and manufacturing sequences limiting the maximum exposure of an integrated circuit upon which the MEMS is manufactured to below 350° C., and potentially to below 250° C., thereby allowing direct manufacturing of the MEMS devices onto electronics, such as Si CMOS circuits. The method further providing for the provisioning of MEMS devices with multiple non-conductive structural layers such as silicon carbide separated with small lateral gaps. Such silicon carbide structures offering enhanced material properties, increased environmental and chemical resilience whilst also allowing novel designs to be implemented taking advantage of the non-conductive material of the structural layer. The use of silicon carbide being beneficial within the formation of MEMS elements such as motors, gears, rotors, translation drives, etc where increased hardness reduces wear of such elements during operation.

Owner:MCGILL UNIV

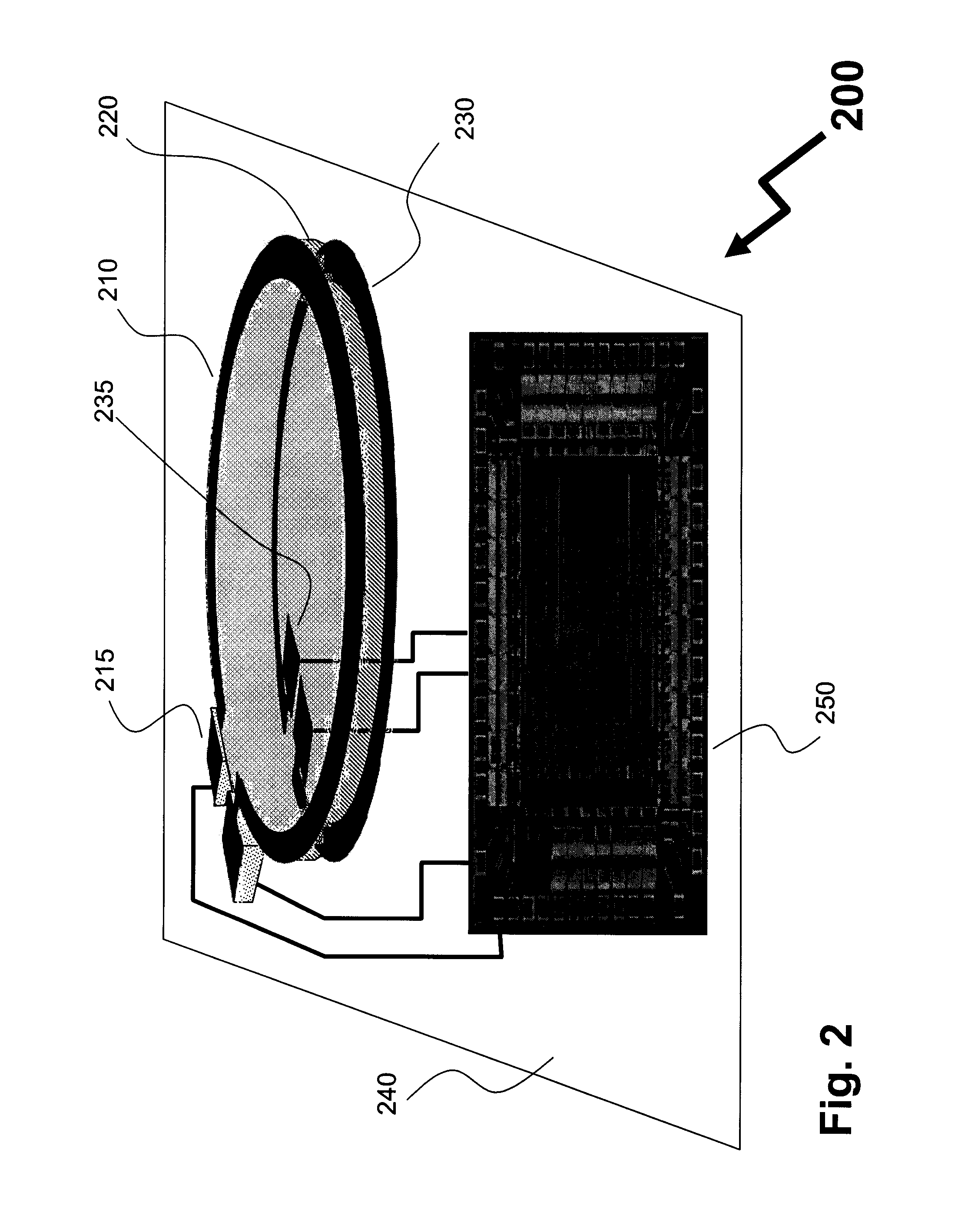

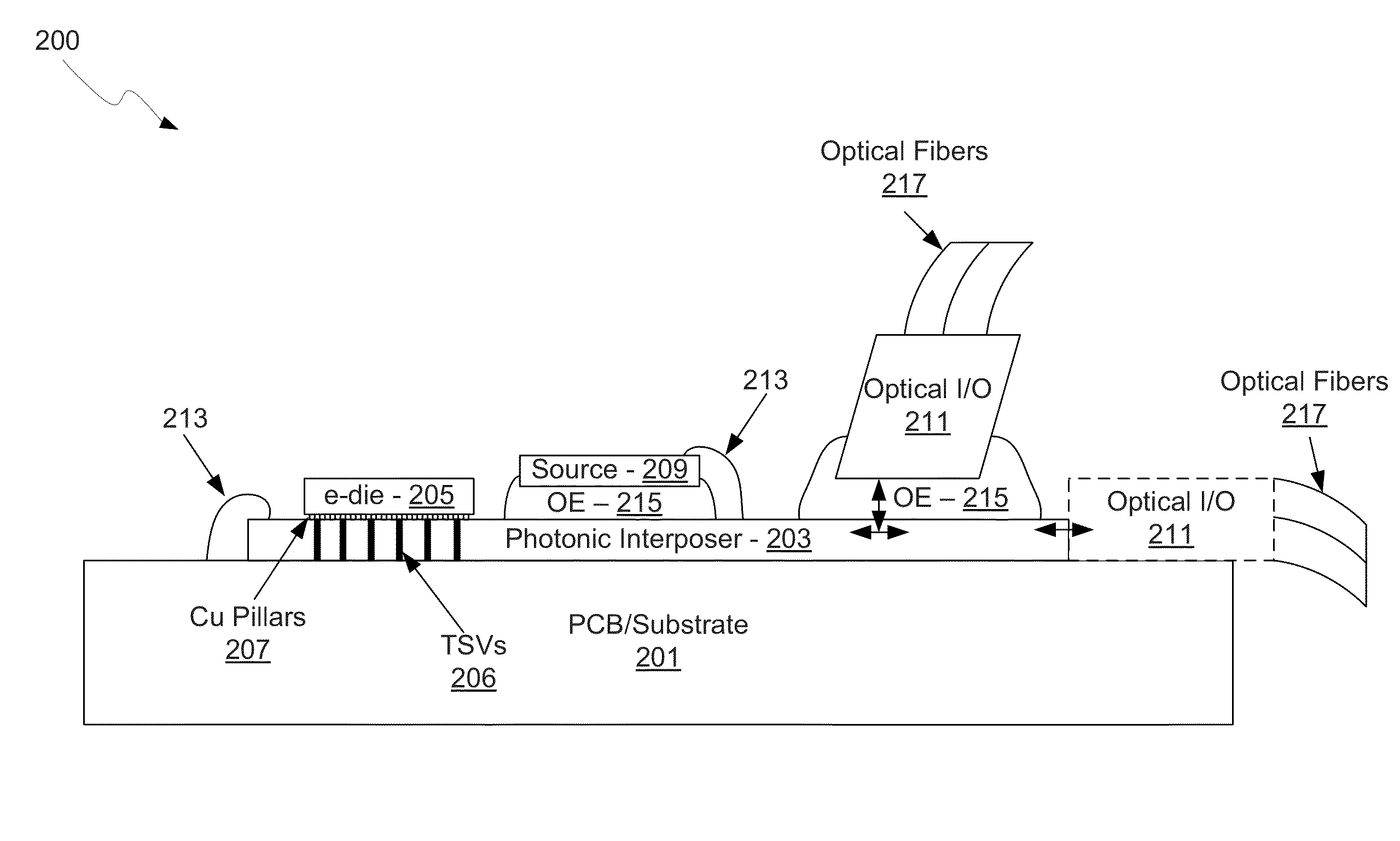

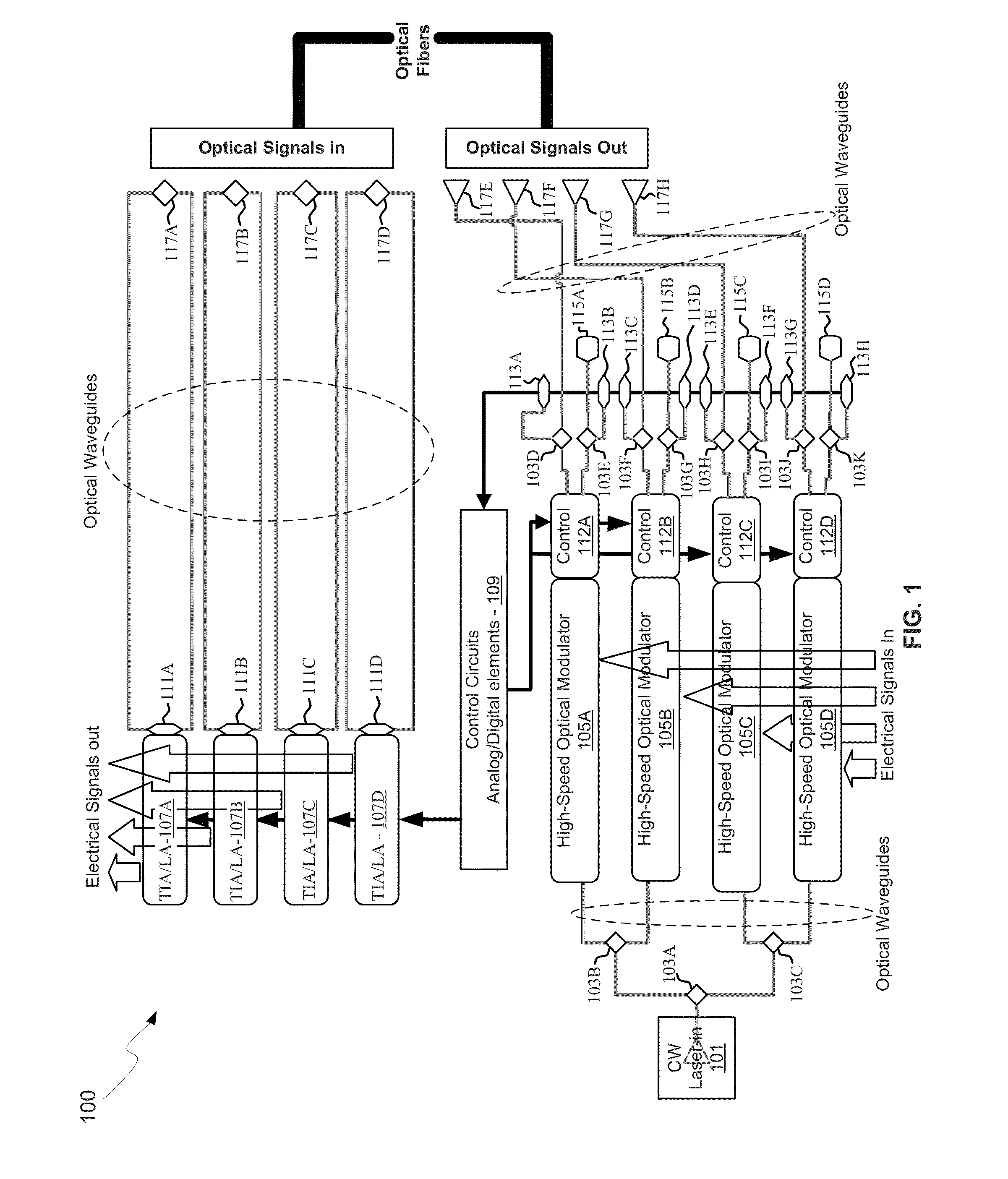

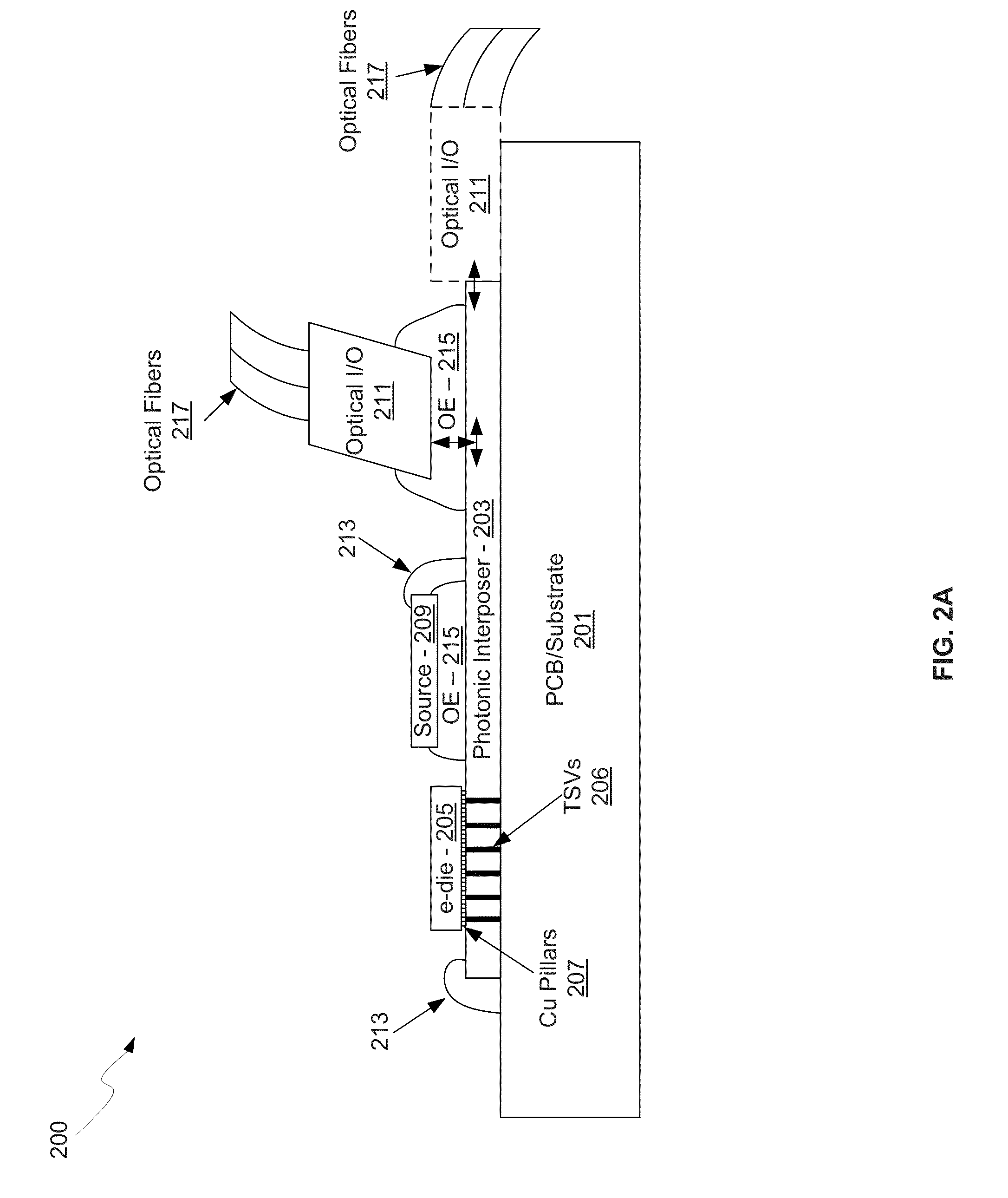

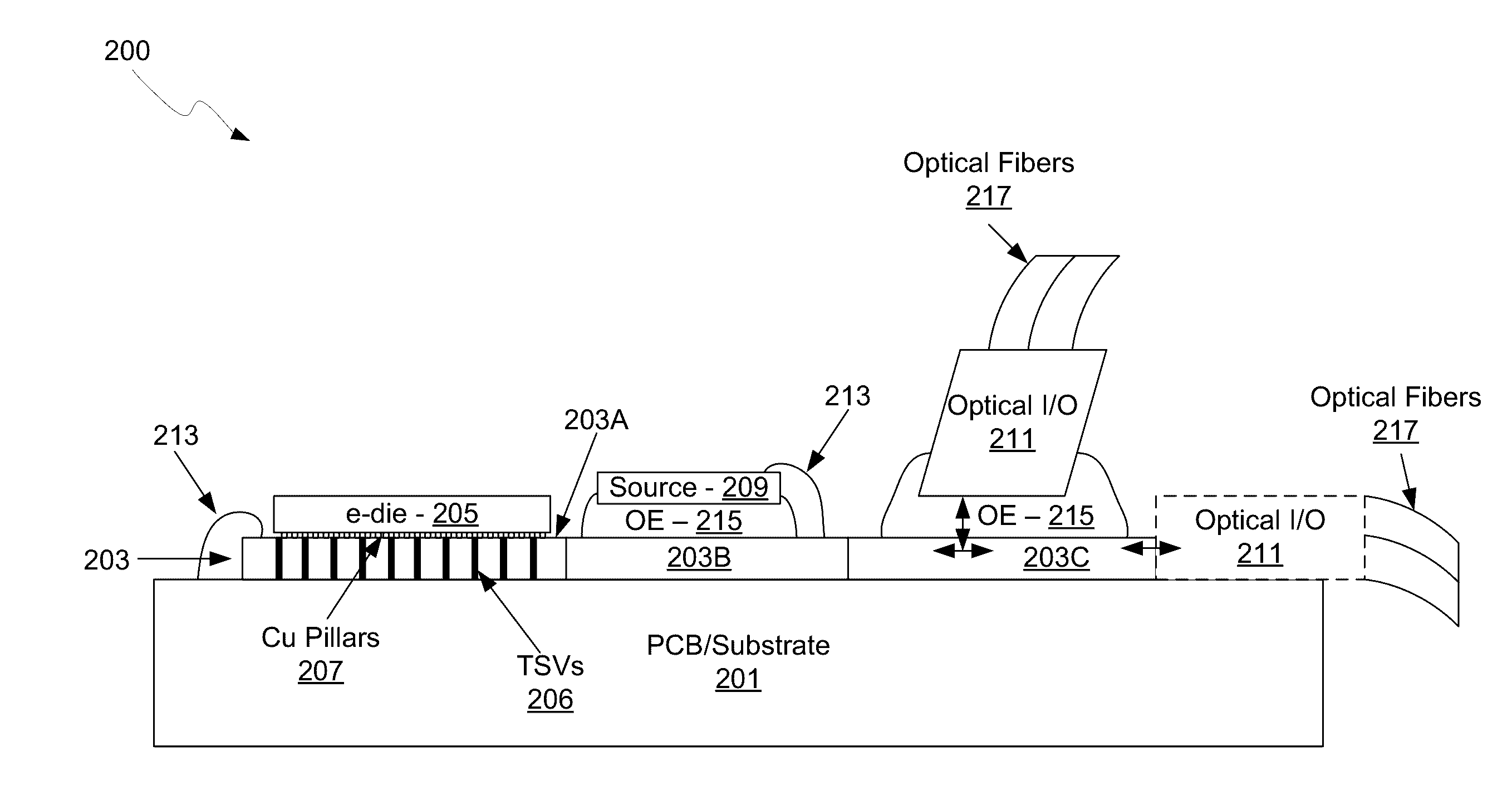

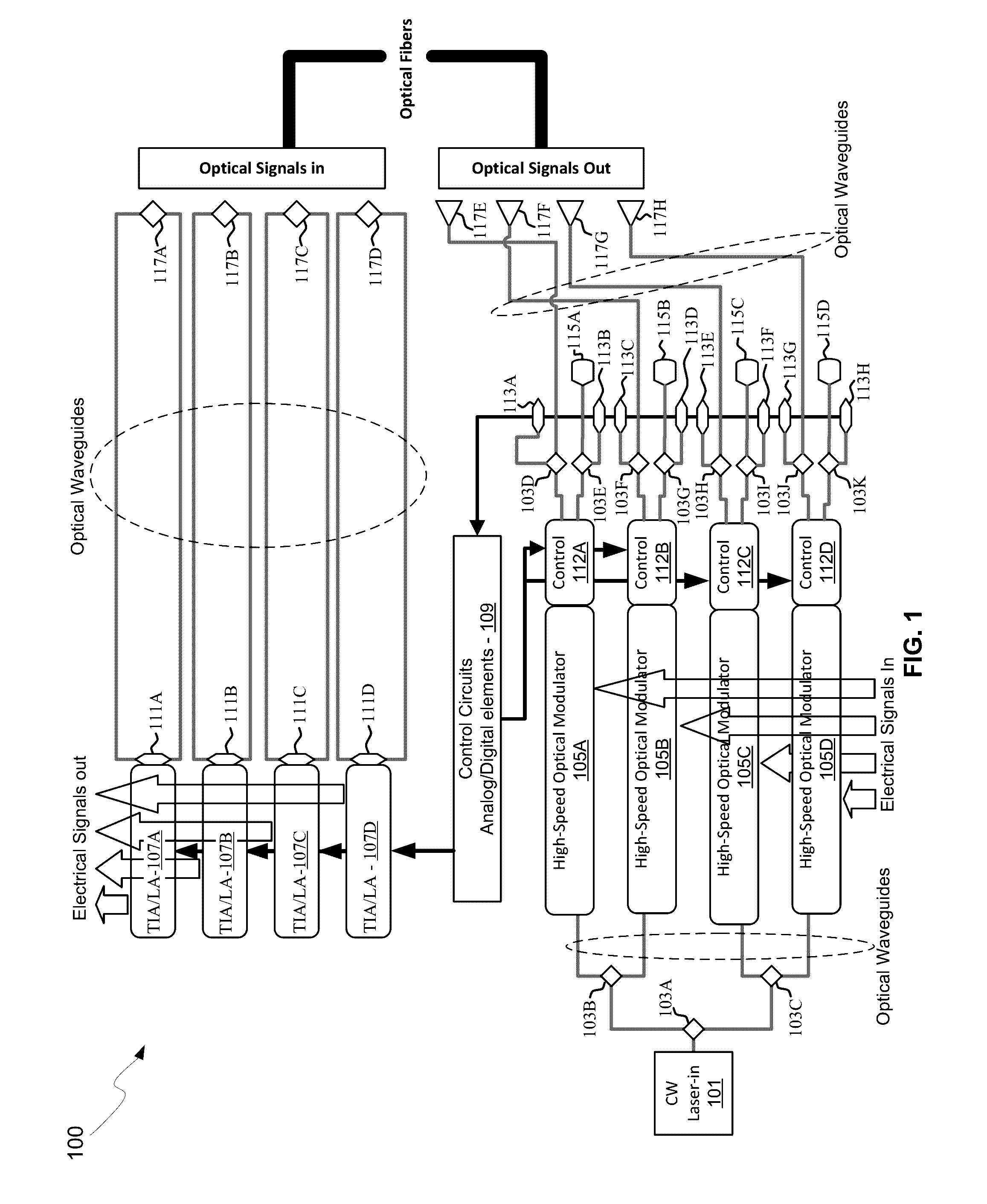

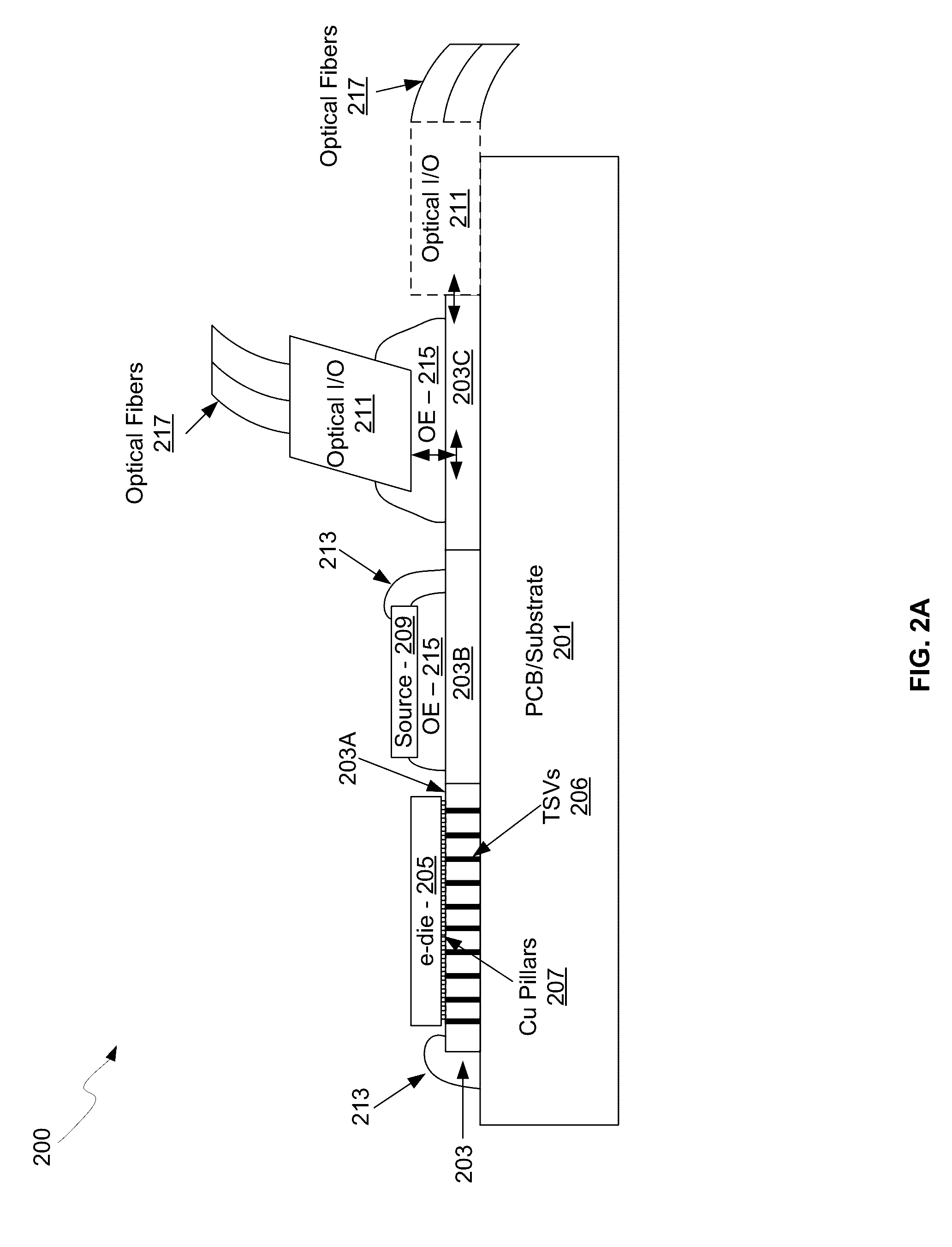

Method and system for a photonic interposer

ActiveUS20140369693A1Semiconductor/solid-state device detailsSolid-state devicesCmos electronicsPhotonics

Methods and systems for a photonic interposer are disclosed and may include receiving one or more continuous wave (CW) optical signals in a silicon photonic interposer from an optical source external to the silicon photonic interposer. The received CW optical signals may be processed based on electrical signals received from a CMOS electronics die bonded to the interposer, and modulated optical signals may be received in the interposer via optical couplers on the interposer. Electrical signals may be generated in the interposer based on the received modulated optical signals, and may be communicated to the CMOS electronics die. The generated electrical signals to may be communicated to the CMOS electronics die via copper pillars. The CW optical signals may be received in the interposer from an optical source assembly coupled to the interposer. The CW optical signals may be received from optical fibers coupled to the interposer.

Owner:CISCO TECH INC

Vertical integration of CMOS electronics with photonic devices

ActiveUS8859394B2Solid-state devicesSemiconductor/solid-state device manufacturingSemiconductor structureCmos electronics

A method of fabricating a composite semiconductor structure includes providing an SOI substrate including a plurality of silicon-based devices, providing a compound semiconductor substrate including a plurality of photonic devices, and dicing the compound semiconductor substrate to provide a plurality of photonic dies. Each die includes one or more of the plurality of photonics devices. The method also includes providing an assembly substrate having a base layer and a device layer including a plurality of CMOS devices, mounting the plurality of photonic dies on predetermined portions of the assembly substrate, and aligning the SOI substrate and the assembly substrate. The method further includes joining the SOI substrate and the assembly substrate to form a composite substrate structure and removing at least the base layer of the assembly substrate from the composite substrate structure.

Owner:SKORPIOS TECH

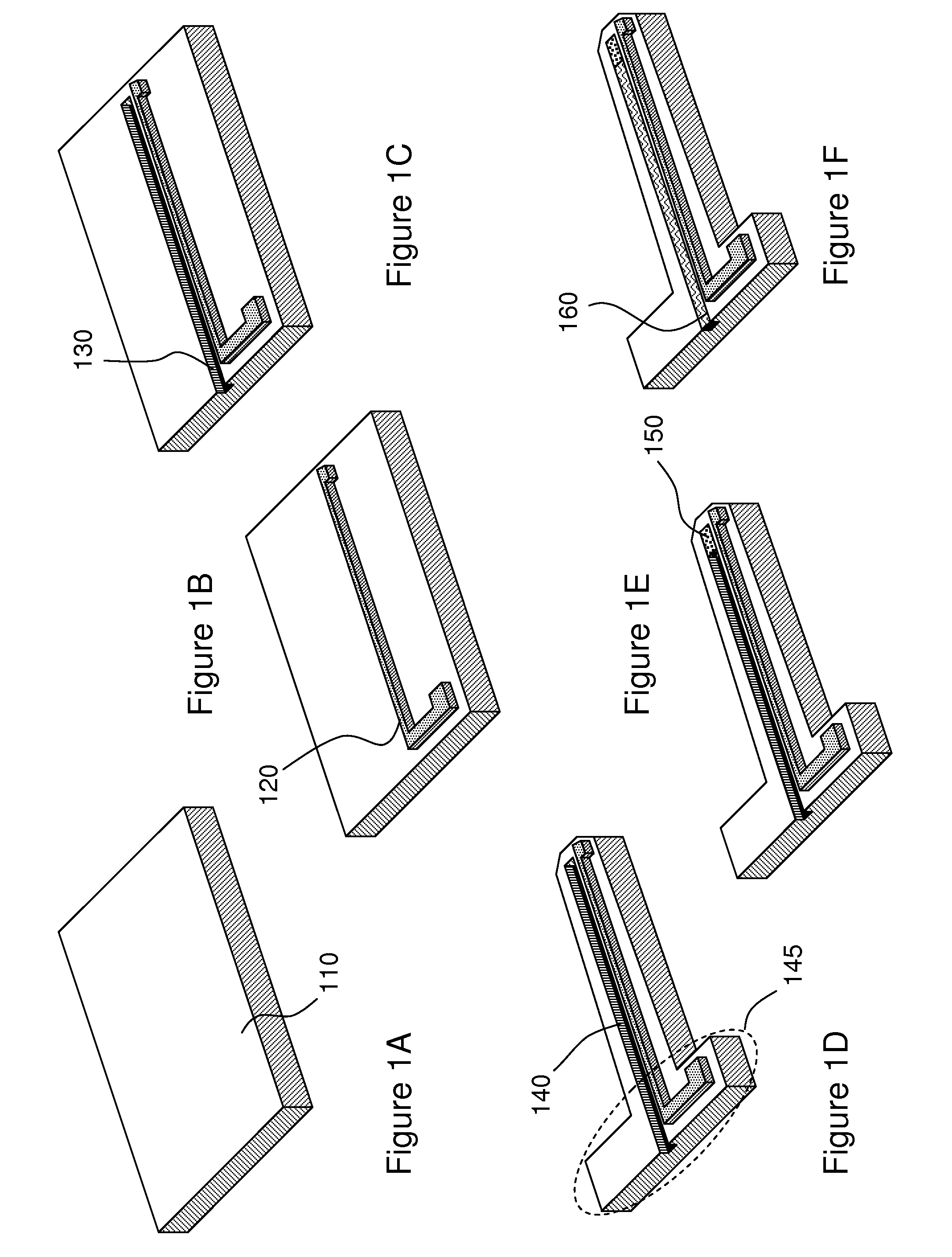

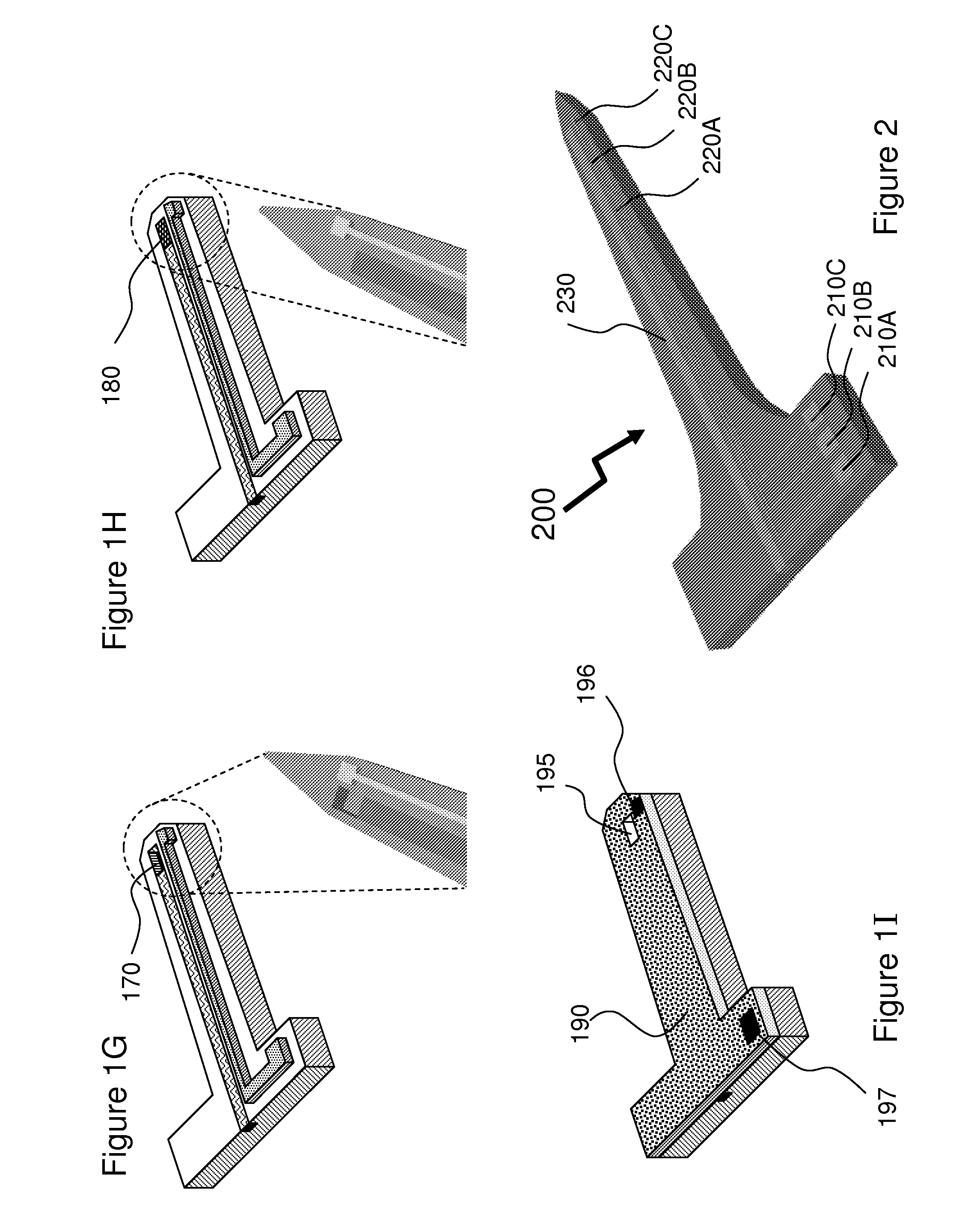

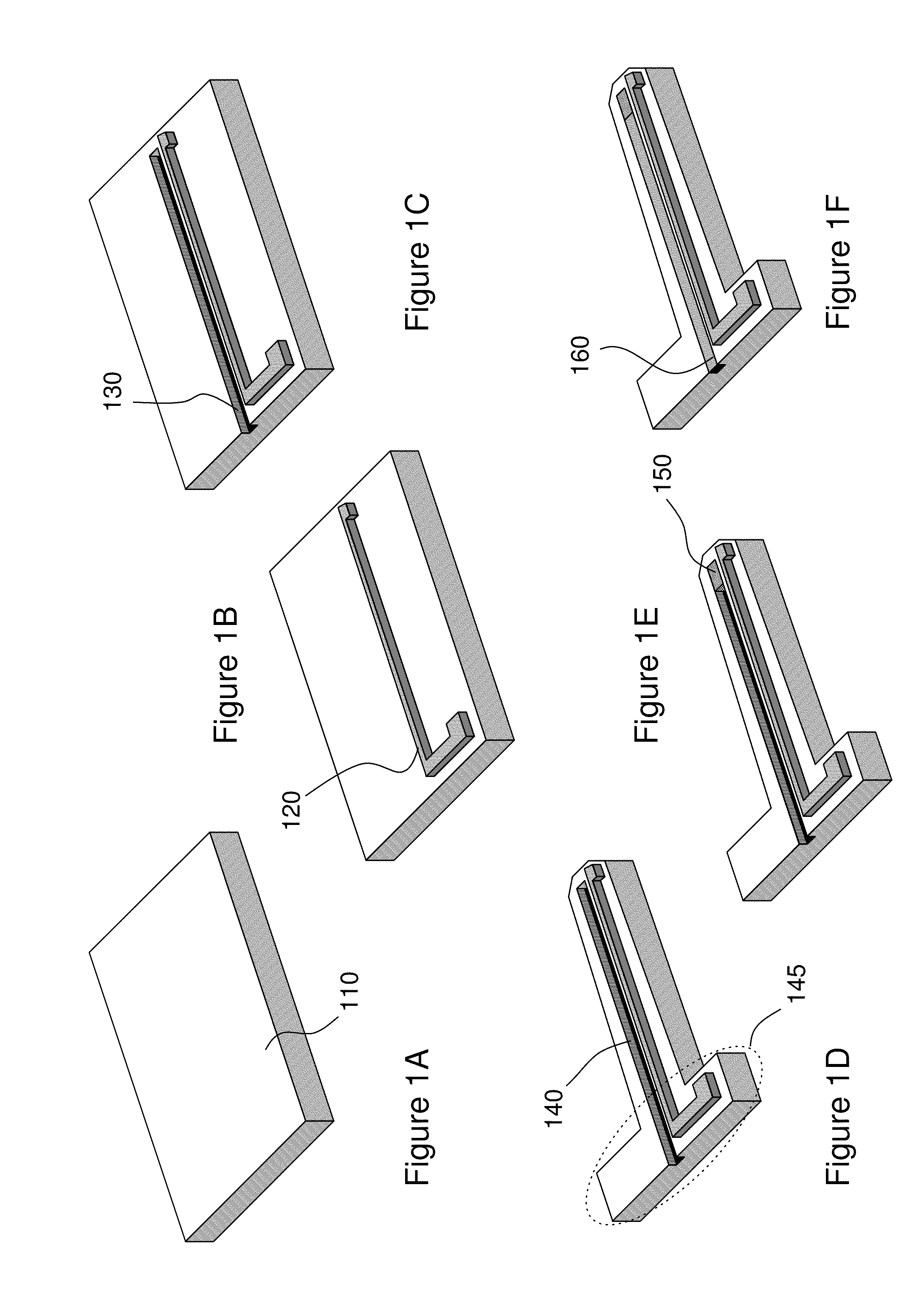

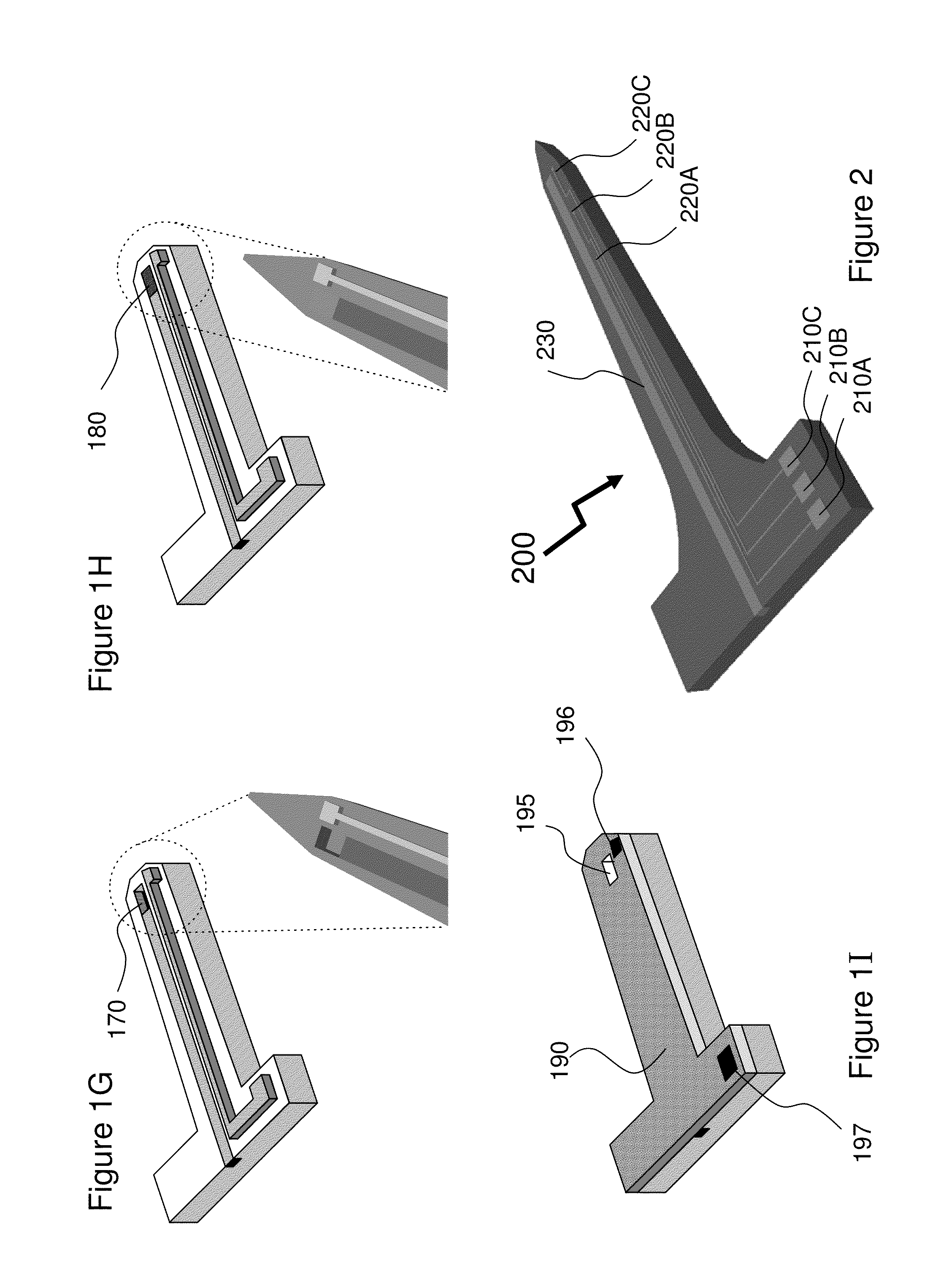

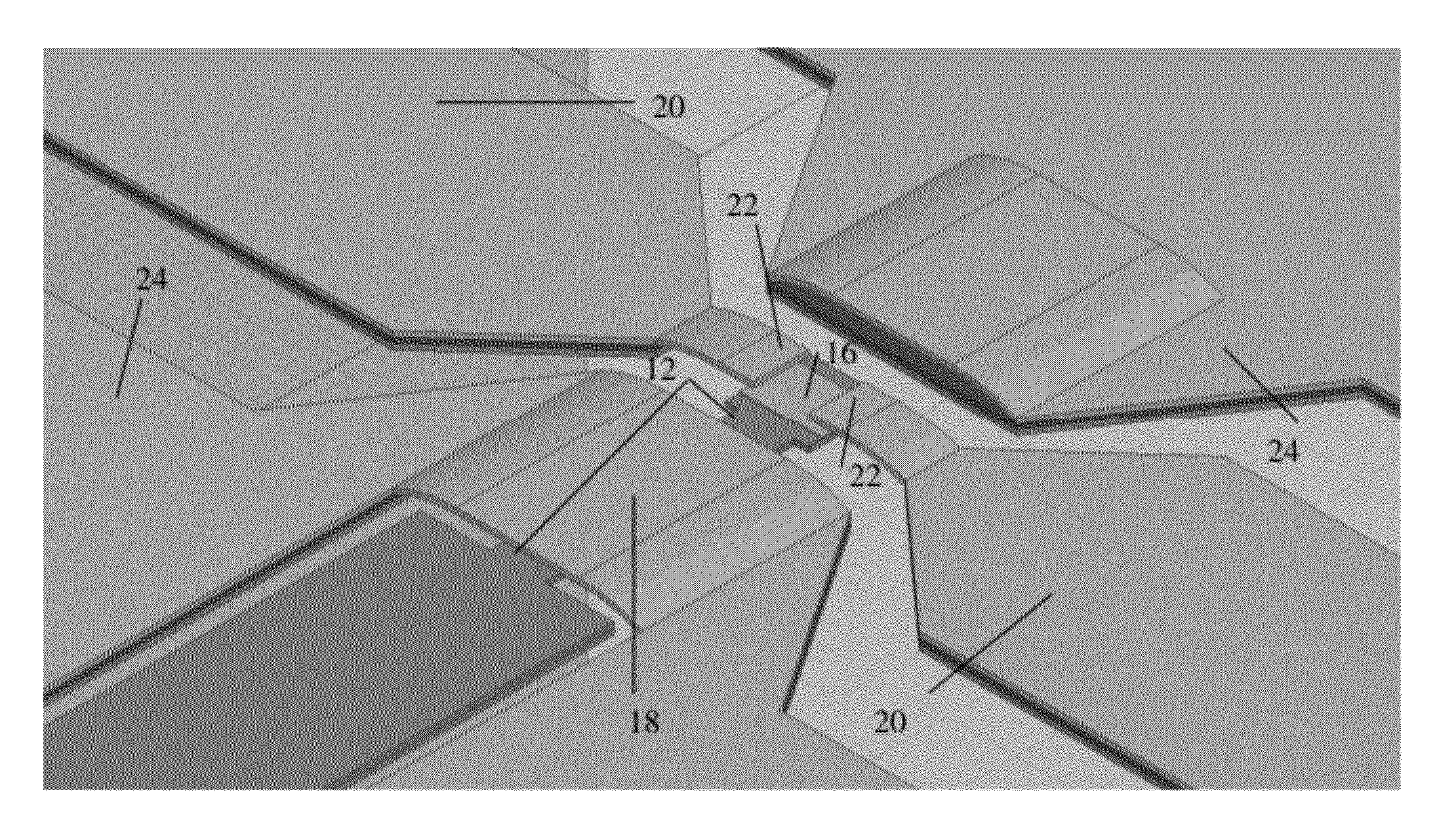

Optically interrogated solid state biosensors incorporating porous materials—devices

ActiveUS8263986B2Solid-state devicesSemiconductor/solid-state device manufacturingEngineeringWaveguide

Quantitative understanding of neural and biological activity at a sub-millimeter scale requires an integrated probe platform that combines biomarker sensors together with electrical stimulus / recording sites. Optically addressed biomarker sensors within such an integrated probe platform allows remote interrogation from the activity being measured. Monolithic or hybrid integrated silicon probe platforms would beneficially allow for accurate control of neural prosthetics, brain machine interfaces, etc as well as helping with complex brain diseases and disorders. According to the invention a silicon probe platform is provided employing ultra-thin silicon in conjunction with optical waveguides, optoelectronic interfaces, porous filter elements, and integrated CMOS circuitry. Such probes allowing simultaneously analysis of both neural electrical activities along with chemical activity derived from multiple biomolecular sensors with porous membrane filters. Such porous silicon and polymer filters providing biomolecular filtering and optical filtering being compatible with post-processing wafers with integrated CMOS electronics.

Owner:MCGILL UNIV

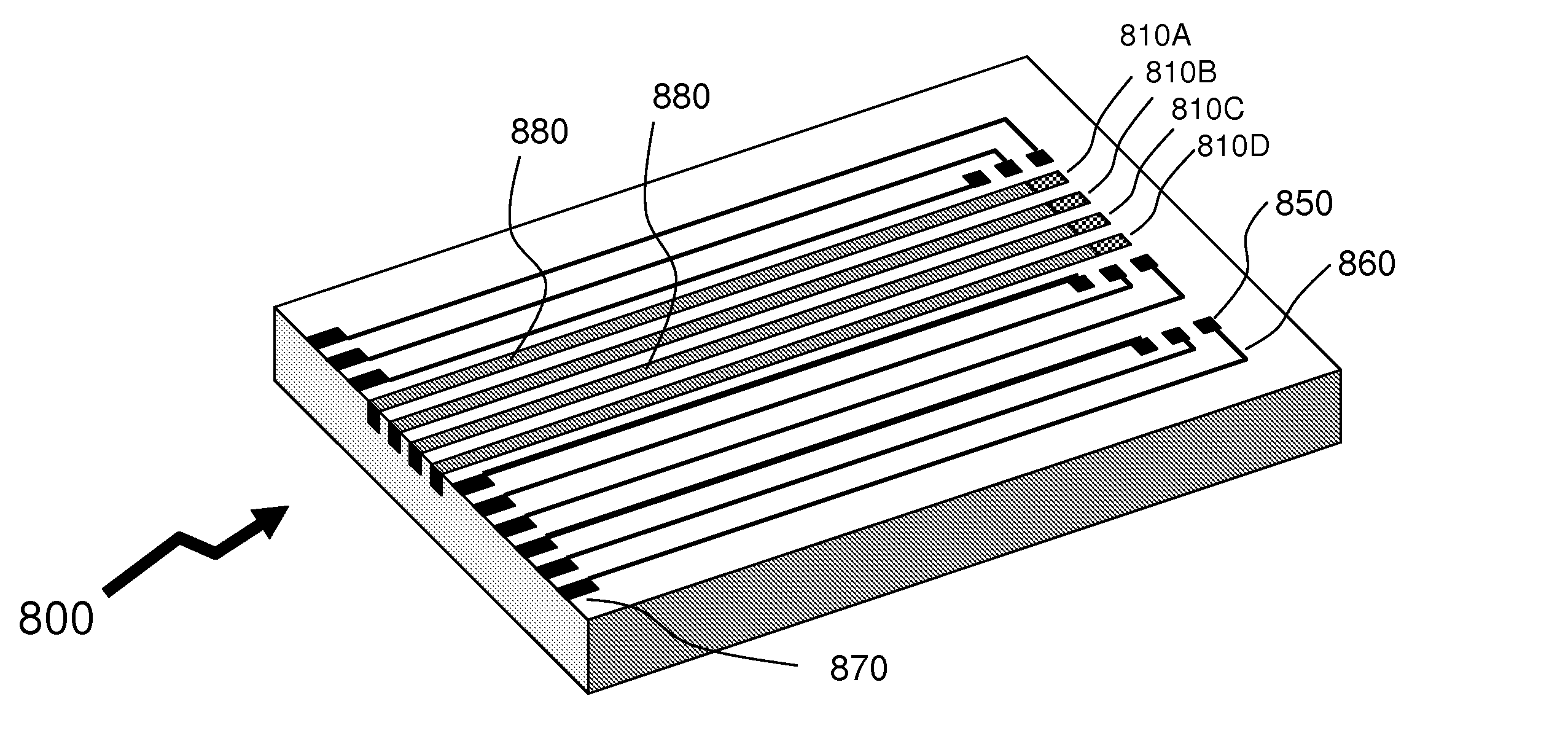

Method And System For Large Silicon Photonic Interposers By Stitching

Methods and systems for large silicon photonic interposers by stitching are disclosed and may include, in an integrated optical communication system including CMOS electronics die coupled to a silicon photonic interposer, where the interposer includes a plurality of reticle sections: communicating an optical signal between two of the plurality of reticle sections utilizing a waveguide. The waveguide may include a taper region at a boundary between the two reticle sections, the taper region expanding an optical mode of the communicated optical signal prior to the boundary and narrowing the optical mode after the boundary. A continuous wave (CW) optical signal may be received in a first of the reticle sections from an optical source external to the interposer. The CW optical signal may be received in the interposer from an optical source assembly coupled to a grating coupler in the first of the reticle sections in the silicon photonic interposer.

Owner:CISCO TECH INC

Optically Interrogated Solid State Biosensors Incorporating Porous Materials - Devices and Methods of Fabrication

Quantitative understanding of neural and biological activity at a sub-millimeter scale requires an integrated probe platform that combines biomarker sensors together with electrical stimulus / recording sites. Optically addressed biomarker sensors within such an integrated probe platform allows remote interrogation from the activity being measured. Monolithic or hybrid integrated silicon probe platforms would beneficially allow for accurate control of neural prosthetics, brain machine interfaces, etc as well as helping with complex brain diseases and disorders. According to the invention a silicon probe platform is provided employing ultra-thin silicon in conjunction with optical waveguides, optoelectronic interfaces, porous filter elements, and integrated CMOS circuitry. Such probes allowing simultaneously analysis of both neural electrical activities along with chemical activity derived from multiple biomolecular sensors with porous membrane filters. Such porous silicon and polymer filters providing biomolecular filtering and optical filtering being compatible with post-processing wafers with integrated CMOS electronics.

Owner:MCGILL UNIV

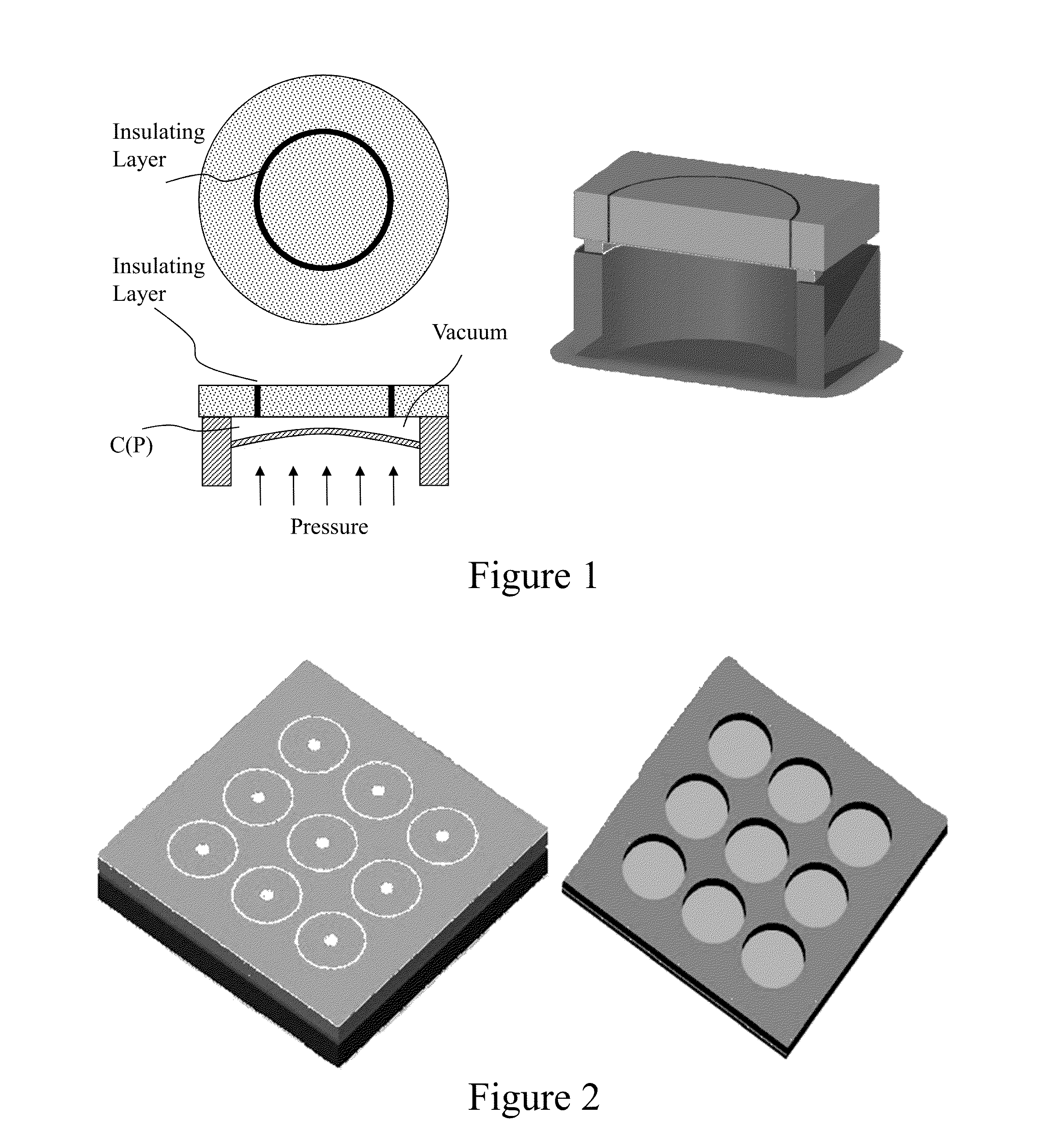

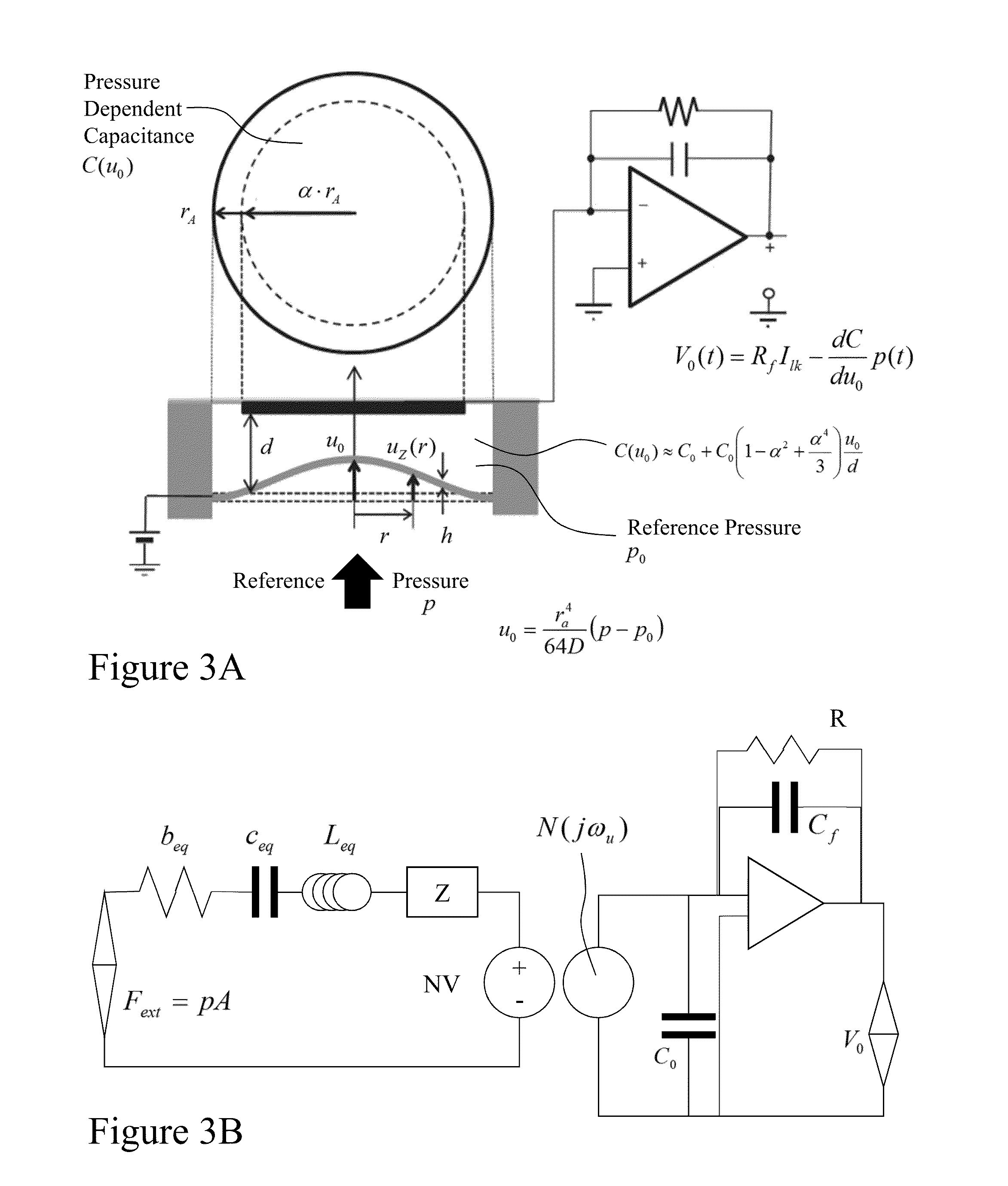

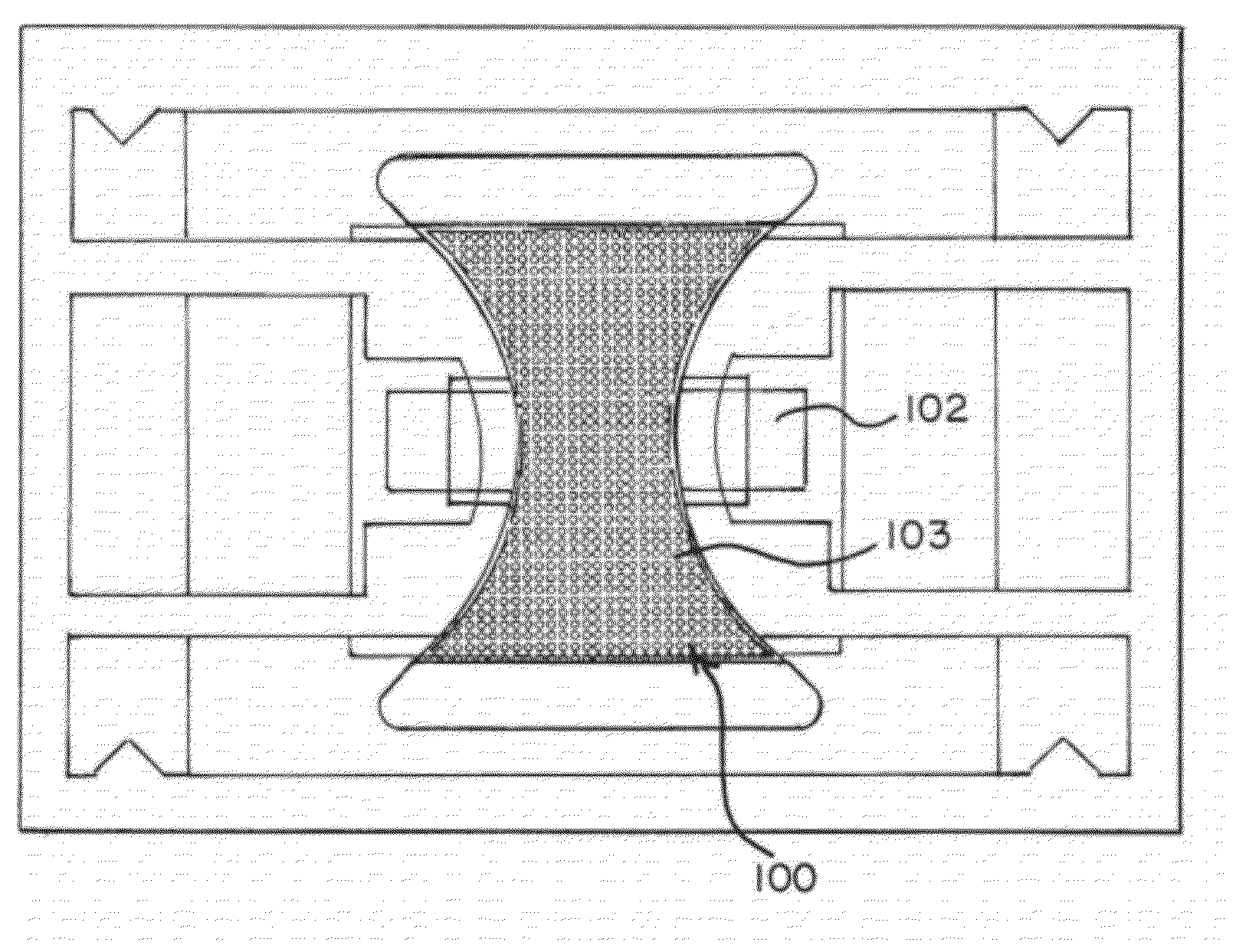

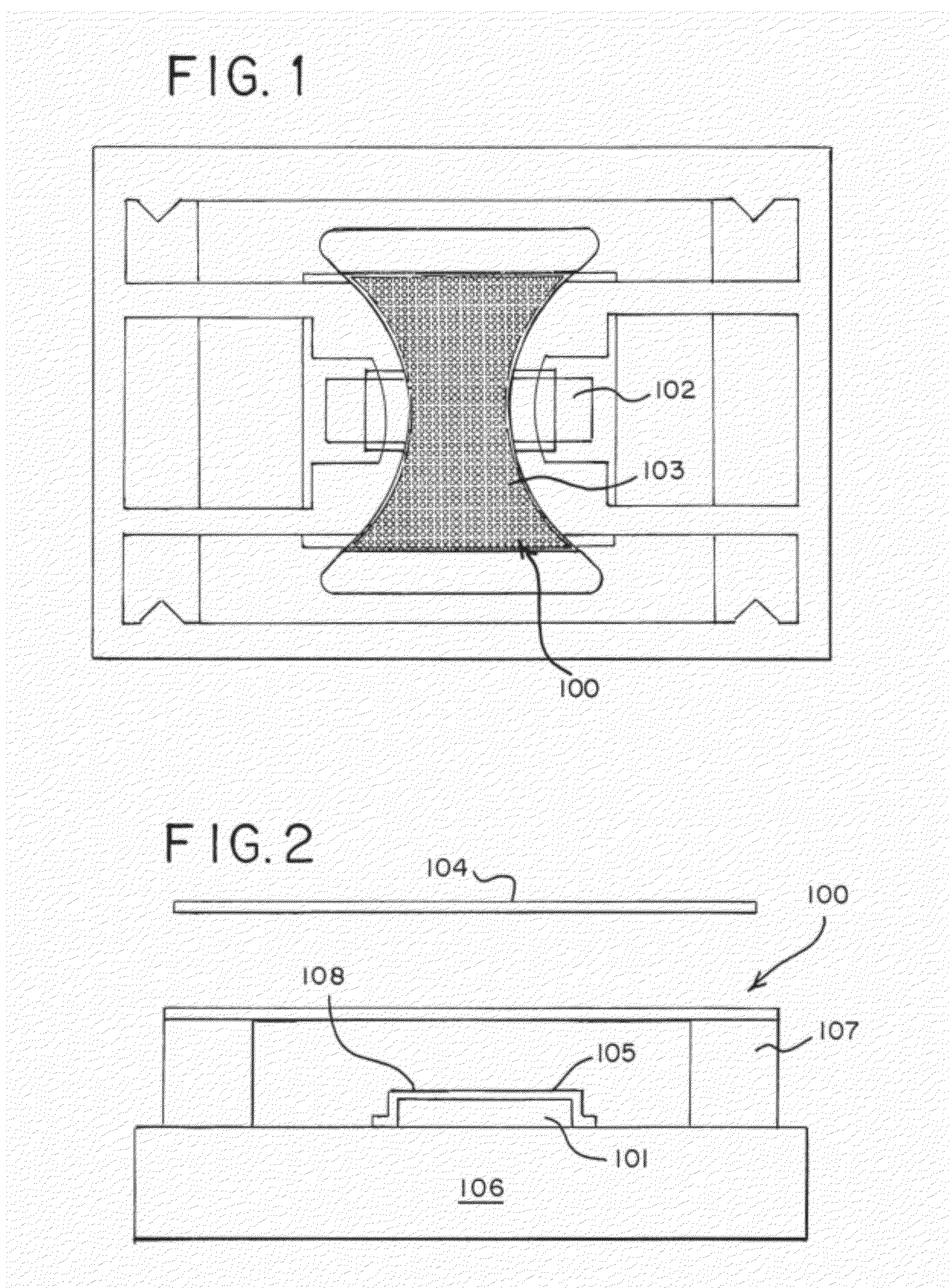

Methods and devices for microelectromechanical pressure sensors

ActiveUS20160002026A1Reduce restrictionsImpedence networksSolid-state devicesCost effectivenessCmos electronics

MEMS based sensors, particularly capacitive sensors, potentially can address critical considerations for users including accuracy, repeatability, long-term stability, ease of calibration, resistance to chemical and physical contaminants, size, packaging, and cost effectiveness. Accordingly, it would be beneficial to exploit MEMS processes that allow for manufacturability and integration of resonator elements into cavities within the MEMS sensor that are at low pressure allowing high quality factor resonators and absolute pressure sensors to be implemented. Embodiments of the invention provide capacitive sensors and MEMS elements that can be implemented directly above silicon CMOS electronics.

Owner:MY01 IP HLDG INC

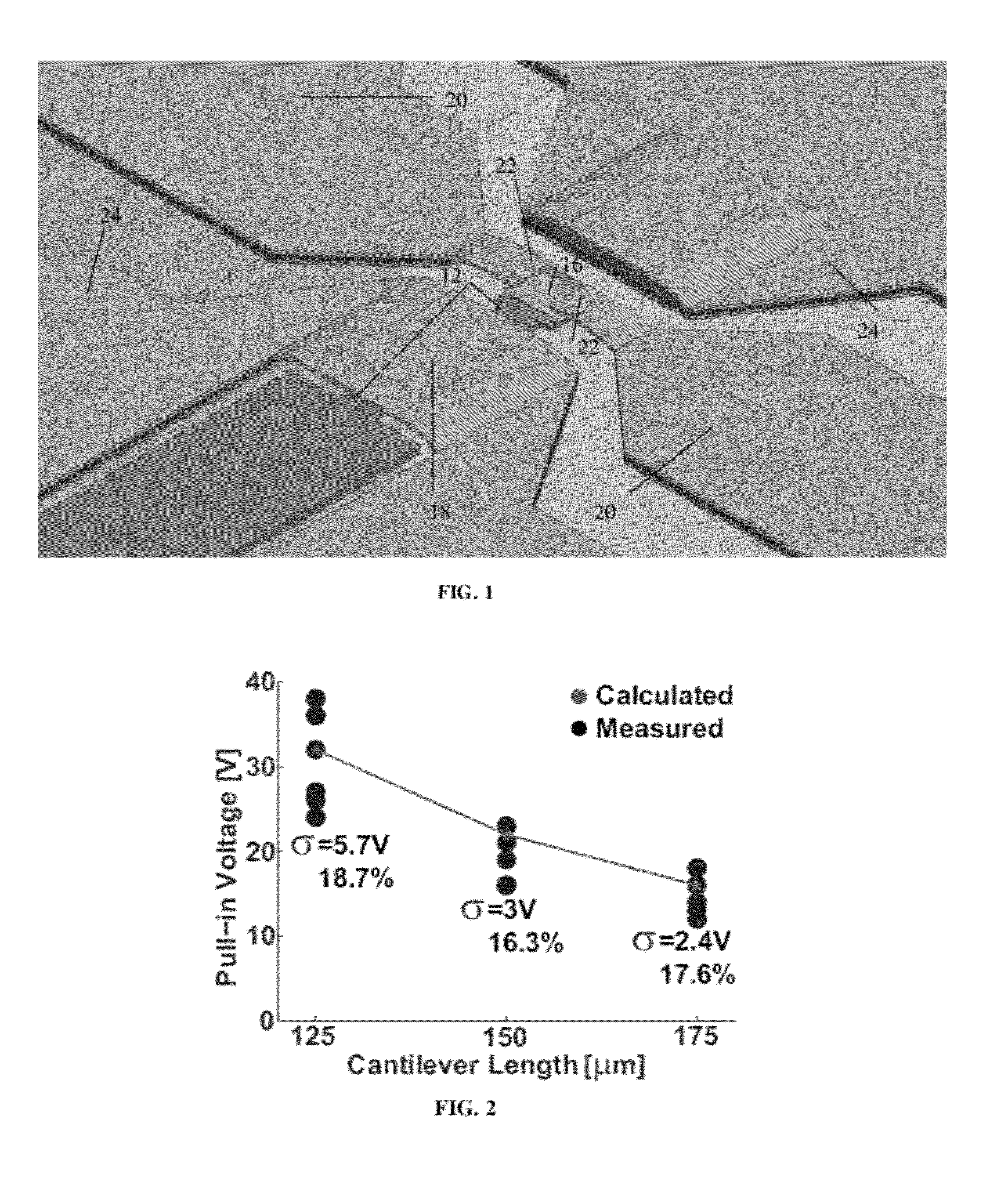

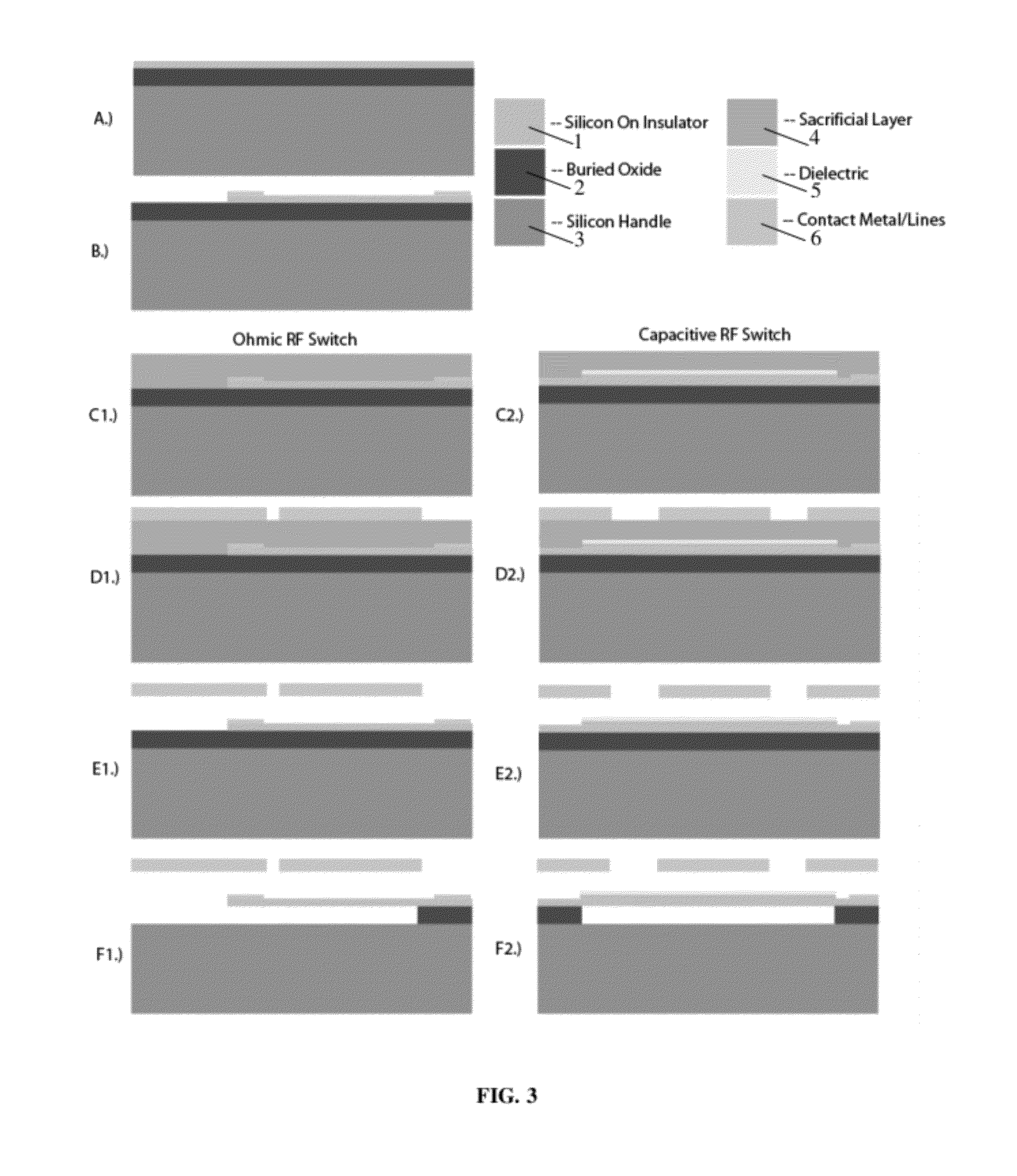

Low-cost process-independent RF MEMS switch

InactiveUS20120318650A1High yieldIncrease variabilityElectrostatic/electro-adhesion relaysElectrostrictive/piezoelectric relaysManufacturing technologyCmos electronics

Owner:PEROULIS DIMITRIOS +1

Methods and devices for microelectromechanical resonators

ActiveUS20160006414A1Reduce restrictionsImpedence networksDecorative surface effectsCost effectivenessCmos electronics

MEMS based sensors, particularly capacitive sensors, potentially can address critical considerations for users including accuracy, repeatability, long-term stability, ease of calibration, resistance to chemical and physical contaminants, size, packaging, and cost effectiveness. Accordingly, it would be beneficial to exploit MEMS processes that allow for manufacturability and integration of resonator elements into cavities within the MEMS sensor that are at low pressure allowing high quality factor resonators and absolute pressure sensors to be implemented. Embodiments of the invention provide capacitive sensors and MEMS elements that can be implemented directly above silicon CMOS electronics.

Owner:MY01 IP HLDG INC

Low temperature wafer level processing for MEMS devices

ActiveUS8409901B2Impedence networksSemiconductor/solid-state device detailsLow temperature depositionElectricity

Microelectromechanical systems (MEMS) are small integrated devices or systems that combine electrical and mechanical components. It would be beneficial for such MEMS devices to be integrated with silicon CMOS electronics and packaged in controlled environments and support industry standard mounting interconnections such as solder bump through the provisioning of through-wafer via-based electrical interconnections. However, the fragile nature of the MEMS devices, the requirement for vacuum, hermetic sealing, and stresses placed on metallization membranes are not present in packaging conventional CMOS electronics. Accordingly there is provided a means of reinforcing the through-wafer vias for such integrated MEMS-CMOS circuits by in filling a predetermined portion of the through-wafer electrical vias with low temperature deposited ceramic materials which are deposited at temperatures below 350° C., and potentially to below 250° C., thereby allowing the re-inforcing ceramic to be deposited after fabrication of the CMOS electronics.

Owner:MCGILL UNIV

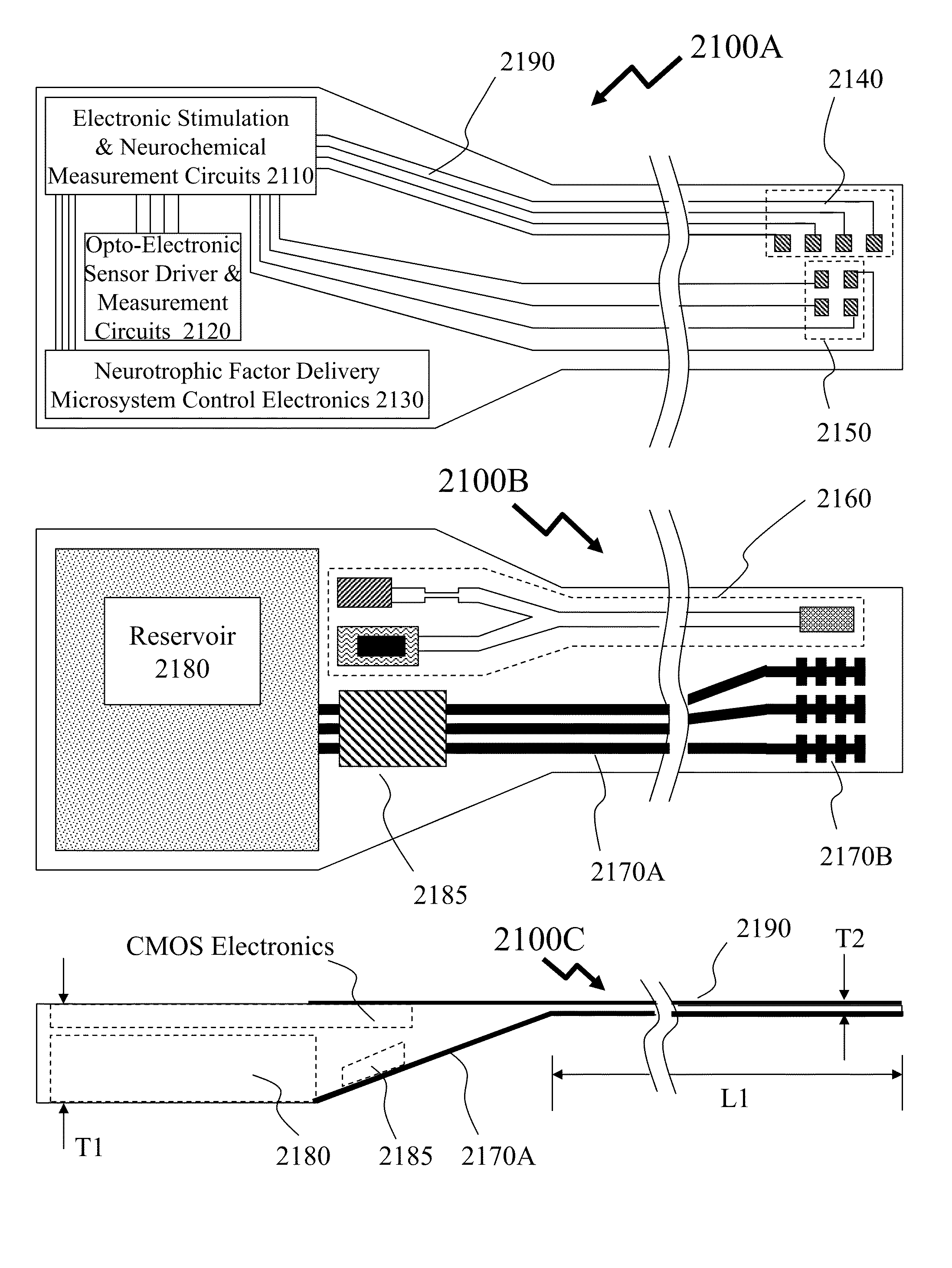

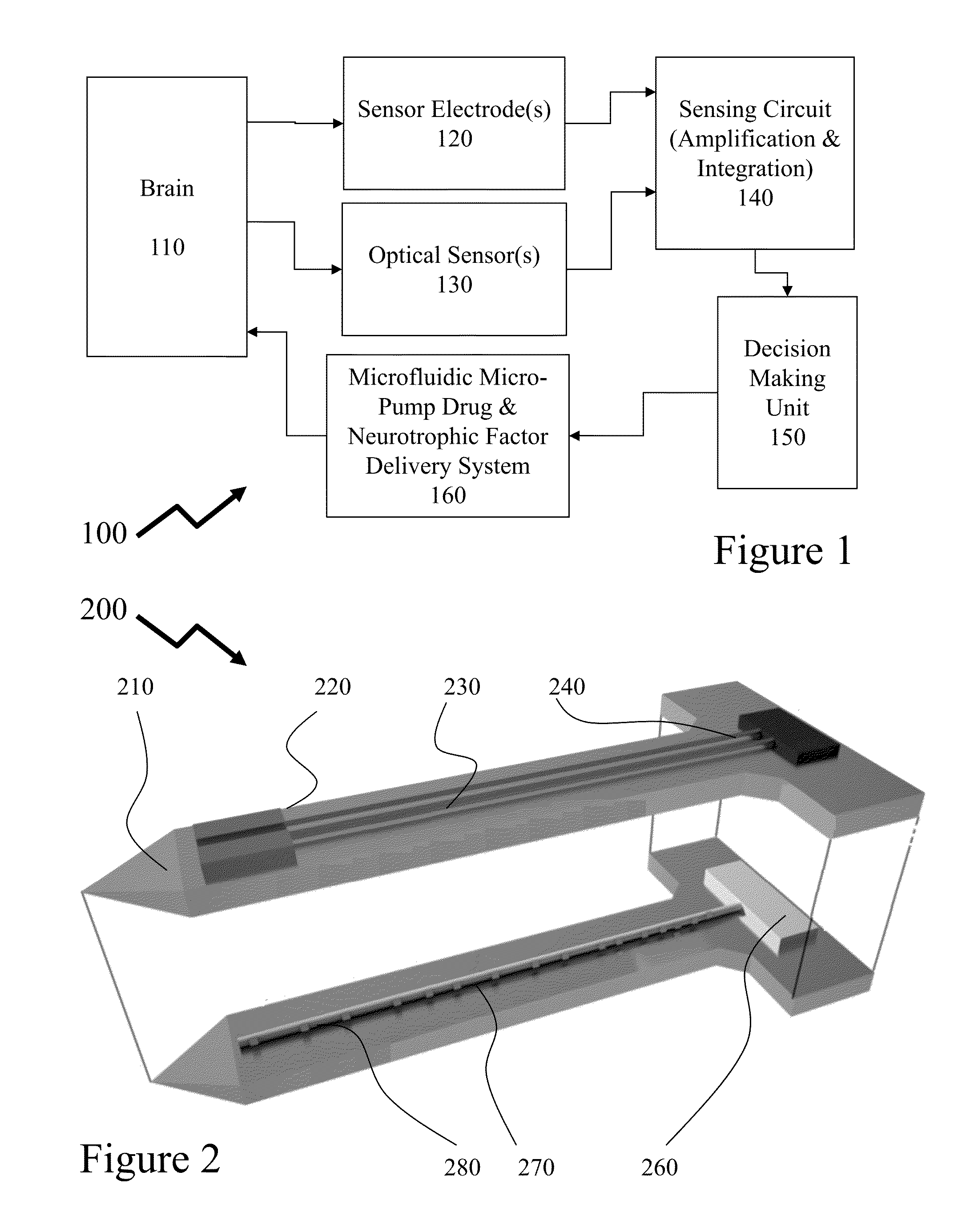

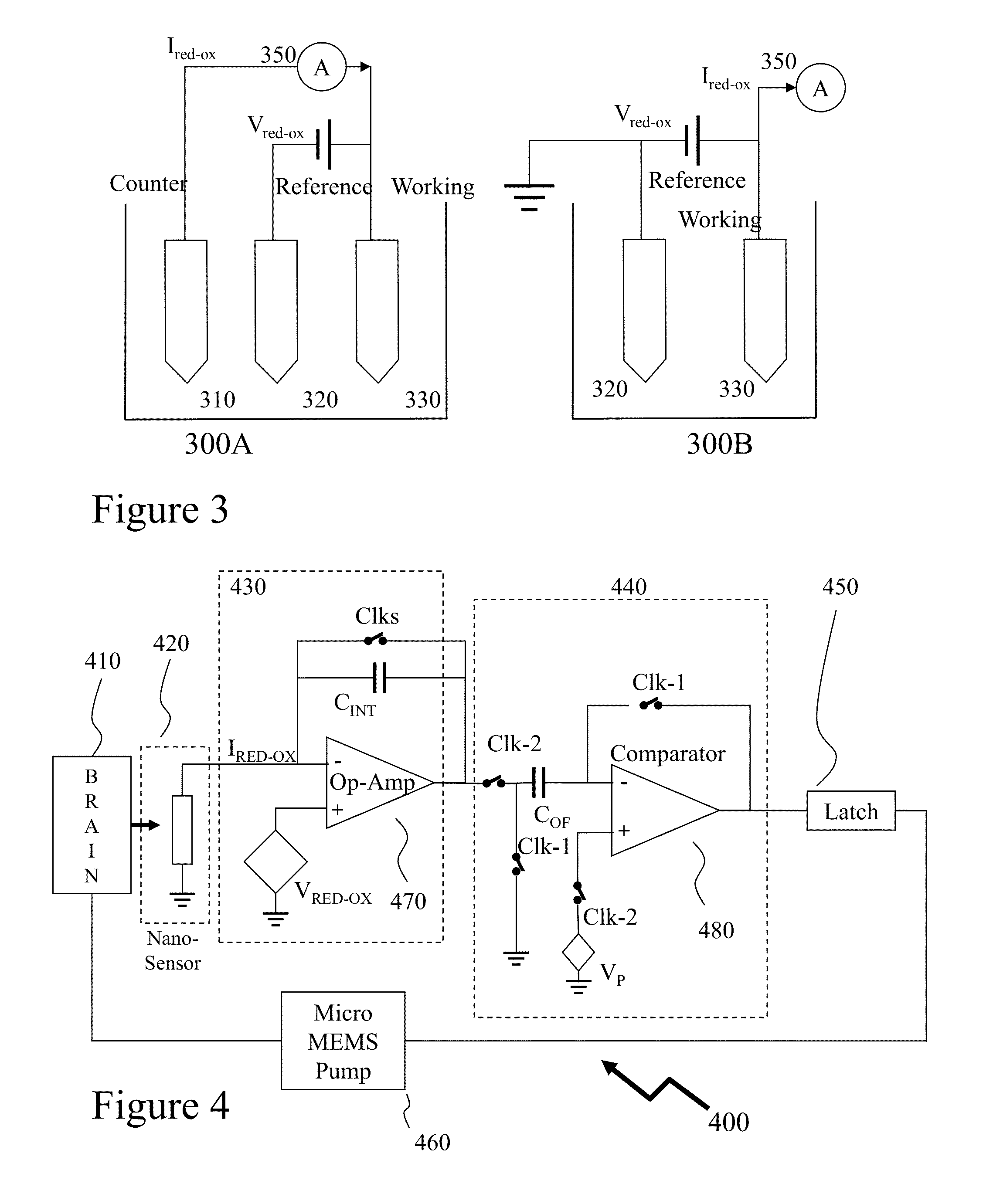

Methods and Systems for Closed Loop Neurotrophic Delivery Microsystems

Brain Machine Interfaces (BMIs) promise to improve the lives of many patients by providing a direct communication pathway between the brain and one or more external devices. As the brain is an electrochemical system additional signals may improve BMI performance beyond direct electrical signals. Further many psychiatric and neurological disorders such as Parkinson's disease, depression, dystonia, or obsessive compulsive disorder are related to neurotransmitter deficiencies or imbalances. Accordingly detection of neurotransmitter chemicals and / or management of these chemicals may enhance BMIs. Embodiments of the invention provide for implantable CMOS based target derived neurotrophic factor delivery microsystems and neurochemical sensors allowing neurotransmitter deficiencies or imbalances to be detected, monitored, and corrected. Such implantable CMOS solutions provide for high volume, low cost manufacturing as well integration options in arrayed formats as well as integration with other CMOS electronic circuits.

Owner:MUSALLAM WISSAM SAM +1

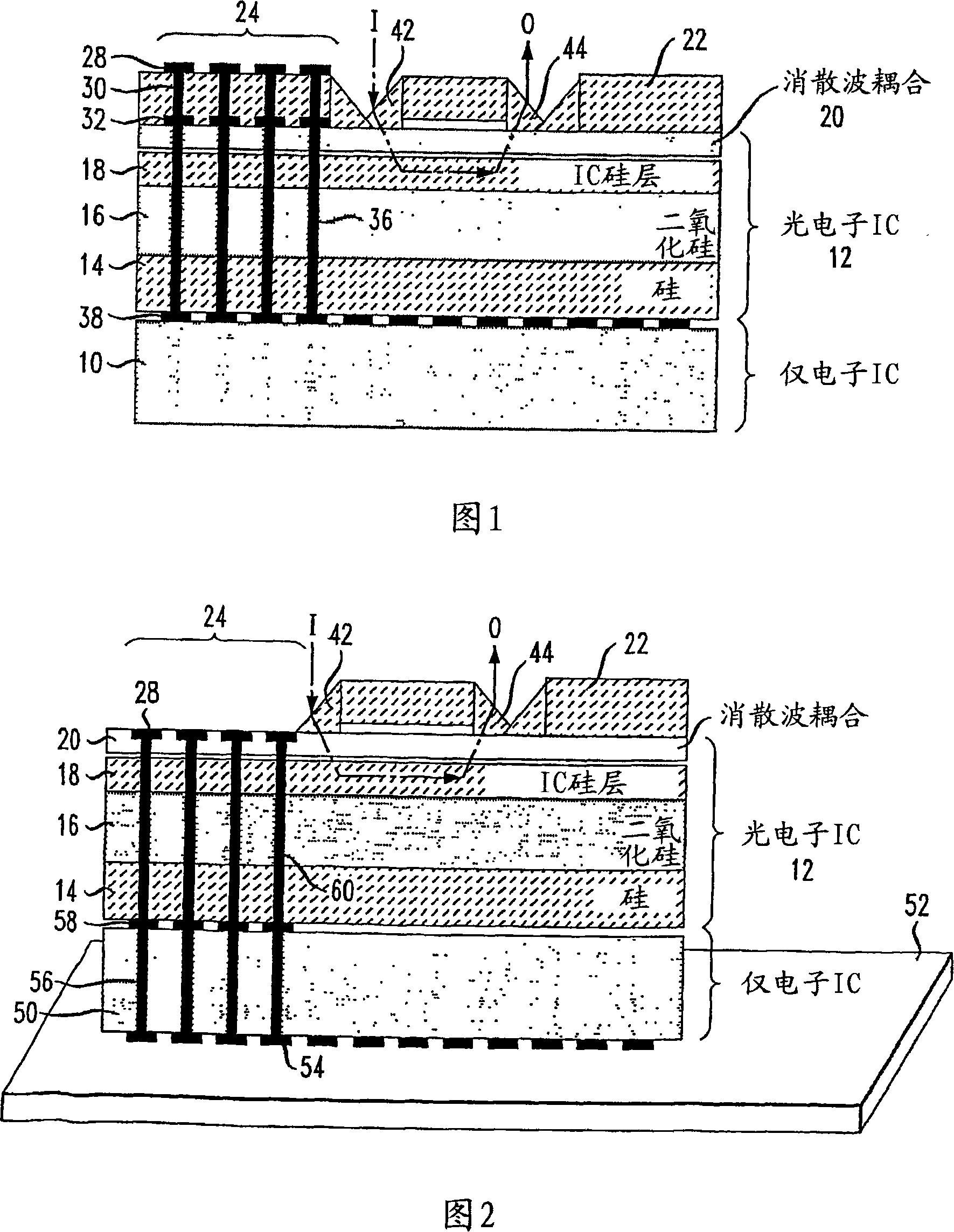

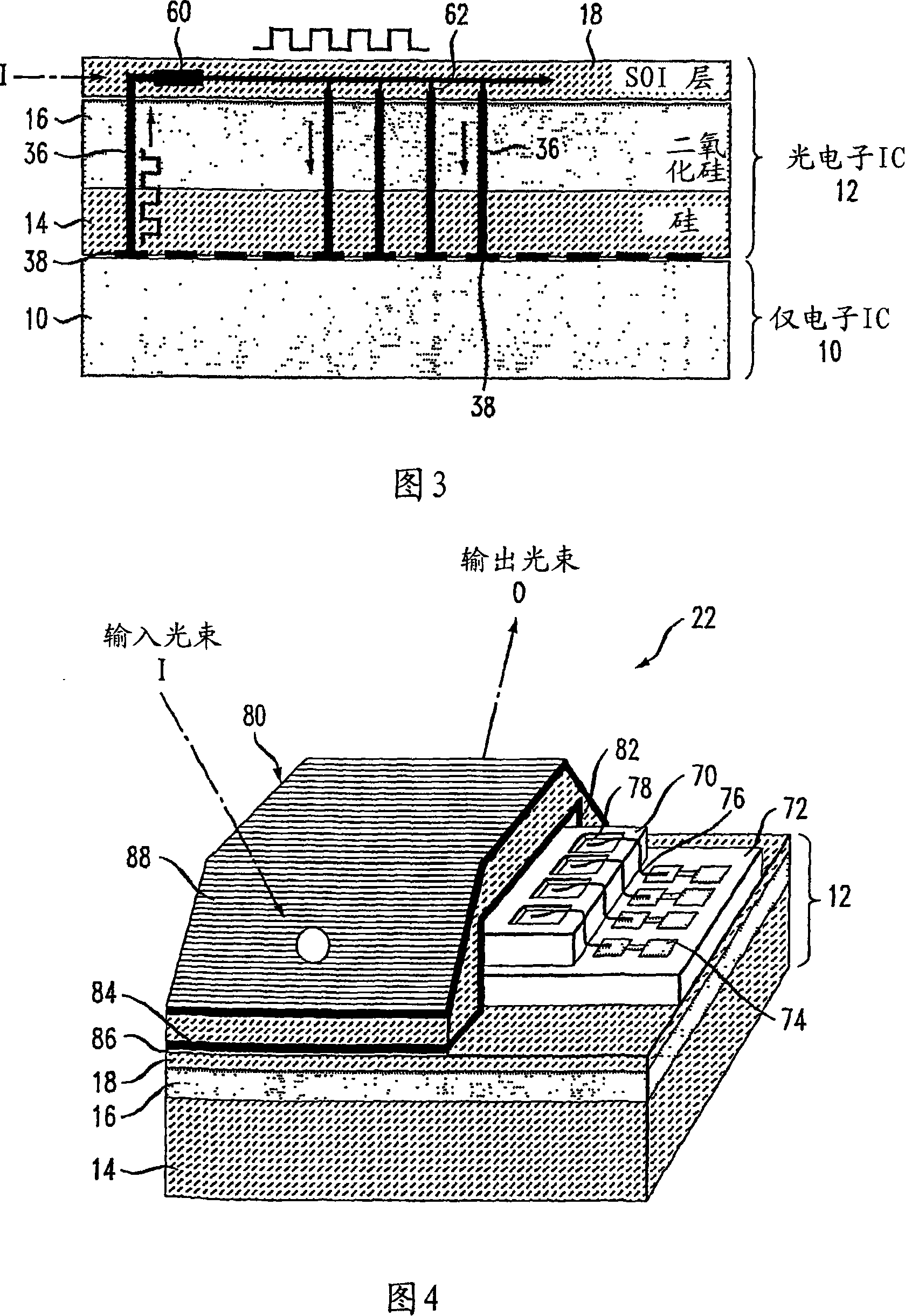

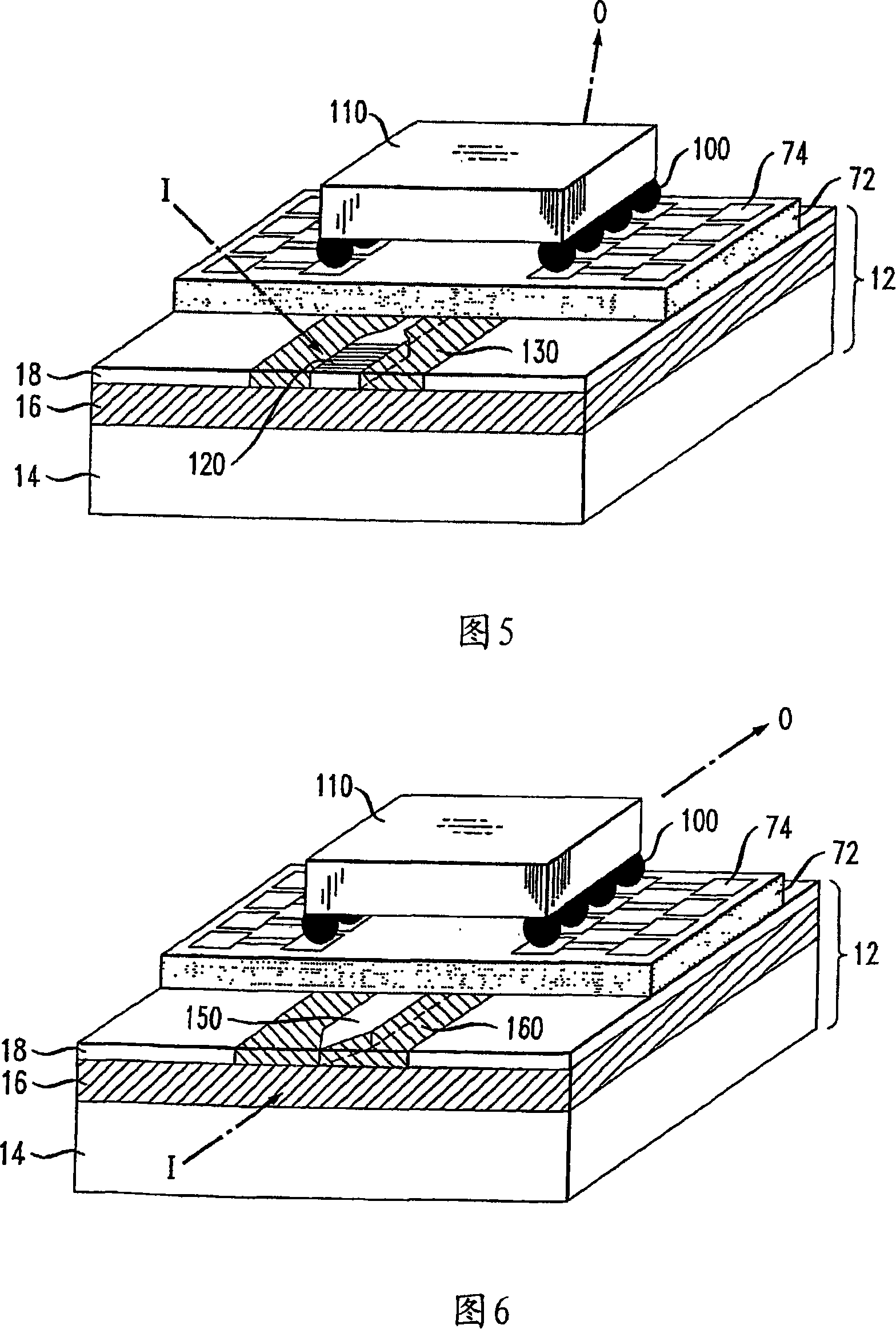

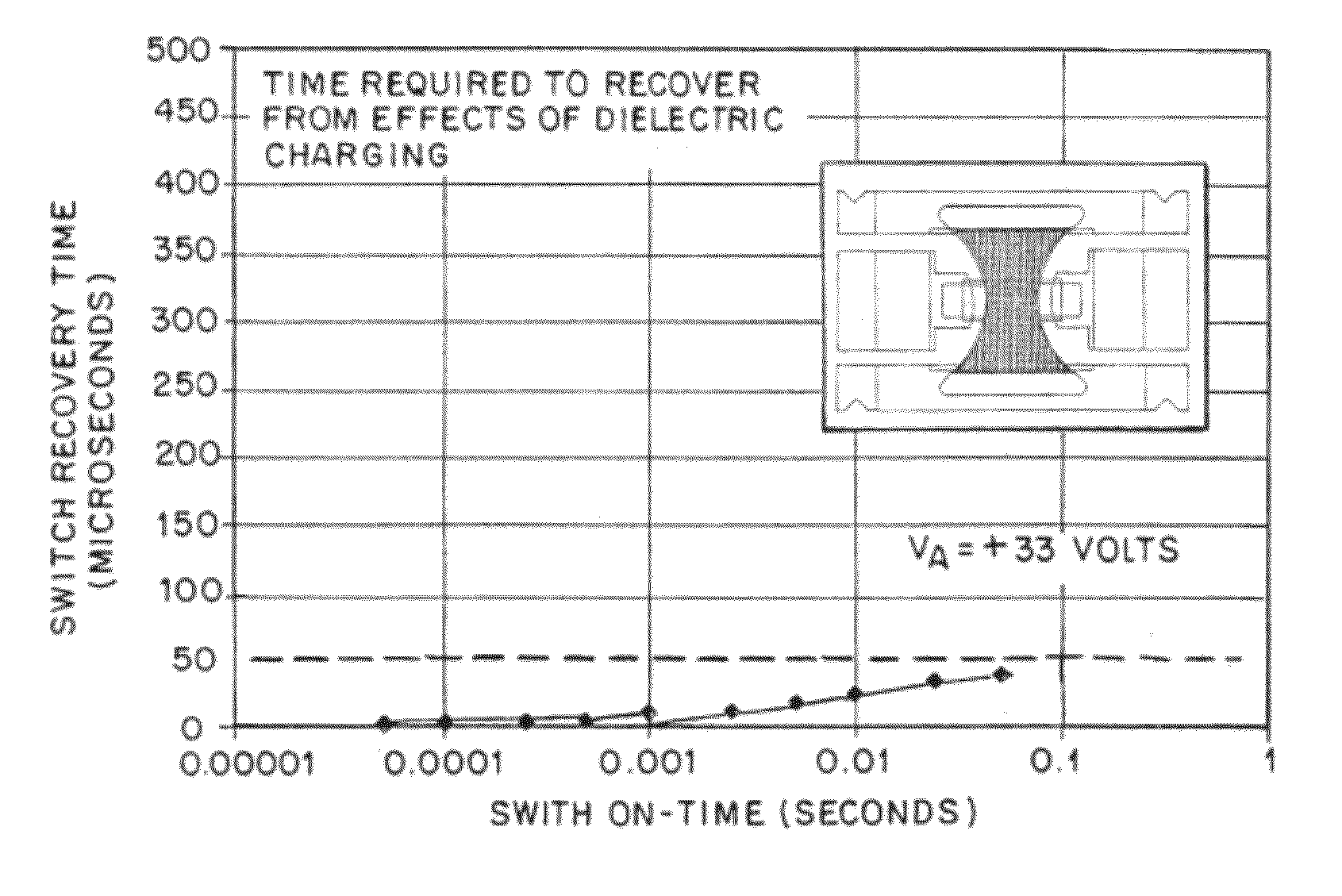

Vertical stacking of multiple integrated circuits including SOI-based optical components

A vertical stack of integrated circuits includes at least one CMOS electronic integrated circuit (IC), an SOI-based opto-electronic integrated circuit structure, and an optical input / output coupling element. A plurality of metalized vias may be formed through the thickness of the stack so that electrical connections can be made between each integrated circuit. Various types of optical input / output coupling can be used, such as prism coupling, gratings, inverse tapers, and the like. By separating the optical and electrical functions onto separate ICs, the functionalities of each may be modified without requiring a re-design of the remaining system. By virtue of using SOI-based opto-electronics with the CMOS electronic ICs, a portion of the SOI structure may be exposed to provide access to the waveguiding SOI layer for optical coupling purposes.

Owner:SIOPTICAL INC

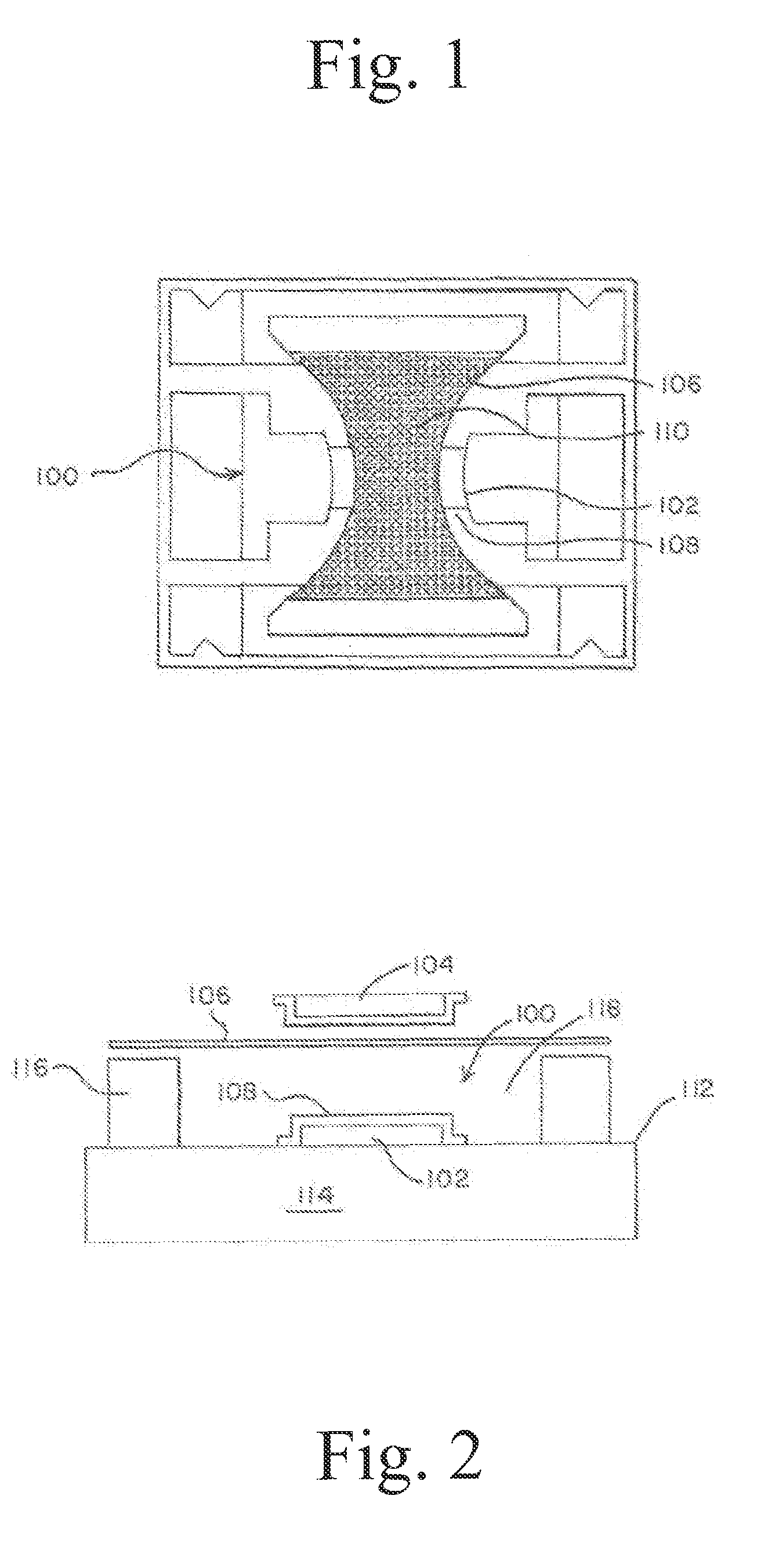

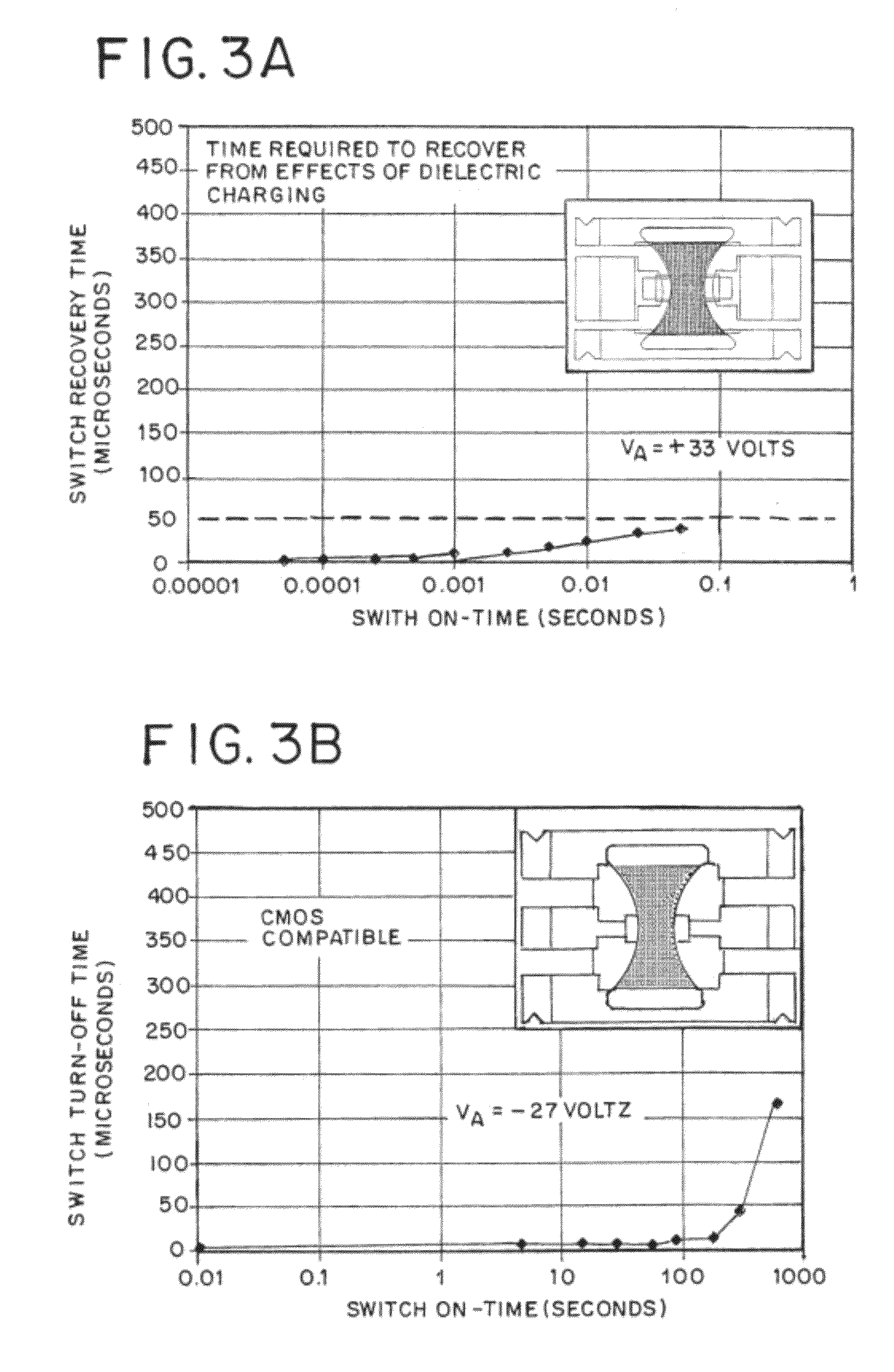

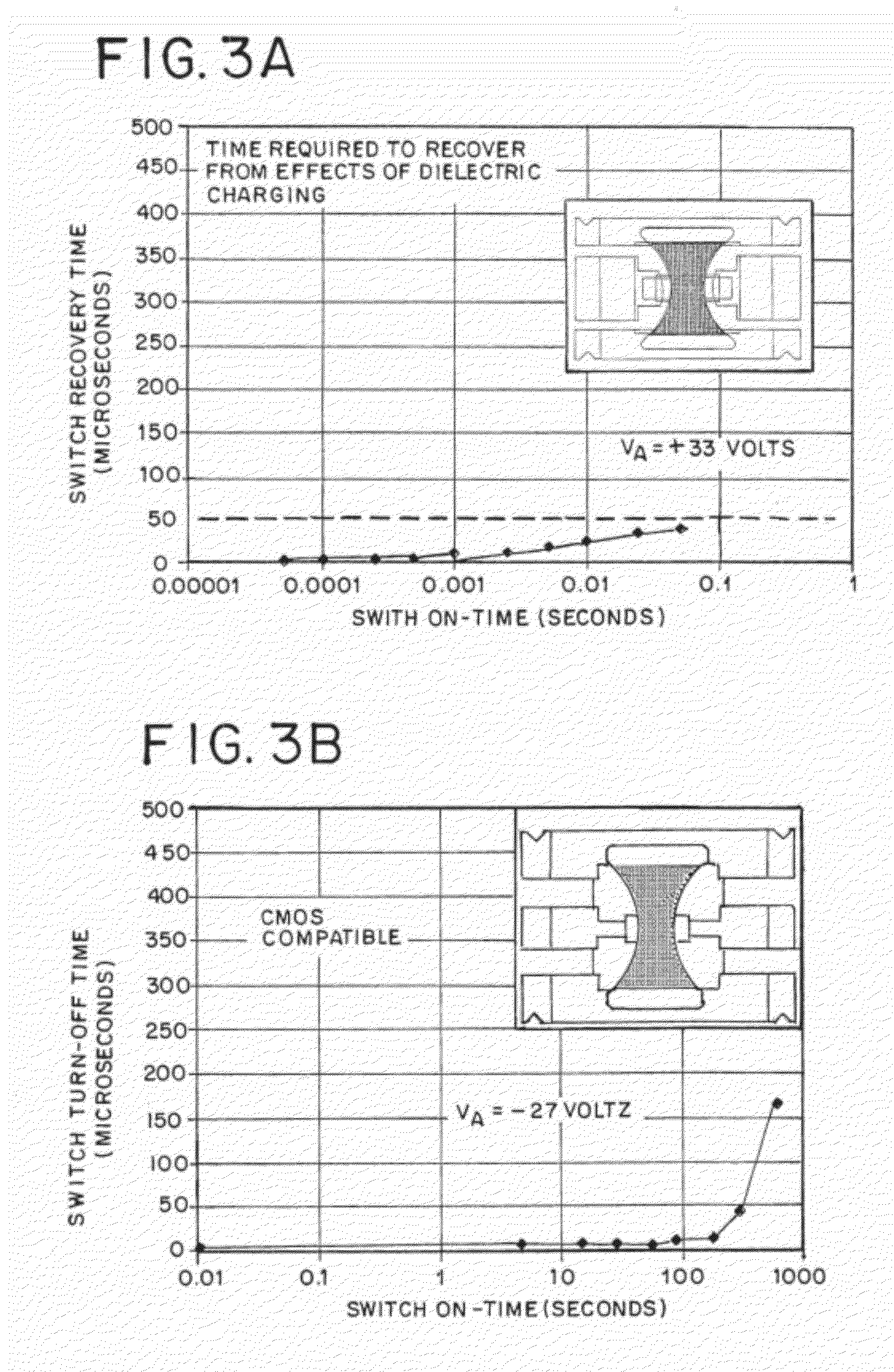

Ultrananocrystalline diamond films with optimized dielectric properties for advanced RF MEMS capacitive switches

ActiveUS8354290B2Reliable and effective and efficientImprove performanceMaterial nanotechnologyElectrostatic/electro-adhesion relaysRadarCmos electronics

An efficient deposition process is provided for fabricating reliable RF MEMS capacitive switches with multilayer ultrananocrystalline (UNCD) films for more rapid recovery, charging and discharging that is effective for more than a billion cycles of operation. Significantly, the deposition process is compatible for integration with CMOS electronics and thereby can provide monolithically integrated RF MEMS capacitive switches for use with CMOS electronic devices, such as for insertion into phase array antennas for radars and other RF communication systems.

Owner:UCHICAGO ARGONNE LLC

Low temperature ceramic microelectromechanical structures

ActiveUS8071411B2Semiconductor/solid-state device detailsSolid-state devicesCmos electronicsEngineering

A method of providing microelectromechanical structures (MEMS) that are compatible with silicon CMOS electronics is provided. The method provides for processing and manufacturing is steps limiting a maximum exposure of an integrated circuit upon which the MEMS is manufactured during MEMS manufacturing to below a temperature wherein CMOS circuitry is adversely affected, for example below 400° C., and sometimes to below 300° C. or 250° C., thereby allowing direct manufacturing of the MEMS devices onto electronic integrated circuits, such as Si CMOS circuits.

Owner:MCGILL UNIV

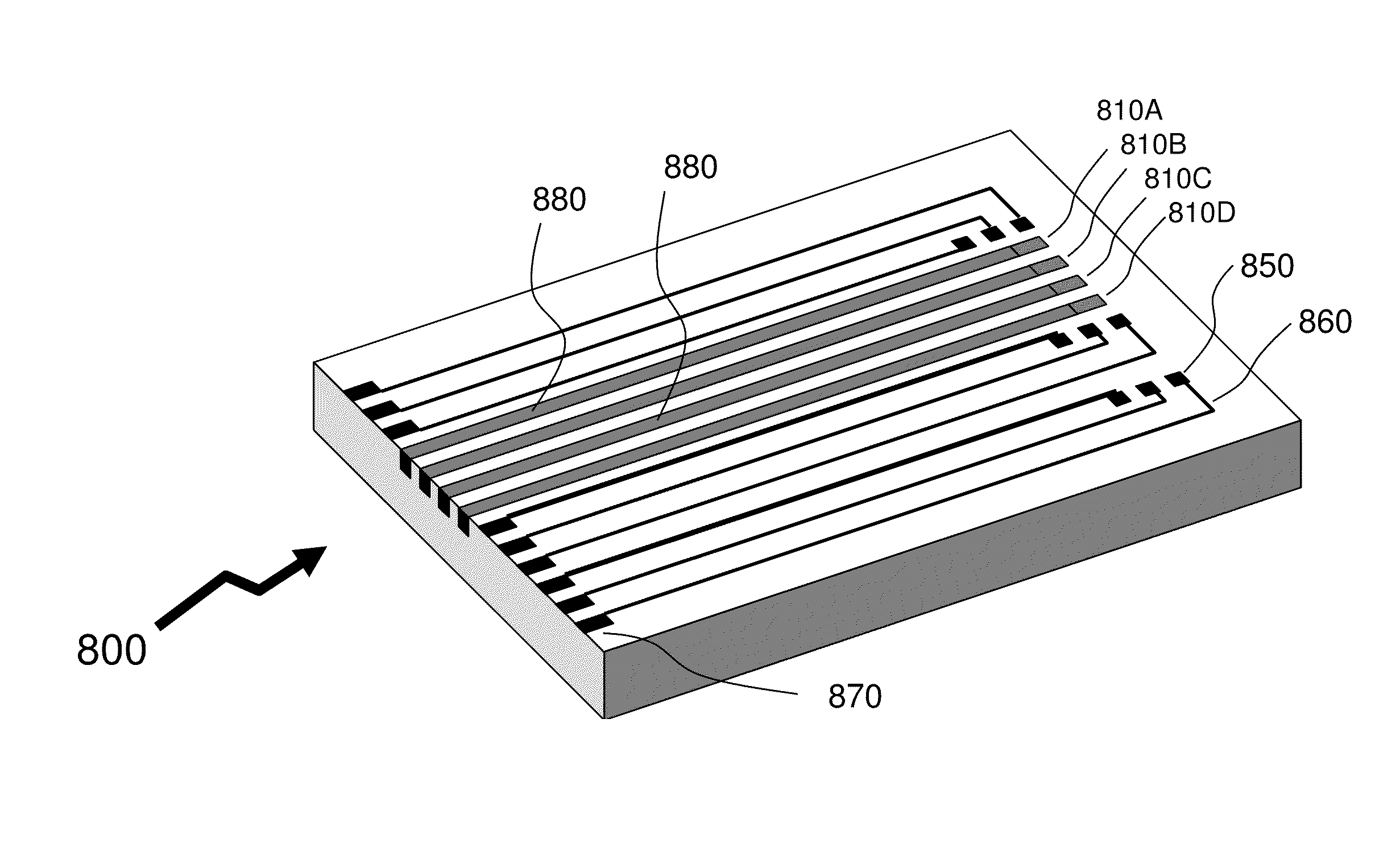

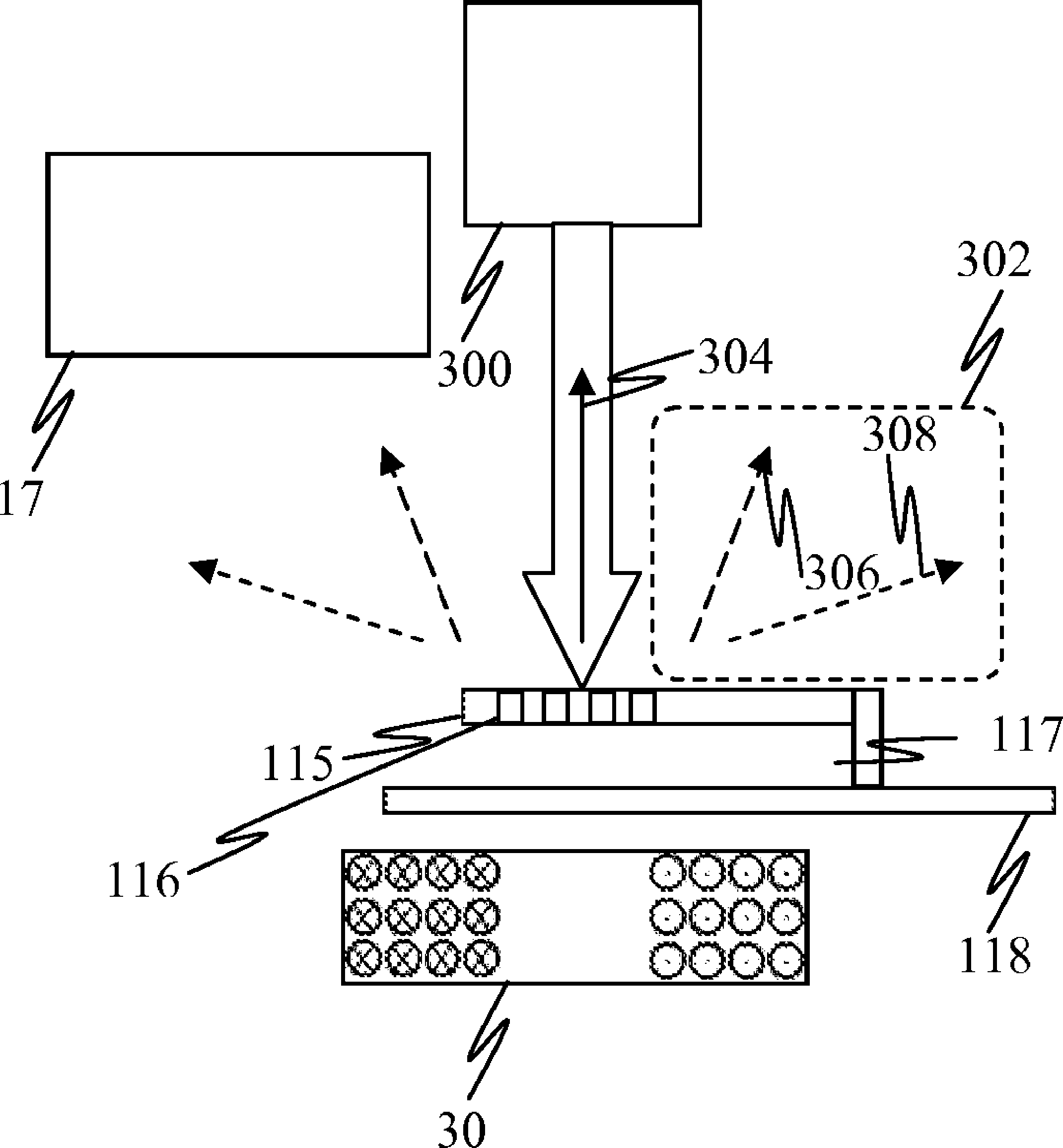

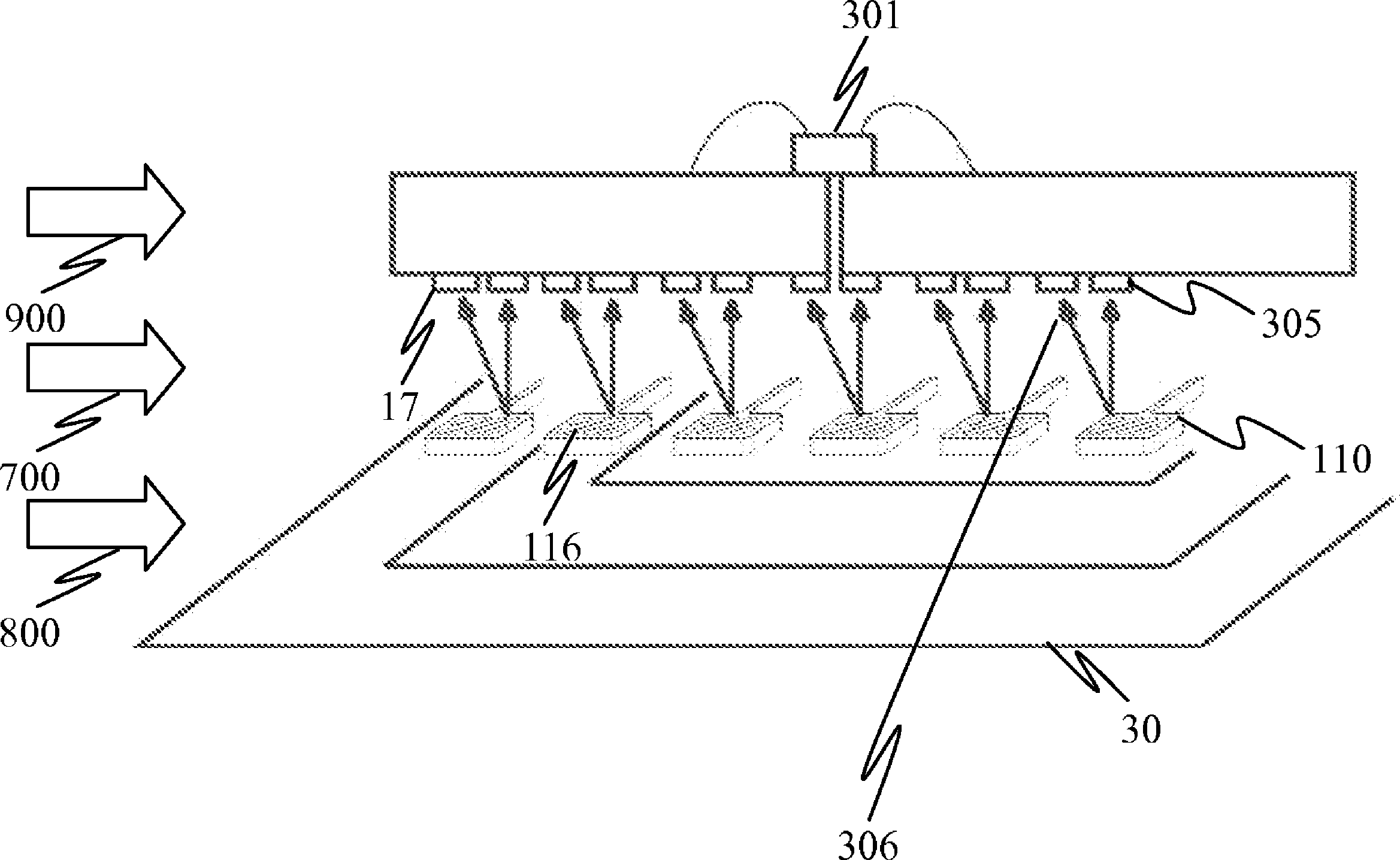

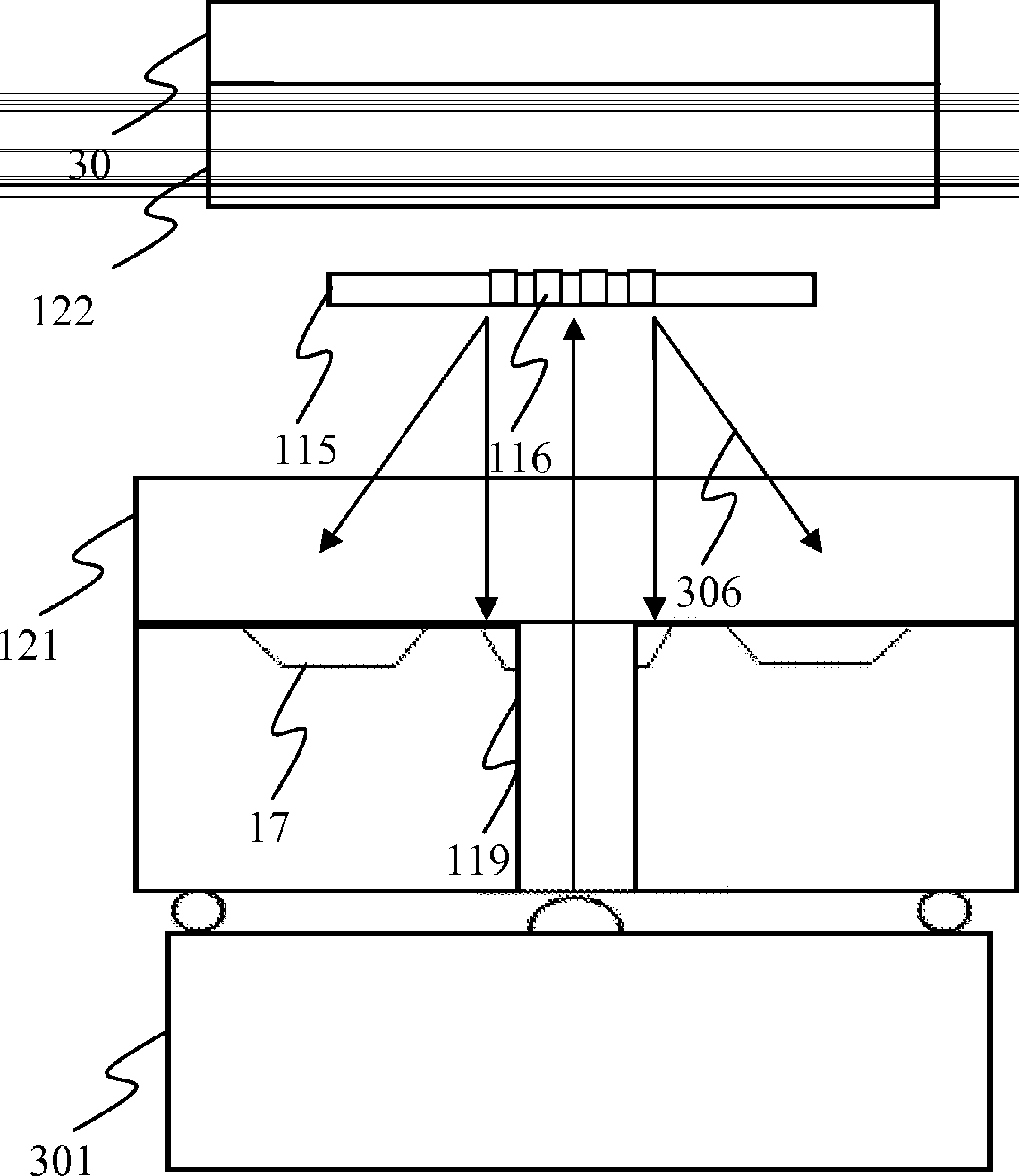

Miniaturized integrated micro electo-mechanical systems (MEMS) optical sensor array

InactiveCN103430018AAnalysing fluids using sonic/ultrasonic/infrasonic wavesMicrostructural devicesSensor arrayMultiplexing

This invention describes a method and apparatus for actuation and multiplexed sensing using an array of sensing elements. The invention can be used for label- free detection of biological and chemical agents in a robust, miniaturized package. The invention integrates photonics, CMOS electronics, and Micro / Nano system technologies and allows multi-analyte sensing in the same package. The preferred actuation method is using magnetic thin films and preferred sensing method is optical using interference means.

Owner:KOC UNIVSI

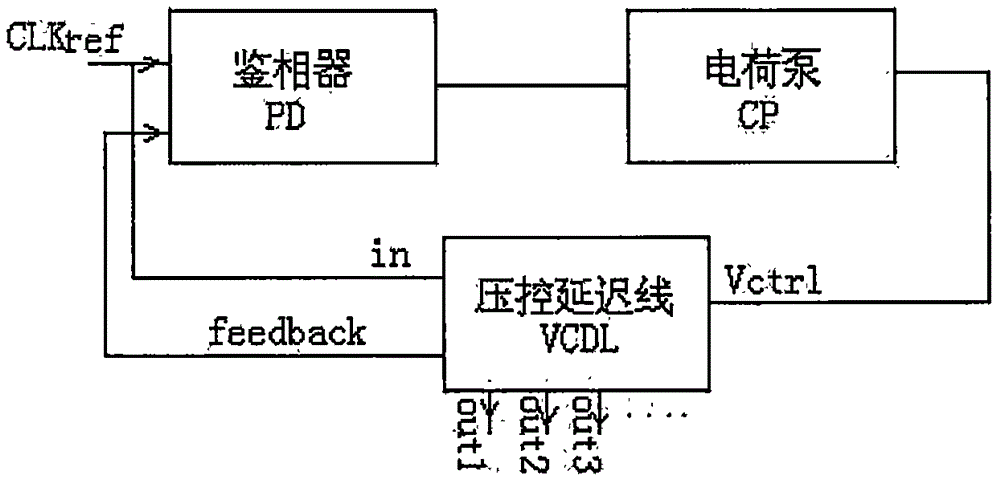

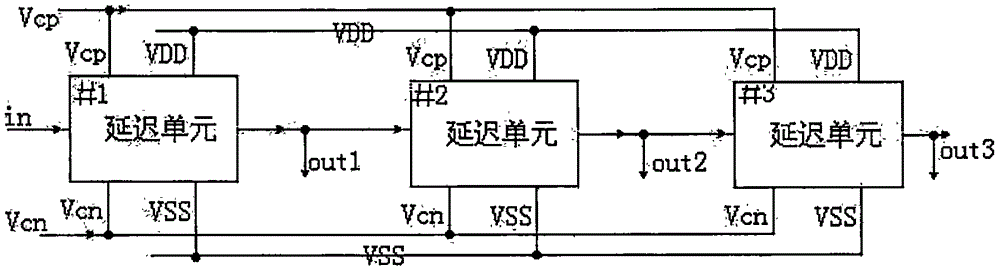

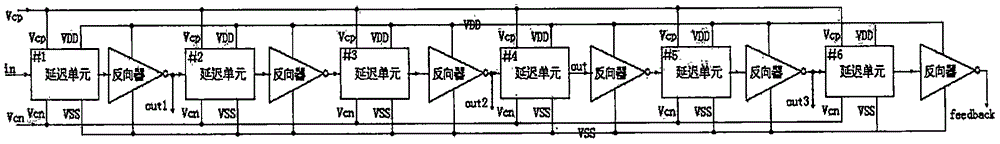

Delay line capable of automatically balancing technological deviations and temperature influences

InactiveCN105871374AReduce latencyIncrease frequency dynamic rangePulse automatic controlPulse manipulationCmos electronicsDelay-locked loop

The present invention is a delay line for automatically balancing process deviation and temperature influence, the delay line is connected in series by a plurality of delay units, each of the delay units includes a delay circuit and an inversion circuit; transistors P1, P2, P3, P4 is a PMOS transistor of the same size, and transistors N1, N2, N3, and N4 are NMOS transistors of the same size; the transistors P1, P3, N1, and N3 form one of the delay circuits; the transistors P2, P4, N2, and N4 One of the reverse circuits is formed. The delay line designed by the method of the present invention can automatically adjust the high and low level duty ratio of the delay unit, so that the high and low level duty ratio of the signal is approximately 1 / 2; the delay line designed by the present invention can effectively increase the frequency of the input signal The dynamic range can reduce the locking time of the delay-locked loop; the delay line designed by the invention has a simple structure and adopts standard CMOS electronic devices, which can effectively save chip area and cost.

Owner:深圳市芯卓微科技有限公司

Ultrananocrystalline Diamond Films with Optimized Dielectric Properties for Advanced RF MEMS Capacitive Switches

ActiveUS20120193684A1Reliable and effective and efficientImprove performanceMaterial nanotechnologyElectrostatic/electro-adhesion relaysCmos electronicsDiamond thin film

An efficient deposition process is provided for fabricating reliable RF MEMS capacitive switches with multilayer ultrananocrystalline (UNCD) films for more rapid recovery, charging and discharging that is effective for more than a billion cycles of operation. Significantly, the deposition process is compatible for integration with CMOS electronics and thereby can provide monolithically integrated RF MEMS capacitive switches for use with CMOS electronic devices, such as for insertion into phase array antennas for radars and other RF communication systems.

Owner:UCHICAGO ARGONNE LLC

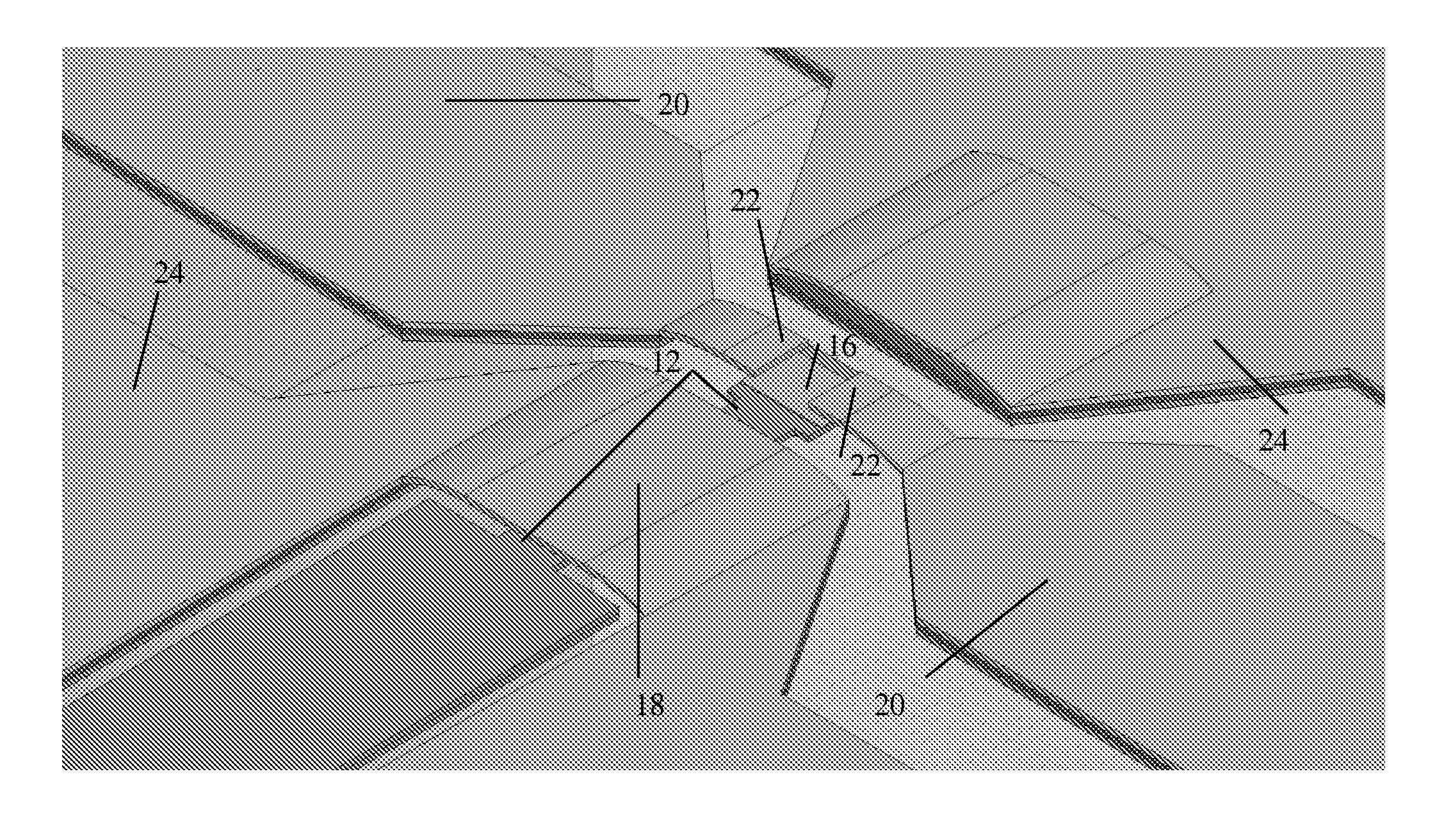

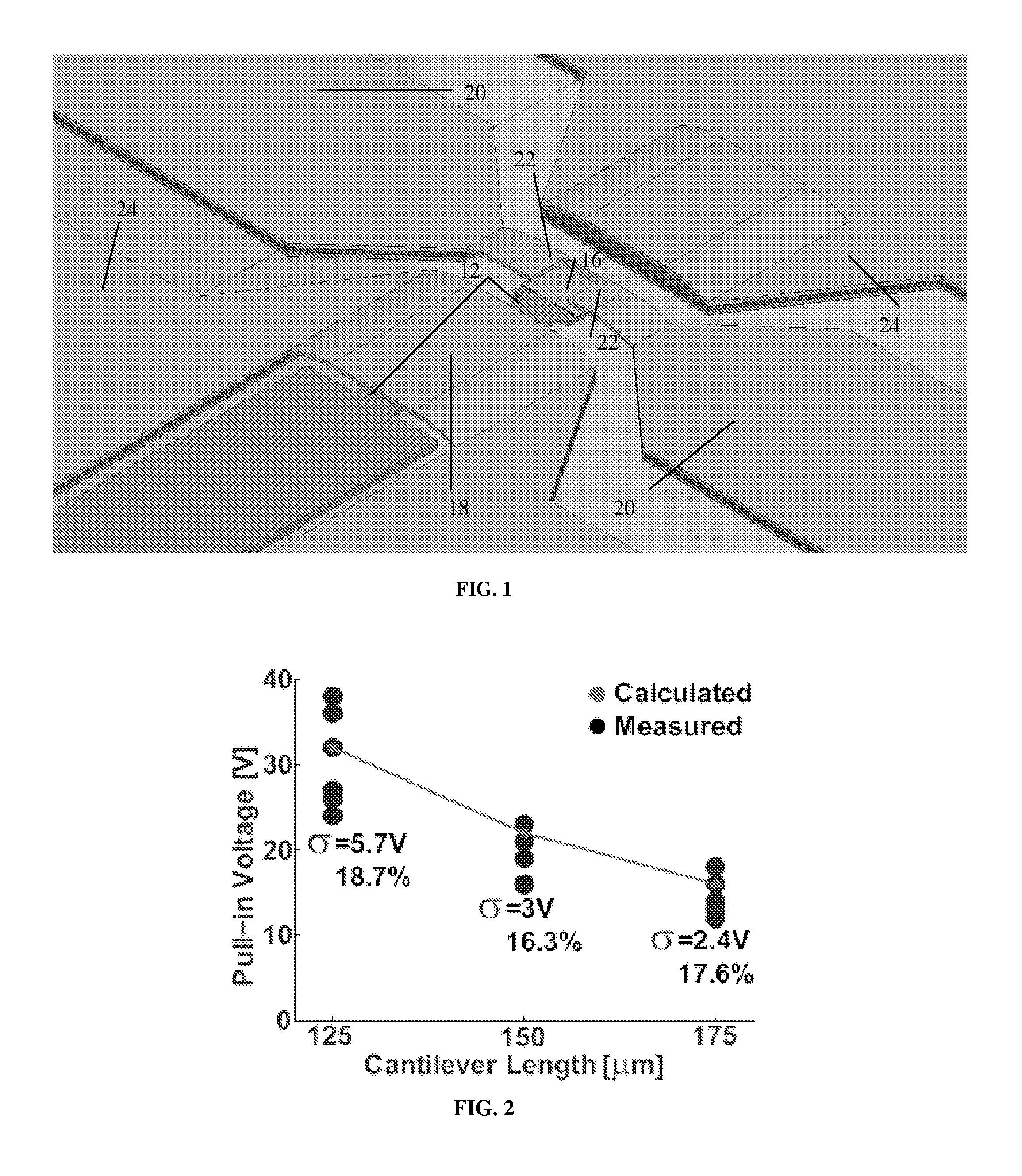

Low-cost process-independent RF MEMS switch

InactiveUS20100263999A1High yieldIncrease variabilityElectrostatic/electro-adhesion relaysSemiconductor/solid-state device manufacturingCmos electronicsSingle crystal

A radio frequency (RF) micro-electro-mechanical systems (MEMS) switch and high yield manufacturing method. The switch can be fabricated with very high yield despite the high variability of the manufacturing process parameters. The switch is fabricated with monocrystalline material, e.g., silicon, as the moving portion. The switch fabrication process is compatible with CMOS electronics fabricated on Silicon-on-Insulator (SOI) substrates. The switch comprises a movable portion having conductive portion selectively positioned with a bias voltage to conductively bridge a gap in a signal line.

Owner:PURDUE RES FOUND INC

Relaxed SiGe platform for high speed CMOS electronics and high speed analog circuits

InactiveUS7501351B2Minimal surface roughnessImprove featuresTransistorSemiconductor/solid-state device manufacturingState of artMOSFET

Structures and methods for fabricating high speed digital, analog, and combined digital / analog systems using planarized relaxed SiGe as the materials platform. The relaxed SiGe allows for a plethora of strained Si layers that possess enhanced electronic properties. By allowing the MOSFET channel to be either at the surface or buried, one can create high-speed digital and / or analog circuits. The planarization before the device epitaxial layers are deposited ensures a flat surface for state-of-the-art lithography.

Owner:TAIWAN SEMICON MFG CO LTD

Methods and devices for microelectromechanical resonators

ActiveUS20200407218A1Reduce restrictionsImpedence networksDecorative surface effectsCmos electronicsMems sensors

MEMS based sensors, particularly capacitive sensors, potentially can address critical considerations for users including accuracy, repeatability, long-term stability, ease of calibration, resistance to chemical and physical contaminants, size, packaging, and cost effectiveness. Accordingly, it would be beneficial to exploit MEMS processes that allow for manufacturability and integration of resonator elements into cavities within the MEMS sensor that are at low pressure allowing high quality factor resonators and absolute pressure sensors to be implemented. Embodiments of the invention provide capacitive sensors and MEMS elements that can be implemented directly above silicon CMOS electronics.

Owner:MY01 IP HLDG INC

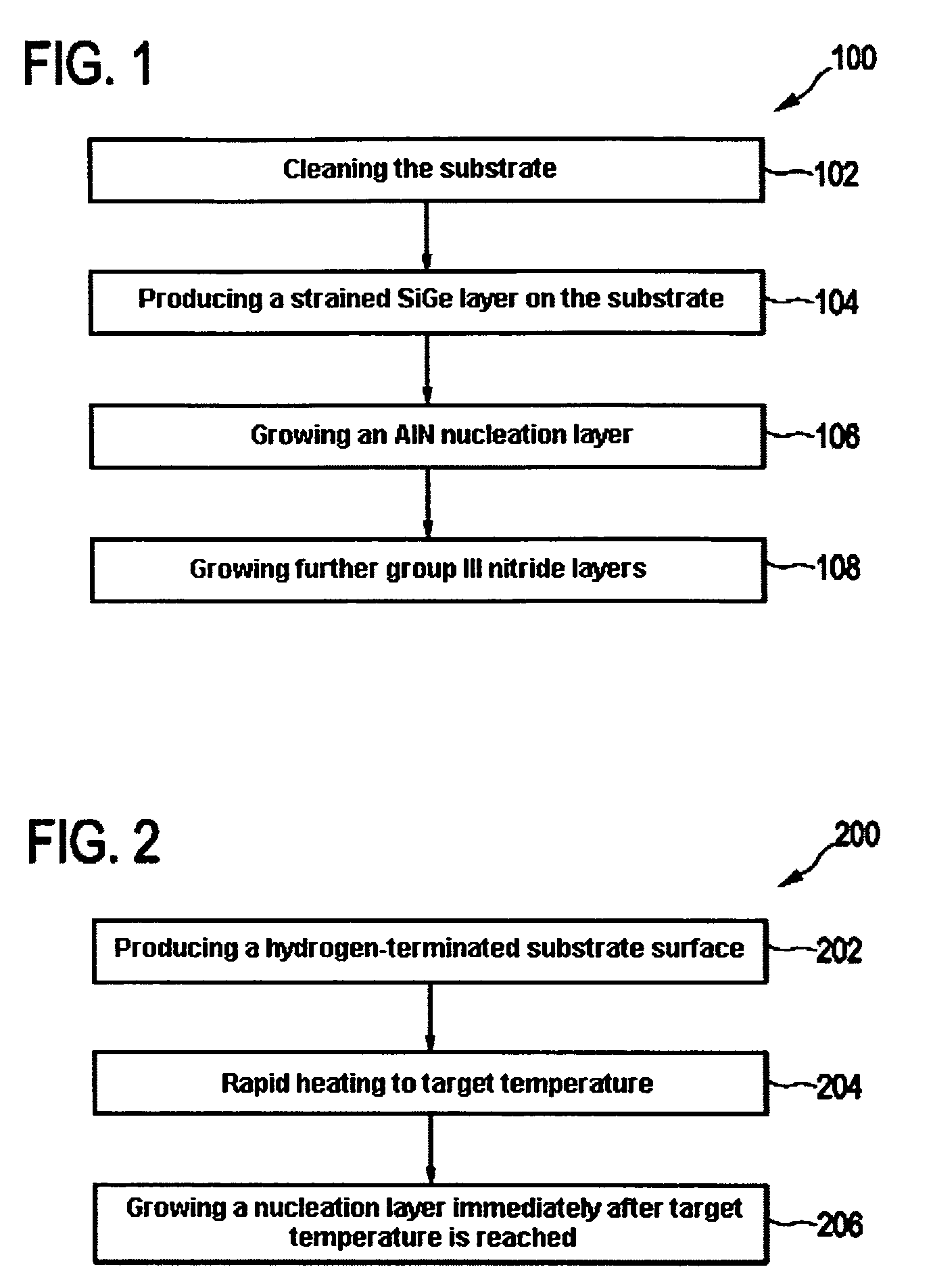

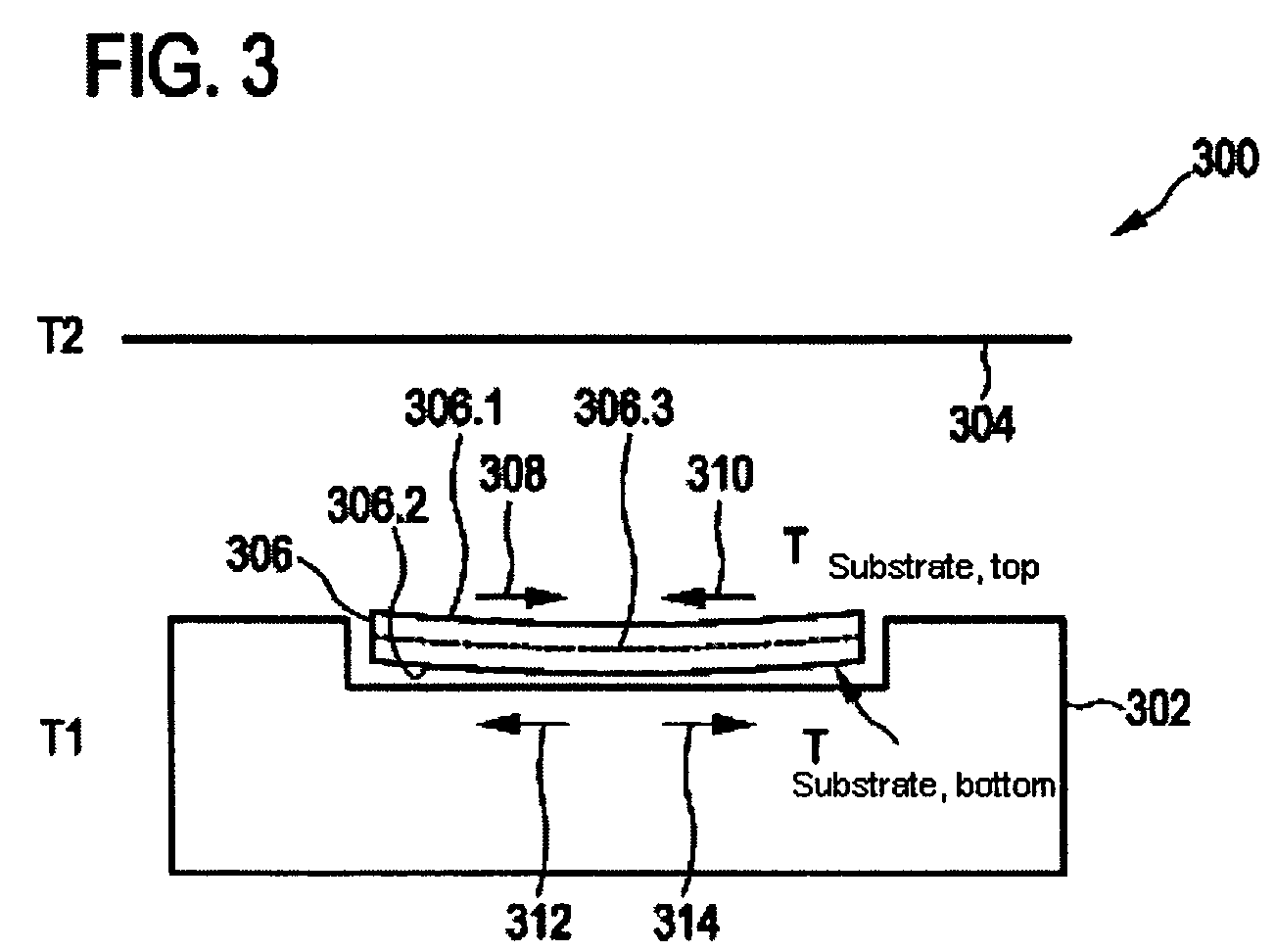

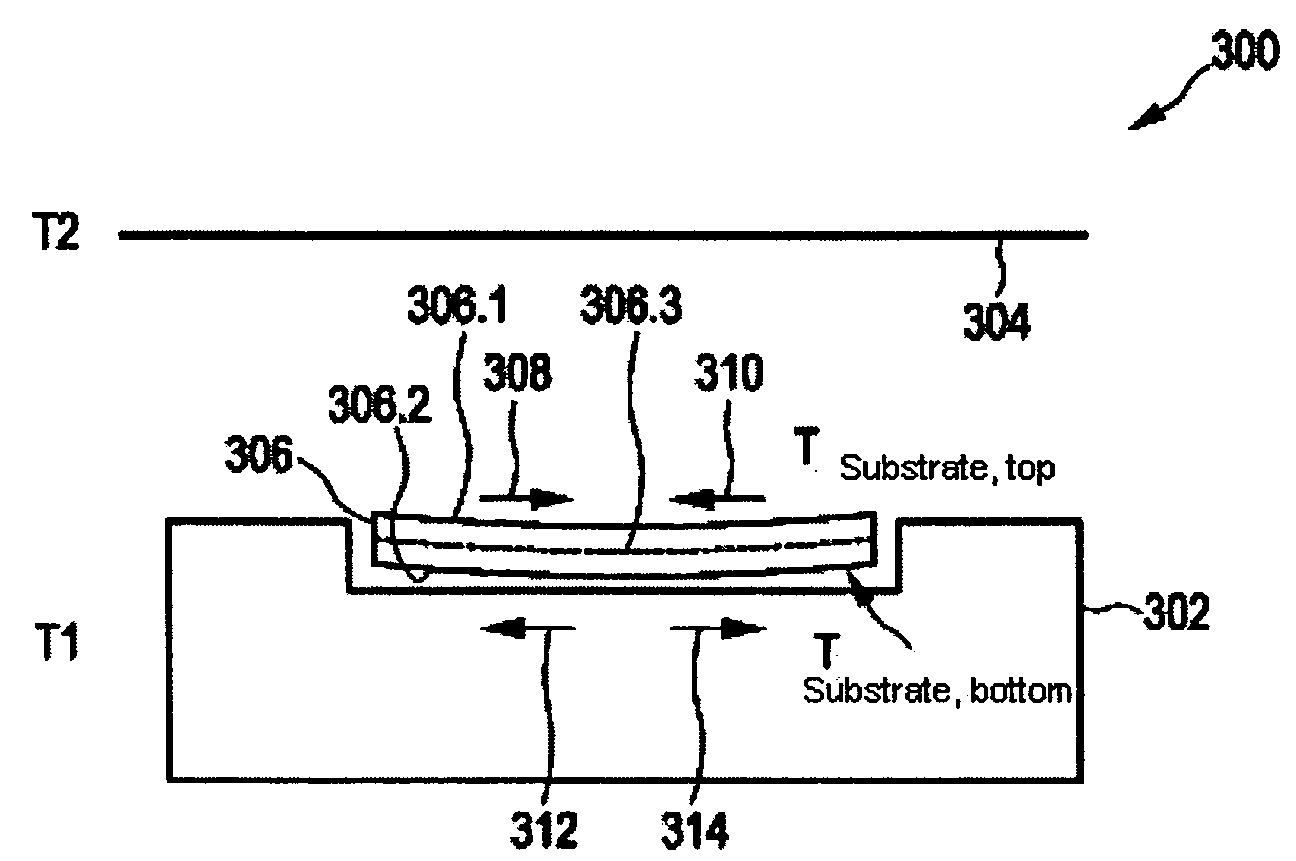

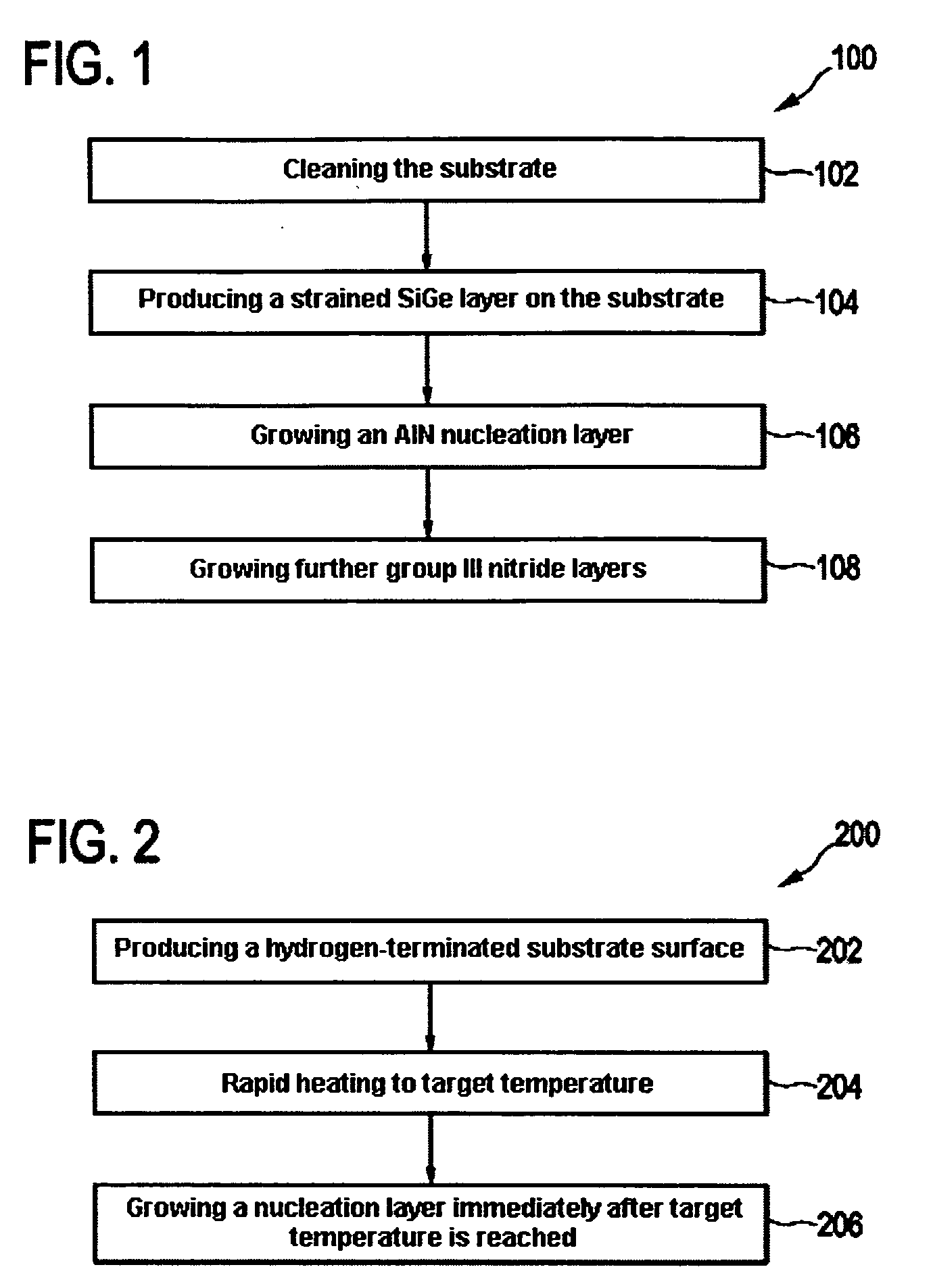

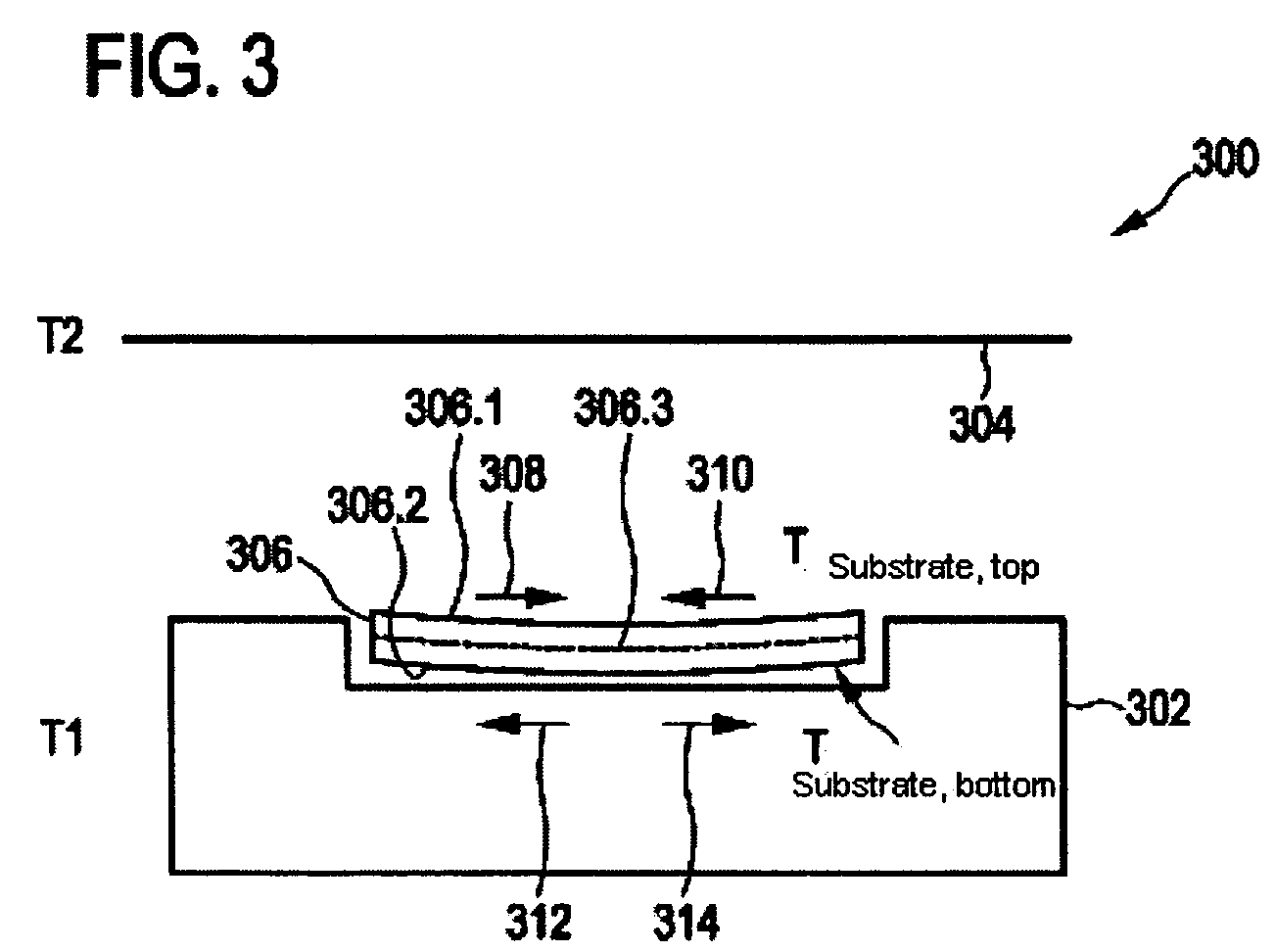

Epitaxial group III nitride layer on (001)-oriented group IV semiconductor

InactiveUS7935987B2Small misorientationsImprove crystal qualitySemiconductor/solid-state device manufacturingSemiconductor devicesCmos electronicsSurface structure

Group III nitride layers have a wide range of uses in electronics and optoelectronics. Such layers are generally grown on substrates such as sapphire, SiC and recently Si(111). For the purpose inter alia of integration with Si-CMOS electronics, growth on Si(001) is indicated, which is possible only with difficulty because of the different symmetries and is currently limited solely to misoriented Si(001) substrates, which restricts the range of use. In addition, the layer quality is not at present equal to that produced on Si(111) material. Growth on exactly oriented Si(001) and an improvement in material quality can now be simply achieved by a modification of the surface structure possible with a plurality of methods.

Owner:AZZURRO SEMICON

Epitaxial group III nitride layer on (001)-oriented group IV semiconductor

InactiveUS20080157123A1Small misorientationsImprove crystal qualitySemiconductor/solid-state device manufacturingSemiconductor devicesCmos electronicsSurface structure

Group III nitride layers have a wide range of uses in electronics and optoelectronics. Such layers are generally grown on substrates such as sapphire, SiC and recently Si(111). For the purpose inter alia of integration with Si-CMOS electronics, growth on Si(001) is indicated, which is possible only with difficulty because of the different symmetries and is currently limited solely to misoriented Si(001) substrates, which restricts the range of use. In addition, the layer quality is not at present equal to that produced on Si(111) material. Growth on exactly oriented Si(001) and an improvement in material quality can now be simply achieved by a modification of the surface structure possible with a plurality of methods.

Owner:AZZURRO SEMICON

Methods and systems for humidity and pressure sensor overlay integration with electronics

ActiveUS10107773B2Material capacitanceFluid pressure measurement using capacitance variationCmos electronicsElectric equipment

Capacitive sensors and MEMS elements that can be implemented directly above silicon CMOS electronics are disclosed. A capacitive based sensor is disposed over a first predetermined portion of a wafer that includes at least a first ceramic element providing protection for the final capacitive based sensor and self-aligned processing during its manufacturing.

Owner:MEMS VISION INT

Methods and devices for microelectromechanical resonators

MEMS based sensors, particularly capacitive sensors, potentially can address critical considerations for users including accuracy, repeatability, long-term stability, ease of calibration, resistance to chemical and physical contaminants, size, packaging, and cost effectiveness. Accordingly, it would be beneficial to exploit MEMS processes that allow for manufacturability and integration of resonator elements into cavities within the MEMS sensor that are at low pressure allowing high quality factor resonators and absolute pressure sensors to be implemented. Embodiments of the invention provide capacitive sensors and MEMS elements that can be implemented directly above silicon CMOS electronics.

Owner:MY01 IP HLDG INC