Solver for hardware based computing

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

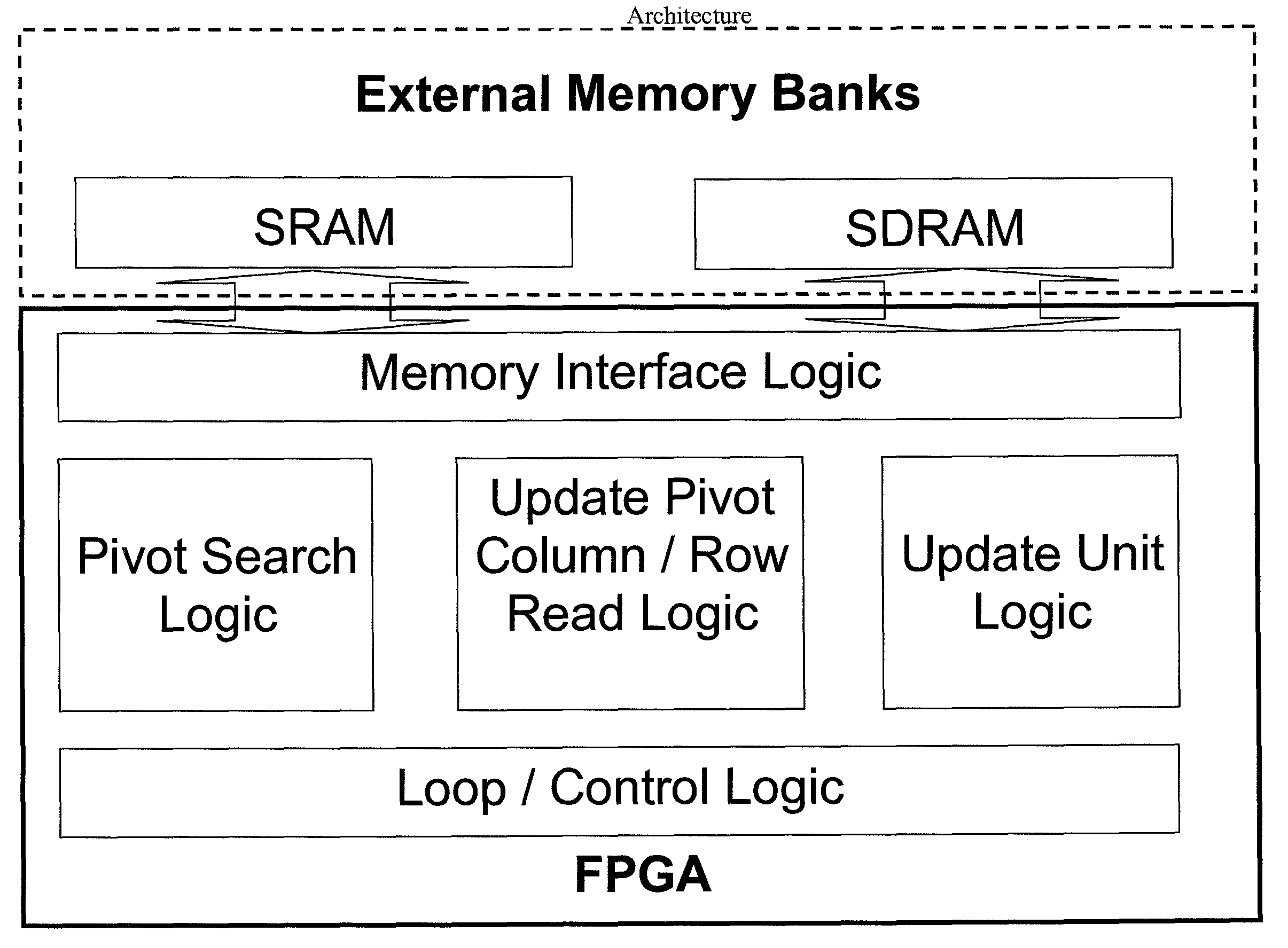

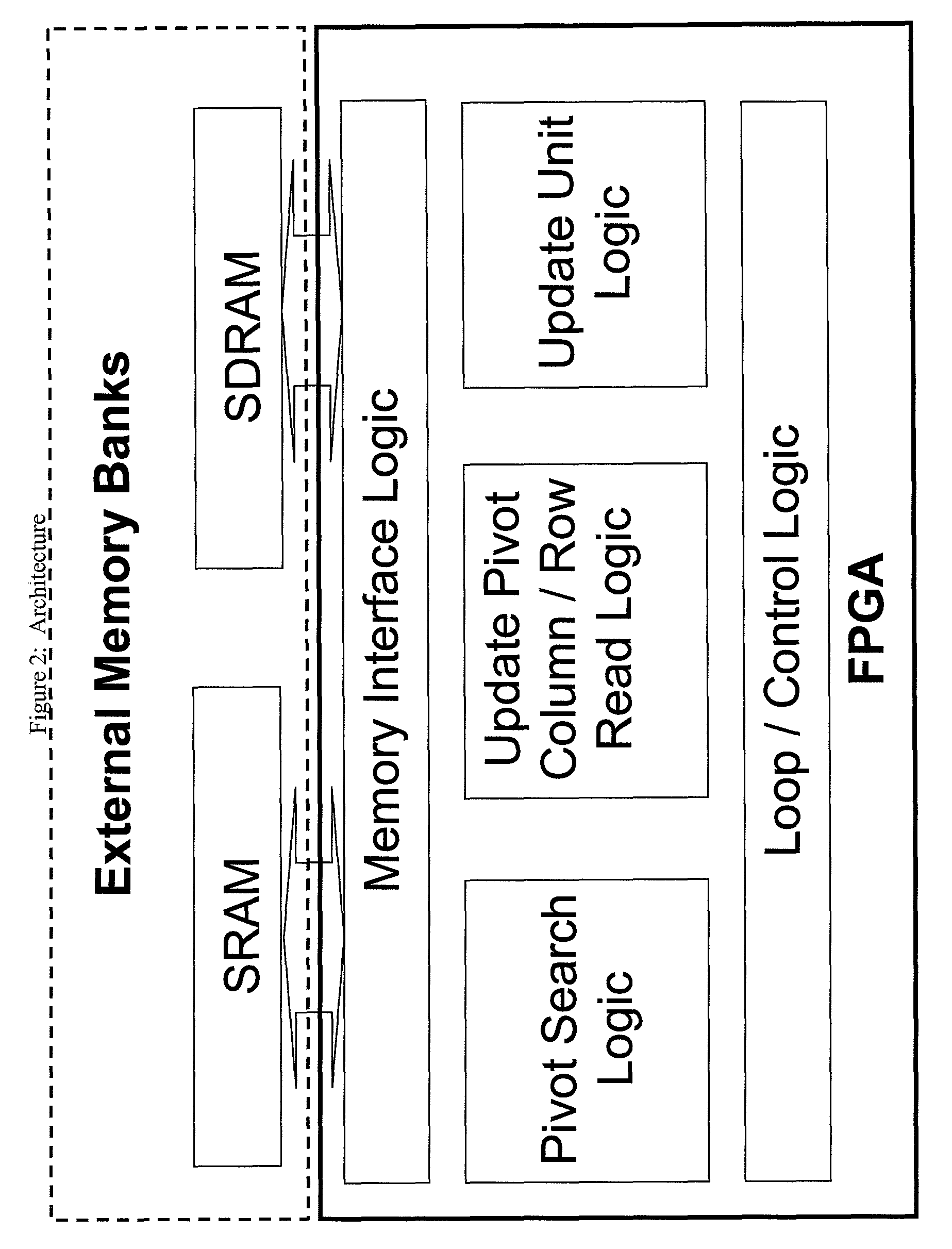

[0063]In the current invention, application-specific hardware is employed to reduce the computation time for the solution of the sparse linear systems arising in complex computations. The use of special-purpose hardware reduces the overhead costs, better utilizes floating-point hardware, and provides fine-grained parallelism. The use of Field Programmable Gate Arrays (FPGA) provides a convenient platform to design and implement such hardware. By building hardware that is specifically designed to solve the sparse matrices found in complex calculations, such as power system calculations, rather than utilizing general-purpose processors and parallel processing, the present invention significantly improves the efficiency of the linear solver and hence reduces the computing time compared to traditional platforms.

[0064]Thus, one aspect of the present invention relates to hardware for the direct solution of sparse linear systems. The hardware design takes advantage of properties of the mat...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More