Low-dropout linear regulator circuit with high power supply rejection ratio

A high power supply rejection ratio, low dropout linear technology, applied in instruments, regulating electrical variables, control/regulating systems, etc., can solve the problems of low power supply rejection, difficult to achieve power supply rejection ratio, and difficult to meet the requirements of on-chip system indicators. Wide application range and good power supply rejection ratio

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0043] The technical solutions of the present invention will be further described through specific embodiments below in conjunction with the accompanying drawings.

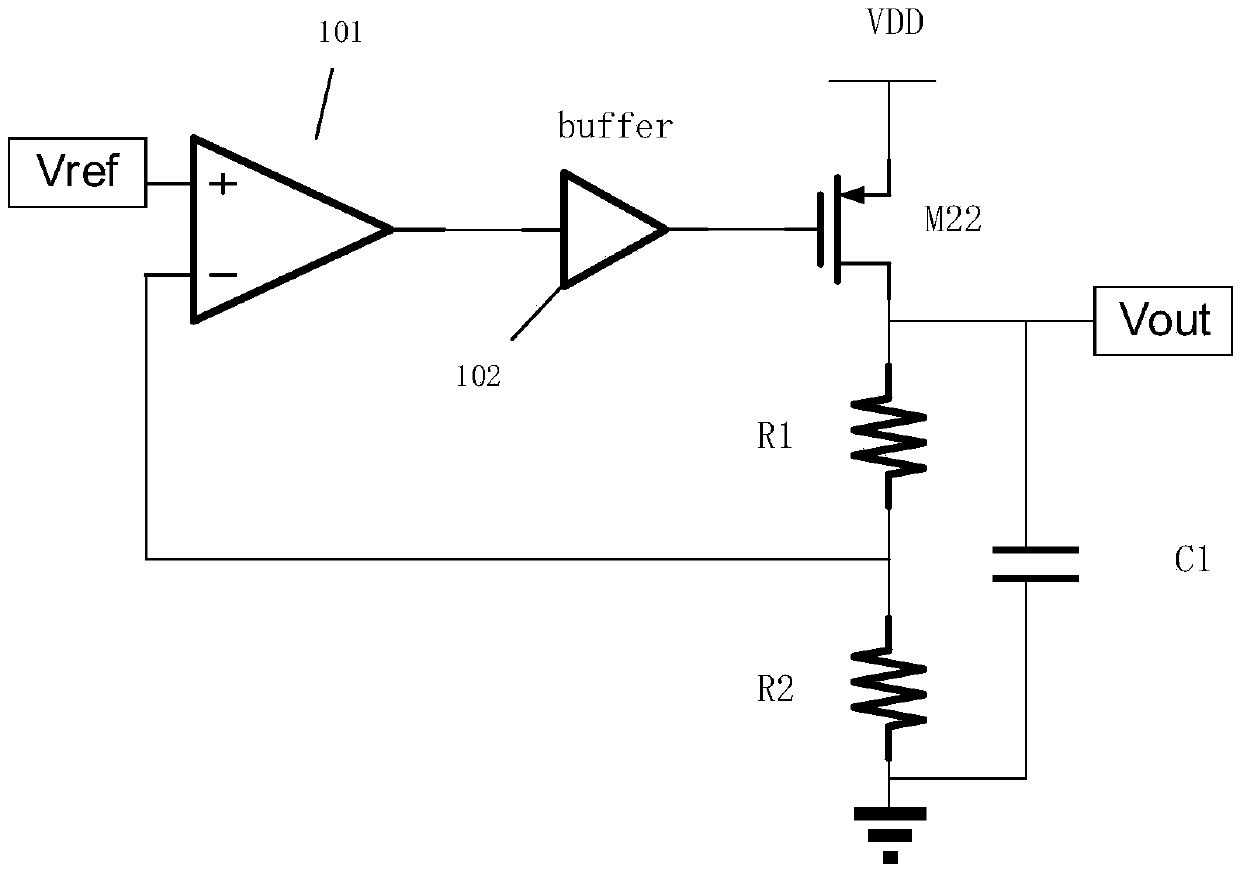

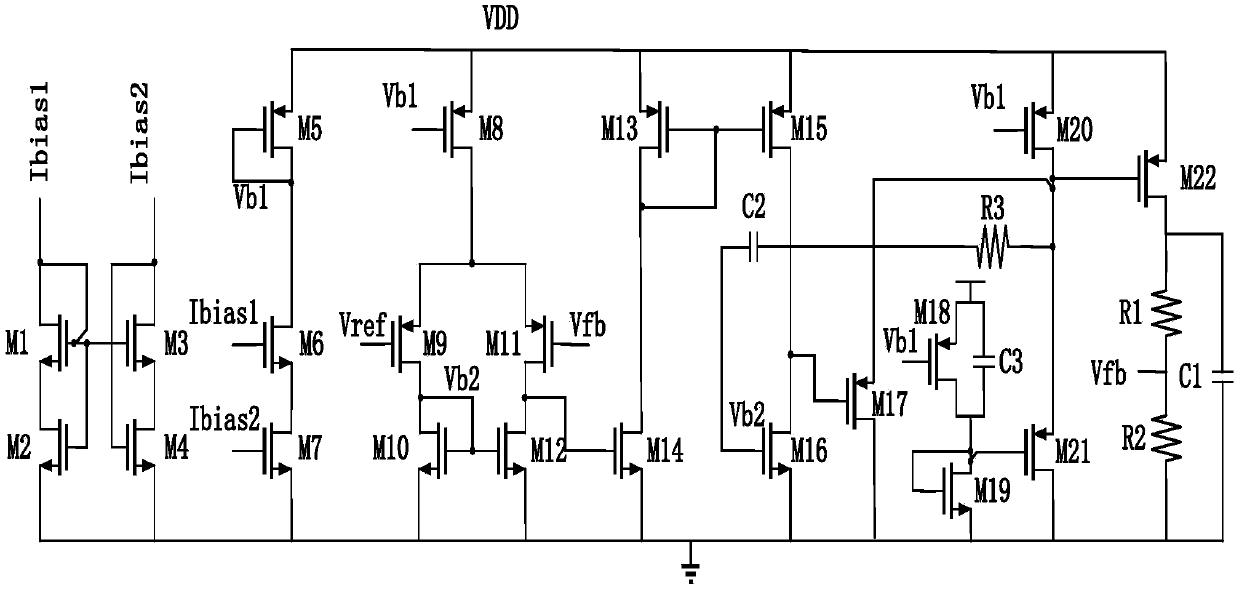

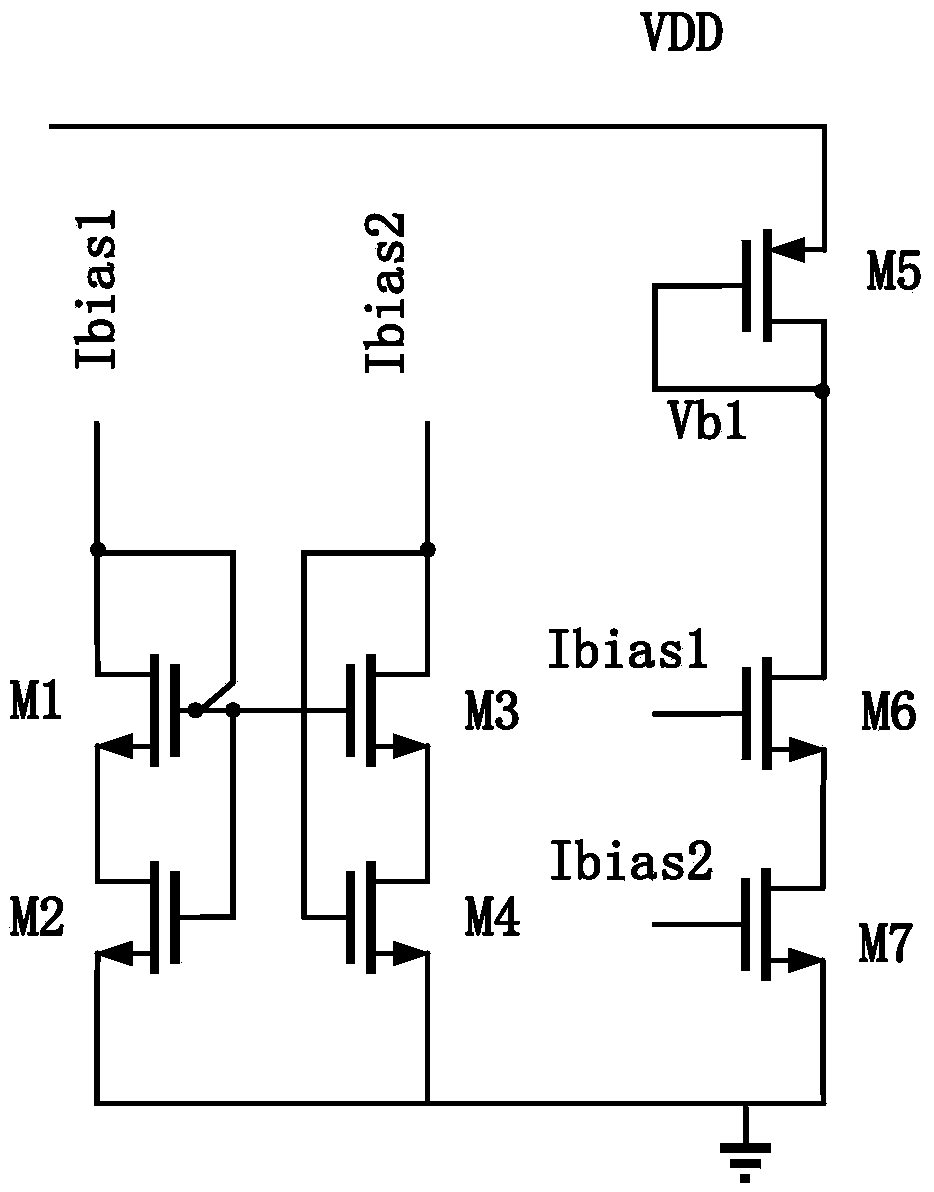

[0044] like figure 1 Shown is a topological structure diagram of a high power supply rejection ratio low dropout linear regulator circuit proposed by the present invention, including a negative feedback loop composed of a bias module, an error amplifier, a buffer and an output stage. The output stage consists of power transistors and feedback resistors, such as figure 1 and figure 2 As shown, the feedback resistor includes the first resistor R1 and the second resistor R2. The first resistor R1 and the second resistor R2 are the same type of resistors. The value of the feedback resistor should fully consider the current required by the load; the power tube width-to-length ratio It must be large enough to ensure sufficient current extraction. The power tube can be a PMOS tube or an NMOS tube. Taking the power tub...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More