Thyristor with high hold voltage and low triggering voltage ESD (electronstatic discharge) characteristic

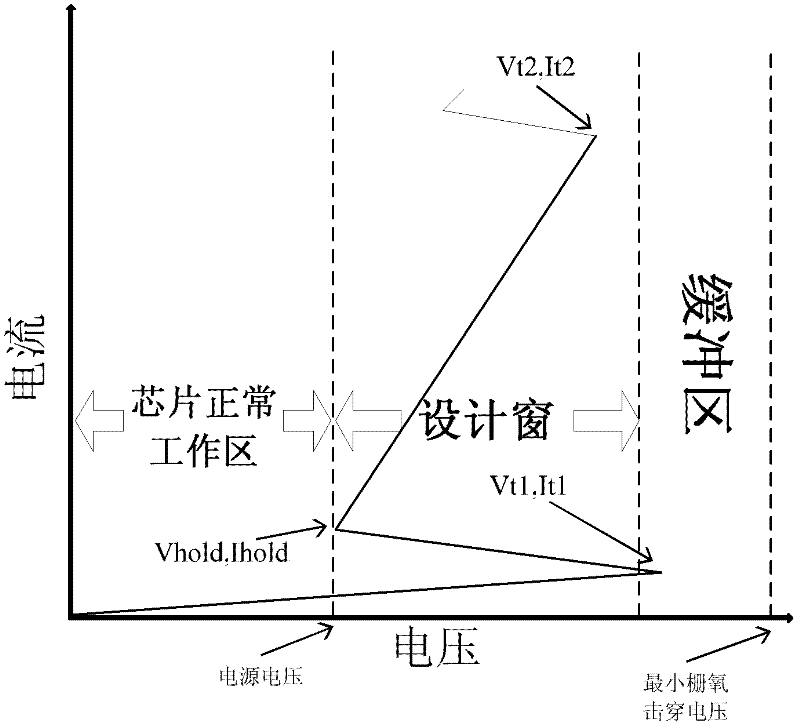

A low trigger voltage, high sustain voltage technology, applied in thyristors, circuits, diodes, etc., can solve the problem that the sustain voltage does not meet the design requirements of ESD clamp protection devices, and achieve the effect of reducing the trigger voltage and increasing the sustain voltage.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

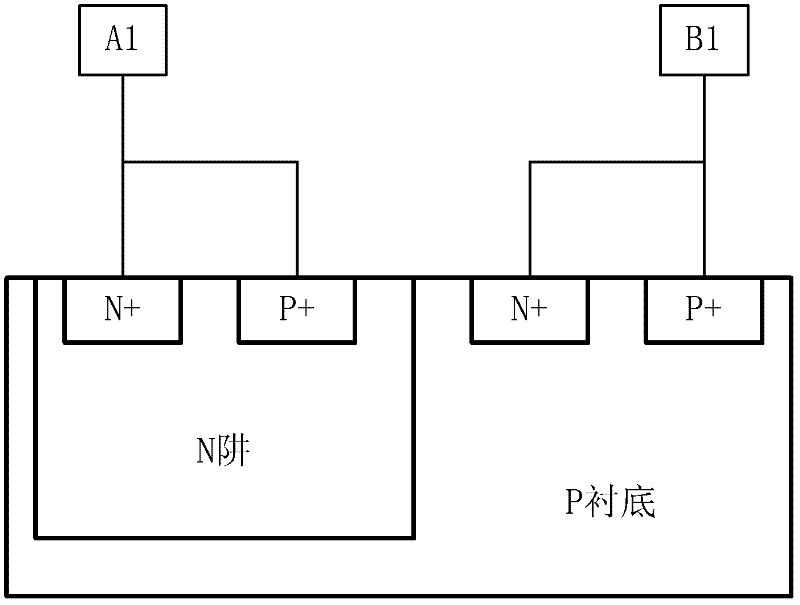

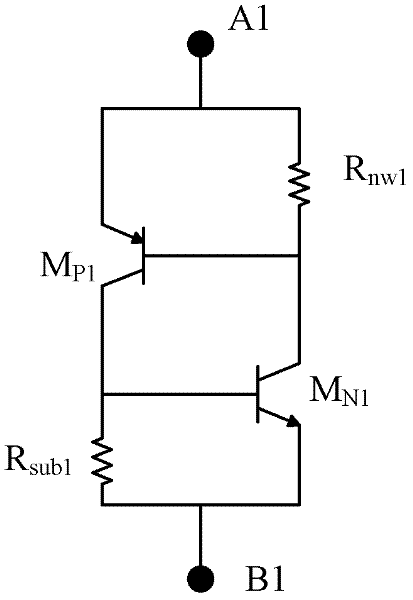

[0041] Figure 7 It is a specific structural schematic diagram of a thyristor with high sustain voltage and low trigger voltage ESD characteristics according to the first embodiment of the present invention. The thyristor includes from bottom to top: a substrate layer 311, a well region layer and a gate oxide layer. The well The region layer includes an N well region and a P well region, the N well region is adjacent to the P well region, and both the N well region and the P well region are in contact with the substrate layer 311, and the well region layer includes a N well region. Well region 309 and a P well region 310, the junction of the P well region 310 and the N well region 309 is provided with a first N+ doped region 305, and the N well region 309 is provided with a first P+ doped region 304, so The P well region 310 is provided with a second N+ doped region 306 and a second P+ doped region 307, the gate oxide layer is arranged on the upper surface of the well region l...

Embodiment 2

[0043] Figure 8 It is a specific structural diagram of a thyristor with high sustain voltage and low trigger voltage ESD characteristics according to the second embodiment of the present invention. On the basis of Embodiment 1, the preferred technical solution of the present invention is that the first P+ doping An insulating material region 313 is provided between the region 304 and the first N+ doped region 305 , and an insulating material region 313 is also provided between the second P+ doped region 307 and the second N+ doped region 306 .

Embodiment 3

[0045] Figure 9 It is a specific structural schematic diagram of a thyristor with high sustain voltage and low trigger voltage ESD characteristics according to the third embodiment of the present invention. The thyristor includes from bottom to top: a substrate layer 311, a well region layer and a gate oxide layer. The well The region layer includes an N well region and a P well region, the N well region is adjacent to the P well region, and both the N well region and the P well region are in contact with the substrate layer 311, and the well region layer includes a N well region. Well region 309 and two P well regions, the junction of the N well region 309 and the first P well region 310 is provided with a first N+ doped region 305, and the second P well region 308 is provided with a first P+ doped region 304, the first P well region 310 is provided with a second N+ doped region 306 and a second P+ doped region 307, the gate oxide layer is arranged on the upper surface of th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More