SCR for electrostatic protection, chip and system

An electrostatic protection and chip technology, applied in the electronic field, can solve problems such as unsatisfactory and ineffective reduction of static electricity impact on internal circuits.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0051] Embodiment 1 provides an SCR for electrostatic protection, such as Figure 6 As shown, it includes a semiconductor substrate 10, an N-type first well 21 located on the semiconductor substrate 10, a P-type second well 22, and an N-type third well 23. The second well 22 is located between the first well 21 and the third well. Between 23.

[0052] The N-type first well 21 is provided with an N-type first heavily doped region 31 and a P-type second heavily doped region 32 .

[0053] The N-type third well 23 is provided with an N-type third heavily doped region 33 .

[0054] The P-type second well 22 is provided with a P-type fourth heavily doped region 34, and the P-type fourth heavily doped region 34 extends to the first well 21 and the third well 23; the P-type fourth heavily doped region 34 and There is a first interval (denoted as L1 ) between the P-type second heavily doped regions 32 , and metal gates 41 are arranged at the first interval.

[0055] Wherein, the fir...

Embodiment 2

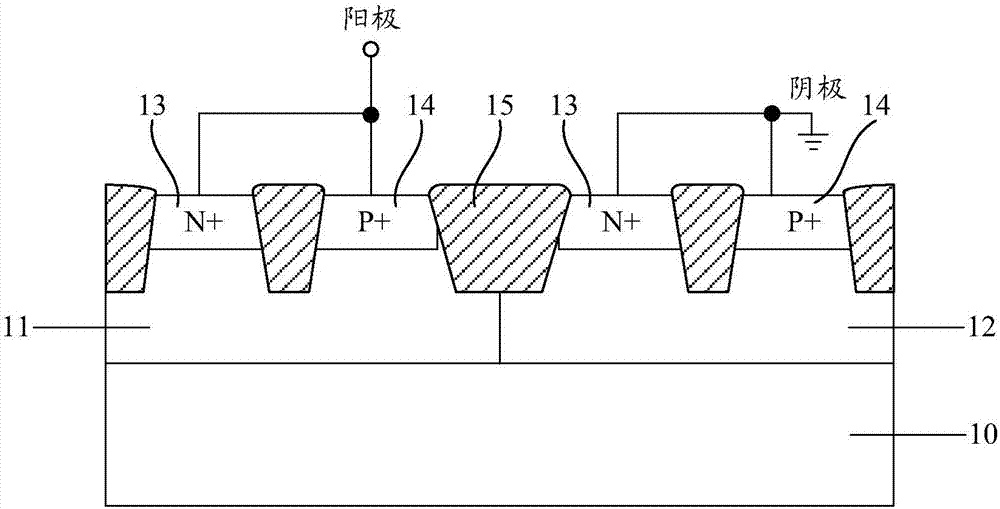

[0066] Embodiment two, provide a kind of SCR that is used for electrostatic protection, such as Figure 8 As shown, it includes a semiconductor substrate 10, a P-type first well 21 located on the semiconductor substrate 10, an N-type second well 22, and a P-type third well 23. The second well 22 is located between the first well 21 and the third well. Between 23.

[0067] The P-type first well 21 is provided with a P-type first heavily doped region 31 and an N-type second heavily doped region 32 .

[0068] The P-type third well 23 is provided with a P-type third heavily doped region 33 .

[0069] N-type second well 22 is provided with N-type fourth heavily doped region 34, N-type fourth heavily doped region 34 extends to first well 21 and third well 23; N-type fourth heavily doped region 34 and There is a first interval L1 (denoted as L1 ) between the N-type second heavily doped regions 32 , and metal gates 41 are disposed at the first interval.

[0070] Wherein, the first ...

Embodiment 3

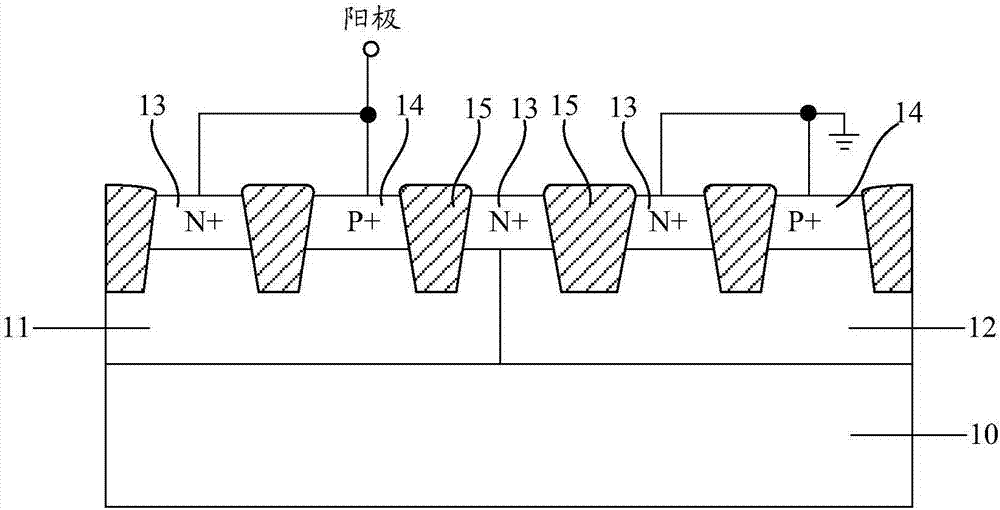

[0088] Embodiment three, provide a kind of SCR that is used for electrostatic protection, such as Figure 10 As shown, it includes a semiconductor substrate 10 , an N-type fourth well 24 , a P-type fifth well 25 and an N-type sixth well 26 located on the semiconductor substrate 10 .

[0089] A P-type fifth heavily doped region 35 is disposed in the N-type fourth well 24 .

[0090] The P-type fifth well 25 is provided with an N-type sixth heavily doped region 36 and an N-type seventh heavily doped region 37, the N-type sixth heavily doped region 36 extends into the fourth well 24, and the N-type seventh heavily doped region 37 extends into the fourth well 24. The heavily doped region 37 extends into the sixth well 26 ; there is a second distance (denoted as L2 ) between the sixth heavily doped region 36 and the seventh heavily doped region 37 , and a metal gate 41 is disposed at the second distance.

[0091] Wherein, the fifth heavily doped region 35 and the sixth heavily dope...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More