LDMOS ESD(Laterally Diffused Metal Oxide Semiconductor Electro-Static Discharge) structure

A source and drain technology, applied in electrical components, circuits, semiconductor devices, etc., can solve the problems of increasing IC design cost and device size, and achieve enhanced antistatic capability, increased effective channel length, and effective channel length. The effect of increasing the channel resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

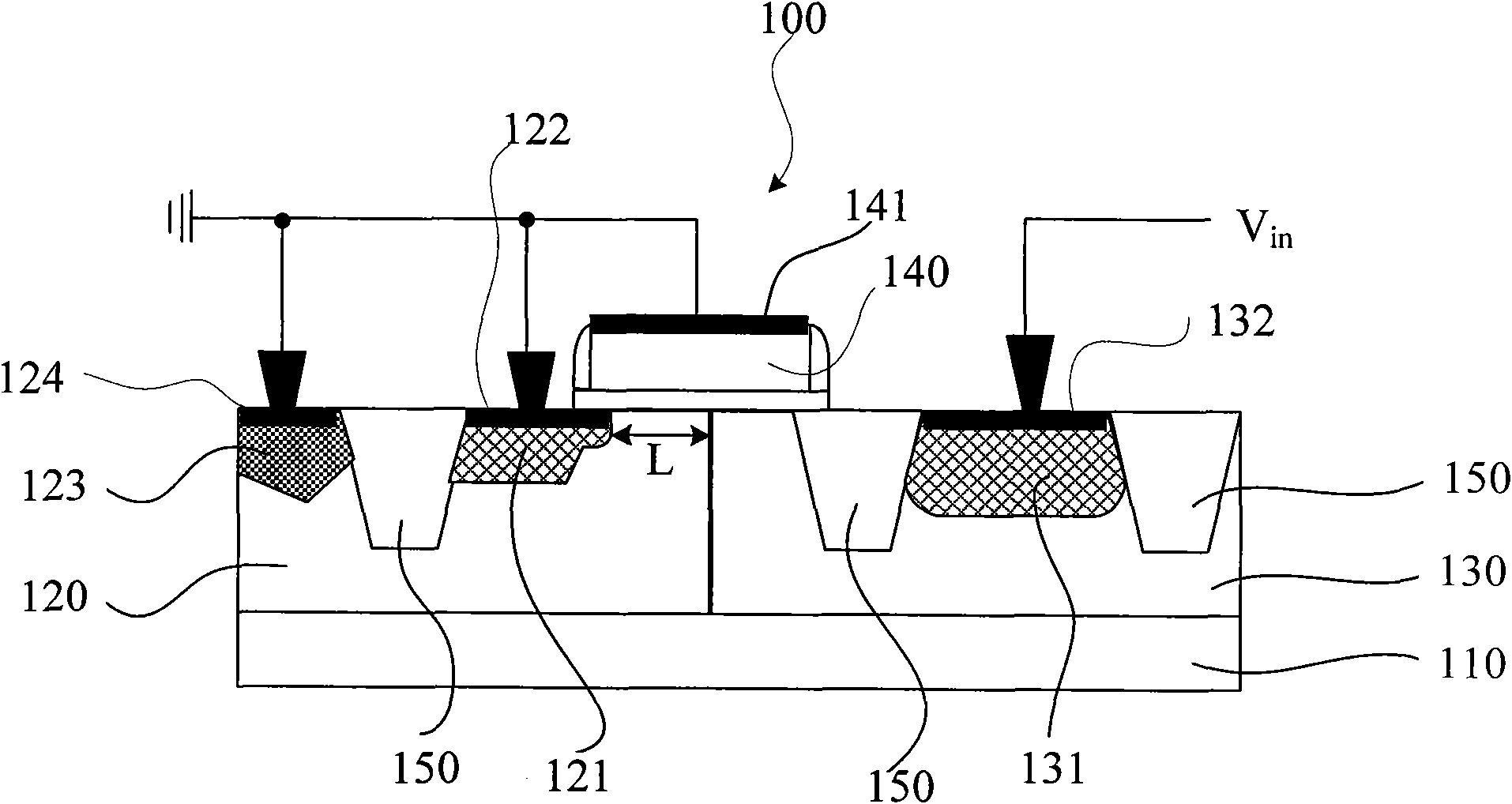

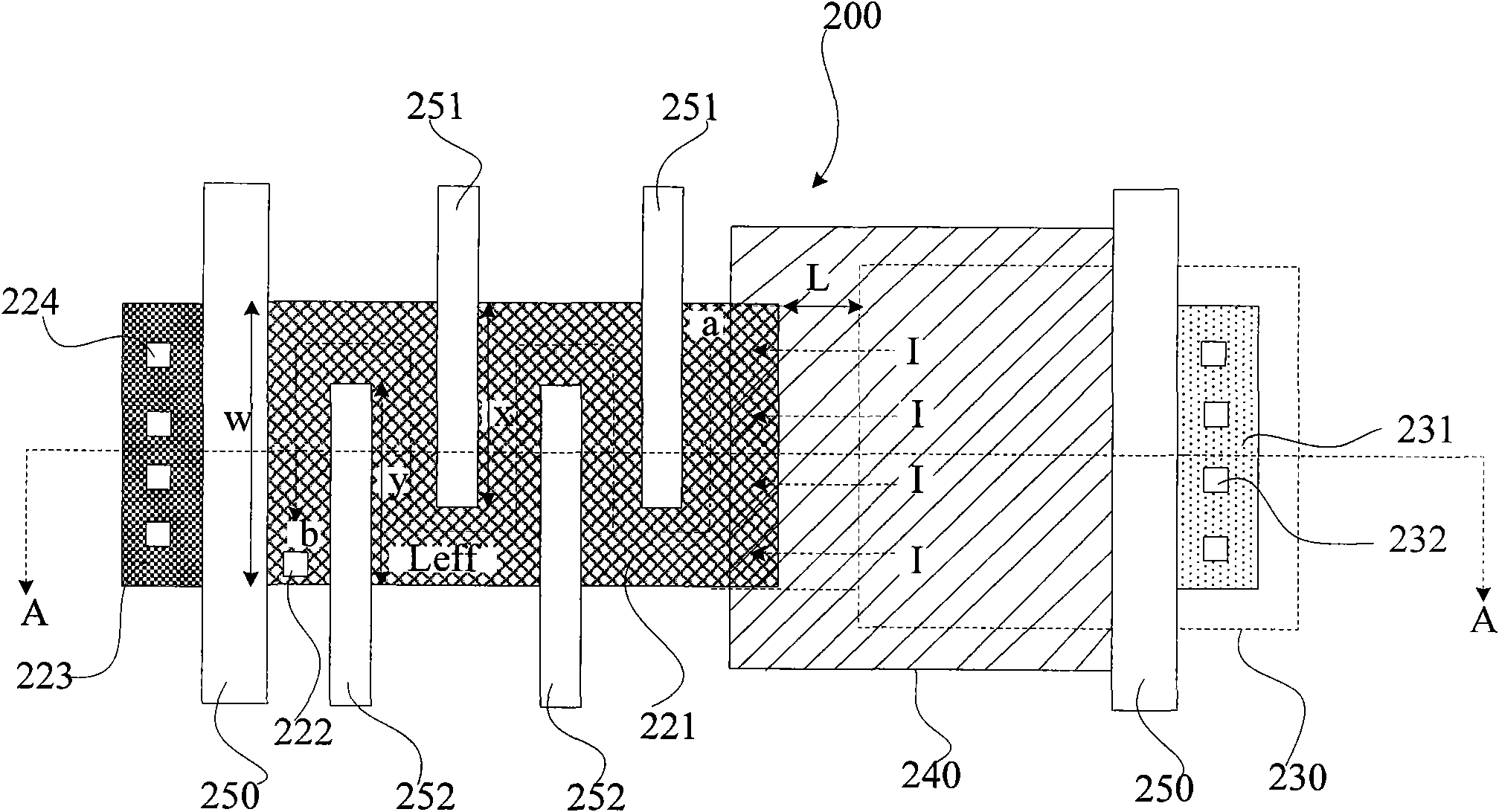

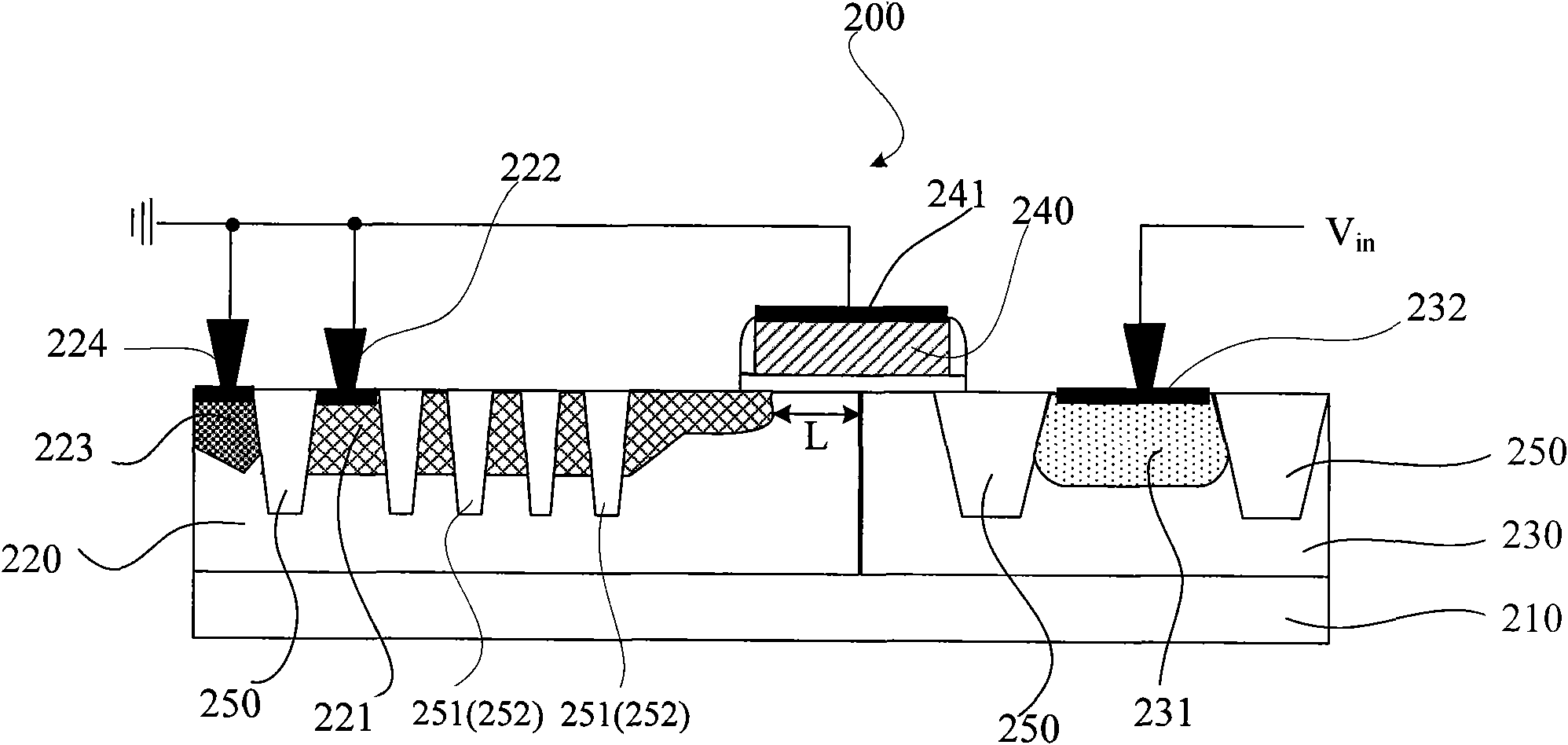

[0033] The LDMOS ESD structure proposed by the present invention will be further described in detail below in conjunction with the drawings and specific embodiments. Advantages and features of the present invention will be apparent from the following description and claims. It should be noted that the drawings are all in a very simplified form and use imprecise ratios, which are only used to facilitate and clearly assist the purpose of illustrating the embodiments of the present invention.

[0034] The core idea of the present invention is to provide an LDMOS ESD structure, the LDMOS ESD structure is provided with an interdigitated STI structure in the source region, so that the flow direction of the electrostatic discharge current of the LDMOS ESD is in a square wave shape, thereby Without increasing the actual channel length, the effective channel length is increased, the effective channel resistance is increased, the holding voltage is further increased, and the antistati...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More