SCR electrostatic protection device and electrostatic protection circuit

An electrostatic protection and device technology, applied in the field of integrated circuit electrostatic protection, can solve the problems of inability to be directly applied, no parasitic transistors directly to the back substrate, no lateral devices, etc., and achieves low trigger voltage, low parasitic noise, and enhanced holding voltage. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

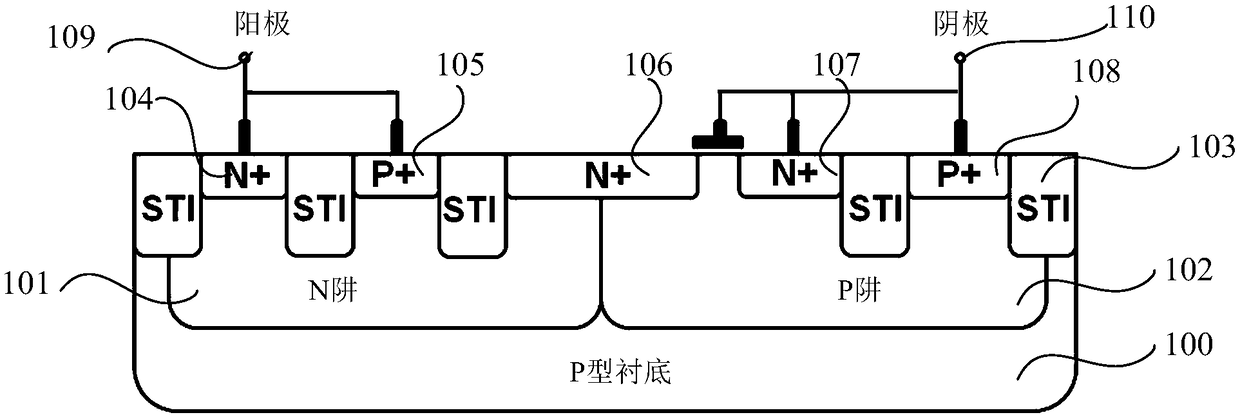

[0027] Please refer to figure 1 , figure 1 It is an existing LVTSCR device for ESD protection, formed in a bulk silicon substrate, specifically including: a P-type substrate 100, an N well 101, a P well 102, and a plurality of STI (Shallow Trench Isolation Structure) 103 , N+ doped regions 104, 106, 107, P+ doped regions 105, 108, wherein N well 101 and P well 102 are adjacent, N+ doped region 104 and P+ doped region 105 are formed in N well 101 and passed through an STI 103, the N+ doped region 106 is formed adjacent to the N well 101 and the P well 102, and is separated from the P+ doped region 105 by another STI 103, and the P+ doped region 108 and the N+ doped region 107 are formed in the P In the well 102 and separated by another STI 103, the N+ doped region 104 and the P+ doped region 105 are connected to the anode, the P well 102 between the N+ doped regions 106, 107 is covered with a gate electrode, the gate electrode, N+ The doped region 107 and the P+ doped region ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More