Use of copper Dimashg process in production of integrated circuits

A back-end process and integrated circuit technology, which is applied in the manufacturing field using the copper damascene back-end process, can solve the problems of metal/insulating medium corrosion, copper metal wire metal/insulating medium corrosion, etc., so as to reduce adverse reactions and improve the quality of finished products. rate effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0031] Now in conjunction with accompanying drawing, the specific embodiment of the present invention is described in further detail:

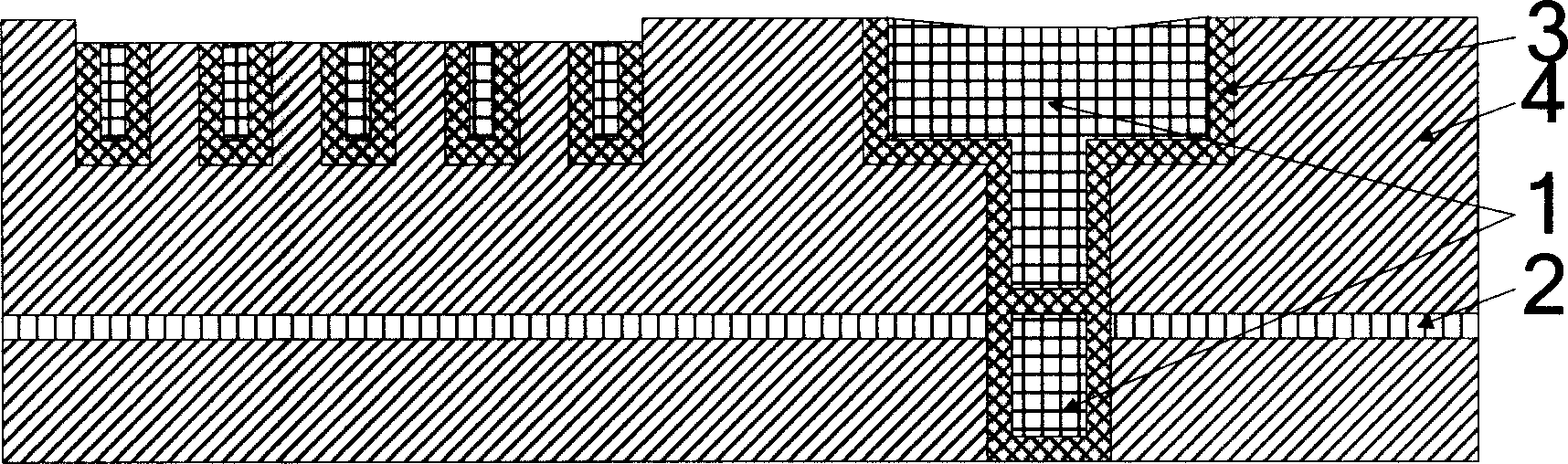

[0032] First, if Figure 2A as shown ( Figure 2A For the schematic diagram of the completed Damascus topography process), complete the Damascus topography process.

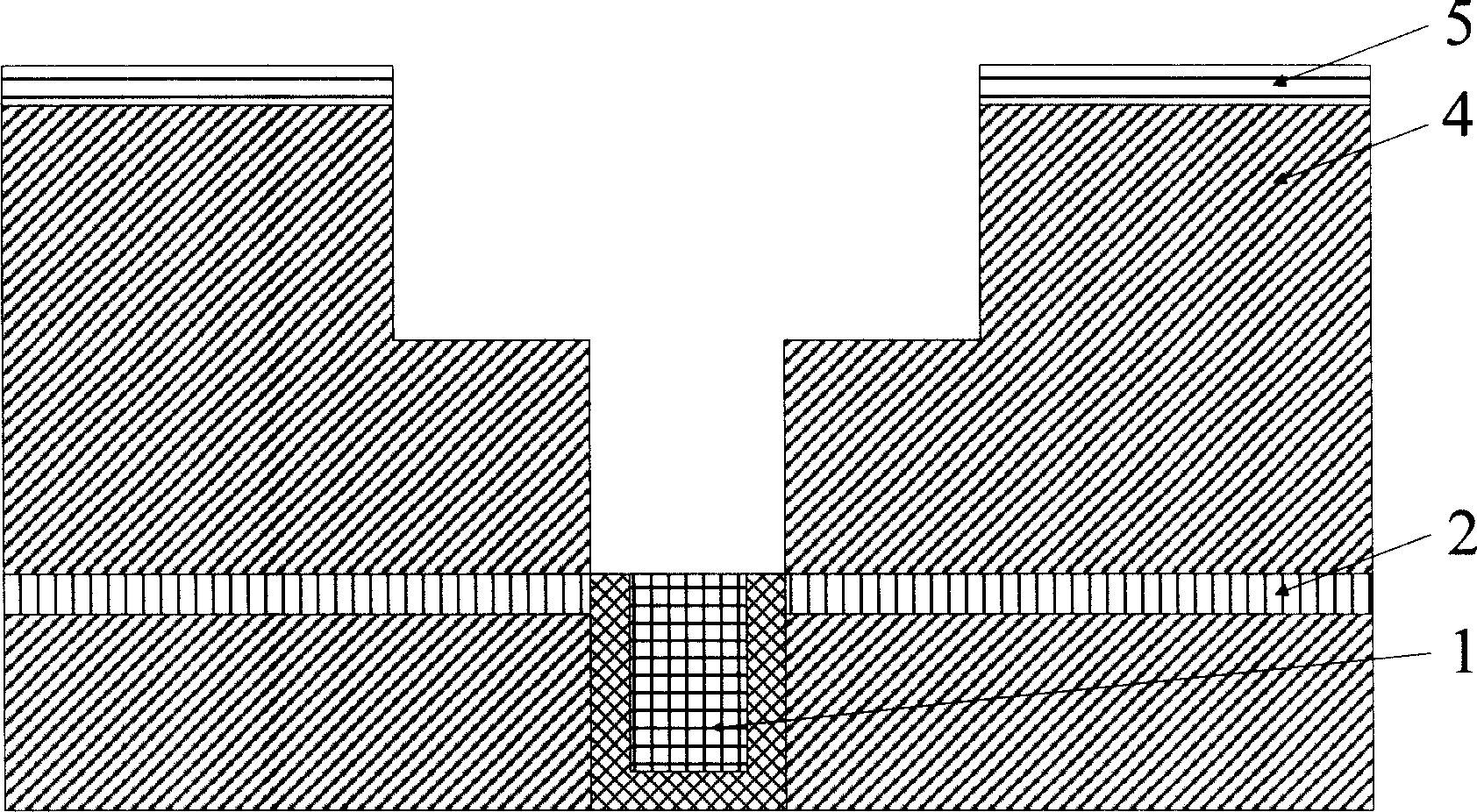

[0033] Secondly, if Figure 2B as shown ( Figure 2B It is a schematic diagram of physical vapor deposition of a tantalum nitride / tantalum metal layer), and a physical vapor deposition of a tantalum nitride / tantalum metal layer on the top etch barrier layer, the damascene dielectric layer, and the bottom copper metal layer.

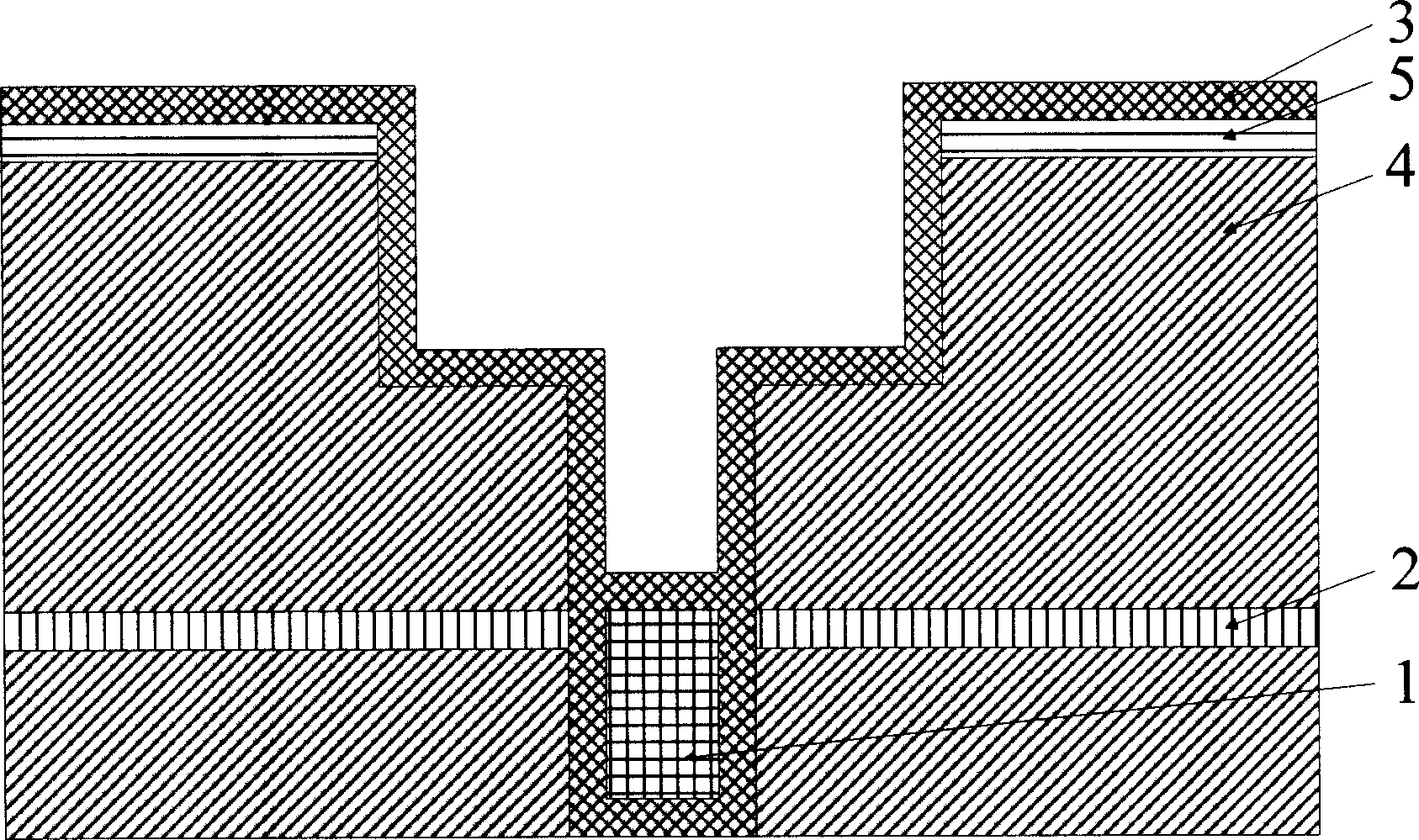

[0034] Secondly, if Figure 2C as shown ( Figure 2C For the schematic diagram of coating the bottom anti-reflection absorption material), the photosensitive material flat surface process is carried out, that is, the bottom anti-reflection absorption material is coated on the tantalum nitride / tantalum metal layer, filled with damascene patterns, and bak...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Surface flatness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More