Method for quickly extracting critical area of layout

A key area, layout technology, applied in special data processing applications, instruments, electrical digital data processing, etc., can solve the problems of large differences in integrated circuit layouts, expansion of scale, and increased complexity.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

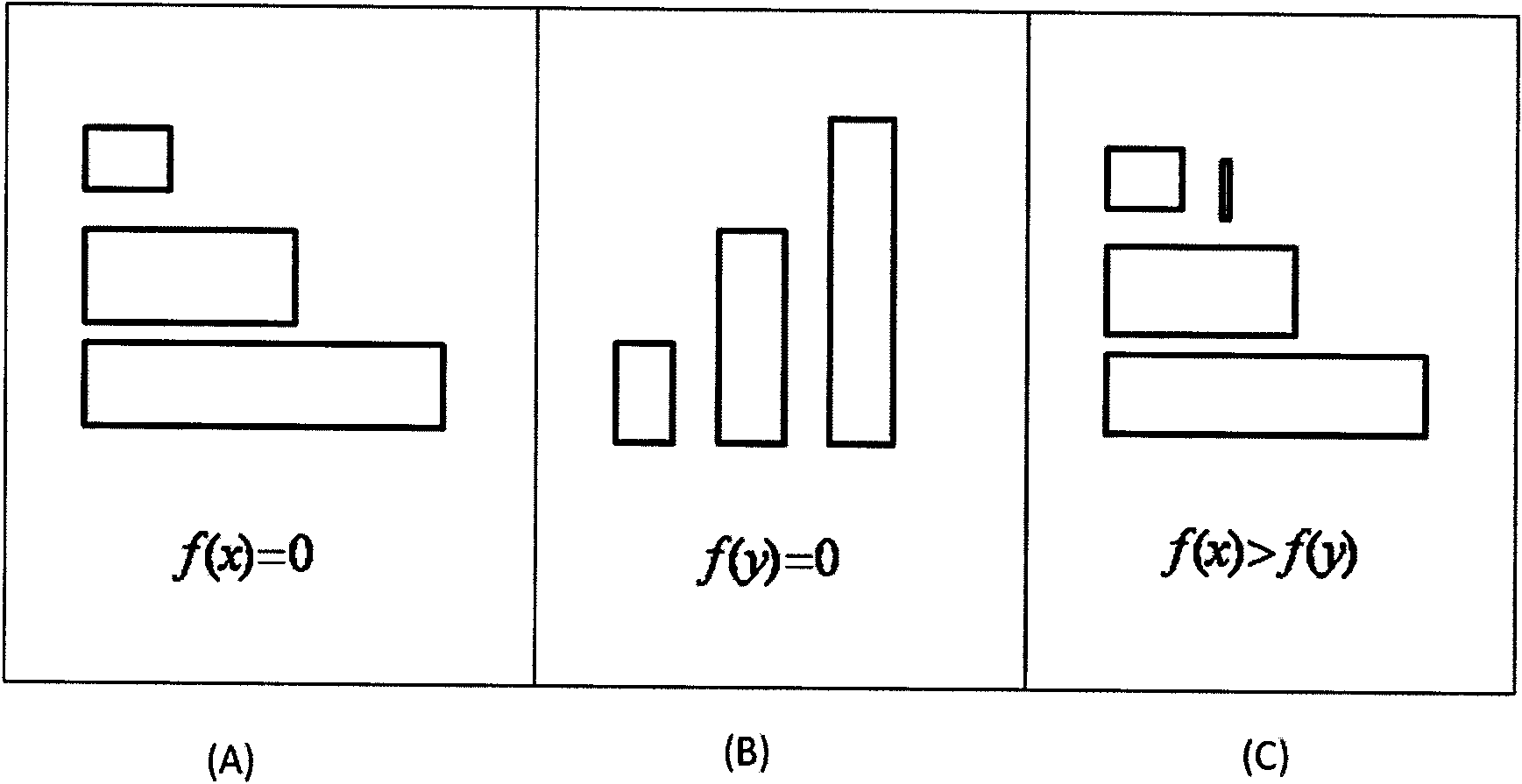

[0049] Figure 4 The flow chart of the method of the present invention, the method mainly includes four steps in the specific operation, namely, extracting layout information, establishing a block-by-block orderly multi-level index table, randomly simulating the production process defect analysis statistical influence, and using block-by-block orderly multi-level The index table calculates the key area; the technical key lies in the block-ordered multi-level index table.

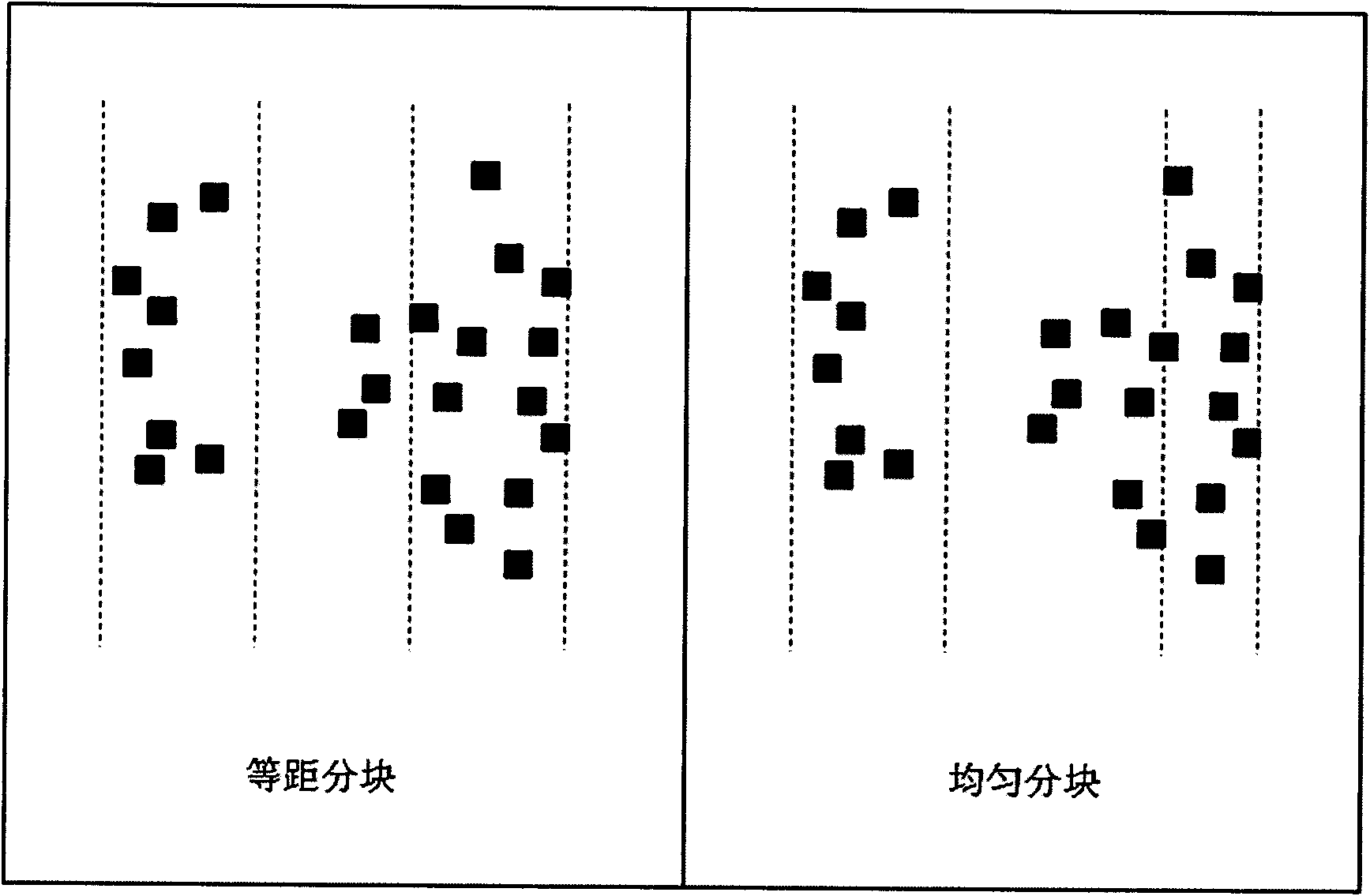

[0050] Figure 5 Shown is the flow chart of establishing the block ordered multi-level index table of the present invention. Combine below Figure 5 Taking a layout with a design size of 0.25um as an example to illustrate how to build a block-ordered multi-level index table.

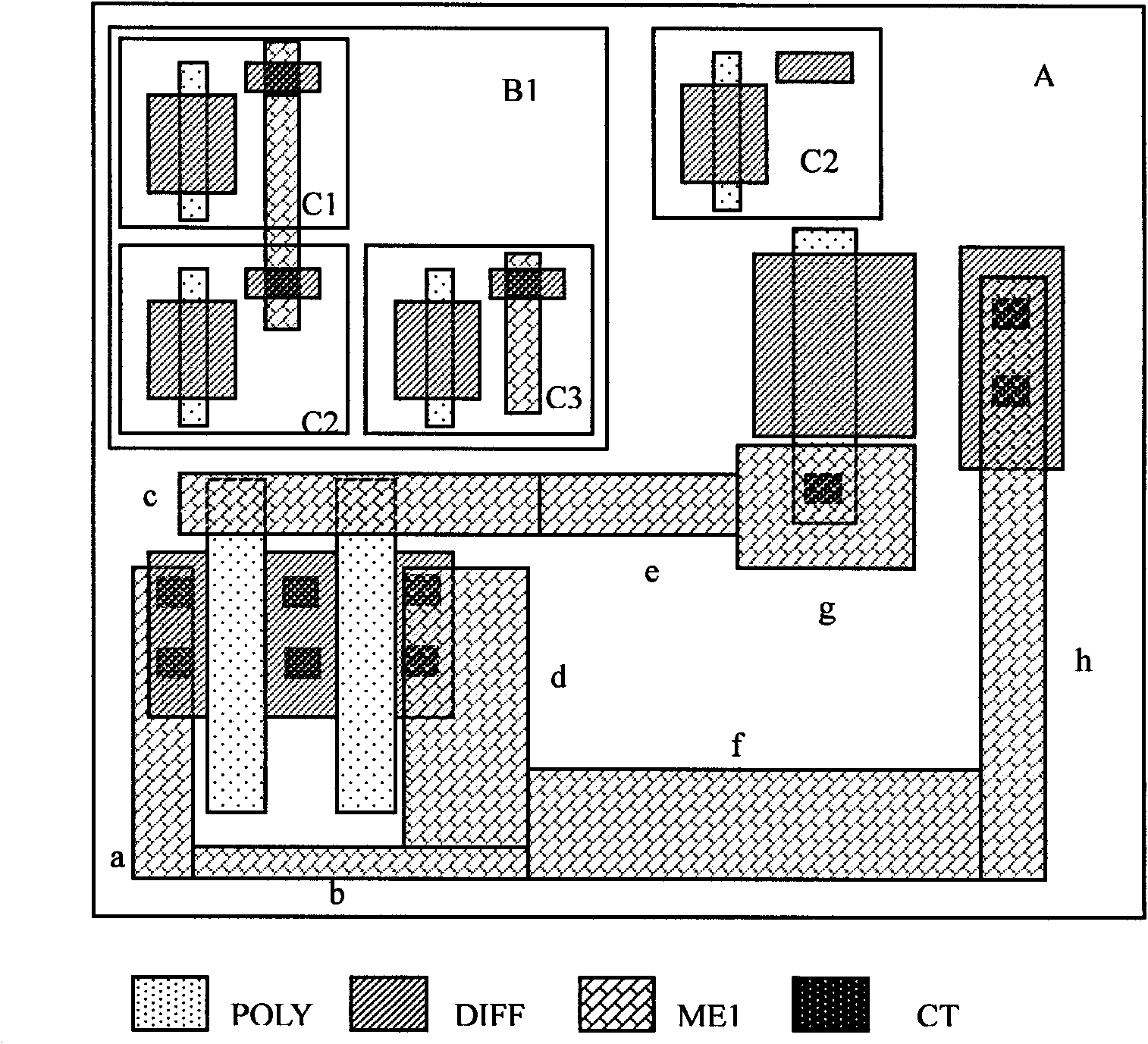

[0051] (1) Traversing the layout tree, extracting all layers contained in the layout, and storing layer numbers, such as POLY, DIFF, ME1, and CT are respectively numbered 1, 2, 3, 4, etc., to save storage space.

[0052] (2) Traver...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More