Semiconductor structure and its manufacture method

一种制造方法、半导体的技术,应用在半导体/固态器件制造、半导体器件、半导体/固态器件零部件等方向,能够解决产量下降、接触电阻上升等问题,达到改善产量、降低接触电阻、降低电迁移的效果

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

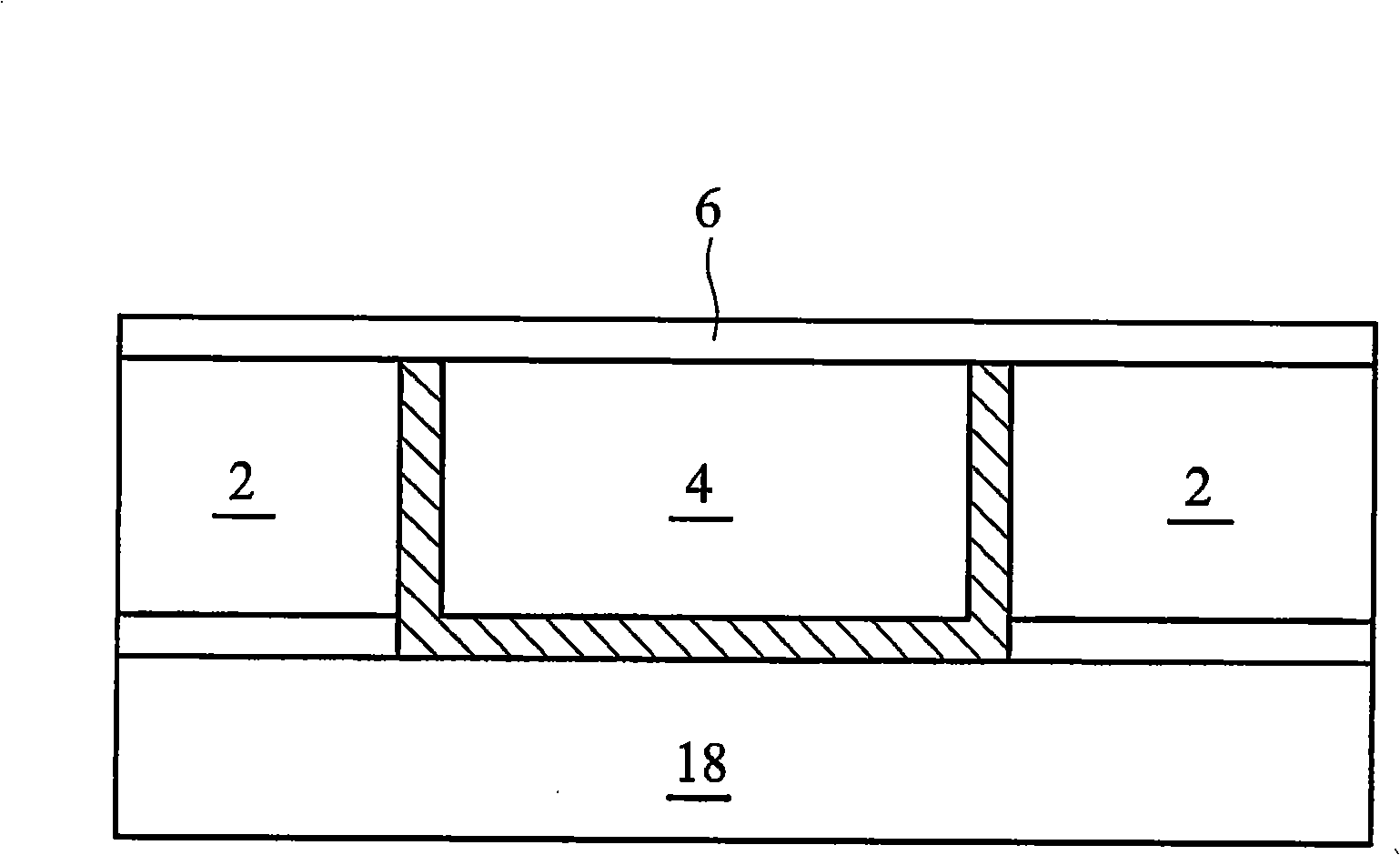

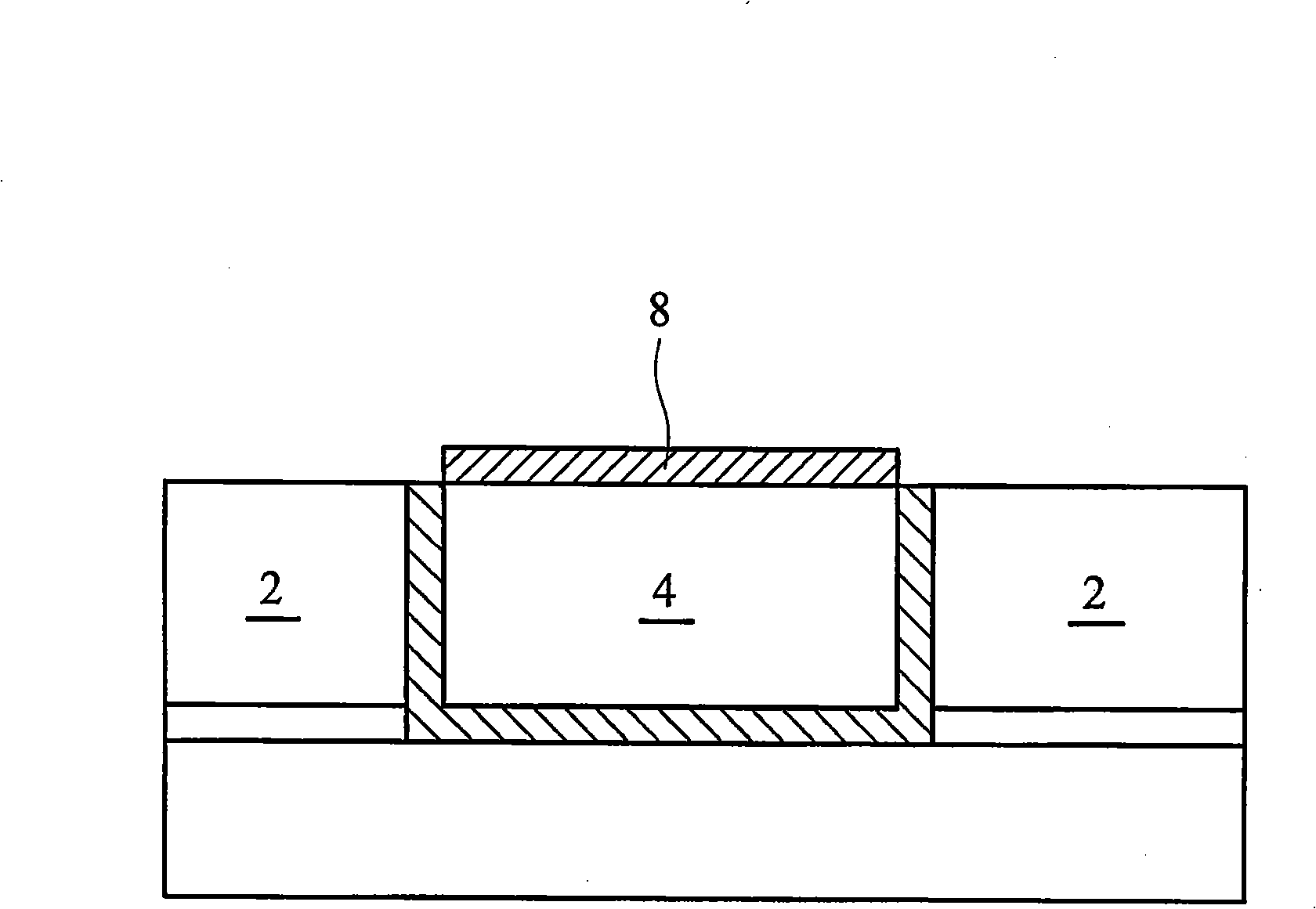

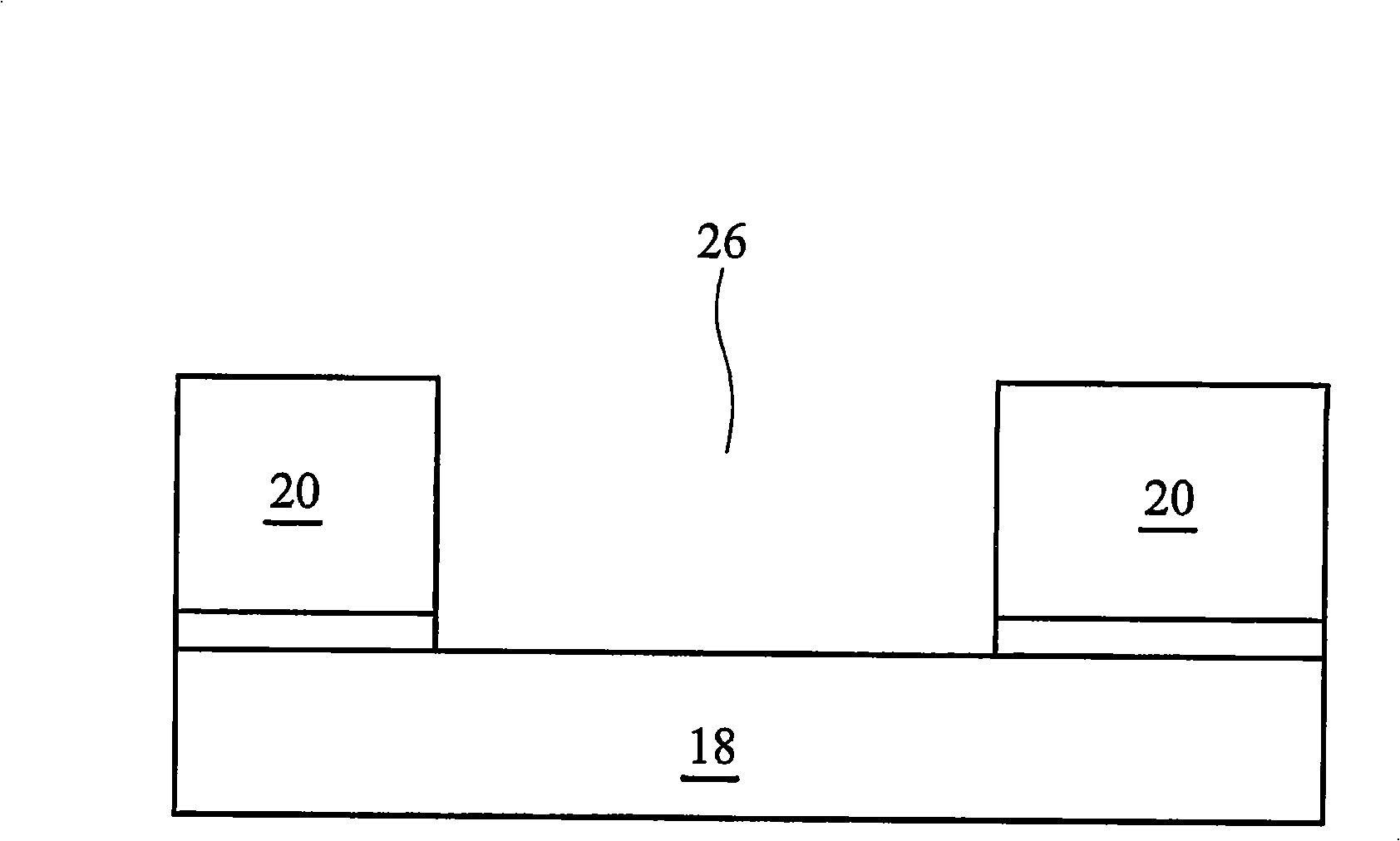

[0028] The following will combine Figure 3-8B A process for manufacturing a semiconductor structure according to an embodiment of the present invention is described. image 3 Openings 26 are shown formed in dielectric layer 20 . Dielectric layer 20 is formed on substrate 18 . The substrate 18 may include a semiconductor substrate and various structures formed thereon, such as an etch stop layer, an interlayer dielectric layer, an intermetal dielectric layer, and the like. The semiconductor substrate may be a single crystal substrate or a compound semiconductor substrate on which active elements (not shown) such as transistors may be formed. Opening 26 may be a trench for forming a wire. In one embodiment, the dielectric layer 20 is preferably a low dielectric constant layer with a dielectric constant of less than about 3, more preferably an ultra-low dielectric constant layer with a dielectric constant of less than about 2.5. The dielectric layer 20 may include commonly u...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More