Patents

Literature

148 results about "Stress migration" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Stress migration is a failure mechanism that often occurs in integrated circuit metallization (aluminum, copper). Voids form as result of vacancy migration driven by the hydrostatic stress gradient. Large voids may lead to open circuit or unacceptable resistance increase that impedes the IC performance. 'Stress migration is often referred as stress voiding, stress induced voiding or SIV.

Radiation-assisted selective deposition of metal-containing cap layers

InactiveUS20100210108A1Semiconductor/solid-state device manufacturingChemical vapor deposition coatingDevice materialSelective deposition

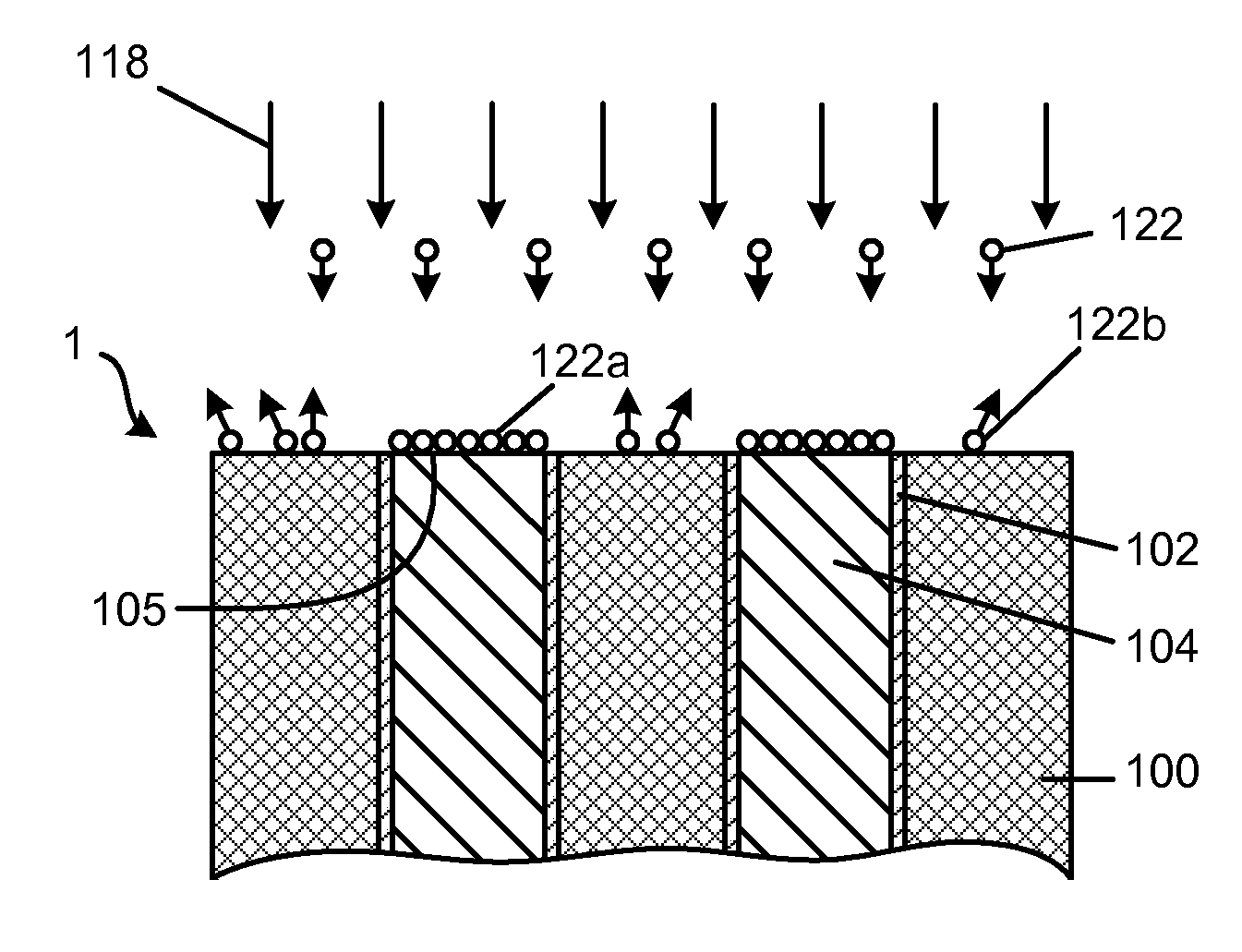

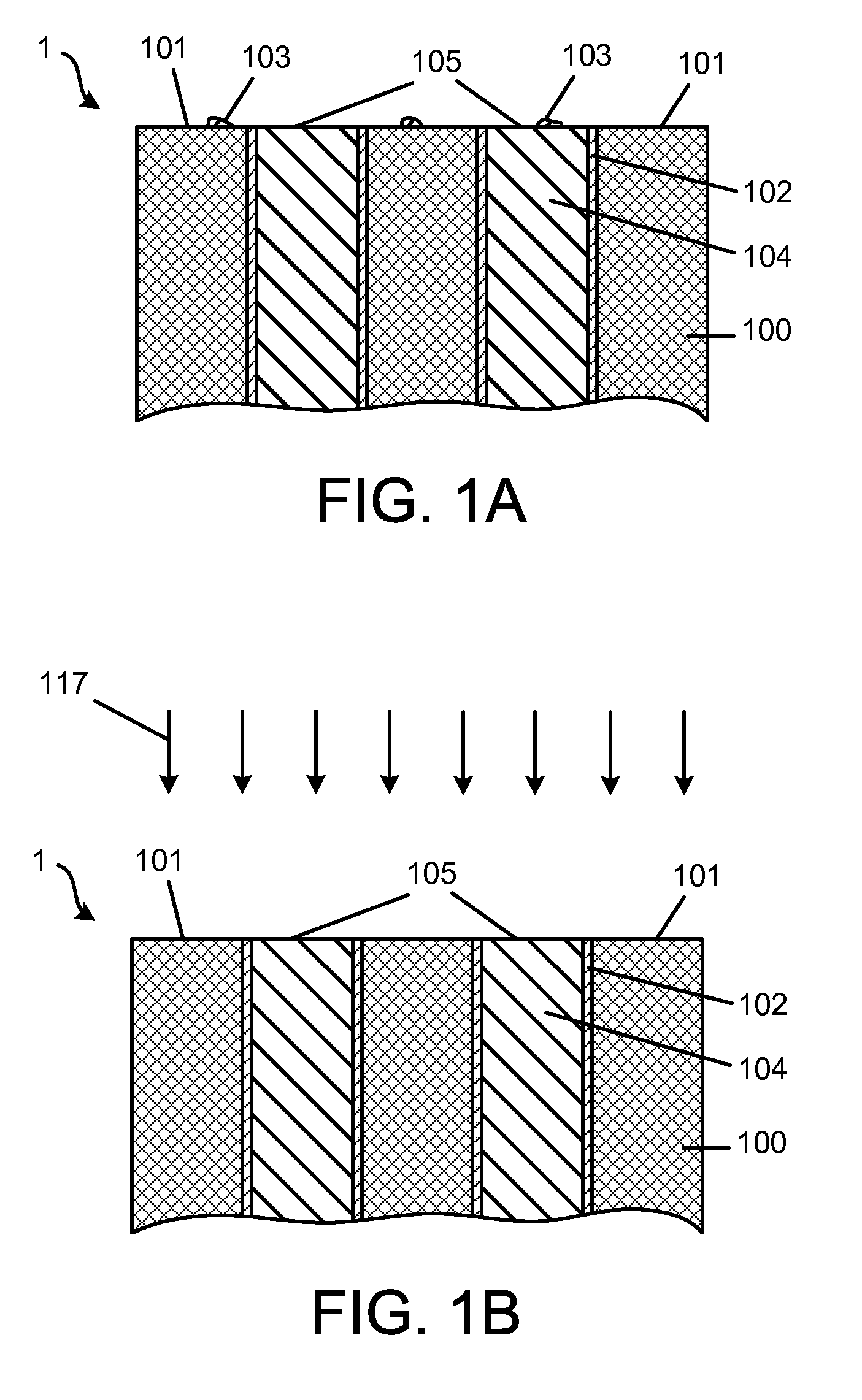

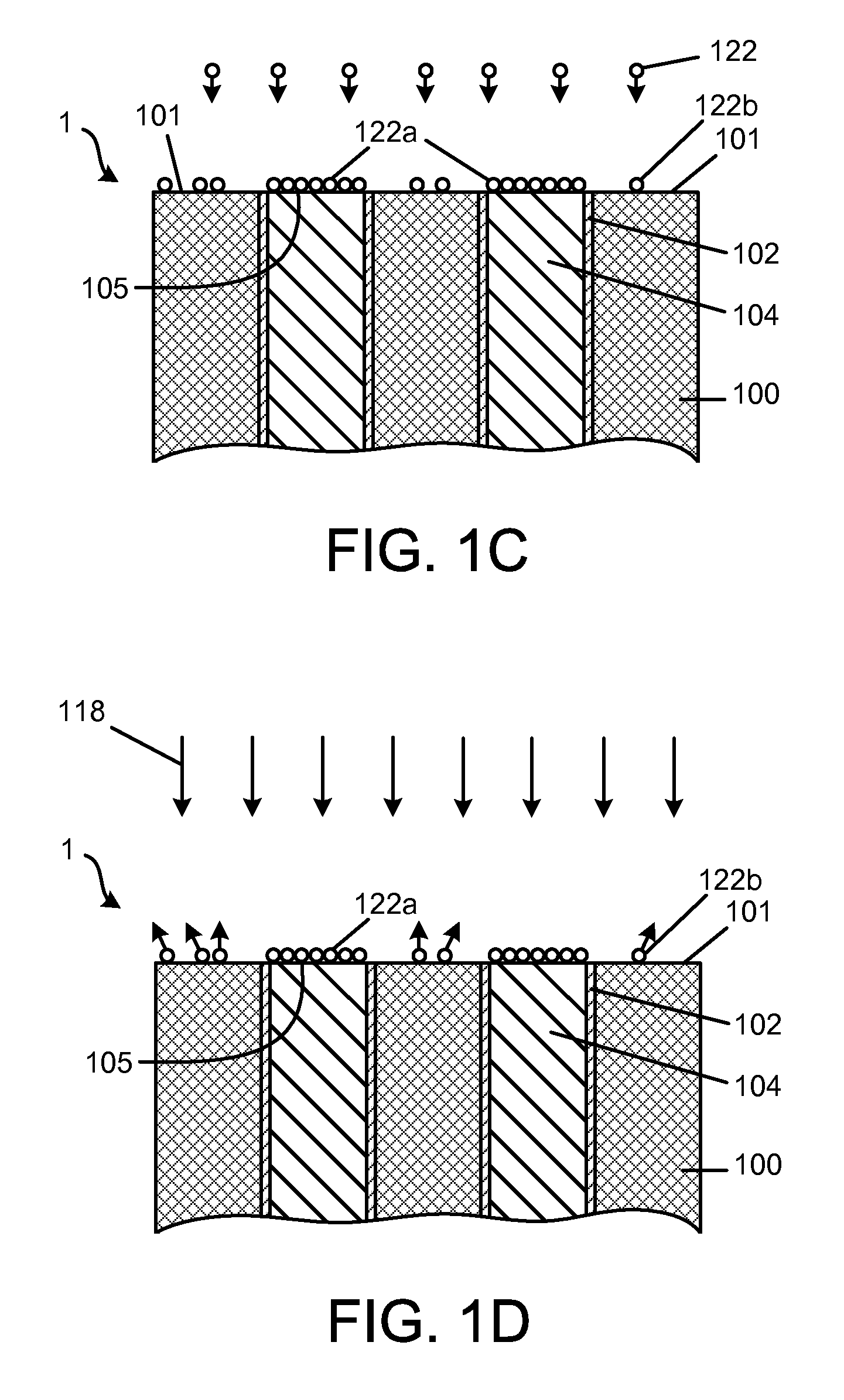

A method for integrating metal-containing cap layers into copper (Cu) metallization of semiconductor devices to improve electromigration and stress migration in bulk Cu metal. In one embodiment, the method includes providing a patterned substrate containing Cu metal surfaces and dielectric layer surfaces, exposing the patterned substrate to a process gas comprising a metal-containing precursor, and irradiating the patterned substrate with electromagnetic radiation, where selective metal-containing cap layer formation on the Cu metal surfaces is facilitated by the electromagnetic radiation. In some embodiments, the method further includes pre-treating the patterned substrate with additional electromagnetic radiation and optionally a cleaning gas prior to forming the metal-containing cap layer.

Owner:TOKYO ELECTRON LTD

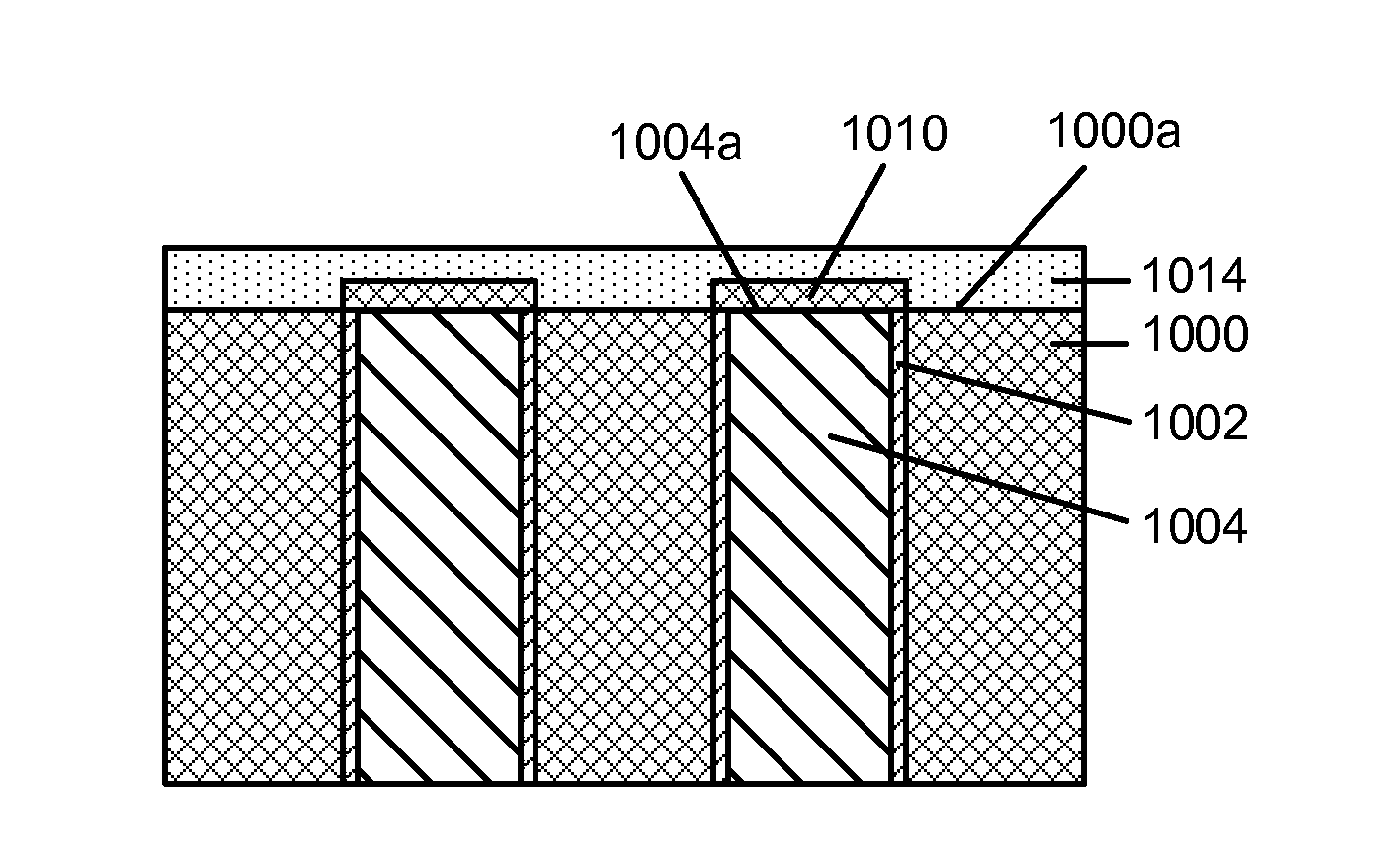

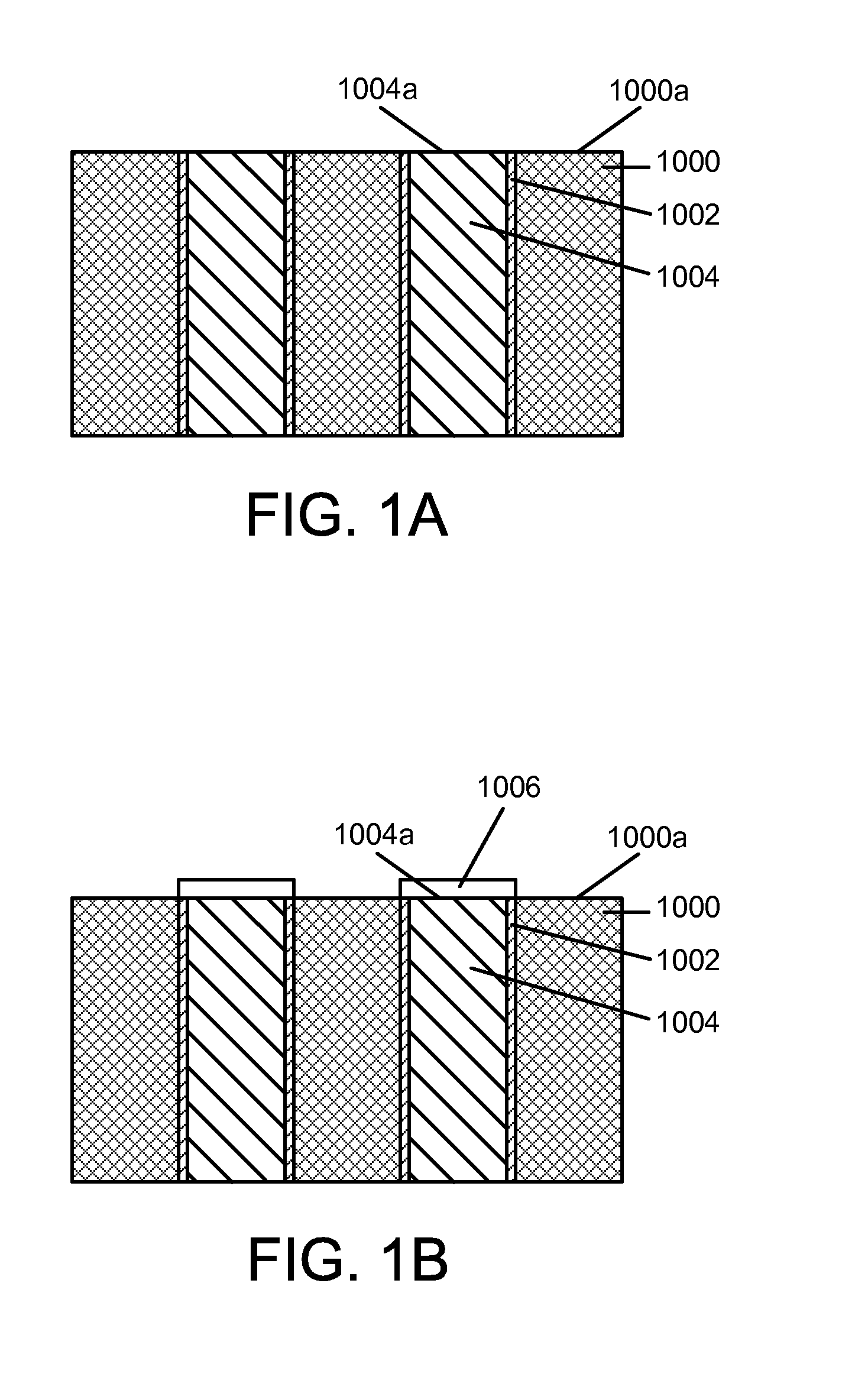

Method for integrating selective low-temperature ruthenium deposition into copper metallization of a semiconductor device

InactiveUS20090186481A1Improve electromigrationImprove stress migrationSemiconductor/solid-state device detailsSolid-state devicesDevice materialRuthenium

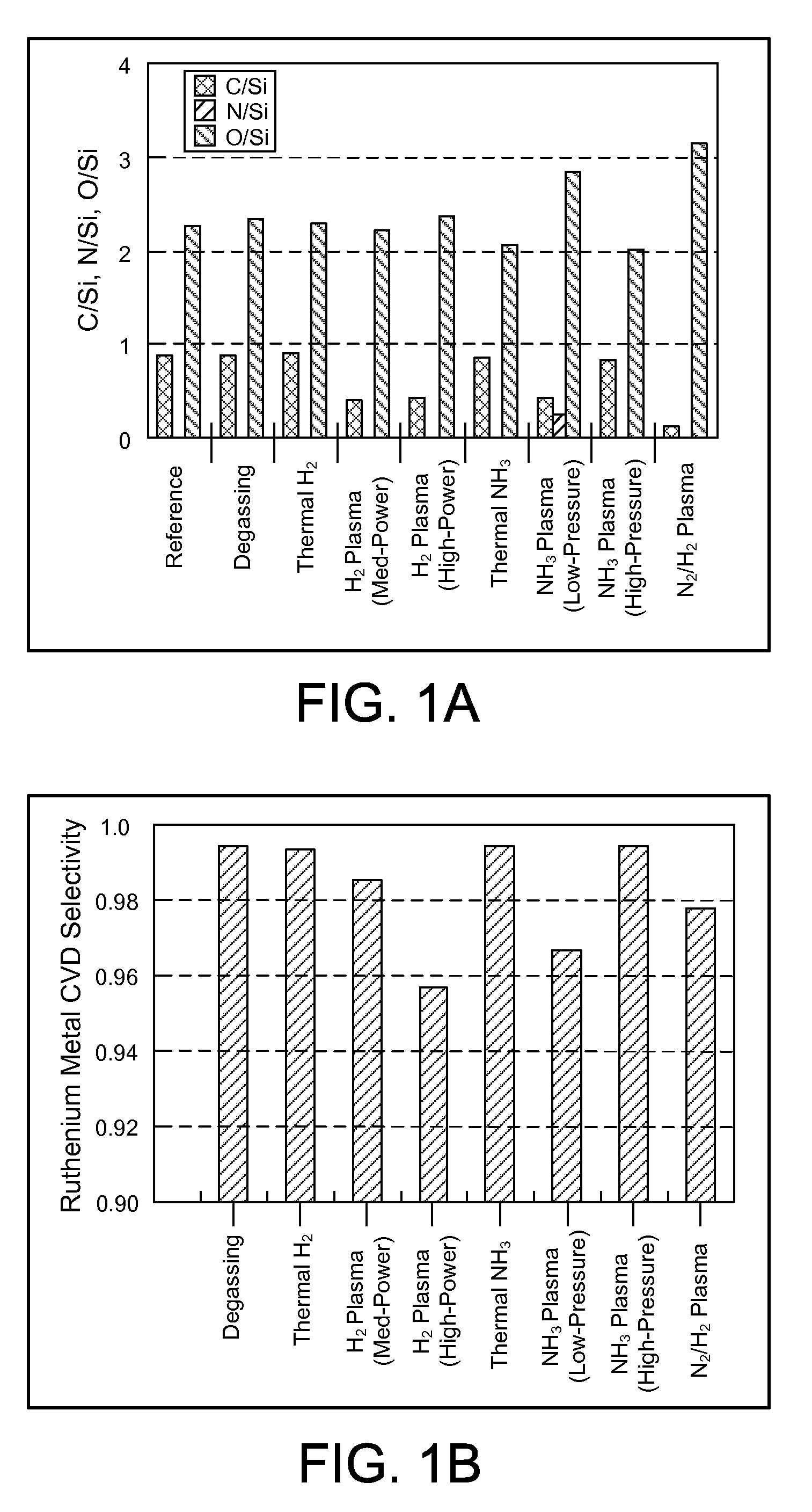

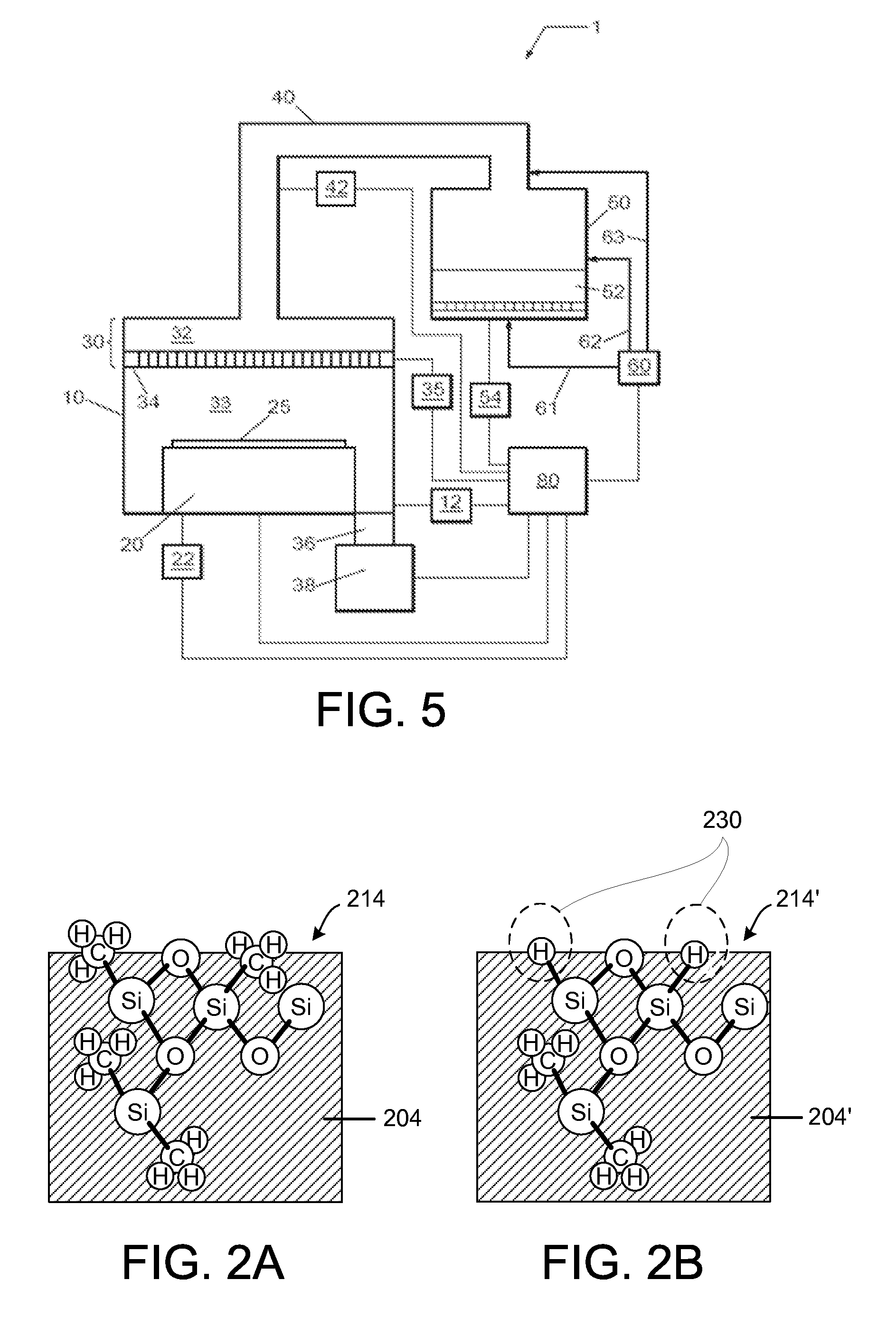

A method for integrating low-temperature selective Ru metal deposition into manufacturing of semiconductor devices to improve electromigration and stress migration in bulk Cu metal. The method includes providing a patterned substrate containing a recessed feature in a dielectric layer, where the recessed feature is at least substantially filled with planarized bulk Cu metal, heat-treating the bulk Cu metal and the dielectric layer in the presence of H2, N2, or NH3, or a combination thereof, and selectively depositing a Ru metal film on the heat-treated planarized bulk Cu metal.

Owner:TOKYO ELECTRON LTD

Method for modifying metal cap layers in semiconductor devices

InactiveUS20120252210A1Improve electromigrationImprove stress migrationSemiconductor/solid-state device manufacturingChemical vapor deposition coatingPatterned substrateAmmonia

A method for forming a semiconductor device with improved electromigration (EM) and stress migration (SM) properties. The method includes providing a planarized patterned substrate containing a copper (Cu) metal surface and a low-k dielectric layer surface, selectively depositing a metal cap layer on the Cu metal surface, and modifying the metal cap layer by exposing the metal cap layer to a process gas containing ammonia (NH3) gas without plasma excitation. The method further includes forming a dielectric barrier film on the modified metal cap layer and on the dielectric layer surface, and exposing the dielectric barrier film to a gaseous oxidizing environment, where the dielectric barrier film and the modified metal cap layer prevent oxidation of the Cu metal surface when the dielectric barrier film is exposed to the gaseous oxidizing environment.

Owner:TOKYO ELECTRON LTD

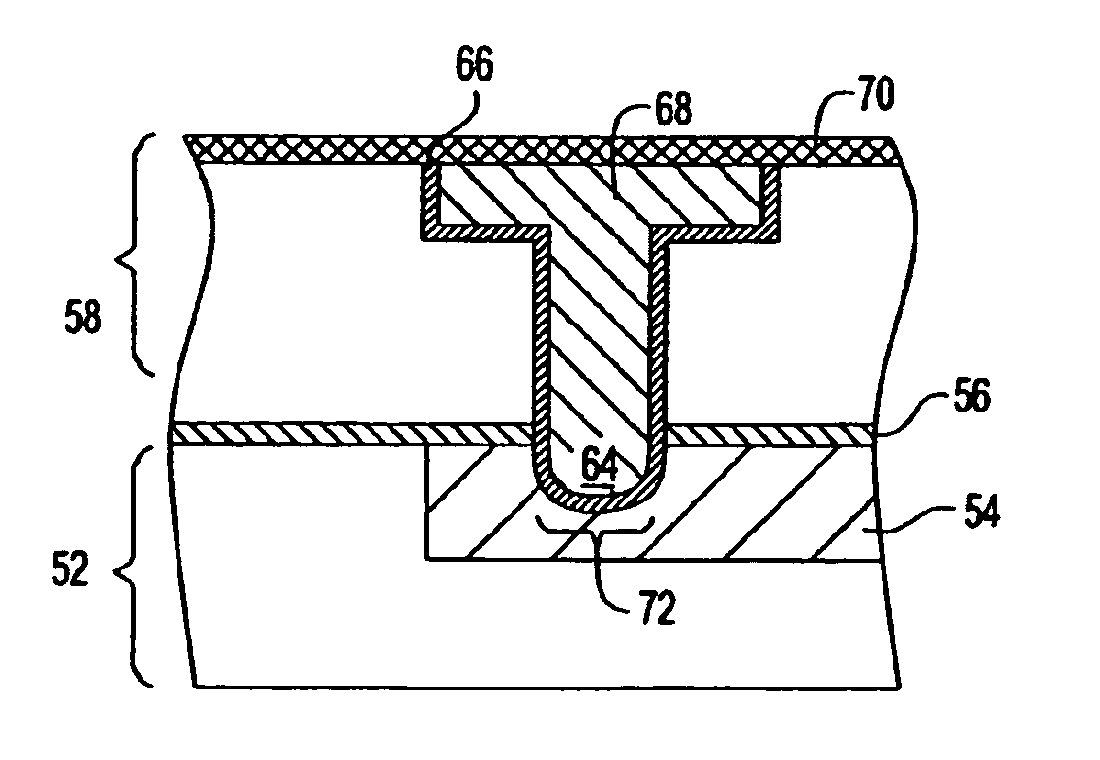

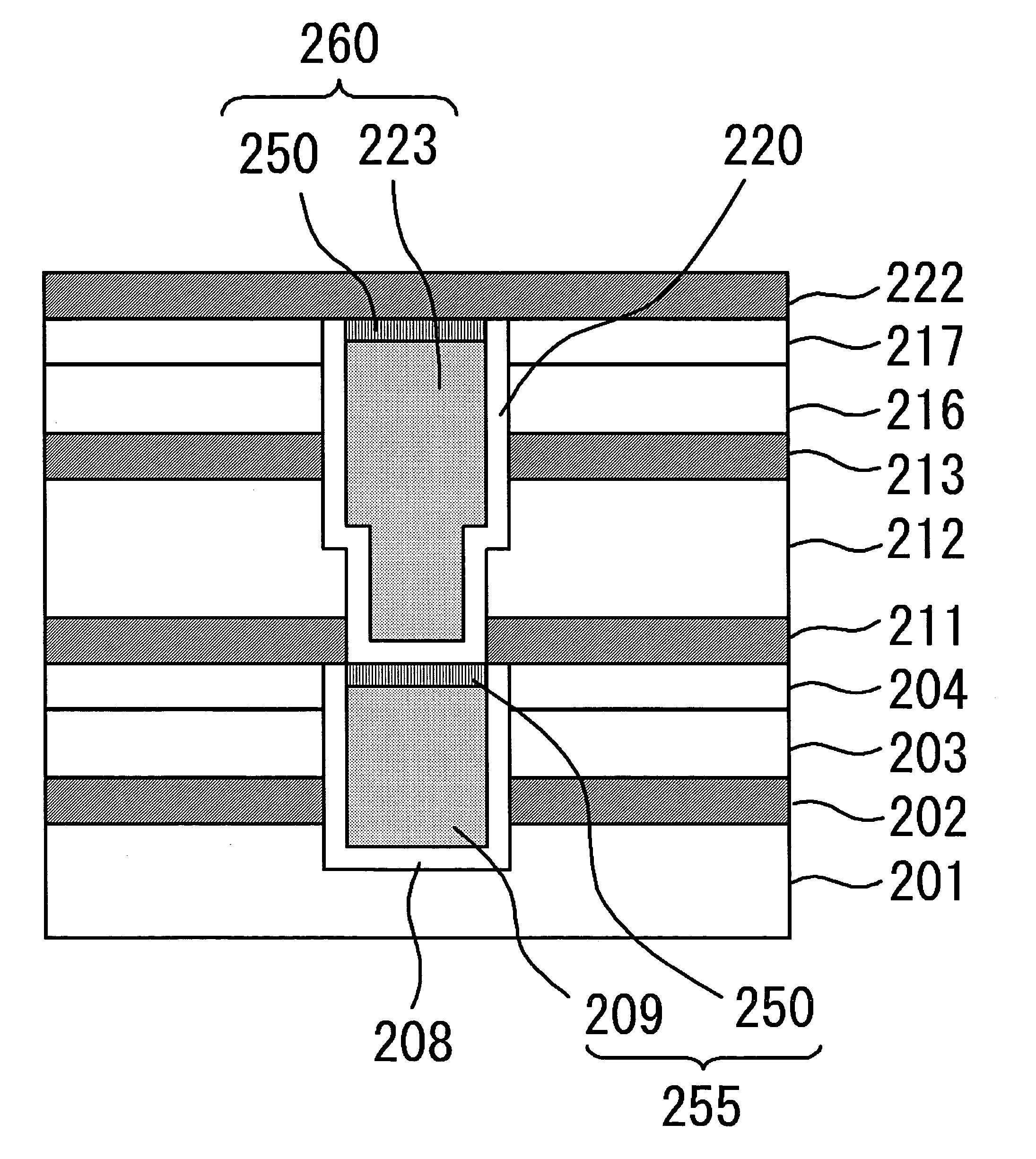

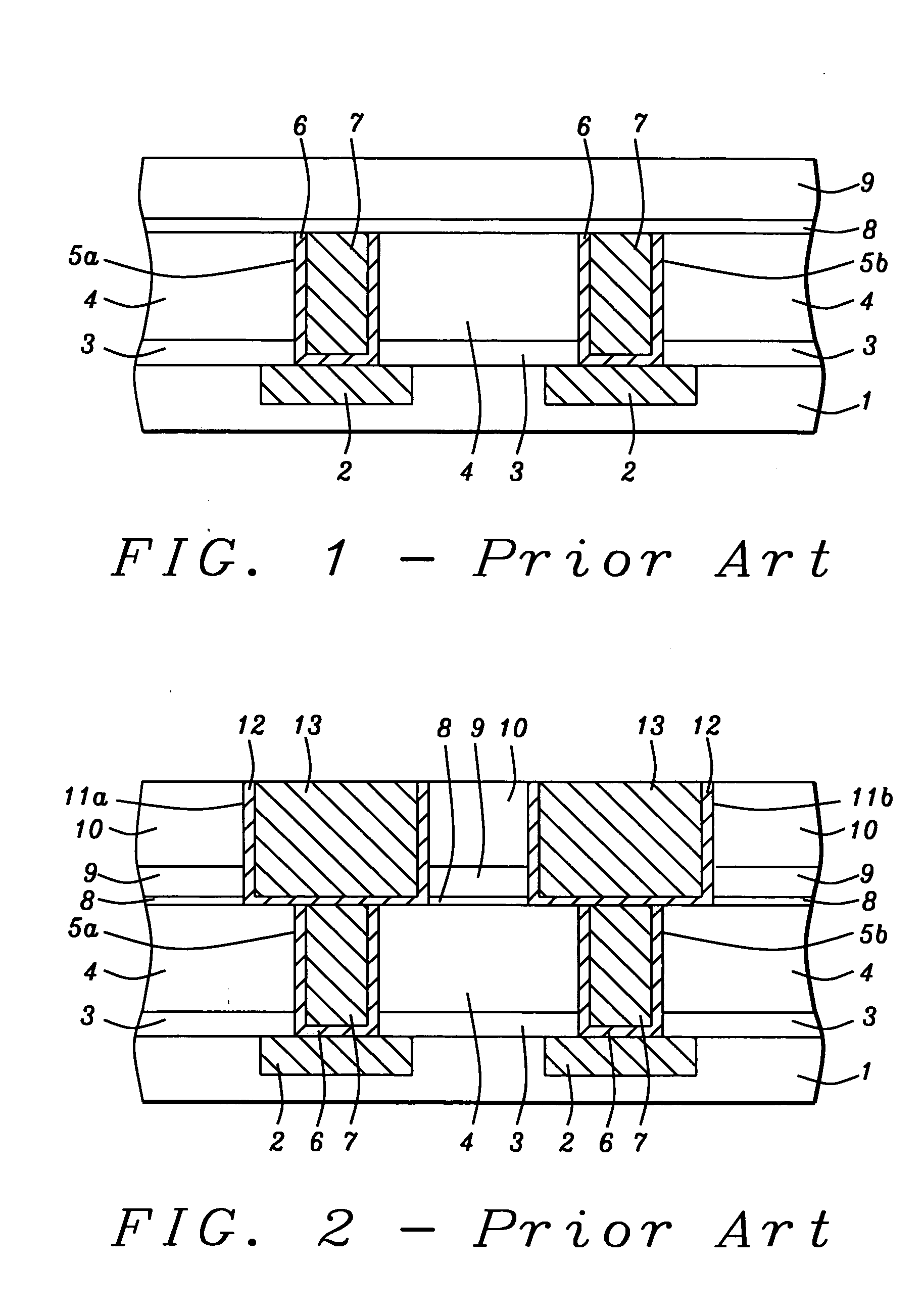

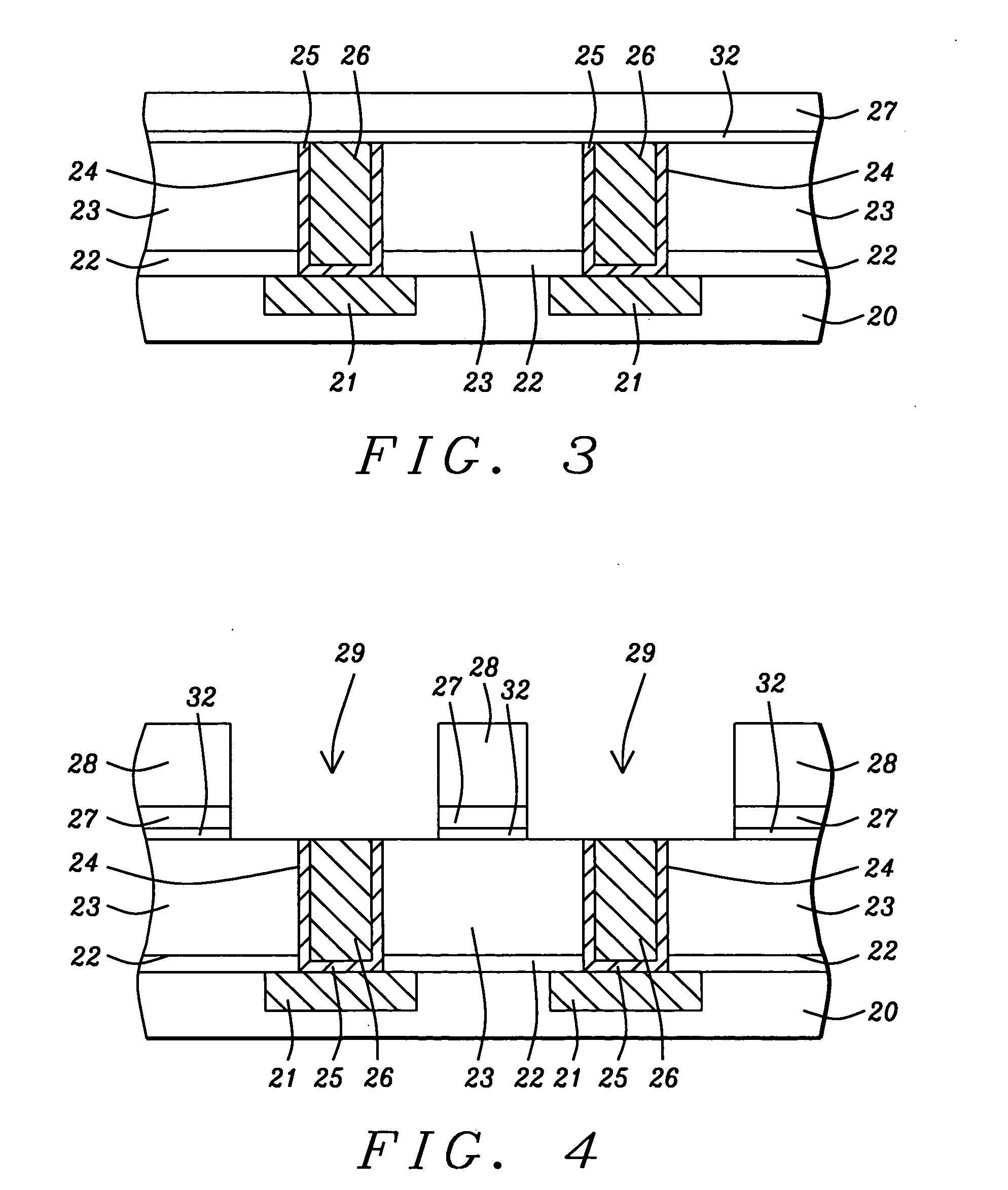

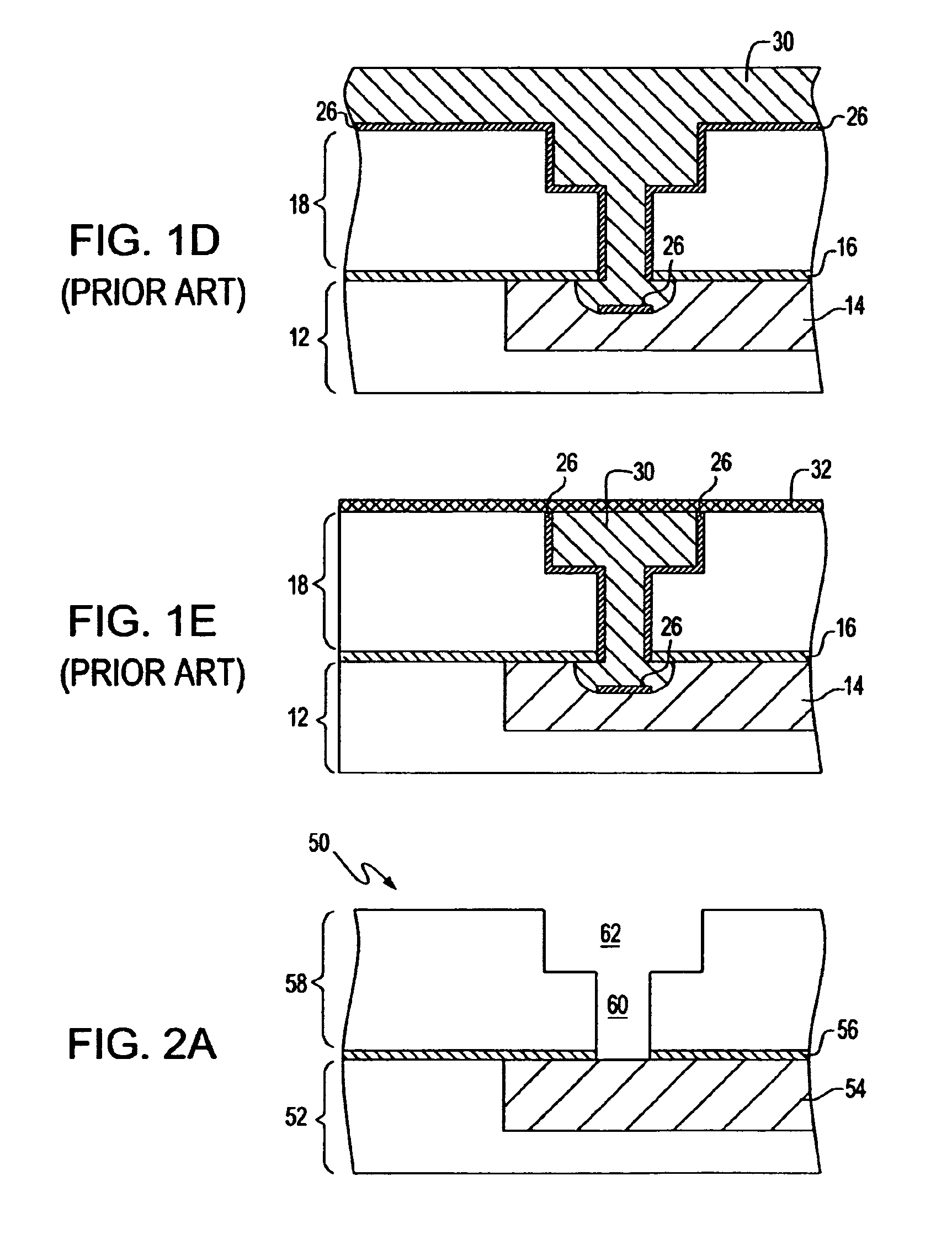

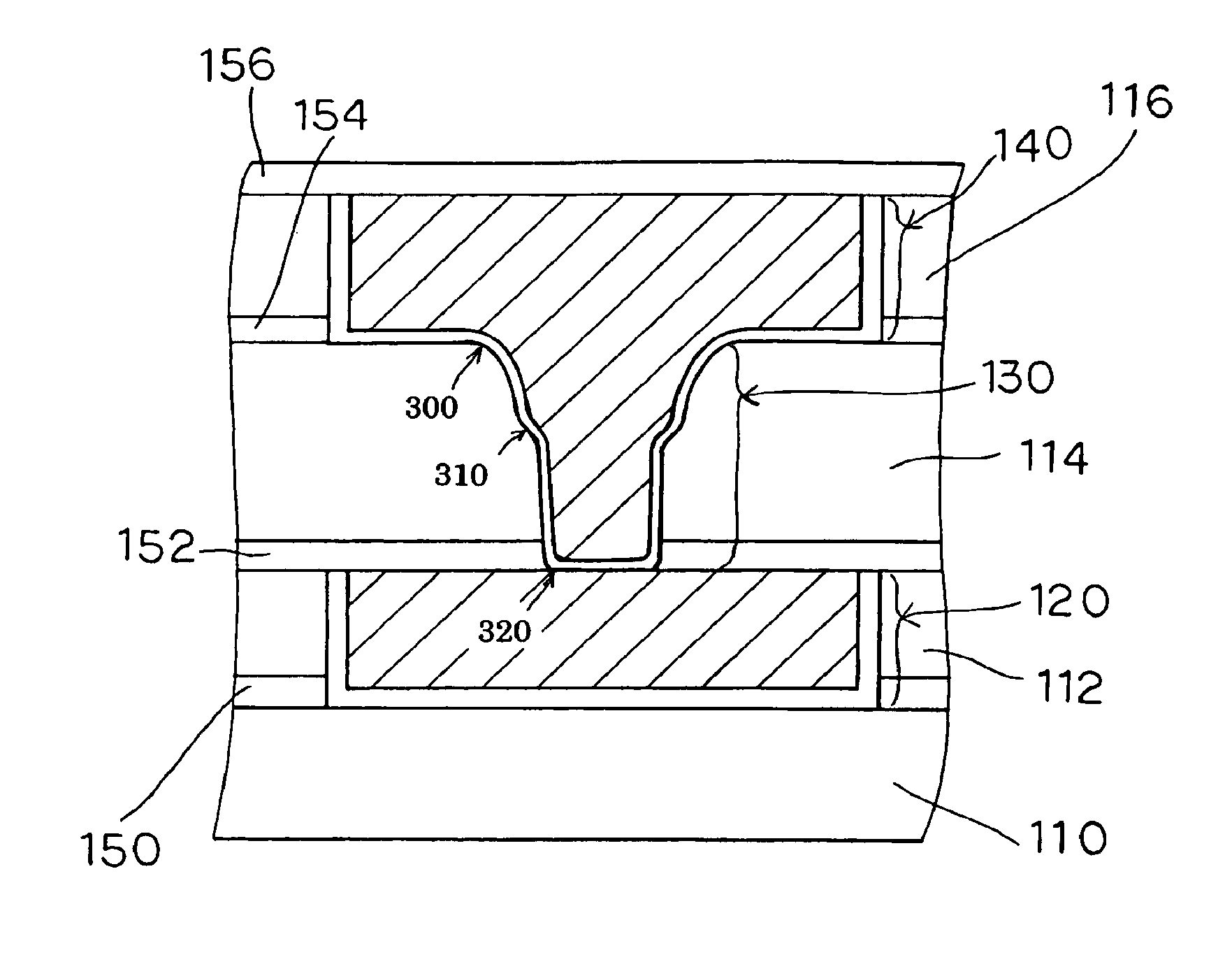

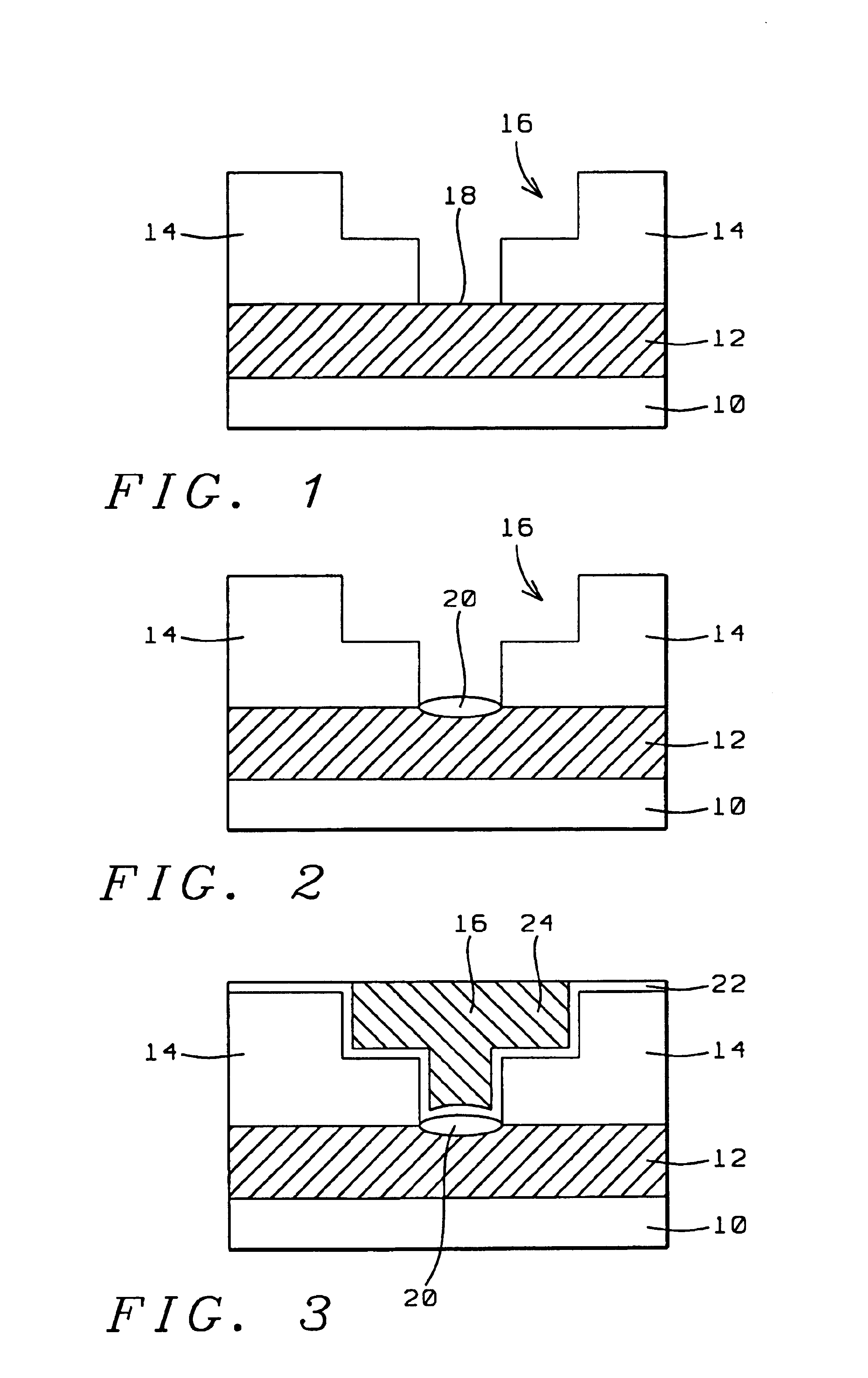

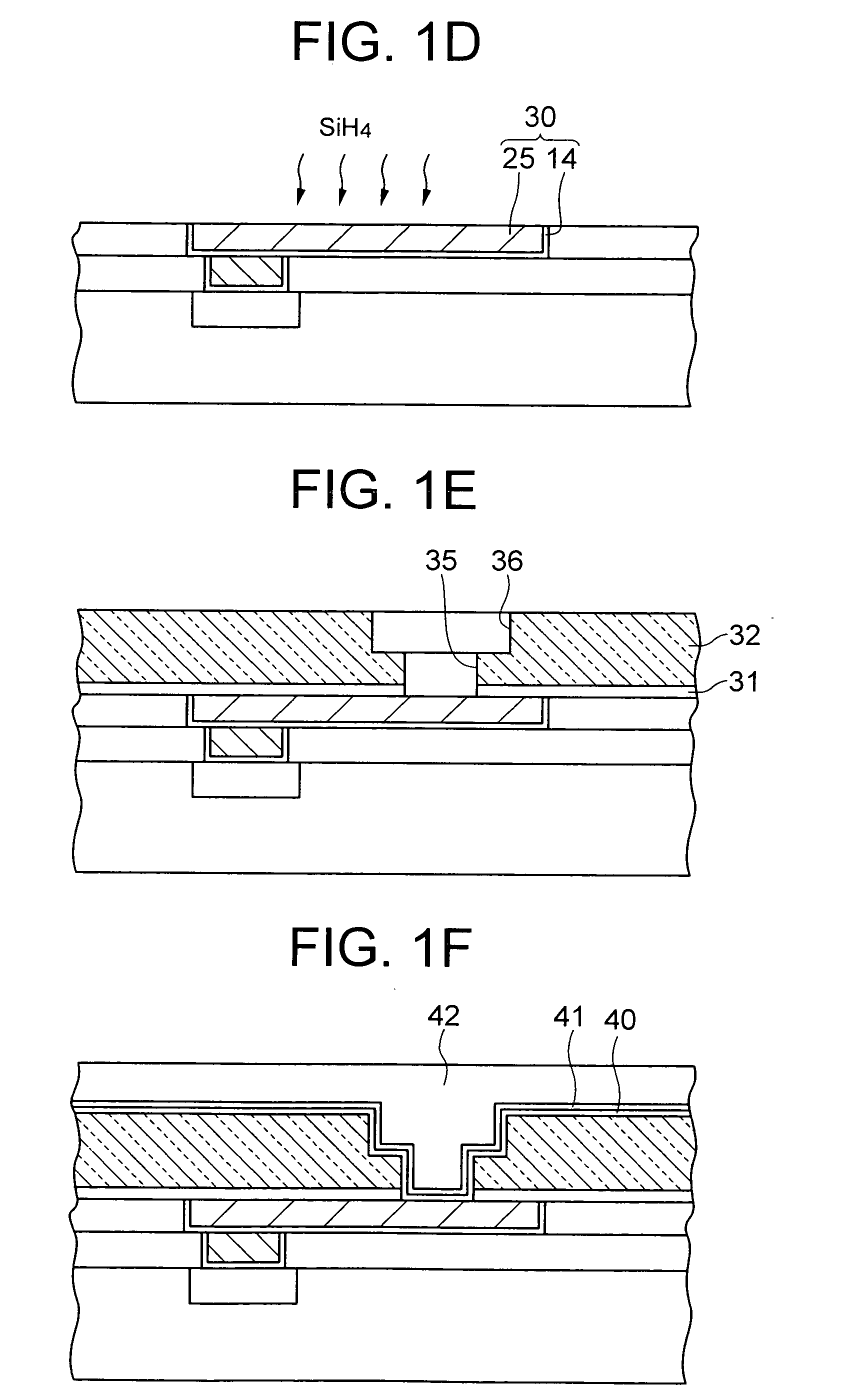

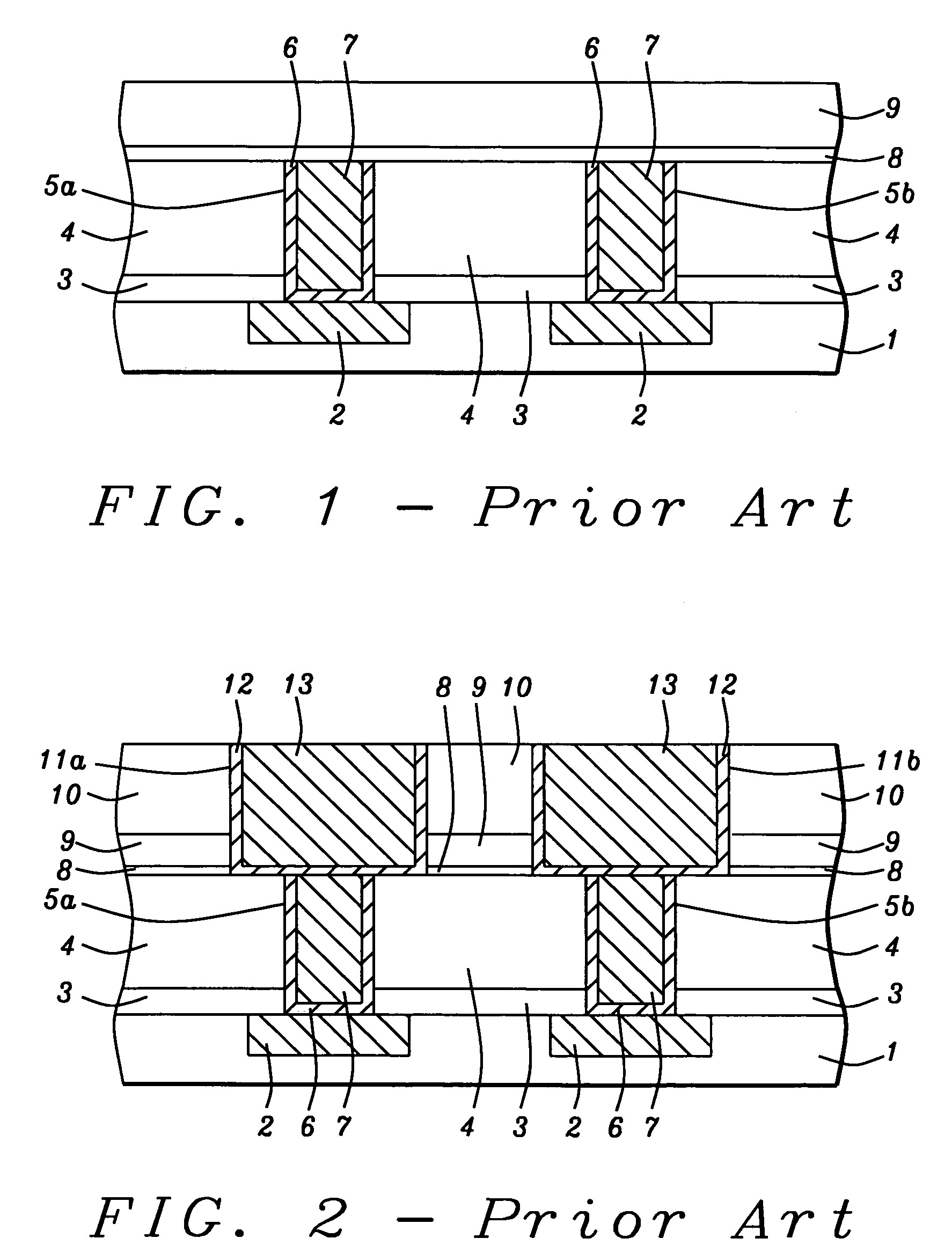

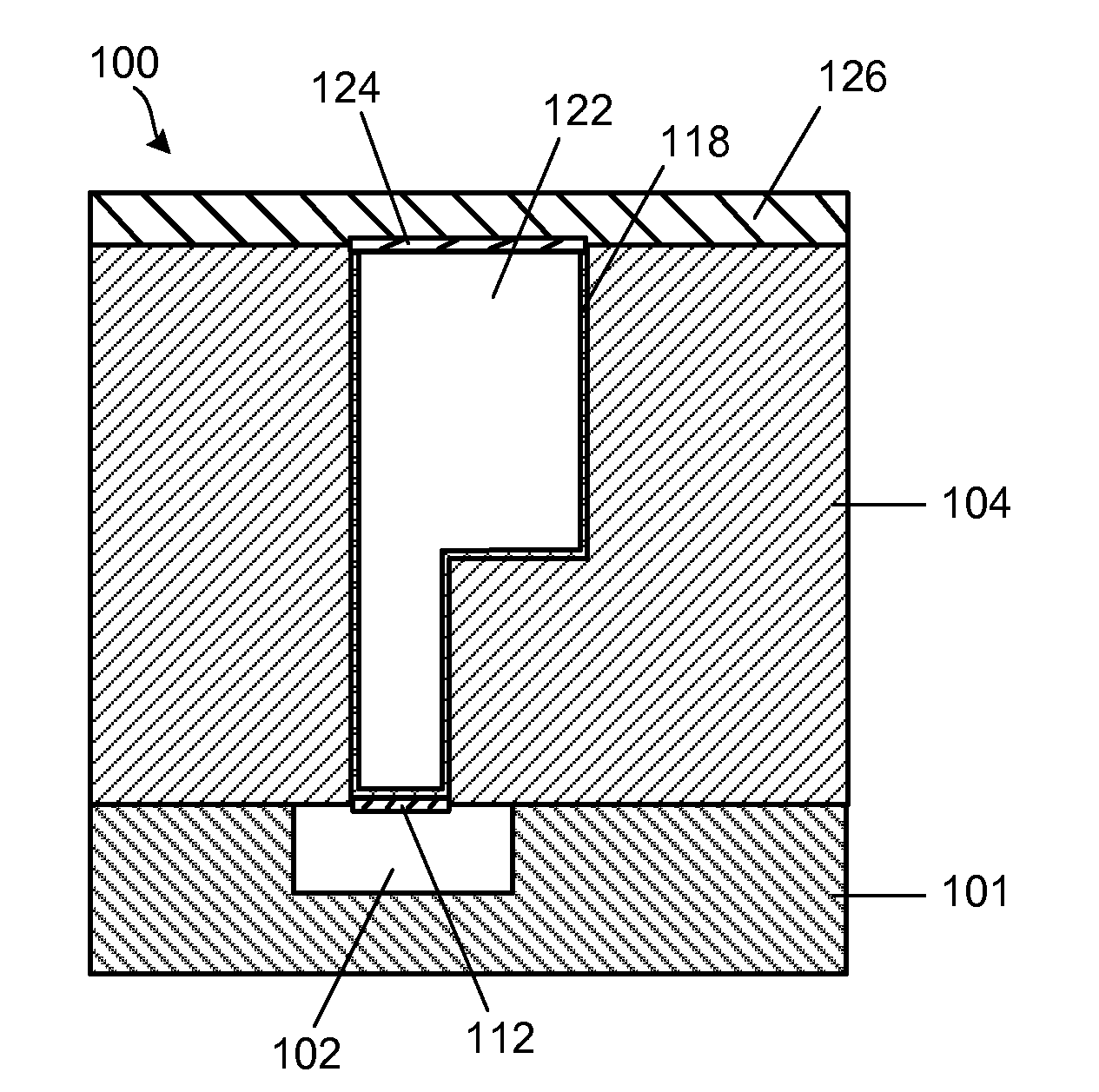

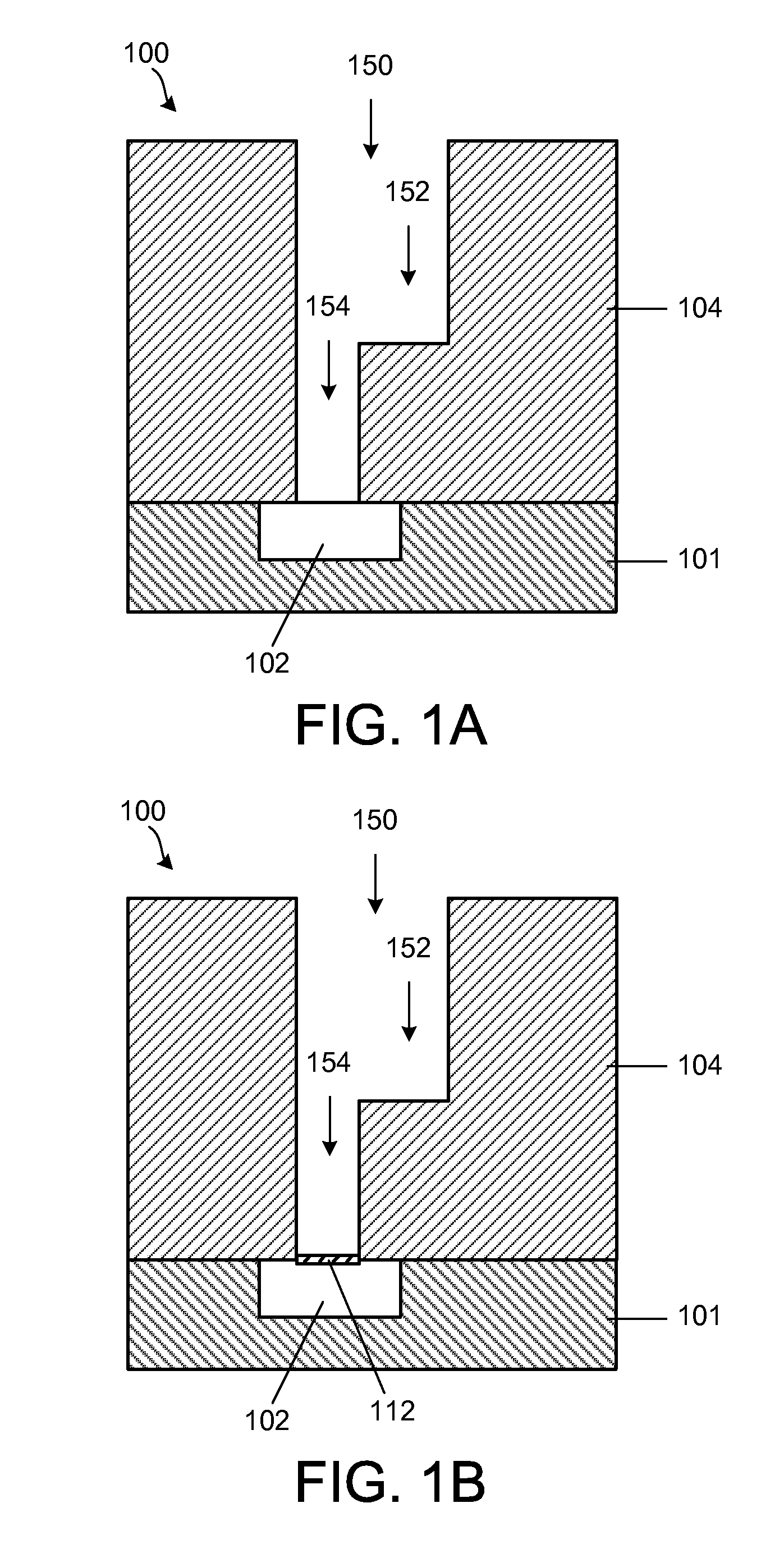

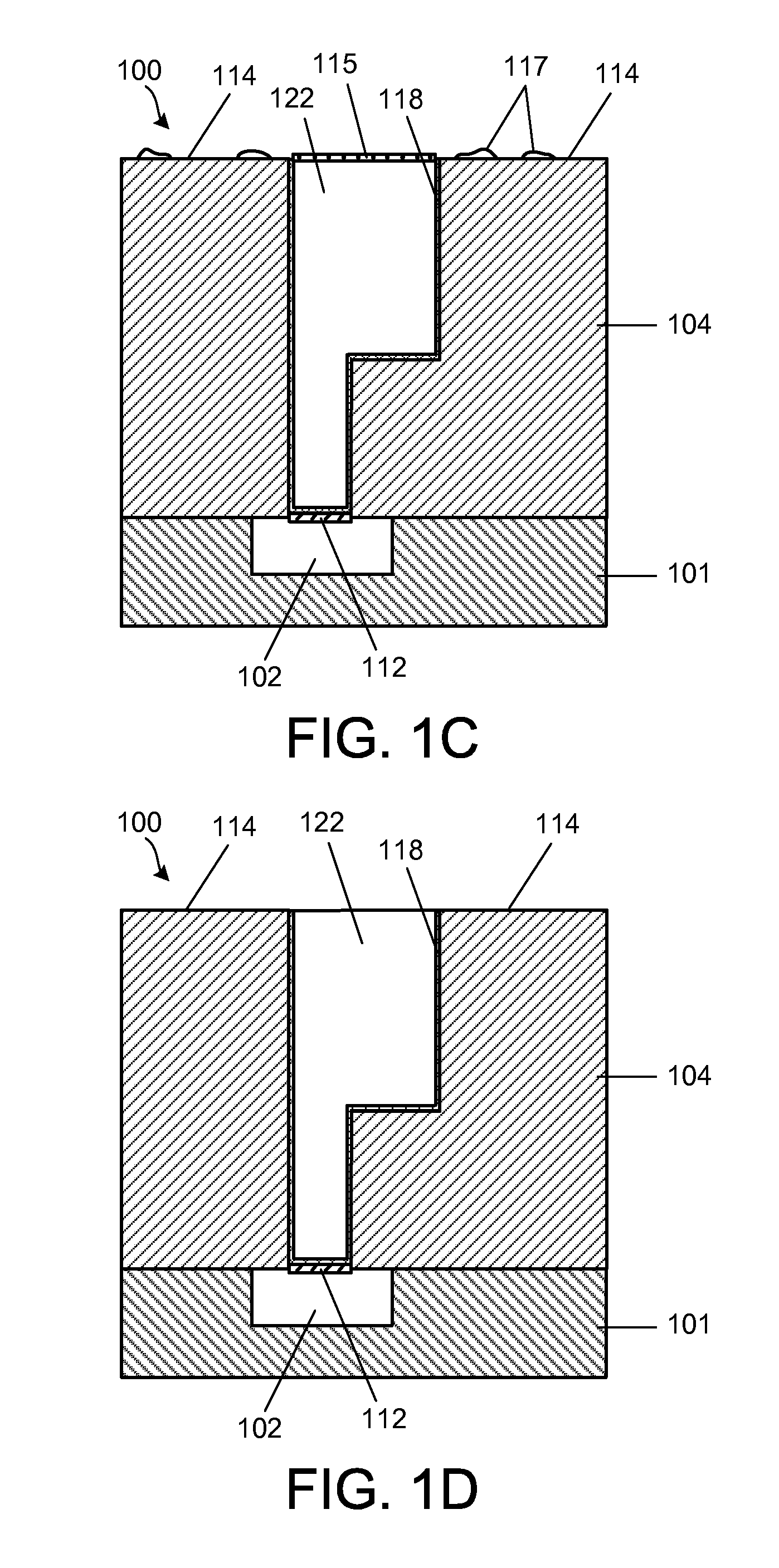

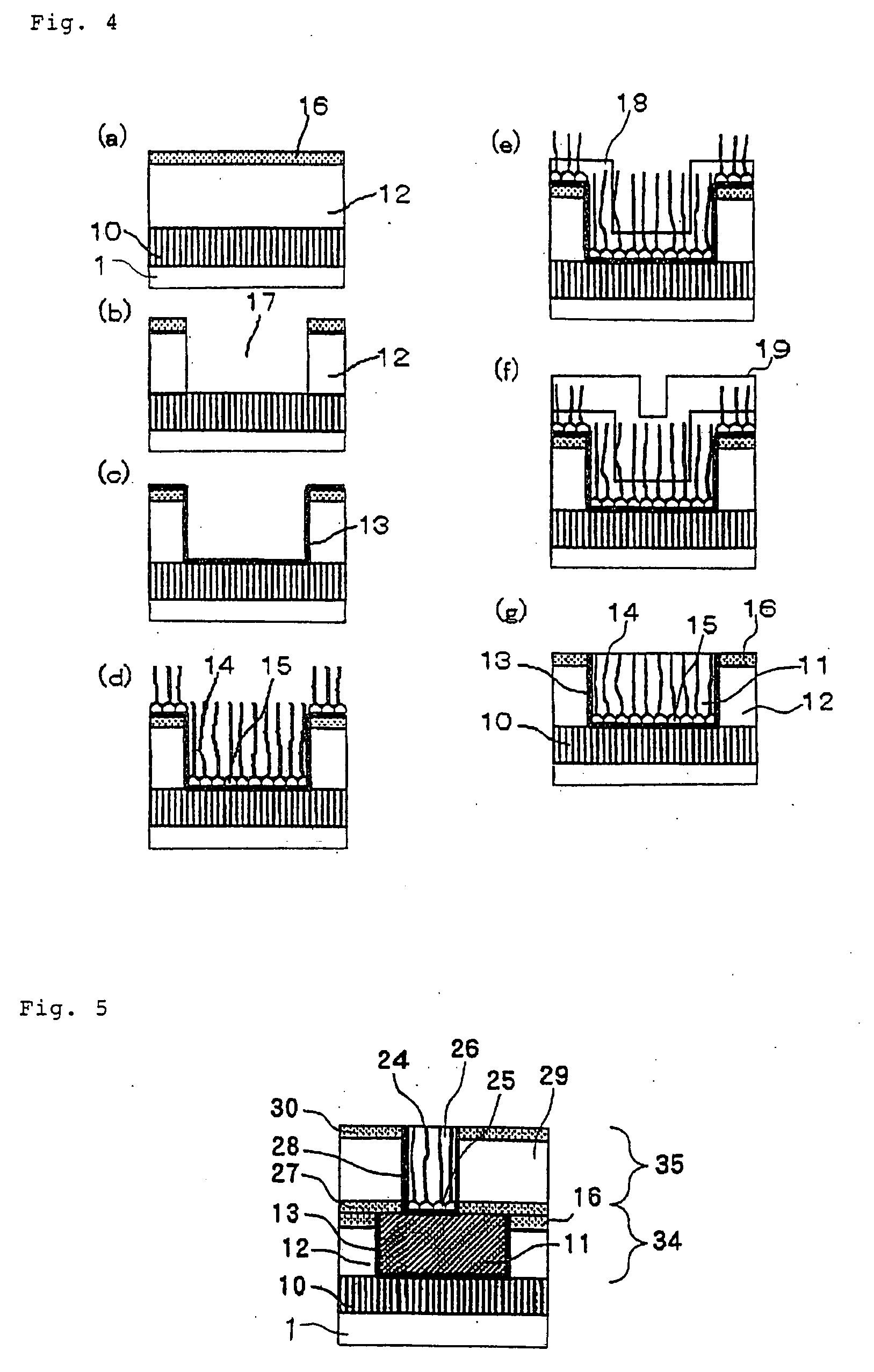

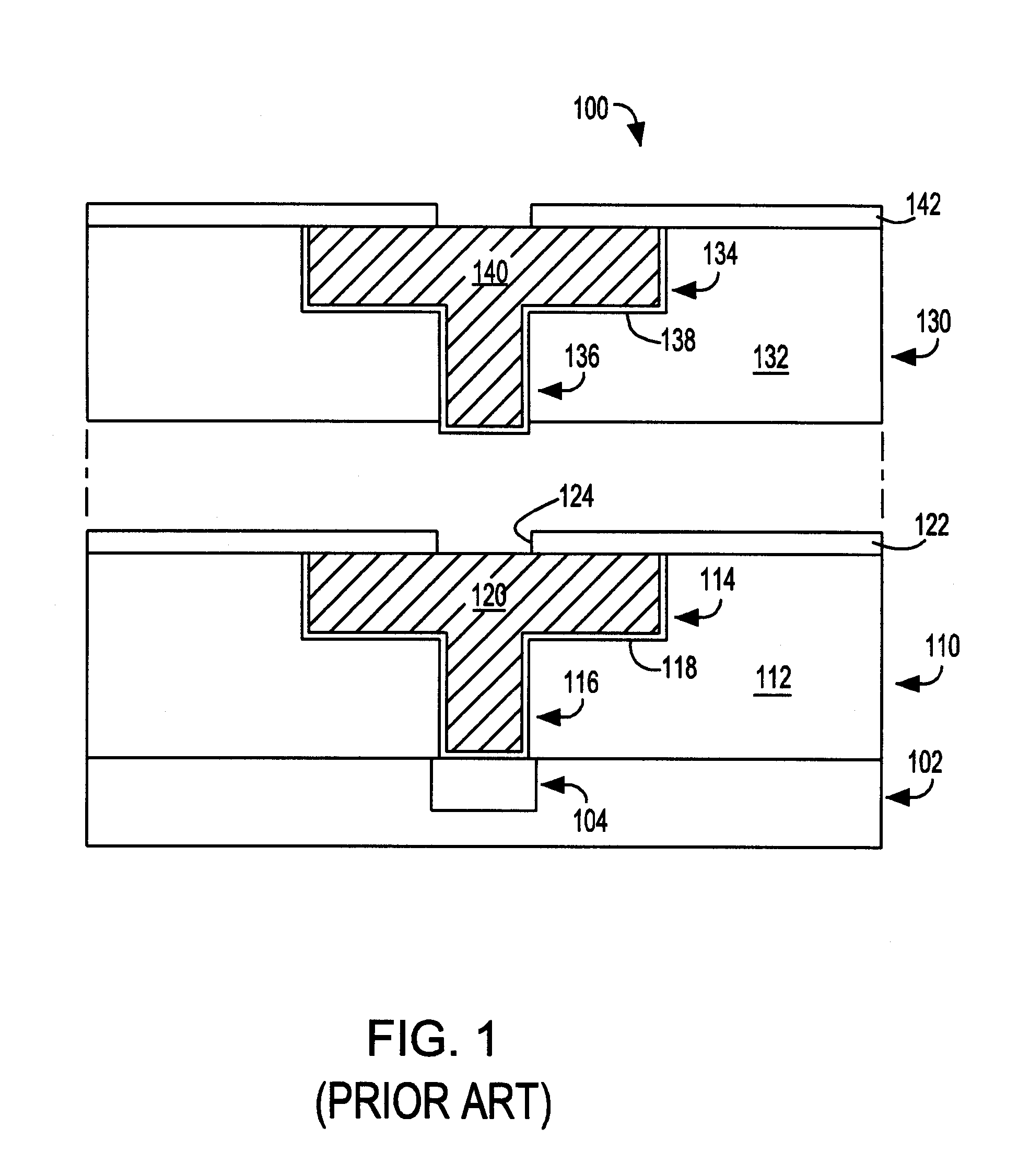

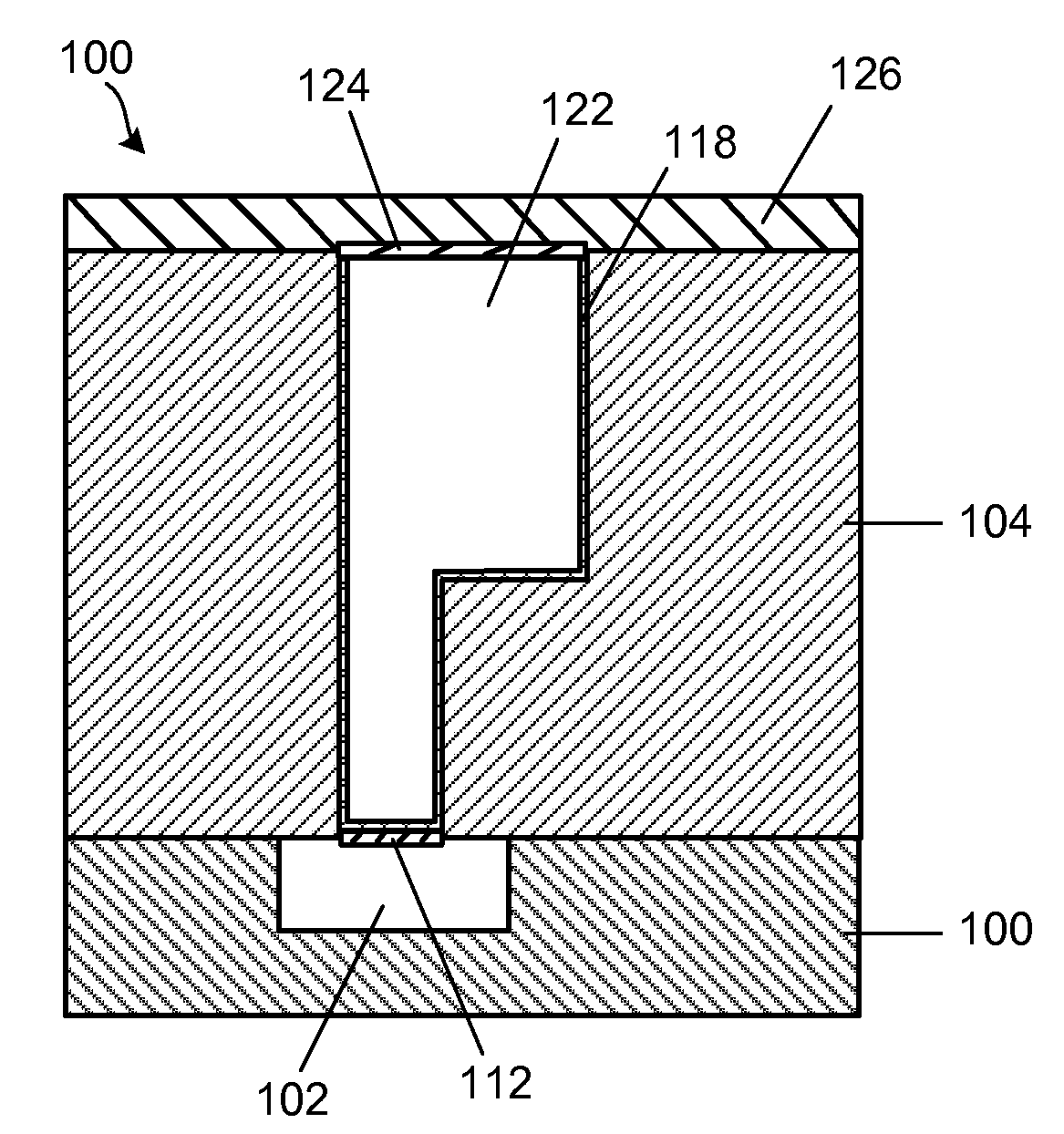

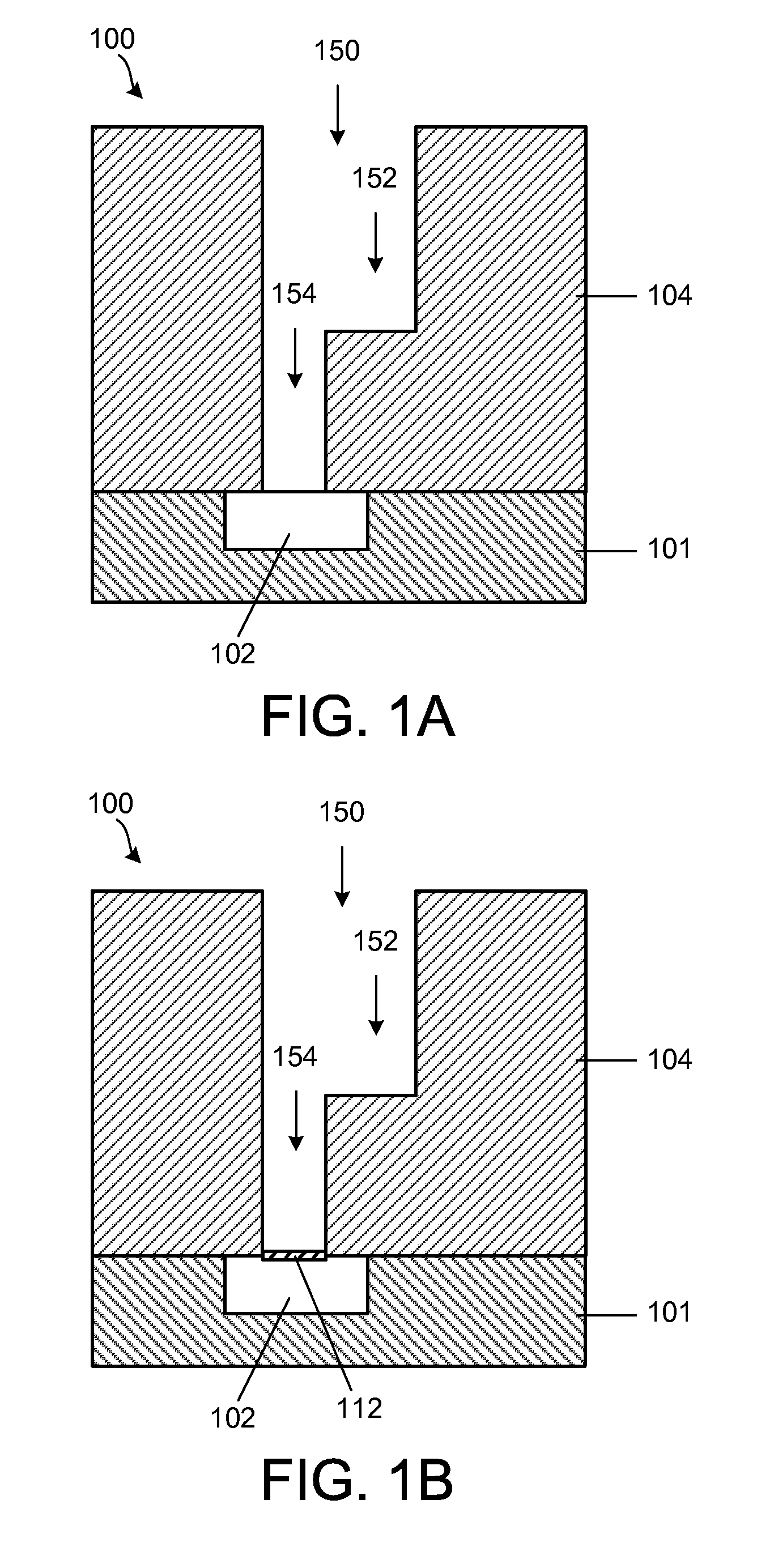

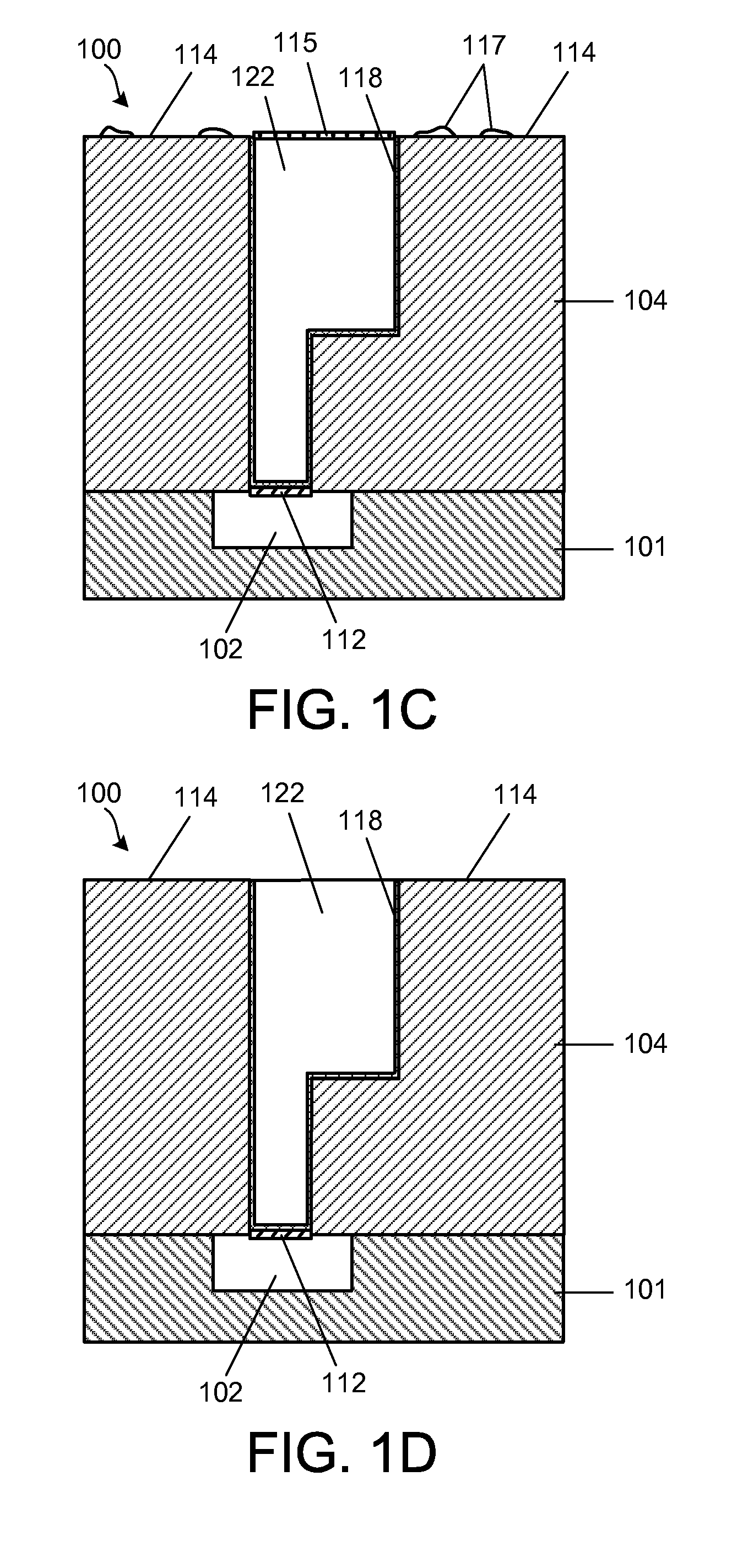

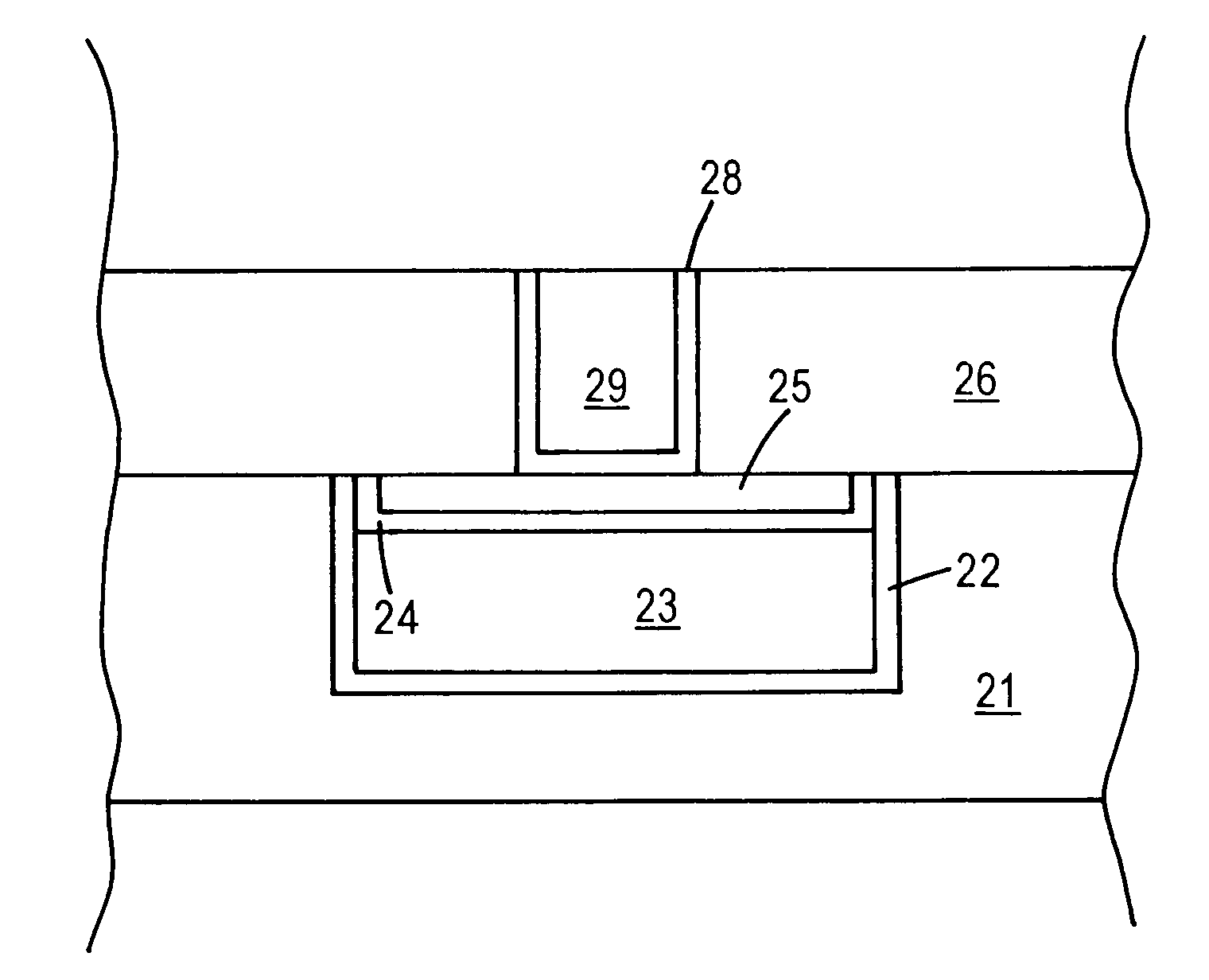

Structure and method of chemically formed anchored metallic vias

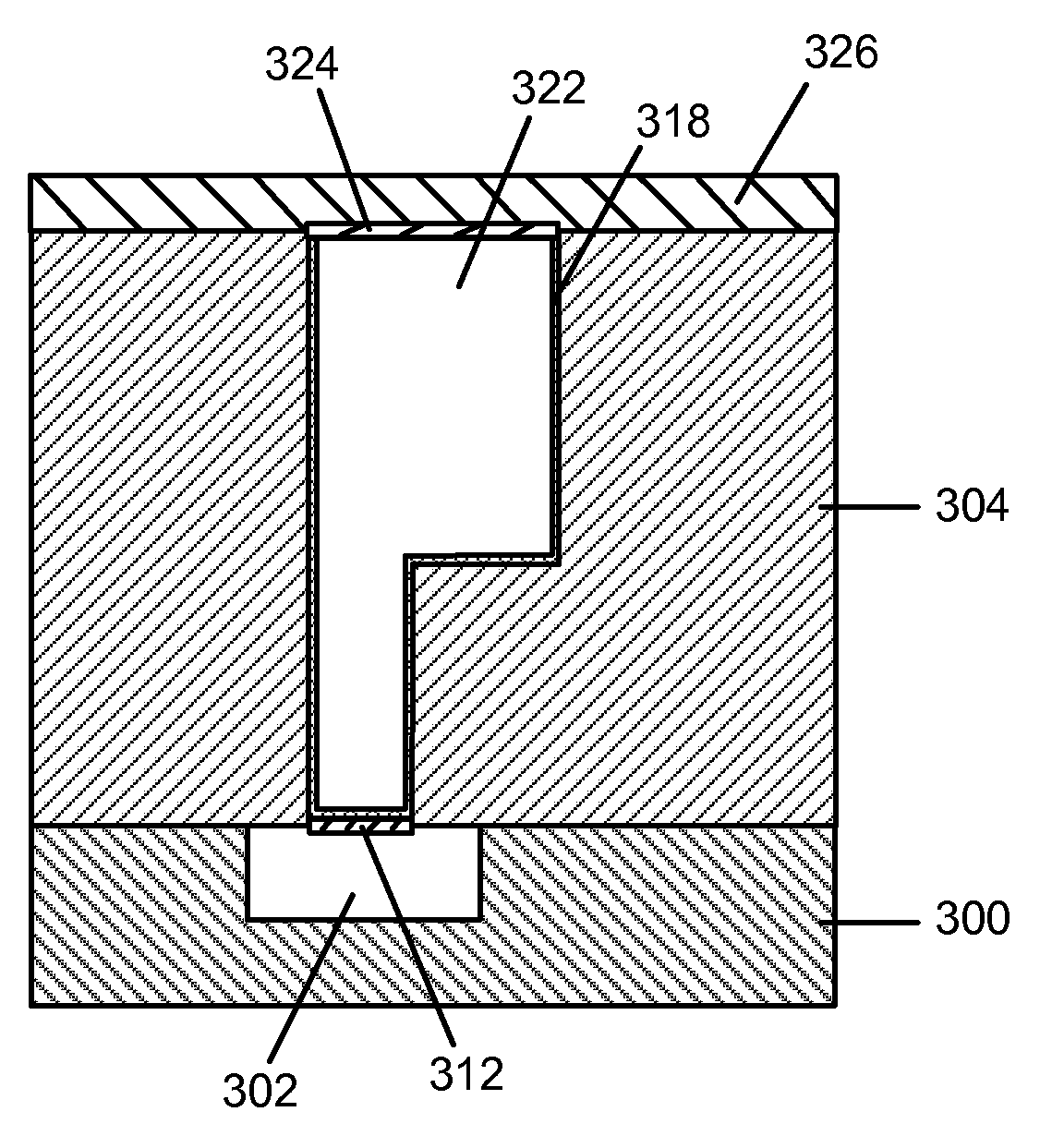

ActiveUS20080012142A1Improve reliabilityHigh stress migrationSemiconductor/solid-state device detailsSolid-state devicesCompound (substance)High stress

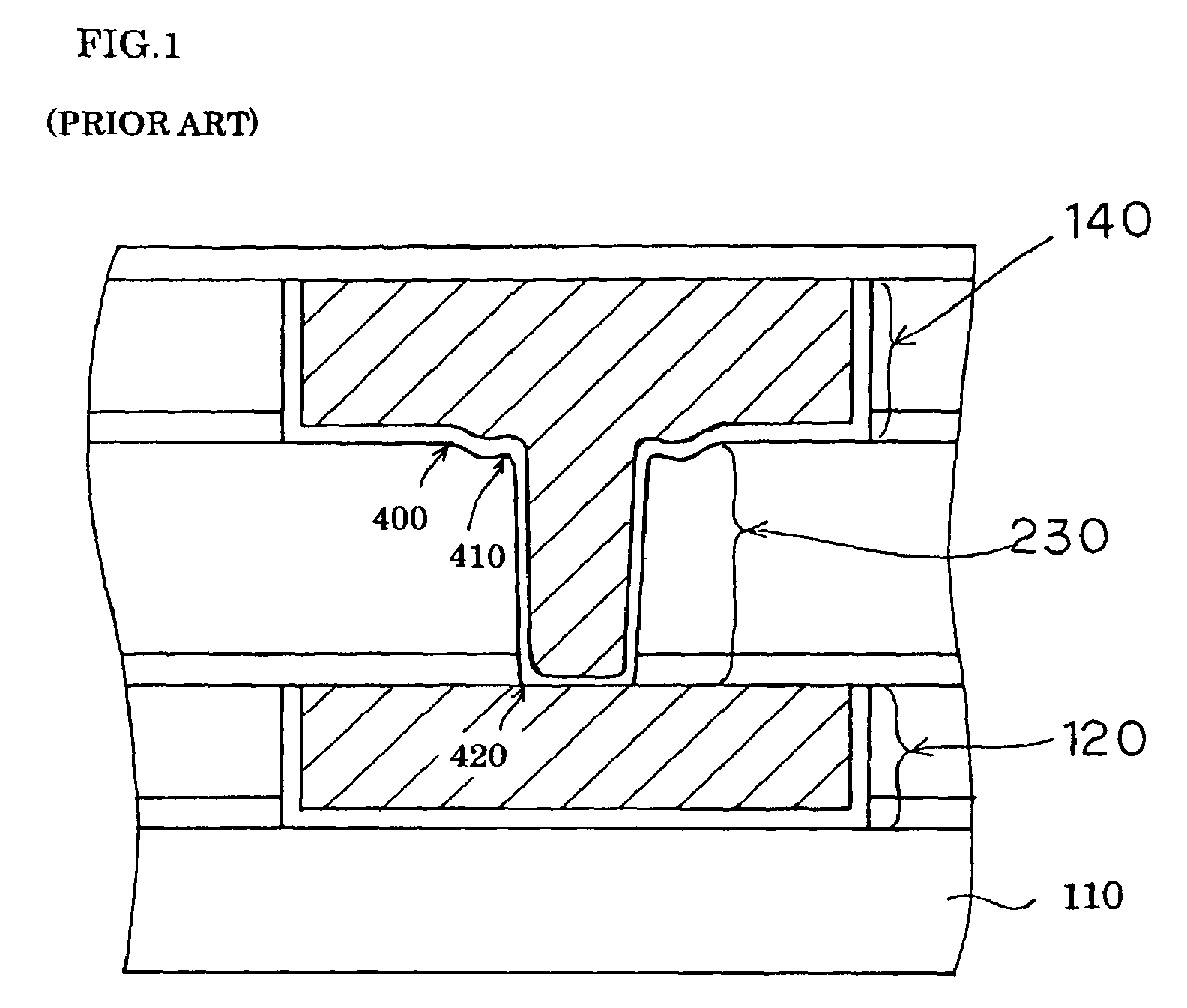

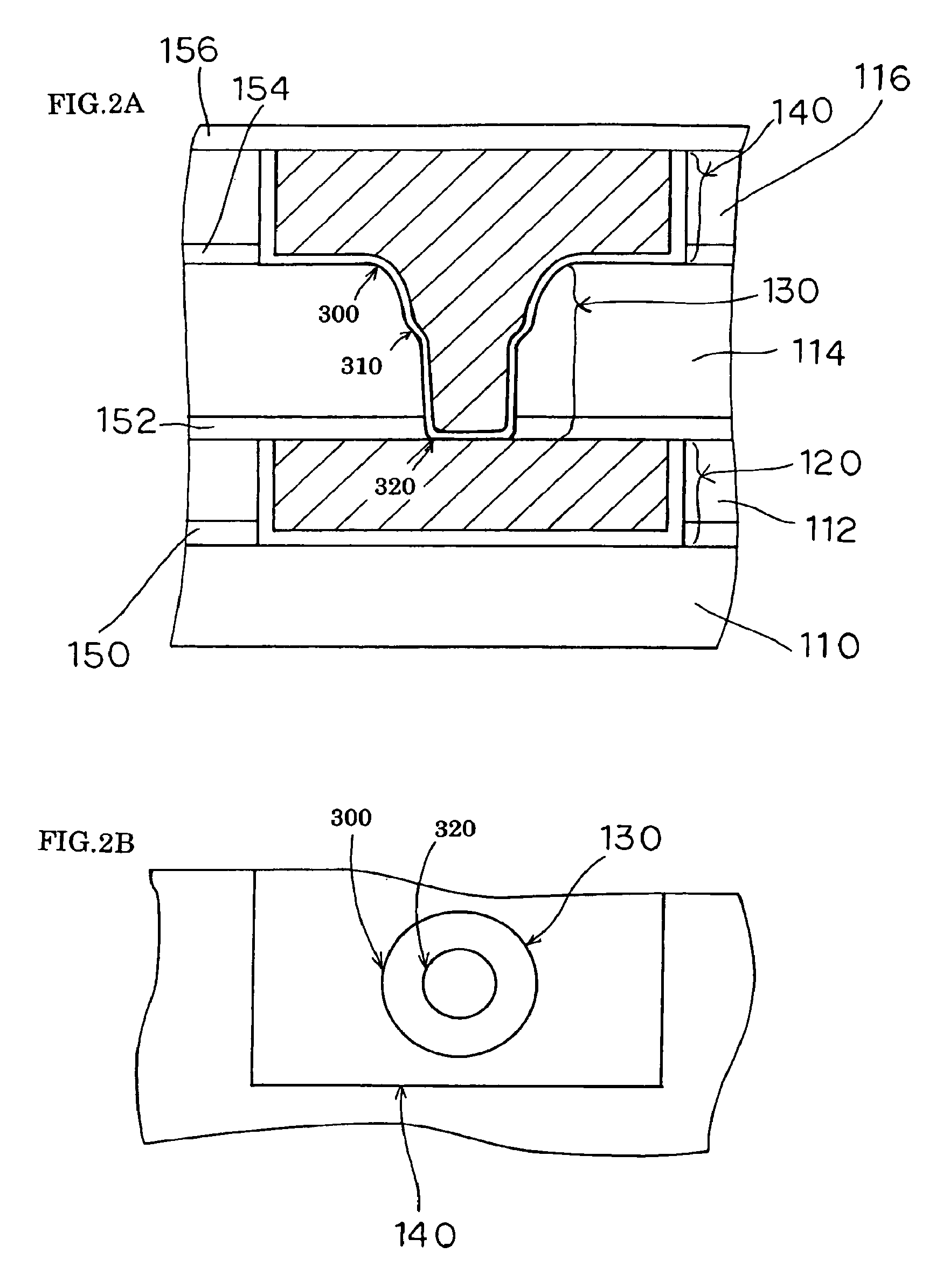

Methods are provided that enable the ability to use a less aggressive liner processes, while producing structures known to give a desired high stress migration and electro-migration reliability. The present invention circumvents the issue of sputter damage of low k (on the order of 3.2 or less) dielectric by creating the via “anchors” (interlocked and interpenetrated vias) through chemical means. This allows the elimination or significant reduction of the sputter-etching process used to create the via penetration (“drilling, gouging”) into the line below in the barrier / seed metallization step. The present invention achieves the above, while maintaining a reliable copper fill and device structure.

Owner:GLOBALFOUNDRIES US INC

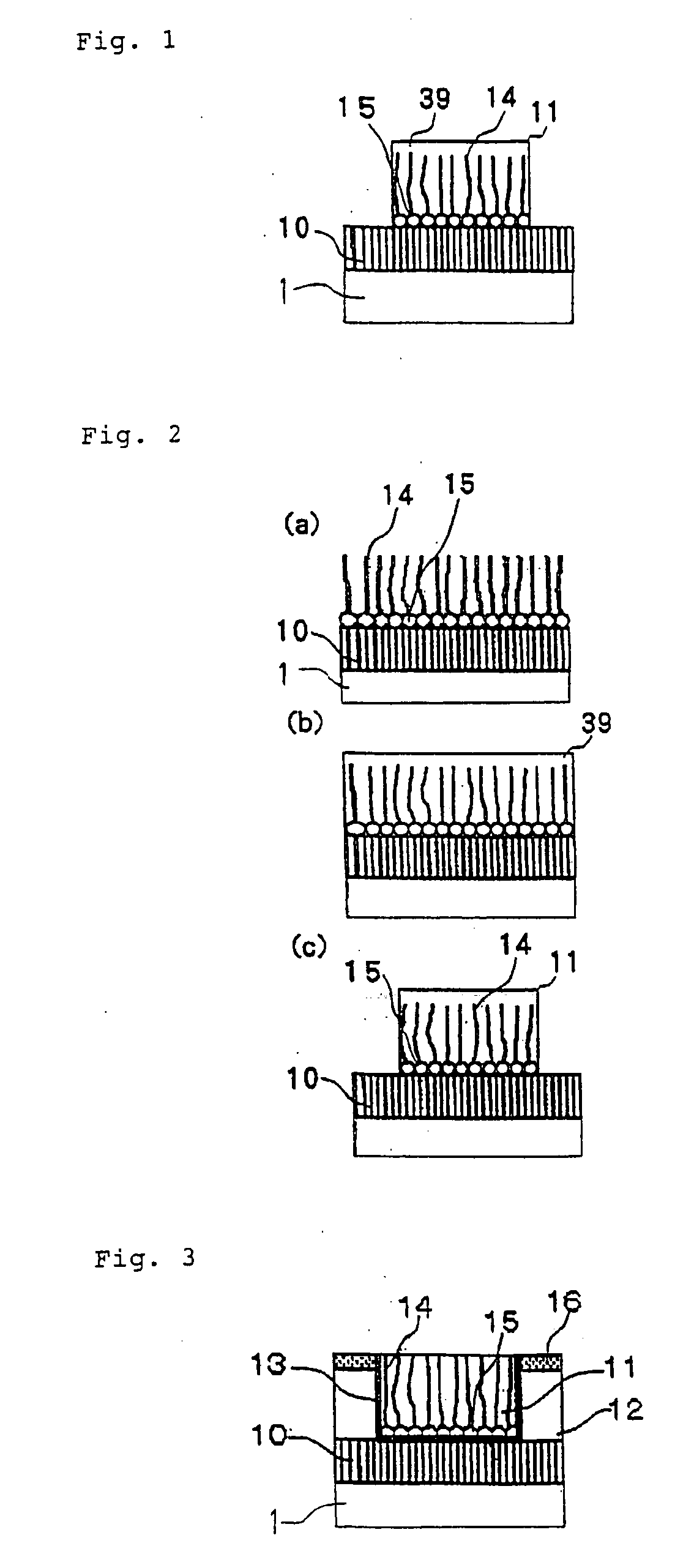

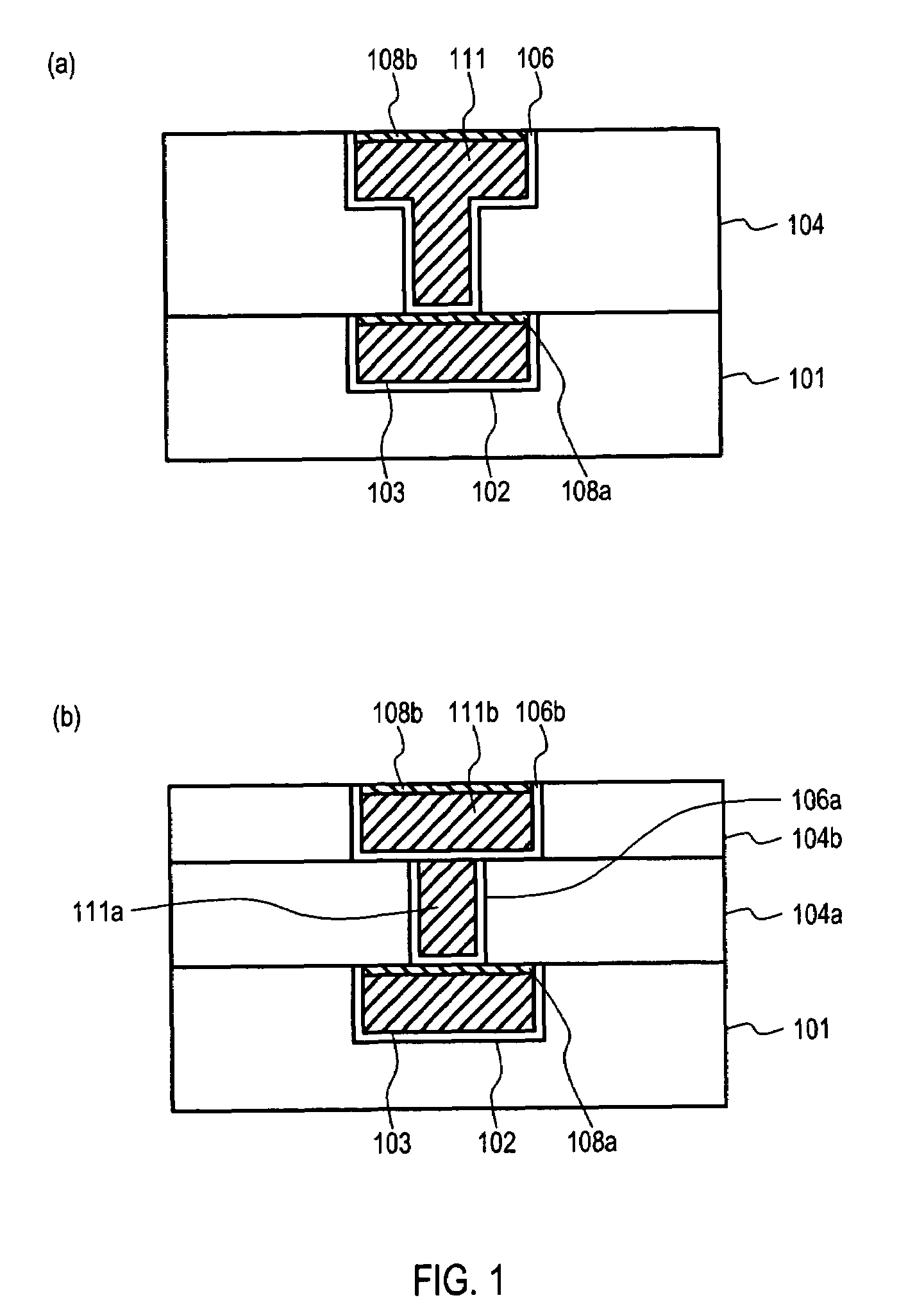

Semiconductor device and method for manufacturing same

ActiveUS20040130030A1Semiconductor/solid-state device detailsSolid-state devicesCopper interconnectMetal interconnect

The present invention provides a semiconductor device comprising a metal interconnect having considerably improved electromigration resistance and / or stress migration resistance. The copper interconnect 107 comprises a silicon-lower concentration region 104 and a silicon solid solution layer 106 disposed thereon. The silicon solid solution layer 106 has a structure, in which silicon atoms are introduced within the crystal lattice structure that constitutes the copper interconnect 107 to be disposed within the lattice as inter-lattice point atoms or substituted atoms. The silicon solid solution layer 106 has the structure, in which the crystal lattice structure of copper (face centered cubic lattice; lattice constant is 3.6 angstrom) remains, while silicon atoms are introduced as inter-lattice point atoms or substituted atoms.

Owner:RENESAS ELECTRONICS CORP

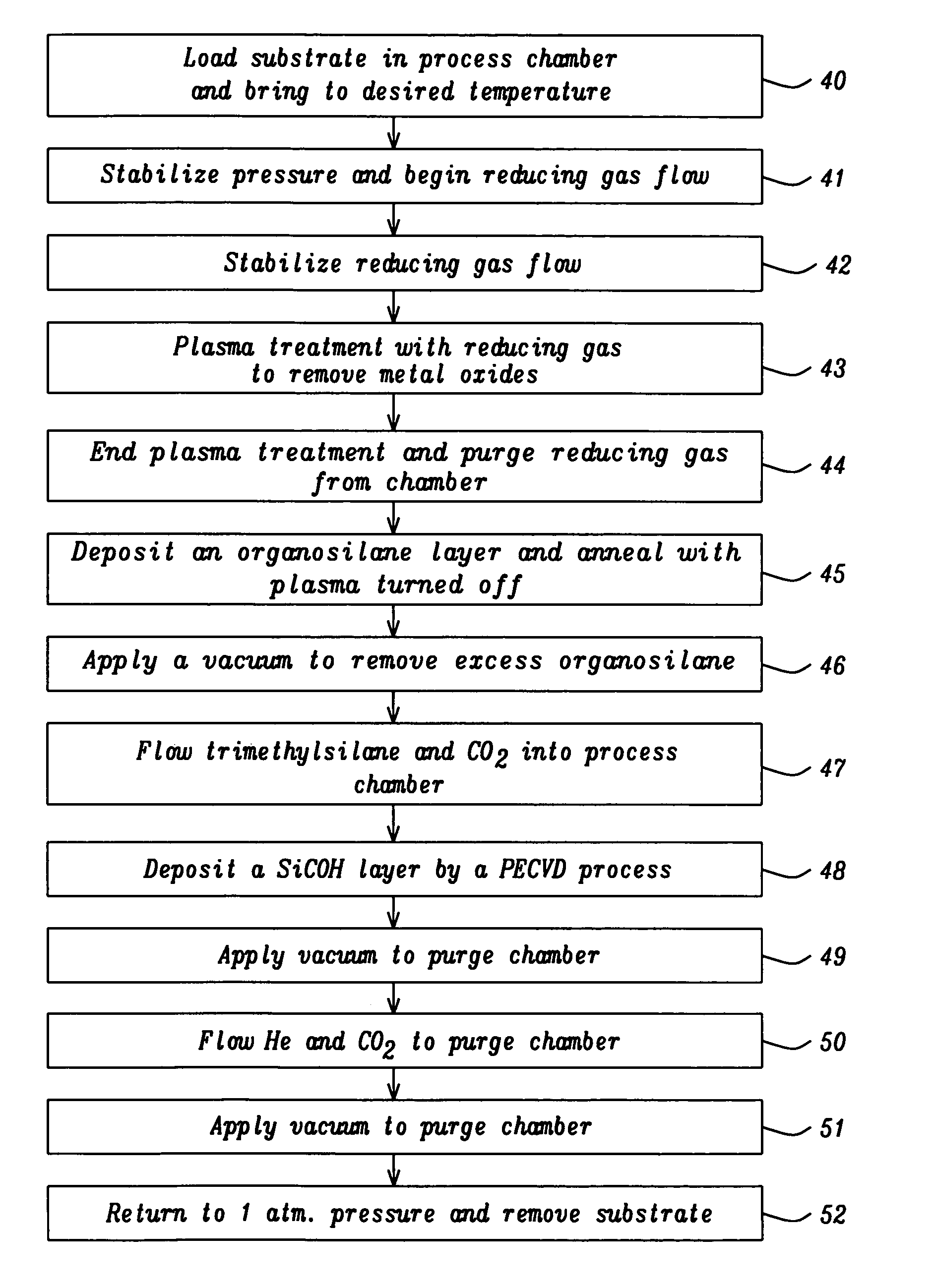

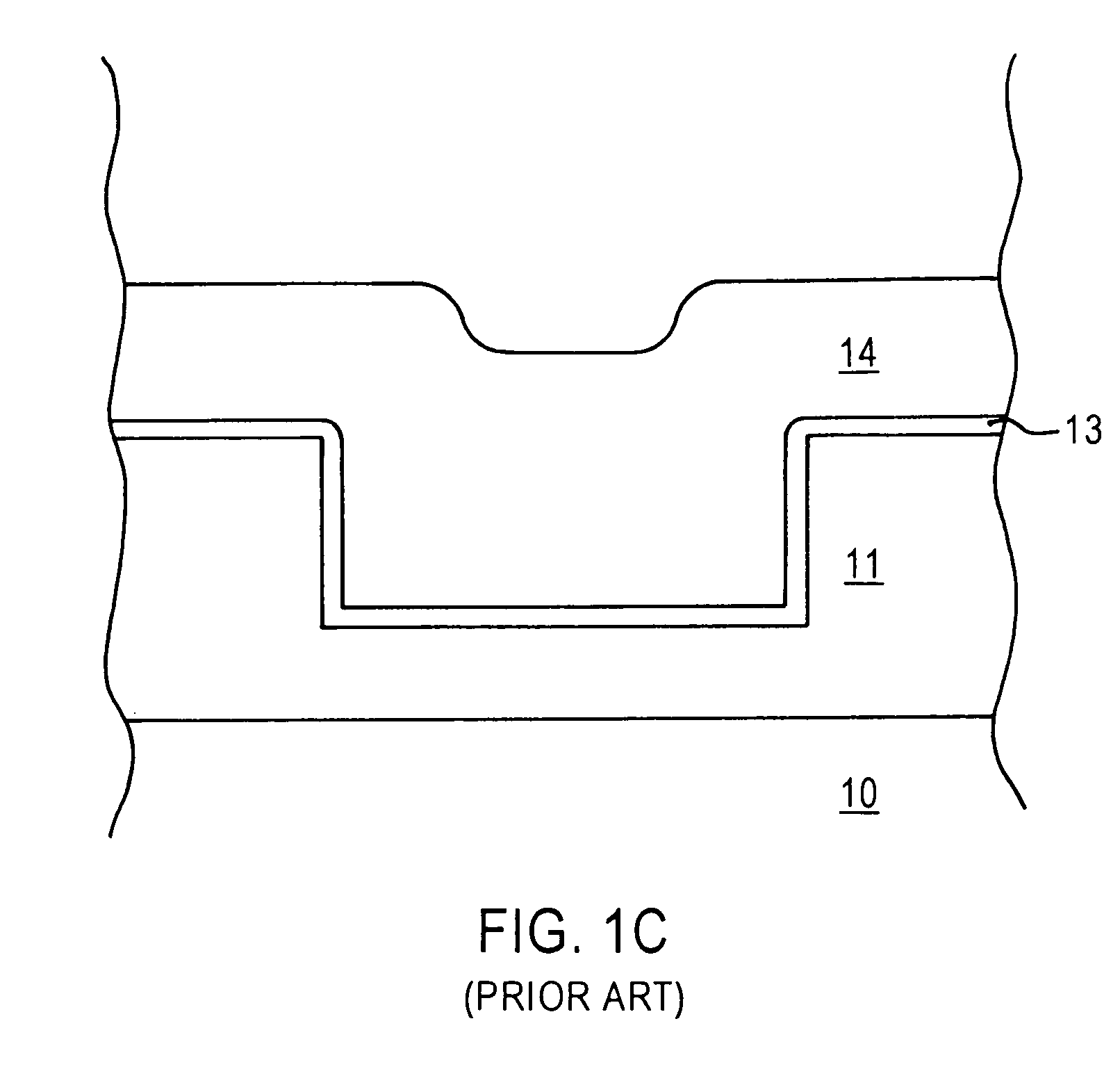

Reliability improvement of SiOC etch with trimethylsilane gas passivation in Cu damascene interconnects

InactiveUS20050245100A1Reduce leakage currentImprove throughputSemiconductor/solid-state device detailsSolid-state devicesTrimethylsilaneLow leakage

A method of forming a SiCOH etch stop layer in a copper damascene process is described. A substrate with an exposed metal layer is treated with H2 or NH3 plasma to remove metal oxides. Trimethylsilane is flowed into a chamber with no RF power at about 350° C. to form at least a monolayer on the exposed metal layer. The SiCOH layer is formed by a PECVD process including trimethylsilane and CO2 source gases. Optionally, a composite SiCOH layer comprised of a low compressive stress layer on a high compressive stress layer is formed on the substrate. A conventional damascene sequence is then used to form a second metal layer on the exposed metal layer. Via Rc stability is improved and a lower leakage current is achieved with the trimethylsilane passivation layer. A composite SiCOH etch stop layer provides improved stress migration resistance compared to a single low stress SiCOH layer.

Owner:TAIWAN SEMICON MFG CO LTD

Structure and method of chemically formed anchored metallic vias

ActiveUS7517736B2High stress migrationElimination significantSemiconductor/solid-state device detailsSolid-state devicesHigh stressMaterials science

Methods are provided that enable the ability to use a less aggressive liner processes, while producing structures known to give a desired high stress migration and electro-migration reliability. The present invention circumvents the issue of sputter damage of low k (on the order of 3.2 or less) dielectric by creating the via “anchors” (interlocked and interpenetrated vias) through chemical means. This allows the elimination or significant reduction of the sputter-etching process used to create the via penetration (“drilling, gouging”) into the line below in the barrier / seed metallization step. The present invention achieves the above, while maintaining a reliable copper fill and device structure.

Owner:GLOBALFOUNDRIES US INC

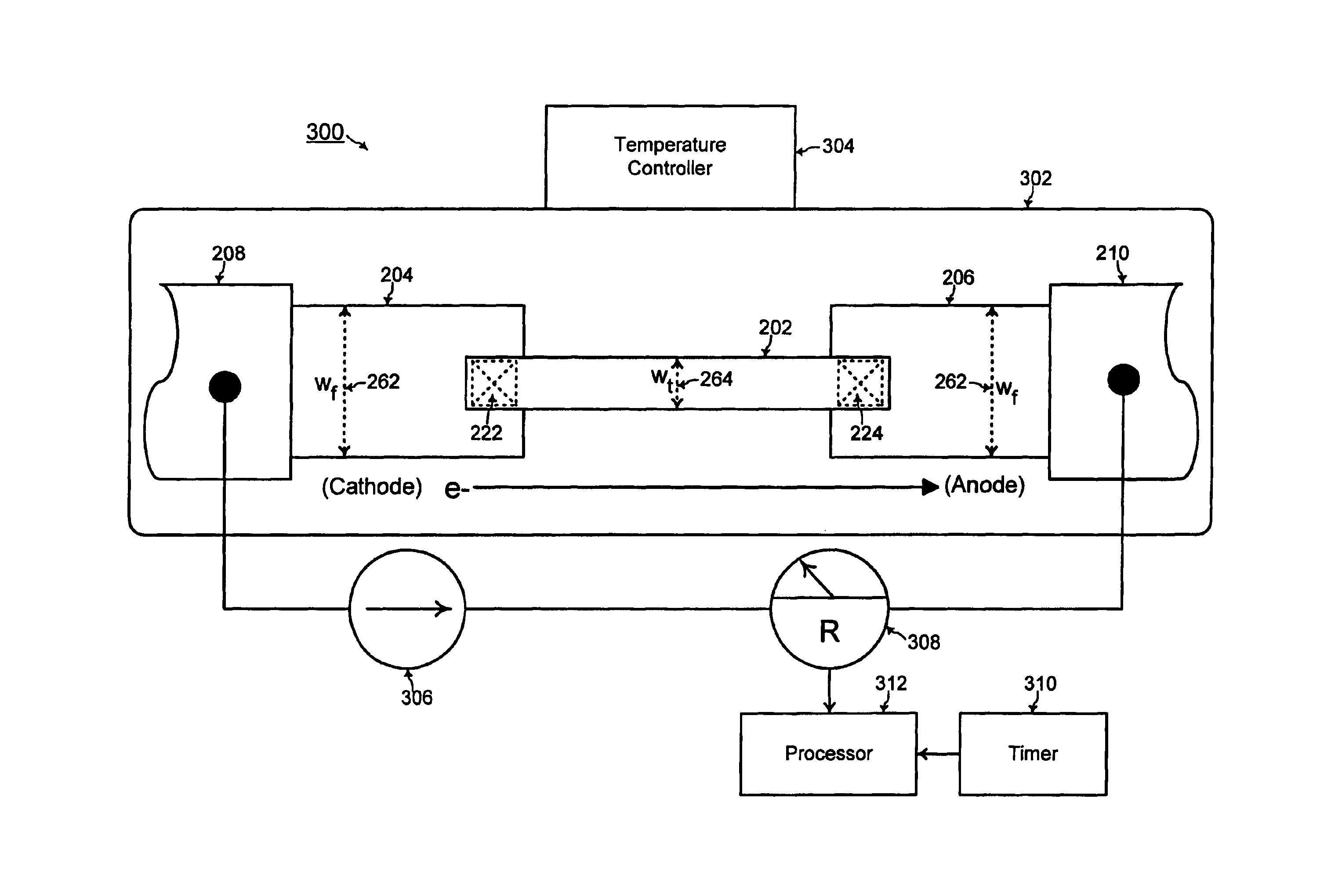

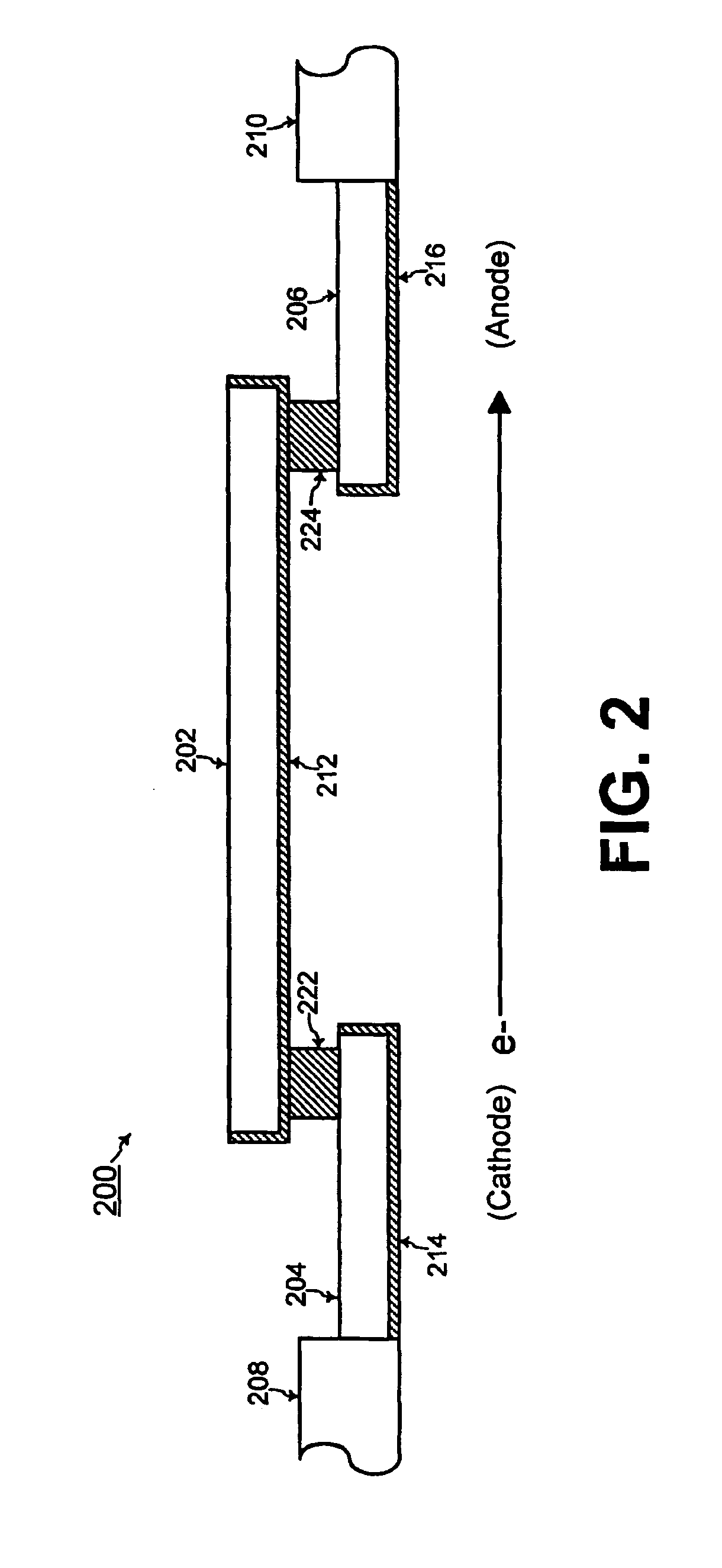

System and method for current-enhanced stress-migration testing of interconnect

InactiveUS6867056B1Reduces time to stress-migration failureShort stress-migration life-timeSemiconductor/solid-state device testing/measurementElectronic circuit testingLife timeTimer

For testing for stress-migration failure of interconnect, an interconnect test structure is formed with a first feeder line coupled to a test line by a first no-flux structure, and with a second feeder line coupled to the test line by a second no-flux structure. A respective width of ea ch of the first and second feeder lines is greater than a width of the test line. A resistance meter and a timer measure a stress-migration life-time of the interconnect test structure with a current being continuously conducted through the interconnect test structure that is continuously heated to a predetermined temperature.

Owner:ADVANCED MICRO DEVICES INC

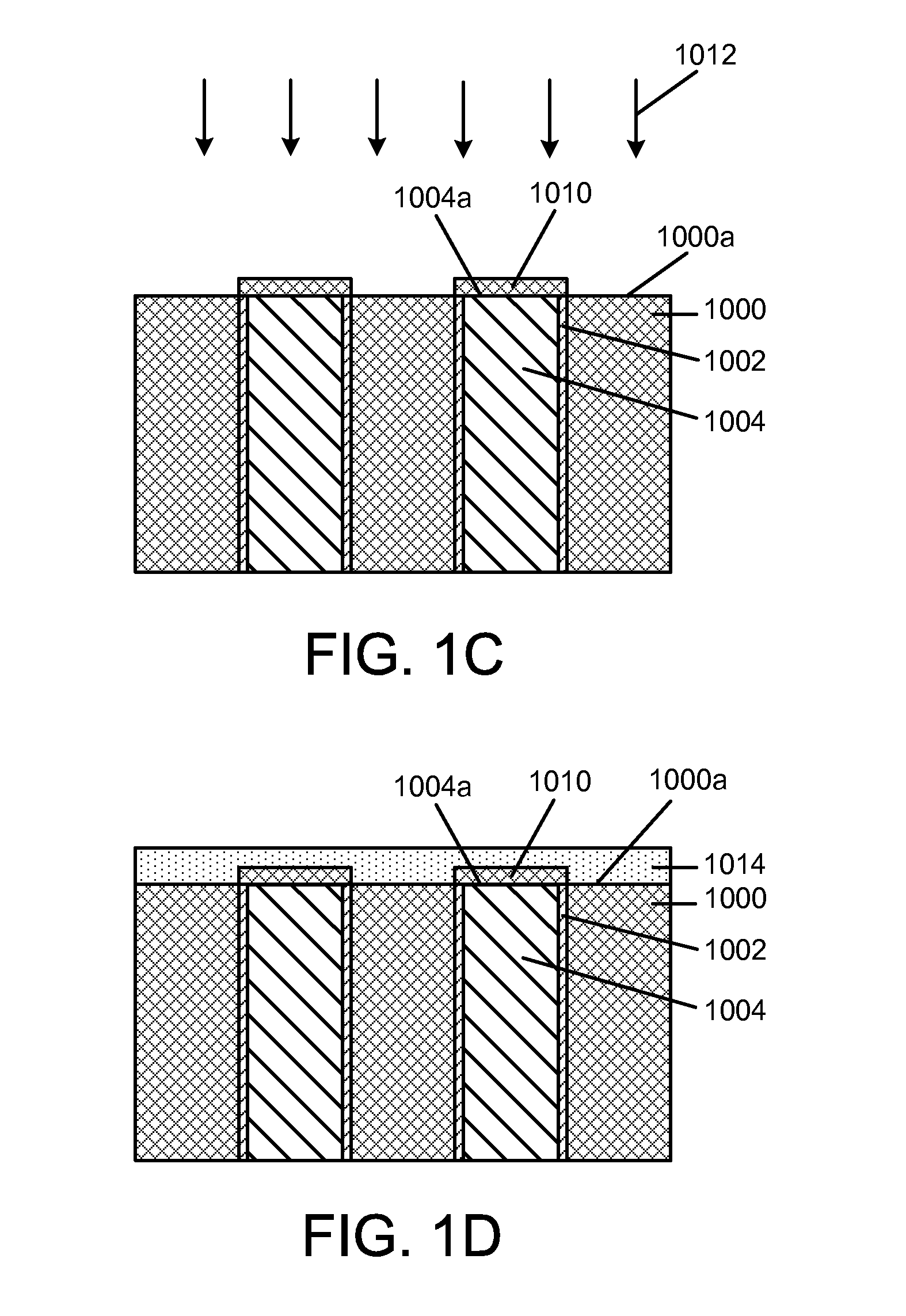

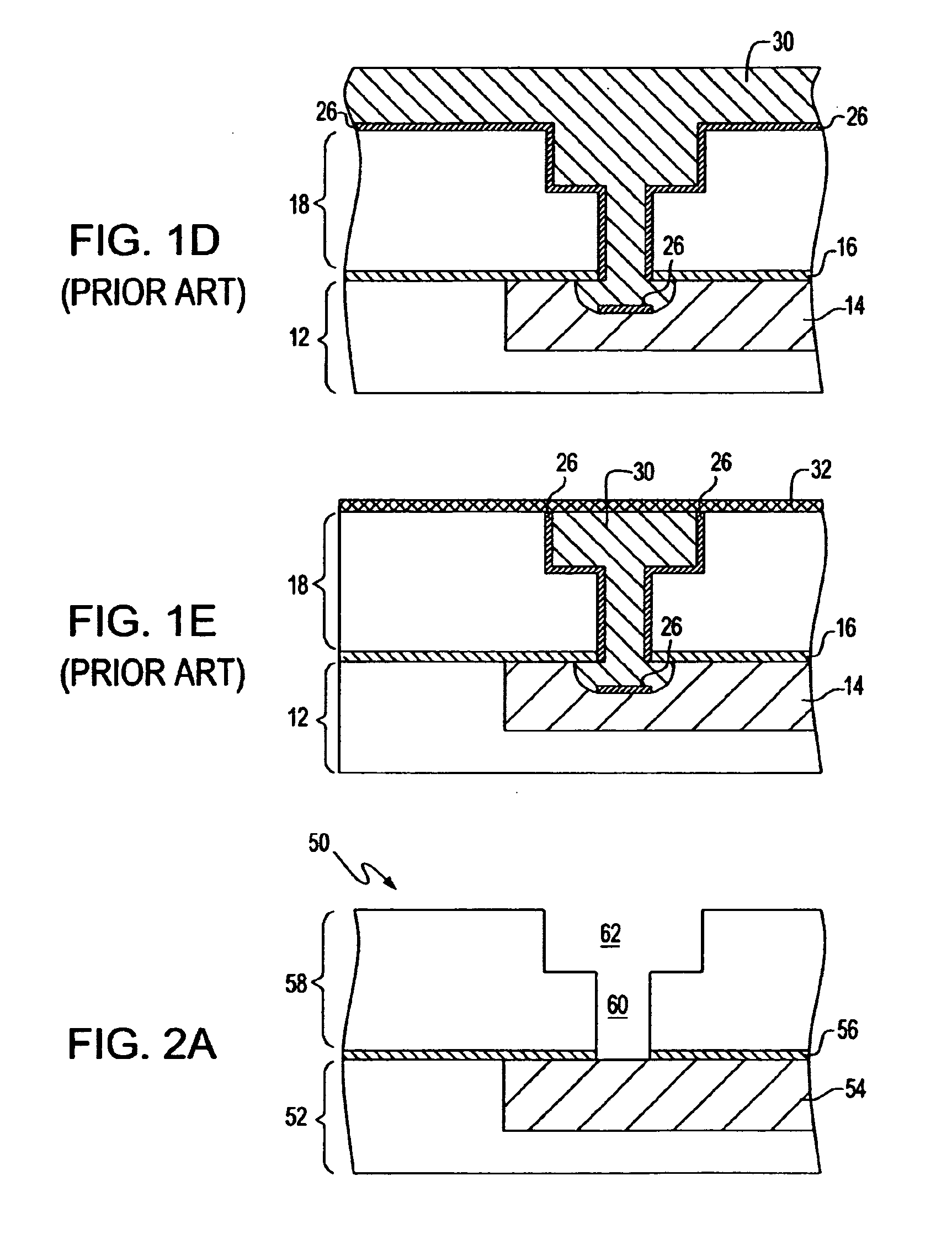

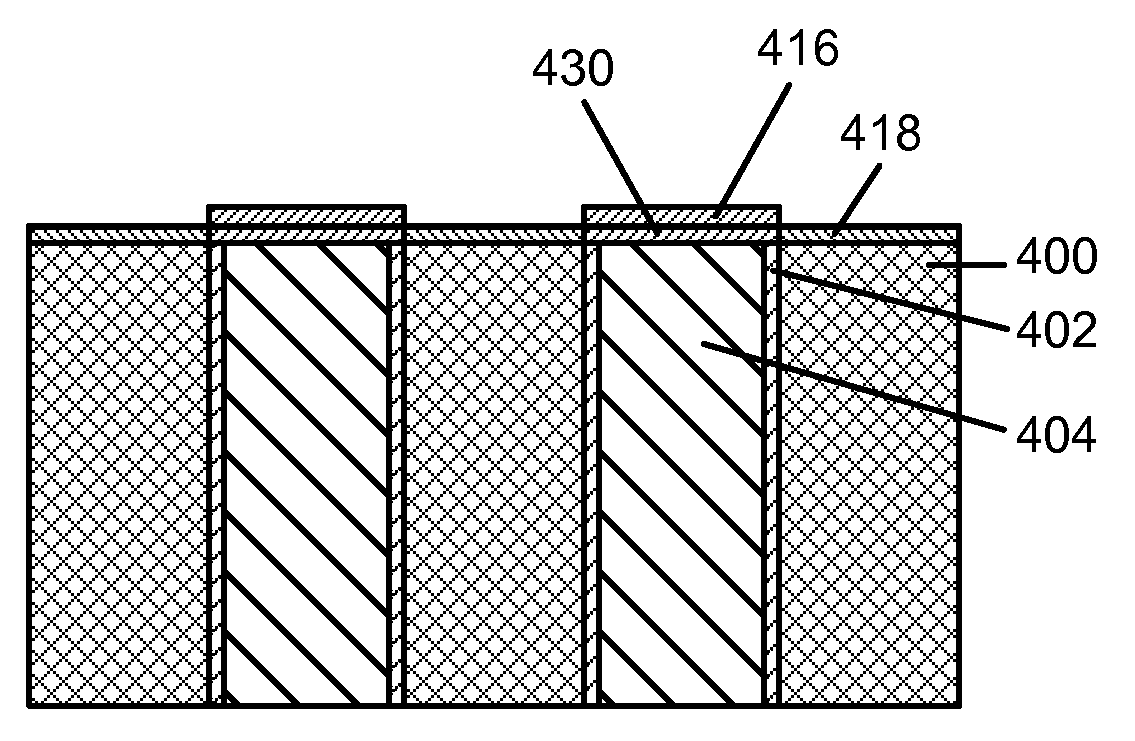

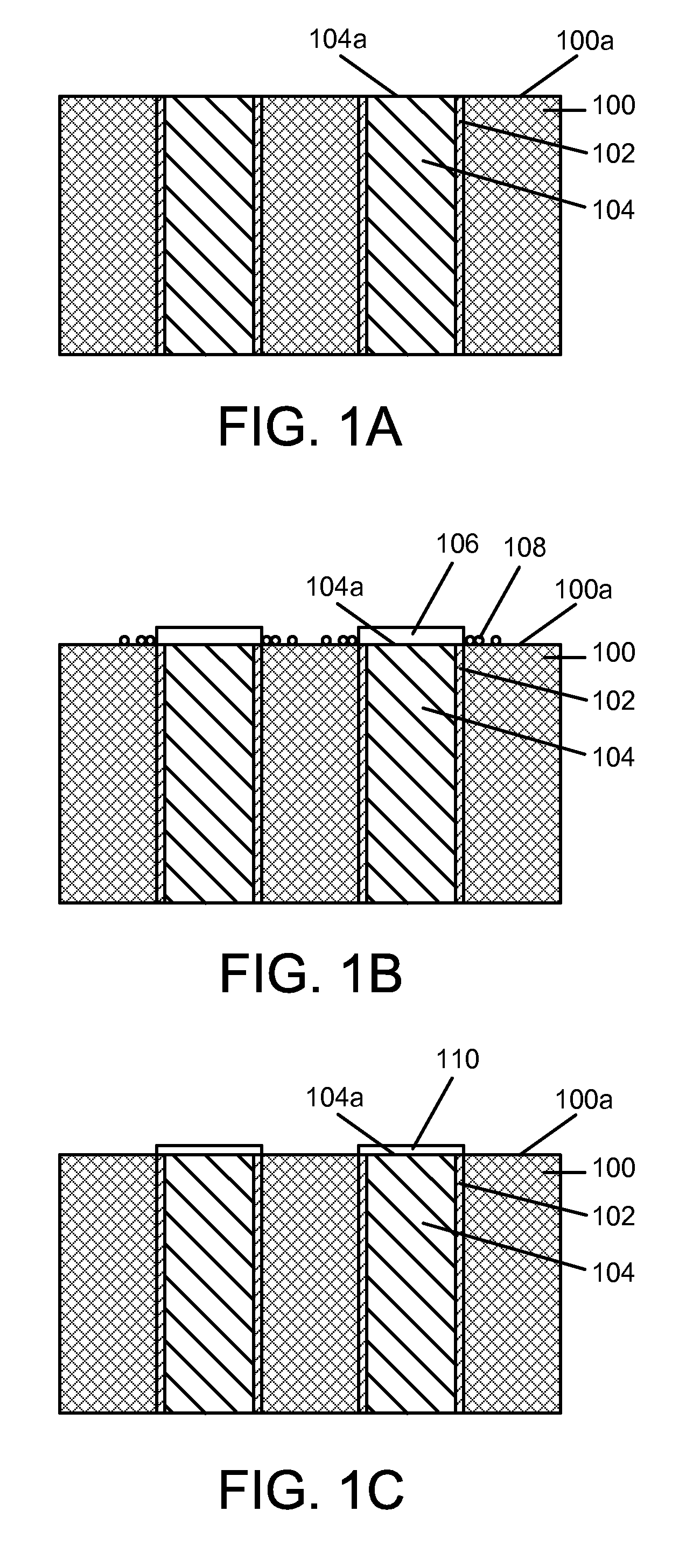

Grain boundary blocking for stress migration and electromigration improvement in CU interconnects

ActiveUS20060286797A1Reduce duplicationSemiconductor/solid-state device manufacturingCopper interconnectDielectric layer

Example embodiments of a structure and method for forming a copper interconnect having a doped region near a top surface. The doped region has implanted alloying elements that block grain boundaries and reduce stress and electro migration. In a first example embodiment, the barrier layer is left over the inter metal dielectric layer during the alloying element implant. The barrier layer is later removed with a planarization process. In a second example embodiment the barrier layer is removed before the alloying element implant and a hard mask blocks the alloying element from being implanted in the inter metal dielectric layer.

Owner:GLOBALFOUNDRIES SINGAPORE PTE LTD +1

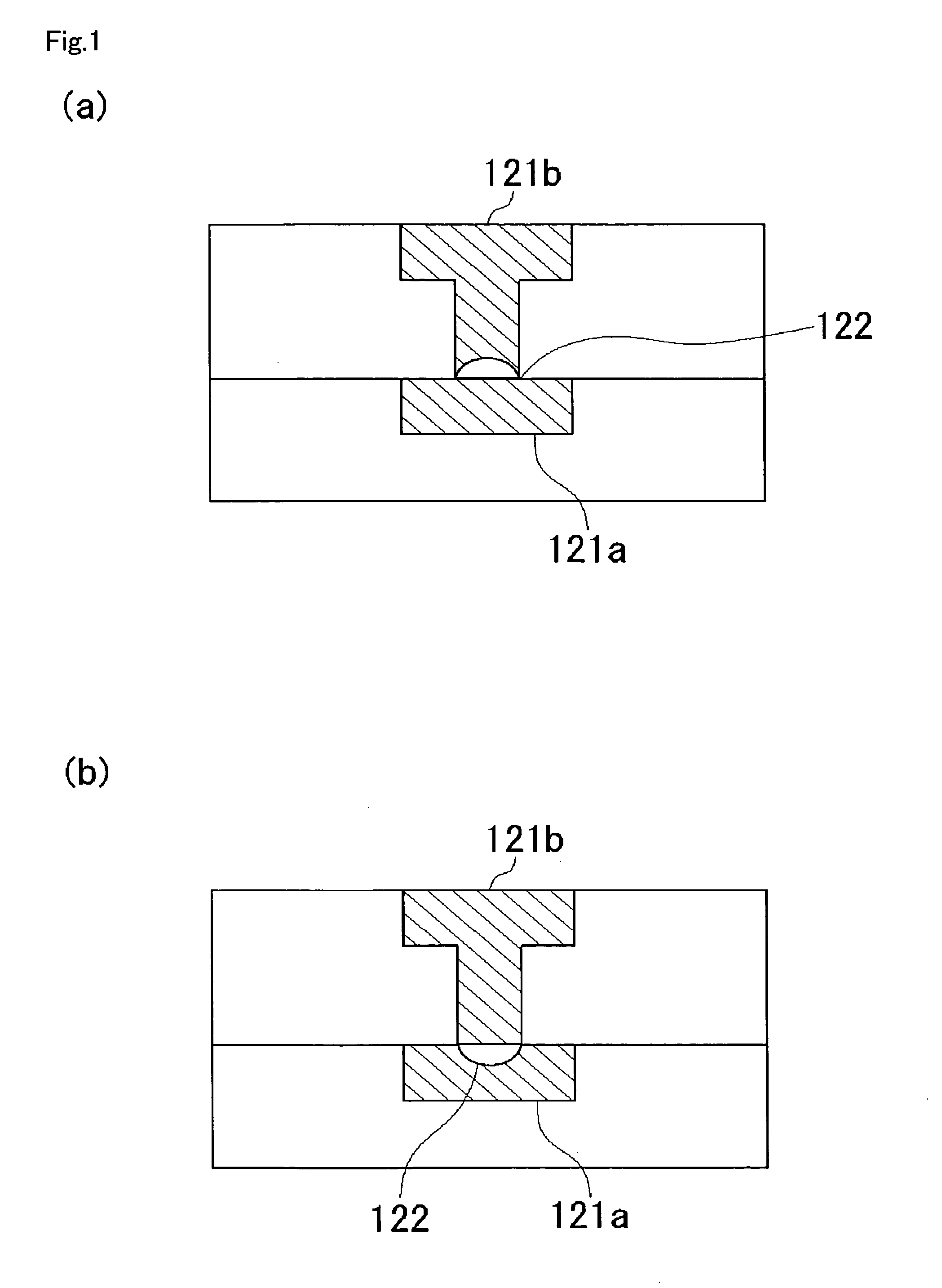

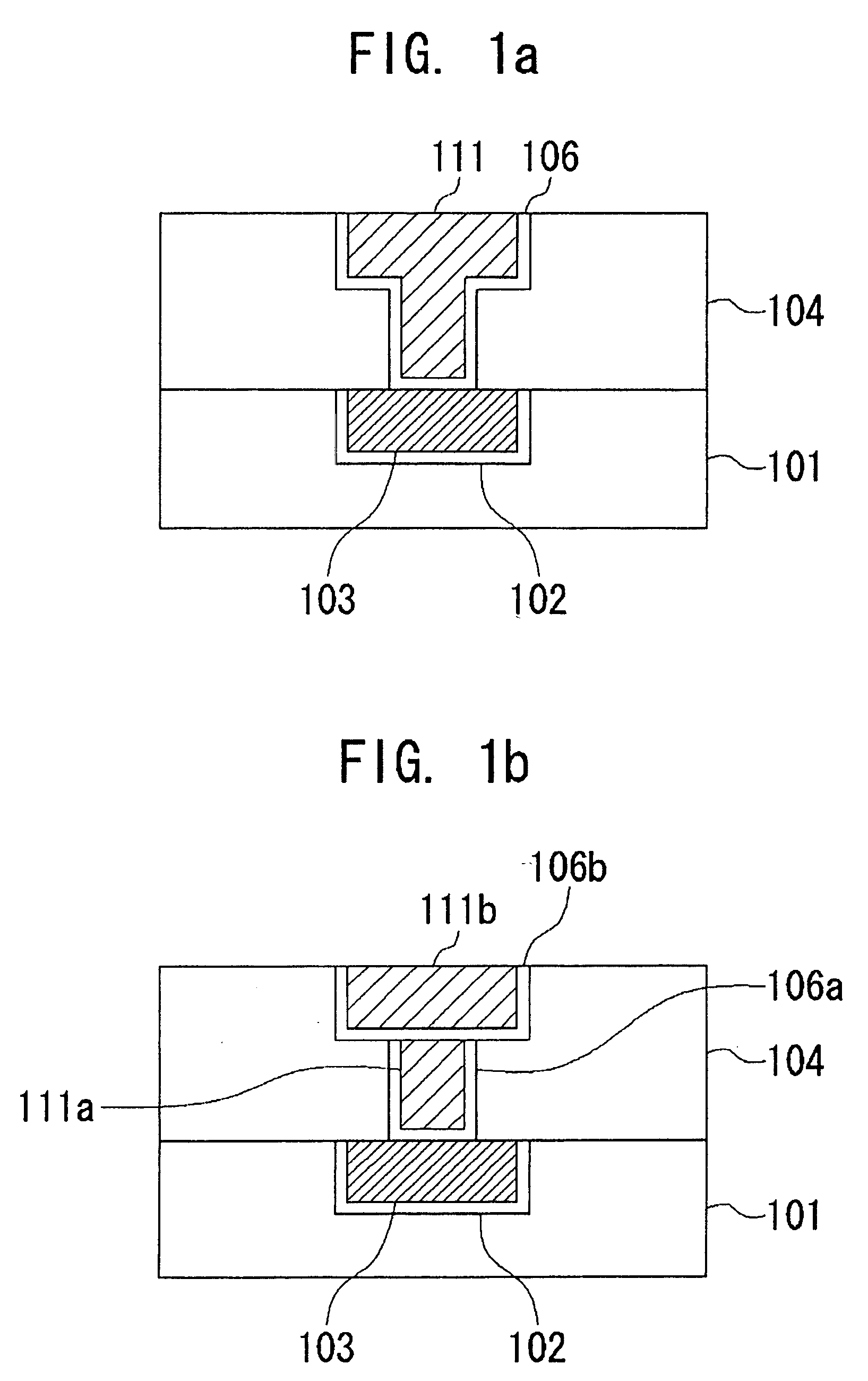

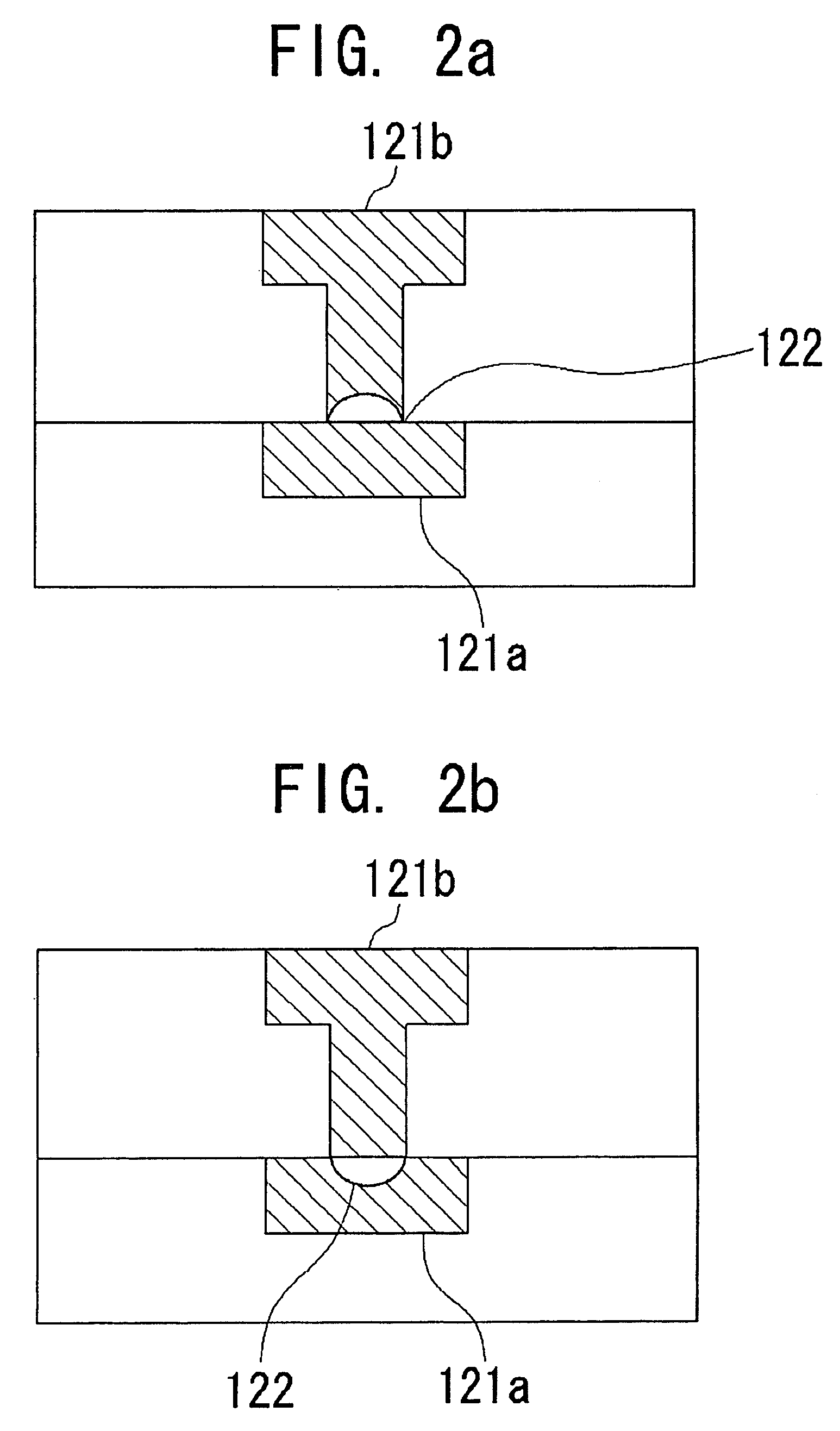

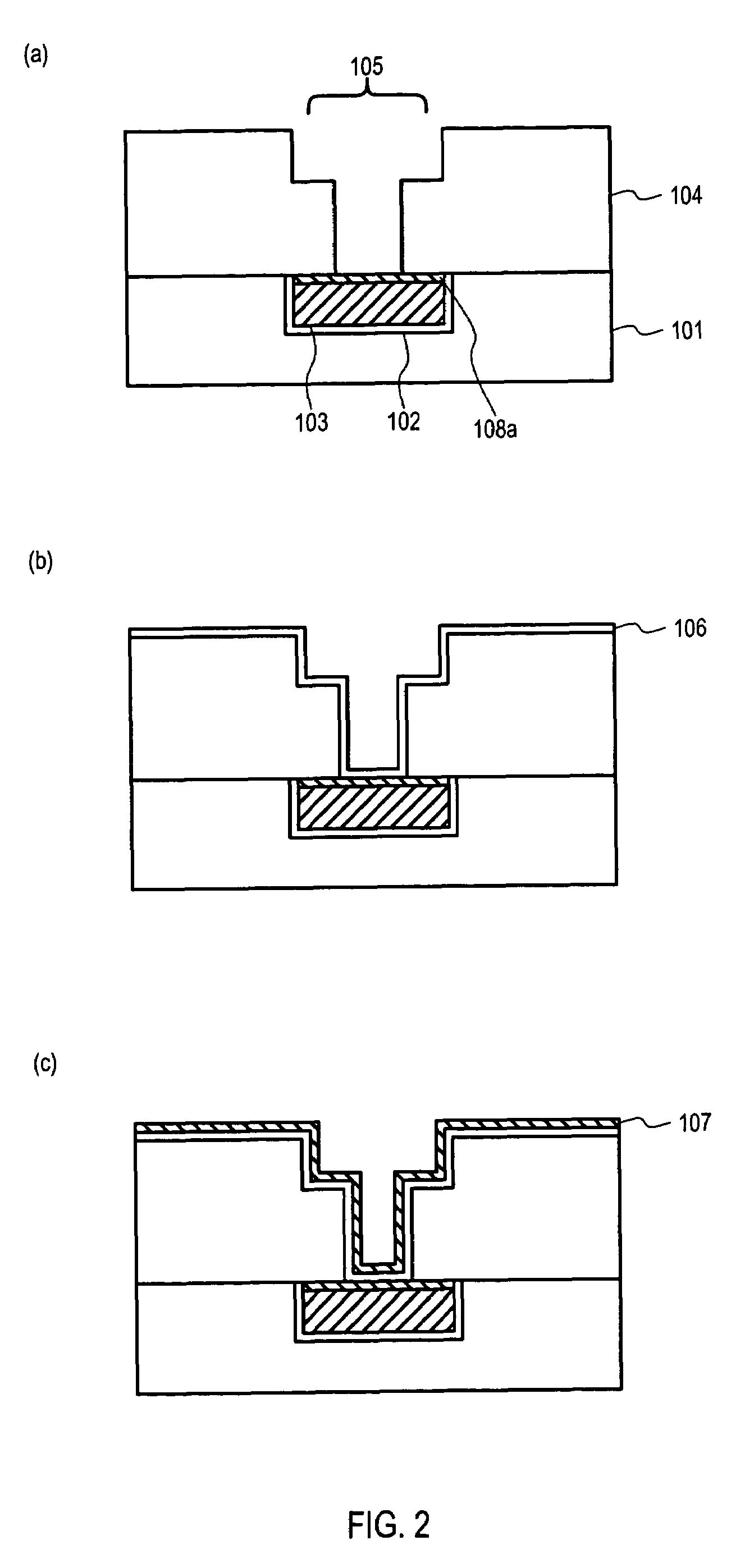

Semiconductor device with interconnection structure for reducing stress migration

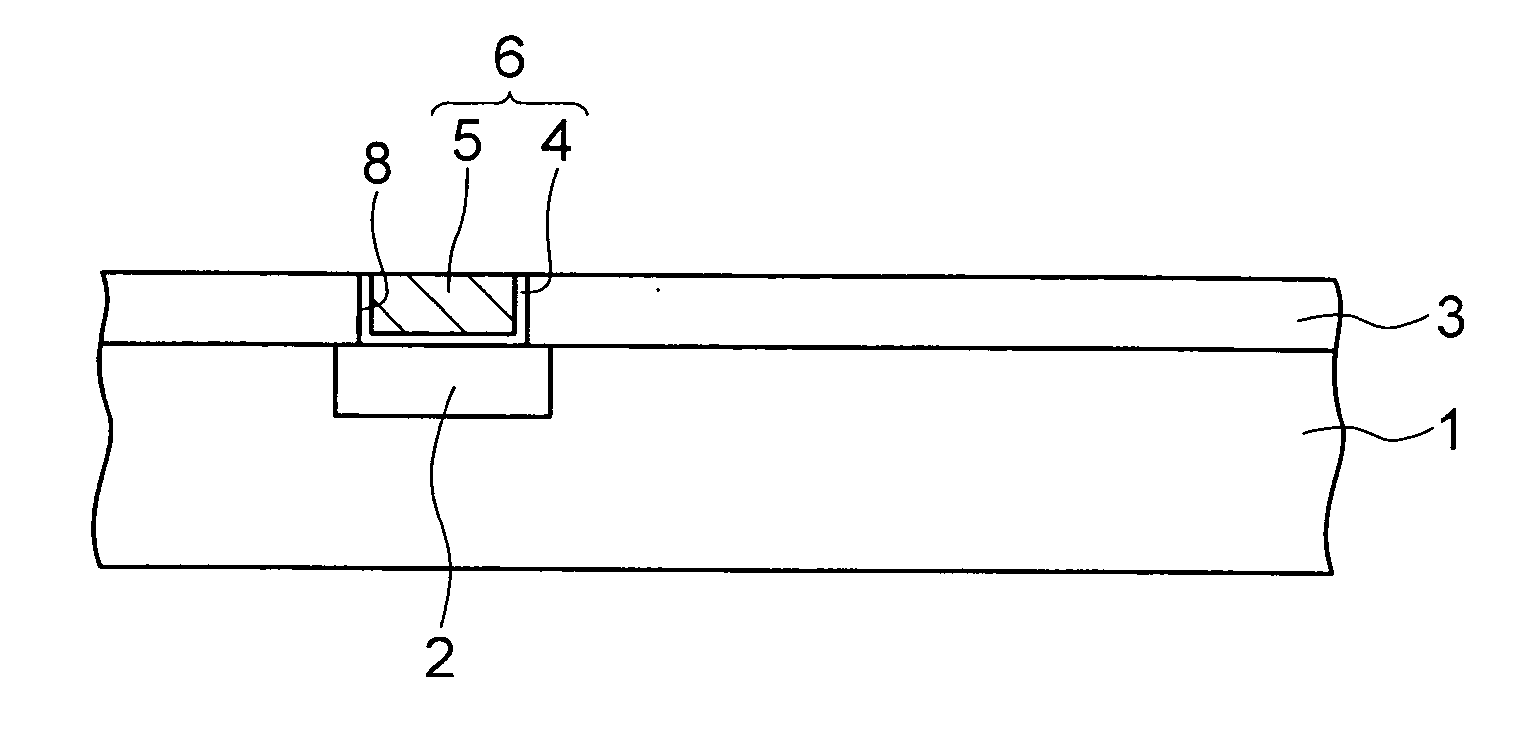

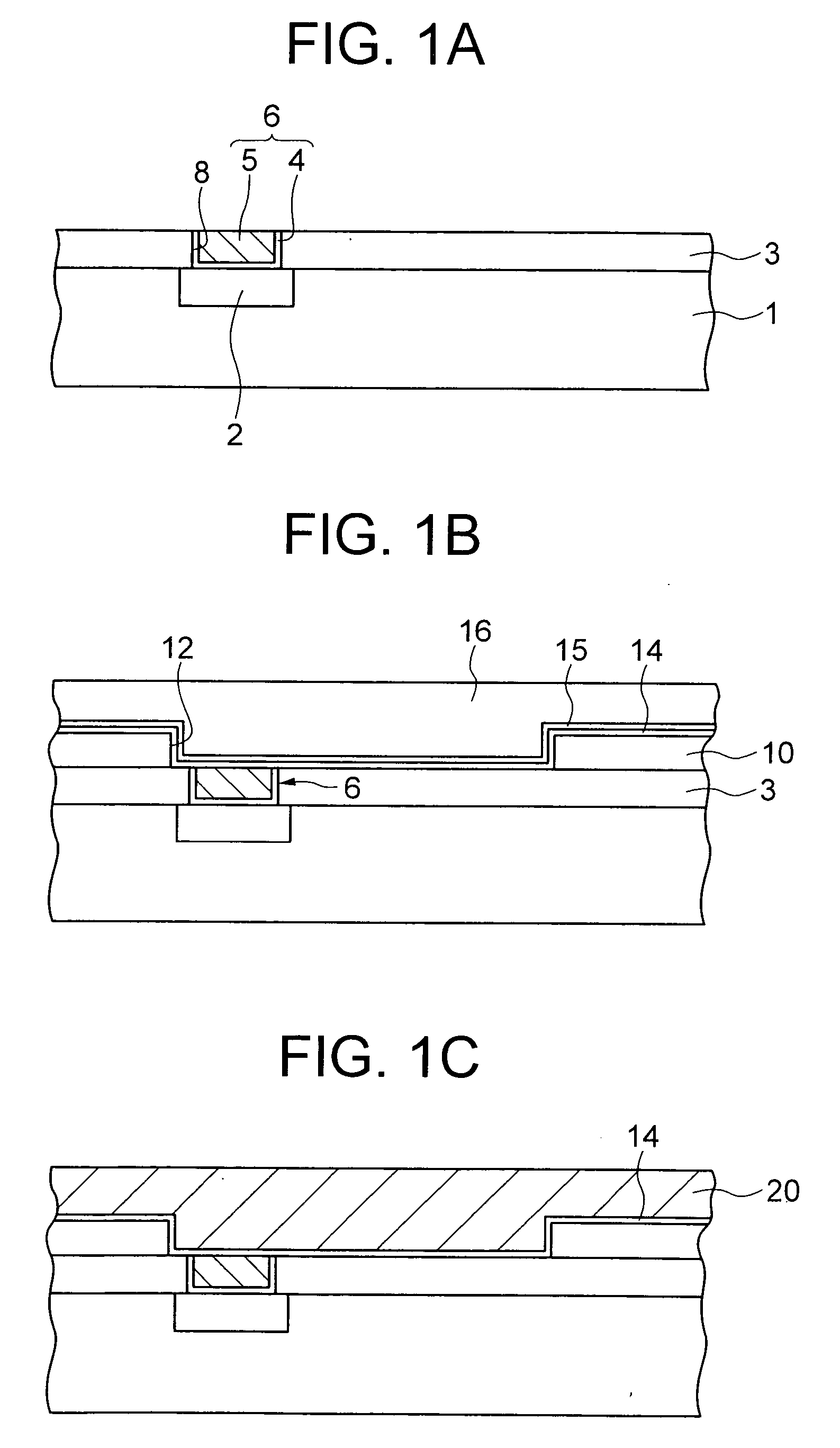

ActiveUS7807567B2Promote migrationAvoid it happening againSemiconductor/solid-state device detailsSolid-state devicesStress concentrationEngineering

The semiconductor device of the present invention includes a first interconnection, a via-plug that is connected to the first interconnection, and a second interconnection that is formed as a single unit with the via-plug. The cross-sectional shape of the via-plug is such that the plug sidewall angle, which indicates the angle of the via-plug sidewall with respect to the surface of the first interconnection, is a positive angle; and moreover, at least two points exist between the base and the top of the via-plug on at least one sidewall of the two sidewalls of the cross-sectional shape of the via-plug at which the plug sidewall angle attains a maximum value. Since shapes that would give rise to the occurrence of concentrations of stress are not formed in the via-plug sidewalls, metal is more effectively embedded in the via-hole, and the incidence of voids is prevented.

Owner:RENESAS ELECTRONICS CORP

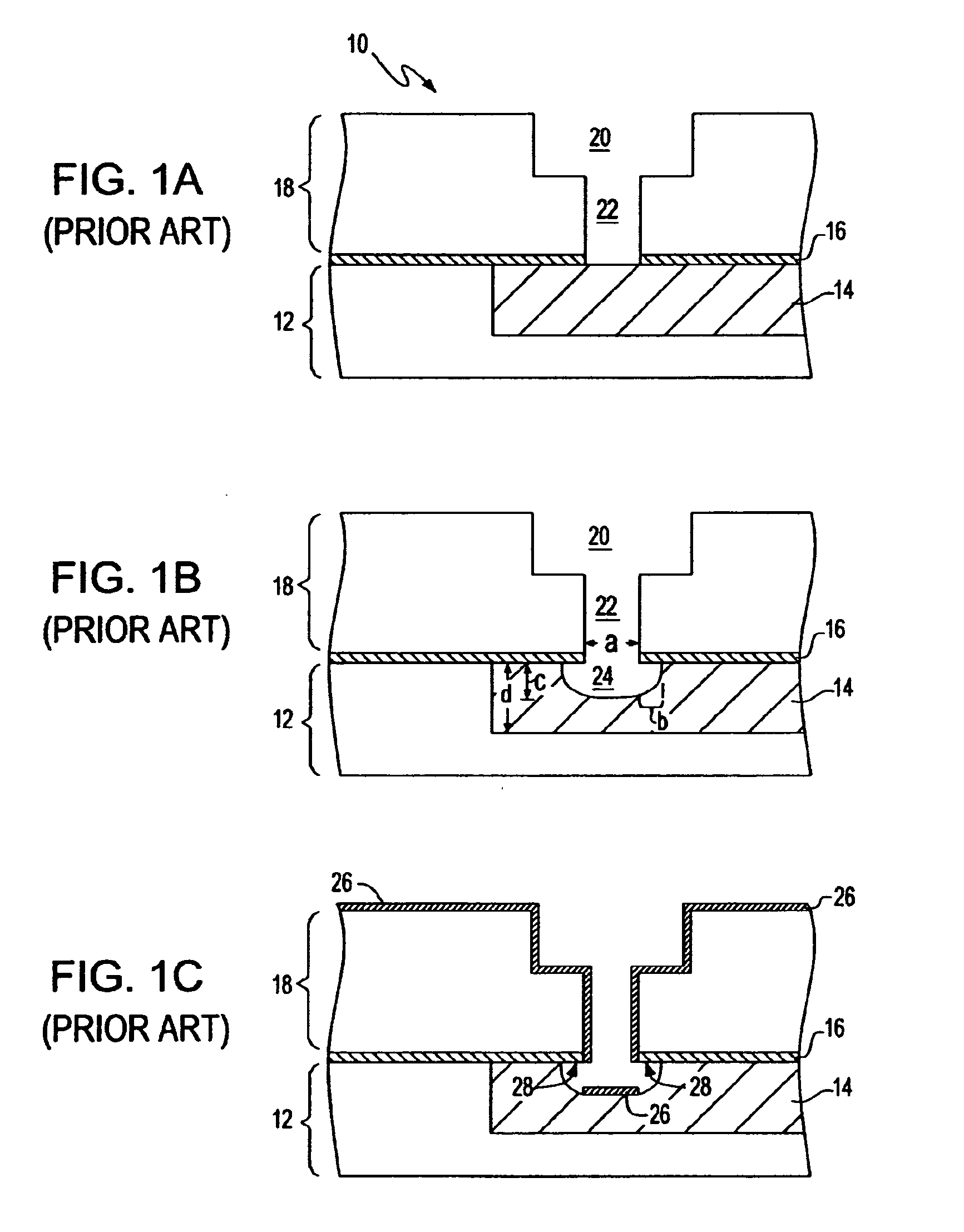

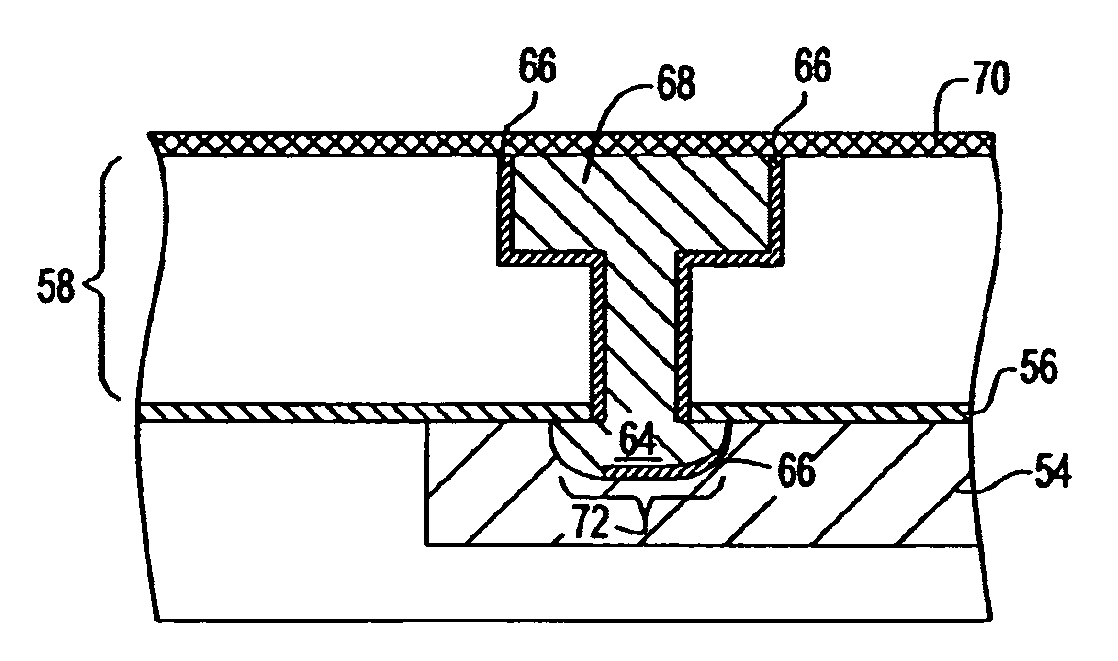

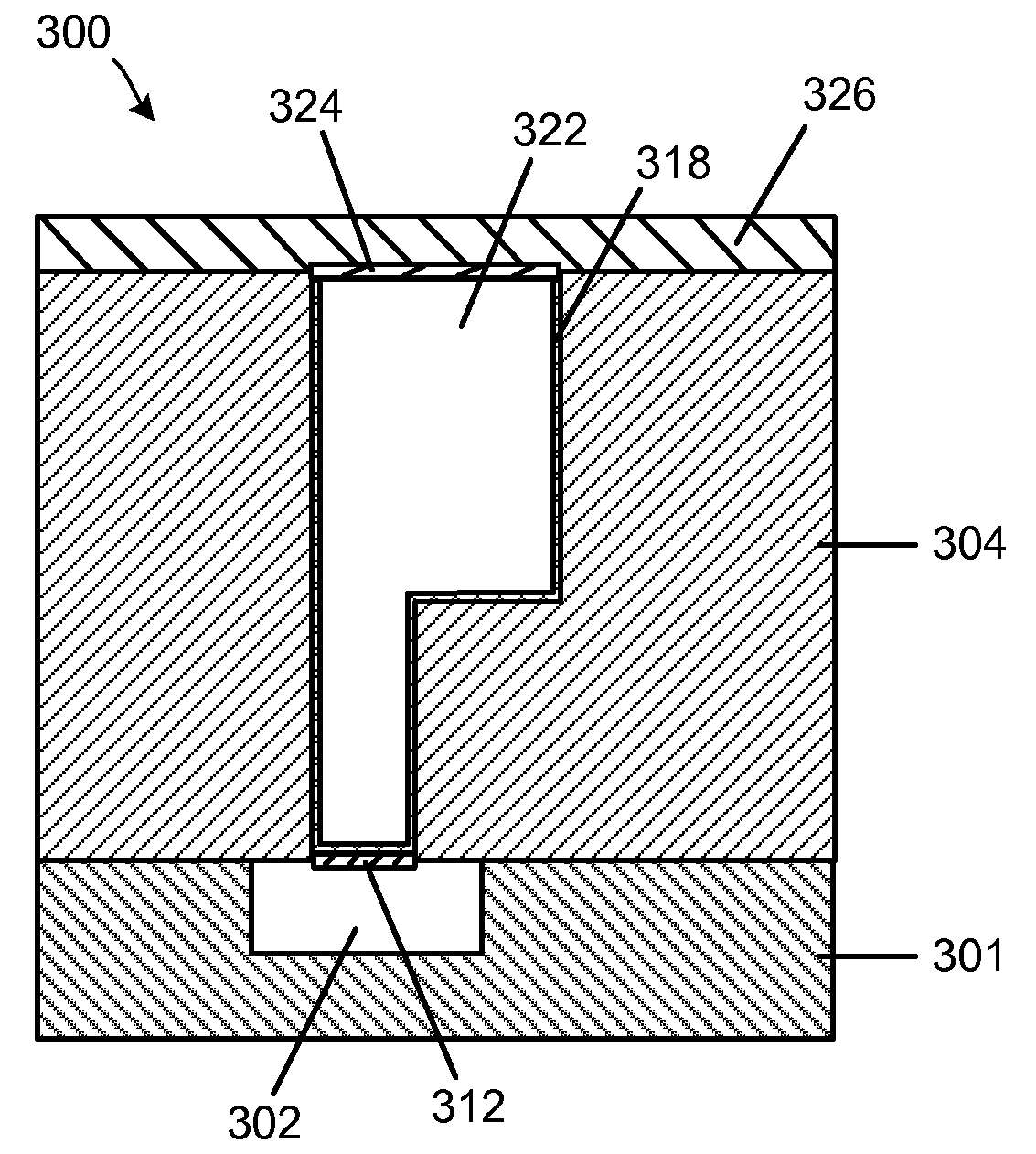

Composite tantalum capped inlaid copper with reduced electromigration and reduced stress migration

ActiveUS7071564B1Reduced via resistanceImprove electromigrationSemiconductor/solid-state device detailsSolid-state devicesTantalum nitrideDielectric layer

The electromigration and stress migration of Cu interconnects is significantly reduced by forming a composite capping layer comprising a layer of β-Ta on the upper surface of the inlaid Cu, a layer of tantalum nitride on the β-Ta layer and a layer of α-Ta on the tantalum nitride layer. Embodiments include forming a recess in an upper surface of Cu inlaid in a dielectric layer, depositing a layer of β-Ta at a thickness of 25 Å to 40 Å, depositing a layer of tantalum nitride at a thickness of 20 Å to 100 Å and then depositing a layer of α-Ta at a thickness of 200 Å to 500 Å. Embodiments further include forming an overlying dielectric layer, forming an opening therein, e.g., a via opening or a dual damascene opening, lining the opening with α-Ta, and filling the opening with Cu in electrical contact with the underlying inlaid Cu.

Owner:GLOBALFOUNDRIES US INC

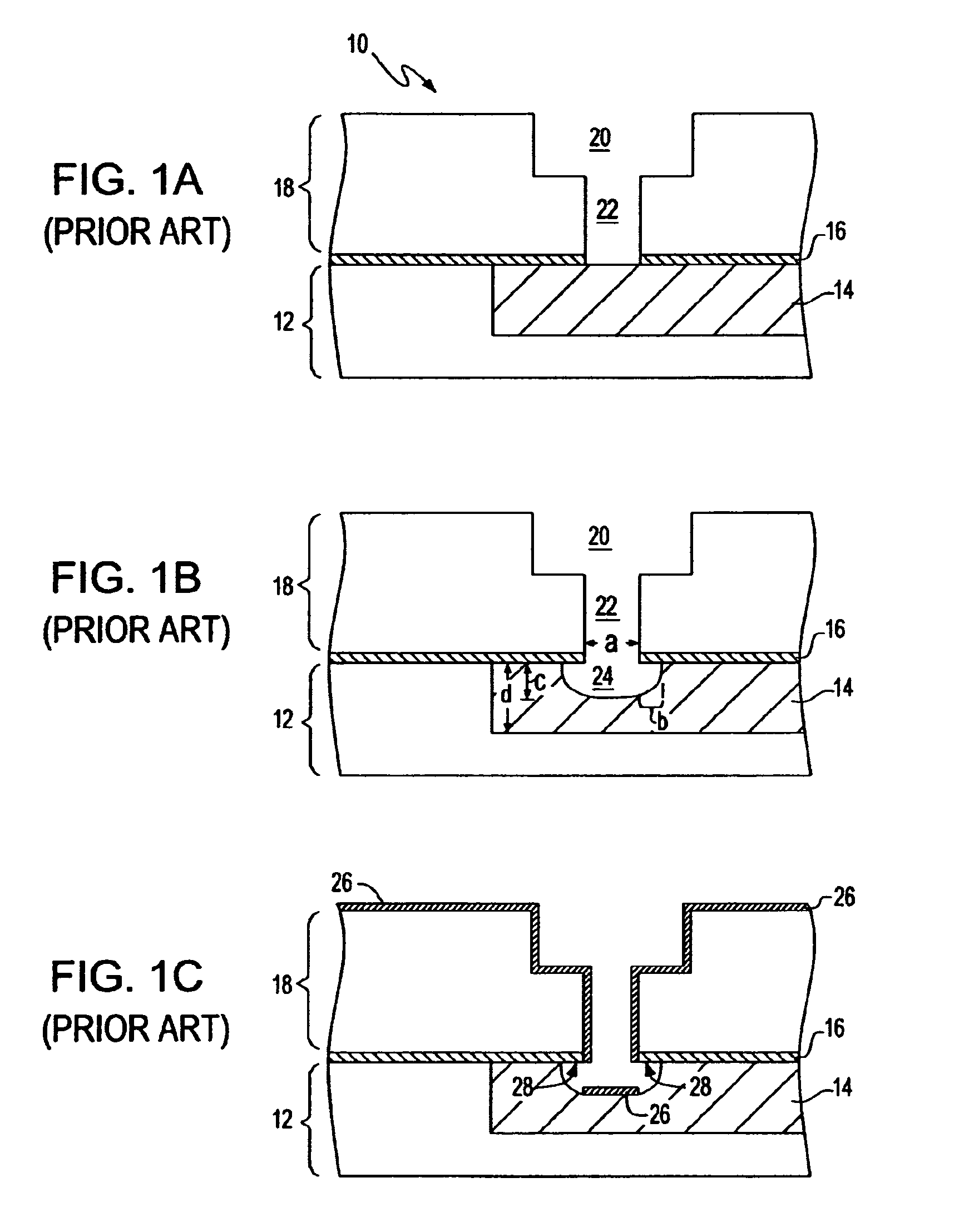

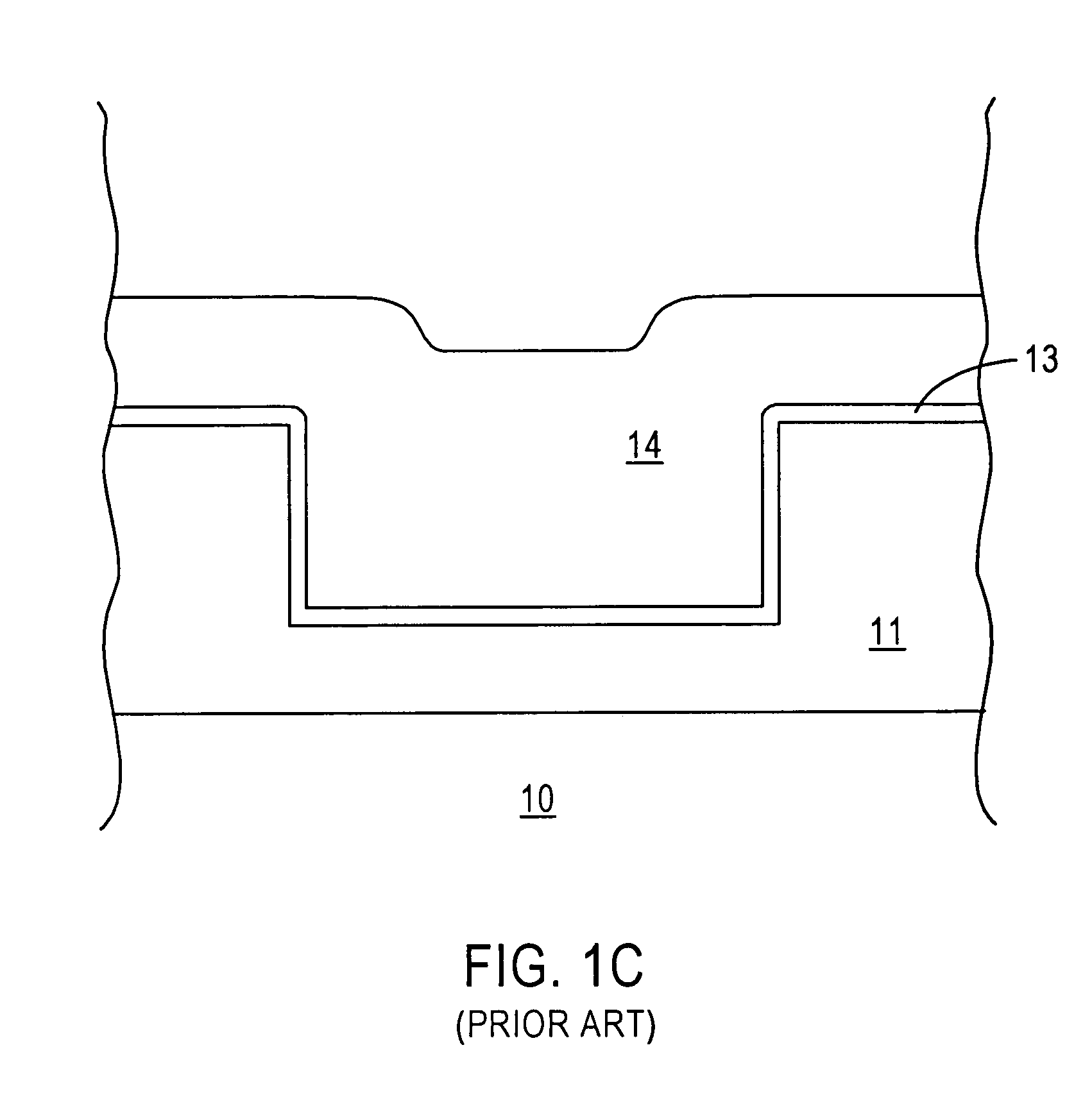

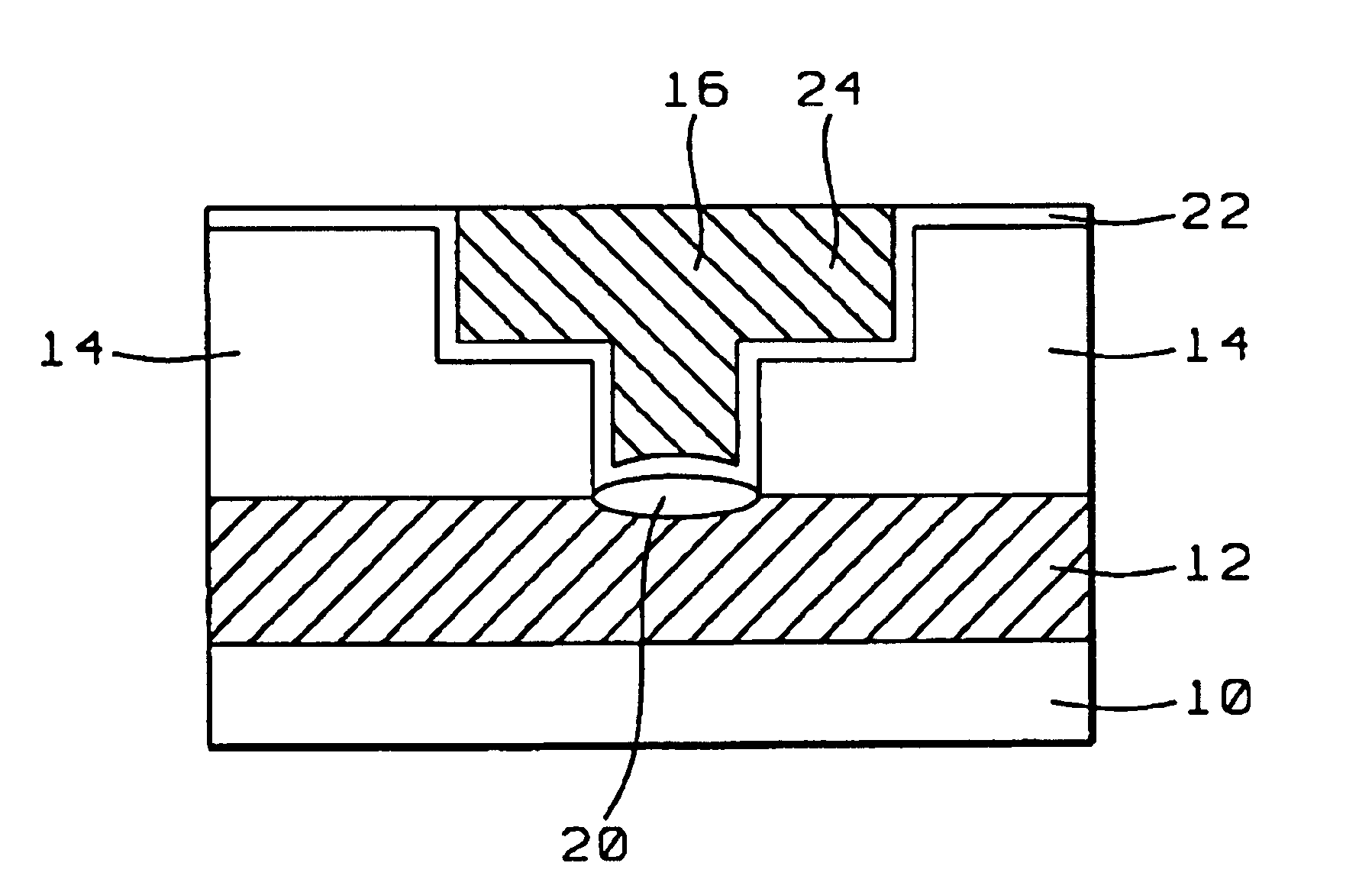

Via bottom copper/barrier interface improvement to resolve via electromigration and stress migration

A method of forming a copper / barrier layer interface comprising the following sequential steps. A structure having a lower copper layer formed thereover is provide. A patterned dielectric layer is formed over the lower copper layer. The patterned dielectric layer having an opening exposing a portion of the lower copper layer. The exposed portion of the lower copper layer is converted to a copper silicide portion. A barrier layer is formed upon the patterned dielectric layer and the copper silicide portion, lining the opening, whereby the lower copper layer / barrier layer interface is formed such that the barrier layer contacts the copper silicide portion to form an interface.

Owner:TAIWAN SEMICON MFG CO LTD

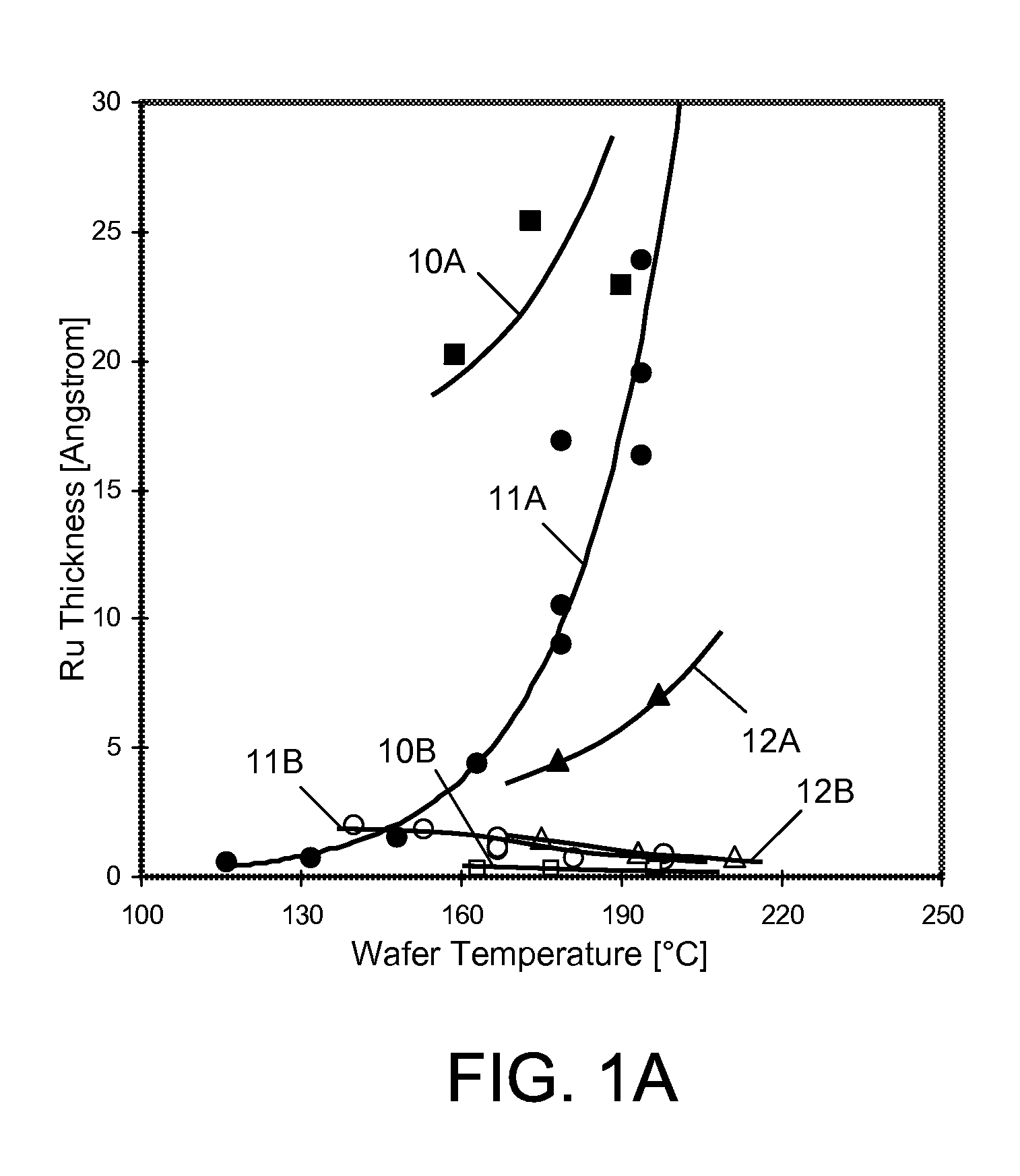

Method for forming ruthenium metal cap layers

InactiveUS20100081274A1Improve electromigrationImprove stress migrationSemiconductor/solid-state device manufacturingChemical vapor deposition coatingMetallurgyRuthenium

A method is provided for integrating ruthenium (Ru) metal deposition into manufacturing of semiconductor devices to improve electromigration and stress migration in copper (Cu) metal. Embodiments of the invention include treating patterned substrates containing metal layers and low-k dielectric materials with NHx (x≦3) radicals and H radicals to improve selective formation of ruthenium (Ru) metal cap layers on the metal layers relative to the low-k dielectric materials.

Owner:TOKYO ELECTRON LTD

Semiconductor device having a Cu interconnection and method for manufacturing the same

InactiveUS20040150113A1Improving electro-migration resistance and stress-migration resistanceSemiconductor/solid-state device detailsSolid-state devicesSemiconductorSilicon

A Cu interconnection in a semiconductor device has an ununiform profile of additive metal atoms wherein the additive metal atoms are rich in the vicinities of bottom and side surfaces of the Cu interconnection. The Cu interconnection also has an ununiform silicon profile wherein additive silicon atoms are rich in the vicinity of the top surface of the Cu interconnection. The structure improves the electro-migration resistance and the stress-migration resistance of the Cu interconnection.

Owner:NEC ELECTRONICS CORP

Reliability improvement of SiOC etch with trimethylsilane gas passivation in Cu damascene interconnects

InactiveUS7193325B2Reduce leakage currentImprove throughputSemiconductor/solid-state device detailsSolid-state devicesTrimethylsilaneLow leakage

A method of forming a SiCOH etch stop layer in a copper damascene process is described. A substrate with an exposed metal layer is treated with H2 or NH3 plasma to remove metal oxides. Trimethylsilane is flowed into a chamber with no RF power at about 350° C. to form at least a monolayer on the exposed metal layer. The SiCOH layer is formed by a PECVD process including trimethylsilane and CO2 source gases. Optionally, a composite SiCOH layer comprised of a low compressive stress layer on a high compressive stress layer is formed on the substrate. A conventional damascene sequence is then used to form a second metal layer on the exposed metal layer. Via Rc stability is improved and a lower leakage current is achieved with the trimethylsilane passivation layer. A composite SiCOH etch stop layer provides improved stress migration resistance compared to a single low stress SiCOH layer.

Owner:TAIWAN SEMICON MFG CO LTD

Method for forming cobalt tungsten cap layers

InactiveUS20100081276A1Improve electromigrationImprove stress migrationSemiconductor/solid-state device detailsSolid-state devicesCobalt metalDevice material

A method is provided for integrating cobalt tungsten cap layers into manufacturing of semiconductor devices to improve electromigration and stress migration in copper (Cu) metal. One embodiment includes providing a patterned substrate containing a recessed feature formed in a low-k material and a first metallization layer at the bottom of the feature, forming a cobalt tungsten cap layer on the first metallization layer, depositing a barrier layer in the recessed feature, including on the low-k dielectric material and on the first cobalt metal cap layer, and filling the recessed feature with Cu metal. Another embodiment includes providing a patterned substrate having a substantially planar surface with Cu paths and low-k regions, and forming a cobalt tungsten cap layer on the Cu paths.

Owner:TOKYO ELECTRON LTD

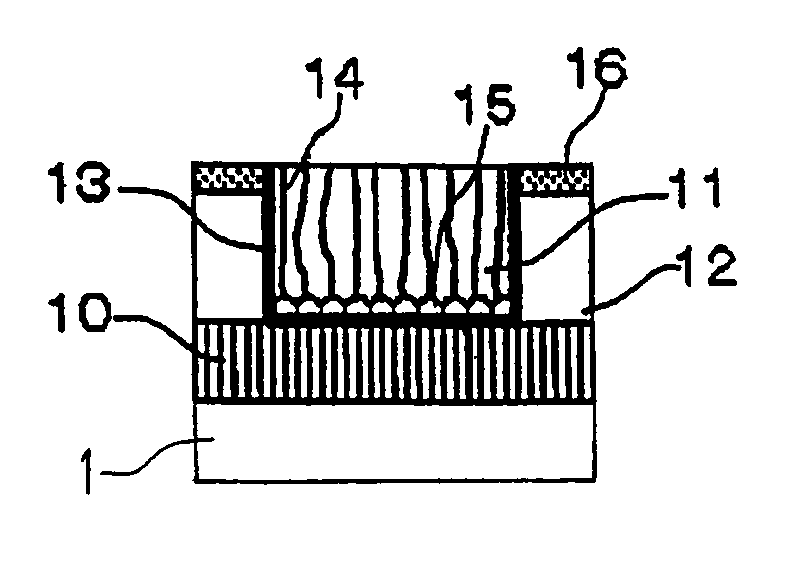

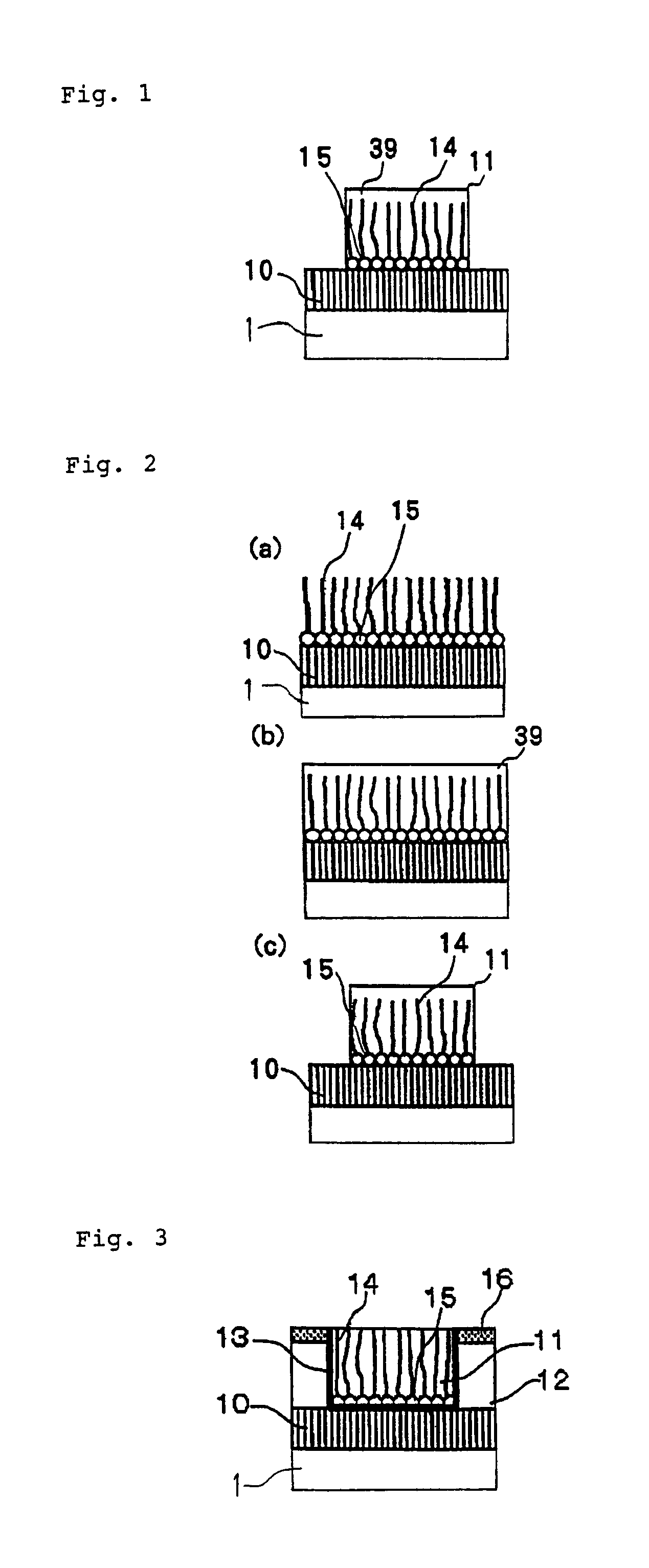

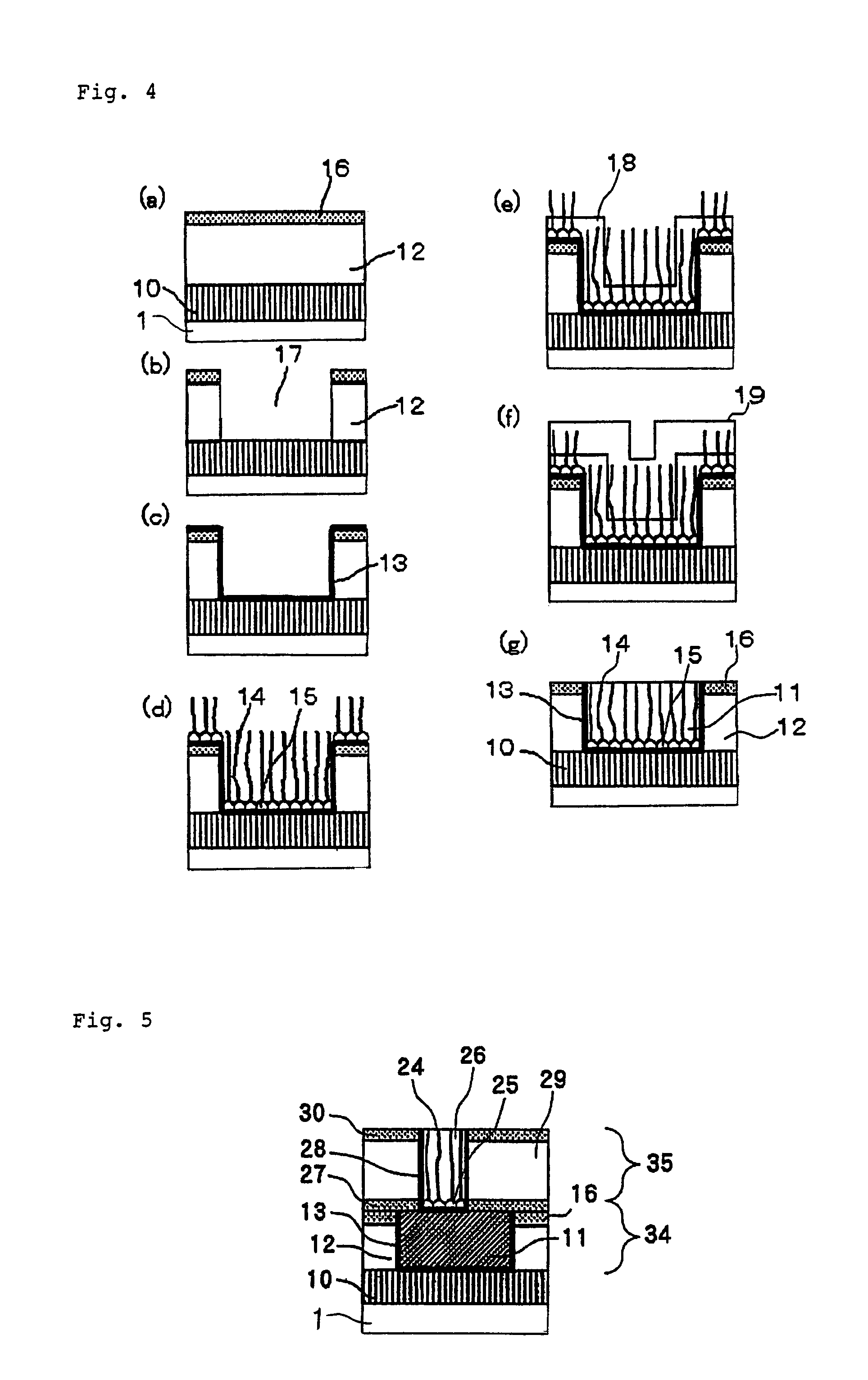

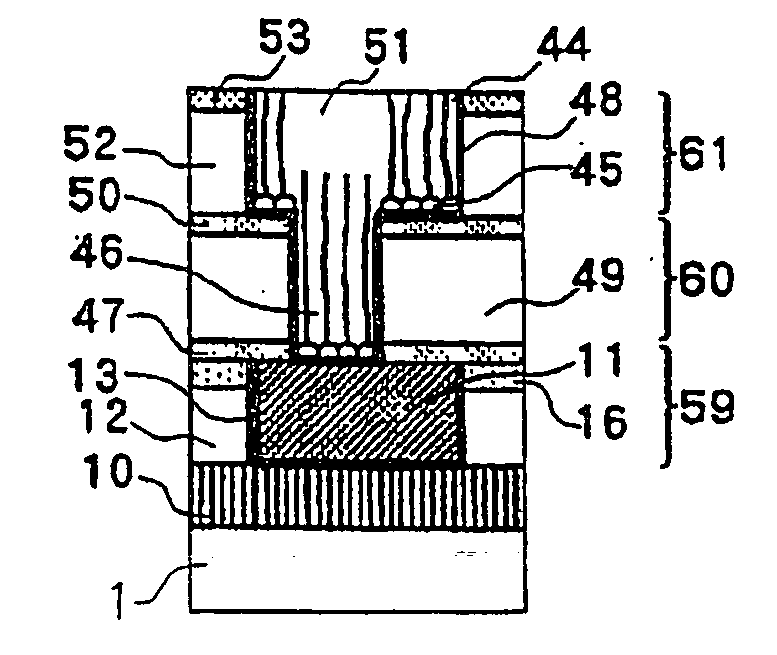

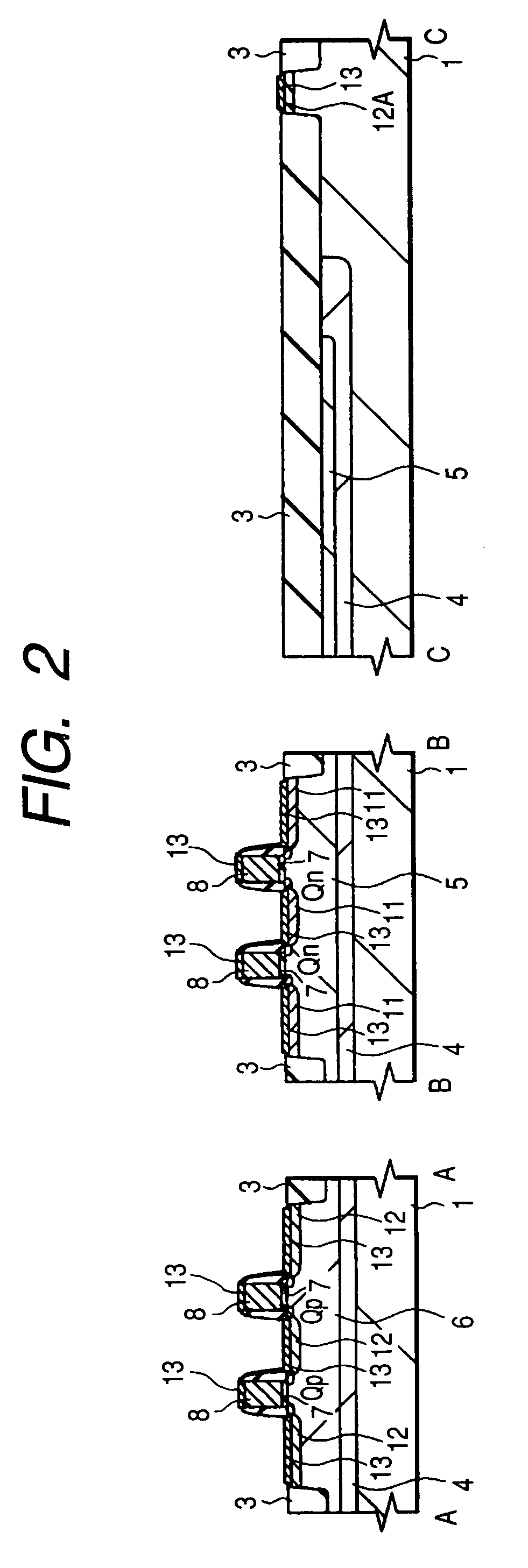

Semiconductor device and its manufacturing method

InactiveUS7518247B2Semiconductor/solid-state device detailsNanoinformaticsDevice materialSemiconductor chip

There has been a problem that micromiaturization causes increase of the resistance of wiring structure and degradation of electron migration resistance and stress migration resistance. The present invention provides a wiring structure of a semiconductor device having a low resistance even when the semiconductor device is microminiaturized, free of electron migration and stress migration, and having a high reliability and a method for manufacturing the same. A semiconductor device having a wiring or a connection plug made of a mixture of a metal and carbon nanotubes berried in a wiring groove or a via hole made in an insulating film on a substrate where a semiconductor chip is fabricated, and its manufacturing method are provided.

Owner:NEC CORP

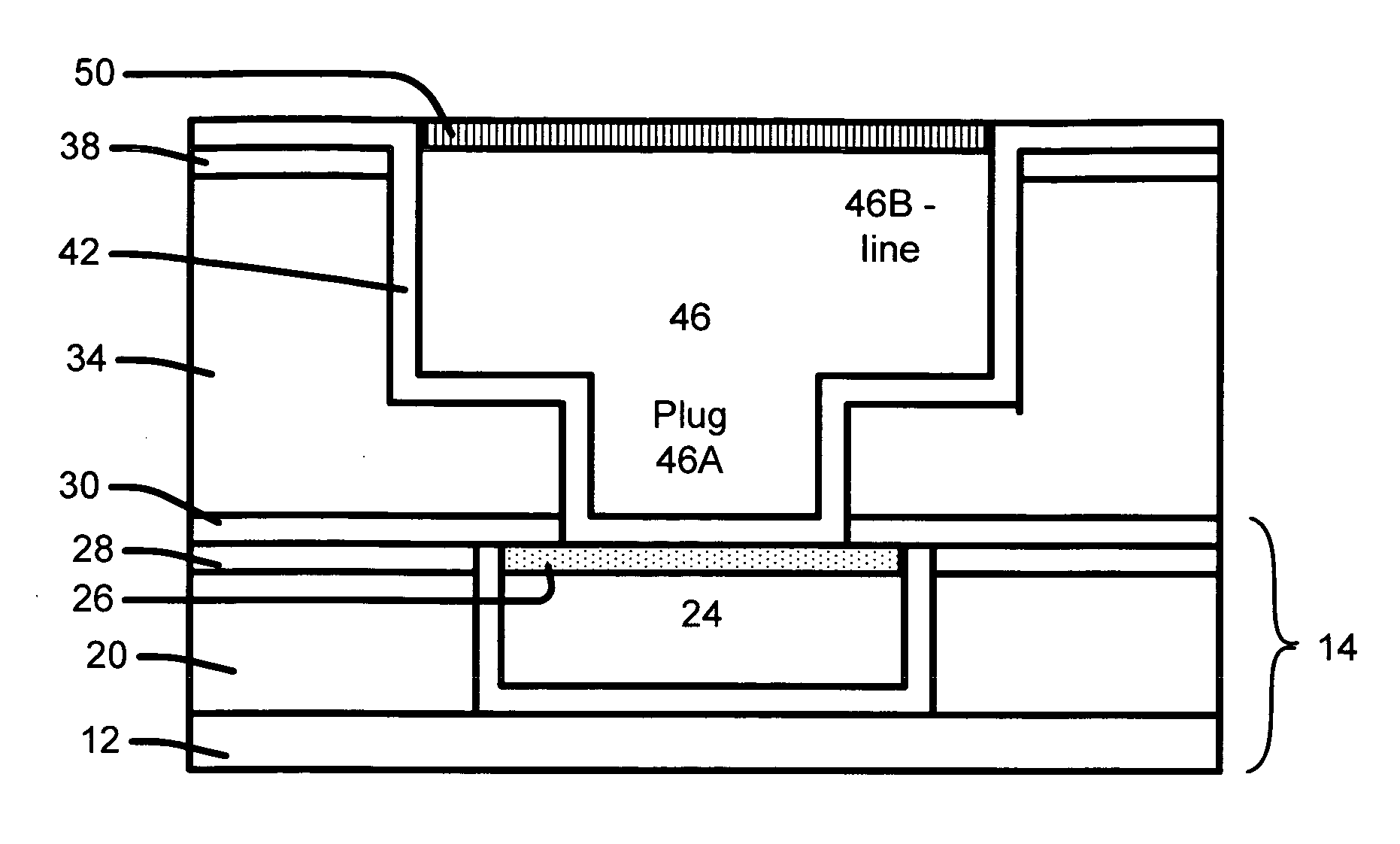

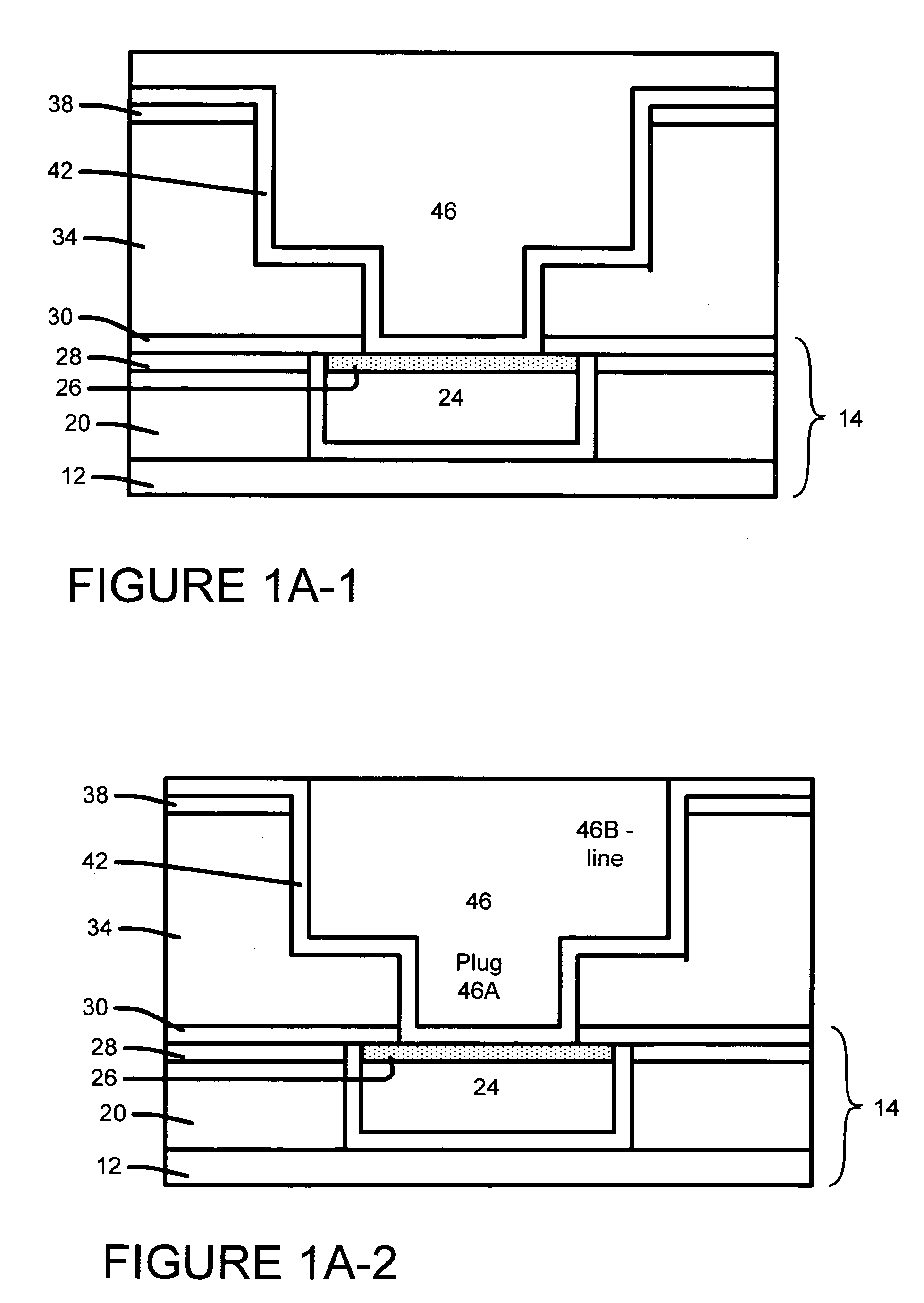

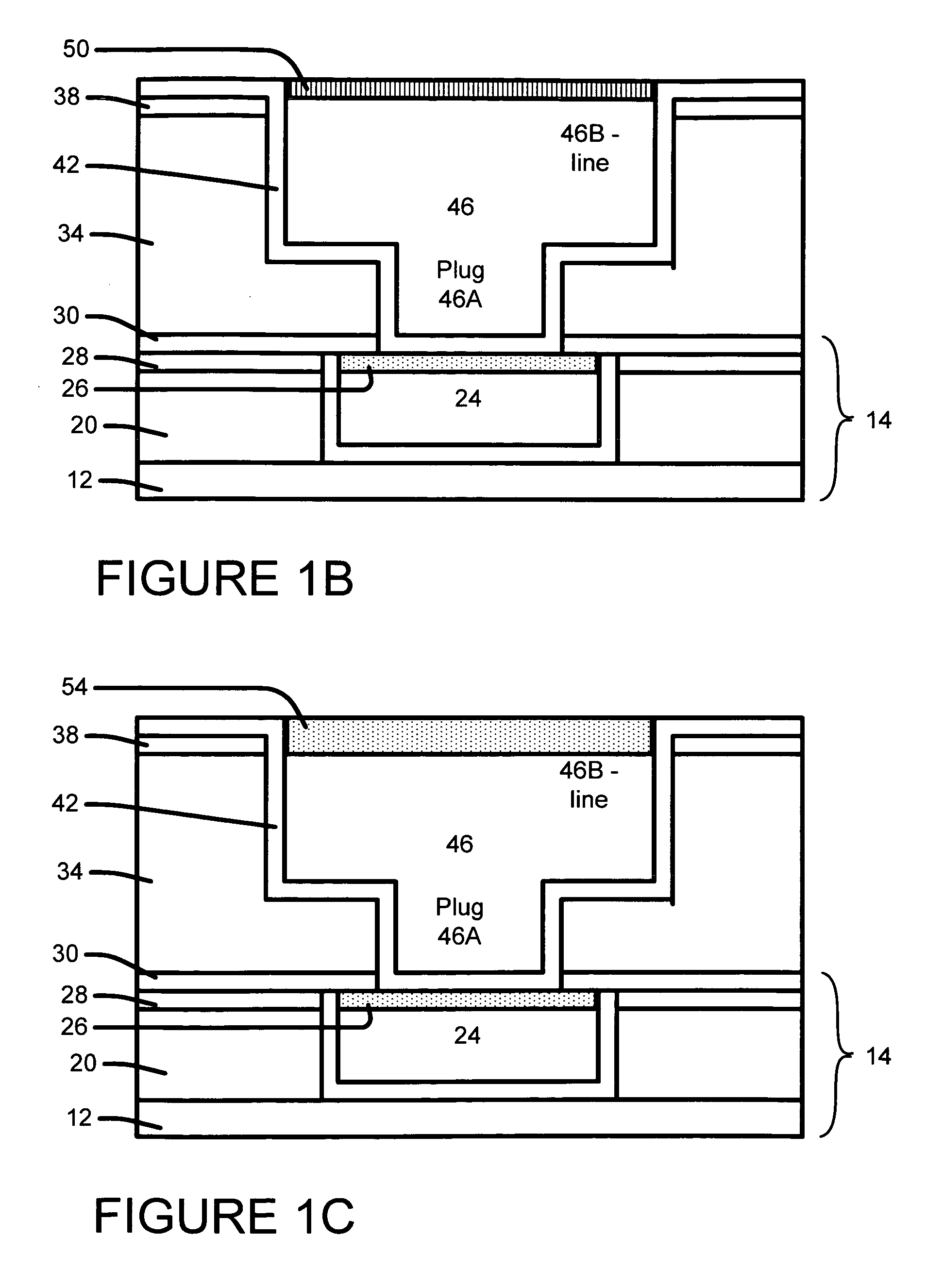

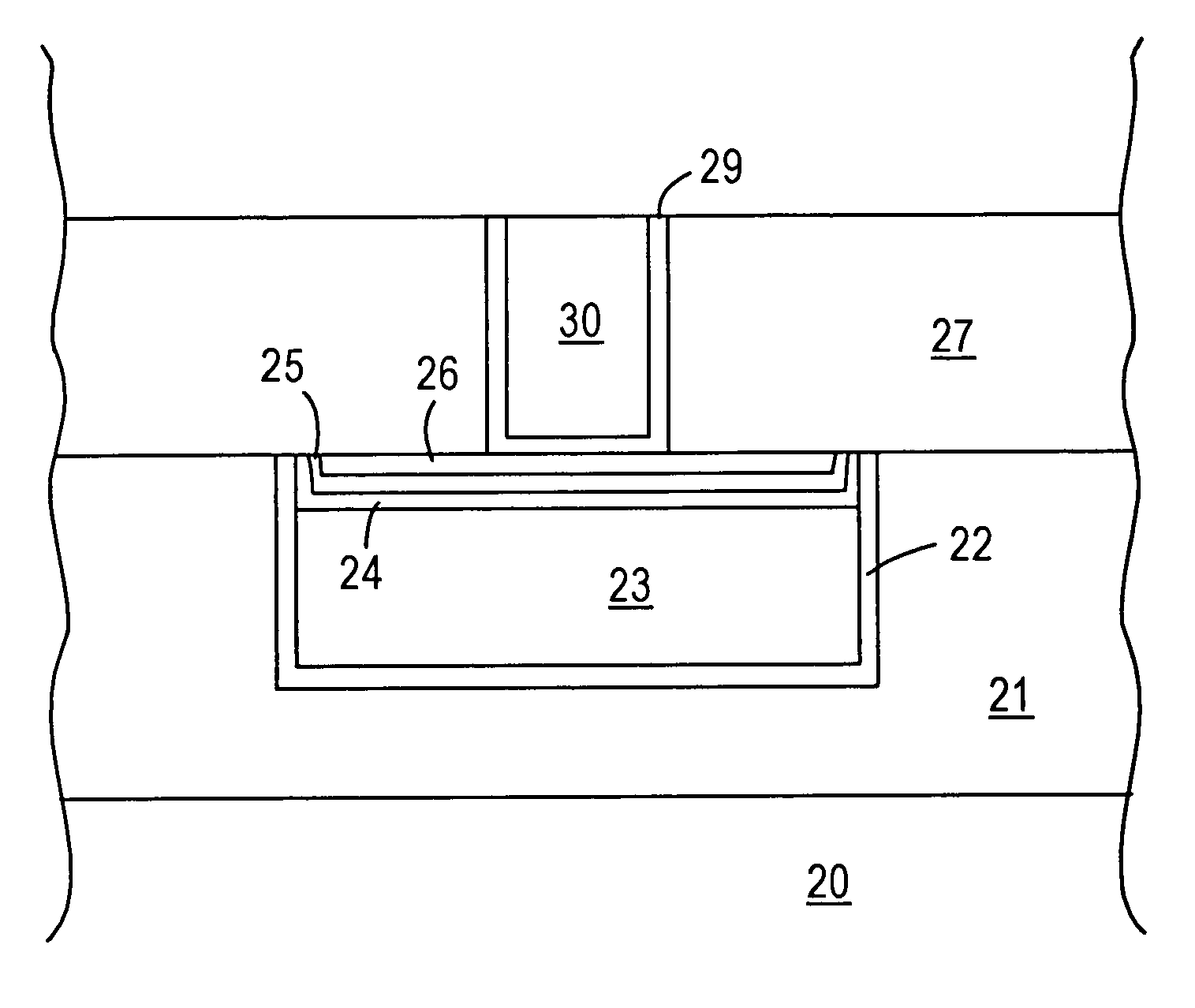

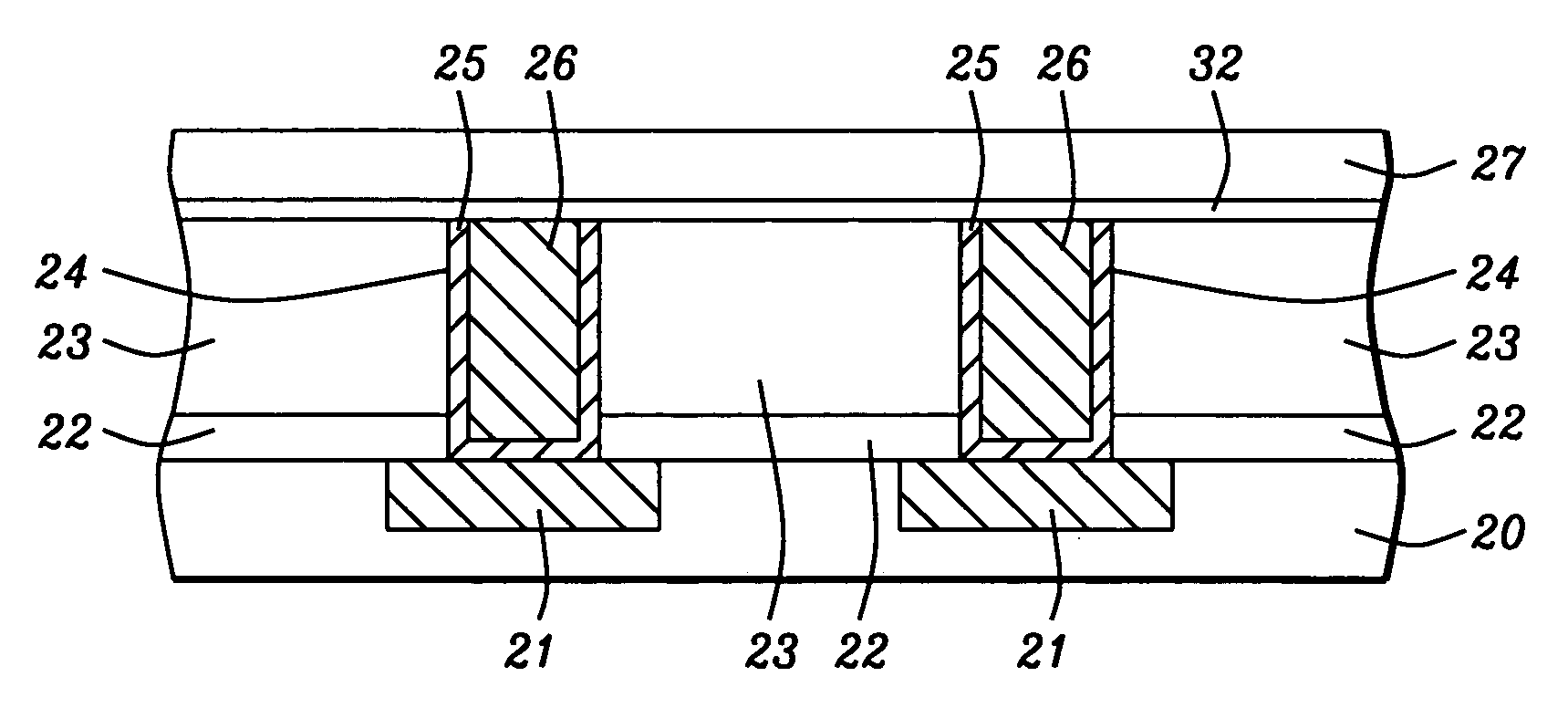

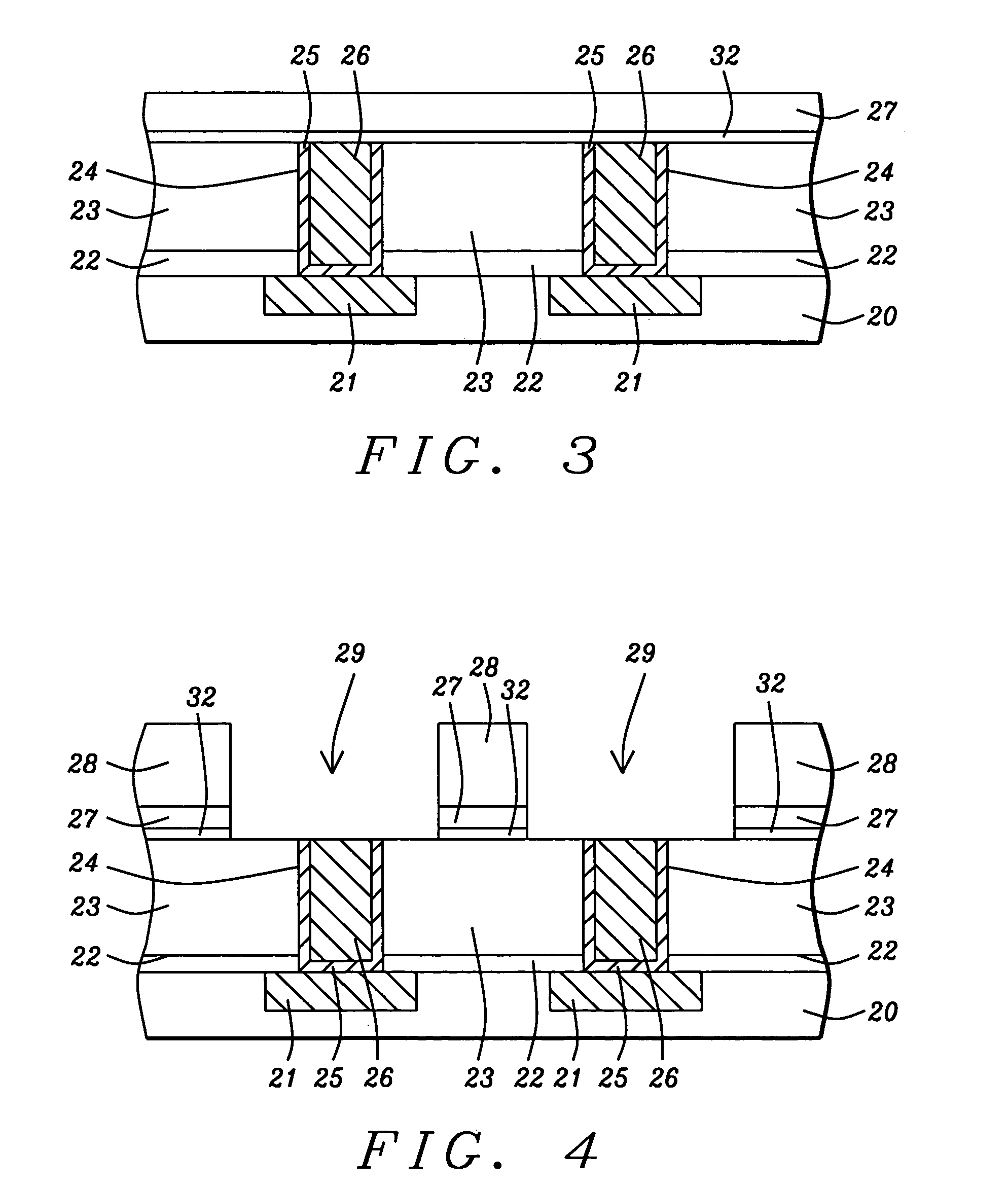

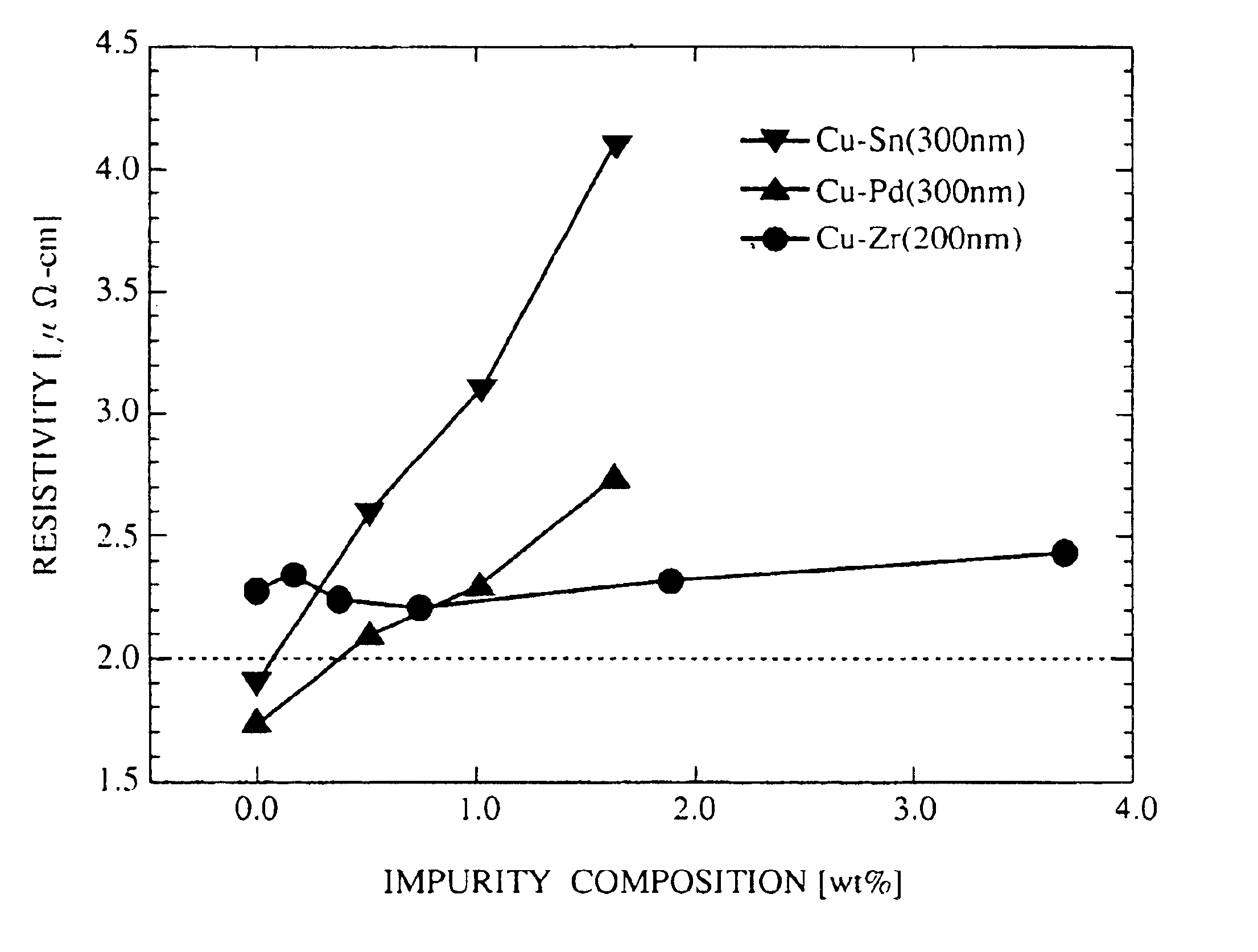

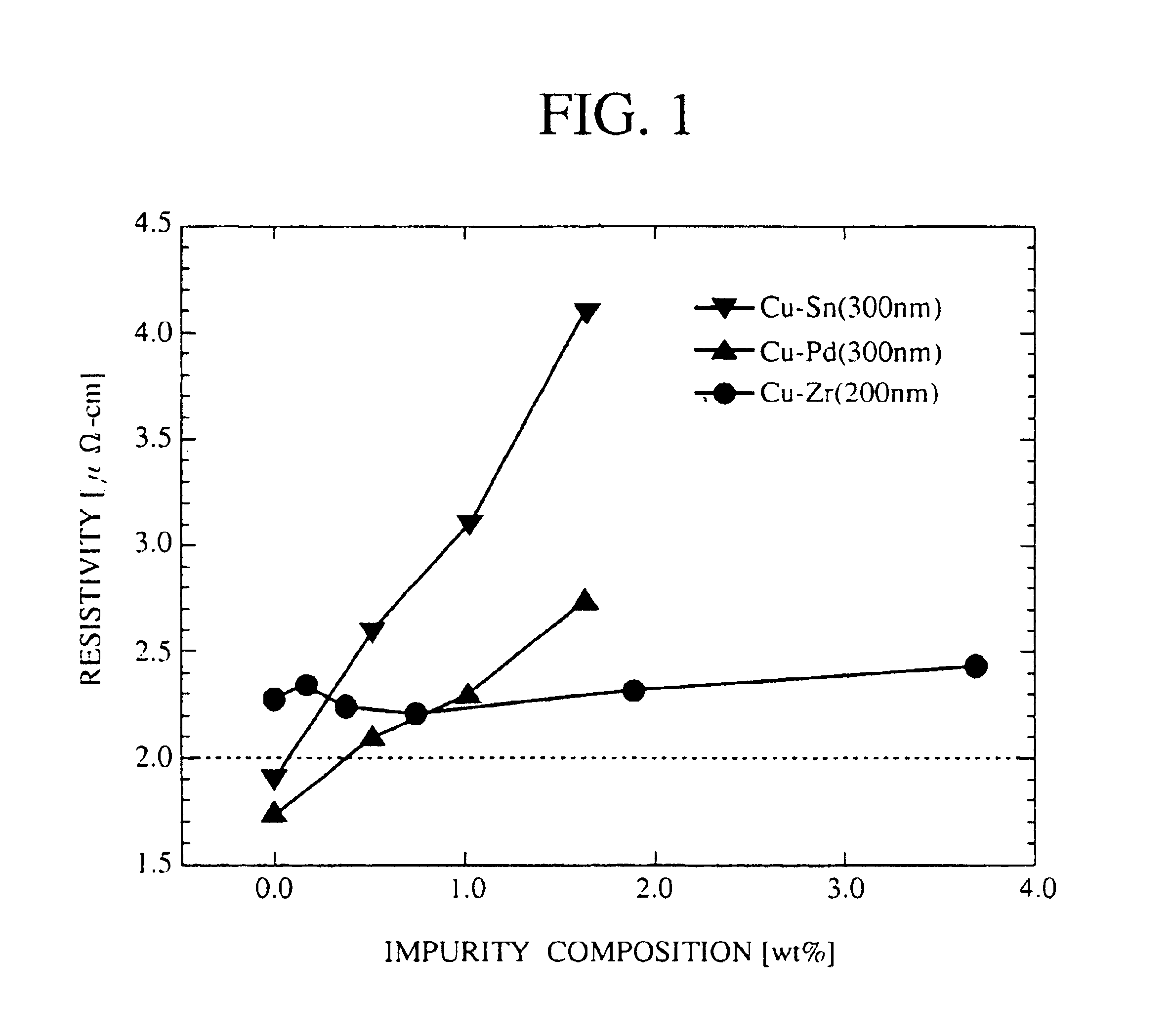

Metal interconnection, semiconductor device, method for forming metal interconnection and method for fabricating semiconductor device

InactiveUS6841477B1Improve electro migration resistanceImprove migration resistance stressSemiconductor/solid-state device detailsSolid-state devicesMetal interconnectEngineering

A semiconductor device comprising: a base substrate including a semiconductor substrate 10 and a semiconductor element formed on the semiconductor substrate 10; an insulation film 22, 24, 26 formed on the base substrate having an opening 30, 32; and a metal interconnection 42 formed buried in the opening 30, 32 including: a barrier layer 34 formed on an inside wall and a bottom of the opening 30, 32; an adhesion layer 36 containing zirconium formed on the barrier layer 34; and a metal interconnection material 38, 40 containing copper as a main component formed on the barrier layer 36. Whereby the peeling of the copper interconnection in the fabrication process can be prevented. The electro migration resistance and stress migration resistance of the copper interconnection can be further improved.

Owner:FUJITSU LTD

Method of manufacturing a semiconductor device

InactiveUS20090181535A1Semiconductor/solid-state device detailsNanoinformaticsElectrical resistance and conductanceCarbon nanotube

Scale down design has posed problems in an increase in the resistance value of an interconnection structure and a decrease in the resistance to electromigration and stress migration. The present invention provides an interconnection structure of a high-reliability semiconductor device which has a low resistance value even in the case of scale down design and does not produce electromigration or stress migration, and a method of manufacturing the interconnection structure. Provided are a semiconductor device which has an interconnection or a connection plug, both of which are fabricated from a mixture of a metal and carbon nanotubes, in an interconnection trench or a via hole, both of which are formed on an insulating film on a substrate on which a semiconductor device element is formed, and a method of manufacturing this semiconductor device.

Owner:NEC CORP

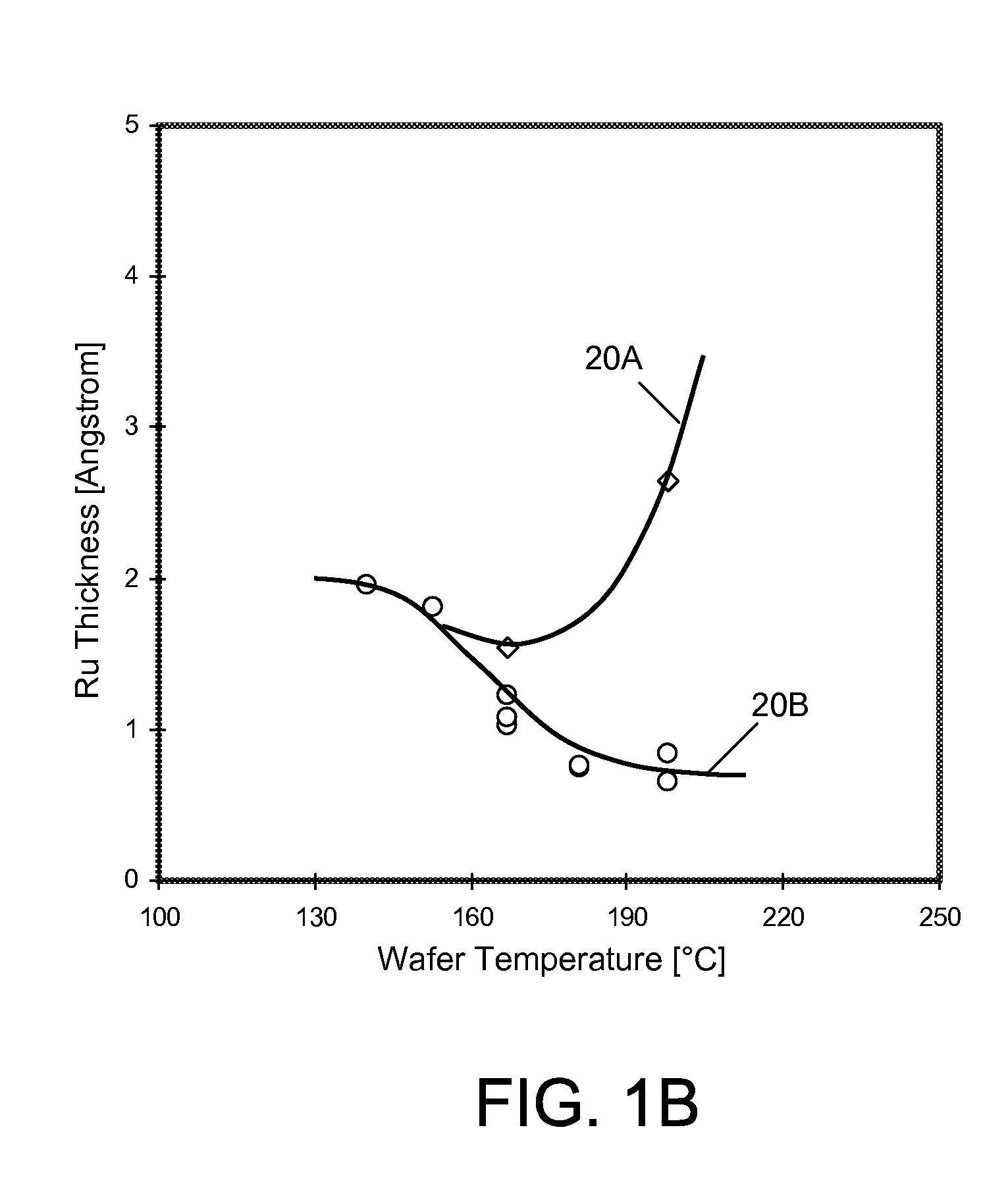

Method for forming a ruthenium metal cap layer

ActiveUS20100015798A1Improve electromigrationImprove stress migrationSemiconductor/solid-state device manufacturingChemical vapor deposition coatingRutheniumPatterned substrate

A method for integrating ruthenium (Ru) metal cap layers and modified Ru metal cap layers into copper (Cu) metallization of semiconductor devices to improve electromigration (EM) and stress migration (SM) in bulk Cu metal. In one embodiment, the method includes providing a planarized patterned substrate containing a Cu metal surface and a dielectric layer surface, depositing first Ru metal on the Cu metal surface, and depositing additional Ru metal on the dielectric layer surface, where the amount of the additional Ru metal is less than the amount of the first Ru metal. The method further includes at least substantially removing the additional Ru metal from the dielectric layer surface to improve the selective formation of a Ru metal cap layer on the Cu metal surface. Other embodiments further include incorporating one or more types of modifier elements into the dielectric layer surface, the Cu metal surface, the Ru metal cap layer, or a combination thereof.

Owner:TOKYO ELECTRON LTD

Semiconductor device and manufacturing process therefor as well as plating solution

InactiveUS20050140013A1Improve stress migration resistanceImprove equipment reliabilitySemiconductor/solid-state device detailsSolid-state devicesDevice materialAlloy

A semiconductor device of improved stress-migration resistance and reliability includes an insulating film having formed therein a lower interconnection consisting of a barrier metal film and a copper-silver alloy film, on which is then formed an interlayer insulating film. In the interlayer insulating film is formed an upper interconnection consisting of a barrier metal film and a copper-silver alloy film. The lower and the upper interconnections are made of a copper-silver alloy which contains silver in an amount more than a solid solution limit of silver to copper.

Owner:RENESAS ELECTRONICS CORP

De-fluorination after via etch to preserve passivation

InactiveUS20060099785A1Improve functionalityEnhance layeringSemiconductor/solid-state device manufacturingEtchingIon current

Novel interconnect structures possessing a dense OSG material for 90 nm and beyond BEOL technologies in which a low power density oxygen-based de-fluorination plasma process is utilized to increase NBLoK selectivity are presented. These BEOL interconnect structures are capable of delivering enhanced reliability and performance due to the reduced risk of Cu exposure and hence electromigration and stress migration related failures. The oxygen based de-fluorination process is such that the plasma conditions employed {low power density (<0.3 Wcm−2); relatively high pressure (>100 mT); negligible ion current to wafer surface (applied source frequency only)} facilitate a physical expulsion of residual fluorine present on the chamber walls, wafer surface, and within the via structure; thus, minimizing the extent of NBLoK etching that can occur subsequent to removing polymeric byproducts of via etching.

Owner:GOOGLE LLC

Method for forming cobalt nitride cap layers

ActiveUS20100081275A1Improve electromigrationImprove stress migrationSemiconductor/solid-state device detailsSolid-state devicesCobalt metalDevice material

A method is provided for integrating cobalt nitride cap layers into manufacturing of semiconductor devices to improve electromigration and stress migration in copper (Cu) metal. One embodiment includes providing a patterned substrate containing a recessed feature formed in a low-k material and a first metallization layer at the bottom of the feature, forming a cobalt nitride cap layer on the first metallization layer, depositing a barrier layer in the recessed feature, including on the low-k dielectric material and on the first cobalt metal cap layer, and filling the recessed feature with Cu metal. Another embodiment includes providing a patterned substrate having a substantially planar surface with Cu paths and low-k dielectric regions, and selectively forming a cobalt nitride cap layer on the Cu paths relative to the low-k dielectric regions.

Owner:TOKYO ELECTRON LTD

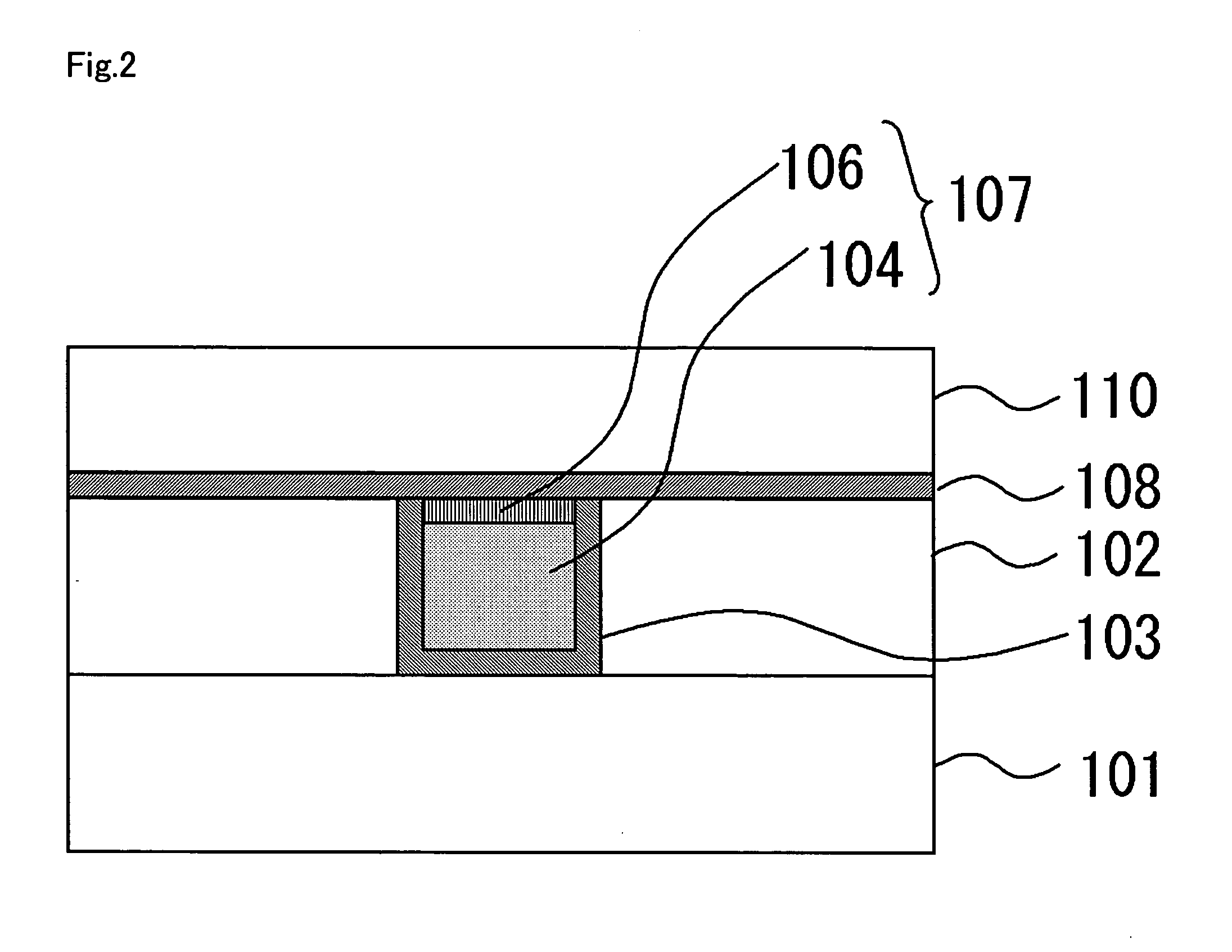

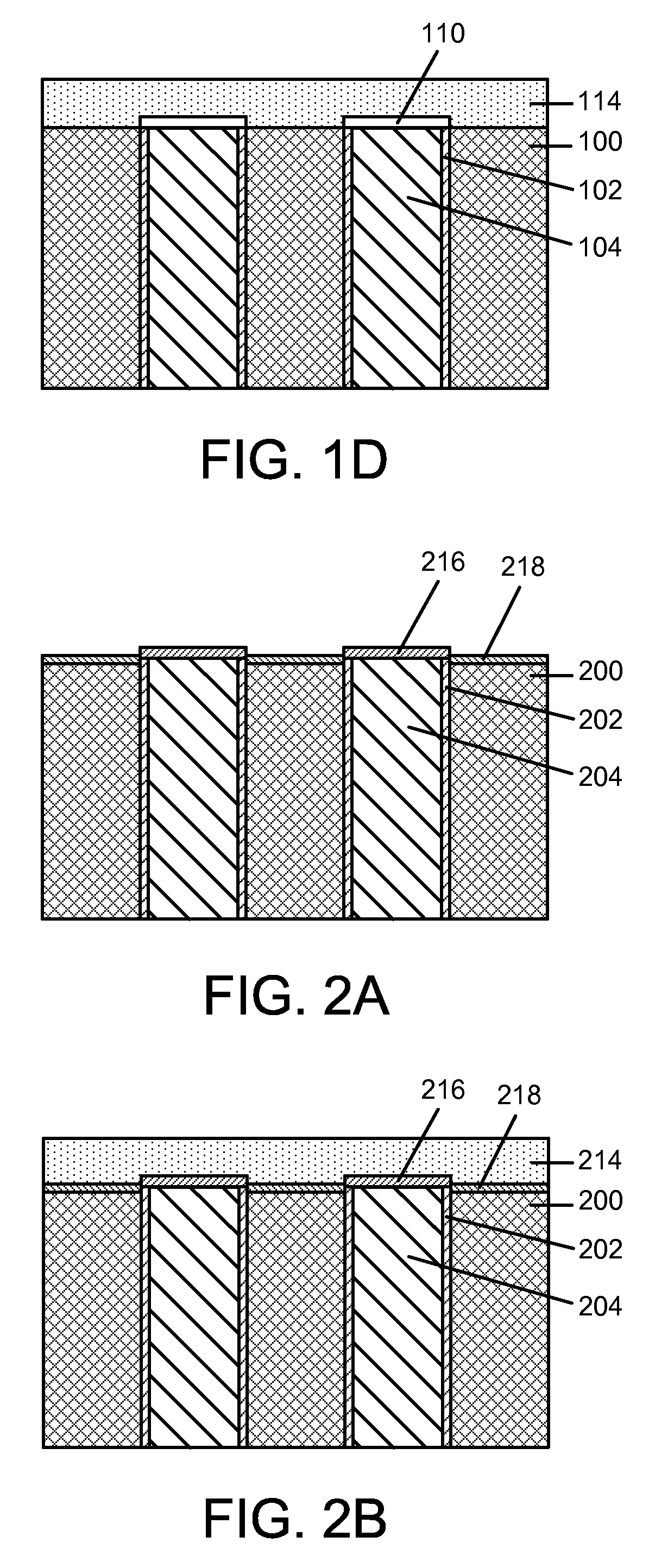

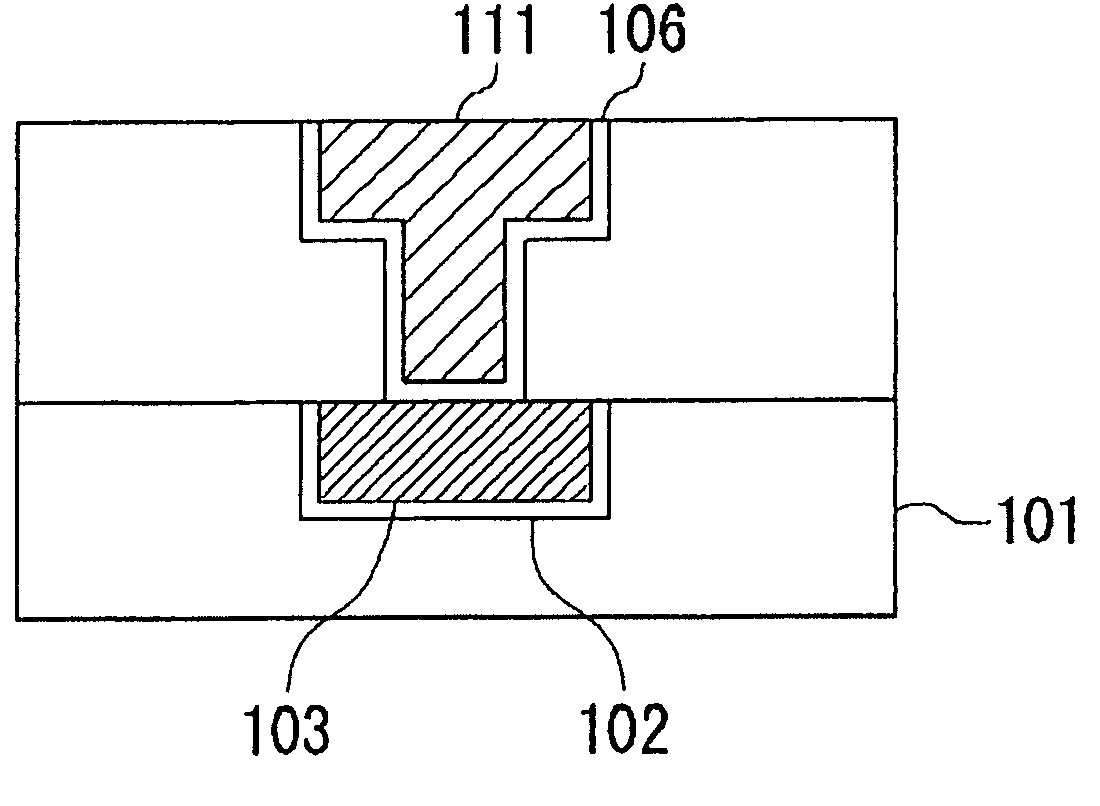

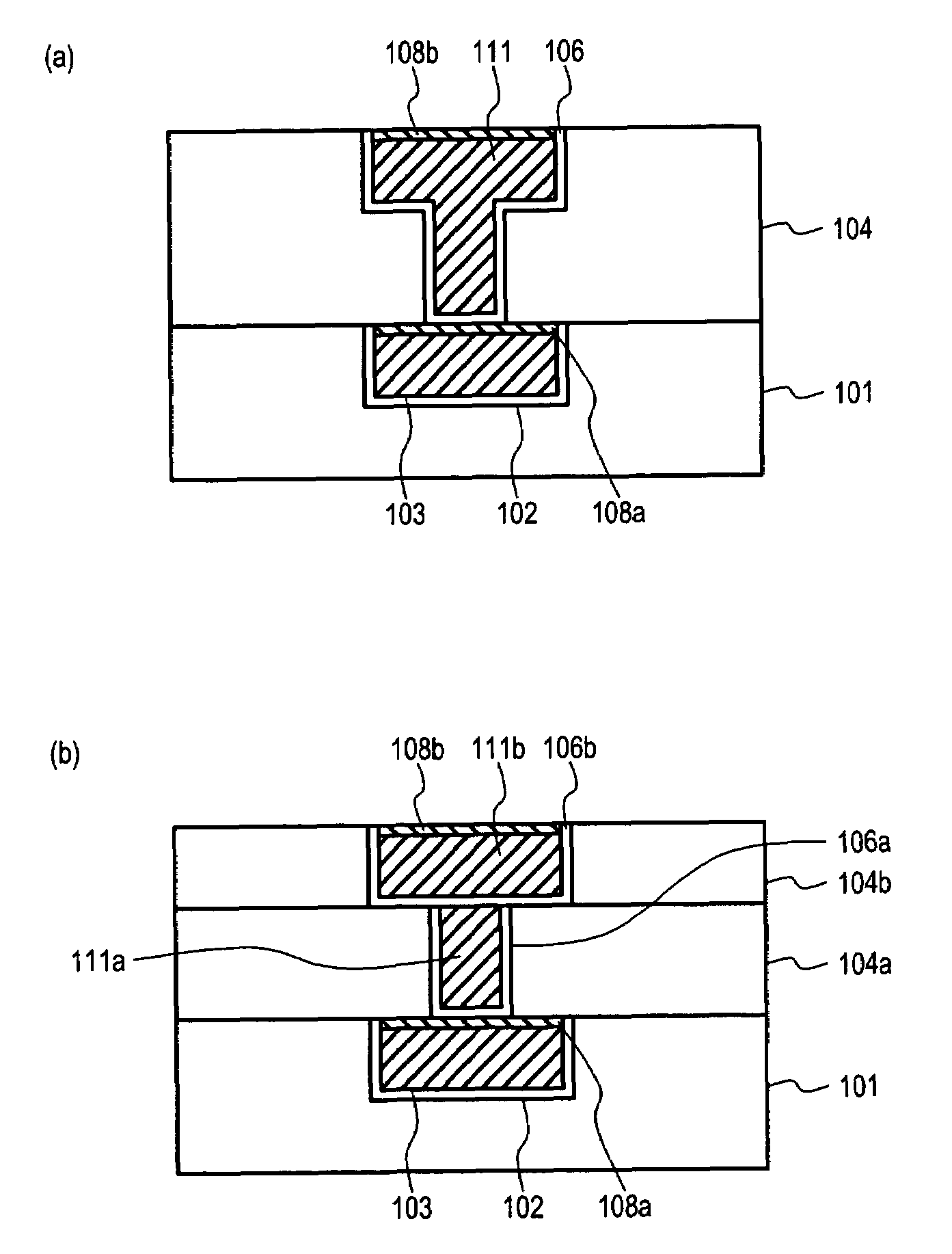

Semiconductor device

InactiveUS7332813B2Large particle sizeLower the resistance valueSemiconductor/solid-state device detailsSolid-state devicesSemiconductorMaterials science

A semiconductor device with a metallic region can have a resistance to stress migration and increased reliability. A lower layer wiring made from a barrier metal film (102) and a copper containing metallic film (103) can be formed within an insulating film (101). An interlayer insulating film (104 or 104a and 104b) can be formed thereon. An upper layer wiring made from a barrier metal film (106 or 106a and 106b) and a copper containing metallic film (111 or 111a and 111b) is formed within the interlayer insulating film (104 or 104a and 104b). A silver containing metallic protective film (108a and 108b) can be formed on surfaces of the lower layer wiring and upper layer wiring.

Owner:RENESAS ELECTRONICS CORP

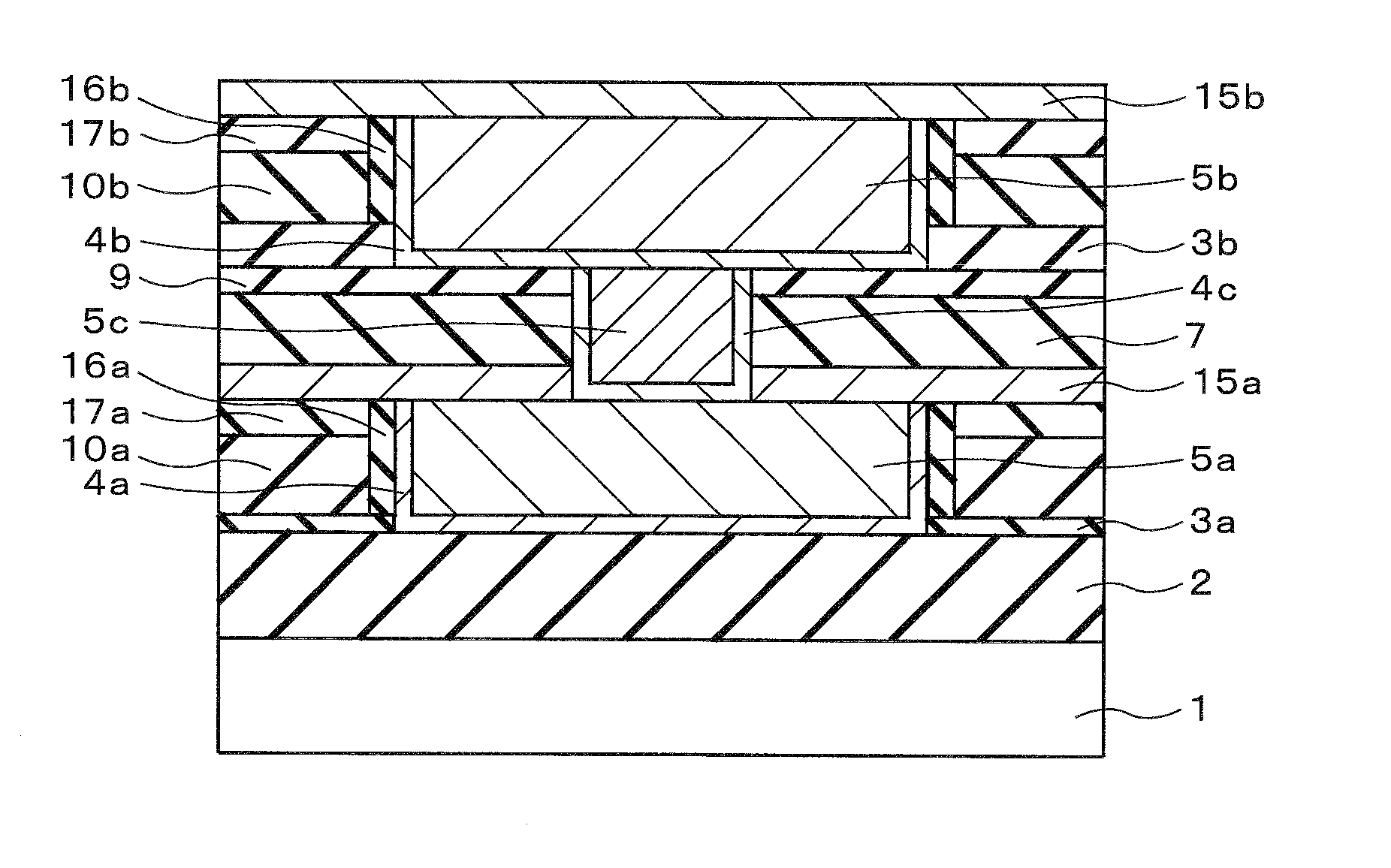

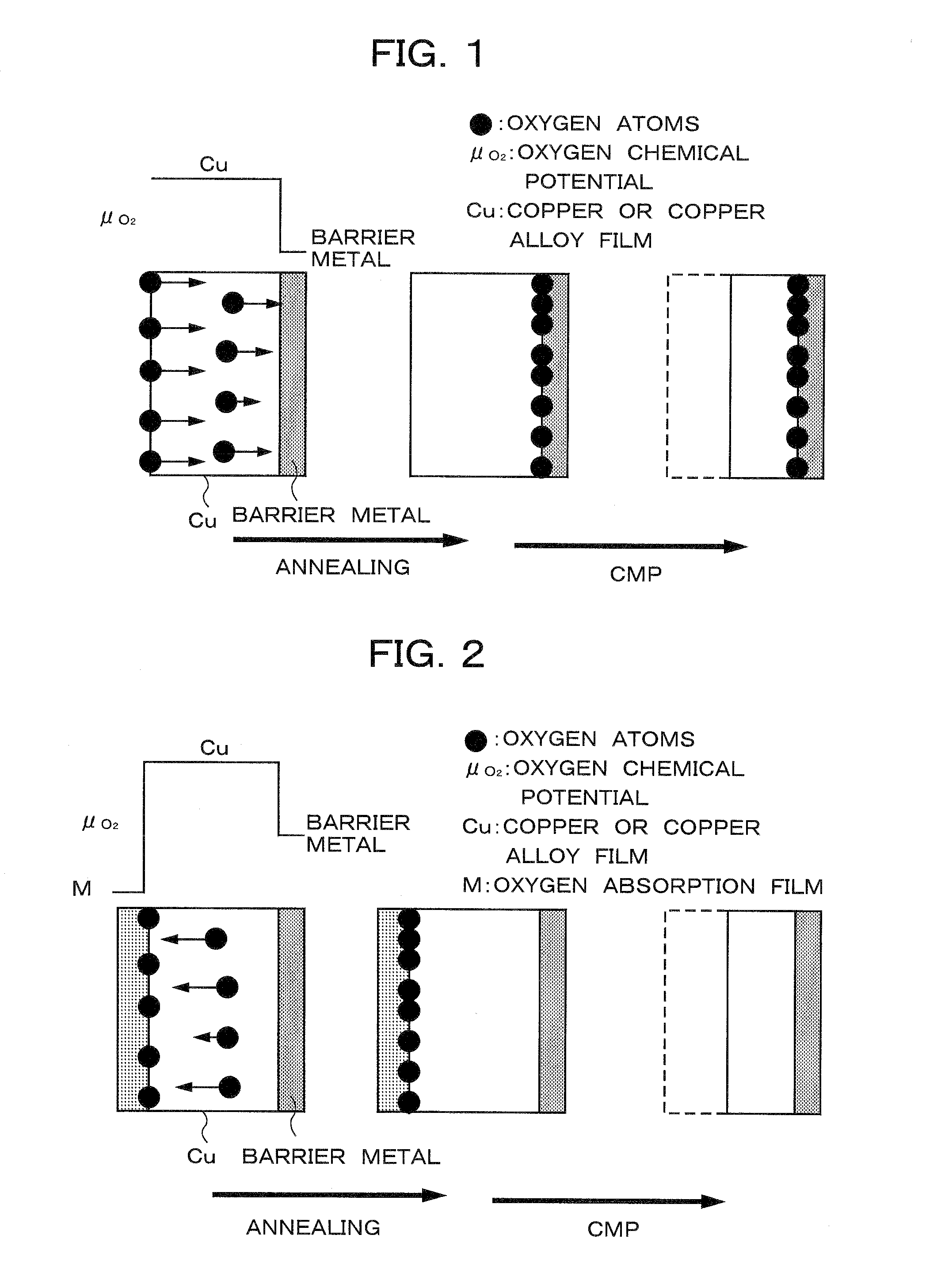

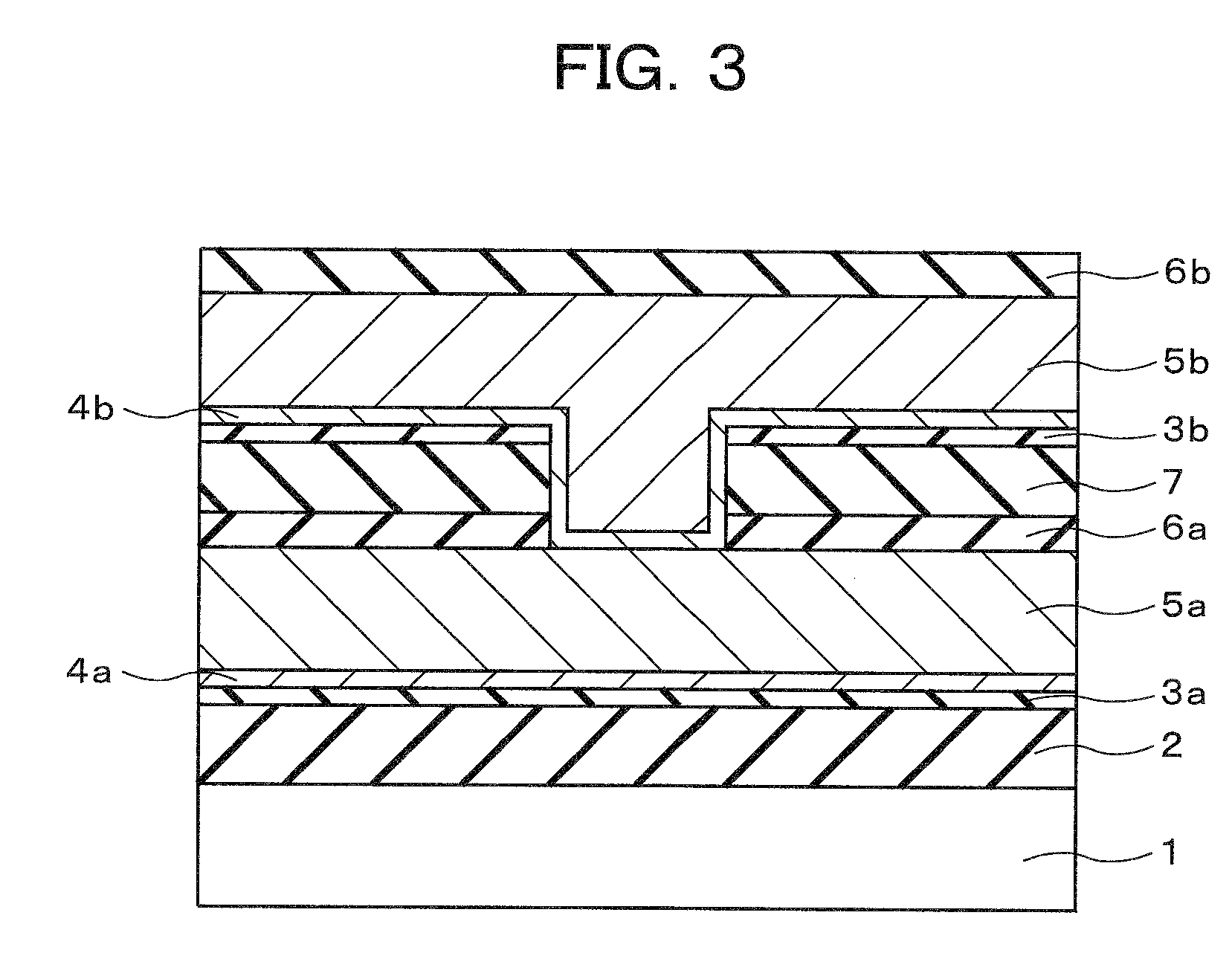

Semiconductor device and method for manufacturing same

ActiveUS20100193953A1Improve adhesionIncrease resistanceSemiconductor/solid-state device detailsSolid-state devicesRoom temperatureSemiconductor

A trench is formed in an insulation film formed on top of a semiconductor substrate, and a barrier metal film is formed on the surface of the trench. After a copper or copper alloy film is formed on the barrier metal film, an oxygen absorption film in which a standard energy of formation of an oxidation reaction in a range from room temperature to 400° C. is negative, and in which an absolute value of the standard energy of formation is larger than that of the barrier metal film is formed, and the assembly is heated in a temperature range of 200 to 400° C. A semiconductor device can thereby be provided that has highly reliable wiring, in which the adhesion to the barrier metal film in the copper interface is enhanced, copper diffusion in the interface is suppressed, and electromigration and stress migration are prevented.

Owner:GK BRIDGE 1

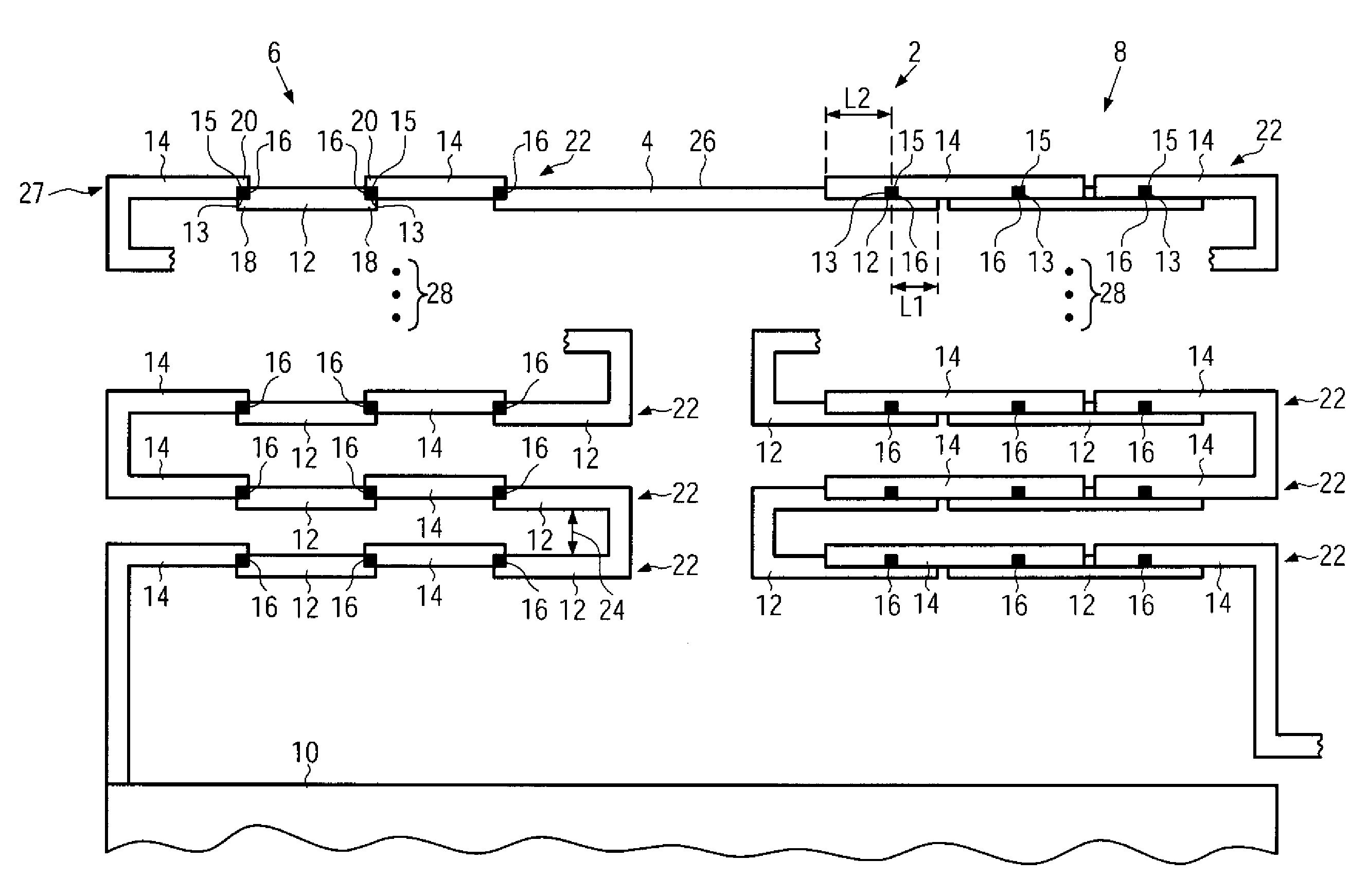

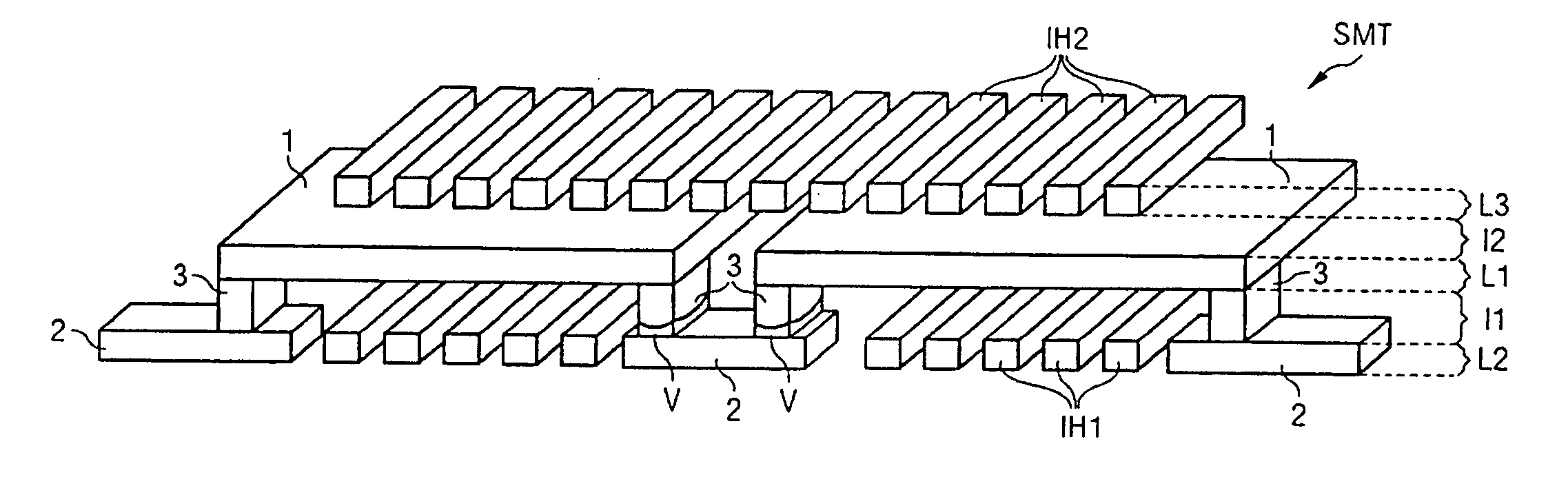

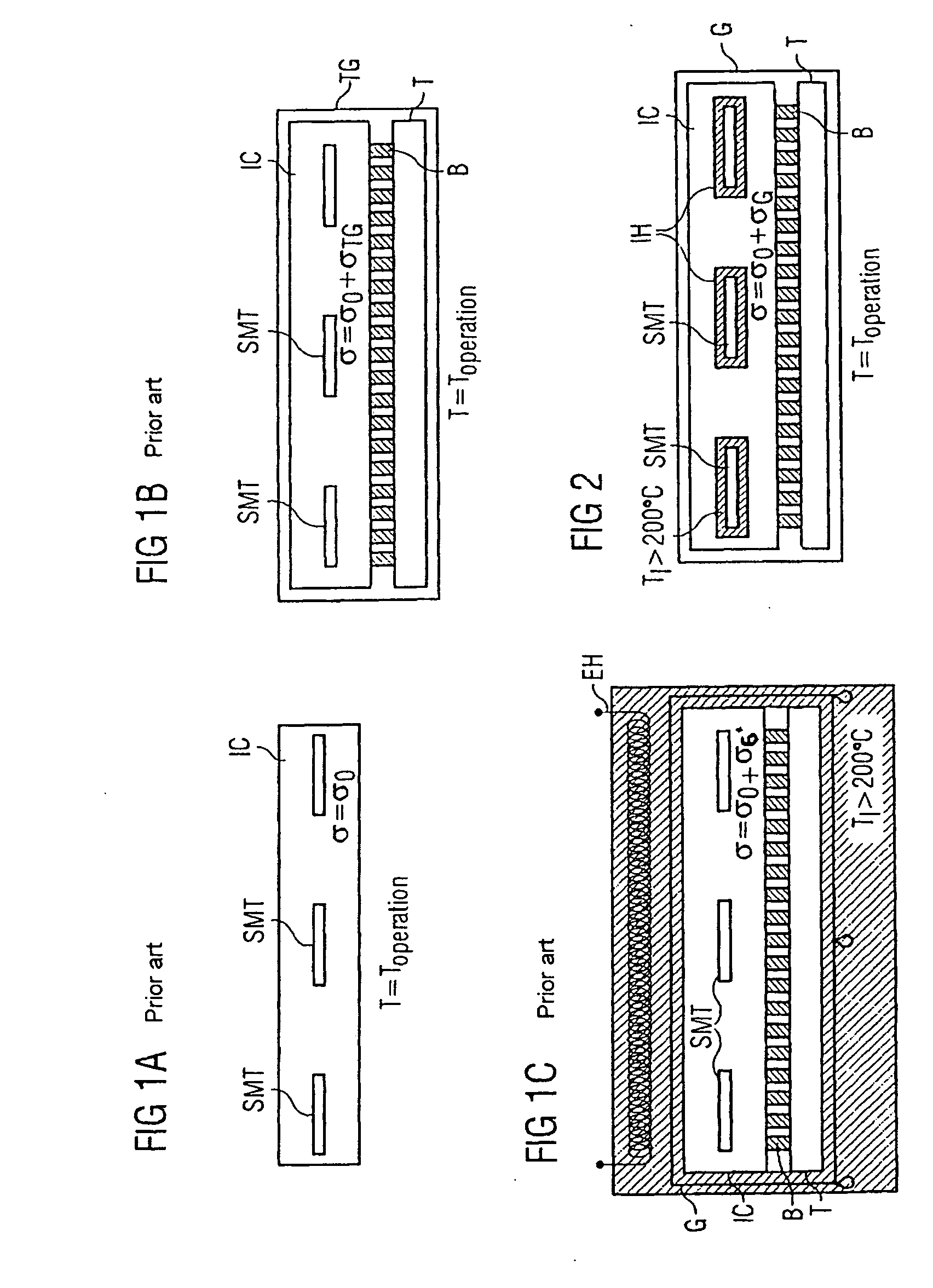

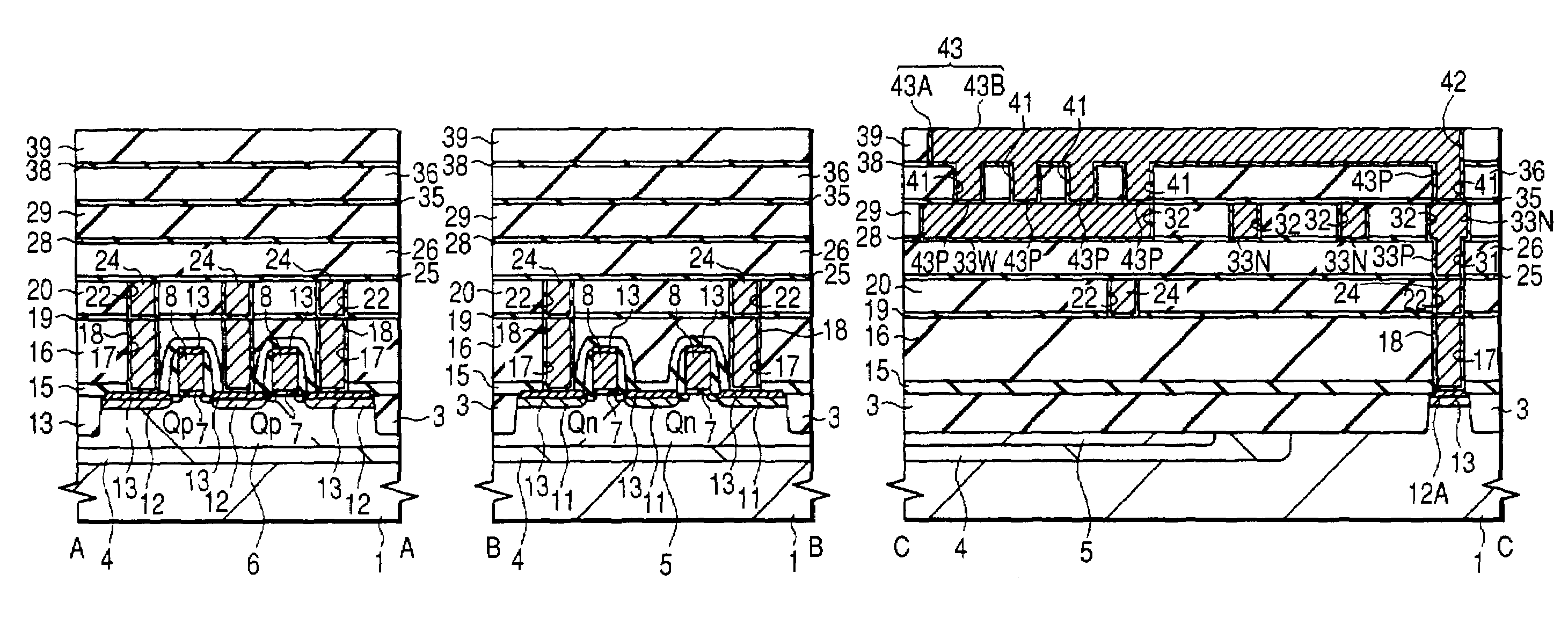

Unified test structure for stress migration tests

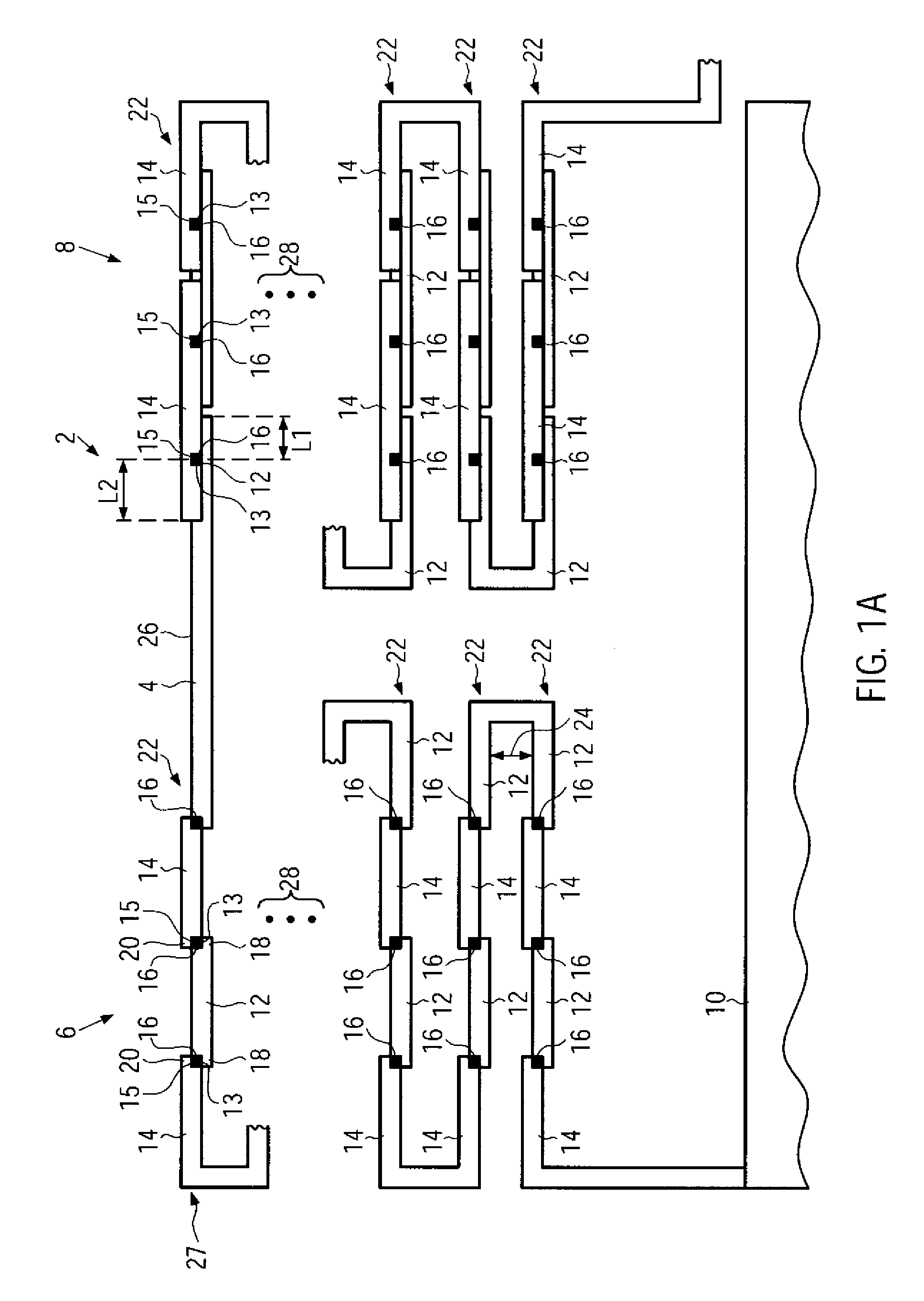

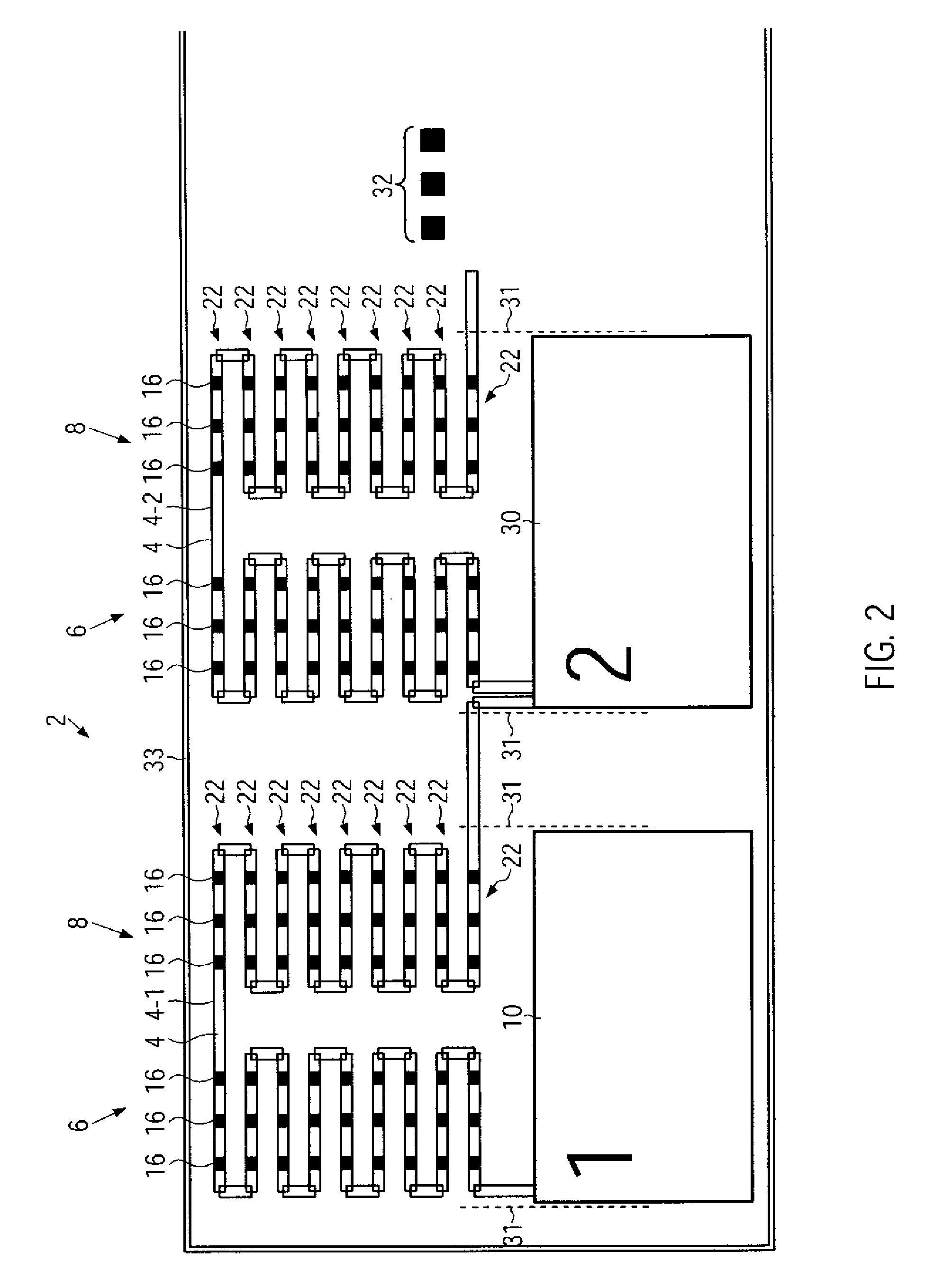

InactiveUS20080265247A1Well formedSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsSemiconductorStress migration

A unified test structure which is applicable for all levels of a semiconductor device including a current path chain having a first half chain and a second half chain, wherein each half chain comprises lower metallization segments, upper metallization segments, an insulating layer between the lower metallization segments and the upper metallization segments, and connection segments. Each of the connection segments is electrically connected to a contact region of one of the lower metallization segments and to a contact region of one of the upper metallization segments to thereby electrically connect the respective lower metallization segment and the respective upper metallization segment, and the first half chain and the second half chain are of different configuration.

Owner:GLOBALFOUNDRIES INC

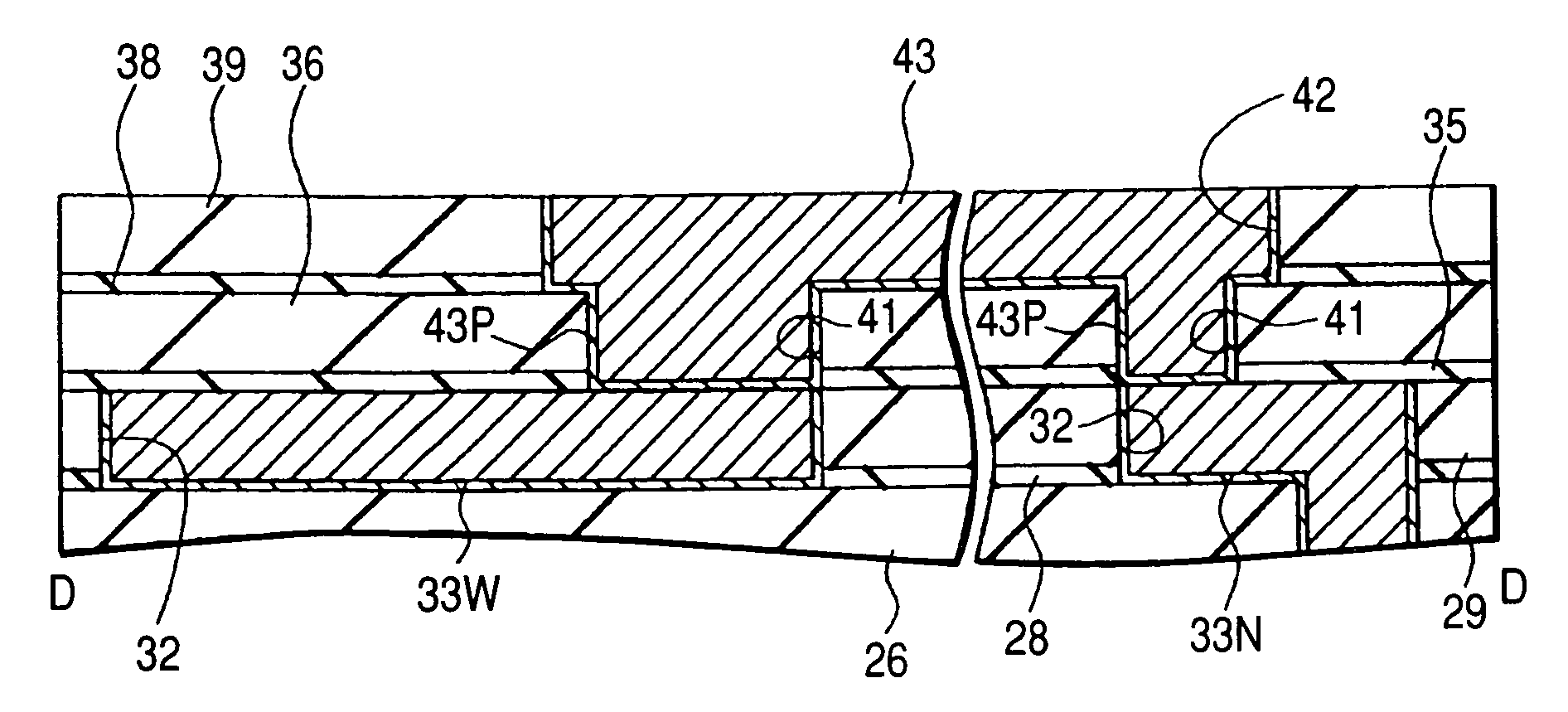

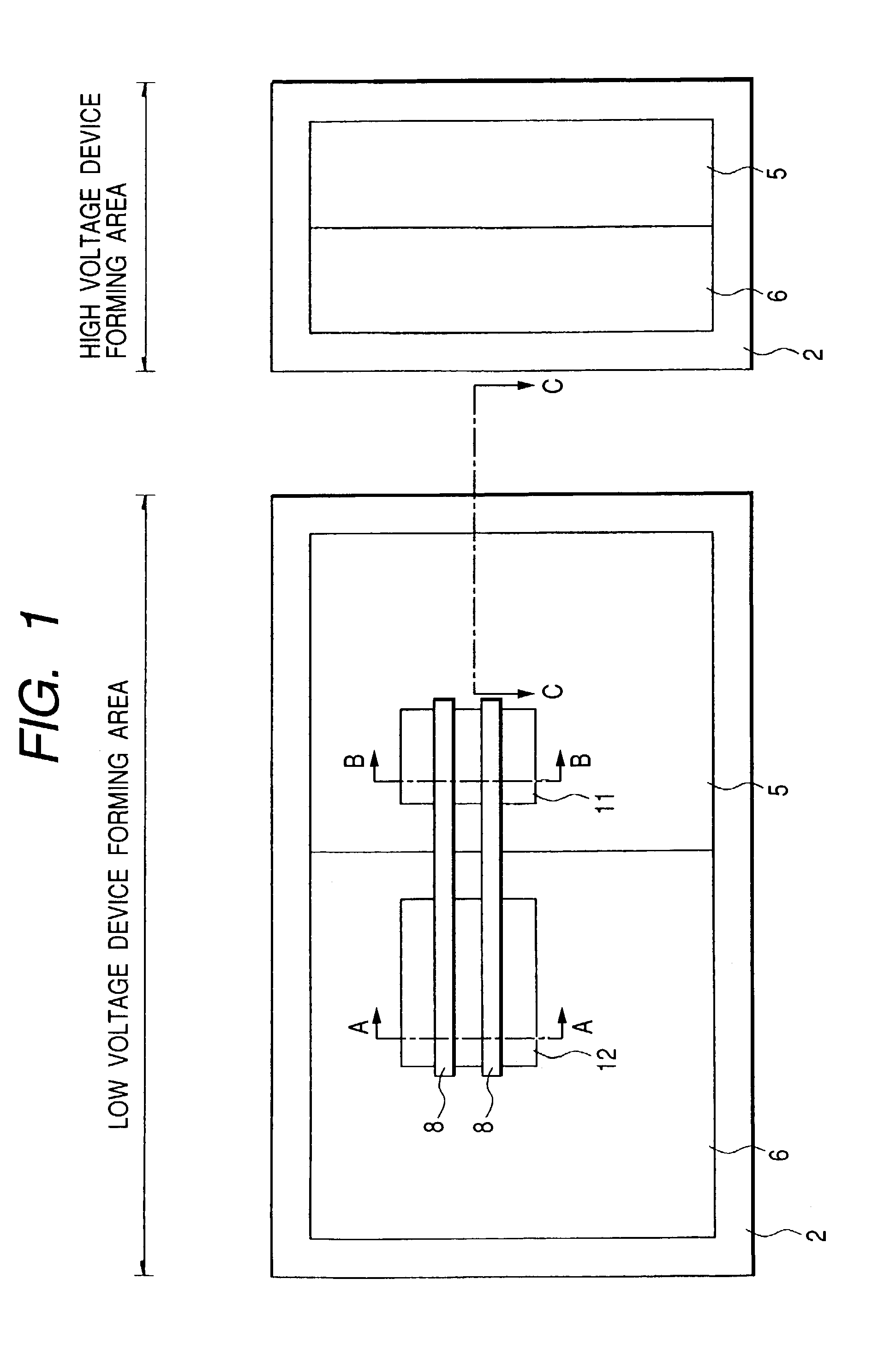

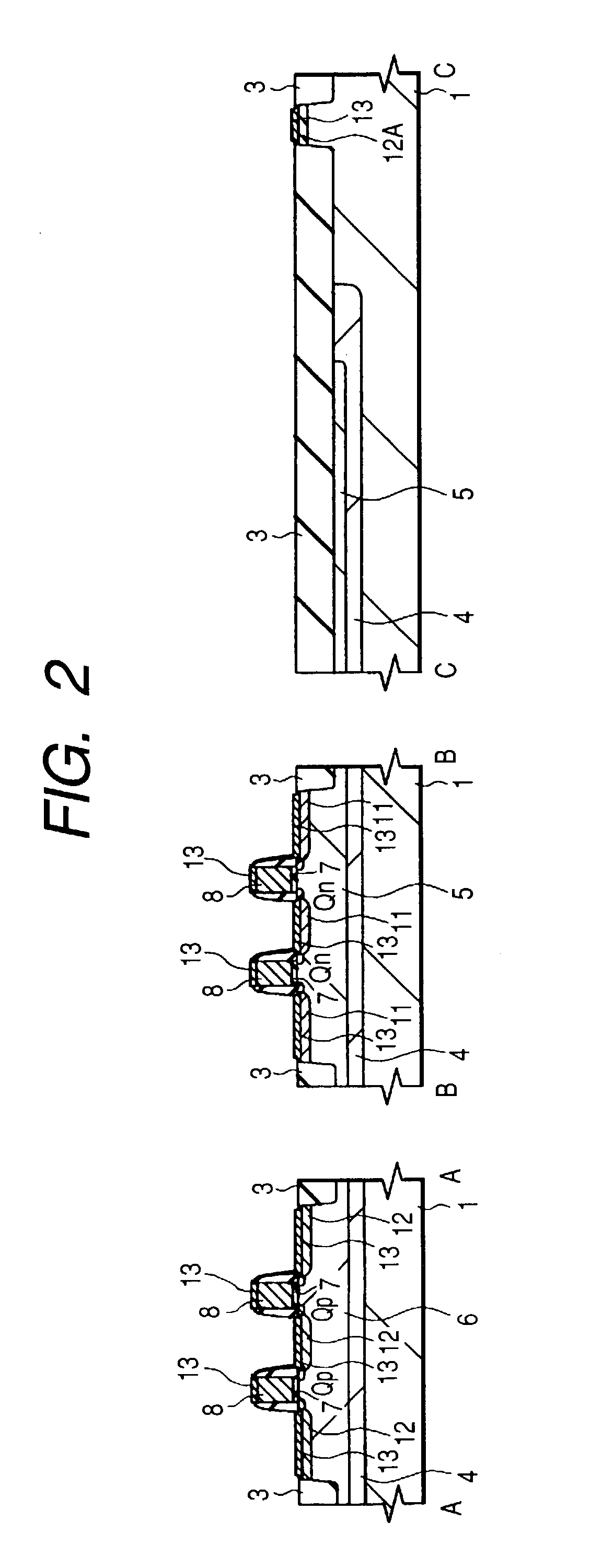

Semiconductor integrated circuit device

InactiveUS7411301B2Relieve pressureEasy to produceSemiconductor/solid-state device detailsSolid-state devicesSemiconductorStress migration

In a semiconductor integrated circuit device having plural layers of buried wirings, it is intended to prevent the occurrence of a discontinuity caused by stress migration at an interface between a plug connected at a bottom thereof to a buried wiring and the buried wiring. For example, in the case where the width of a first Cu wiring is not smaller than about 0.9 μm and is smaller than about 1.44 μm, and the width of a second Cu wiring and the diameter of a plug are about 0.18 μm, there are arranged two or more plugs which connect the first wirings and the second Cu wirings electrically with each other.

Owner:RENESAS ELECTRONICS CORP

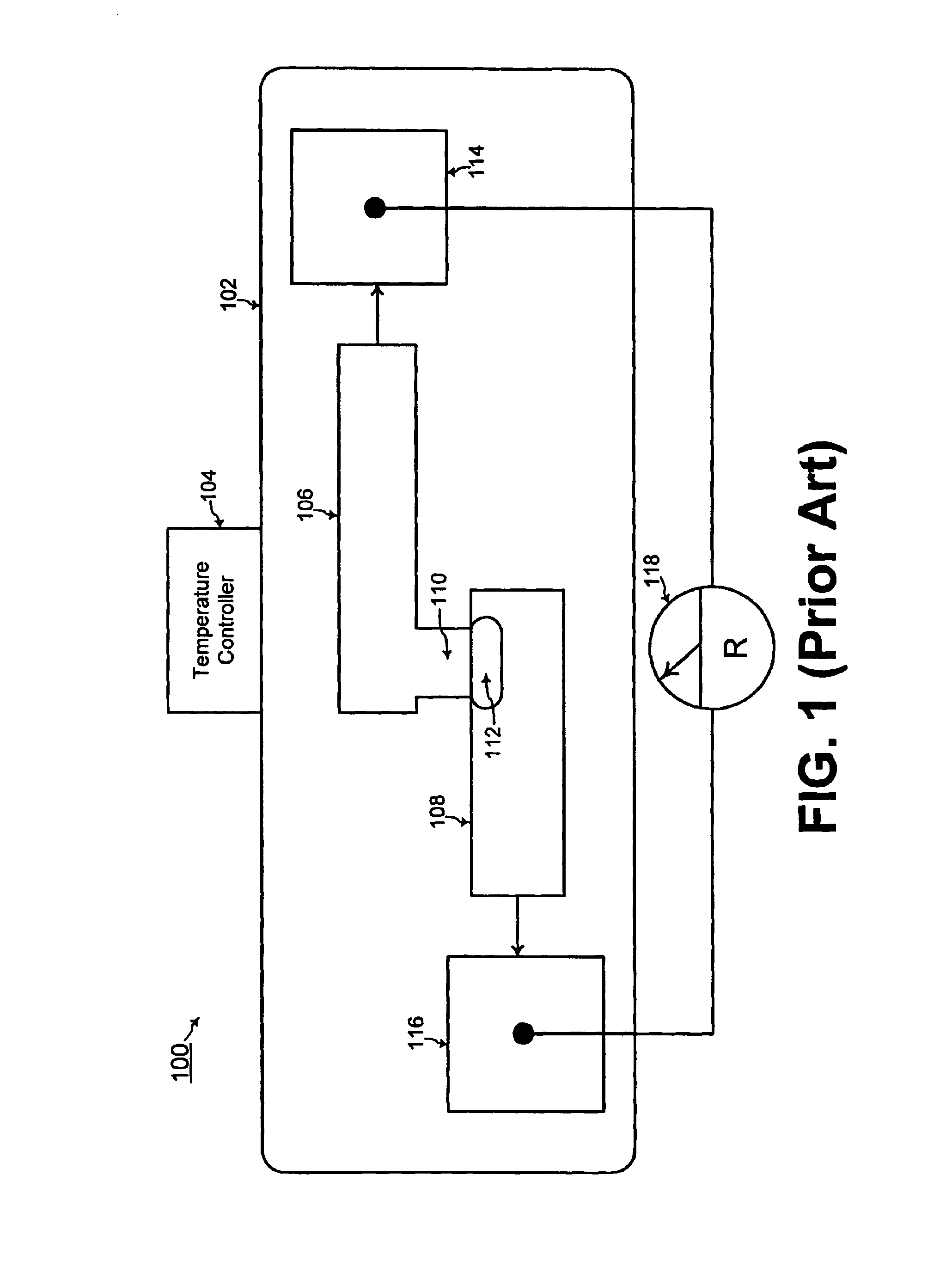

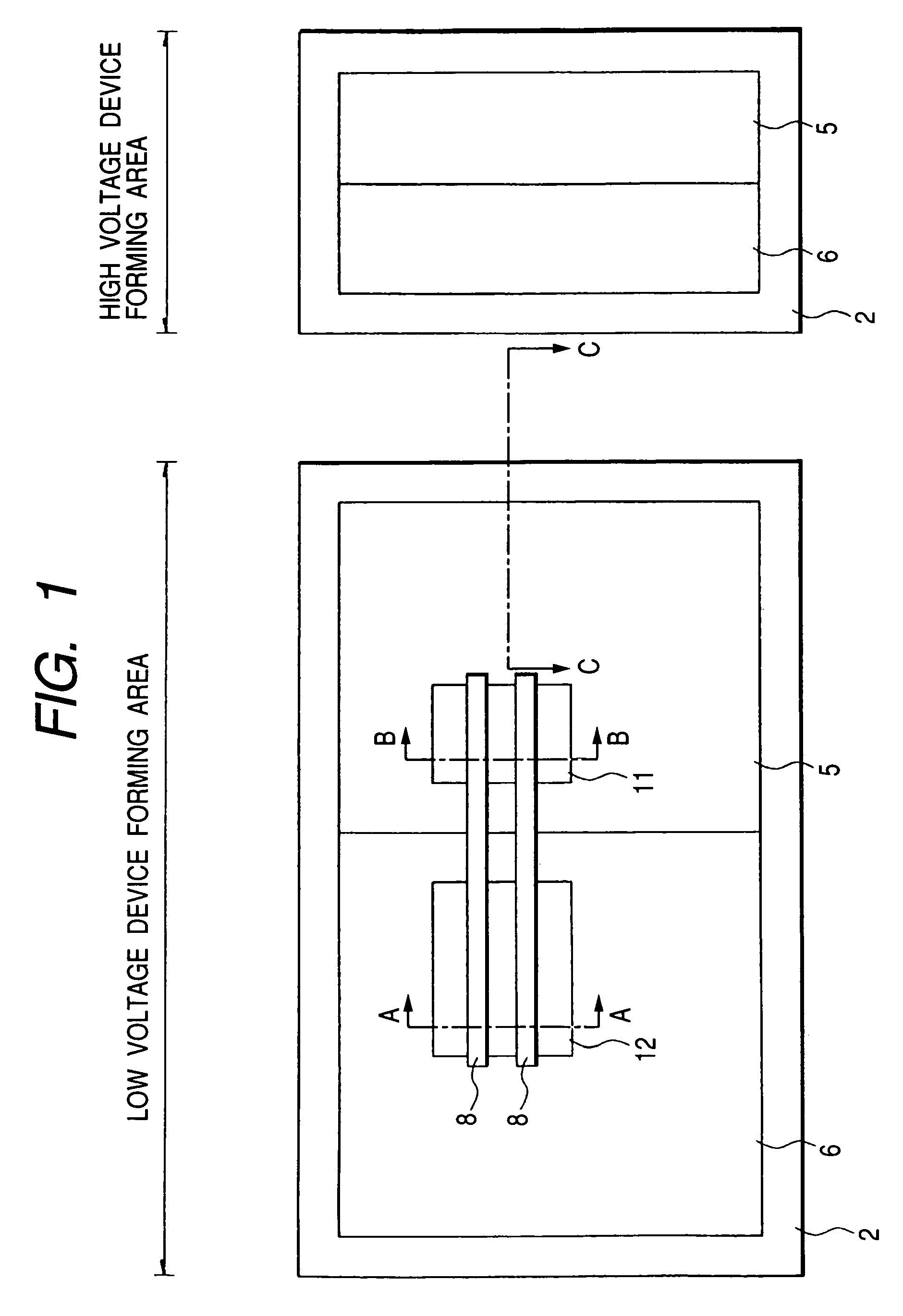

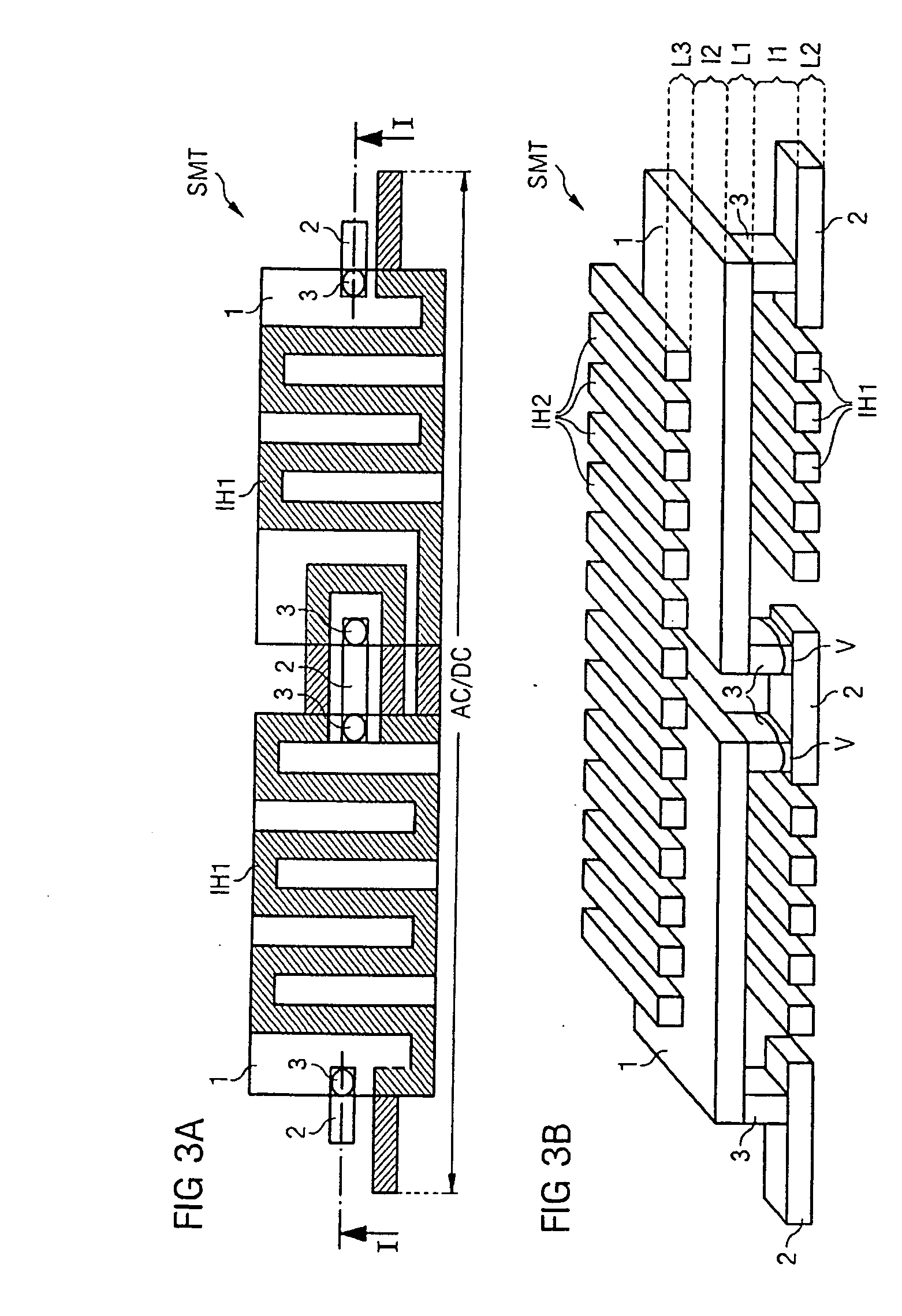

Device and method for detecting stress migration properties

InactiveUS20050211980A1Accurate assessmentShort timeSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsSemiconductorStress migration

A device and method are provided for detecting stress migration properties of a semiconductor module mounted in a housing. A stress migration test (SMT) structure is formed in the semiconductor module. An integrated heating (IH) device is formed within or in direct proximity to the SMT structure. The SMT structure includes a first interconnect region in a first interconnect layer, a second interconnect region in a second interconnect layer, and a connecting region electrically connecting the interconnect regions through a first insulating layer. The IH device includes a heating interconnect region through which a heating current flows. The heating interconnect region is within or outside the first or second interconnect region or connecting region. When the heating current is applied, a measurement voltage is applied to the SMT structure, and a current through the SMT structure is measured to detect stress migration properties of the semiconductor module.

Owner:INFINEON TECH AG

Composite tantalum nitride/tantalum copper capping layer

ActiveUS7157795B1Reducing interconnect capacitanceImprove electromigrationSemiconductor/solid-state device detailsSolid-state devicesTantalum nitrideTitanium nitride

Electromigration and stress migration of Cu interconnects are significantly reduced by forming a composite capping layer comprising a layer of tantalum nitride on the upper surface of the inlaid Cu and a layer of α-Ta on the titanium nitride layer. Embodiments include forming a recess in an upper surface of an upper surface of Cu inlaid in a dielectric layer, depositing a layer of titanium nitride of a thickness of 20 Å to 100 Å and then depositing a layer of α-Ta at a thickness of 200 Å to 500 Å.

Owner:INNOVATIVE FOUNDRY TECH LLC

Semiconductor integrated circuit device

InactiveUS7023091B2Preventing exertion of bad influenceInhibited DiffusionSemiconductor/solid-state device detailsSolid-state devicesSemiconductorStress migration

In a semiconductor integrated circuit device having plural layers of buried wirings, it is intended to prevent the occurrence of a discontinuity caused by stress migration at an interface between a plug connected at a bottom thereof to a buried wiring and the buried wiring. For example, in the case where the width of a first Cu wiring is not smaller than about 0.9 μm and is smaller than about 1.44 μm, and the width of a second Cu wiring and the diameter of a plug are about 0.18 μm, there are arranged two or more plugs which connect the first wirings and the second Cu wirings electrically with each other.

Owner:RENESAS ELECTRONICS CORP