Method of manufacturing a semiconductor device

a manufacturing method and semiconductor technology, applied in semiconductor devices, semiconductor/solid-state device details, electrical equipment, etc., can solve problems such as ineffective connection plugs, electrical interference, and changes in tim

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

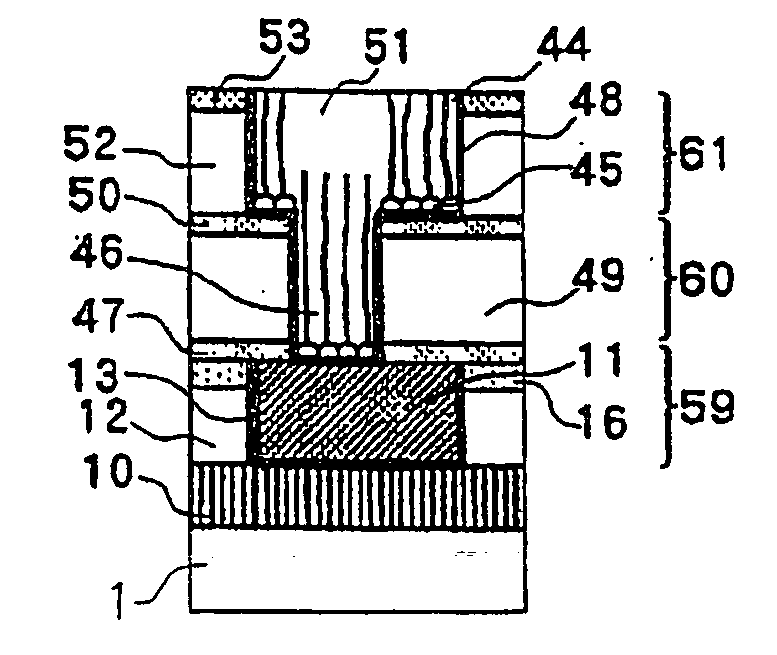

[0050]The description will be given by using FIG. 1 that is a schematic sectional view of an interconnection structure in a semiconductor device of the first embodiment.

[0051]In FIG. 1, an interconnection 11 is constituted by a metal layer 39, which is formed on an insulating film 10 formed on a semiconductor substrate 1 on which a device element or an interconnection is formed. Carbon nanotubes 14 are mixed in the metal layer 39 which constitutes the interconnection 11. The carbon nanotube 14 is formed on a particle 15 of nickel formed on the insulating film 10. The particle 15 acts as a catalyst during the growth of the carbon nanotube, and the carbon nanotube 14 grows, with the particle 15 serving as a nucleus.

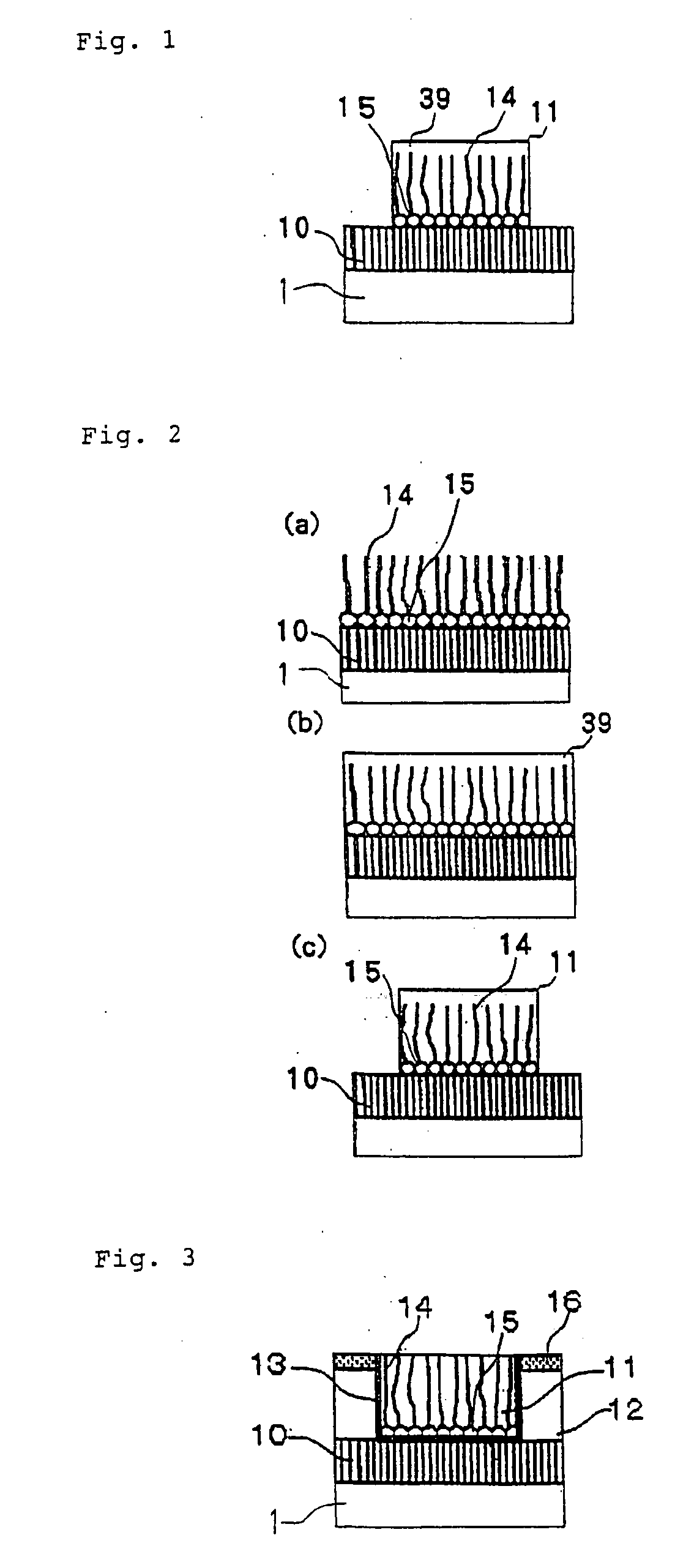

[0052]A manufacturing method of a semiconductor device of the first embodiment will be described with reference to FIGS. 2(a) to 2(c).

(Formation of Substrate and Formation of Carbon Nanotubes)

[0053]The insulating film 10 is formed on a silicon substrate 1 on which a semicon...

second embodiment

[0078]The second embodiment of the present invention is an interconnection trench structure by the single damascene process.

[0079]FIG. 3 shows an interconnection structure by the single damascene process.

[0080]The interconnection structure by the single damascene process will be described. There are formed an insulating film 10, which is formed on a semiconductor substrate 1 on which a device element or an interconnection is formed, an interlayer dielectric film 12 formed on the insulating film 10, and an etching stopper layer 16.

[0081]An interconnection 11 is formed in a trench which is formed in the interlayer dielectric film 12 and the etching stopper layer 16. The interconnection 11 has particles 15 formed on a barrier metal layer 13 and carbon nanotubes 14 which are caused to grow on the particles 15, and is embedded with a metal layer 39.

[0082]The particle 15 may be formed from Fe or Ni and the carbon nanotube 14 may be formed from a carbon fiber, such as a carbon nanotube, a ...

third embodiment

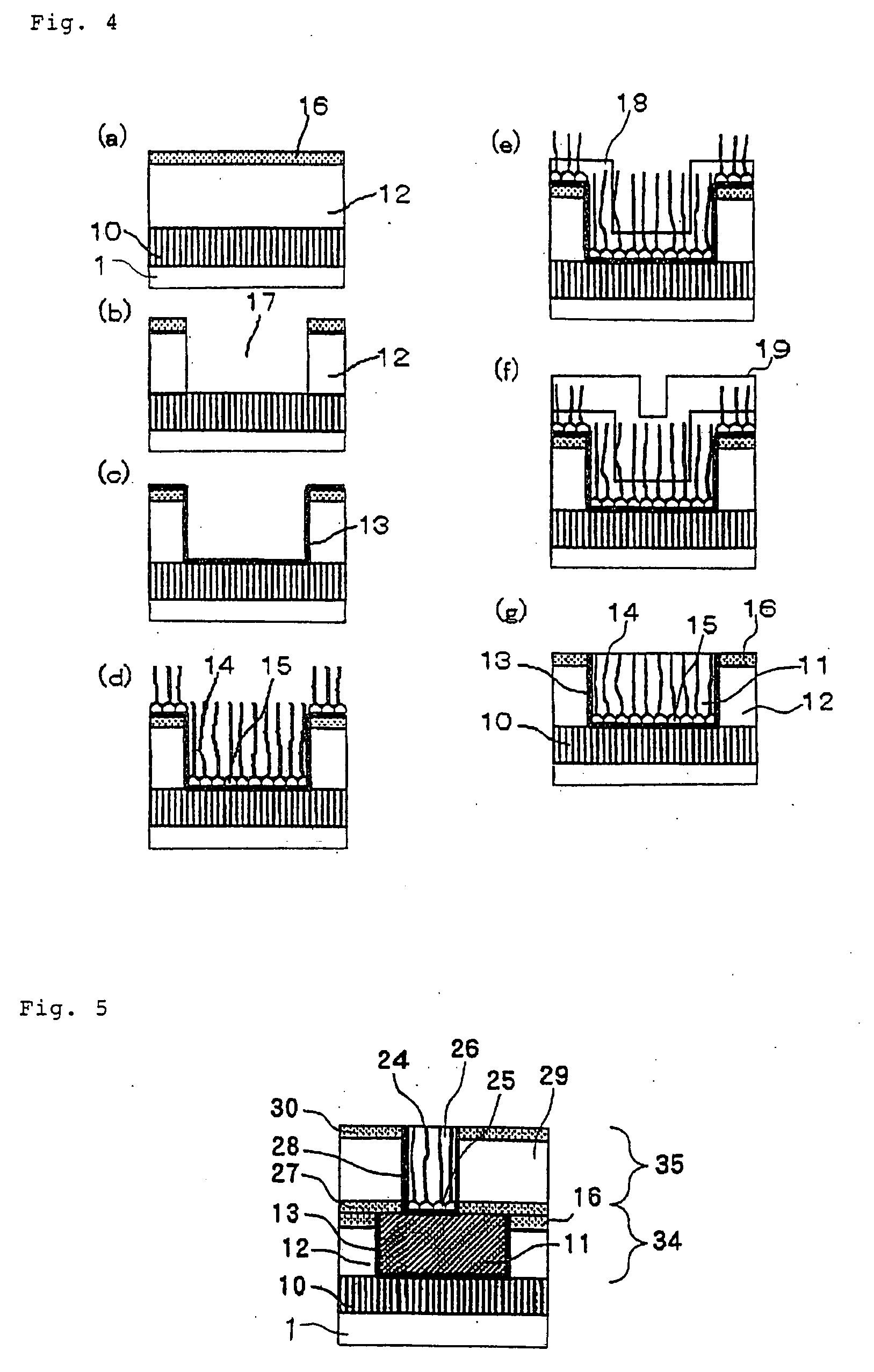

[0118]In the third embodiment, a description is given of a trench interconnection structure by the dual damascene process in which an interconnection and a connection plug are simultaneously formed.

[0119]An interconnection structure by the dual damascene process will be described with reference to FIG. 7.

[0120]Also in FIG. 7, the same numerals are given to the same parts as used in FIGS. 3 and 5.

[0121]Incidentally, although carbon nanotubes are not mixed in the interconnection 11 of FIG. 7, carbon nanotubes 14 may be mixed as shown in FIG. 3.

[0122]A first interconnection layer 59 is constituted by an interlayer dielectric layer 12, an interconnection 11, a barrier metal layer 13, and etching stopper layers 16 and 47.

[0123]This embodiment provides, on an insulating film 10 formed on a substrate 1 including a semiconductor device element, the first interconnection layer 59, a connection plug 60 and a second interconnection layer 61. The first interconnection layer 59 is constituted by...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More