Patents

Literature

40 results about "Copper silicide" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Copper silicide (Cu₅Si), also called pentacopper silicide, is a binary compound of silicon with copper. It is an intermetallic compound, meaning that it has properties intermediate between an ionic compound and an alloy. This a solid crystalline material is a silvery solid that is insoluble in water. It forms upon heating mixtures of copper and silicon.

Integrated circuit and manufacturing method of copper germanide and copper silicide as copper capping layer

ActiveUS7858519B2Improve barrier propertiesAvoiding Cu out diffusingSemiconductor/solid-state device detailsSolid-state devicesGermanideCopper silicide

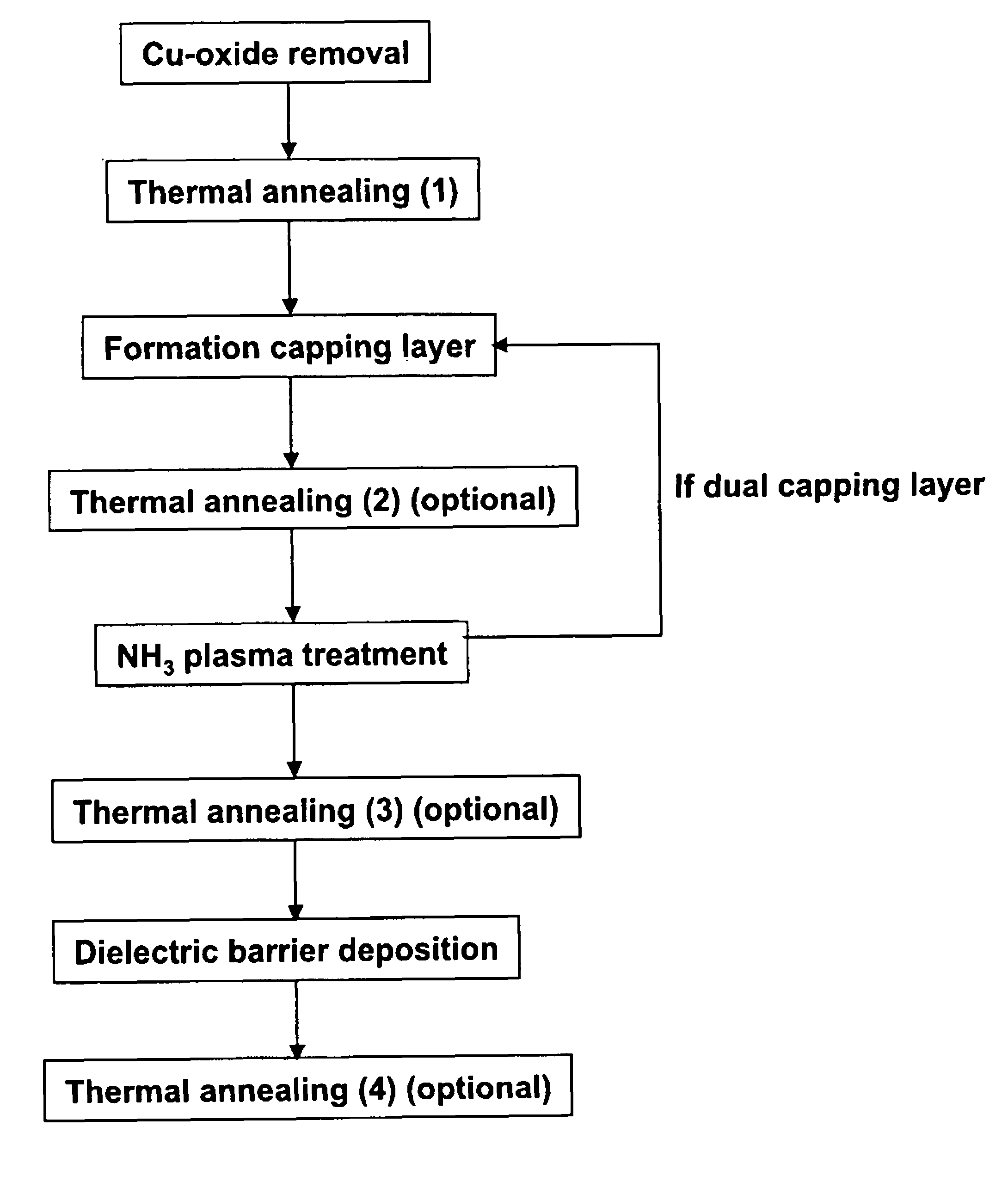

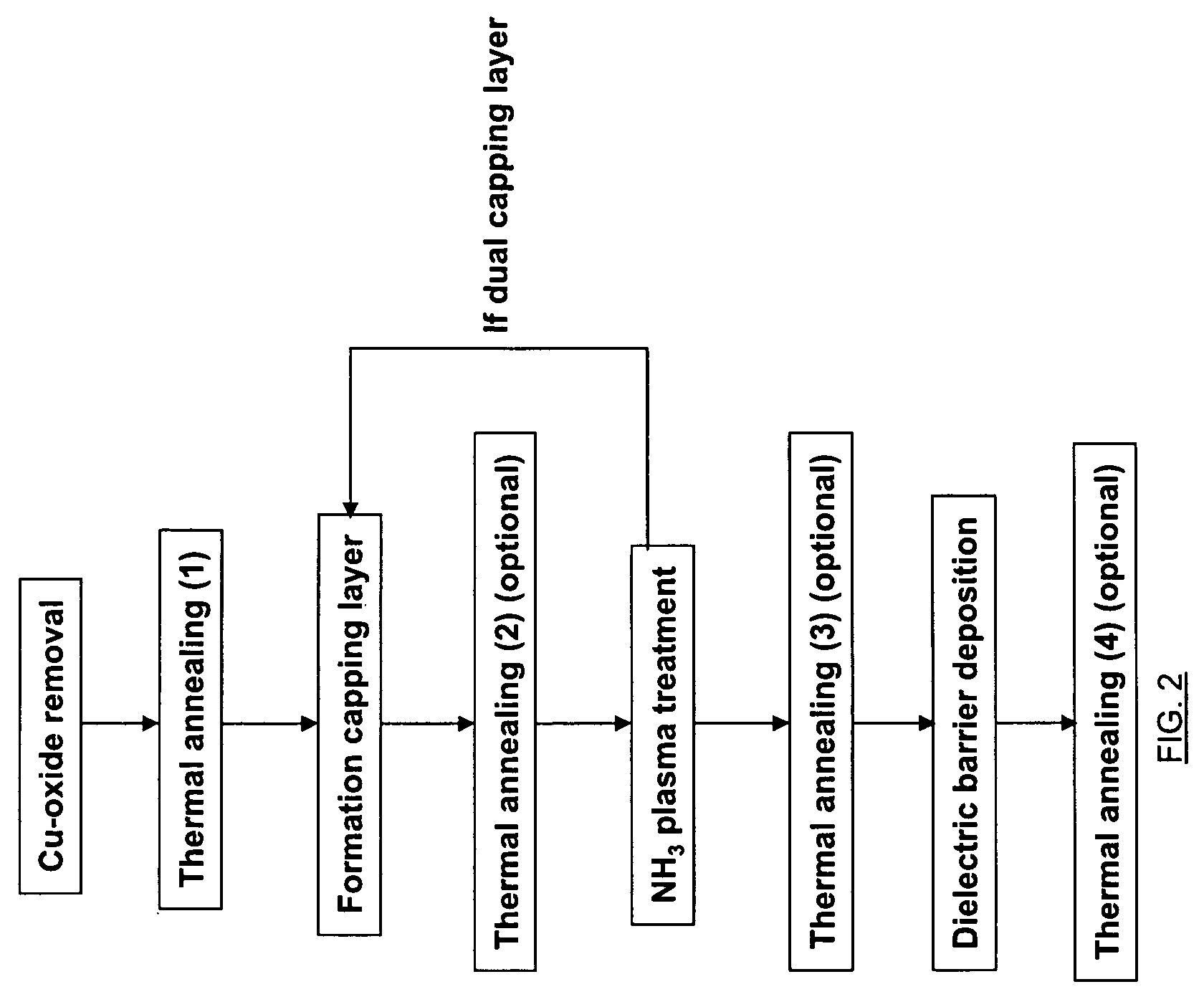

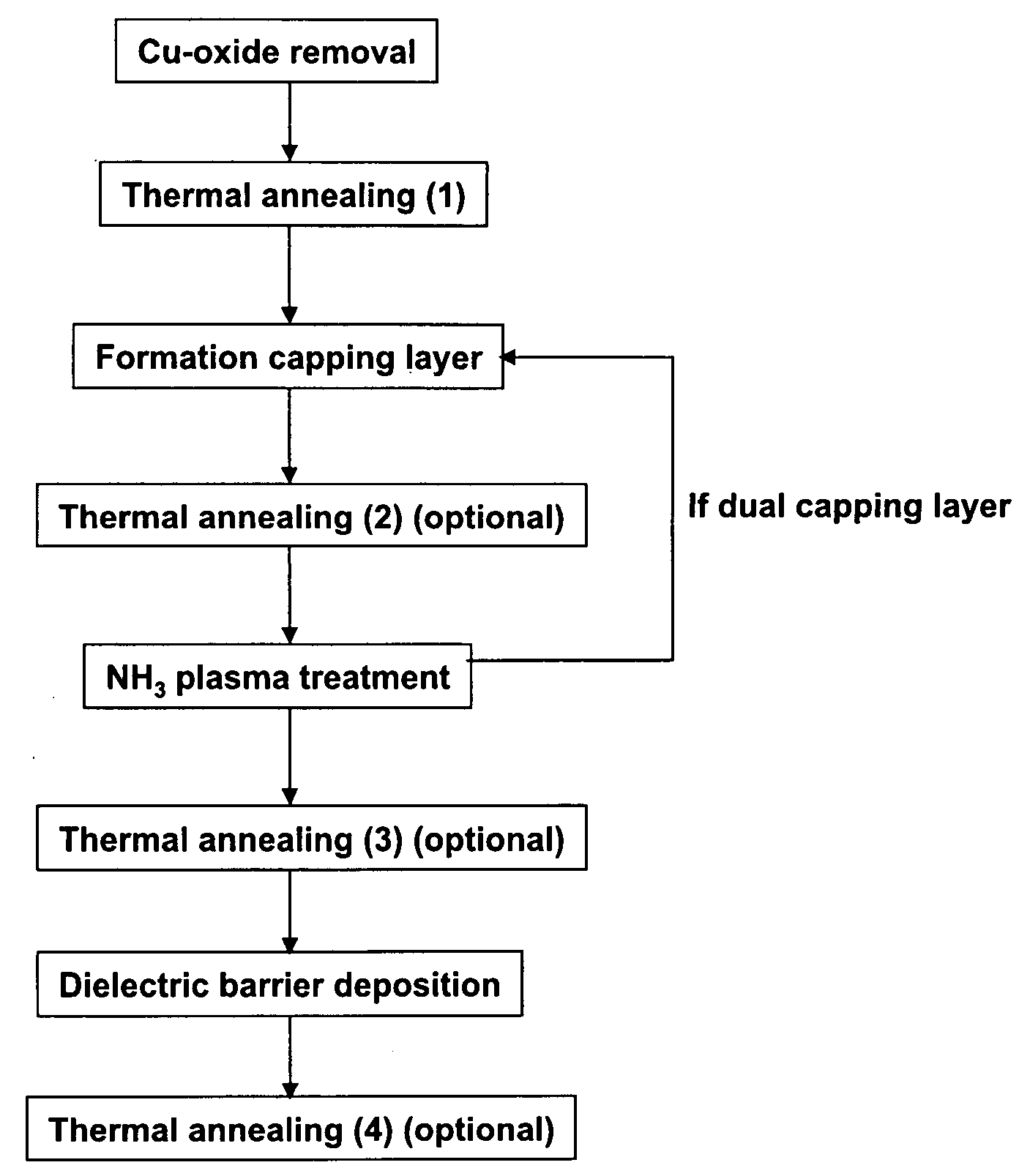

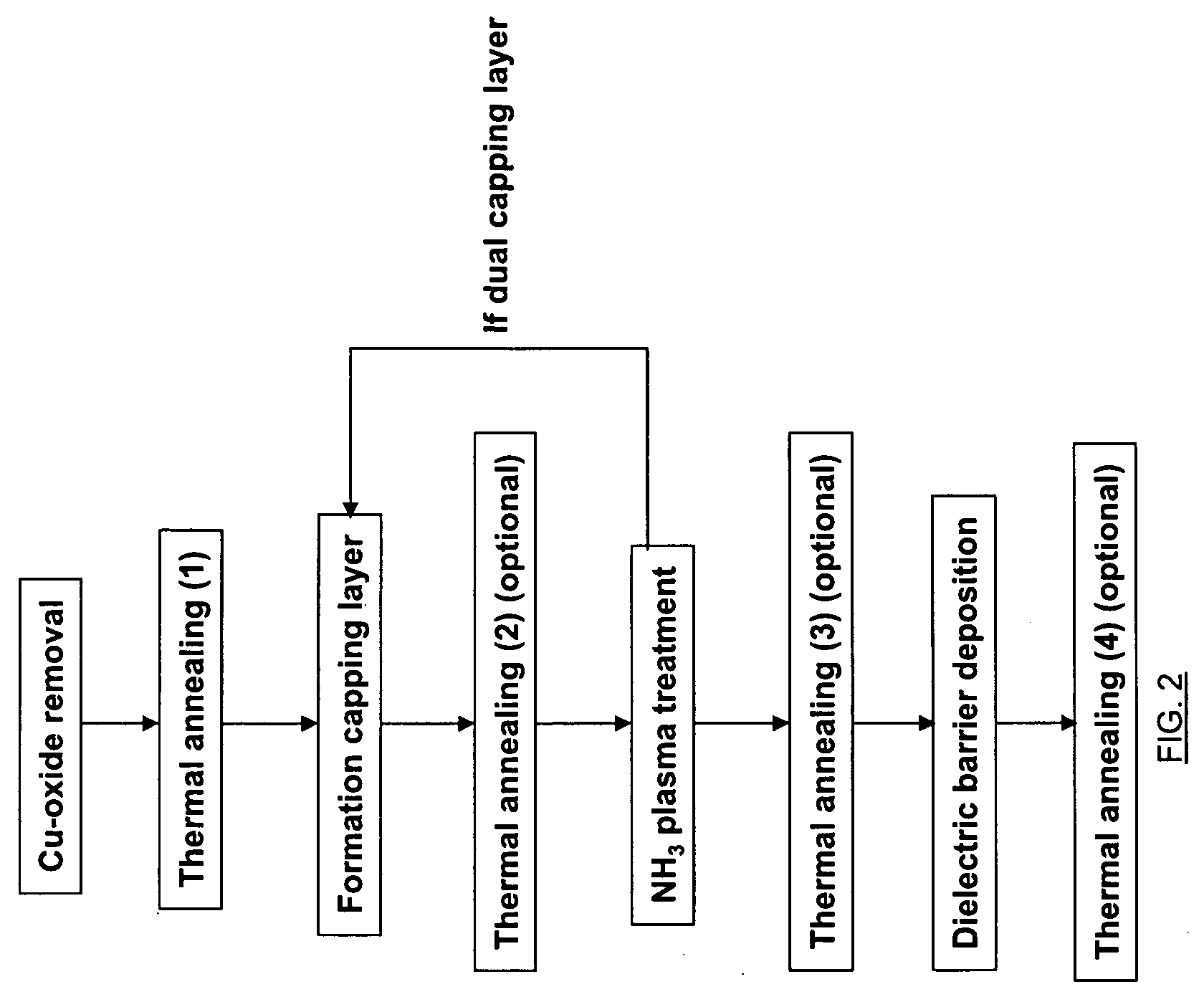

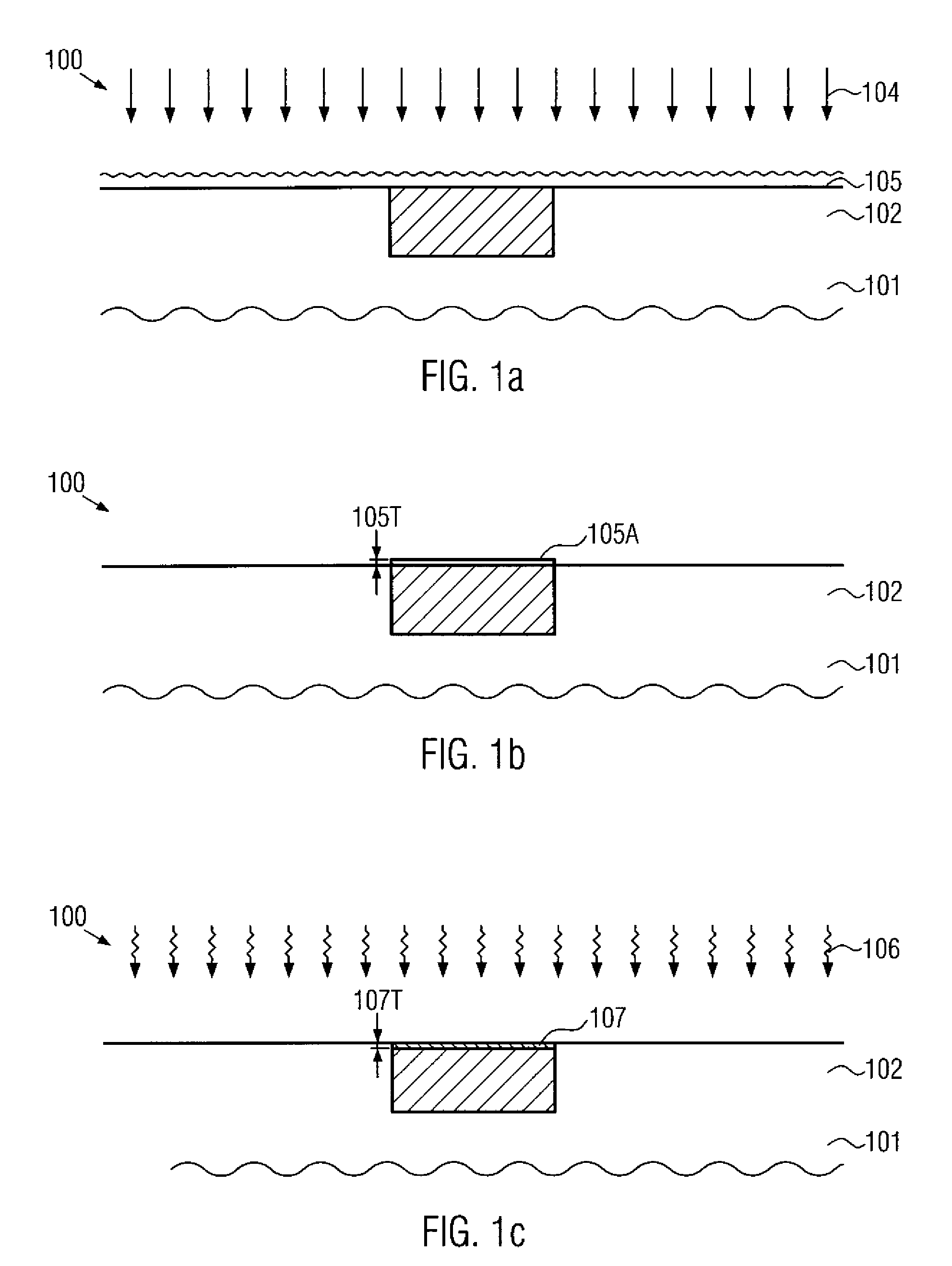

A method is provided for forming a capping layer comprising Cu, N, and also Si and / or Ge onto a copper conductive structure, said method comprising the sequential steps of: forming, at a temperature range between 200° C. up to 400° C., at least one capping layer onto said copper conductive structure by exposing said structure to a GeH4 and / or a SiH4 comprising ambient, performing a NH3 plasma treatment thereby forming an at least partly nitrided capping layer, forming a dielectric barrier layer onto said at least partly nitrided capping layer, wherein prior to said step of forming said at least one capping layer a pre-annealing step of said copper conductive structure is performed at a temperature range between 250° C. up to 450° C.

Owner:TAIWAN SEMICON MFG CO LTD +1

Method of forming reliable copper interconnects

InactiveUS6211084B1Semiconductor/solid-state device detailsSolid-state devicesCopper interconnectSilanes

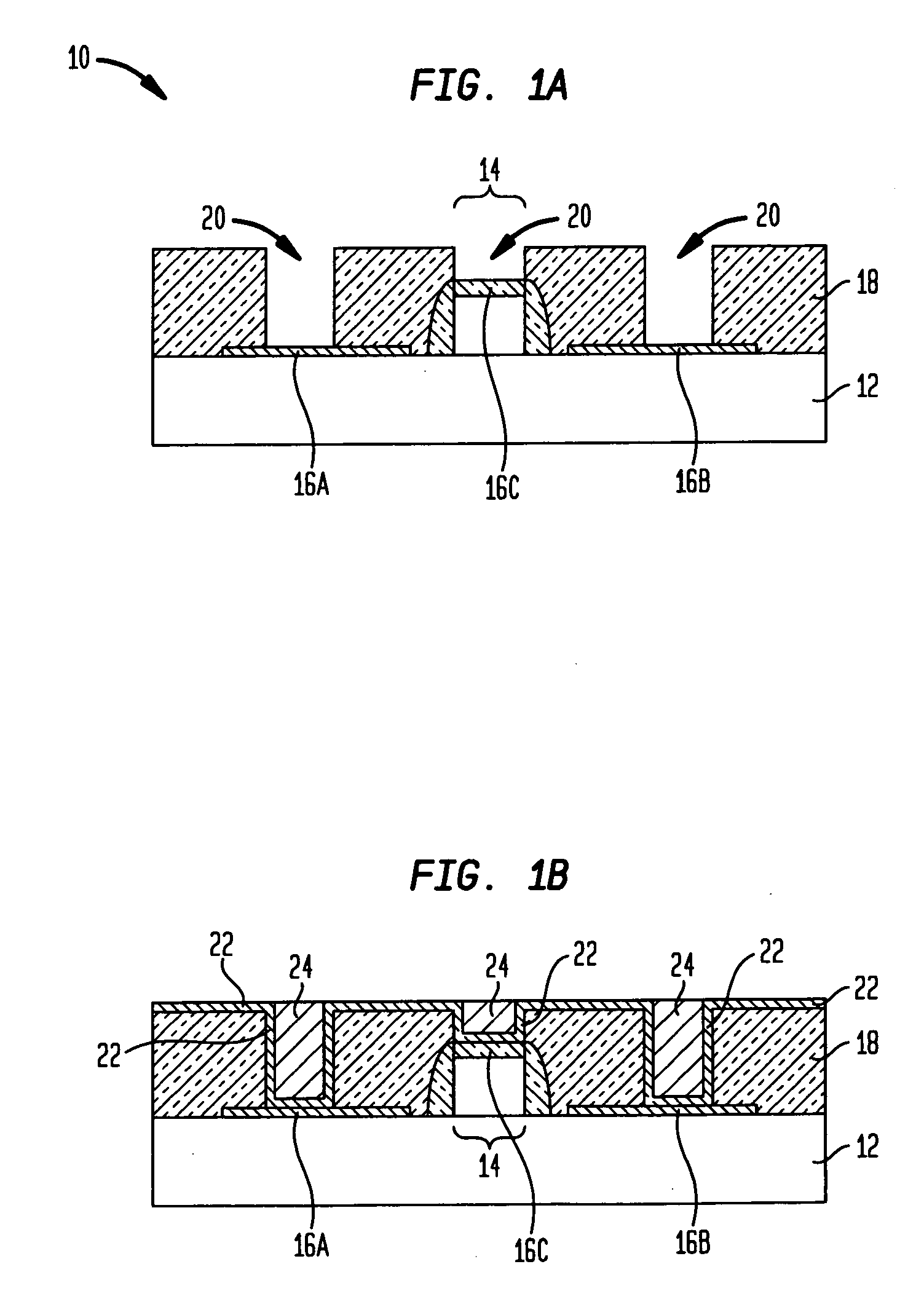

The adhesion of a diffusion barrier or capping layer to Cu and / or Cu alloy interconnect members is significantly enhanced by treating the exposed surface of the Cu and / or Cu alloy interconnect members with a silane or dichlorosilane plasma to form a layer of copper silicide thereon prior to depositing the capping layer. Embodiments include electroplating or electroless plating Cu or a Cu alloy to fill a damascene opening in a dielectric interlayer, chemical mechanical polishing, treating the exposed surface of the Cu or Cu alloy interconnect member in a silane or dichlorosilane plasma to form the copper silicide layer and depositing a capping layer of silicon nitride thereon.

Owner:GLOBALFOUNDRIES INC

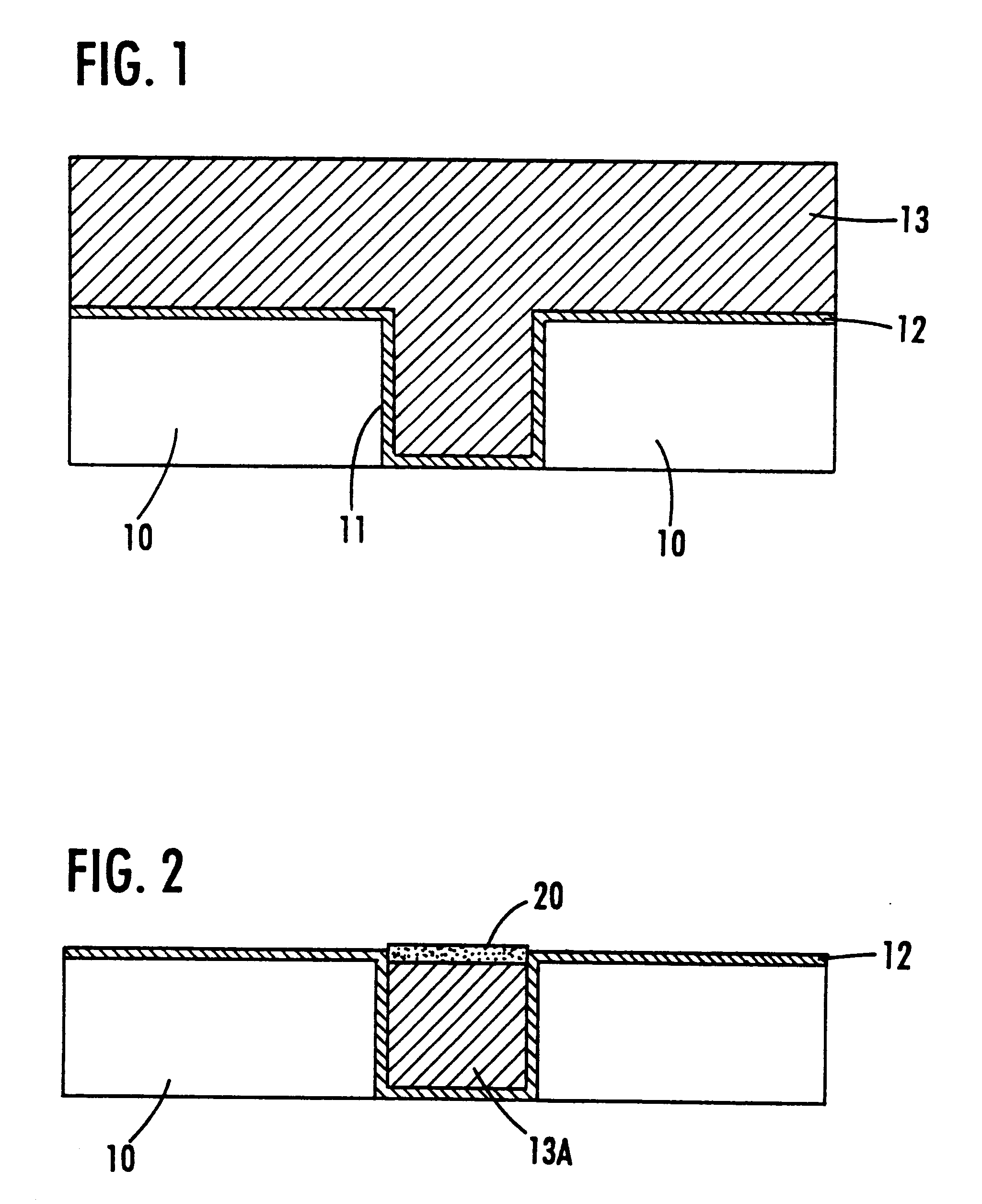

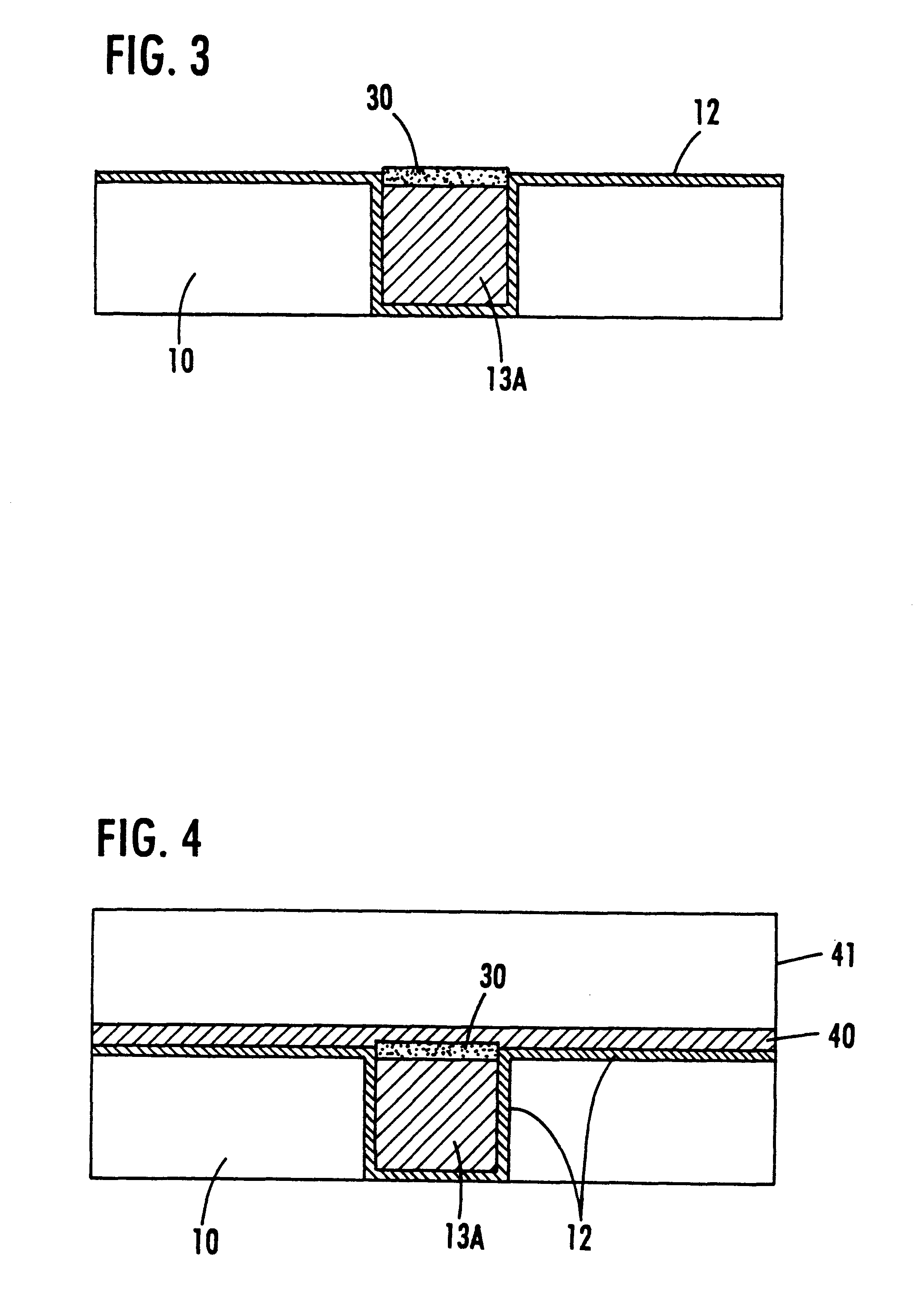

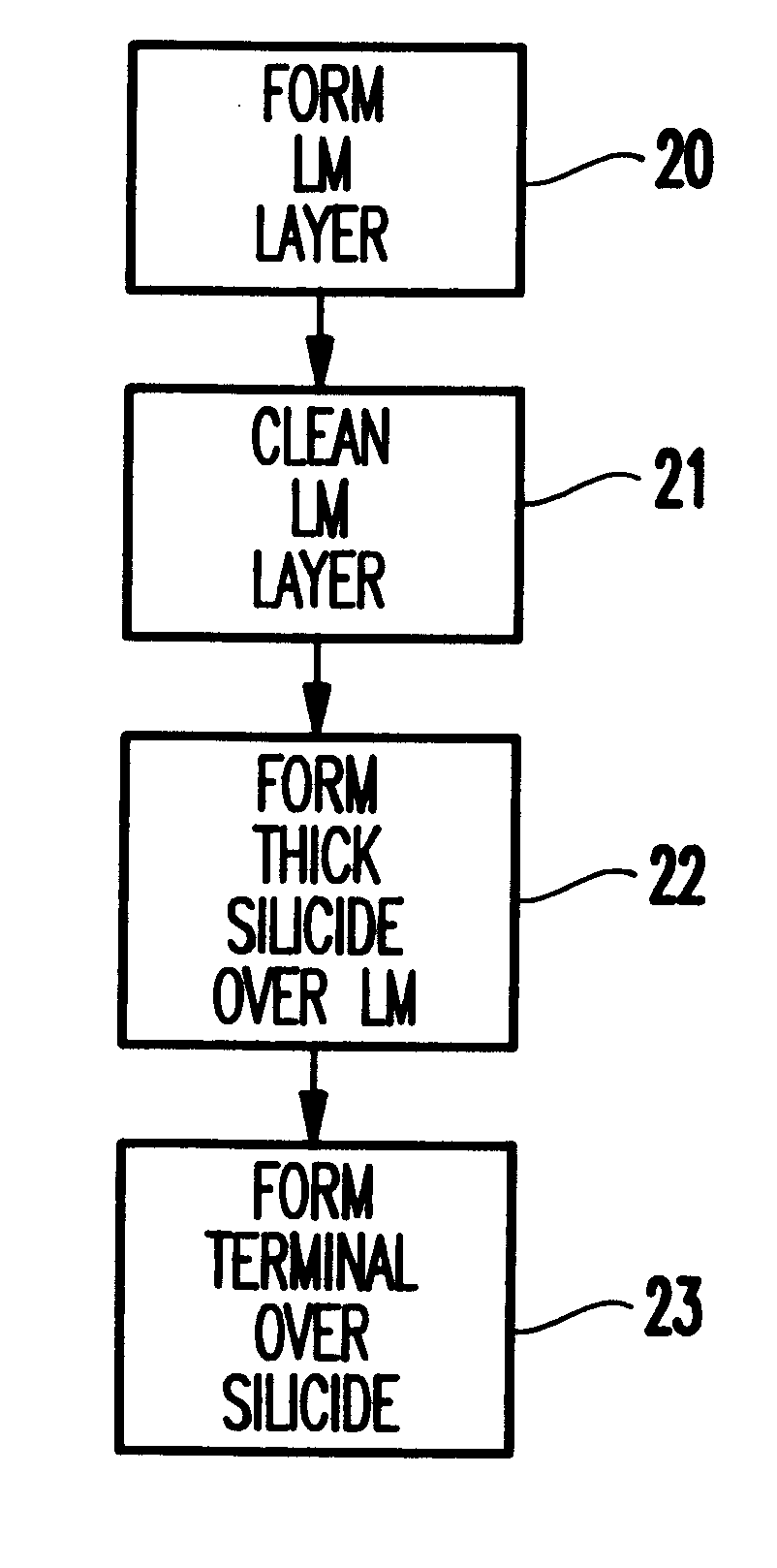

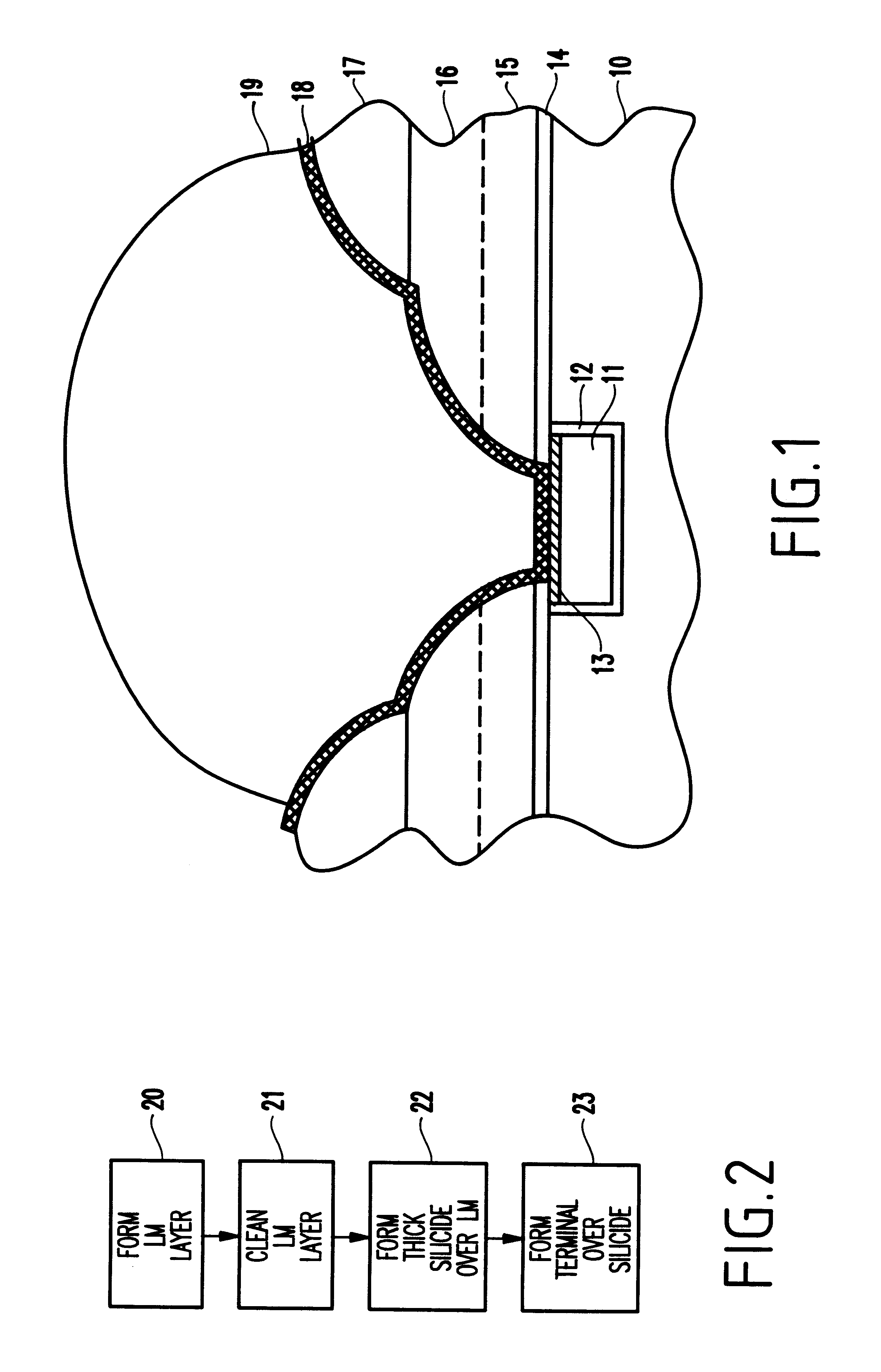

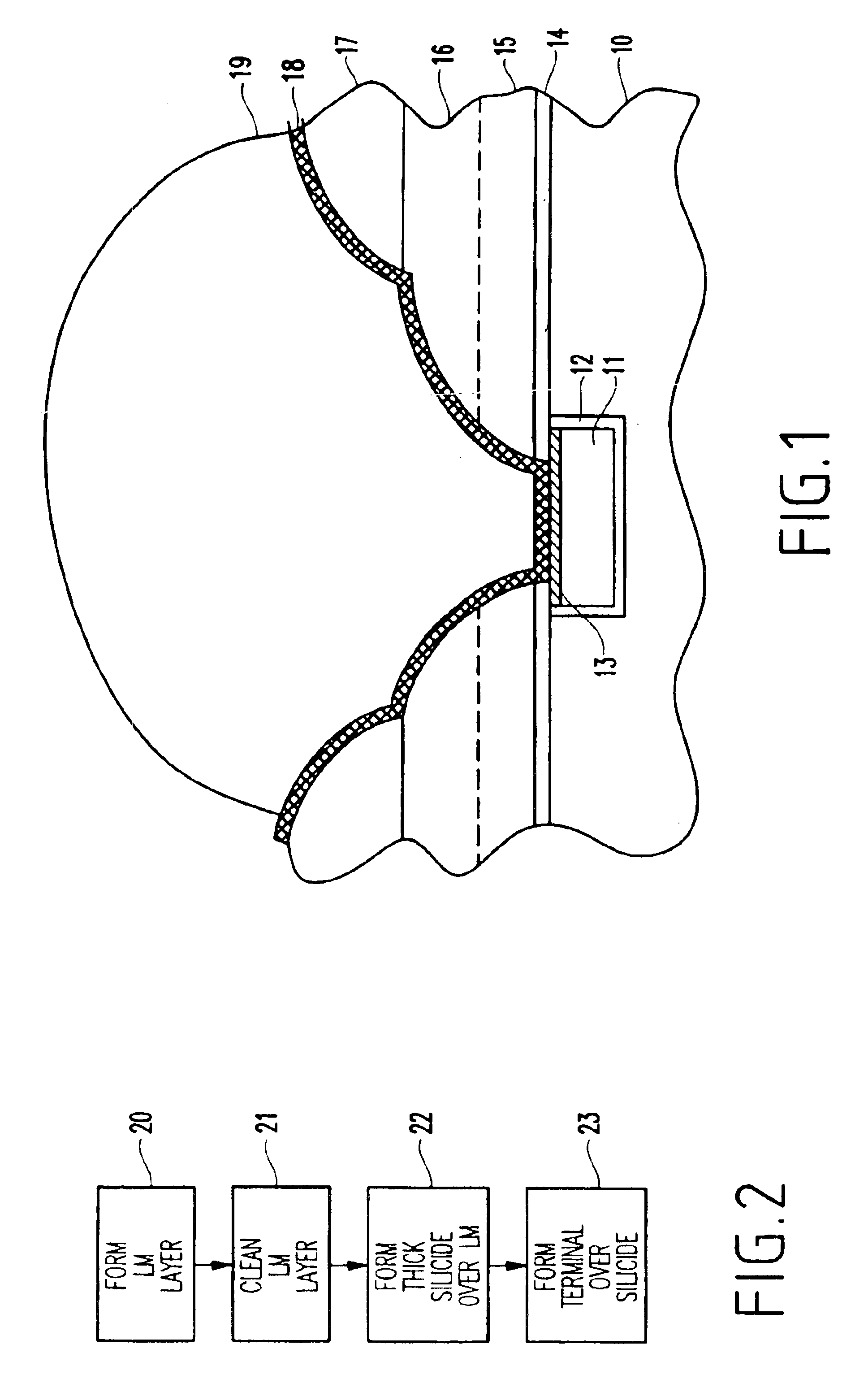

Self-aligned copper silicide formation for improved adhesion/electromigration

InactiveUS6251775B1Reduce layeringLess resistivitySemiconductor/solid-state device detailsSolid-state devicesSalicideSemiconductor structure

A method for forming a semiconductor structure includes supplying a structure having an exposed last metalization layer, cleaning the last metalization layer, forming a silicide in a top portion of the last metalization layer and forming a terminal over the silicide.

Owner:GLOBALFOUNDRIES INC

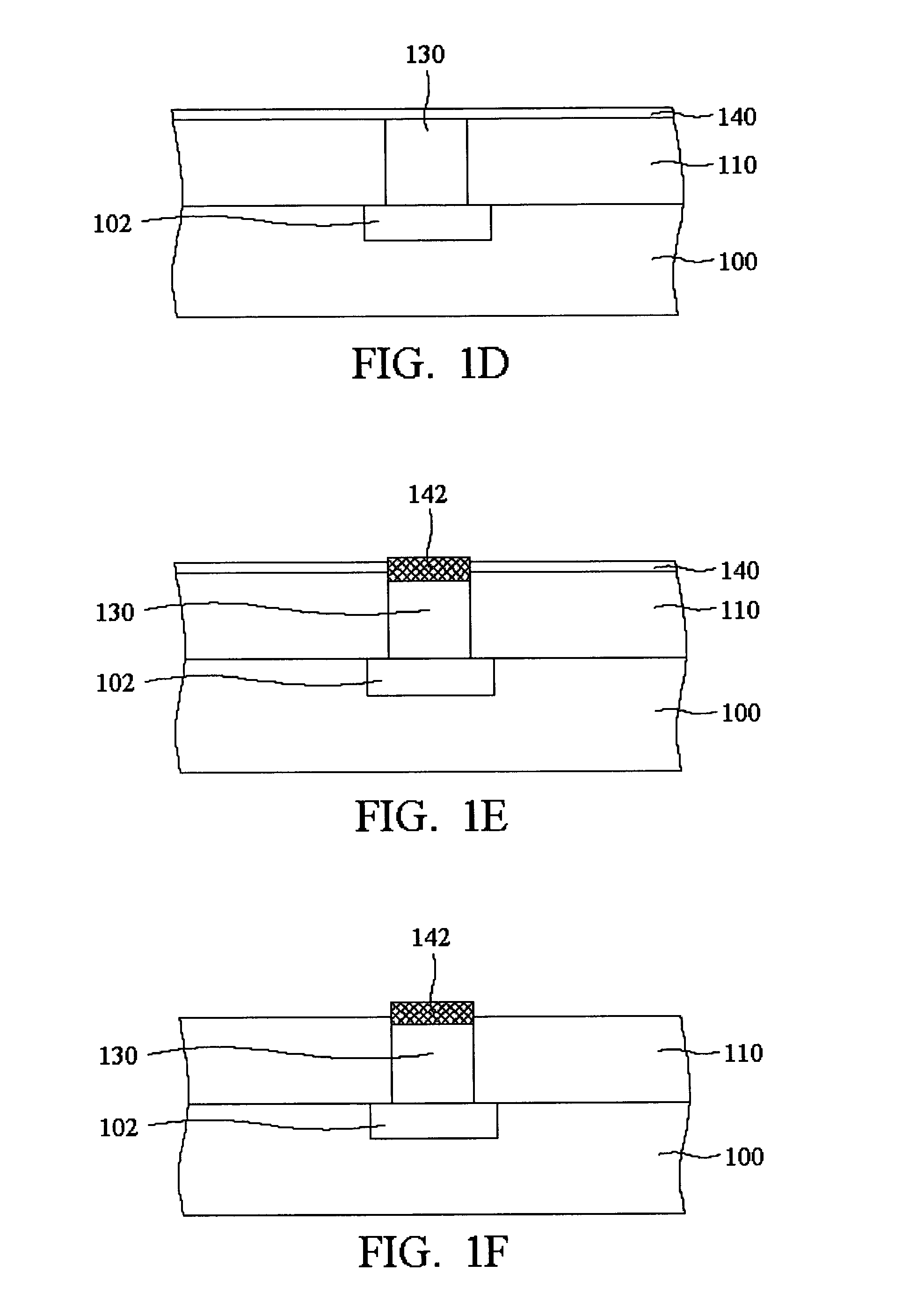

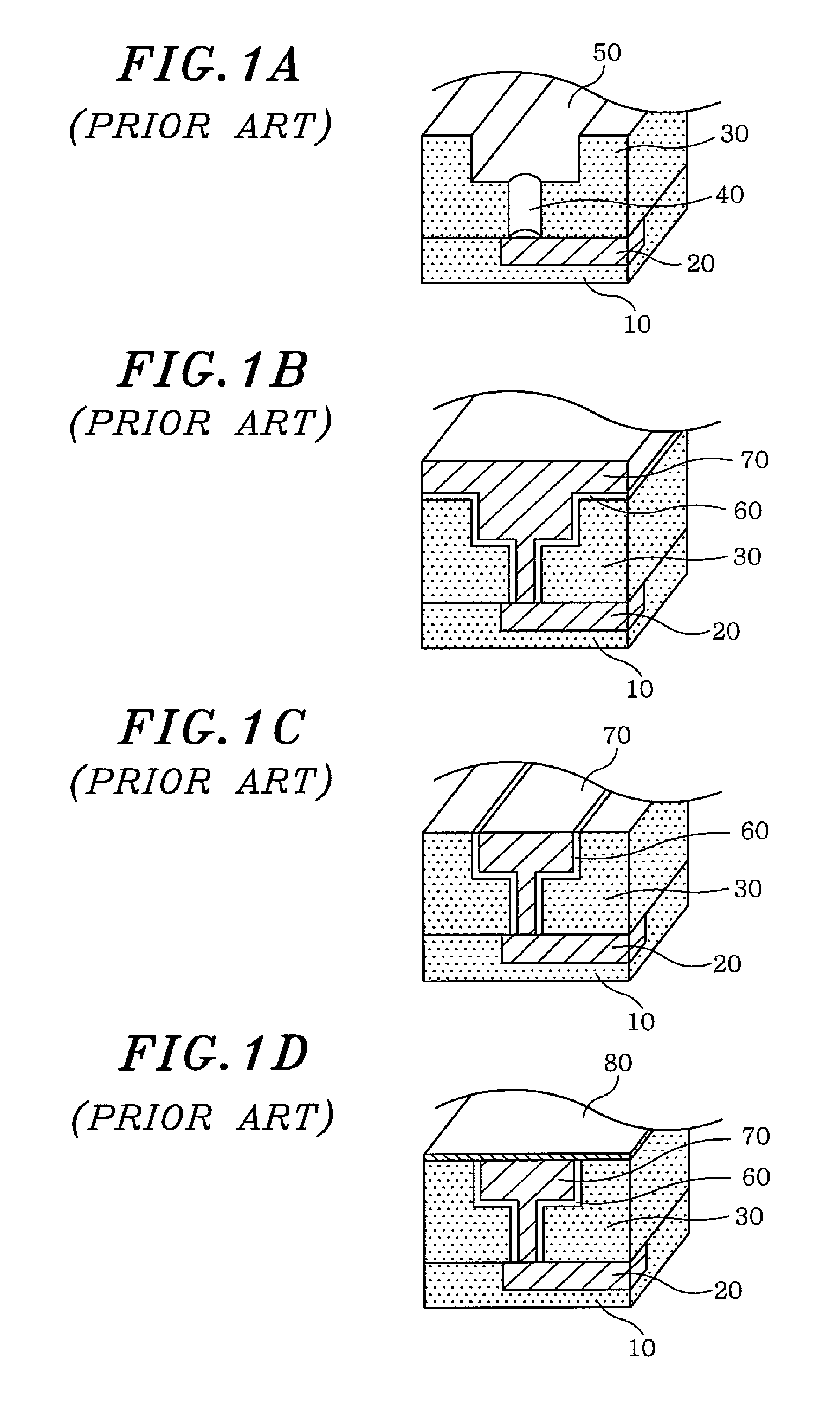

Method for fabricating copper interconnects

InactiveUS20050014360A1Semiconductor/solid-state device manufacturingCopper interconnectCopper silicide

A method for capping copper or copper alloy interconnects. A dielectric layer is formed overlaying a semiconductor substrate. An opening is formed in the dielectric layer and subsequently embedded copper or copper alloy form an interconnect structure. A silicon layer is formed on the copper or copper alloy by sputtering or chemical vapor deposition. A copper silicide layer is formed by reacting the silicon layer with the underlying copper or copper alloy as a capping layer.

Owner:TAIWAN SEMICON MFG CO LTD

Method and structure for reducing contact resistance between silicide contact and overlying metallization

InactiveUS20070275548A1Lower resistance contactReduce contact resistanceSemiconductor/solid-state device detailsSolid-state devicesSemiconductor structureMetal silicide

A semiconductor structure in which the contact resistance in the contact opening is reduced as well as a method of forming the same are provided. This is achieved in the present invention by replacing conventional contact metallurgy, such as tungsten, or a metal silicide, such as Ni silicide or Cu silicide, with a metal germanide-containing contact material. The term “metal germanide-containing” is used in the present application to denote a pure metal germanide (i.e., MGe alloy) or a metal germanide that includes Si (i.e., MSiGe alloy).

Owner:GLOBALFOUNDRIES INC

Method for fabricating copper interconnects

A method for capping copper or copper alloy interconnects. A dielectric layer is formed overlaying a semiconductor substrate. An opening is formed in the dielectric layer and subsequently embedded copper or copper alloy form an interconnect structure. A silicon layer is formed on the copper or copper alloy by sputtering or chemical vapor deposition. A copper silicide layer is formed by reacting the silicon layer with the underlying copper or copper alloy as a capping layer.

Owner:TAIWAN SEMICON MFG CO LTD

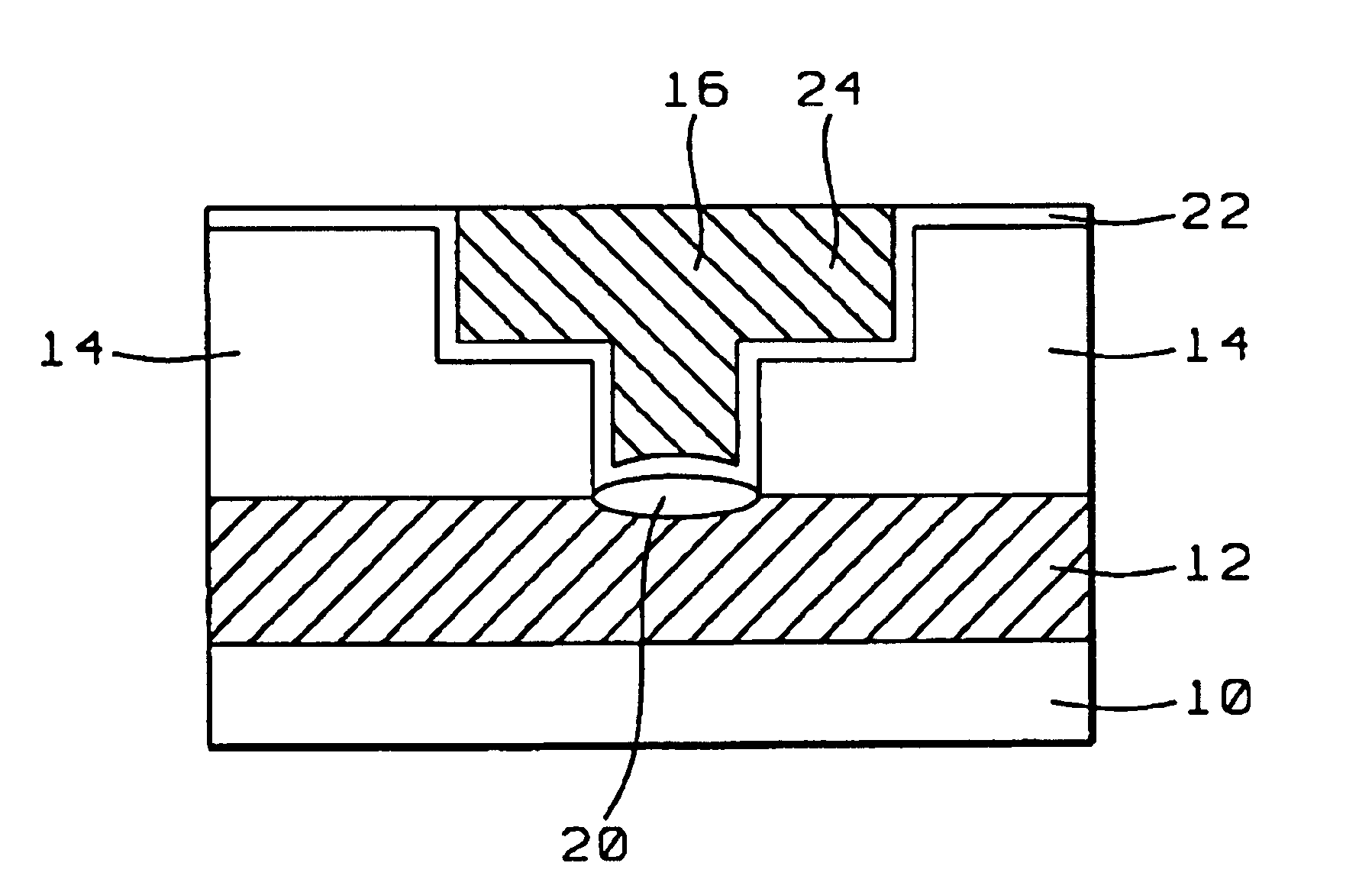

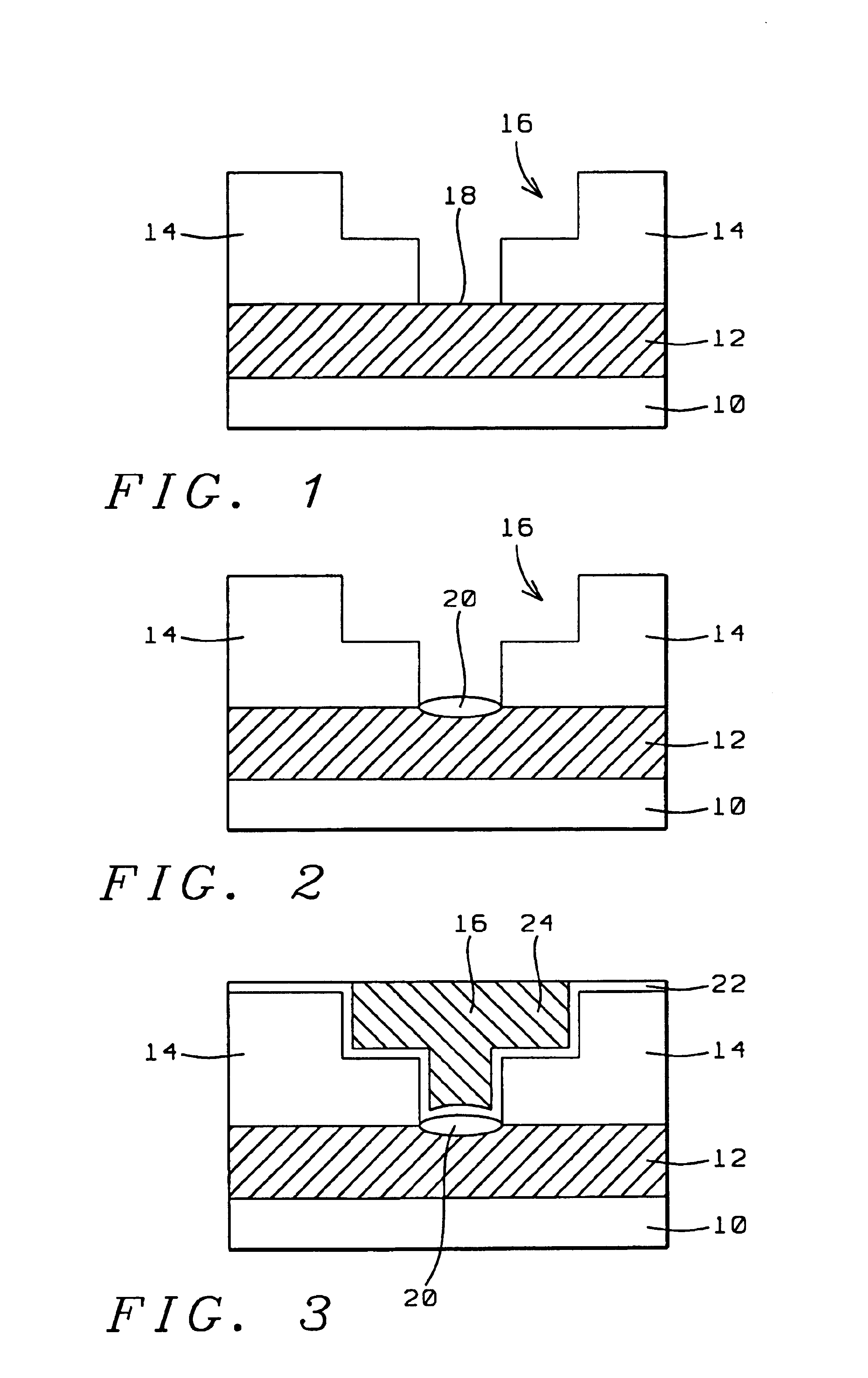

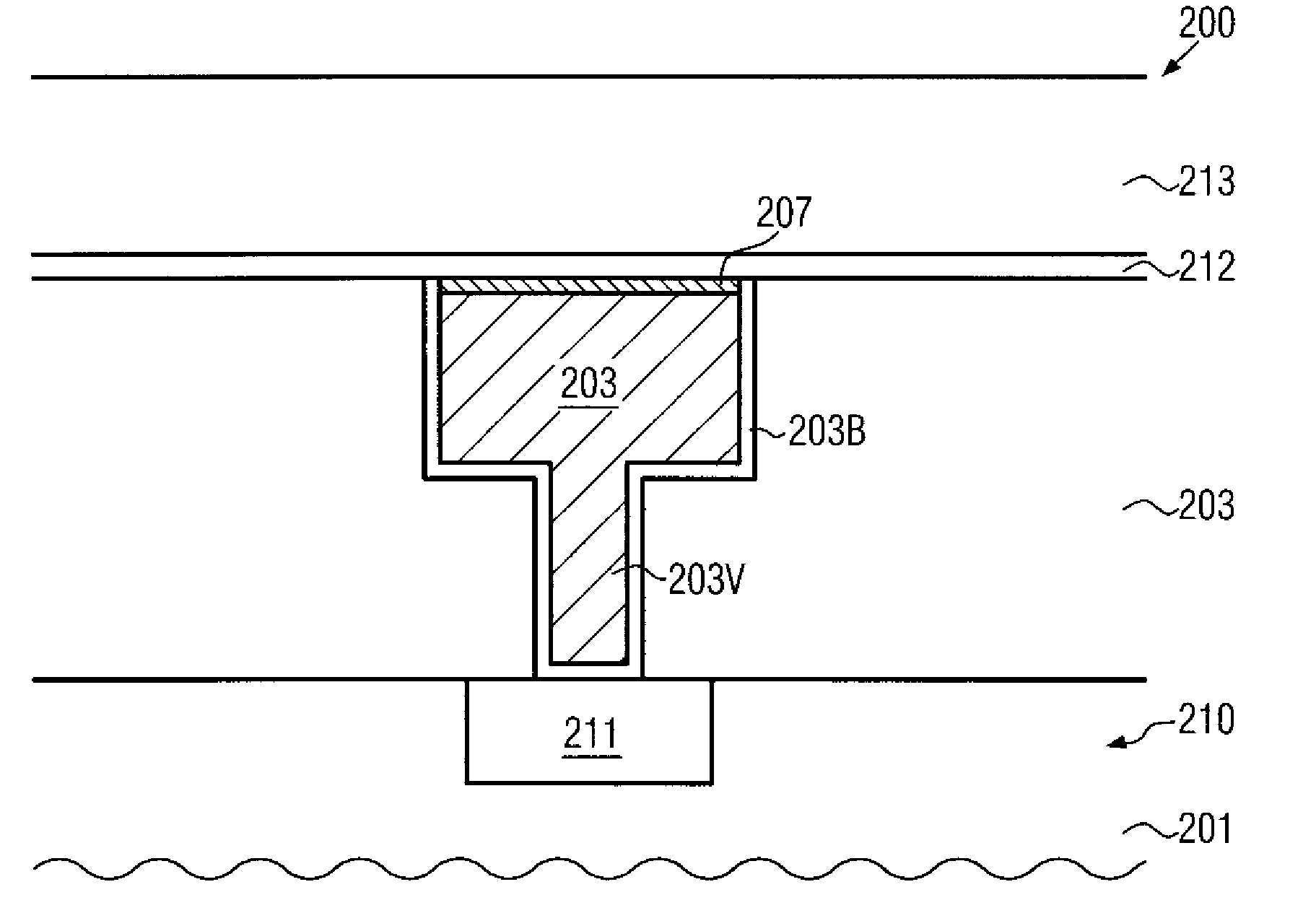

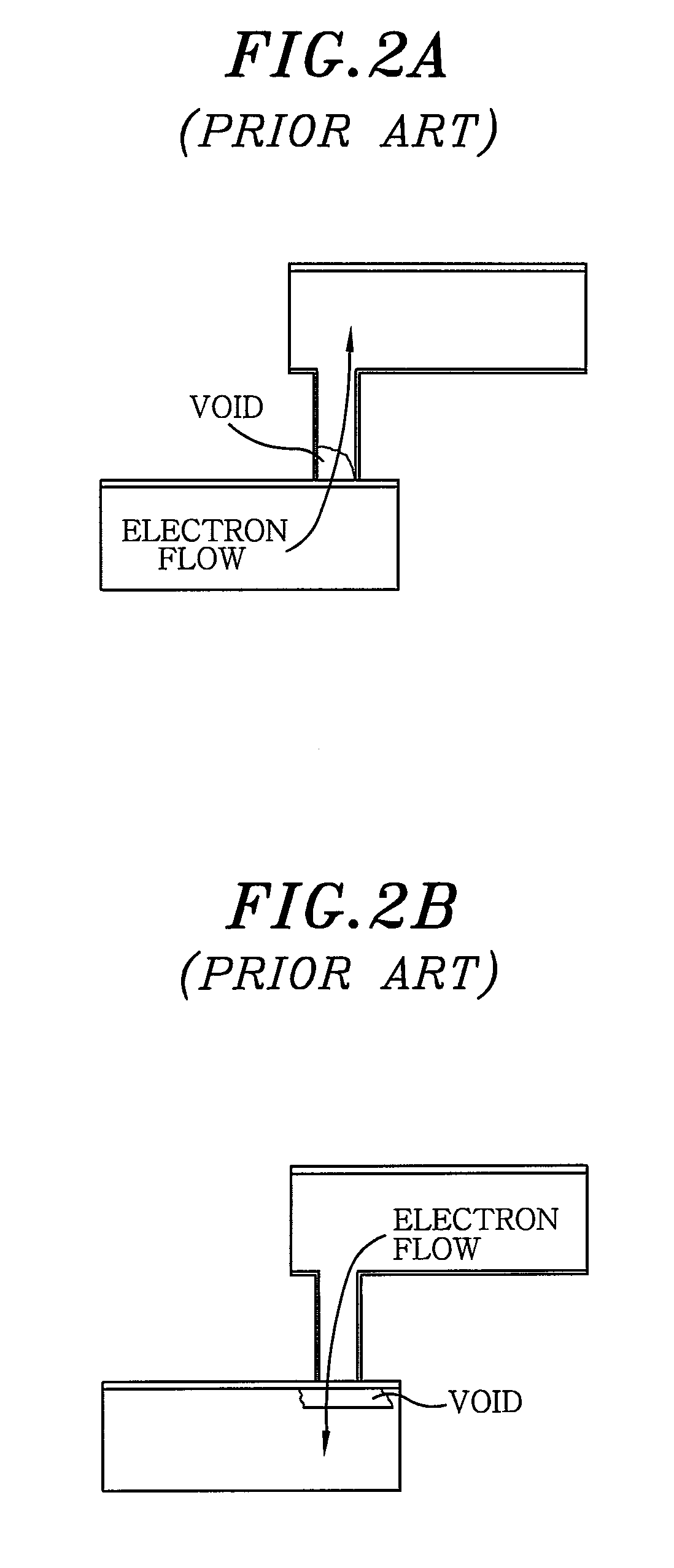

Via bottom copper/barrier interface improvement to resolve via electromigration and stress migration

A method of forming a copper / barrier layer interface comprising the following sequential steps. A structure having a lower copper layer formed thereover is provide. A patterned dielectric layer is formed over the lower copper layer. The patterned dielectric layer having an opening exposing a portion of the lower copper layer. The exposed portion of the lower copper layer is converted to a copper silicide portion. A barrier layer is formed upon the patterned dielectric layer and the copper silicide portion, lining the opening, whereby the lower copper layer / barrier layer interface is formed such that the barrier layer contacts the copper silicide portion to form an interface.

Owner:TAIWAN SEMICON MFG CO LTD

Copper silicide passivation for improved reliability

InactiveUS6869873B2Preventing diffusion of copperInhibited DiffusionSemiconductor/solid-state device detailsSolid-state devicesCopper interconnectSilanes

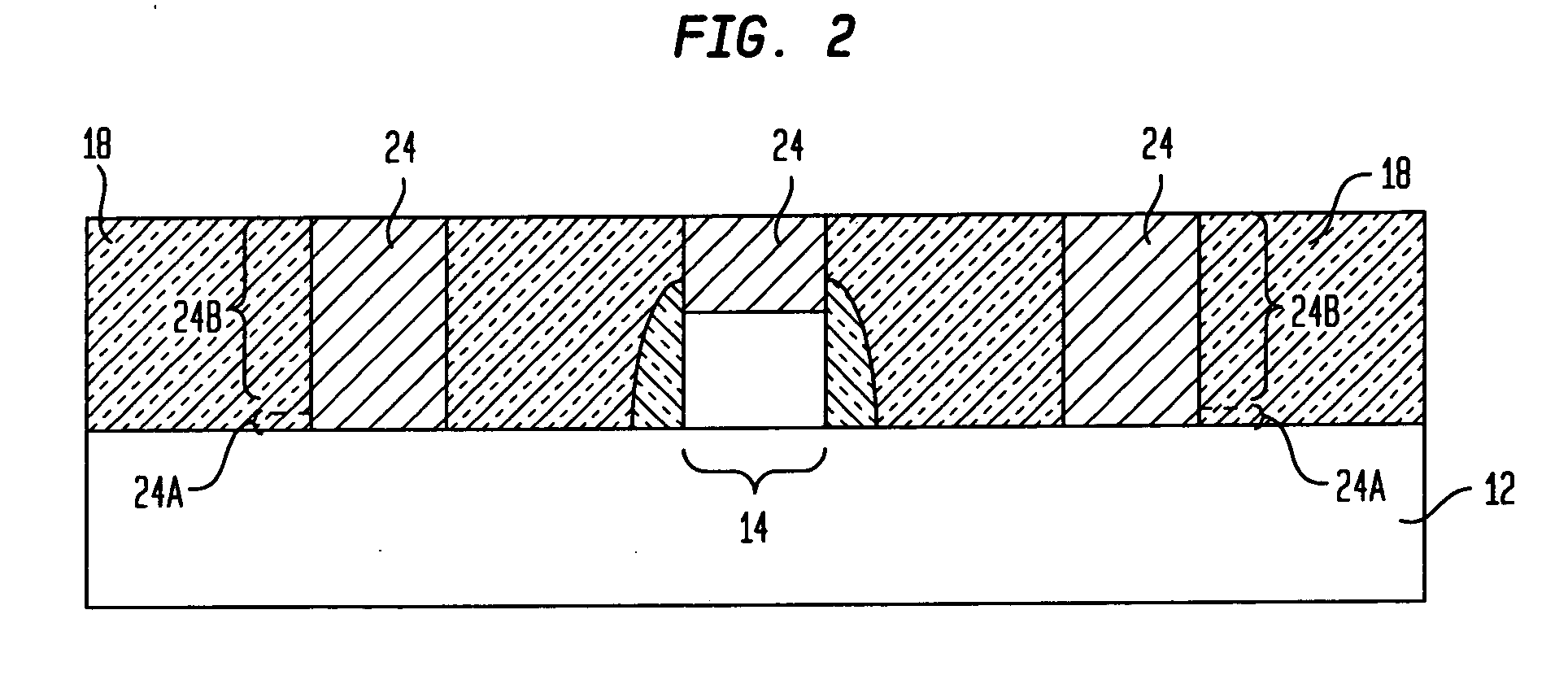

A silane passivation process, carried out in-situ together with the formation of a subsequent dielectric film, converts the exposed Cu surfaces of a Cu interconnect structure, to copper silicide. The copper silicide suppresses Cu diffusion and electromigration and serves as a barrier material in regions where contact to further conductive material is made. An entire copper surface of a copper interconnect structure may be silicided or a local portion of the surface silicided after an opening is formed in an overlying dielectric to expose a portion of the copper surface.

Owner:BELL SEMICON LLC

Integrated circuit and manufacturing method of copper germanide and copper silicide as copper capping layer

ActiveUS20090134521A1Avoid damageImprove barrier propertiesSemiconductor/solid-state device detailsSolid-state devicesGermanideCopper silicide

A method is provided for forming a capping layer comprising Cu, N, and also Si and / or Ge onto a copper conductive structure, said method comprising the sequential steps of: forming, at a temperature range between 200° C. up to 400° C., at least one capping layer onto said copper conductive structure by exposing said structure to a GeH4 and / or a SiH4 comprising ambient, performing a NH3 plasma treatment thereby forming an at least partly nitrided capping layer, forming a dielectric barrier layer onto said at least partly nitrided capping layer, wherein prior to said step of forming said at least one capping layer a pre-annealing step of said copper conductive structure is performed at a temperature range between 250° C. up to 450° C.

Owner:TAIWAN SEMICON MFG CO LTD +1

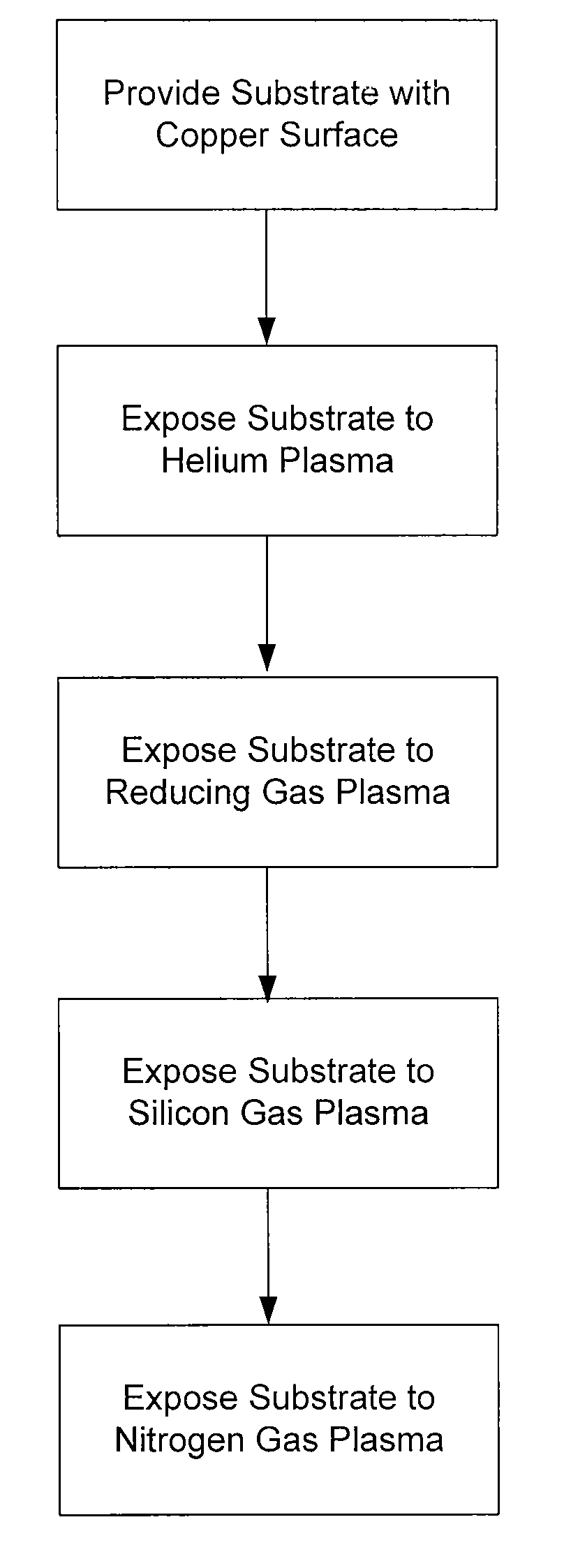

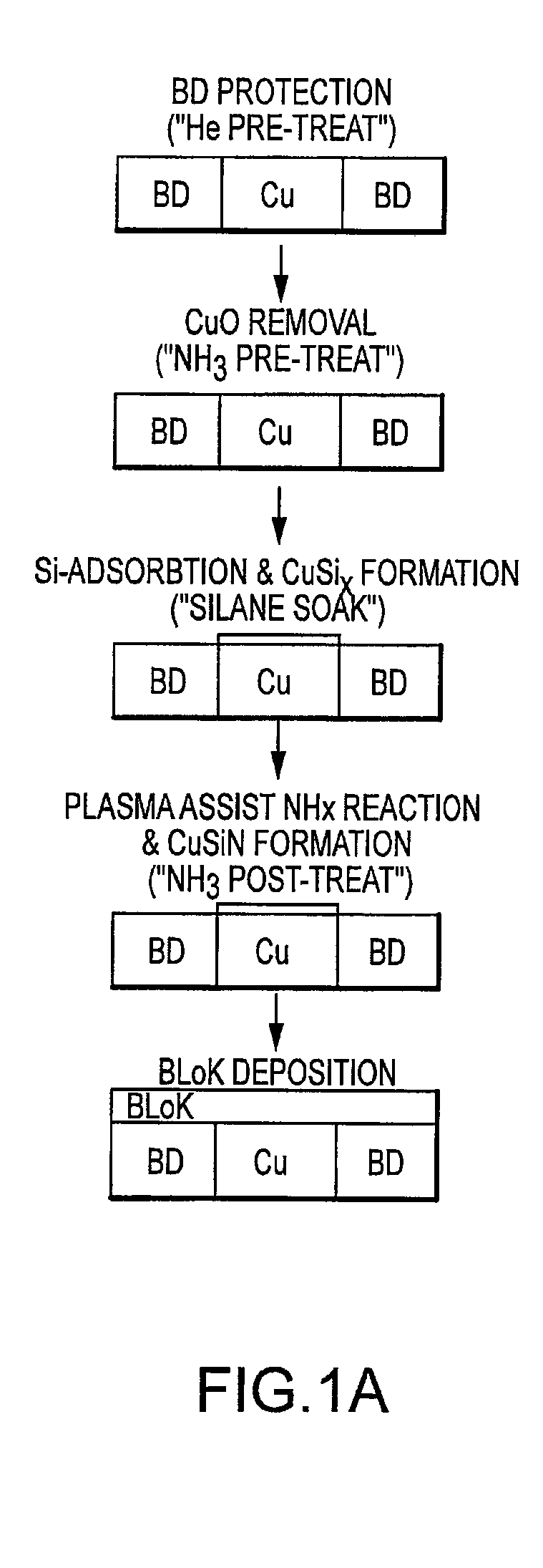

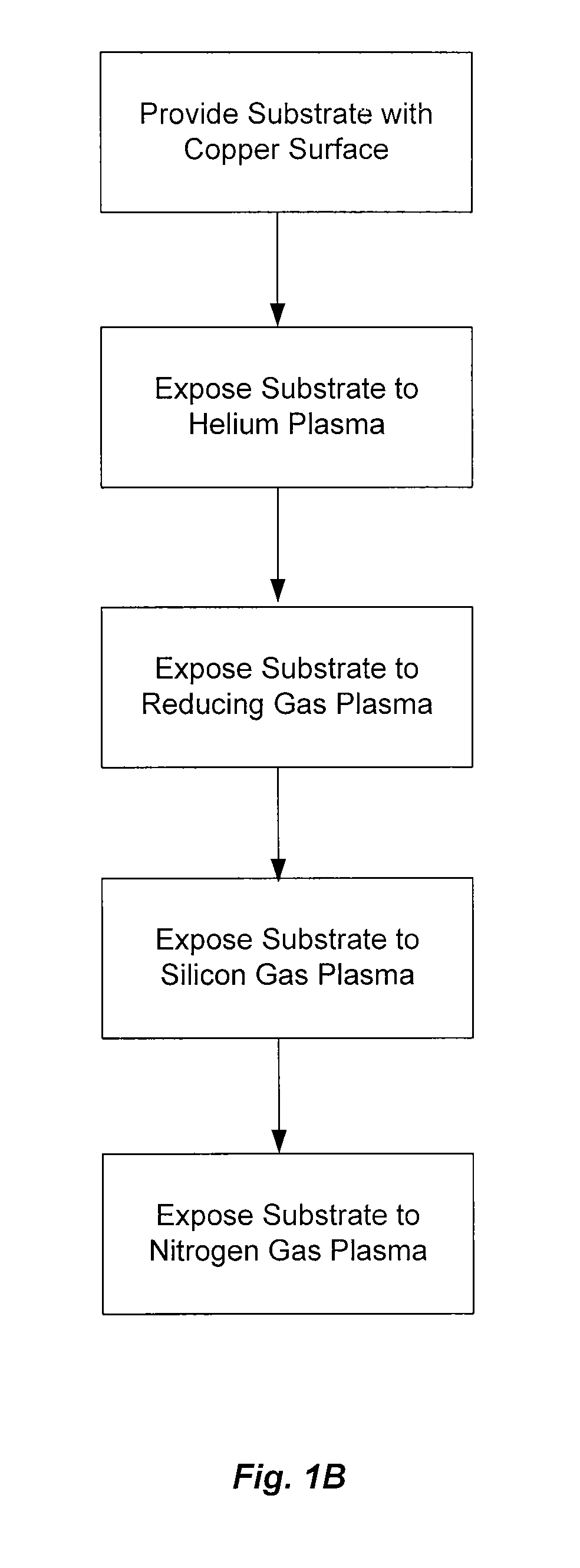

Selective copper-silicon-nitride layer formation for an improved dielectric film/copper line interface

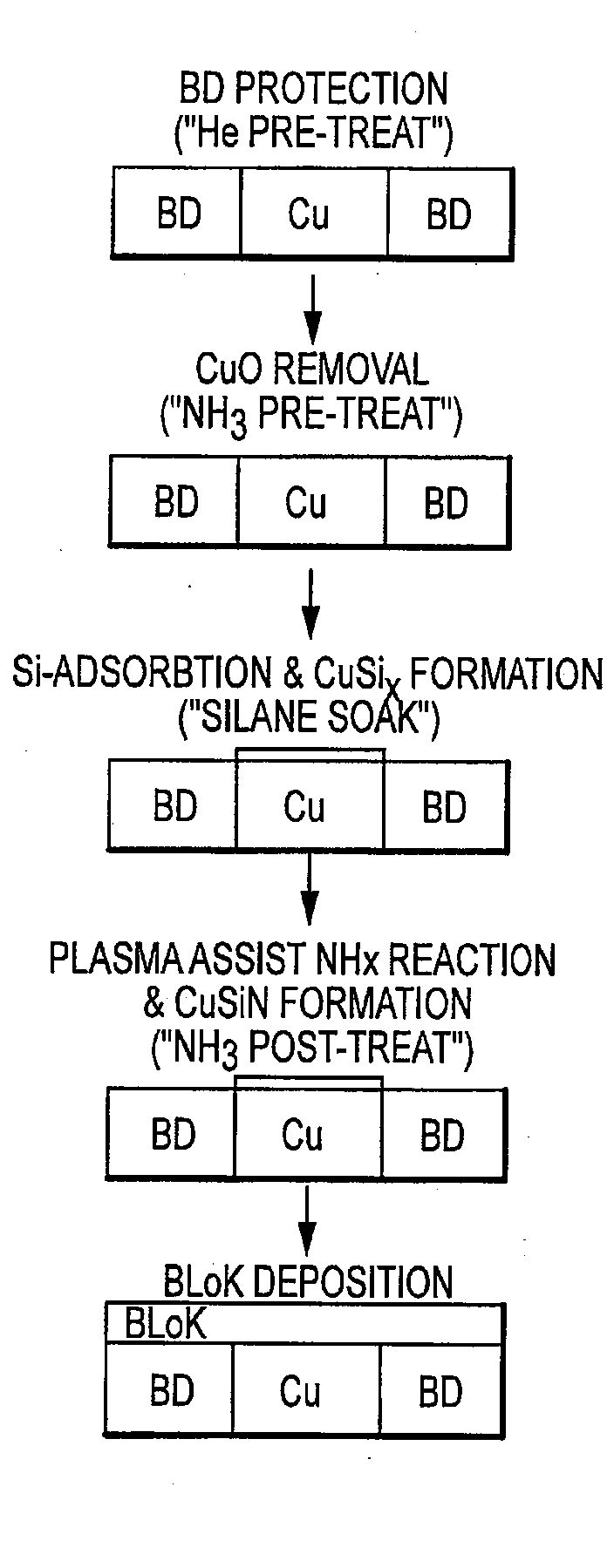

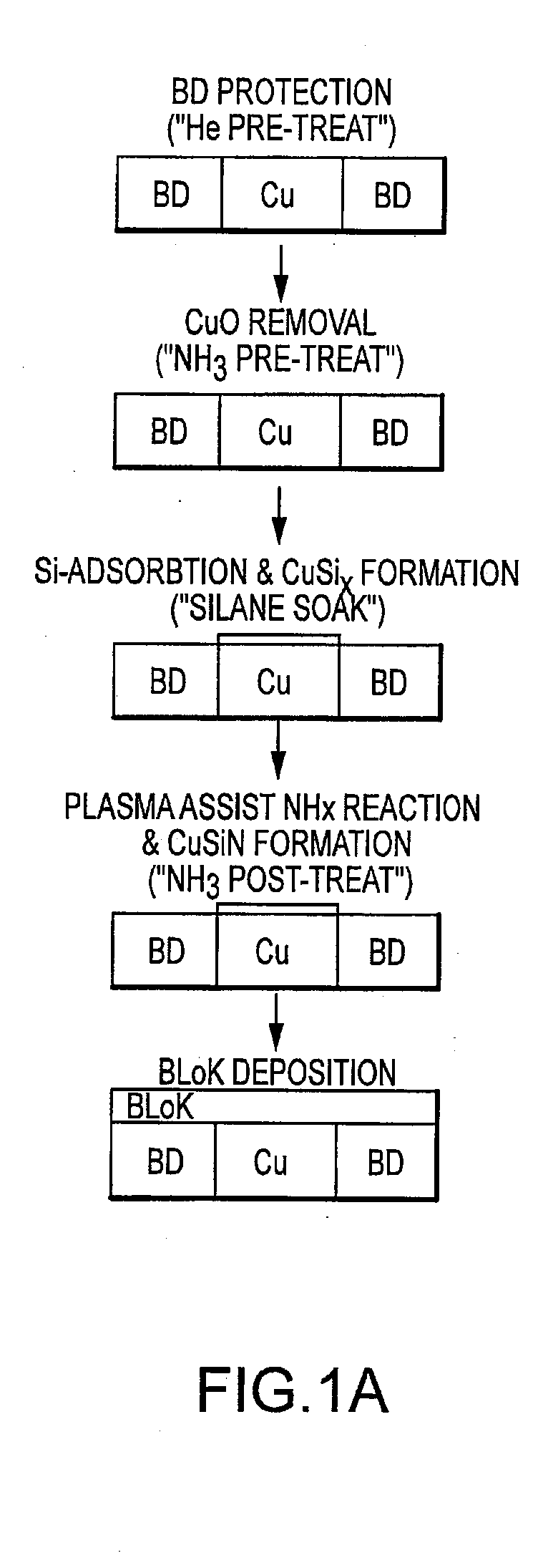

InactiveUS20080213997A1Improve adhesionLow dielectric constantPretreated surfacesSemiconductor/solid-state device manufacturingSilanesCopper oxide

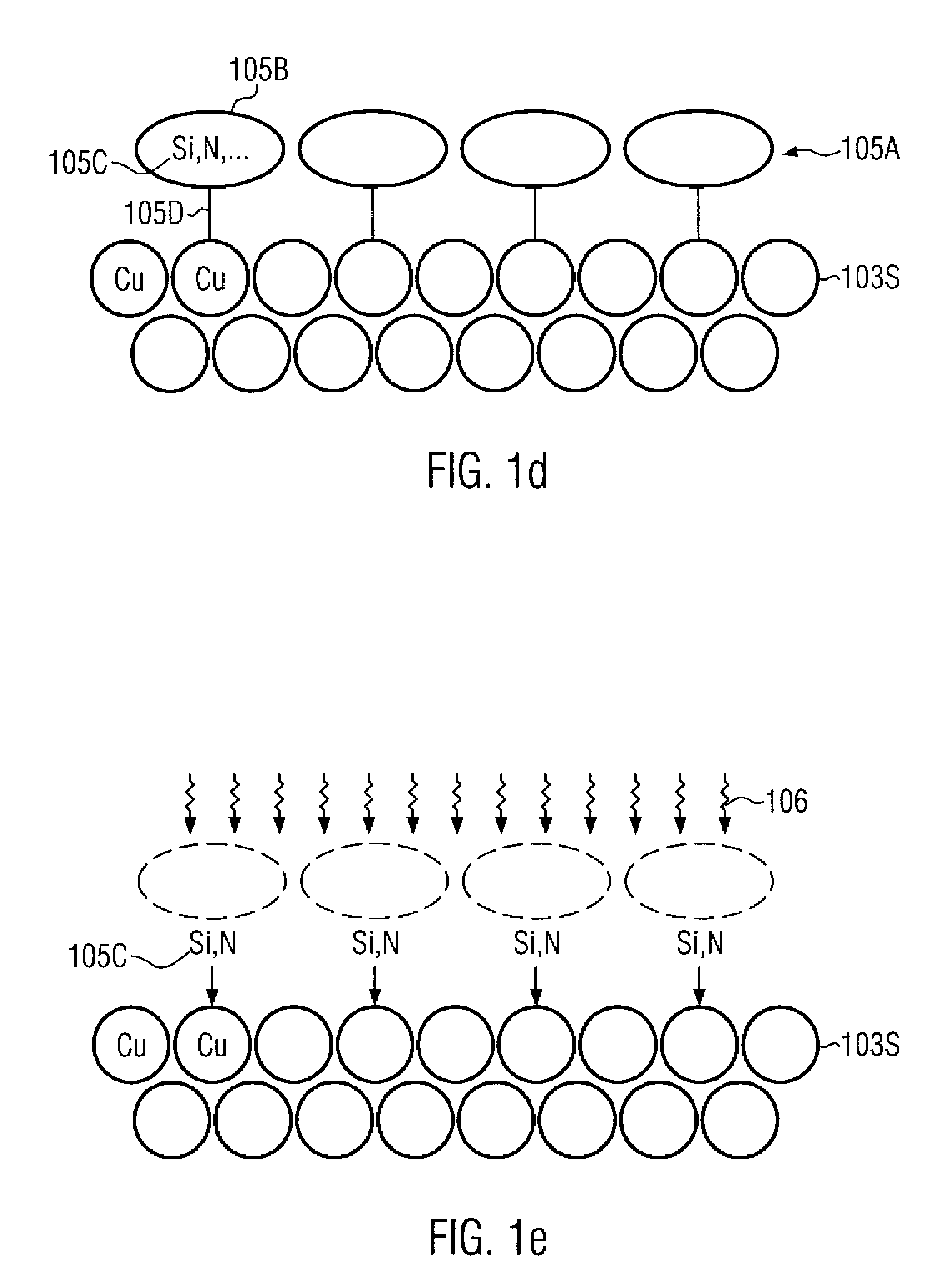

A process to form a copper-silicon-nitride layer on a copper surface on a semiconductor wafer is described. The process may include the step of exposing the wafer to a first plasma made from helium. The process may also include exposing the wafer to a second plasma made from a reducing gas, where the second plasma removes copper oxide from the copper surface, and exposing the wafer to silane, where the silane reacts with the copper surface to selectively form copper silicide. The process may further include exposing the wafer to a third plasma made from ammonia and molecular nitrogen to form the copper silicon nitride layer.

Owner:APPLIED MATERIALS INC

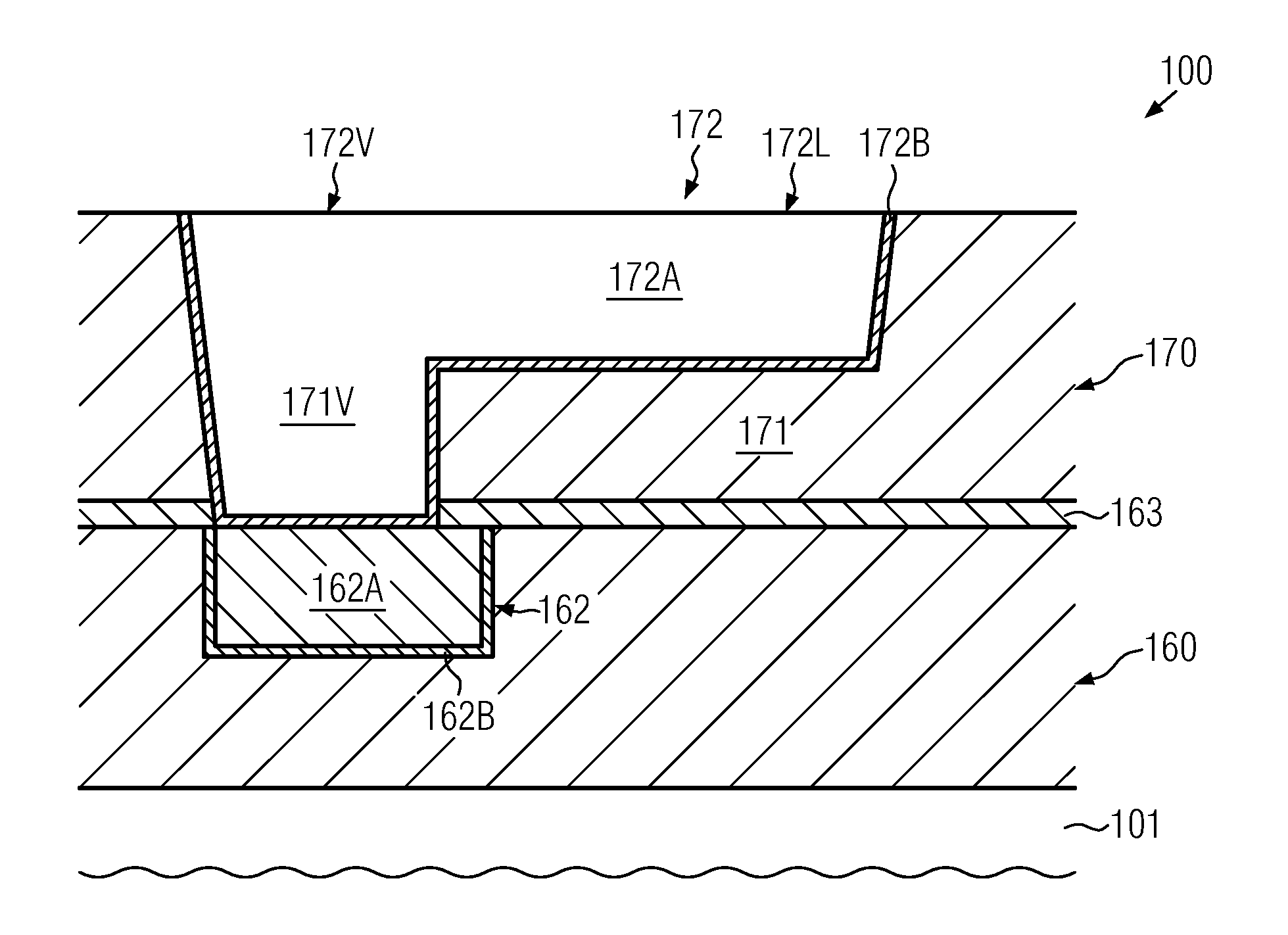

Metallization Systems of Semiconductor Devices Comprising a Copper/Silicon Compound as a Barrier Material

ActiveUS20120153480A1Superior electromigration behaviorLower electrical resistivitySemiconductor/solid-state device detailsSolid-state devicesTantalum nitrideCopper silicide

In sophisticated metallization systems of semiconductor devices, a sensitive core metal, such as copper, may be efficiently confined by a conductive barrier material comprising a copper / silicon compound, such as a copper silicide, which may provide superior electromigration behavior and higher electrical conductivity compared to conventionally used tantalum / tantalum nitride barrier systems.

Owner:GLOBALFOUNDRIES US INC

Selective copper-silicon-nitride layer formation for an improved dielectric film/copper line interface

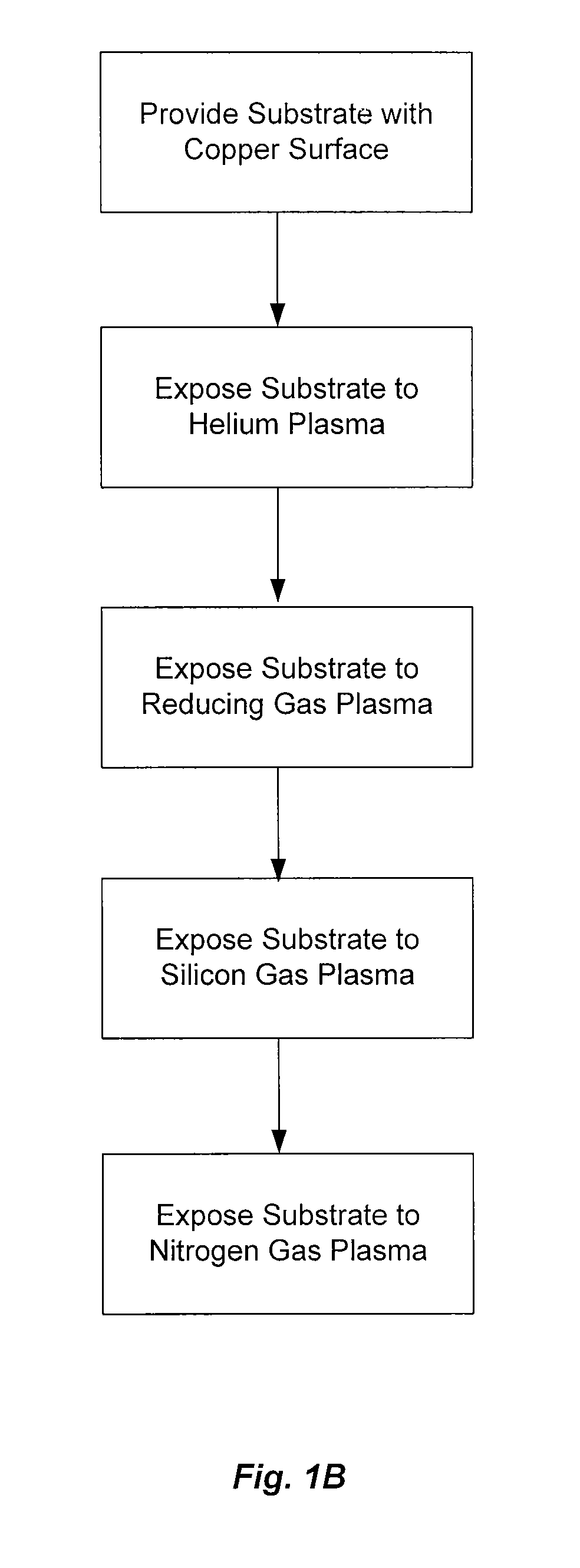

InactiveUS7718548B2Improve adhesionLow dielectric constantPretreated surfacesSemiconductor/solid-state device manufacturingSilanesCopper oxide

A process to form a copper-silicon-nitride layer on a copper surface on a semiconductor wafer is described. The process may include the step of exposing the wafer to a first plasma made from helium. The process may also include exposing the wafer to a second plasma made from a reducing gas, where the second plasma removes copper oxide from the copper surface, and exposing the wafer to silane, where the silane reacts with the copper surface to selectively form copper silicide. The process may further include exposing the wafer to a third plasma made from ammonia and molecular nitrogen to form the copper silicon nitride layer.

Owner:APPLIED MATERIALS INC

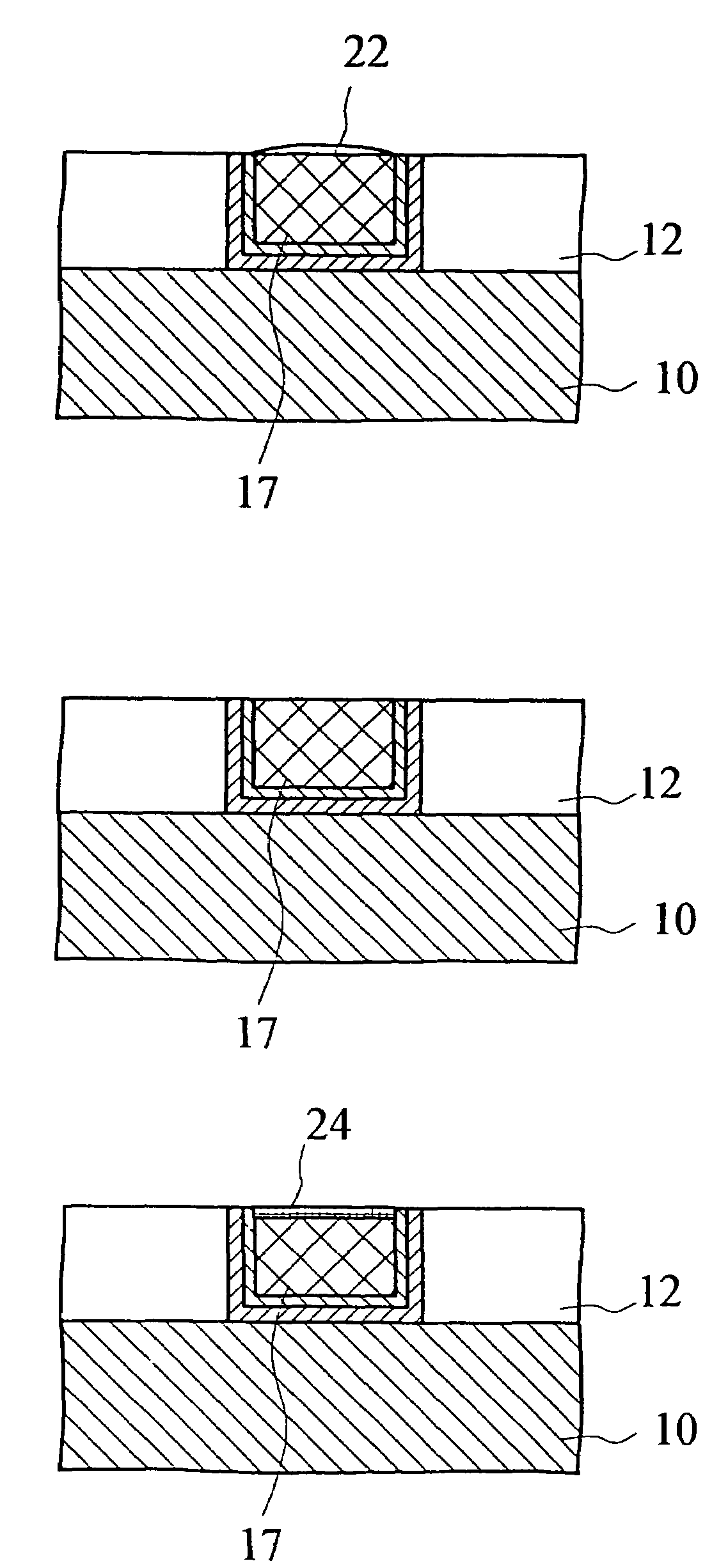

Manufacturing method of semiconductor device

InactiveUS7268087B2Lower capability requirementsImprove the immunitySemiconductor/solid-state device detailsSolid-state devicesNitrogenInterconnection

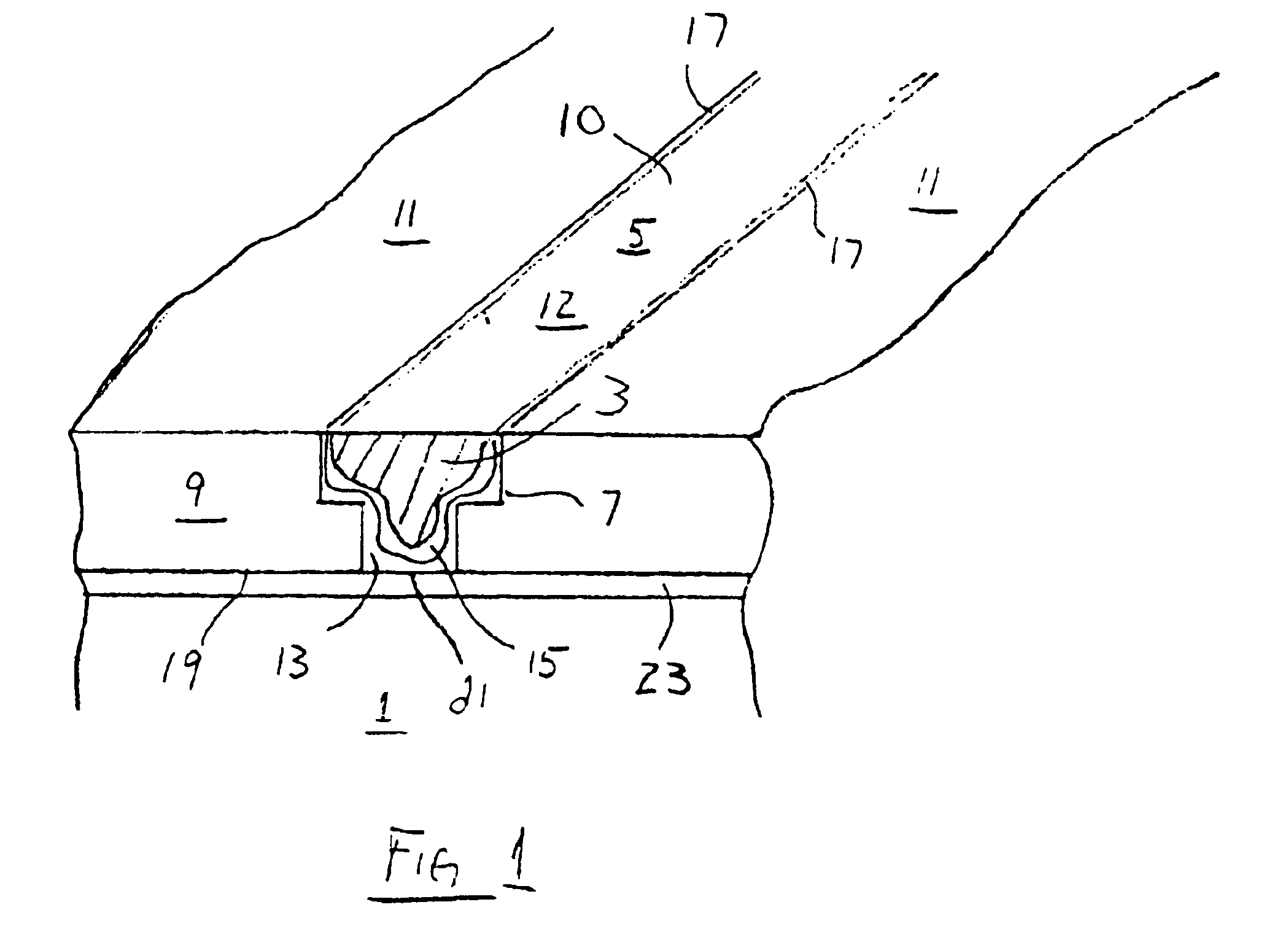

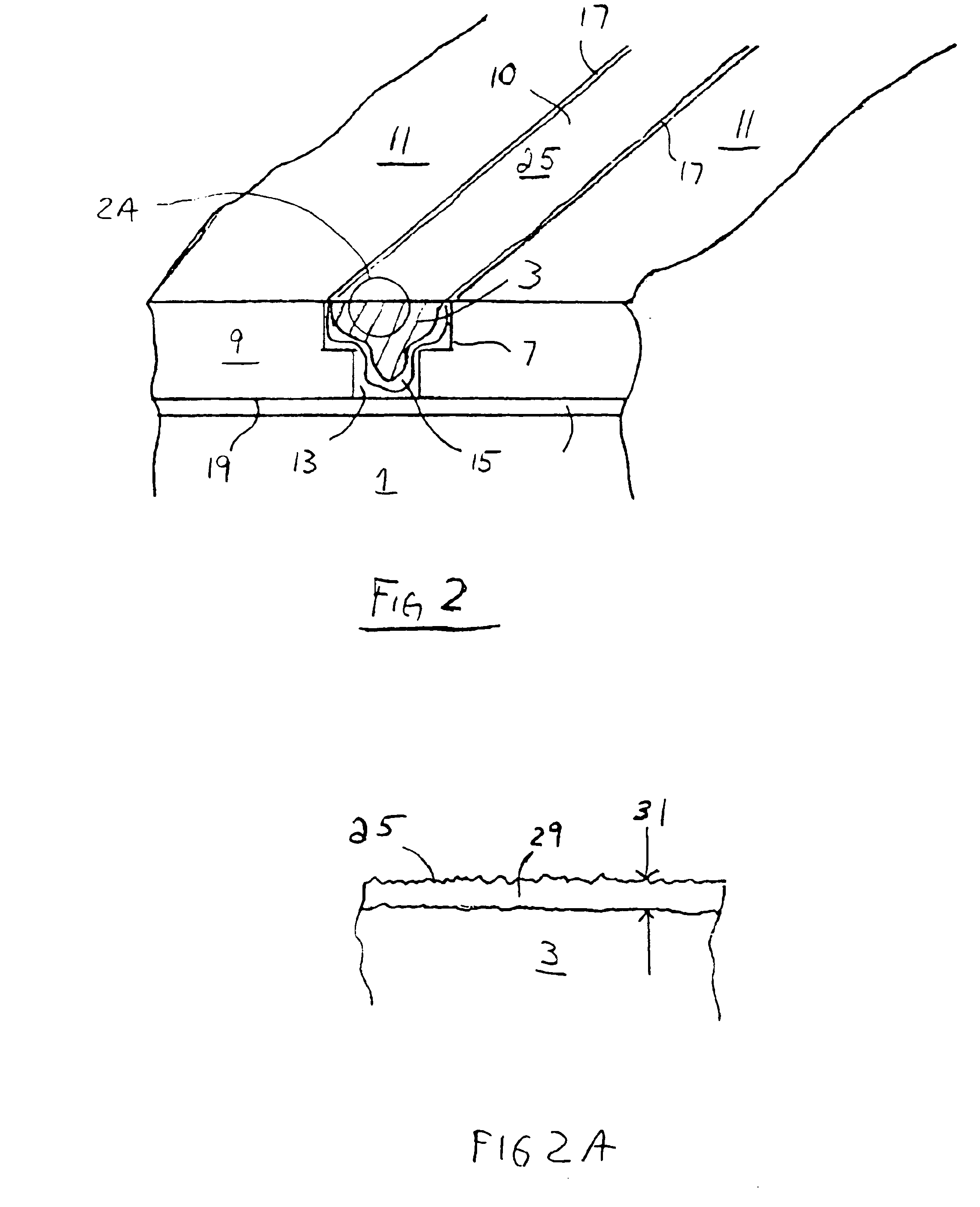

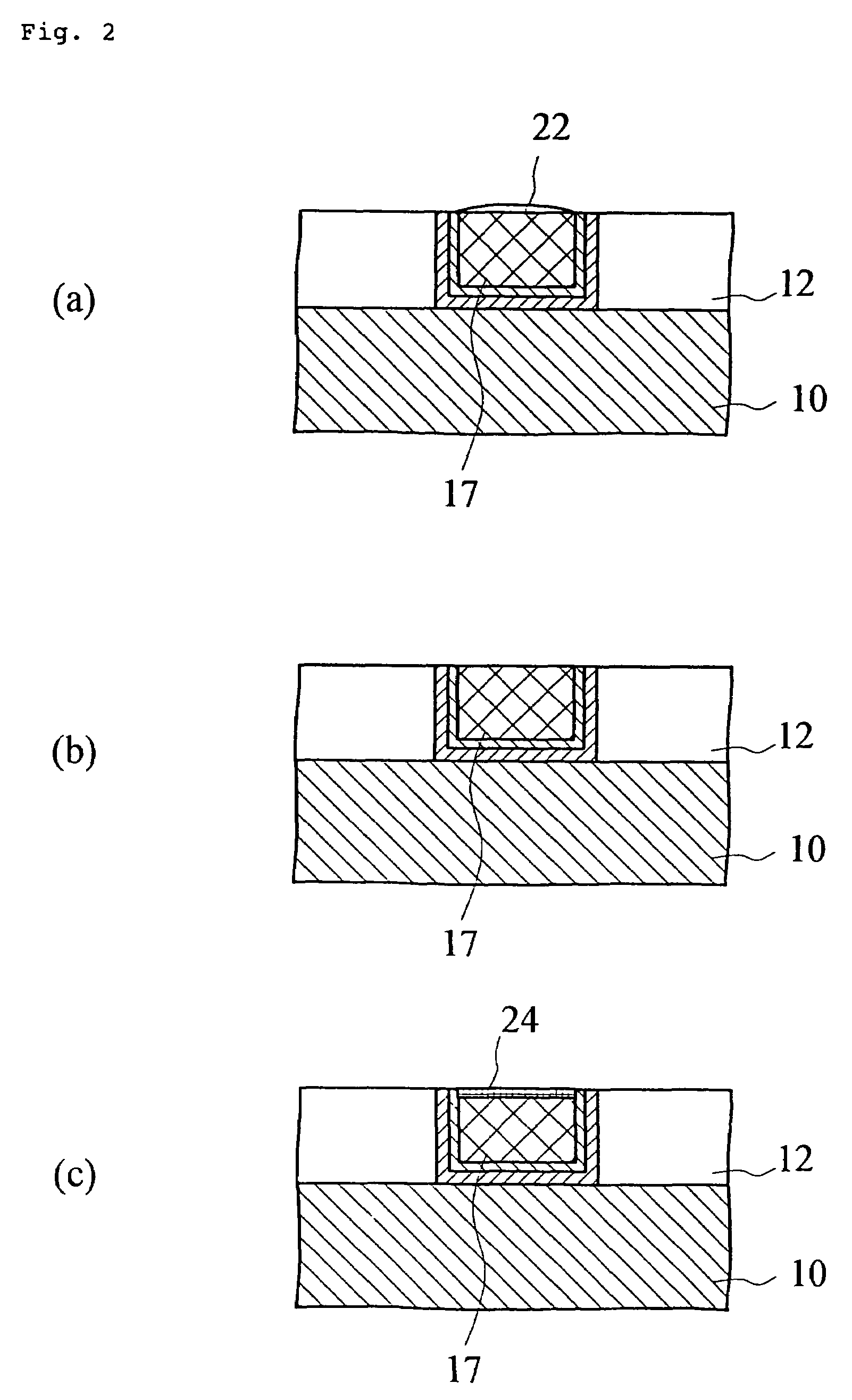

In order to provide a manufacturing method of a semiconductor device which can improve the interconnection lifetime, while controlling the increase in resistance thereof, and, in addition, can raise the manufacturing stability; by applying a plasma treatment to the surface of a copper interconnection 17 with a source gas comprising a nitrogen element being used, a copper nitride layer 24 is formed, and thereafter a silicon nitride film 18 is formed. Hereat, under the copper nitride layer 24, a thin copper silicide layer 25 is formed.

Owner:RENESAS ELECTRONICS CORP

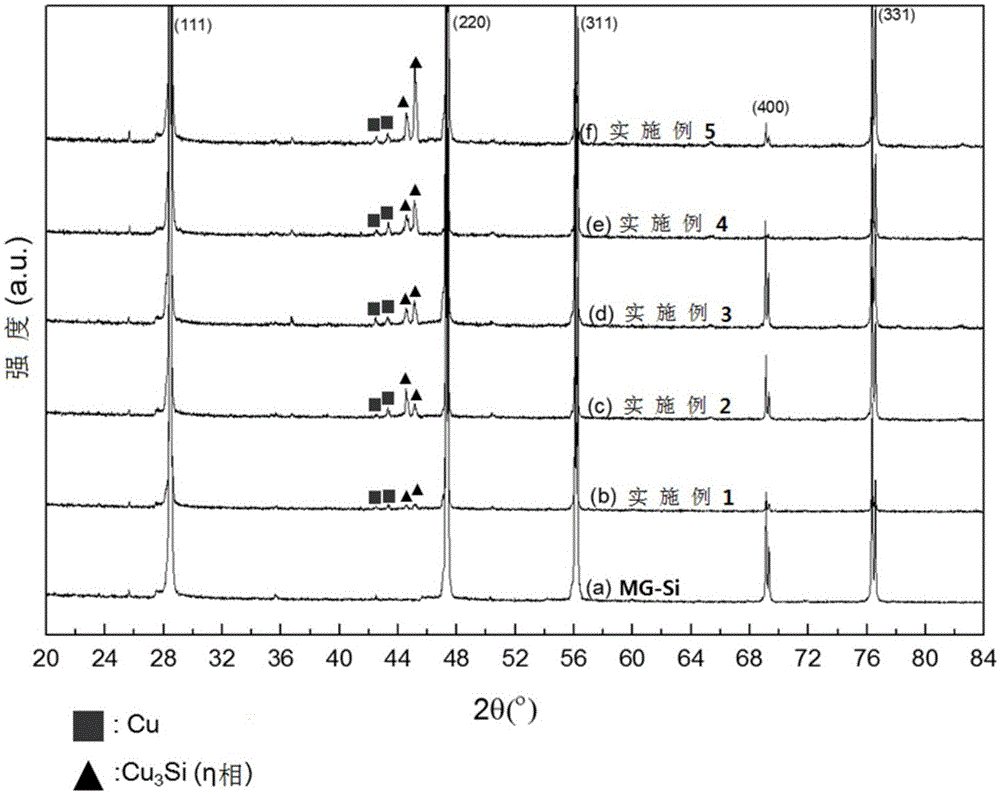

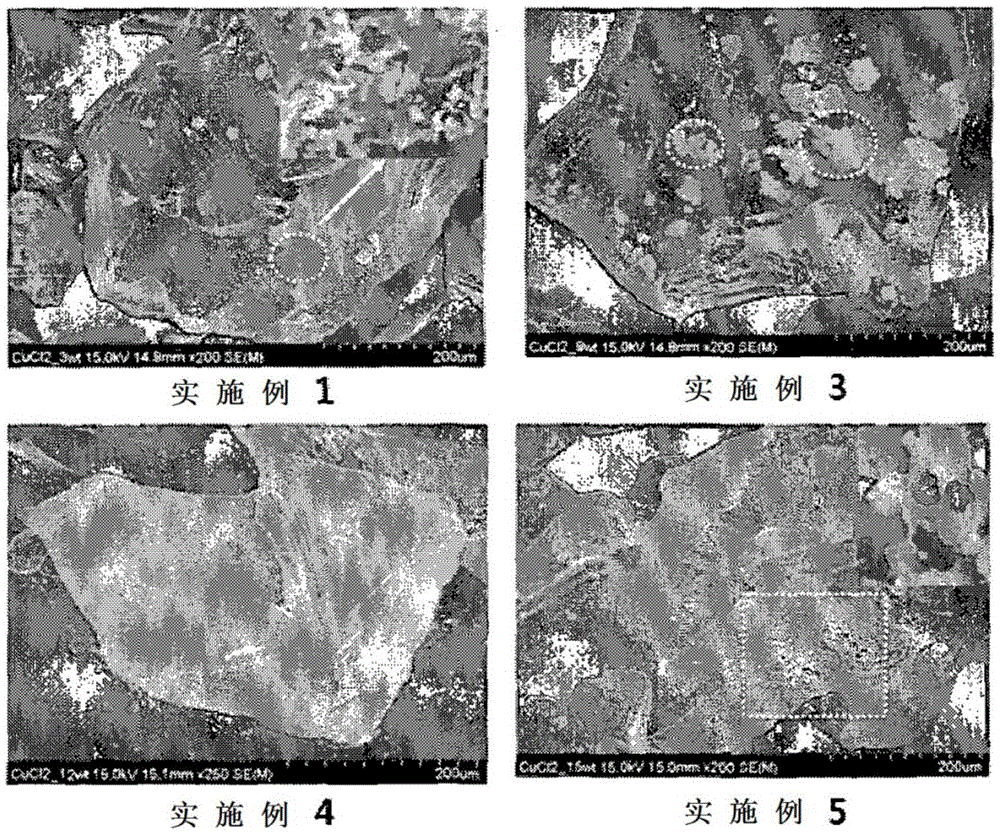

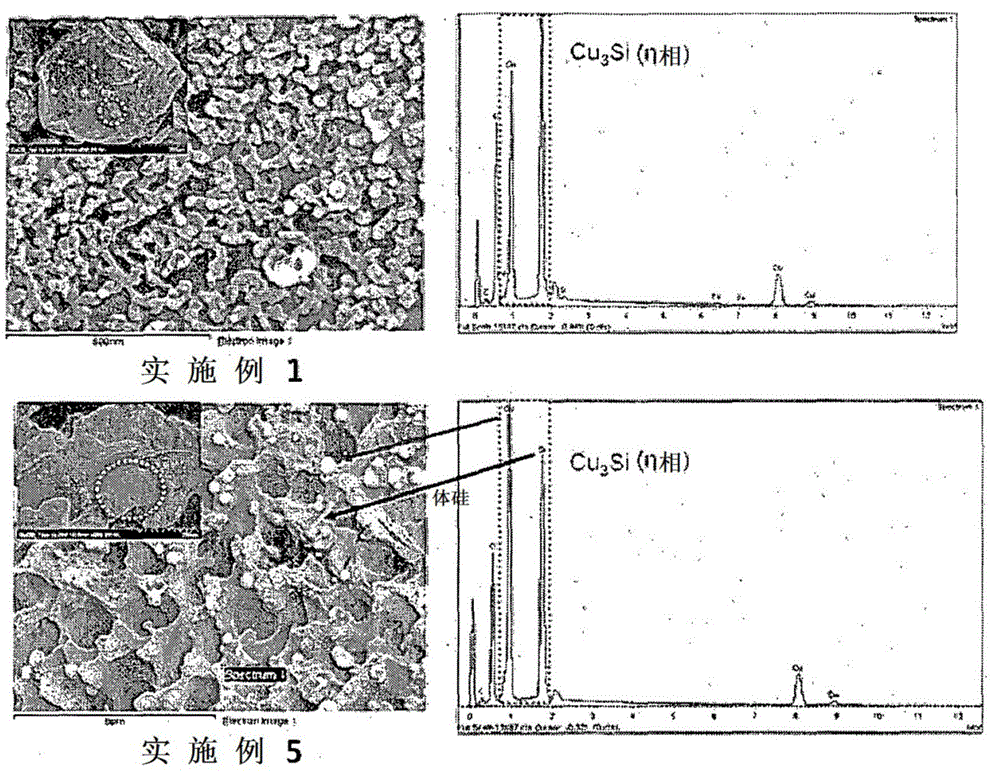

Copper-containing silicon material, method for manufacturing same, negative-electrode active substance, and secondary cell

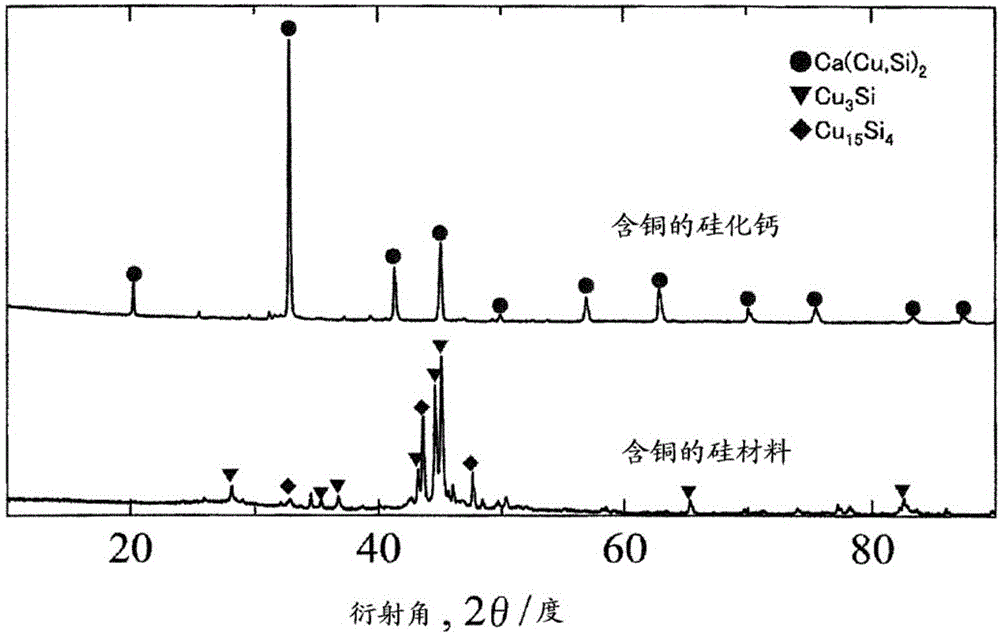

InactiveCN106458610AImprove electronic conductivityHybrid capacitor electrodesCell electrodesElectrical batteryAmorphous phase

Provided is a negative-electrode active substance having enhanced electron conductivity. In the present invention, a copper-containing silicon material is obtained by reacting copper-containing calcium silicide represented by the formula CaCuxSiy with oxygen and heat-treating the reaction product in a non-oxidizing atmosphere. The copper-containing silicon material includes Si and copper in an amorphous phase, and fine copper silicides are uniformly deposited in the amorphous phase, and the copper-containing silicon material therefore has enhanced electron conductivity. A secondary cell which uses the negative-electrode active substance in a negative electrode thereof therefore has enhanced lead characteristics and increased charge / discharge capacity.

Owner:TOYOTA IND CORP

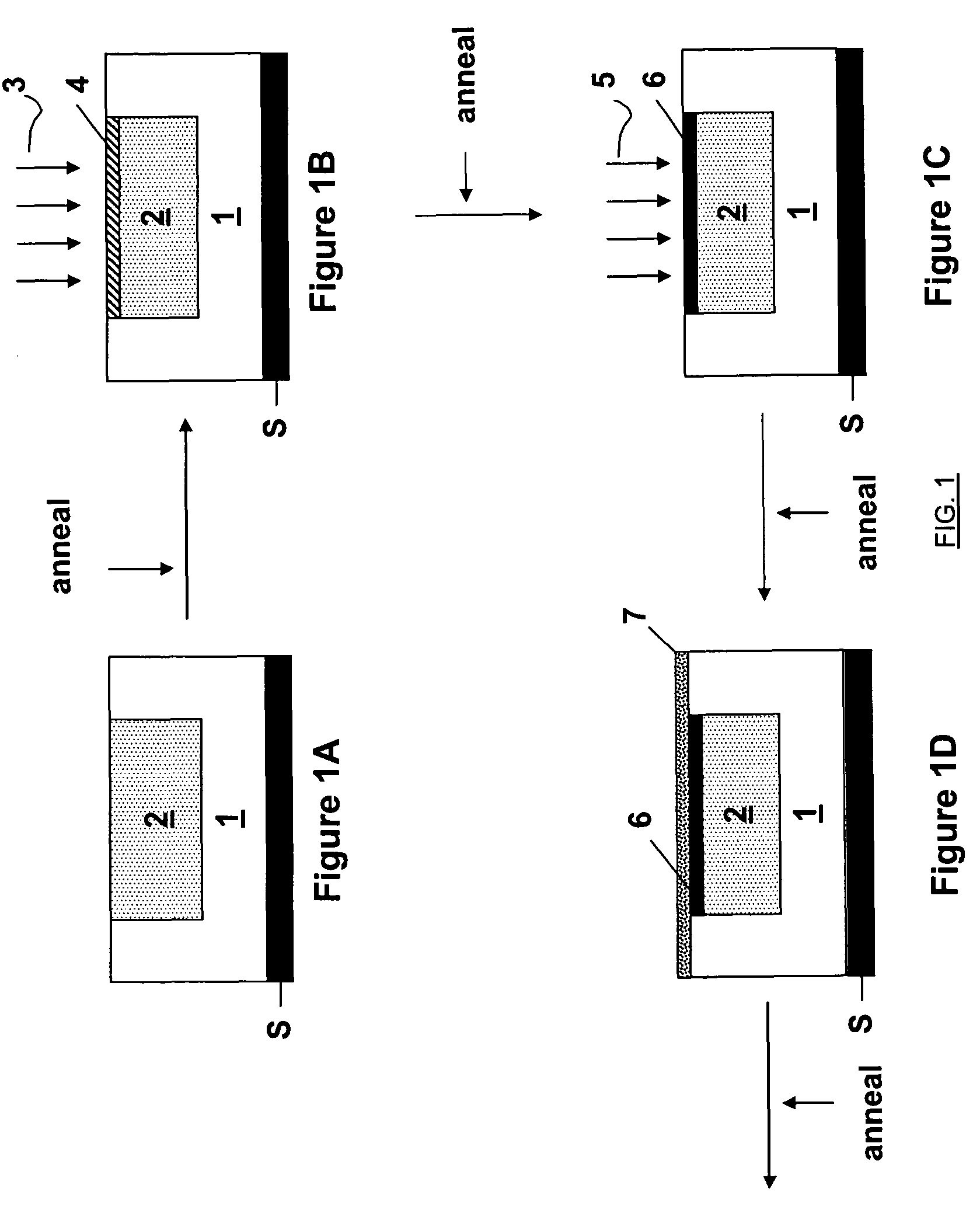

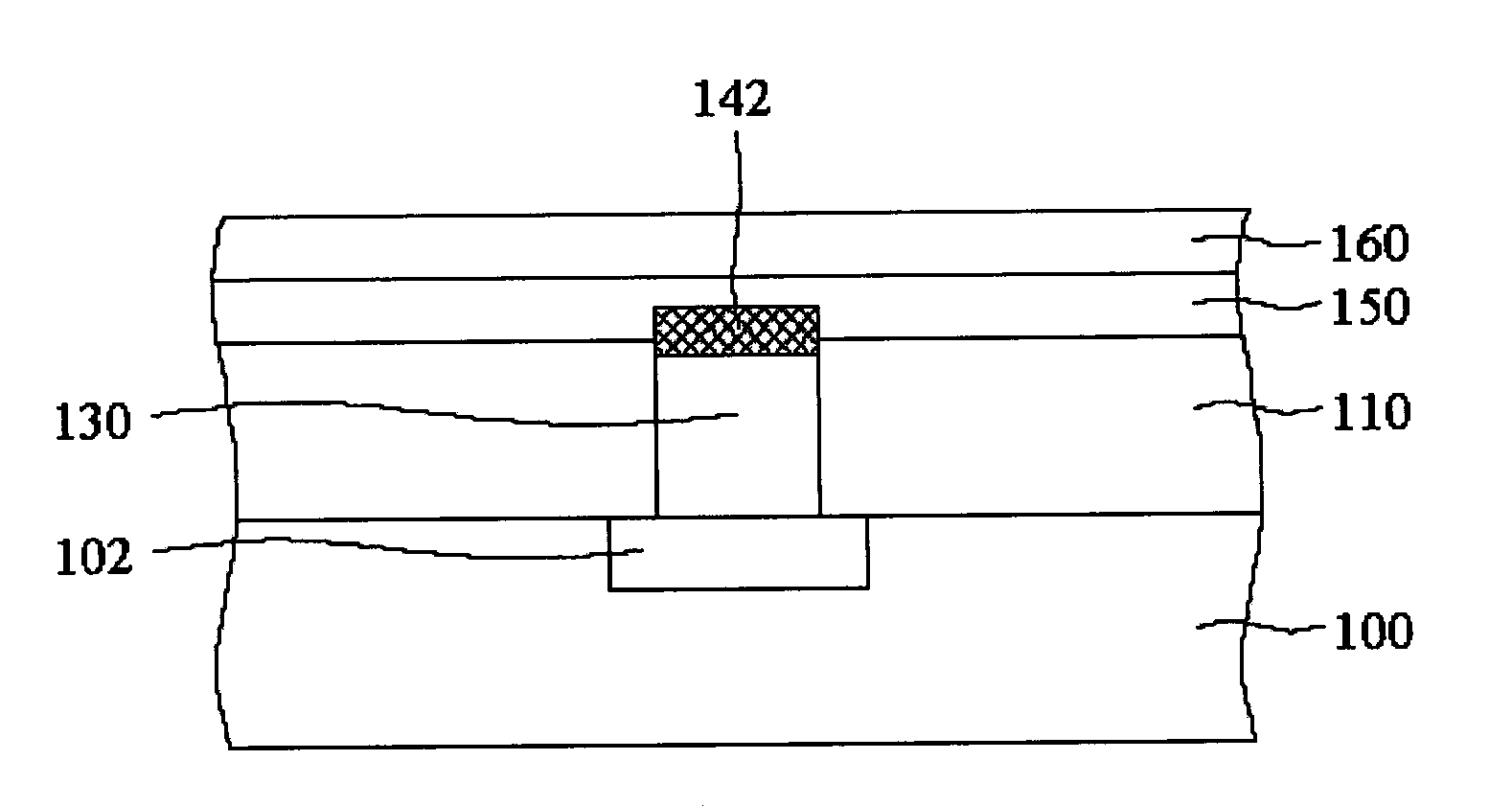

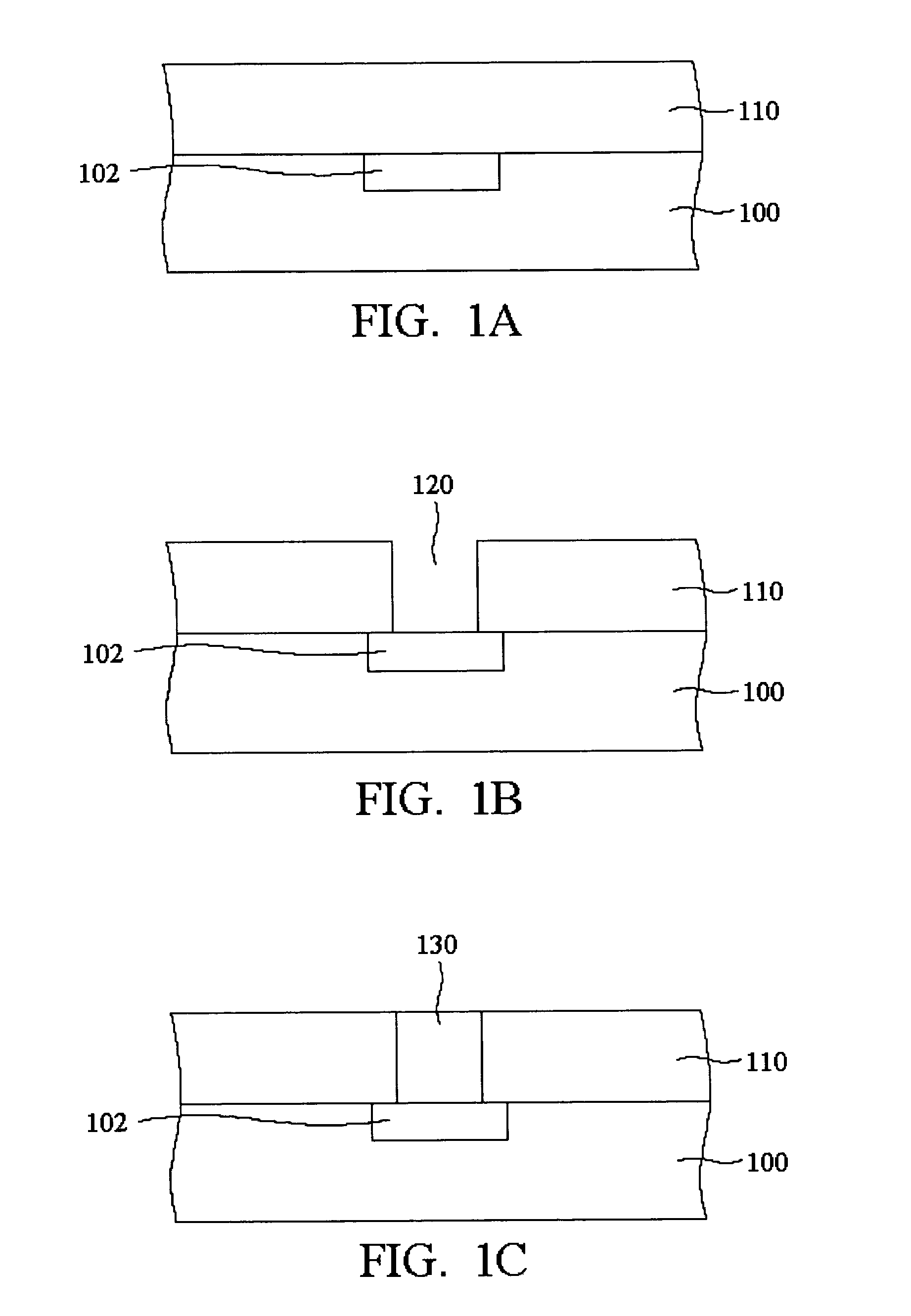

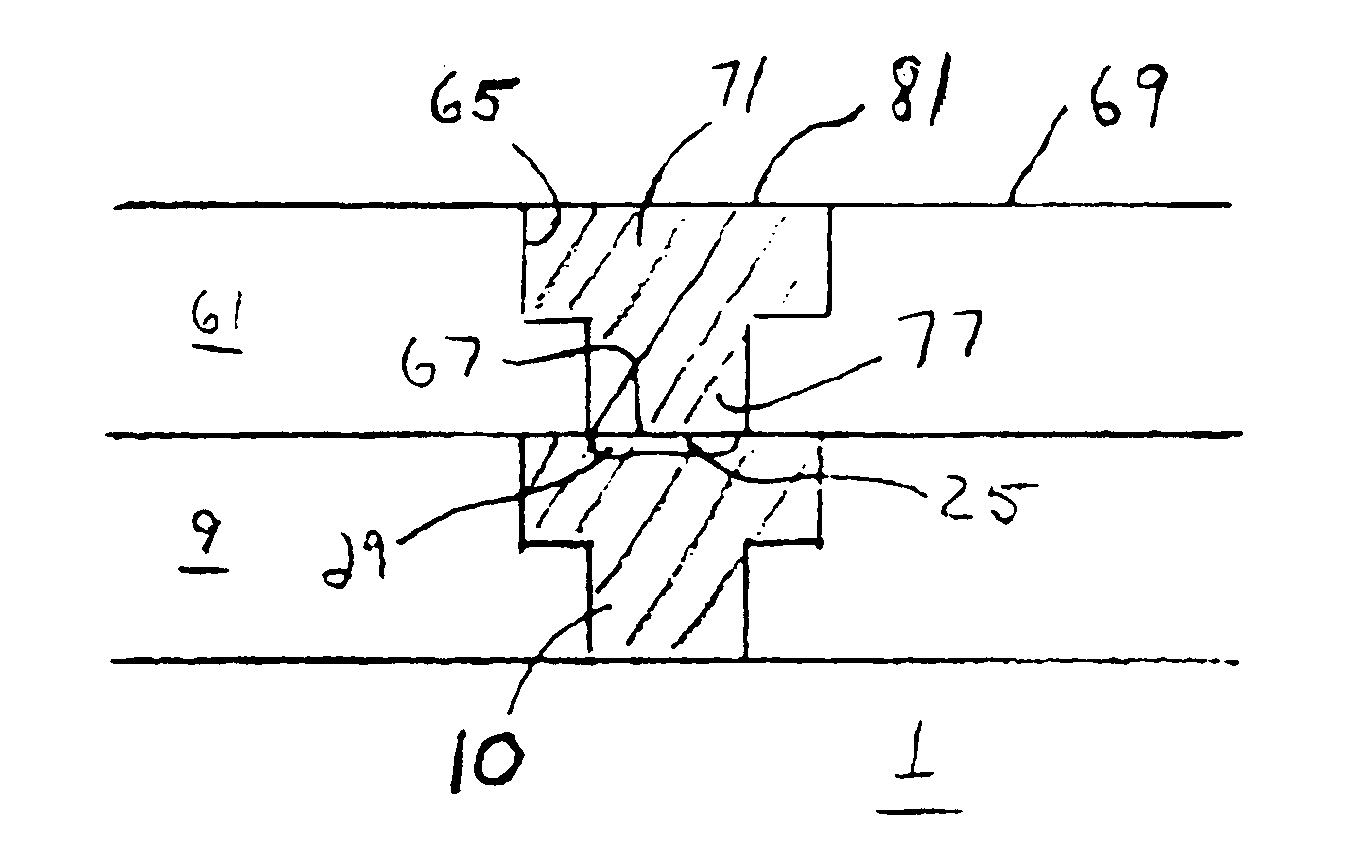

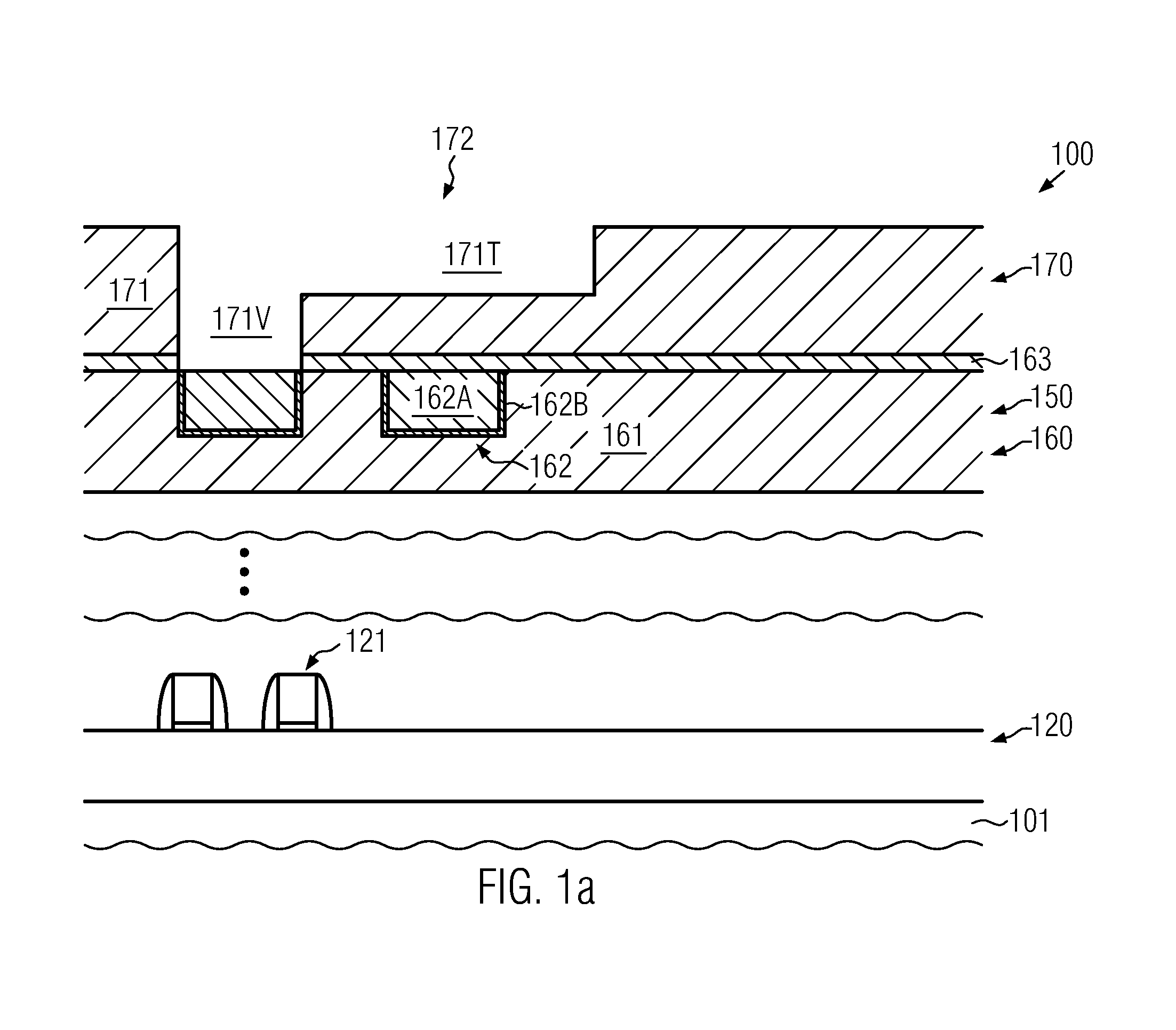

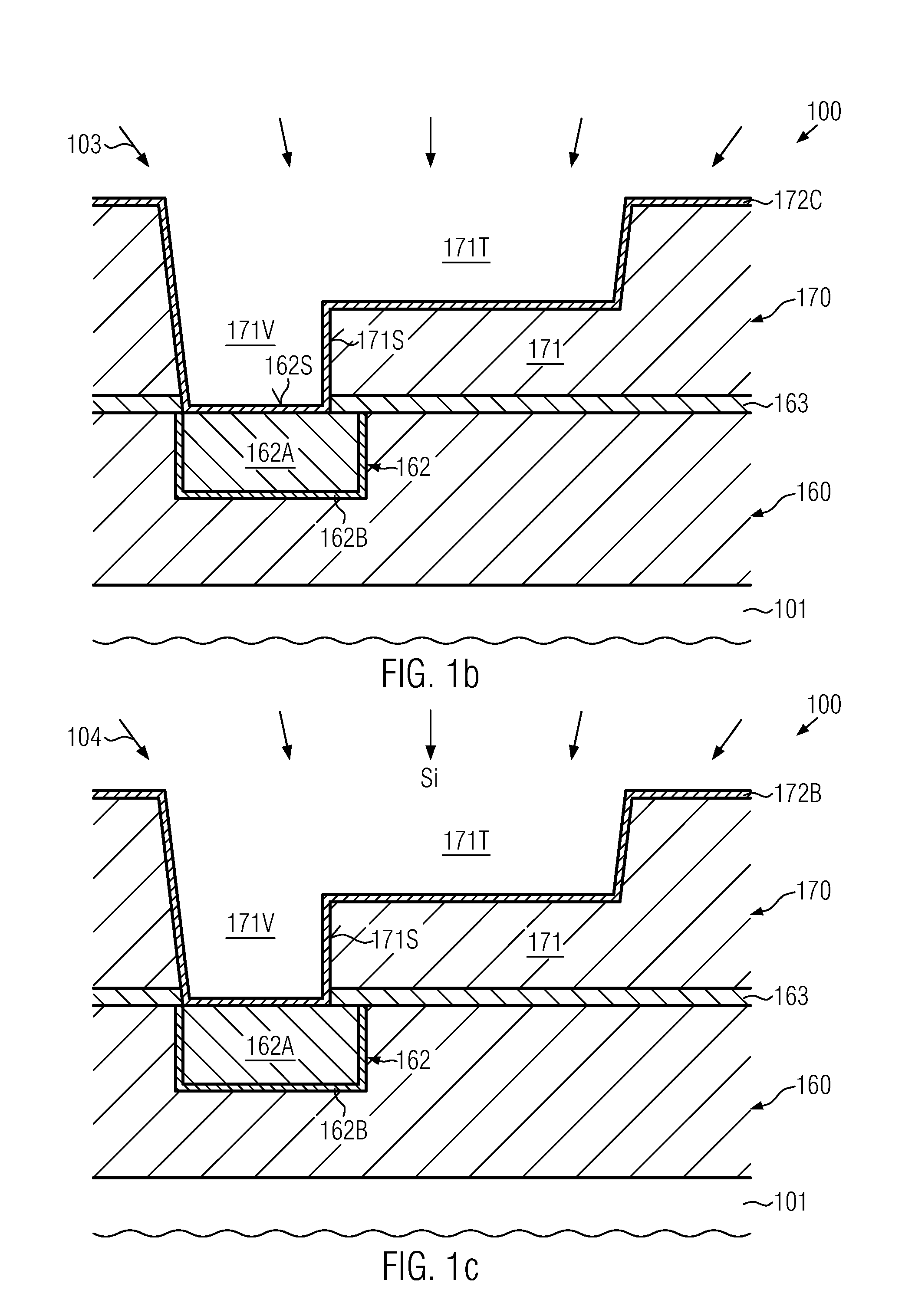

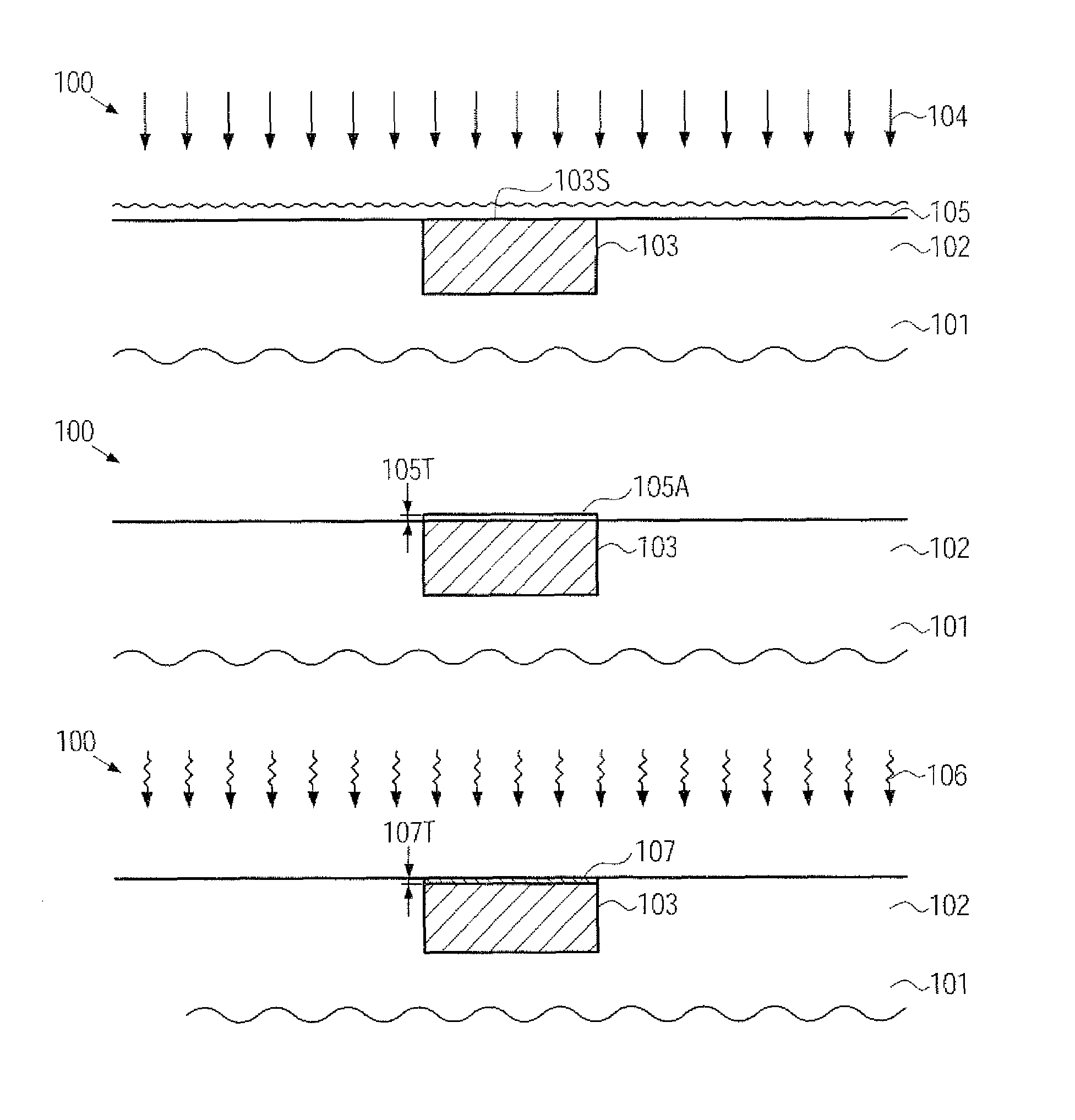

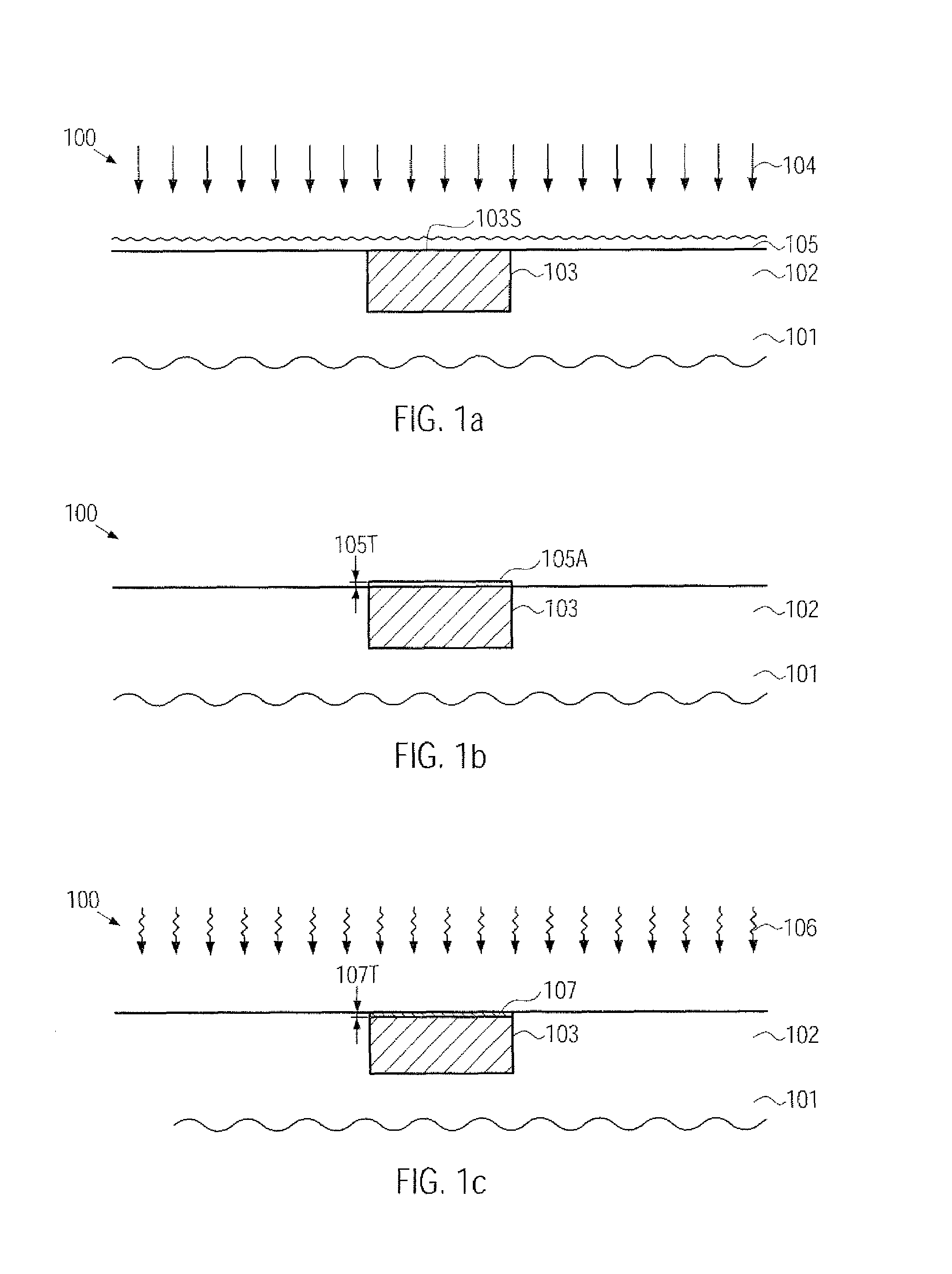

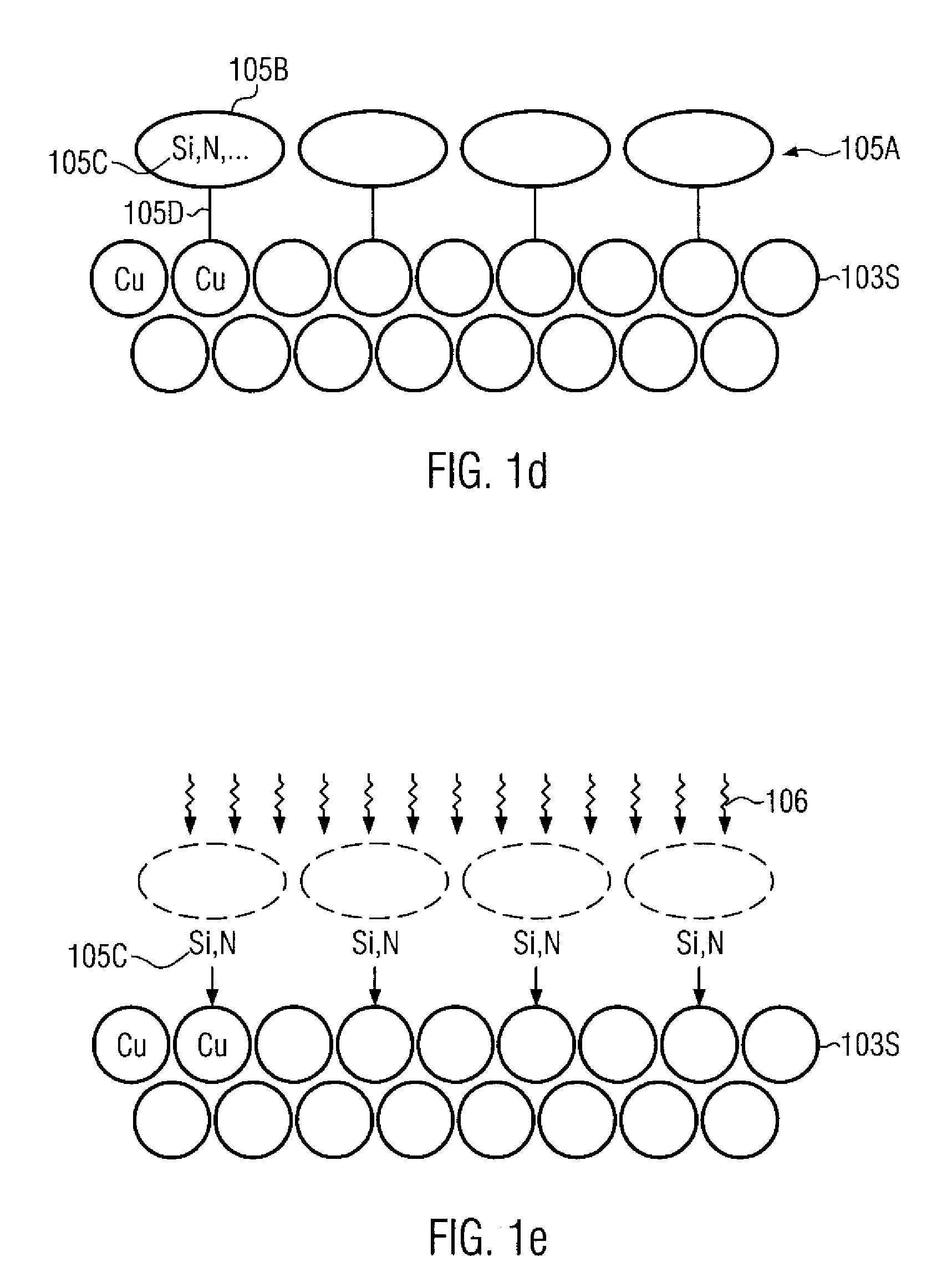

Method for forming a self-aligned nitrogen-containing copper silicide capping layer in a microstructure device

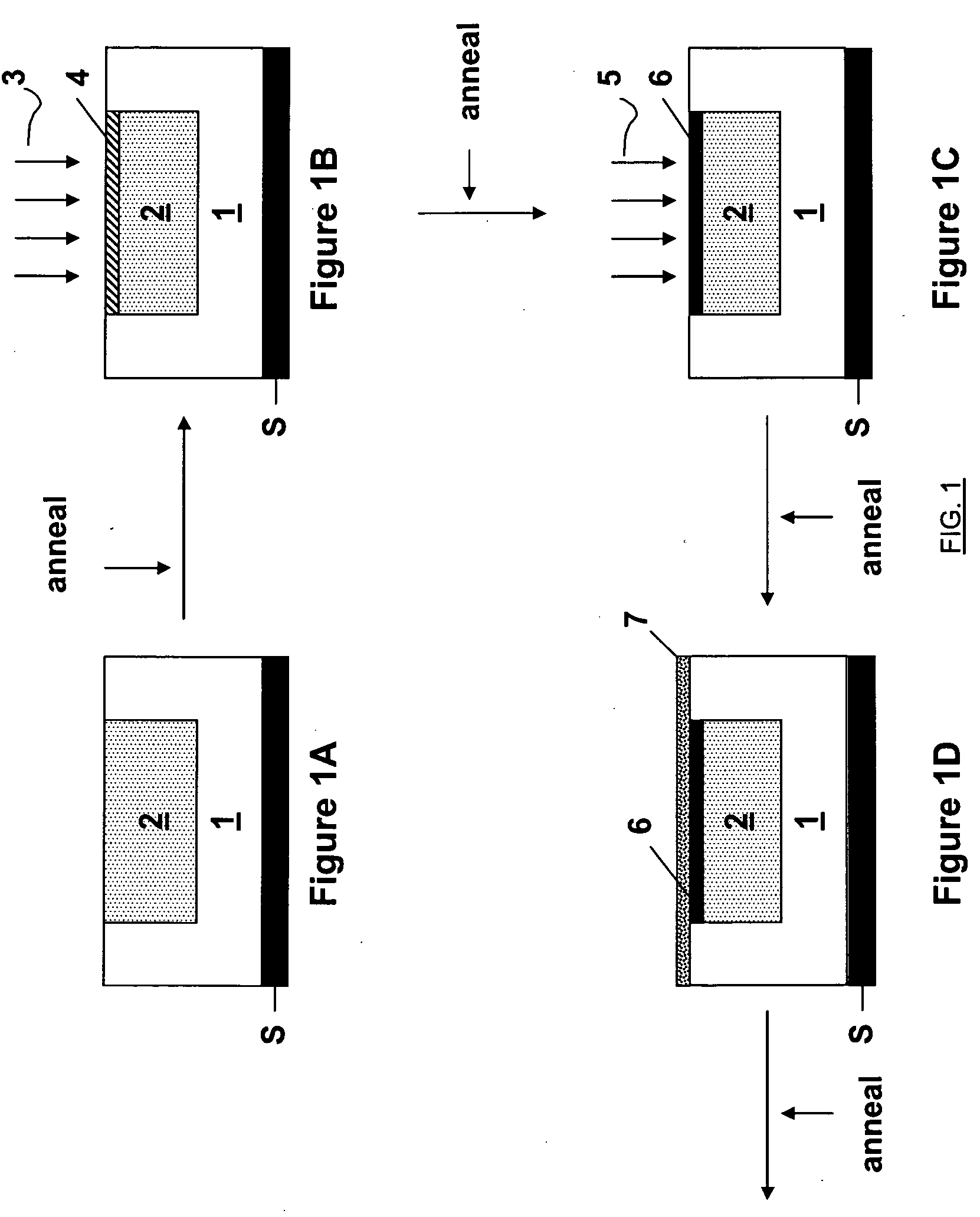

ActiveUS7413985B2High degree of processingImprove featuresSemiconductor/solid-state device manufacturingSelf limitingSalicide

By forming a copper / silicon / nitrogen alloy in a surface portion of a copper-containing region on the basis of a precursor layer, highly controllable and reliable process conditions may be established. The precursor layer may be formed on the basis of a liquid precursor solution, which may exhibit a substantially self-aligned and self-limiting deposition behavior.

Owner:TESSERA ADVANCED TECH

Brake pad with good braking effect and manufacturing method thereof

InactiveCN105440567AAvoid stratificationReduce pollutionLaminationLamination apparatusMild heatHeat stability

A manufacturing method of a brake pad with a good braking effect relates to the technical field of brake pad production. The brake pad comprises a friction material and steel back. The friction material comprises the following raw materials: phenolic resin, cis-polybutadiene rubber, carbon fiber resin, talcum powder, zirconium silicide, aluminium carbide, barium sulfate, graphite, molybdenum disulfide, copper silicide, steel fibre, silicon carbide whisker, aramid fiber and molybdenum fibre. The manufacturing method comprises the following steps: burdening, mixing materials by a water method, carrying out pre-press forming and primary heat treatment to produce a friction material workblank; carrying out mild heat treatment, putting the friction material workblank into scalding hot oil to undergo scaling for 3-5 s, taking the friction material workblank out and cleaning with alcohol, and airing; carrying out steel back shot-blasting, and gluing steel back; carrying out hot press molding; and successively carrying out secondary heat-treatment, grinding, slotting chamfer, sand-blasting, and gluing silent blades. The brake pad of the invention has high strength, is oxidation resistant, and has long service life, good heat stability, high friction coefficient and good environmental protection property for production.

Owner:安徽创新电磁离合器有限公司

Method for forming a self-aligned nitrogen-containing copper silicide capping layer in a microstructure device

ActiveUS20080132064A1Improve controllabilityImprove featuresSemiconductor/solid-state device manufacturingSelf limitingSalicide

By forming a copper / silicon / nitrogen alloy in a surface portion of a copper-containing region on the basis of a precursor layer, highly controllable and reliable process conditions may be established. The precursor layer may be formed on the basis of a liquid precursor solution, which may exhibit a substantially self-aligned and self-limiting deposition behavior.

Owner:TESSERA ADVANCED TECH

Protective cover for a copper containing conductor

InactiveUS20150295103A1Good surface protectionHigh resolutionSemiconductor/solid-state device manufacturingPhotovoltaic energy generationSurface layerElectrical conductor

The method of manufacturing a solar cell comprises the steps of: (a) providing the semiconductor substrate in a deposition chamber of a vapour deposition apparatus, which semiconductor substrate comprises a passivation layer at a first side thereof which passivation layer is patterned to define contact areas at which the copper-containing conductor is present; (b) supplying a gaseous silicon species into the deposition chamber, resulting in the formation of a surface layer of a copper silicide on a surface of the copper-containing conductor and in the formation of amorphous silicon on top of the passivation layer, and (c) providing a protective layer of an insulating silicon compound on the surface layer, wherein the protective cover comprising both the surface layer and the protective layer.

Owner:M4SI

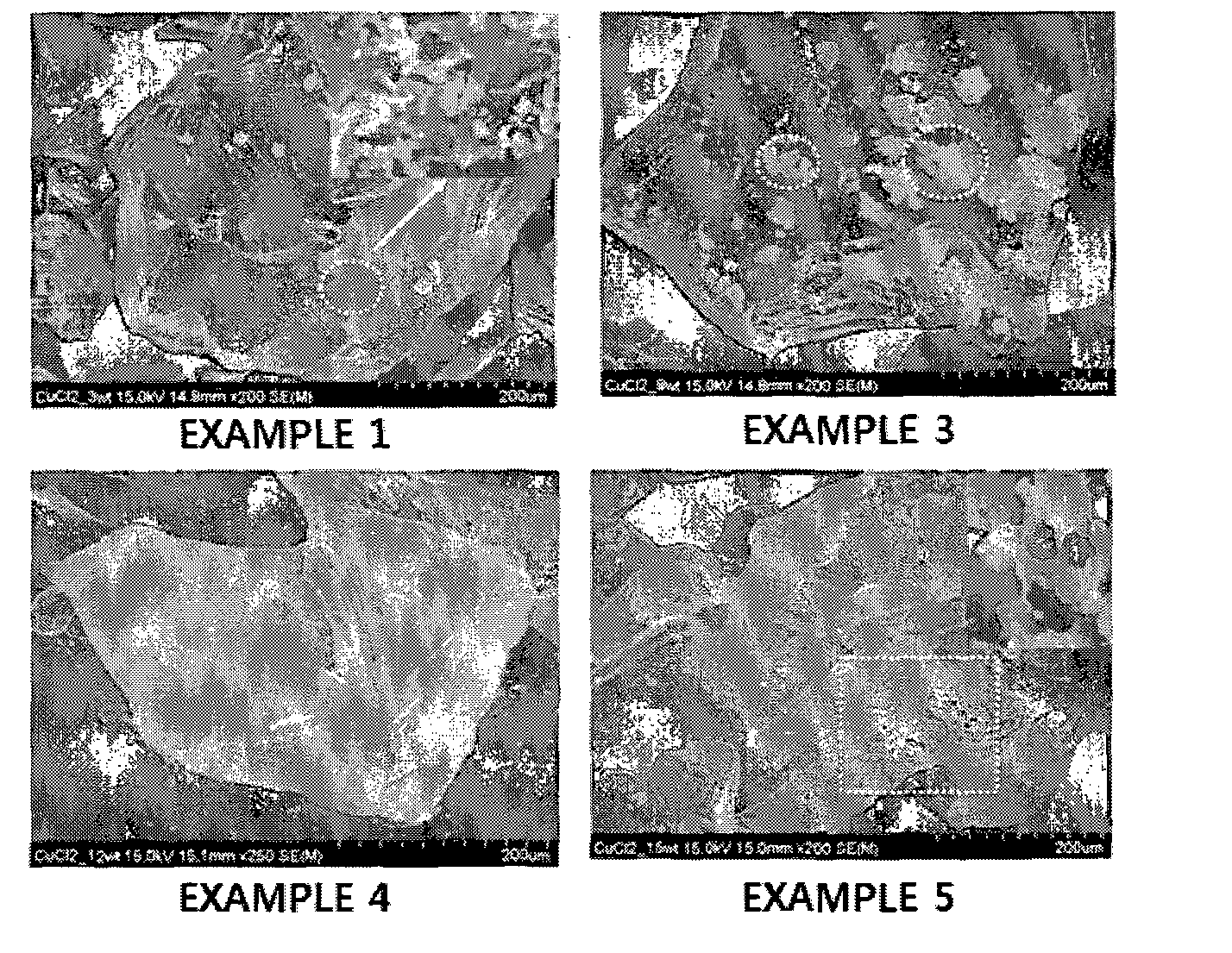

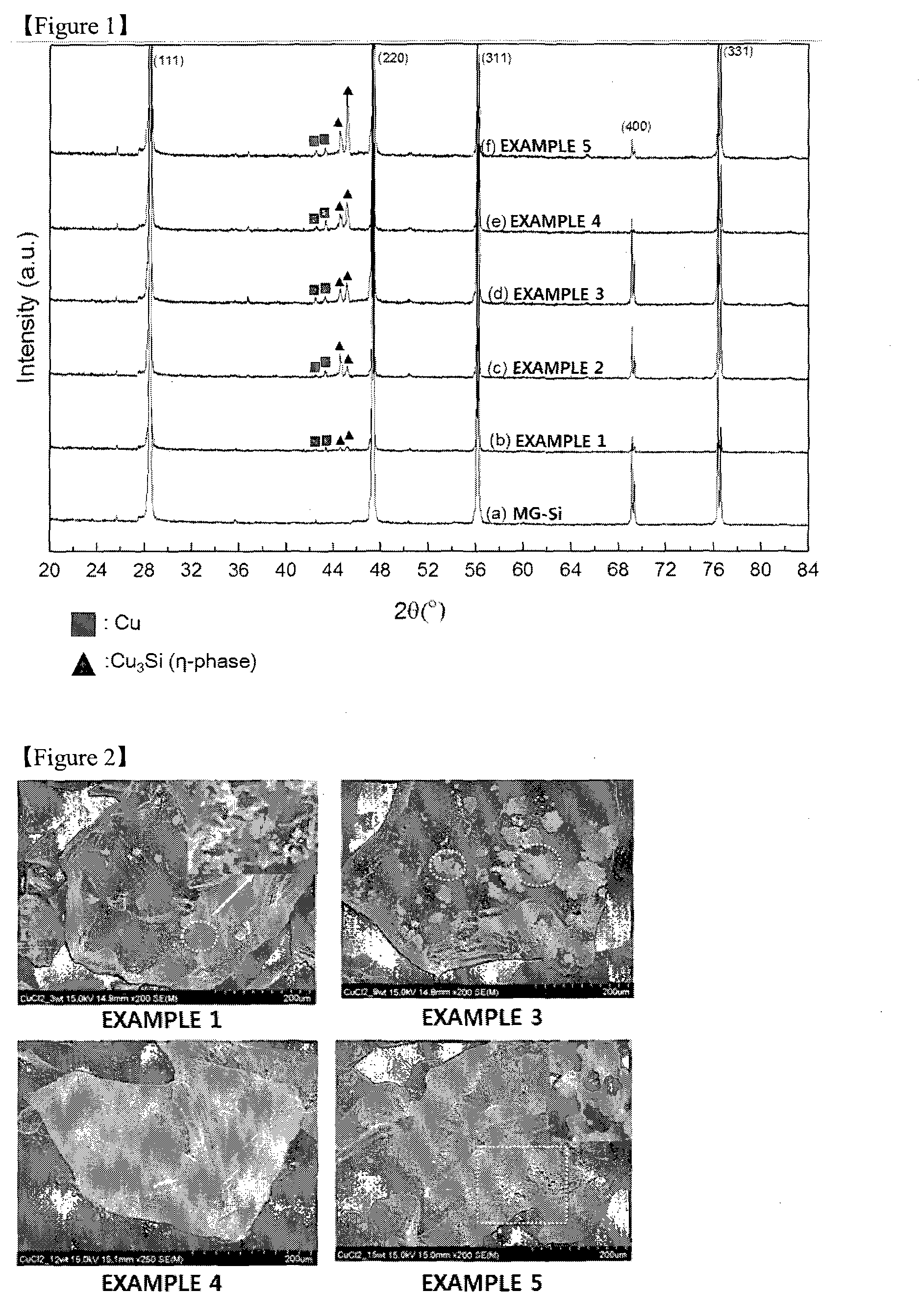

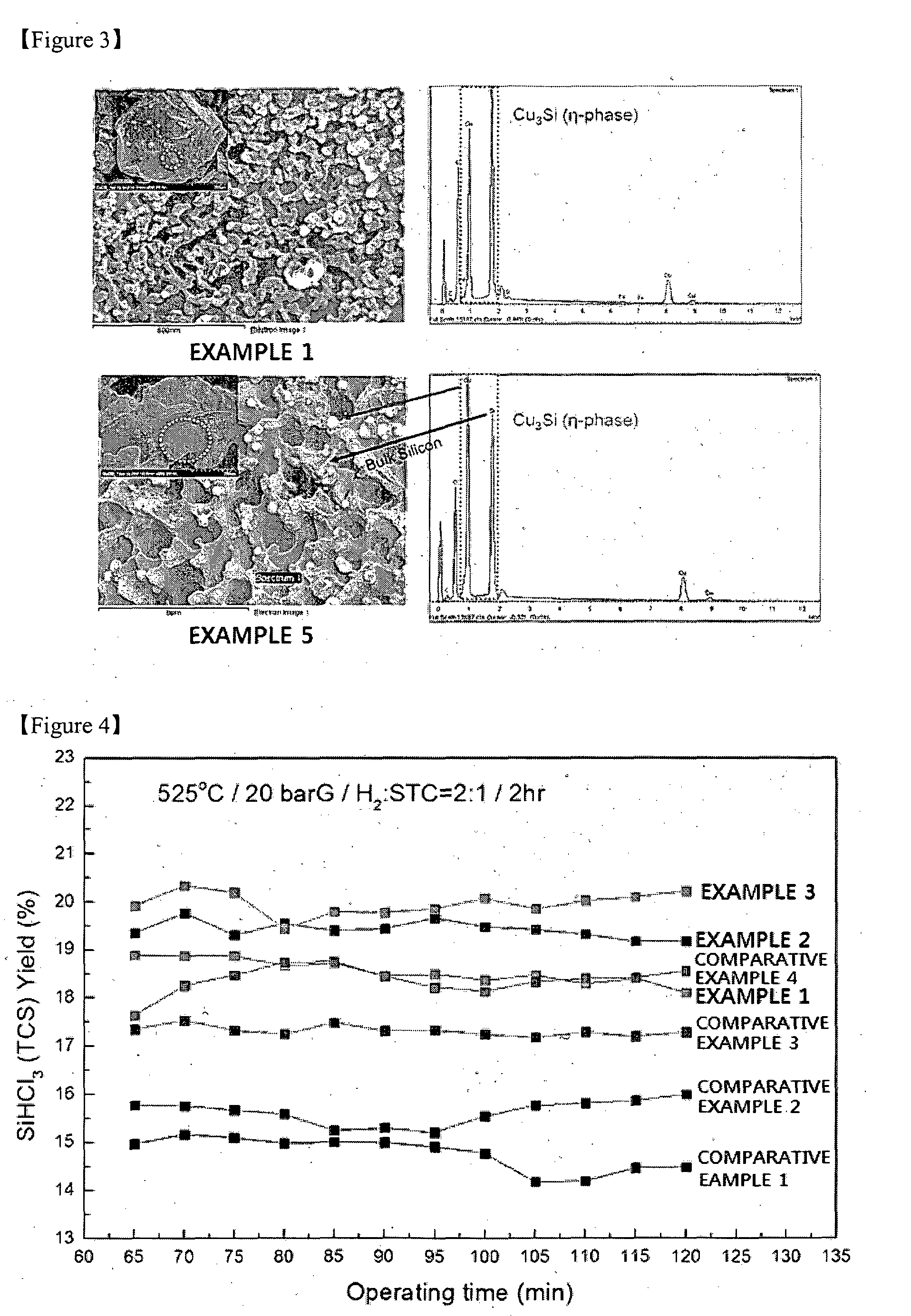

A method for preparing trichlorosilane

The present invention relates to a method for preparing trichlorosilane. According to the method for preparing trichlorosilane of the present invention, trichlorosilane may be obtained with improved yield using silicon where copper silicide is formed.

Owner:HANWHA CHEMICAL CORPORATION

High-temperature-resistant brake block and manufacturing method thereof

InactiveCN105508478AAvoid stratificationReduce pollutionFriction liningMaleic anhydrideCopper silicide

The invention provides a manufacturing method of a high-temperature-resistant brake block, and relates to the technical fields of production of brake blocks. The high-temperature-resistant brake block comprises a friction material and a steel backing, wherein the friction material comprises the following components and raw materials in parts by weight: phenolic resins, butadiene rubber, high-temperature-resistant carbon fiber resins, maleic anhydride, steel fibers, silicon carbide whiskers, aramid, molybdenum fibers, graphite, barites, silicon disulfide, copper silicide, dolomite, talcum powder, mica powder, copper powder and barium sulfate. The manufacturing method comprises the following steps of preparing the materials, mixing the materials by an aqueous method, performing prepressing forming and performing heat treatment once, so as to produce friction material blanks; performing warming treatment, putting the friction material blanks in boiling oil for scalding for 3-5 seconds, and then fishing out the scalded blanks for drying; performing shot blasting treatment on the steel backing, and spreading glue to the steel backing after the shot blasting treatment is performed; hot-forming the blanks and the steel backing; and then, sequentially performing reheat treatment, grinding, fluting, chamfering, grit blasting treatment and sticking of noisedamping sheets. The brake blocks manufactured by the method disclosed by the invention are high in intensity, oxidation-resistant, good in heat stability, high in friction coefficient, and good in production environmentally-friendly performance.

Owner:安徽创新电磁离合器有限公司

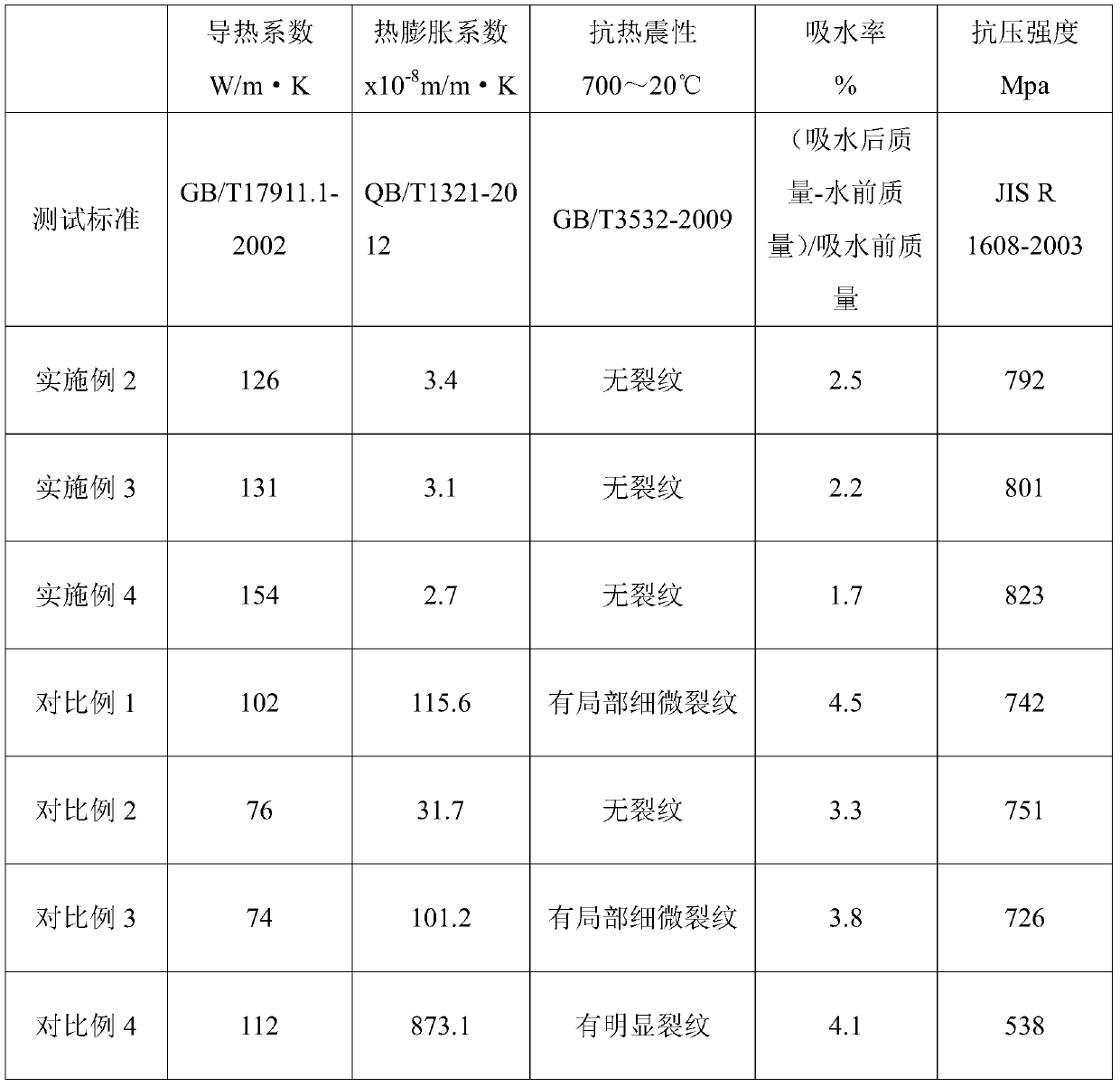

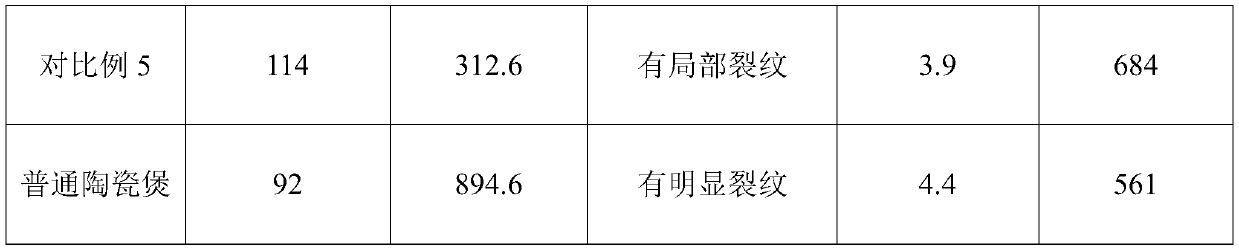

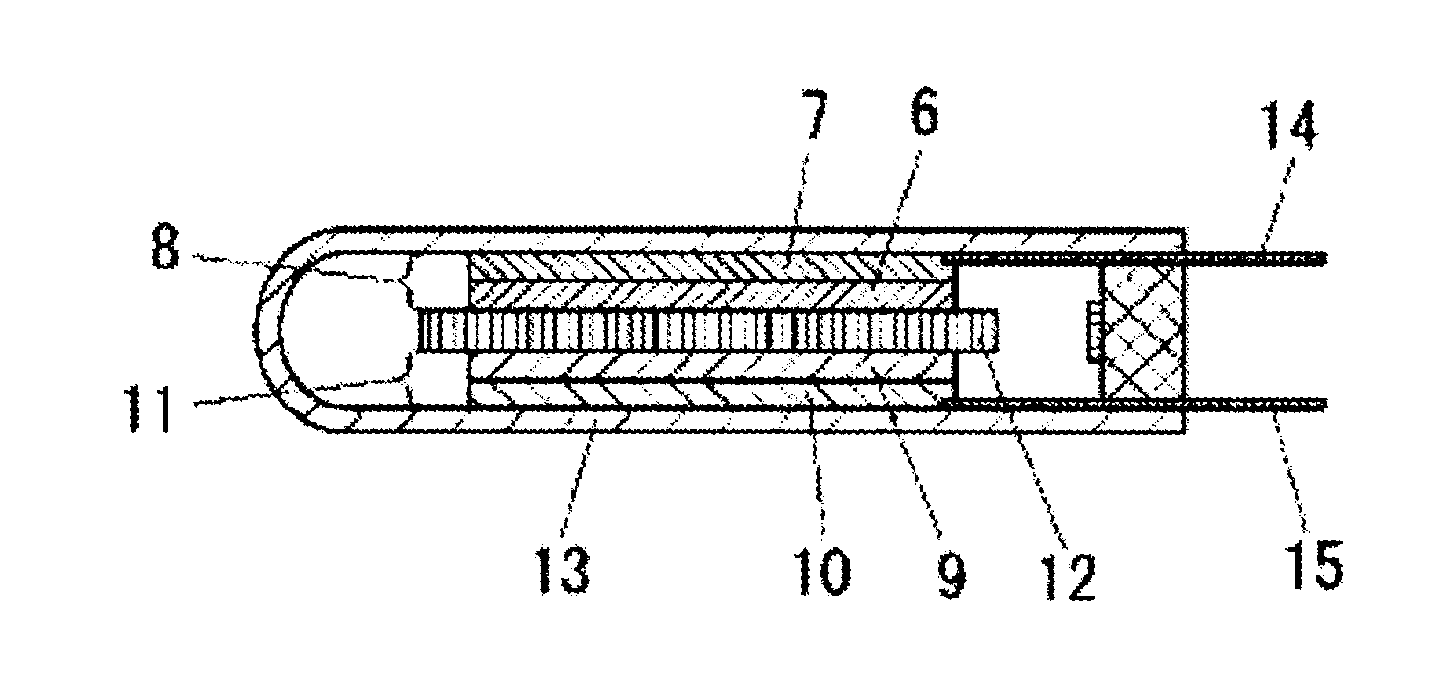

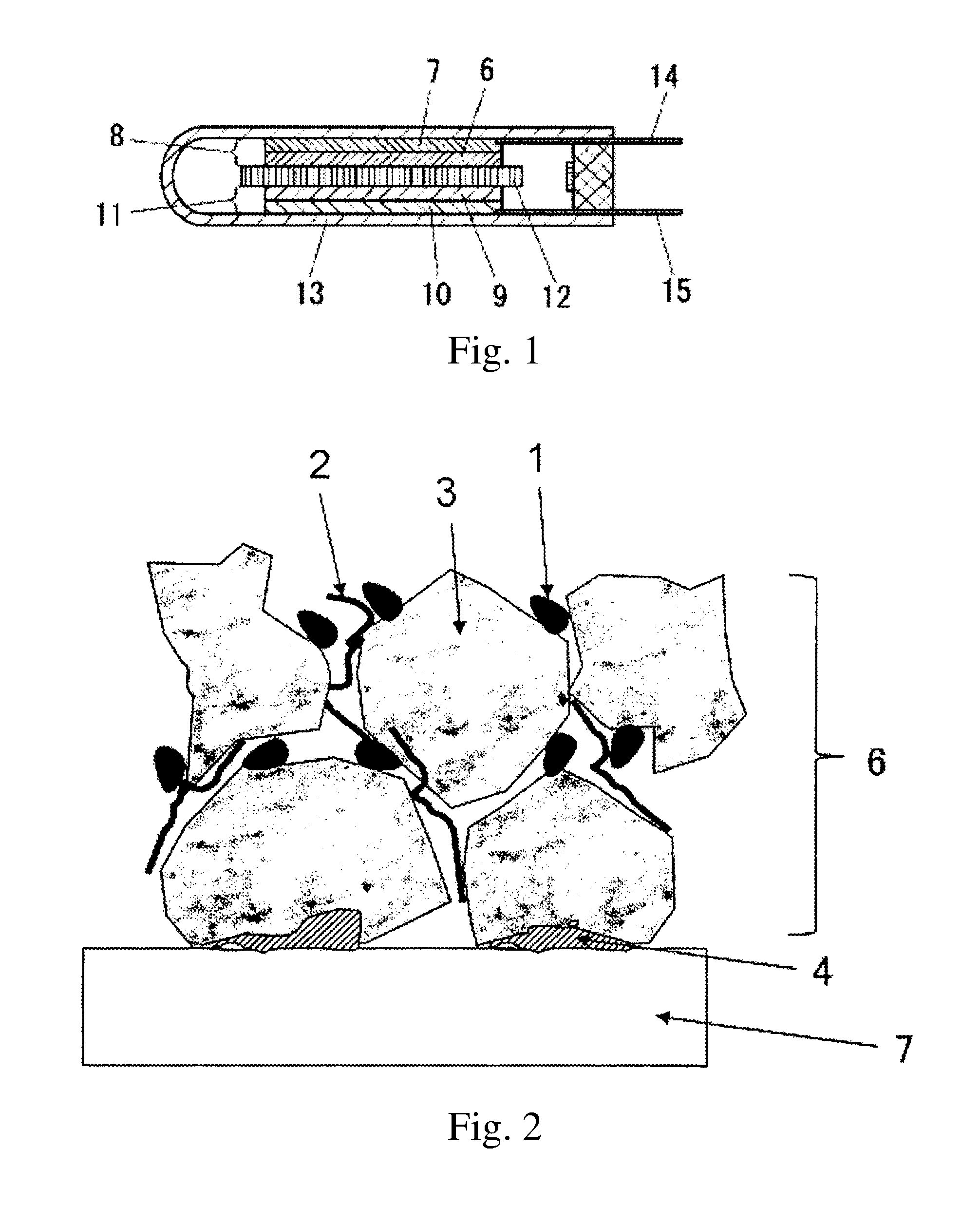

High-thermal-conductivity ceramic crucible and preparation method thereof

The invention discloses a high-thermal-conductivity ceramic crucible. The high-thermal-conductivity ceramic crucible is prepared from the following raw materials in parts by weight: 60 to 75 parts ofa mixture of calcined spodumene powder and petalite powder, 15 to 25 parts of quartz, 25 to 35 parts of bauxite, 12 to 17 parts of a mixture of copper silicide and copper powder, 5 to 7.5 parts of silicon carbide fibers and 9 to 15 parts of calcined kaolin, wherein in the mixture of the calcined spodumene powder and the petalite powder, the mass ratio of the calcined spodumene powder to the petalite powder is 1:(0.2 to 0.4); in the mixture of the copper silicide and the copper powder, the mass ratio of the copper silicide to the copper powder is 1:(0.8 to 1.1). The high-thermal-conductivity ceramic crucible disclosed by the invention has excellent thermal conductivity, good heat resistance, low water absorption and high compressive strength.

Owner:福建省嘉悦陶瓷科技有限公司

Negative electrode, method for producing the same, and battery

ActiveUS20160211525A1Lower electrode resistanceInhibit deteriorationElectrode thermal treatmentElectrode carriers/collectorsSlurryCopper foil

Owner:NEC ENERGY DEVICES LTD

Self-aligned copper silicide formation for improved adhesion/electromigration

InactiveUS6818992B1Reduce layeringLess resistivitySemiconductor/solid-state device detailsSolid-state devicesSemiconductor structureEngineering

A method for forming a semiconductor structure includes supplying a structure having an exposed last metalization layer, cleaning the last metalization layer, forming a silicide in a top portion of the last metalization layer and forming a terminal over the silicide.

Owner:GLOBALFOUNDRIES INC

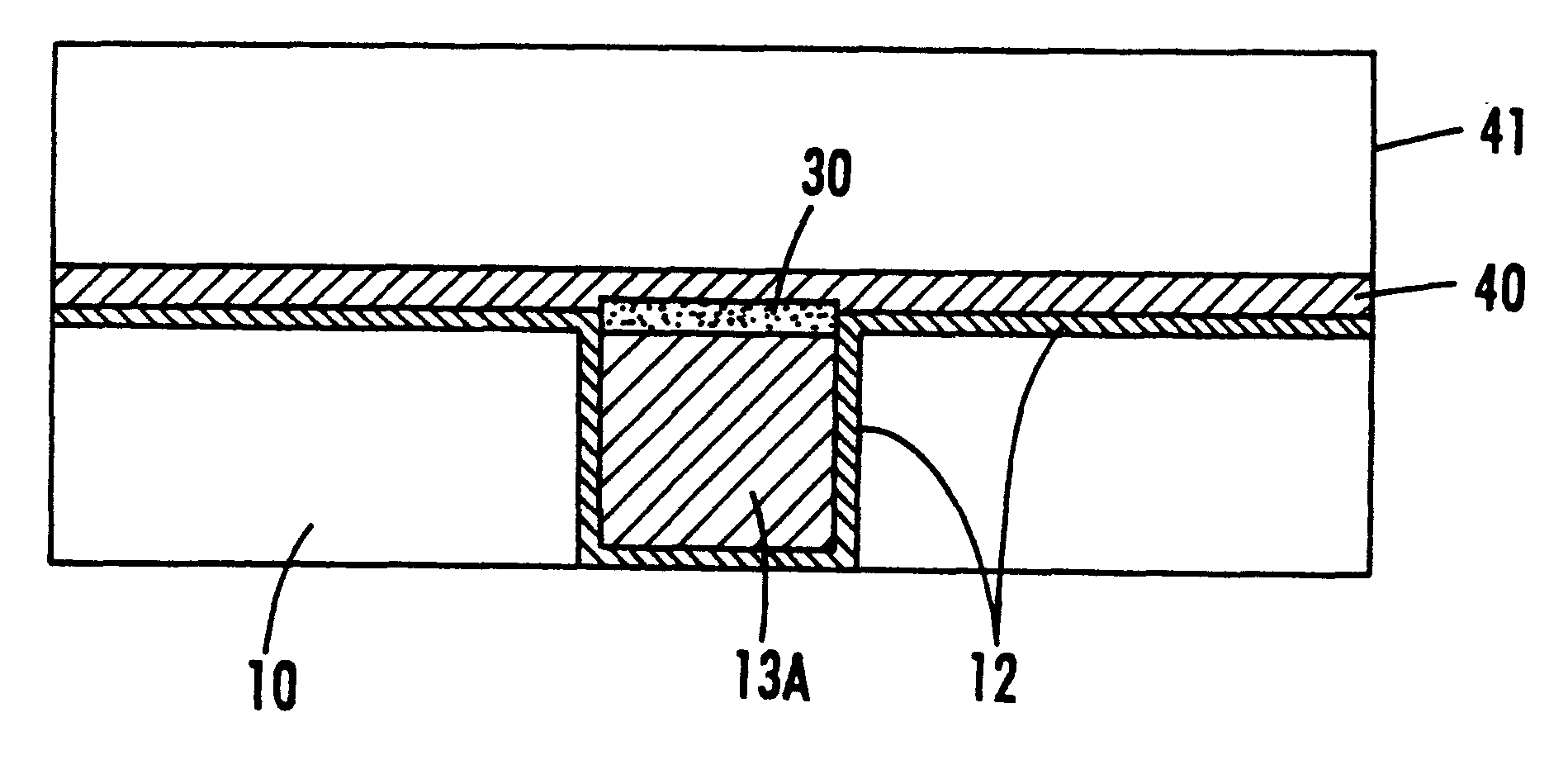

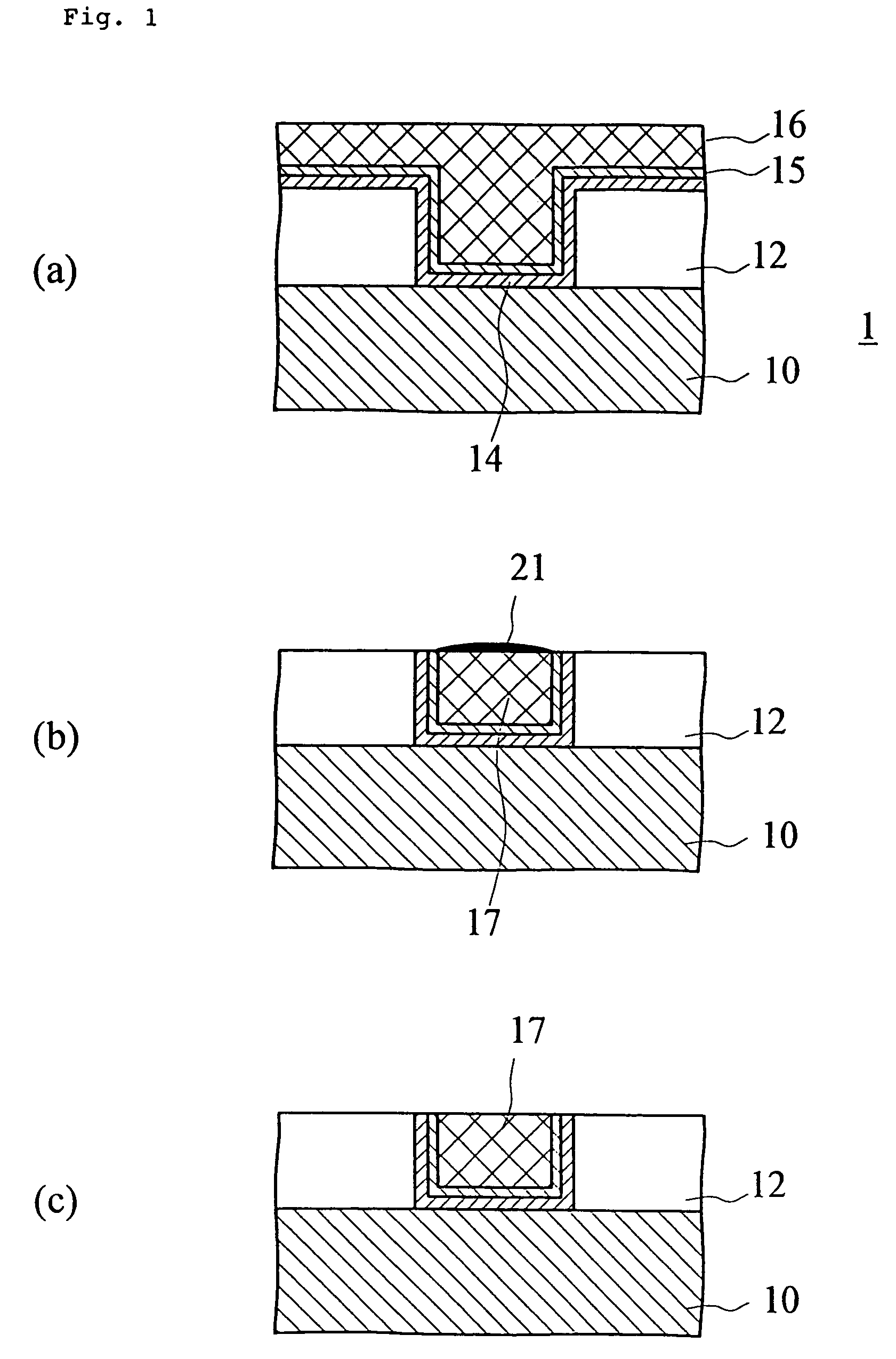

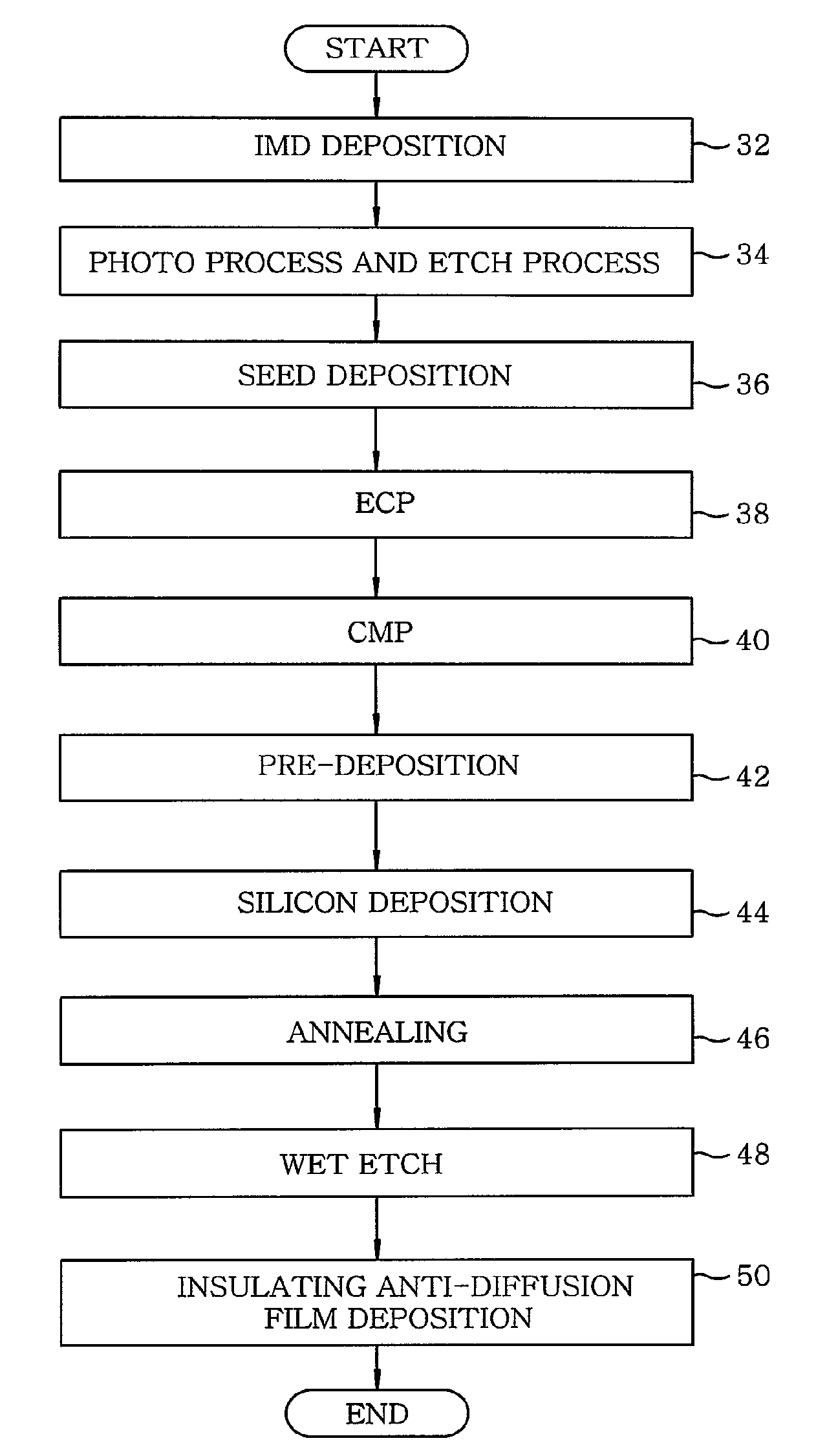

Semiconductor device having copper metal line and method of forming the same

InactiveUS7678686B2Prevent degradationImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesCopper silicideSemiconductor

A method of forming a copper metal line in a semiconductor device includes depositing an interlayer insulating layer on a semiconductor substrate having a lower metal line, forming a via contact hole and a metal line pattern in the semiconductor substrate, sequentially depositing a barrier metal film and a copper seed layer, forming a copper film on a surface of the semiconductor substrate, removing the copper film and the barrier metal film, other than the portion of a copper metal line to be formed, removing a native oxide film existing on a surface of the copper metal line of the semiconductor substrate, depositing a silicon layer on the semiconductor substrate, making the deposited silicon layer and copper metal react to each other to form a copper silicide layer, removing a remaining silicon layer without being reacted, and depositing an insulating anti-diffusion film over the semiconductor substrate.

Owner:DONGBU HITEK CO LTD

Method of preparing trichlorosilane

InactiveUS20160101983A1Continuous and efficient preparationIncrease productionHalogenated silanesCopper silicideHeat treating

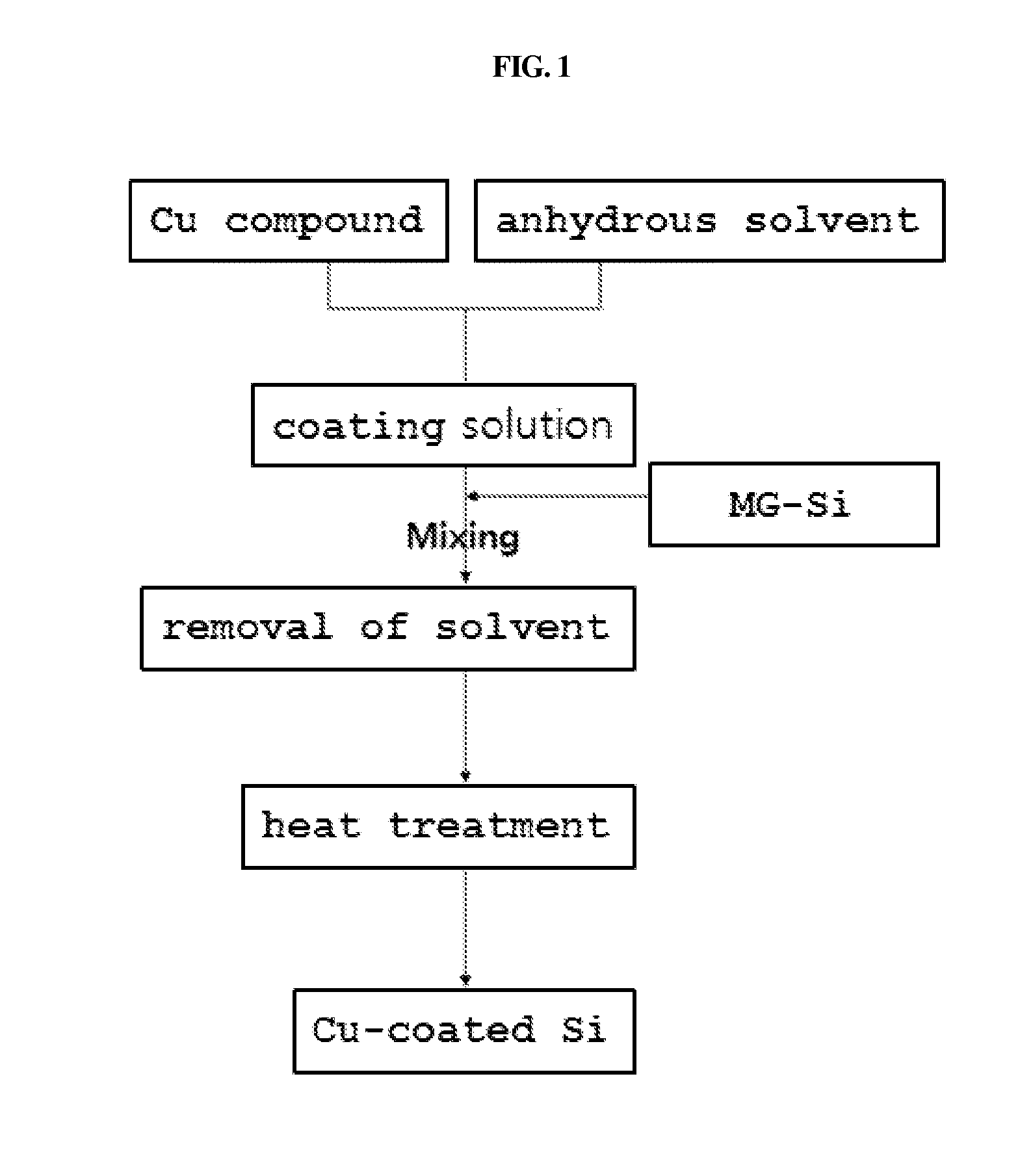

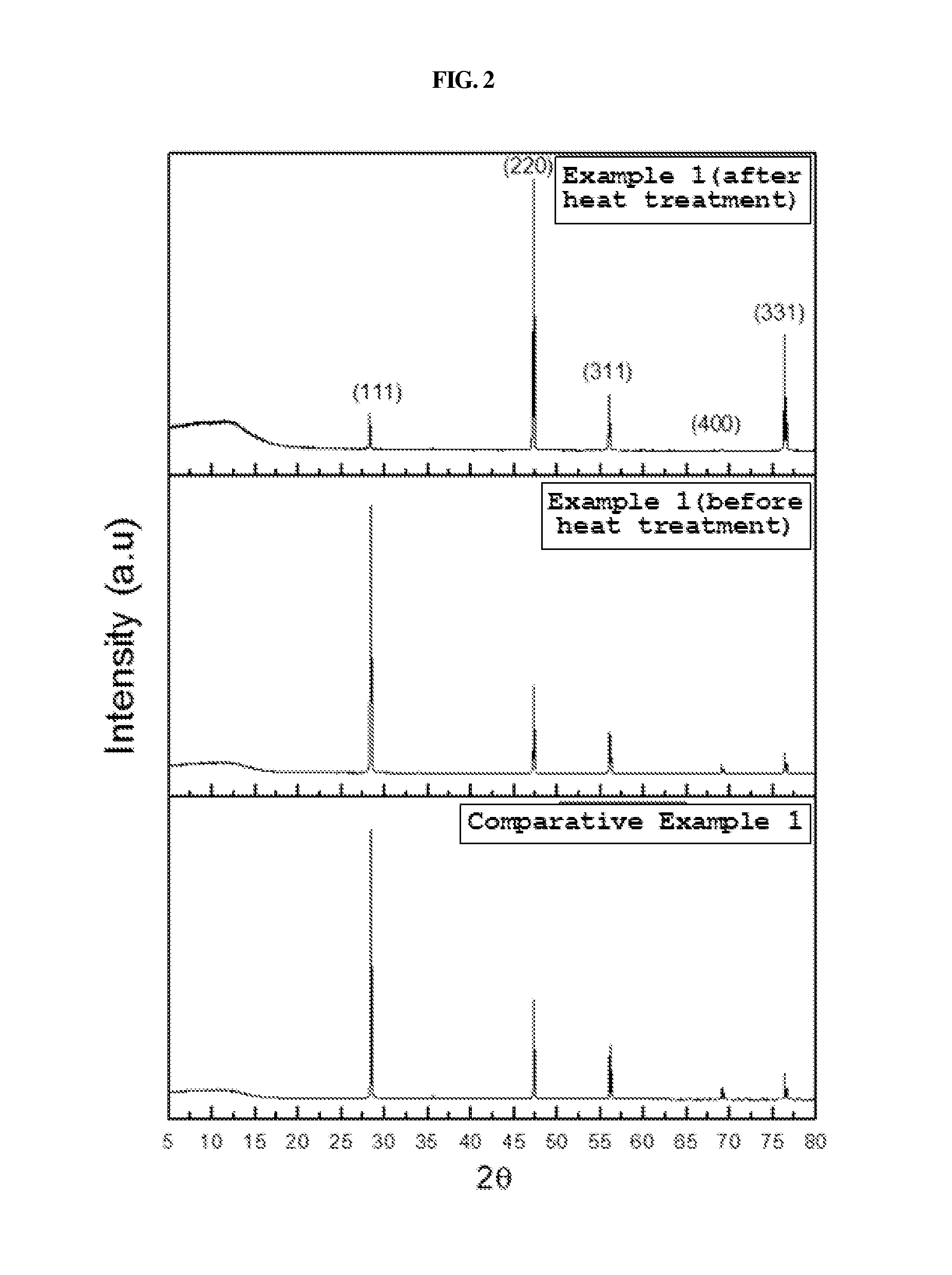

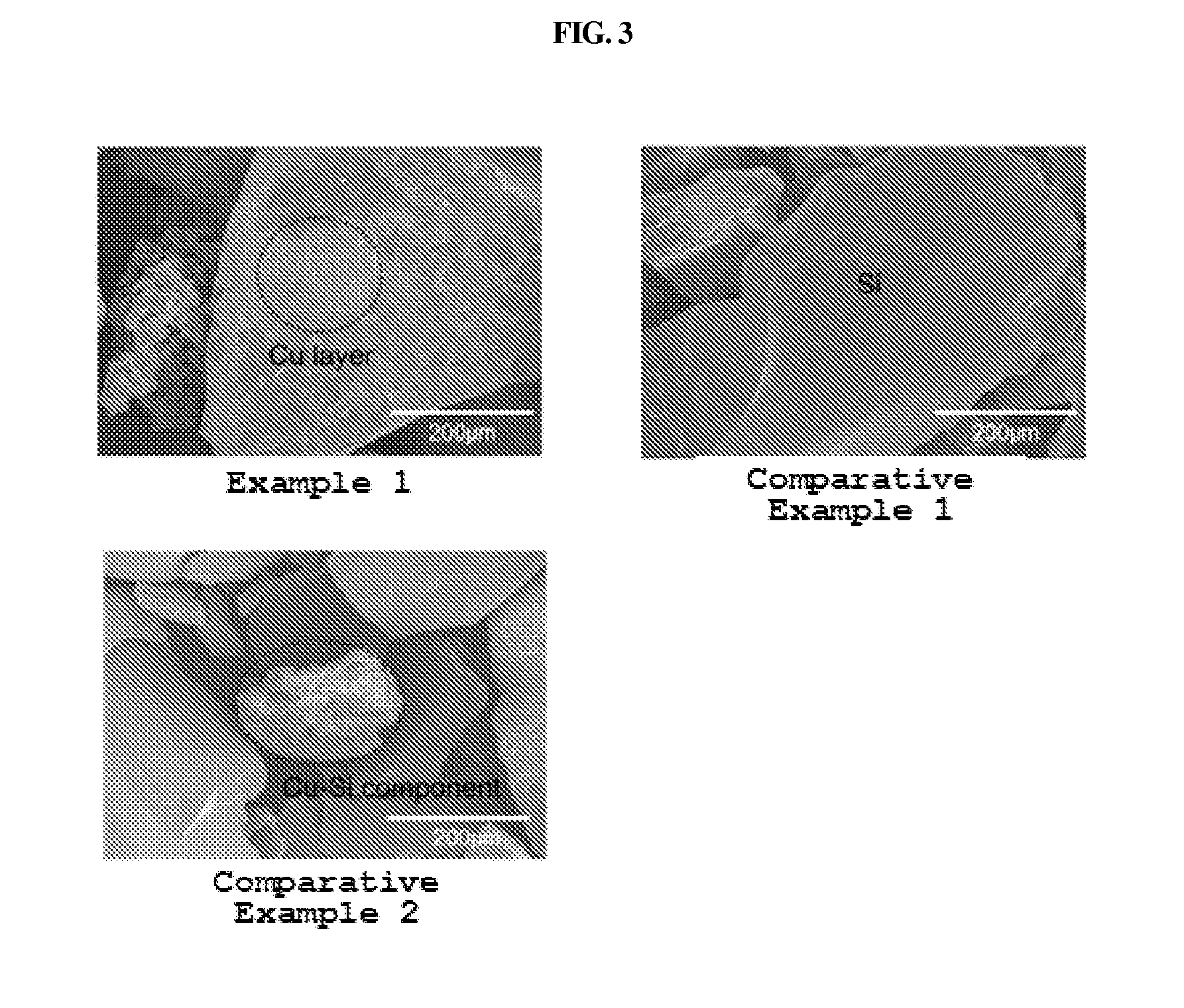

This invention relates to a method of preparing trichlorosilane, which enables trichlorosilane to be obtained at improved yield using silicon having copper silicide uniformly formed thereon, by uniformly distributing and applying a copper compound on the surface of silicon and then performing heat treatment.

Owner:HANWHA CHEMICAL CORPORATION

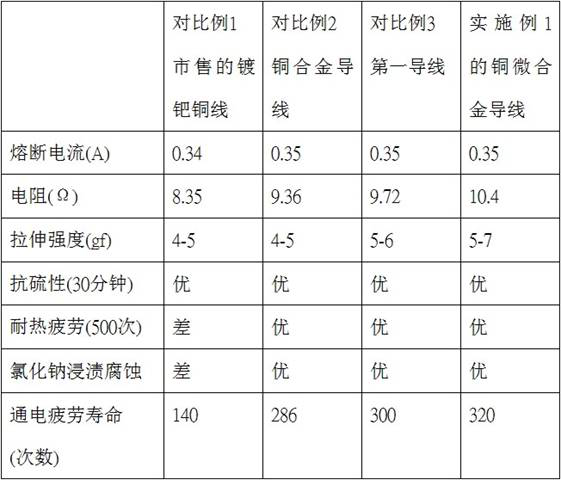

Copper microalloy, copper microalloy wire and preparation methods of copper microalloy and copper microalloy wire

ActiveCN113046593AHigh tensile strengthImprove antioxidant capacityConductive materialMetal/alloy conductorsPlatinumCopper wire

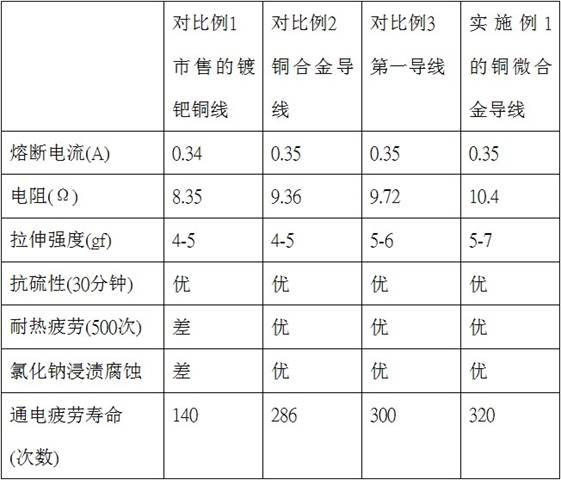

A copper microalloy is prepared from the components including, by weight, 0.5%-0.7% of palladium, 0.3%-0.5% of gold, 0.1%-0.3% of silver, 0.05%-0.2% of platinum, 0.05%-0.1% of phosphorus, 0.05%-0.1%of silicon and the balance copper. In the copper microalloy, phosphorus exists in the form of copper phosphide (Cu3P2), and silicon exists in the form of copper silicide (Cu5Si). The invention further provides a copper microalloy wire which is manufactured from the copper microalloy through a wire drawing technology. The invention further provides preparation methods of the copper microalloy and the copper microalloy wire. The copper microalloy wire has good conductivity, high corrosion resistance (the corrosion resistance is higher than that of a pure copper wire), and excellent mechanical strength and electrical fatigue characteristics. The tensile strength of the copper microalloy wire is 5-7 gf, and the power-on fatigue life of the copper microalloy wire is greater than 300 times.

Owner:NICHE TECH KAISER SHANTOU

Method for preparing trichlorosilane

InactiveUS20150329367A1Increase productionHeat treatmentsMetal silicidesCopper silicideTrichlorosilane

The present invention relates to a method for preparing trichlorosilane. According to the method for preparing trichlorosilane of the present invention, trichlorosilane may be obtained with improved yield using silicon where copper silicide is formed.

Owner:HANWHA CHEMICAL CORPORATION

Copper microalloy, copper microalloy wire and preparation method thereof

ActiveCN113046593BHigh tensile strengthImprove antioxidant capacityConductive materialMetal/alloy conductorsPlatinumCopper wire

A copper microalloy containing by weight: palladium 0.5-0.7%, gold 0.3-0.5%, silver 0.1-0.3%, platinum 0.05-0.2%, phosphorus 0.05-0.1%, silicon 0.05-0.1%, and the balance is copper. In the copper microalloy, phosphorus is copper phosphide (Cu 3 P 2 ) exists in the form of silicon as copper silicide (Cu 5 Si) exists in the form. The present invention also provides a copper micro-alloy wire, which is made by using the above-mentioned copper micro-alloy through drawing process. The present invention also provides a preparation method for the above-mentioned copper microalloy and copper microalloy wire. The copper micro-alloy wire of the invention has good electrical conductivity and high corrosion resistance (more corrosion resistance than pure copper wire), and excellent mechanical strength and electrical fatigue properties. The copper micro-alloy wire of the present invention has a tensile strength of 5-7gf and a fatigue life of more than 300 times.

Owner:NICHE TECH KAISER SHANTOU

A kind of composite material and its preparation method and application

ActiveCN110396616BReduce production processImprove thermal conductivityCeramicwareCarbide siliconCopper silicide

The invention relates to a composite material and a preparation method and application thereof. The method comprises the following steps: preparing a carbon-coated silicon carbide framework; and filling pores of the carbon-coated silicon carbide framework with copper or a copper alloy. The composite material provided by the invention has low copper silicide content and good thermal conductivity.

Owner:BYD CO LTD

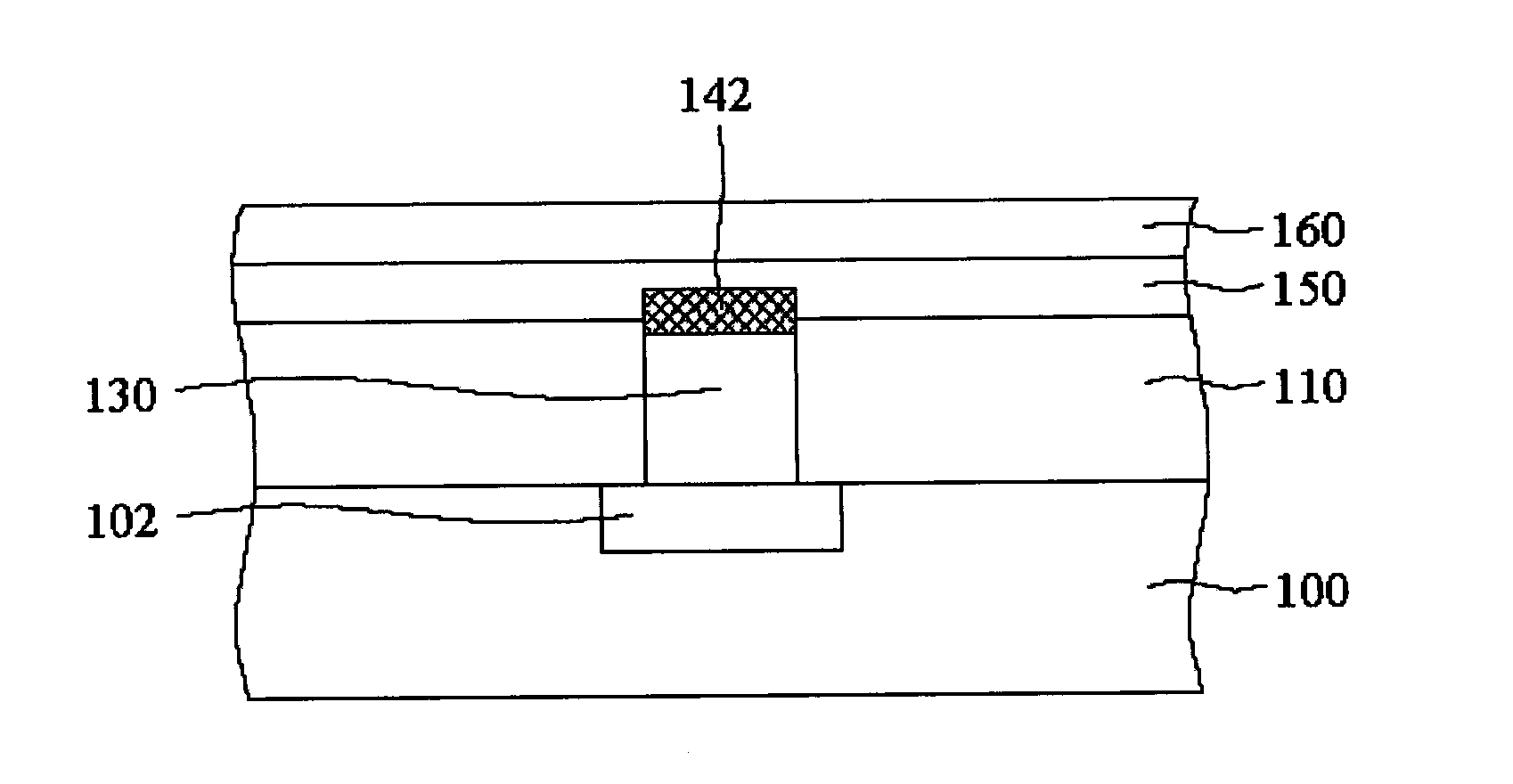

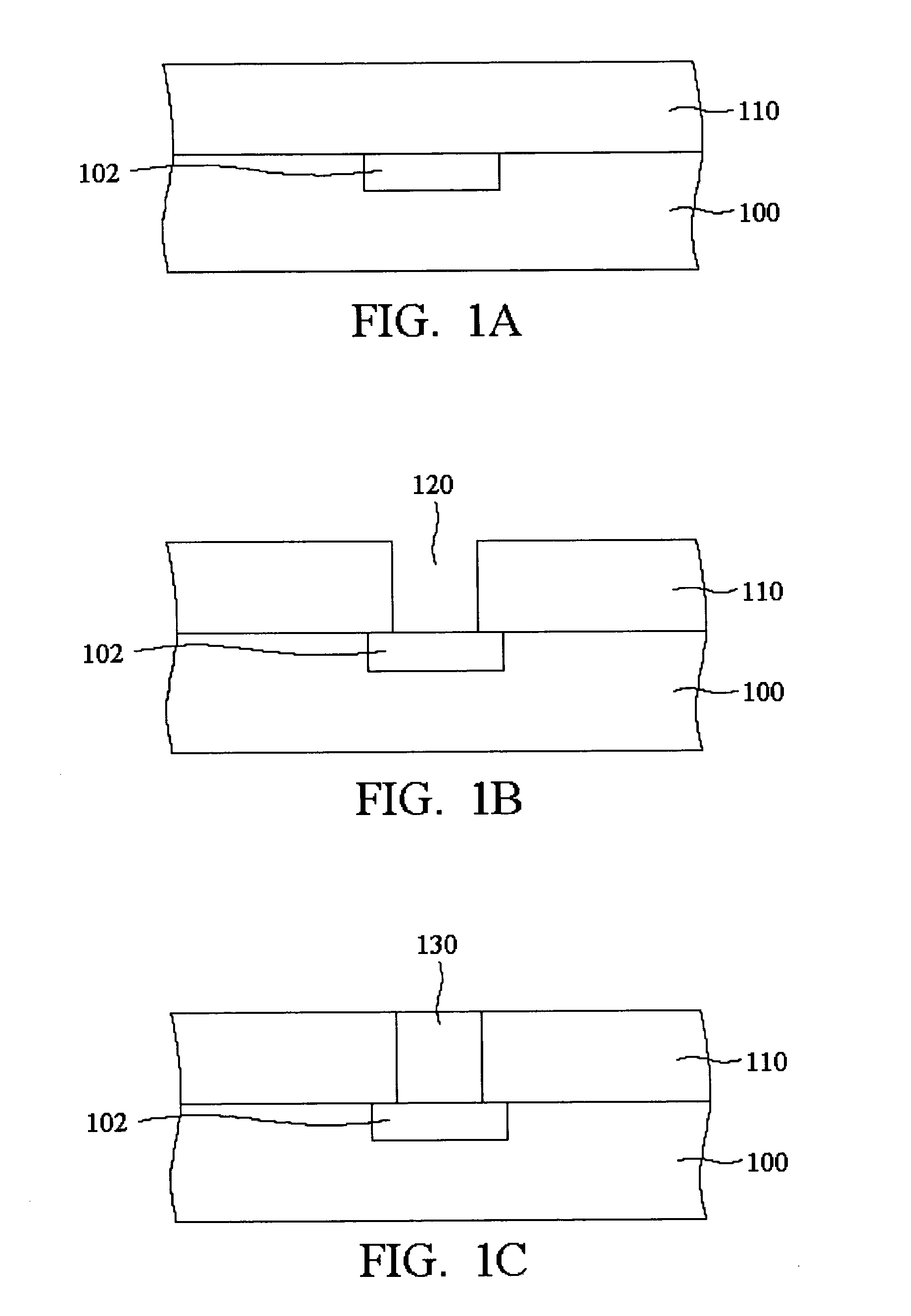

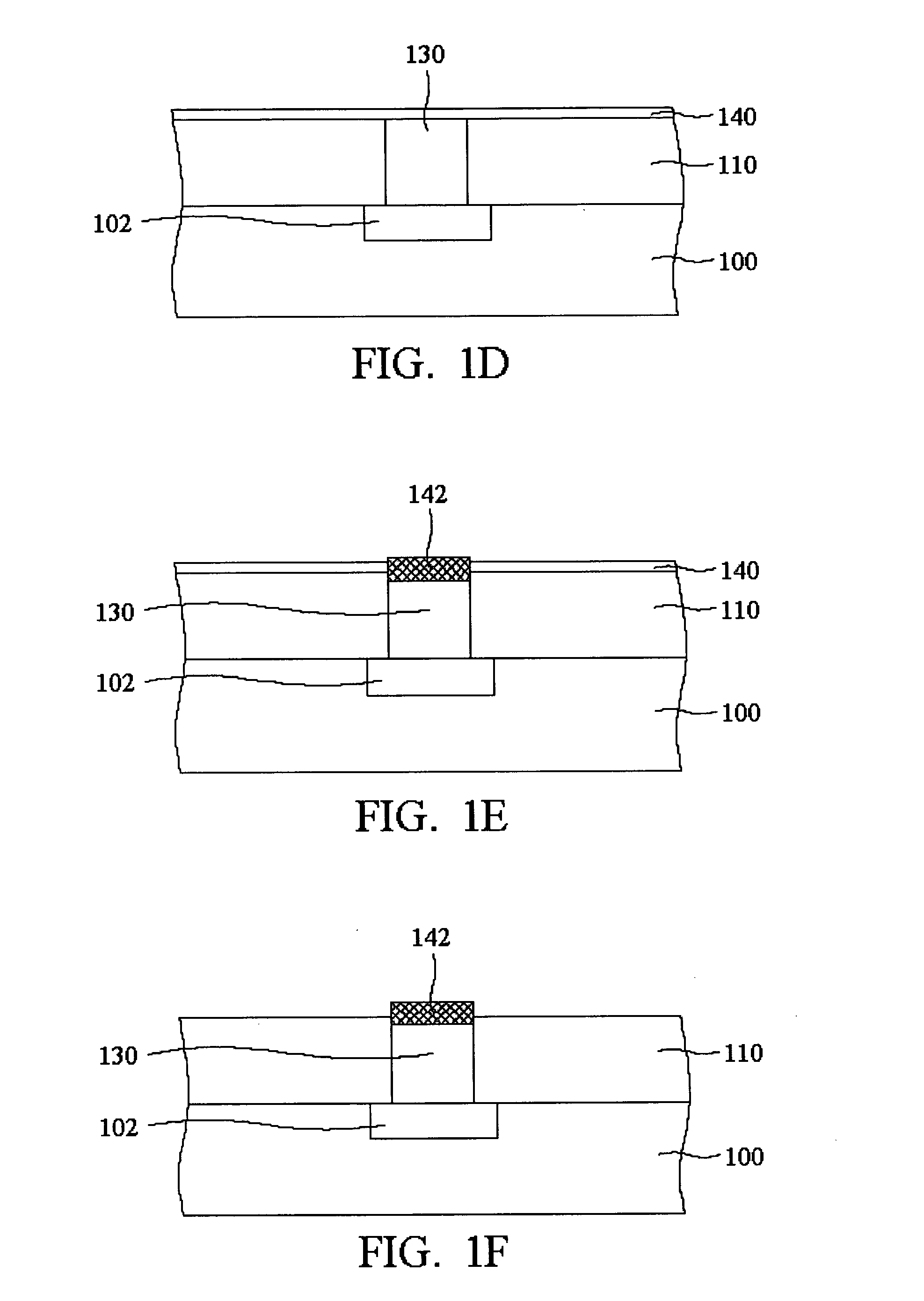

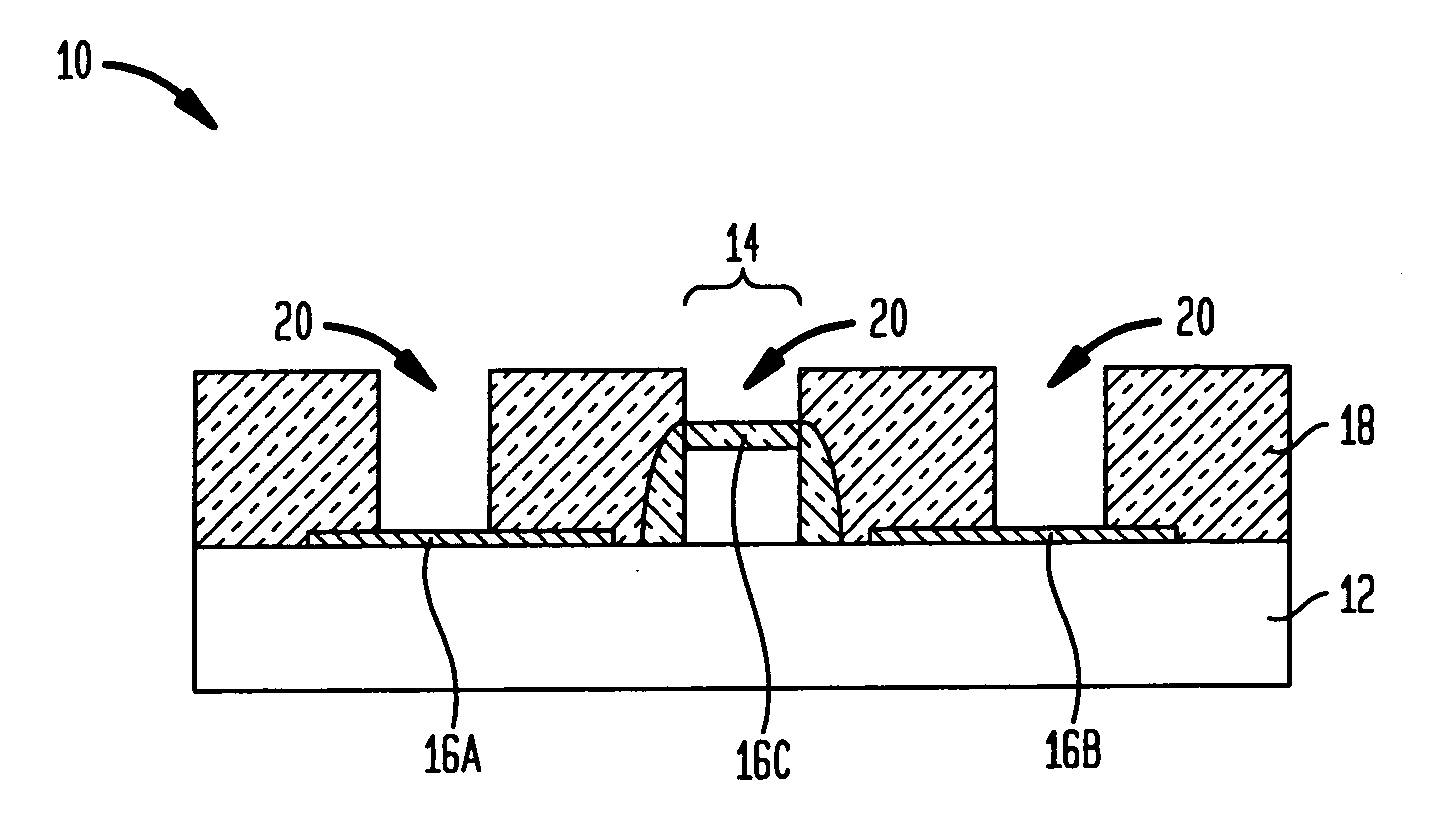

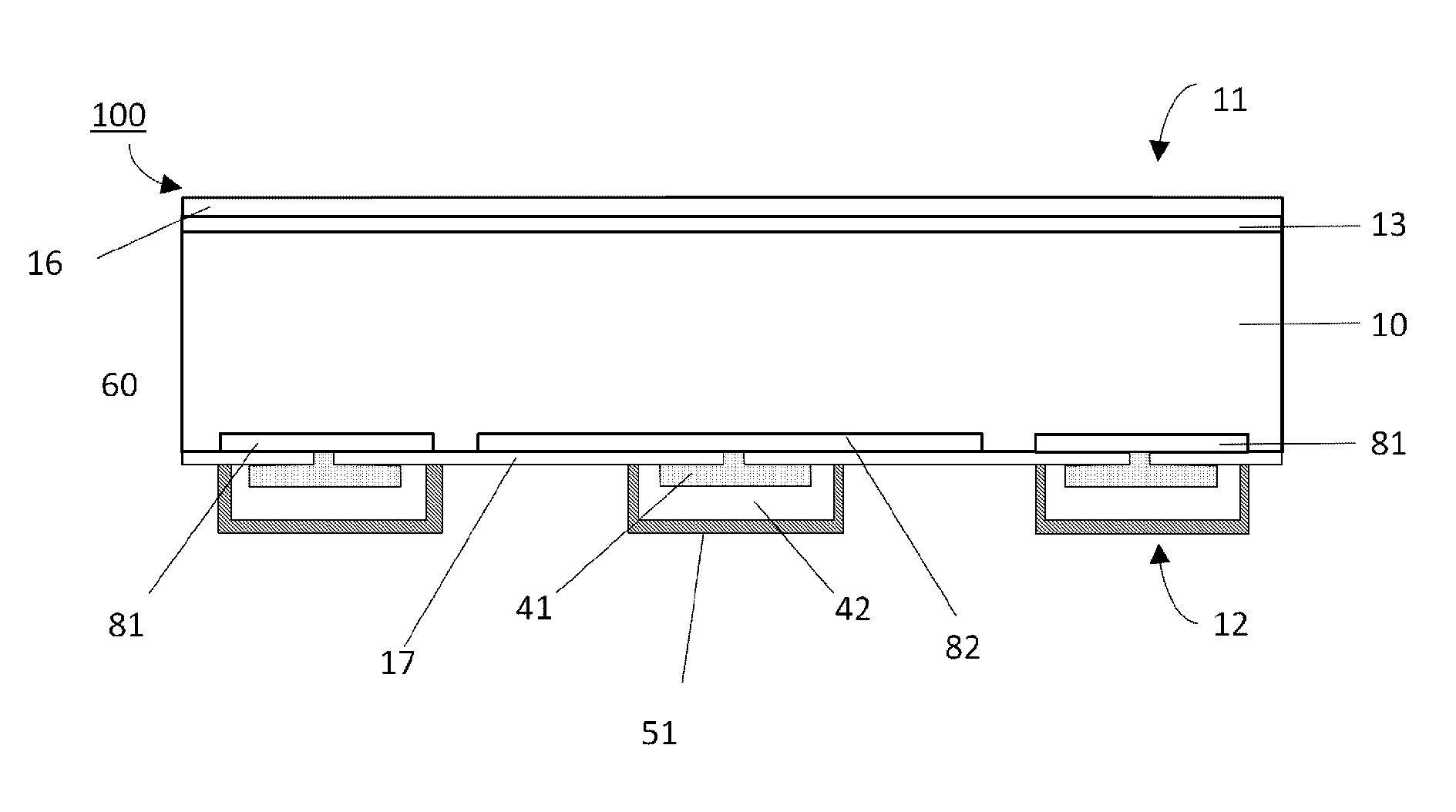

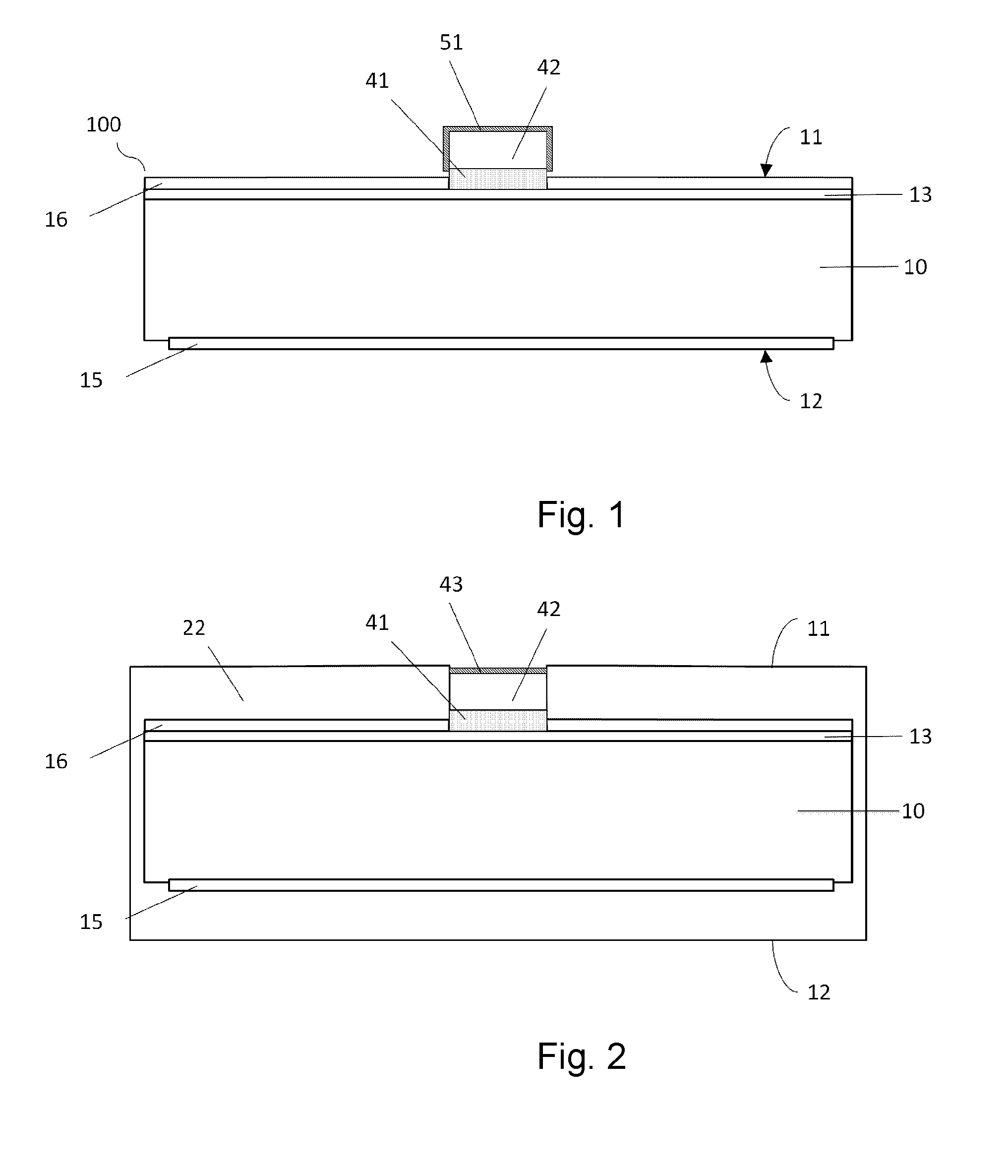

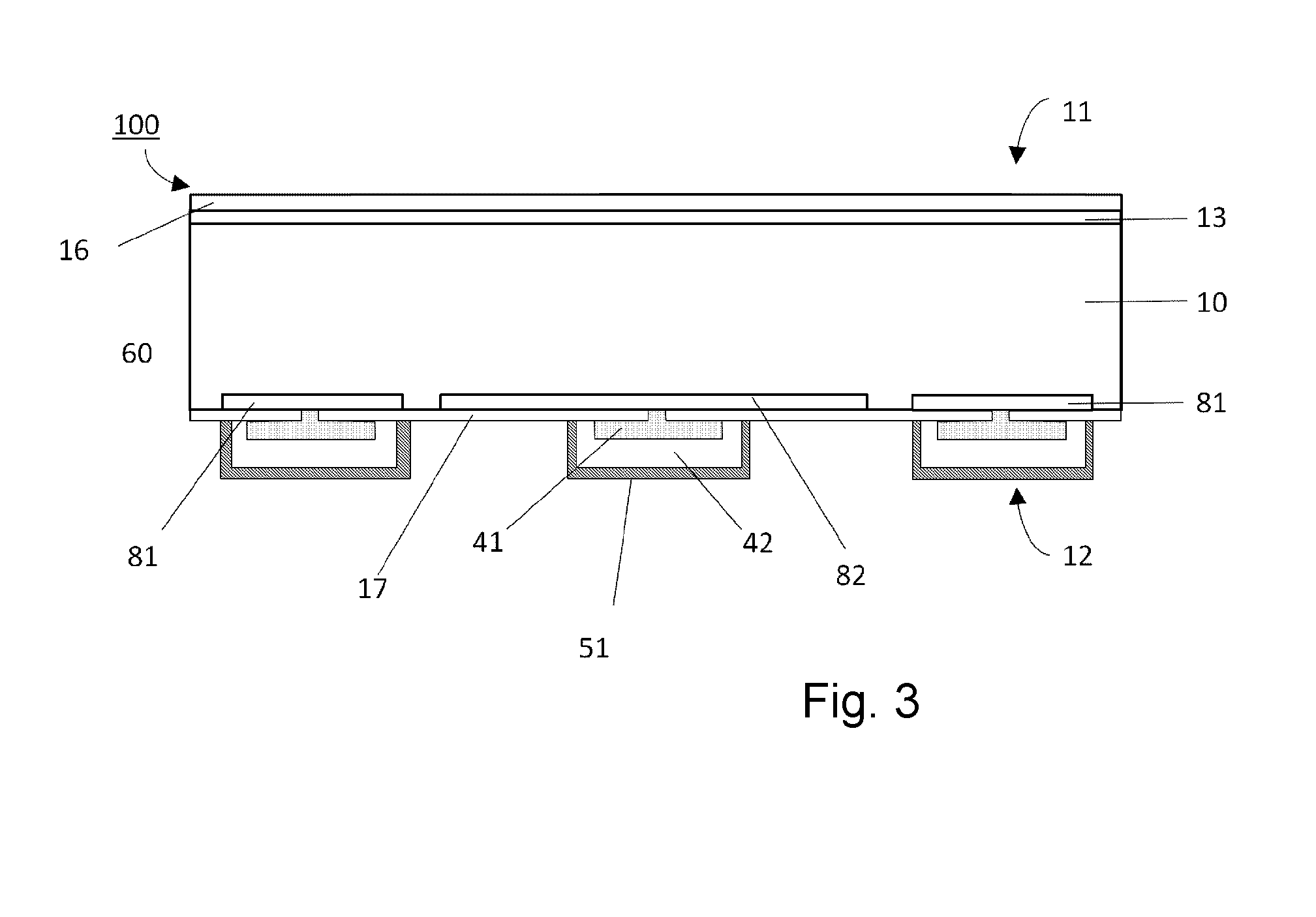

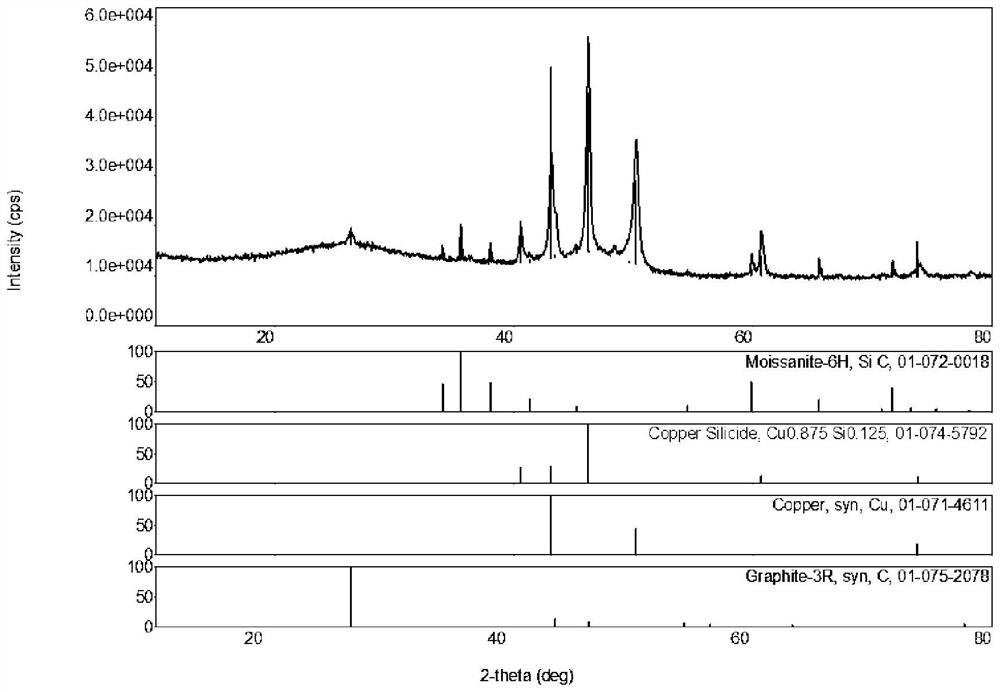

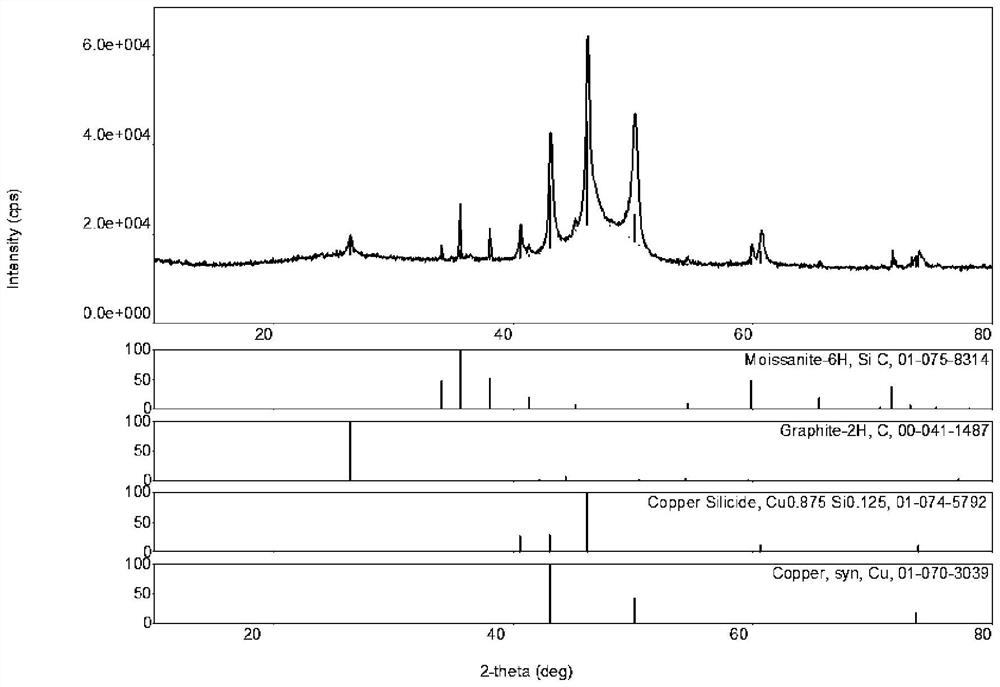

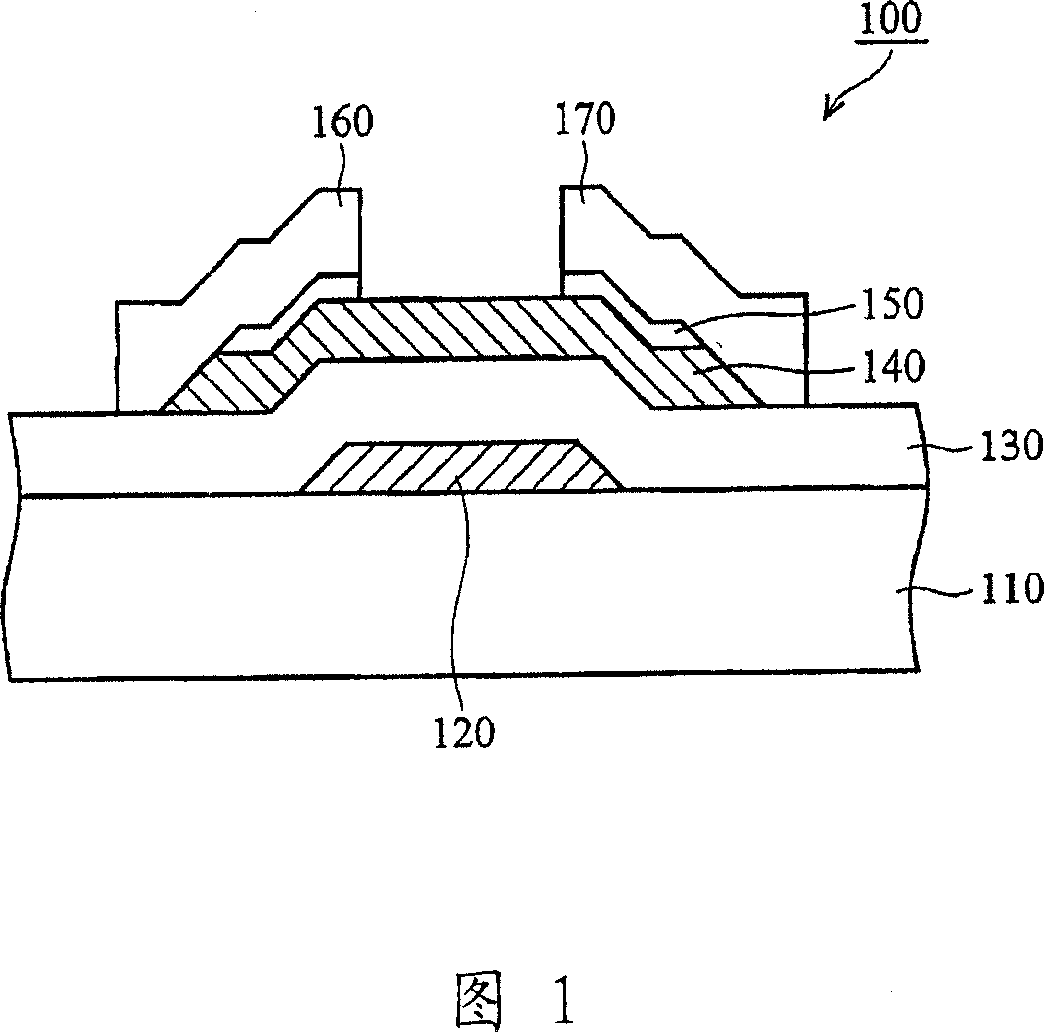

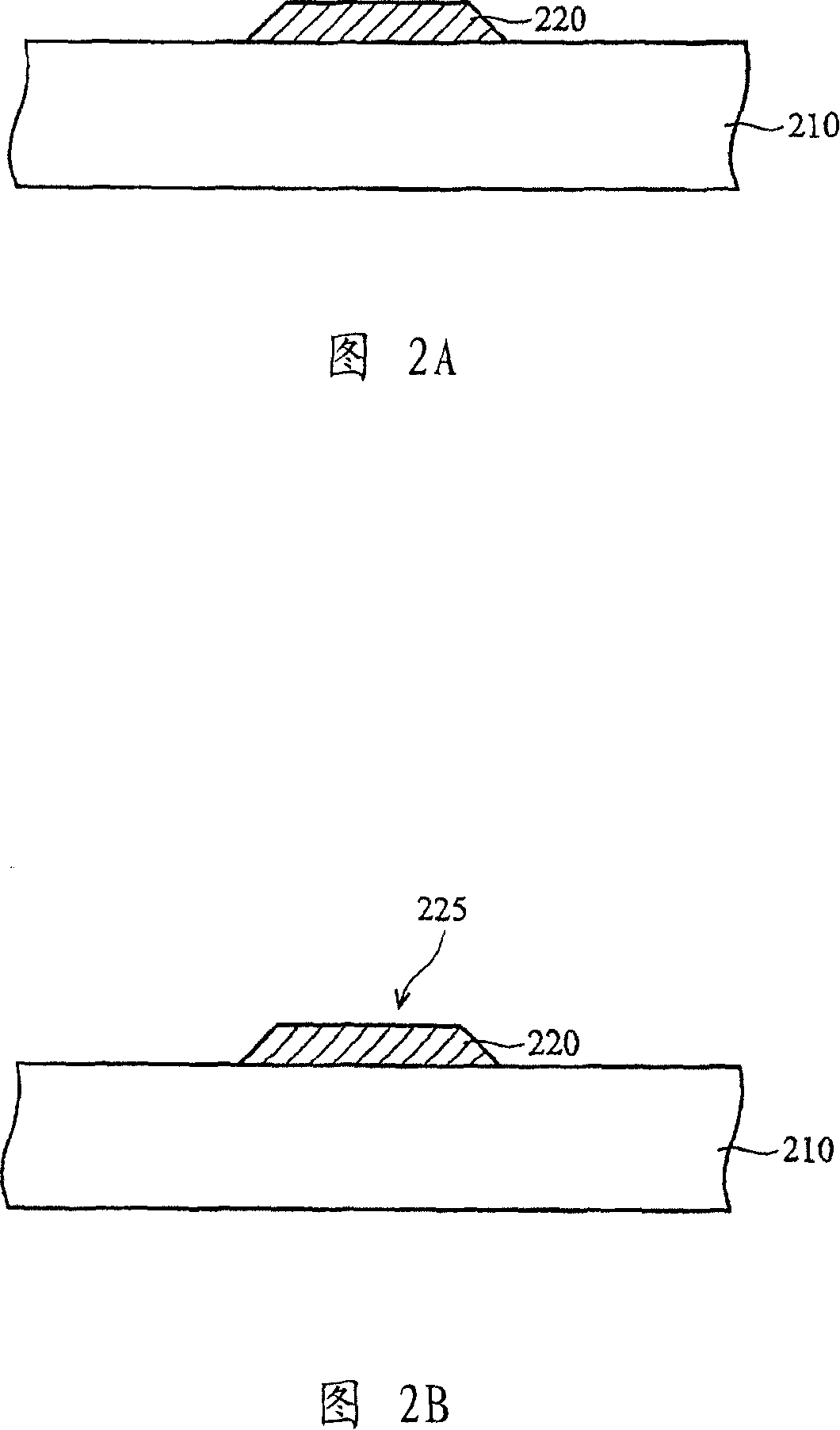

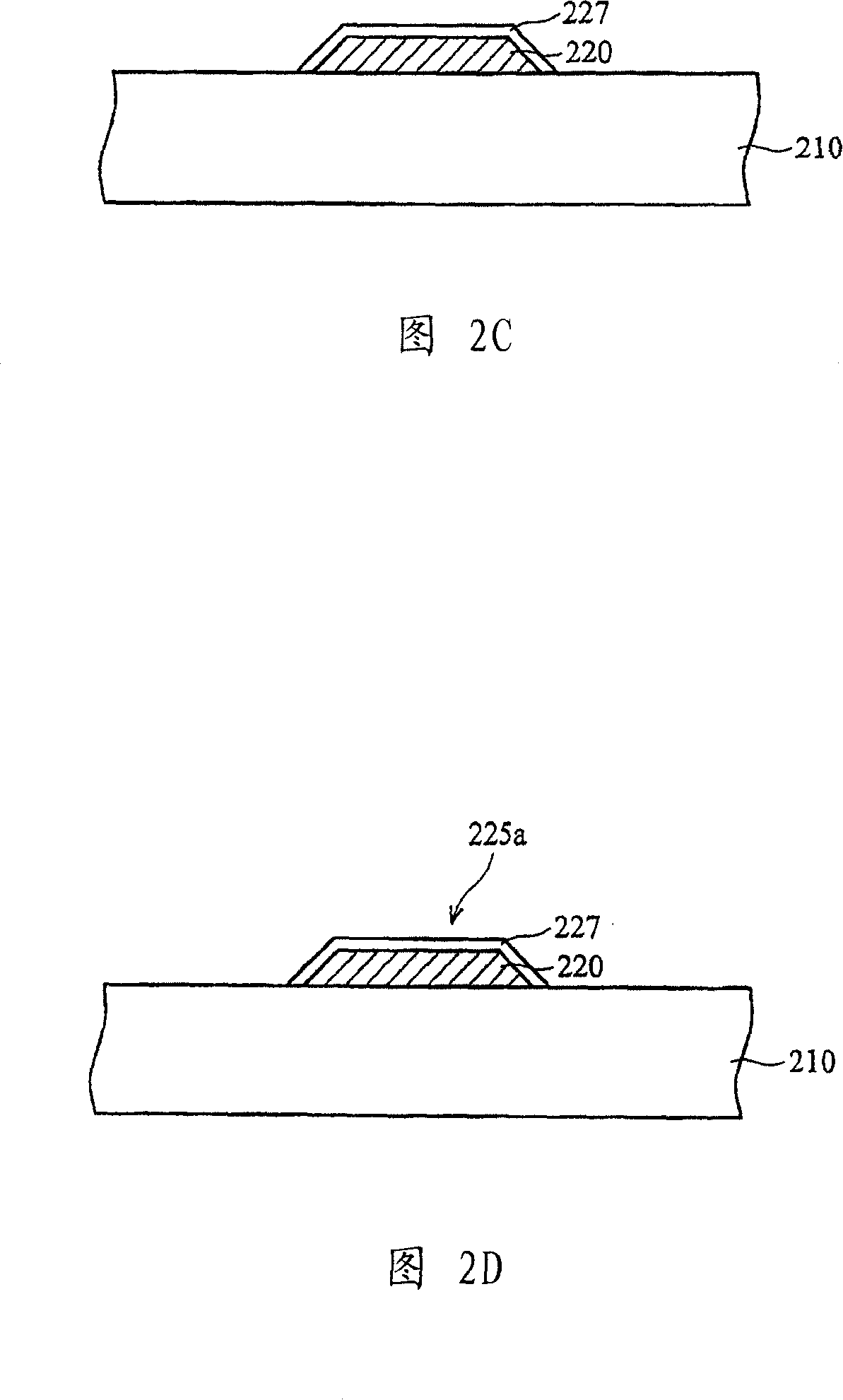

Picture-element electrode switch element and manufacturing method thereof

The method includes steps: forming a gate pole on a base plate; forming a first layer of copper silicide on the gate pole; forming a insulating layer on the first layer of copper silicide; forming a semiconductor layer on the insulating layer; forming a source pole / drain pole on the semiconductor layer. Moreover, the method also includes procedure: forming a second layer of copper silicide on the semiconductor layer, and the second layer of copper silicide is located between the semiconductor layer and the source pole / drain pole.

Owner:AU OPTRONICS CORP