Patents

Literature

104results about How to "Reduce electromigration" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

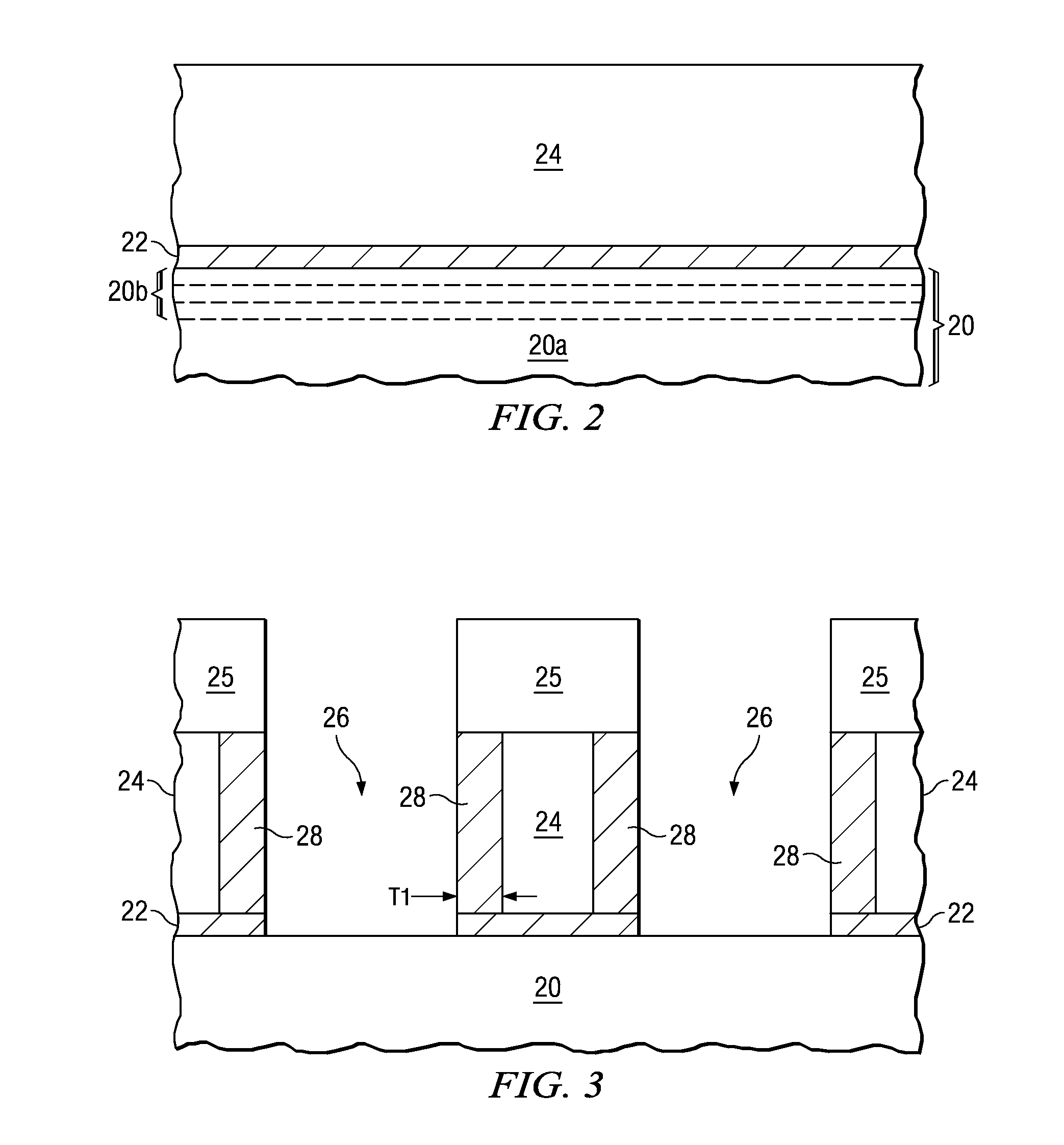

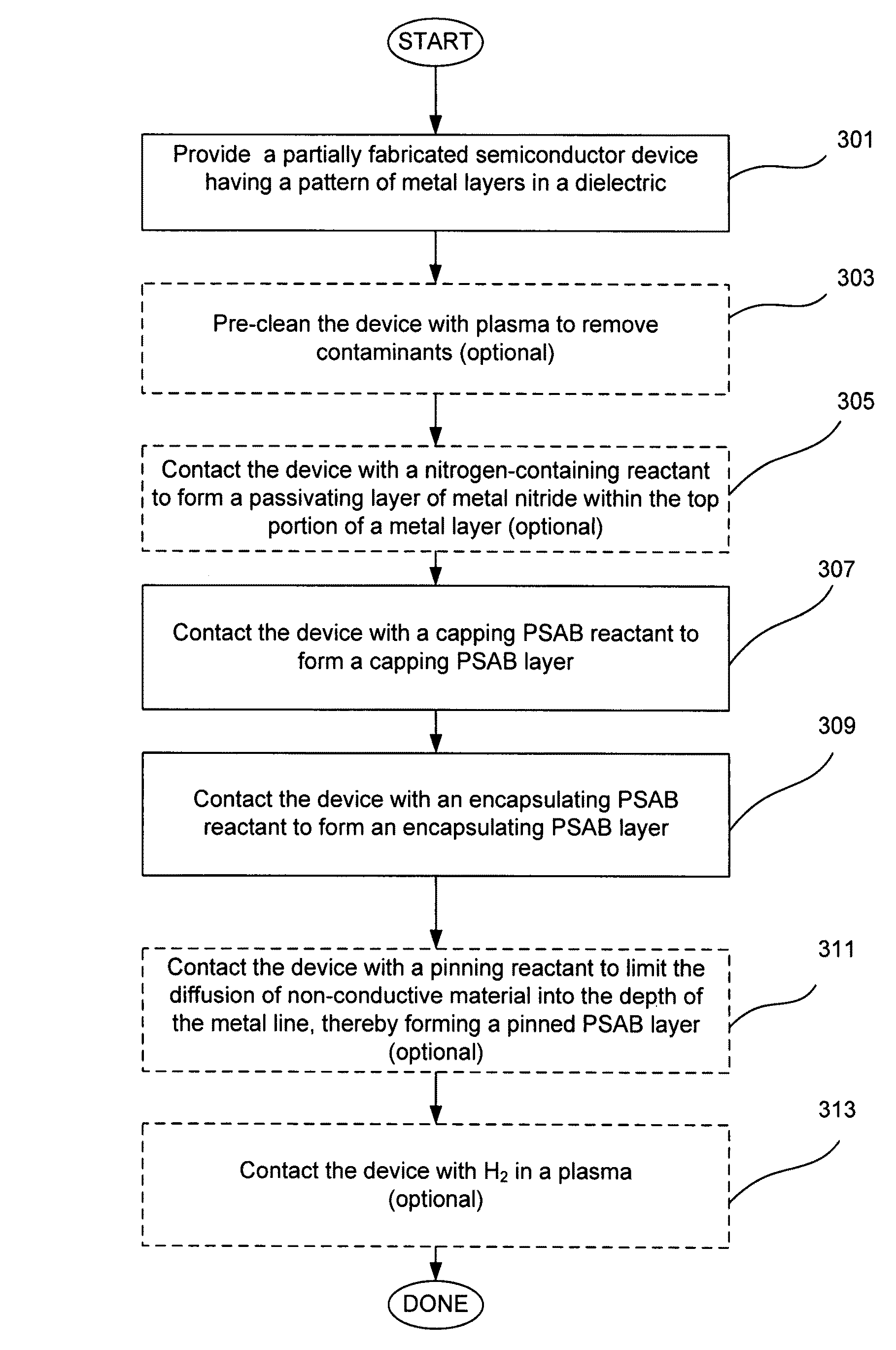

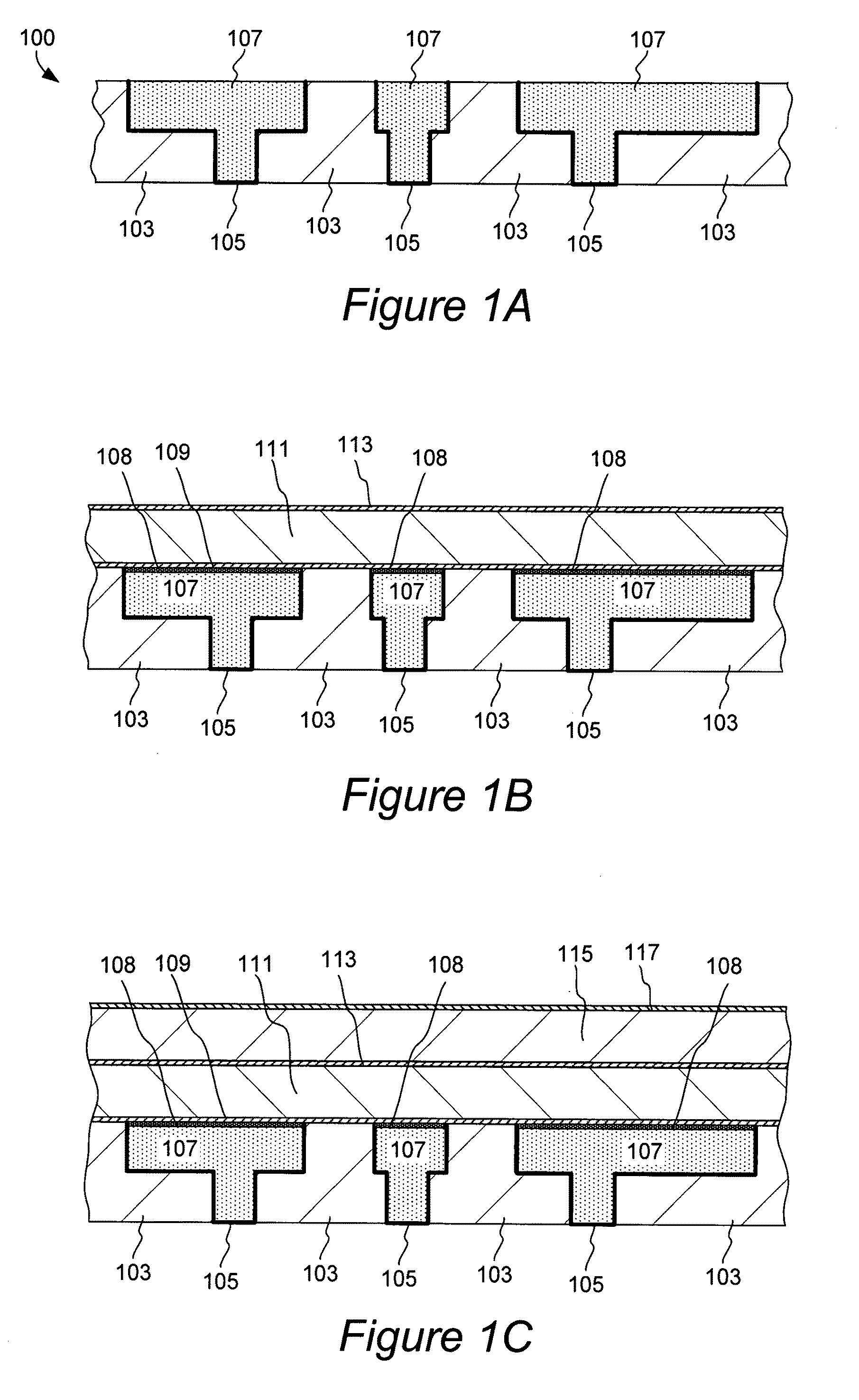

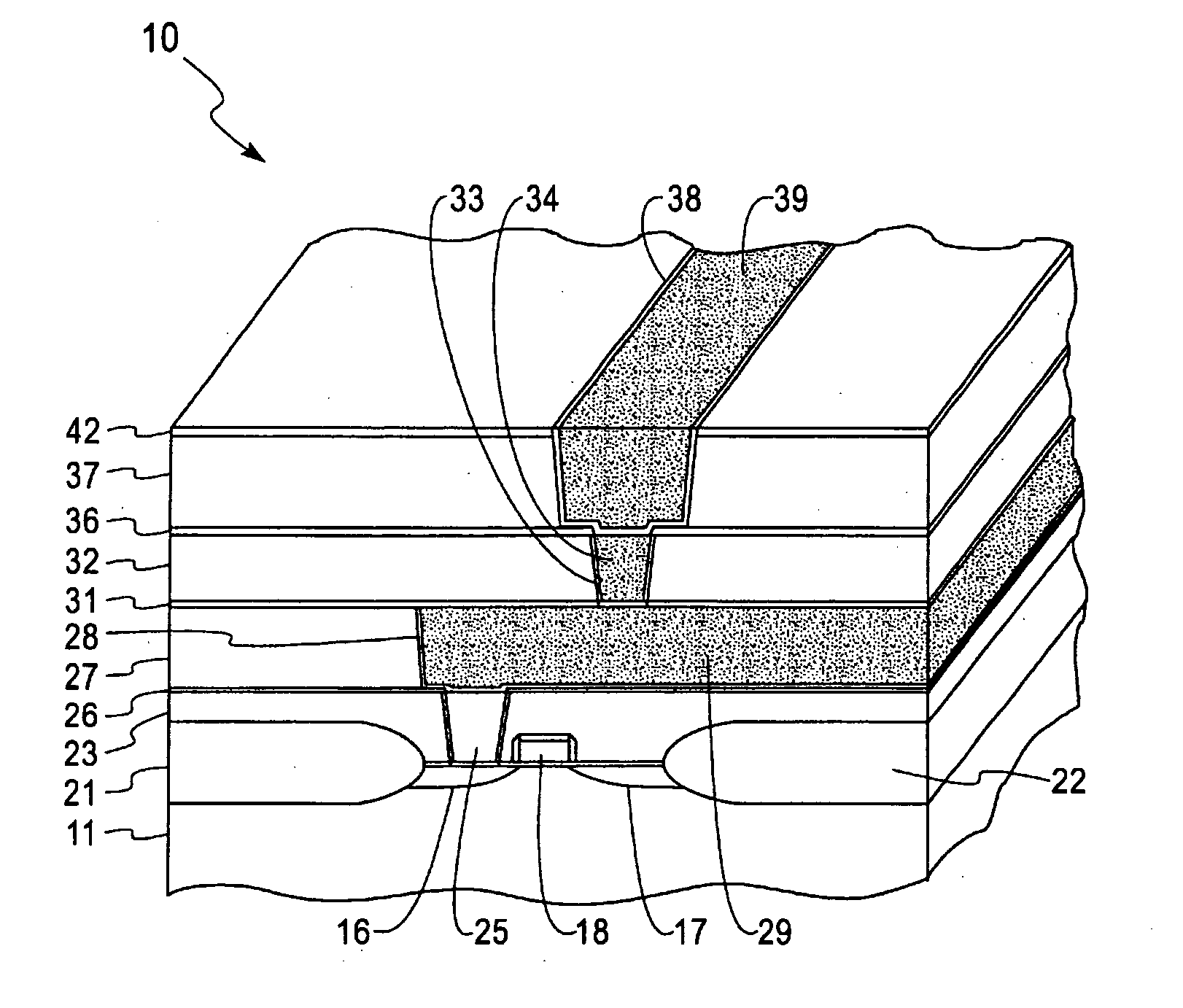

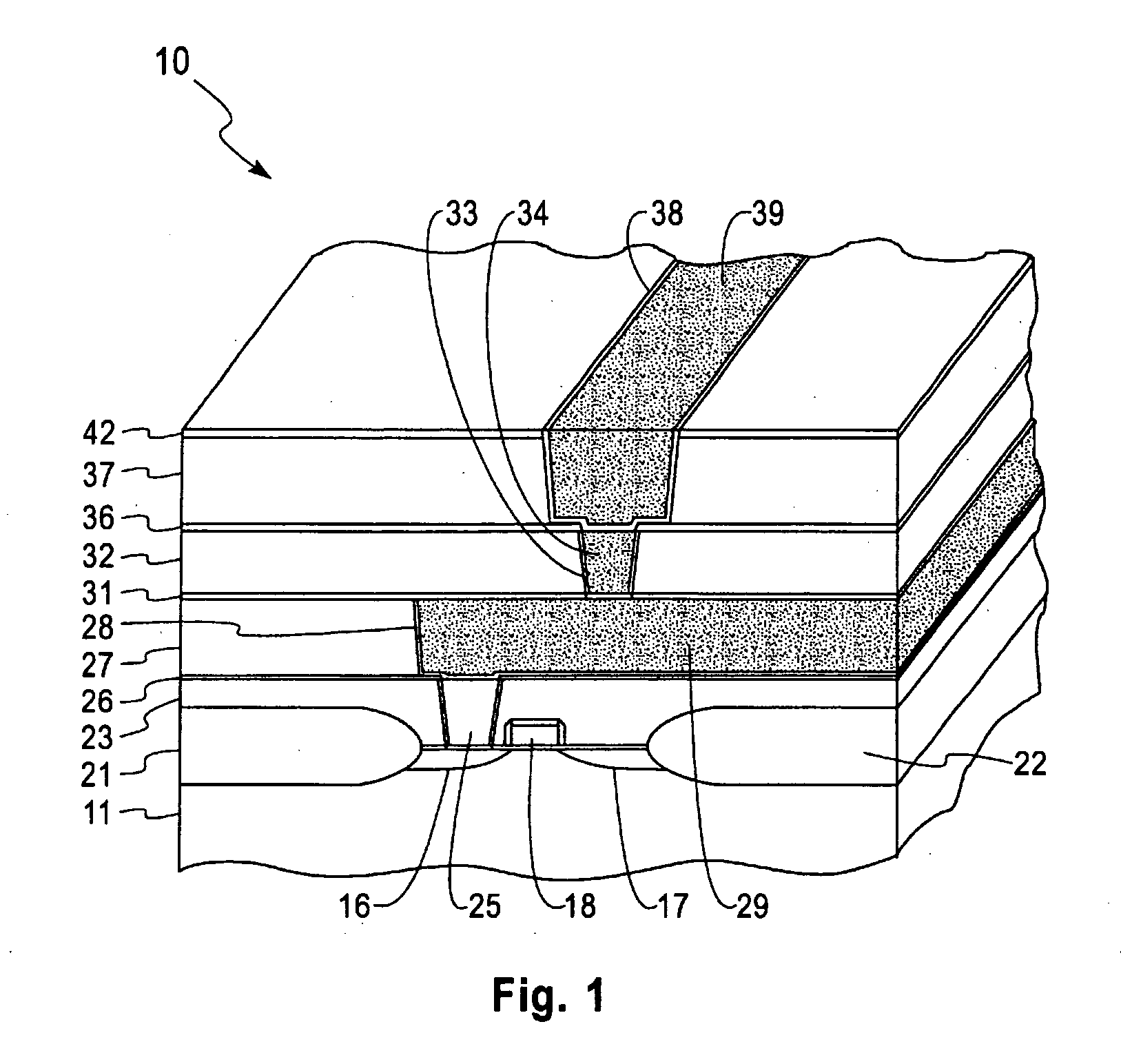

Protective self-aligned buffer layers for damascene interconnects

ActiveUS7727880B1Improving several propertyDecrease in metal electromigrationSemiconductor/solid-state device detailsSolid-state devicesSalicideMetal silicide

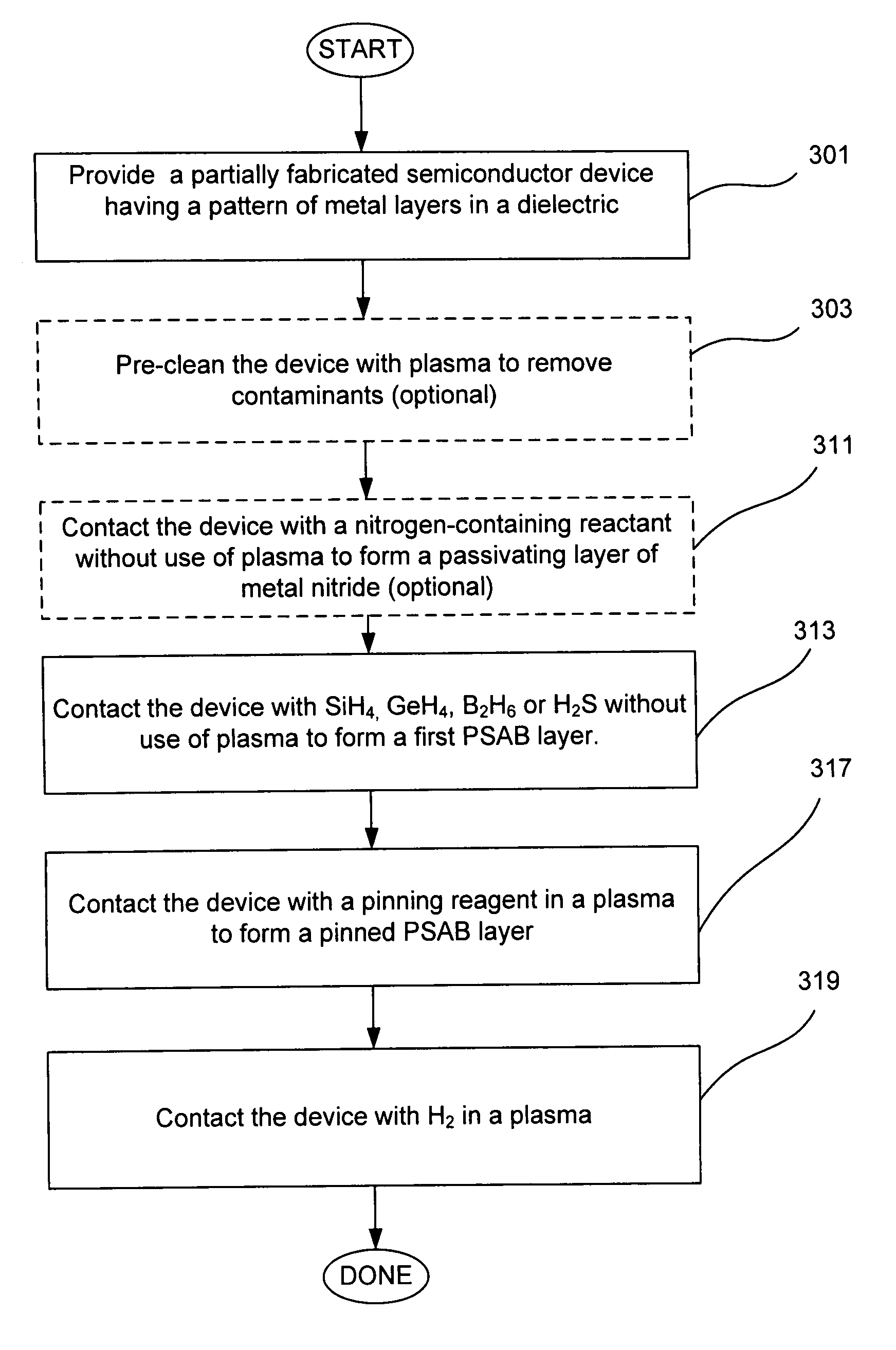

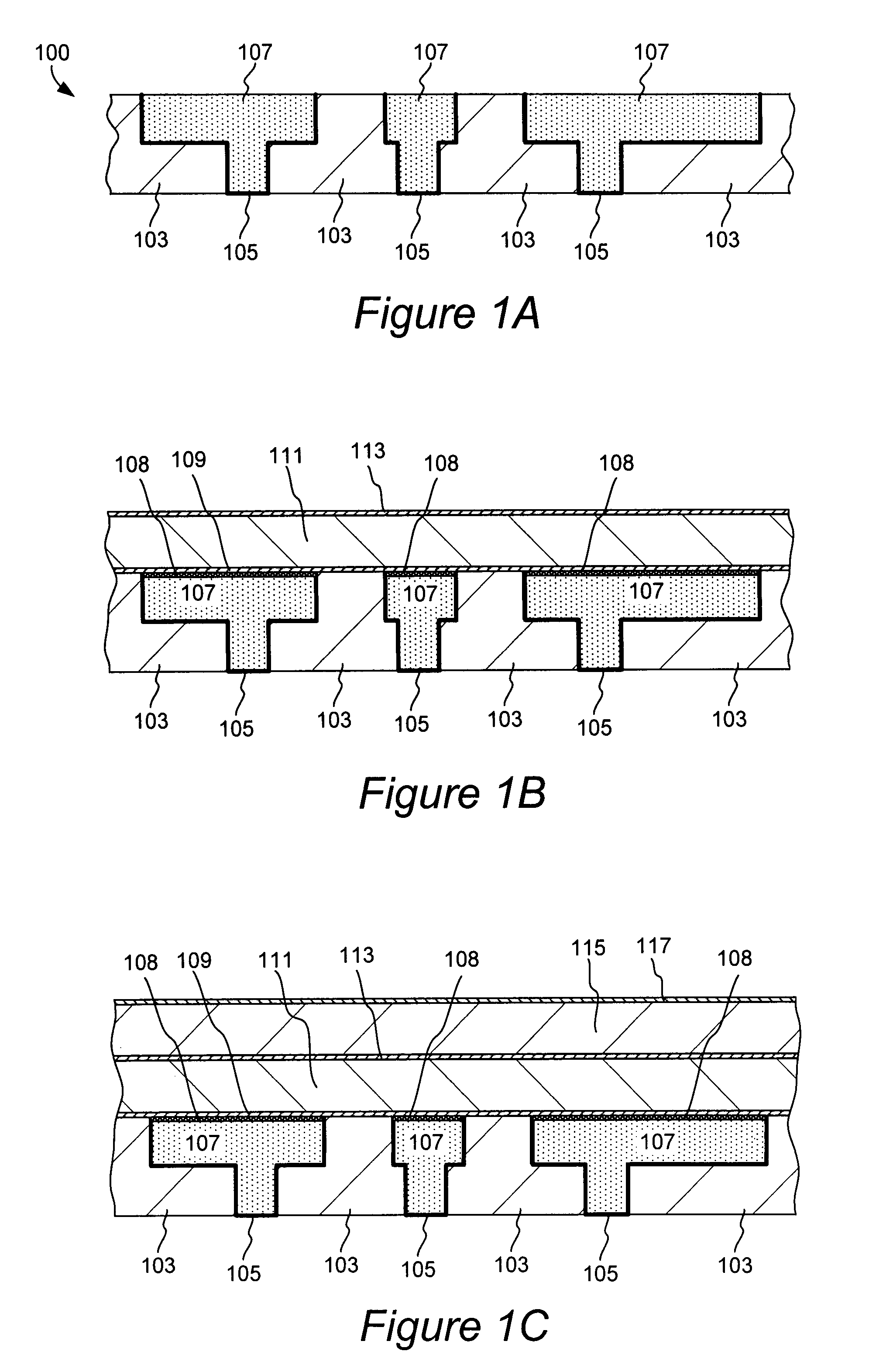

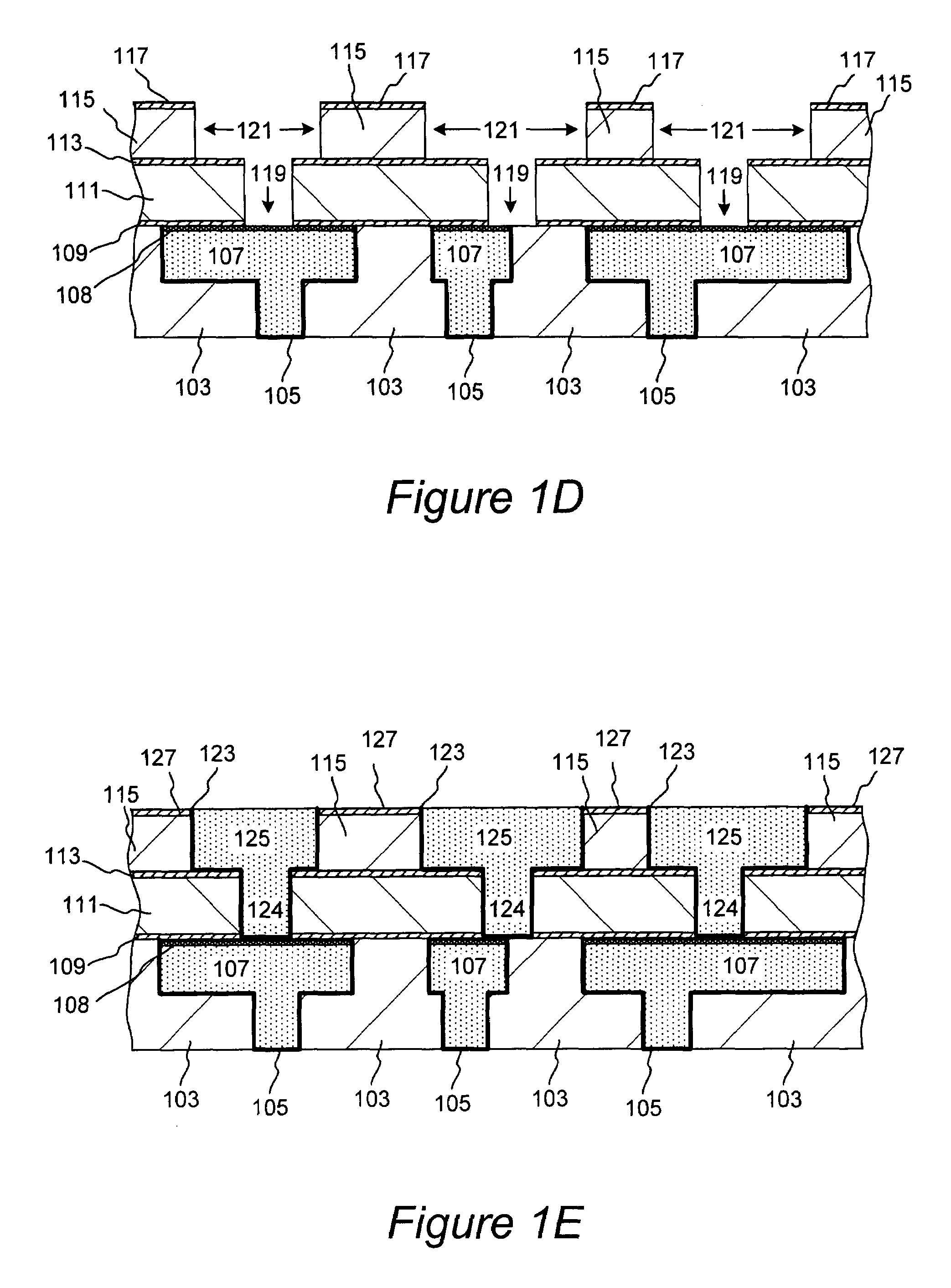

Protective self aligned buffer (PSAB) layers are layers of material that are selectively formed at the surface of metal layers in a partially fabricated semiconductor device. In a Damascene interconnect, PSAB layer typically resides at an interface between the metal layer and a dielectric diffusion barrier layer. PSAB layers promote improved adhesion between a metal layer and an adjacent dielectric diffusion barrier layer. Further, PSAB layers can protect metal surfaces from inadvertent oxidation during fabrication process. A PSAB layer may be formed entirely within the top portion of a metal layer, by, for example, chemically converting metal surface to a thin layer of metal silicide. Thickness of PSAB layers, and, consequently resistance of interconnects can be controlled by partially passivating metal surface prior to formation of PSAB layer. Such passivation can be accomplished by controllably treating metal surface with a nitrogen-containing compound to convert metal to metal nitride.

Owner:NOVELLUS SYSTEMS

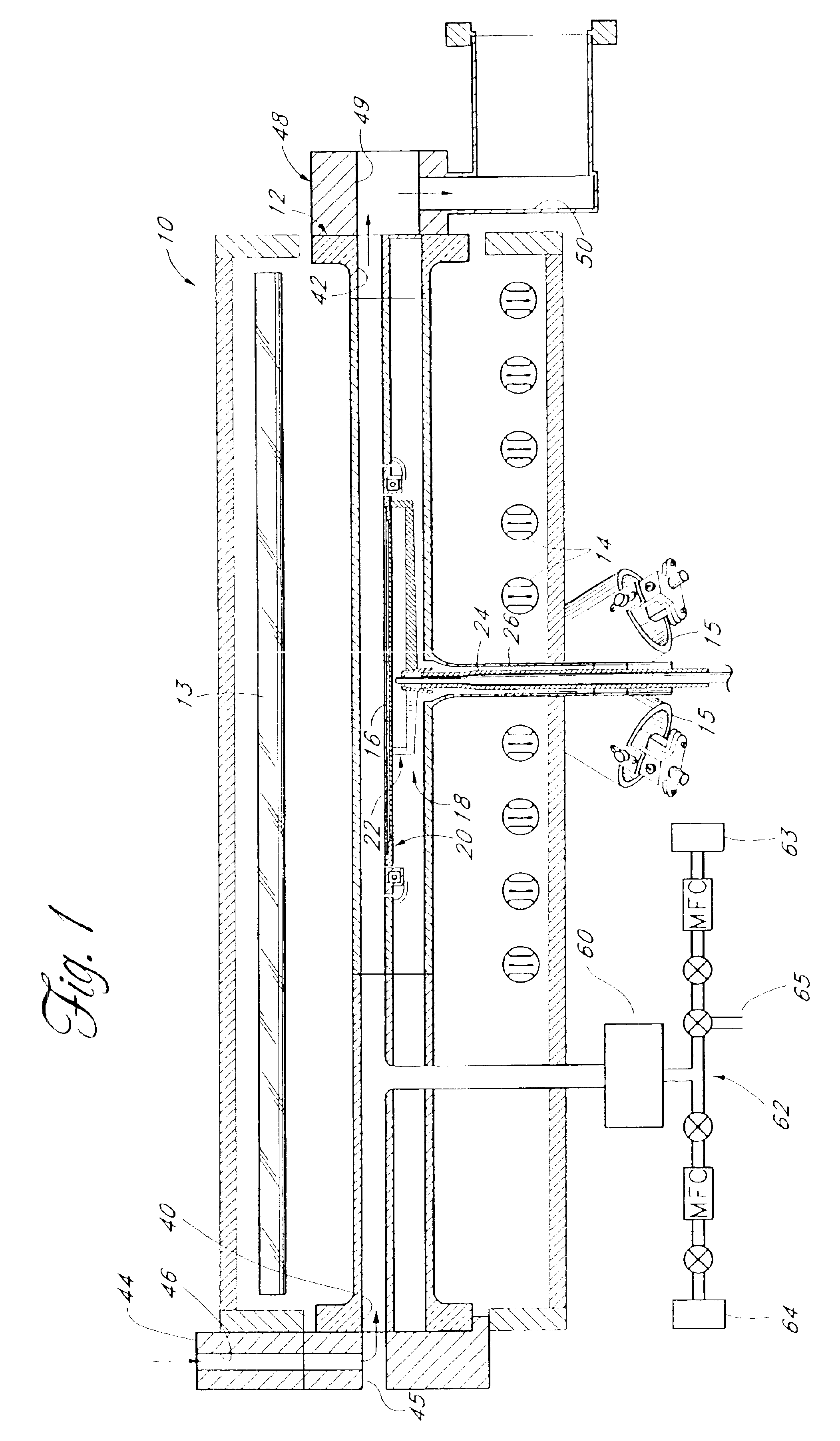

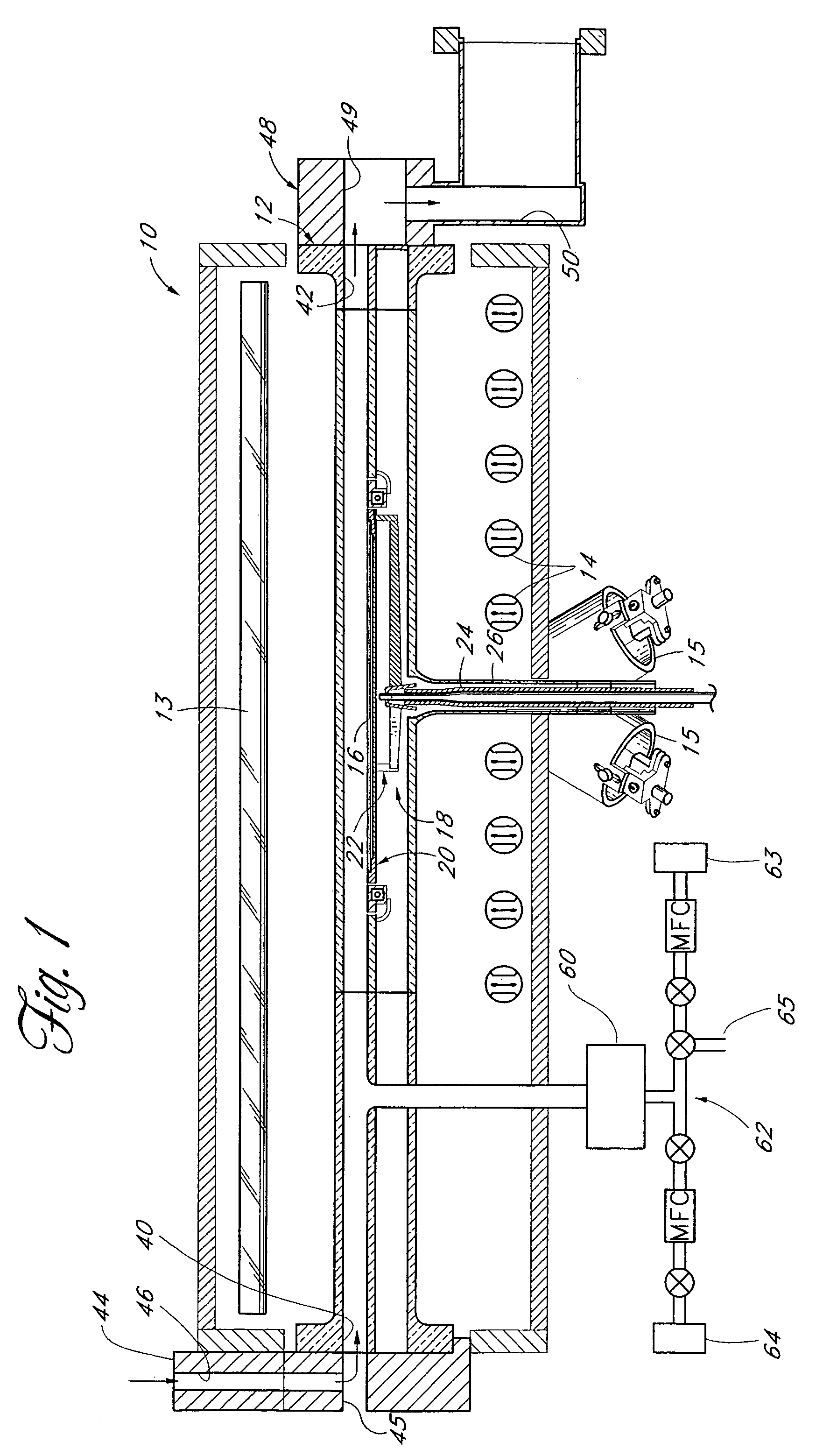

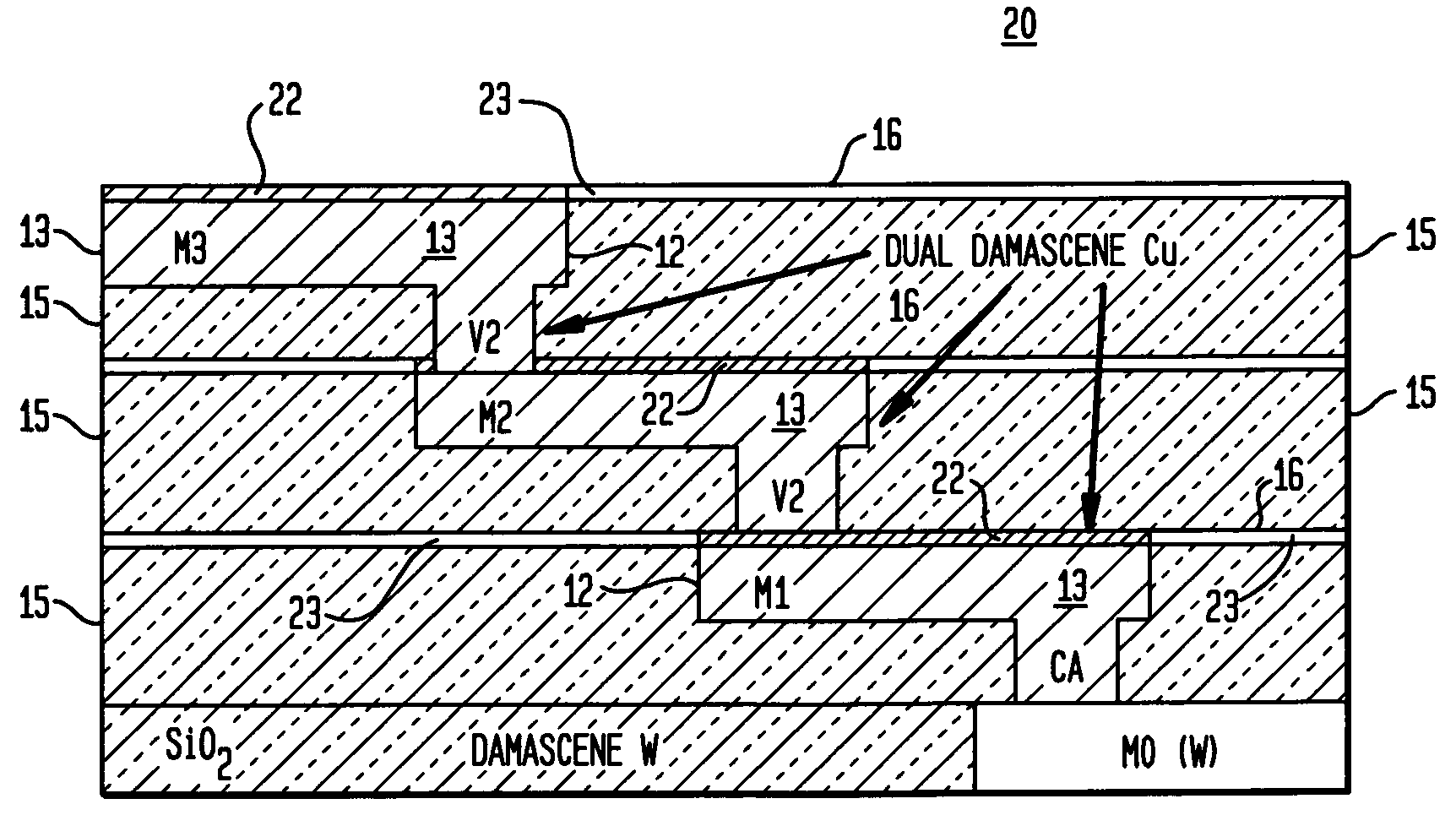

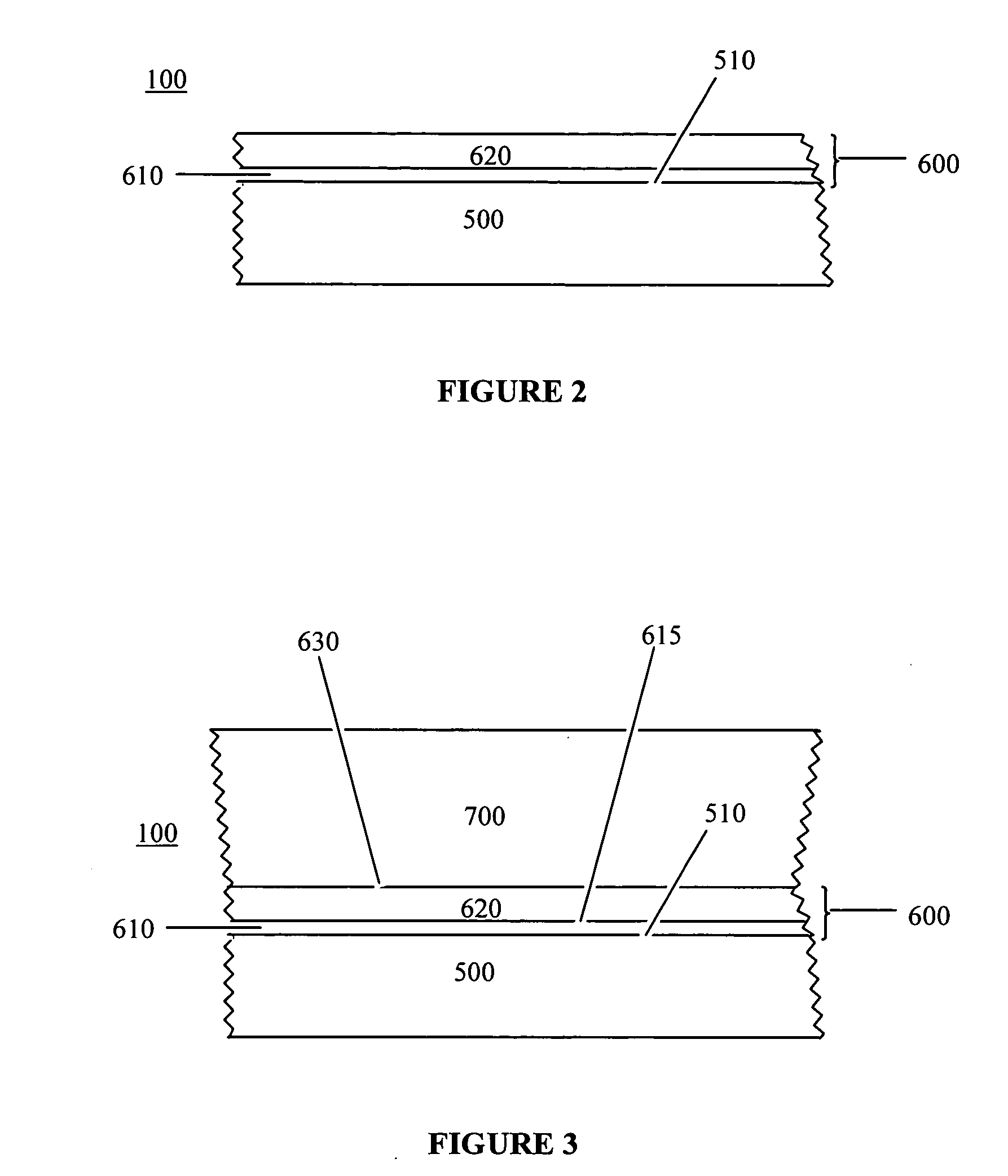

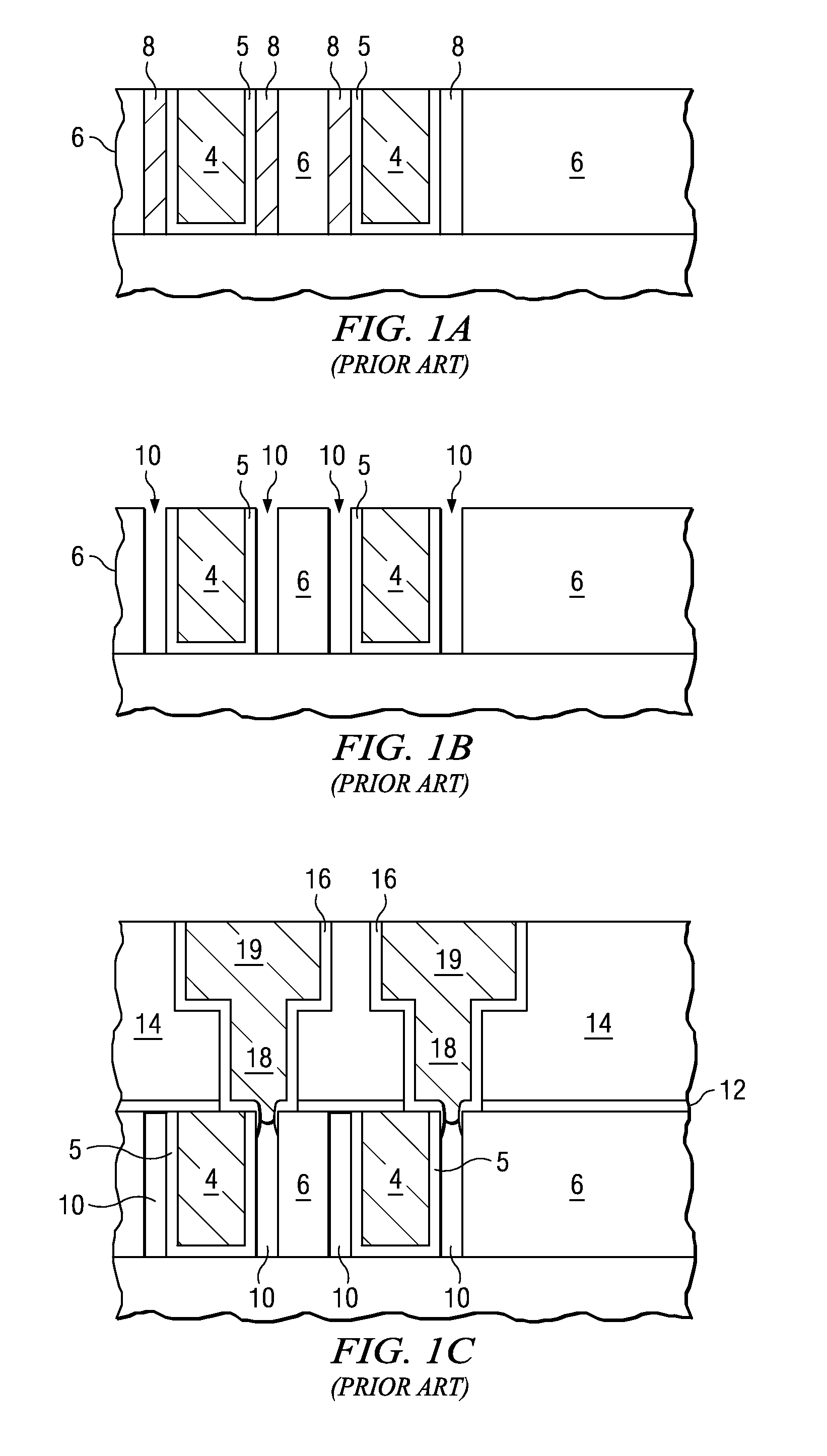

Graded thin films

InactiveUS6933225B2Reduce the temperatureDesirable interface propertySolid-state devicesSemiconductor/solid-state device manufacturingGate dielectricSilicon oxide

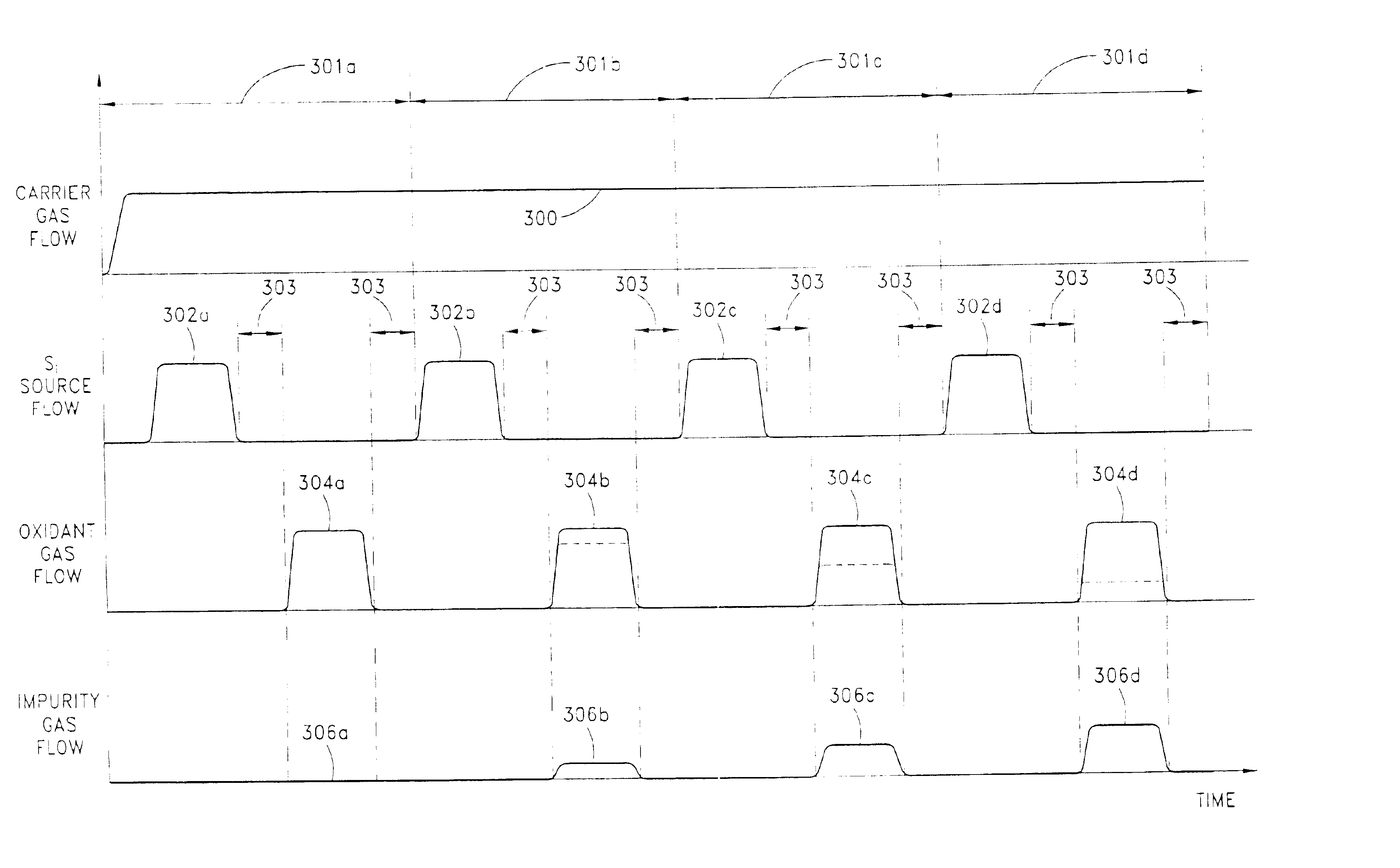

Thin films are formed by atomic layer deposition, whereby the composition of the film can be varied from monolayer to monolayer during cycles including alternating pulses of self-limiting chemistries. In the illustrated embodiments, varying amounts of impurity sources are introduced during the cyclical process. A graded gate dielectric is thereby provided, even for extremely thin layers. The gate dielectric as thin as 2 nm can be varied from pure silicon oxide to oxynitride to silicon nitride. Similarly, the gate dielectric can be varied from aluminum oxide to mixtures of aluminum oxide and a higher dielectric material (e.g., ZrO2) to pure high k material and back to aluminum oxide. In another embodiment, metal nitride (e.g., WN) is first formed as a barrier for lining dual damascene trenches and vias. During the alternating deposition process, copper can be introduced, e.g., in separate pulses, and the copper source pulses can gradually increase in frequency, forming a graded transition region, until pure copper is formed at the upper surface. Advantageously, graded compositions in these and a variety of other contexts help to avoid such problems as etch rate control, electromigration and non-ohmic electrical contact that can occur at sharp material interfaces.

Owner:ASM INTERNATIONAL

Thin films

InactiveUS7419903B2Desirable interface propertyQuality improvementSolid-state devicesSemiconductor/solid-state device manufacturingGate dielectricSilicon oxide

Thin films are formed by formed by atomic layer deposition, whereby the composition of the film can be varied from monolayer to monolayer during cycles including alternating pulses of self-limiting chemistries. In the illustrated embodiments, varying amounts of impurity sources are introduced during the cyclical process. A graded gate dielectric is thereby provided, even for extremely thin layers. The gate dielectric as thin as 2 nm can be varied from pure silicon oxide to oxynitride to silicon nitride. Similarly, the gate dielectric can be varied from aluminum oxide to mixtures of aluminum oxide and a higher dielectric material (e.g., ZrO2) to pure high k material and back to aluminum oxide. In another embodiment, metal nitride (e.g., WN) is first formed as a barrier for lining dual damascene trenches and vias. During the alternating deposition process, copper can be introduced, e.g., in separate pulses, and the copper source pulses can gradually increase in frequency, forming a transition region, until pure copper is formed at the upper surface. Advantageously, graded compositions in these and a variety of other contexts help to avoid such problems as etch rate control, electromigration and non-ohmic electrical contact that can occur at sharp material interfaces. In some embodiments additional seed layers or additional transition layers are provided.

Owner:ASM INTERNATIONAL

Modification of pb-free solder alloy compositions to improve interlayer dielectric delamination in silicon devices and electromigration resistance in solder joints

InactiveUS20090197114A1Good mechanical integrityImprove reliabilitySolid-state devicesPrinted circuit manufactureDielectricSilicon

A solder joint comprising a solder capture pad on a substrate having a circuit; and a lead free solder selected from the group comprising Sn—Ag—Cu solder and Sn—Ag solder adhered to the solder capture pad; the solder selected from the group comprising between 0.1 to 2.0% by weight Sb or Bi, and 0.5 to 3.0% Ag. Formation of voids at an interface between the solder and the solder capture pad is suppressed, by including Zn. Interlayer dielectric delamination is suppressed, and electromigration characteristics are greatly improved. Methods for forming solder joints using the solders.

Owner:SHIH YUAN +5

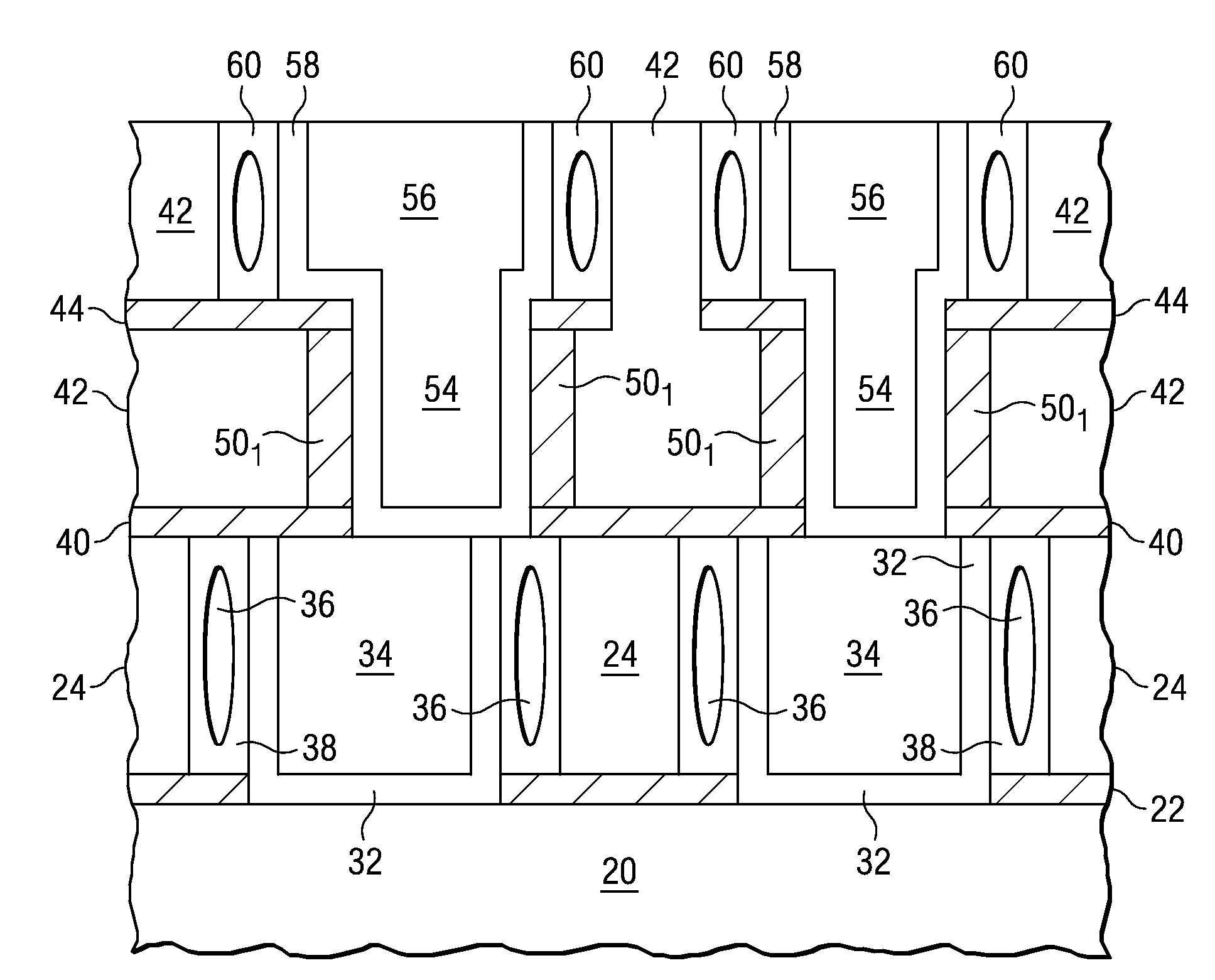

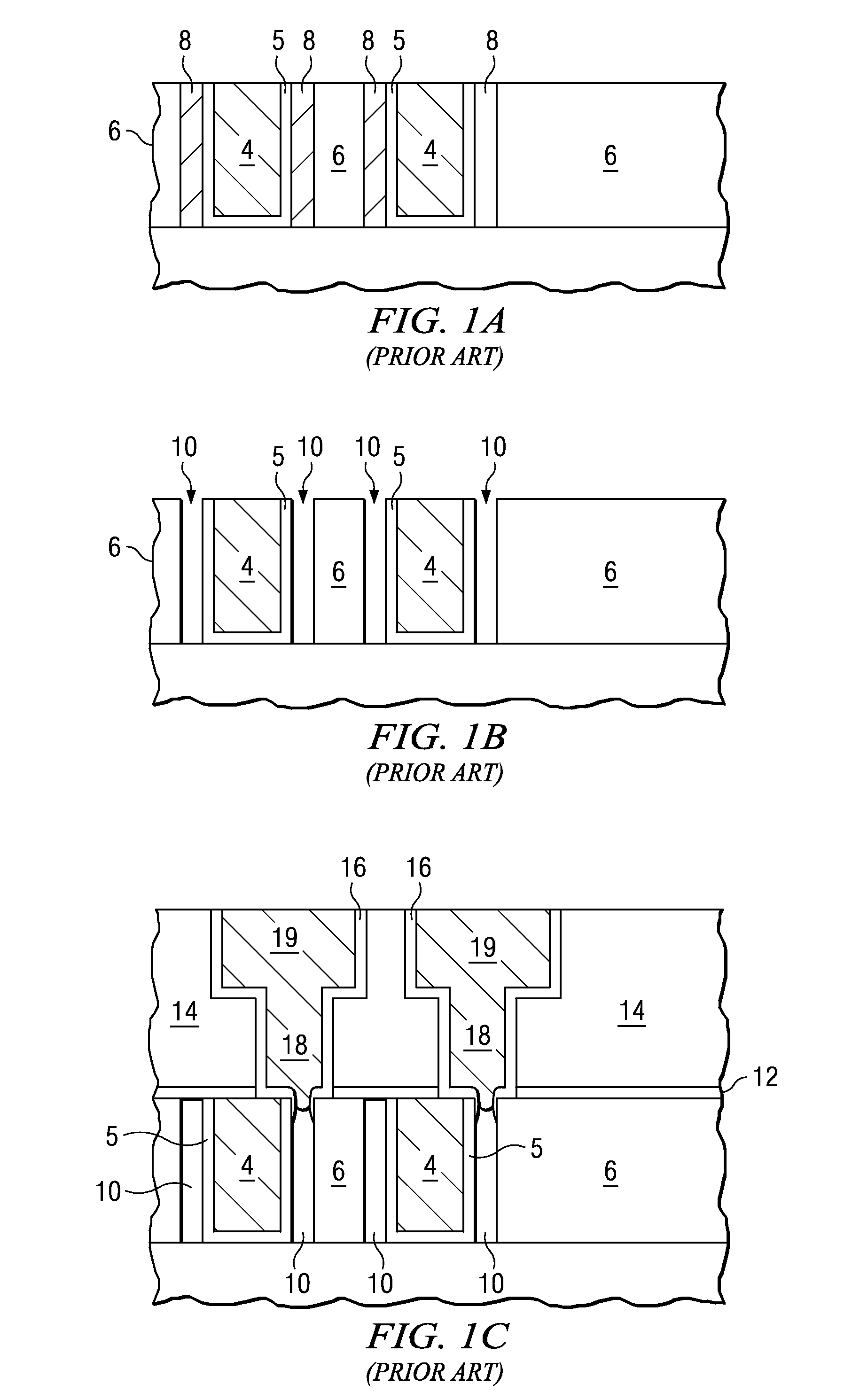

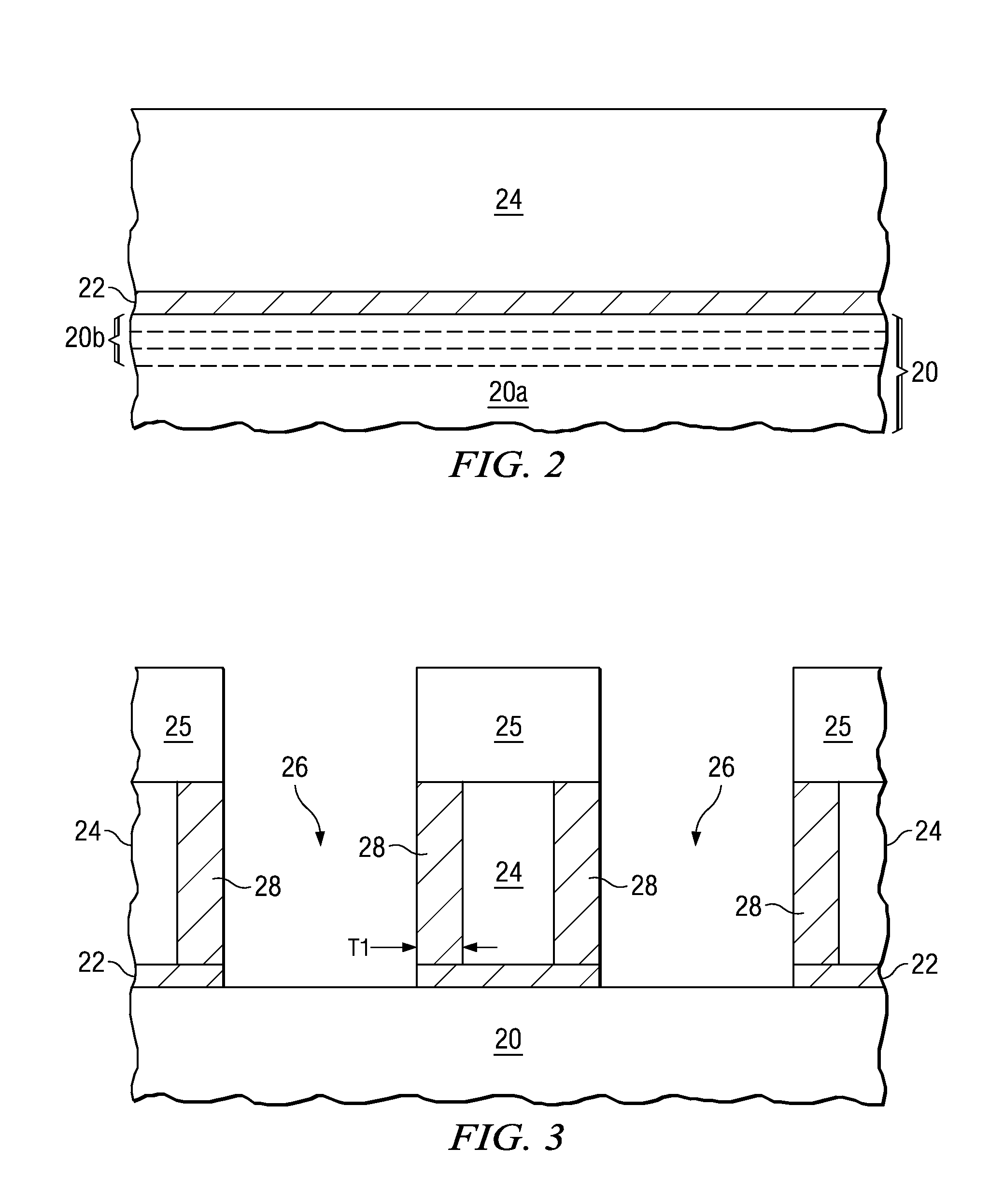

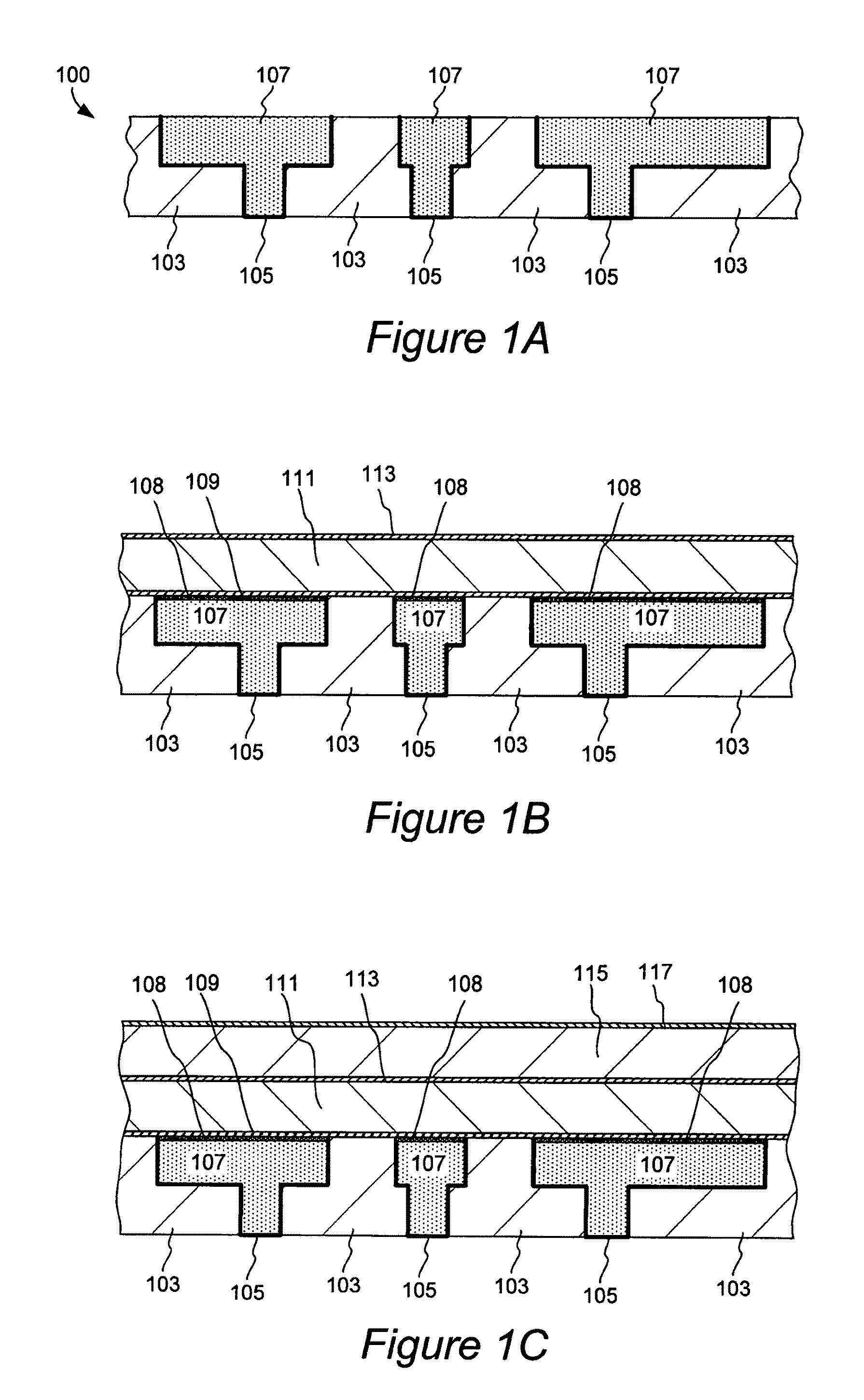

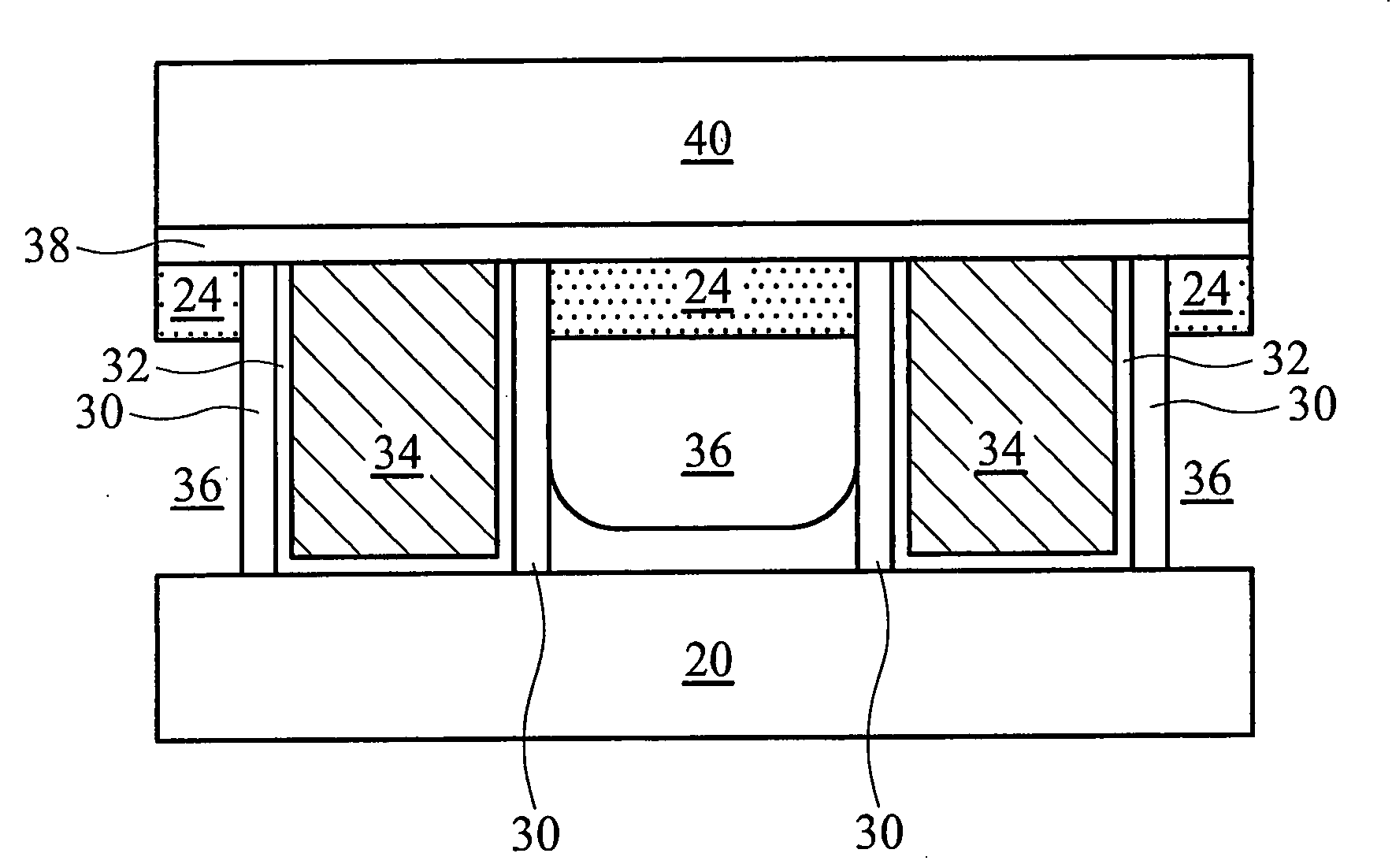

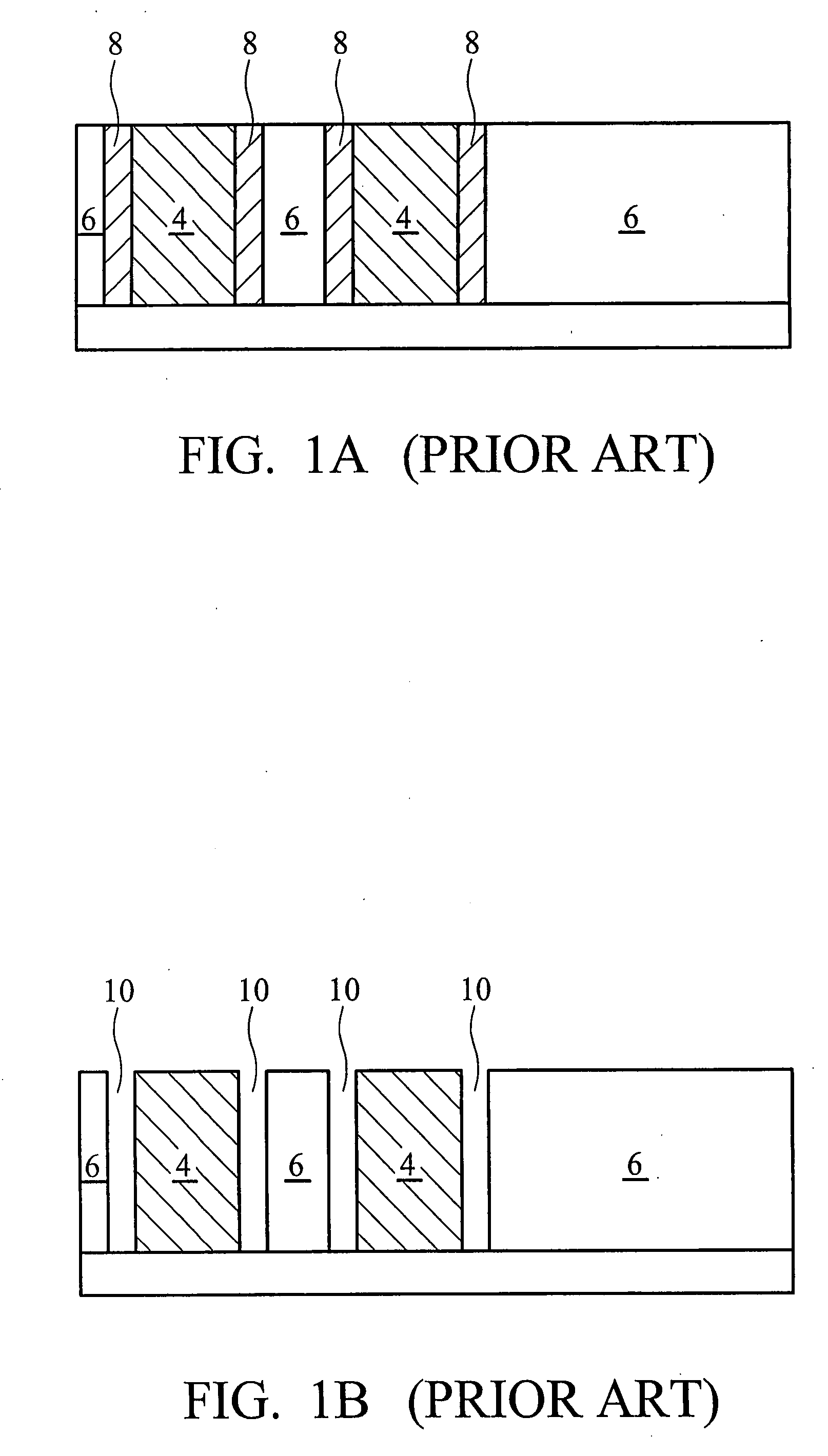

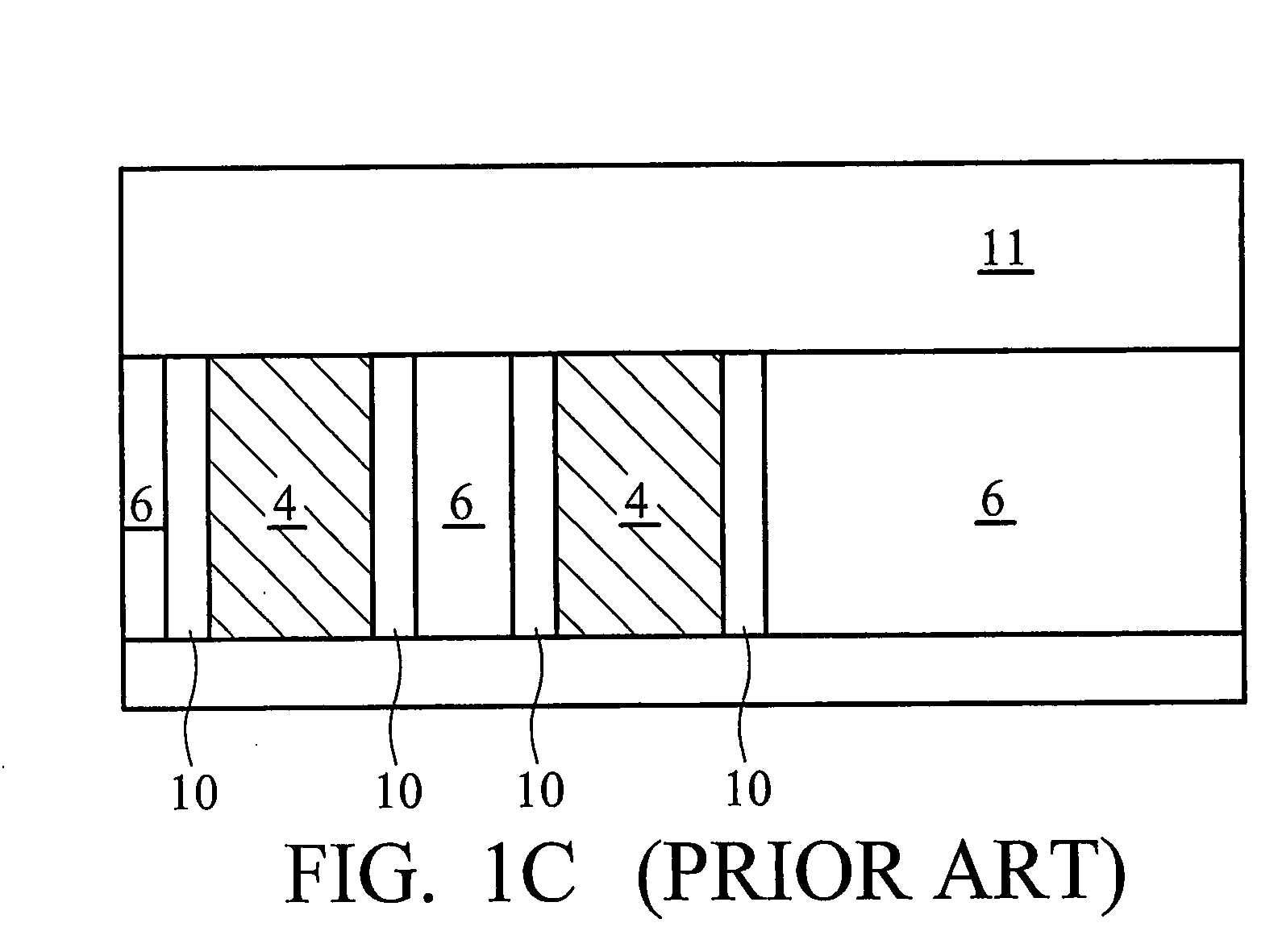

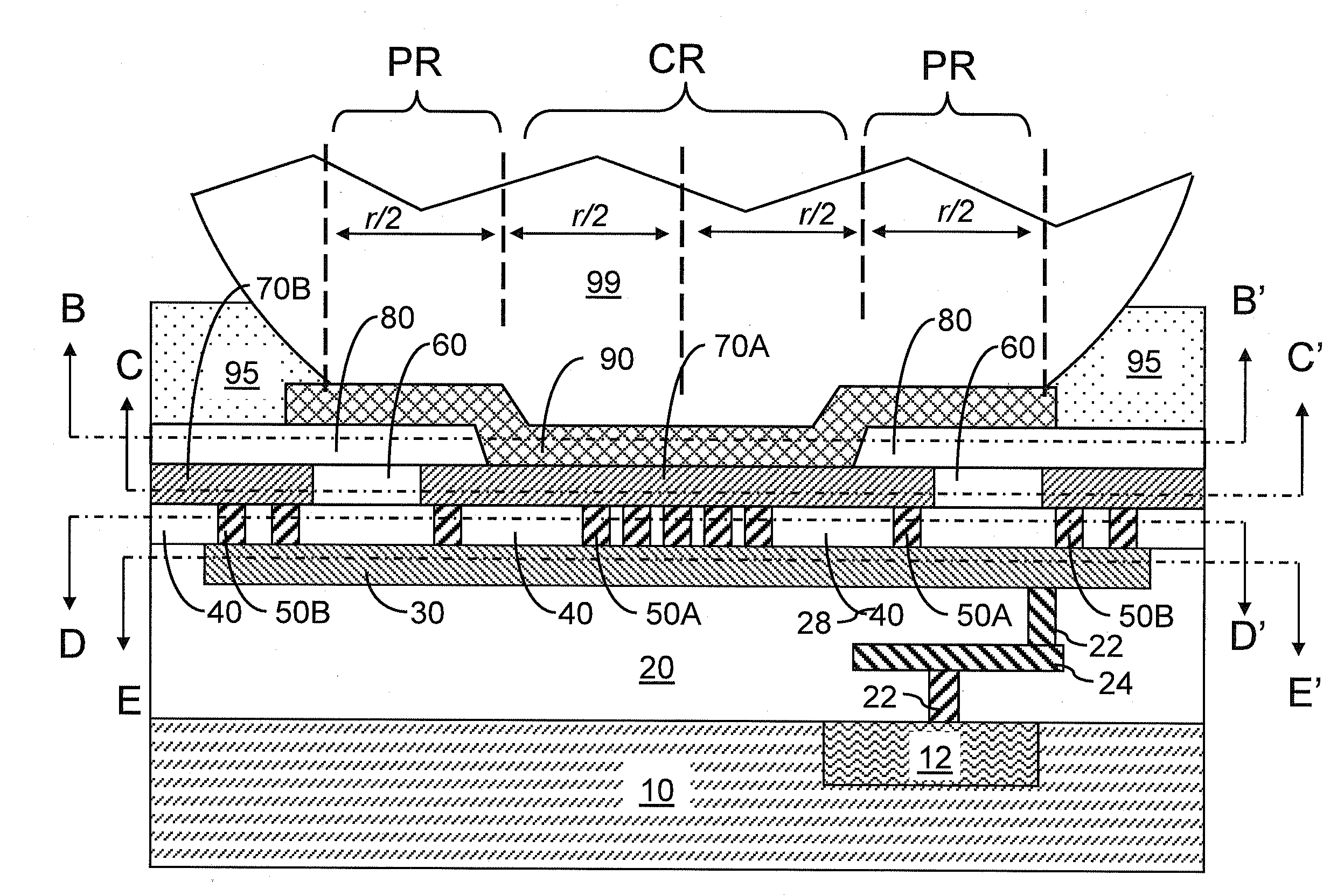

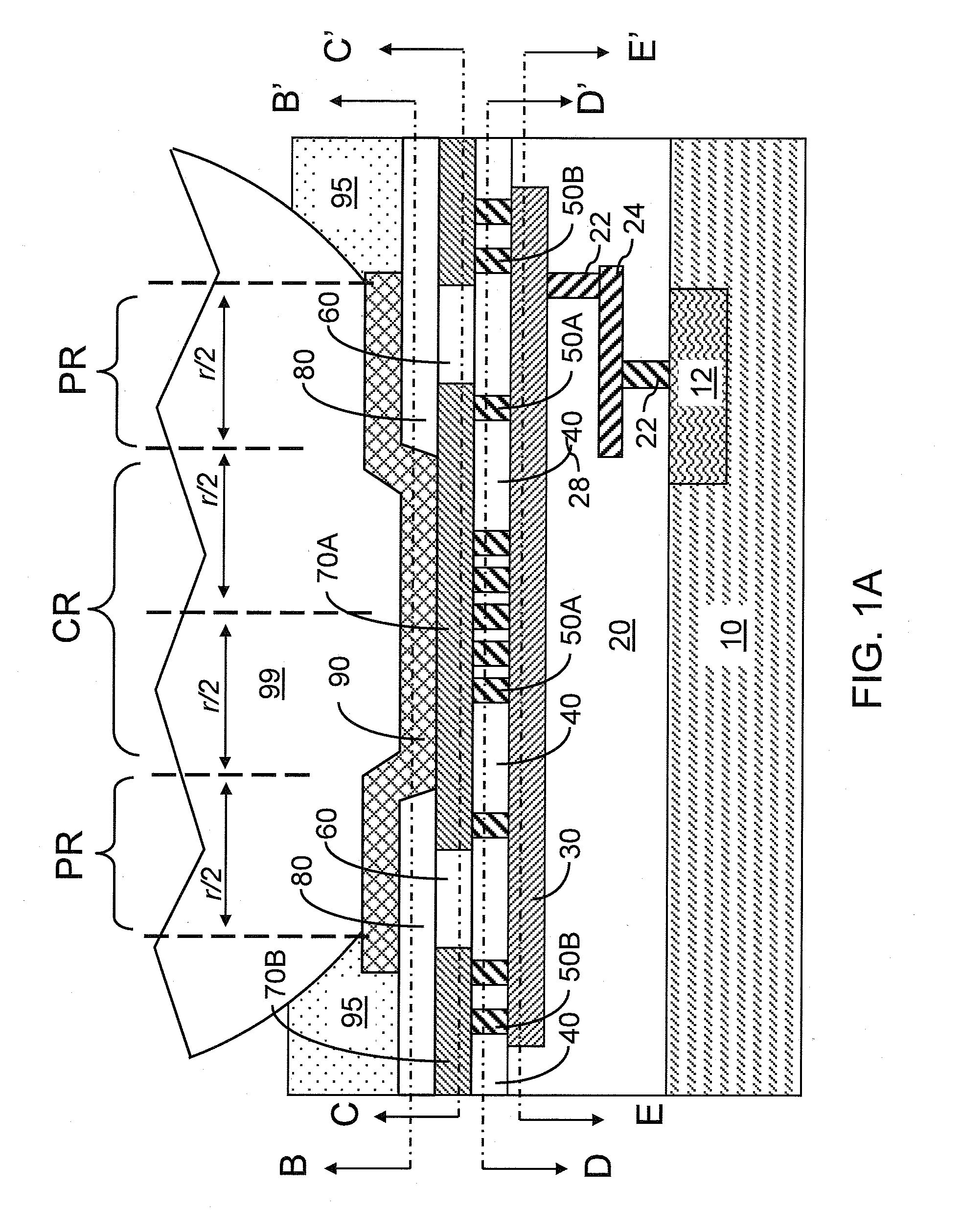

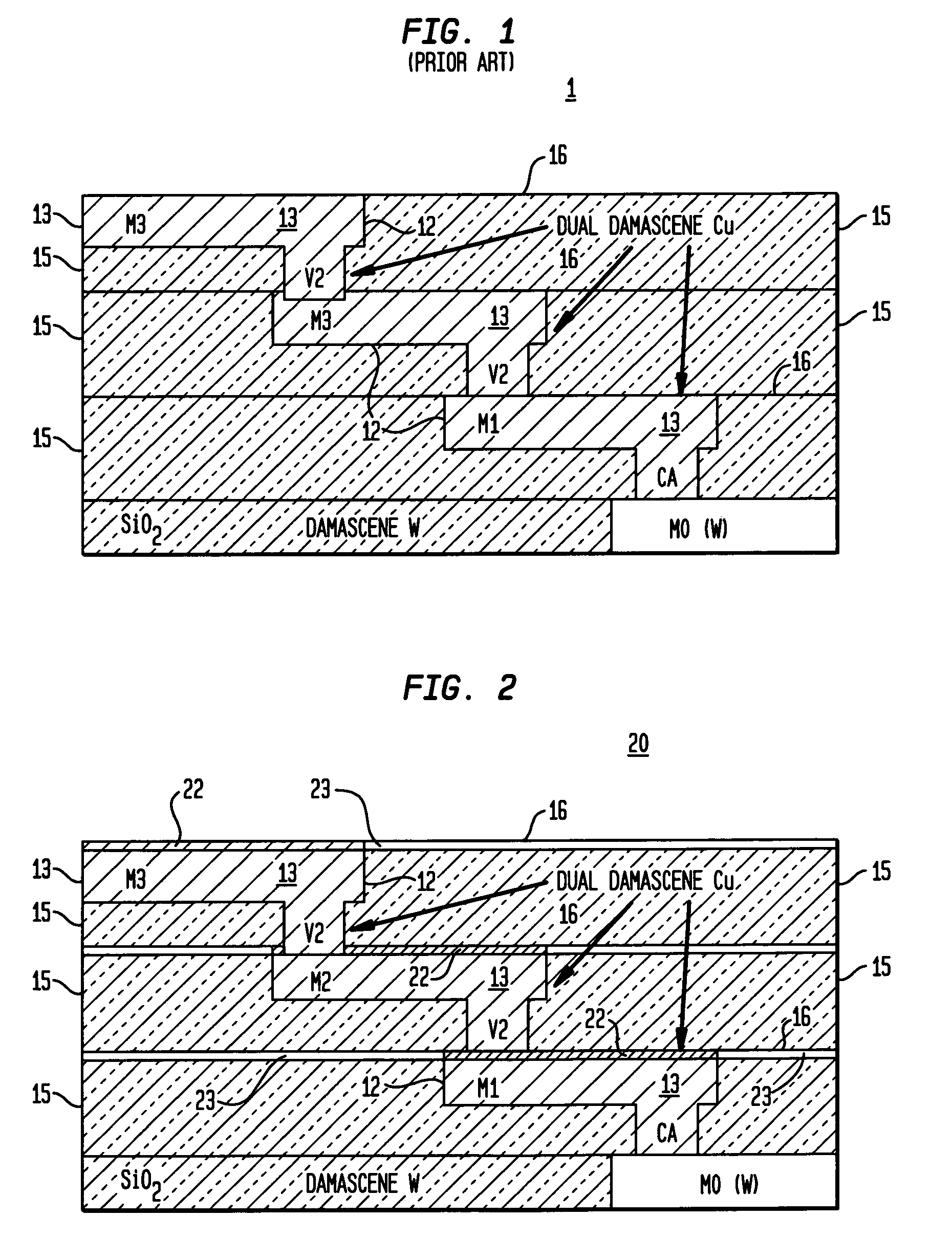

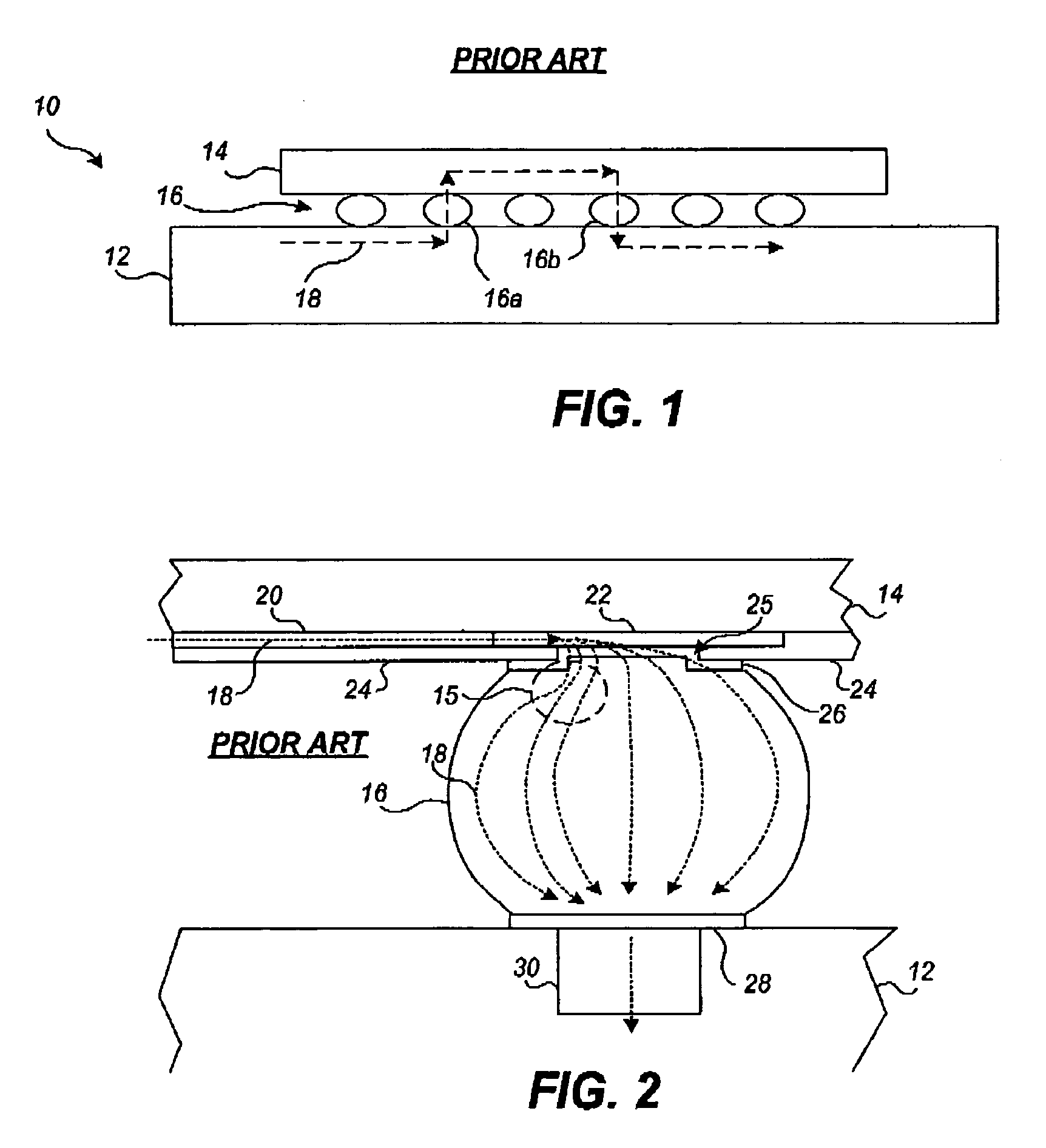

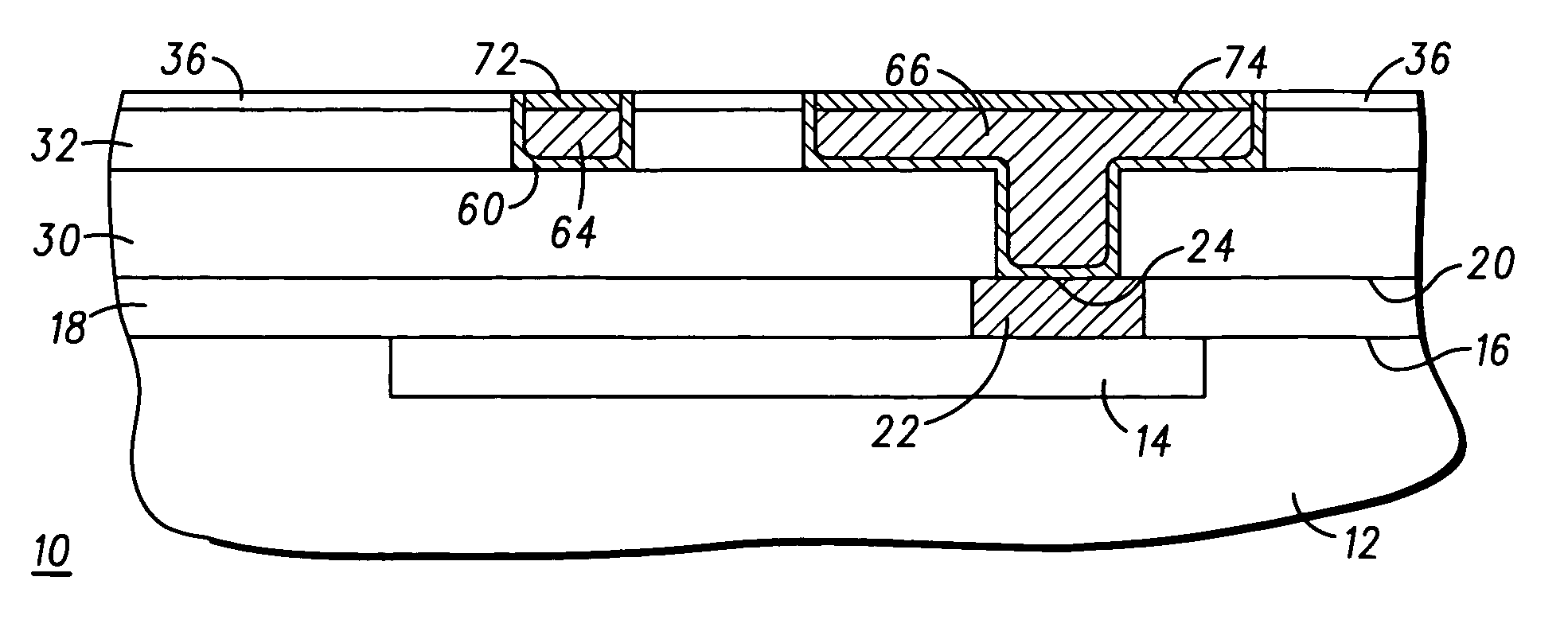

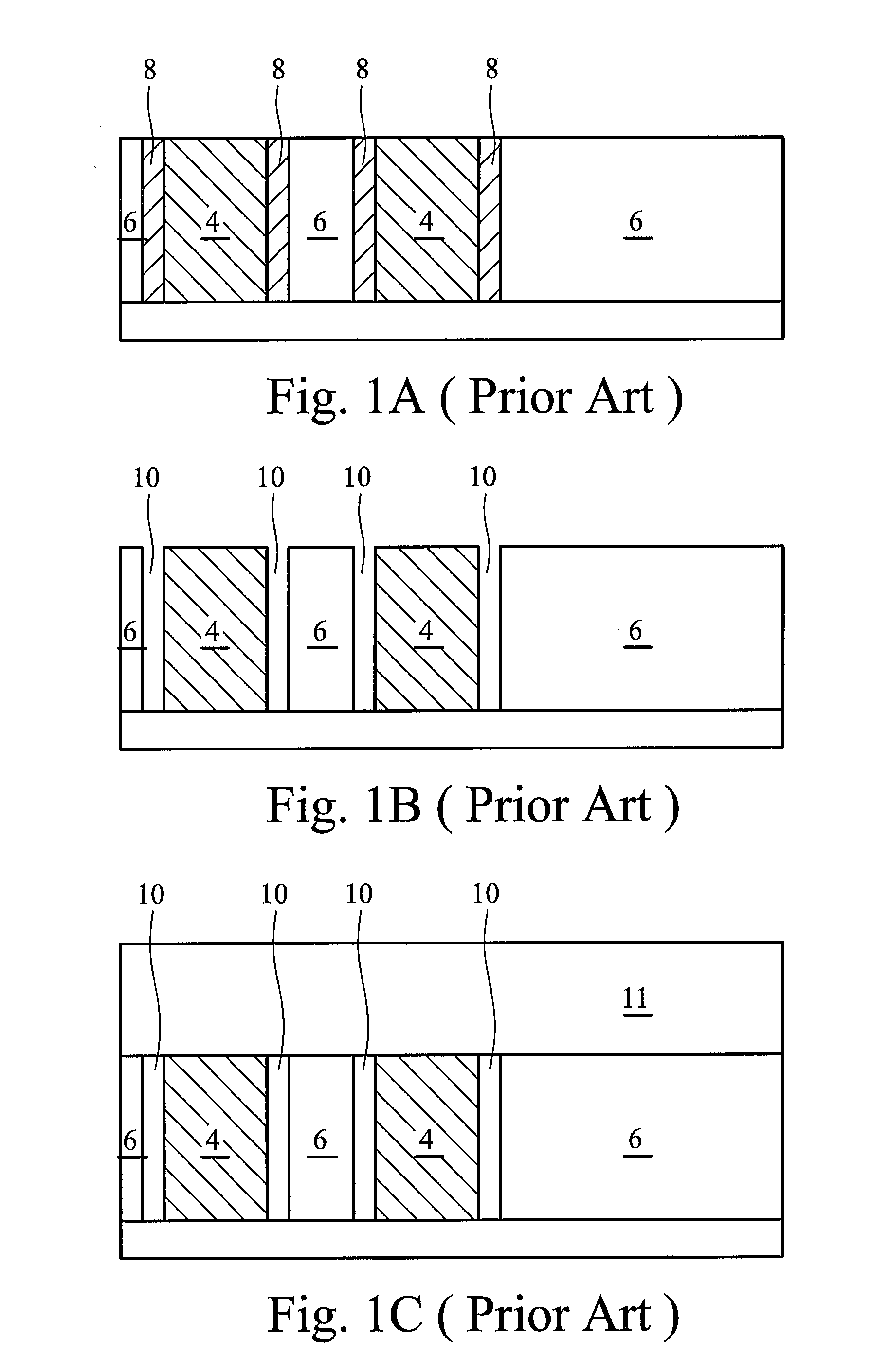

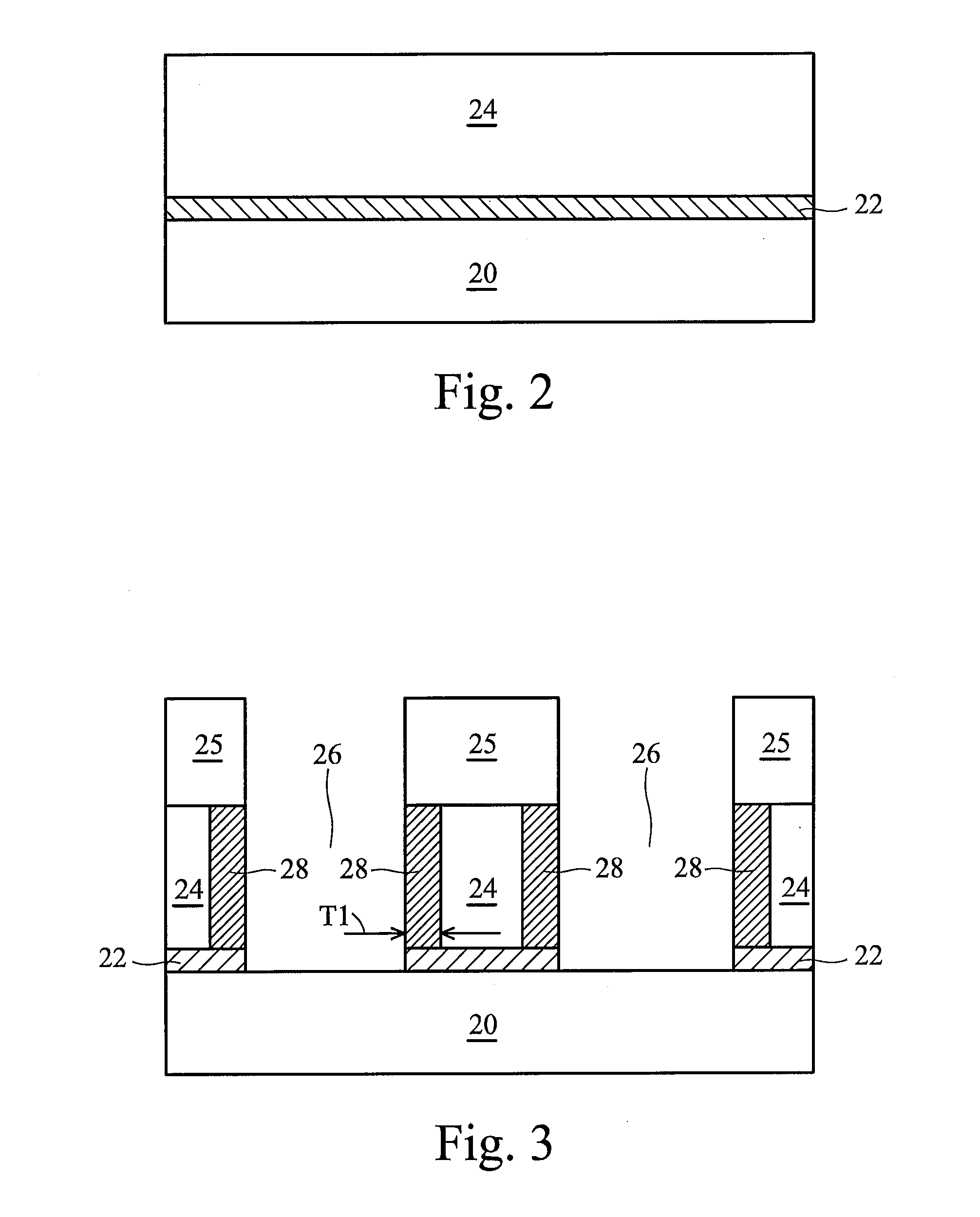

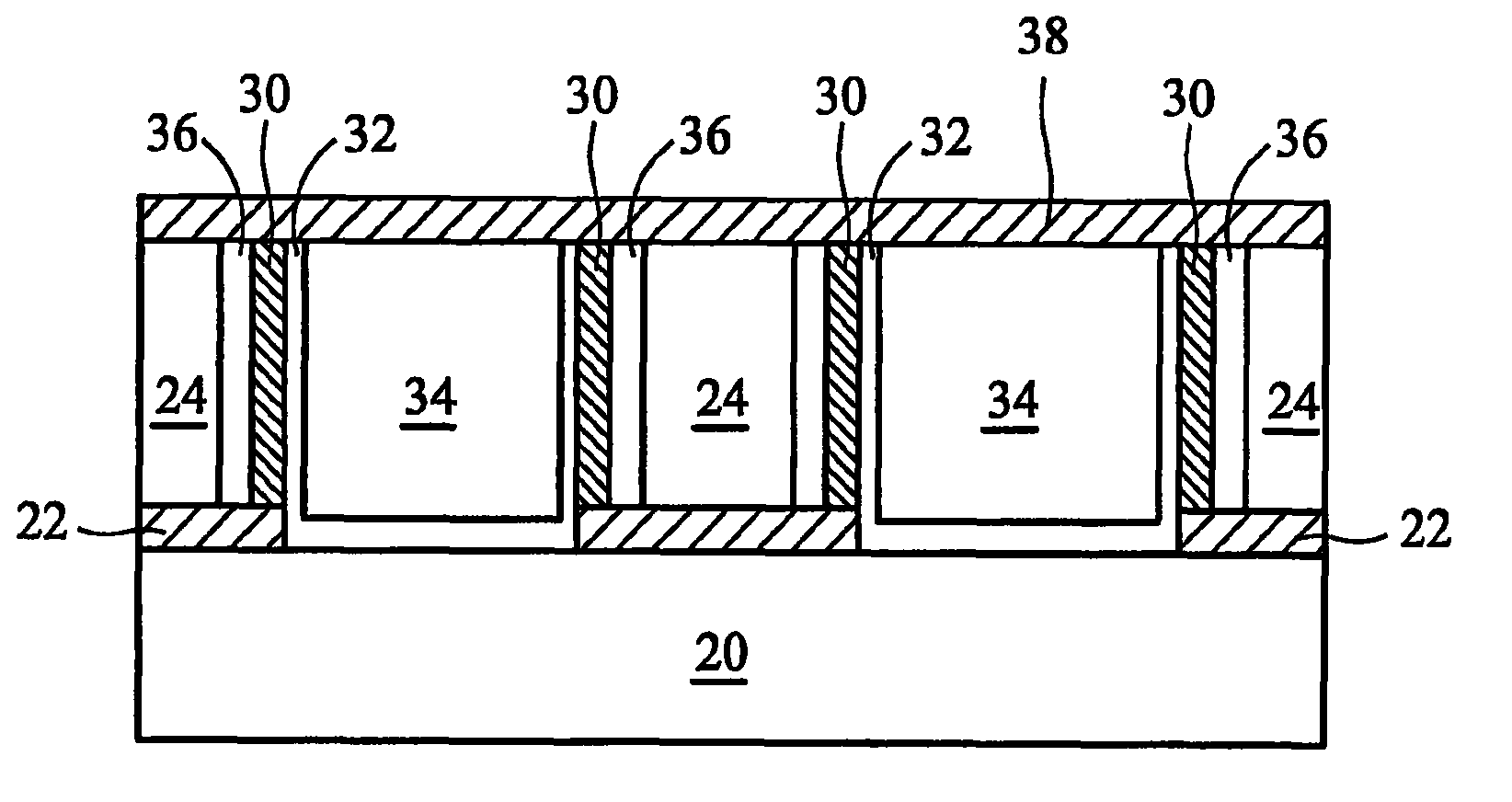

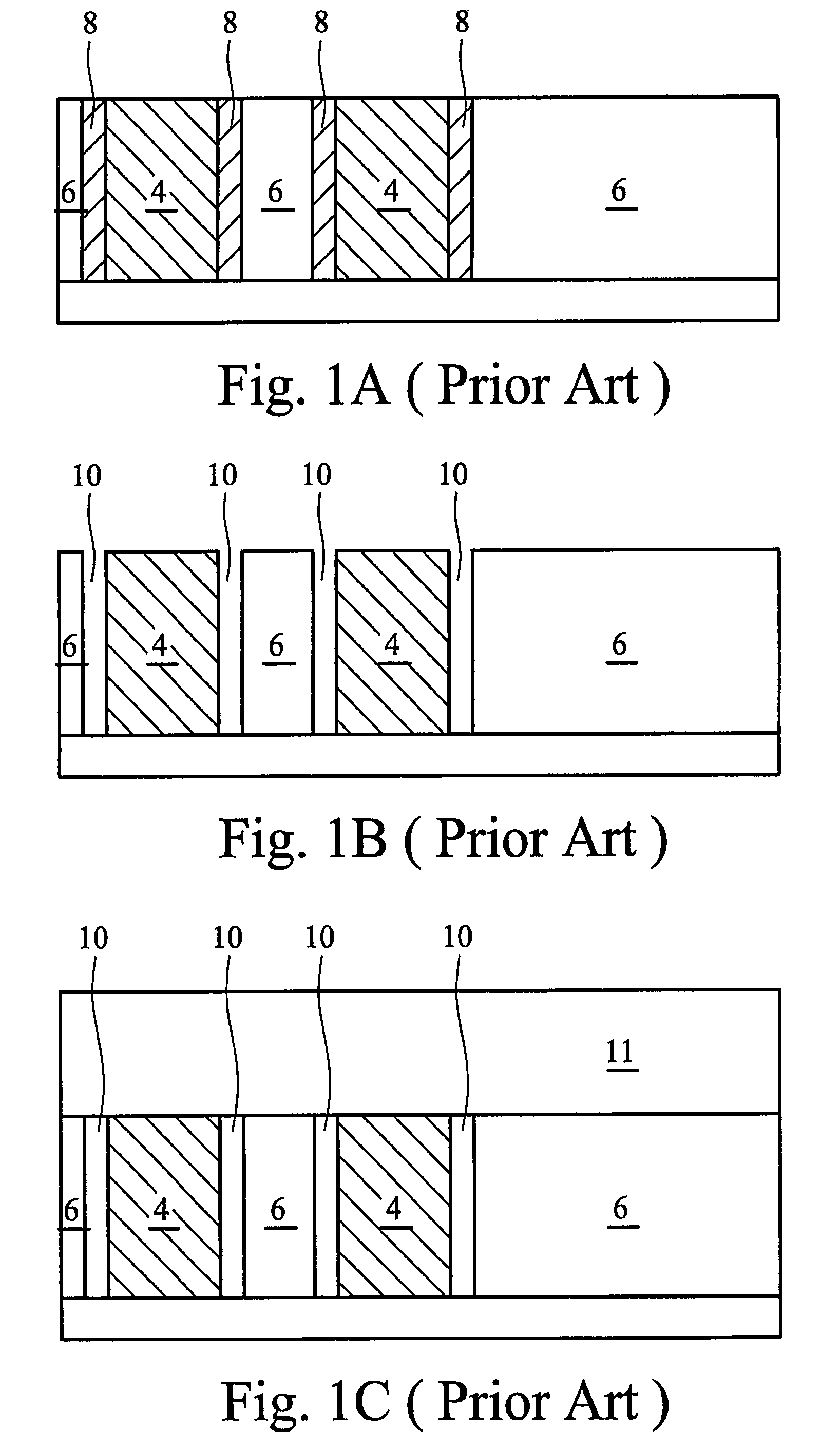

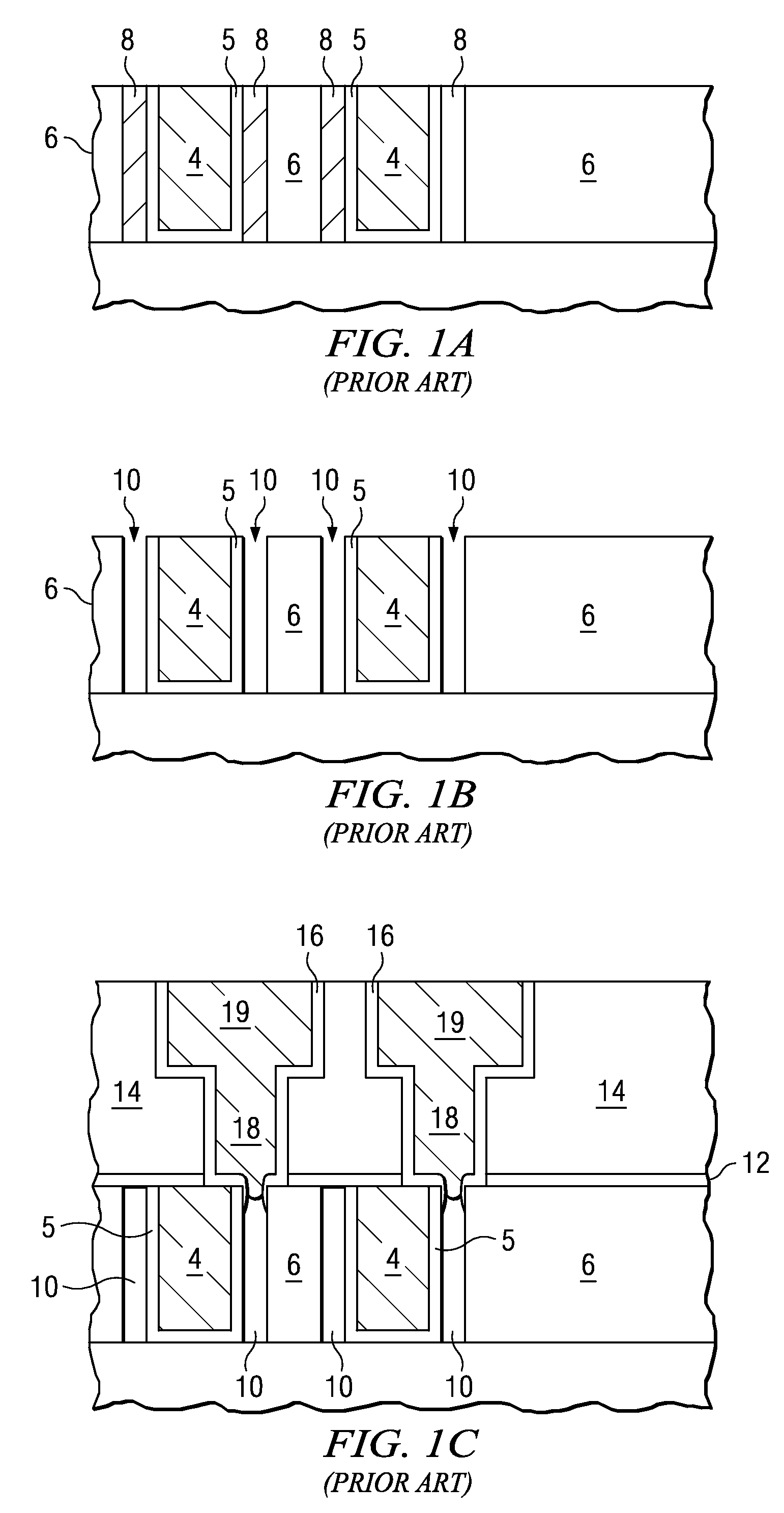

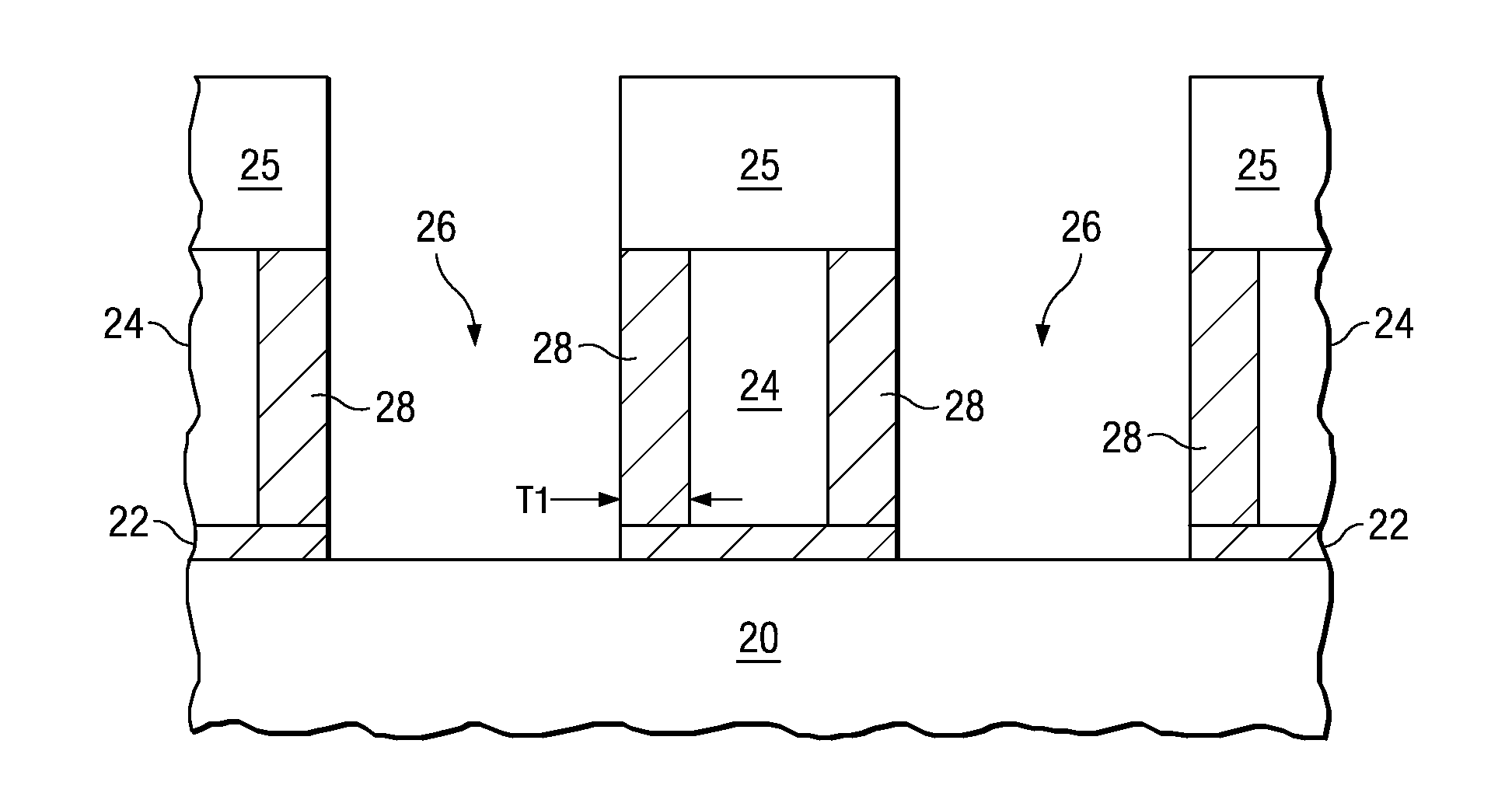

Solving Via-Misalignment Issues in Interconnect Structures Having Air-Gaps

ActiveUS20090115061A1Reduce parasitic capacitanceReduce electro-migrationSemiconductor/solid-state device detailsSolid-state devicesLow-k dielectricIntegrated circuit

An integrated circuit structure is provided. The integrated circuit structure includes a semiconductor substrate; and a metallization layer over the semiconductor substrate. The metallization layer includes a conductive line; a low-k dielectric region adjacent and horizontally spaced apart from the conductive line by a space; and a filler dielectric material filling at least a portion of the space, wherein the filler dielectric material and the low-k dielectric region are formed of different materials. The integrated circuit structure further includes a capping layer over and adjoining the filler dielectric material and the low-k dielectric region. The filler dielectric material has a dielectric constant (k value) less than a k value of the capping layer.

Owner:TAIWAN SEMICON MFG CO LTD

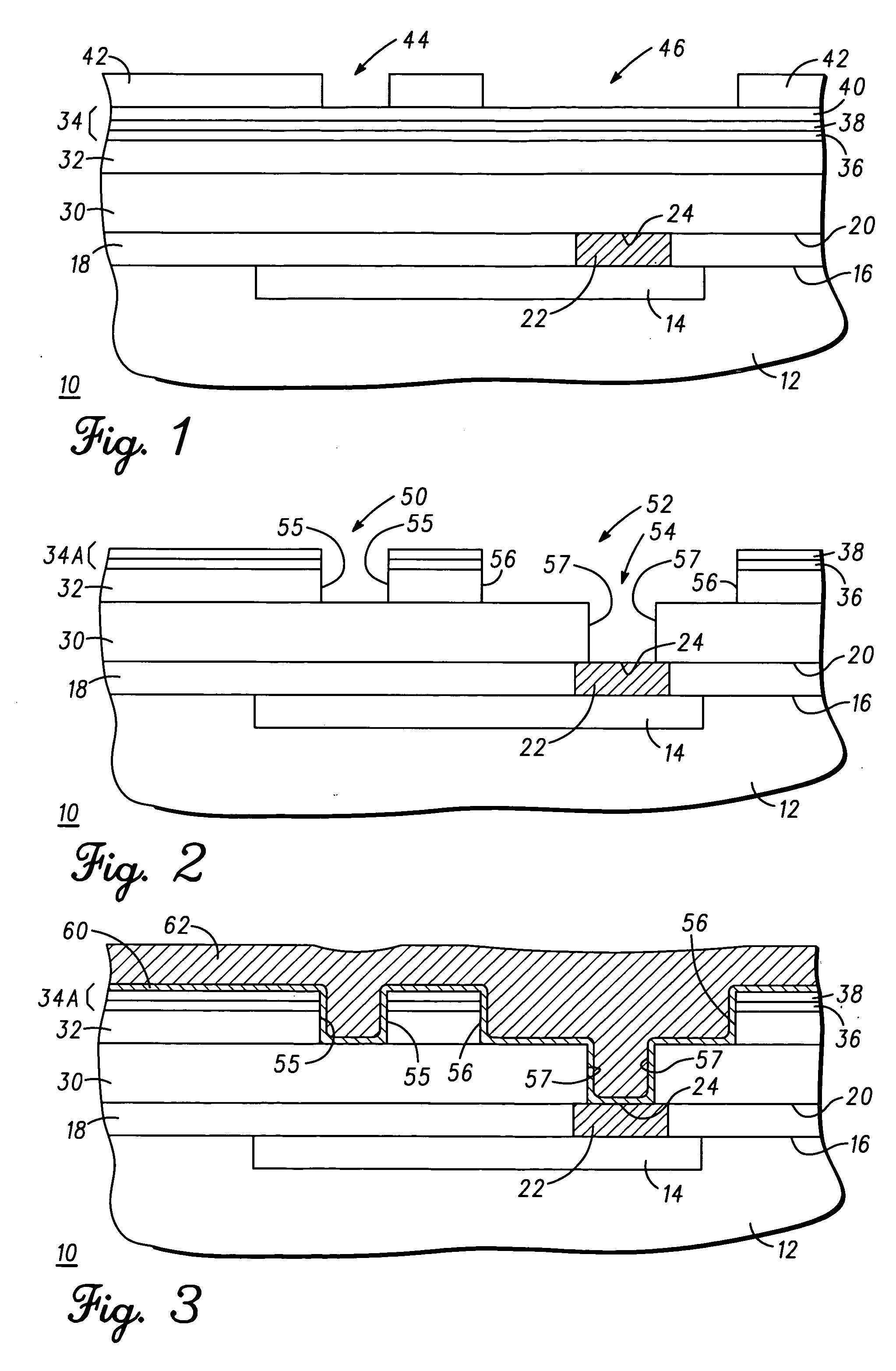

Protective self-aligned buffer layers for damascene interconnects

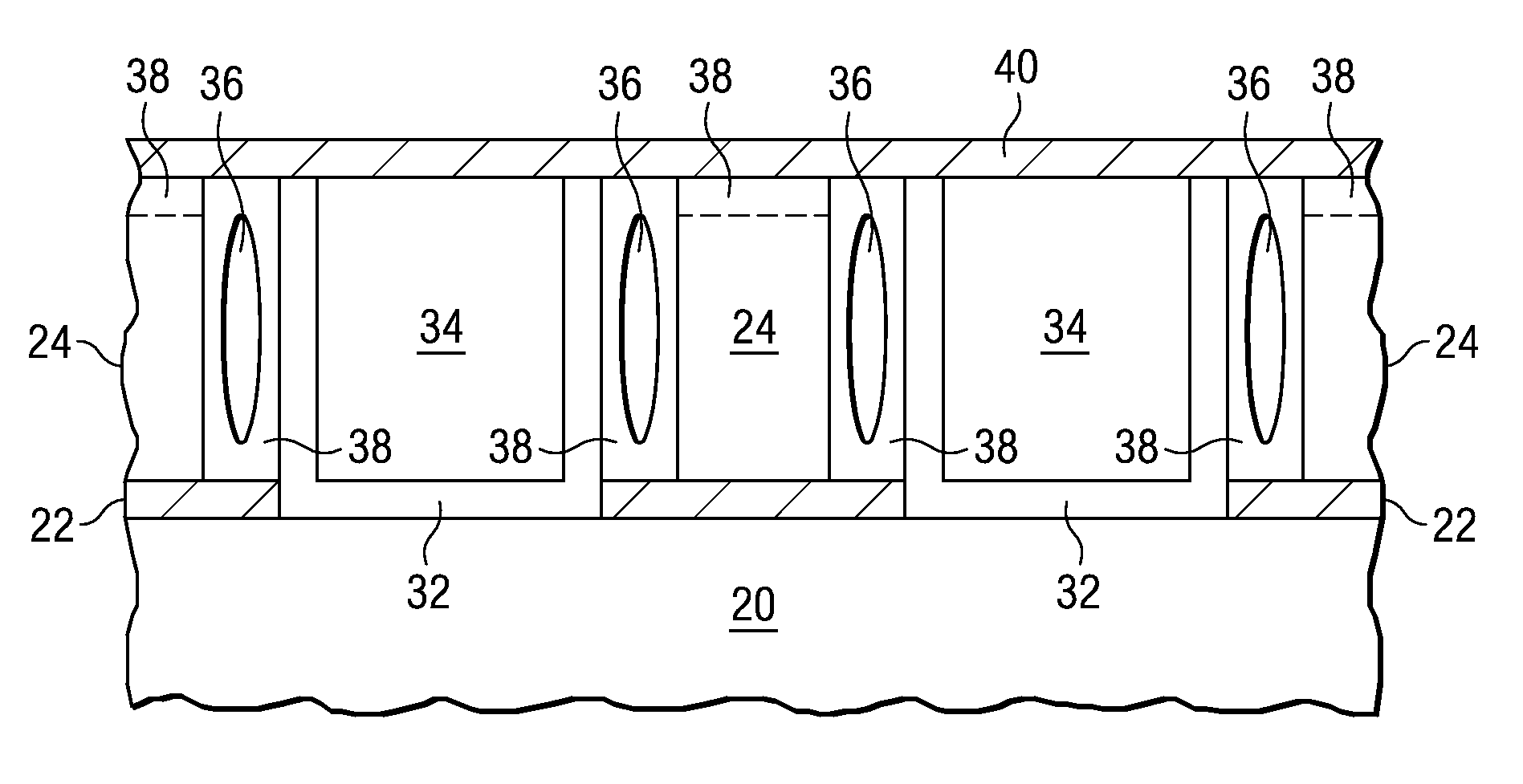

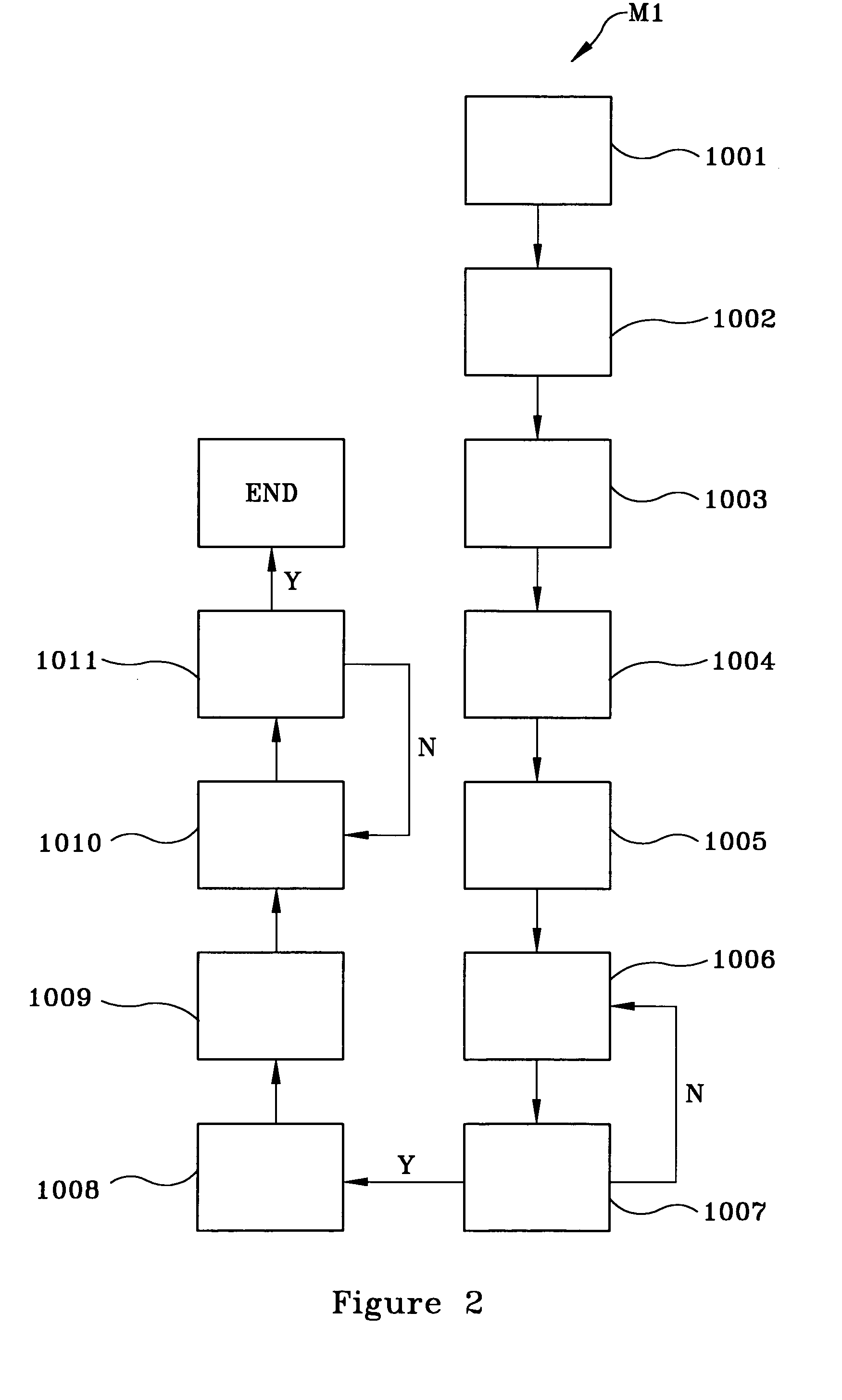

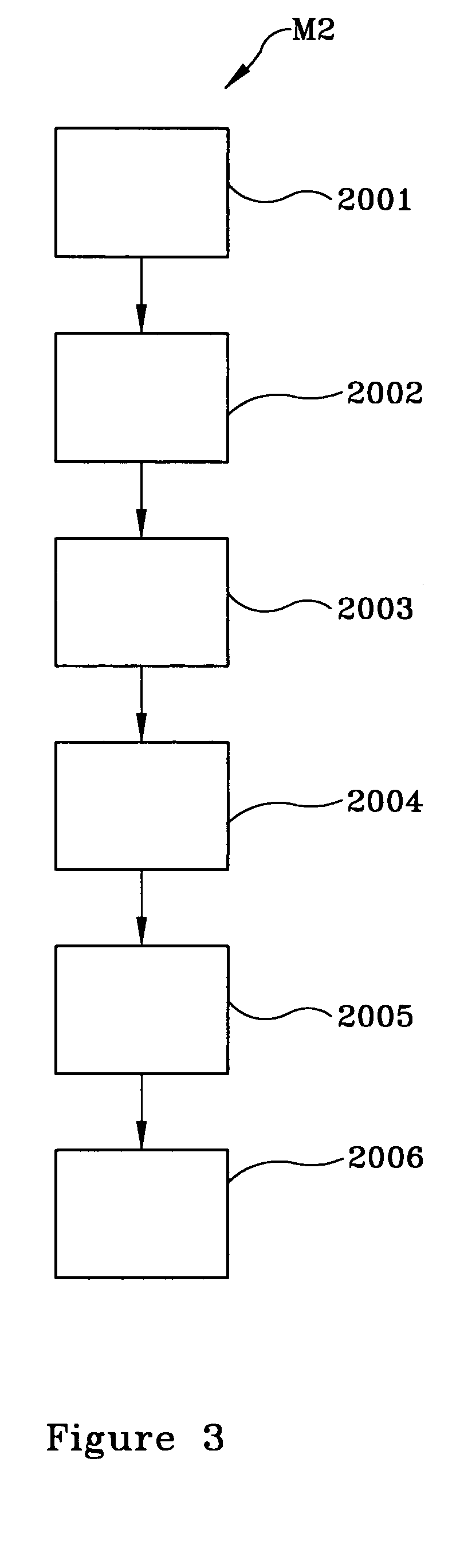

ActiveUS7576006B1Improve mobilityImproving several propertySemiconductor/solid-state device manufacturingThin material handlingDiffusion barrierSemiconductor

Capping protective self aligned buffer (PSAB) layers are layers of material that are selectively formed at the surface of metal layers in a partially fabricated semiconductor device. Encapsulating PSAB layers are formed not only at the surface of the metal layers, but also within the unexposed portions of the metal lines. Encapsulating PSAB layer, for example, can surround the metal line with the PSAB material, thereby protecting interfaces between the metal line and diffusion barriers. Encapsulating PSAB layers can be formed by treating the exposed surfaces of metal lines with GeH4. Capping PSAB layers can be formed by treating the exposed surfaces of metal lines with SiH4. Interconnects having both a silicon-containing capping PSAB layer and a germanium-containing encapsulating PSAB layer provide good performance in terms of adhesion, resistance shift, and electromigration characteristics.

Owner:NOVELLUS SYSTEMS

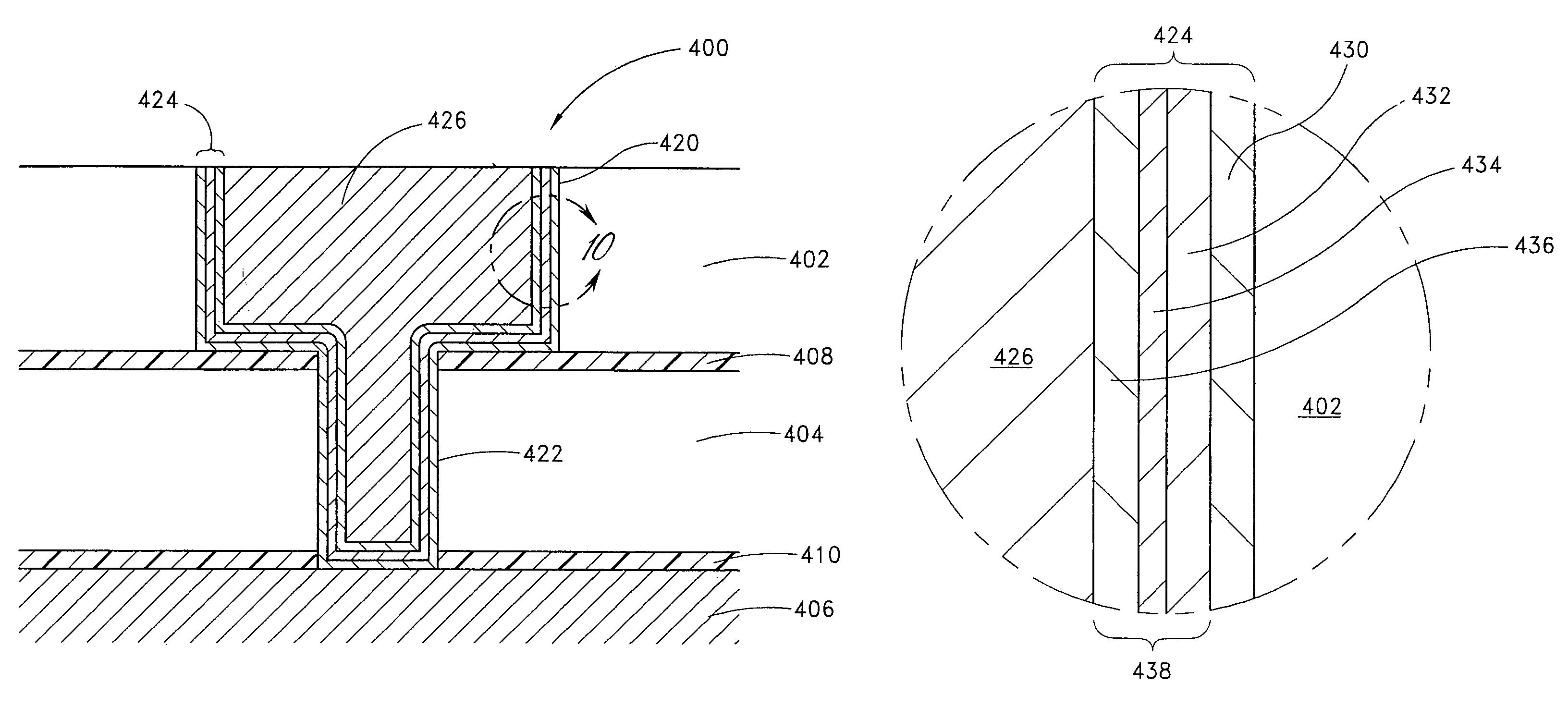

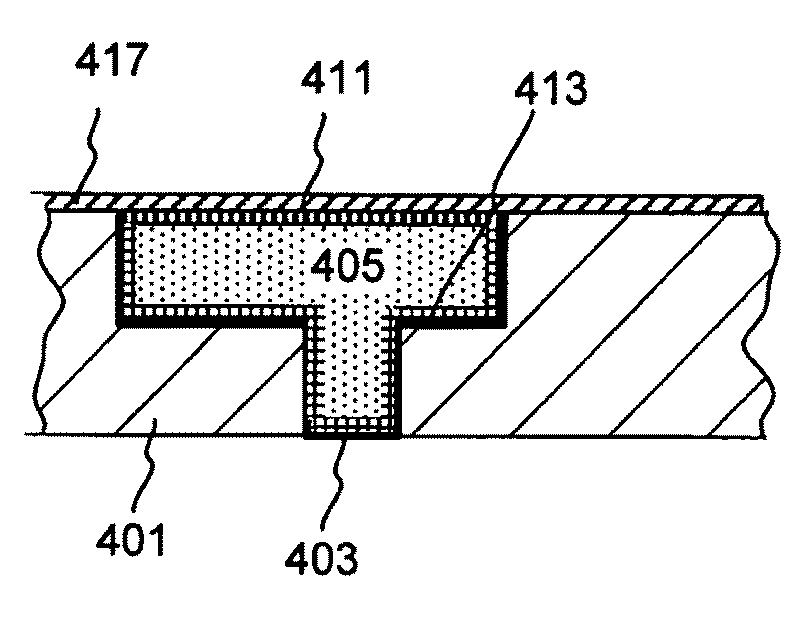

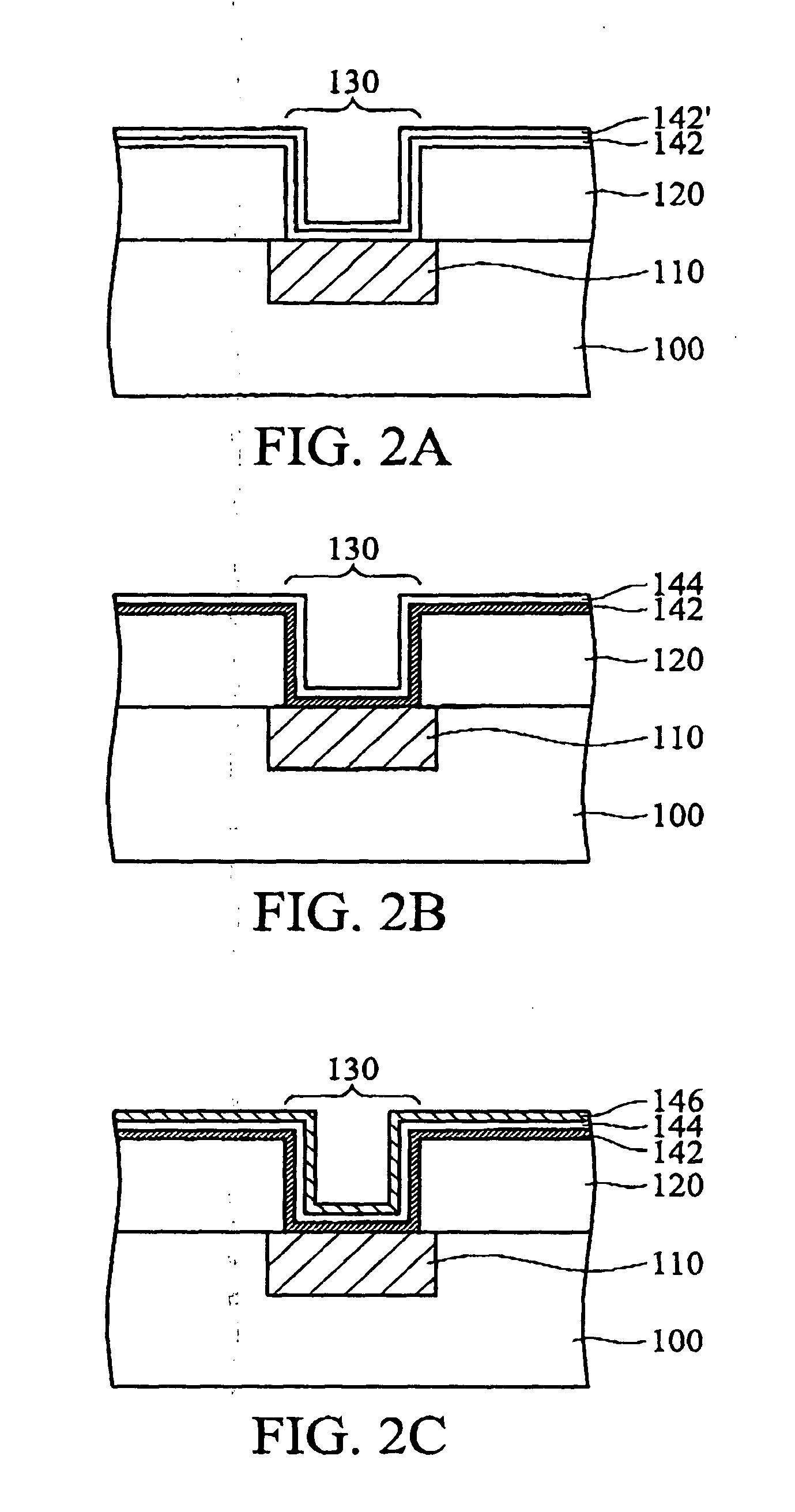

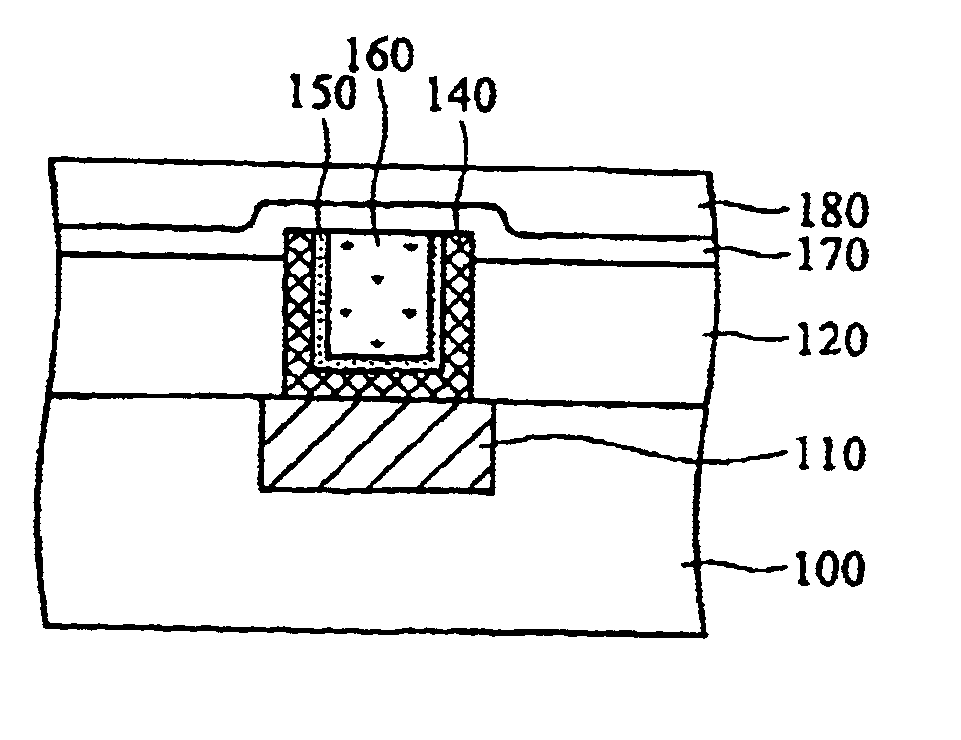

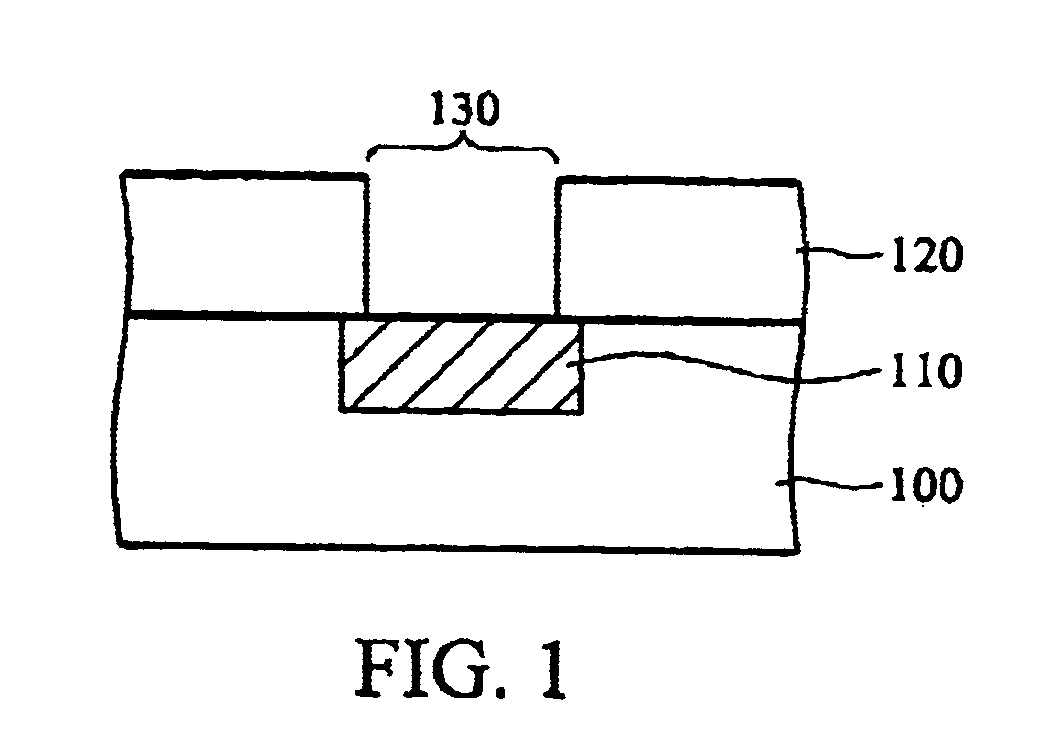

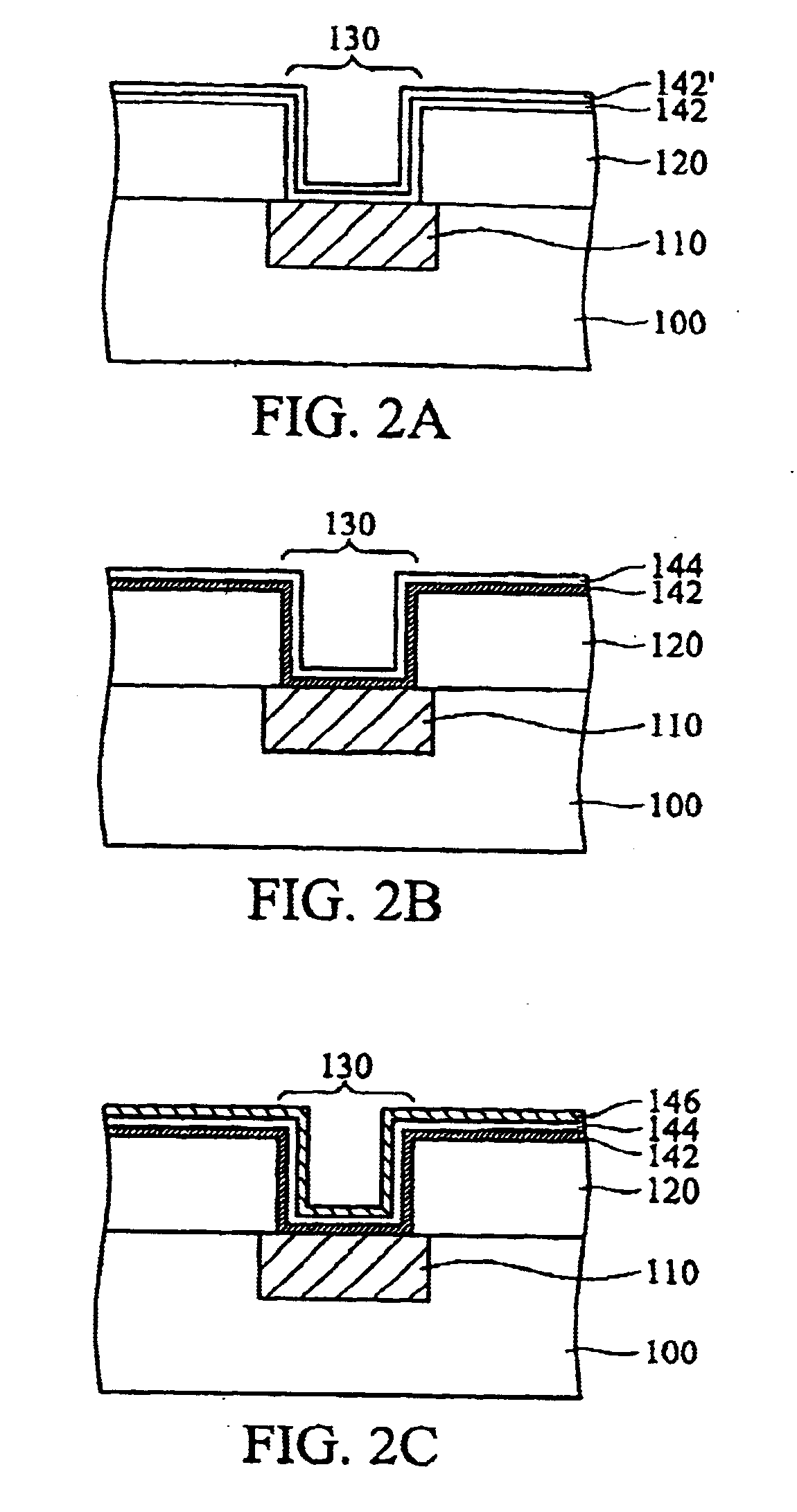

Interconnect with composite barrier layers and method for fabricating the same

ActiveUS20050054191A1Improve adhesionGood step coverageSemiconductor/solid-state device manufacturingDielectricTantalum nitride

Composite ALD-formed diffusion barrier layers. In a preferred embodiment, a composite conductive layer is composed of a diffusion barrier layer and / or a low-resistivity metal layer formed by atomic layer deposition (ALD) lining a damascene opening in dielectrics, serving as diffusion blocking and / or adhesion improvement. The preferred composite diffusion barrier layers are dual titanium nitride layers or dual tantalum nitride layers, triply laminar of tantalum, tantalum nitride and tantalum-rich nitride, or tantalum, tantalum nitride and tantalum, formed sequentially on the opening by way of ALD.

Owner:TAIWAN SEMICON MFG CO LTD

Micro-hotplates

ActiveUS20110174799A1Improve reliabilityExtended service lifeSolid-state devicesSemiconductor/solid-state device manufacturingDriving currentElectrical resistance and conductance

A micro-hotplate is provided in the form of a device comprising a sensor and one or more resistive heaters within the micro-hotplate arranged to heat the sensor. Furthermore a controller is provided for applying a bidirectional drive current to at least one of the heaters to reduce electromigration. The controller also serves to drive the heater at a substantially constant temperature. Such an arrangement is advantageous over an arrangement in which a unidirectional DC drive current is applied to the heater. This is because the unidirectional drive current causes electromigration which results in an increase in resistance over time. This is undesirable because it can lead to failure of the micro-hotplate. In contrast, the application of the bidirectional current reduces electromigration and as a result there is insignificant change in the resistance of the heater over time and under high temperature. This in turn improves the reliability of the micro-hotplate and therefore helps to improve the lifetime of the sensor

Owner:SCIOSENSE BV

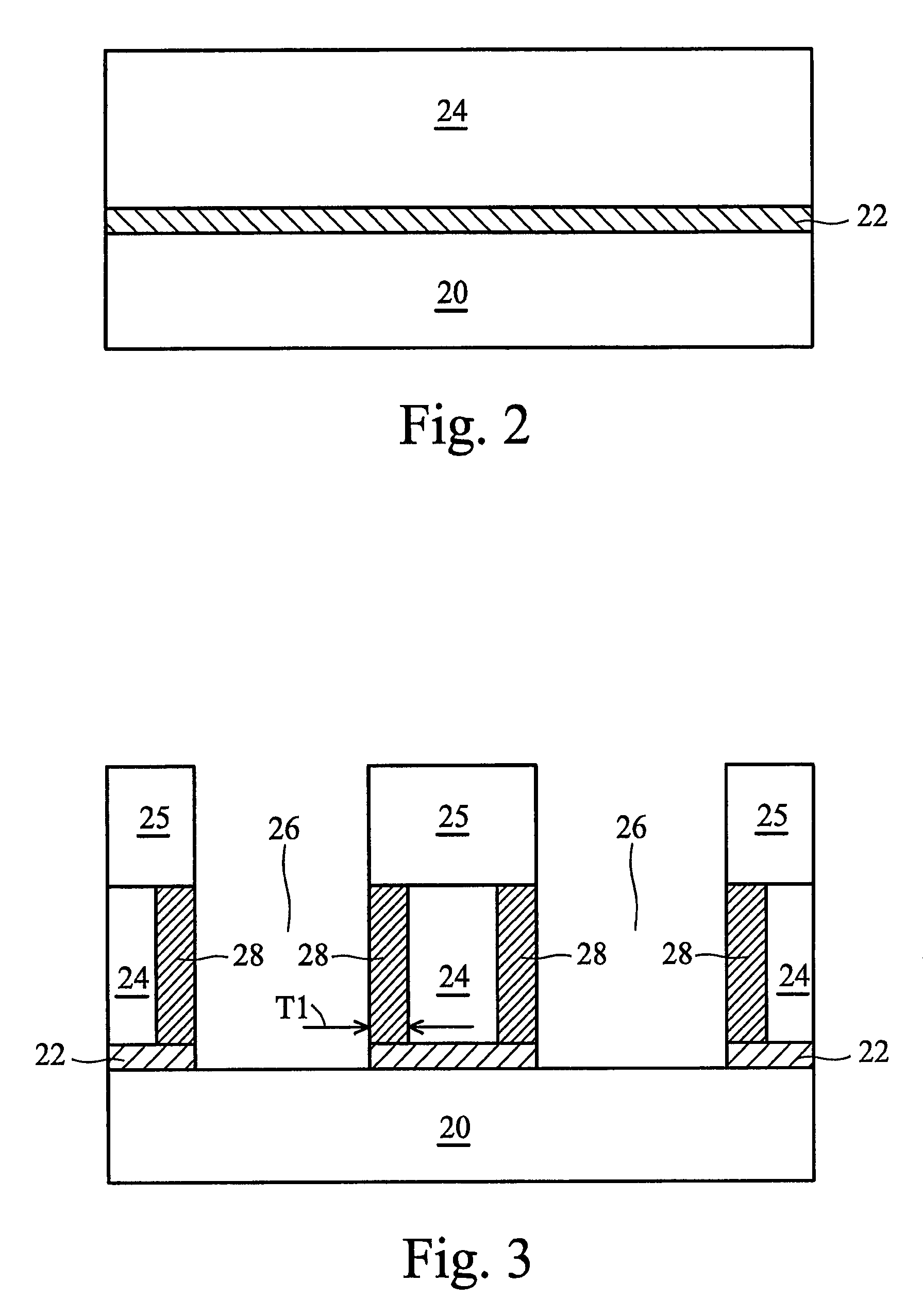

Formation process of interconnect structures with air-gaps and sidewall spacers

InactiveUS20080185722A1Reduce electromigrationImproved time dependent dielectric breakdownSemiconductor/solid-state device detailsSolid-state devicesEngineeringDielectric layer

An integrated circuit structure having air gaps is provided. The integrated circuit includes a conductive line; a sidewall spacer on a sidewall of the conductive line, wherein the sidewall spacer comprises a dielectric material; an air-gap horizontally adjoining the sidewall spacer; and a dielectric layer on the air-gap.

Owner:TAIWAN SEMICON MFG CO LTD

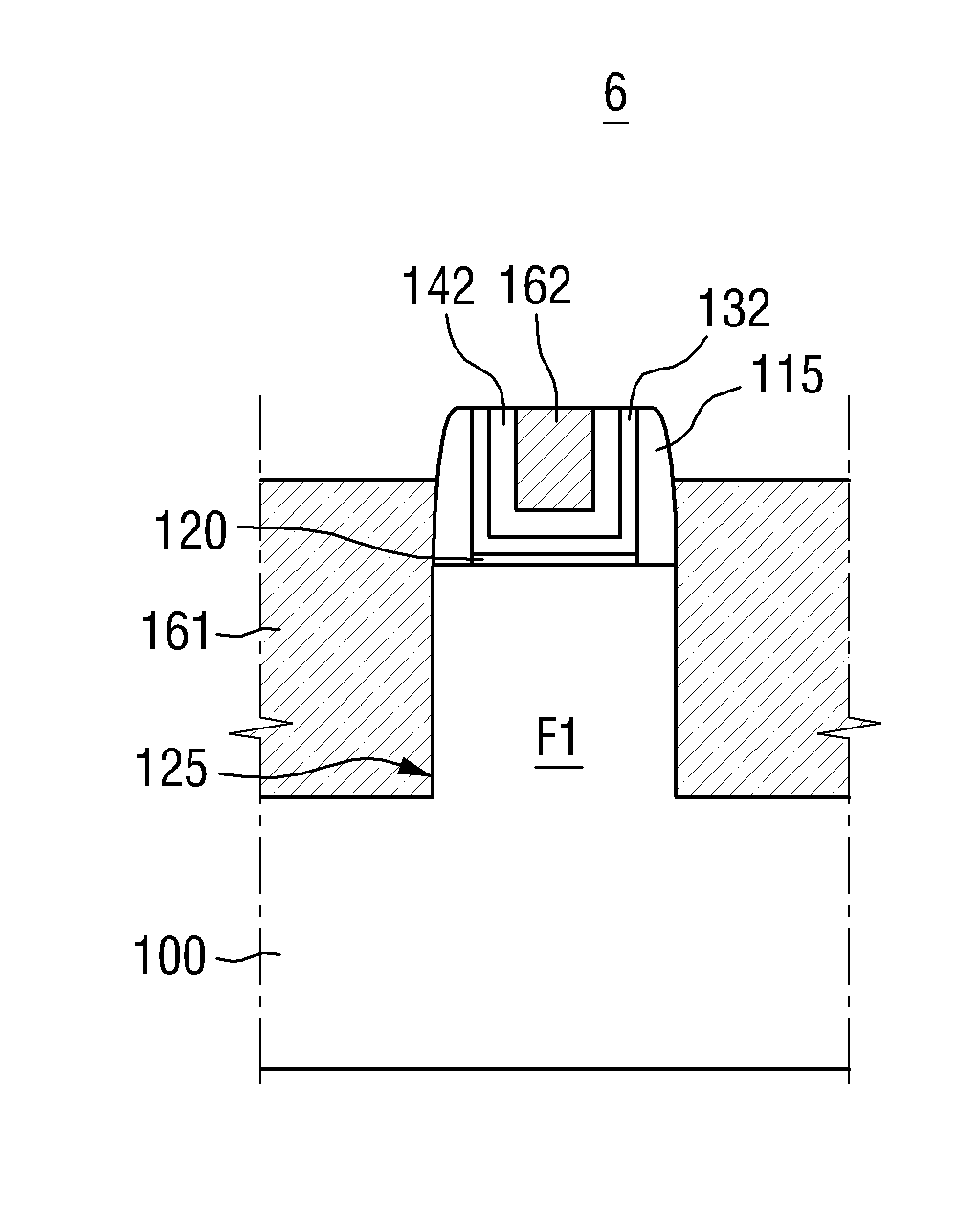

Semiconductor device and method of fabricating the same

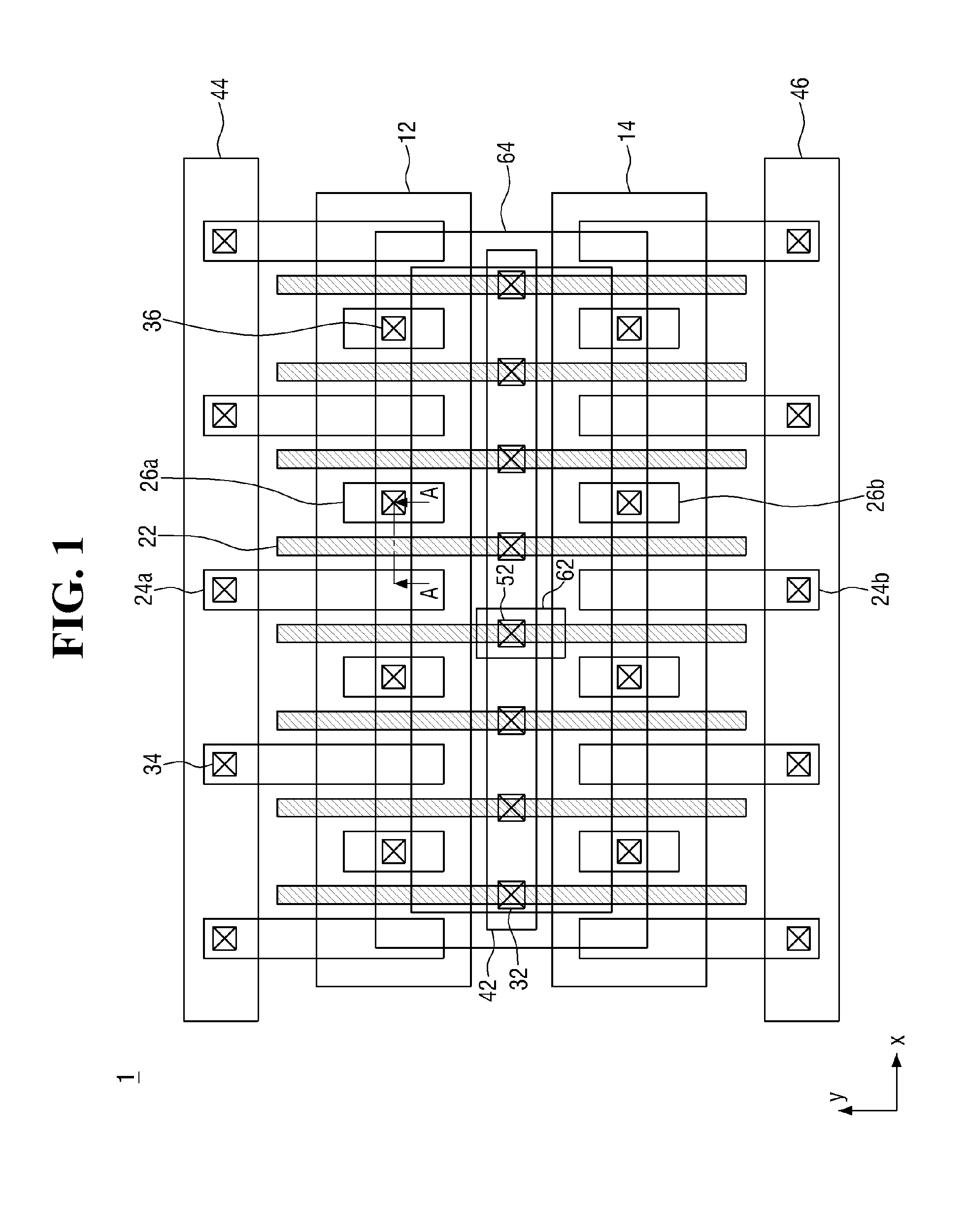

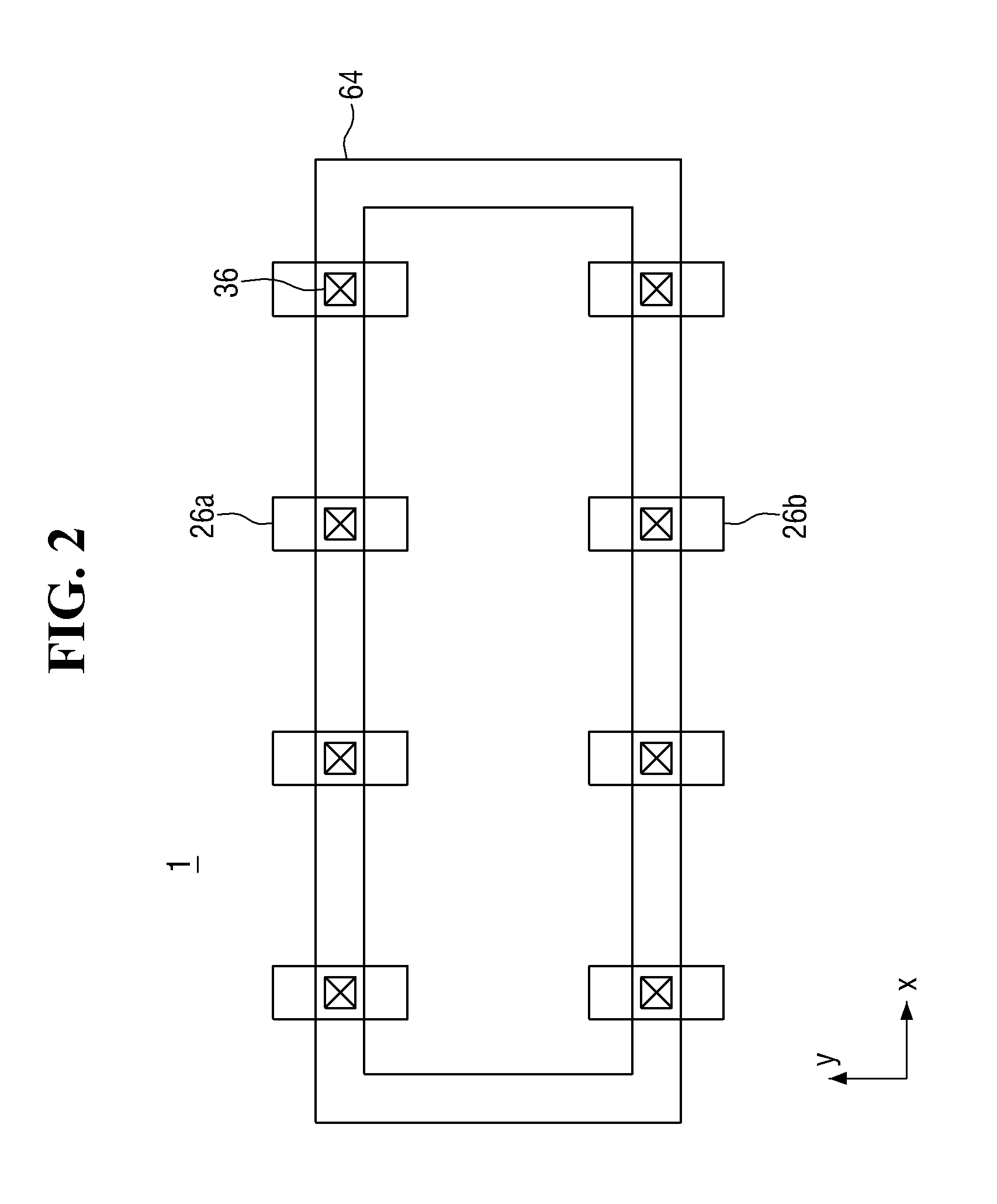

ActiveUS20150014775A1Reduce electromigrationTransistorSemiconductor/solid-state device detailsDevice materialClosed loop

Provided are a semiconductor device and a method of fabricating the semiconductor device. The semiconductor device includes a first source electrode configured to connect a first power rail to a first impurity region, the first power rail coupled to a first voltage source, a second source electrode configured to connect a second power rail to a second impurity region, the second power rail coupled to a second voltage source, the first and second voltage sources being different, a gate electrode on the first and second impurity regions, a first drain electrode on the first impurity region, a second drain electrode on the second impurity region and an interconnection line connected to the first drain electrode and the second drain electrode, the interconnection line forming at least one closed loop.

Owner:SAMSUNG ELECTRONICS CO LTD

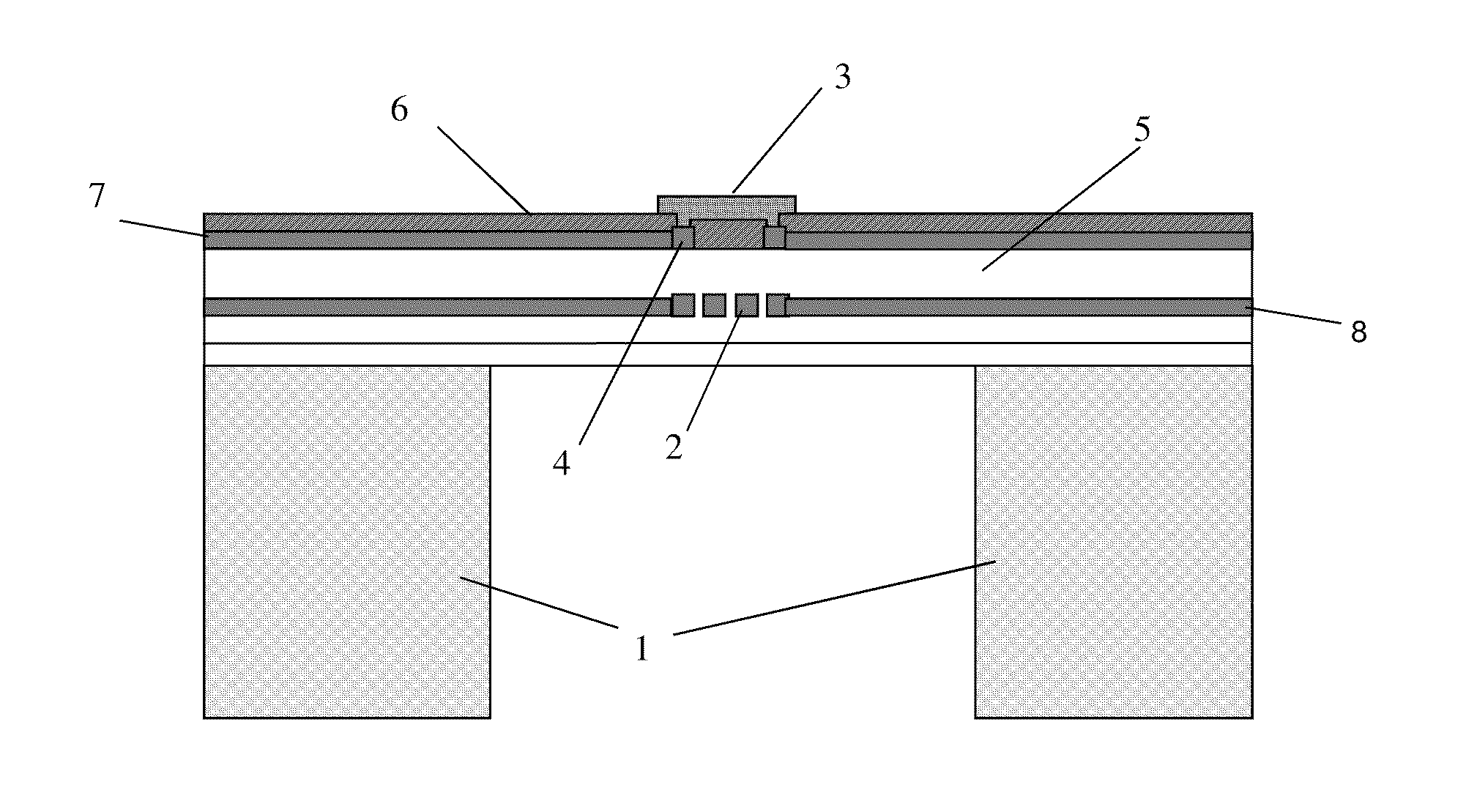

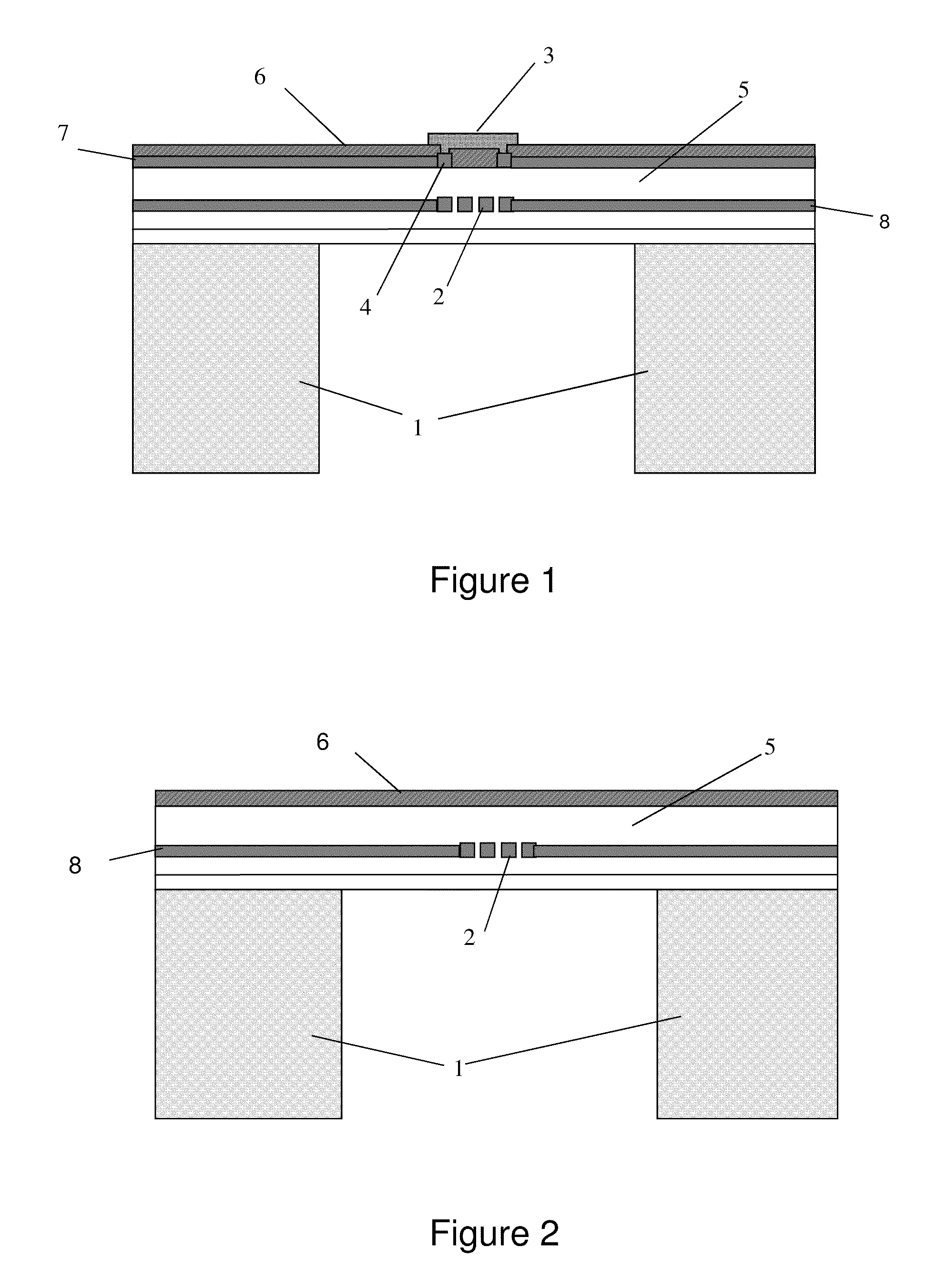

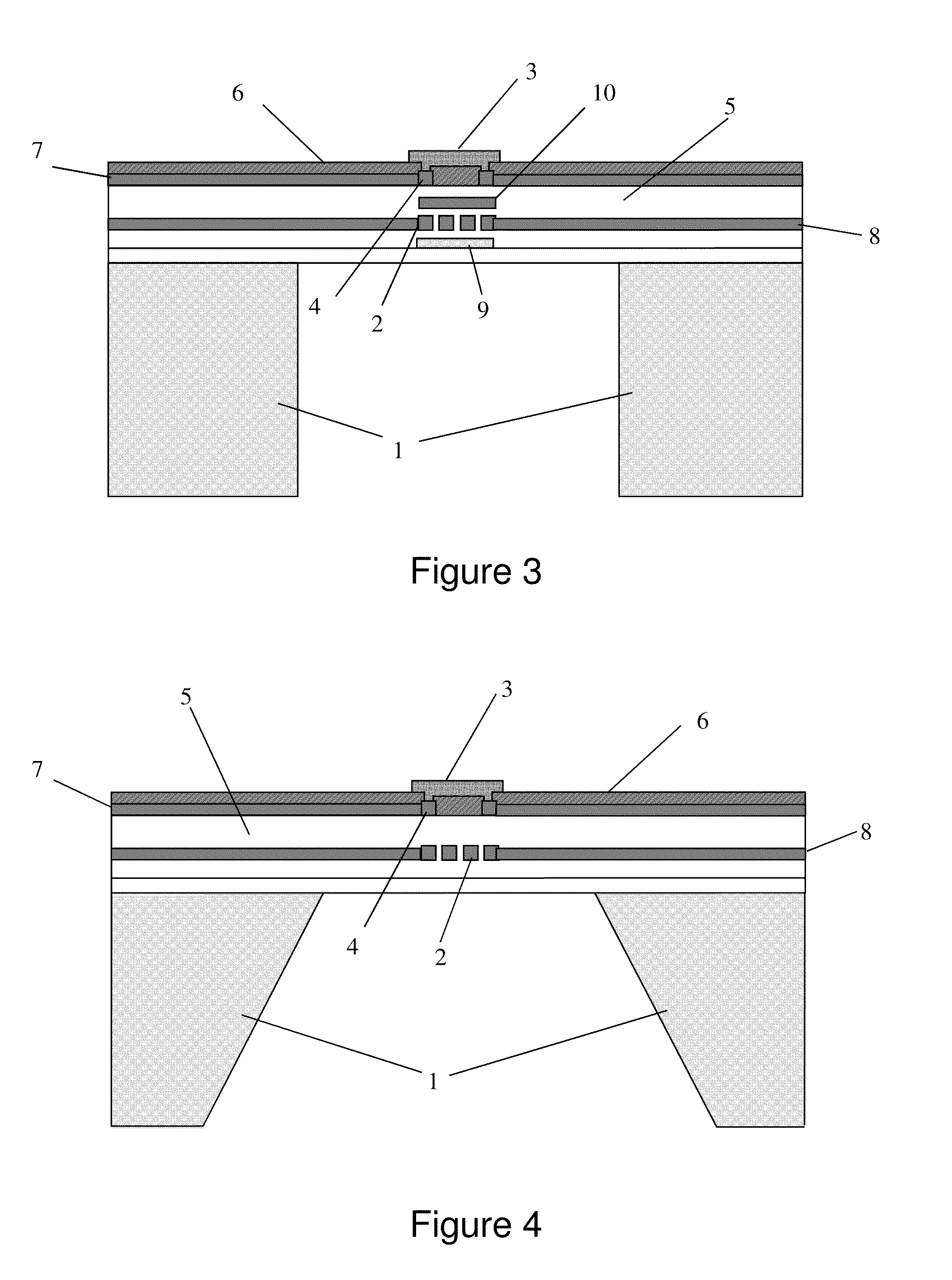

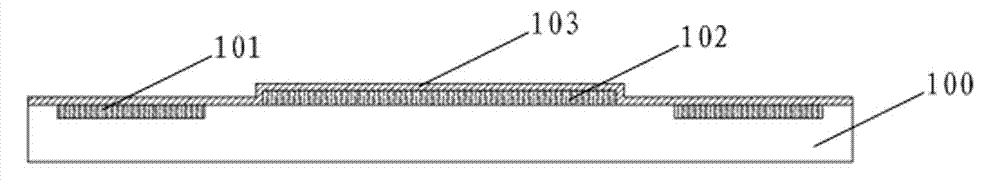

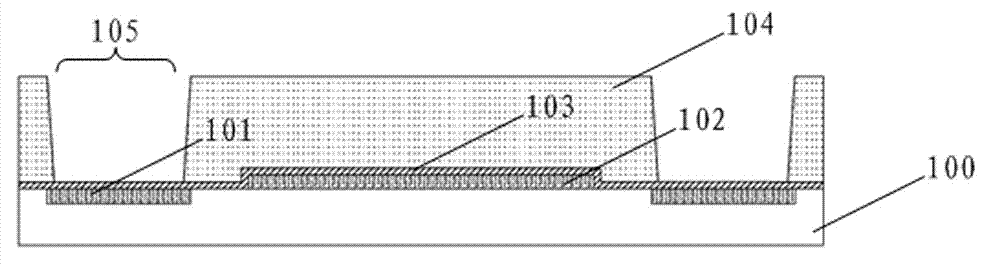

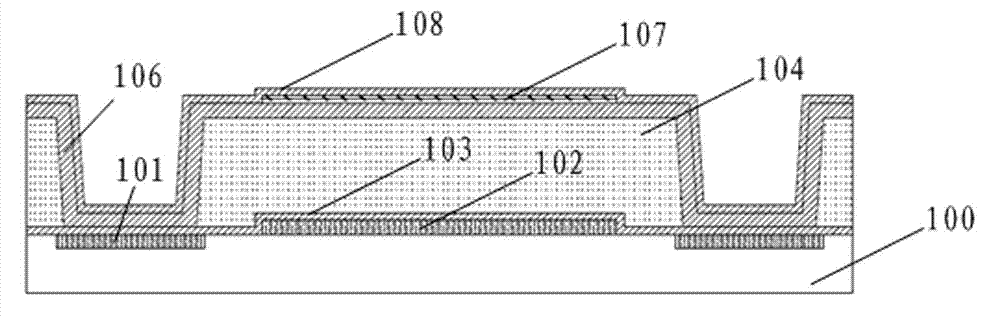

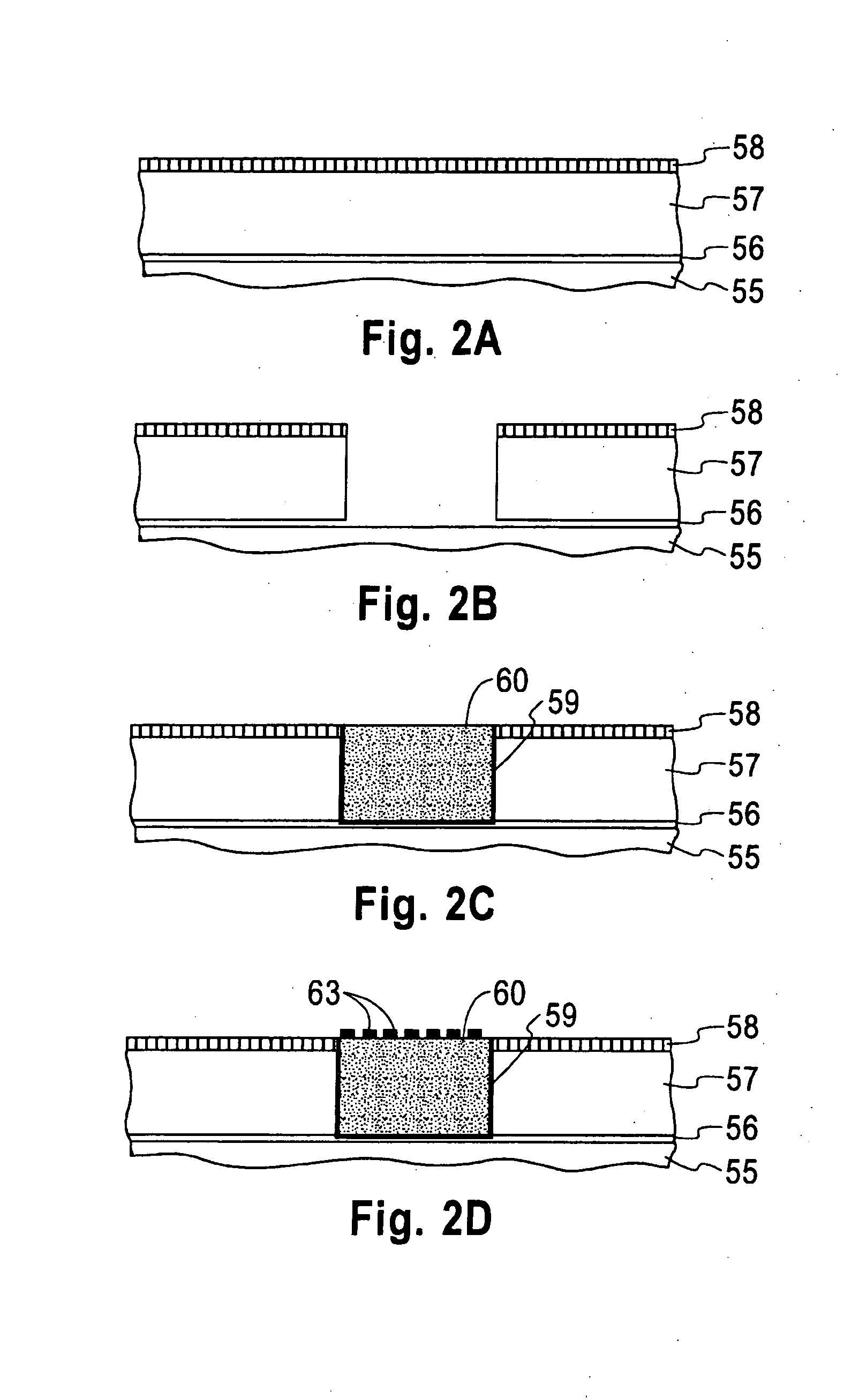

Preparation method of micro-bridge structured infrared detector, and micro-bridge structure

ActiveCN102951597AImprove mechanical propertiesEnhanced support thicknessDecorative surface effectsPyrometry using electric radation detectorsEtchingFilling materials

The invention relates to a preparation method of a micro-bridge structured infrared detector, and a micro-bridge structure. The method comprises the steps that: a metal reflective layer and a sacrificial layer are sequentially deposited on an infrared detector readout circuit substrate; PI holes are etched on the sacrificial layer, wherein the PI holes are positioned at an out-leading electrode of the readout circuit; a deposition support layer, a thermo-sensitive layer and a protective layer are sequentially deposited on the sacrificial layer; through holes are prepared in the PI holes, and a contact hole is prepared on the protective layer; electrode layer metal is deposited on the protective layer, and U-shaped metals with bridge pier structures are filled in the PI holes and the through holes; and U-shaped metal structures are formed through photolithography and etching; photolithography and etching is carried out upon the electrode layer metal; a passivation layer is deposited on the surface of the device, and the passivation layer is subjected to photolithography and etching, such that a passivation layer pattern is formed; and sacrificial layer releasing is carried out, such that the micro-bridge structure is formed. According to the invention, a U-shape filling method is adopted, and Al is adopted as a filling material. Therefore, sputtering and depositing are easy, and etching is convenient. The heat insulation property of the detector is better than that of a copper filling process, and a CMP step is not needed.

Owner:WUXI INFISENSE PERCEPTION TECH CO LTD

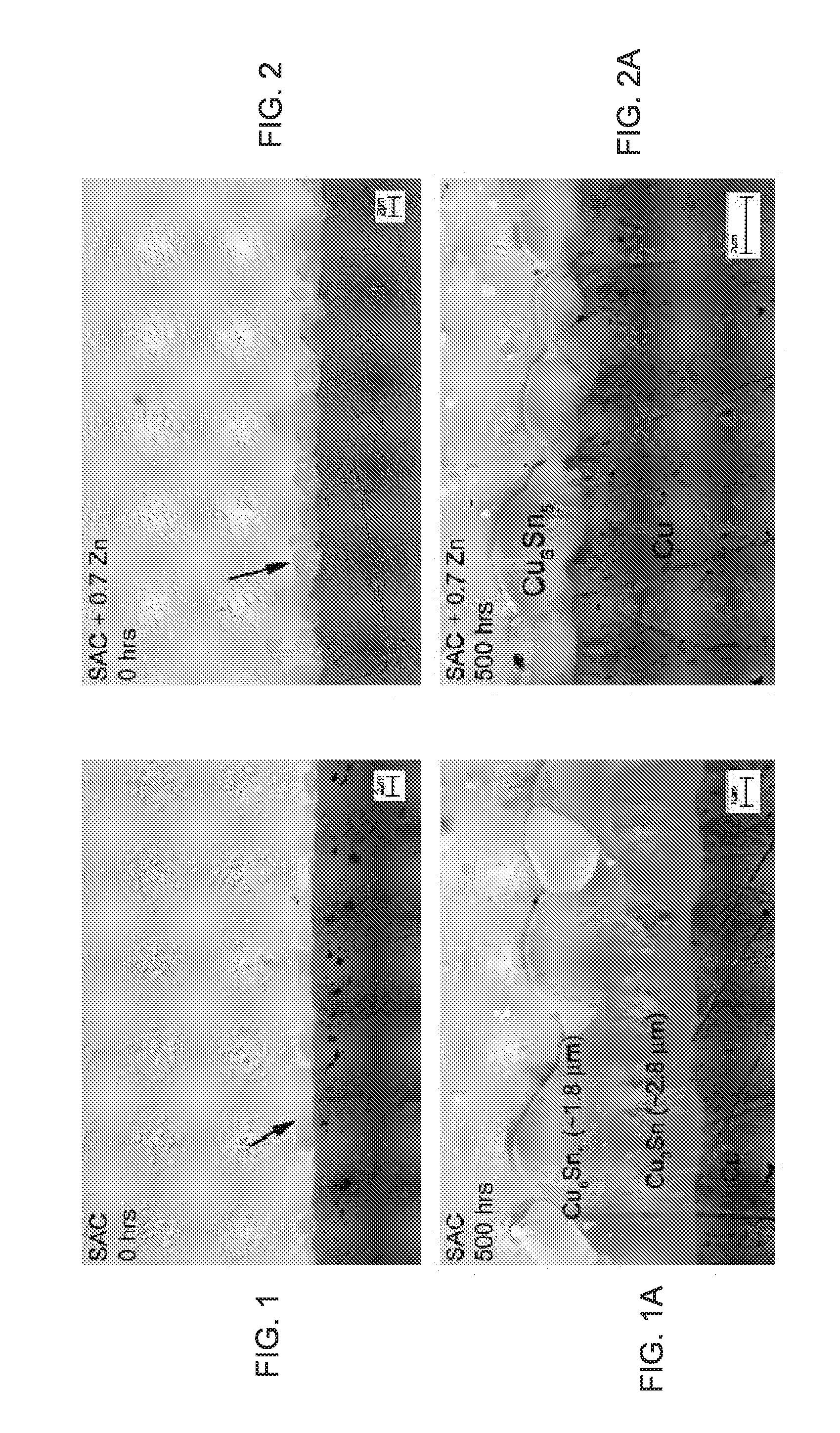

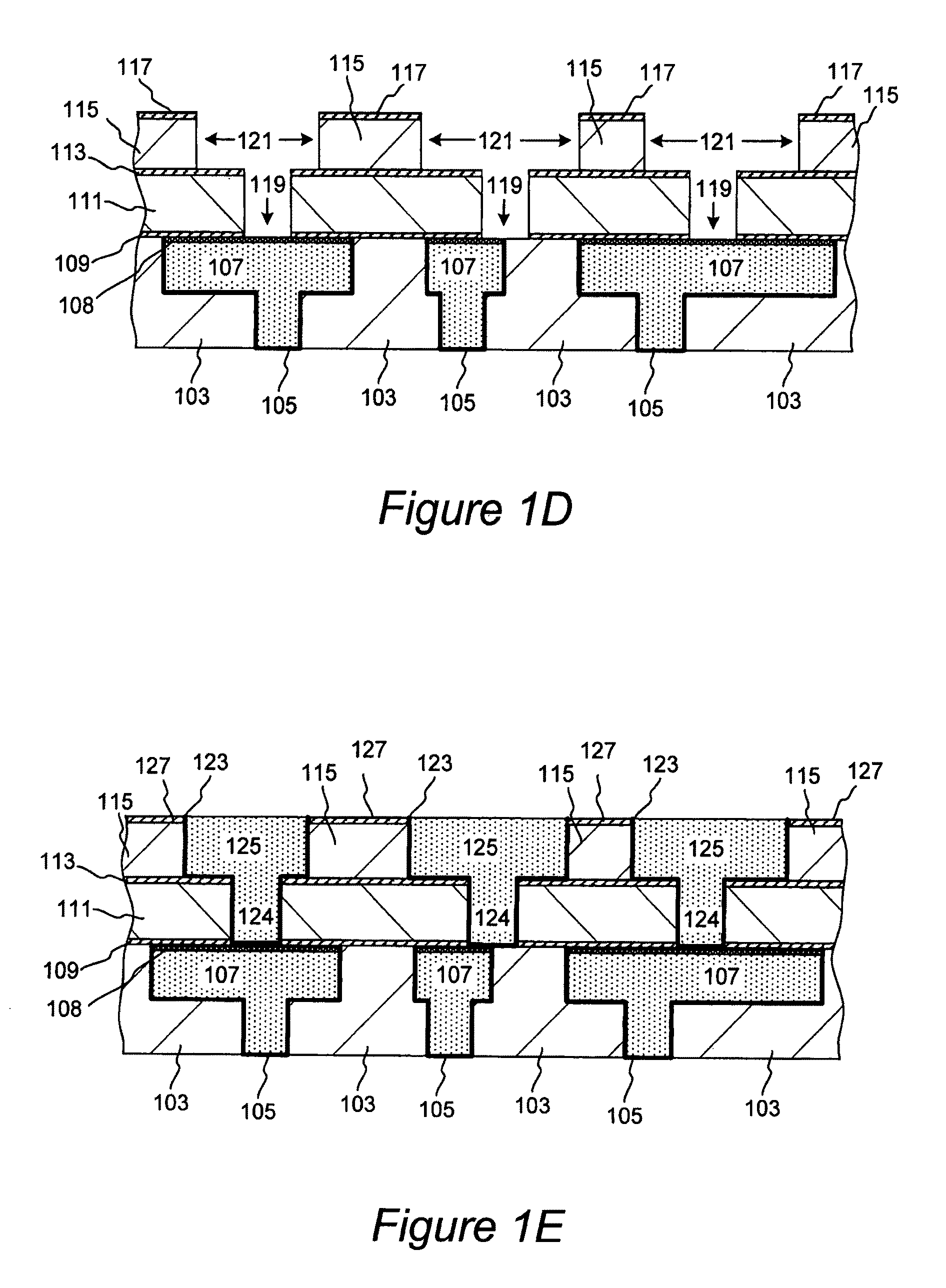

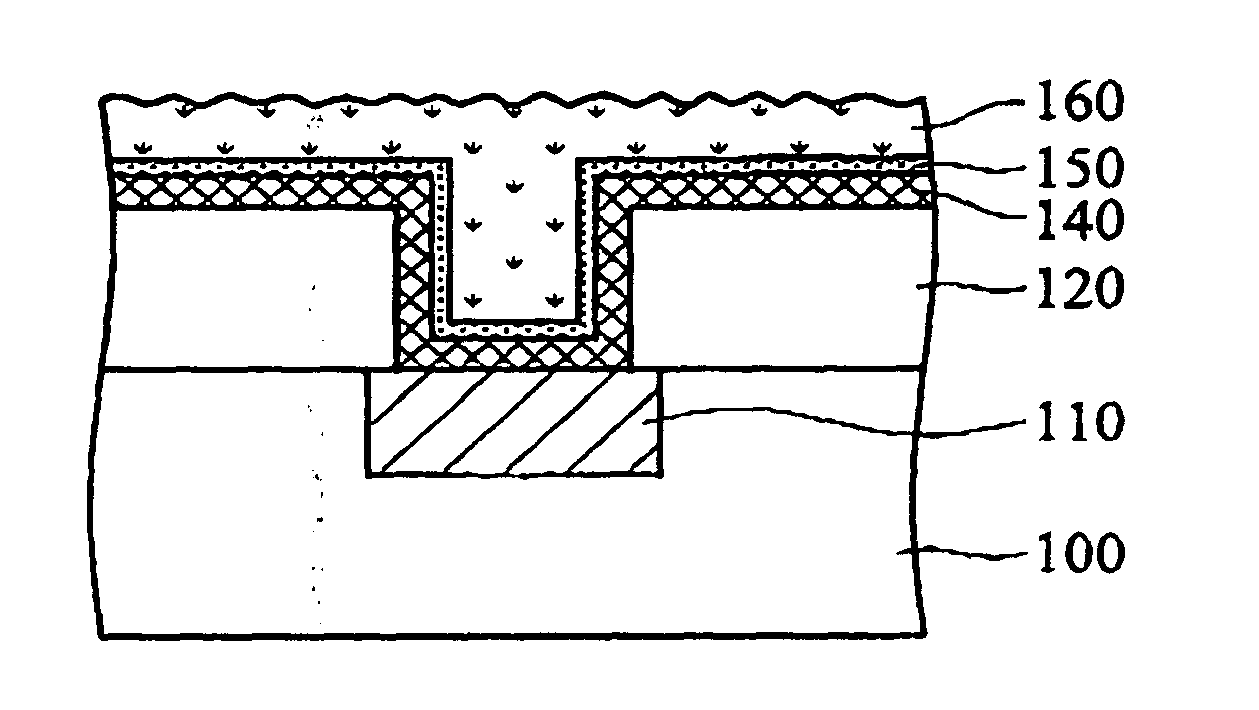

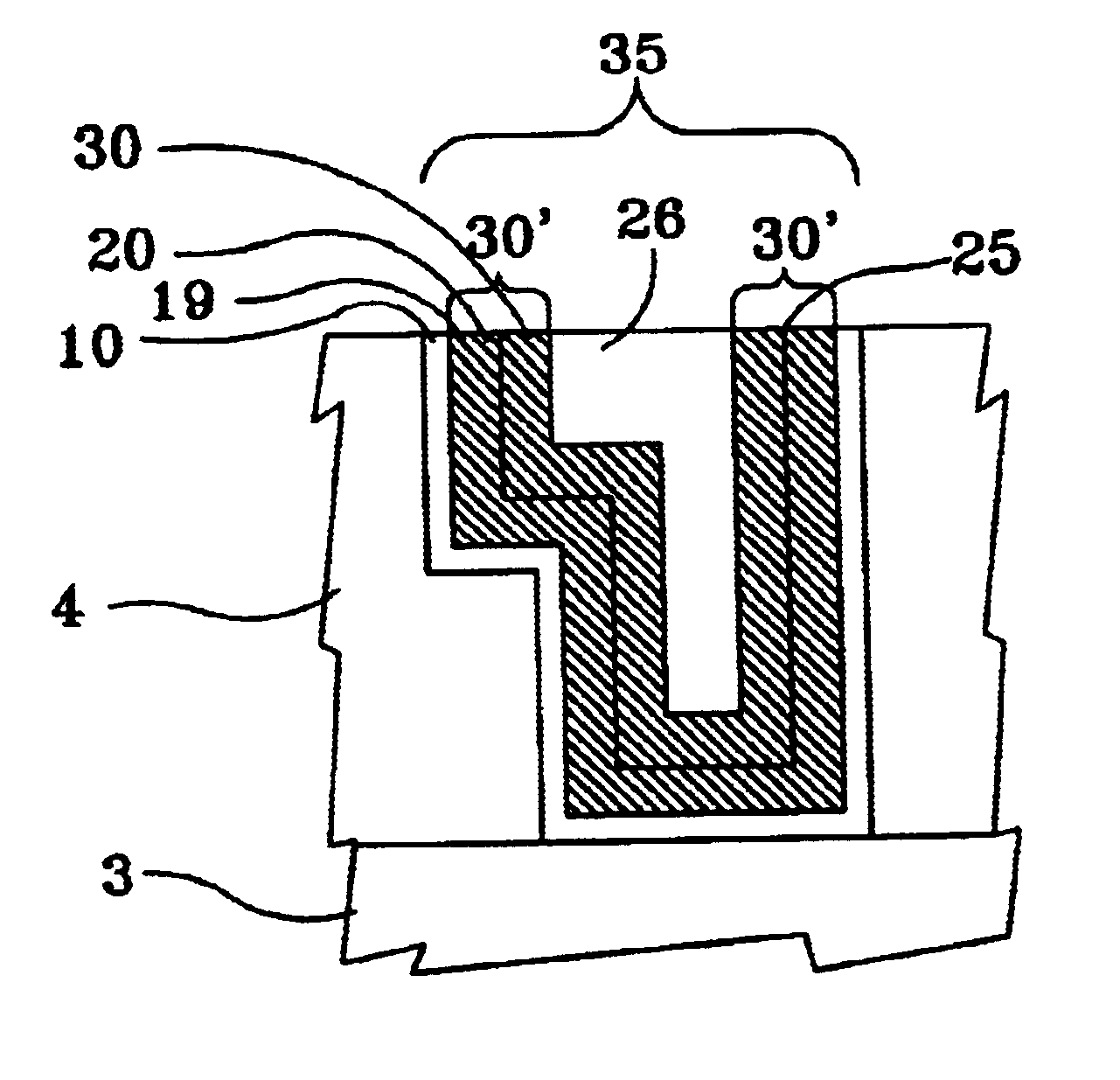

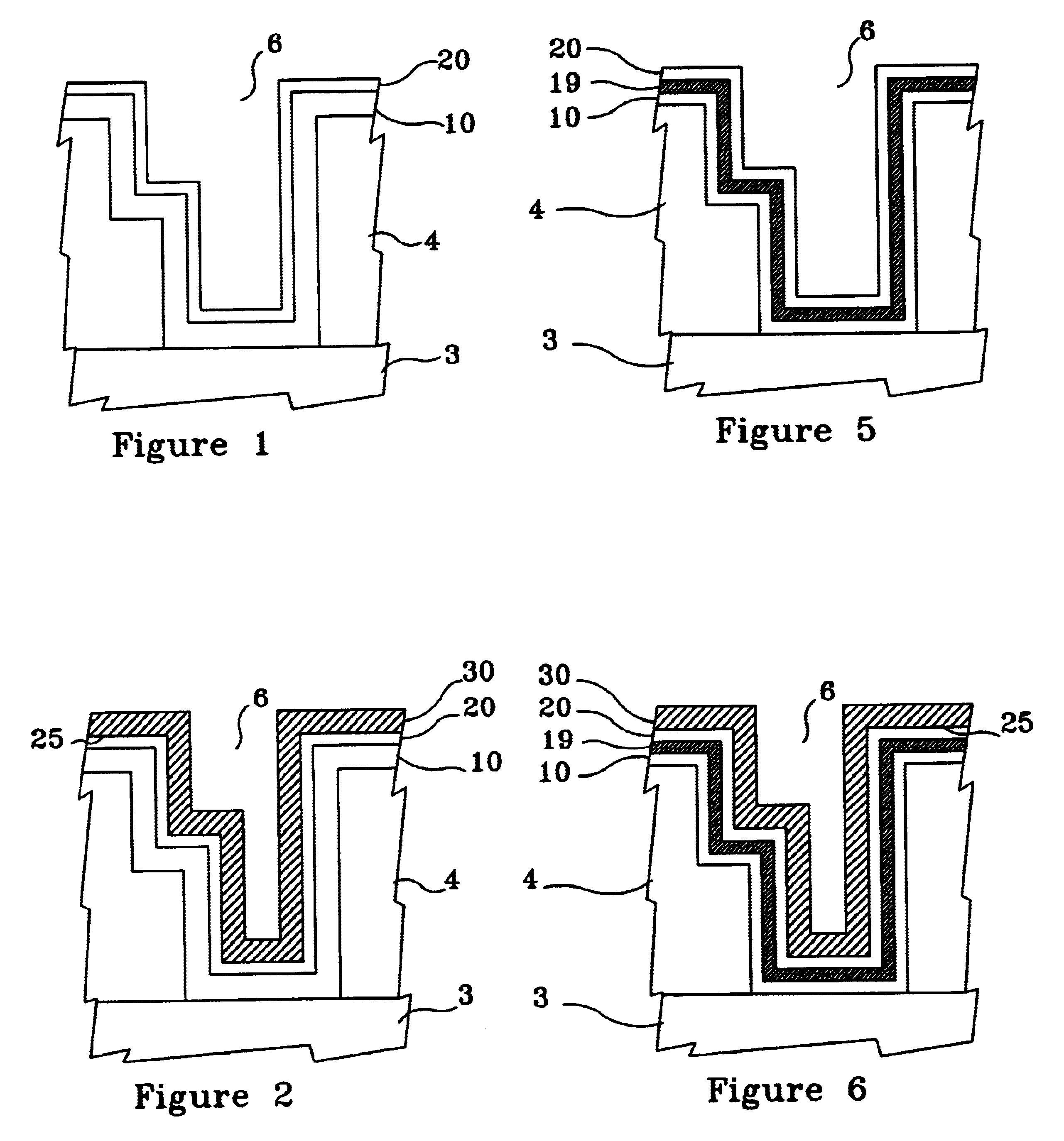

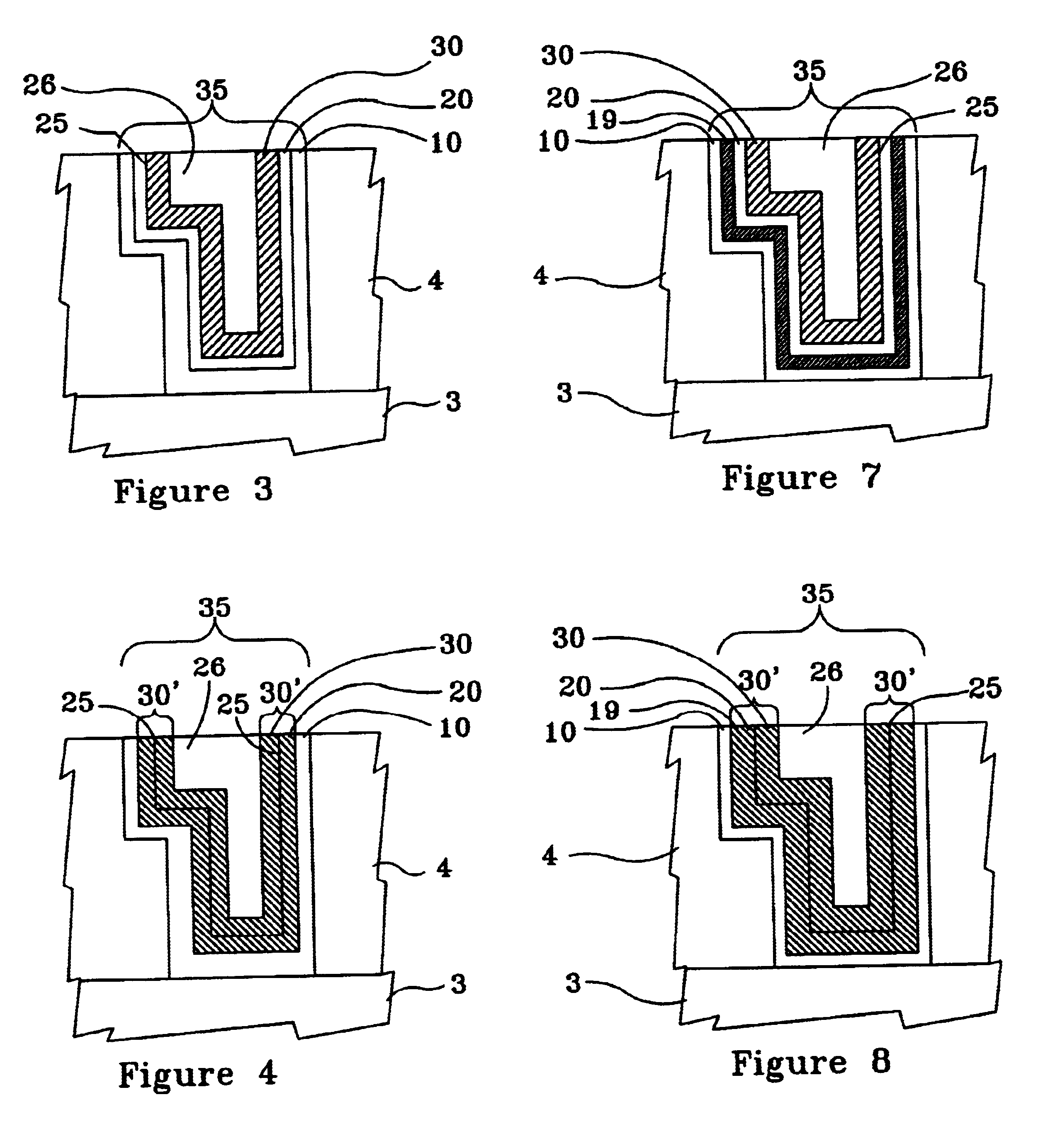

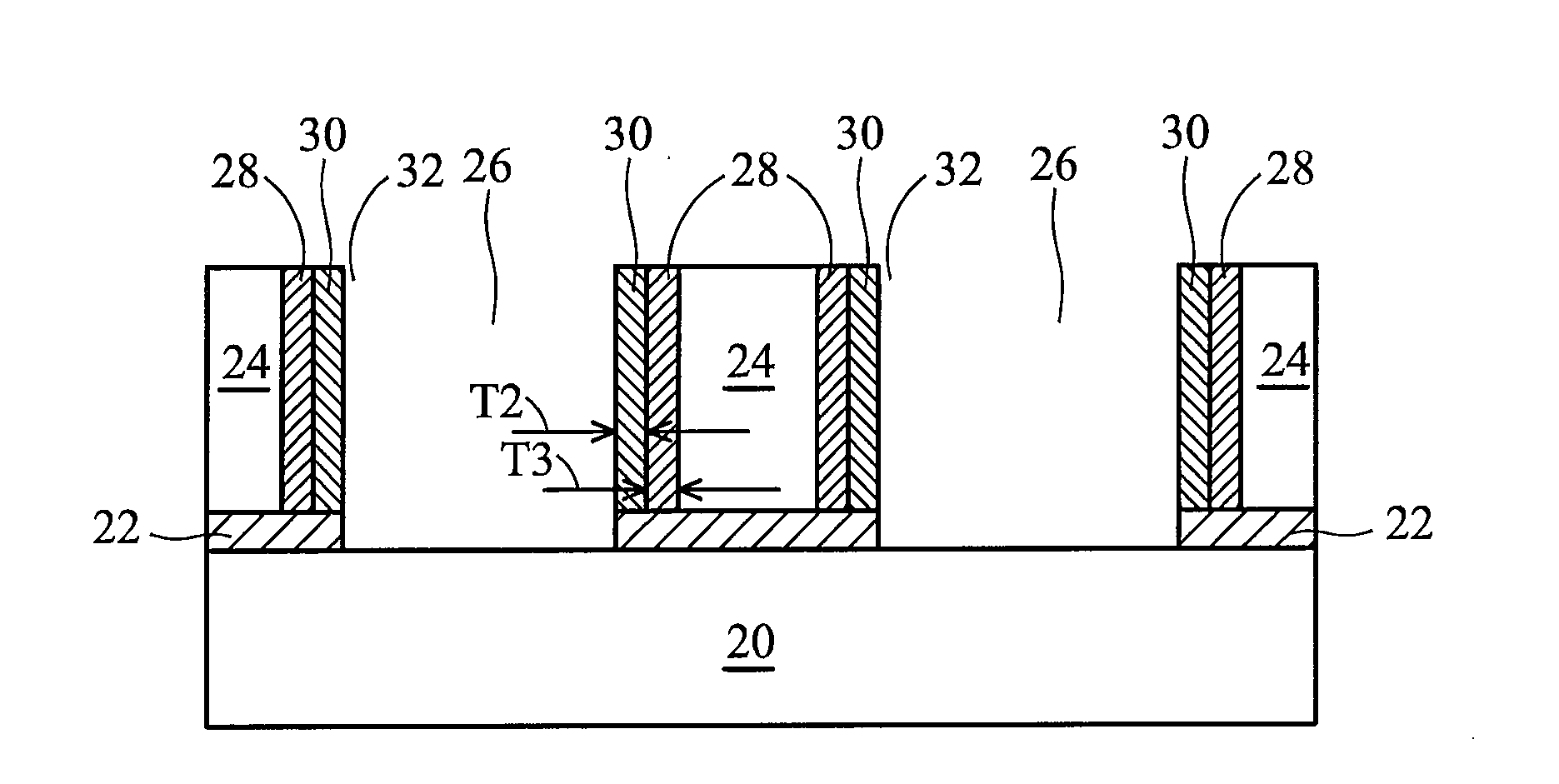

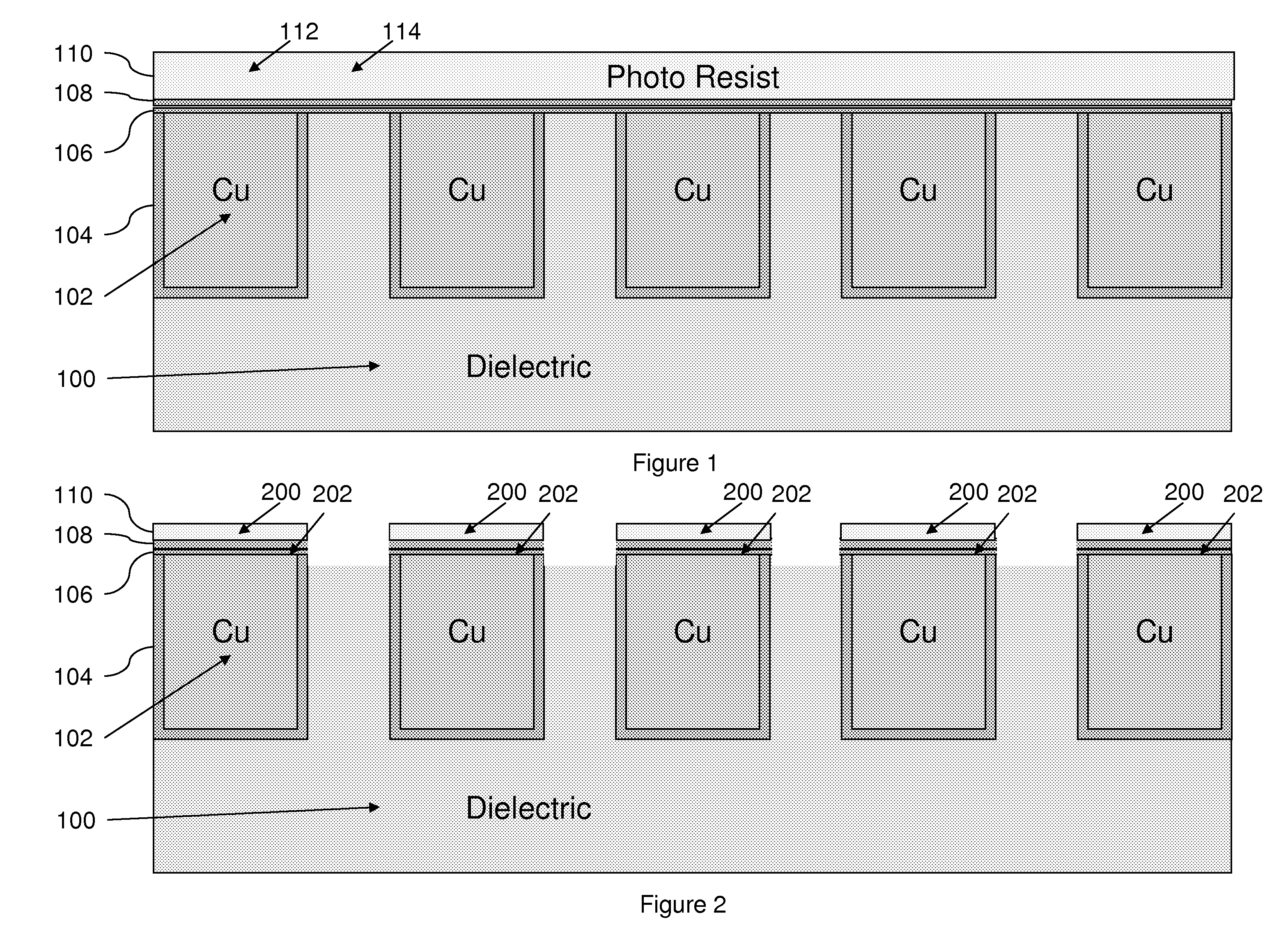

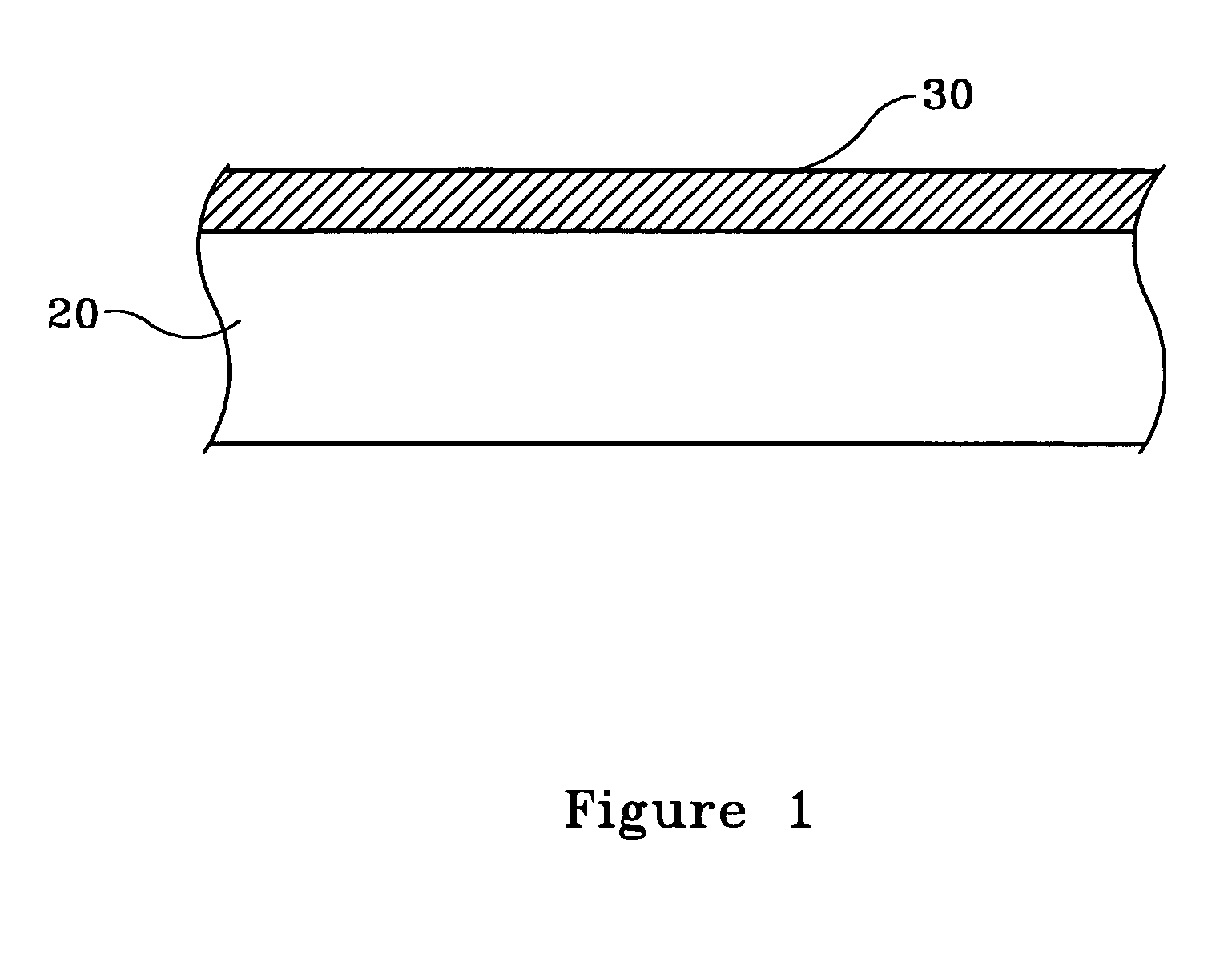

Method of reducing electromigration in a copper line by electroplating an interim copper-zinc alloy thin film on a copper surface and a semiconductor device thereby formed

InactiveUS6660633B1Improves Cu interconnect reliabilityReduce manufacturing costElectrolysis componentsSolid-state devicesCopper interconnectChemical solution

A method of fabricating a semiconductor device, having an interim reduced-oxygen Cu-Zn alloy thin film (30) electroplated on a blanket Cu surface (20) disposed in a via (6) by electroplating, using an electroplating apparatus, the Cu surface (20) in a unique chemical solution containing salts of Zn and Cu, their complexing agents, a pH adjuster, and surfactants; and annealing the interim electroplated Cu-Zn alloy thin film (30); filling the via (6) with further Cu (26); annealing and planarizing the interconnect structure (35); and a semiconductor device thereby formed. The reduction of electromigration in copper interconnect lines (35) is achieved by decreasing the drift velocity in the copper line (35) / via (6), thereby decreasing the copper migration rate as well as the void formation rate, by using an interim conformal Cu-rich Cu-Zn alloy thin film (30) electroplated on a Cu surface (20) from a stable chemical solution, and by controlling the Zn-doping thereof, which improves also interconnect reliability and corrosion resistance.

Owner:GLOBALFOUNDRIES US INC

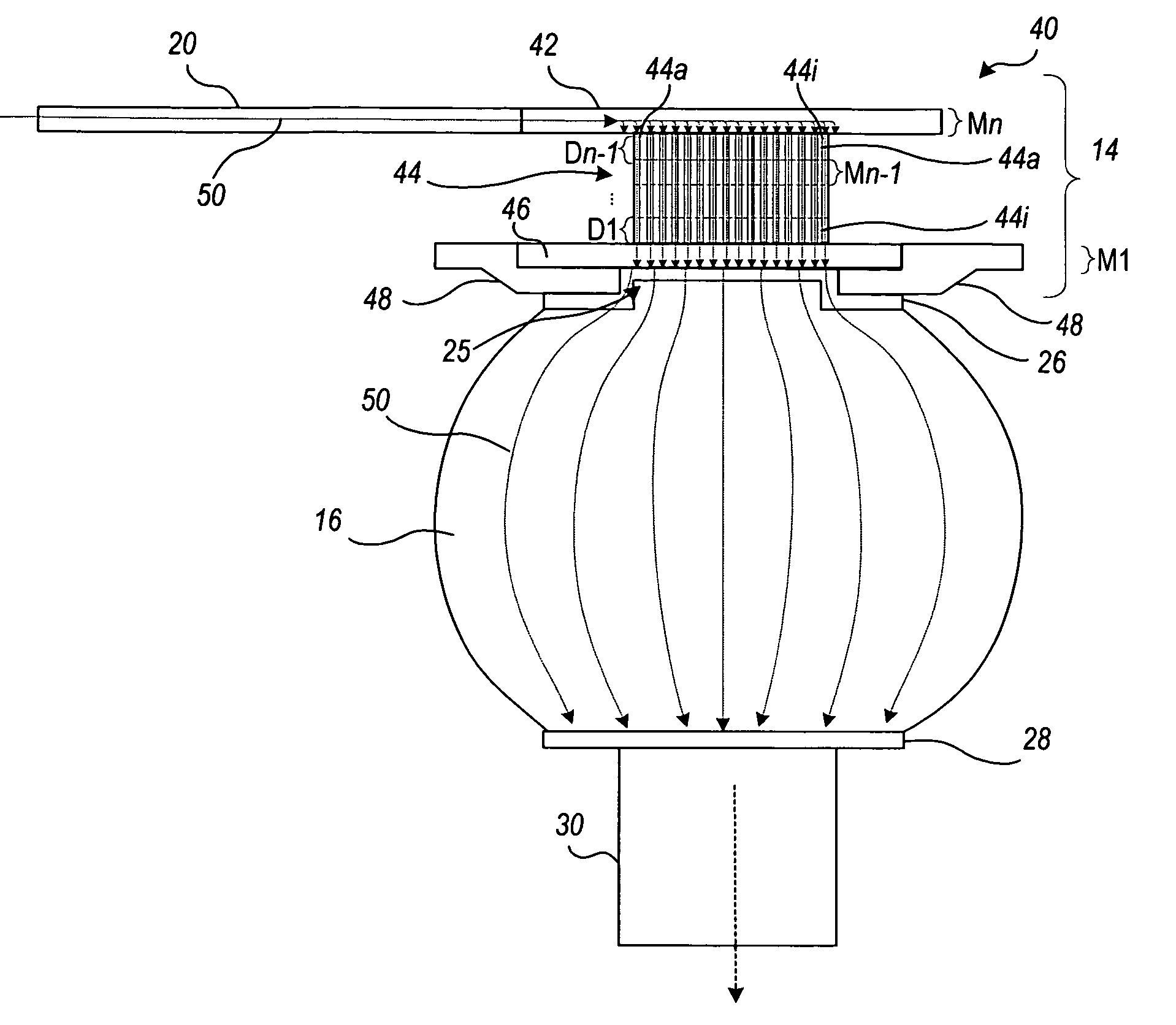

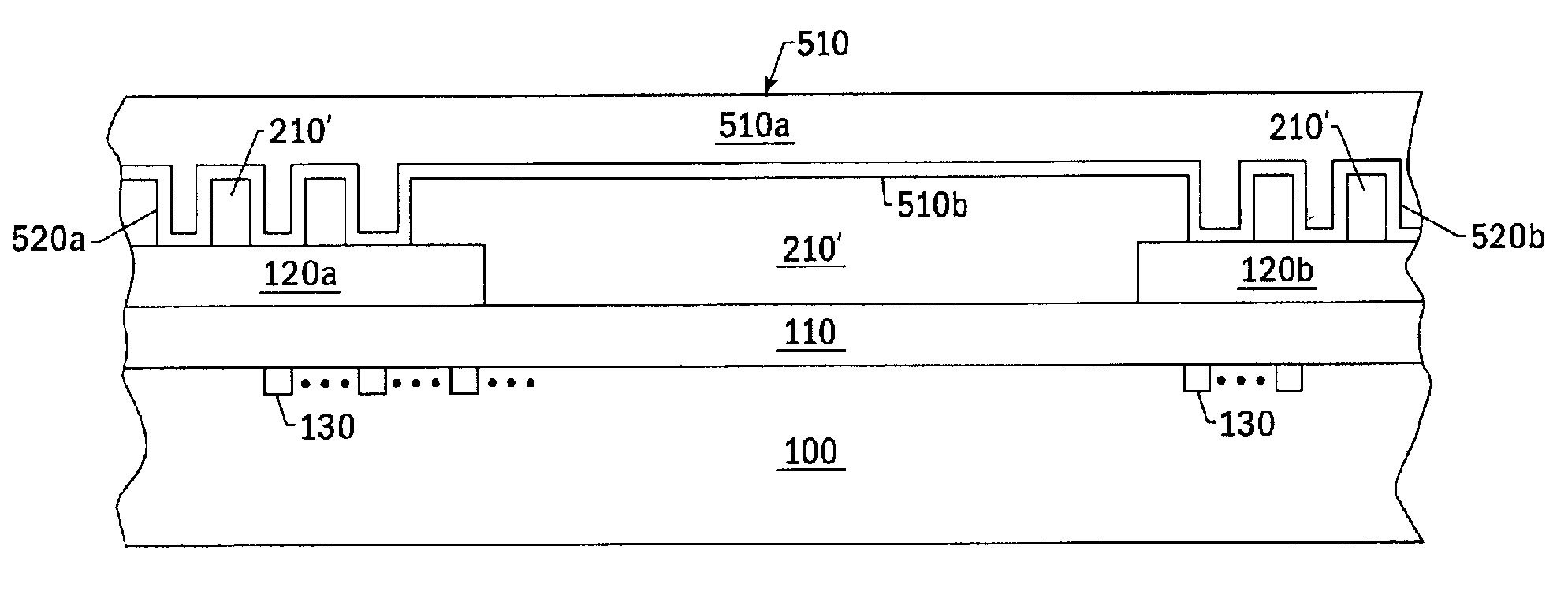

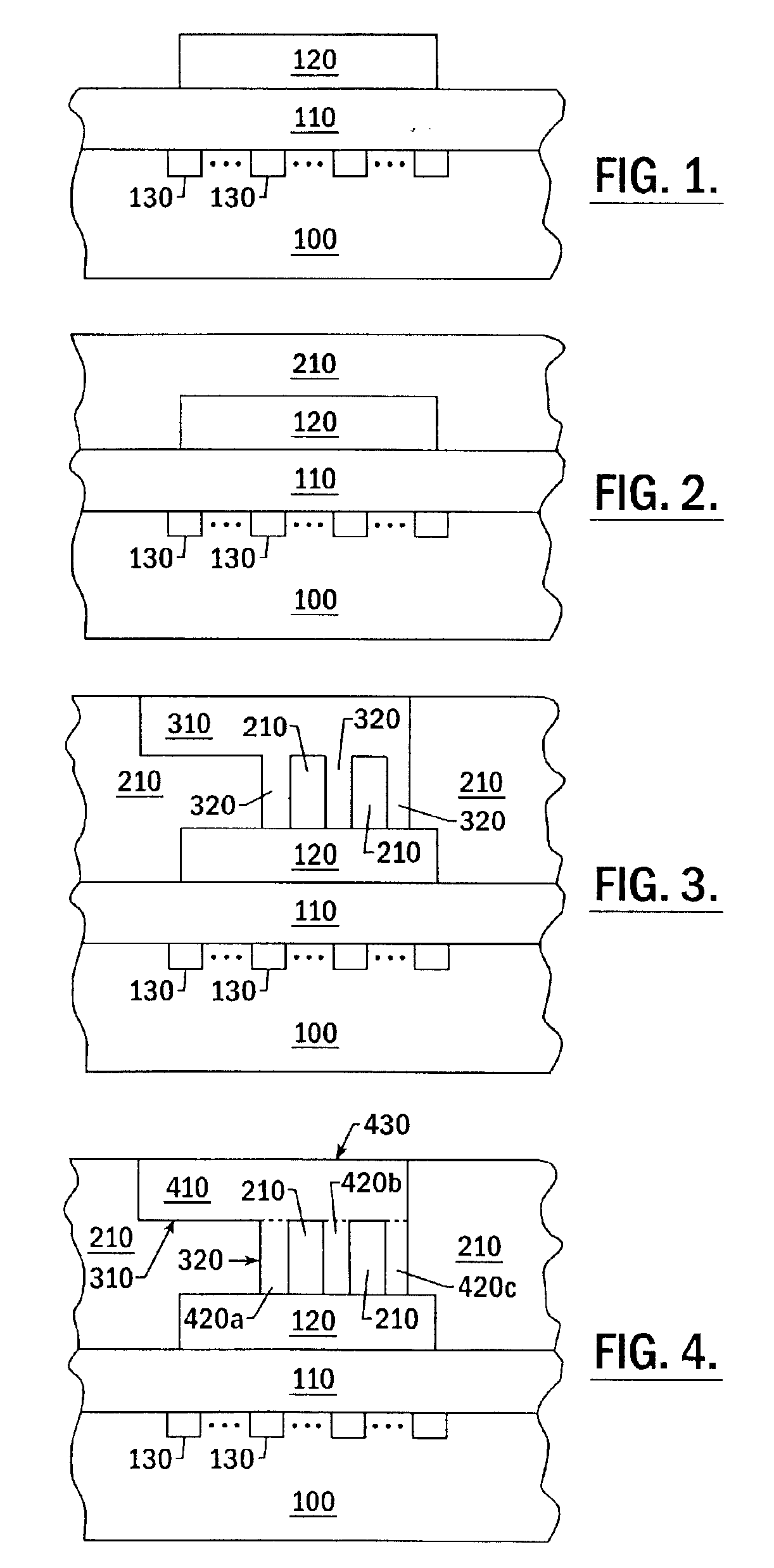

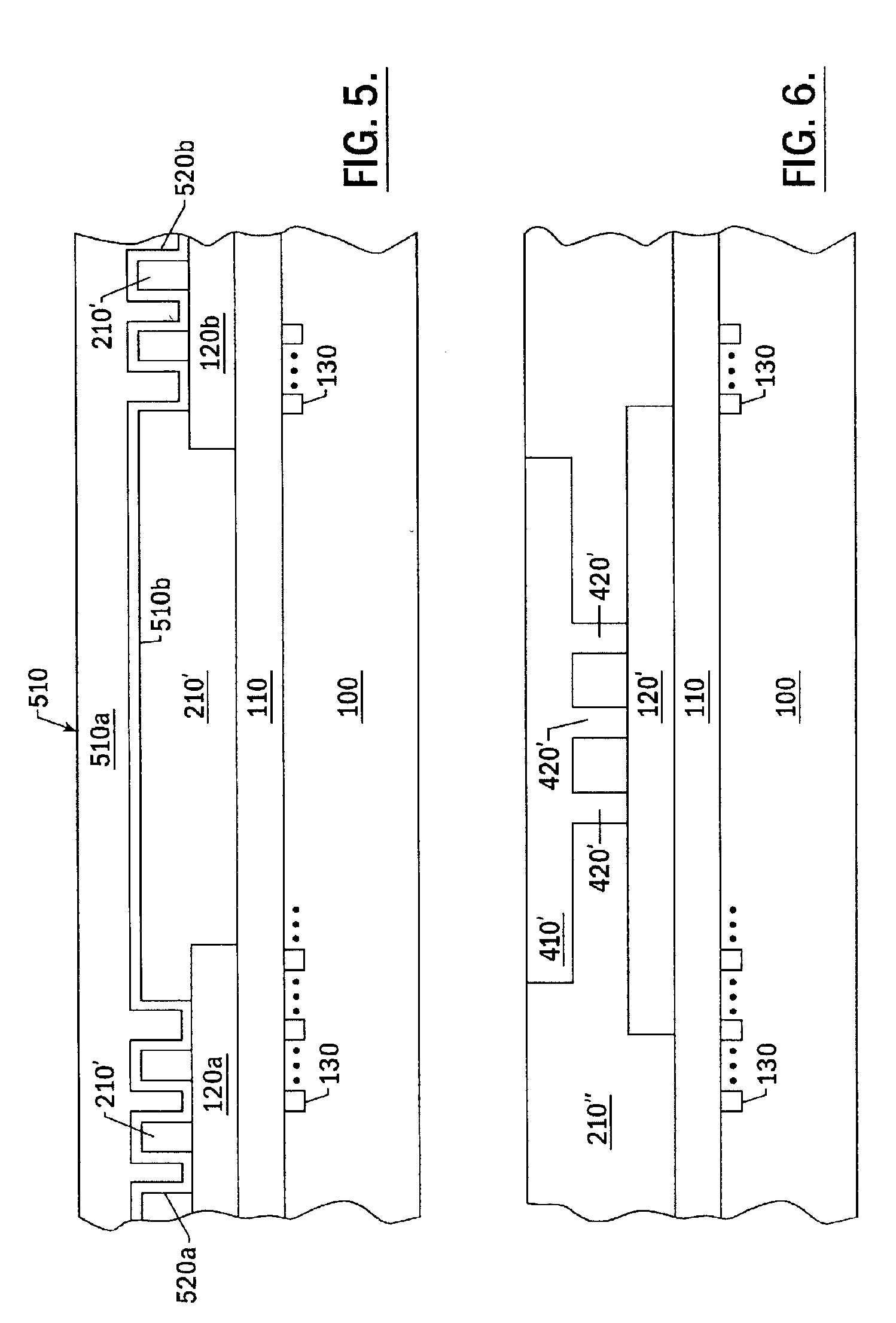

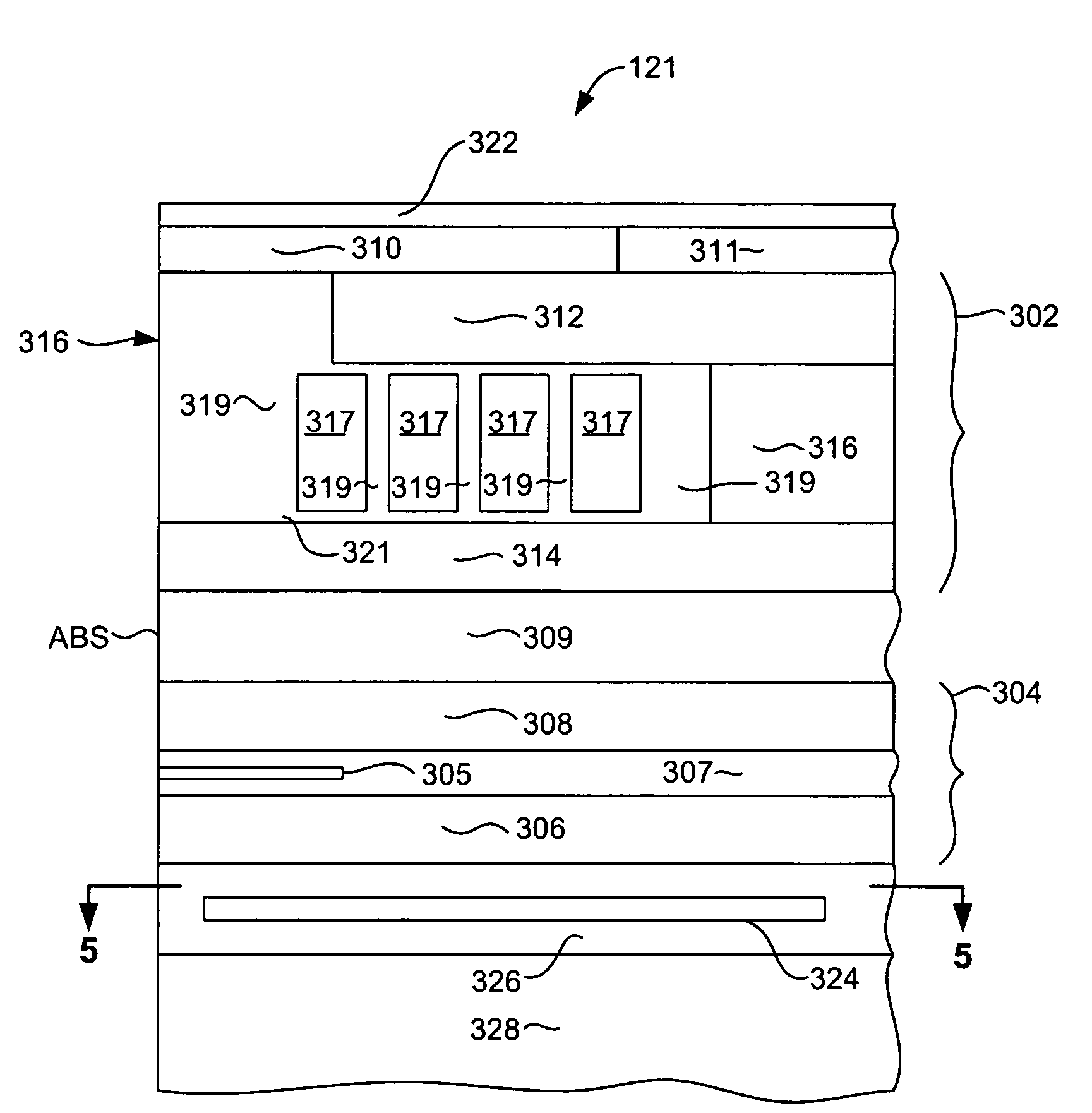

Metal wiring structures for uniform current density in c4 balls

ActiveUS20100263913A1Improve reliabilityFacilitates uniform current density distributionSemiconductor/solid-state device detailsSolid-state devicesElectricityElectrical connection

In one embodiment, a sub-pad assembly of metal structures is located directly underneath a metal pad. The sub-pad assembly includes an upper level metal line structure abutting the metal pad, a lower level metal line structure located underneath the upper level metal line structure, and a set of metal vias that provide electrical connection between the lower level metal line structure located underneath the upper level metal line structure. In another embodiment, the reliability of a C4 ball is enhanced by employing a metal pad structure having a set of integrated metal vias that are segmented and distributed to facilitate uniform current density distribution within the C4 ball. The area1 density of the cross-sectional area in the plurality of metal vias is higher at the center portion of the metal pad than at the peripheral portion of the planar portion of the metal pad.

Owner:GLOBALFOUNDRIES US INC

On-chip Cu interconnection using 1 to 5 nm thick metal cap

ActiveUS7247946B2Improve electromigrationIncrease resistanceSemiconductor/solid-state device detailsSolid-state devicesDielectricSolubility

Disclosed is a procedure to coat the free surface of Cu damascene lines by a 1-5 nm thick element prior to deposition of the inter-level dielectric or dielectric diffusion barrier layer. The coating provides protection against oxidation, increases the adhesion strength between the Cu and dielectric, and reduces interface diffusion of Cu. In addition, the thin cap layer further increases electromigration Cu lifetime and reduces the stress induced voiding. The selective elements can be directly deposited onto the Cu embedded within the under layer dielectric without causing an electric short circuit between the Cu lines. These chosen elements are based on their high negative reduction potentials with oxygen and water, and a low solubility in and formation of compounds with Cu.

Owner:GLOBALFOUNDRIES US INC

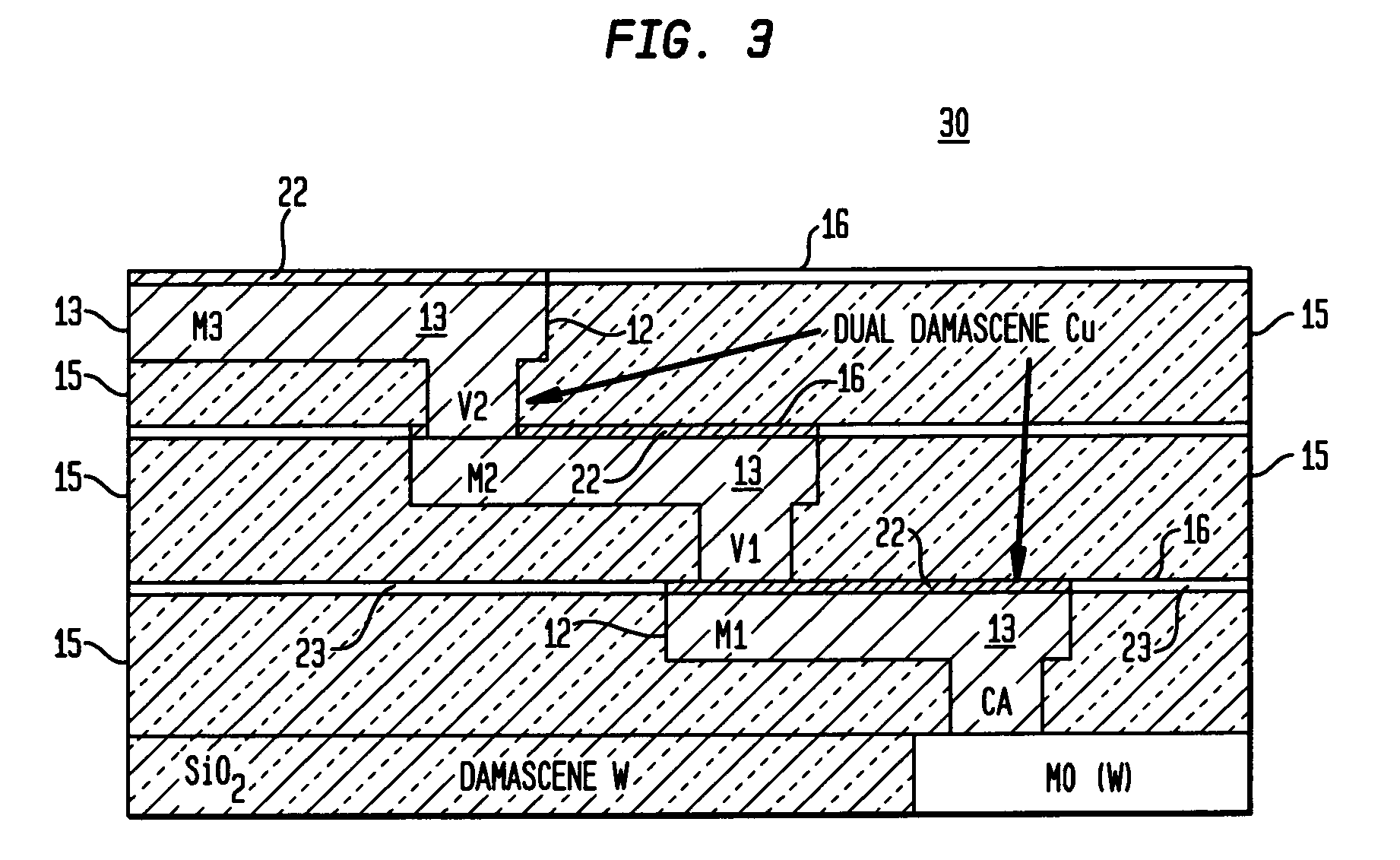

Siloxane epoxy polymers as metal diffusion barriers to reduce electromigration

ActiveUS20050236711A1Reduce electromigrationGood performanceSemiconductor/solid-state device detailsSolid-state devicesElectromigrationSiloxane

Structures employing siloxane epoxy polymers as diffusion barriers adjacent conductive metal layers are disclosed. The siloxane epoxy polymers exhibit excellent adhesion to conductive metals, such as copper, and provide an increase in the electromigration lifetime of metal lines. In addition, the siloxane epoxy polymers have dielectric constants less then 3, and thus, provide improved performance over conventional diffusion barriers.

Owner:POLYSET +1

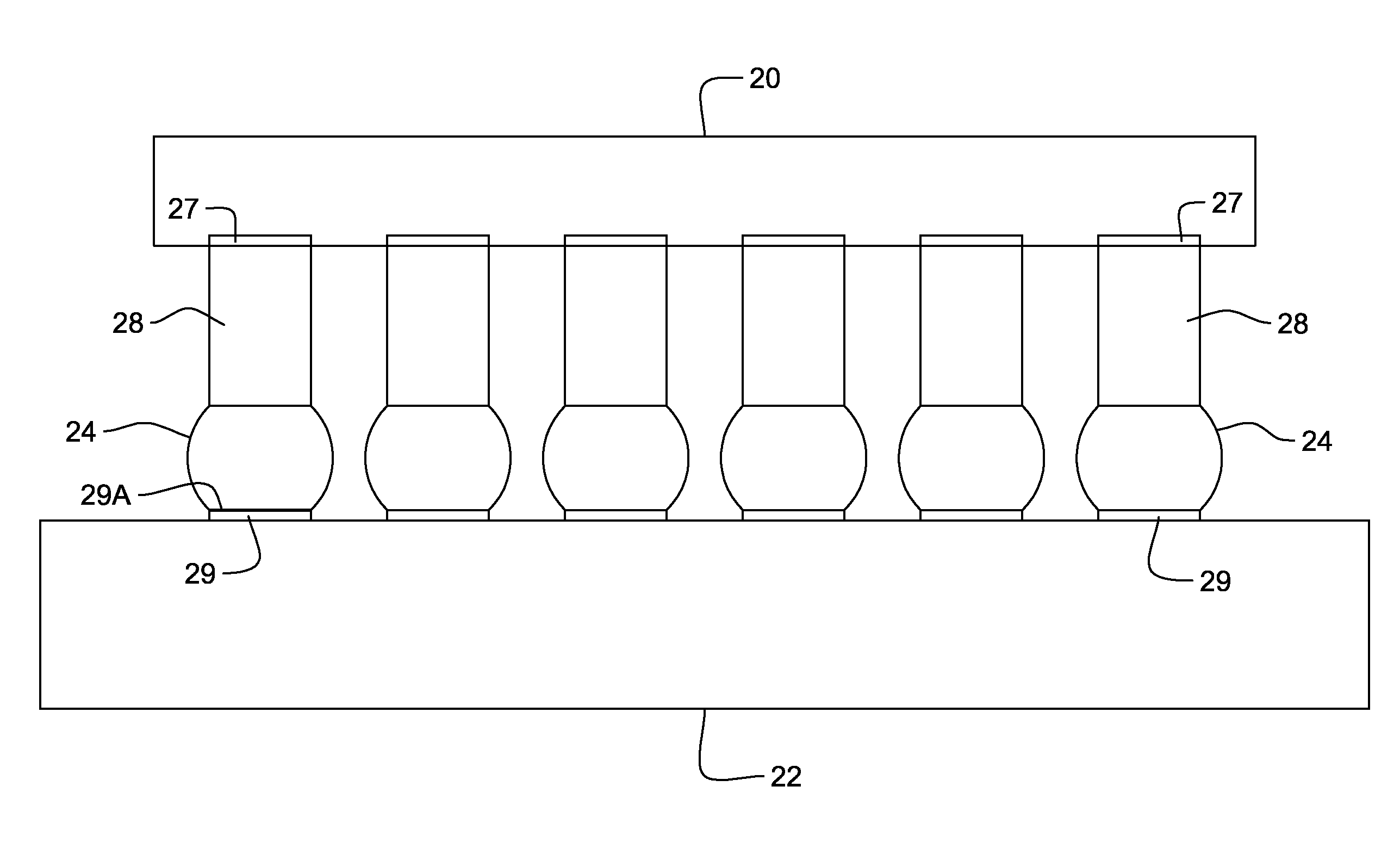

Routing design to minimize electromigration damage to solder bumps

ActiveUS7208843B2Total current dropReduce electromigrationSemiconductor/solid-state device detailsSolid-state devicesCurrent distributionEngineering

A novel pad structure for an integrated circuit component that utilizes a bump interconnect for connection to other integrated circuit components that produces a relatively uniform current distribution within the bump of the bump interconnect is presented. The pad structure includes an inner pad implemented on an inner conductive layer of the integrated circuit component, an outer pad implemented on an outer conductive layer of the integrated circuit component, and a plurality of vias connecting the inner pad and outer pad. The outer pad is sealed preferably around its edges with a passivation layer, which includes an opening exposing a portion of the outer pad. The vias connecting the inner pad and outer pad are preferably implemented to lie in a via region within the footprint of the pad opening.

Owner:AVAGO TECH INT SALES PTE LTD

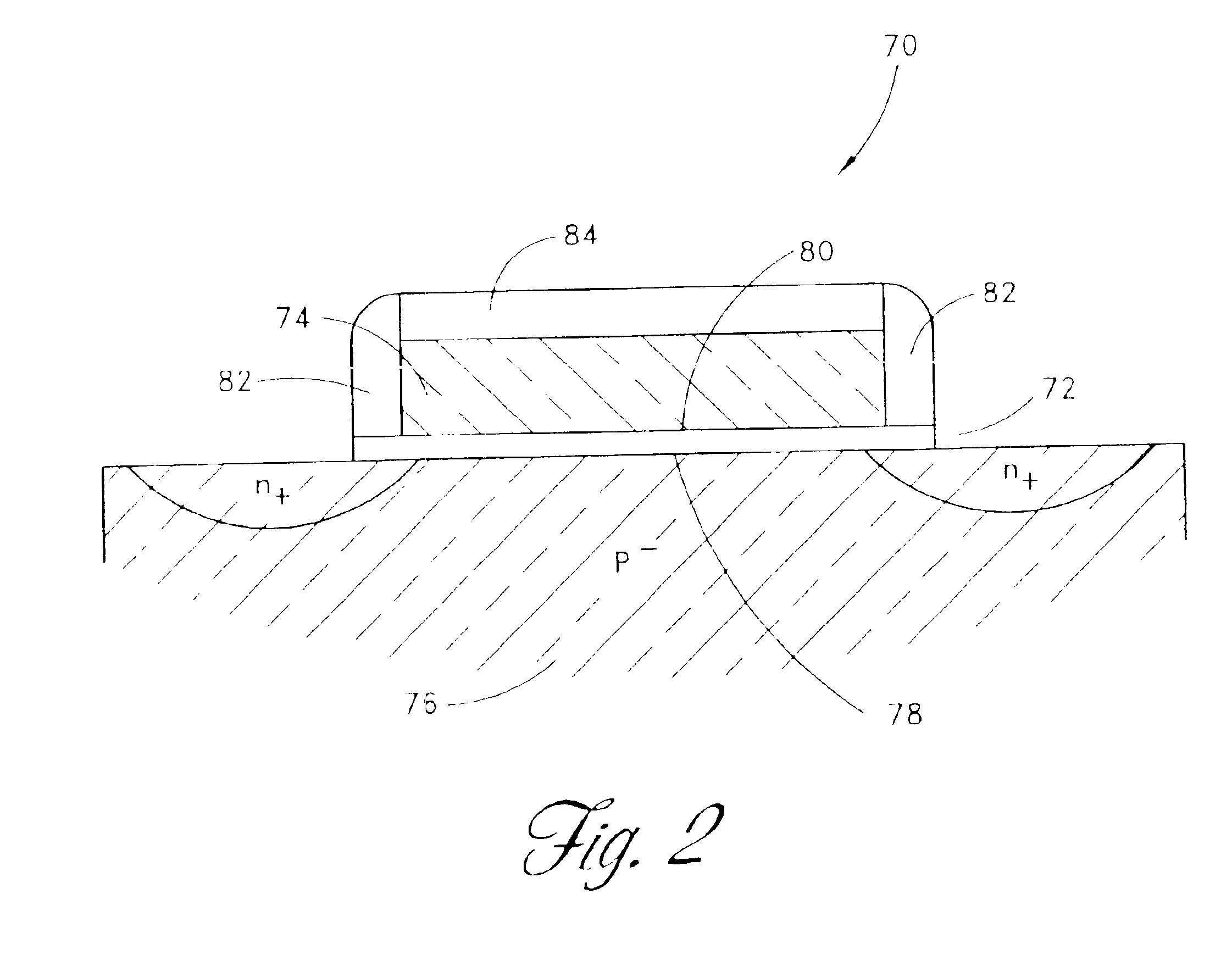

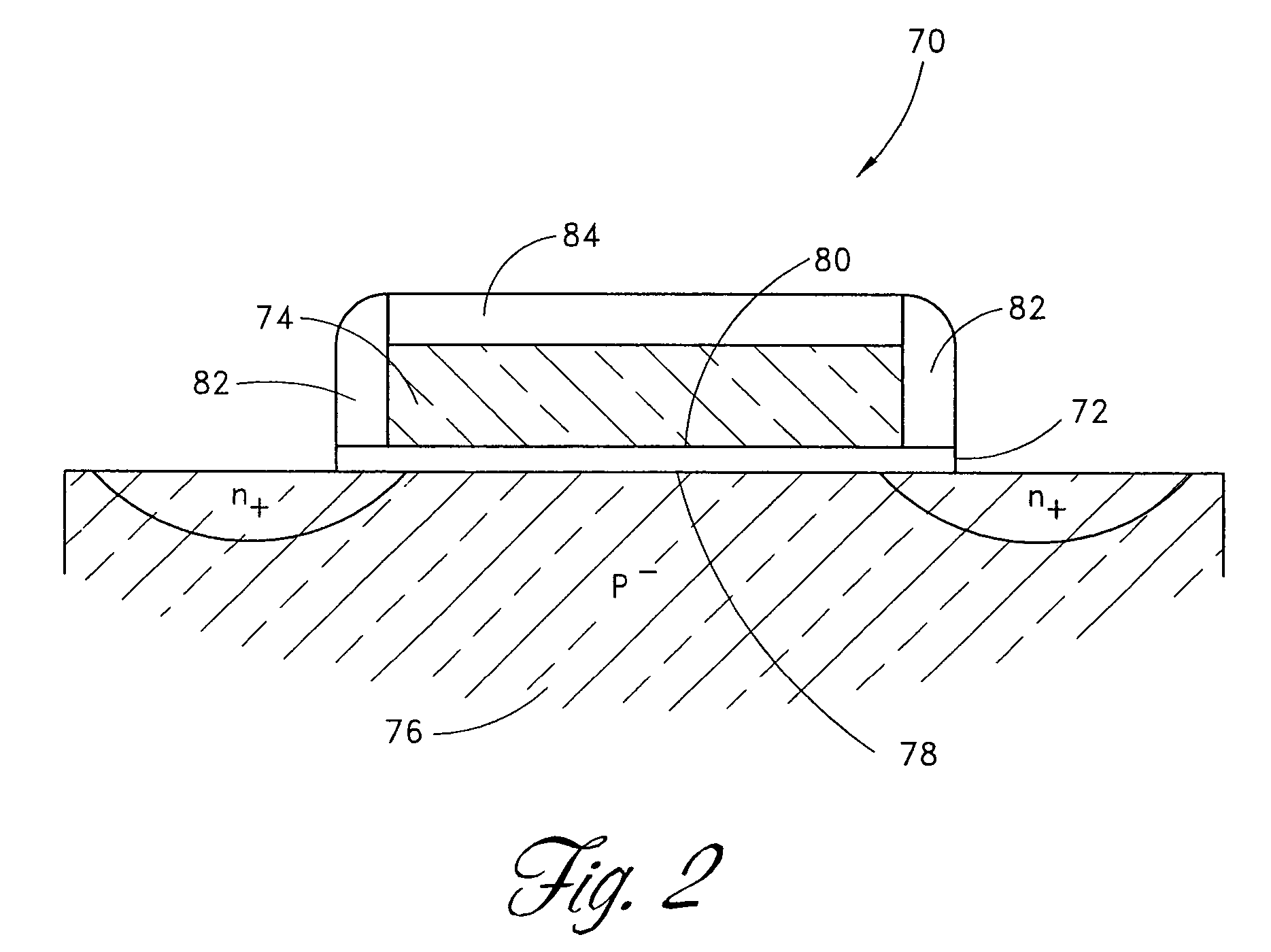

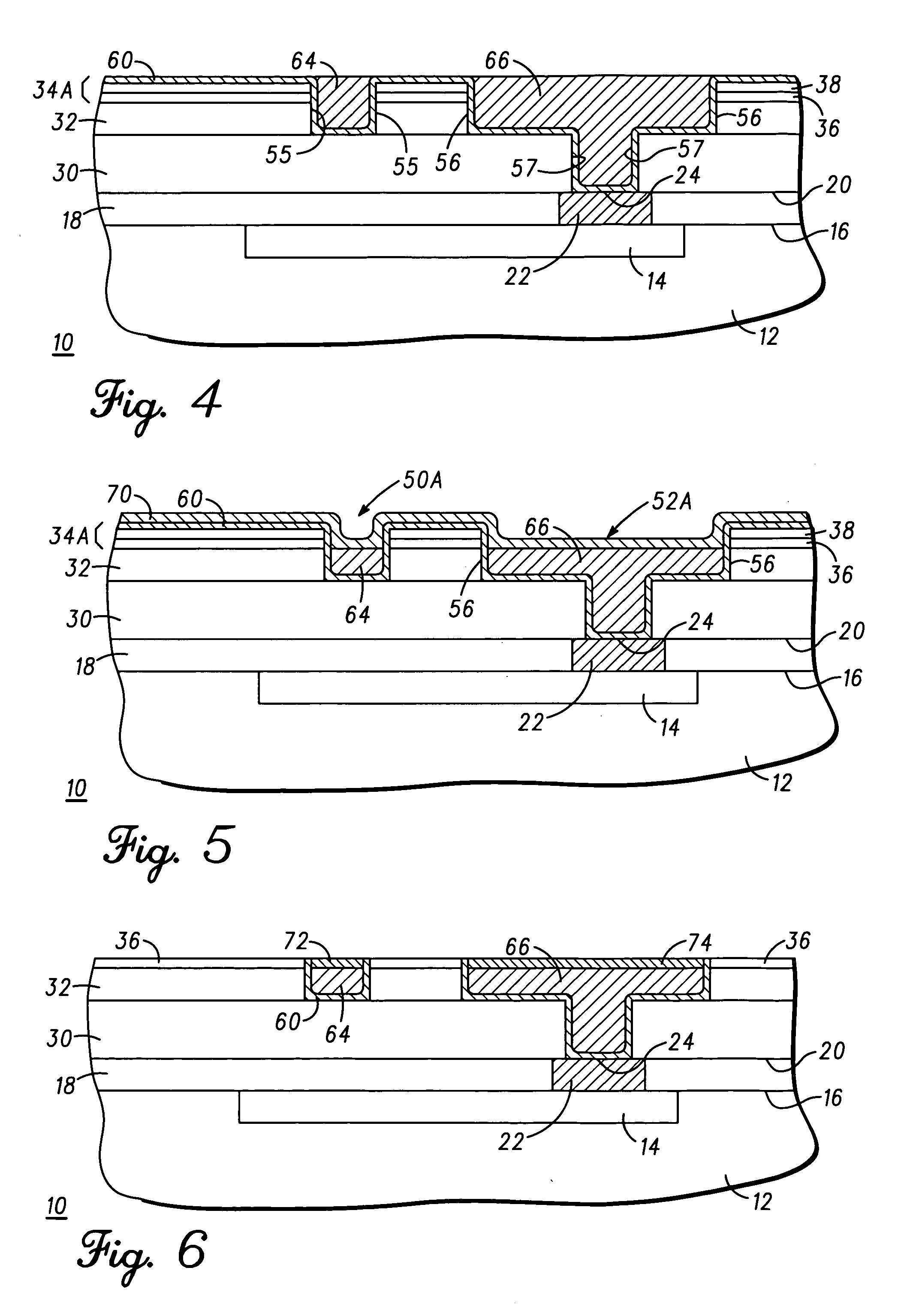

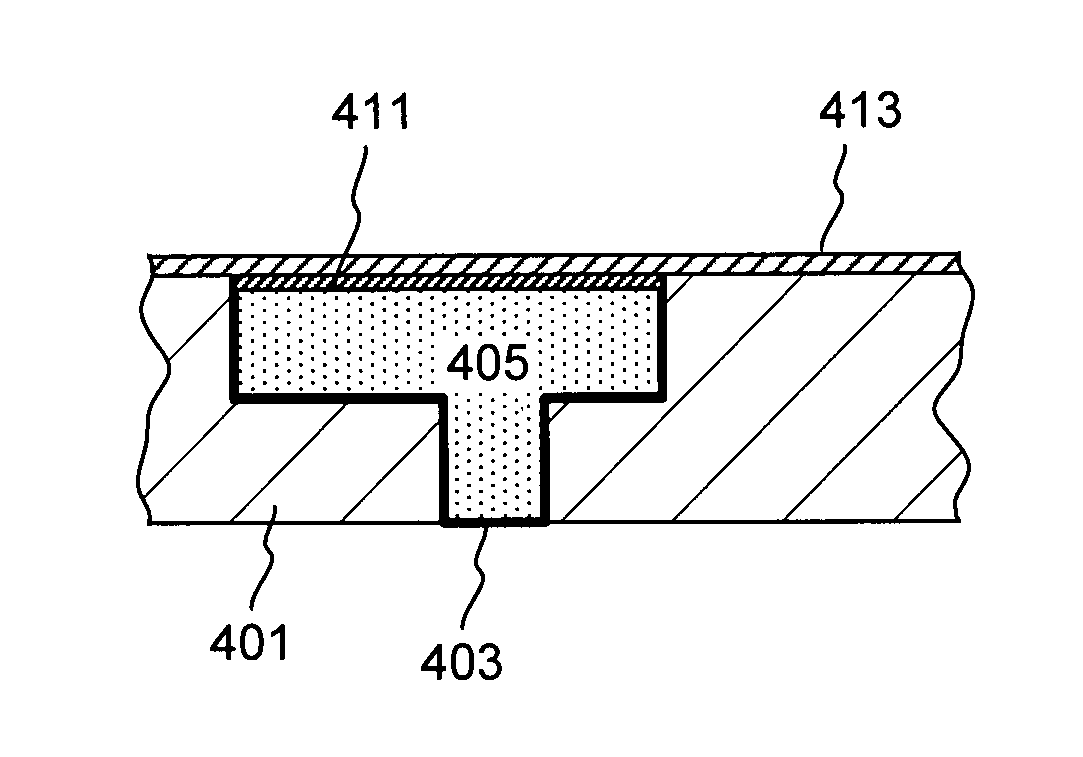

Semiconductor component and method of manufacture

ActiveUS6927113B1Reduce electromigration and stress migrationLow levelSemiconductor/solid-state device detailsSolid-state devicesElectrically conductiveMetal interconnect

A semiconductor component and a method for manufacturing the semiconductor component that mitigates electromigration and stress migration in a metallization system of the semiconductor component. A hardmask is formed over a dielectric layer and an opening is etched through the hardmask and into the dielectric layer. The opening is lined with a barrier layer and filled with an electrically conductive material. The electrically conductive material is planarized, where the planarization process stops on the barrier layer. Following planarization, the electrically conductive material is recessed using either an over-polishing process with highly selective copper slurry or a wet etching process to partially re-open the filled metal-filled trench or via. The recess process is performed such that the exposed portion of the electrically conductive material is below the dielectric layer. A capping layer is then deposited on both the dielectric portion and the exposed metal interconnect portion of the electrically conductive material.

Owner:ADVANCED MICRO DEVICES INC

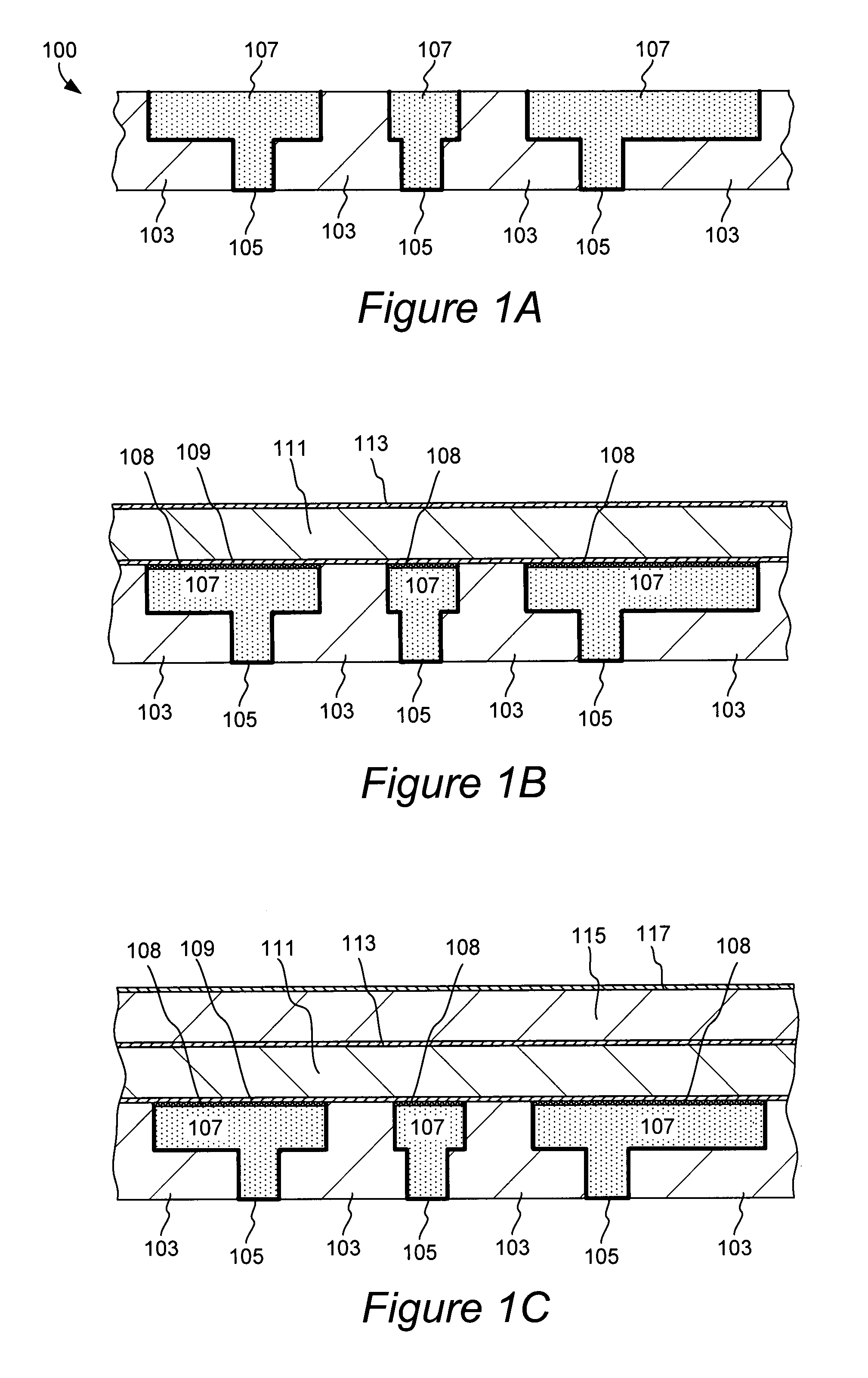

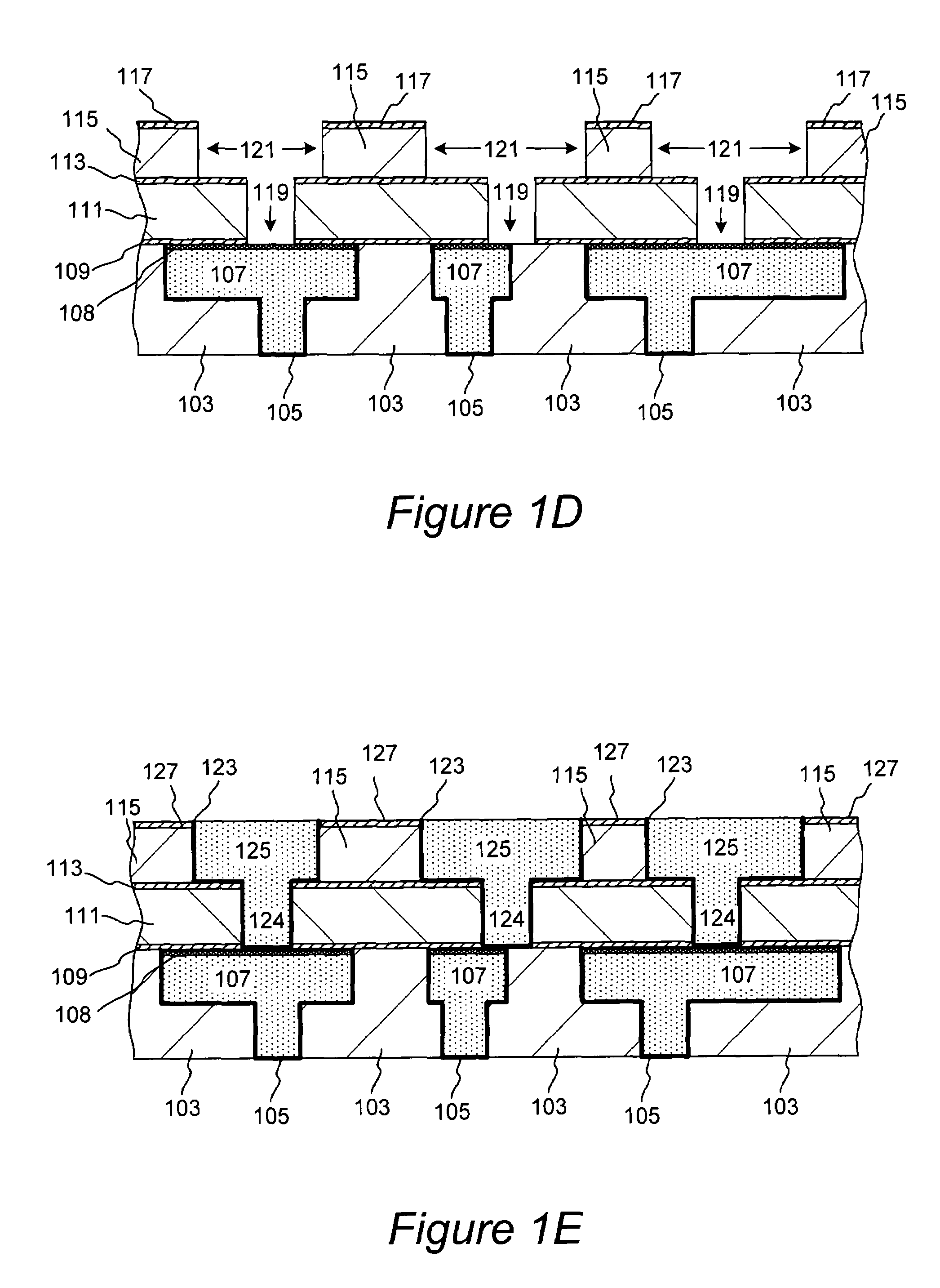

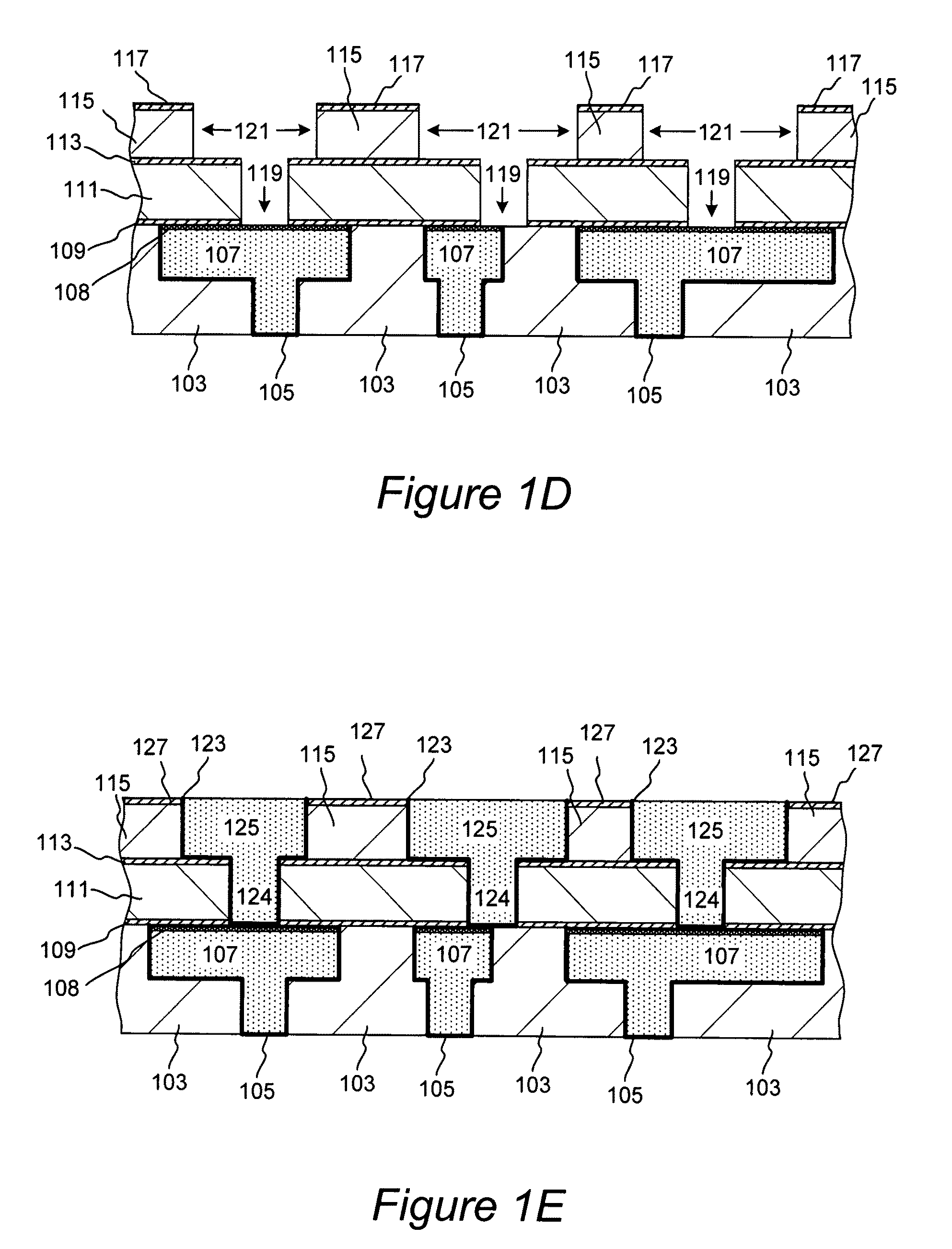

Self Aligned Air-Gap in Interconnect Structures

ActiveUS20110084357A1Reduce parasitic capacitanceReduce electromigrationSemiconductor/solid-state device detailsSolid-state devicesDielectric layerIntegrated circuit

An integrated circuit structure comprising an air gap and methods for forming the same are provided. The integrated circuit structure includes a conductive line; a self-aligned dielectric layer on a sidewall of the conductive line; an air-gap horizontally adjoining the self-aligned dielectric layer; a low-k dielectric layer horizontally adjoining the air-gap; and a dielectric layer on the air-gap and the low-k dielectric layer.

Owner:TAIWAN SEMICON MFG CO LTD

Self-aligned air-gap in interconnect structures

InactiveUS7871923B2Reduce parasitic capacitanceReduce electromigrationSolid-state devicesSemiconductor/solid-state device manufacturingDielectric layerIntegrated circuit

An integrated circuit structure comprising an air gap and methods for forming the same are provided. The integrated circuit structure includes a conductive line; a self-aligned dielectric layer on a sidewall of the conductive line; an air-gap horizontally adjoining the self-aligned dielectric layer; a low-k dielectric layer horizontally adjoining the air-gap; and a dielectric layer on the air-gap and the low-k dielectric layer.

Owner:TAIWAN SEMICON MFG CO LTD

Interconnect with composite barrier layers and method for fabricating the same

InactiveUS6958291B2Improve adhesionGood step coverageSemiconductor/solid-state device manufacturingDielectricTantalum nitride

Composite ALD-formed diffusion barrier layers. In a preferred embodiment, a composite conductive layer is composed of a diffusion barrier layer and / or a low-resistivity metal layer formed by atomic layer deposition (ALD) lining a damascene opening in dielectrics, serving as diffusion blocking and / or adhesion improvement. The preferred composite diffusion barrier layers are dual titanium nitride layers or dual tantalum nitride layers, triply laminar of tantalum, tantalum nitride and tantalum-rich nitride, or tantalum, tantalum nitride and tantalum, formed sequentially on the opening by way of ALD.

Owner:TAIWAN SEMICON MFG CO LTD

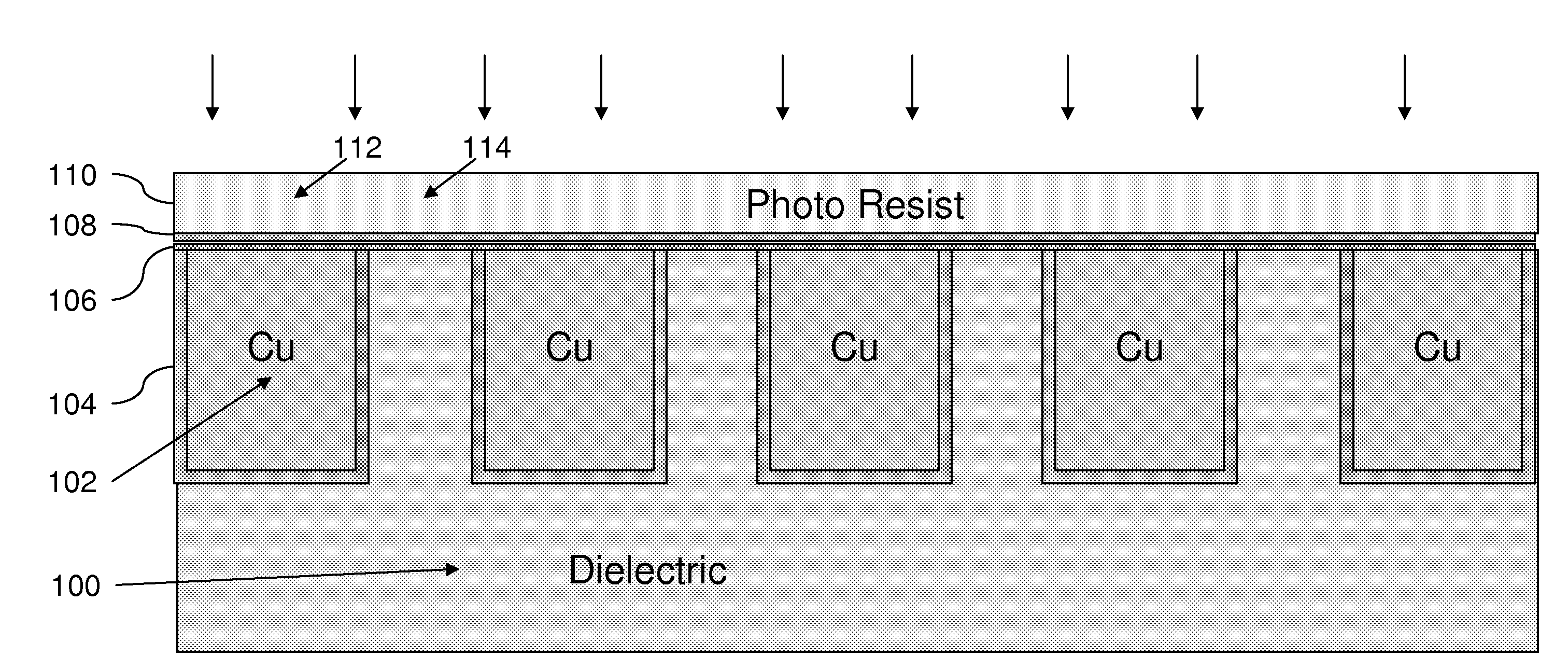

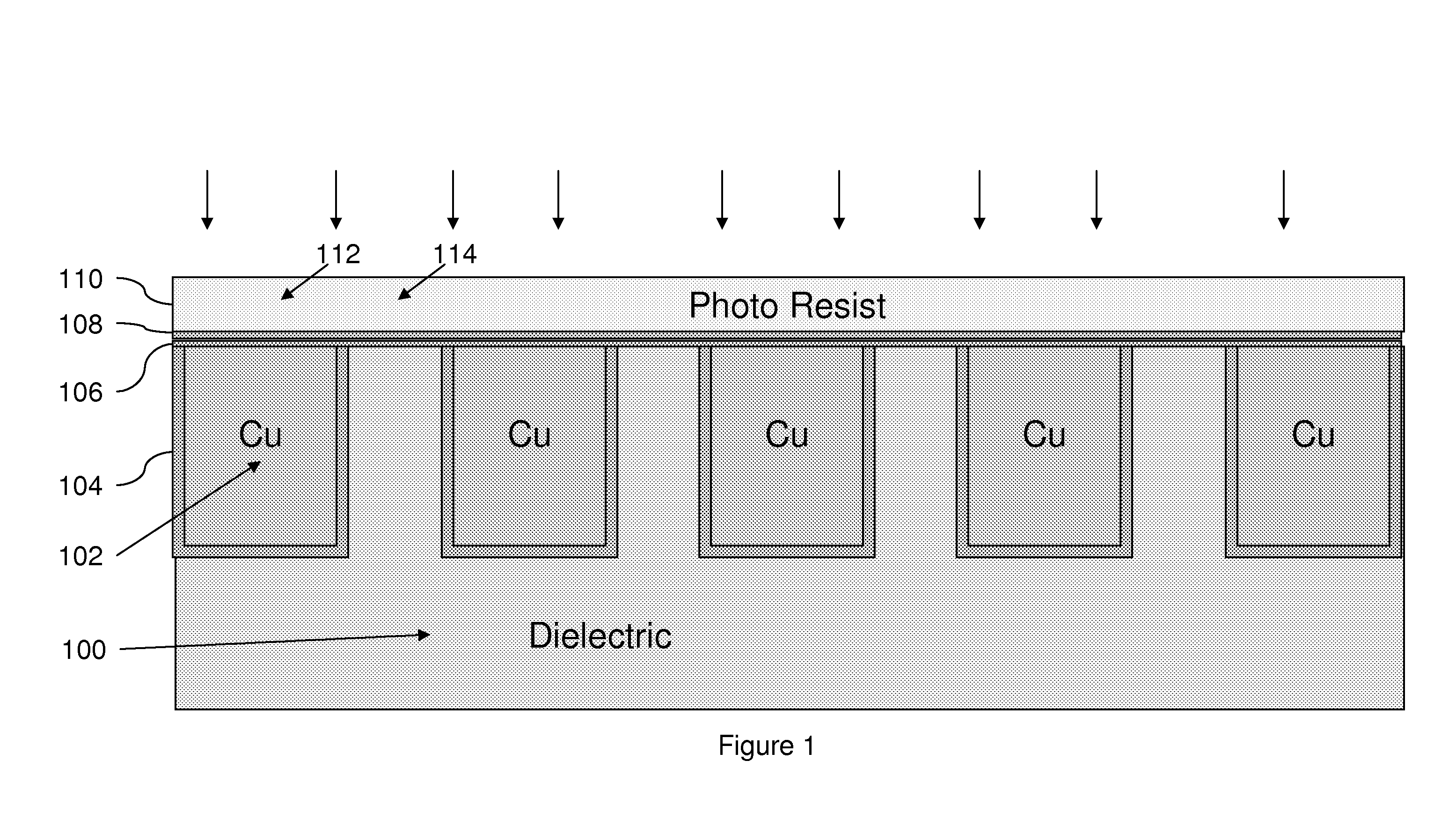

Selective thin metal cap process

ActiveUS20090053890A1Electrical conductivity of the wiring material becomes increasingly more importantGood conductorSemiconductor/solid-state device manufacturingThin metalResist

A method of creating metal caps on copper lines within an inter-line dielectric (ILD) deposits a thin (e.g., 5 nm) metal blanket film (e.g., Ta / TaN) on top the copper lines and dielectric, after the wafer has been planarized. Further a thin dielectric cap is formed over the metal blanket film. A photoresist coating is deposited over the thin dielectric cap and a lithographic exposure process is performed, but without a lithographic mask. A mask is not needed in this situation, because due to the reflectivity difference between copper and the ILD lying under the two thin layers, a mask pattern is automatically formed for etching away the Ta / TaN metal cap between copper lines. Thus, this mask pattern is self-aligned above the copper lines.

Owner:TAIWAN SEMICON MFG CO LTD

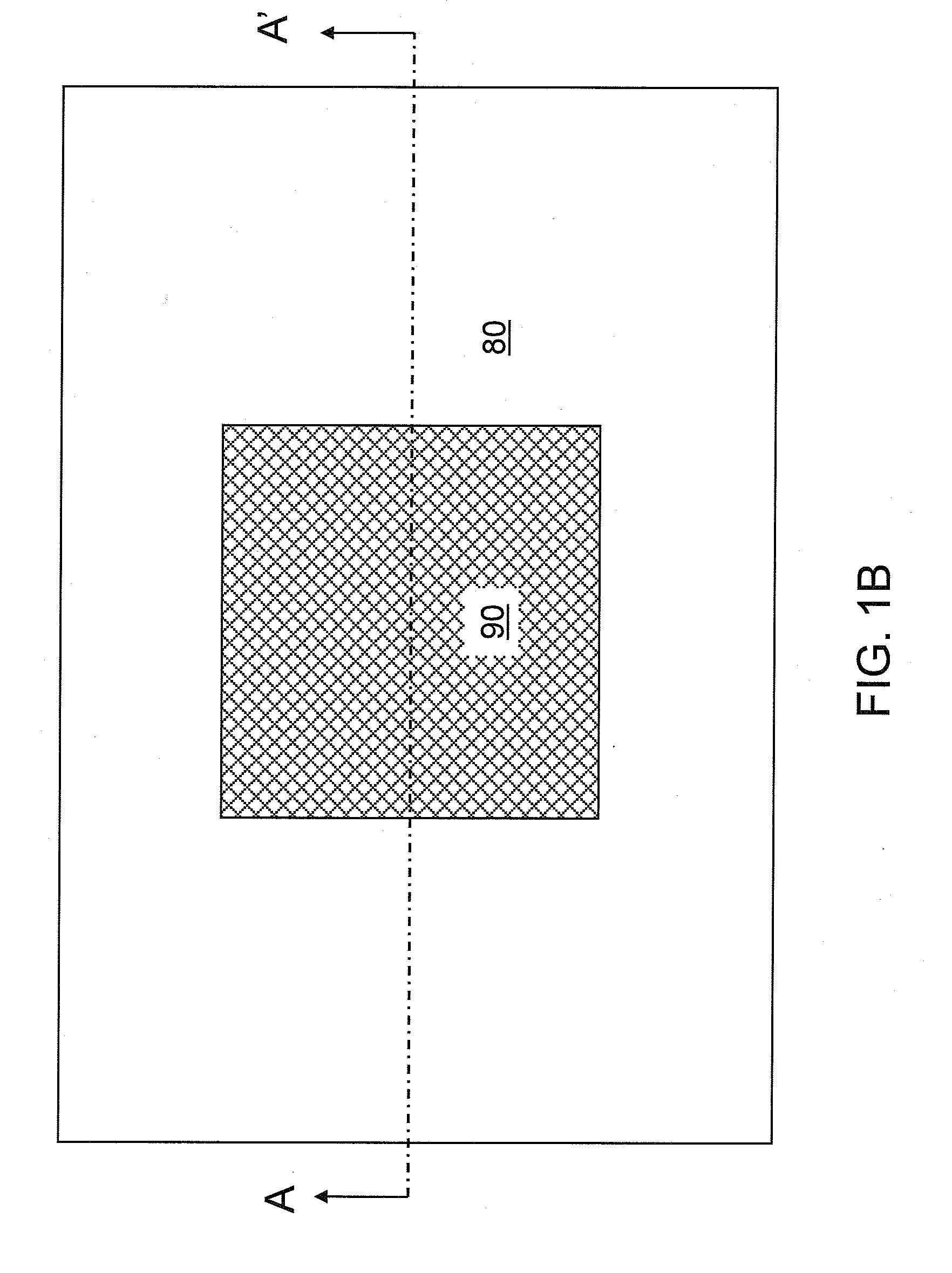

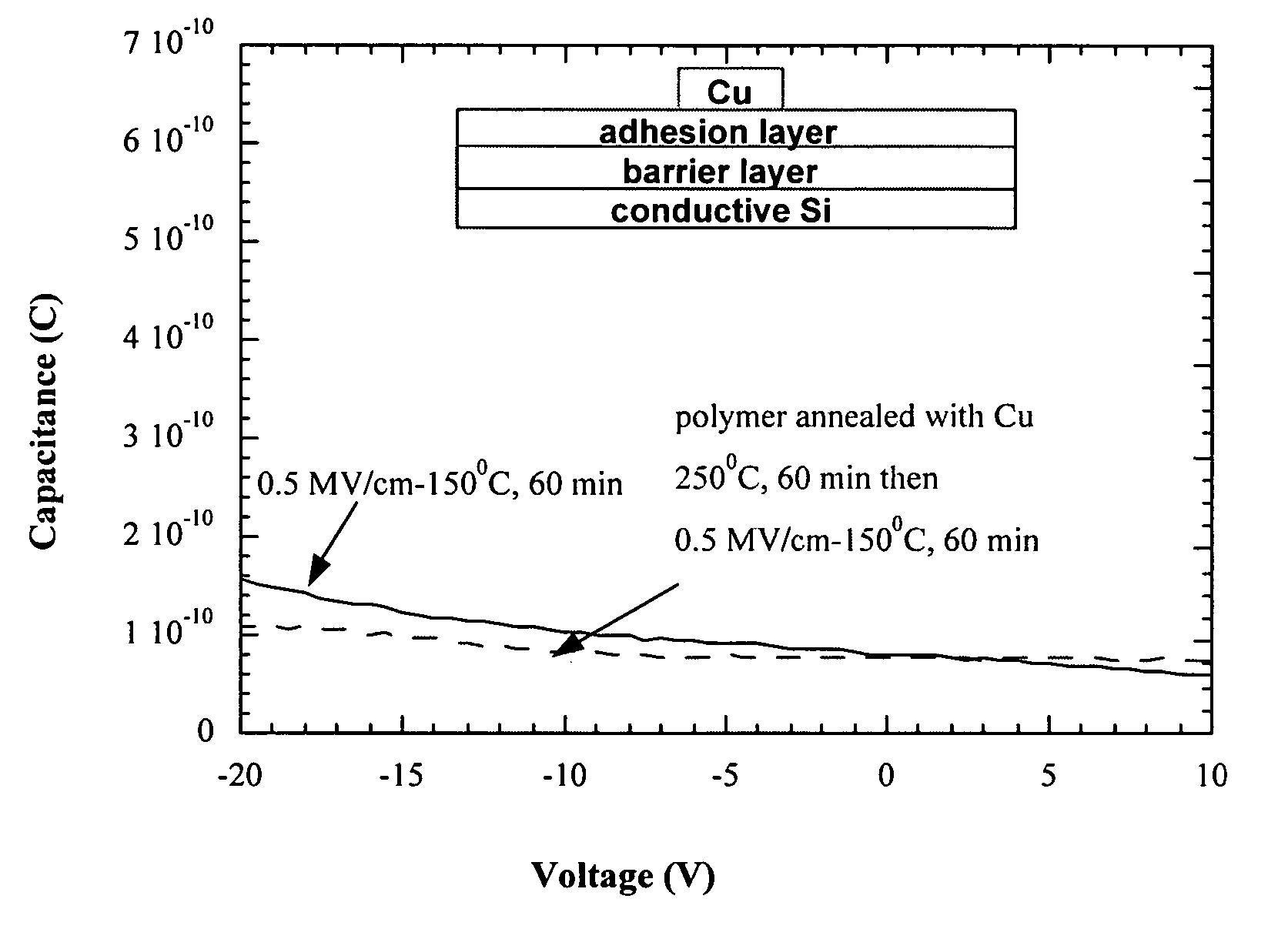

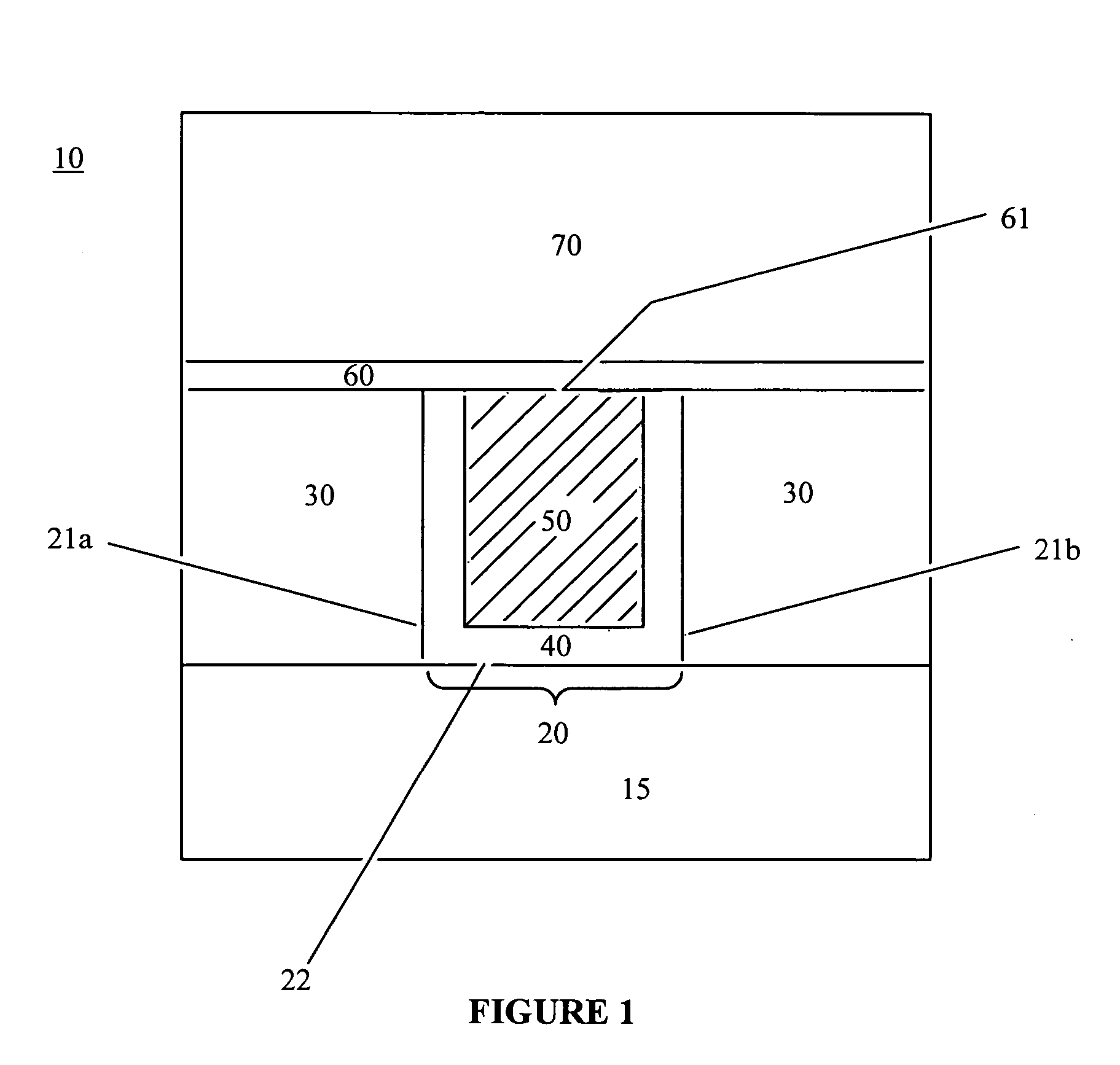

Solving via-misalignment issues in interconnect structures having air-gaps

ActiveUS7868455B2Reduce parasitic capacitanceReduce electromigrationSemiconductor/solid-state device detailsSolid-state devicesElectricityDielectric permittivity

Owner:TAIWAN SEMICON MFG CO LTD

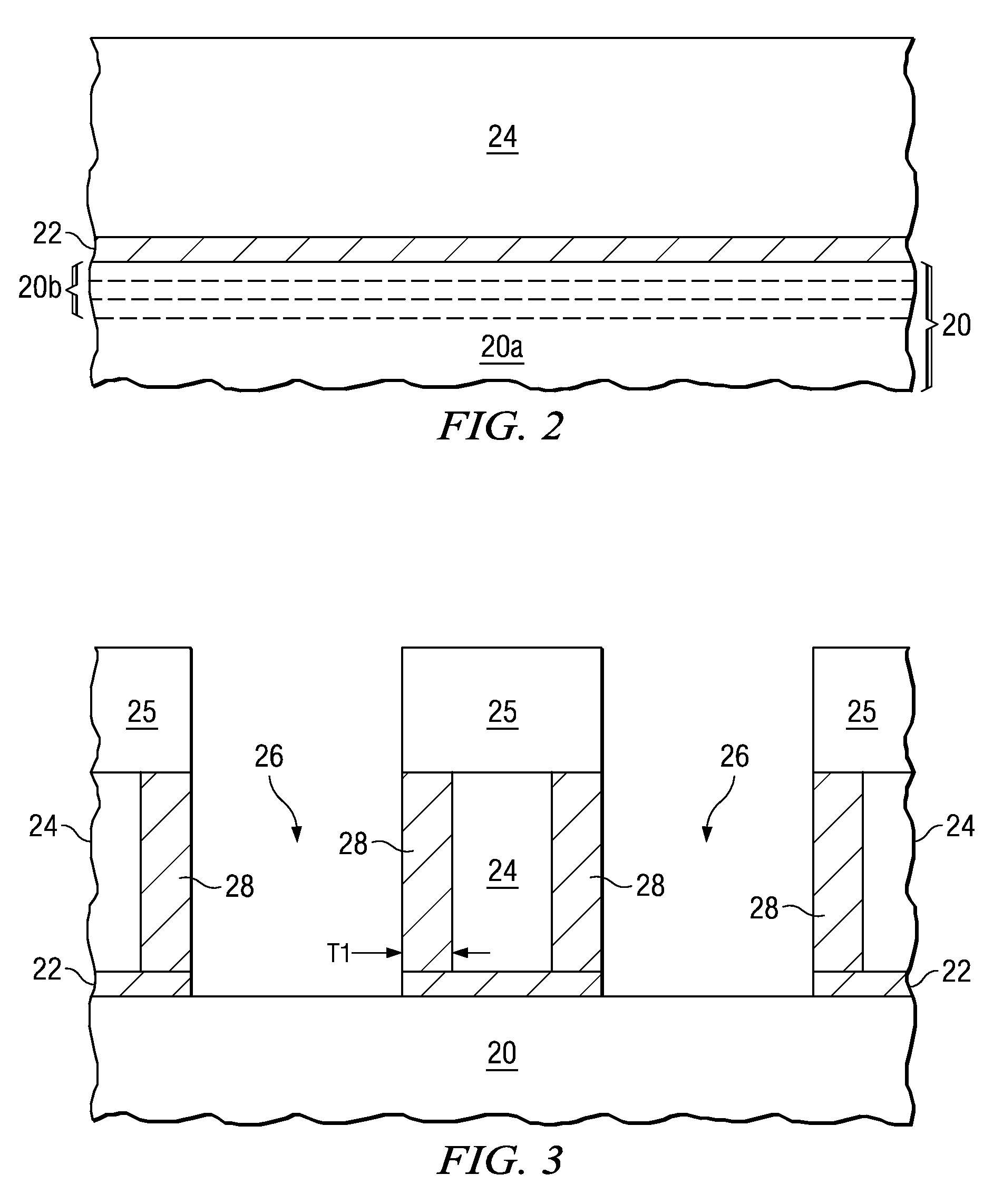

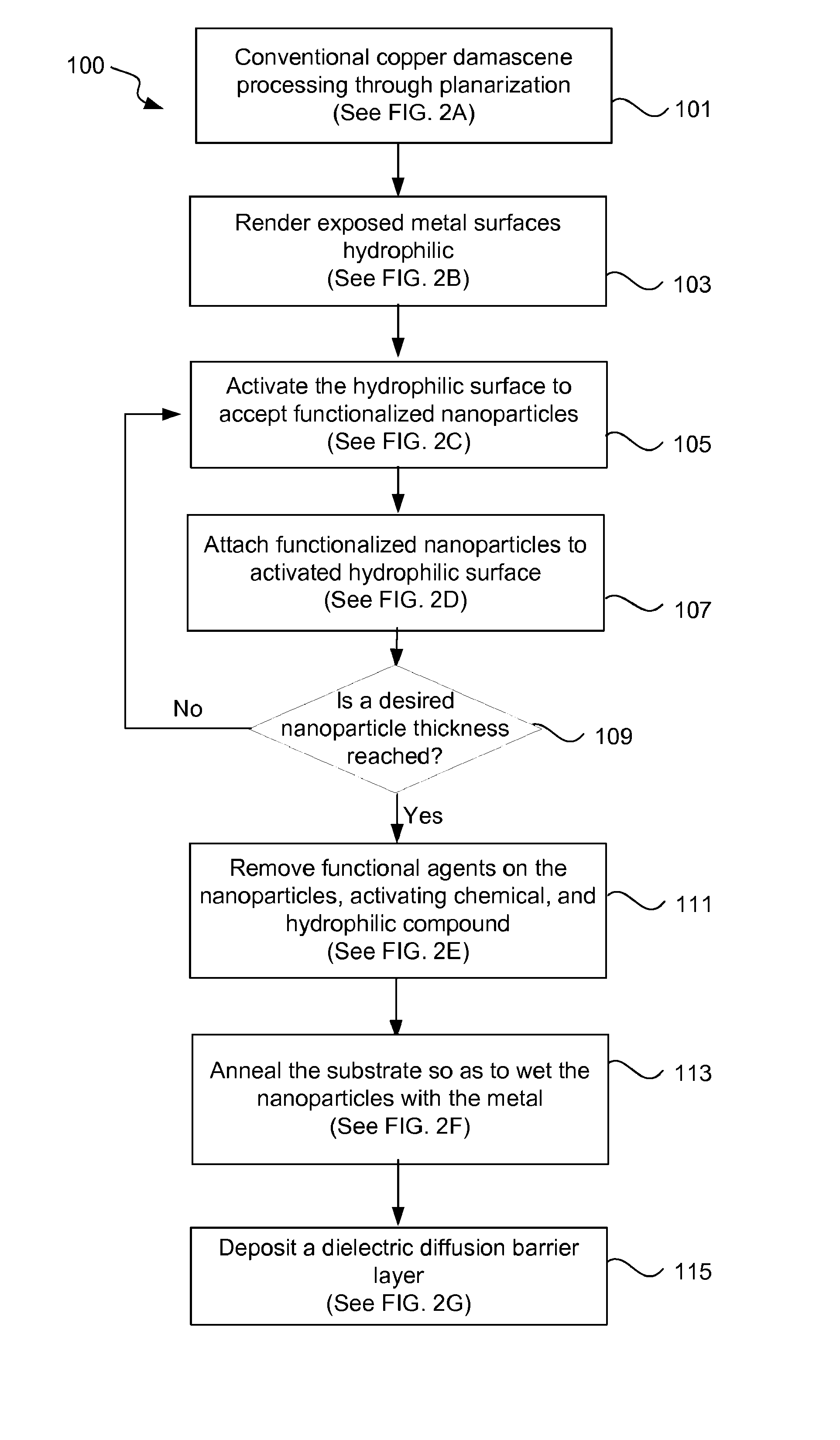

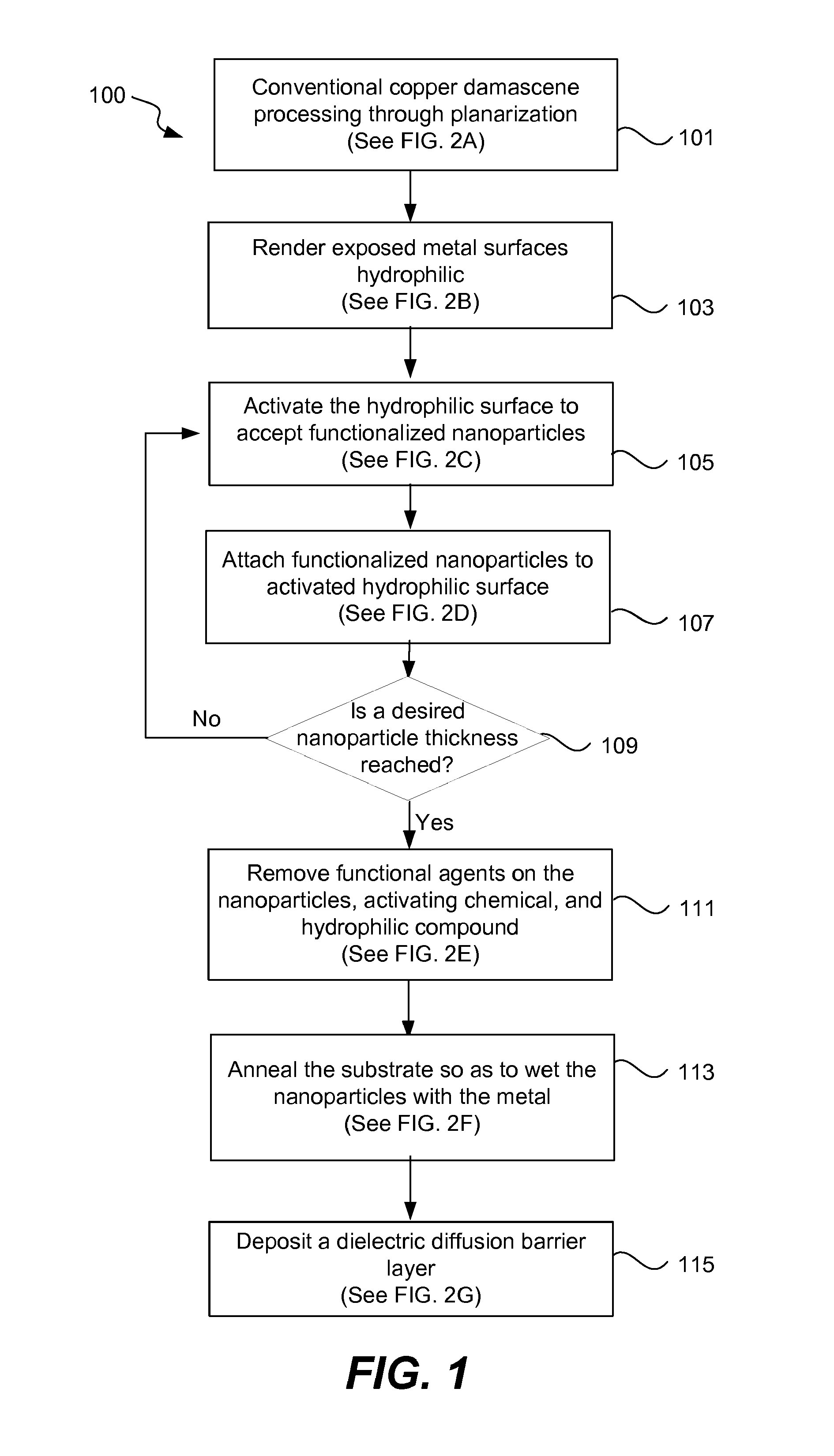

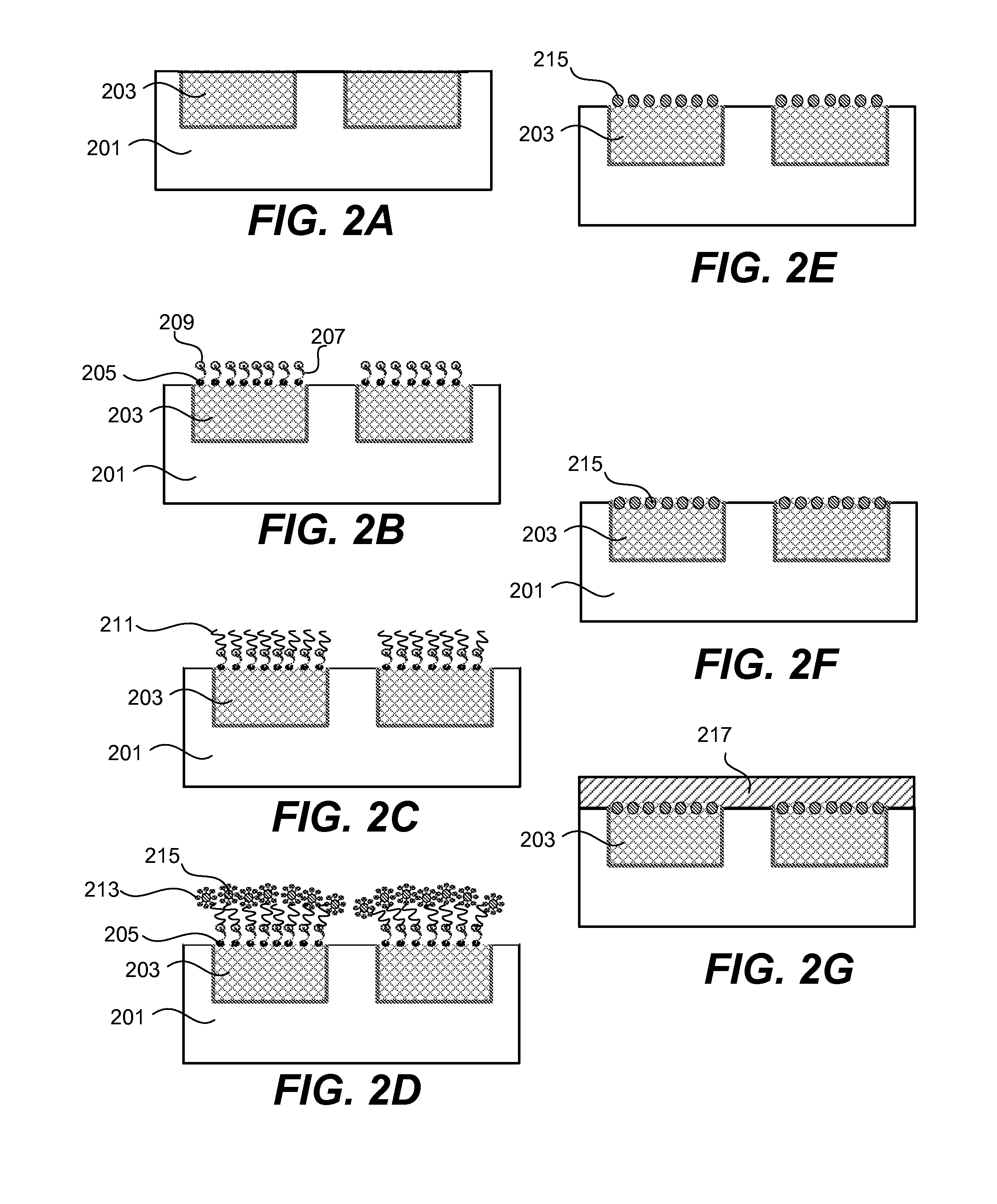

Nanoparticle cap layer

InactiveUS8039379B1Reduce electromigrationIncrease the footprintSemiconductor/solid-state device manufacturingDielectricFunctionalized nanoparticles

Functionalized nanoparticles are deposited on metal lines inlaid in dielectric to form a metal cap layer that reduces electromigration in the metal line. The functionalized nanoparticles are deposited onto activated metal surfaces, then sintered and annealed to remove the functional agents leaving behind a continuous capping layer. The resulting cap layer is about 1 to 10 nm thick with 30-100% atomic of the nanoparticle material. Various semiconductor processing tools may be adapted for this deposition process without adding footprint in the semiconductor fabrication plant.

Owner:NOVELLUS SYSTEMS

Protective self-aligned buffer layers for damascene interconnects

ActiveUS7727881B1Improving several propertyDecrease in metal electromigrationSemiconductor/solid-state device detailsSolid-state devicesThin layerNitrogen

Protective self aligned buffer (PSAB) layers are layers of material that are selectively formed at the surface of metal layers in a partially fabricated semiconductor device. In a Damascene interconnect, PSAB layer typically resides at an interface between the metal layer and a dielectric diffusion barrier layer. PSAB layers promote improved adhesion between a metal layer and an adjacent dielectric diffusion barrier layer. Further, PSAB layers can protect metal surfaces from inadvertent oxidation during fabrication process. A PSAB layer may be formed entirely within the top portion of a metal layer, by, for example, chemically converting metal surface to a thin layer of metal silicide. Thickness of PSAB layers, and, consequently resistance of interconnects can be controlled by partially passivating metal surface prior to formation of PSAB layer. Such passivation can be accomplished by controllably treating metal surface with a nitrogen-containing compound to convert metal to metal nitride.

Owner:NOVELLUS SYSTEMS

Solving Via-Misalignment Issues in Interconnect Structures Having Air-Gaps

InactiveUS20110076831A1Reduce parasitic capacitanceReduce electromigrationSemiconductor/solid-state device detailsSolid-state devicesElectricityDielectric permittivity

An integrated circuit structure is provided. The integrated circuit structure includes a semiconductor substrate; and a metallization layer over the semiconductor substrate. The metallization layer includes a conductive line; a low-k dielectric region adjacent and horizontally spaced apart from the conductive line by a space; and a filler dielectric material filling at least a portion of the space, wherein the filler dielectric material and the low-k dielectric region are formed of different materials. The integrated circuit structure further includes a capping layer over and adjoining the filler dielectric material and the low-k dielectric region. The filler dielectric material has a dielectric constant (k value) less than a k value of the capping layer.

Owner:TAIWAN SEMICON MFG CO LTD

Chemical solution for electroplating a copper-zinc alloy thin film

InactiveUS6974767B1Improves Cu interconnect reliabilityManufacturing cost be reduceSemiconductor/solid-state device manufacturingSemiconductor devicesElectromigrationCorrosion

A method of fabricating a semiconductor device, having a Cu—Zn alloy thin film (30) formed on a Cu surface (20) by electroplating the Cu surface (20) in a unique chemical solution containing salts of zinc (Zn) and copper (Cu), their complexing agents, a pH adjuster, and surfactants; and a semiconductor device thereby formed. The method controls the parameters of pH, temperature, and time in order to form a uniform Cu—Zn alloy thin film (30) for reducing electromigration in Cu interconnect lines by decreasing the drift velocity therein which decreases the Cu migration rate in addition to decreasing the void formation rate, for improving Cu interconnect reliability, and for increasing corrosion resistance.

Owner:ADVANCED MICRO DEVICES INC

Protective self-aligned buffer layers for damascene interconnects

ActiveUS7704873B1Improve mobilityImproving several propertySemiconductor/solid-state device manufacturingThin material handlingDevice materialDiffusion barrier

Owner:NOVELLUS SYSTEMS

Multiple copper vias for integrated circuit metallization and methods of fabricating same

InactiveUS6919639B2Reduce electromigrationImprove failureSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsElectricityEngineering

Owner:BOARD OF RGT THE UNIV OF TEXAS SYST

Reduced electromigration and stressed induced migration of copper wires by surface coating

InactiveUS20050266673A1Improve reliabilityHigh yieldSemiconductor/solid-state device detailsSolid-state devicesDielectricStress induced

The idea of the invention is to coat the free surface of patterned Cu conducting lines in on-chip interconnections (BEOL) wiring by a 1-20 nm thick metal layer prior to deposition of the interlevel dielectric. This coating is sufficiently thin so as to obviate the need for additional planarization by polishing, while providing protection against oxidation and surface, or interface, diffusion of Cu which has been identified by the inventors as the leading contributor to metal line failure by electromigration and thermal stress voiding. Also, the metal layer increases the adhesion strength between the Cu and dielectric so as to further increase lifetime and facilitate process yield. The free surface is a direct result of the CMP (chemical mechanical polishing) in a damascene process or in a dry etching process by which Cu wiring is patterned. It is proposed that the metal capping layer be deposited by a selective process onto the Cu to minimize further processing. We have used electroless metal coatings, such as CoWP, CoSnP and Pd, to illustrate significant reliability benefits, although chemical vapor deposition (CVD) of metals or metal forming compounds can be employed.

Owner:GLOBALFOUNDRIES INC

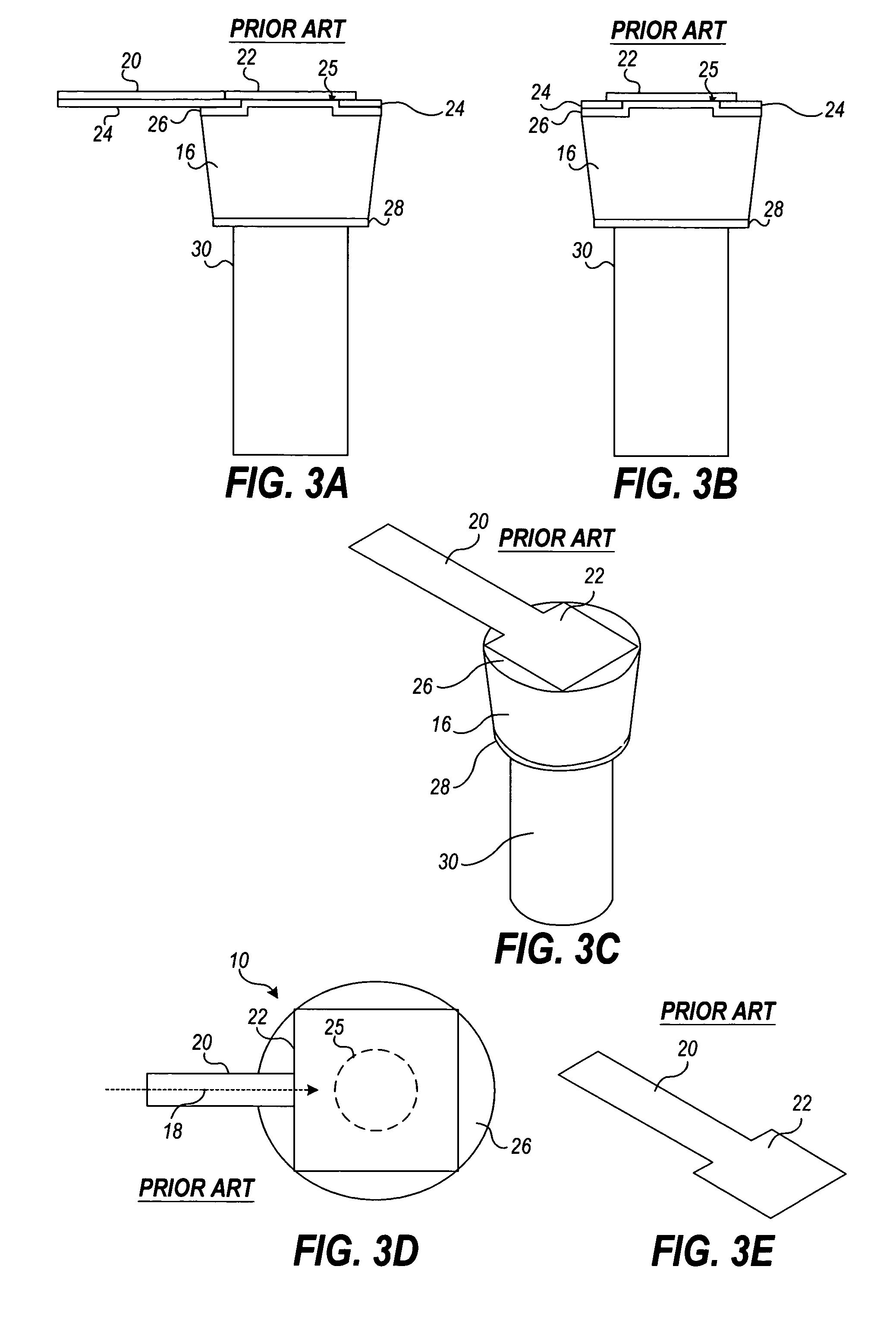

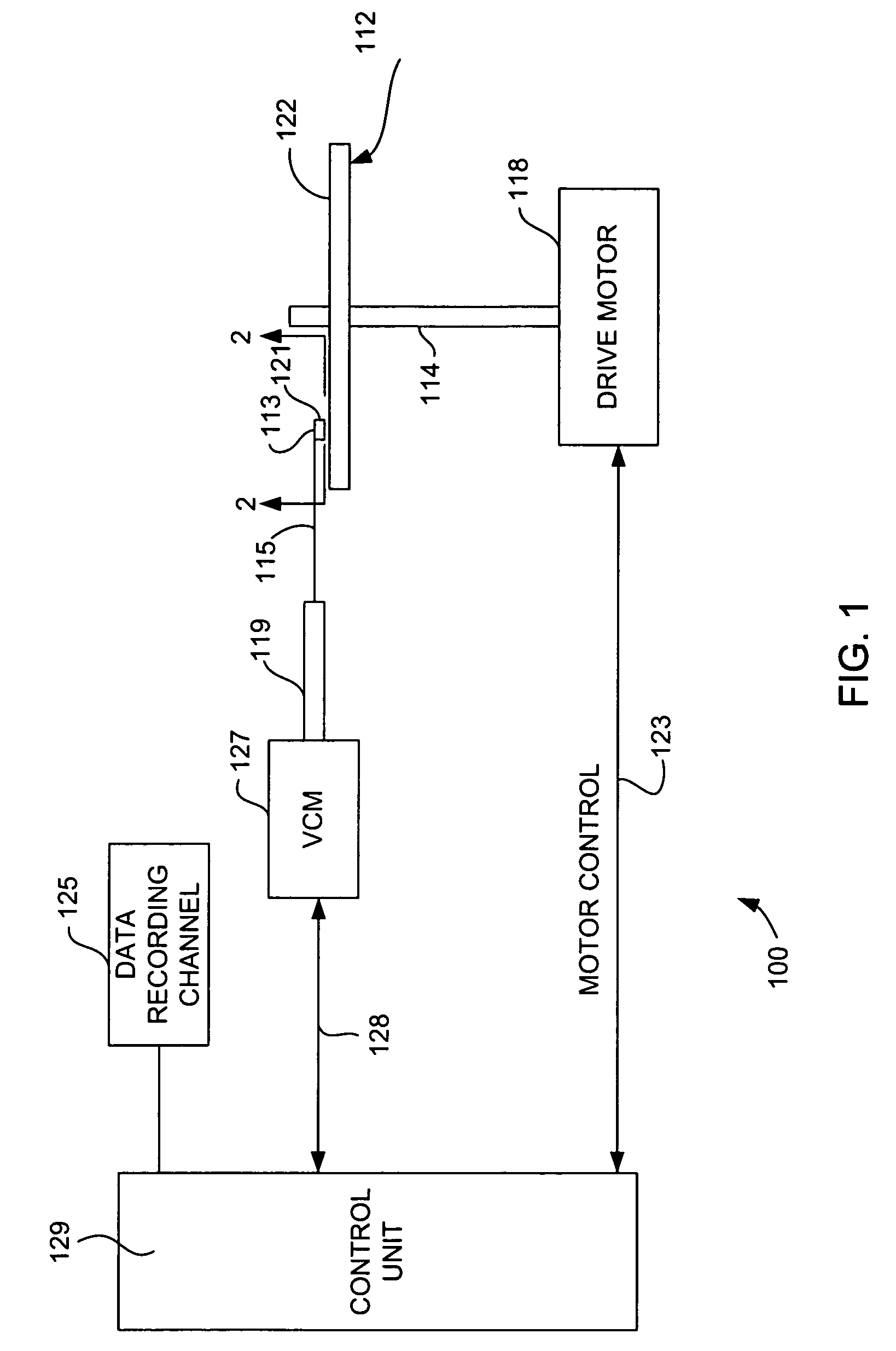

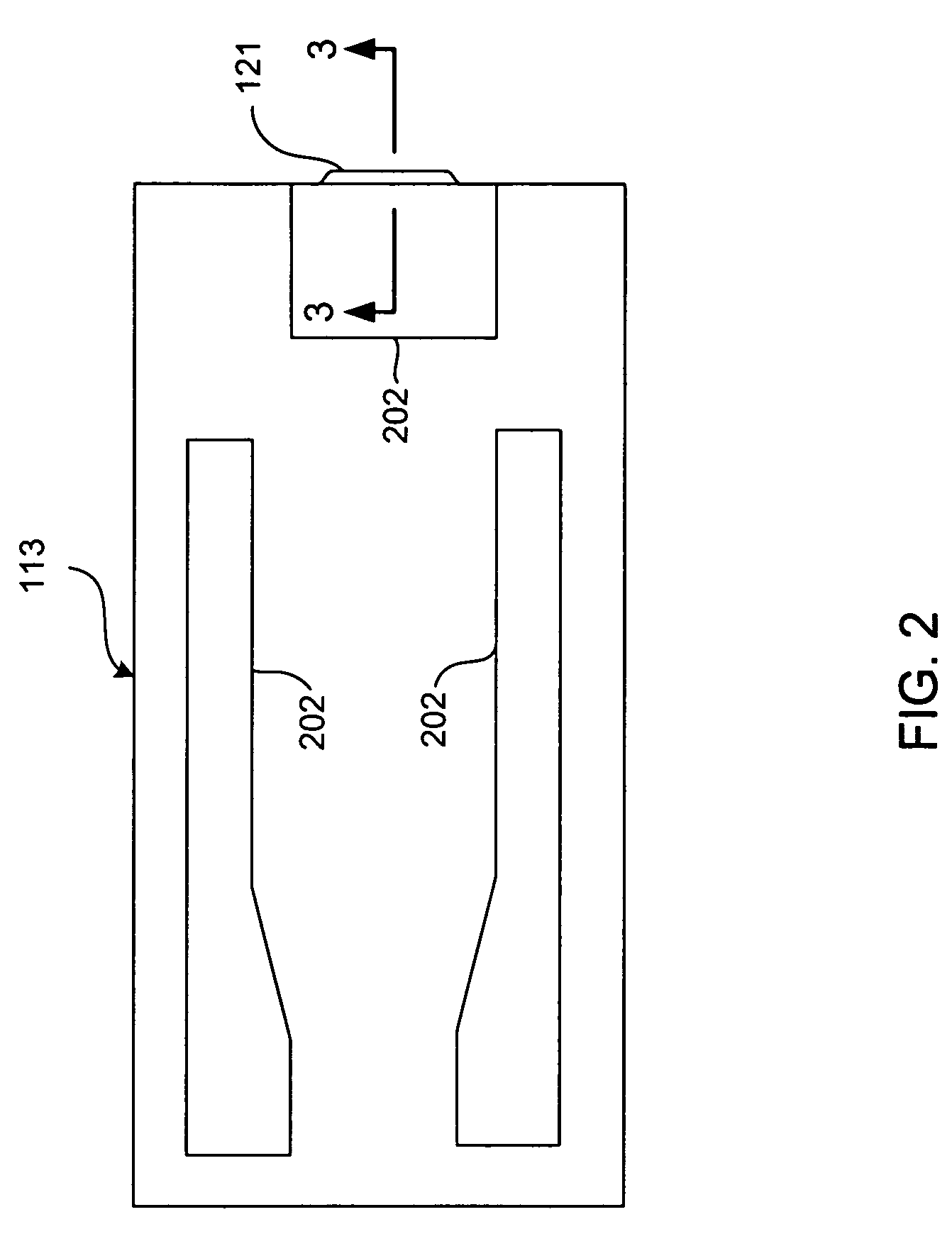

Dual polarity bias for prolonging the life of a heating element in magnetic data storage devices

InactiveUS7330336B2Reduce electromigrationProlong lifeRecord information storageAnalogue recordingMagnetic mediaElectrical polarity

A magnetic read / write head having a heating element to induce a desired amount of thermal protrusion in the read and write elements to control the fly height of the read and write elements over a magnetic medium. The heating element is connected with circuitry that provides an electrical bias (voltage or current) that switches polarity in order to prevent electromigration, thereby greatly increasing the life of the heating element. The polarity of the heating element can be switched upon the occurrence of a predetermined event such as between read or write events or upon activating deactivating the disk drive device or could be performed at regular, predetermined time intervals. The dual polarity bias could also be provided by applying an AC bias to the heating element.

Owner:WESTERN DIGITAL TECH INC