Patents

Literature

39results about How to "Suppress signal delay" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

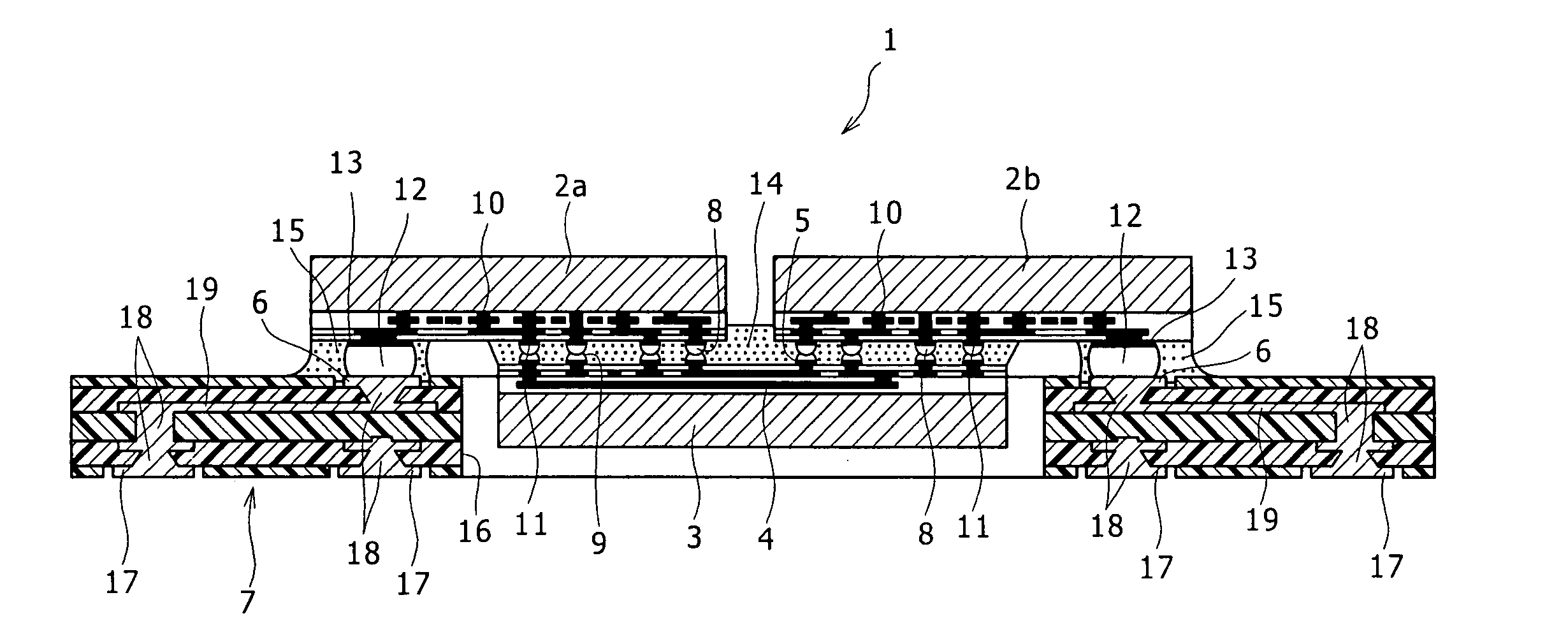

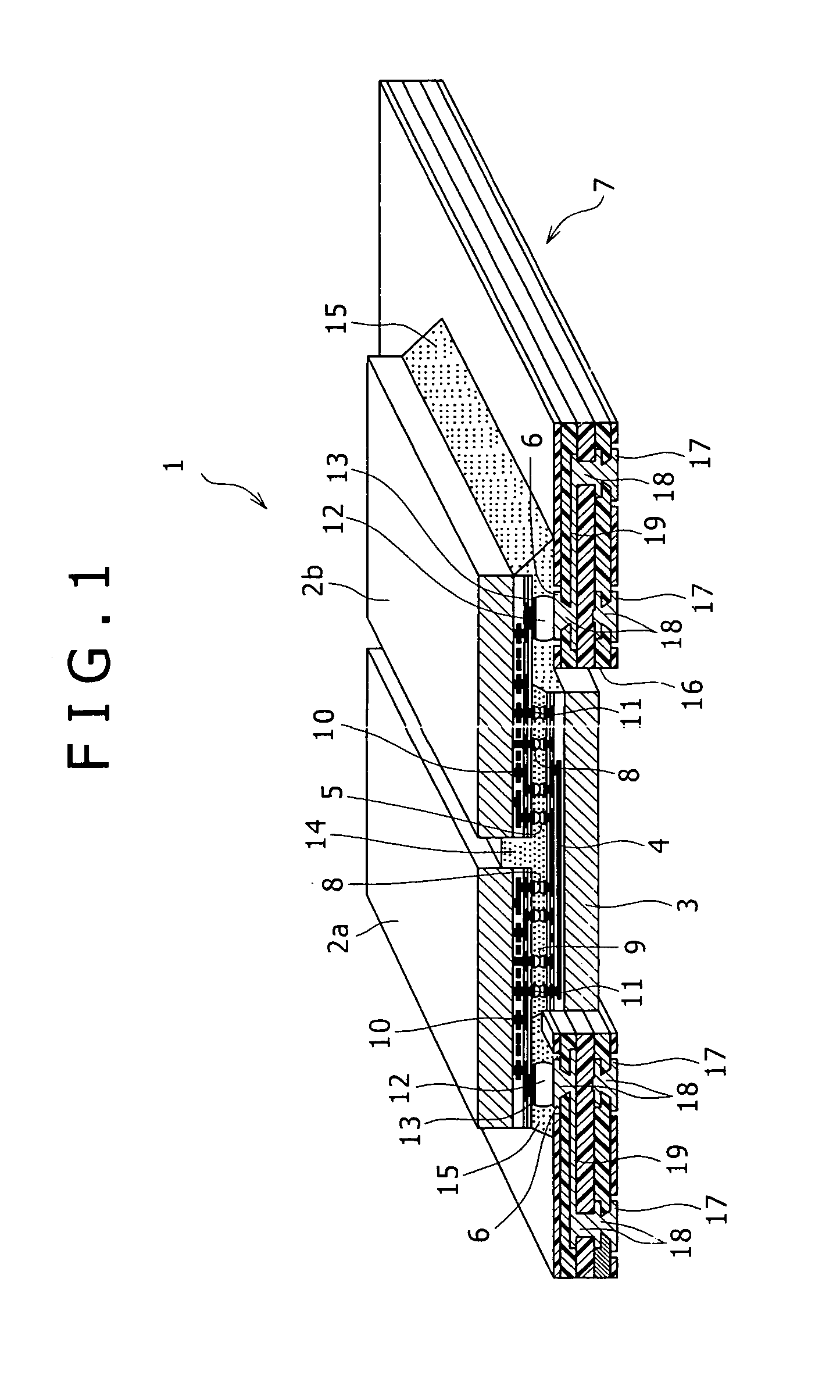

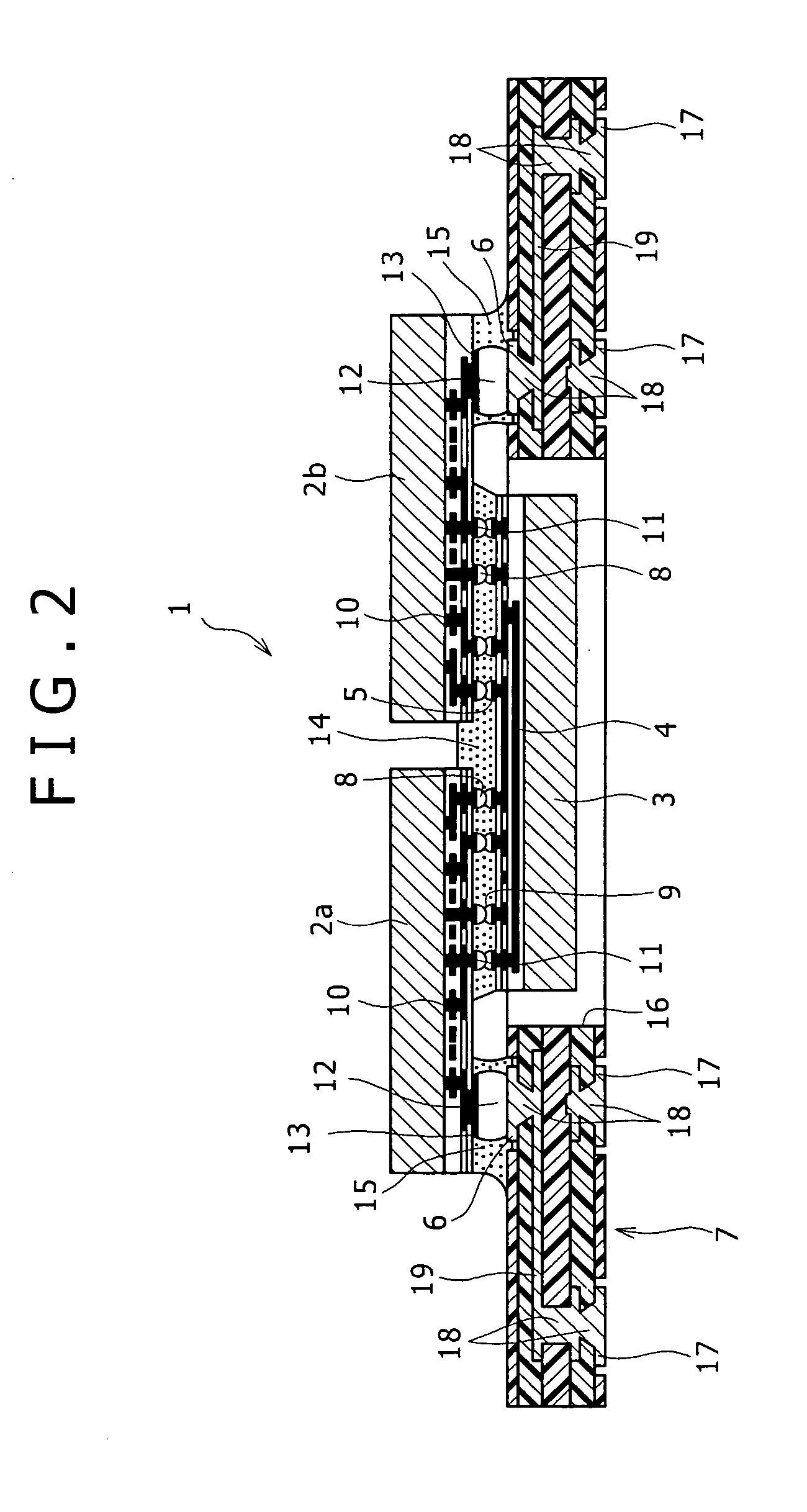

Semiconductor device and method of manufacturing semiconductor device

ActiveUS20060226527A1Low costSmall sizeSemiconductor/solid-state device detailsSolid-state devicesDevice materialSemiconductor chip

The present invention provides a semiconductor device that is inexpensive and can suppress signal transmission delay, and a manufacturing method thereof. The semiconductor device includes: a plurality of semiconductor chips; a semiconductor substrate that has, on the same surface thereof, a chip-to-chip interconnection for electrically connecting the plurality of semiconductor chips to each other, and a plurality of chip-connection pads connected to the chip-to-chip interconnection; and a wiring board that has a plurality of lands of which pitch is larger than a pitch of the chip-connection pads, wherein a major surface of each of the plurality of semiconductor chips is connected to the chip-connection pads via a first connector so that the plurality of semiconductor chips are mounted on the semiconductor substrate, and an external-connection pad is formed on the major surface other than a region facing the semiconductor substrate, and is connected to the land on the wiring board via a second connector.

Owner:SONY CORP

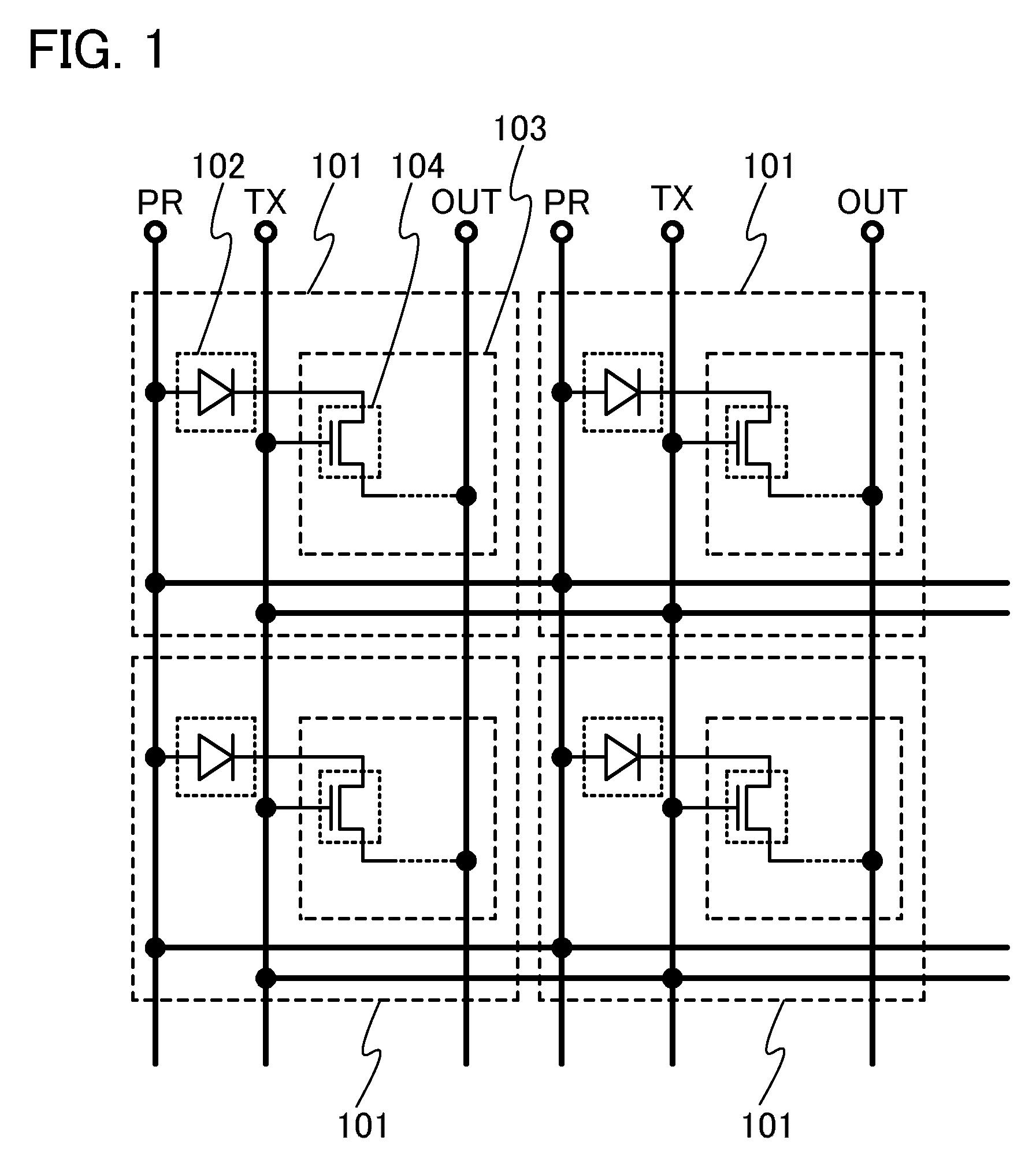

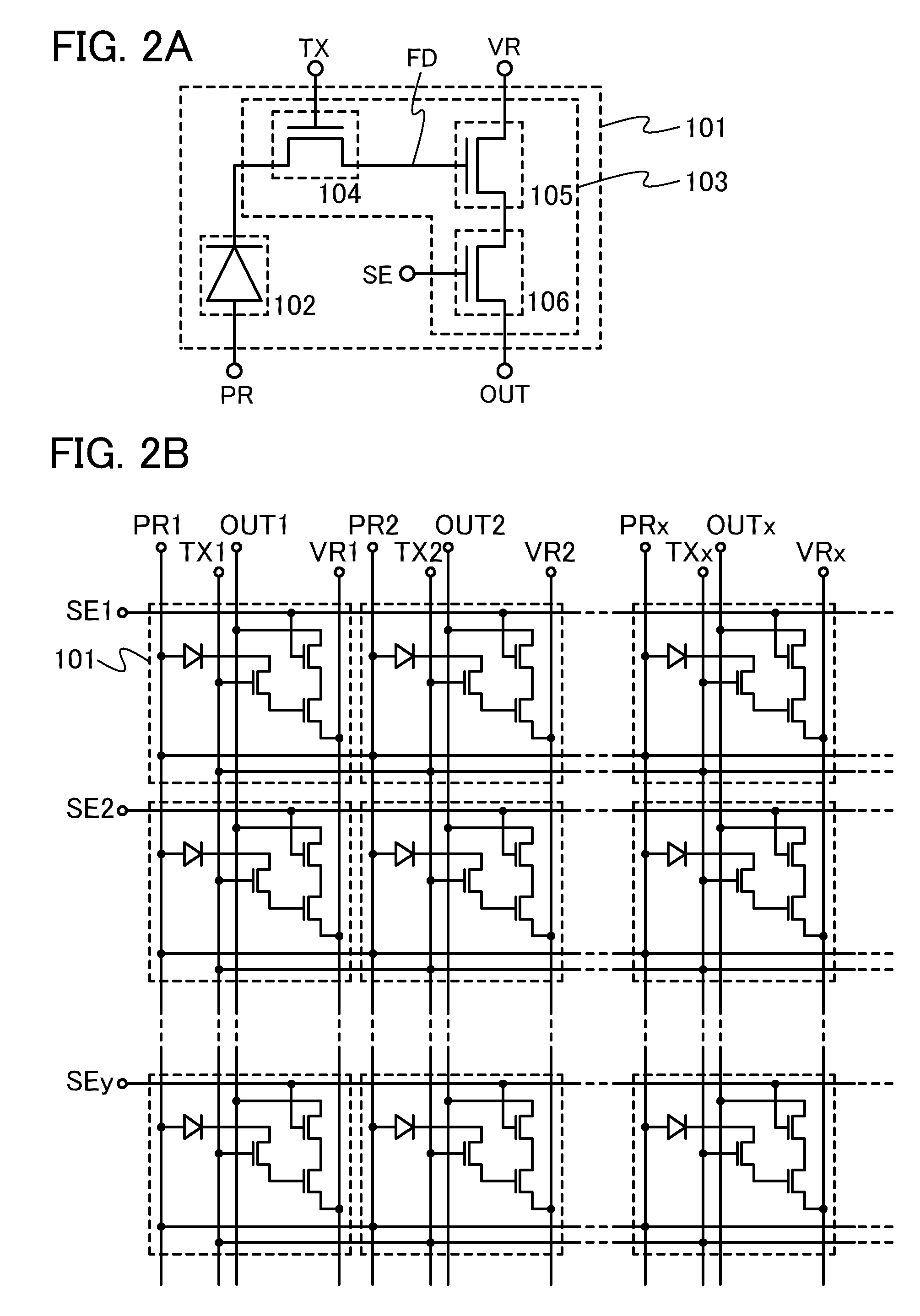

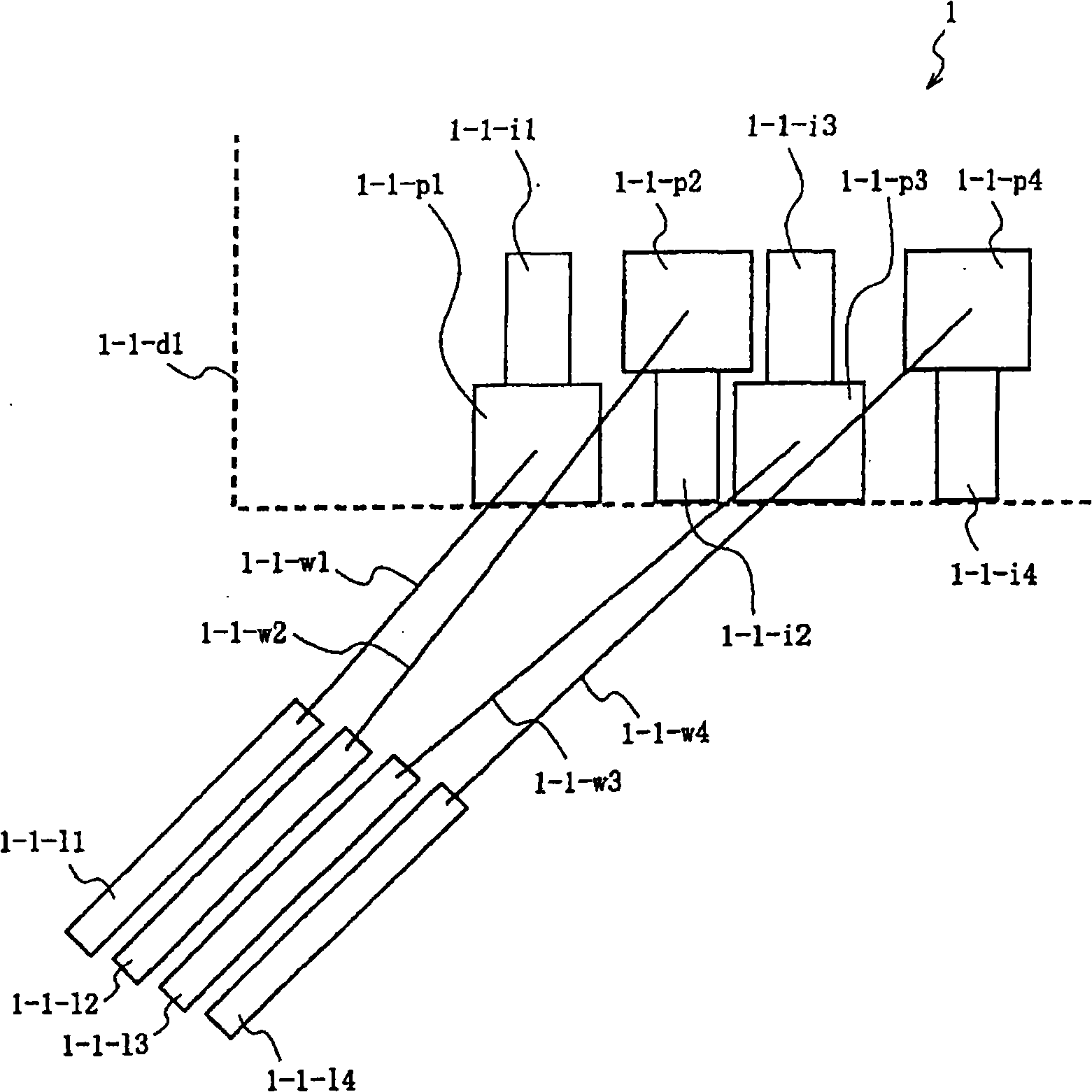

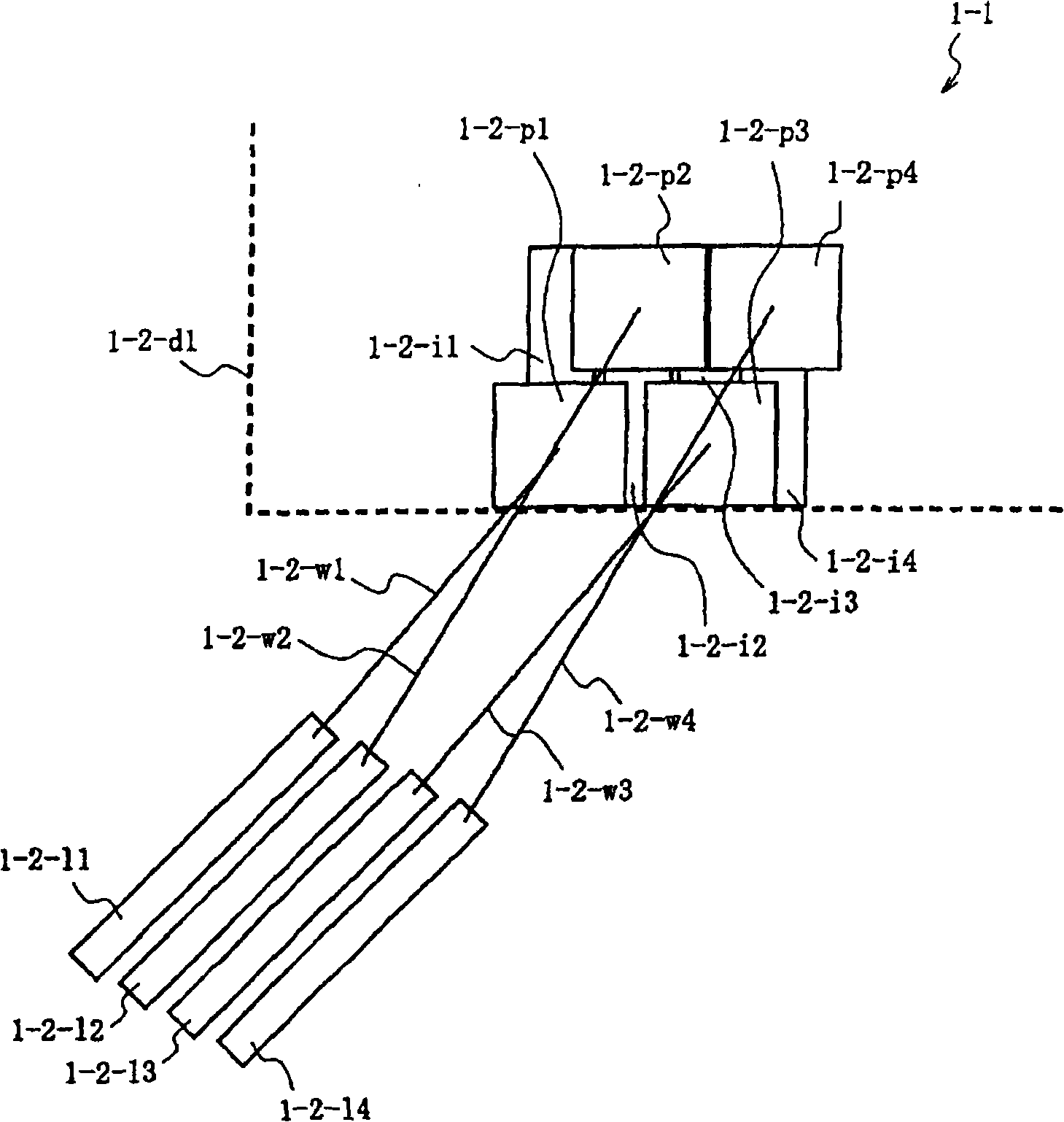

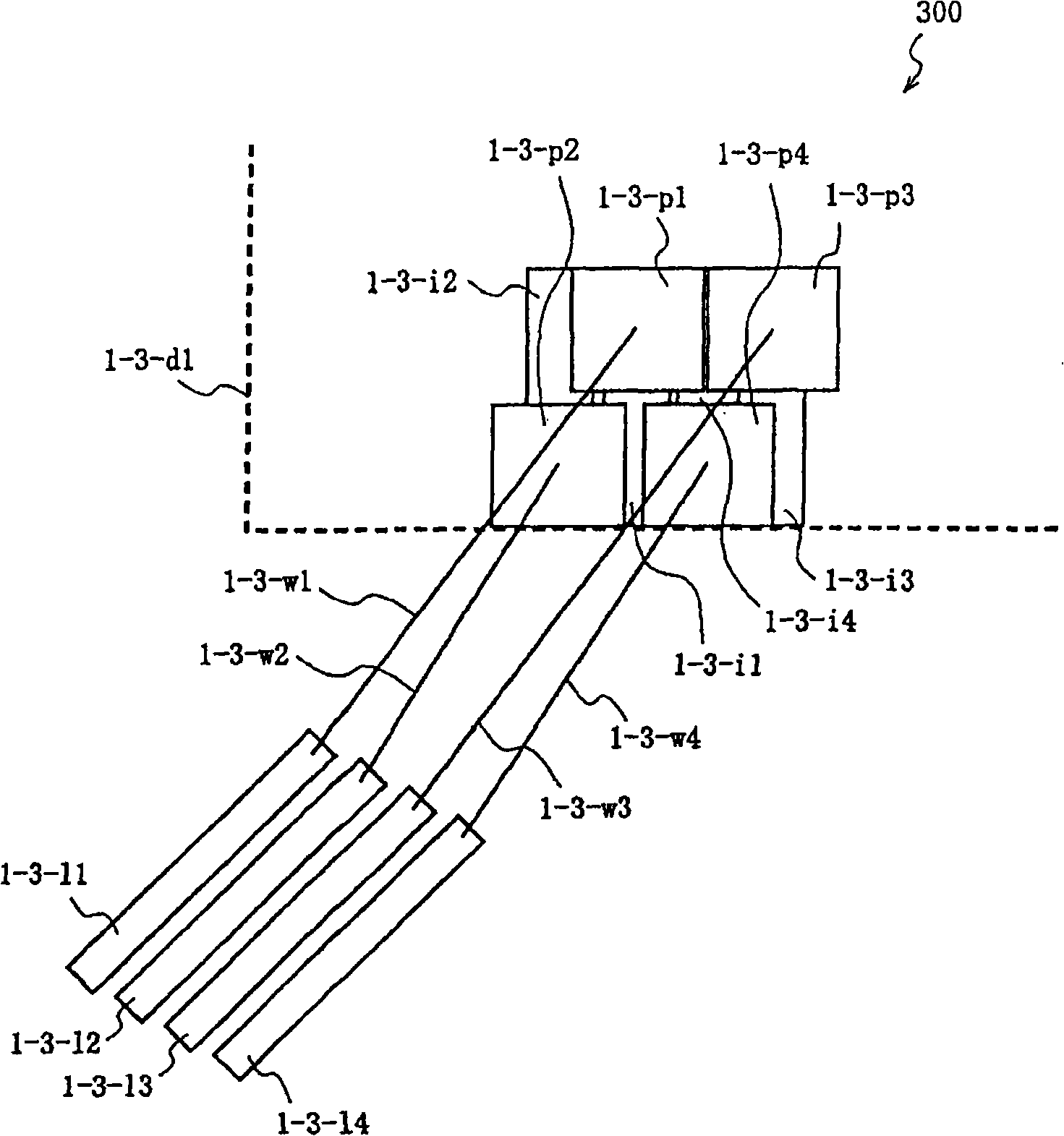

Solid-state imaging device and semiconductor display device

ActiveUS20120002090A1Suppress potential decreaseSuppress signal delayTelevision system detailsTelevision system scanning detailsDisplay deviceEngineering

An object is to provide a solid-state imaging device or a semiconductor display device with which a high-quality image can be taken. By performing operation using a global shutter method, a potential for controlling charge accumulation operation can be shared by all pixels. In addition, a first photosensor group includes a plurality of photosensors connected to a wiring supplied with an output signal, and a second photosensor group includes a plurality of photosensors connected to another wiring supplied with the output signal. A wiring for supplying a potential or a signal for controlling charge accumulation operation to the first photosensor group is connected to a wiring for supplying the potential or signal to the second photosensor group.

Owner:SEMICON ENERGY LAB CO LTD

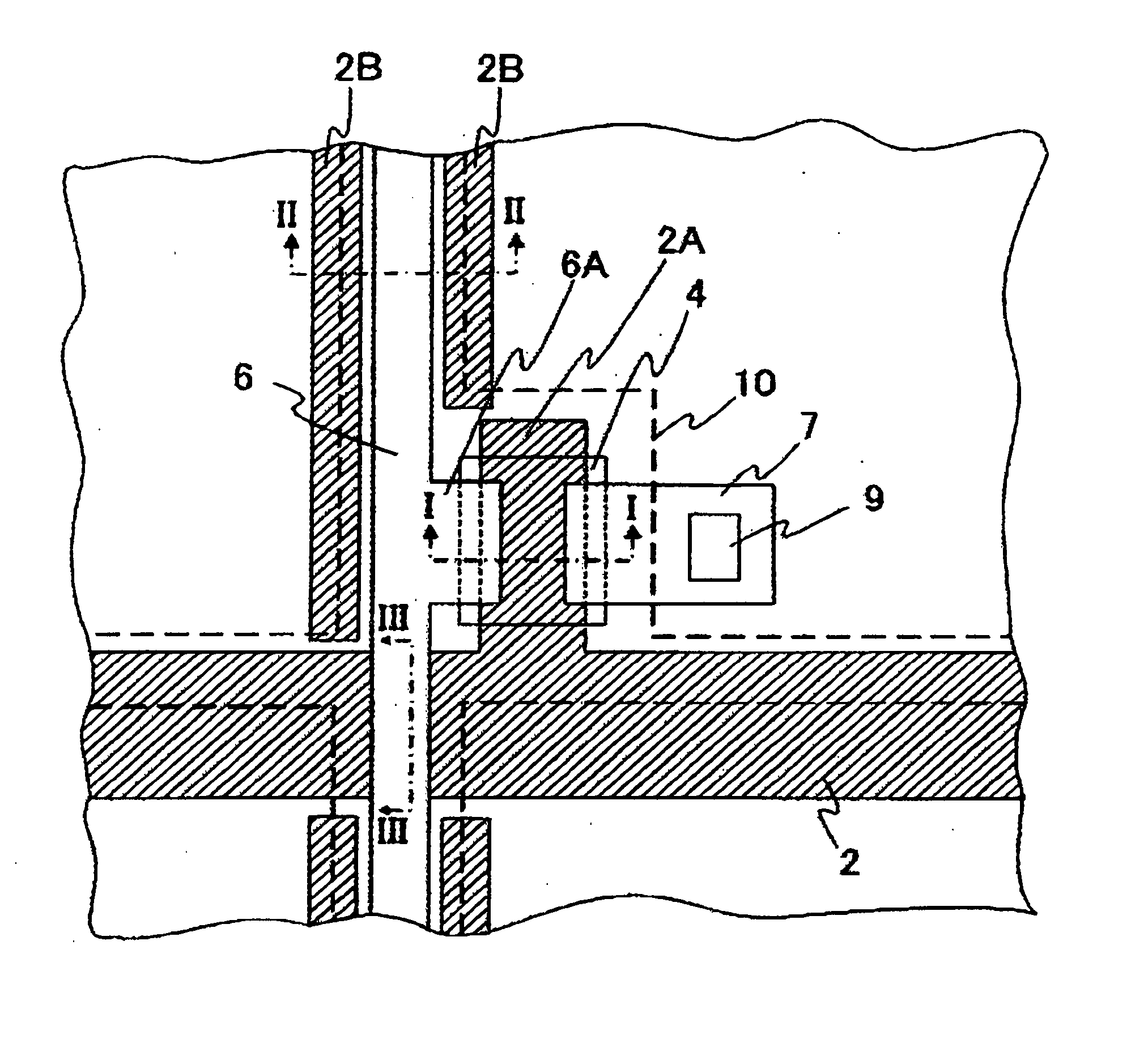

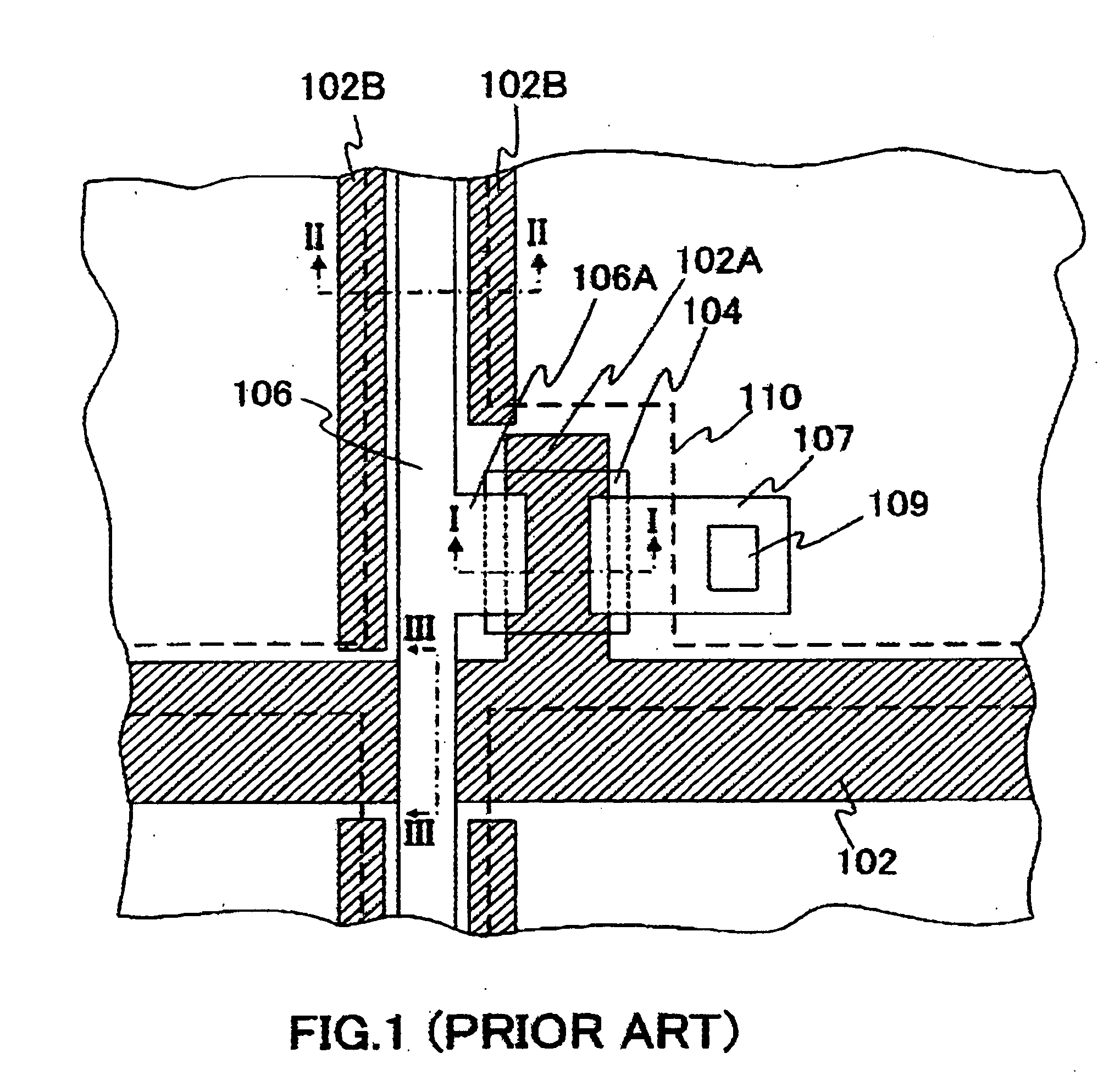

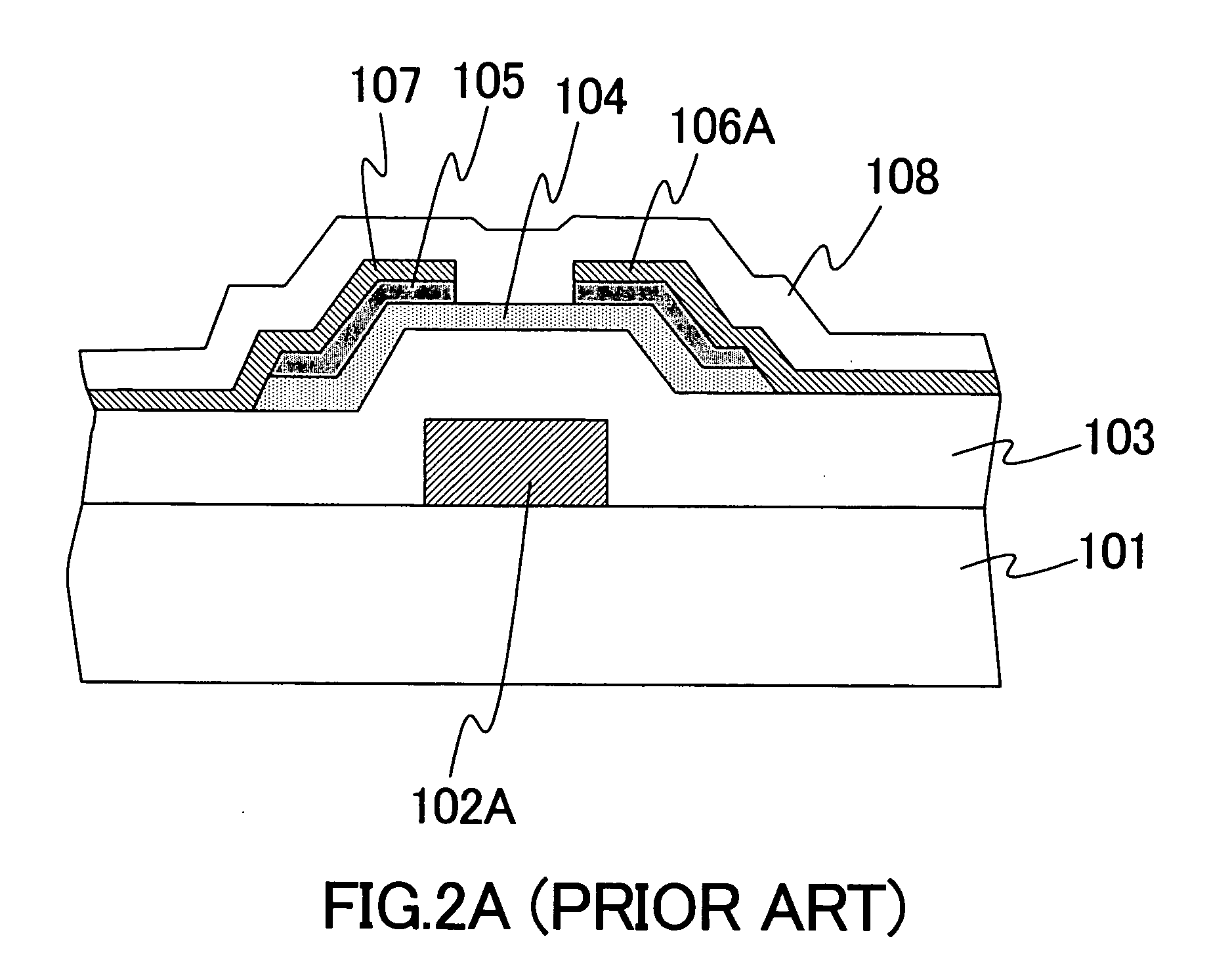

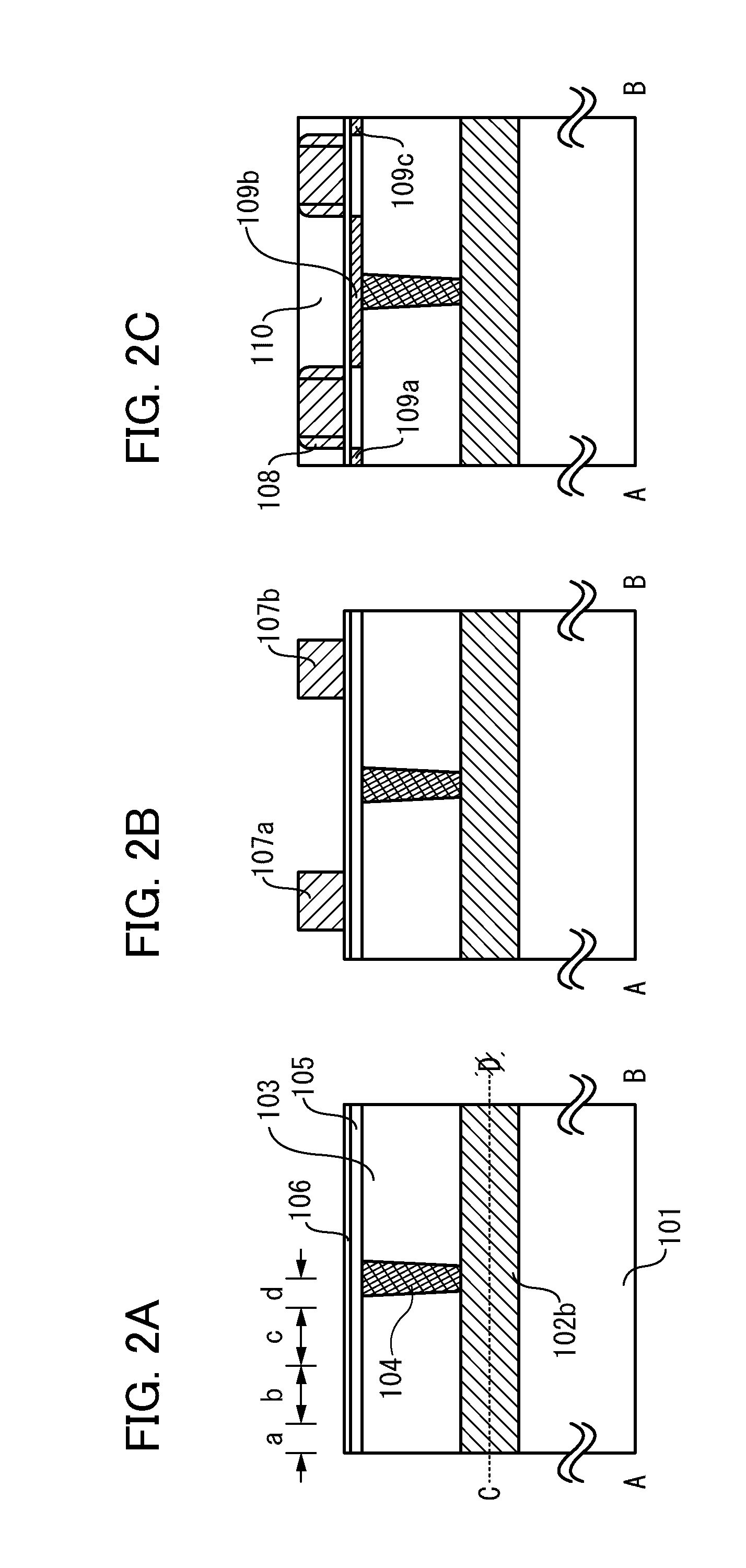

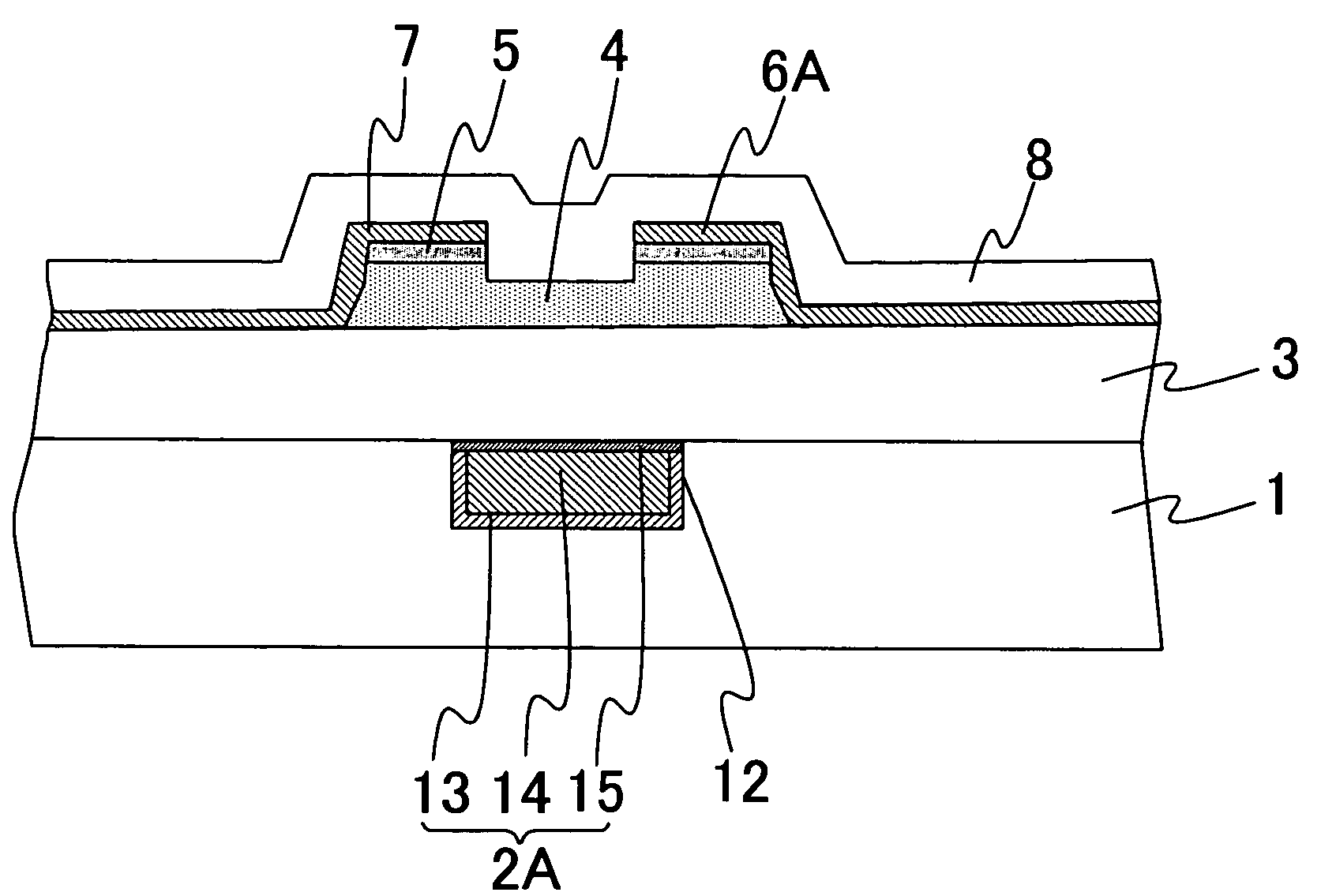

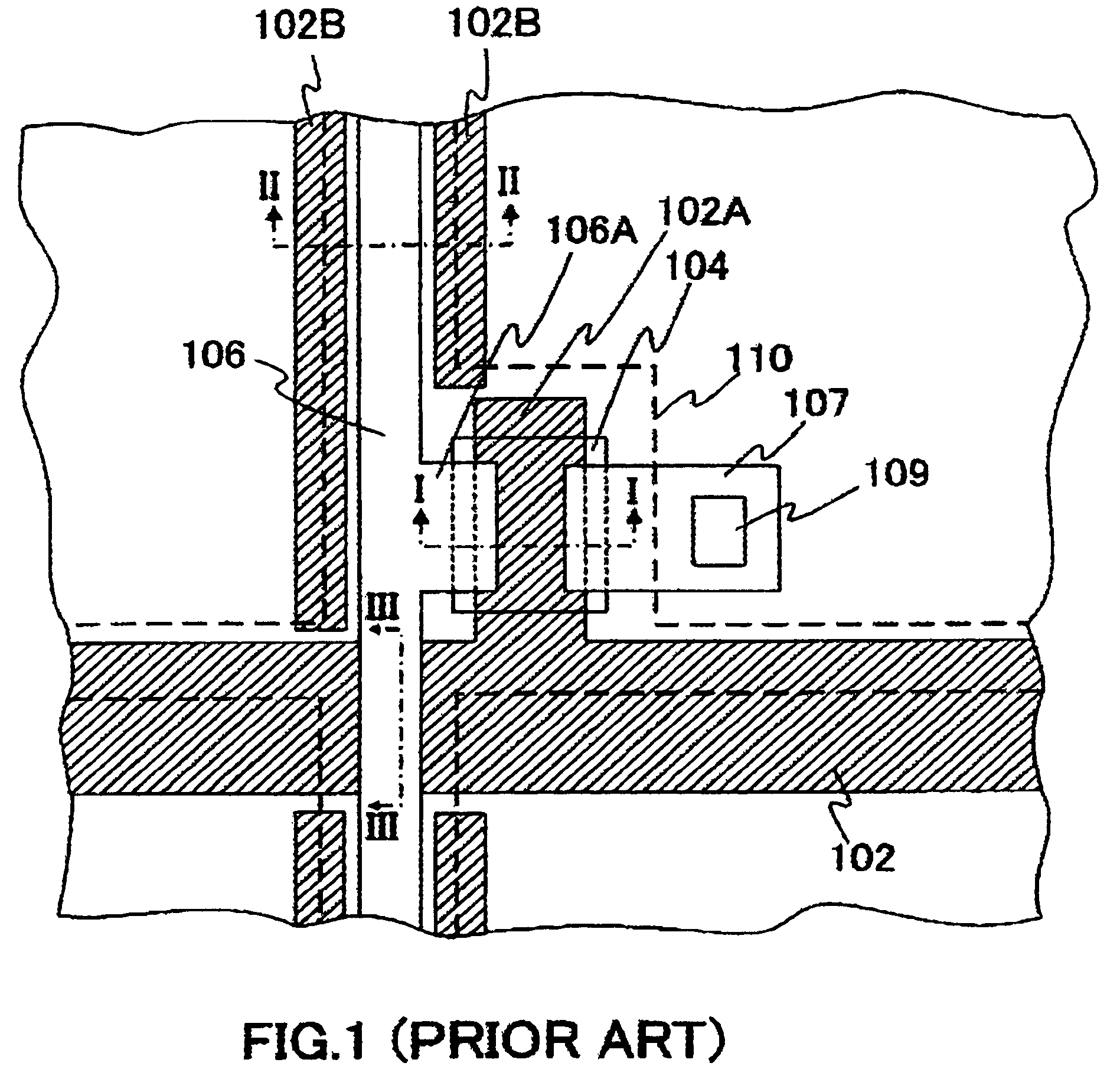

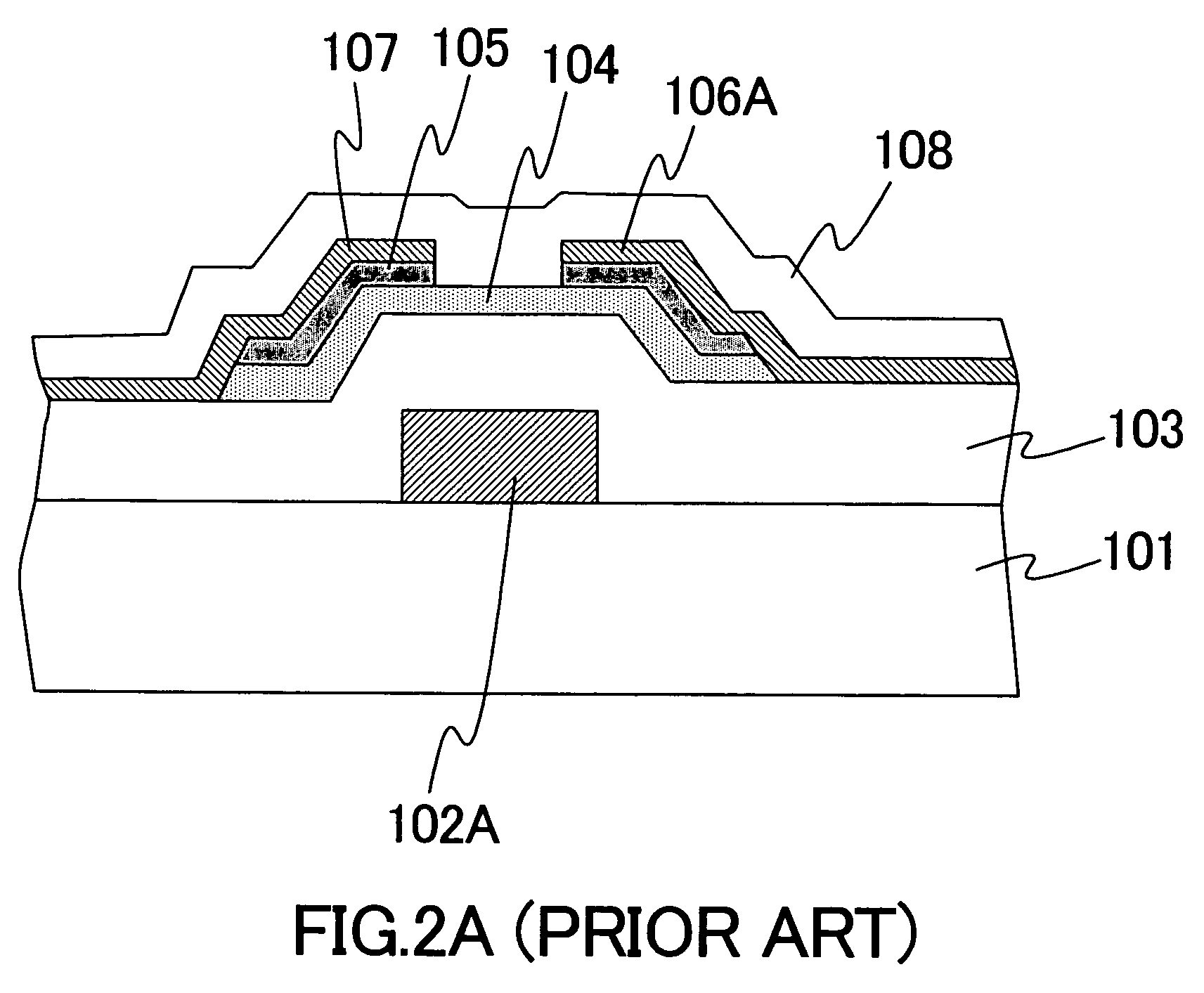

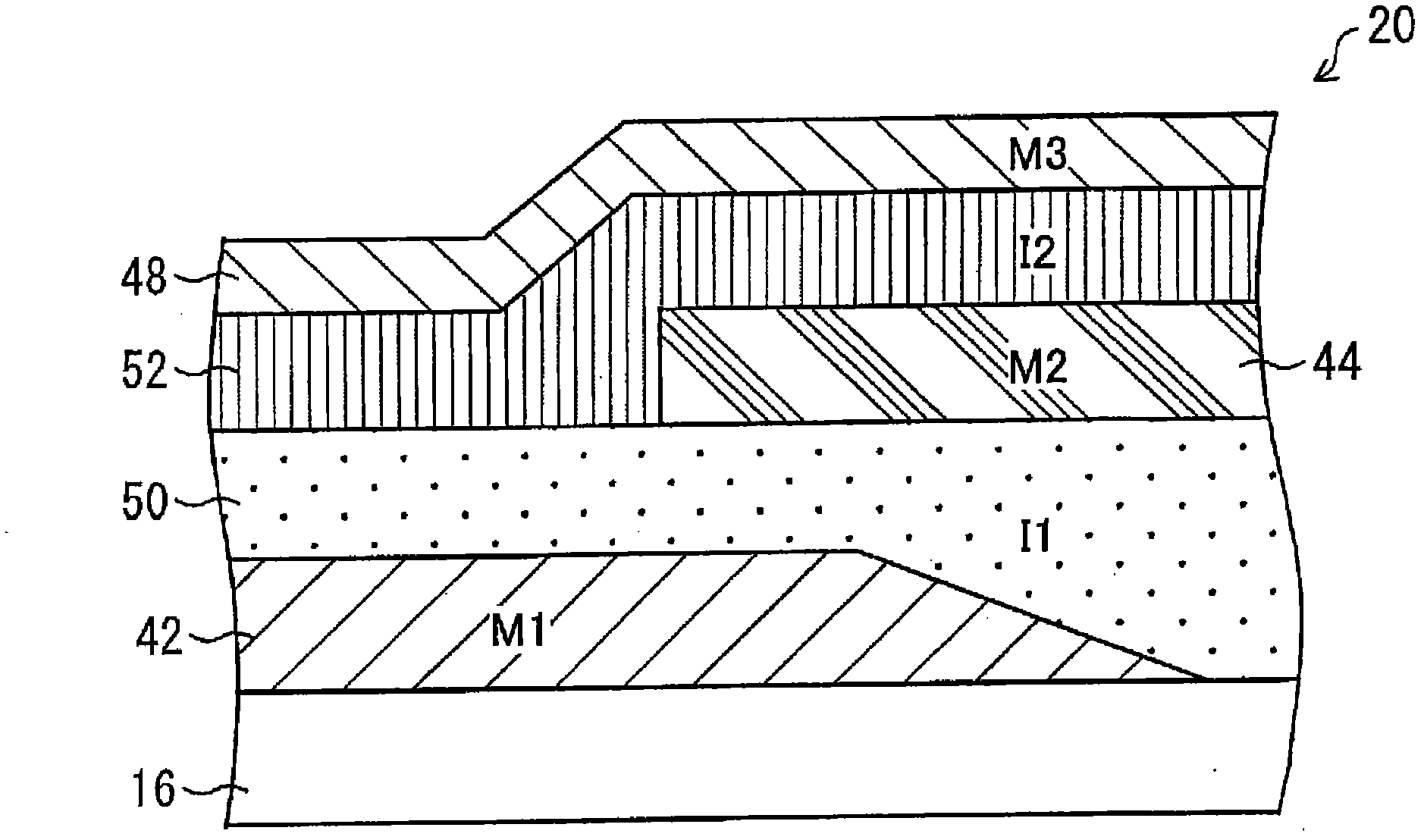

Liquid crystal display device and manufacturing method of the same

InactiveUS20060209222A1Small sizeHigh densitySolid-state devicesNon-linear opticsHigh densityLiquid-crystal display

An active matrix substrate or TFT substrate is provided with a lower layer wiring with a groove wiring structure covering surroundings of a copper layer with a barrier metal film is formed by forming a groove at an insulating substrate and depositing the barrier metal film and the copper layer in this groove. This groove wiring structure is used for a TFT substrate of a liquid crystal display (LCD) device. It is possible to manufacture an LCD device with large size, high density, a large aperture ratio and in which the disclination defects originating from a different in level of the lower layer wiring and an occurrence of disconnection failures in an upper layer wiring are suppressed.

Owner:VISTA PEAK VENTURES LLC

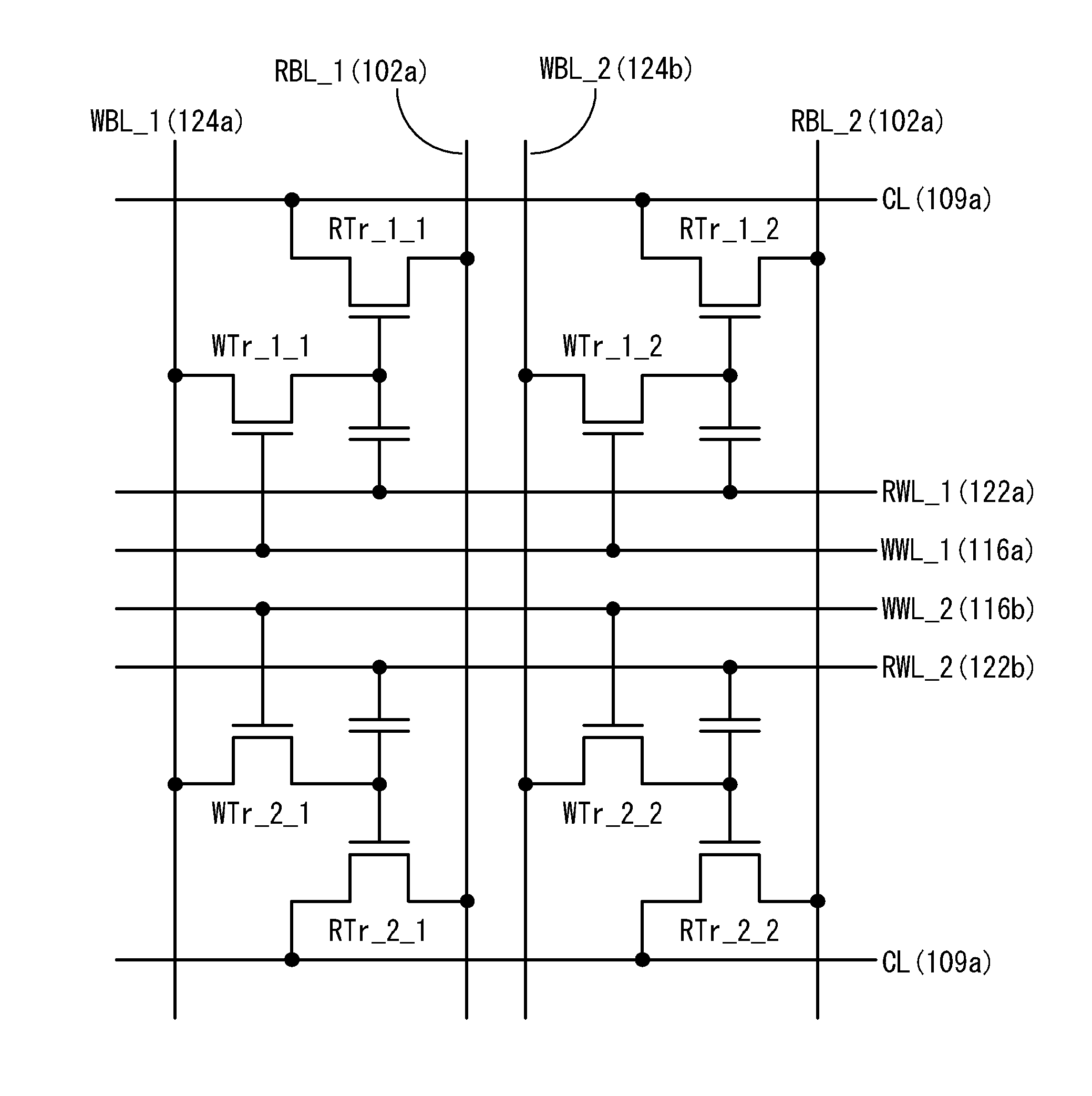

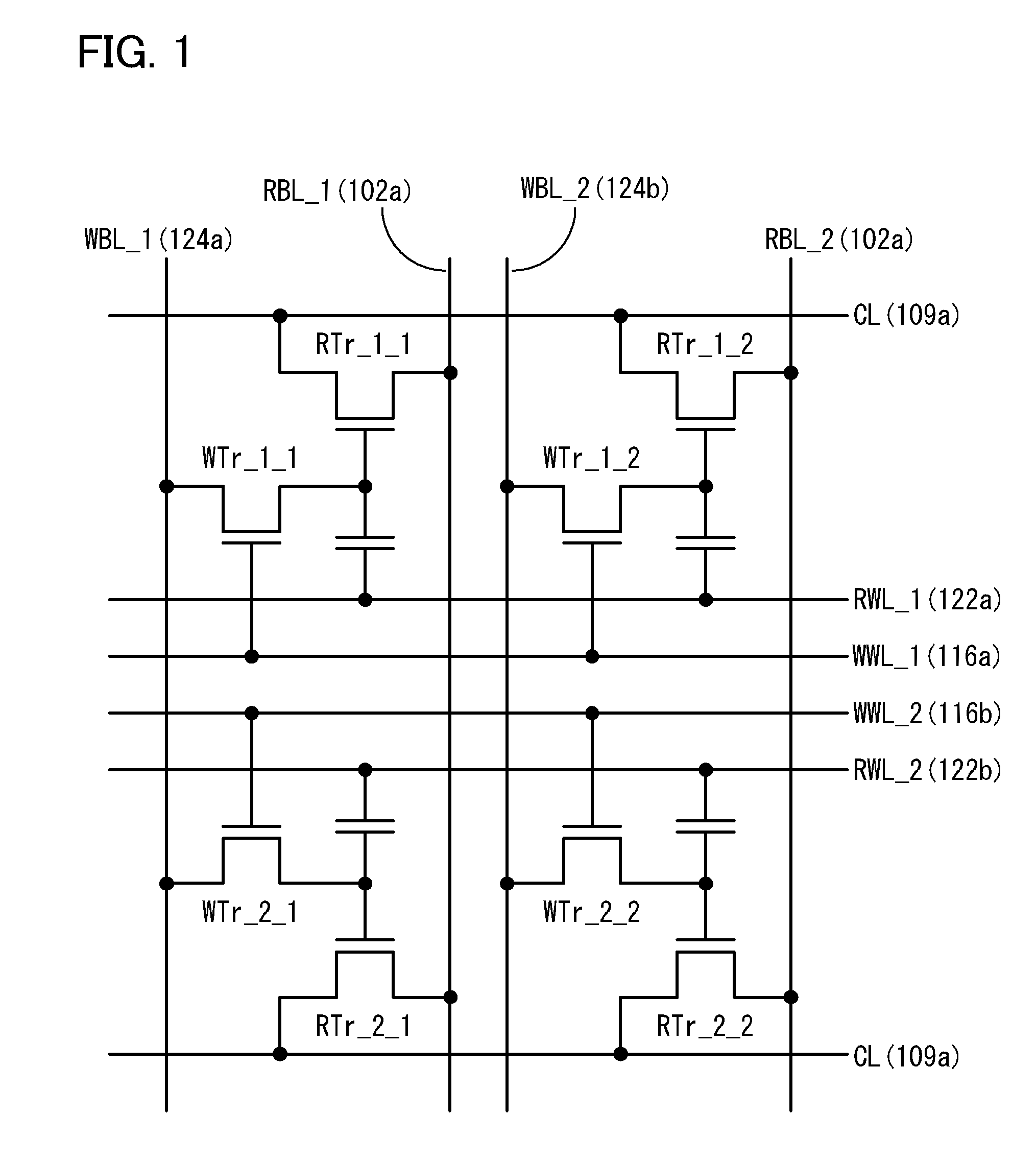

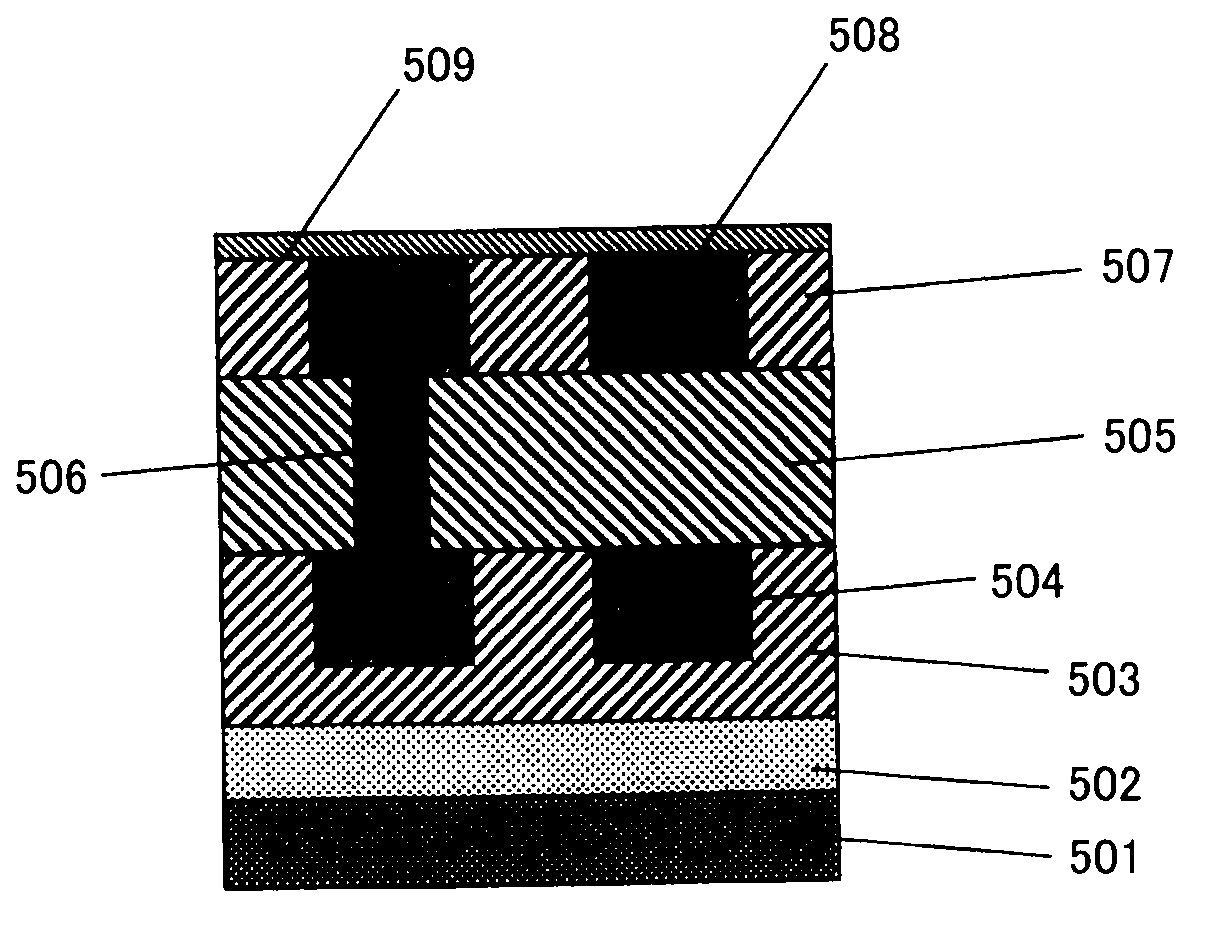

Semiconductor memory device and method of manufacturing semiconductor memory device

InactiveUS20120213000A1Reduce parasitic capacitanceParasitic capacitance is generatedTransistorSolid-state devicesWrite bitMemory cell

A highly integrated gain cell-type semiconductor memory is provided. A first insulator, a read bit line, a second insulator, a third insulator, a first semiconductor film, first conductive layers, and the like are formed. A projecting insulator is formed thereover. Then, second semiconductor films and a second gate insulating film are formed to cover the projecting insulator. After that, a conductive film is formed and subjected to anisotropic etching, so that write word lines are formed on side surfaces of the projecting insulator. A third contact plug for connection to a write bit line is formed over a top of the projecting insulator. With such a structure, the area of the memory cell can be 4 F2 at a minimum.

Owner:SEMICON ENERGY LAB CO LTD

Liquid crystal display device and manufacturing method of the same

InactiveCN1834740AGood chemical resistanceAccelerated corrosionTransistorStatic indicating devicesHigh densityLiquid-crystal display

An active matrix substrate or TFT substrate is provided with a lower layer wiring with a groove wiring structure covering surroundings of a copper layer with a barrier metal film is formed by forming a groove at an insulating substrate and depositing the barrier metal film and the copper layer in this groove. This groove wiring structure is used for a TFT substrate of a liquid crystal display (LCD) device. It is possible to manufacture an LCD device with large size, high density, a large aperture ratio and in which the disclination defects originating from a different in level of the lower layer wiring and an occurrence of disconnection failures in an upper layer wiring are suppressed.

Owner:GETNER FOUND L L C

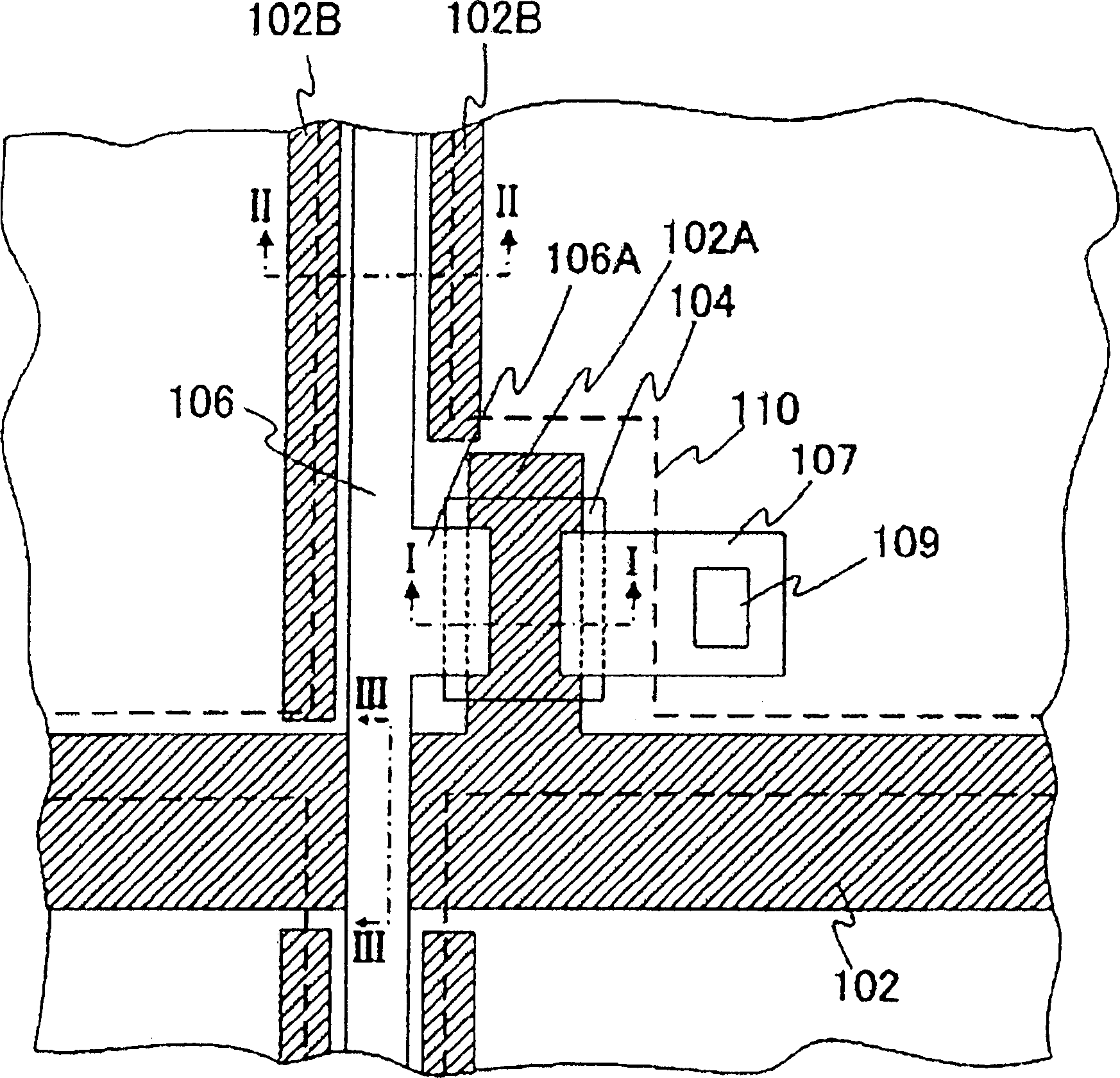

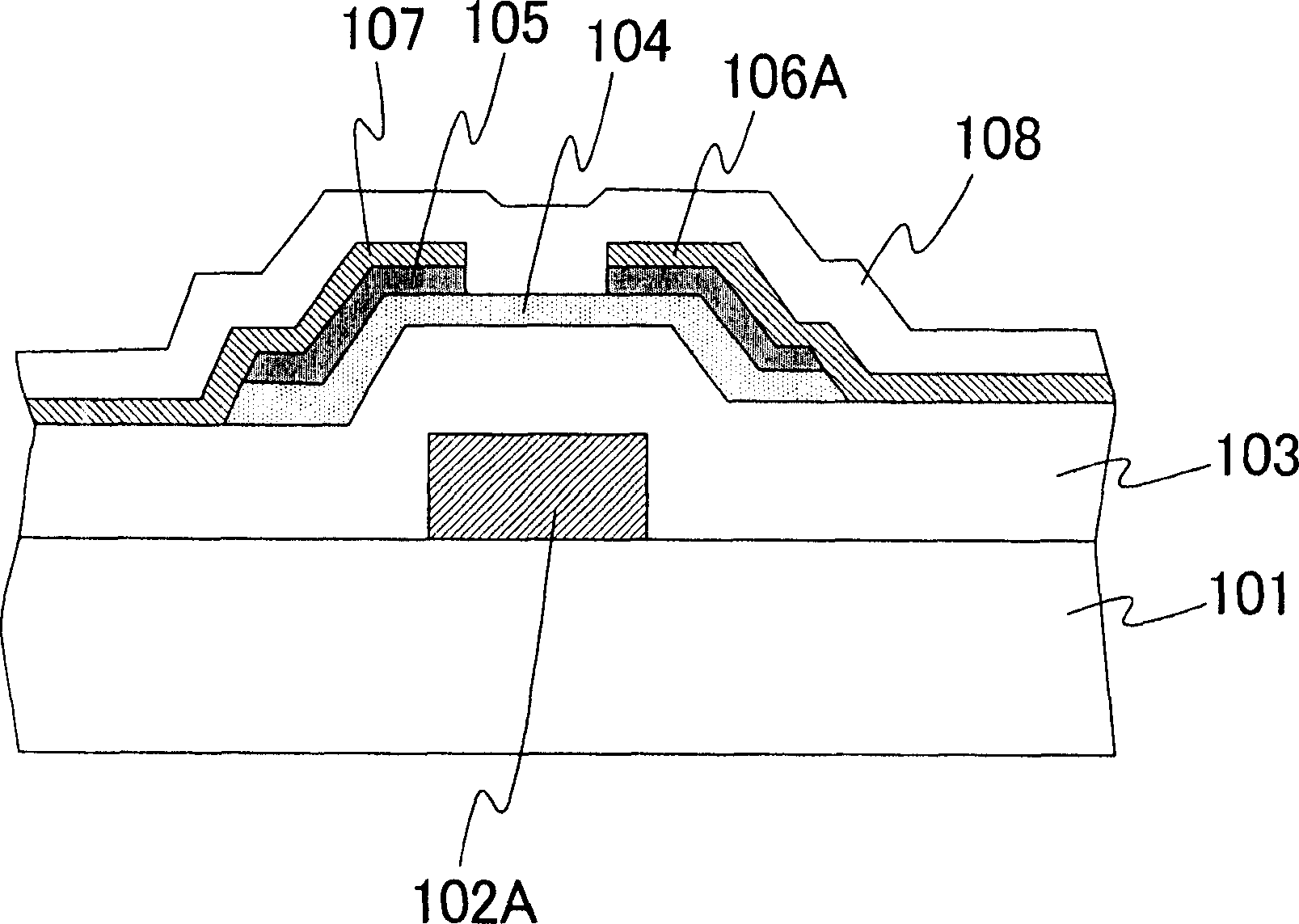

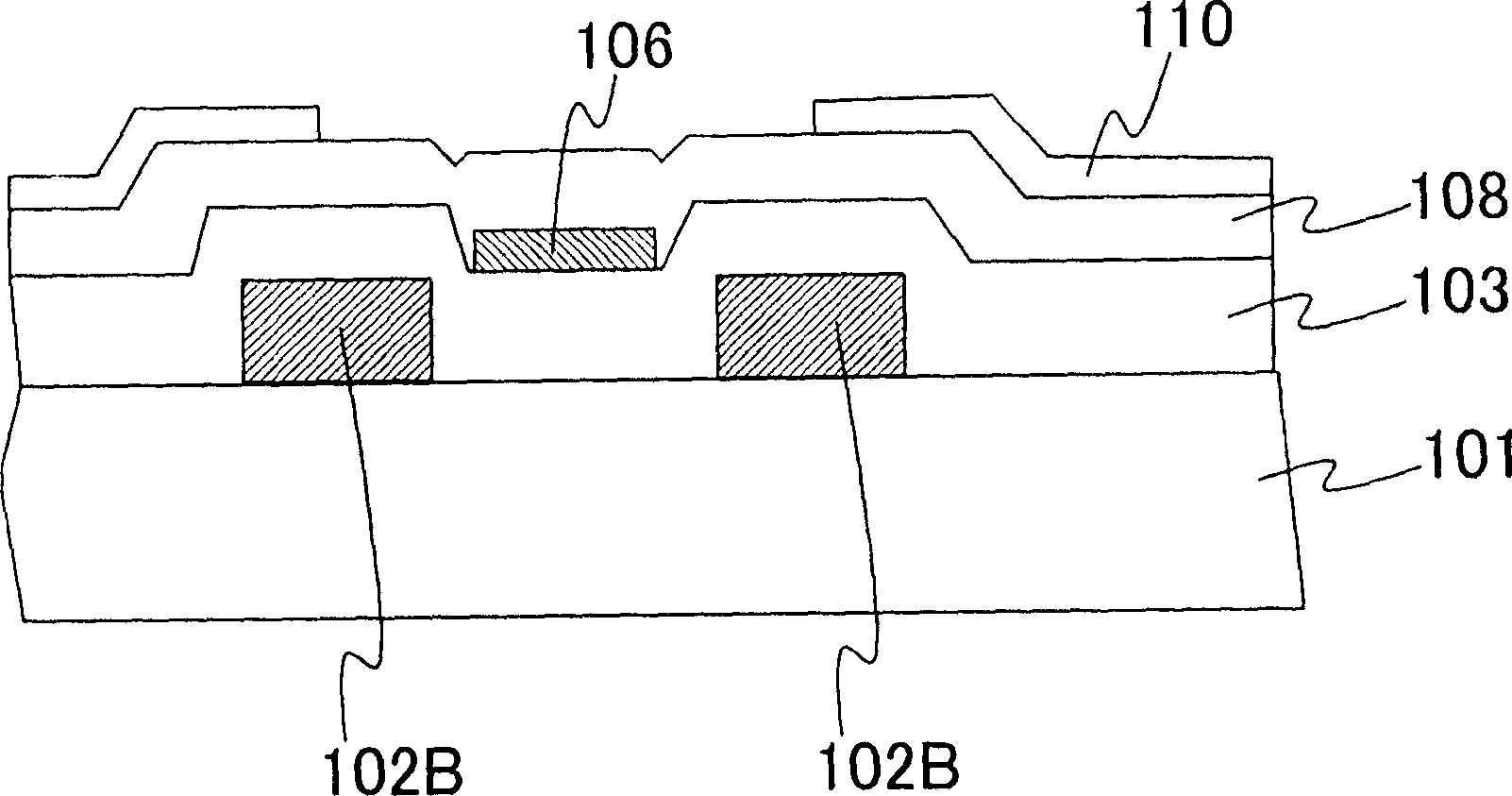

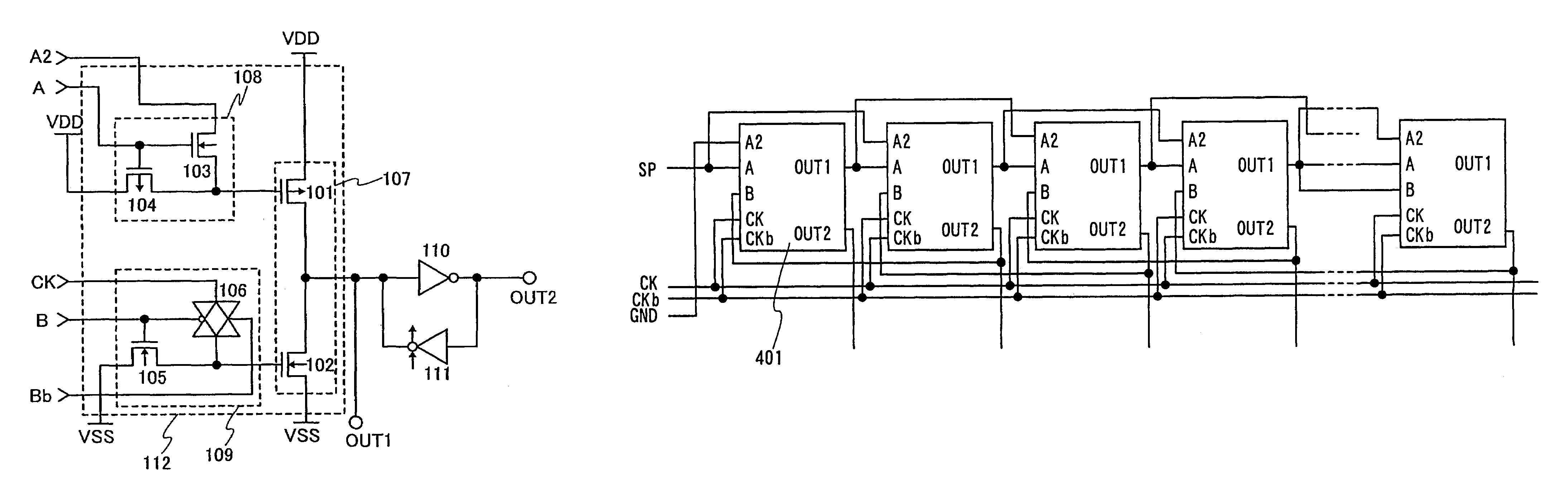

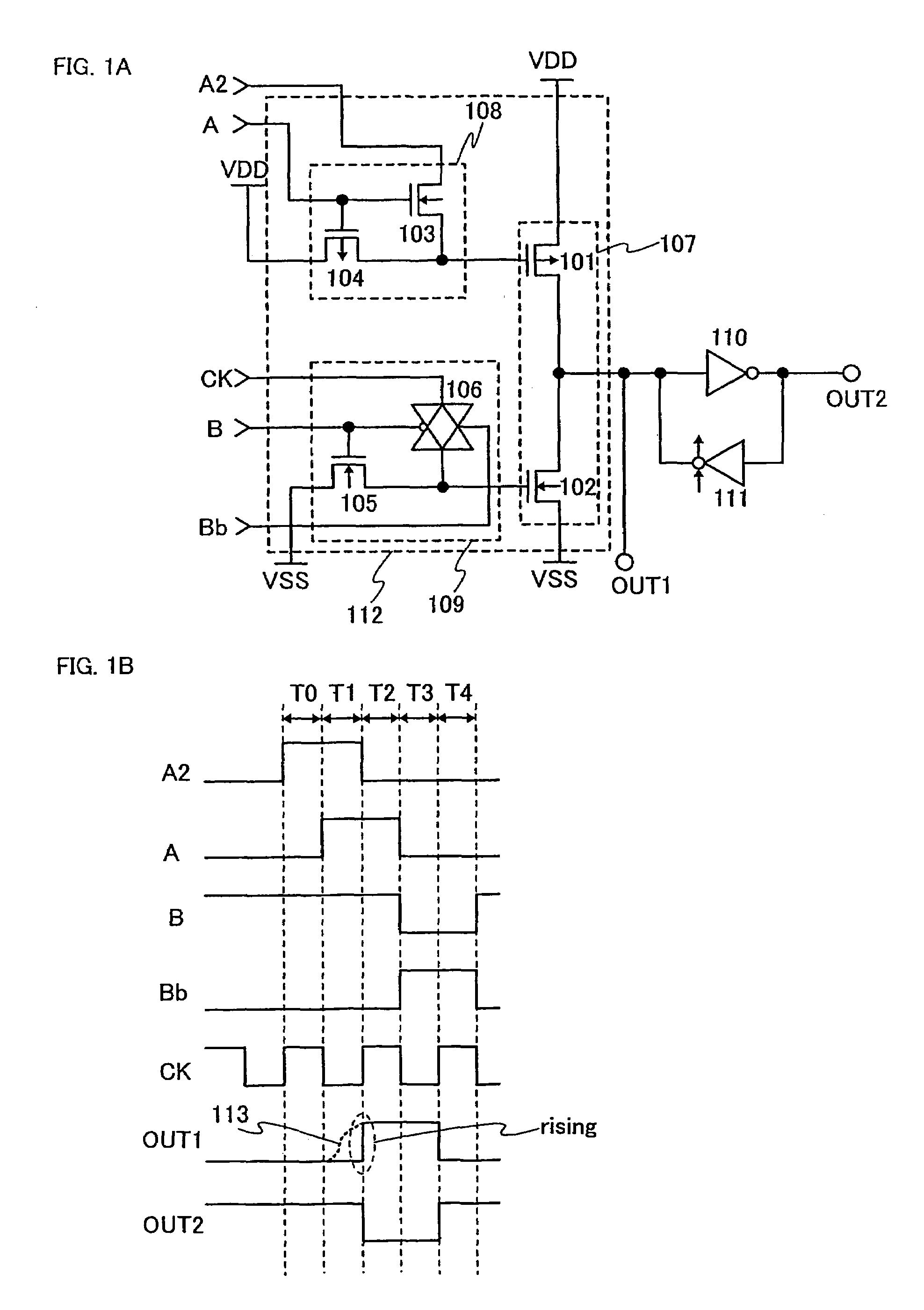

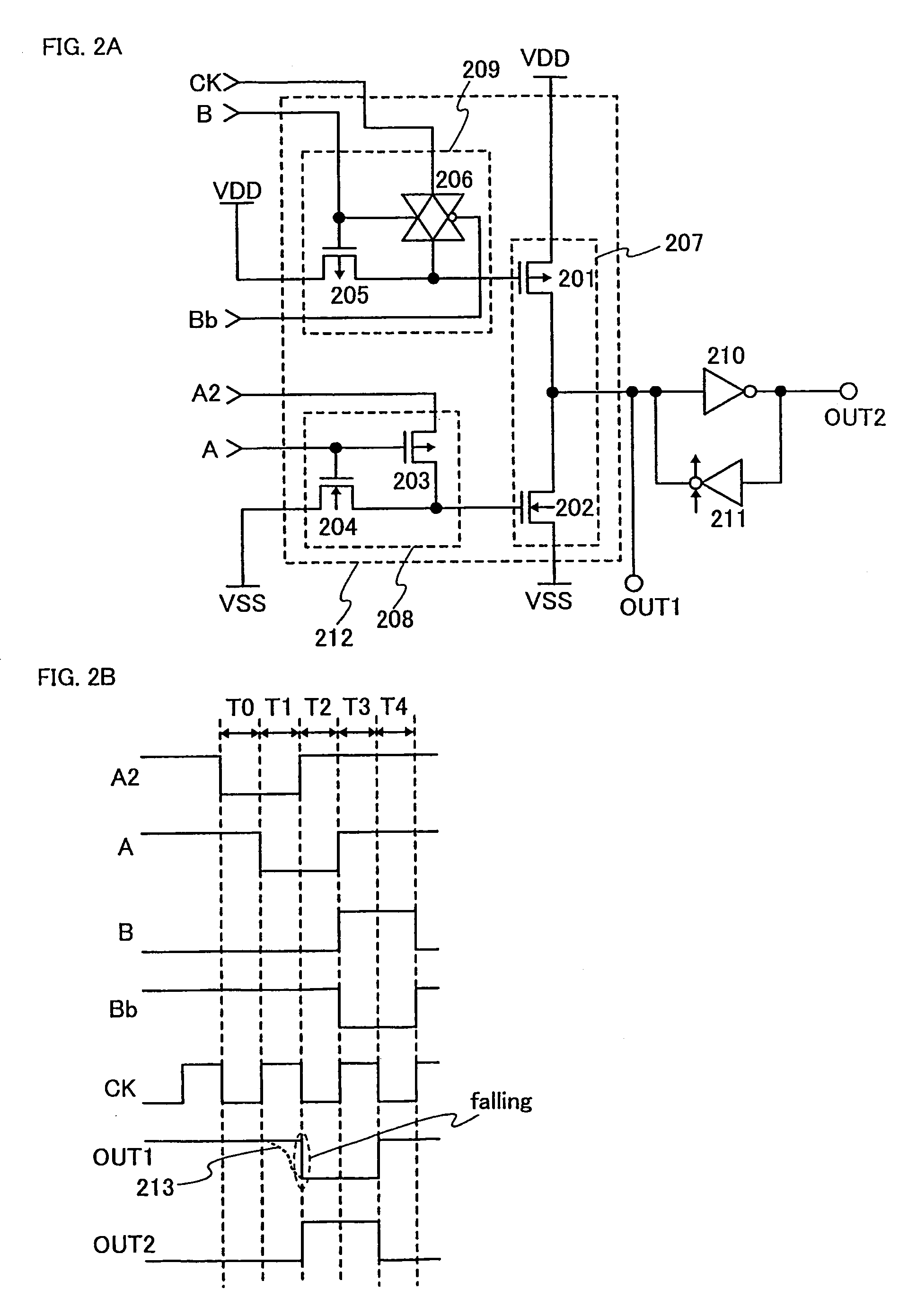

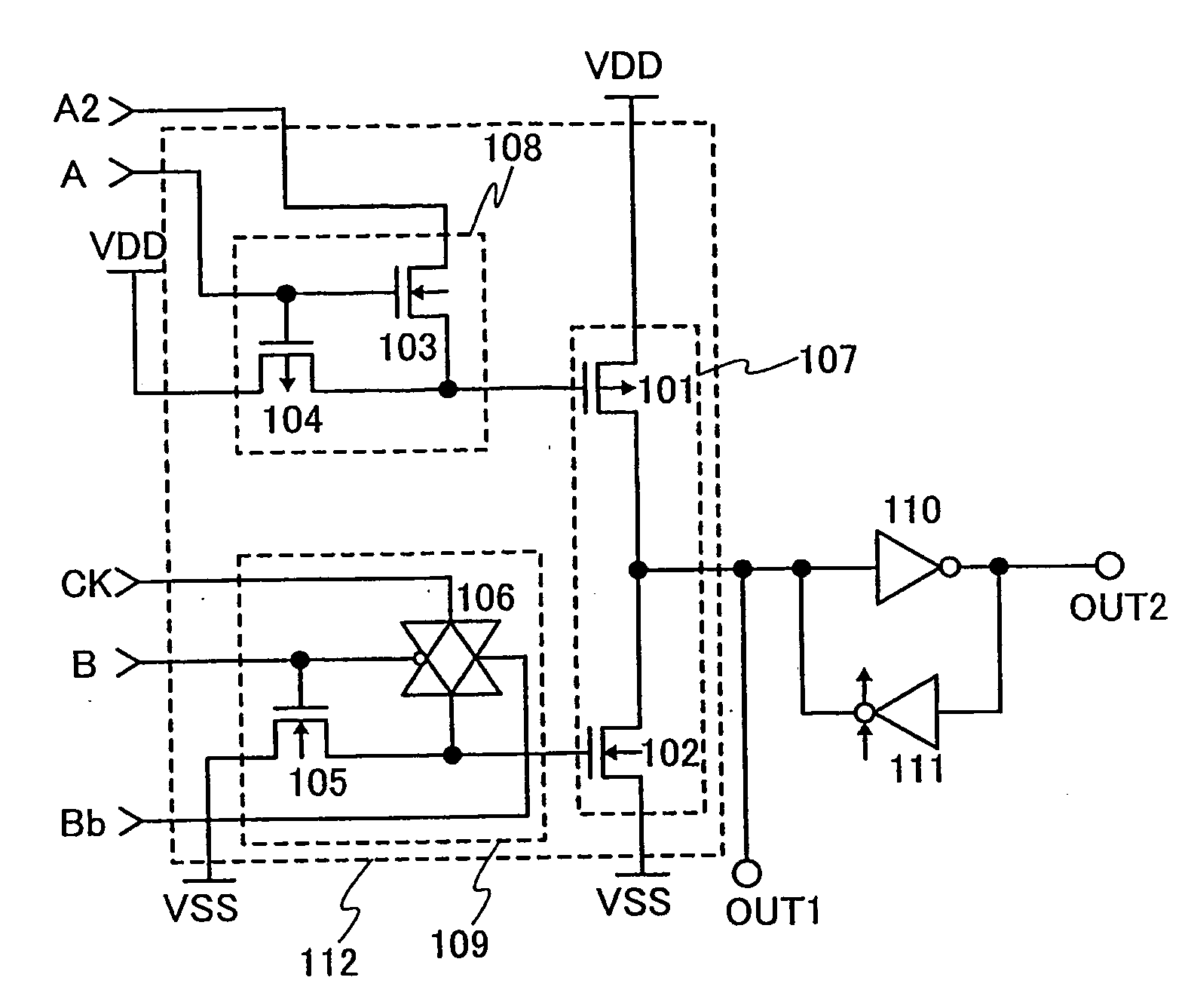

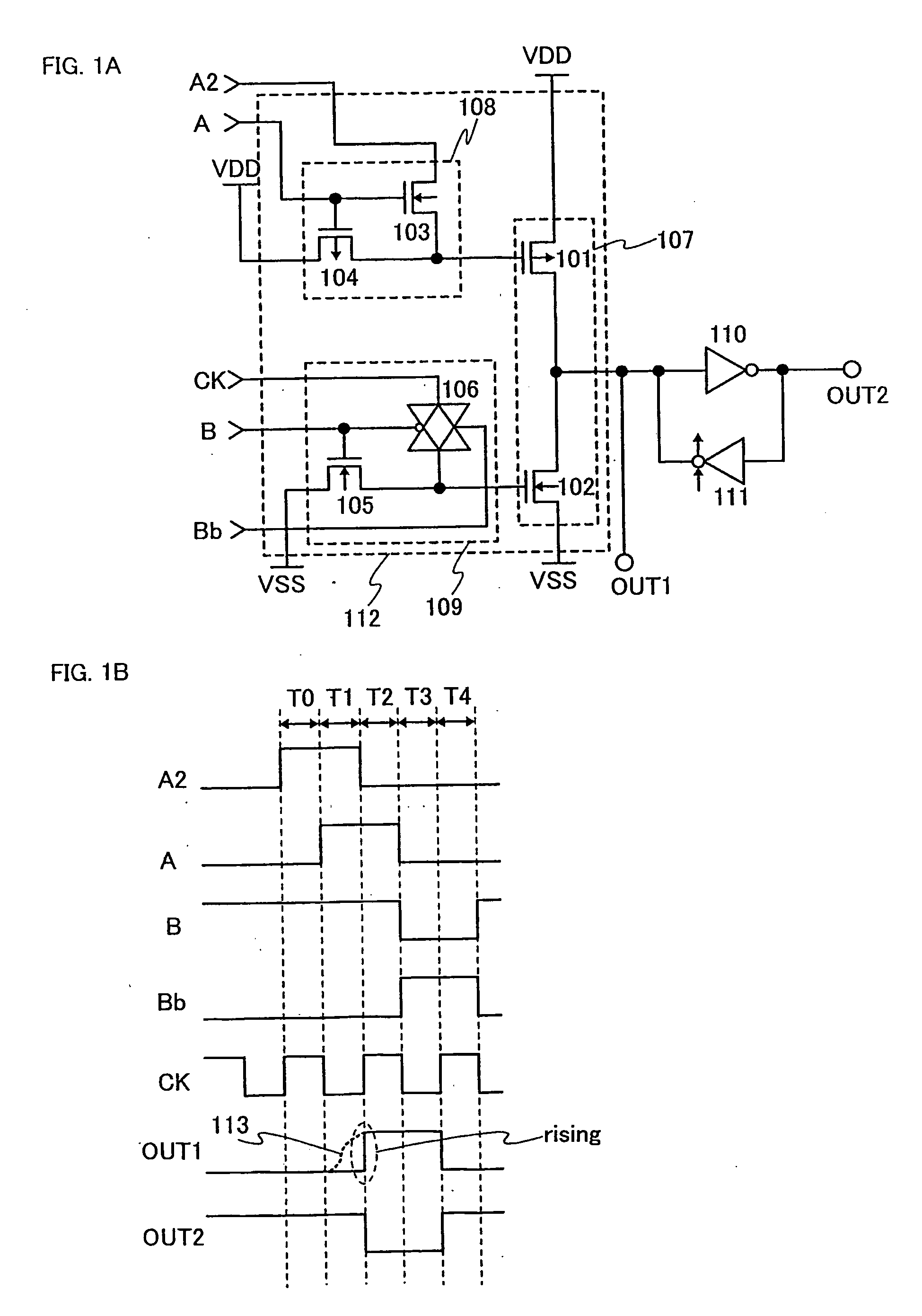

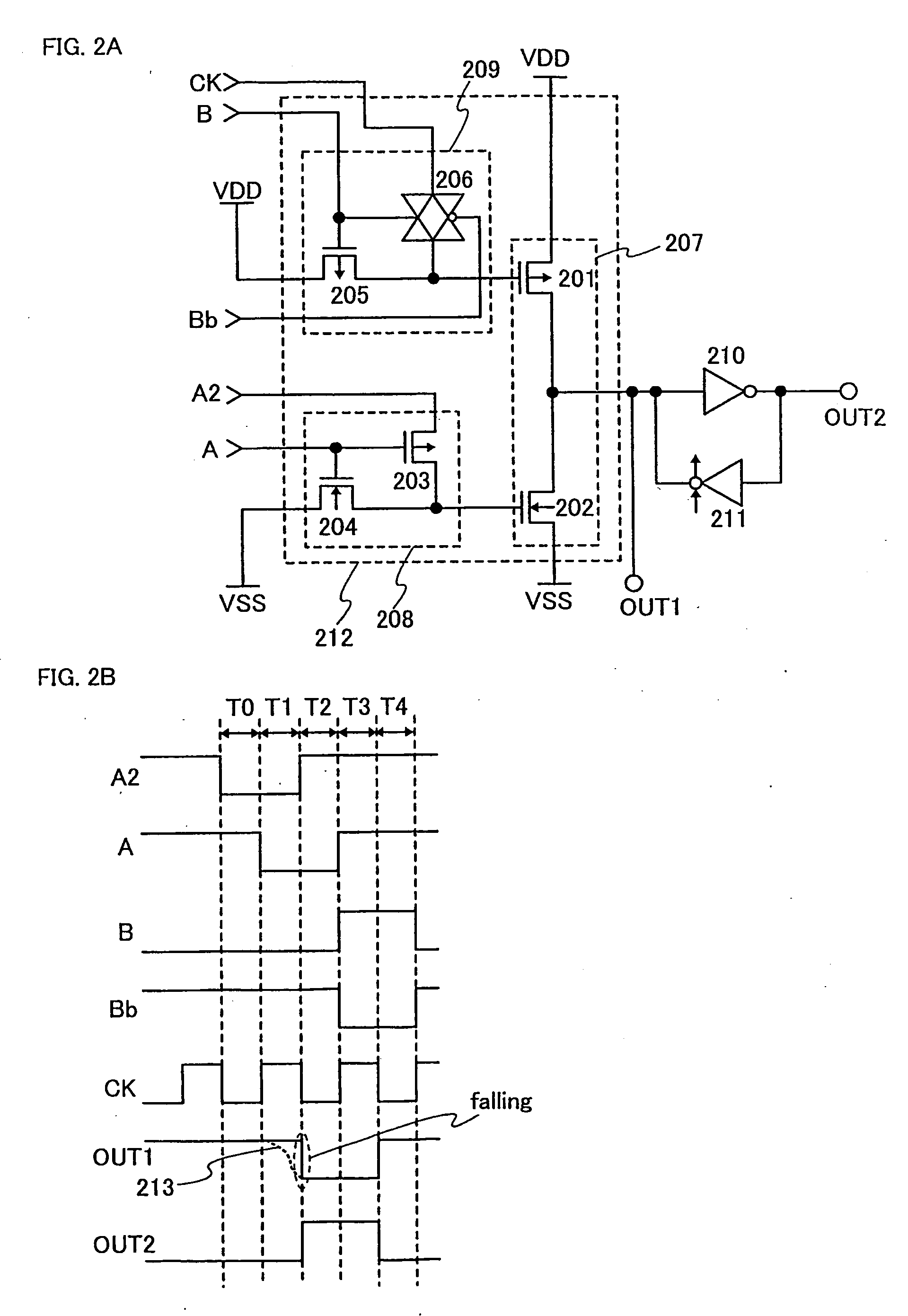

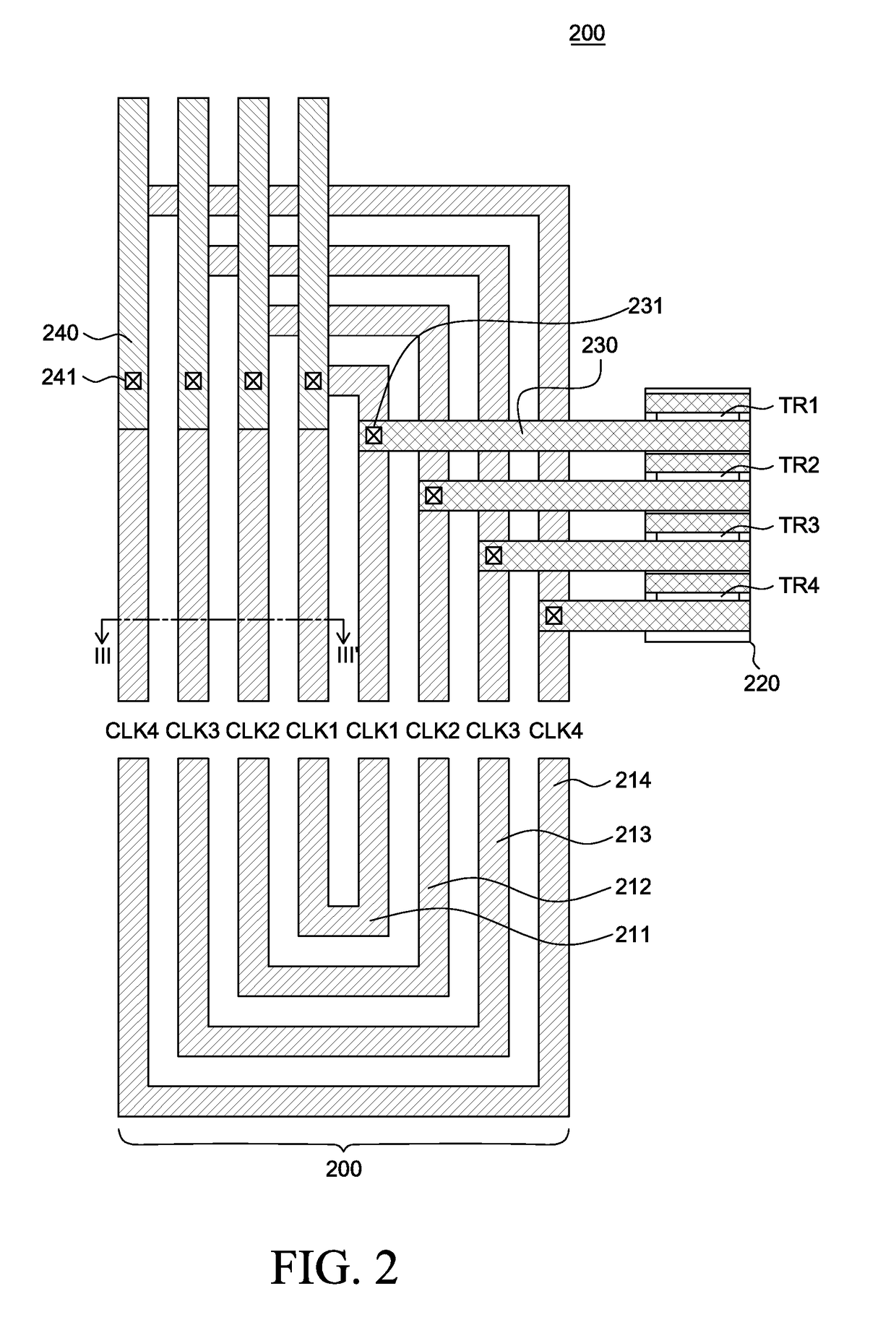

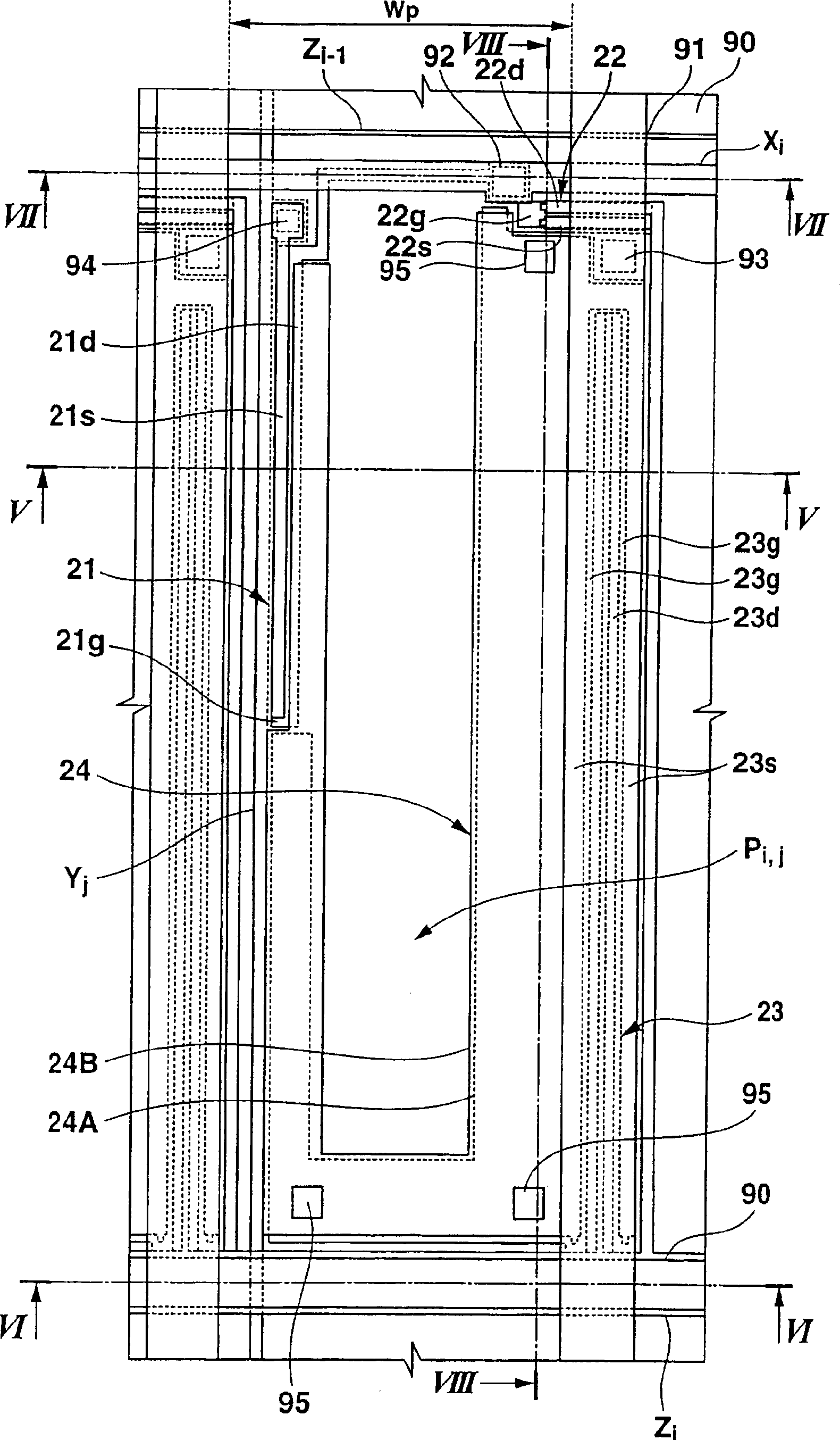

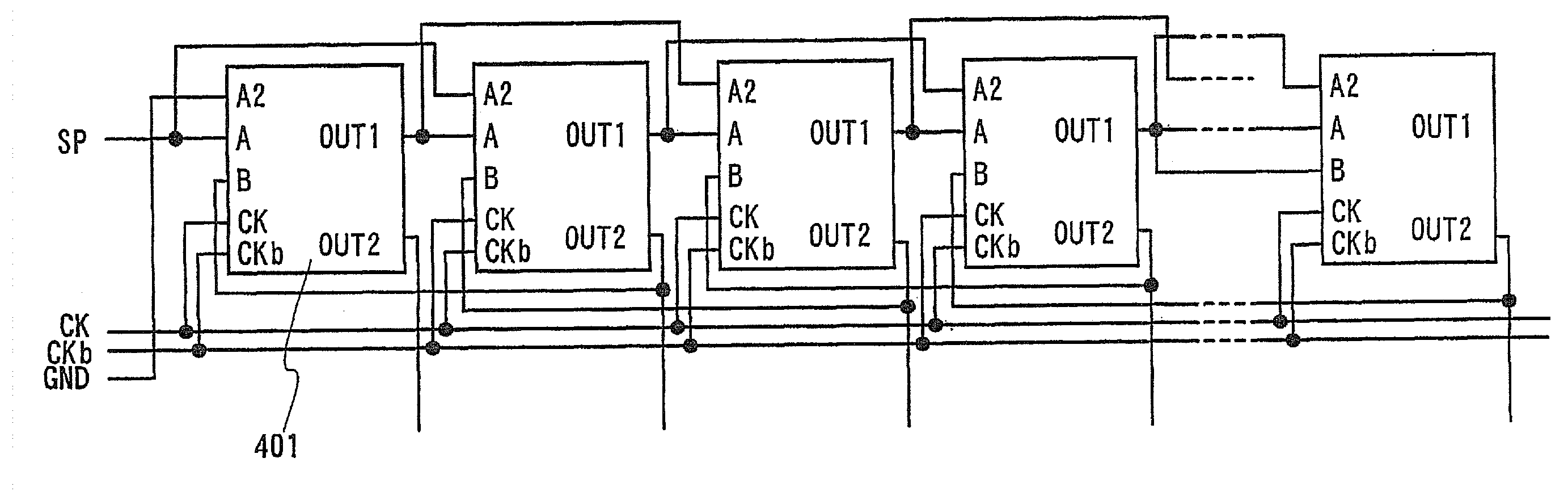

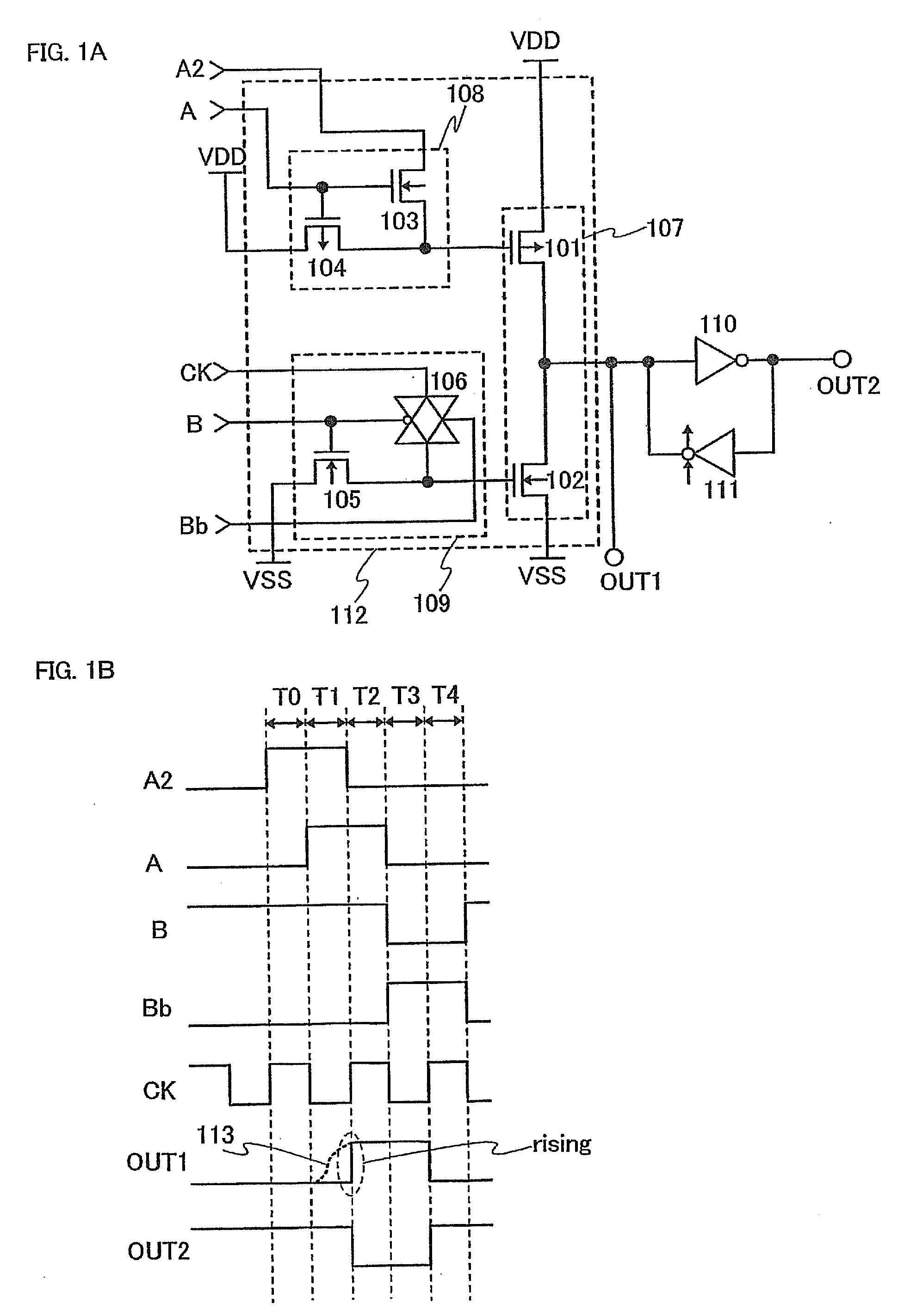

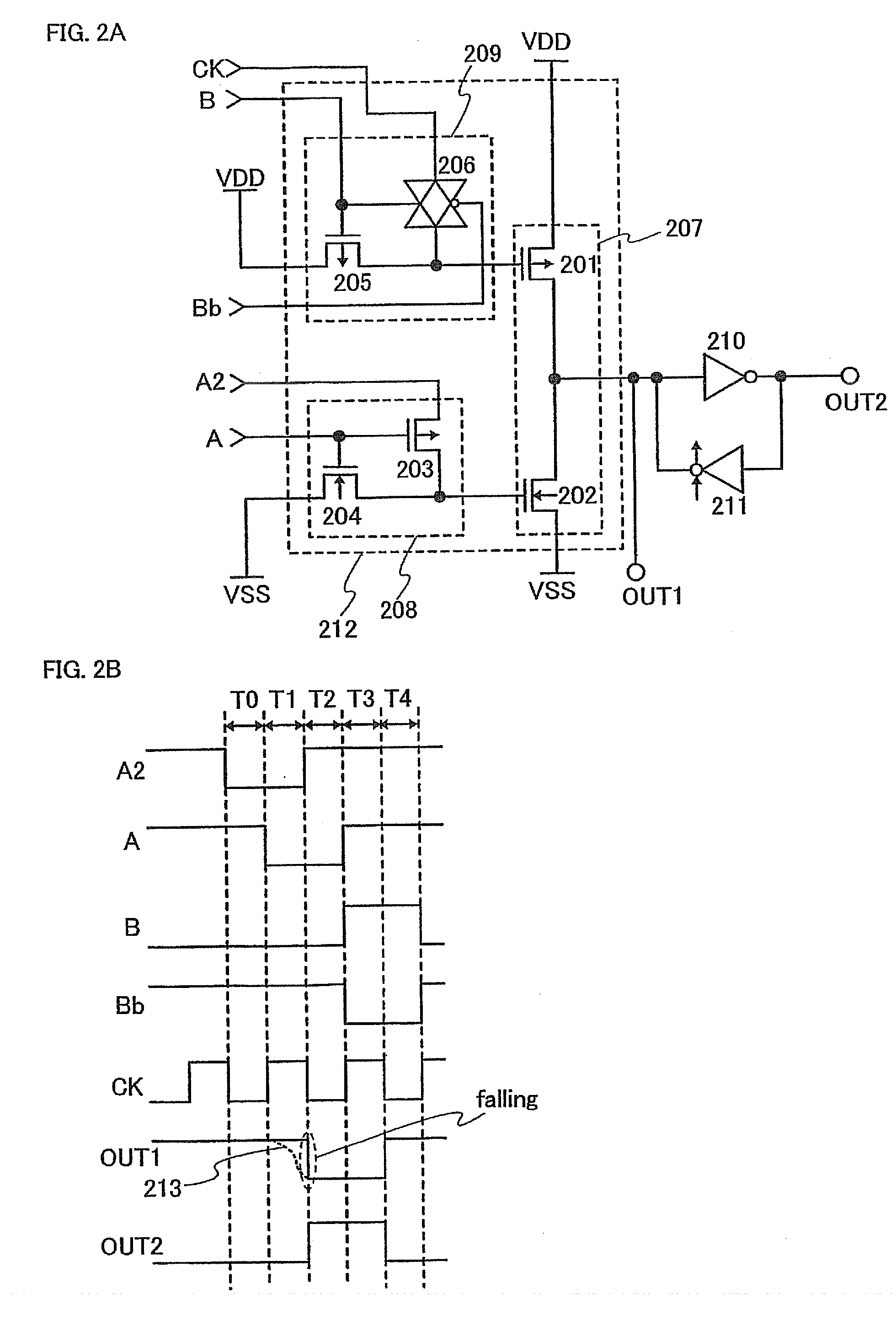

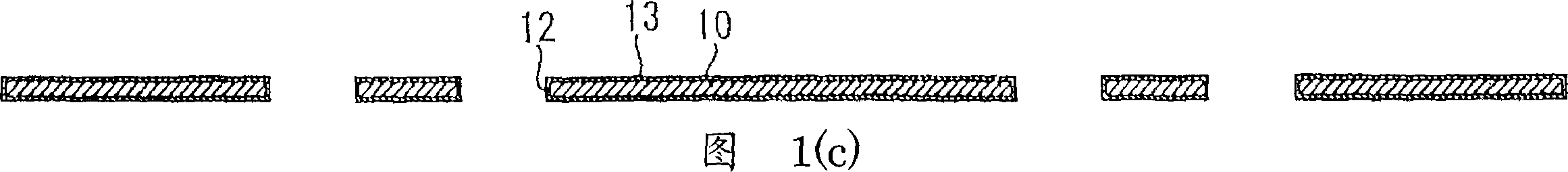

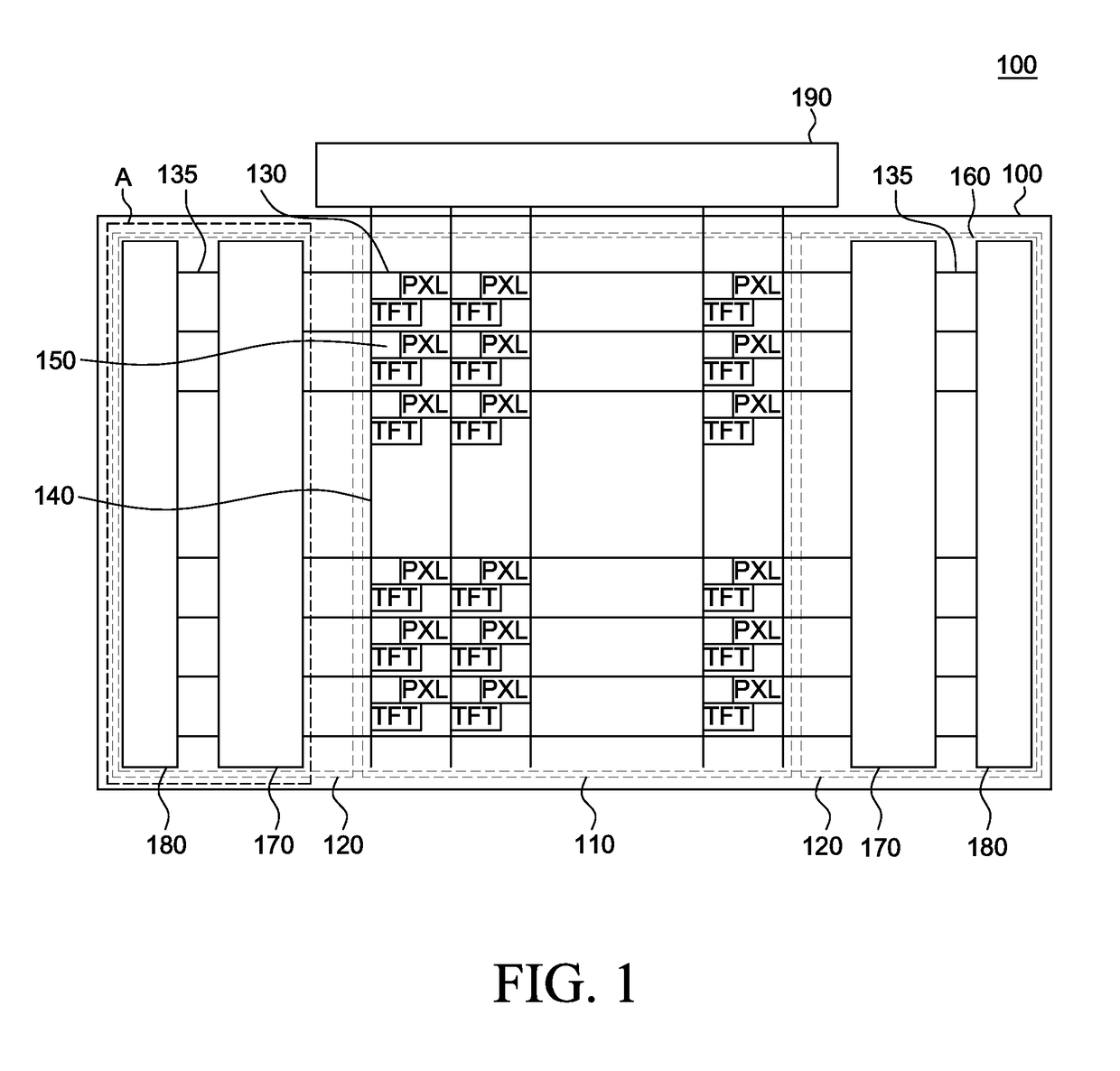

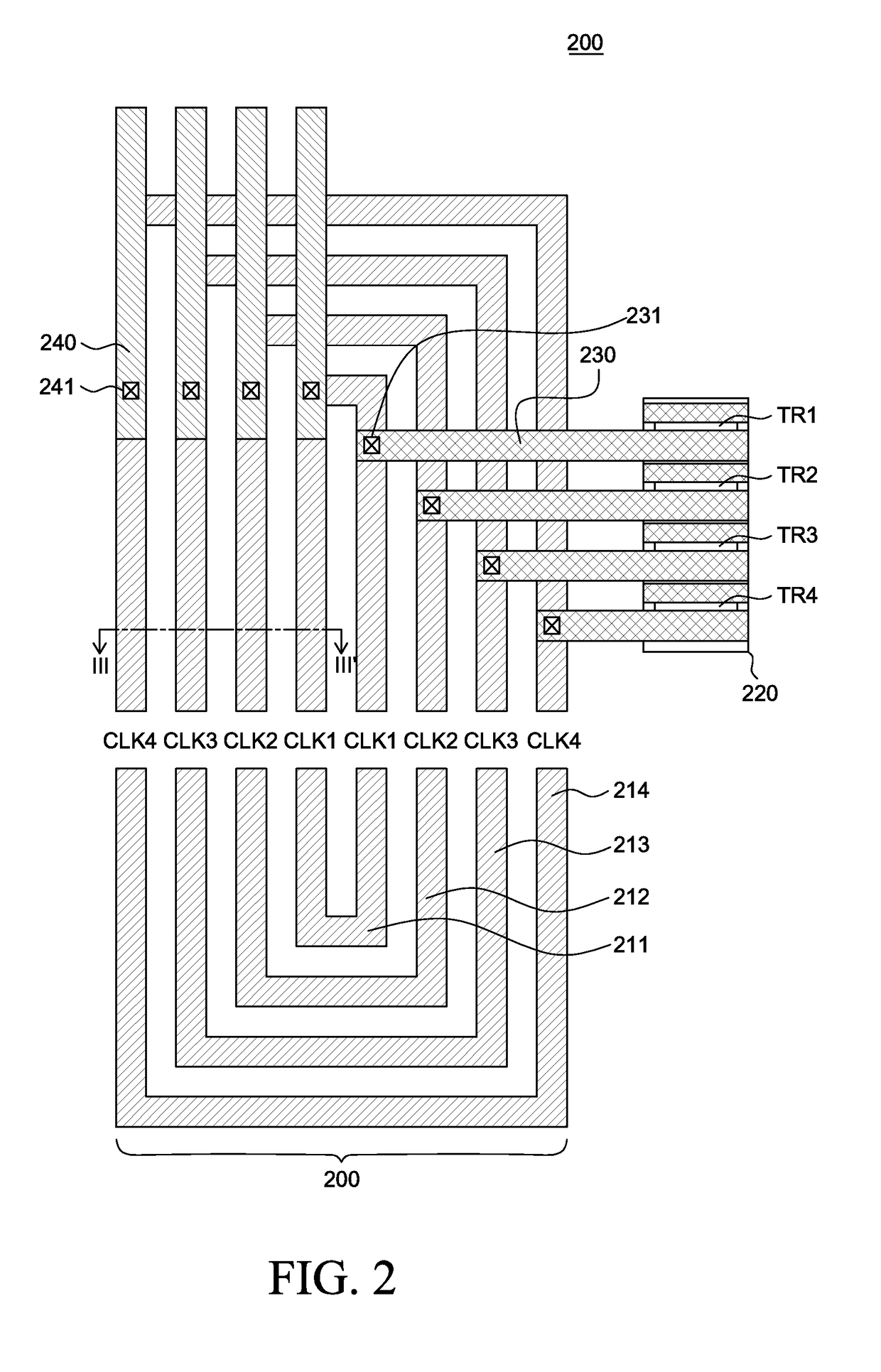

Shift register and semiconductor display device

ActiveUS7602215B2Reduce sizeSuppress signal delayStatic indicating devicesCounting chain pulse countersShift registerPower inverter

The invention provides a shift register which can operate normally while suppressing a delay of signal and a rounding of waveform. The shift register of the invention includes a plurality of stages of flip-flop circuits each of which includes a clocked inverter. The clocked inverter includes a first transistor and a second transistor which are connected in series, a first compensation circuit including a third transistor and a fourth transistor which are connected in series, and a second compensation circuit including a fifth transistor and a transmission gate. According to the first compensation circuit, a timing at which a signal outputted from the flip-flop circuit rises or falls can be controlled in synchronization with an output of two stages before. The second compensation circuit can control a clock signal input can be controlled.

Owner:SEMICON ENERGY LAB CO LTD

Shift Register and Semiconductor Display Device

ActiveUS20080273004A1Stable in free energyImprove lattice distortionStatic indicating devicesCounting chain pulse countersShift registerTransmission gate

The invention provides a shift register which can operate normally while suppressing a delay of signal and a rounding of waveform. The shift register of the invention includes a plurality of stages of flip-flop circuits each of which includes a clocked inverter. The clocked inverter includes a first transistor and a second transistor which are connected in series, a first compensation circuit including a third transistor and a fourth transistor which are connected in series, and a second compensation circuit including a fifth transistor and a transmission gate. According to the first compensation circuit, a timing at which a signal outputted from the flip-flop circuit rises or falls can be controlled in synchronization with an output of two stages before. The second compensation circuit can control a clock signal input can be controlled.

Owner:SEMICON ENERGY LAB CO LTD

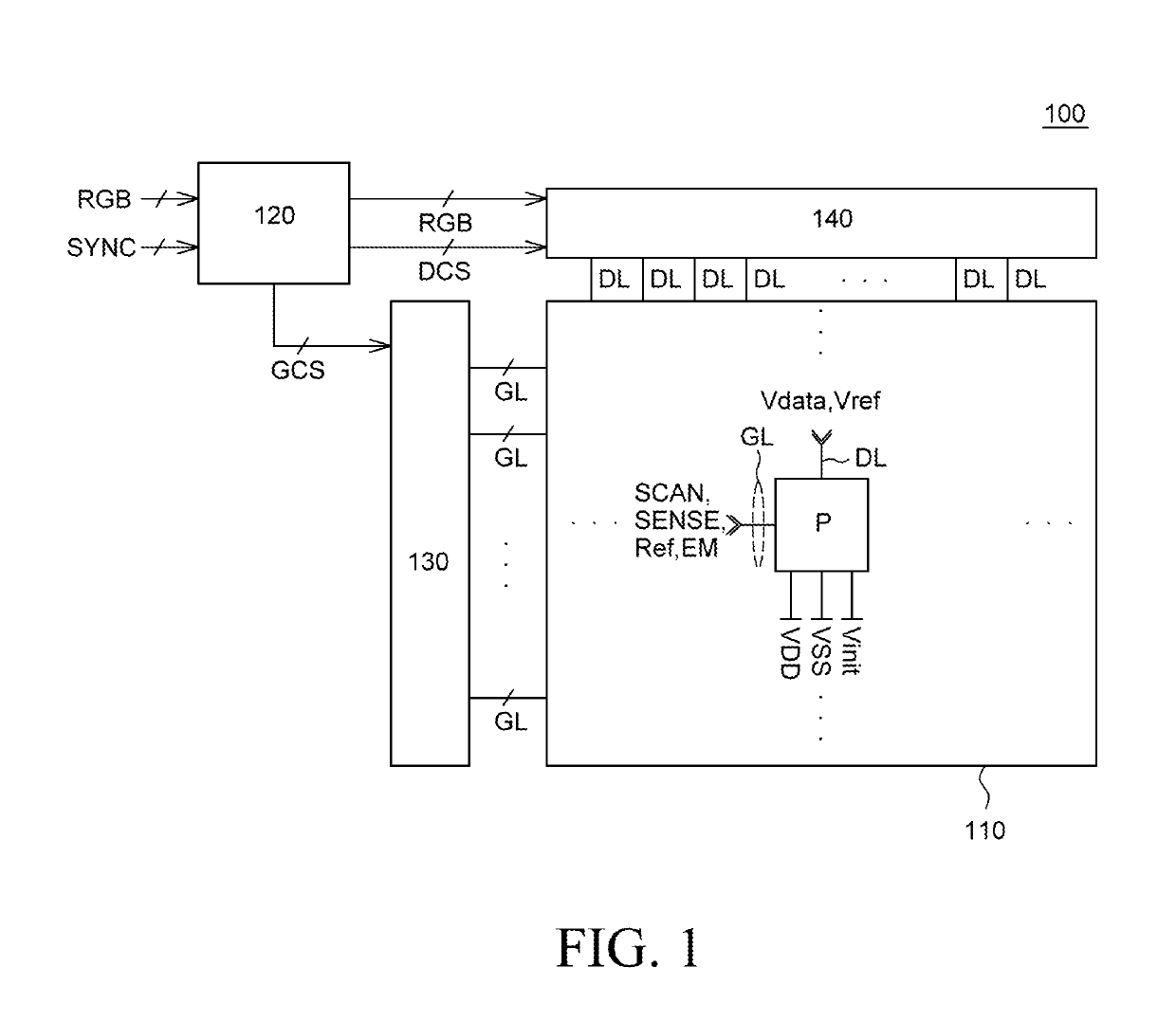

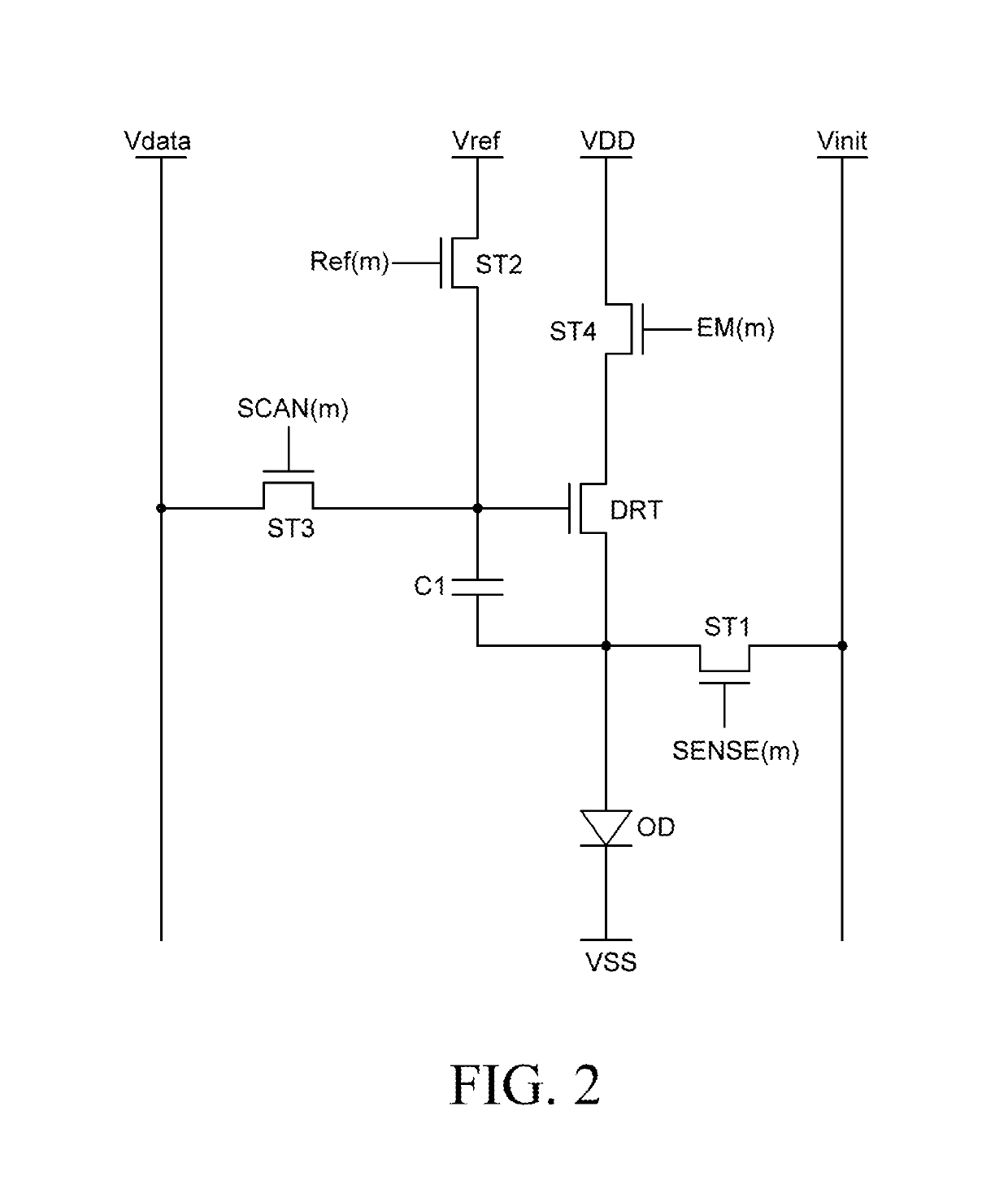

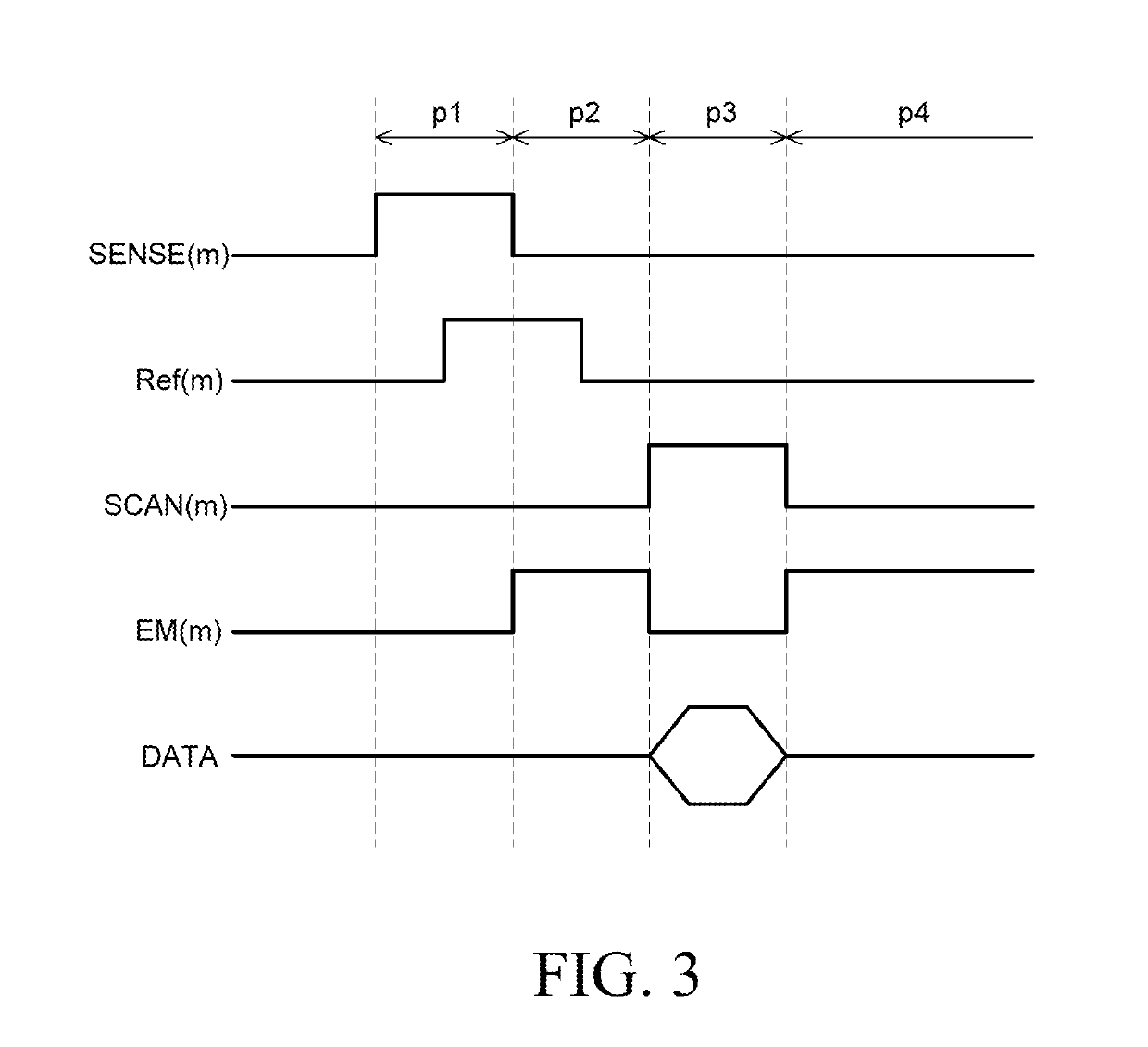

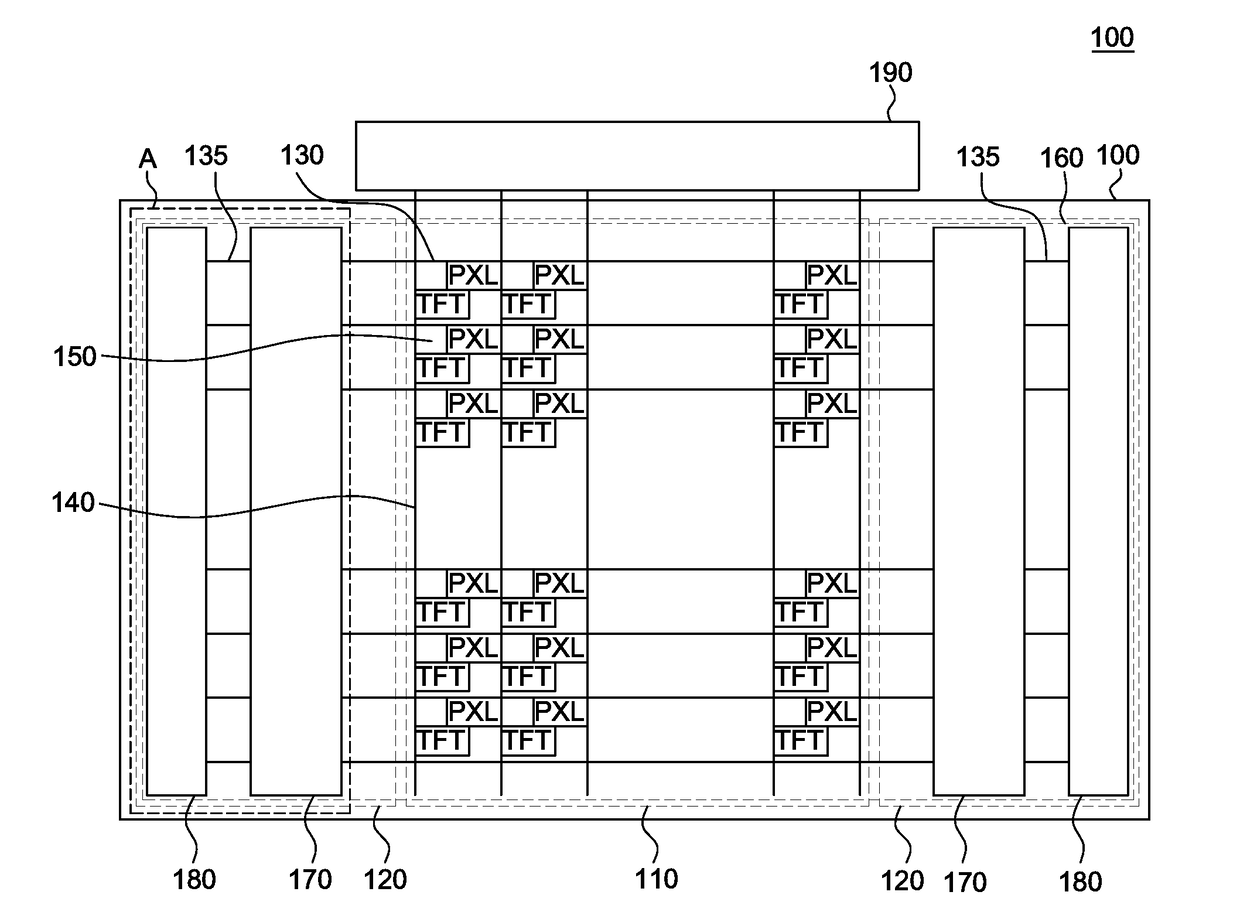

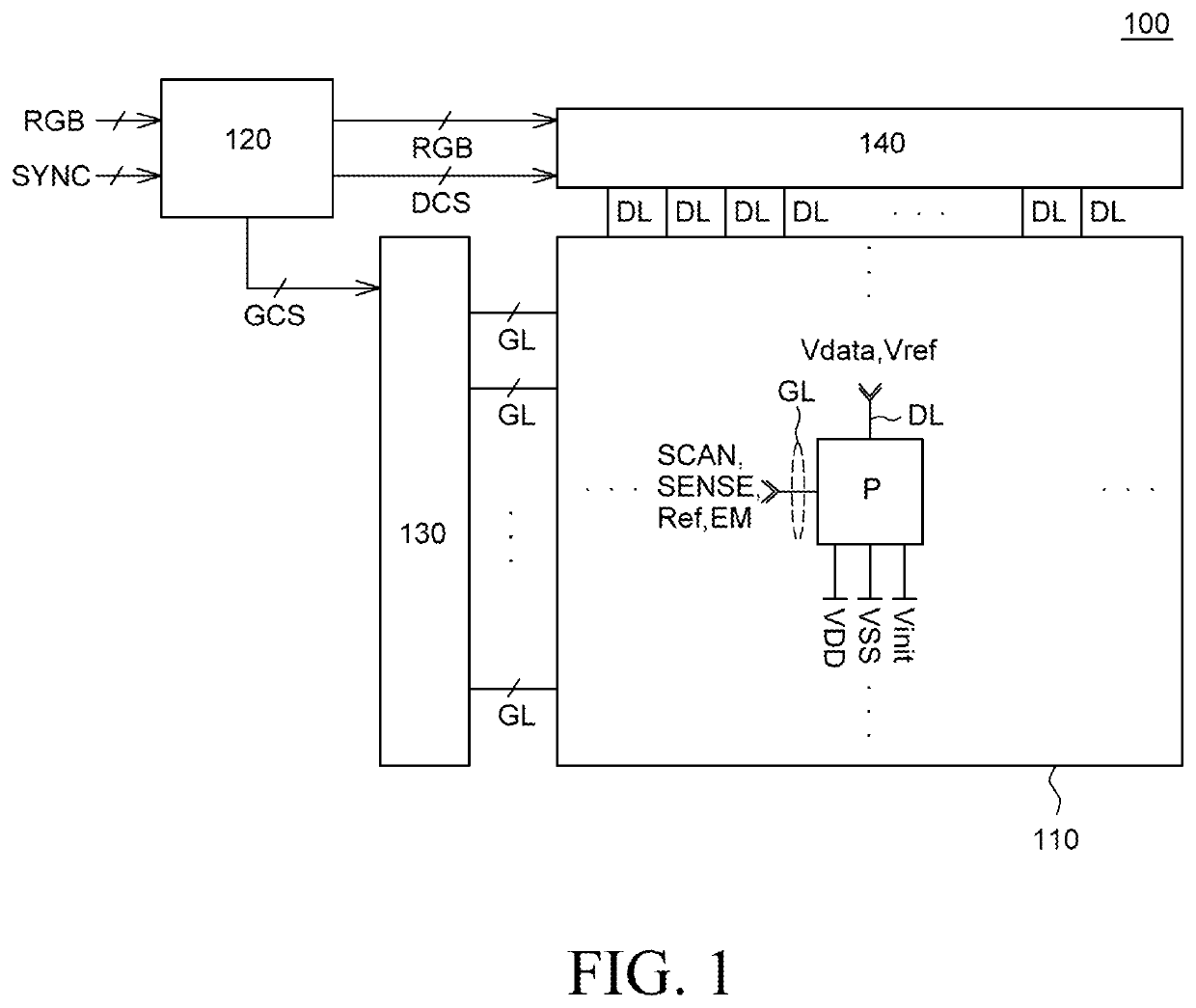

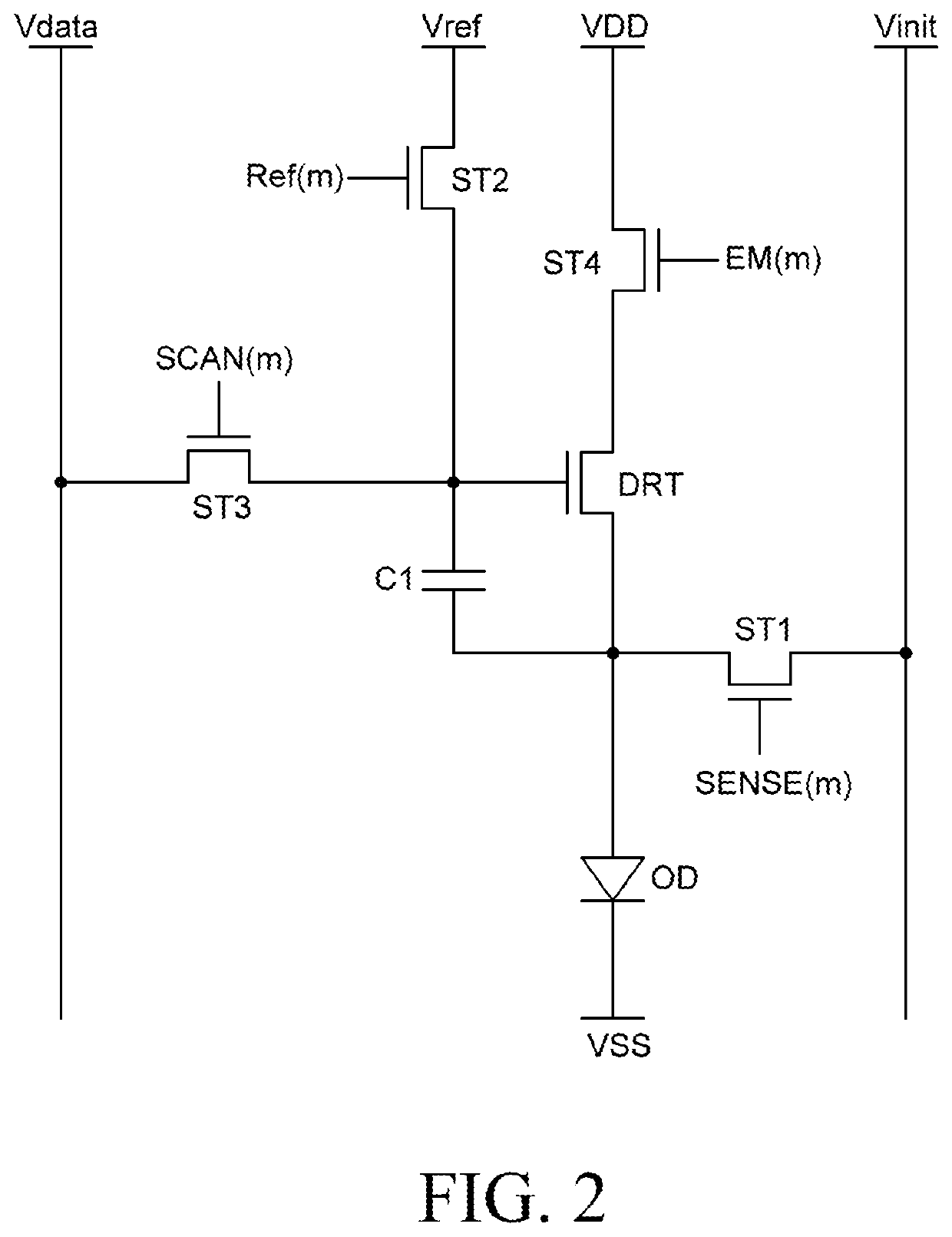

Gate driver and organic light emitting display device including the same

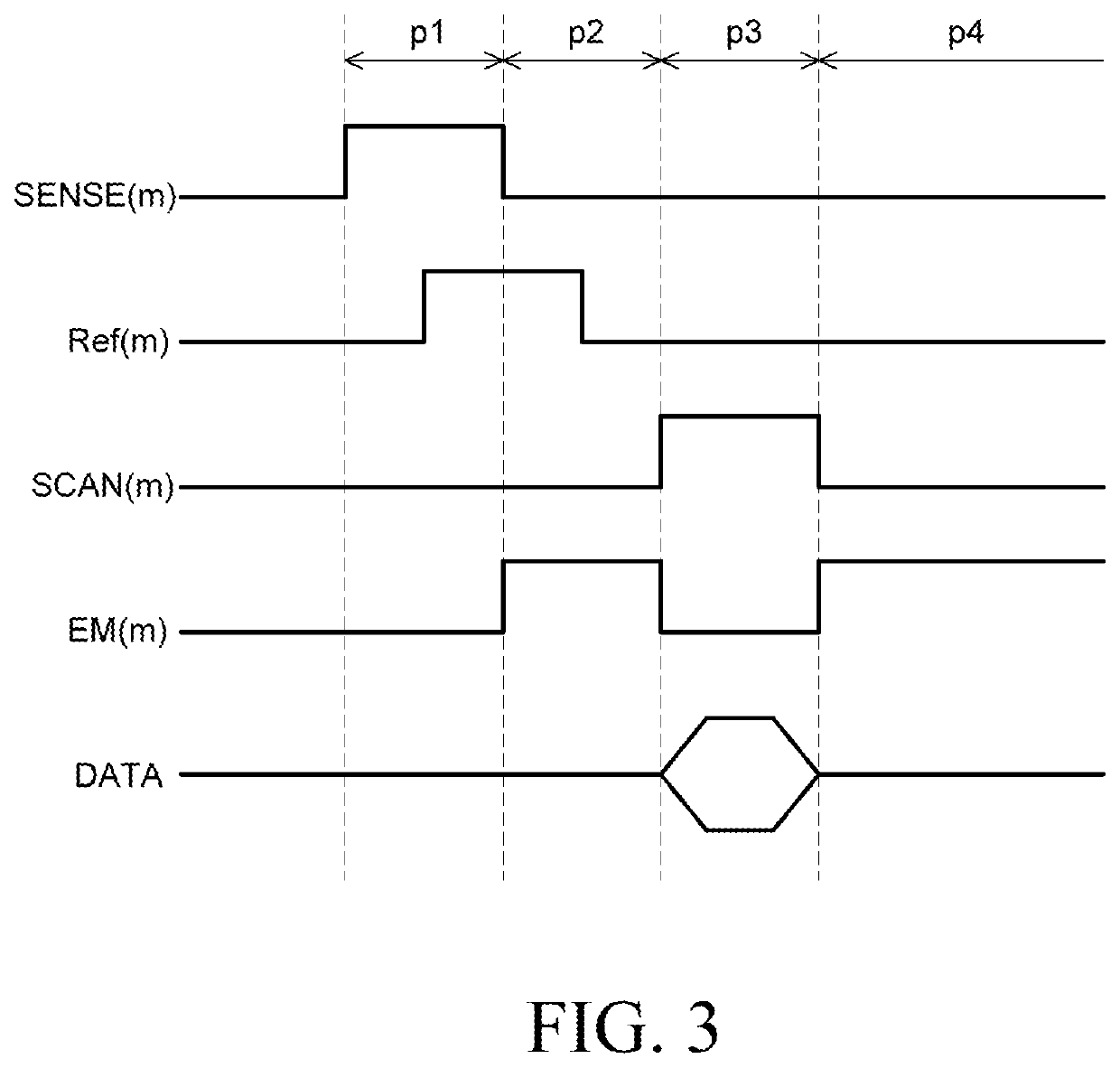

ActiveUS20190130842A1Suppress signal delayReduce border sizeStatic indicating devicesDisplay deviceEngineering

According to an aspect of the present disclosure, a gate driver includes a plurality of stages which is dependently connected to each other and each of the plurality of pixels includes: a first output unit which outputs a sensing signal by voltages of a Q node and a QB node; a second output unit which outputs a reference signal by the voltages of the Q node and the QB node; a third output unit which outputs a scan signal by the voltages of the Q node and the QB node; a first controller which controls the Q node; and a second controller which controls the QB node, and at least two of the first to third output units share at least one clock signal among a plurality of clock signals, thereby reducing an area of the gate driver.

Owner:LG DISPLAY CO LTD

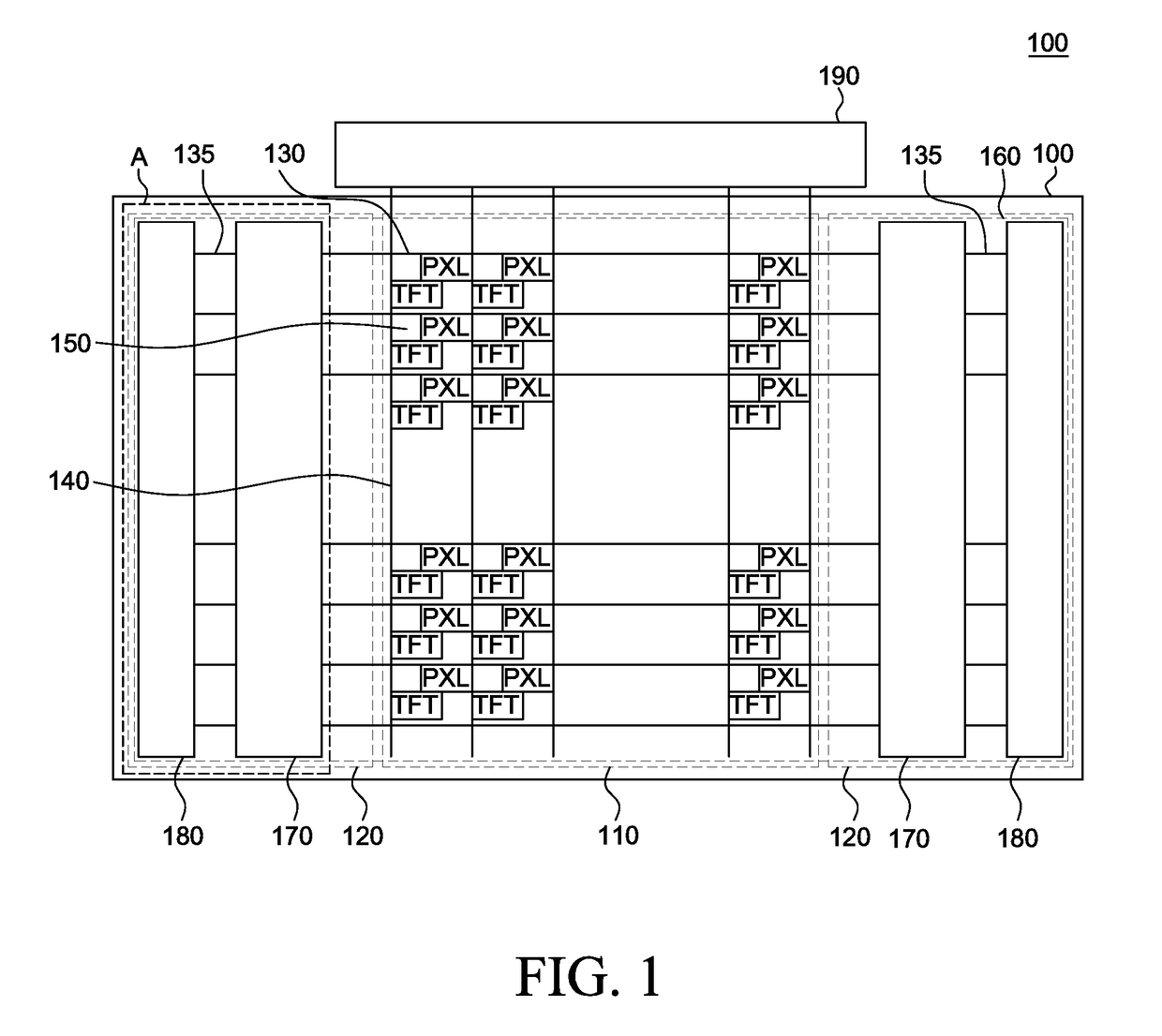

Array substrate

ActiveUS20170124972A1Suppress signal delayReduce widthStatic indicating devicesDigital storageEngineeringClock signal

An array substrate includes: a display area; a non-display area outside of the display area; a gate-in-panel (GIP) circuit in the non-display area; a plurality of clock signal lines in the non-display area and configured to transfer signals to the GIP circuit; and connection lines in the non-display area and configured to connect the plurality of clock signal lines to the GIP circuit. Each of the plurality of clock signal lines is a ring shaped line.

Owner:LG DISPLAY CO LTD

LCD device and method including a plastic substrate with metal layer containing copper surrounded by barrier metal film embedded in a groove within the plastic substrate

InactiveUS7564531B2Lower resistanceSuppress disconnectionSolid-state devicesNon-linear opticsHigh densityLiquid-crystal display

Owner:VISTA PEAK VENTURES LLC

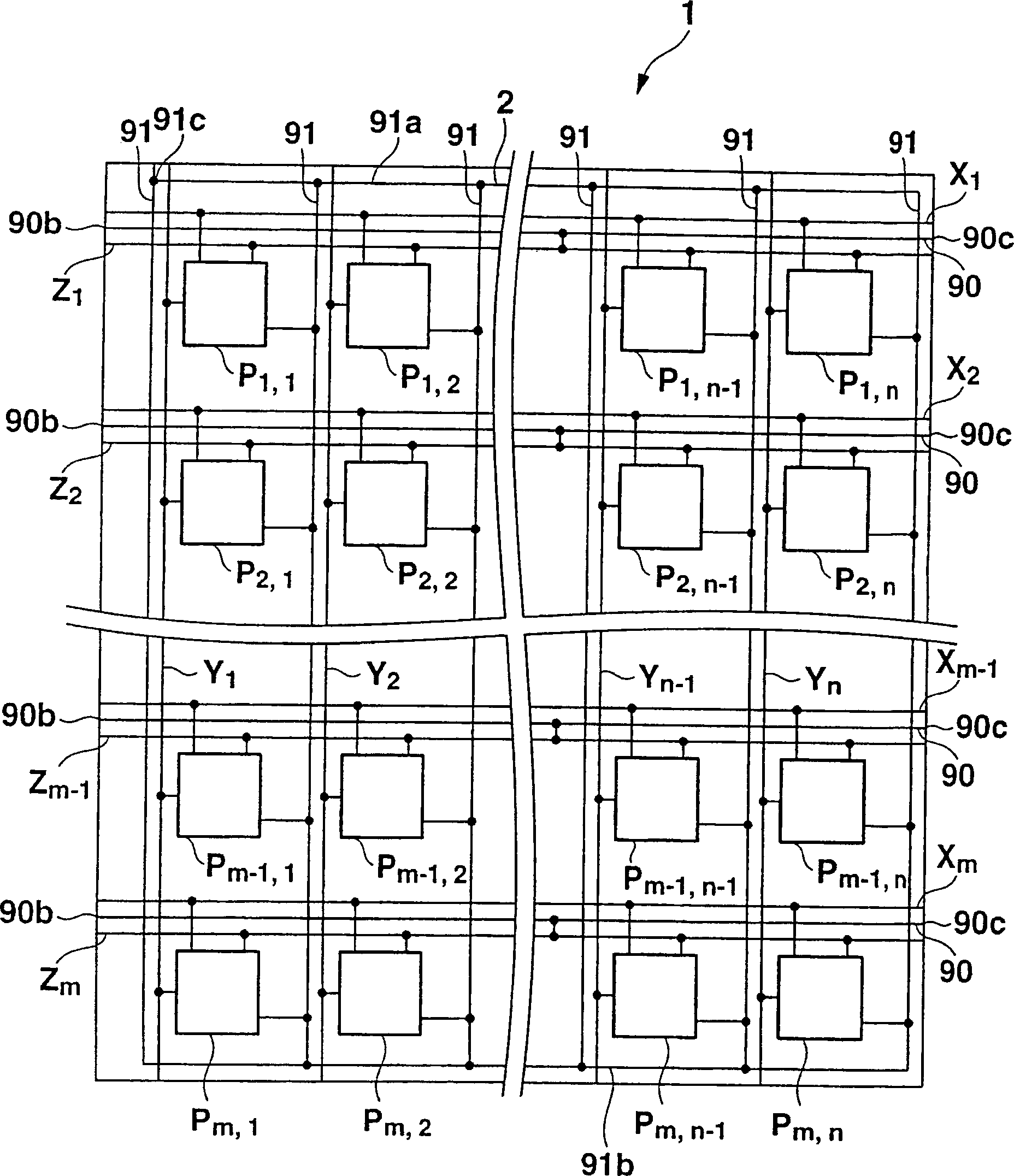

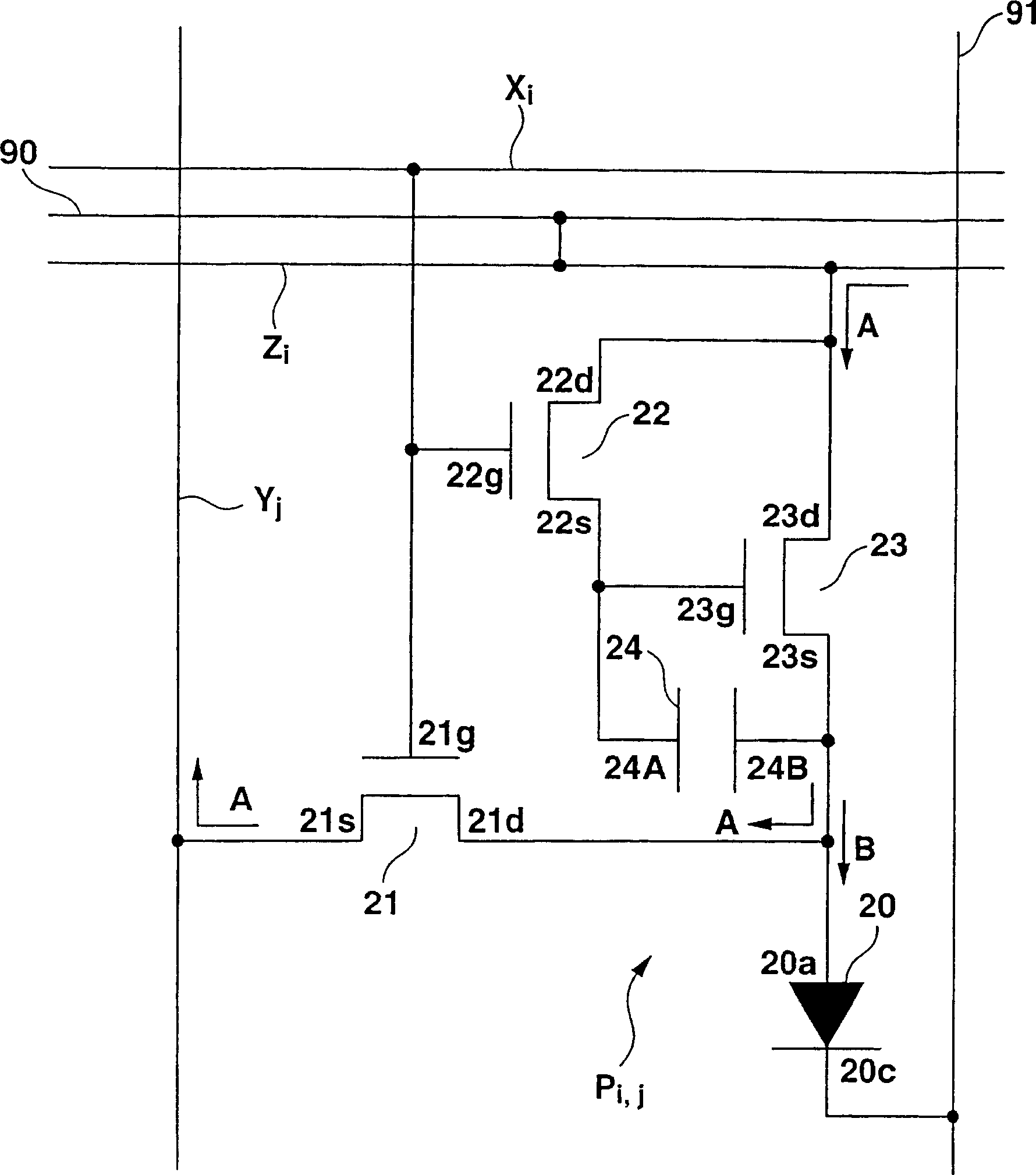

Transistor array substrate and display panel

InactiveCN1770243ASuppress voltage dropSuppress signal delayElectrical apparatusStatic indicating devicesSignal linesEngineering

The transistor array substrate of the present invention reduces the voltage drop of wiring. The transistor array substrate includes: a substrate; a plurality of driving transistors arranged in a matrix on the substrate, and a gate insulating film is sandwiched between the gate, the source, and the drain; a plurality of signal lines connected to the The gates of a plurality of drive transistors are laid out together and arranged to extend in a predetermined direction on the substrate; a plurality of supply lines are laid out together with the sources and drains of the drive transistors, and are arranged across the gates. The electrode insulating film is arranged crosswise with the plurality of signal lines, and conducts with one of the source and drain of the driving transistor; a plurality of power supply wirings are respectively stacked on the plurality of supply lines along the plurality of supply lines .

Owner:SOLAS OLED LTD

Shift register and semiconductor display device

InactiveUS20100034338A1Reduce sizeSuppress signal delayMultiple input and output pulse circuitsStatic indicating devicesShift registerTransmission gate

The invention provides a shift register which can operate normally while suppressing a delay of signal and a rounding of waveform. The shift register of the invention includes a plurality of stages of flip-flop circuits each of which includes a clocked inverter. The clocked inverter includes a first transistor and a second transistor which are connected in series, a first compensation circuit including a third transistor and a fourth transistor which are connected in series, and a second compensation circuit including a fifth transistor and a transmission gate. According to the first compensation circuit, a timing at which a signal outputted from the flip-flop circuit rises or falls can be controlled in synchronization with an output of two stages before. The second compensation circuit can control a clock signal input can be controlled.

Owner:SEMICON ENERGY LAB CO LTD

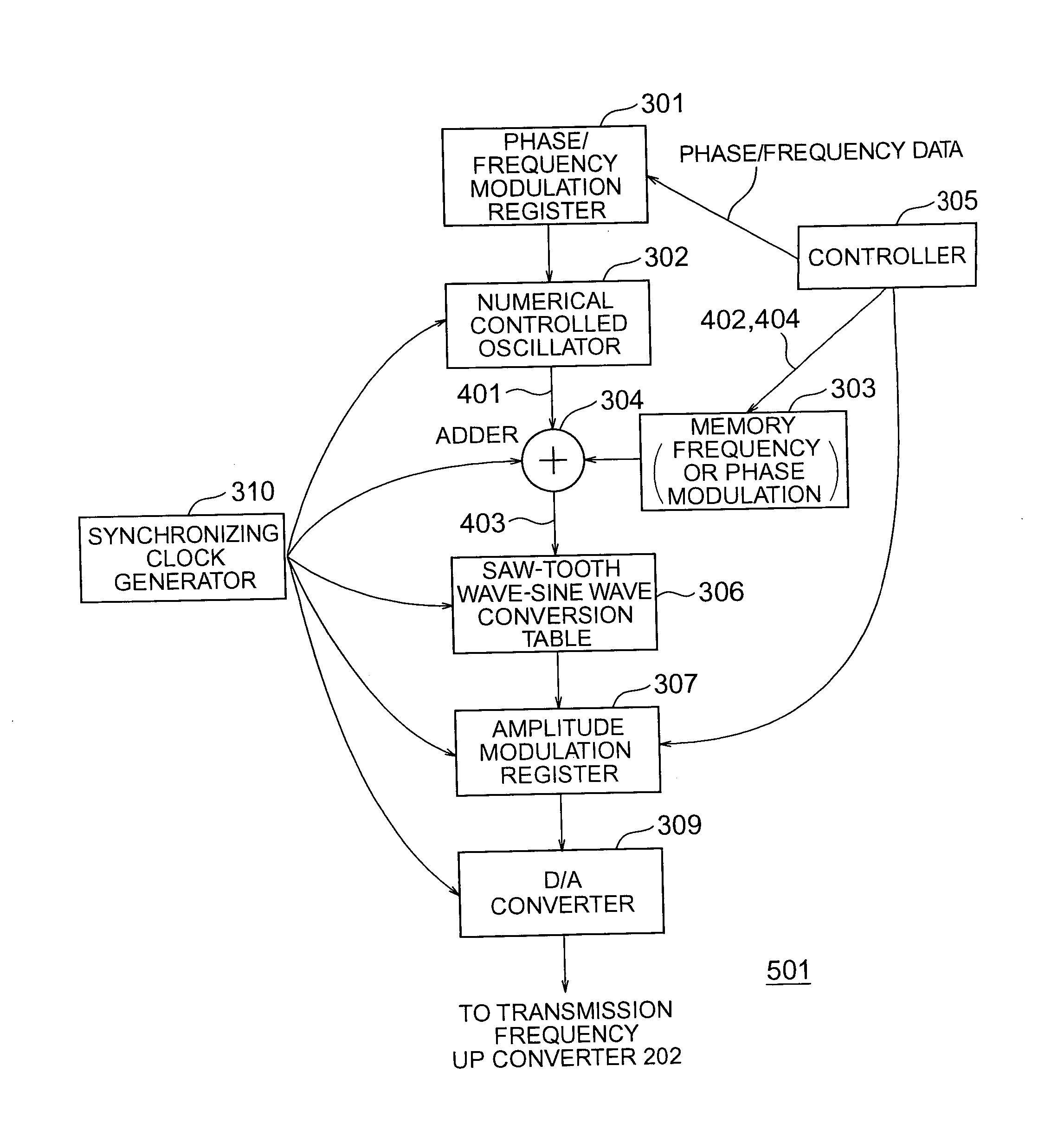

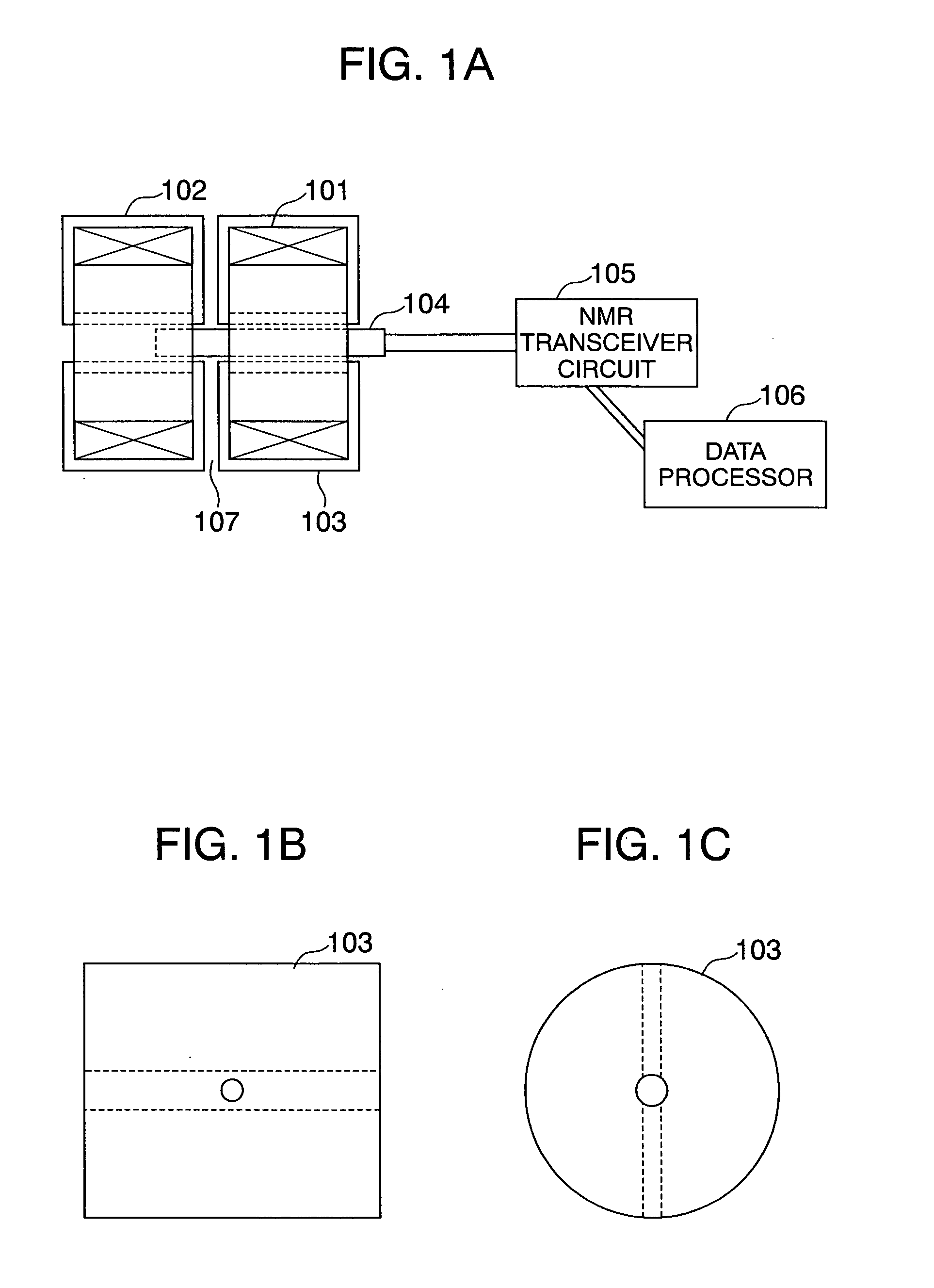

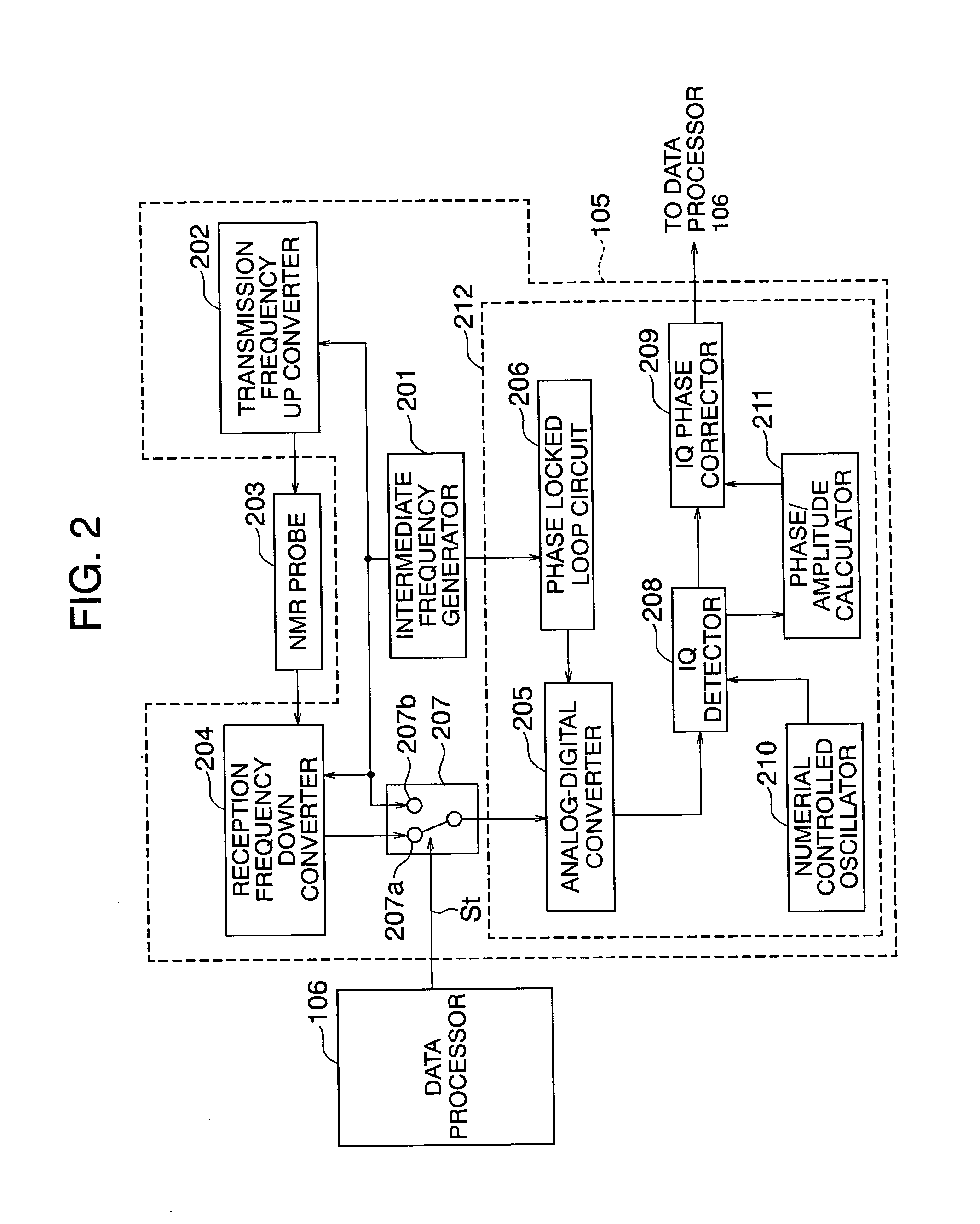

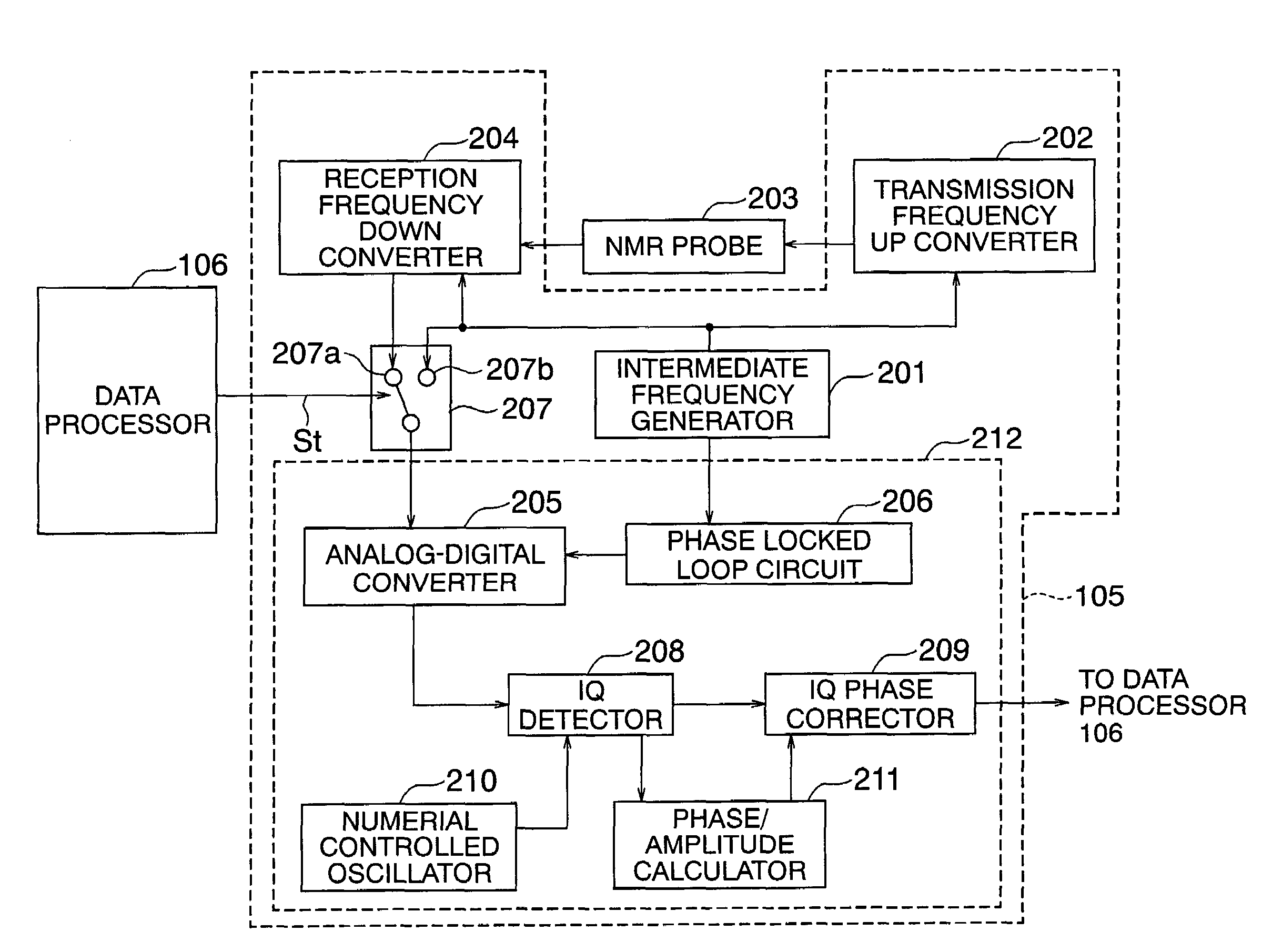

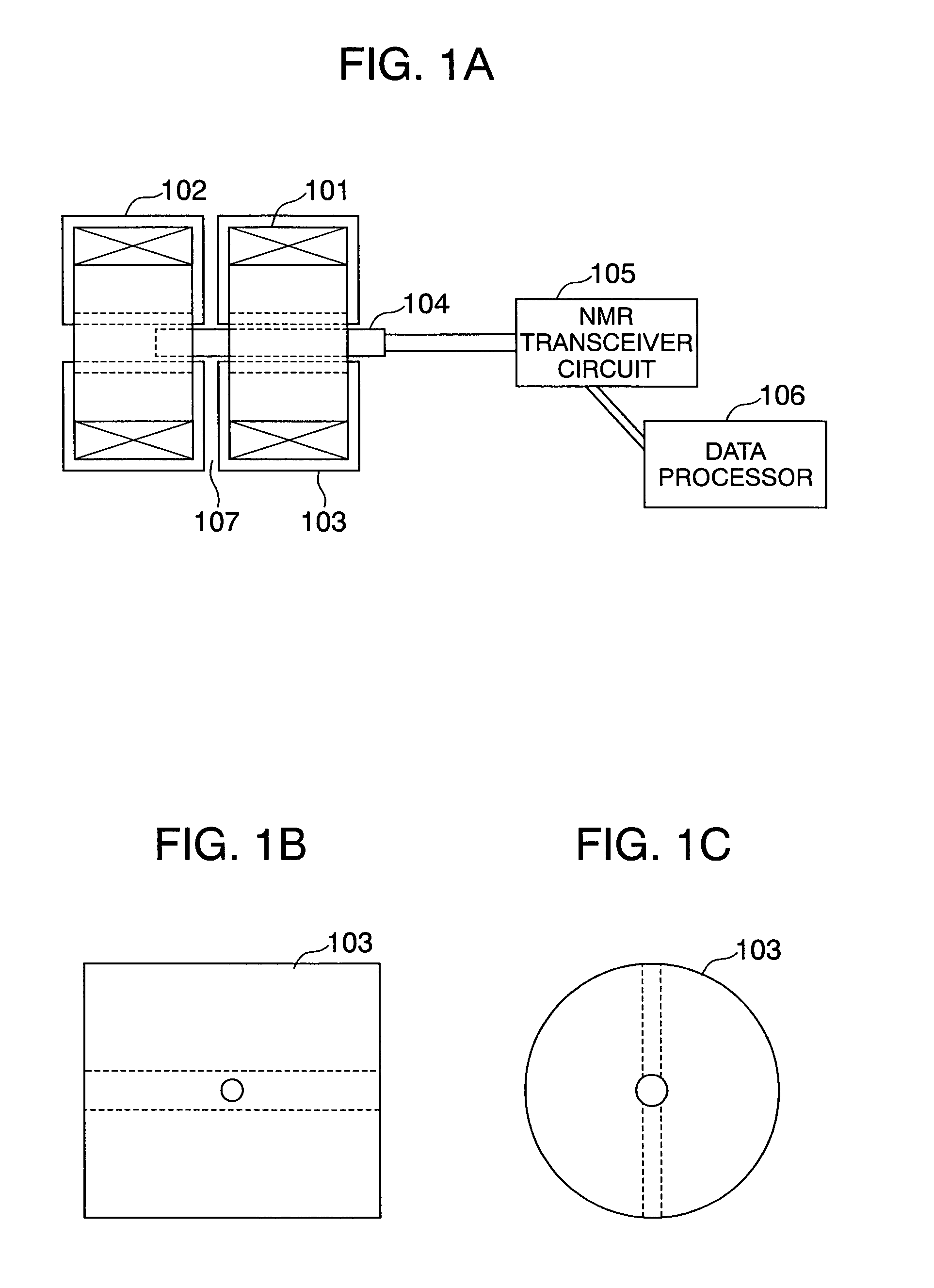

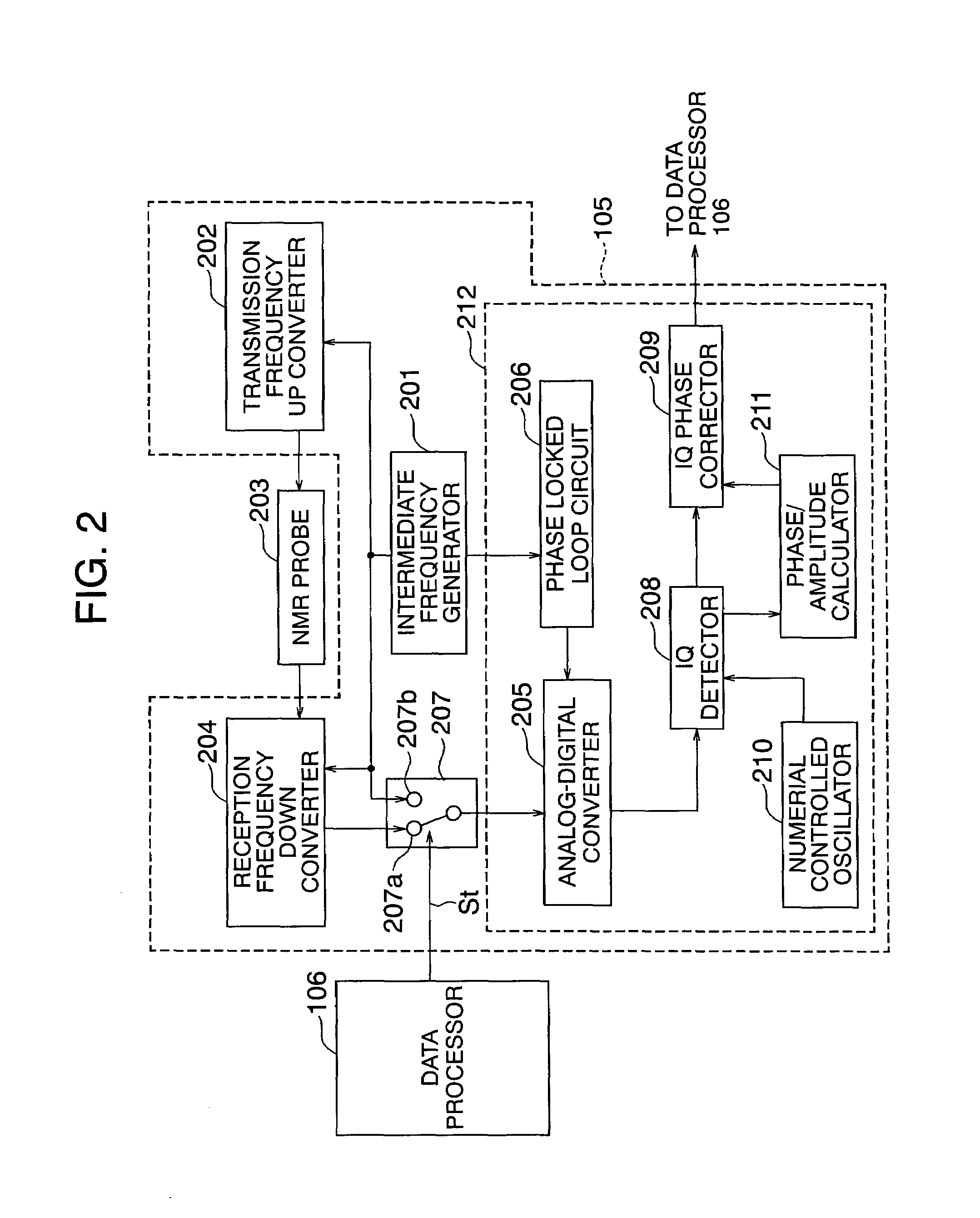

Electromagnetic wave transceiver apparatus and nuclear magnetic resonance analyzing apparatus using it

InactiveUS20060049825A1Increase speedIncrease freedomSolid-state devicesMagnetic field measurement using galvano-magnetic devicesTransmitter coilTransceiver

An electromagnetic transceiver apparatus for a NMR apparatus has an intermediate frequency generator for preparing an intermediate wave, a transmission frequency converter for preparing, on the basis of an intermediate frequency of the intermediate wave, an electromagnetic wave to be radiated from a transmitter coil, a reception frequency converter for processing a signal received by the NMR probe, an analog-digital converter for converting an output of the reception frequency converter into a digital signal, an IQ detector for performing detection on the basis of an output of the analog-digital converter, a phase locked loop and a switch inserted between the analog-digital converter and the reception frequency converter to select either an input from the intermediate frequency generator or an input from the reception frequency converter.

Owner:HITACHI LTD

Electromagnetic wave transceiver apparatus and nuclear magnetic resonance analyzing apparatus using it

InactiveUS7372272B2Accurate measurementSuppress signal delaySolid-state devicesMagnetic field measurement using galvano-magnetic devicesTransmitter coilNMR - Nuclear magnetic resonance

Owner:HITACHI LTD

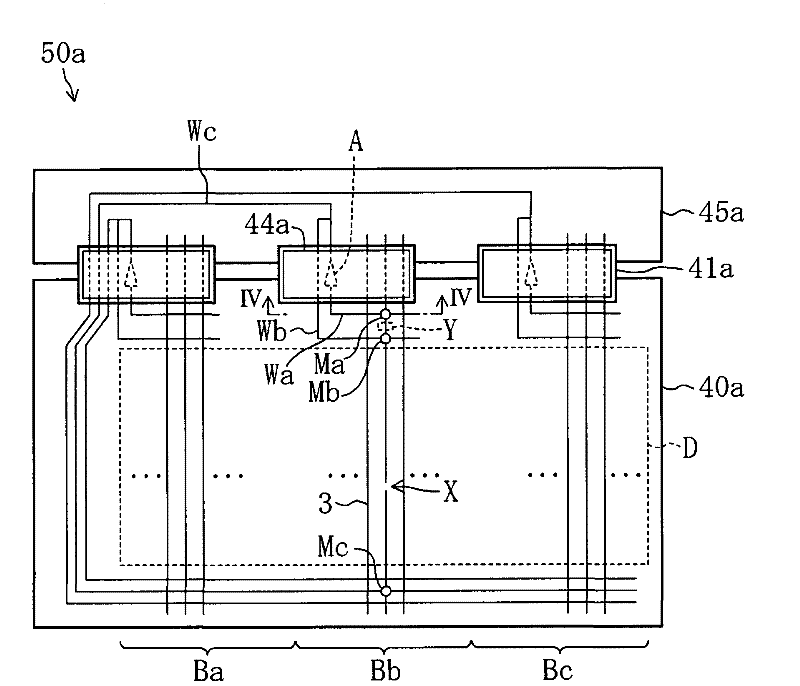

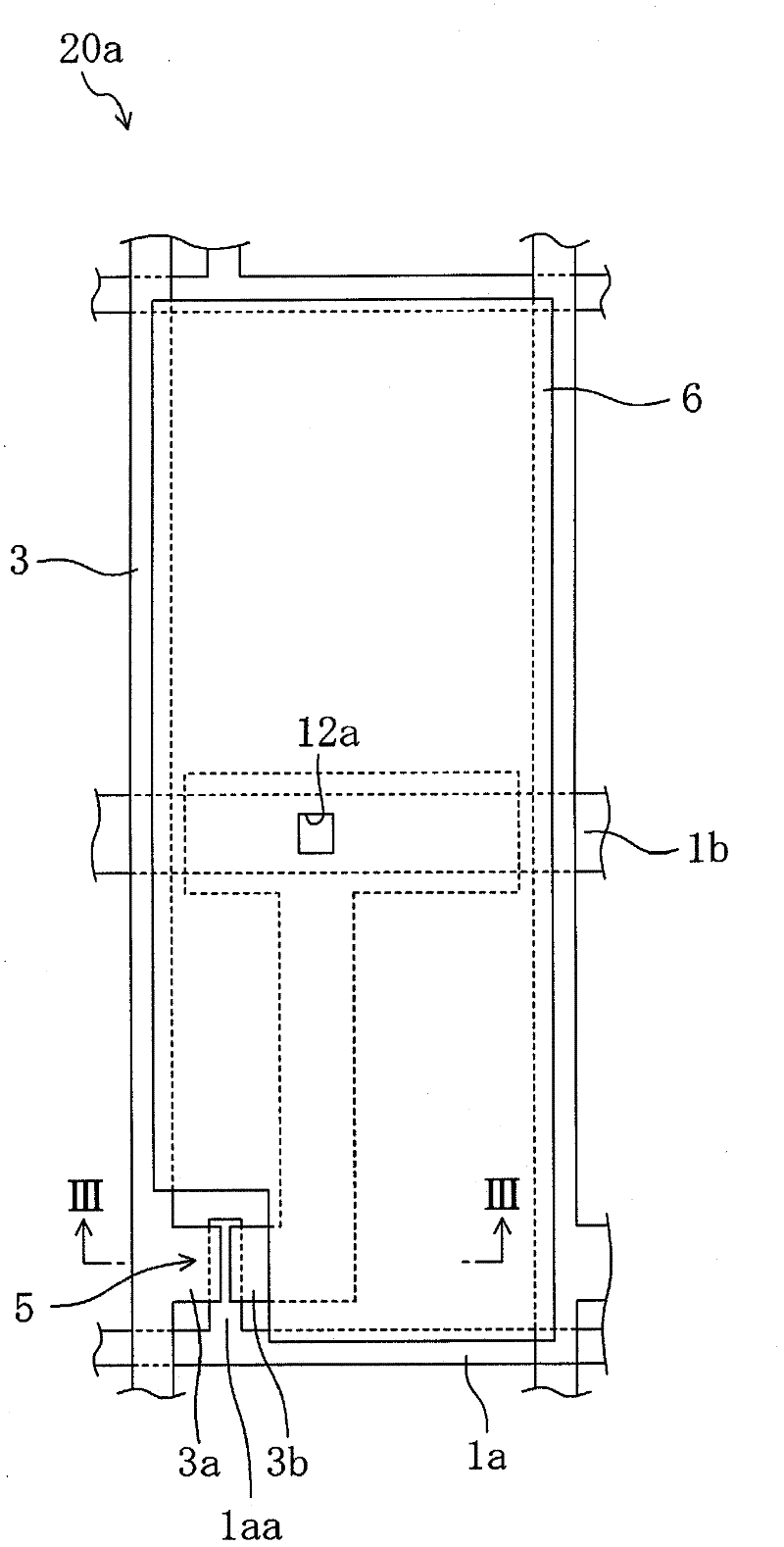

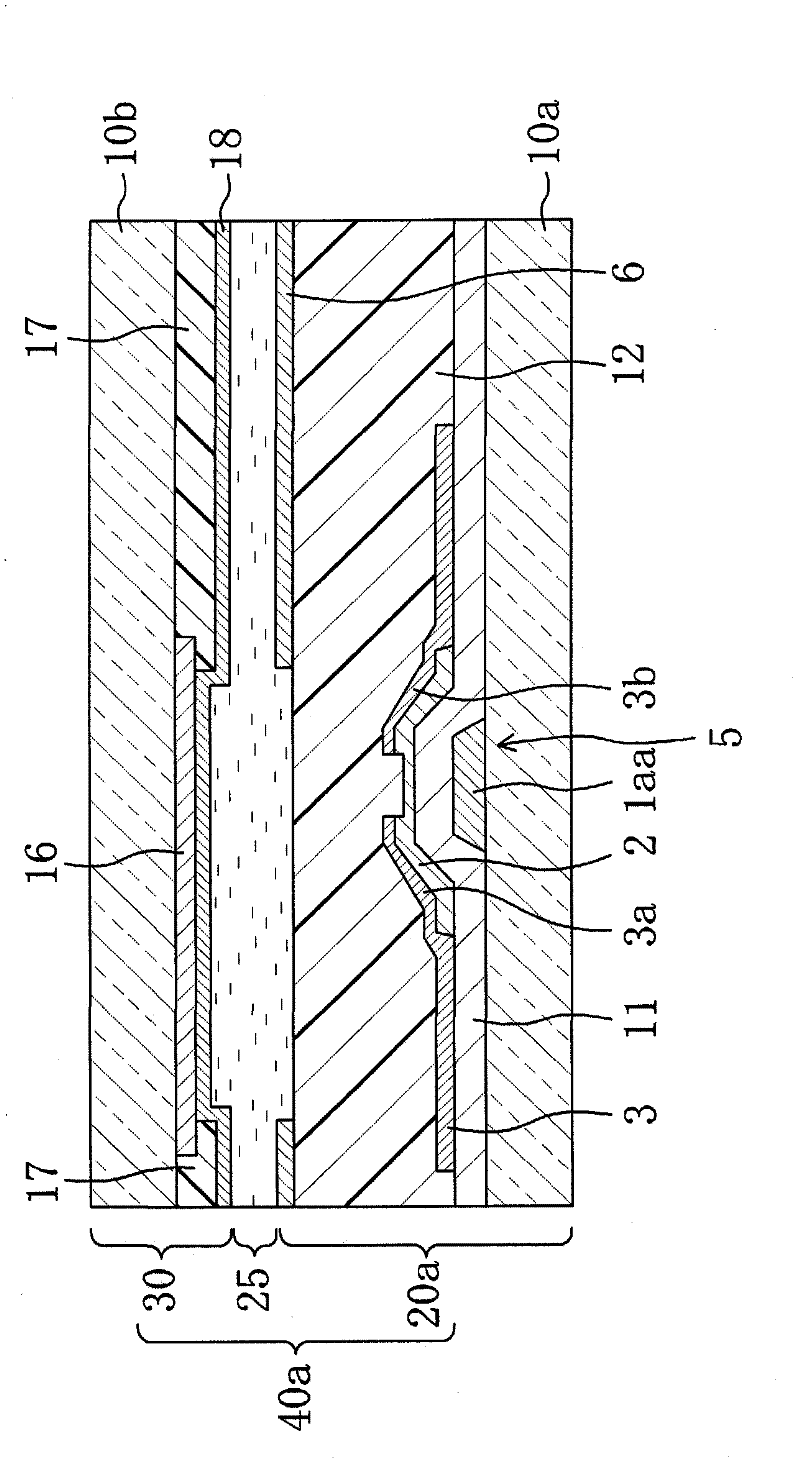

Display device, manufacturing method thereof, and active matrix substrate

InactiveCN102301408ASuppress signal delayNon-linear opticsIdentification meansActive matrixDisplay device

A display device is provided with: a display panel (40a) provided with a plurality of display wiring lines (3) extending in parallel to each other; a drive circuit (44a), which is provided on one end section of each display wiring line (3) and is connected to each display wiring line (3); a first wiring line path (Wa) and a second wiring line path (Wb) arranged to intersect with each other in theinsulated state on the end section of each display wiring line (3); and a third wiring line path (Wc), which intersects with the other end section of each display wiring line (3) in the insulated state and is connected to the first wiring line path (Wa) and the second wiring line path (Wb). An amplifying circuit (A) is arranged in a path which includes the first wiring line path (Wa) and the second wiring line path (Wb), and in a path which includes the first wiring line path (Wa) and the third wiring line path (Wc).

Owner:SHARP KK

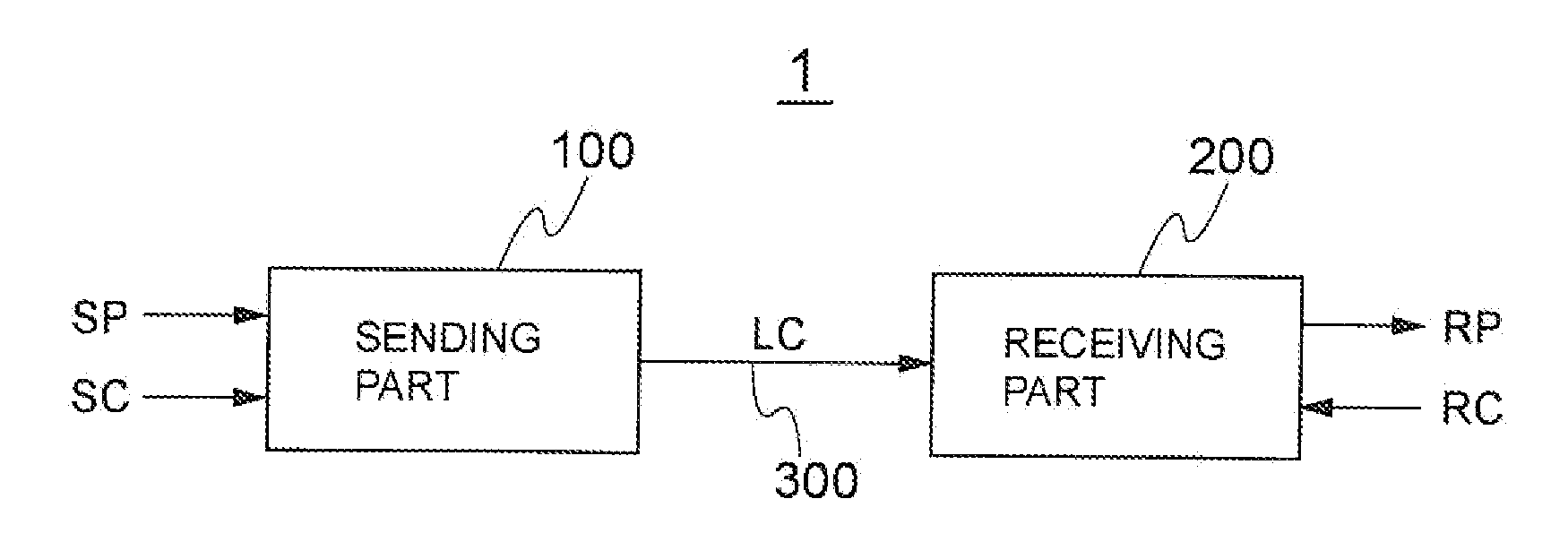

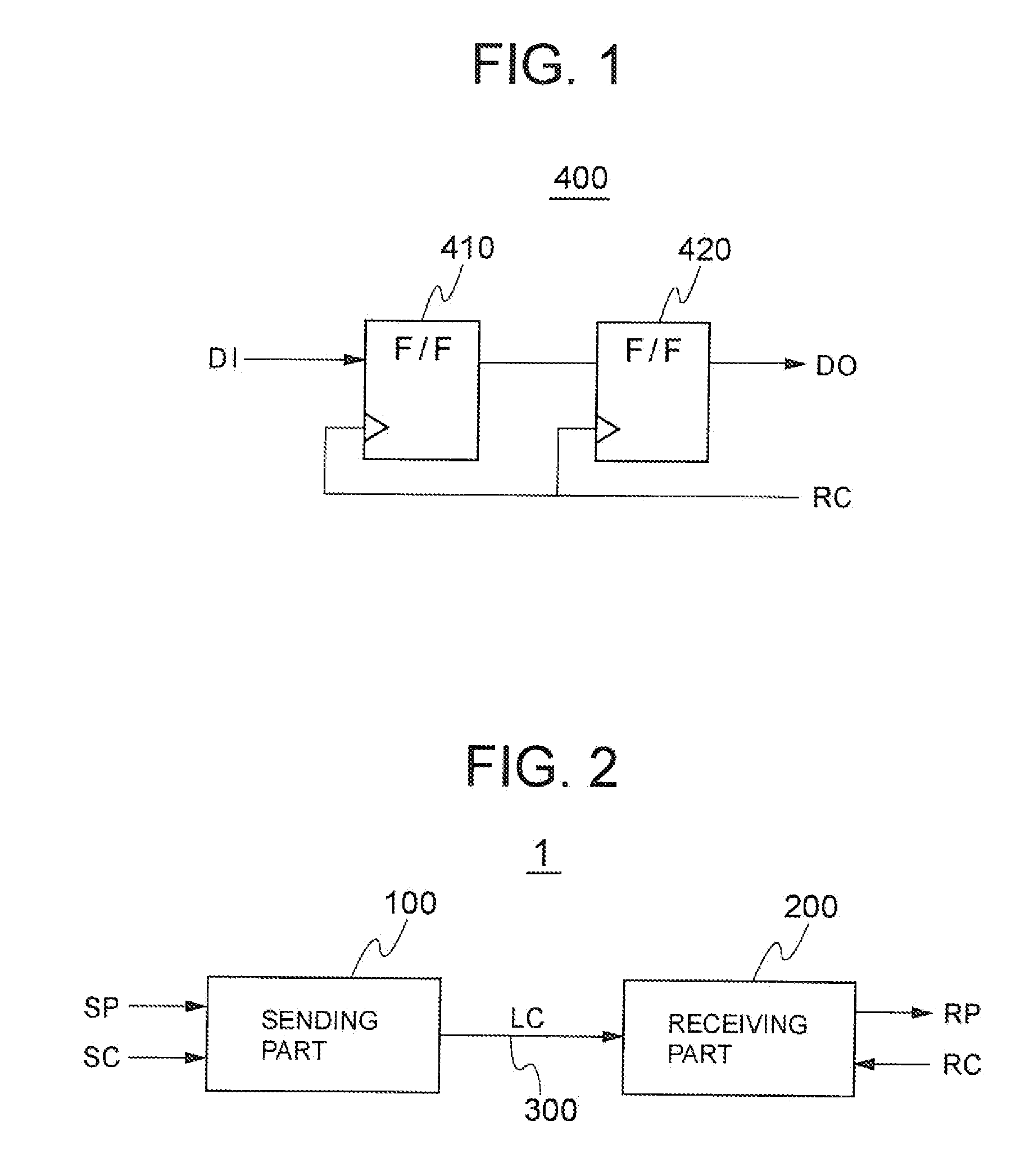

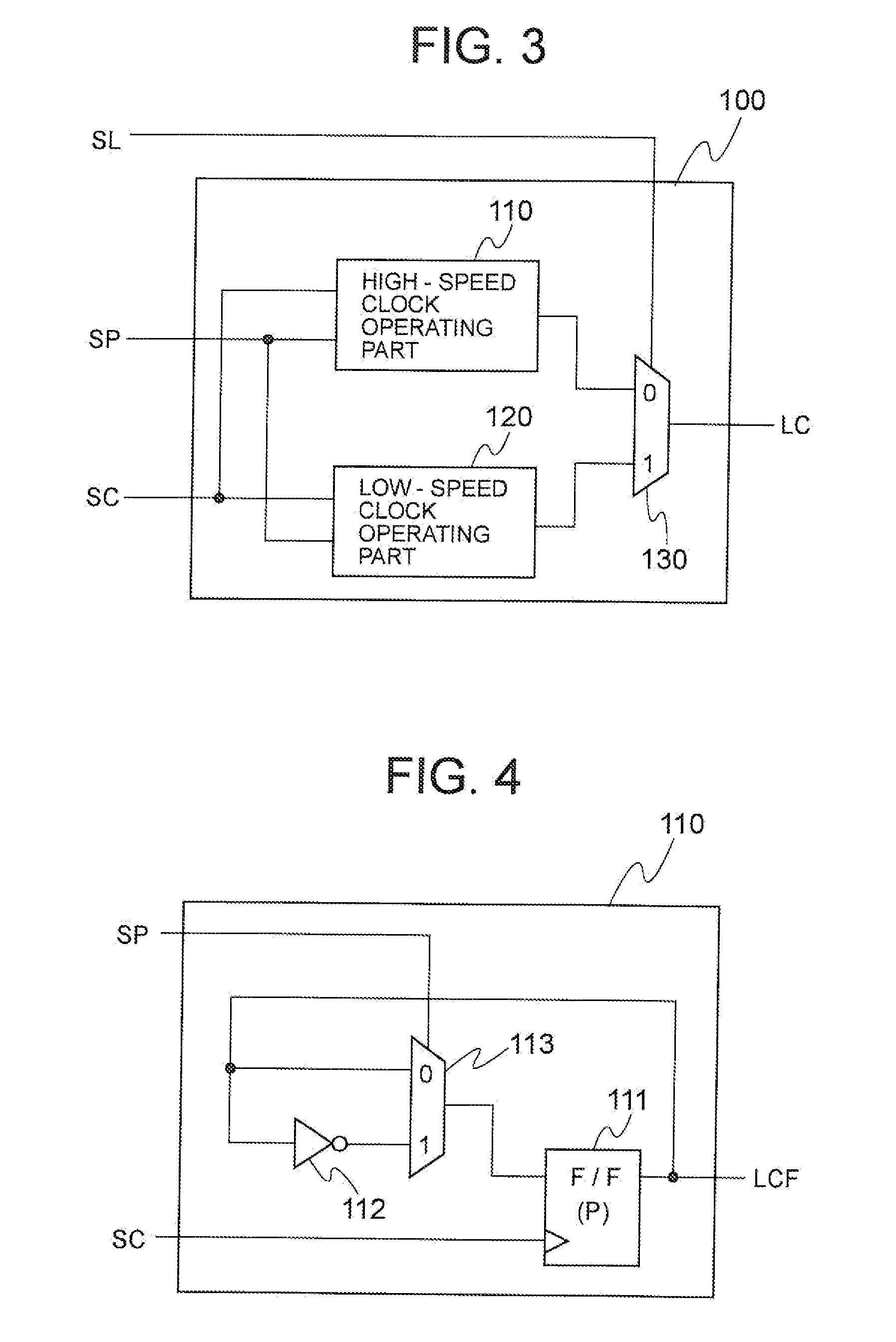

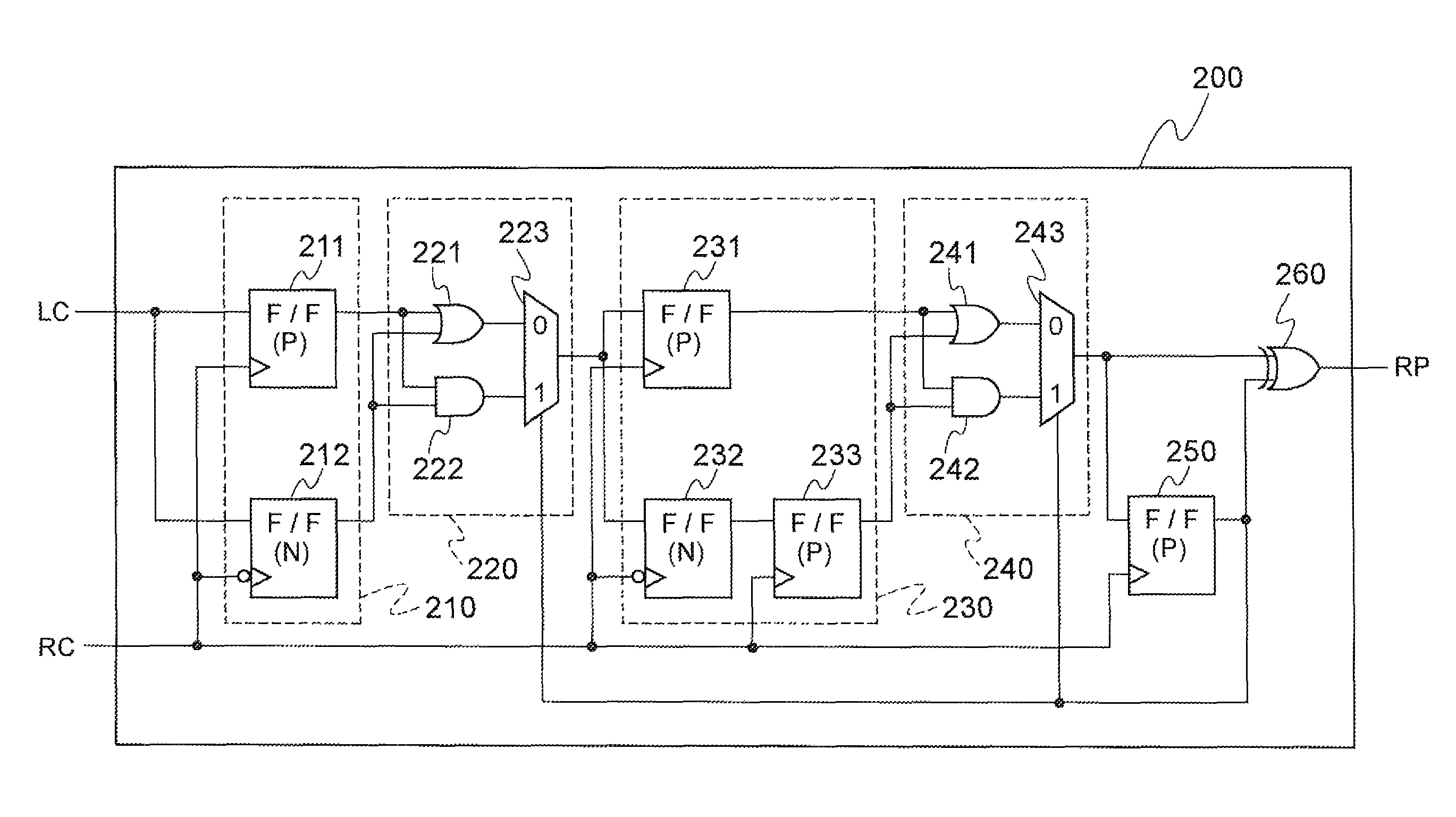

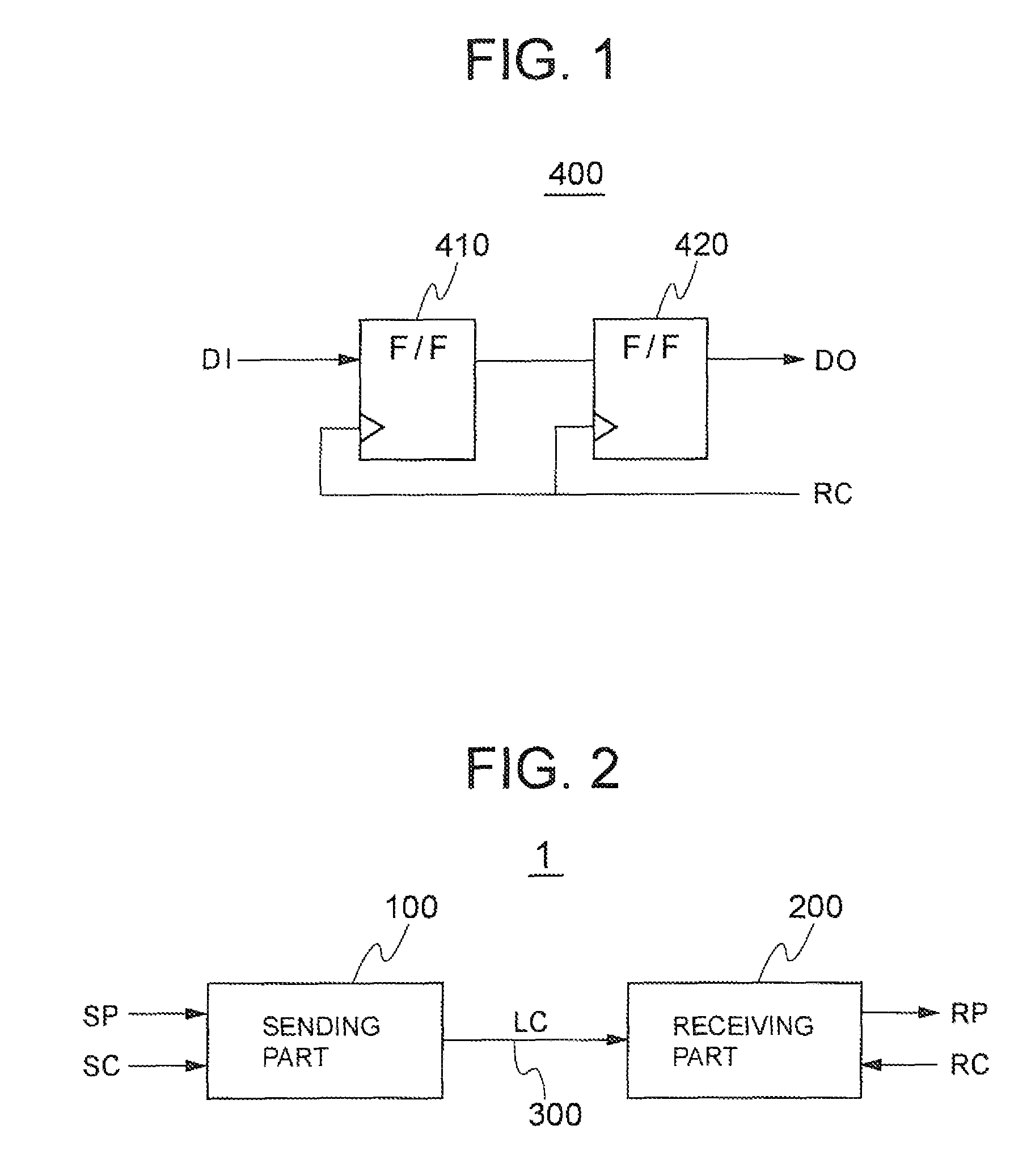

Transmission apparatus, signal sending apparatus, and signal receiving apparatus, and transmission method, signal sending method, and signal receiving method

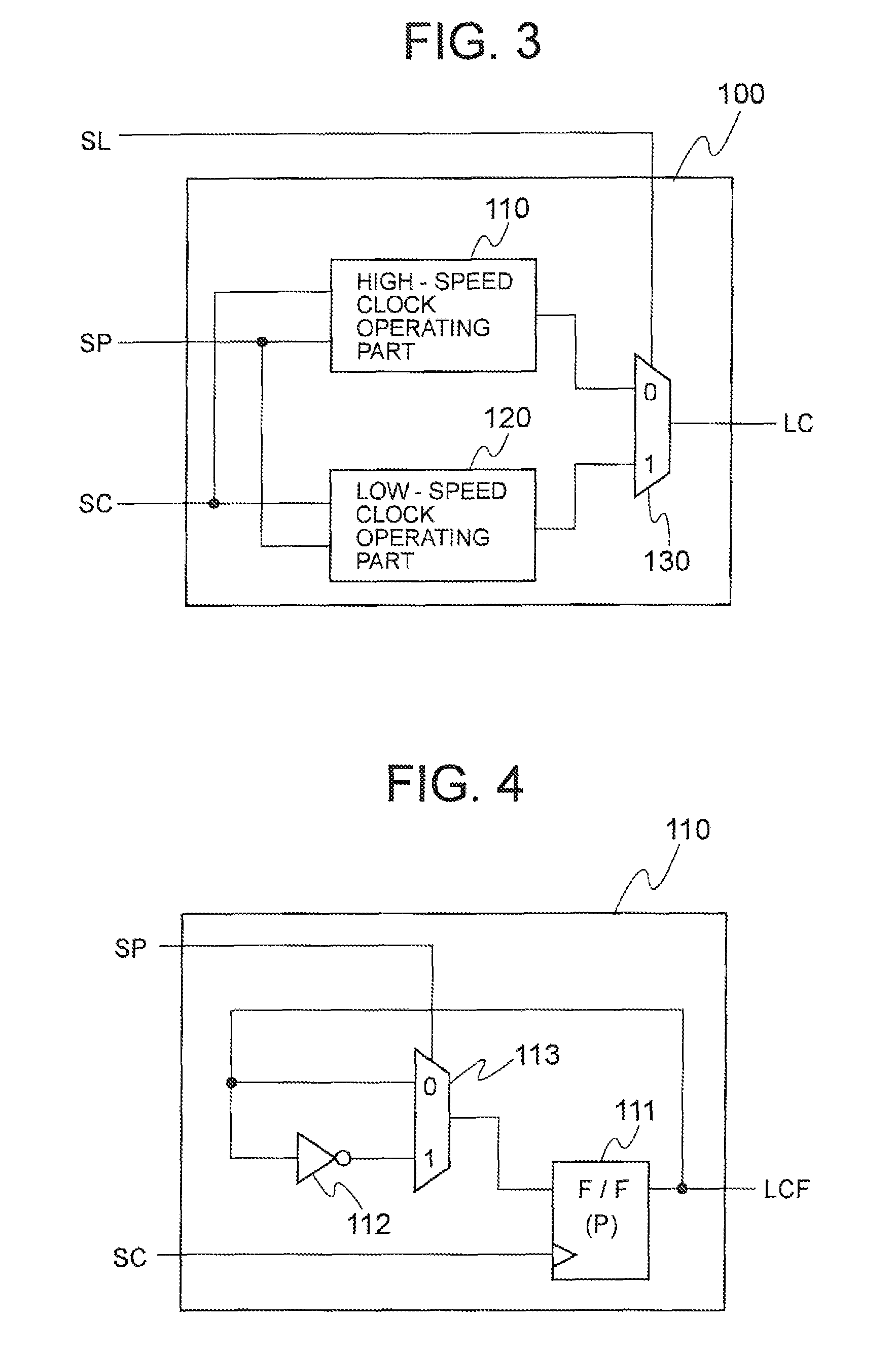

ActiveUS20110103511A1Delay of control can be suppressedSolve the real problemModulated-carrier systemsSynchronisation transmittersMetastabilityClock synchronization

A transmission apparatus, a signal sending apparatus, and a signal receiving apparatus, and a transmission method, a signal sending method, and a signal receiving method capable of solving a problem of metastability and suppressing a delay of a signal when sending and receiving apparatuses having different operation clock frequencies send / receive the signal representative of control information, for example. Included are a sending part that operates in synchronization with a first clock having a first period to output a transmission signal having a signal level that is inverted in response to an input of a first pulse signal corresponding to the first period and a receiving part that operates in synchronization with a second clock having a second period to output a second pulse signal corresponding to the second period in response to inversion of a signal level of the transmission signal.

Owner:LAPIS SEMICON CO LTD

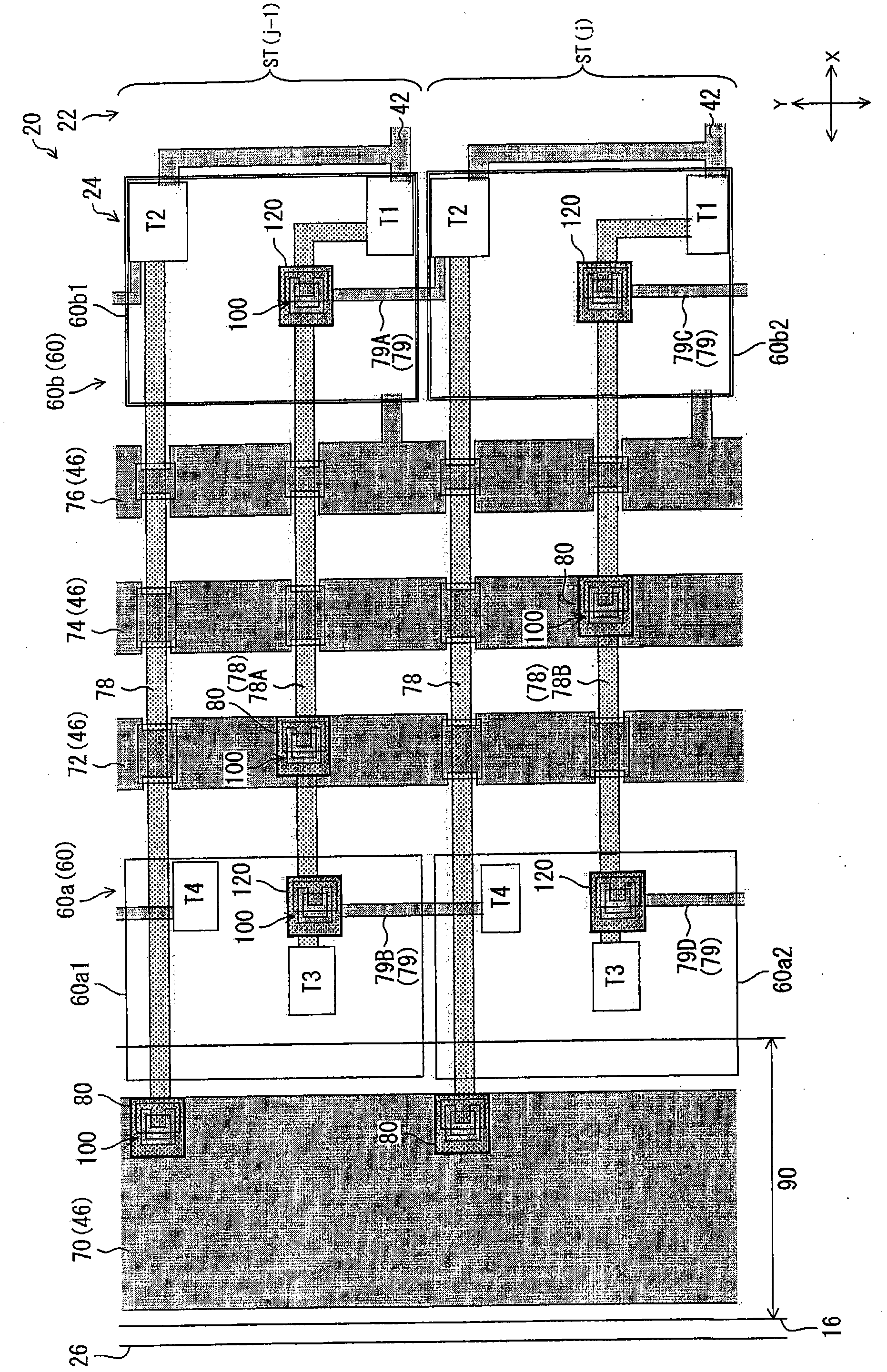

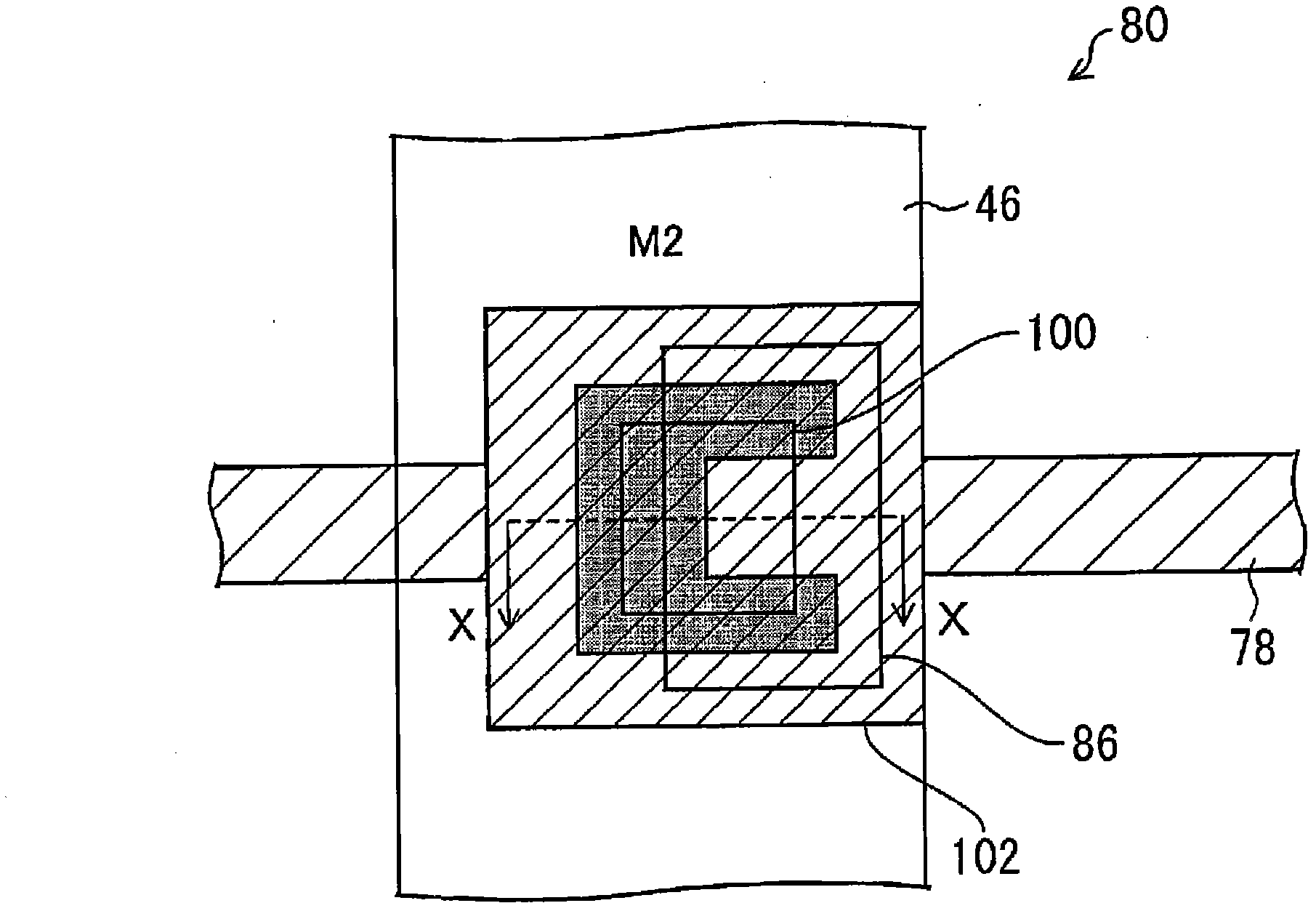

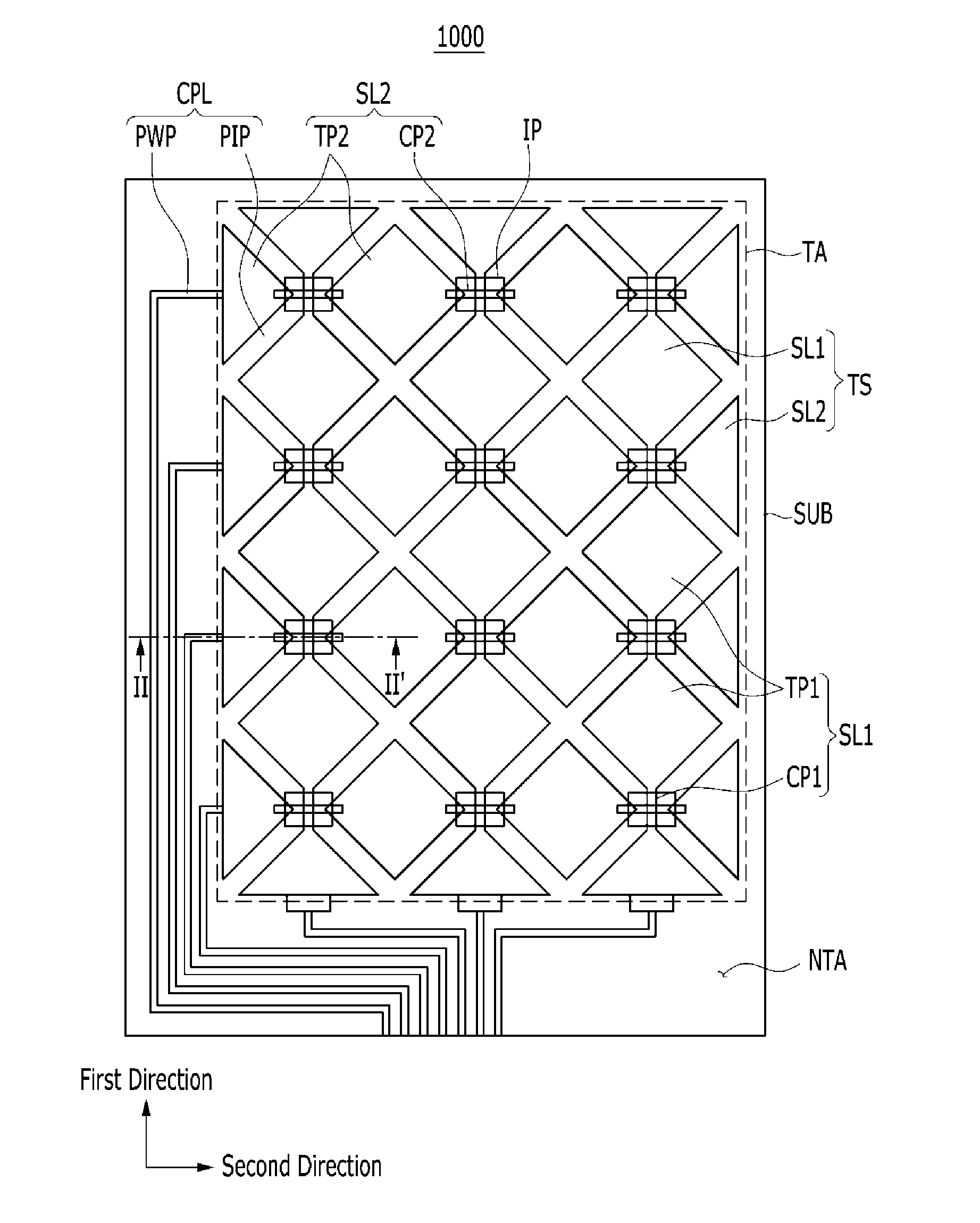

Array substrate and liquid crystal display panel

ActiveCN102713998ASuppression of Yield DecreaseIntersection reductionSolid-state devicesNon-linear opticsLiquid-crystal displayDriving circuit

A gate drive circuit (60) divided into a plurality of stages (ST) is provided. In each of the stages (ST), TFT elements (T1-T4) are provided, and branch lines (78) which connect clock lines (72, 74) and the TFT elements are provided. When attention is paid to one branch line (78A), divergent lines (79A, 79B) which electrically connect TFT elements (T2, T4) provided in a stage (ST(j)) different from a stage (ST(j-1)) in which TFT elements (T1, T3) connected to the branch line (78A) are provided and the branch line (78A) are provided to extend from the branch line (78A).

Owner:SHARP KK

Printed wiring board

ActiveCN101080956ASuppress crosstalkSuppress signal delayPrinted circuit detailsMultilayer circuit manufactureElectrical conductorInsulation layer

The present invention provides a printed wiring board, where insulation layers and conductive circuits are laminated alternately, the cross-section of each conductive circuit is rectangular, and when the upper conductive circuit space between adjacent conductive circuits of the PWB is referred to as (W1) and the lower conductive circuit space as (W2), the difference between those spaces with reference to the conductive circuit thickness (T) satisfies the formula 0.10T <=||W1 - W2| |<=0.73T. The above-described structure can suppress crosstalk and delayed signal transmission and prevent malfunctions of ICs even when high-speed driven ICs are mounted.

Owner:IBIDEN CO LTD

Transmission and receiving apparatus and method having different sending and receiving clocks

ActiveUS8804887B2Suppress signal delaySolve the real problemModulated-carrier systemsSynchronisation transmittersClock rateClock synchronization

A transmission apparatus, a signal sending apparatus, and a signal receiving apparatus, and a transmission method, a signal sending method, and a signal receiving method capable of solving a problem of metastability and suppressing a delay of a signal when sending and receiving apparatuses having different operation clock frequencies send / receive the signal representative of control information, for example. Included are a sending part that operates in synchronization with a first clock having a first period to output a transmission signal having a signal level that is inverted in response to an input of a first pulse signal corresponding to the first period and a receiving part that operates in synchronization with a second clock having a second period to output a second pulse signal corresponding to the second period in response to inversion of a signal level of the transmission signal.

Owner:LAPIS SEMICON CO LTD

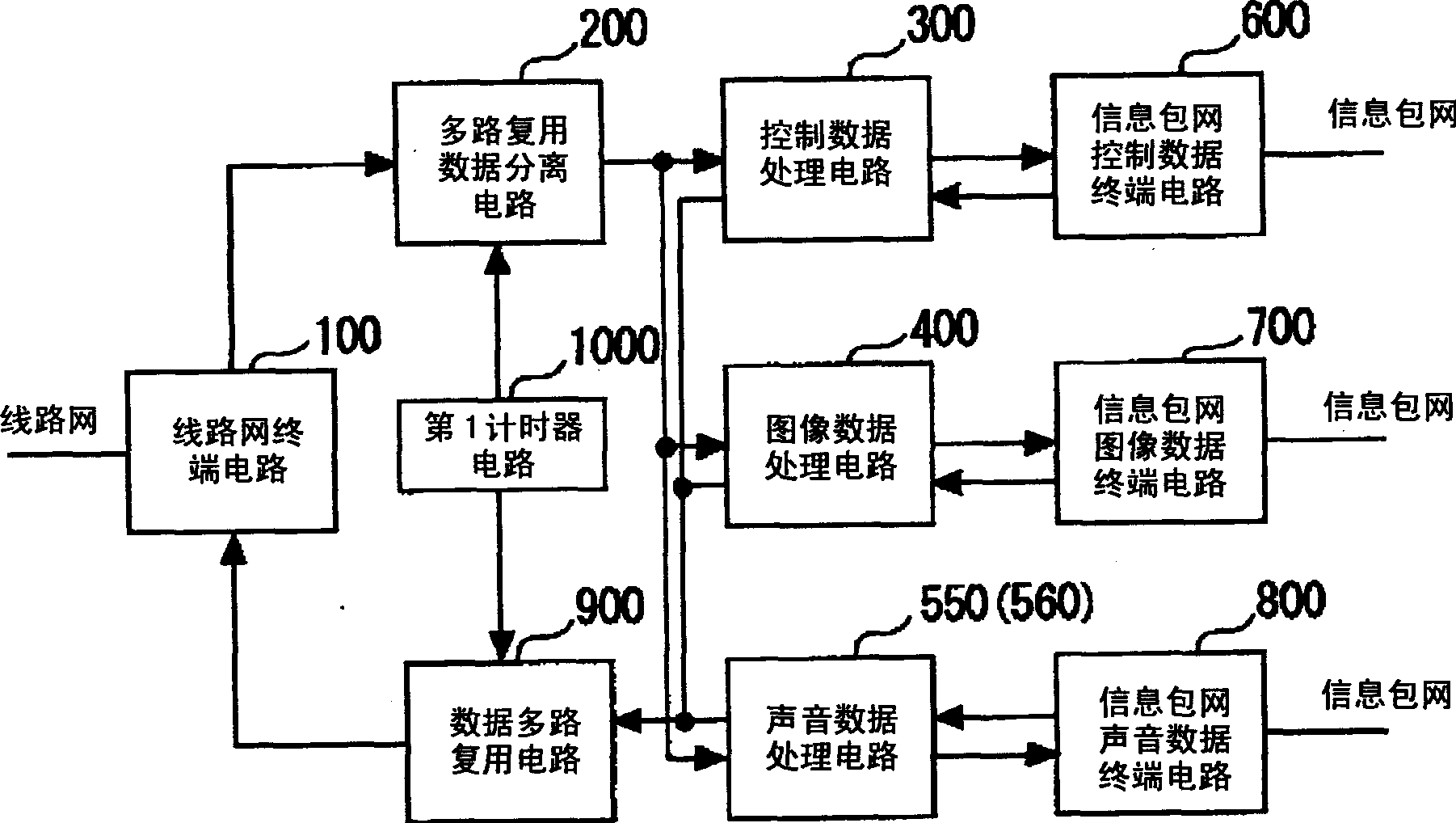

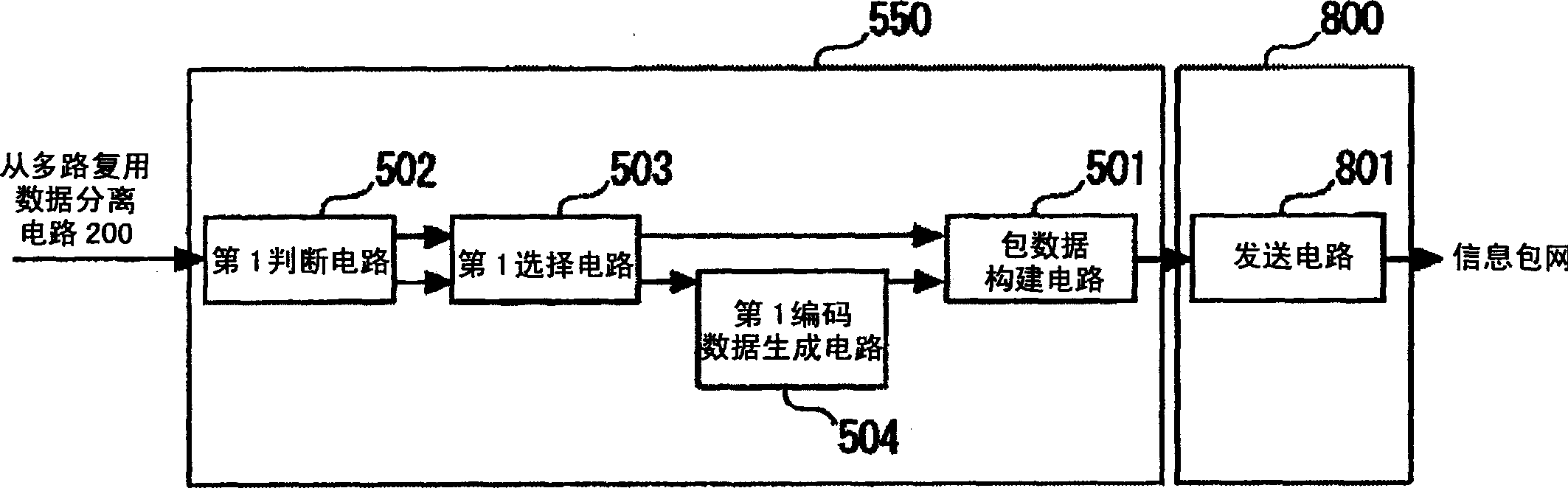

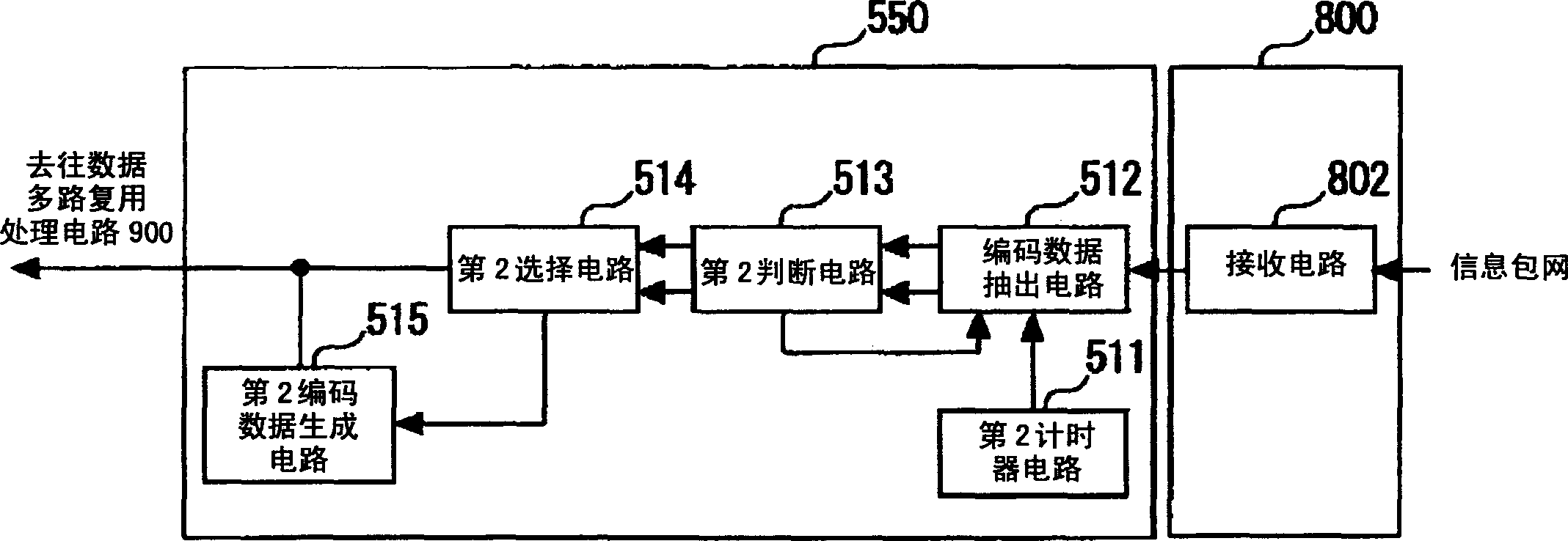

Method for processing encoded data in interconnecting different types of communication networks, and gateway apparatus

InactiveCN1886946AInhibit deteriorationSuppress signal delayHybrid transportAutomatic exchangesError concealmentTelephone communication

In a gateway apparatus for interconnecting different types of communication networks that are a line network and a packet network, a method and an apparatus for eliminating sound interruptions that would otherwise occur due to delay or loss of sound encoded data, minimizing the degradation of sound quality, and maintaining a short delay for telephone communication. A sound data processing circuit (550) of the gateway apparatus compares an expected value of the number of sound encoded data as expected outputs to be developed from a multiplexed-data separating circuit (200) in a unit period with the actual number of sound encoded data. If the actual number of sound encoded data is below the expected value, then the sound data processing circuit (550) generates encoded data for causing a destination terminal to execute an error encapsulation, and packetizes and transmits the generated encoded data together with the sound encoded data to the packet network from a transmission circuit (801). If acquiring no sound data from a reception circuit of the packet network in a given period, the sound data processing circuit (550) generates a signal indicative of no acquisition, selects either generation or disposal of the encoded data, and sends the signal to the line network from a data multiplexing circuit (900) and a line network terminating circuit (100).

Owner:NEC CORP

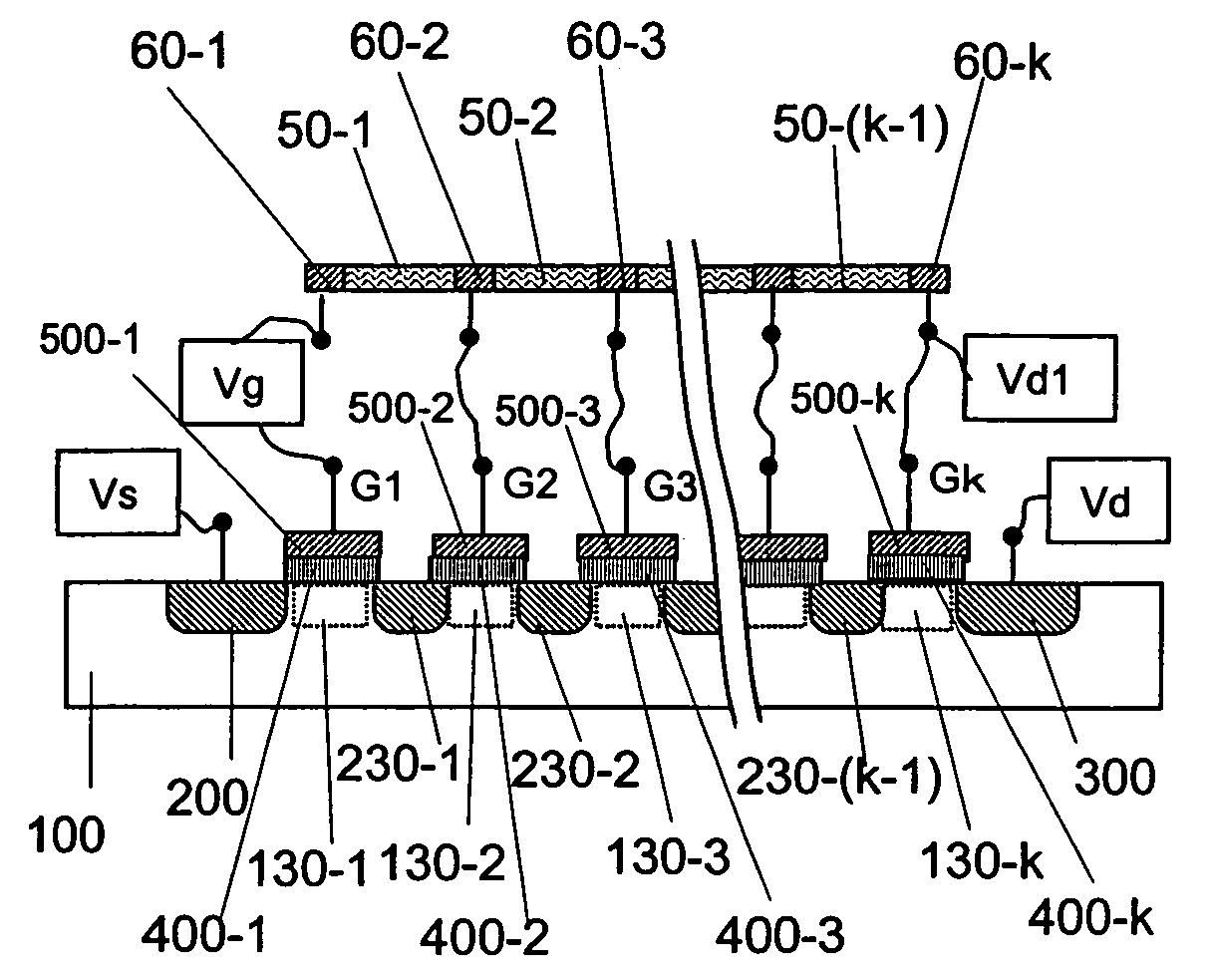

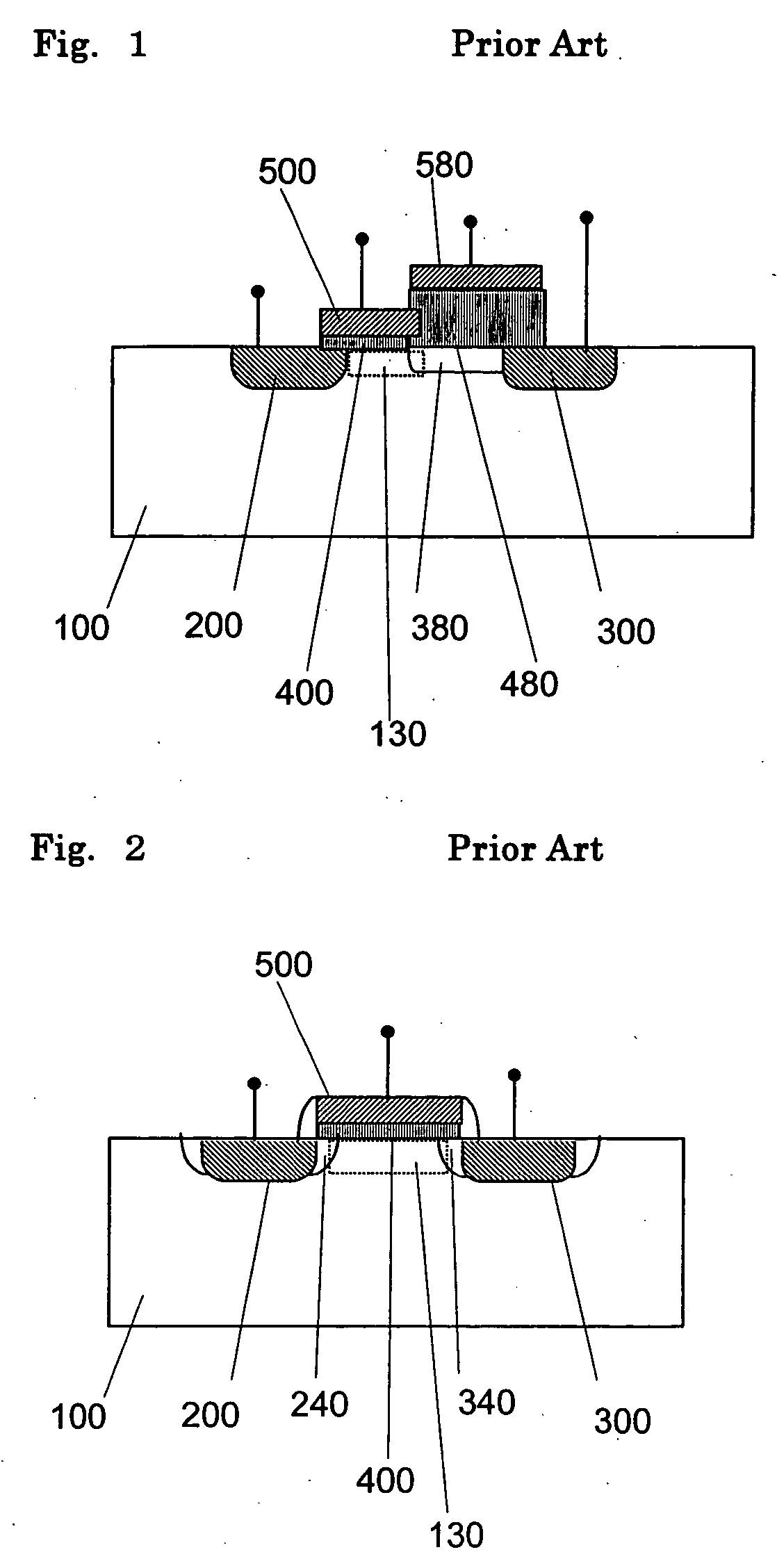

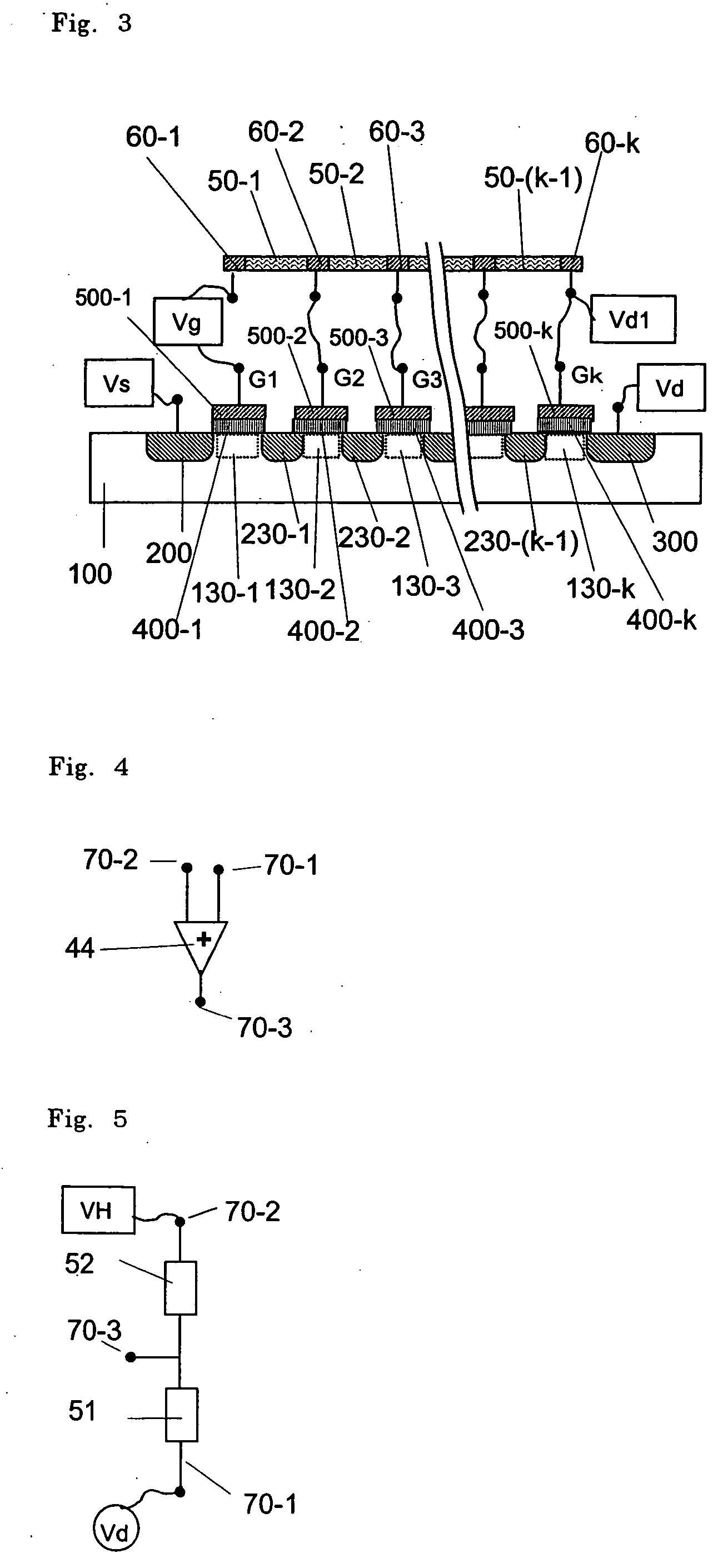

High voltage operating field effect transistor, bias circuit therefor and high voltage circuit thereof

InactiveUS20050184349A1Decrease in driving current valueSuppress signal delayTransistorWriting connectorsHigh pressureField-effect transistor

A high voltage operating field effect transistor is formed in an IC or LSI by utilizing a constituent portion of a transistor or a process technique for a standard power supply voltage of the IC or LSI. In order to increase an operating voltage of a field effect transistor, measures are taken in which a gate is divided into division gates, and electric potentials which are closer to a drain electric potential and which change according to increase or decrease in the drain electric potential are supplied to the division gates nearer a drain, respectively.

Owner:HAYASHI YUTAKA

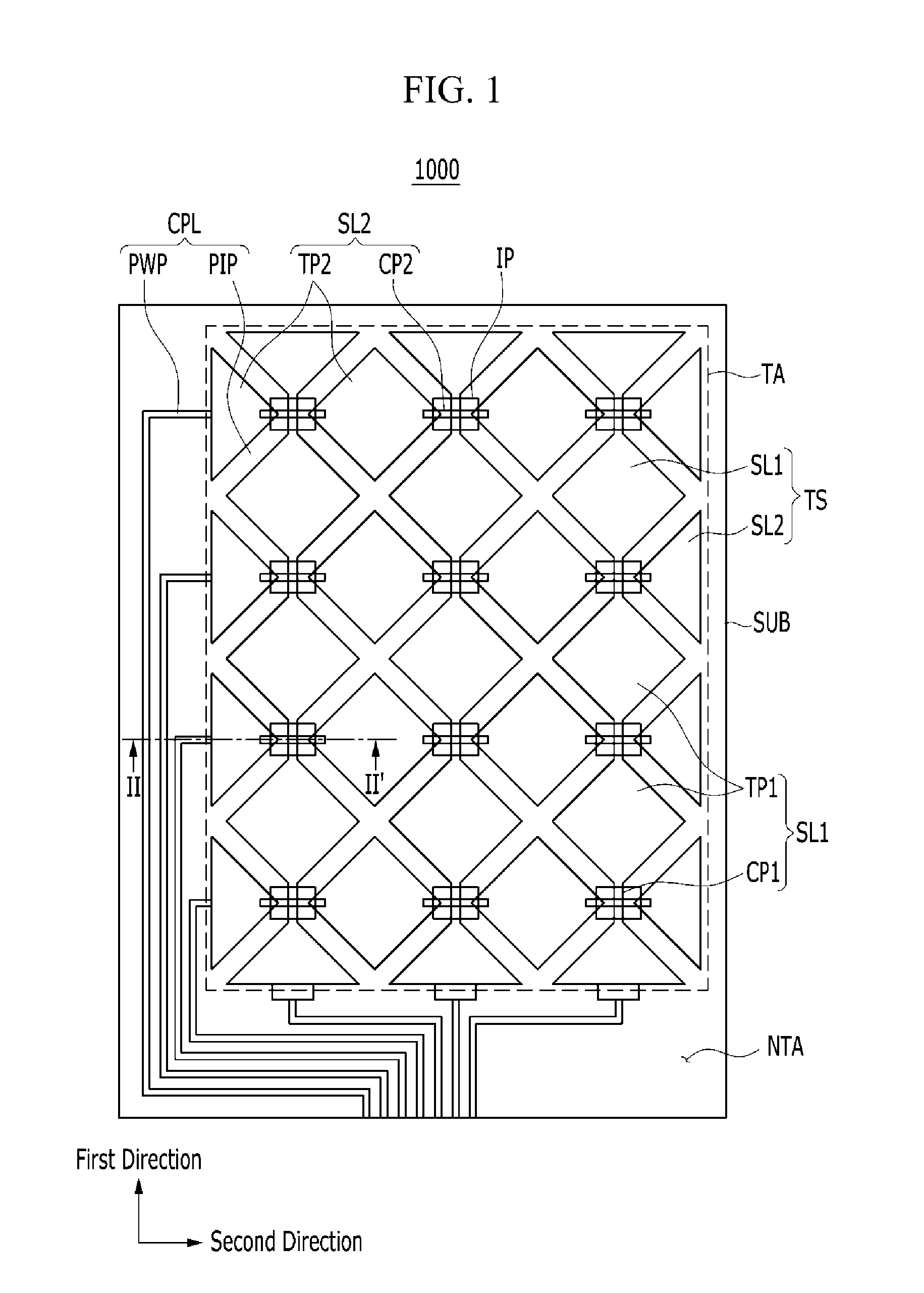

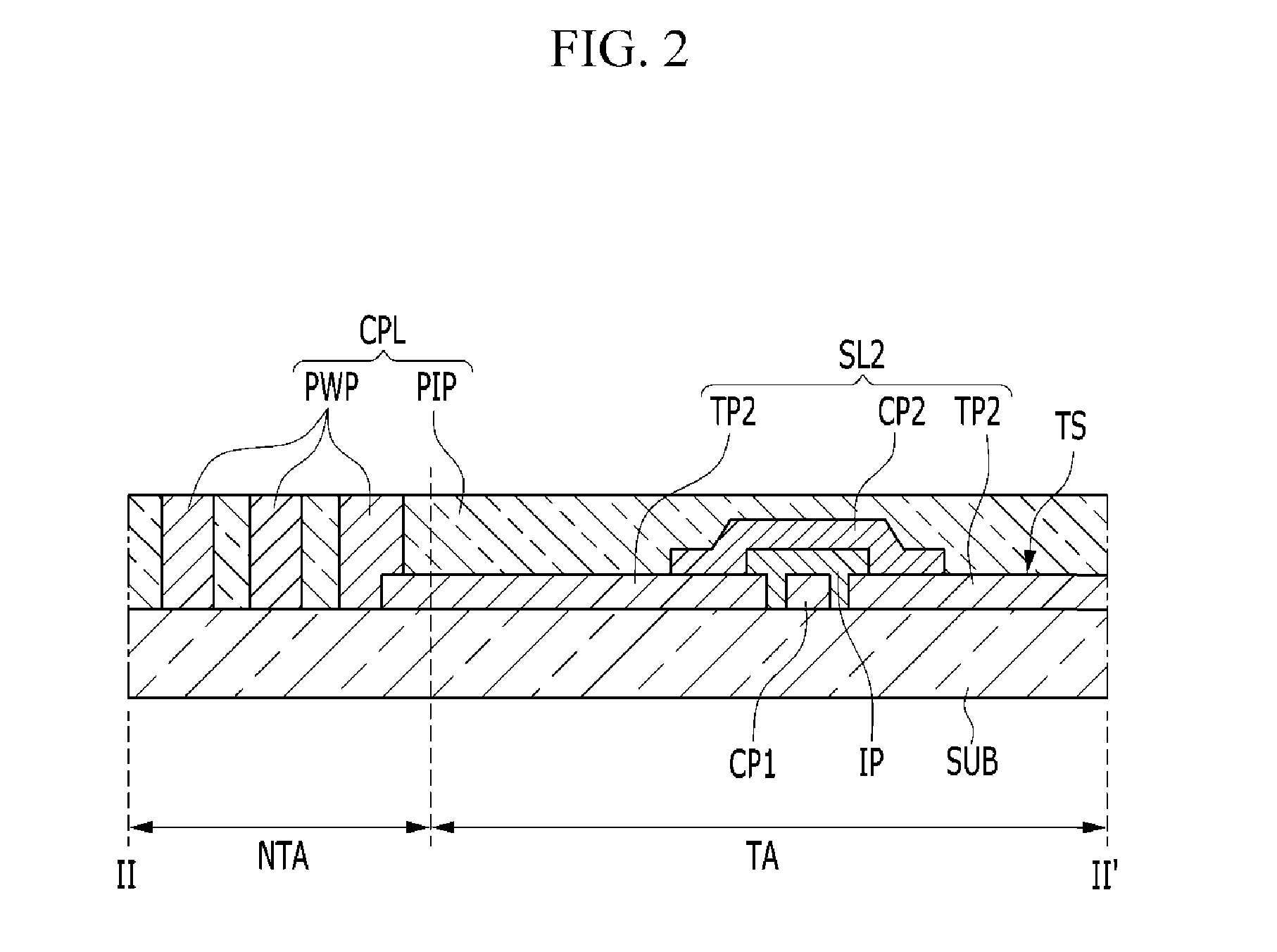

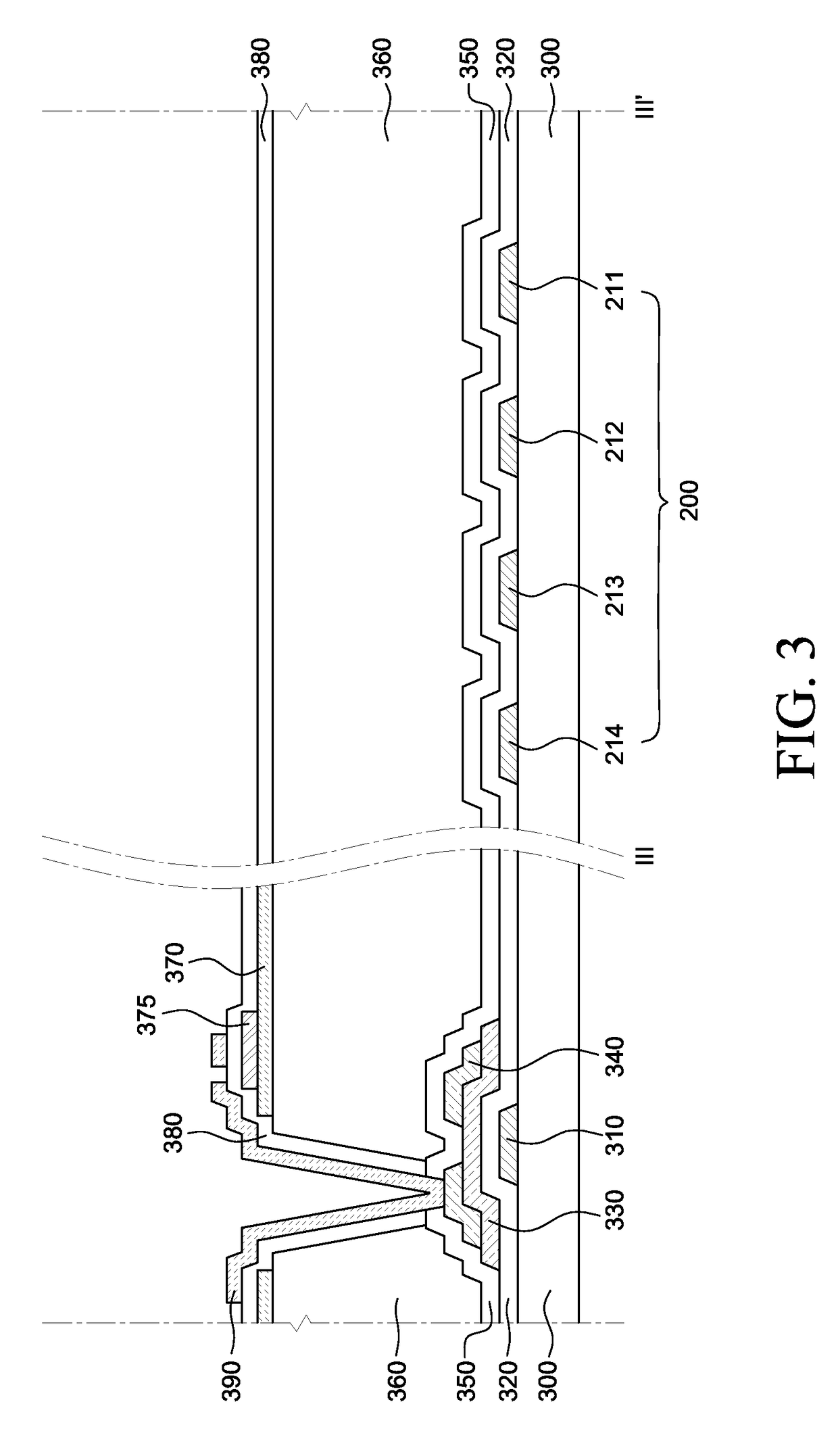

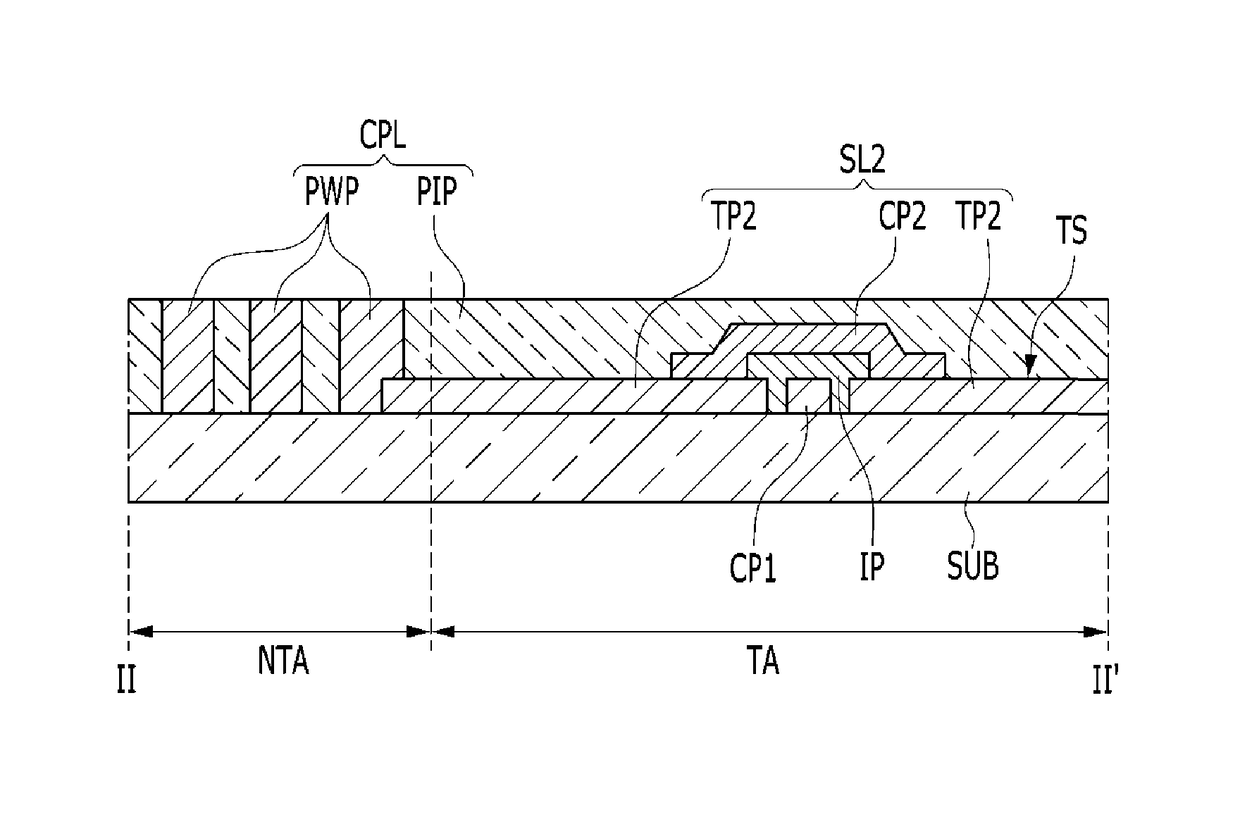

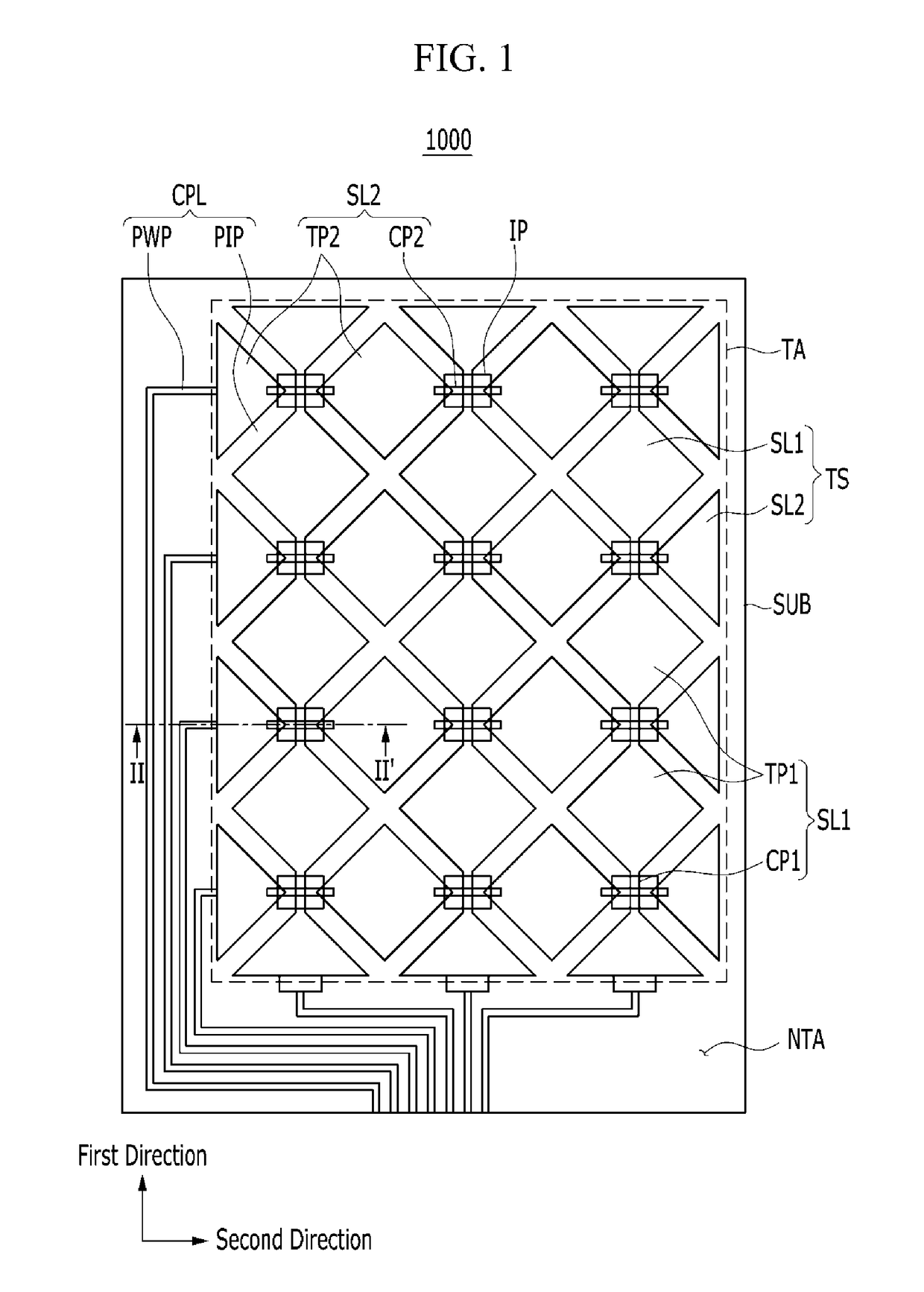

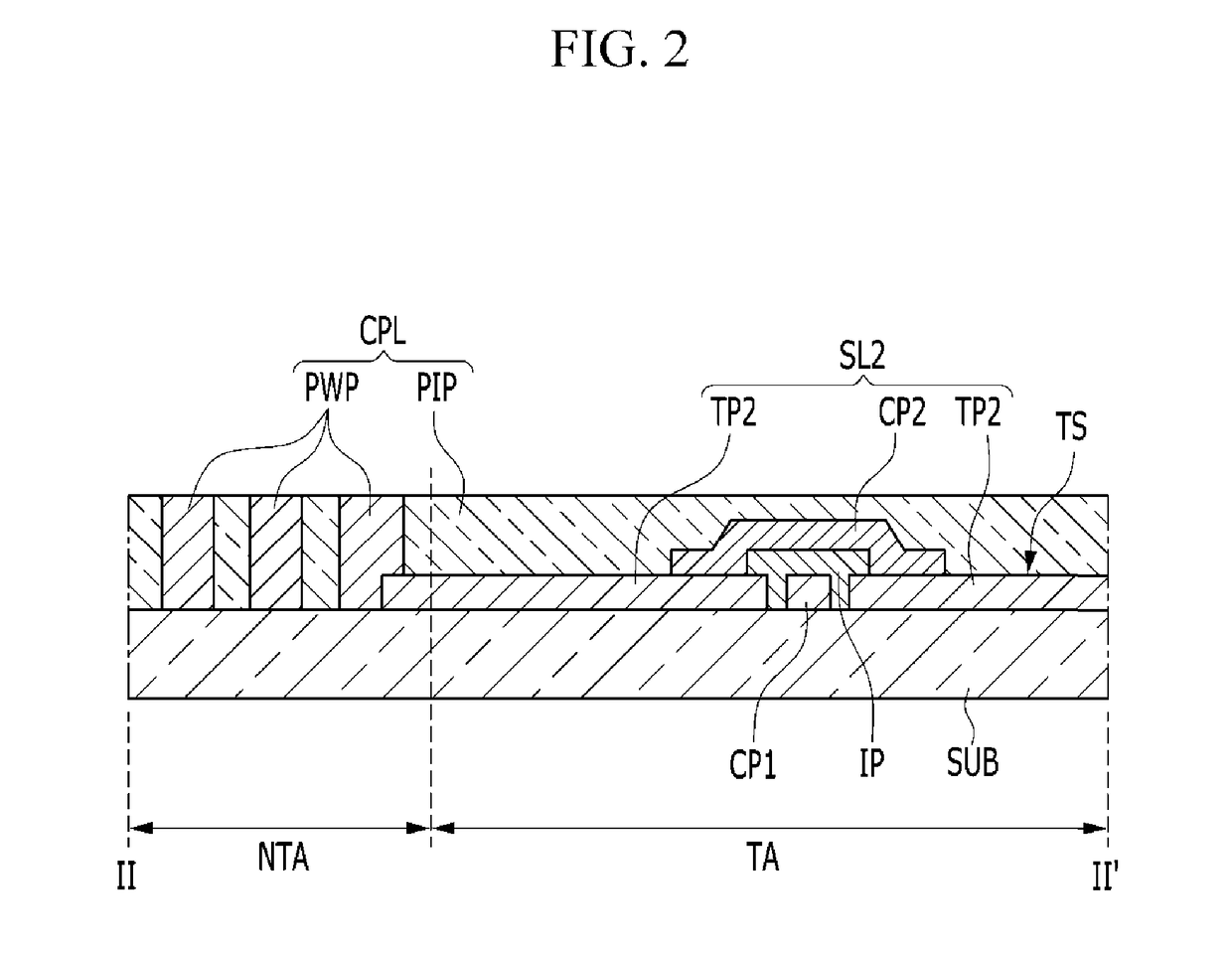

Touch panel

ActiveUS20160313826A1Suppress signal delayInput/output processes for data processingConductive polymerEngineering

A touch panel includes a substrate including a touch area and a non-touch area adjacent to the touch area, a conductive polymer layer disposed on the substrate, and a touch sensor unit disposed between the conductive polymer layer and the touch area of the substrate. The conductive polymer layer includes a polymer wiring pattern disposed in the non-touch area of the substrate and includes a conductive polymer connected to the touch sensor unit.

Owner:SAMSUNG DISPLAY CO LTD

Gate driver and organic light emitting display device including the same

ActiveUS10706786B2Reduce areaSuppress signal delayStatic indicating devicesDisplay deviceEngineering

According to an aspect of the present disclosure, a gate driver includes a plurality of stages which is dependently connected to each other and each of the plurality of pixels includes: a first output unit which outputs a sensing signal by voltages of a Q node and a QB node; a second output unit which outputs a reference signal by the voltages of the Q node and the QB node; a third output unit which outputs a scan signal by the voltages of the Q node and the QB node; a first controller which controls the Q node; and a second controller which controls the QB node, and at least two of the first to third output units share at least one clock signal among a plurality of clock signals, thereby reducing an area of the gate driver.

Owner:LG DISPLAY CO LTD

Semiconductor device

InactiveCN101263587ASmall sizeSituations to Avoid Causes of Bad WorkSemiconductor/solid-state device detailsSolid-state devicesChip sizePosition shift

Provided is a semiconductor device having staggered pad arrangement wherein pads are arranged by being alternately shifted, as a pad arrangement for connecting with an external package on an LSI. In the semiconductor device, wire short-circuit during assembly, chip size increase due to wire short-circuit prevention, propagation of power supply and GND noise due to reduction of an IO cell interval, signal transmission delay difference due to pad position shift, and the like can be eliminated. In the semiconductor device, a plurality of pads to be connected with functional terminals of the external package on the semiconductor element are arranged in two rows along the periphery of the semiconductor element. The arrangement order of the pads on the semiconductor element is different from that of the functional terminals of the external package.

Owner:PANASONIC SEMICON SOLUTIONS CO LTD

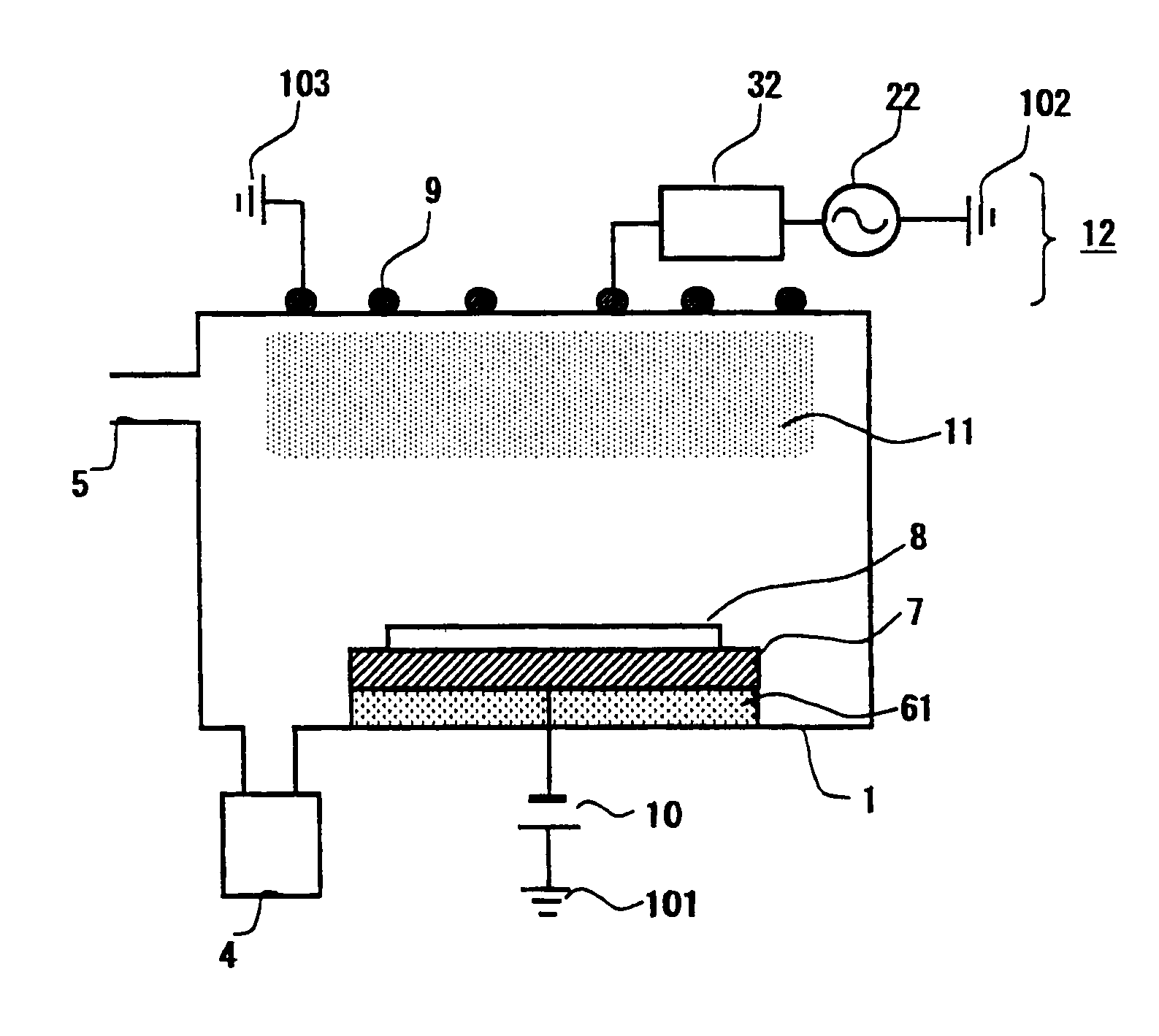

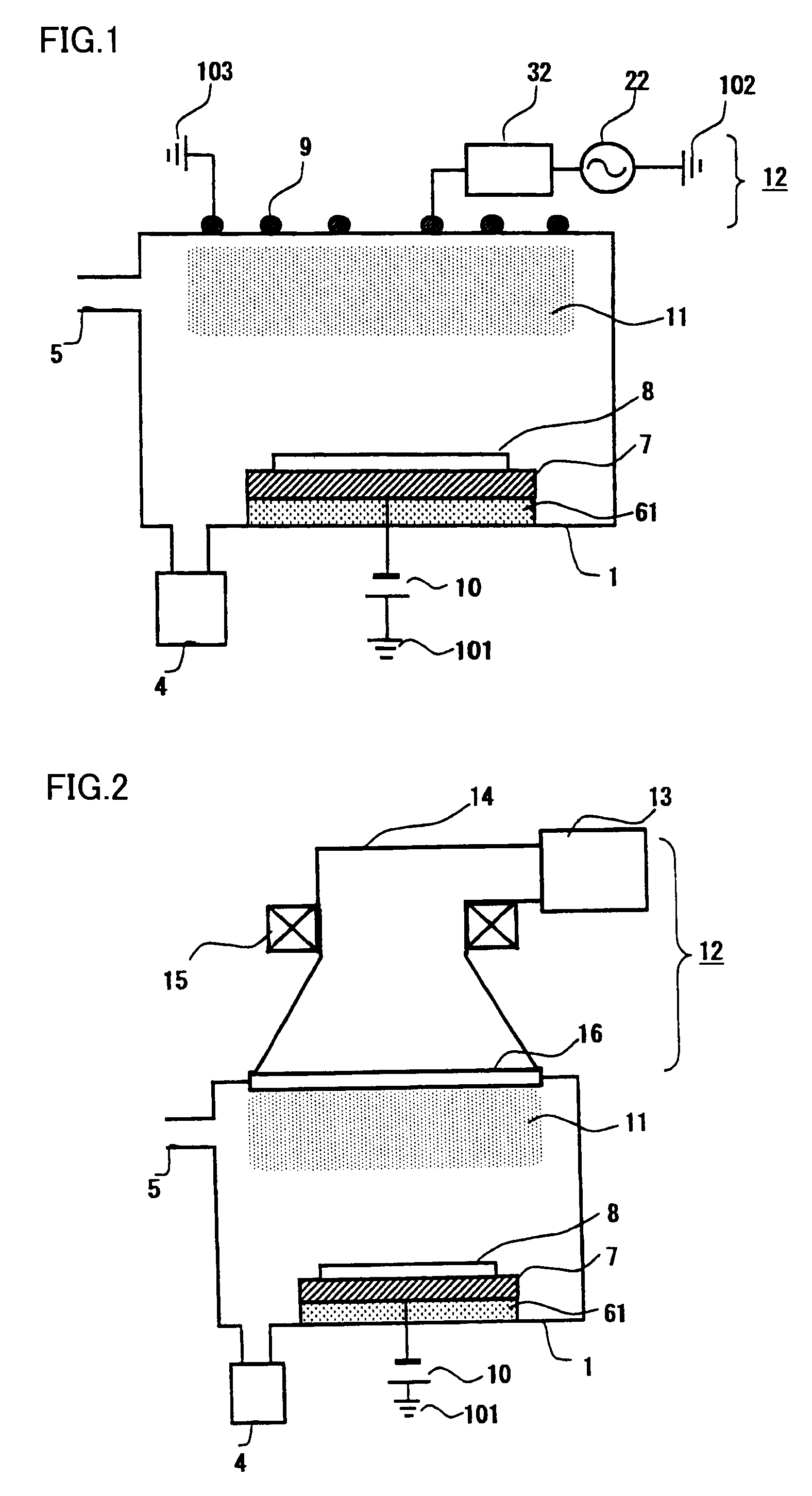

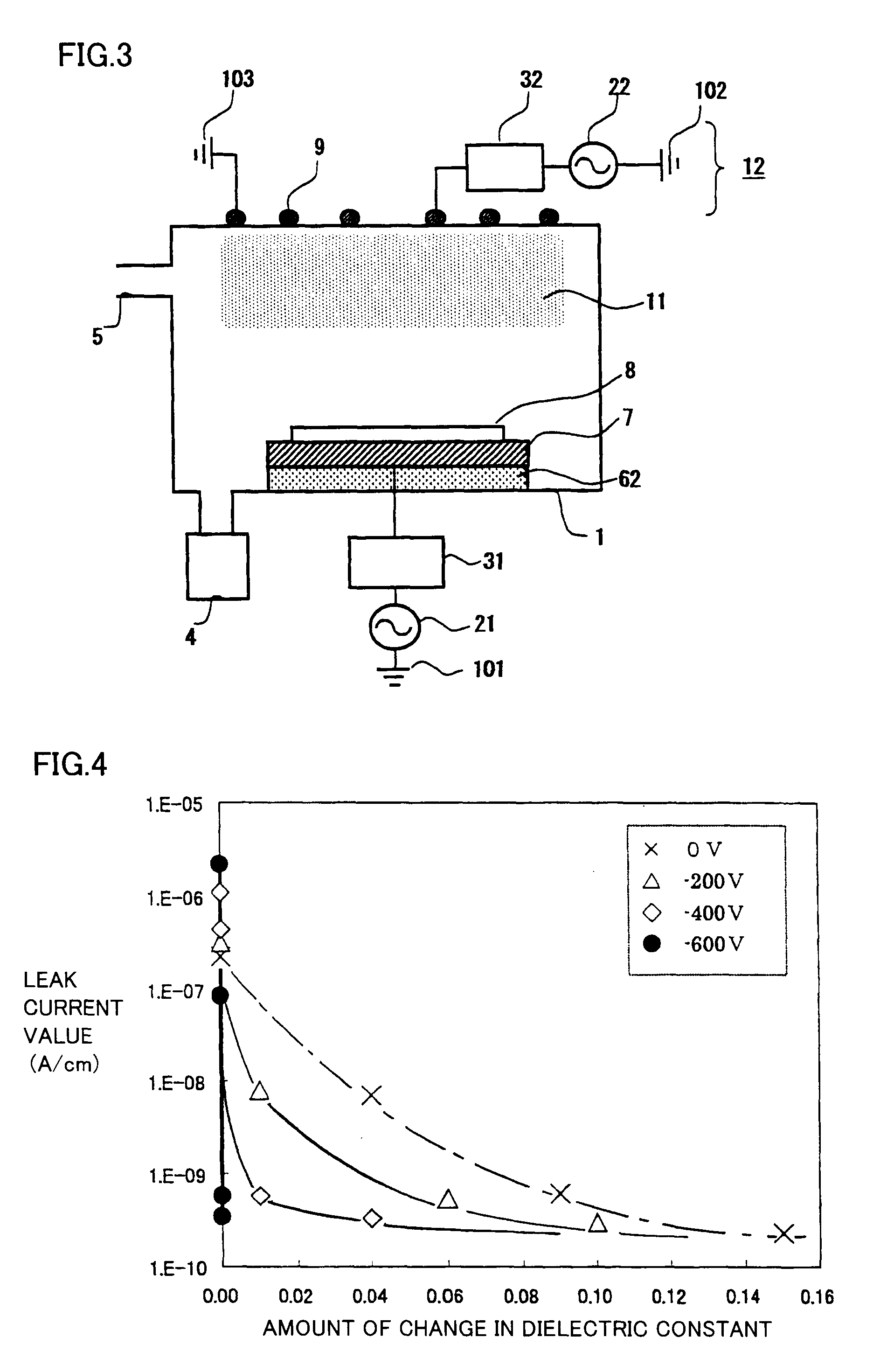

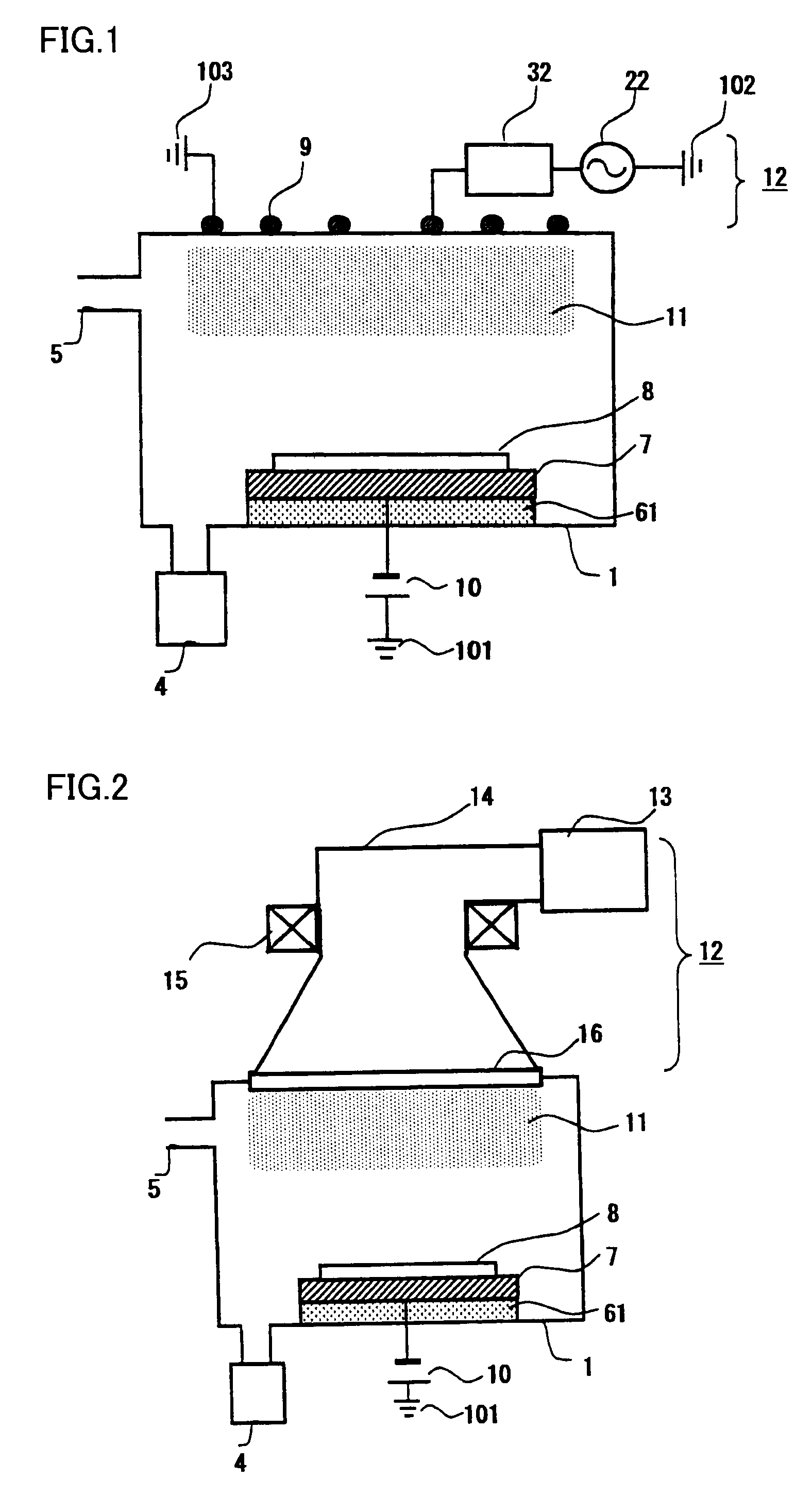

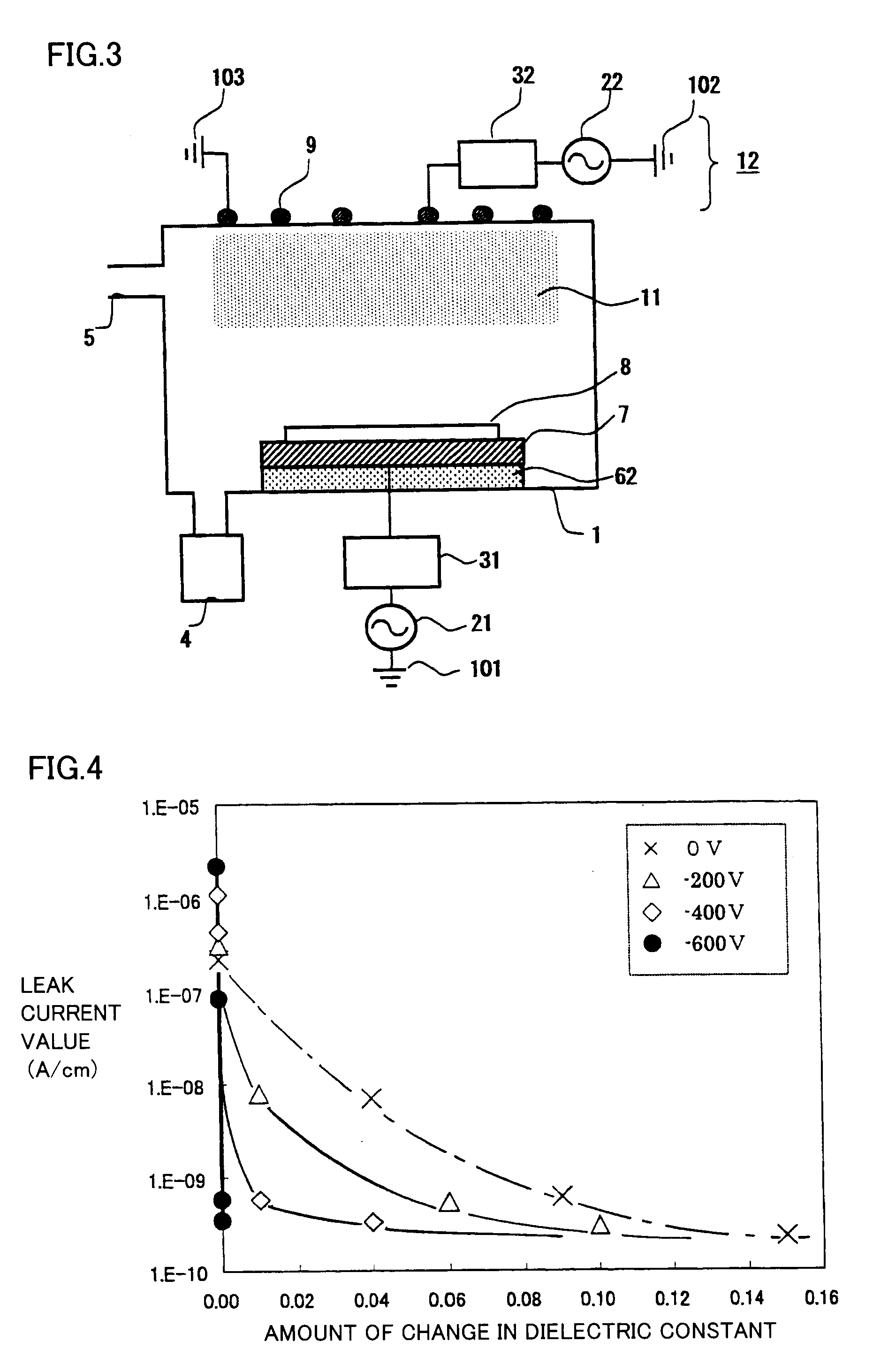

Plasma CVD apparatus, method for forming thin film and semiconductor device

InactiveUS8404314B2Increase speedLow dielectric constantLiquid surface applicatorsElectric discharge tubesPower semiconductor deviceEngineering

A plasma CVD apparatus including a reaction chamber including an inlet for supplying a compound including a borazine skeleton, a feeding electrode, arranged within the reaction chamber, for supporting a substrate and being applied with a negative charge, and a plasma generating mechanism, arranged opposite to the feeding electrode via the substrate, for generating a plasma within the reaction chamber. A method forms a thin film wherein a thin film is formed by using a compound including a borazine skeleton as a raw material, and a semiconductor device includes a thin film formed by such a method as an insulating film. The apparatus and method enable to produce a thin film wherein low dielectric constant and high mechanical strength are stably maintained for a long time and insulating characteristics are secured.

Owner:MITSUBISHI ELECTRIC CORP

Plasma CVD apparatus, method for forming thin film and semiconductor device

InactiveUS20100164072A1Suppress signal delayHigh mechanical strengthLiquid surface applicatorsElectric discharge tubesEngineeringUltimate tensile strength

A plasma CVD apparatus including a reaction chamber including an inlet for supplying a compound including a borazine skeleton, a feeding electrode, arranged within the reaction chamber, for supporting a substrate and being applied with a negative charge, and a plasma generating mechanism, arranged opposite to the feeding electrode via the substrate, for generating a plasma within the reaction chamber. A method forms a thin film wherein a thin film is formed by using a compound including a borazine skeleton as a raw material, and a semiconductor device includes a thin film formed by such a method as an insulating film. The apparatus and method enable to produce a thin film wherein low dielectric constant and high mechanical strength are stably maintained for a long time and insulating characteristics are secured.

Owner:MITSUBISHI ELECTRIC CORP

Array substrate and display device

ActiveUS10176774B2Suppress signal delayReduce widthStatic indicating devicesDigital storageDisplay deviceEngineering

An array substrate includes: a display area; a non-display area outside of the display area; a gate-in-panel (GIP) circuit in the non-display area; a plurality of clock signal lines in the non-display area and configured to transfer signals to the GIP circuit; and connection lines in the non-display area and configured to connect the plurality of clock signal lines to the GIP circuit. Each of the plurality of clock signal lines is a ring shaped line.

Owner:LG DISPLAY CO LTD

Touch panel including a conductive polymer layer

ActiveUS9720552B2Suppress signal delayInput/output processes for data processingConductive polymerEngineering

A touch panel includes a substrate including a touch area and a non-touch area adjacent to the touch area, a conductive polymer layer disposed on the substrate, and a touch sensor unit disposed between the conductive polymer layer and the touch area of the substrate. The conductive polymer layer includes a polymer wiring pattern disposed in the non-touch area of the substrate and includes a conductive polymer connected to the touch sensor unit.

Owner:SAMSUNG DISPLAY CO LTD

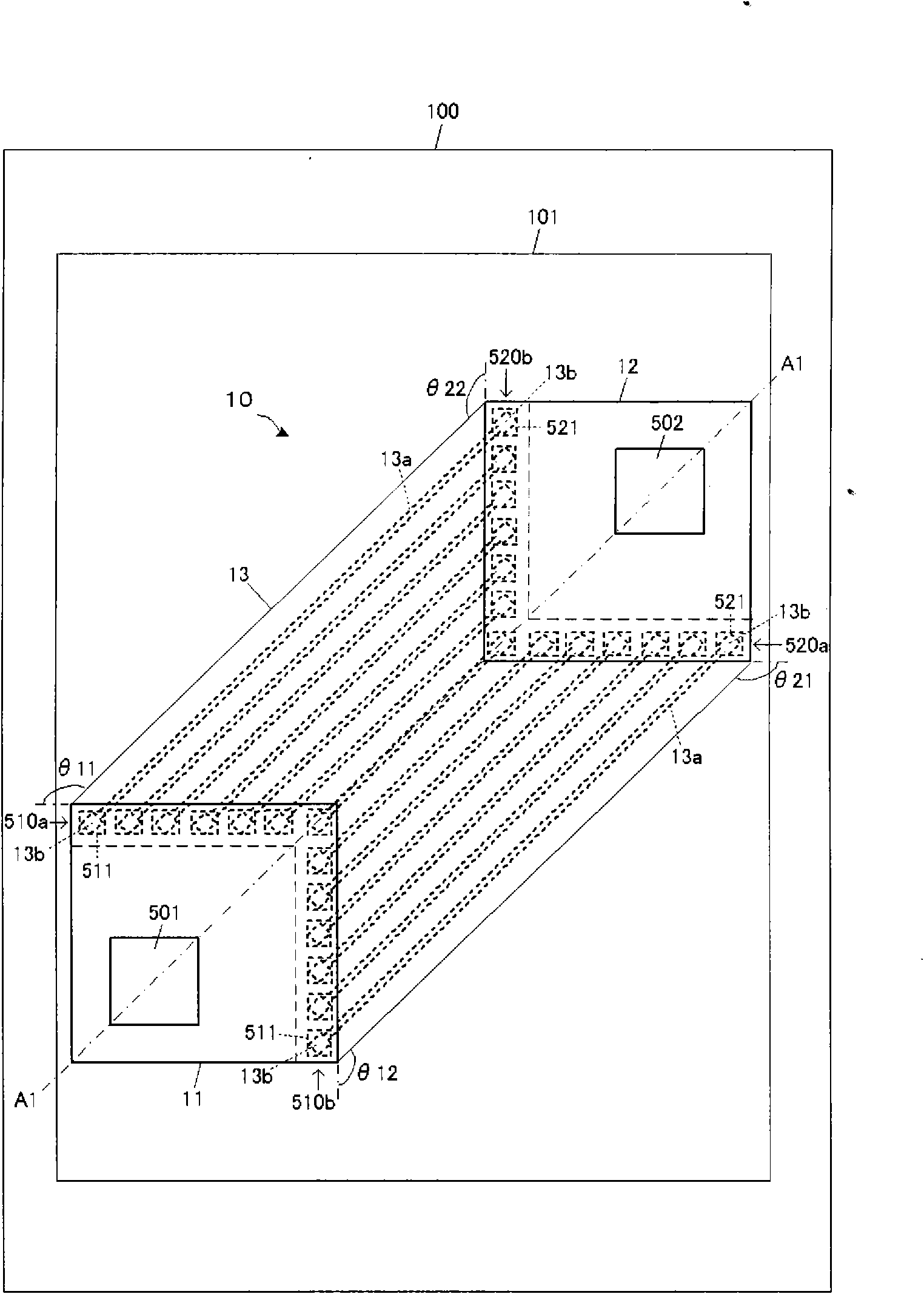

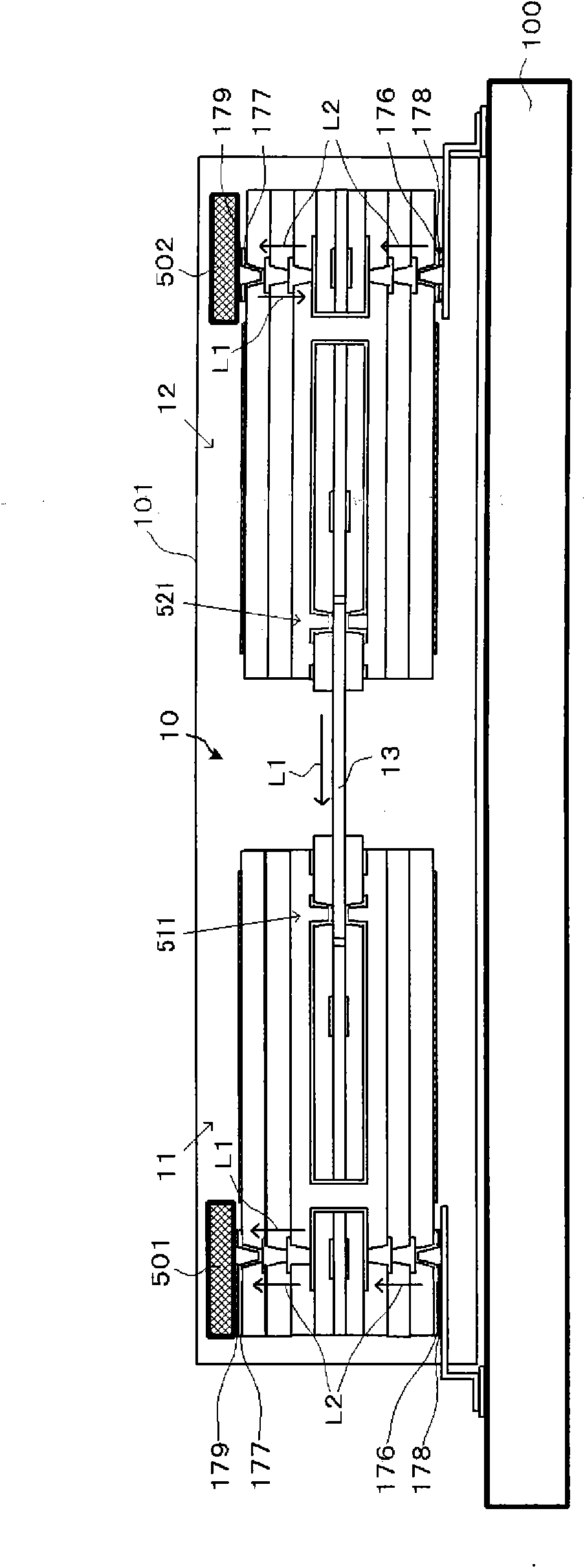

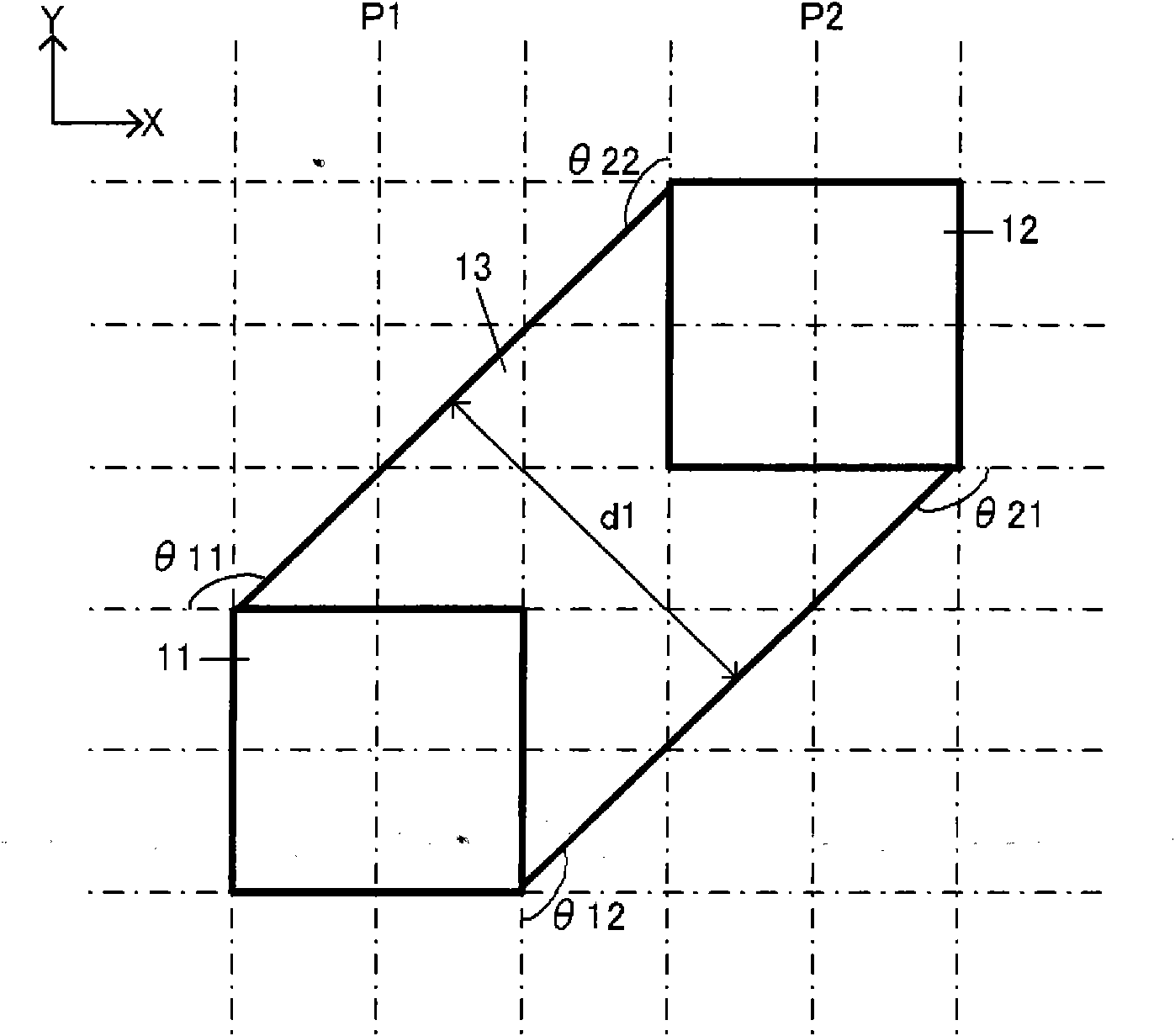

Flex-rigid wiring board and electronic device

InactiveCN102113425BShorten the signal pathSuppress signal delayPrinted electric component incorporationPrinted circuit aspectsElectrical conductorAcute angle

A flex-rigid wiring board including a rigid printed wiring board having a rectangular shape and having a rigid base material and a conductor, and a flexible printed wiring board having a flexible base material and a conductor formed over the flexible base material. The conductor of the flexible printed wiring board is electrically connected to the conductor of the rigid printed wiring board. The flexible printed wiring board is connected to the rigid printed wiring board and extends from one or more sides of the rectangular shape of the rigid printed wiring board such that the flexible printed wiring board extends in a direction which makes an acute angle with respect to one or more sides of the rectangular shape of the rigid printed wiring board.

Owner:IBIDEN CO LTD

Printed wiring board

ActiveCN100556228CSuppress crosstalkSuppress signal delayPrinted circuit detailsMultilayer circuit manufactureElectrical conductorPrinted circuit board

The present invention provides a printed circuit board, which is formed by alternately stacking insulating layers and conductor circuits, each conductor circuit has a rectangular cross-section, wherein the upper side interval of the conductor circuit among the intervals between adjacent conductor circuits is set to W1, When the interval on the lower surface side of the conductor circuit is W2, the relationship between these intervals and the thickness T of the conductor circuit satisfies 0.10T≦|W1-W2|≦0.73T. According to such a configuration, even if an IC driven at high speed is mounted, crosstalk and signal delay can be suppressed, and malfunction of the IC can be prevented.

Owner:IBIDEN CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com