Semiconductor device

A semiconductor and wire technology, applied in the field of semiconductor devices, can solve problems such as poor work, deterioration of work quality, and increase in chip size, and achieve the effect of reducing chip size, reducing impact, and preventing chip size increase.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach 1

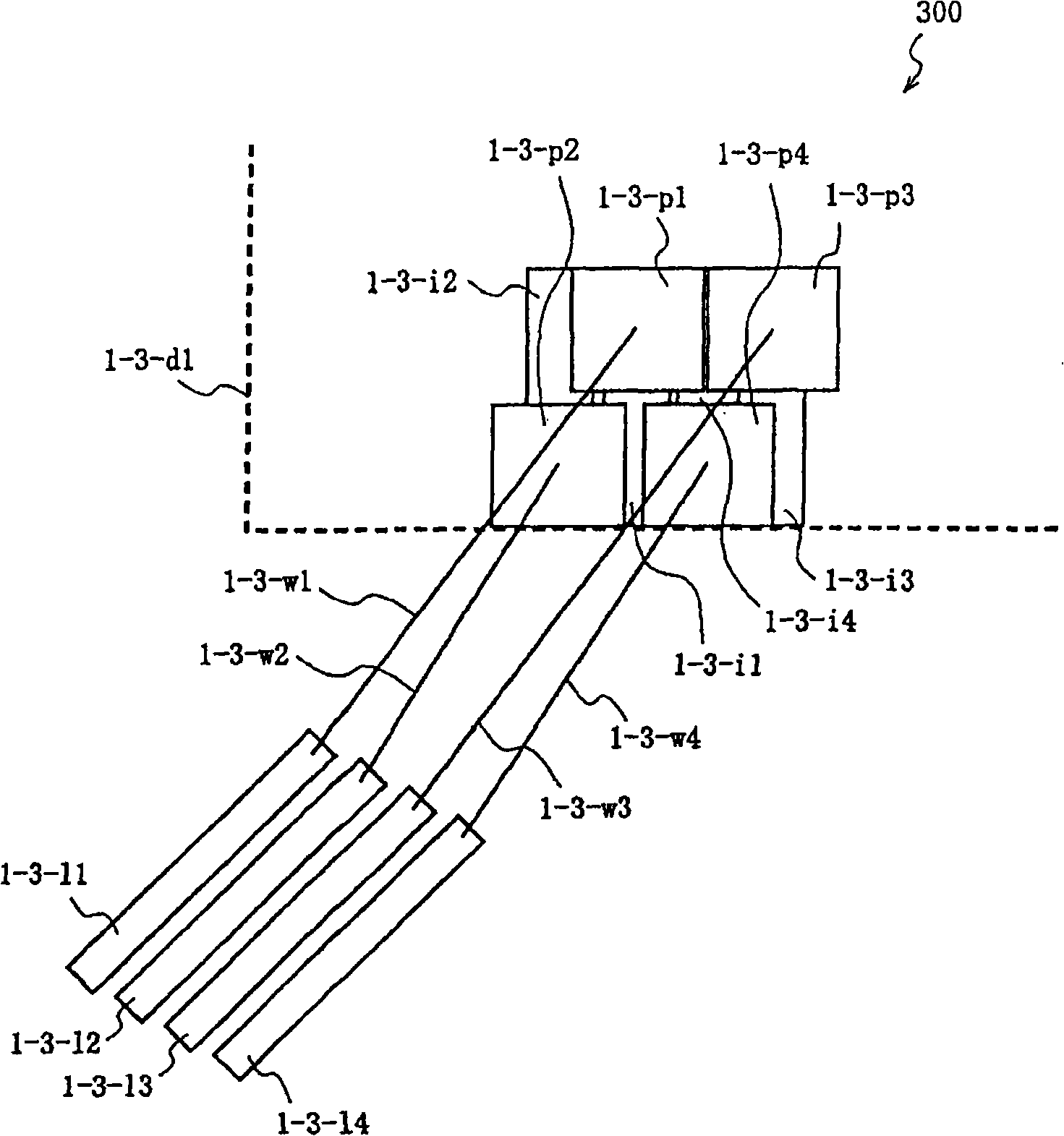

[0190] Hereinafter, the semiconductor device 300 (semiconductor device 1 ) according to Embodiment 1 of the present invention will be described with reference to the drawings.

[0191] image 3 It is a partially enlarged plan view showing a semiconductor device 300 according to Embodiment 1 of the present invention corresponding to Invention 1.

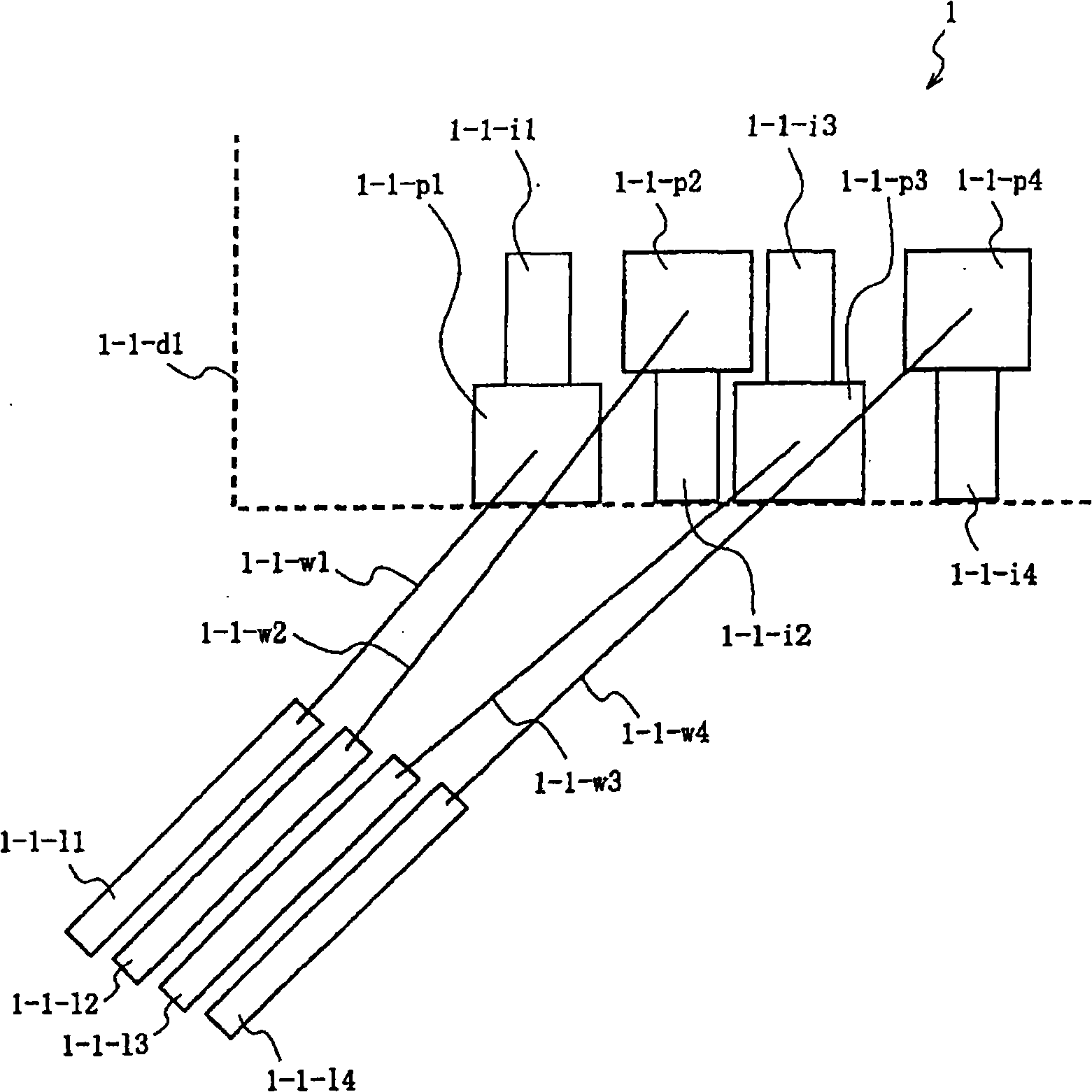

[0192] here, figure 1 is a partially enlarged plan view of a conventional semiconductor device 1, and figure 1 In the conventional semiconductor device 1, the lead terminal 1-1-l1 is connected to the pad 1-1-p1 through the wire 1-1-w1, and is connected to the inside of the semiconductor element through the IO circuit part 1-1-i1. Similarly, the lead terminal 1-1-l2 is connected to the pad 1-1-p2 via the lead wire 1-1-w2, and is connected to the inside of the semiconductor element through the IO circuit part 1-1-i2, and the lead terminal 1-1 The same is true after -l3 figure 1 connection shown.

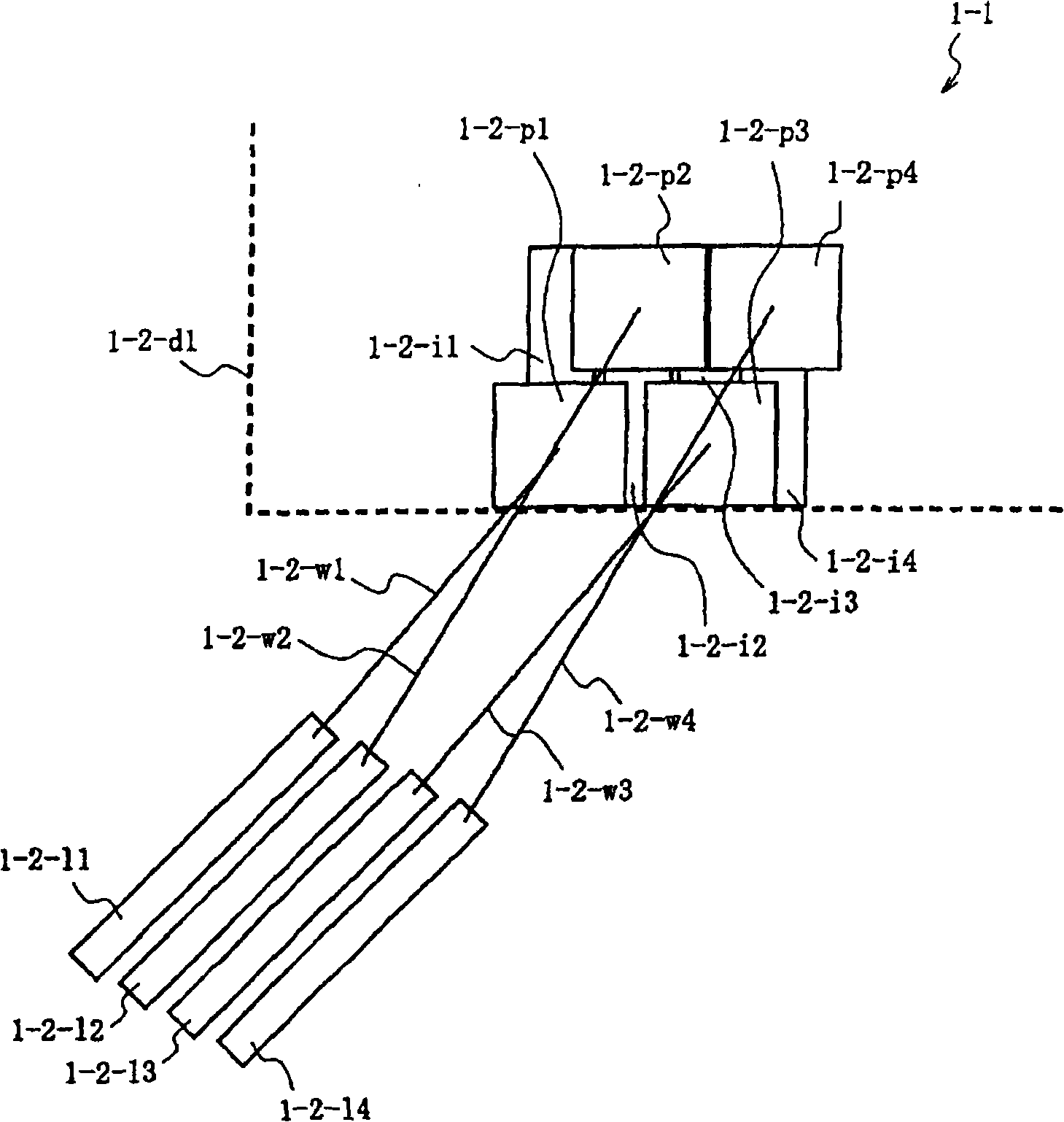

[0193] in addition, figure 2 is...

Embodiment approach 2

[0199] Next, the semiconductor device 400 (semiconductor device 1-1) according to Embodiment 2 of the present invention will be described.

[0200] Figure 4 It is a plan view showing a semiconductor device 400 according to Embodiment 2 of the present invention corresponding to Invention 2.

[0201] In the semiconductor device 400 of Embodiment 2, from image 3 In the shown semiconductor device 300 of Embodiment 1, the lead terminal 1-3-12 connects two wires to two pads.

[0202] Conventionally, there has been a method of connecting two wires from one lead terminal to two pads. However, in the conventional method, it is necessary to arrange the connection destination pad of the two wires adjacent to the IO circuit part so that no wire contact occurs.

[0203] exist Figure 4 In the shown semiconductor device 400 of the second embodiment, as a method of avoiding wire contact, the arrangement order of the pads and the IO circuit portion is changed.

[0204] That is, if Fi...

Embodiment approach 3

[0207] Next, a semiconductor device 500 (semiconductor device 1-2) according to Embodiment 3 of the present invention corresponding to Invention 3 will be described.

[0208] The semiconductor device 500 of the third embodiment, like the semiconductor device 400 of the second embodiment, has Figure 4 Its plan view is shown in , as the terminal function of the lead terminal 1-4-l2, the power supply or GND function is distributed, and the lead terminal 1-4-l2 is respectively connected to the soldering terminal via the wire 1-4-w2 and 1-4-w3 The pads 1-4-p2, 1-4-p3, as the IO circuit part connected to the pads 1-4-p2, 1-4-p3, configure the IO circuit as the IO circuit for power supply or GND Section 1-4-i2, 1-4-i3.

[0209] Thereby, power supply or GND can be supplied from the circuit parts 1-4-i2 and 1-4-i3 for IO of two separated positions.

[0210] In this way, in the semiconductor device 500 (semiconductor device 1-2) of the third embodiment, the terminal connecting the tw...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More