Transistor array substrate and display panel

A transistor array and display panel technology, applied in static indicators, lighting devices, light sources, etc., can solve problems such as wiring current flow delay, transistor characteristic change, voltage drop, etc., and achieve the effect of suppressing signal delay and voltage drop.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 Embodiment approach

[0071] Hereinafter, embodiments for carrying out the present invention will be described with reference to the drawings. However, in the following embodiments, it is preferable to add various limitations technically in order to implement the present invention, but the scope of the invention is not limited to the following embodiments and illustrations.

[0072] [Overall configuration of EL display panel]

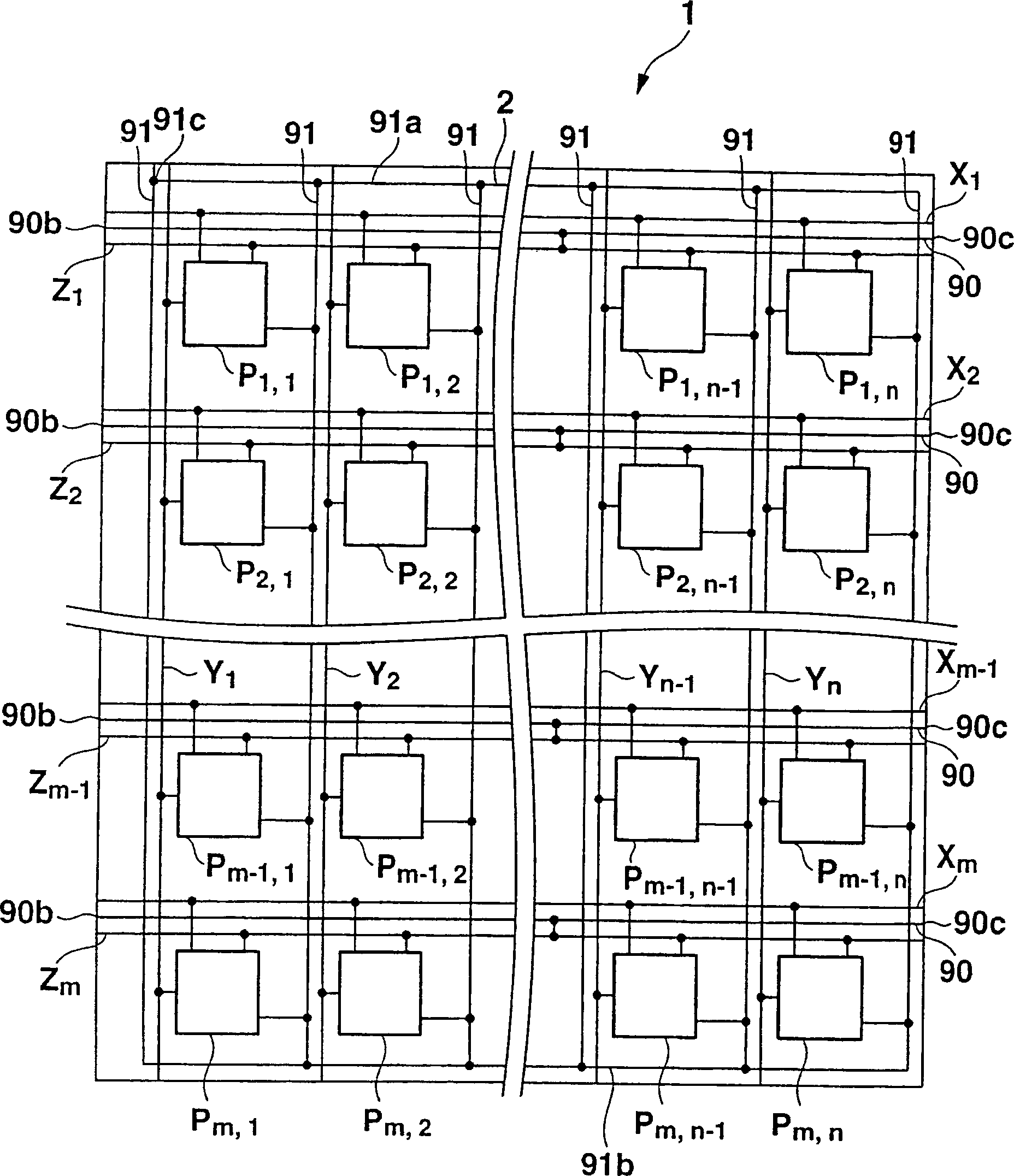

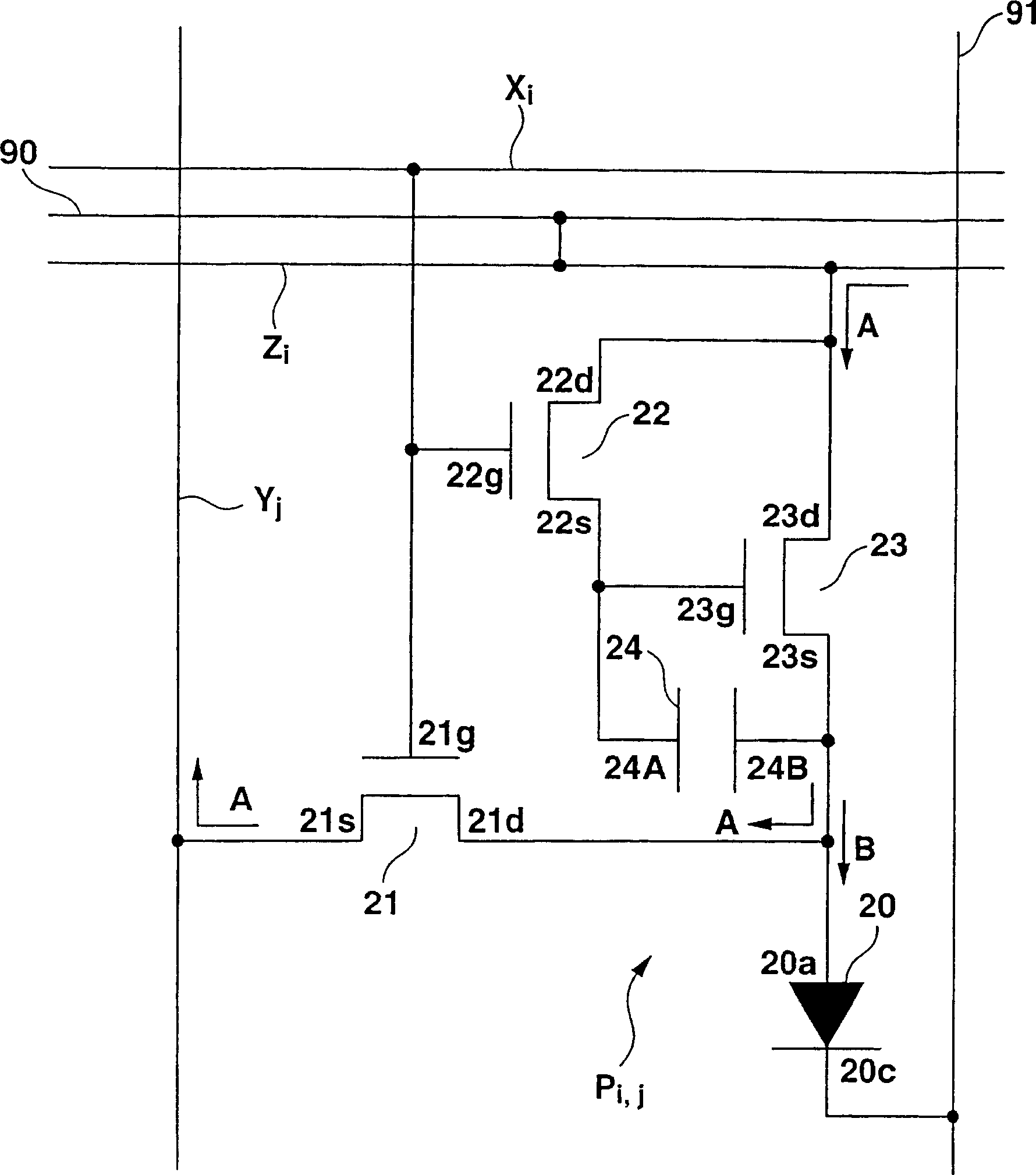

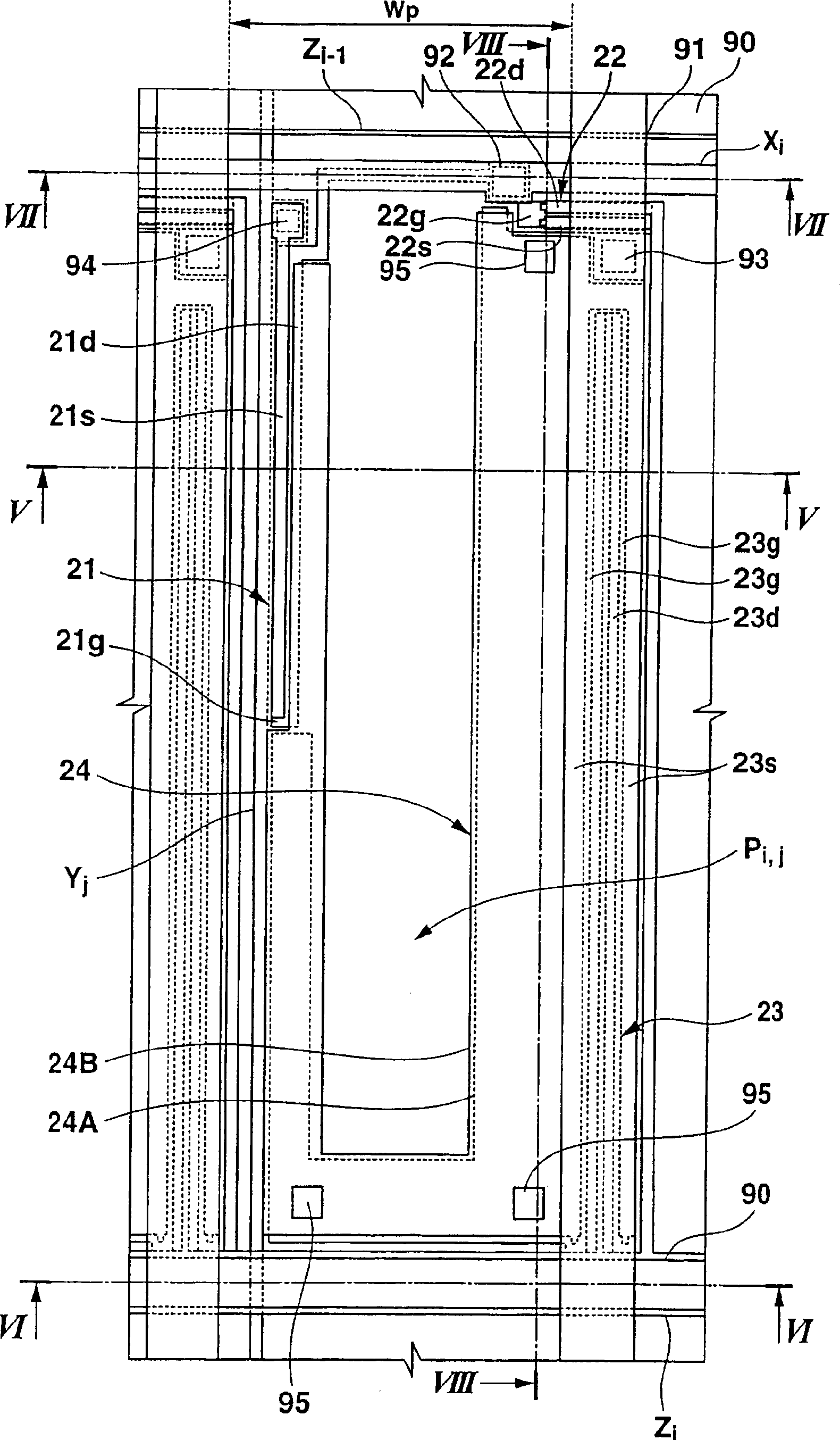

[0073] figure 1 A schematic diagram of an EL display panel 1 of an active matrix driving method is shown in . like figure 1 As shown, the EL display panel 1 has a light-transmitting flexible sheet-shaped or rigid plate-shaped insulating substrate 2; n (multiple) signal lines Y arranged parallel to each other on the insulating substrate 2 1 -Y n ; When looking down on the insulating substrate 2 and the signal line Y 1 -Y n m (multiple) scanning lines X arranged orthogonally on the insulating substrate 2 1 -X m ; at scan line X 1 -X m Between each and scan line X 1 ...

no. 2 Embodiment approach

[0189] [Overall configuration of EL display panel]

[0190] Figure 20 A schematic diagram of an EL display panel 1 of an active matrix driving method is shown in . like Figure 20 As shown, the EL display panel 1 has a light-transmitting flexible sheet-shaped or rigid plate-shaped insulating substrate 2; n (multiple) signal lines Y arranged parallel to each other on the insulating substrate 2 1 -Y n ; Insulating substrate 2, relative to signal line Y when viewed from above 1 -Y n m (multiple) scanning lines X arranged orthogonally on the insulating substrate 2 1 -X m ; at each scan line X 1 -X m Between and scan line X 1 -X m m (multiple) supply lines Z arranged in parallel and differently from each other on the insulating substrate 2 1 -Z m ; along signal line Y 1 -Y n and scanline X 1 -X m (m×n) groups of pixel circuits P arranged in a matrix on the insulating substrate 2 1,1 -P m,n ;connected to the supply line Z 1 -Z m And the signal line Y relative to...

Deformed example 1

[0243] In addition, the present invention is not limited to the above-described embodiments, and various improvements and design changes can be made without departing from the spirit of the present invention.

[0244] In addition, in the above-described embodiment, the transistors 21 to 23 have been described as N-channel type field effect transistors. Transistors 21-23 may also be P-channel type field effect transistors. At this time, at figure 2 In the circuit configuration of , the relationship between the sources 21s, 22s, and 23s of the transistors 21-23 and the drains 21d, 22d, and 23d of the transistors 21-23 is reversed. For example, when the driving transistor 23 is a P-channel type field effect transistor, the drain 23d of the driving transistor 23 is connected to the pixel electrode 20a of the organic EL element 20, and the source 23s is connected to the supply line Z. i conduction.

PUM

| Property | Measurement | Unit |

|---|---|---|

| Film thickness | aaaaa | aaaaa |

| Width | aaaaa | aaaaa |

| Resistivity | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More