Patents

Literature

254results about How to "Improve reference" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

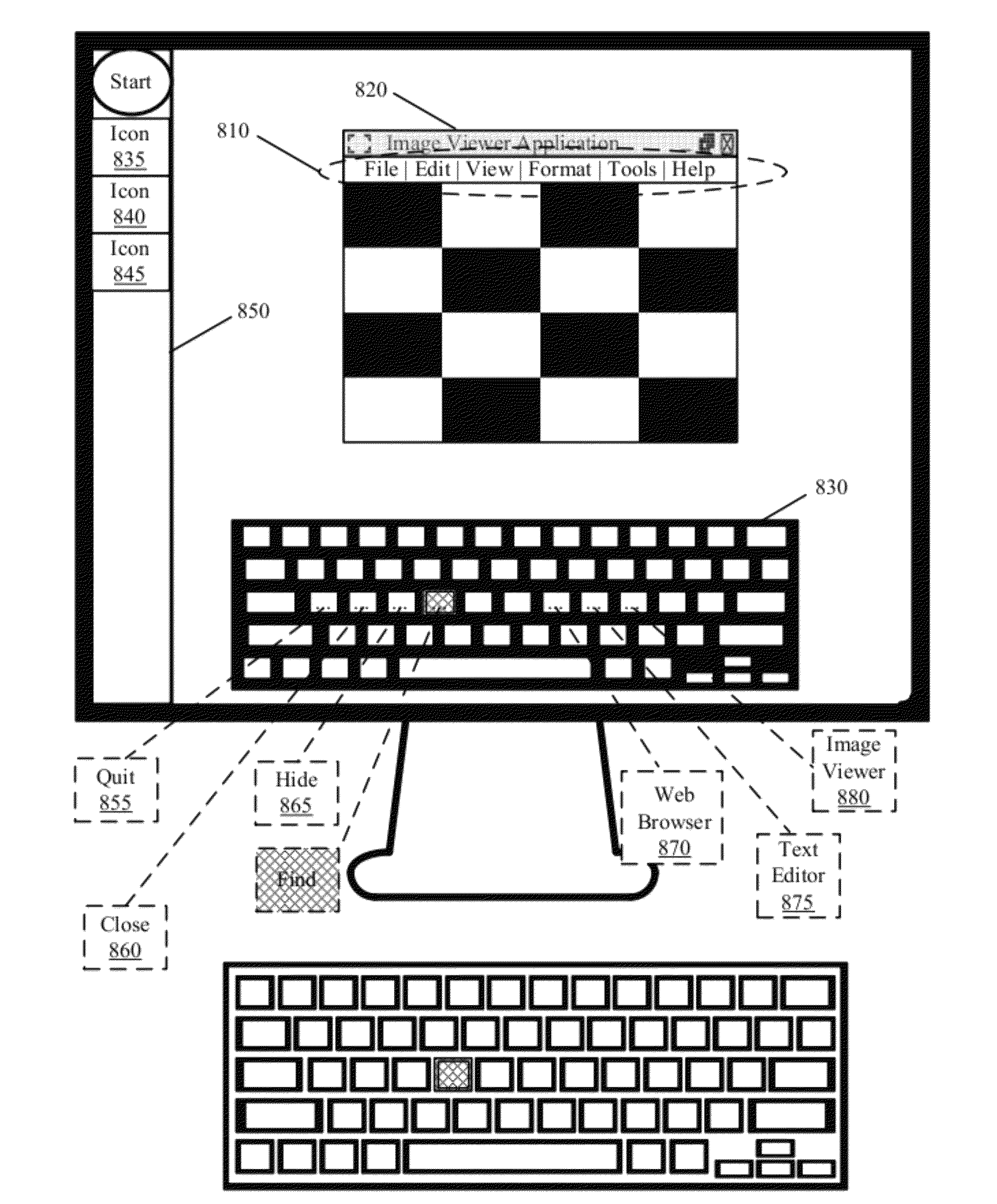

Input Device Enhanced Interface

ActiveUS20120235921A1Improve efficiencyIncreases expressivityInput/output for user-computer interactionCathode-ray tube indicatorsGraphicsOperation mode

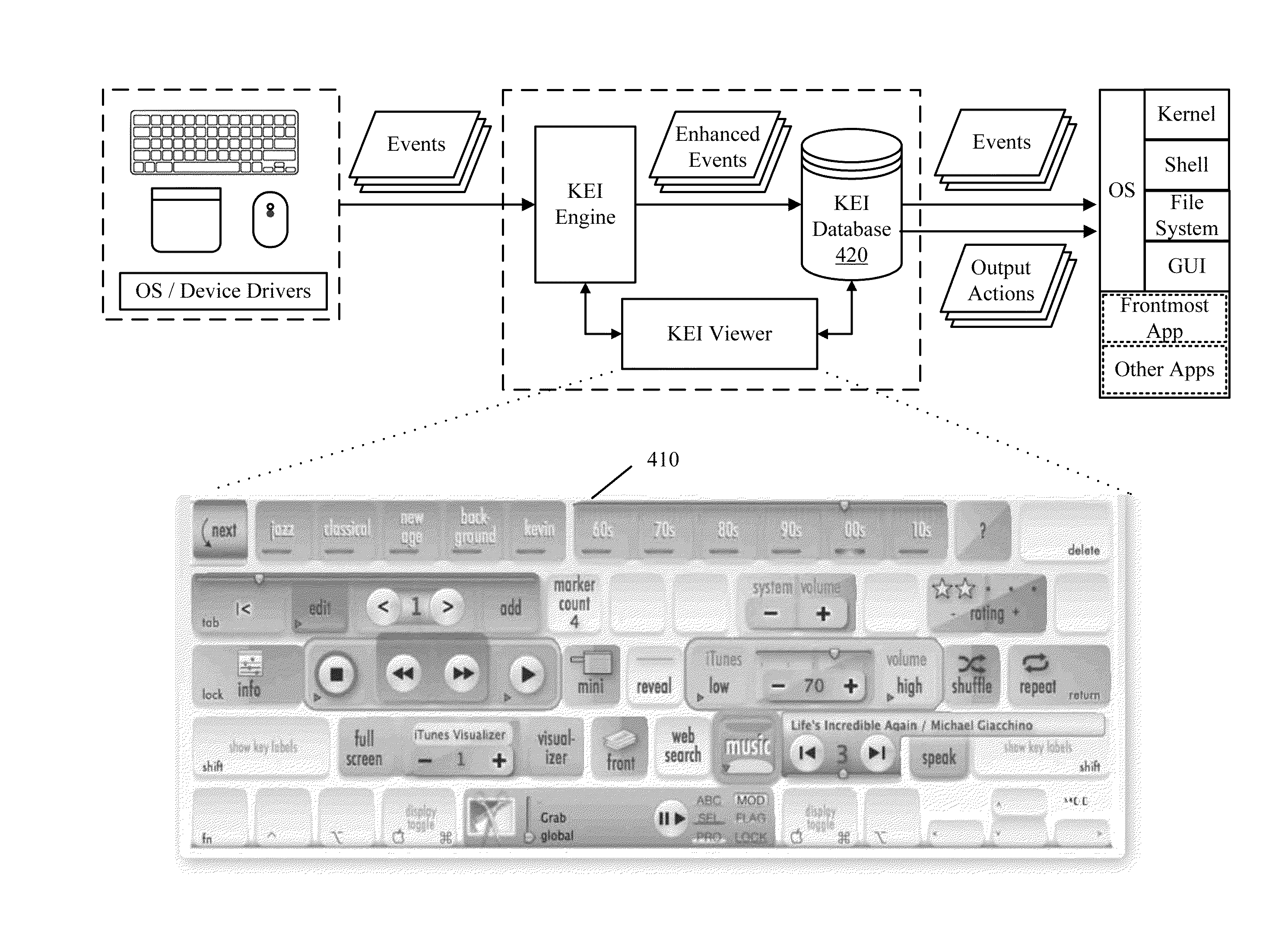

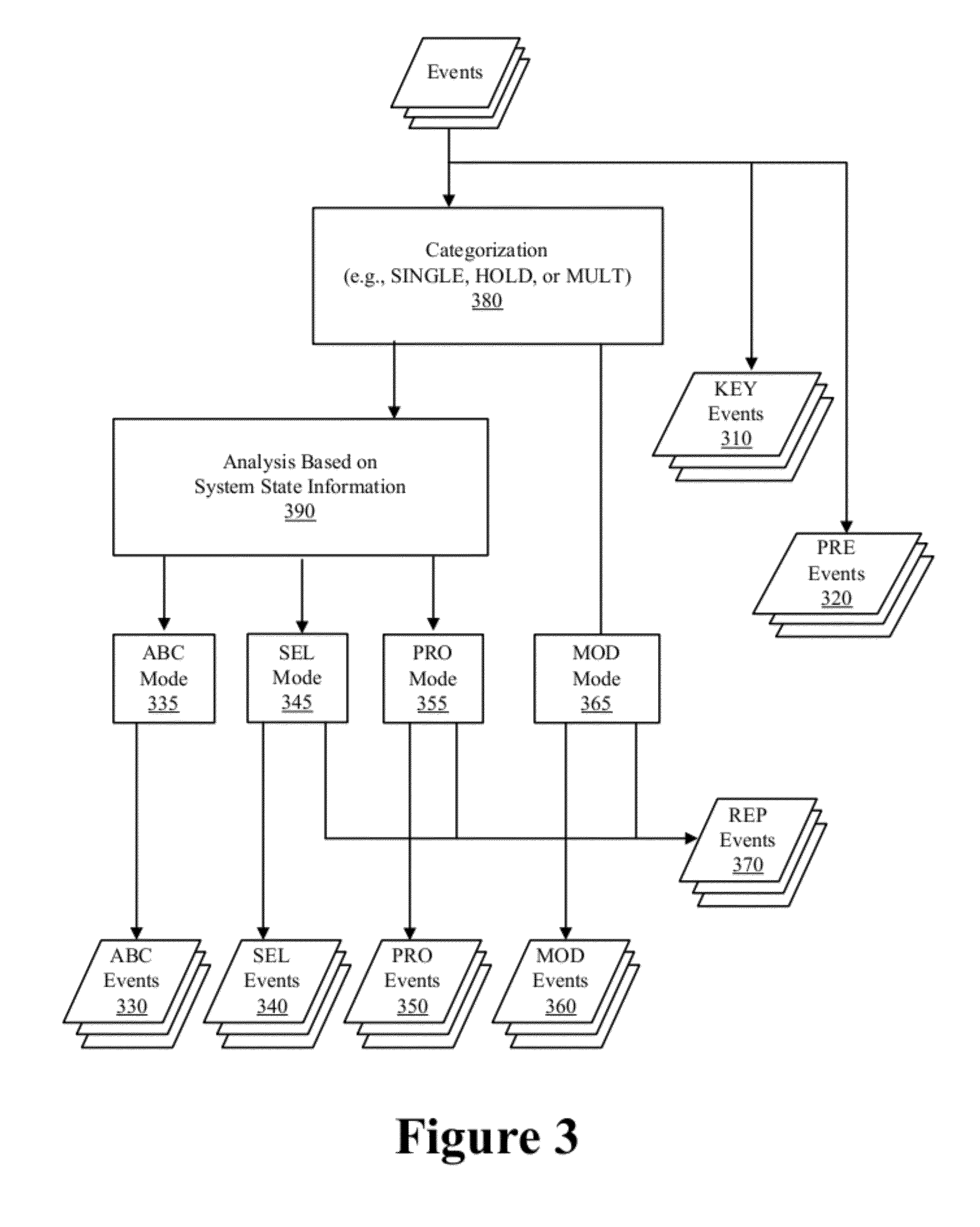

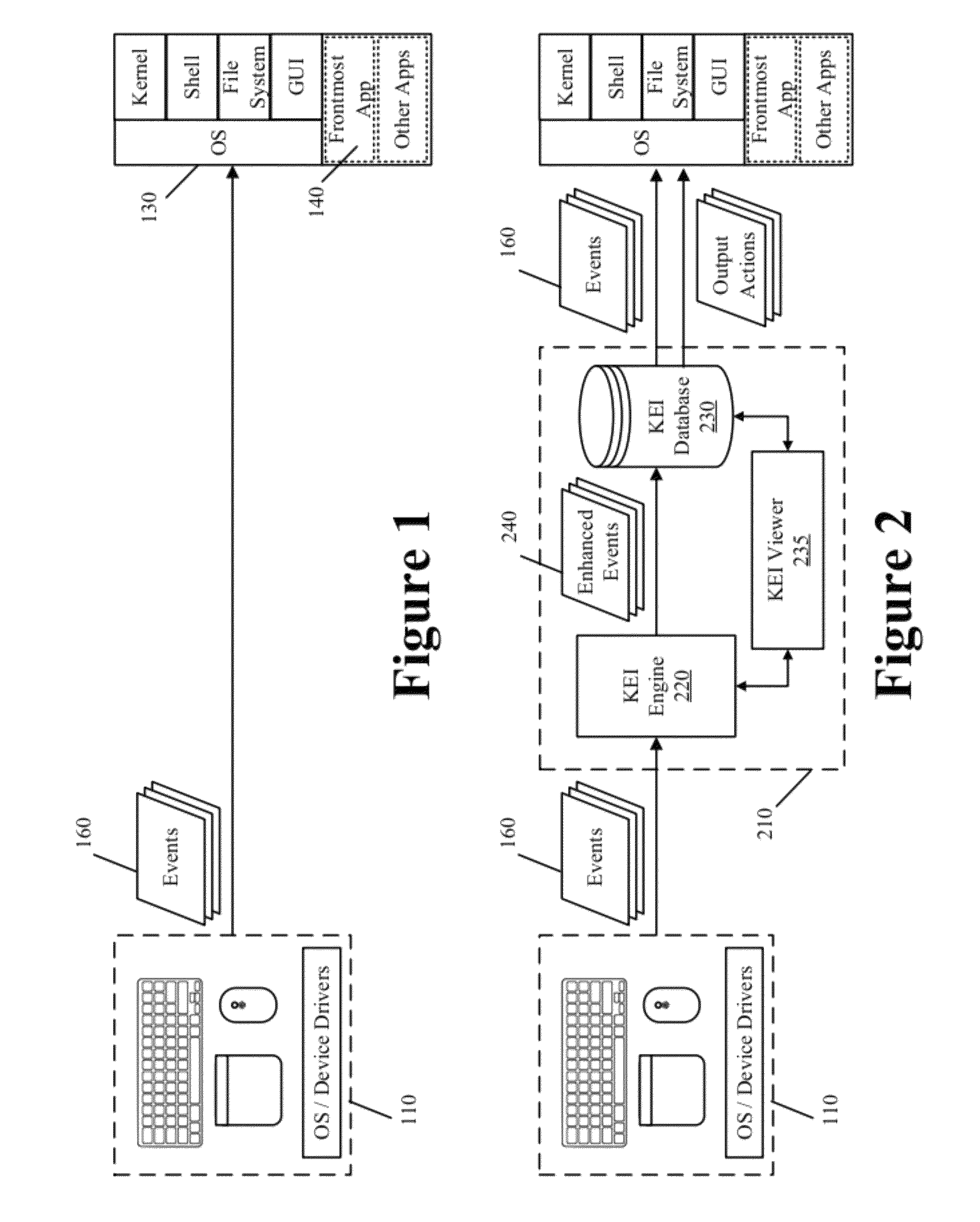

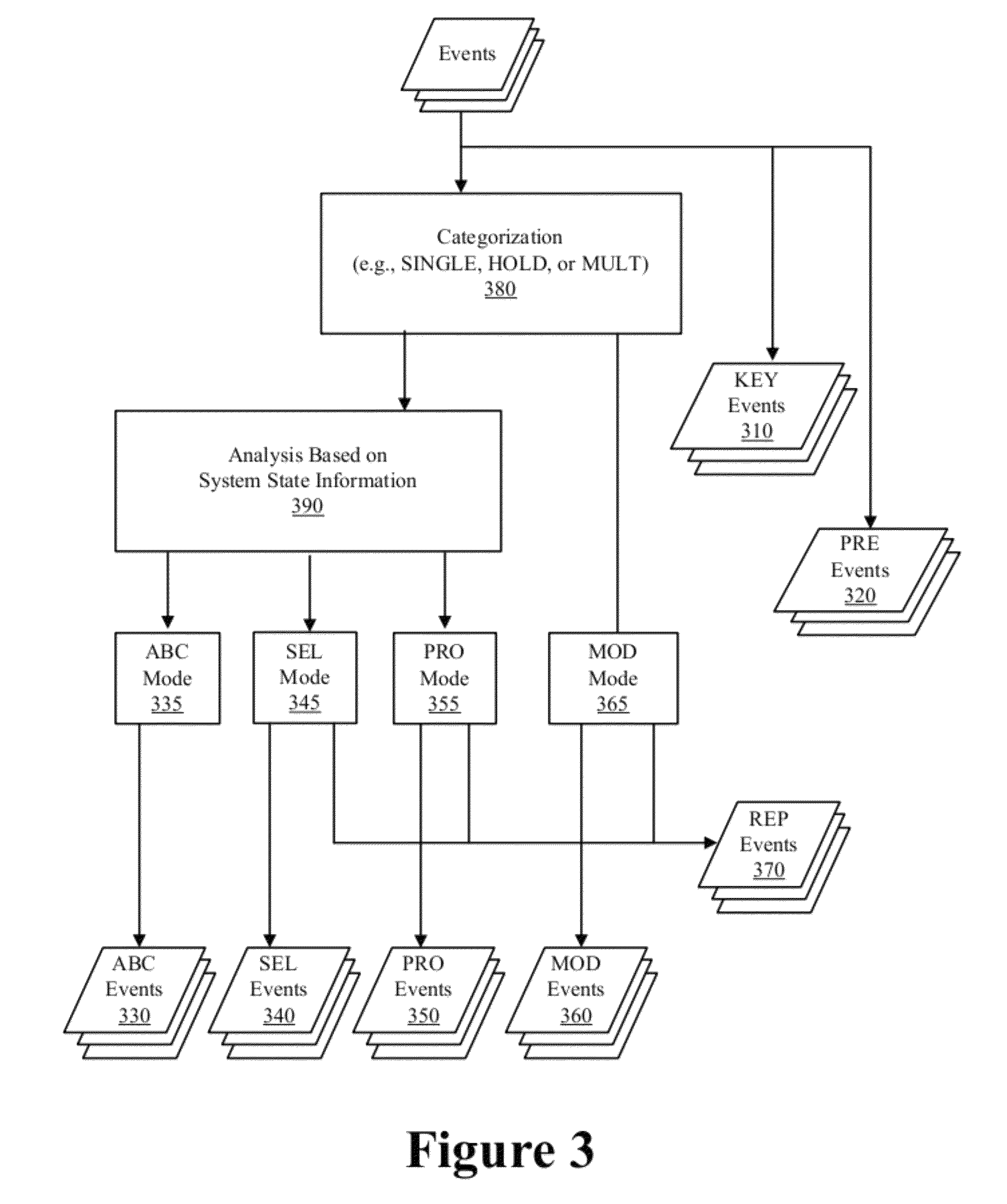

Some embodiments provide an interactive viewer for an input device interface. Specifically, some embodiments provide a Keyboard Enhanced Interface (KEI) system that includes a KEI viewer. The KEI viewer includes multiple graphical keys that correspond to keys of a key based input device. The KEI viewer also includes multiple symbols that identify different output actions and logic for presenting a set of symbols over a set of graphical keys to identify a set of keys of the key based input device that are usable to directly invoke a set of output actions based on an active operational mode of the KEI system. A symbol identifies a particular output action that is directly invocable with a press of a key of the key based input device that corresponds to a graphical key over which said symbol is presented.

Owner:INTELLITACT

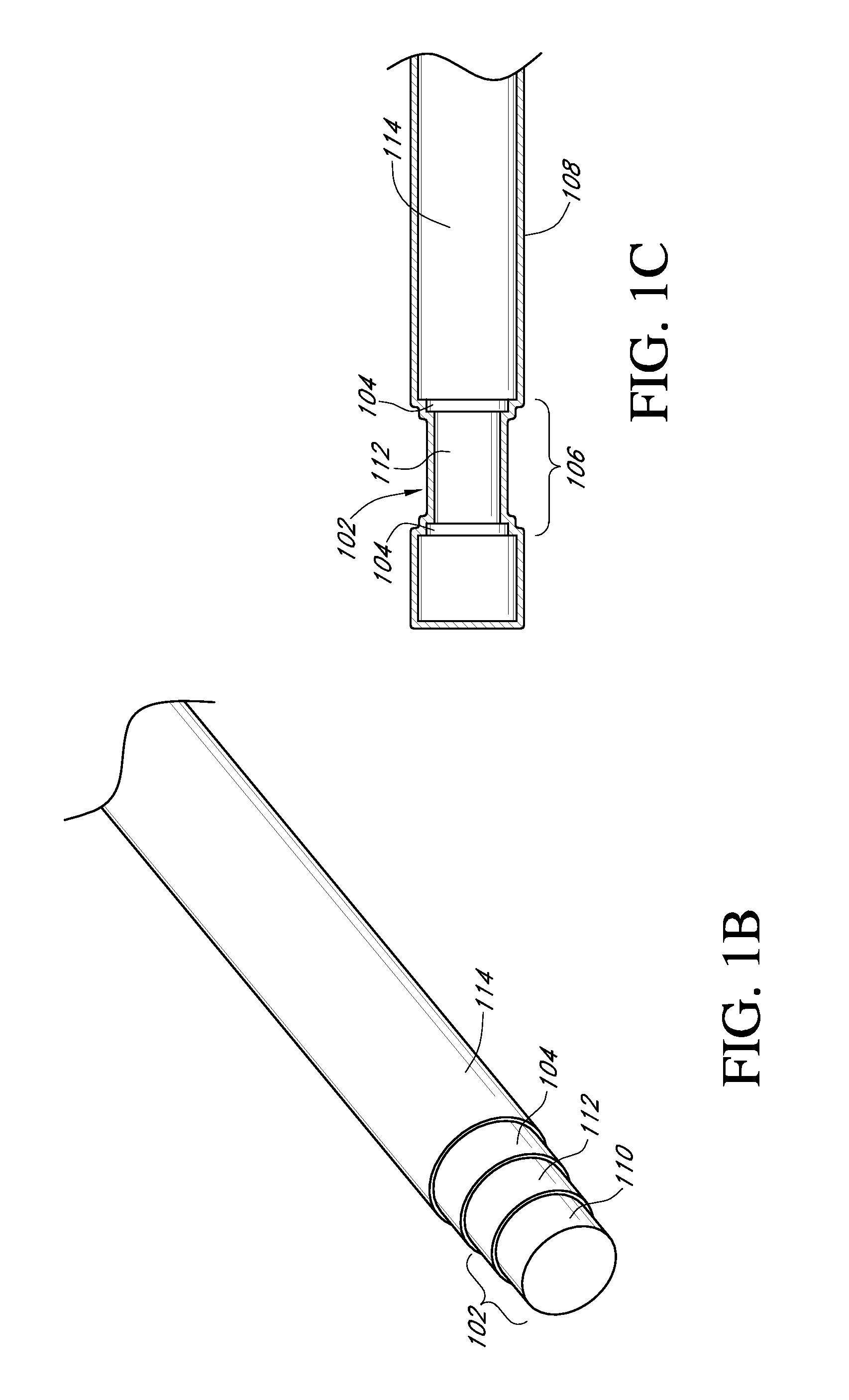

Analyte sensor with increased reference capacity

ActiveUS20130245412A1Reference capacity of reference is increasedImprove referenceCatheterSensorsElectrochemical gas sensorAnalyte

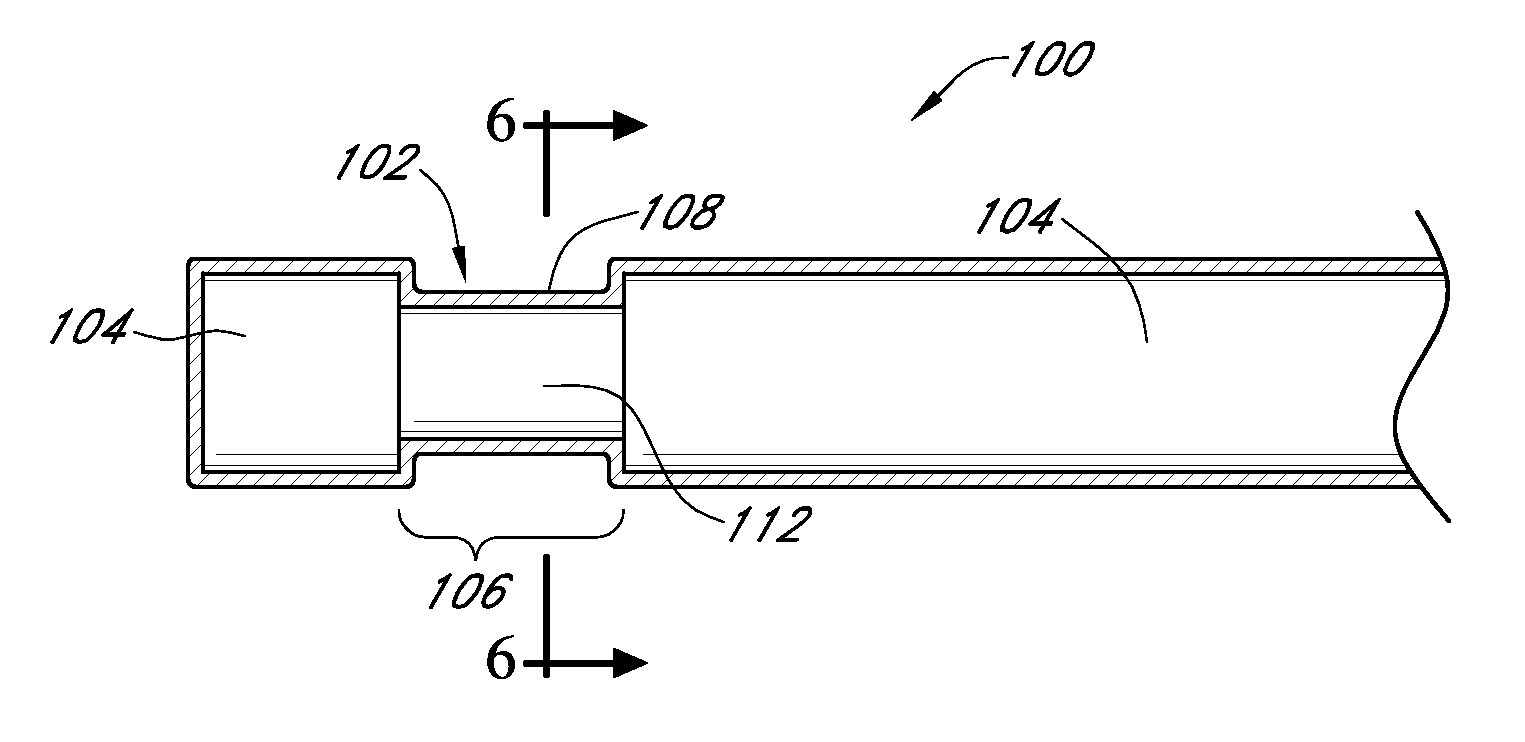

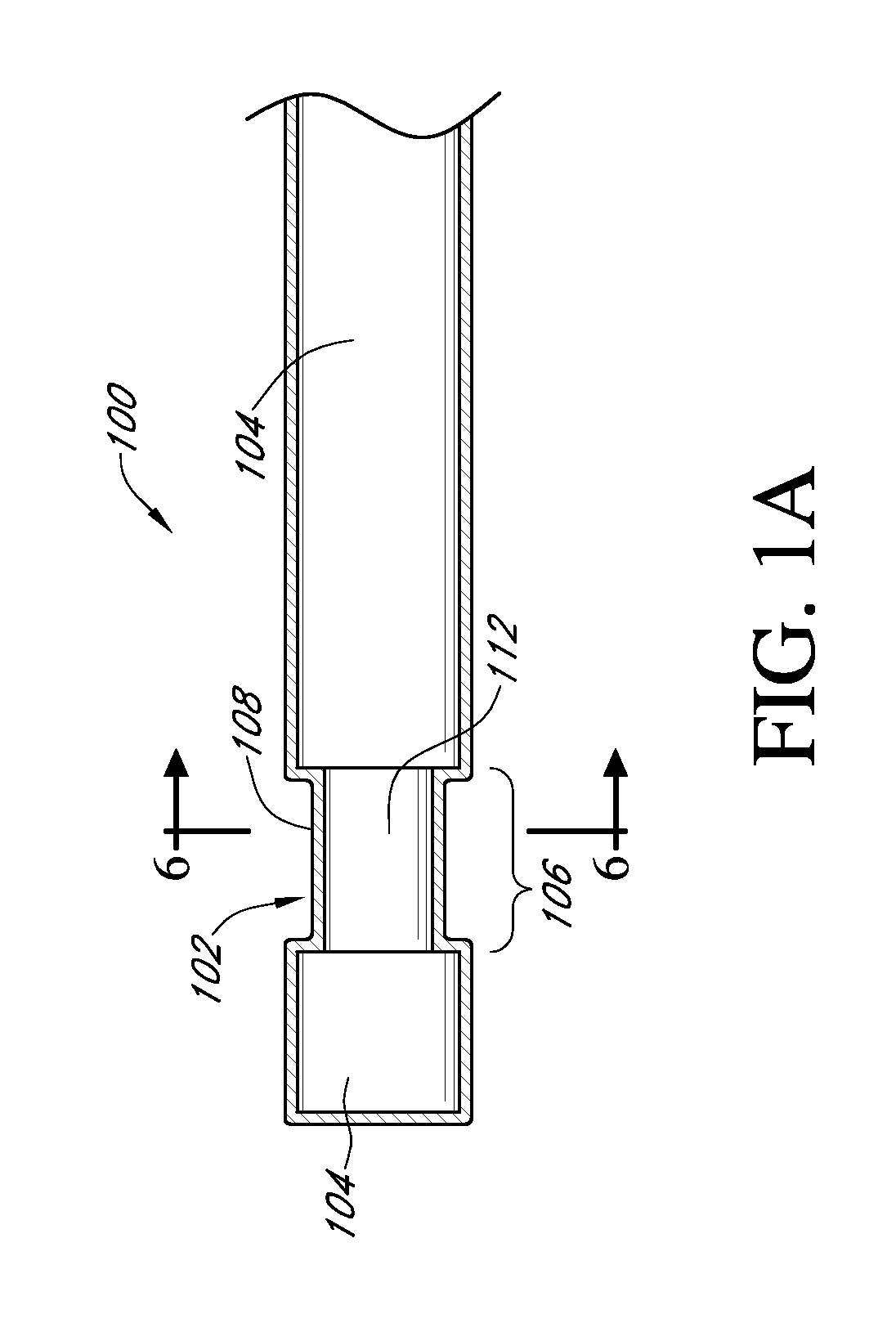

Systems and methods of use for continuous analyte measurement of a host's vascular system are provided. In some embodiments, a continuous glucose measurement system includes an electrochemical sensor incorporating a silver / silver chloride reference electrode, wherein a capacity of the reference electrode is controlled.

Owner:DEXCOM

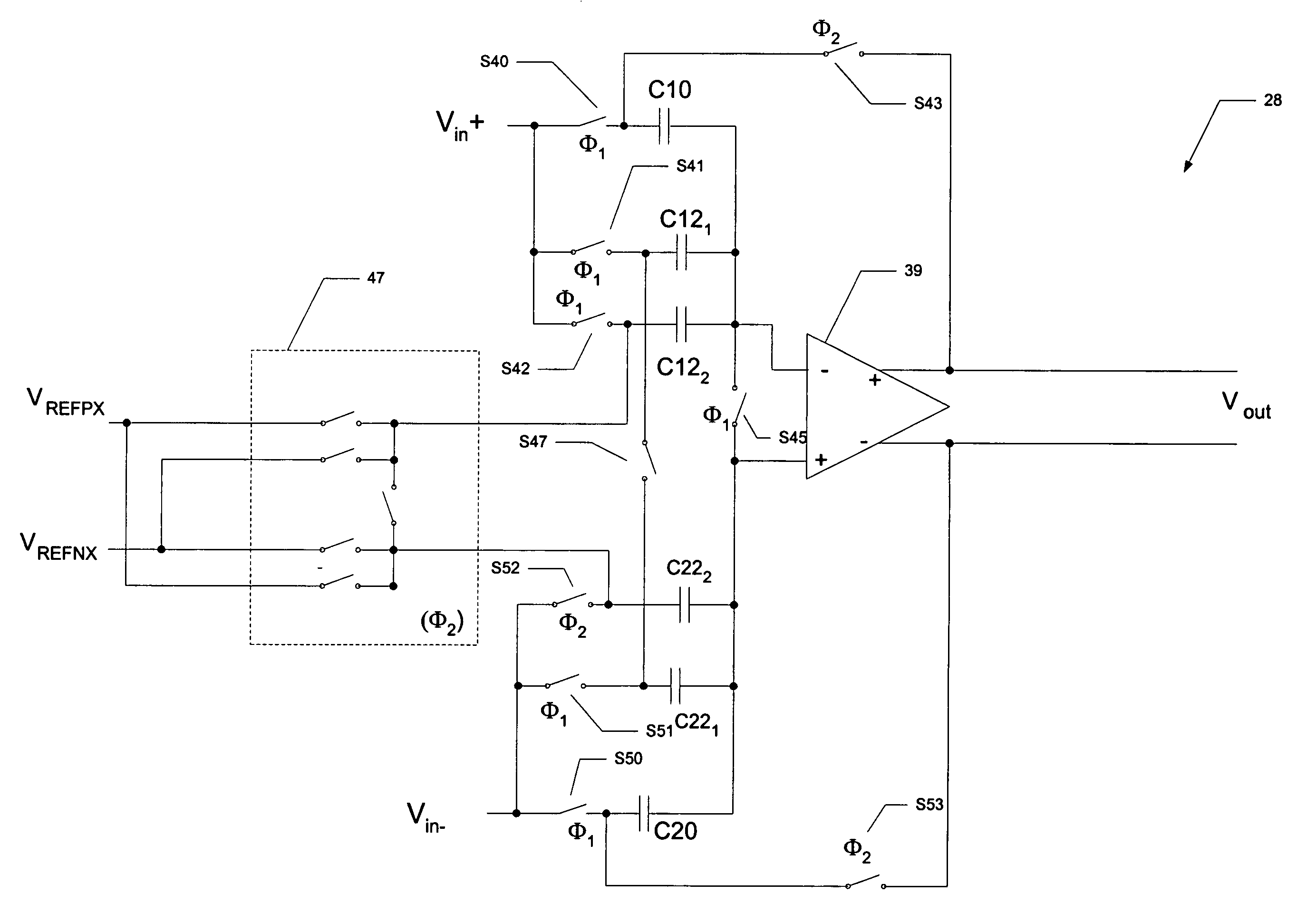

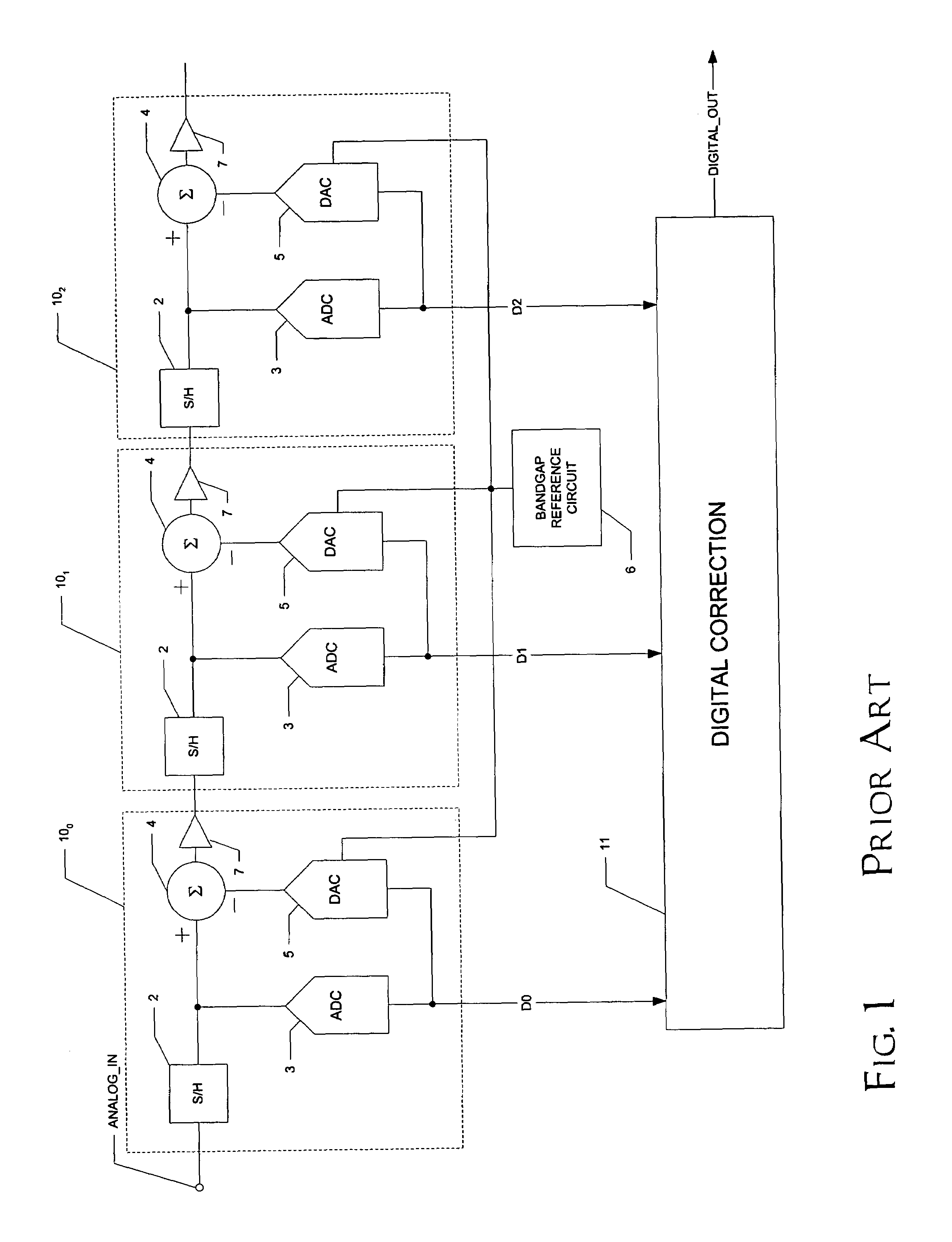

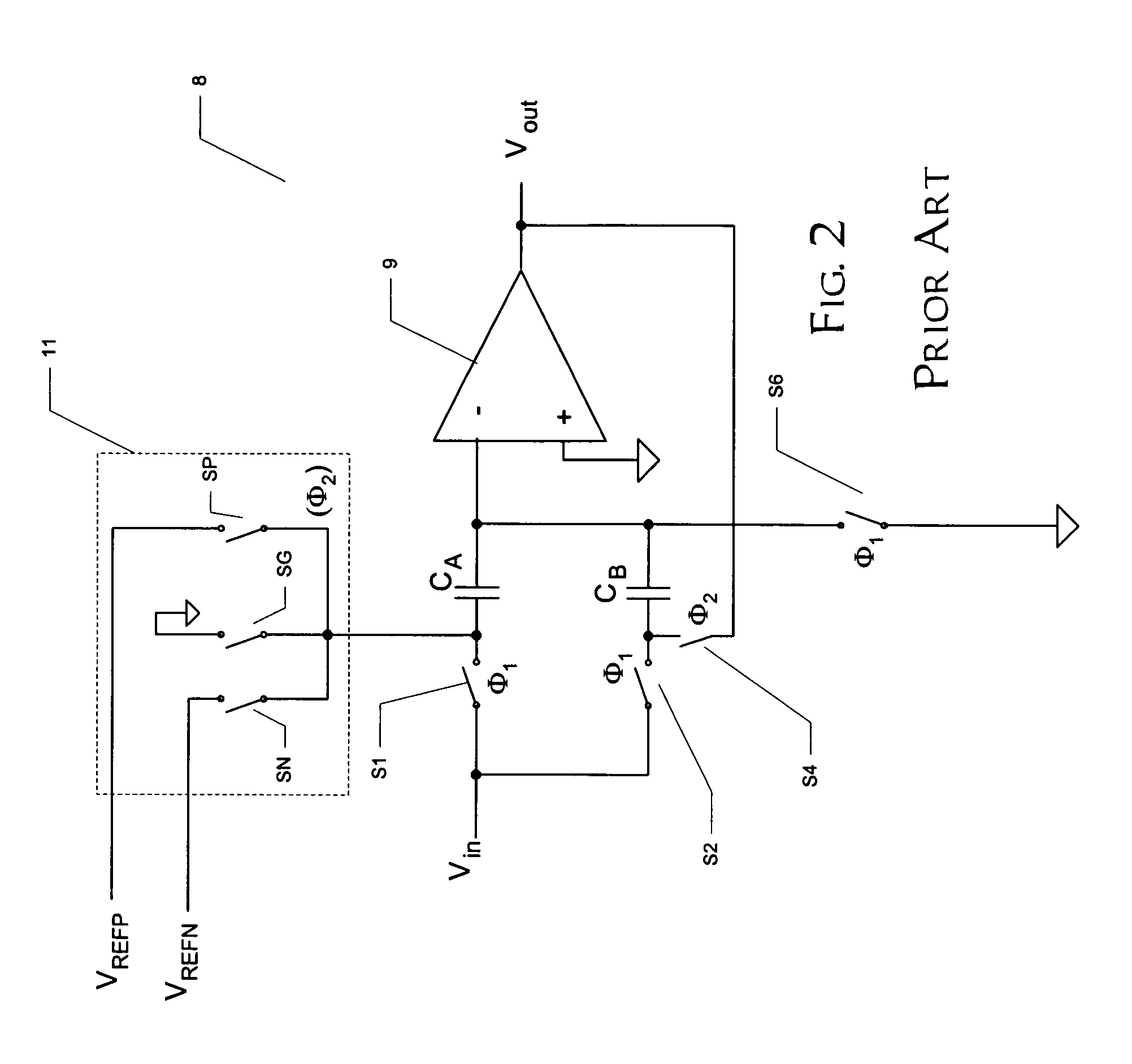

Switched-capacitor circuit with scaled reference voltage

ActiveUS7009549B1Improve precisionImprove stabilityElectric signal transmission systemsAnalogue-digital convertersCapacitanceAudio power amplifier

A pipelined analog-to-digital converter (ADC) (30) with improved precision is disclosed. The pipelined ADC (30) includes a sequence of stages (20), each of which includes a sample-and-hold circuit (22), an analog-to-digital converter (23), and the functions of a digital-to-analog converter (DAC) (25), an adder (24), and a gain stage (27) at which a residue signal (RES) is generated for application to the next stage (20) in the sequence. A multiplying DAC (28) performs the functions of the DAC (25), adder (24), and gain stage (27) in the stage (20), and is based on an operational amplifier (29). Sample capacitors (C10, C20) and reference capacitors (C122, C222) receive the analog input from the sample-and-hold circuit (22) in a sample phase; parallel capacitors (C121, C221) are provided to maintain constant circuit gain. Extended reference voltages (VREFPX, VREFNX) at levels that exceed the output range (V0+, V0−) of the operational amplifier (29) are applied to the reference capacitors, in response to the digital output of the analog-to-digital converter (23) in its stage (20). The reference capacitors (C12, C22) are scaled according to the extent to which the extended reference voltages (VREFPX, VREFNX) exceed the op amp output levels (V0+, V0−). The effects of noise on the reference voltages (VREFPX, VREFNX) on the residue signal (RES) are thus greatly reduced.

Owner:TEXAS INSTR INC

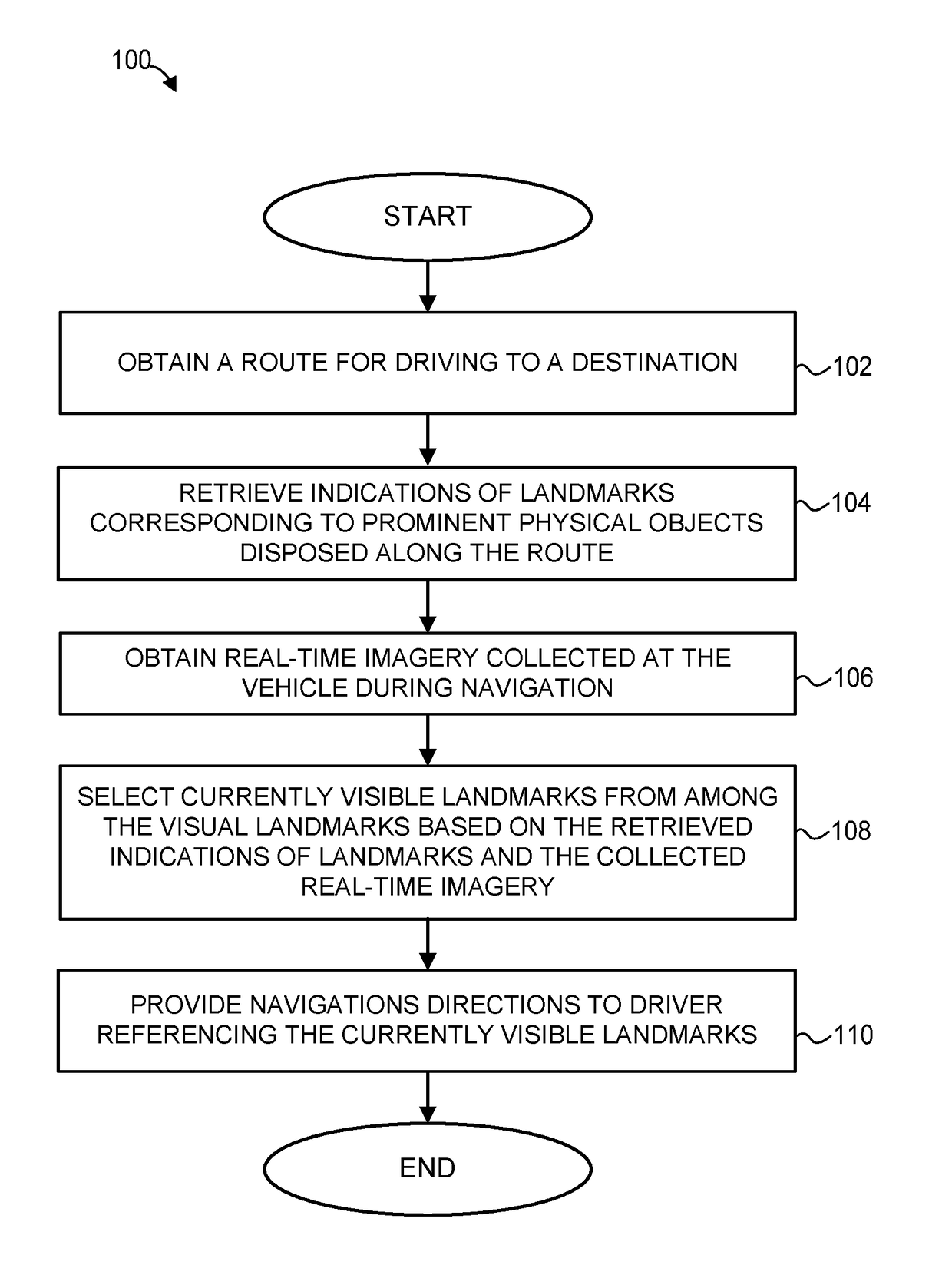

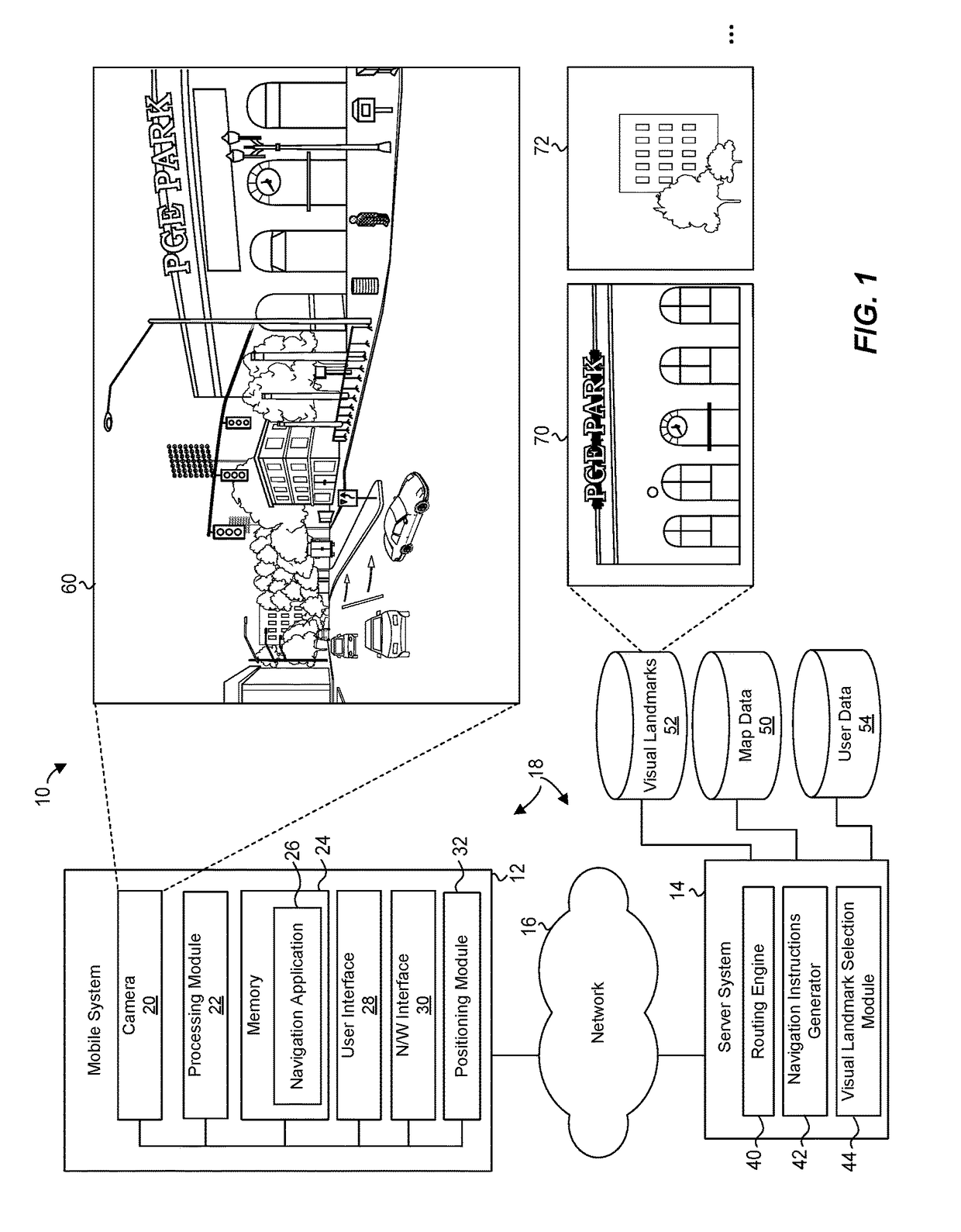

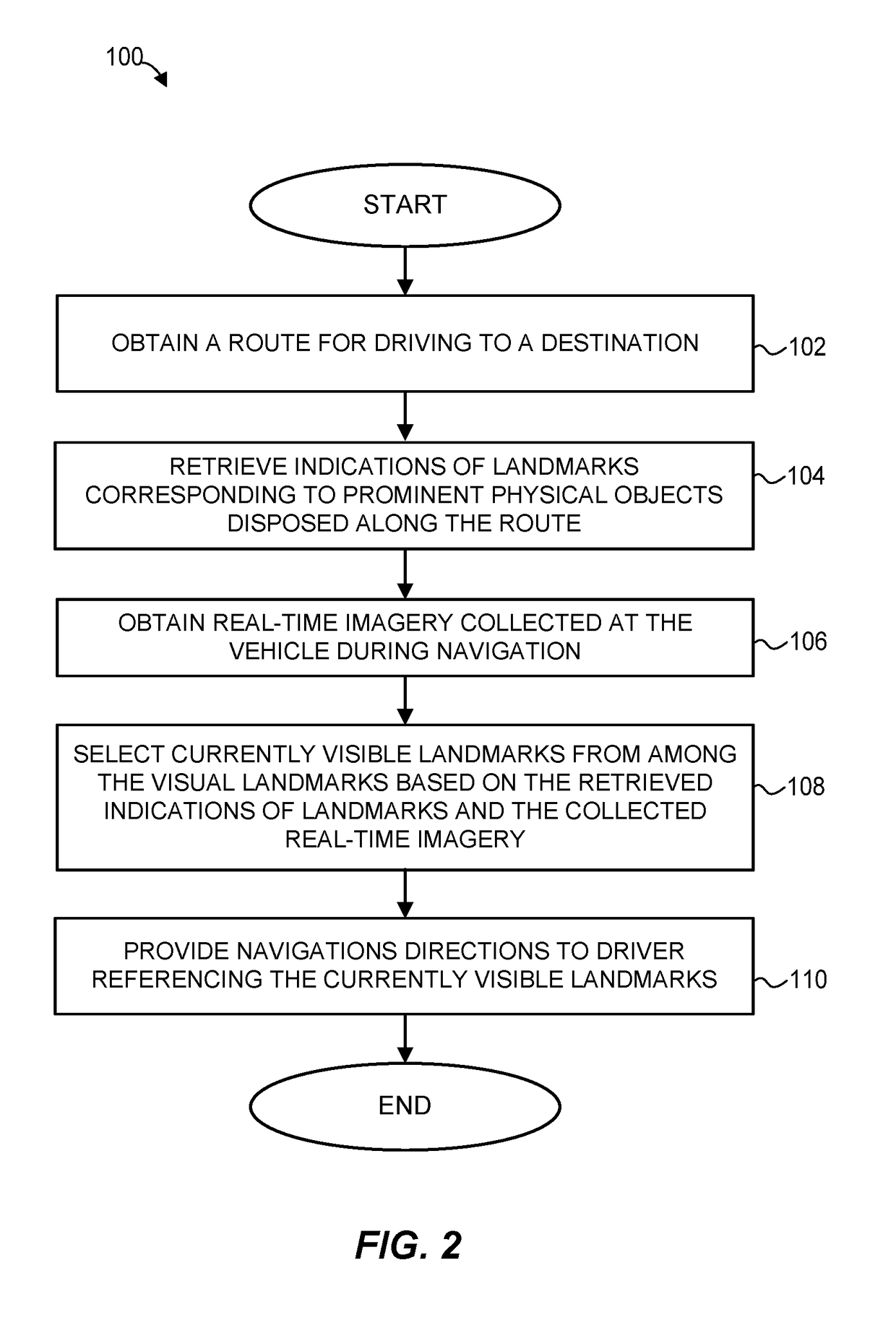

Systems and Methods for Using Real-Time Imagery in Navigation

ActiveUS20170314954A1Improve referenceInstruments for road network navigationRoad vehicles traffic controlDriver/operatorVisual landmarks

To generate navigation directions for a driver of a vehicle, a route for guiding the driver to a destination is obtained, visual landmarks corresponding to prominent physical objects disposed along the route are retrieved, and real-time imagery is collected at the vehicle approximately from a vantage point of the driver during navigation along the route. Using (i) the retrieved visual landmarks and (ii) the imagery collected at the vehicle, a subset of the visual landmarks that are currently visible to the driver is selected. Navigation directions describing the route are provided the driver, the navigation directions referencing the selected subset of the visual landmarks and excluding the remaining visual landmarks.

Owner:GOOGLE LLC

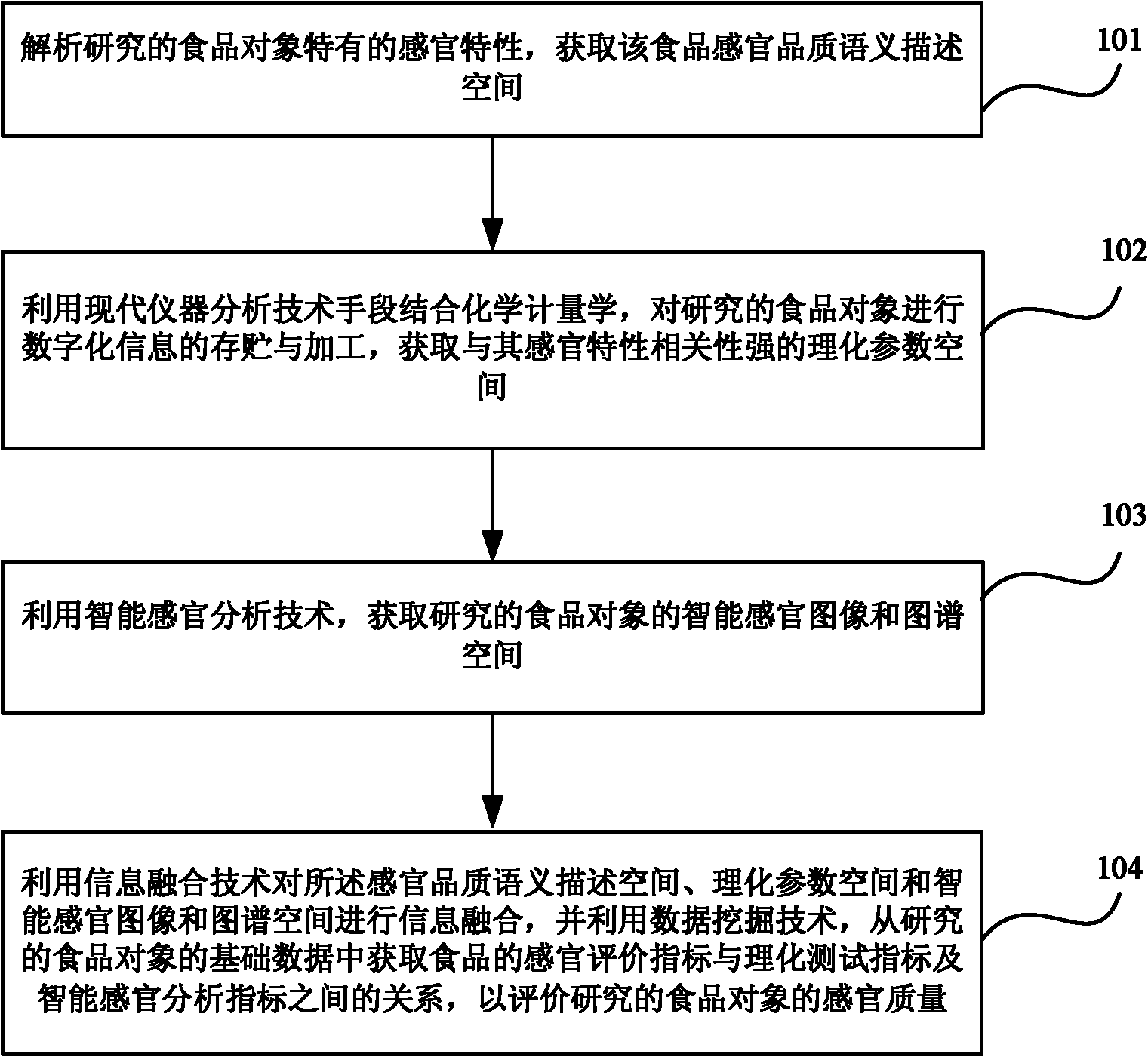

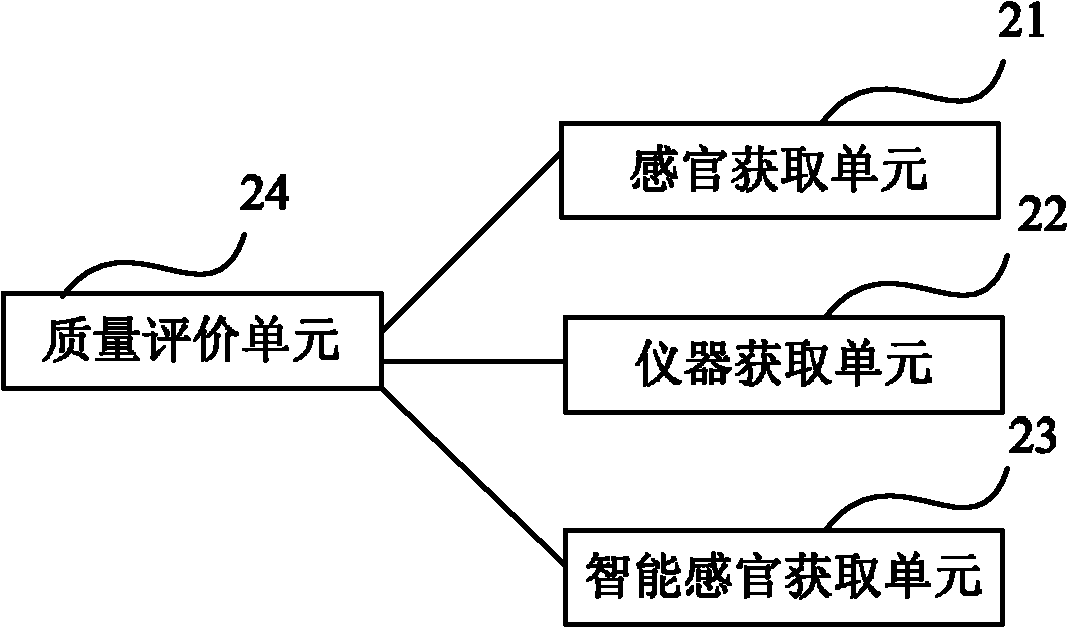

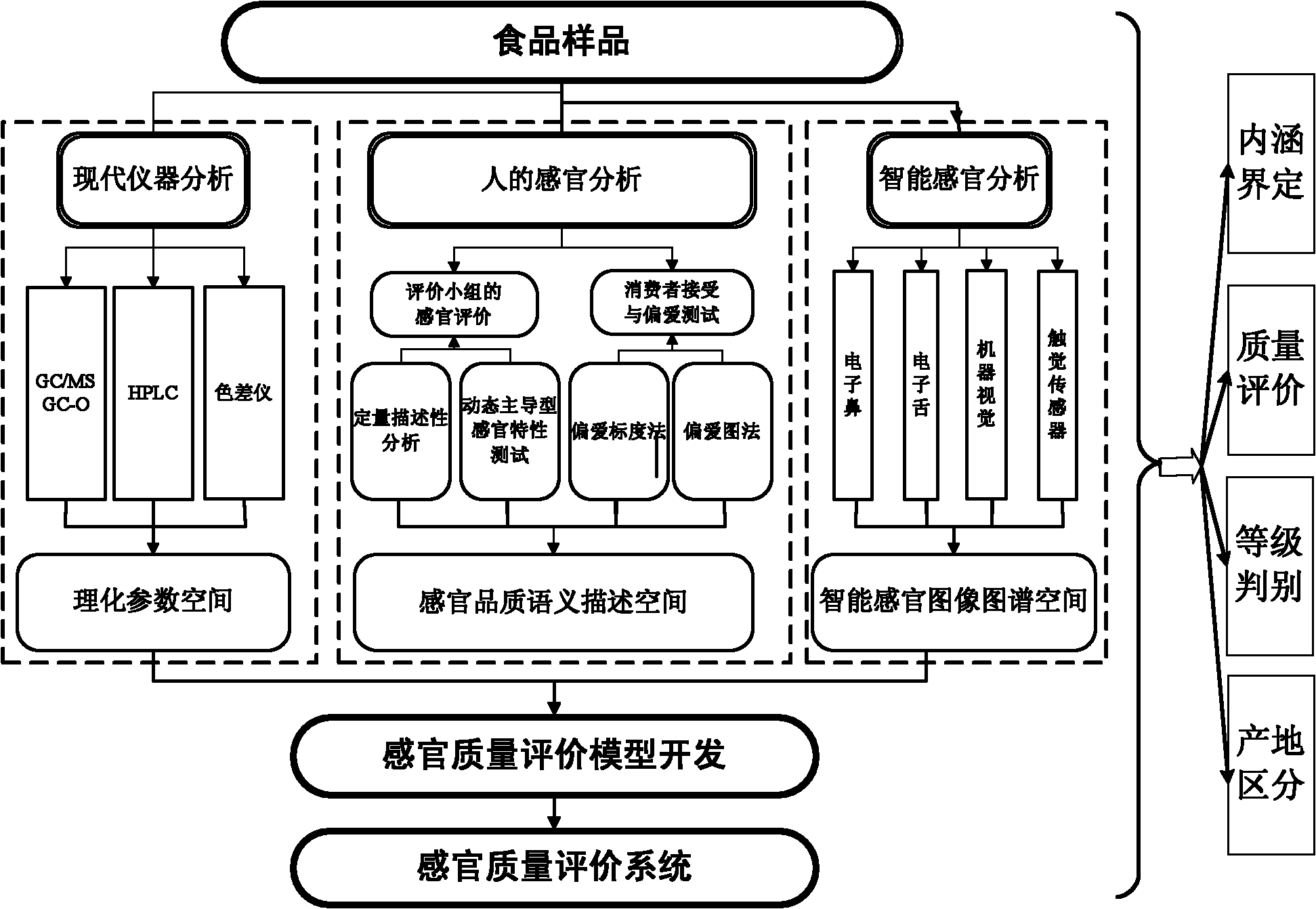

Food sensory quality evaluation method and system thereof

InactiveCN102222164AImprove objectivity and precisionHigh versatility and referenceComponent separationColor/spectral properties measurementsSensory analysisChemometrics

The invention provides a food sensory quality evaluation method and a system thereof. The method comprises the following steps: analyzing the special sensory characteristics of a food object to be researched to obtain a food sensory quality semantic description space; utilizing a modern instrument analyzing technical means combined with chemometrics to carry out storage and processing with digital information to the food object to be researched so as to obtain a food physicochemical parameter space; utilizing an intelligent sensory analysis technology to obtain an intelligent sensor image and a map space of the food object to be researched; utilizing an information fusion technology to carry out information fusion to the food sensory quality semantic description space, the food physicochemical parameter space, the intelligent sensor image and the map space; and utilizing a data mining technology to obtain the relationship between a sensory evaluation index, a physicochemical testing index and an intelligent sensory analysis index from basic data of the food object to be researched so as to evaluate the sensory quality of the food object to be researched. The invention can improve the objectivity and the accuracy of the food sensory quality evaluation.

Owner:CHINA NAT INST OF STANDARDIZATION

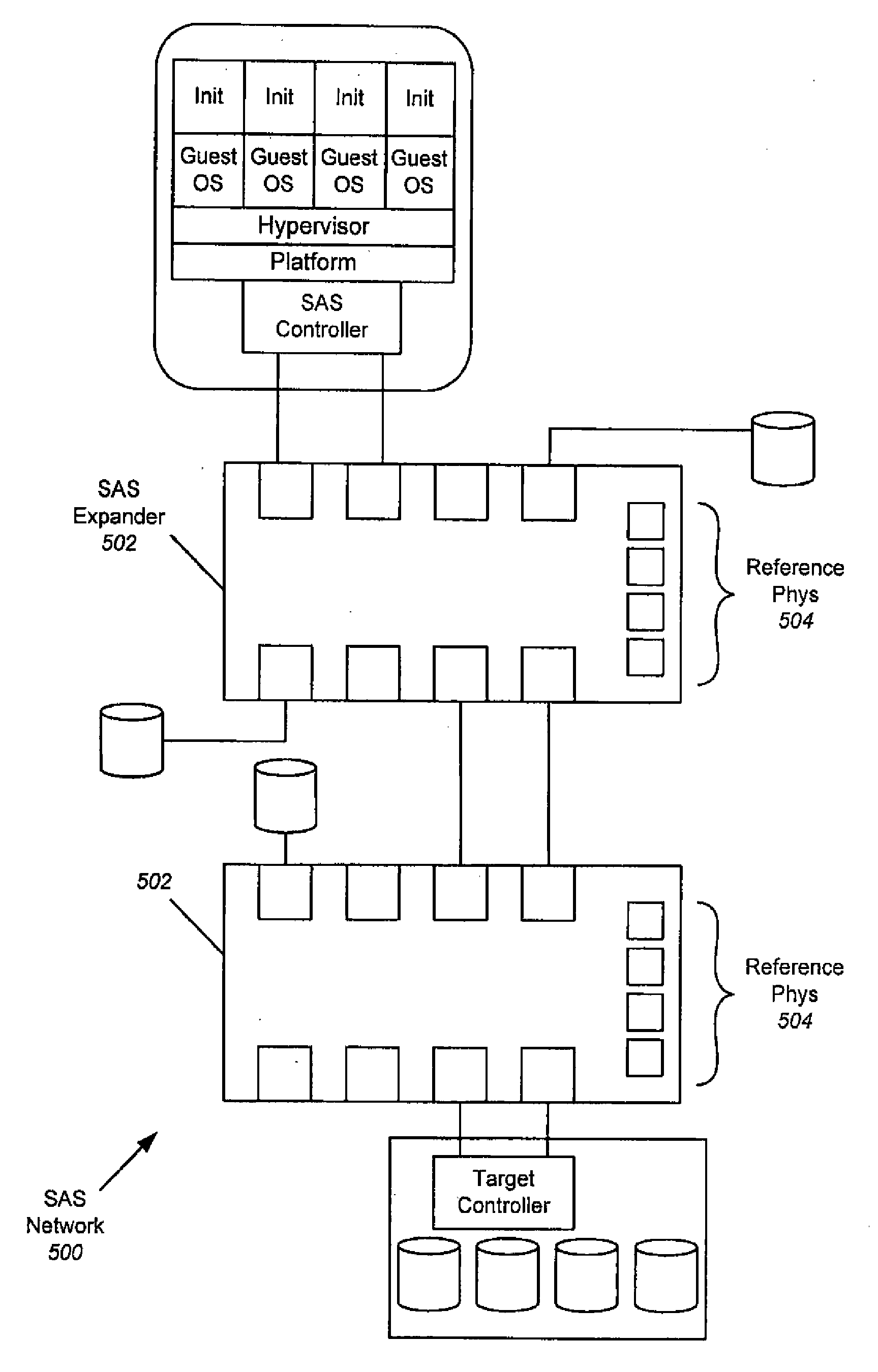

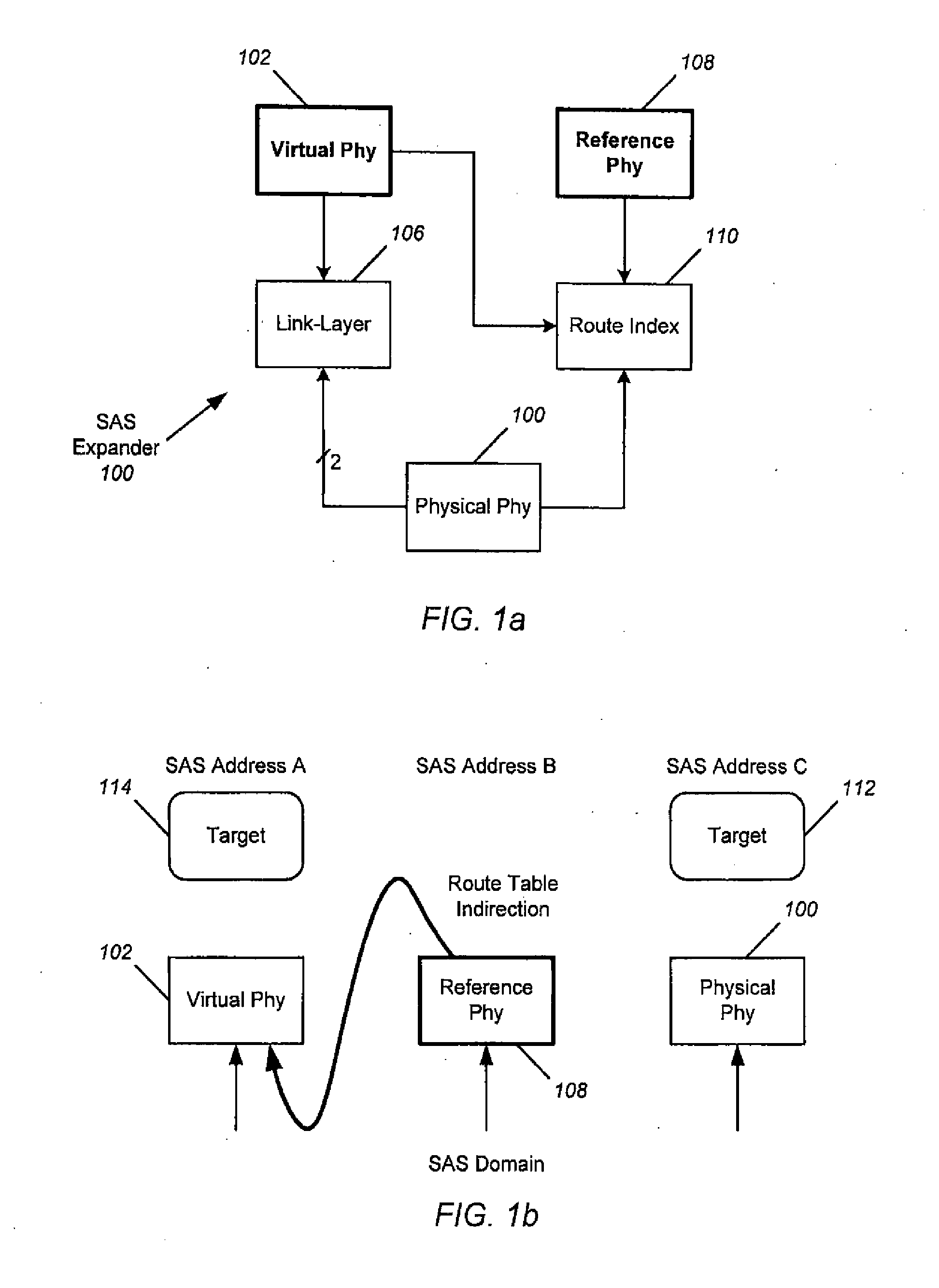

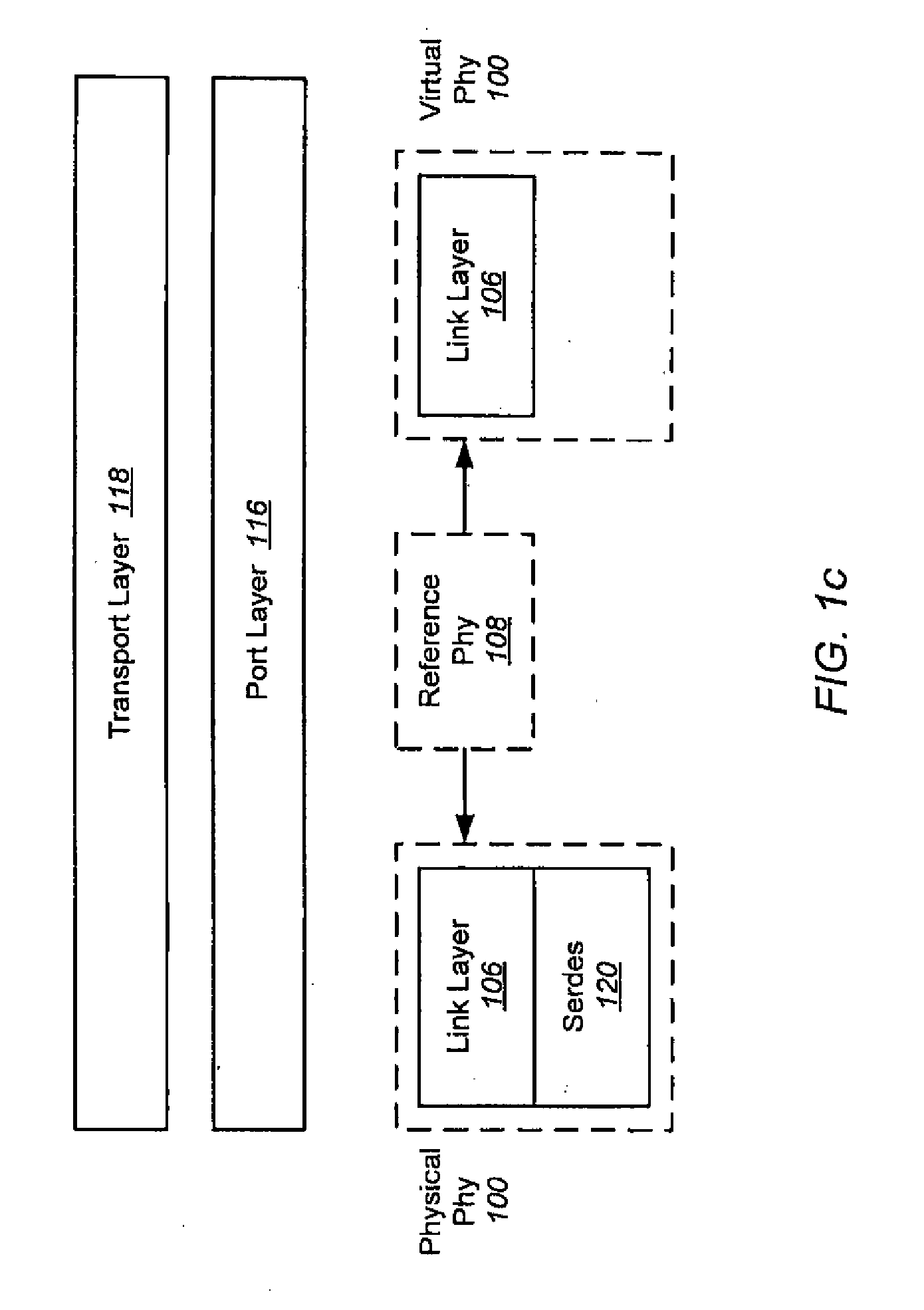

SAS reference Phys for virtualization and traffic isolation

InactiveUS20090150643A1Reduce in quantityIncreased address spaceMemory adressing/allocation/relocationTransmissionVirtualizationRouting table

Enabling virtualization in a SAS expander is disclosed. For each SAS address to be virtualized through one or more physical or virtual Phy, a reference Phy associated with each SAS address is created within the expander. Next, a route table is generated that includes an entry for each of the SAS addresses being virtualized, each entry associated with one or more of the physical or virtual Phy through which the SAS address is being virtualized. With the route table so established, requests for a virtualized SAS address are routed to a particular one of the one or more physical or virtual Phy associated with the virtualized SAS address in the route table.

Owner:AVAGO TECH INT SALES PTE LTD

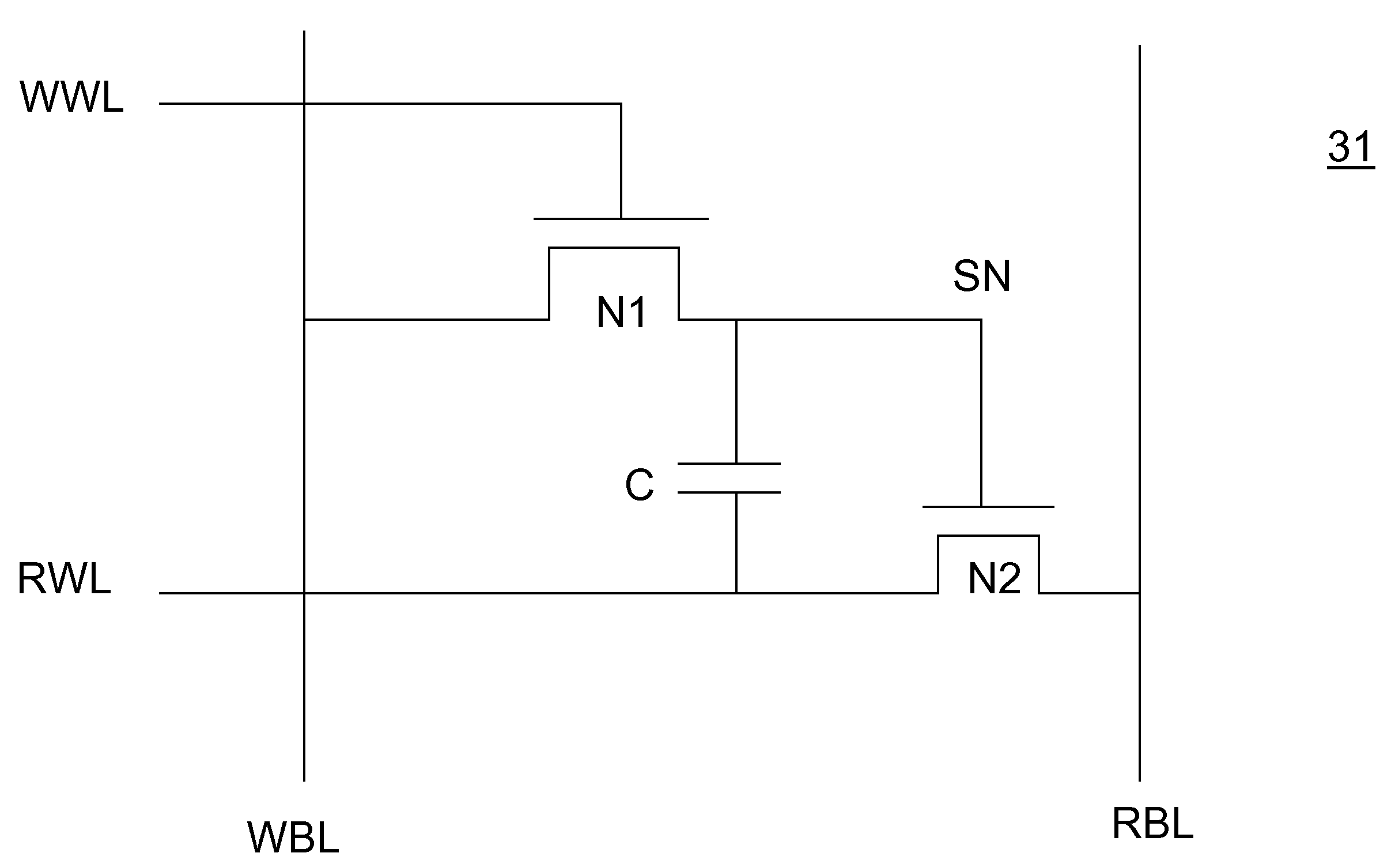

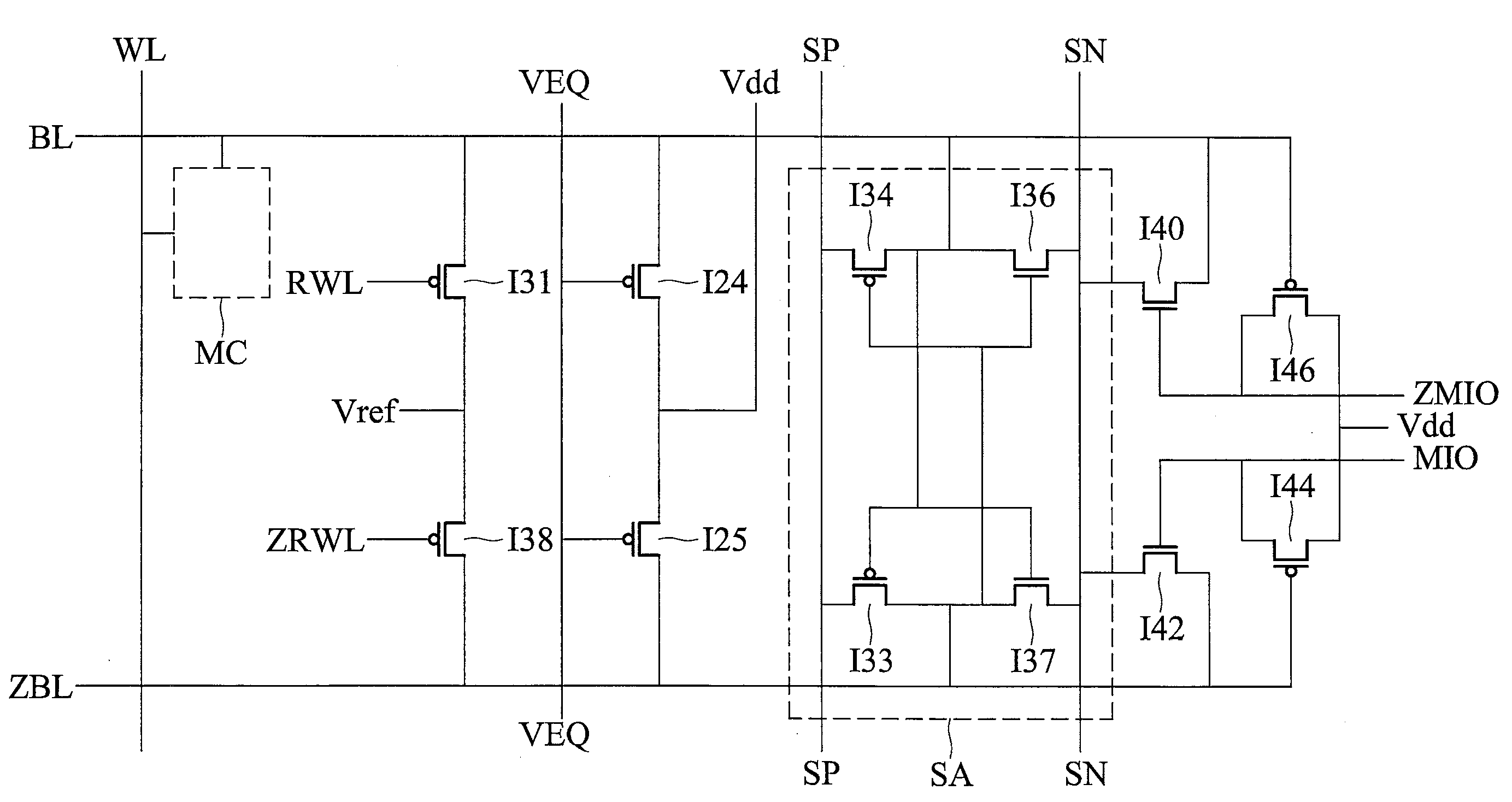

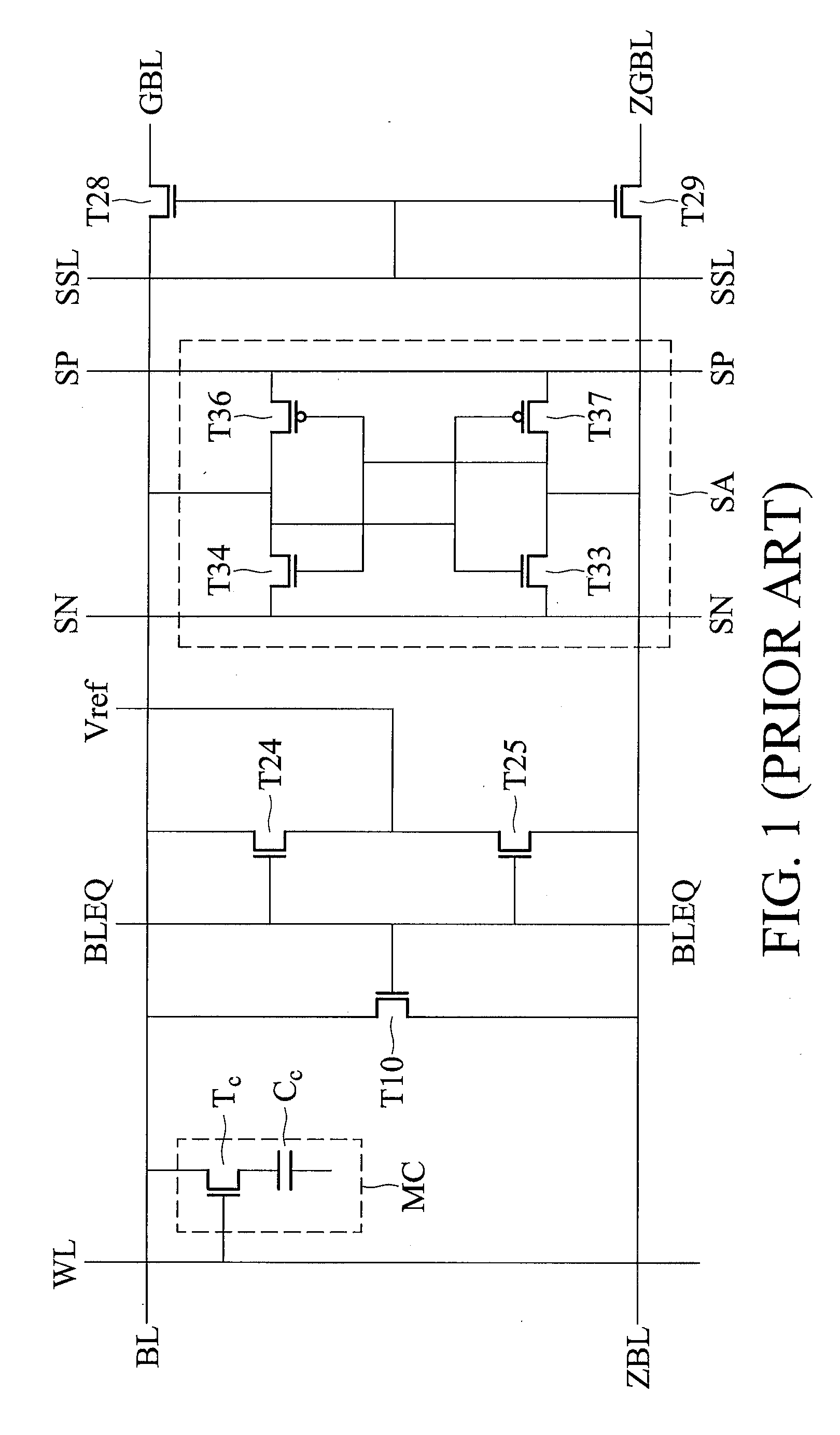

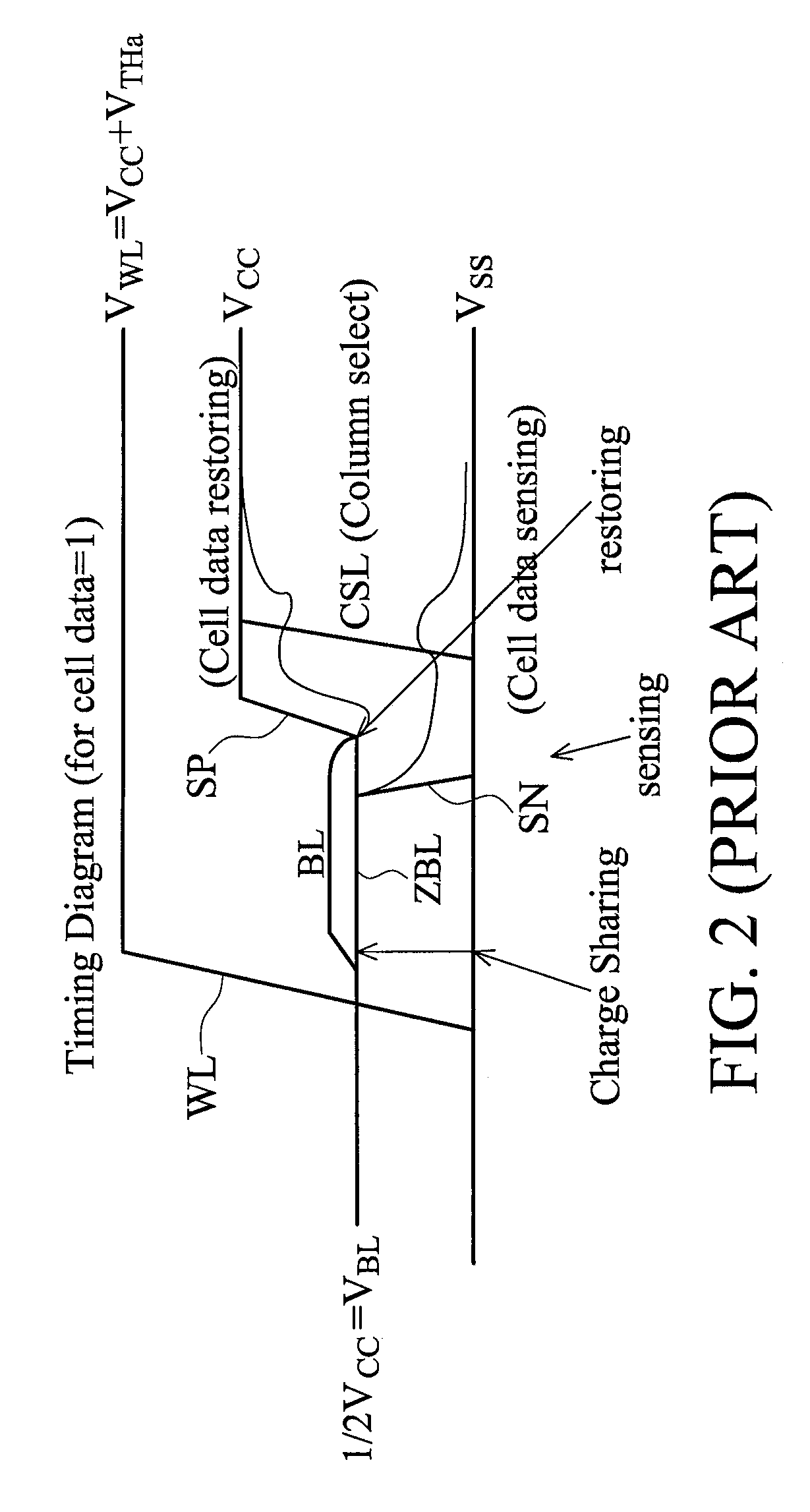

Circuit and Method for a High Speed Memory Cell

InactiveUS20100165704A1Easy to operateHigh operating requirementsDigital storageWrite bitHigh speed memory

A memory cell is disclosed, including a write access transistor coupled between a storage node and a write bit line, and active during a write cycle responsive to a voltage on a write word line; a read access transistor coupled between a read word line and a read bit line, and active during a read cycle responsive to a voltage at the storage node; and a storage capacitor coupled between the read word line and the storage node. Methods for operating the memory cell are also disclosed.

Owner:TAIWAN SEMICON MFG CO LTD

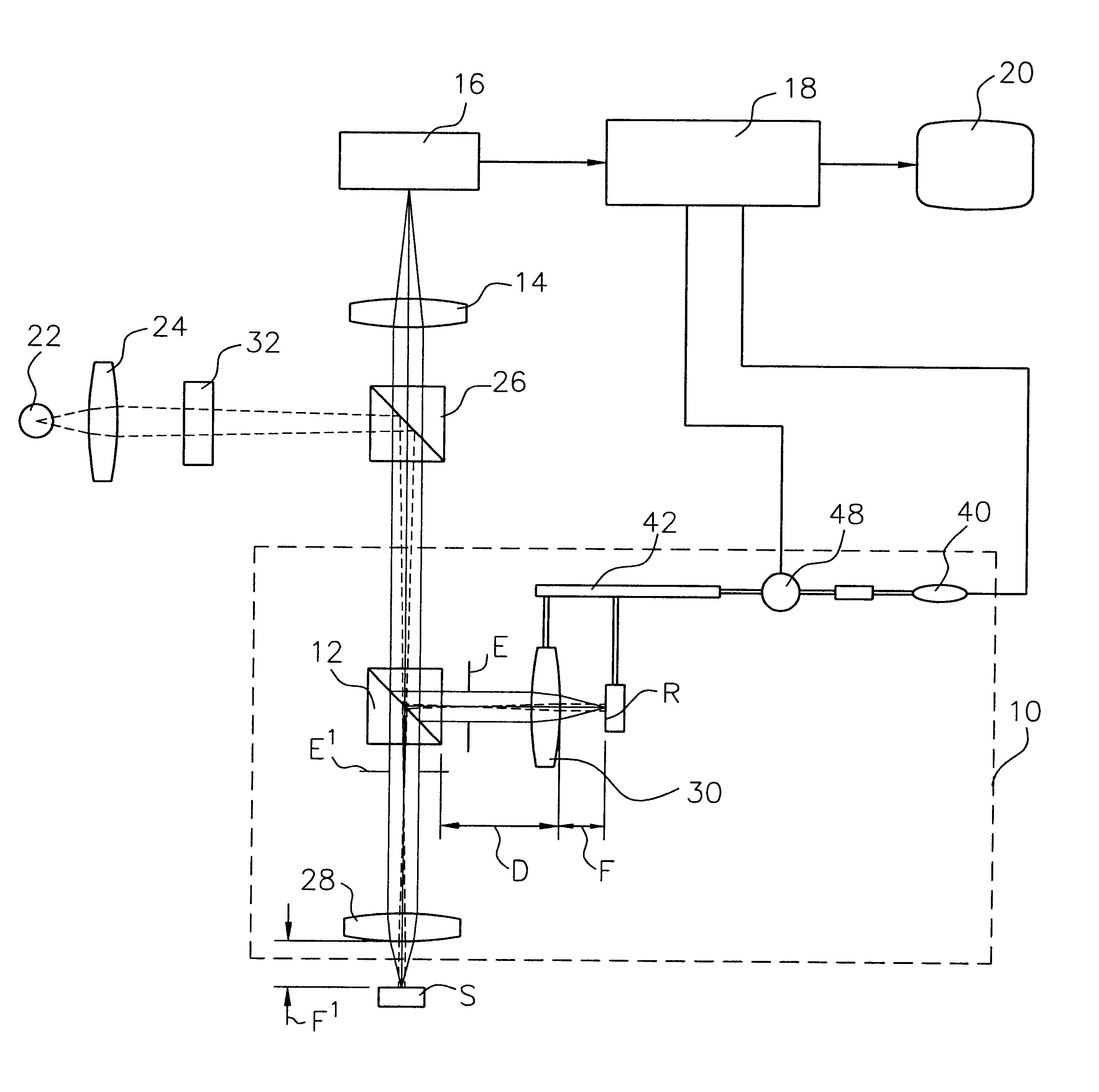

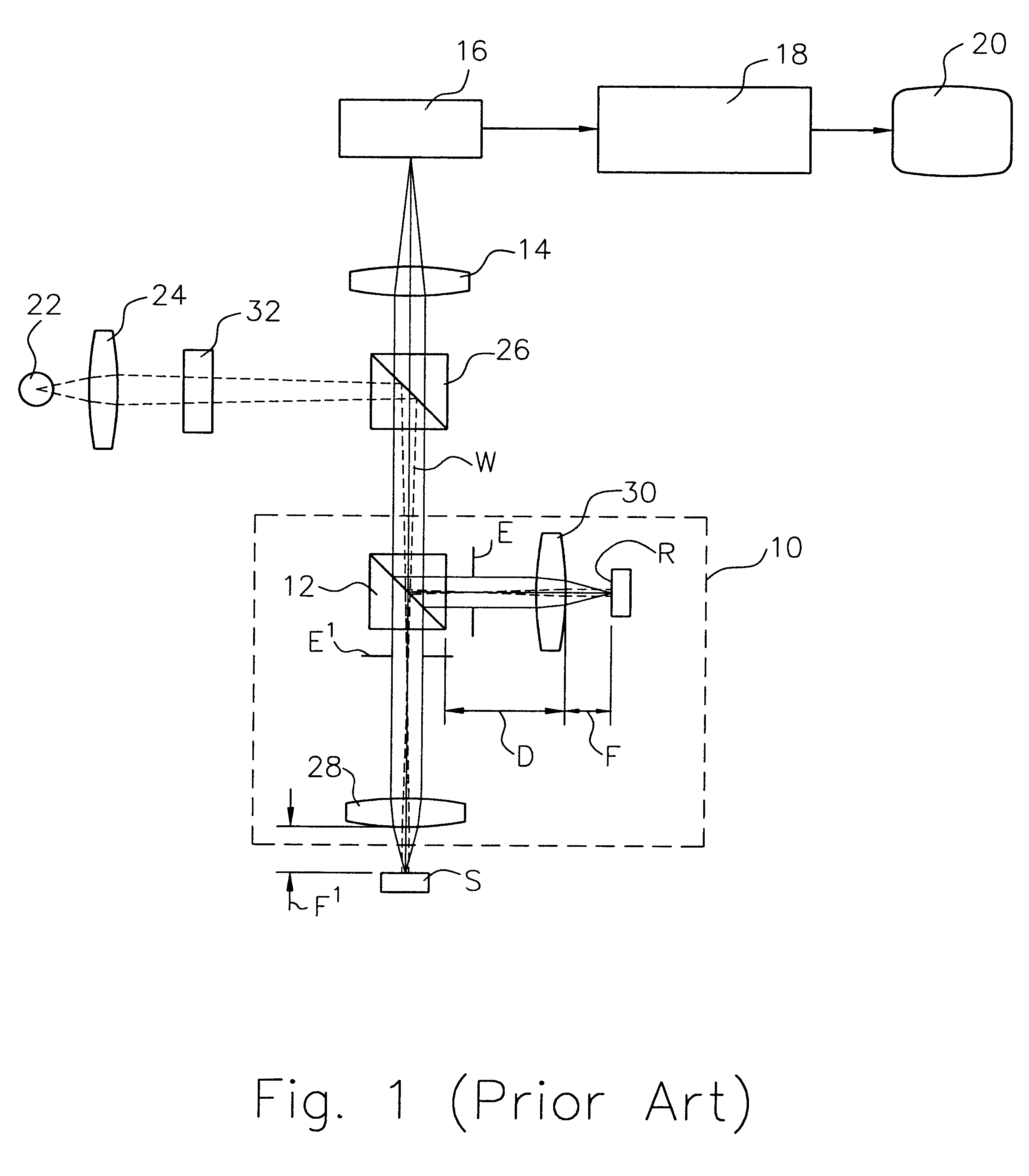

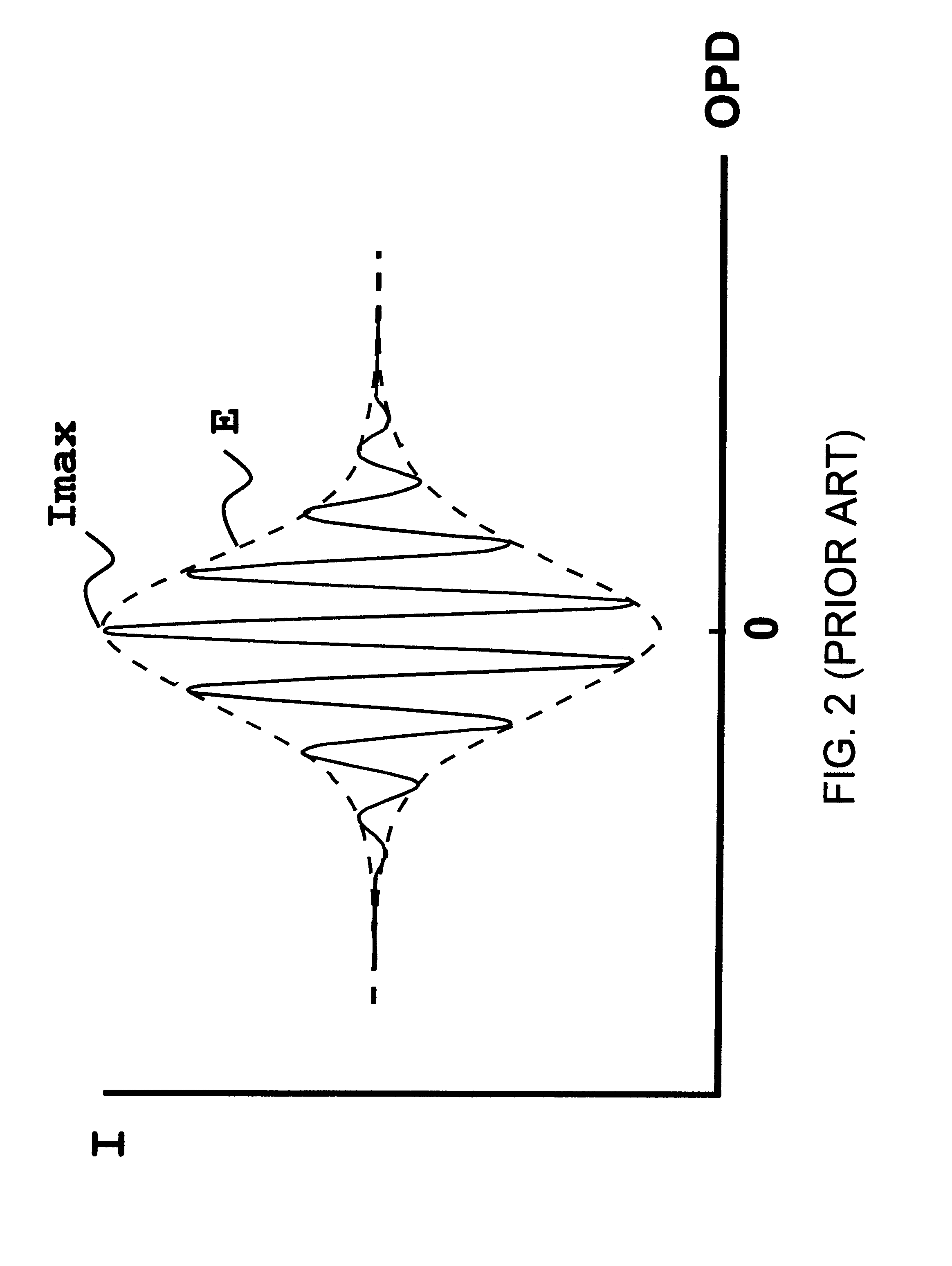

Automated minimization of optical path difference and reference mirror focus in white-light interference microscope objective

InactiveUS6552806B1Implemented easily and economicallyMaximise variationUsing optical meansPhysicsOptical path

Average fringe contrast is determined by PSI measurements at each step of relatively large translations of the reference optics and mirror of a white-light Linnik interference objective and the resulting data are used to minimize the OPD between the reference and test beam paths of the instrument. Utilizing the same algorithms used in the art to perform conventional vertical scanning interferometry, the position of minimum OPD is determined by finding the position of maximum average fringe contrast. Furthermore, by automating the system with a precise translation mechanism, operator-to-operator variations are completely eliminated and the precision of the process of OPD minimization is greatly improved. In another embodiment of the invention, the optimal focal position of the reference mirror is found at the same time by calculating the average lateral variation of fringe contrast as a function of OPD and focal position. The optimal OPD and focal position correspond to the maximum average lateral variation of fringe contrast in the resulting three-dimensional space.

Owner:BRUKER NANO INC

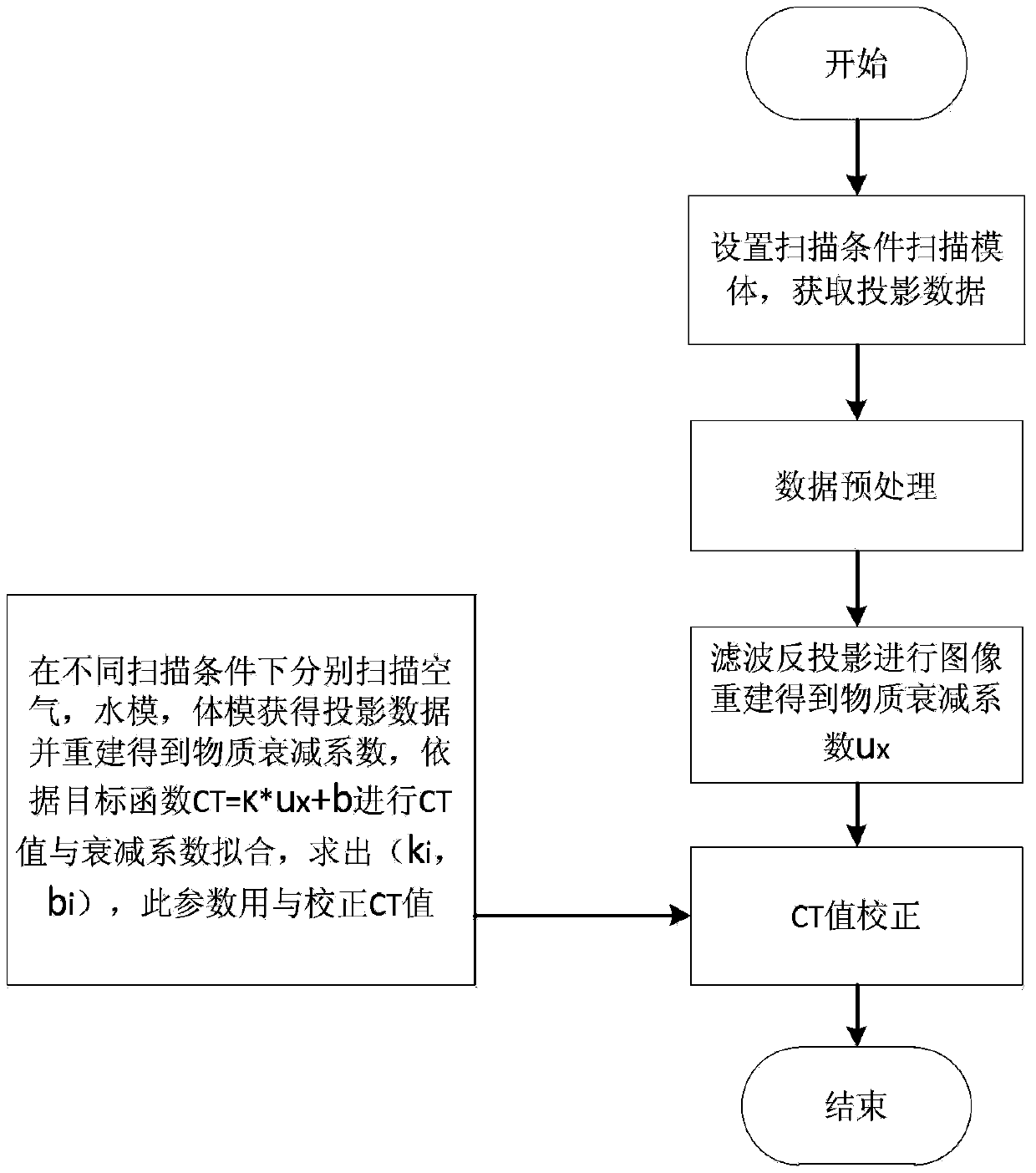

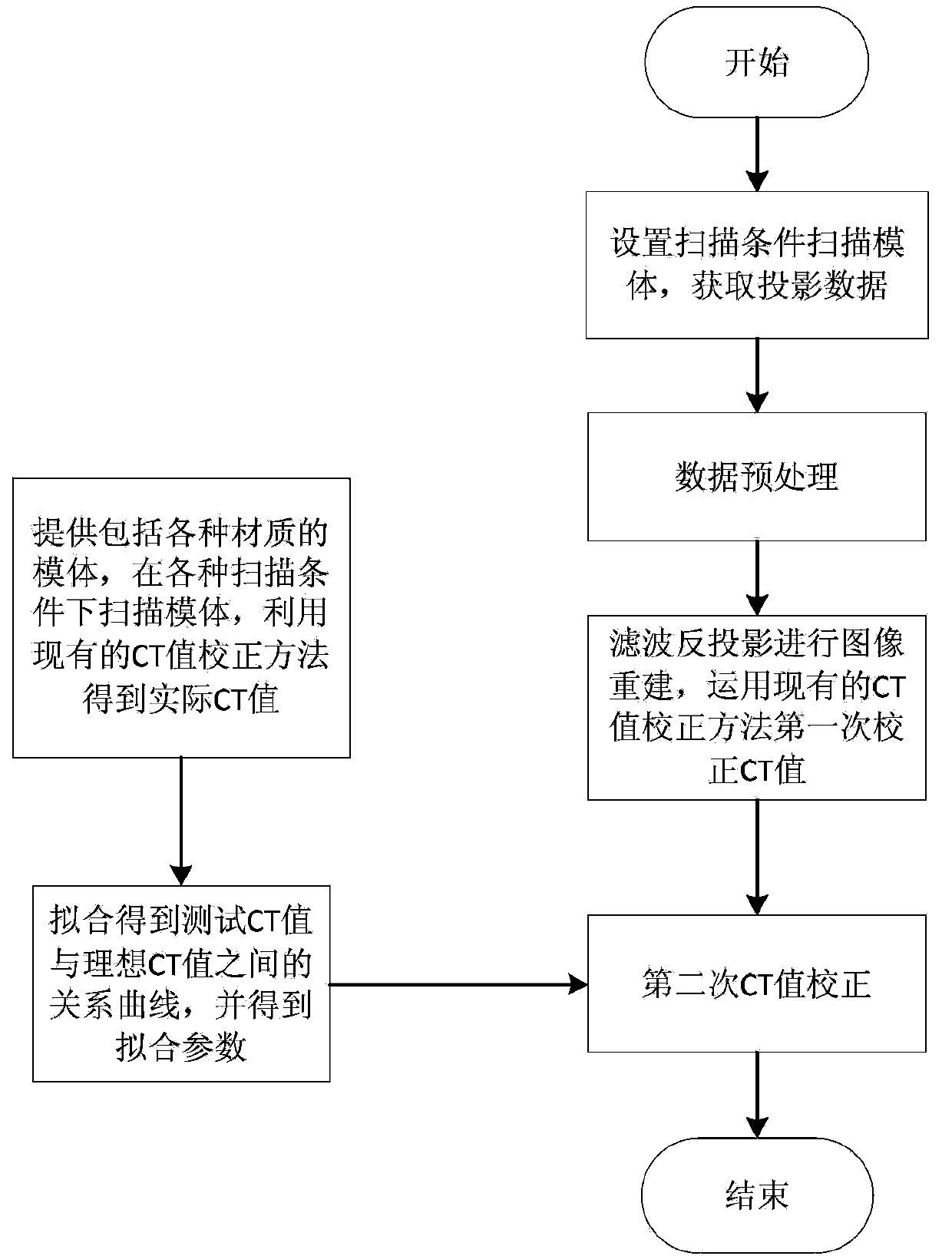

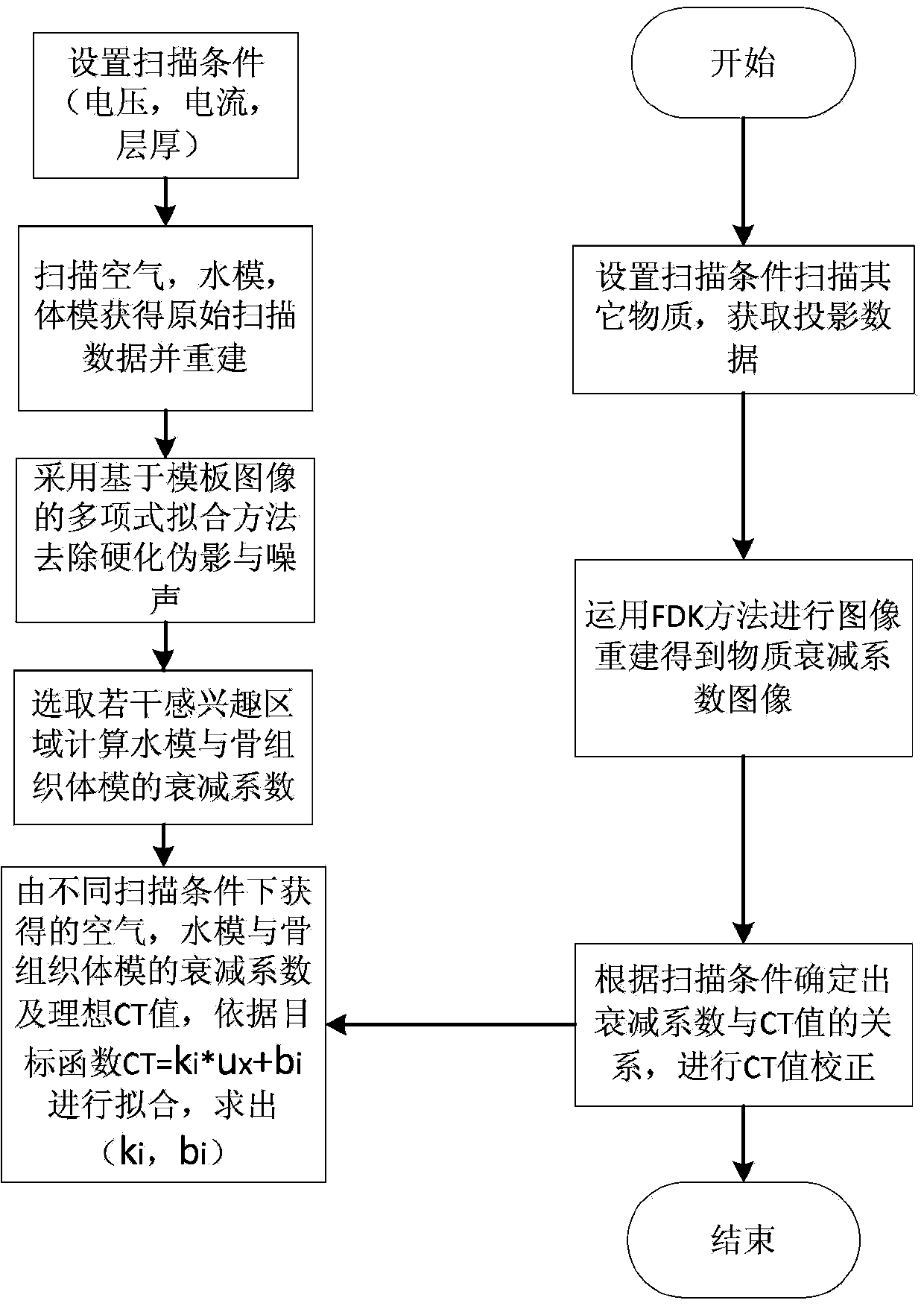

CT (Computed Tomography) value correcting method for cone-beam CT

ActiveCN103961125AAccurate Attenuation CoefficientGuaranteed accuracyComputerised tomographsTomographyAttenuation coefficientUltrasound attenuation

The invention discloses a CT (Computed Tomography) value correcting method for cone-beam CT. The CT value correcting method comprises the following steps: scanning air, a water phantom and a bone tissue body phantom under different scanning conditions to respectively obtain projection data; reestablishing an image; removing noise and artifacts by adopting a polynomial fitting method based on a template image; selecting a plurality of interested regions and calculating a mean value of an attenuation coefficient and a standard deviation of the attenuation coefficient; obtaining the value range of the attenuation coefficient and taking the attenuation coefficient of maximum occurrence probability; fitting the attenuation coefficients of the air, the water phantom and the bone tissue body phantom under the different scanning conditions with corresponding ideal CT values to obtain respective fitting curves; performing CT scanning and image reestablishment on a scanned material; obtaining a CT value image according to a material attenuation coefficient image and a fitting curve and finishing the CT value correction. According to the CT value correcting method disclosed by the invention, image noise and artifact can be effectively reduced, the reestablished image of single material reaches the uniformity to the great degree, the precision of the attenuation coefficient of the material becomes higher and further high accuracy for the fitting of the curve of the CT value and the material attenuation coefficient is realized.

Owner:NORTHEASTERN UNIV

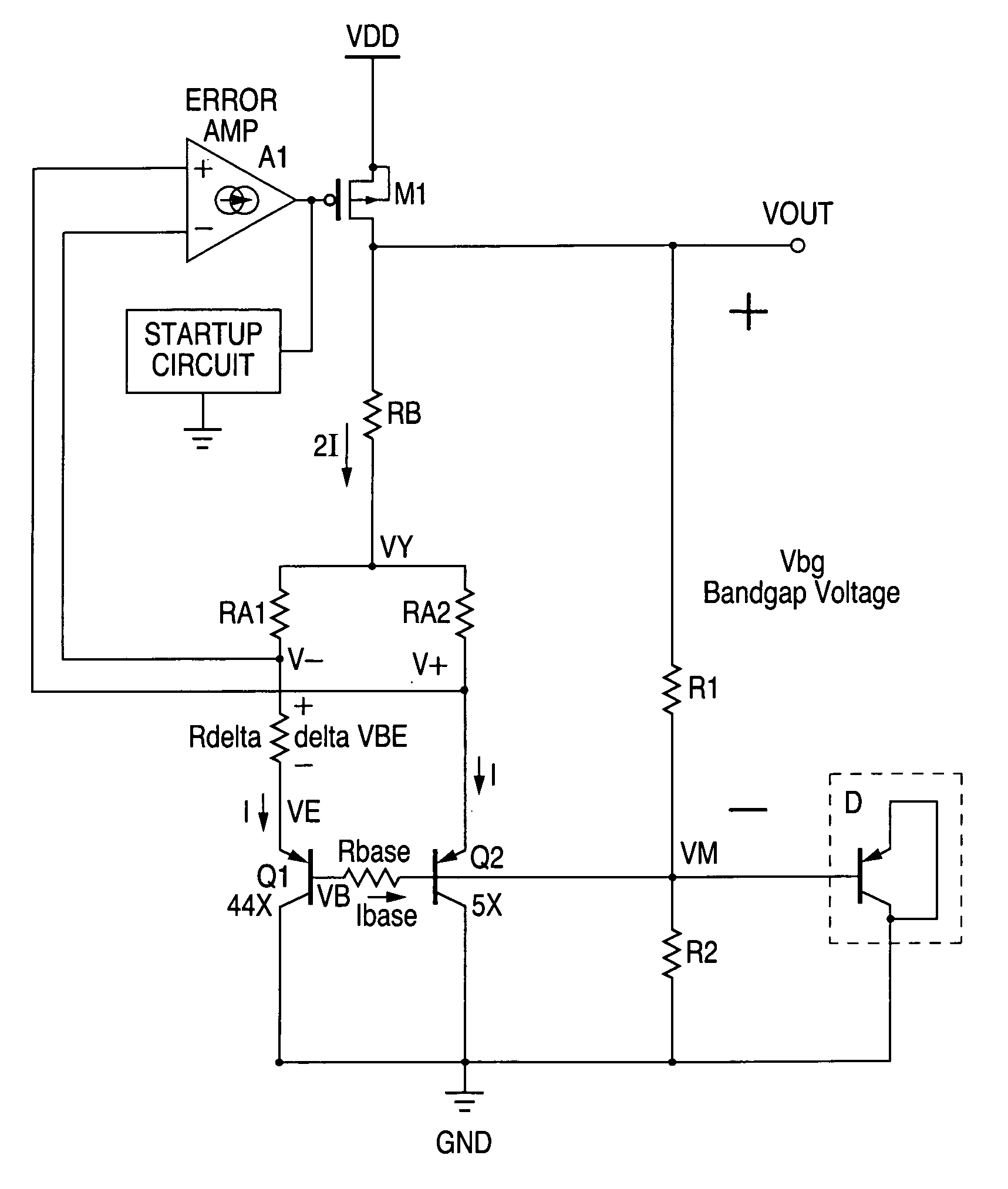

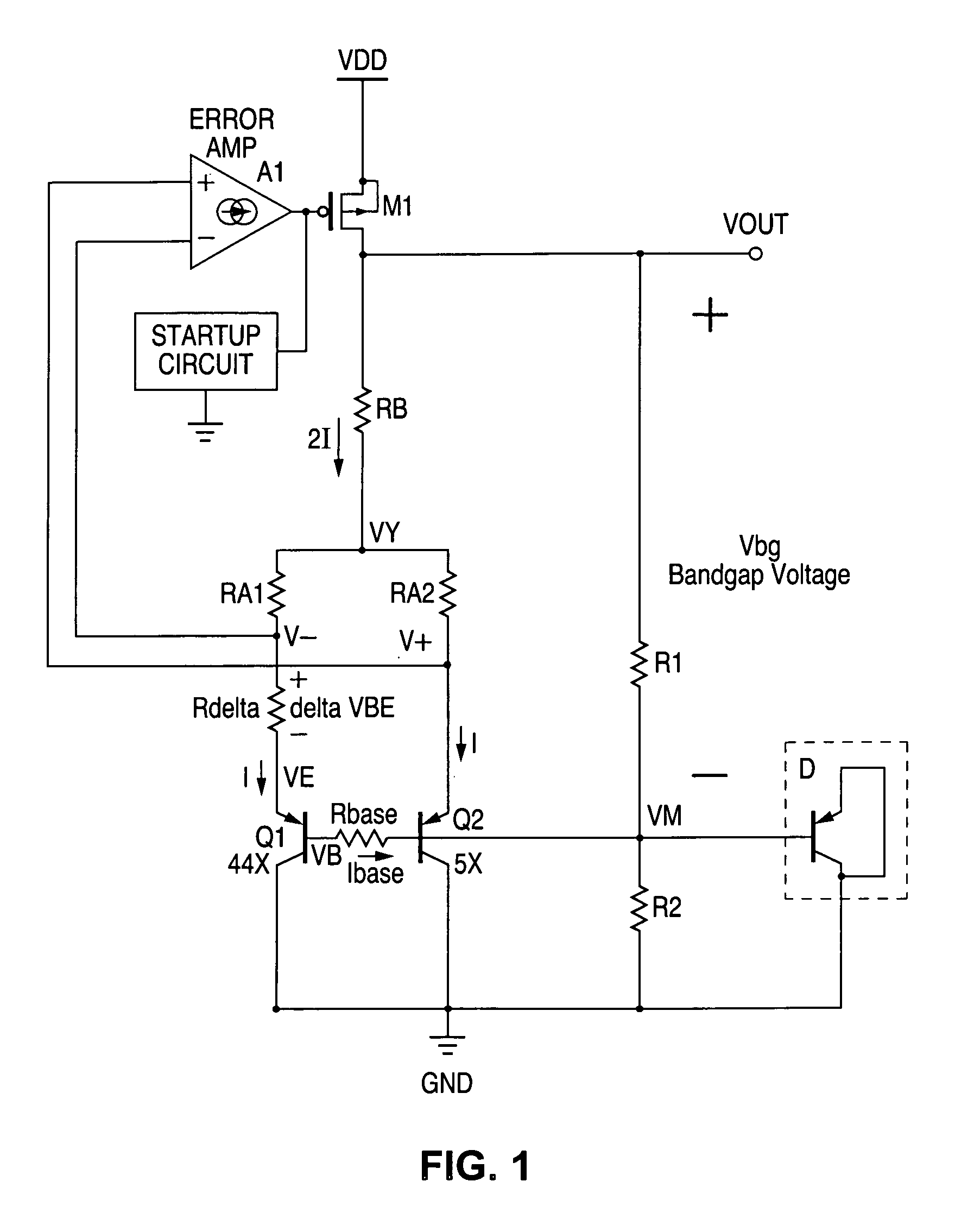

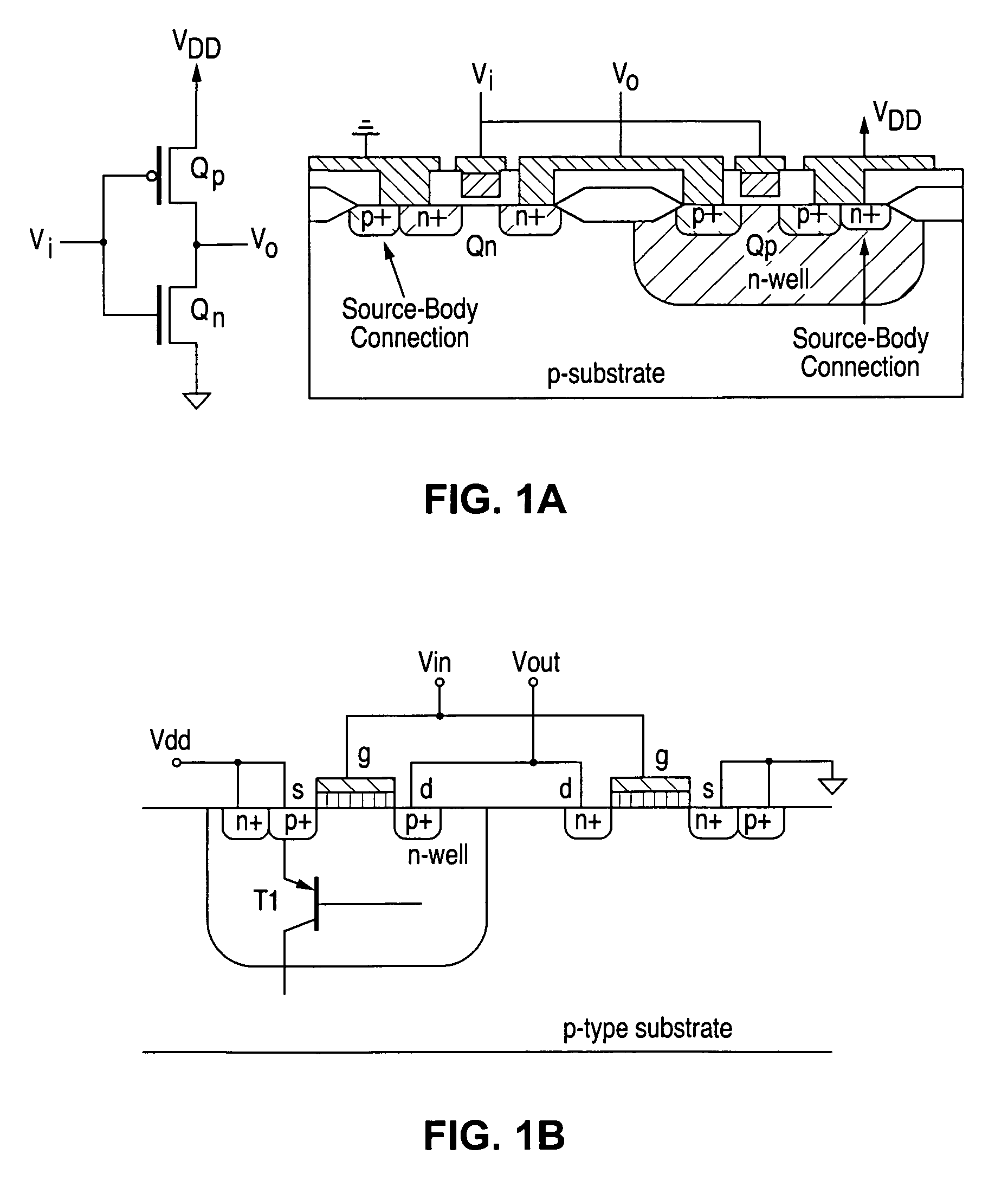

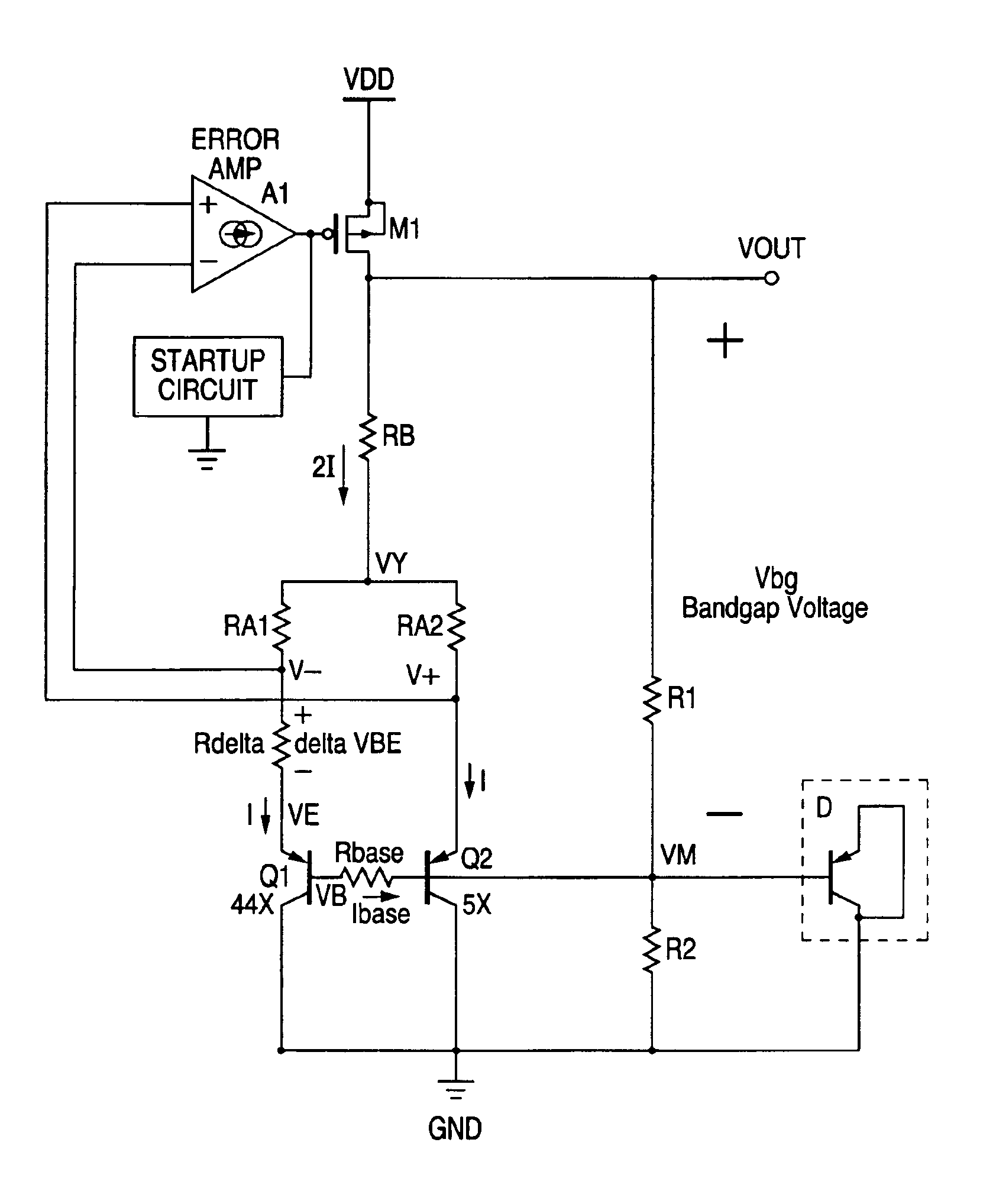

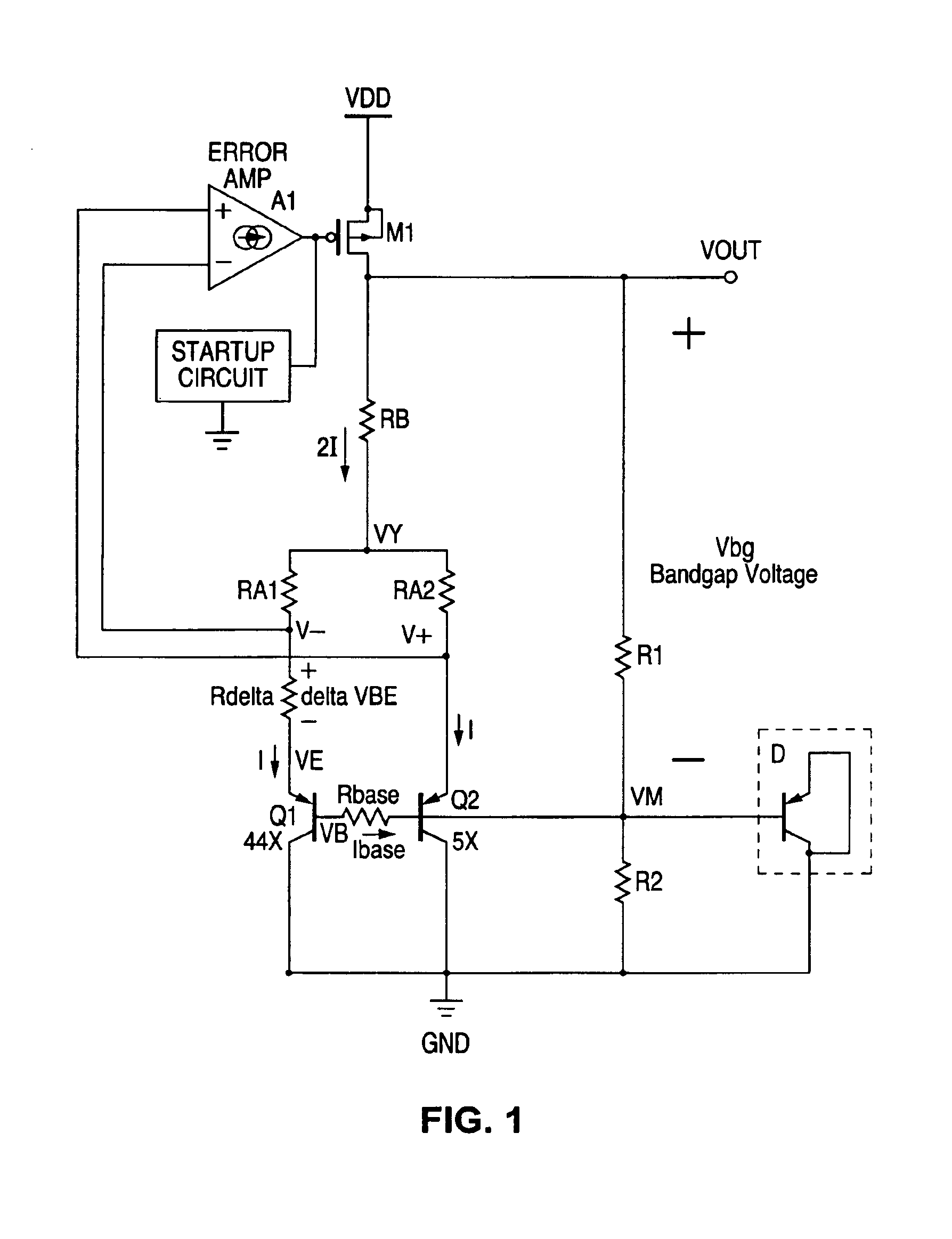

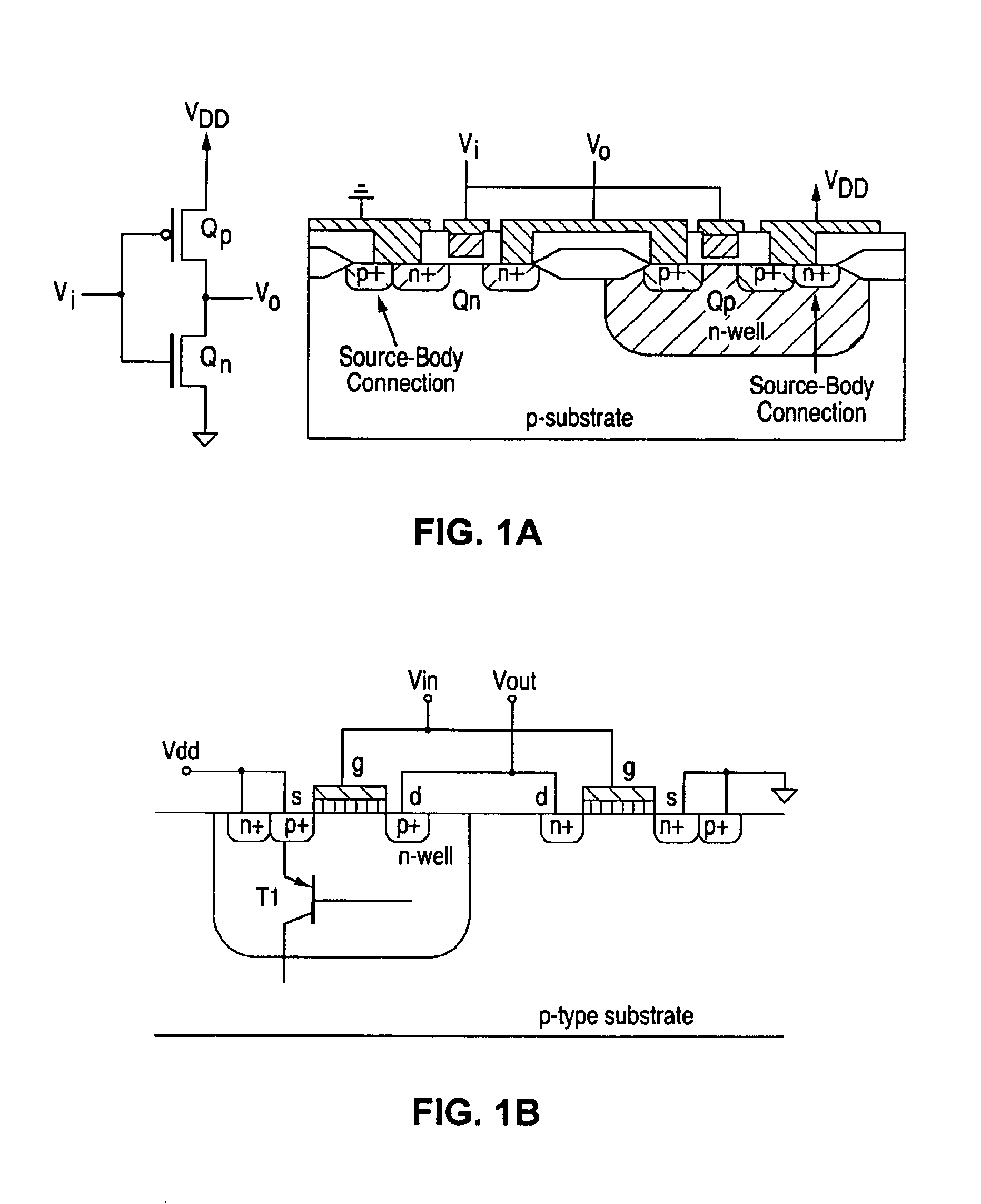

Metal oxide semiconductor (MOS) bandgap voltage reference circuit

ActiveUS6933770B1Increase capacitanceImprove referenceTransistorSolid-state devicesParasitic capacitanceEngineering

Owner:NAT SEMICON CORP

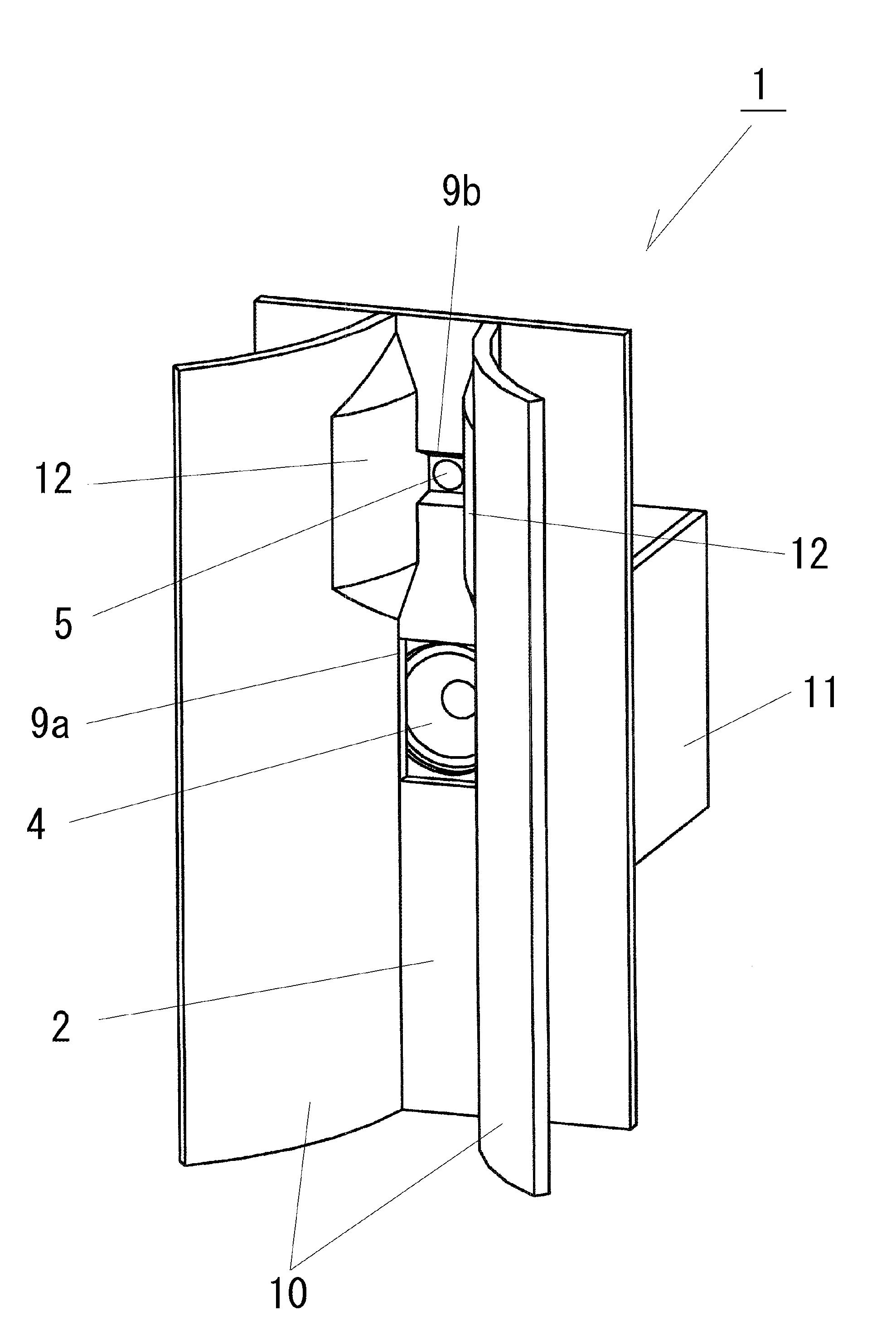

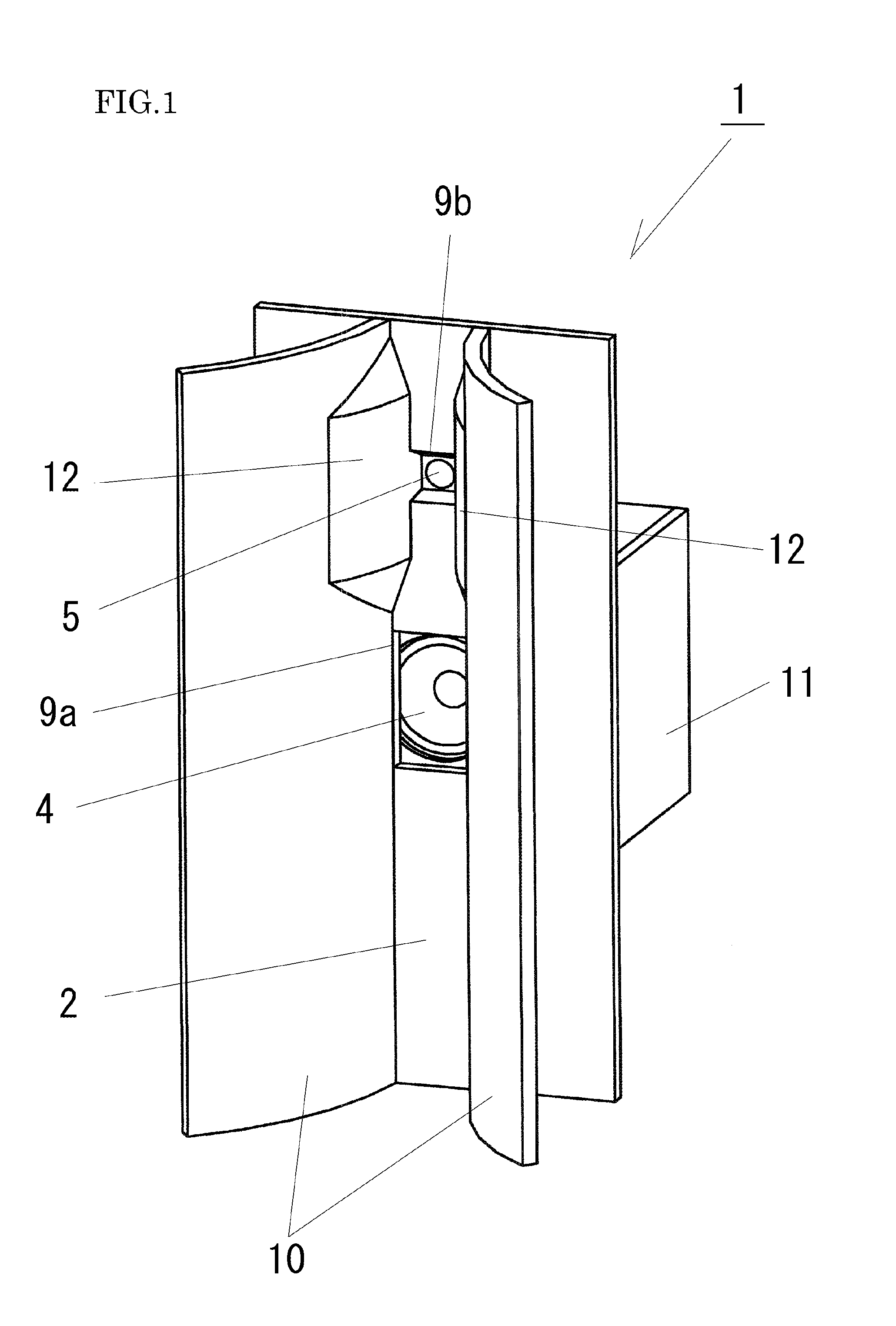

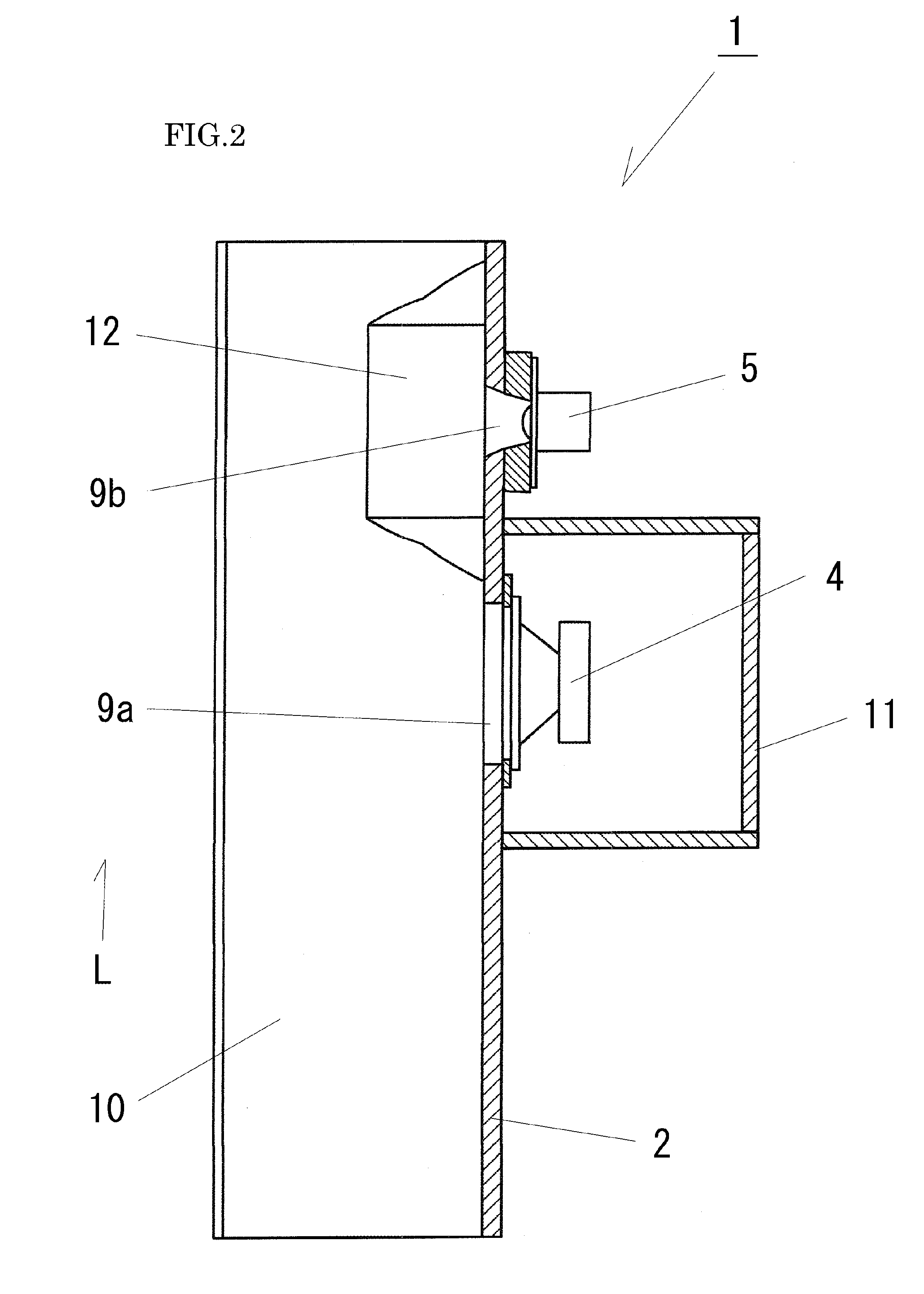

Speaker device

InactiveUS20090046875A1Enhance effectExcellent acoustic characteristicTransducers for sound channels pluralityFrequency/directions obtaining arrangementsWooferEngineering

To provide a speaker system in which arrival times of sounds radiated from each speaker are aligned, sound pressures of speakers other than a woofer are enhanced as in a horn-type speaker, and each speaker unit, which disperses with a conventional horn, is gathered to integrate functions of each speaker and present a balanced appearance.Two or more types of speakers 3, 4, 5 including a reference speaker 4 for reproducing a high frequency range next to a reproduction range of a woofer 3 are arranged in line and a pair of enhanced walls 10a is disposed on a front face of a baffle board 2 to pass by left and right sides of a radiating face of the reference speaker 4, vertically extend along the front face of the baffle board 2, and open left and right toward forward. Accordingly, the radiated sound from the reference speaker 4 is enhanced by an inside space of the pair of enhanced walls 10a without enhancing the radiated sound from the woofer 3.

Owner:MASUDA TADASHI

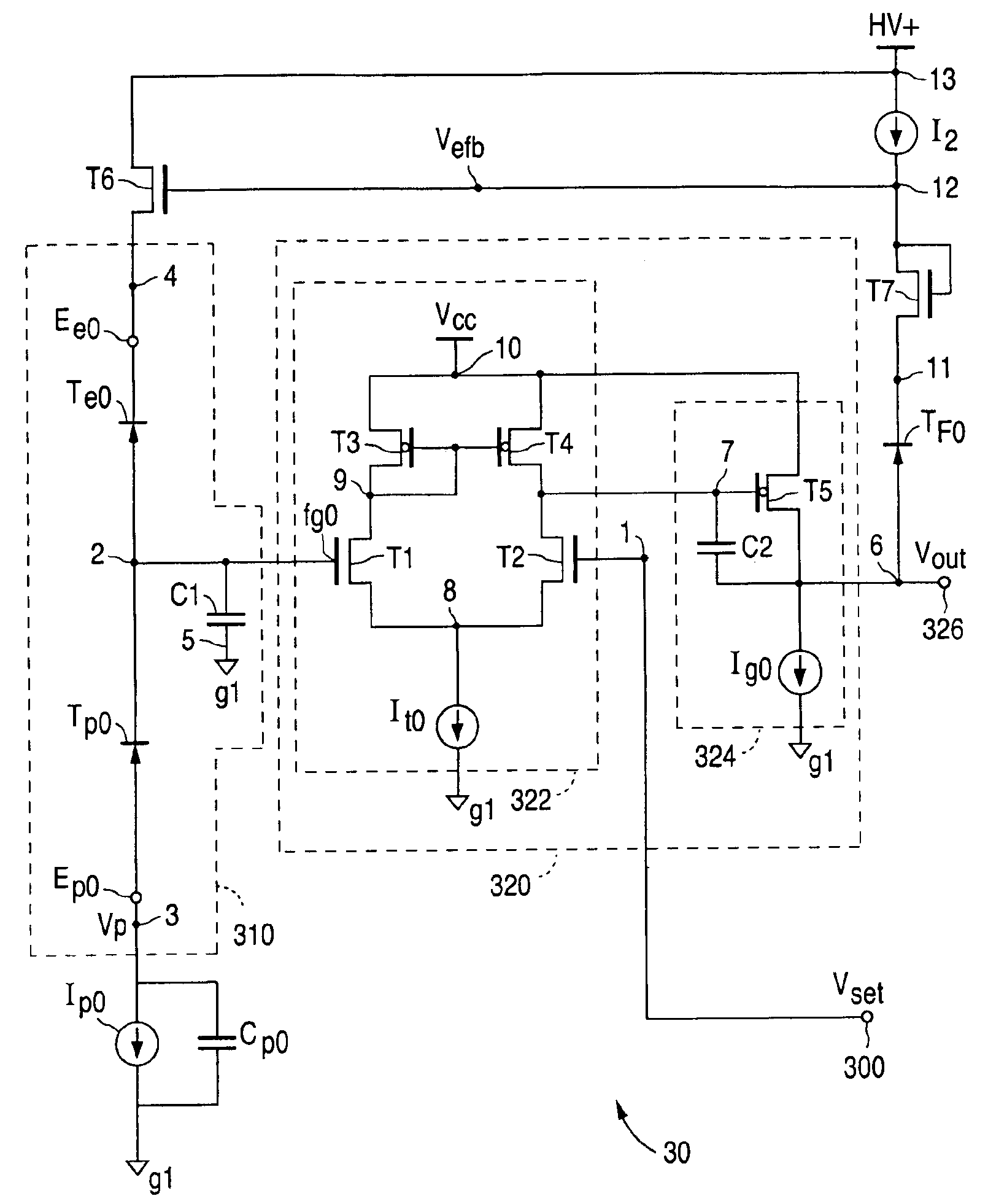

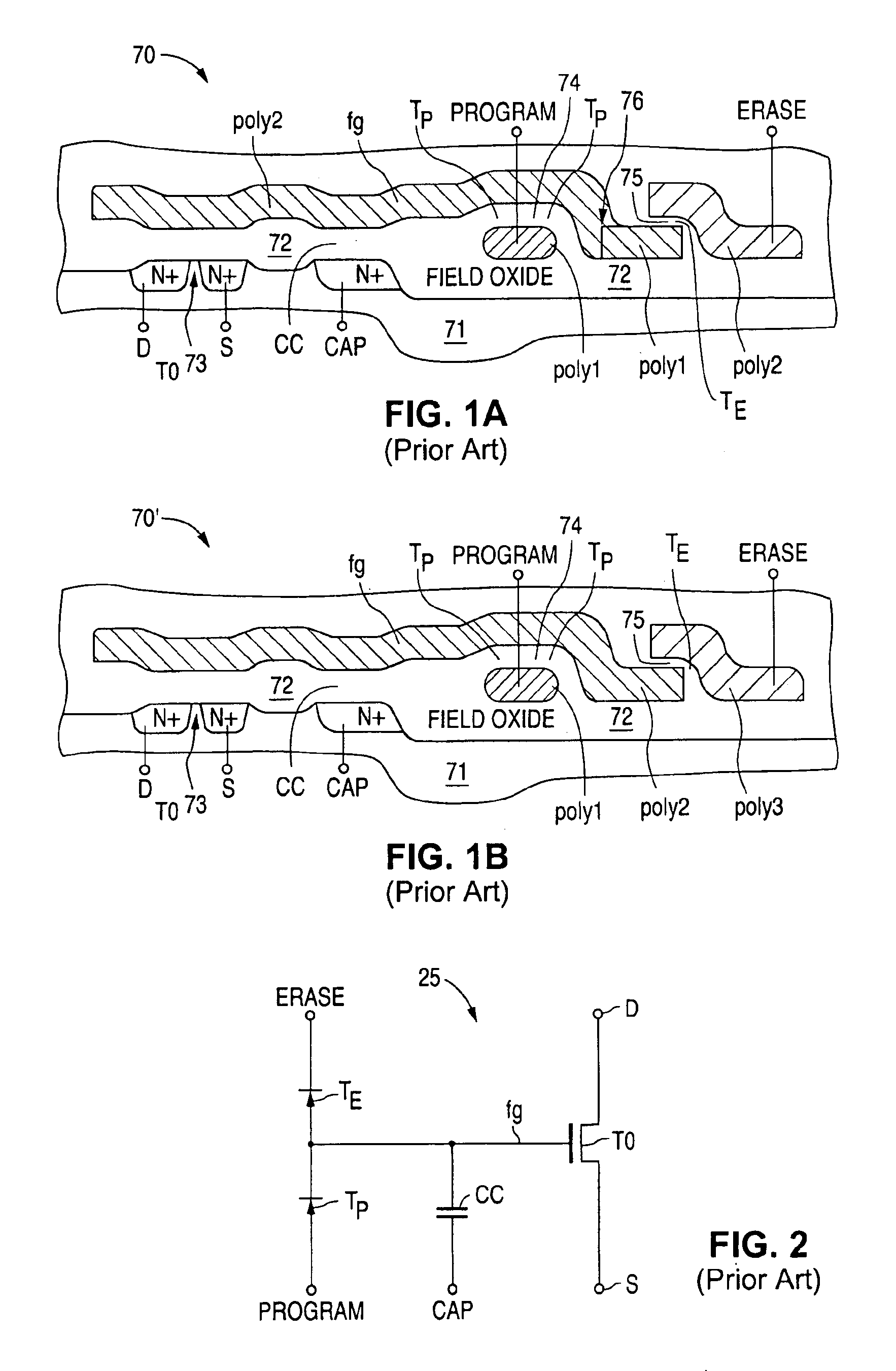

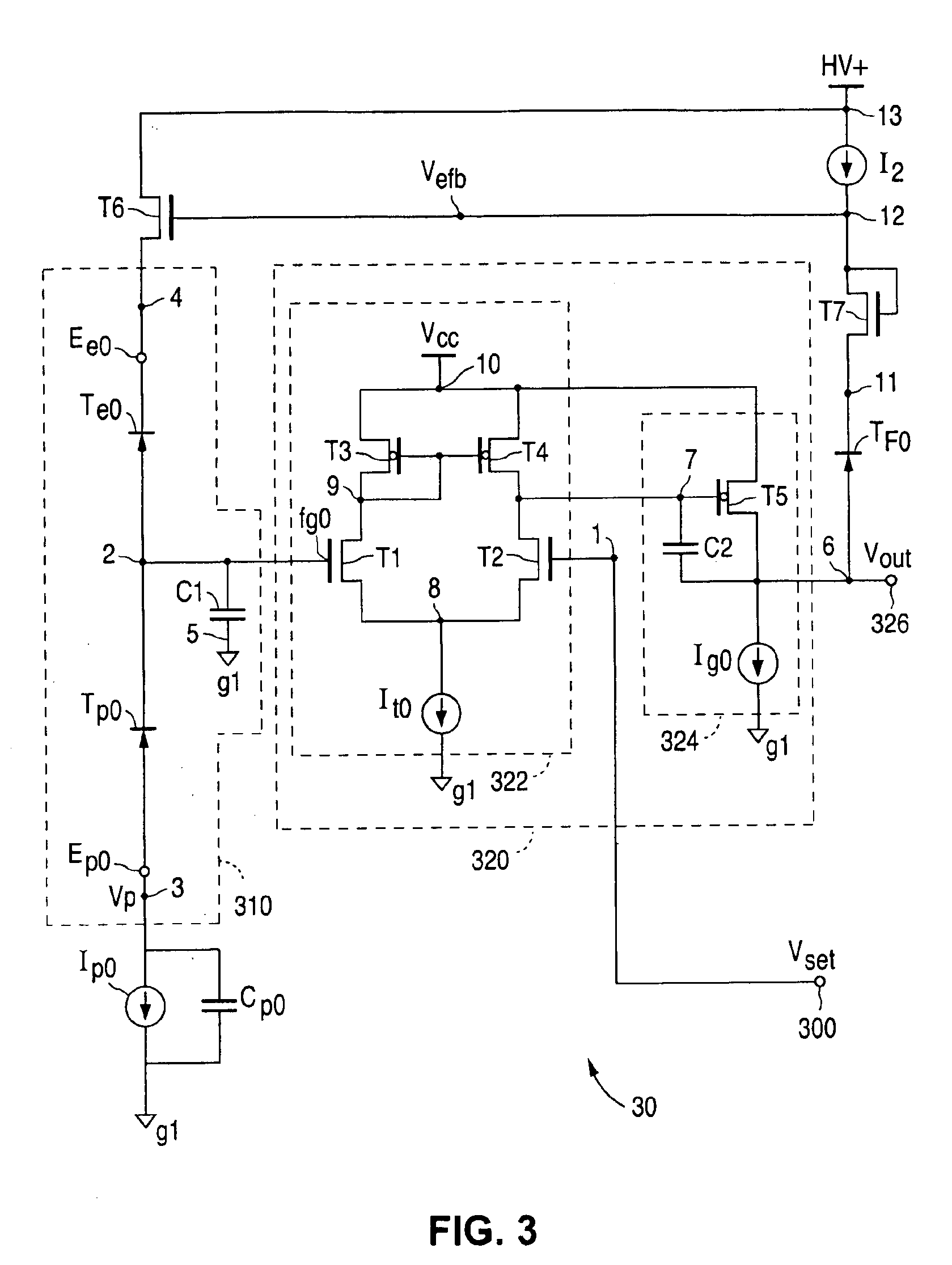

Differential dual floating gate circuit and method for programming

InactiveUS6898123B2Improved initial setting accuracyImprove accuracyElectric analogue storesRead-only memoriesCapacitanceCapacitive coupling

A method and circuit for setting a reference voltage in a dual floating gate circuit is disclosed. During a set mode, a first and second floating gate are programmed to different charge levels that are a function of an input set voltage capacitively coupled to the first floating gate during the set mode. During a read mode, this difference in charge level is used by the dual floating gate circuit to generate a reference voltage that is a function of the input set voltage, and is preferably equal to the input set voltage.

Owner:XICOR

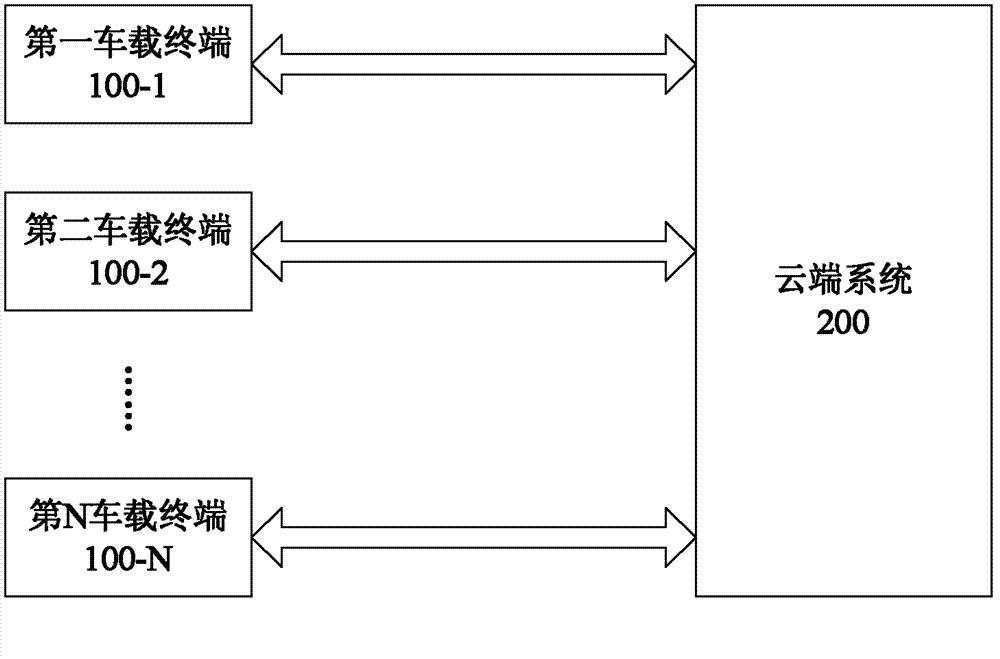

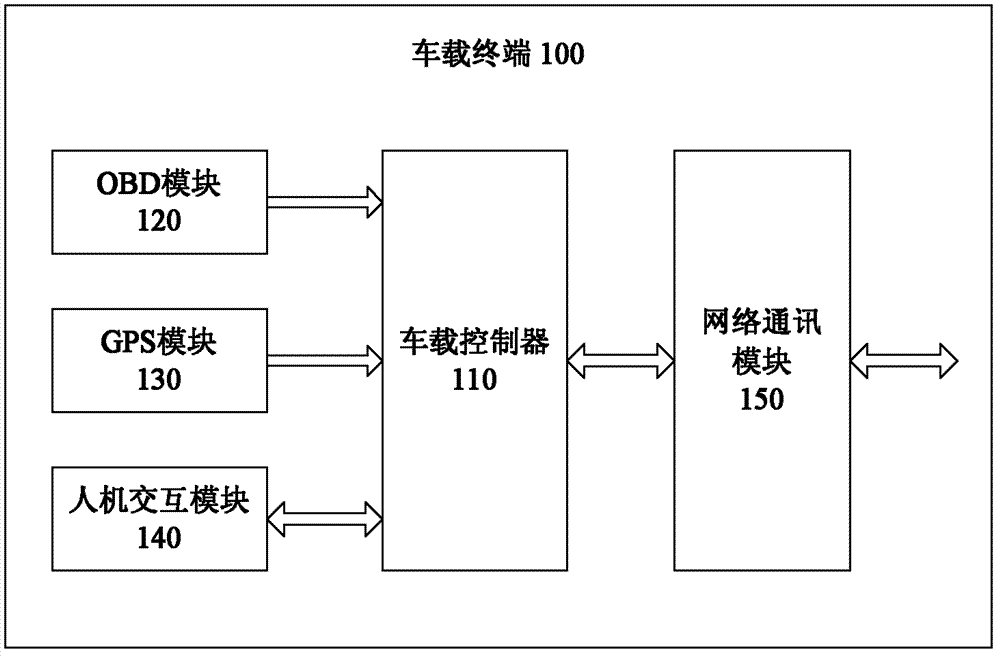

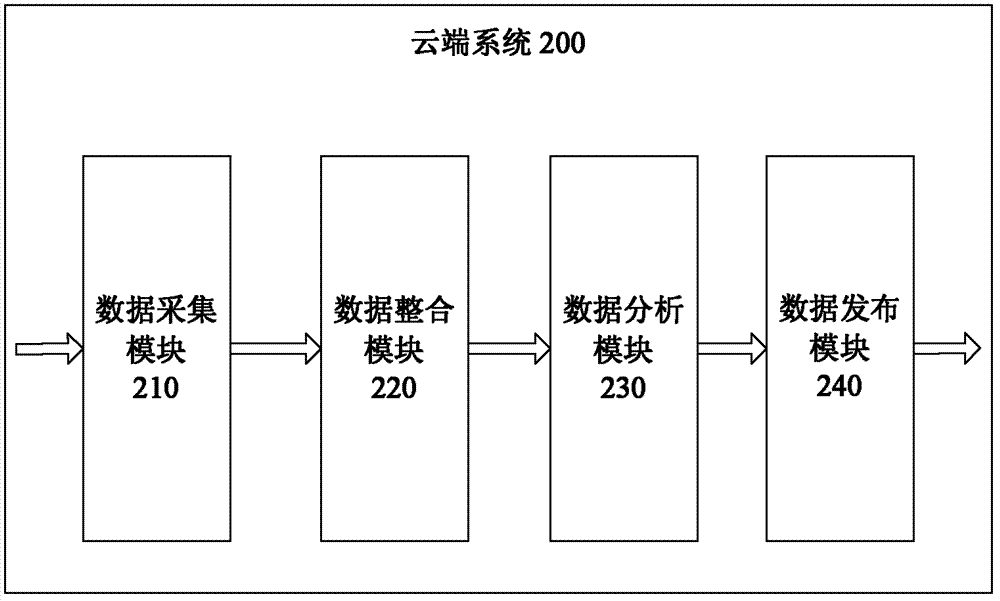

Intelligent GPS (global position system) route planning system and method based on cloud service

InactiveCN103364001AImprove referenceInstruments for road network navigationBeacon systems using radio wavesCar drivingUser input

The invention provides an intelligent GPS (global position system) route planning system and method based on cloud service. The system comprises a cloud system and multiple car-mounted terminals, wherein the car-mounted terminals are used for acquiring real-time operation parameters of a car by an OBD (on board diagnostics) and acquiring real-time position information of the car by a GPS, and sending the parameters and the information to the cloud system; the car-mounted terminals also send navigation instructions inputted by a user to the cloud system; the cloud system is used for receiving and integrating the required real-time operation parameters of the car, the real-time position information of the car and regional map information, extracting integrated data according to the navigation instructions inputted by the user and sent by the car-mounted terminals so as to establish a virtual model of traffic road conditions, and calculating a driving route and issuing the driving route to a corresponding car-mounted terminal. According to the system and the method provided by the invention, by combining the existing GPS technology and the existing OBD technology, the acquired real-time operation parameters and real-time position information of the car are collected to a cloud computing platform, and an intelligent dynamic car driving route is planned through cloud computing; the reference is higher than that of the existing static route planning.

Owner:HARBIN INST OF TECH SHENZHEN GRADUATE SCHOOL

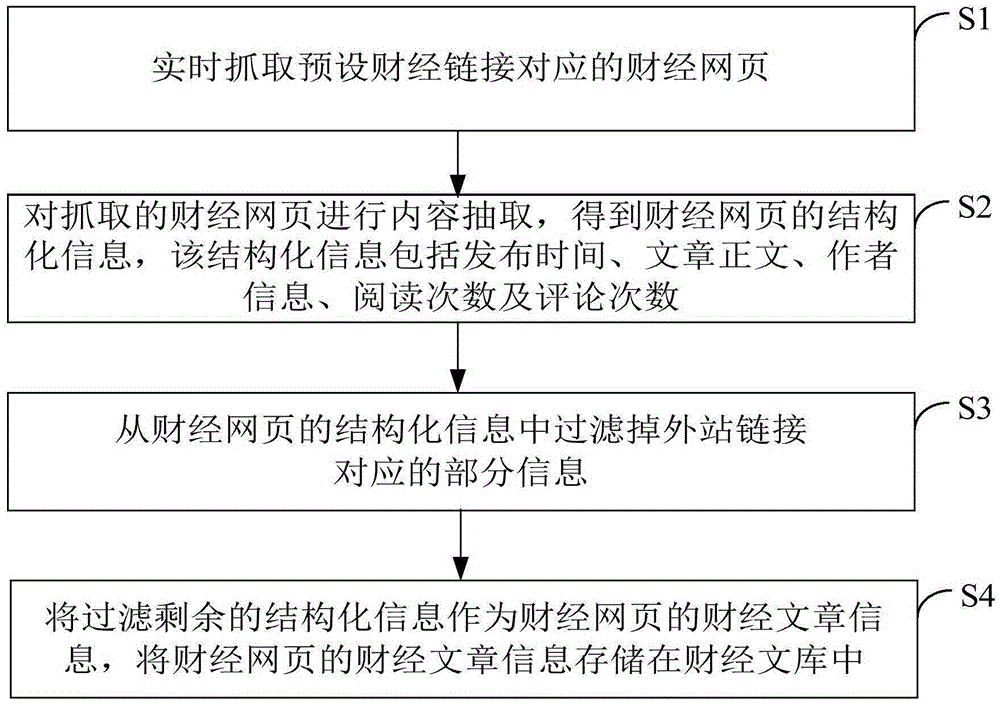

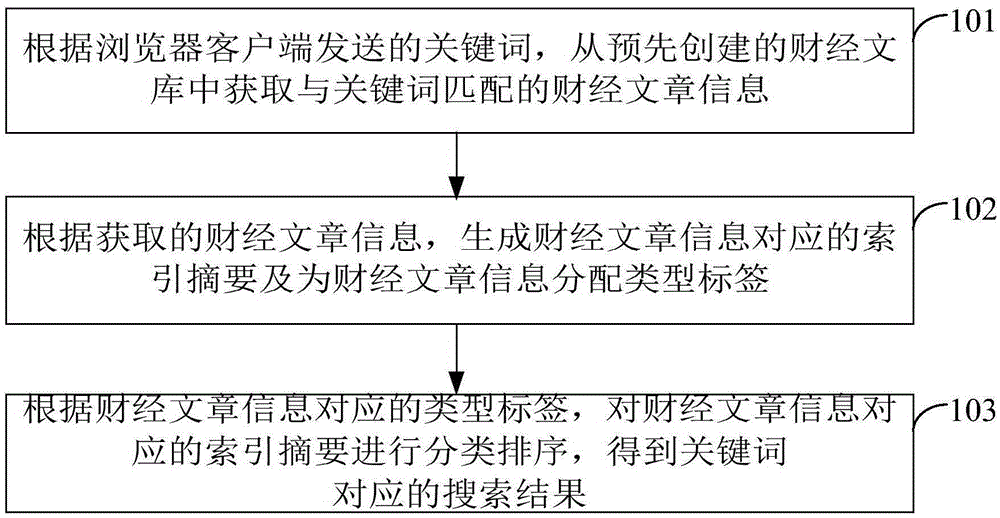

Method, device and server for searching articles of finance and economics

InactiveCN105404699AImprove referenceClear typeNatural language data processingSpecial data processing applicationsClient-sideResearch result

The invention provides a method, a device and a server for searching articles of finance and economics. The method comprises the steps of according to a key word sent from a browser client, acquiring articles of finance and economics matched with the key word out of a pre-established library of finance and economics; according to the article information of finance and economics, generating index abstracts corresponding to the article information of finance and economics and distributing type tags for the article information of finance and economics; according to the type tags corresponding to the article information of finance and economics, sorting and ordering the index abstracts corresponding to the article information of finance and economics to obtain a search result corresponding to the key word. According to the technical scheme of the invention, type tags are distributed for the article information of finance and economics, and then the index abstracts of the article information are sorted and ordered according to the type tags. In this way, the obtained research result is clear in type, so that the browser client can display the search result in the sorted manner. Users can browse articles according to the types of the article information of finance and economics. Therefore, the searching reference for articles of finance and economics is improved.

Owner:GUANGZHOU SHENMA MOBILE INFORMATION TECH

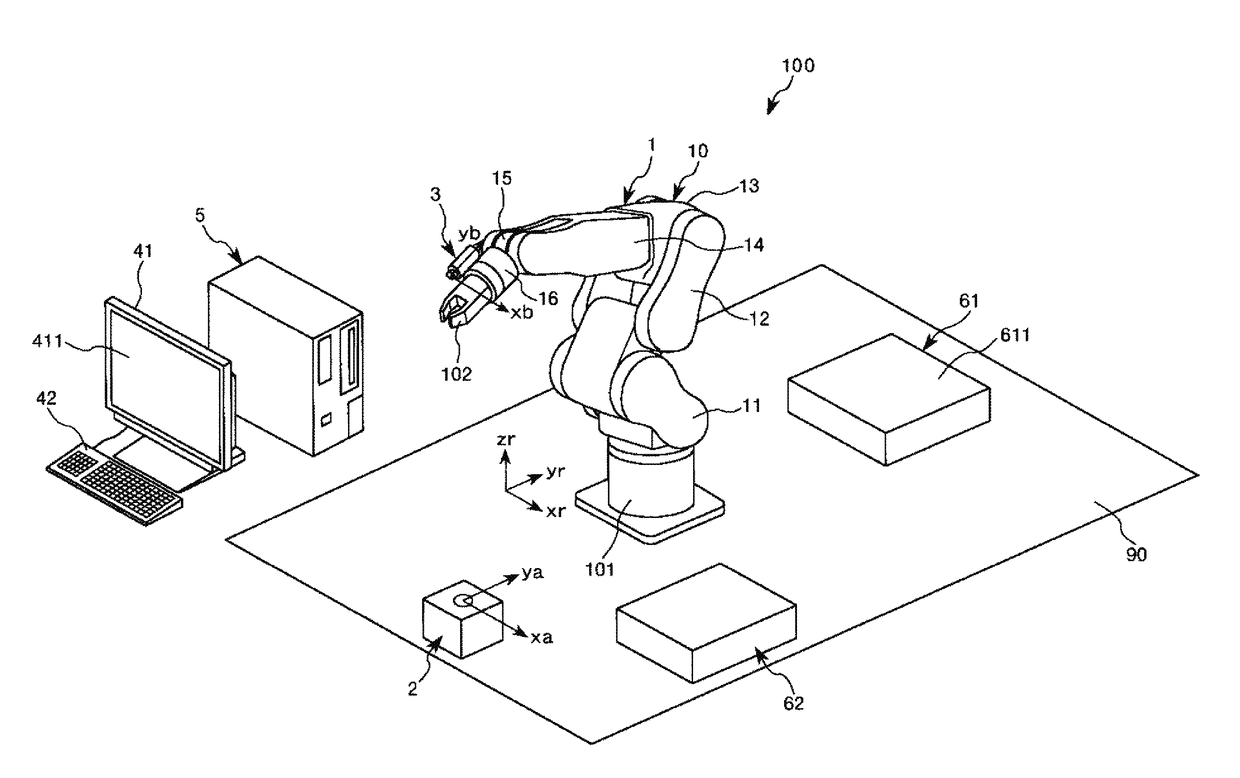

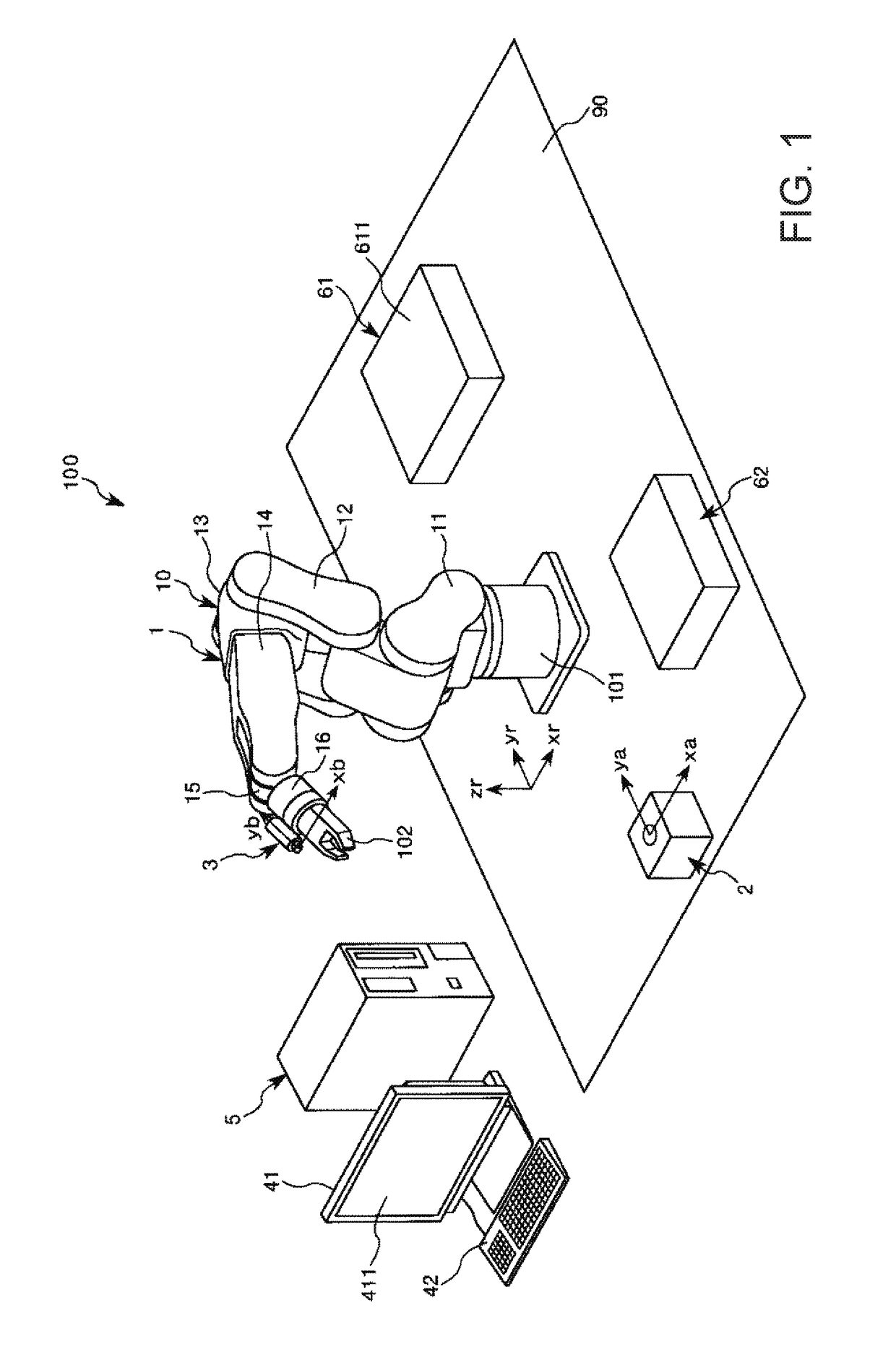

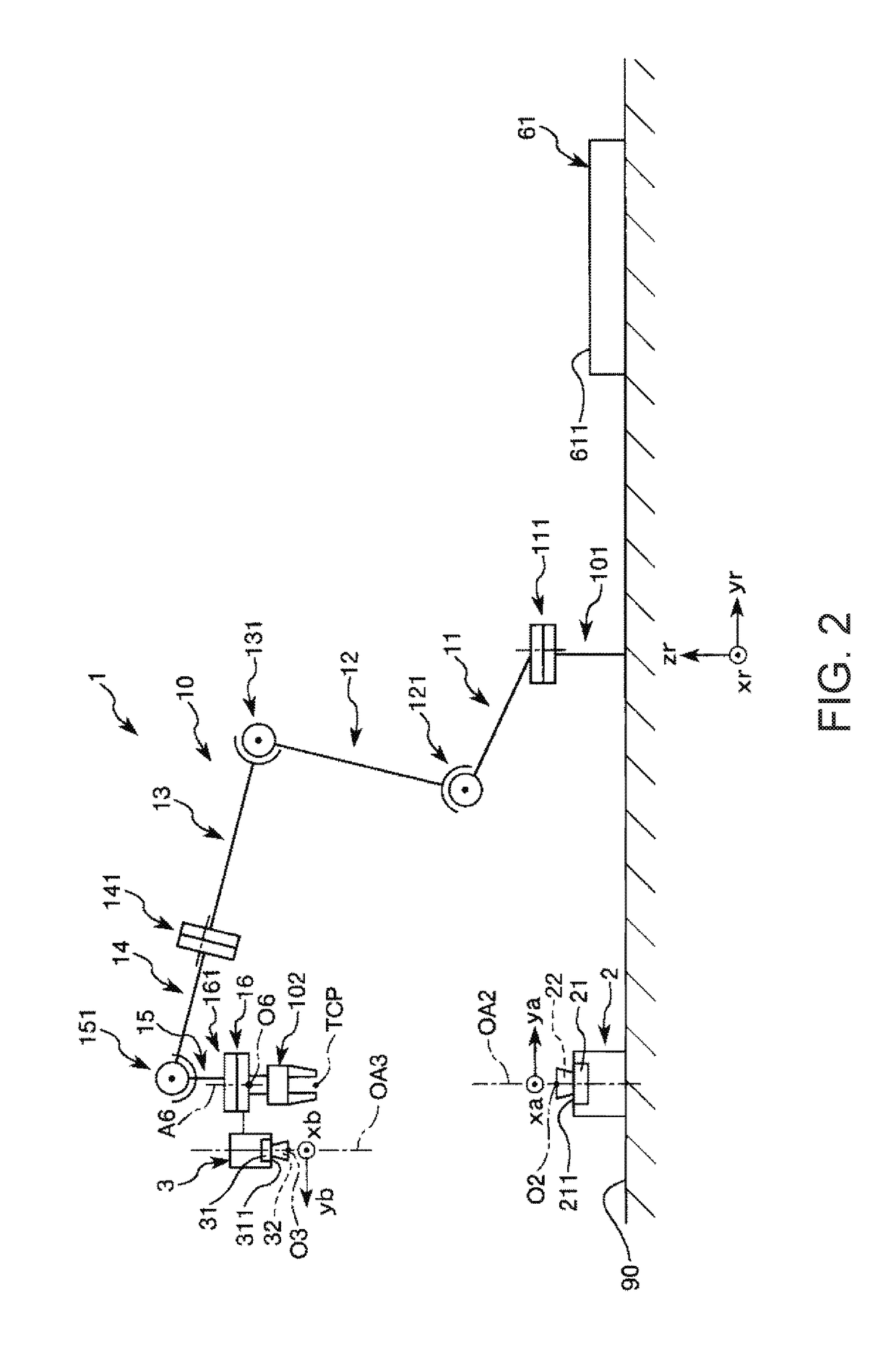

Control device, robot, and robot system

ActiveUS20170151671A1Ensure correct executionAvoid changeProgramme-controlled manipulatorImage enhancementRobotic systemsComputer vision

A control device is capable of controlling each of a robot having a robot arm, and an imaging portion which is capable of capturing a first reference marker, a second reference marker, and a third reference marker, any one of the imaging portion, the first reference marker, the second reference marker, and the third reference marker is provided in the robot, and a posture of a reference surface parallel to a plane which passes through the first reference marker, the second reference marker, and the third reference marker, is acquired based on a first image in which the first reference marker is captured by the imaging portion, a second image in which the second reference marker is captured by the imaging portion, and a third image which captures the third reference marker by the imaging portion.

Owner:SEIKO EPSON CORP

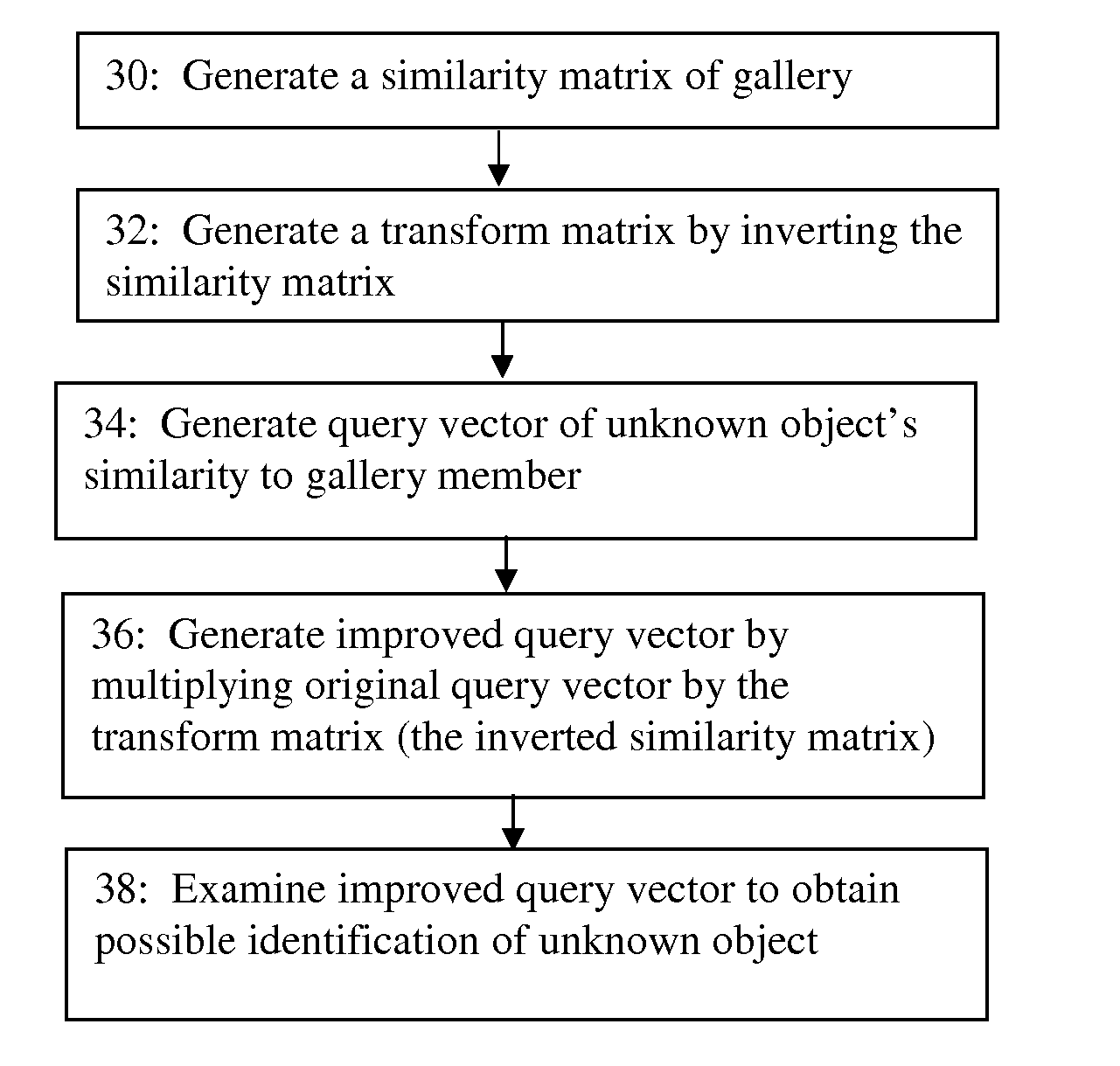

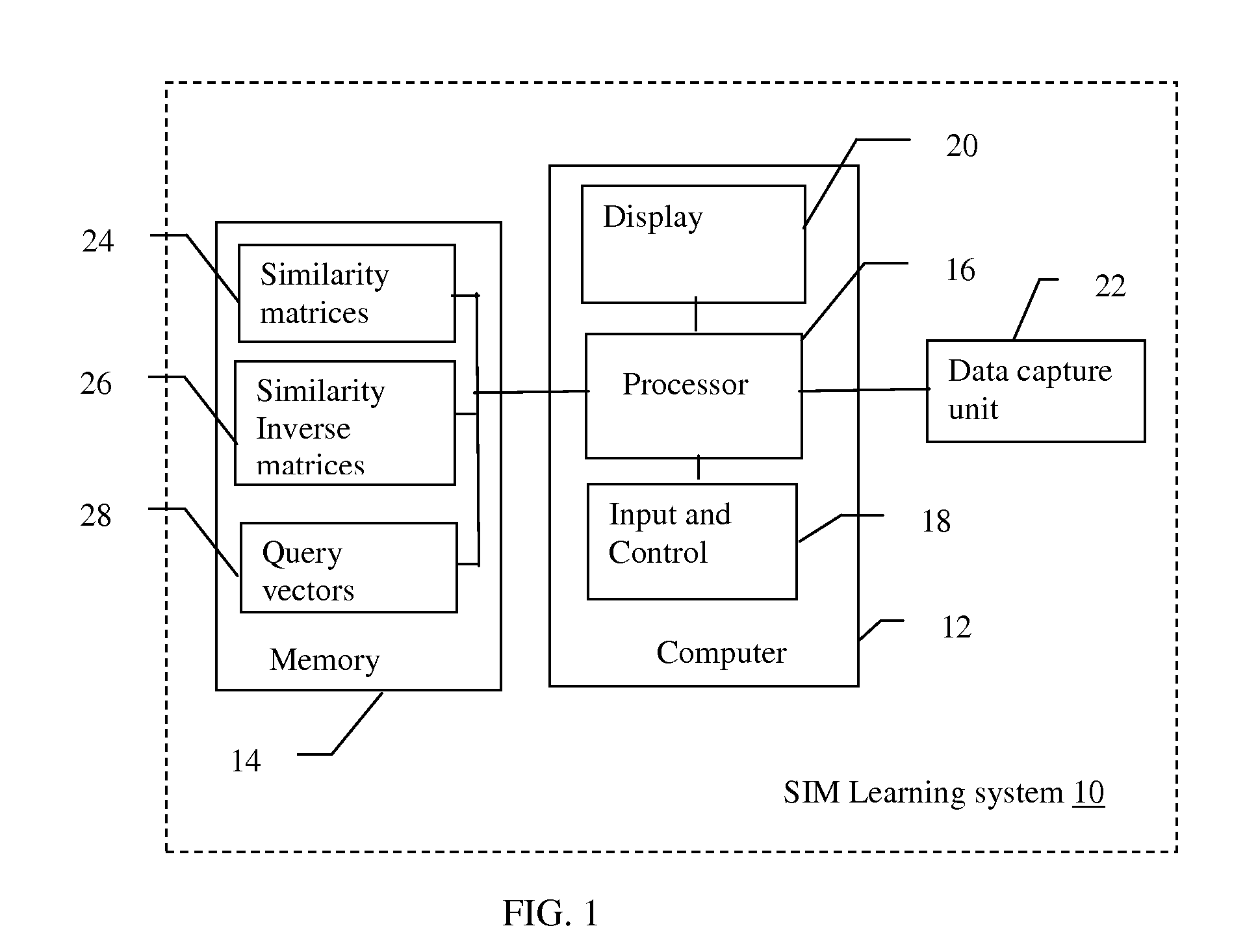

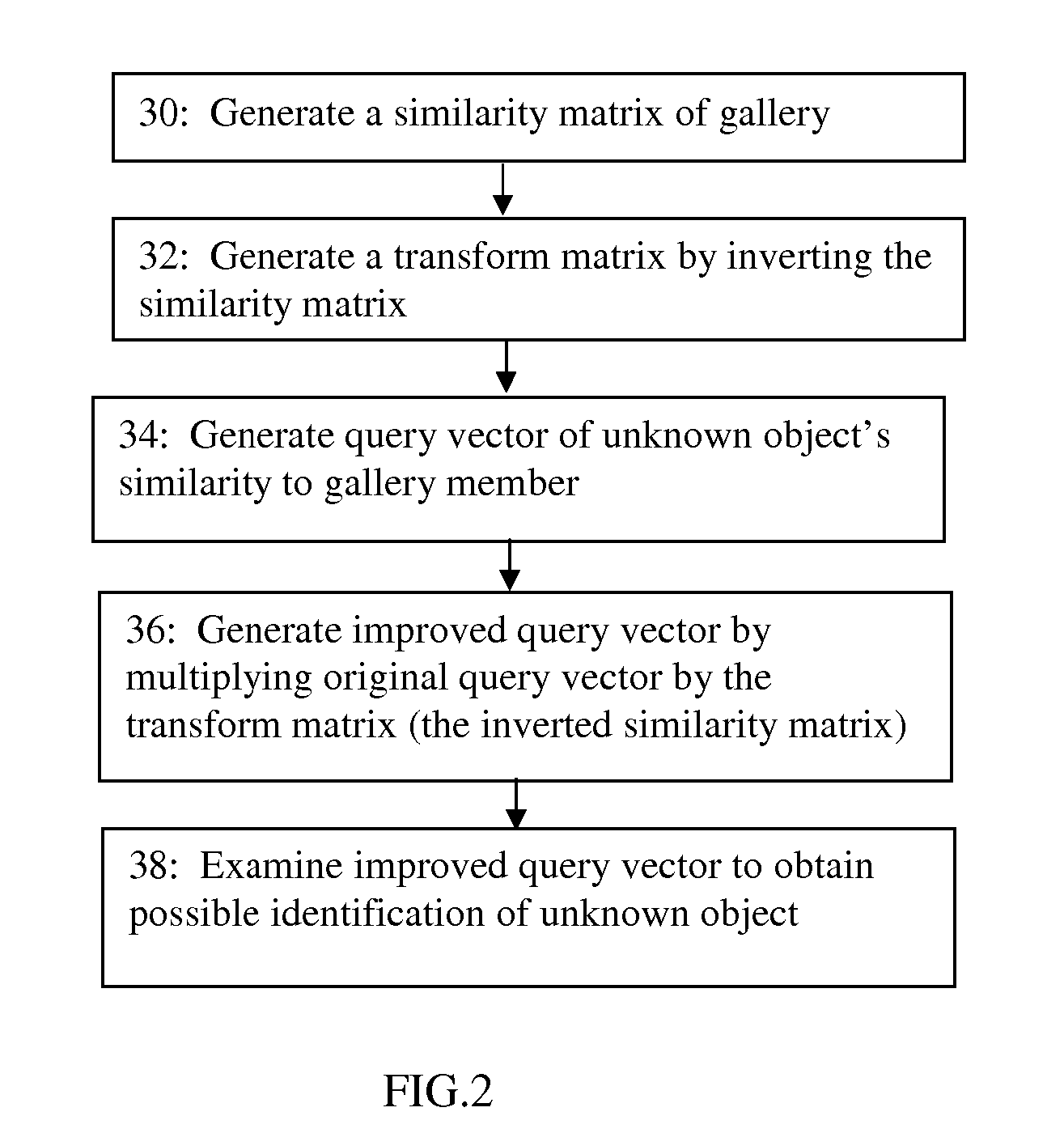

System and Method for Machine Learning using a Similarity Inverse Matrix

InactiveUS20080025596A1Good and consistent resultEasy to useCharacter and pattern recognitionAdaptive controlPattern recognitionEdit distance

A system and method of machine learning that uses an inverse matrix of a reference similarity matrix as a transformation matrix. The reference similarity matrix relates a reference set of objects to themselves using a distance metric such as an image edit distance. The transformation matrix is used to improve the performance of query vectors in classifying or identifying digital representations of an unknown object. The query vector is a measure of similarity between the unknown object and the members of the reference set. Multiplying the query vector by the transformation matrix produces an improved query vector having improved similarity scores. The highest improved similarity score indicates the best match member of the reference set If the similarity score is high enough, the unknown object may either be classified as belonging to the same class, or recognized as being the same object, as the best match object.

Owner:D& S CONSULTANTS

Input device enhanced interface

ActiveUS8843844B2Improve efficiencyIncreases expressivityInput/output for user-computer interactionCathode-ray tube indicatorsGraphicsOperation mode

Some embodiments provide an interactive viewer for an input device interface. Specifically, some embodiments provide a Keyboard Enhanced Interface (KEI) system that includes a KEI viewer. The KEI viewer includes multiple graphical keys that correspond to keys of a key based input device. The KEI viewer also includes multiple symbols that identify different output actions and logic for presenting a set of symbols over a set of graphical keys to identify a set of keys of the key based input device that are usable to directly invoke a set of output actions based on an active operational mode of the KEI system. A symbol identifies a particular output action that is directly invocable with a press of a key of the key based input device that corresponds to a graphical key over which said symbol is presented.

Owner:INTELLITACT

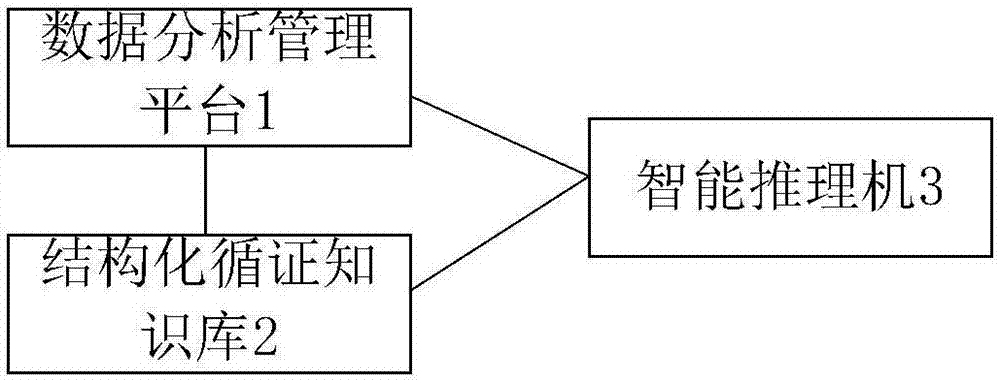

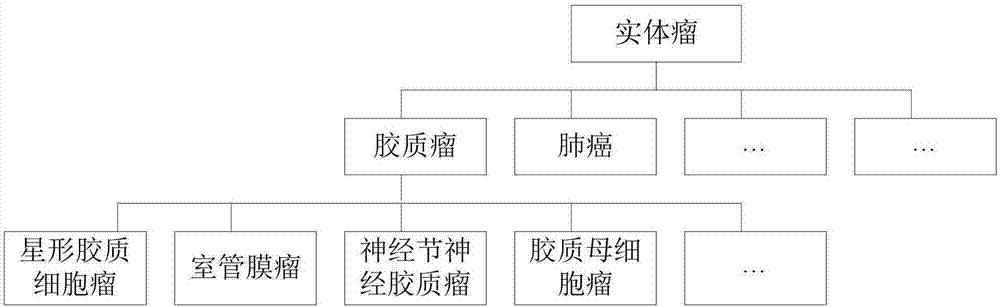

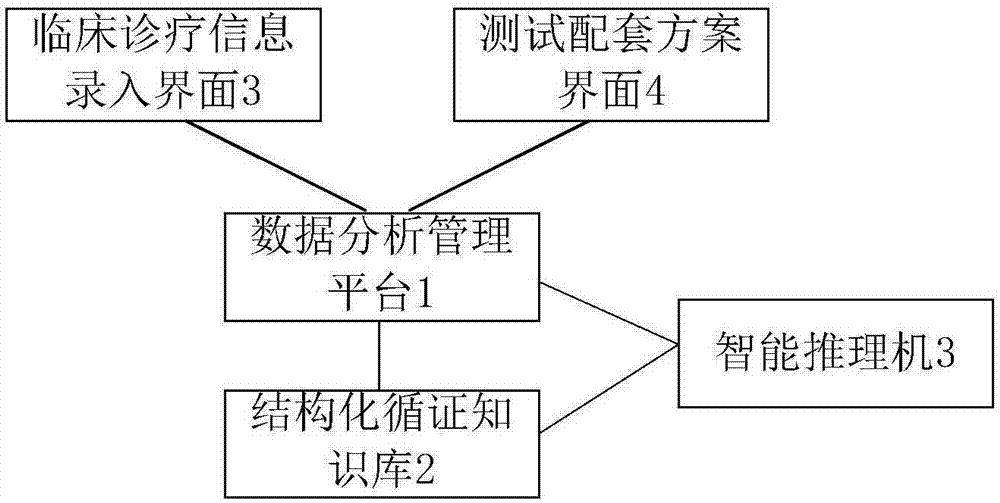

Clinical decision support system and method

InactiveCN106971071AImprove accuracyImprove referenceMedical automated diagnosisSpecial data processing applicationsRNAMetabolome

The invention provides a clinical decision support system and method. The system comprises a data analysis management platform, a structured evidence-based knowledge base and an intelligent inference machine, wherein the data analysis management platform stores and processes patient data, detects the data according to biomarkers, and generates omics variation data of the patient; the structured evidence-based knowledge base stores clinical phenotype data, biomarker detection data, the omics variation data, drug diagnosis and treatment research information and evidence-based clinical annotations, and establishes a rule of correlation among the data; and the intelligent inference machine, according to the clinical phenotype data and the omics variation data of the patient, calls the structured evidence-based knowledge base to generate clinical decision reference information. Based on the structured evidence-based knowledge base, omics variation is introduced, so that clinical decision is supported in gene level, and DNA, RNA, protein, metabolome and epigenome level variation is covered; and by performing analysis and evidence-based annotation on the omics variation data, the reference information is provided for the clinical decision, so that the accuracy and reference of clinical decision support are improved.

Owner:为朔医学数据科技(北京)有限公司

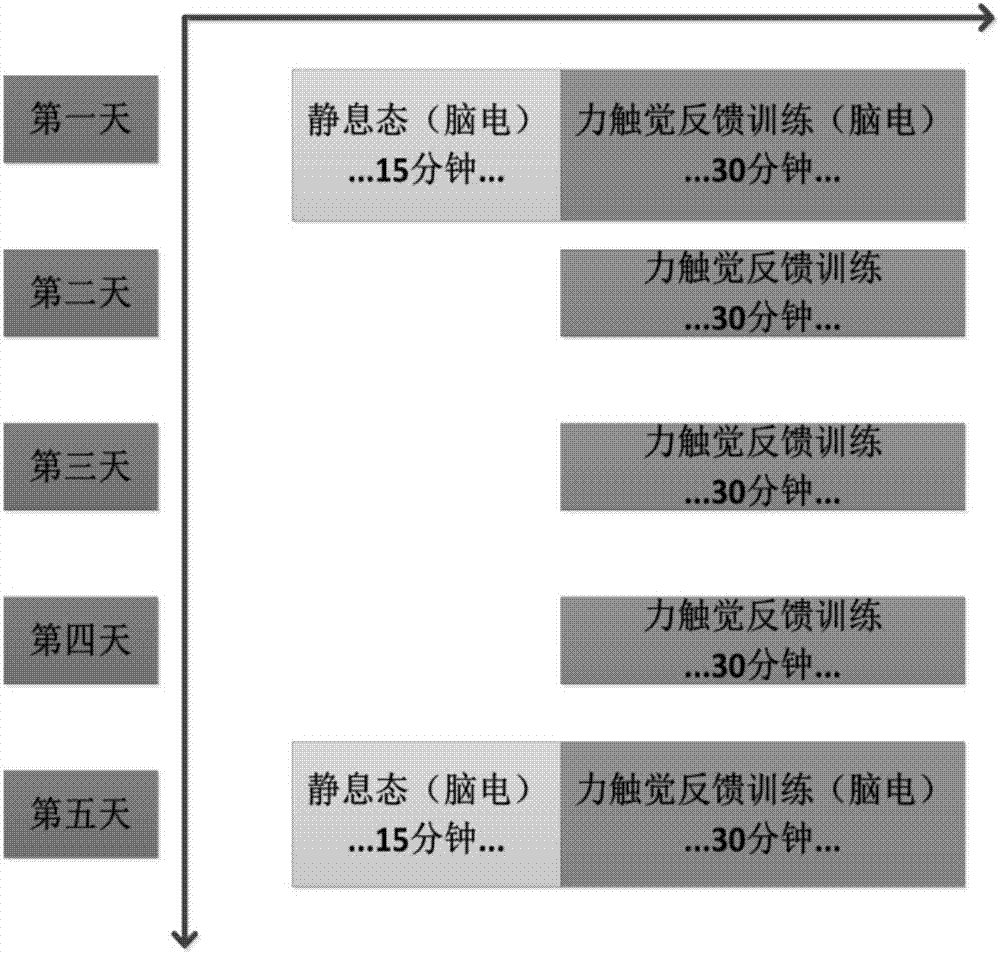

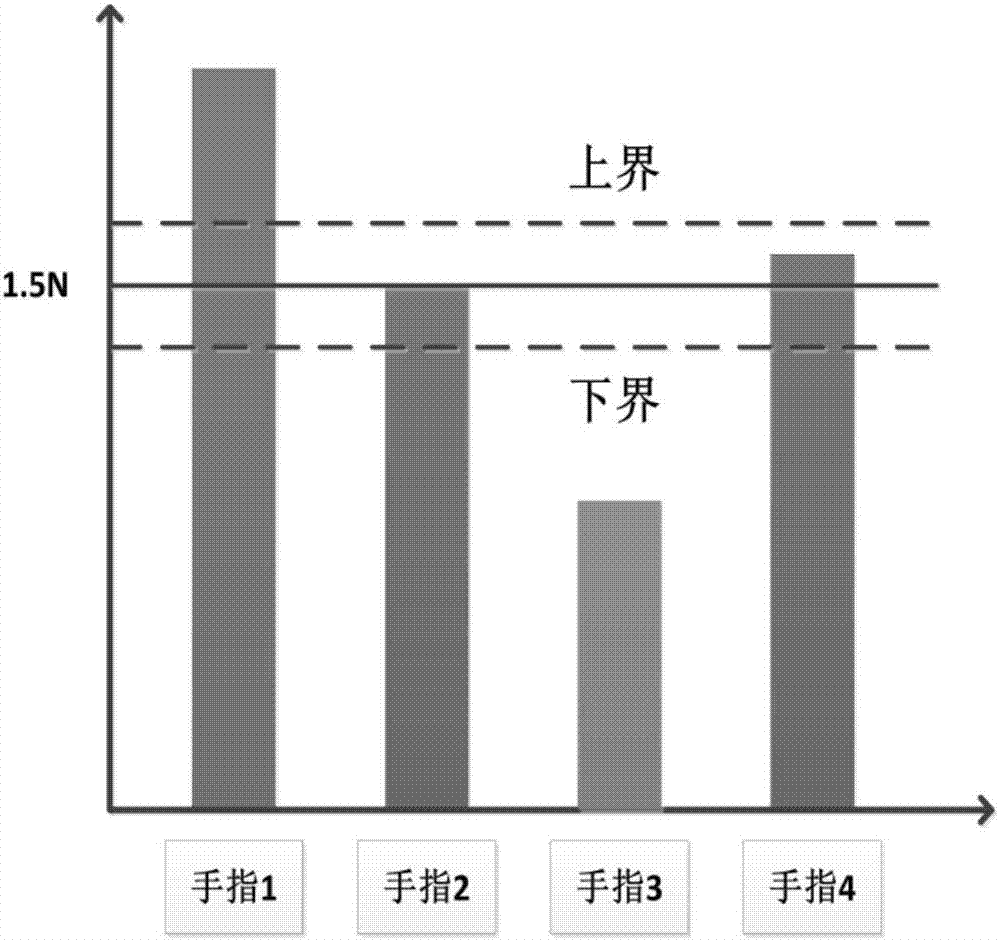

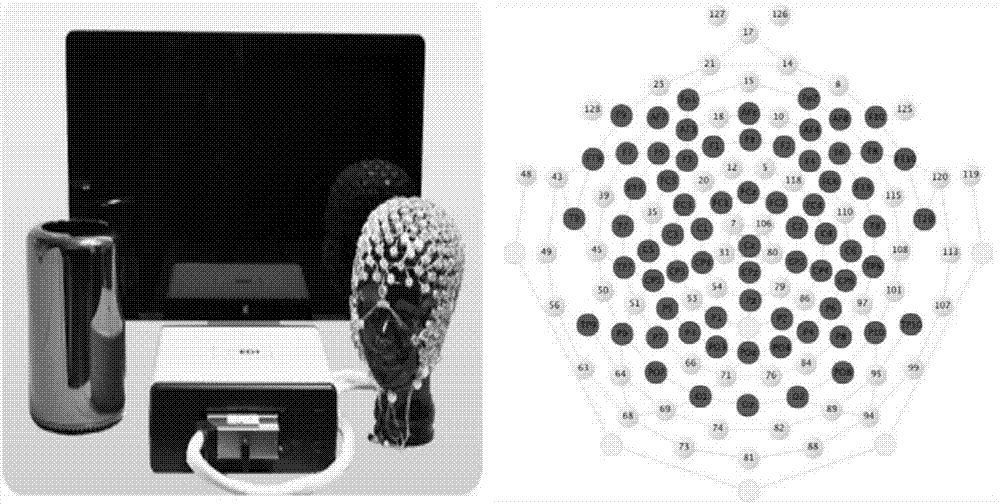

Attentiveness training and evaluation device based on force tactile-sensation feedback and electroencephalic signal analysis

ActiveCN107577343AImprove referenceReal-time monitoring statusInput/output for user-computer interactionGraph readingTactile sensationEeg signal analysis

The invention discloses an attentiveness training and evaluation device based on force tactile-sensation feedback and electroencephalic signal analysis. The device includes a force tactile-sensation training unit, an electroencephalic recording unit and a control unit. The force tactile-sensation training unit is used to send finger touch force data of a trainee to the control unit. The electroencephalic recording unit is used to send electroencephalic signals of the trainee in a training process to the control unit. The control unit includes a training module, an evaluation module and a control module. The training module is used to store training modes. The evaluation module evaluates data fed back by the force tactile-sensation training unit and the electroencephalic recording unit. Thecontrol module adaptively adjusts training difficulty according to an evaluation result. A physiological index and a behavioral index which characterize an attentiveness level are obtained at the same time, the attentiveness level of the subject can be improved in a short term, an anastomosis degree between the obtained physiological index and behavioral index is very high, and the attentivenesslevel of the trainee can be reliably analyzed and evaluated.

Owner:BEIHANG UNIV

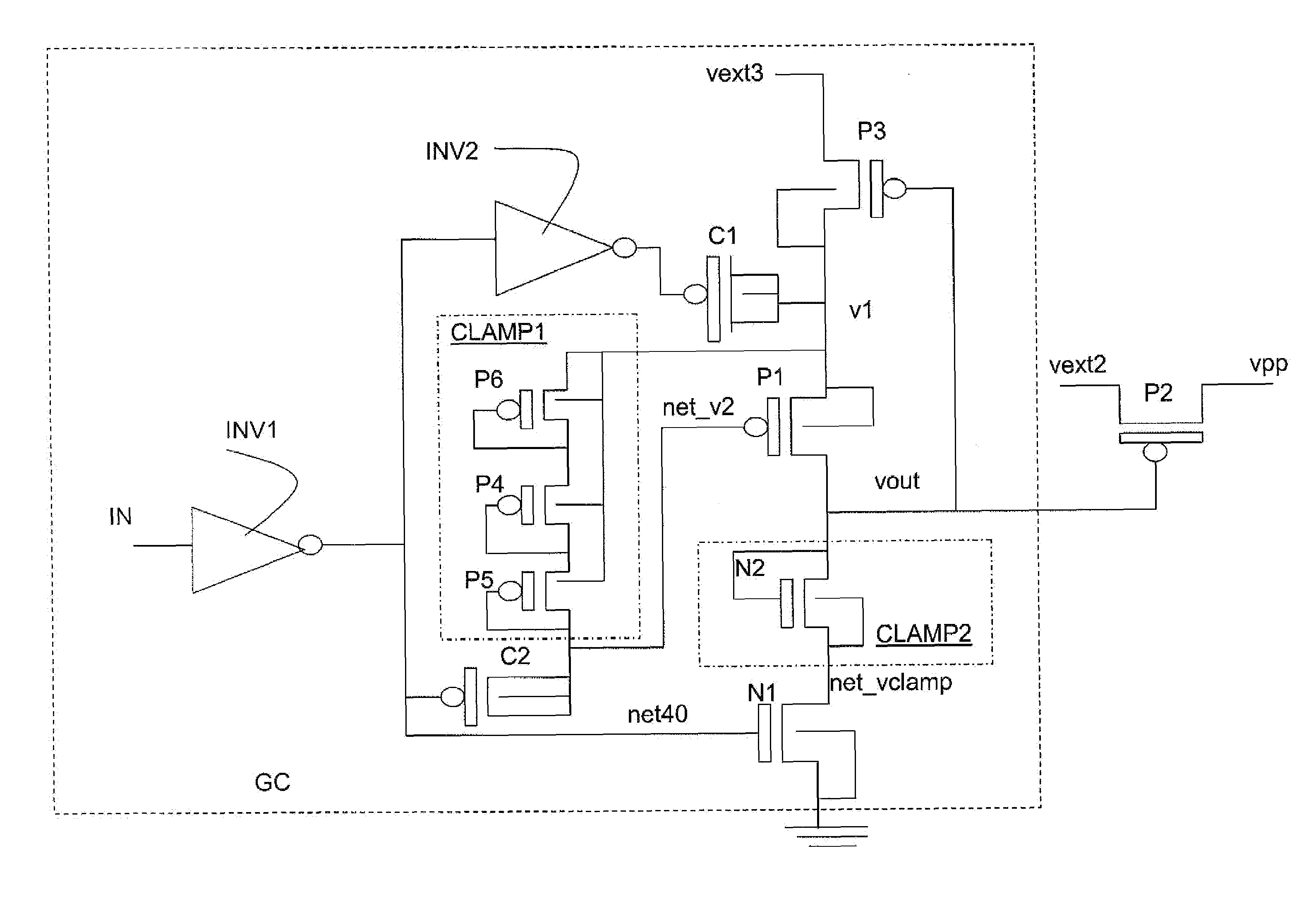

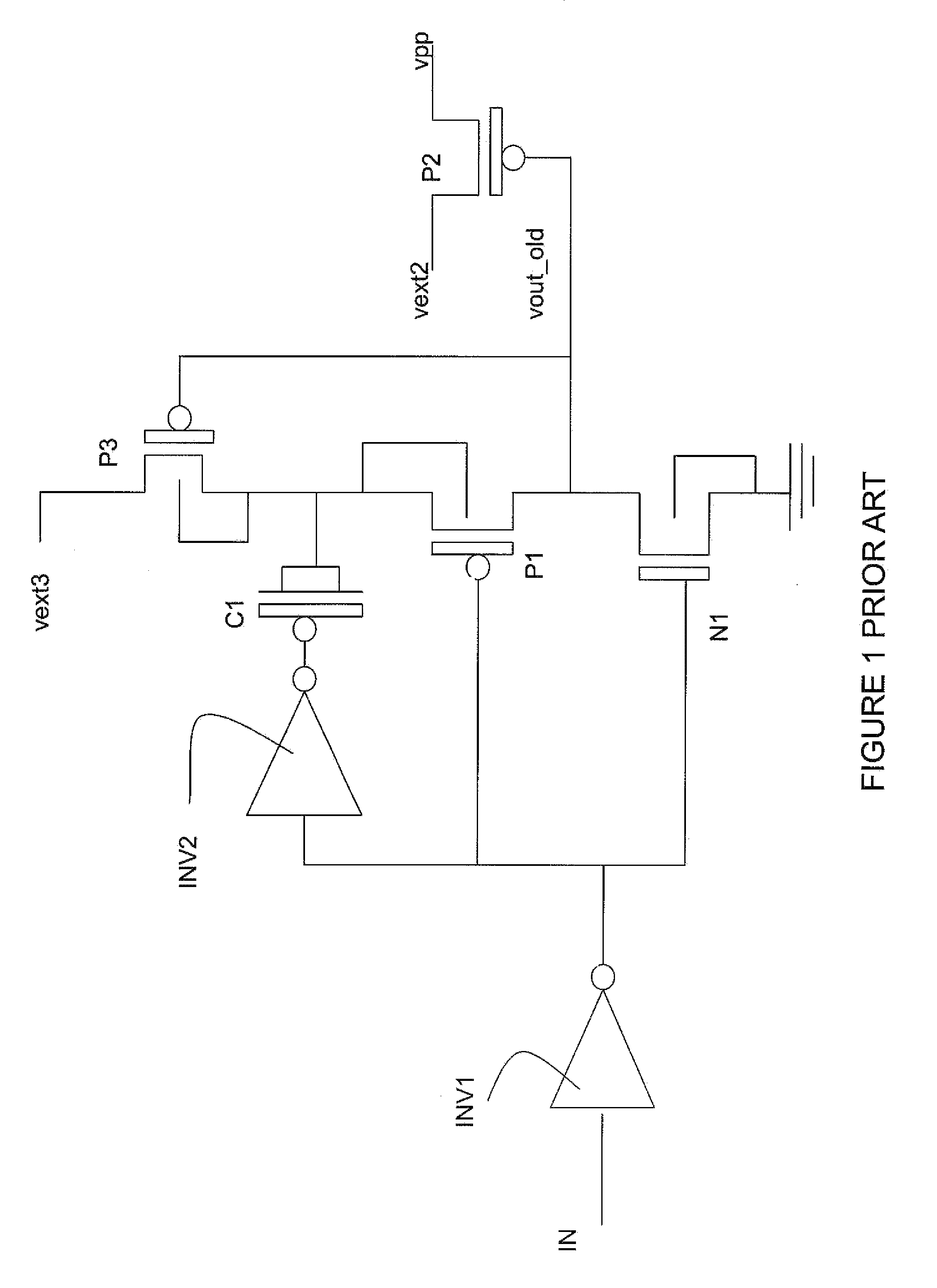

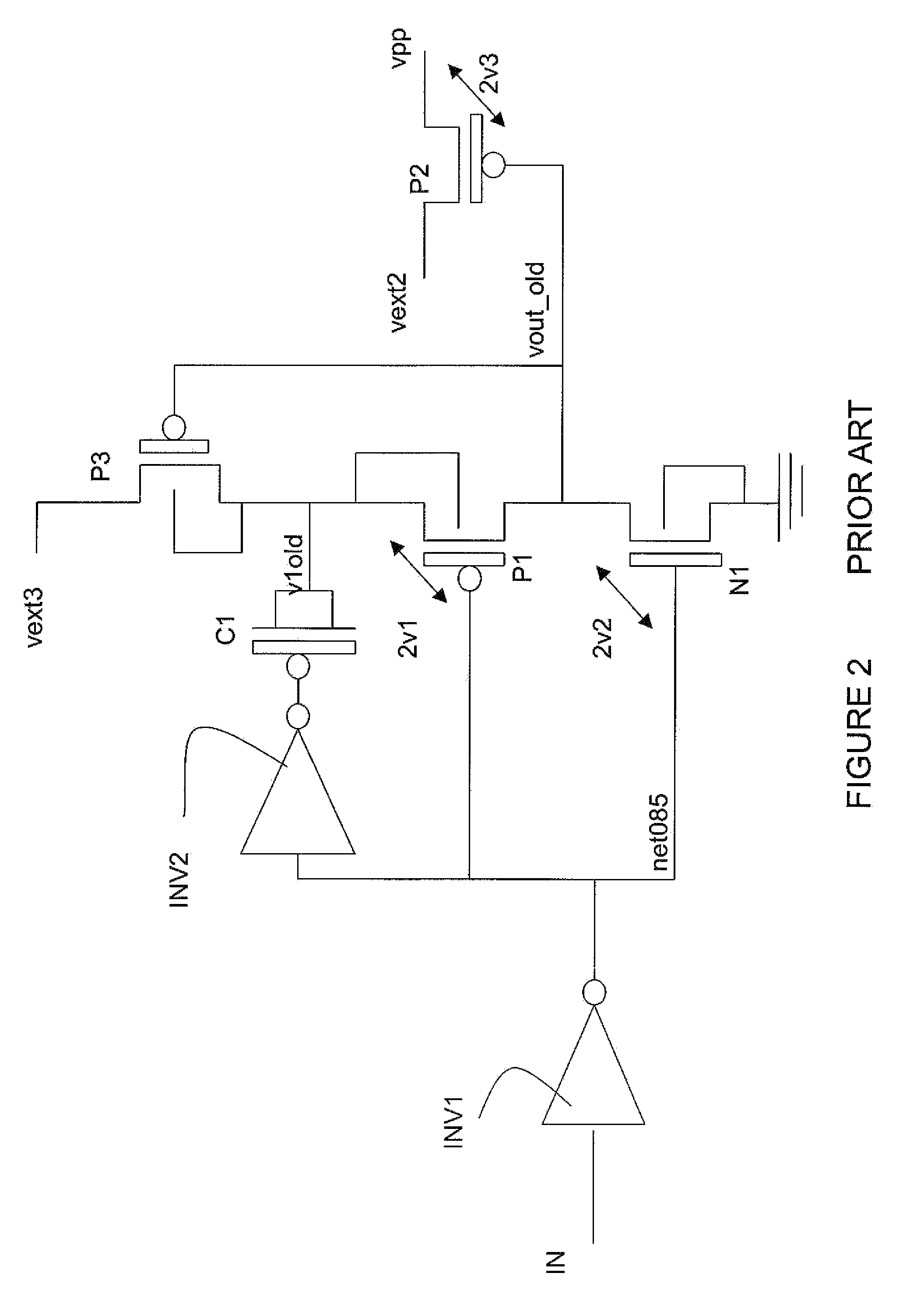

Circuit and method for a gate control circuit with reduced voltage stress

InactiveUS7592858B1Improve operationHigh operatingTransistorPulse automatic controlGate controlControl circuit

Circuit and method for a gate control output circuit having reduced voltage stress on the devices is disclosed. In a circuit of MOS transistors for supplying an output to control a transfer gate, the output having a high voltage level that exceeds a supply voltage, first and second clamping circuits are provided. The first clamping circuit ensures a voltage between the gate and the source / drain and drain / source of a PMOS transistor that couples a pumped voltage to the output does not exceed a predetermined voltage. The second clamping circuit ensures that the voltage between the gate of an NMOS transistor and the output which is coupled to the drain / source of the NMOS transistor does not exceed a predetermined amount. The clamping circuits prevent gate stress problems on the transistors by ensuring the voltages between the gates and the source / drain and drain / source terminals do not exceed predetermined voltages.

Owner:TAIWAN SEMICON MFG CO LTD

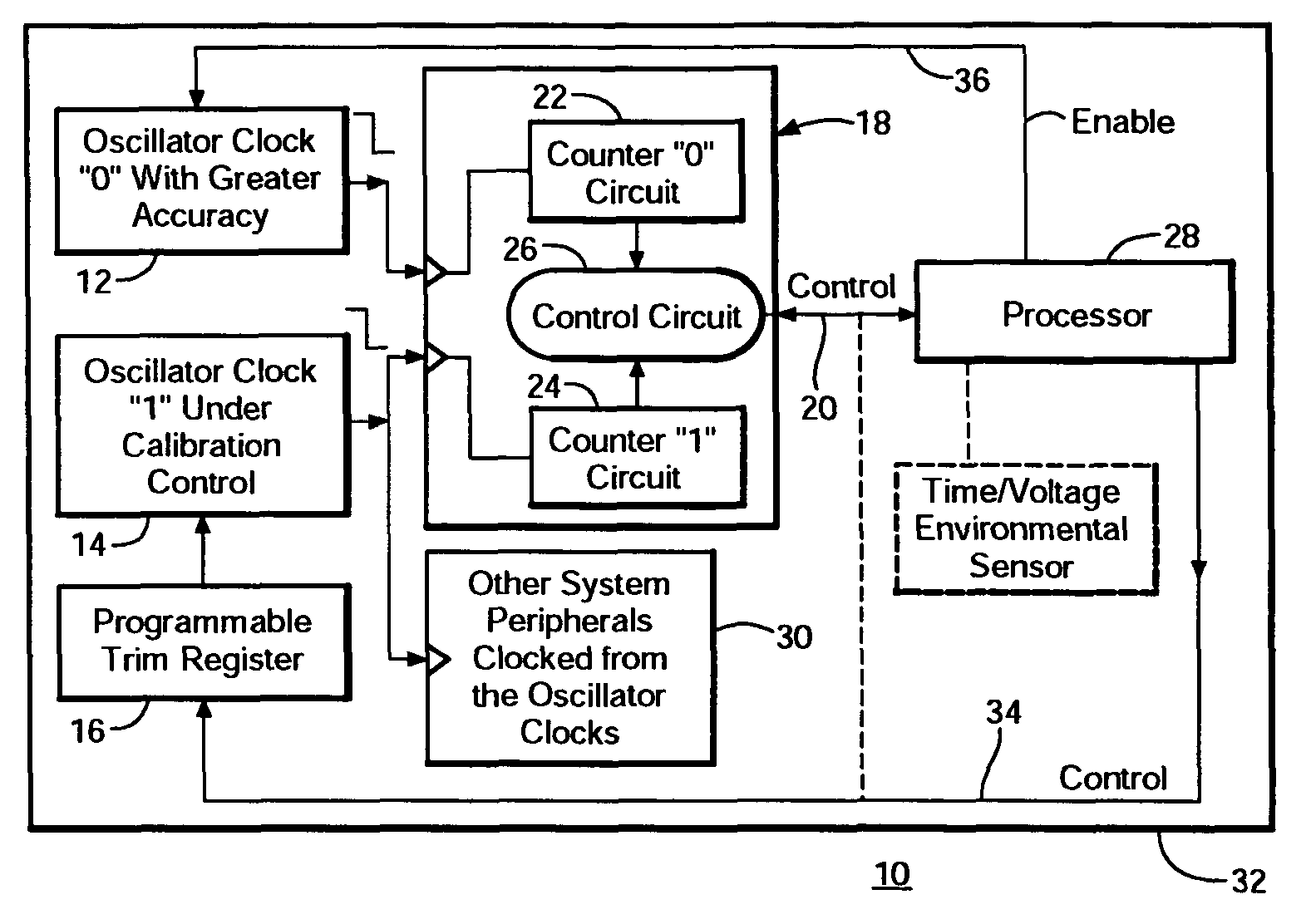

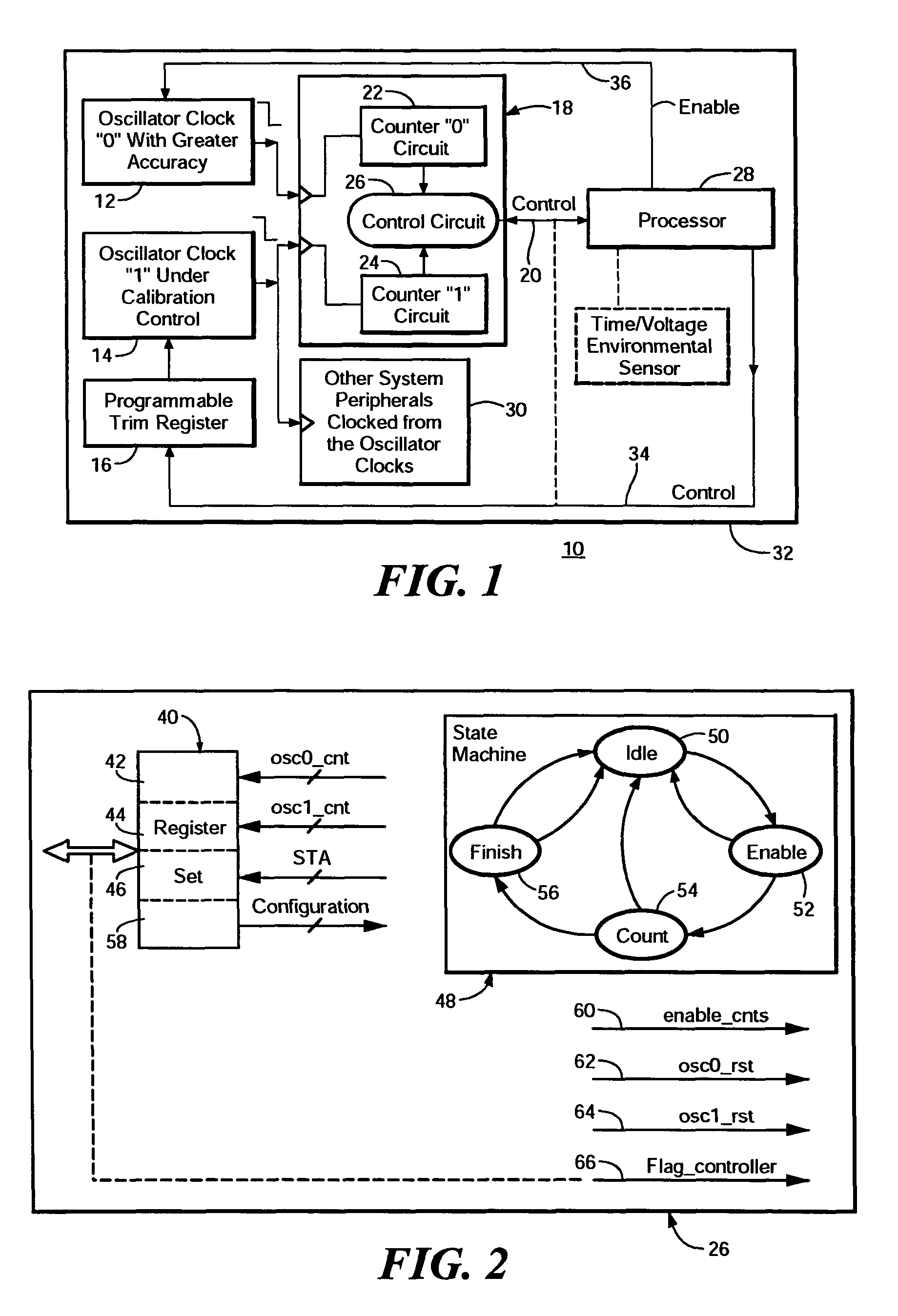

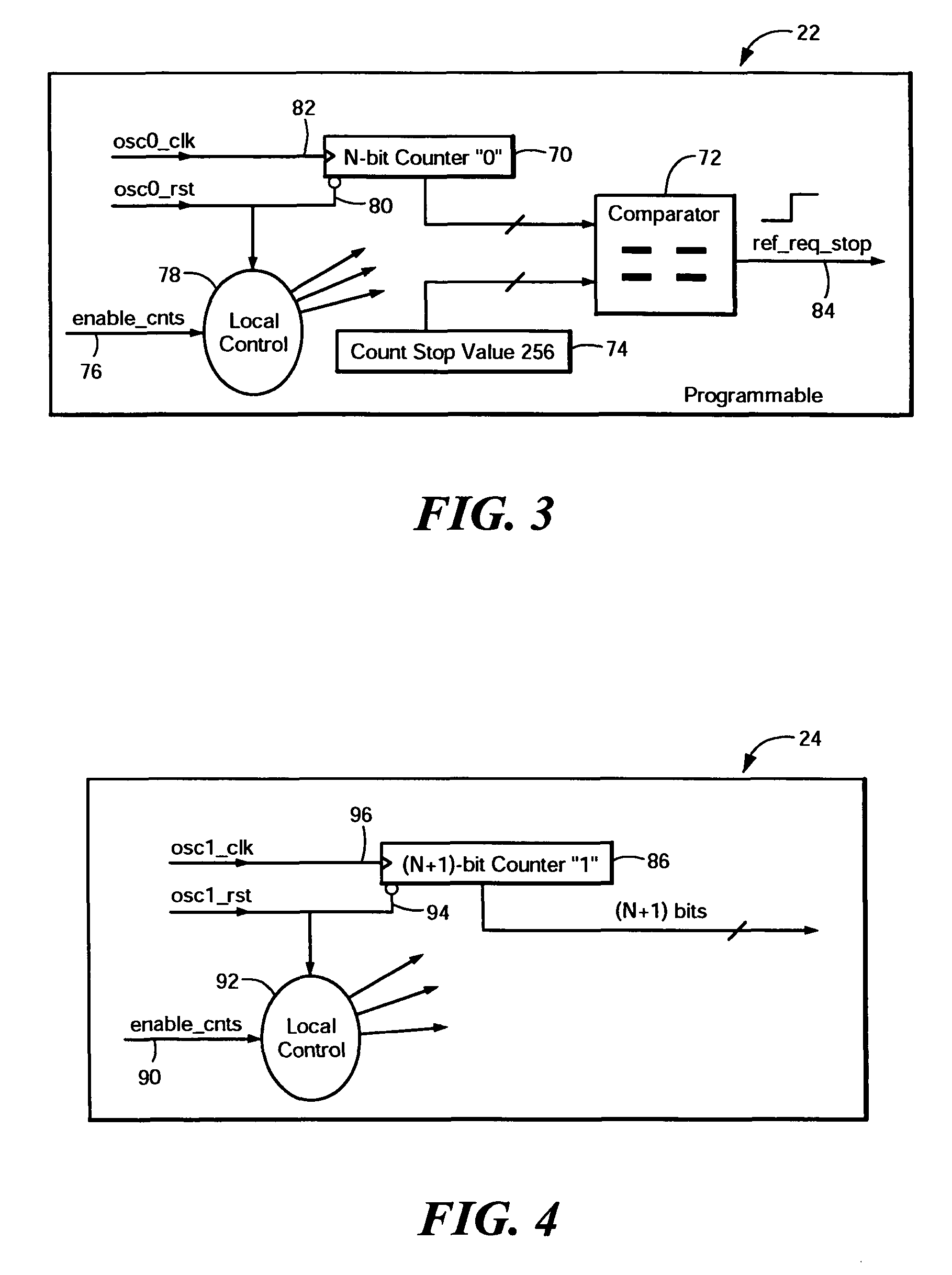

Microprocessor programmable clock calibration system and method

ActiveUS7890787B2Improve accuracyLow powerReceiver initialisationPulse automatic controlMicroprocessorPhysics

A microprocessor programmable clock calibration device compares, in response to a calibration command from a programmable processor, turns on a normally off reference oscillator clock, compares the frequency of the reference oscillator clock with the frequency of a calibratable oscillator clock, turns off the reference oscillator clock and adjusts, in response to a difference in those frequencies, the frequency of the calibratable oscillator clock towards that of the reference oscillator clock.

Owner:ANALOG DEVICES INC

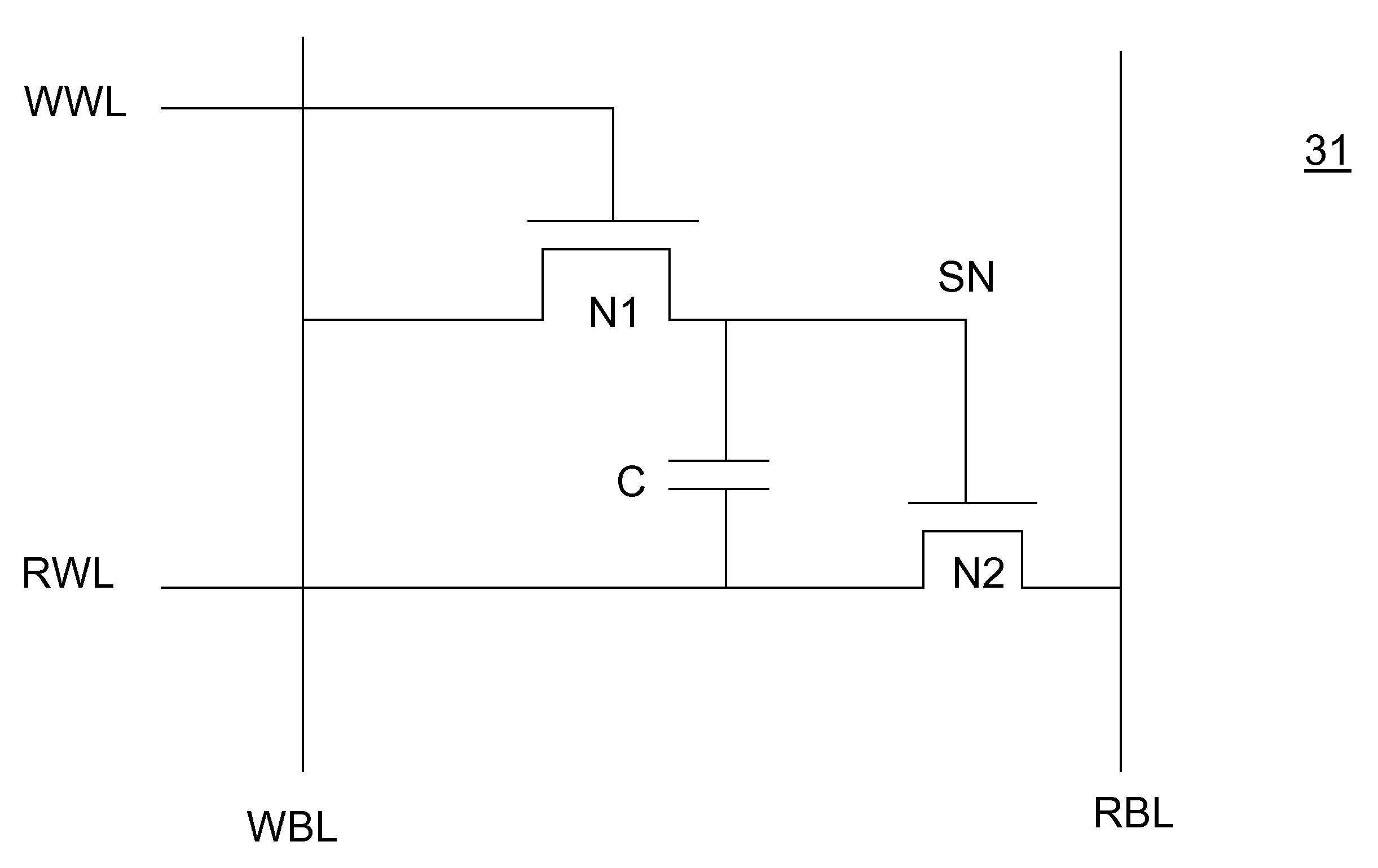

Circuit for high speed dynamic memory

A memory cell includes a write access transistor coupled between a storage node and a write bit line, and active during a write cycle responsive to a voltage on a write word line; a read access transistor coupled between a read word line and a read bit line, and active during a read cycle responsive to a voltage at the storage node; and a storage capacitor coupled between the read word line and the storage node. Methods for operating the memory cell are also disclosed.

Owner:TAIWAN SEMICON MFG CO LTD

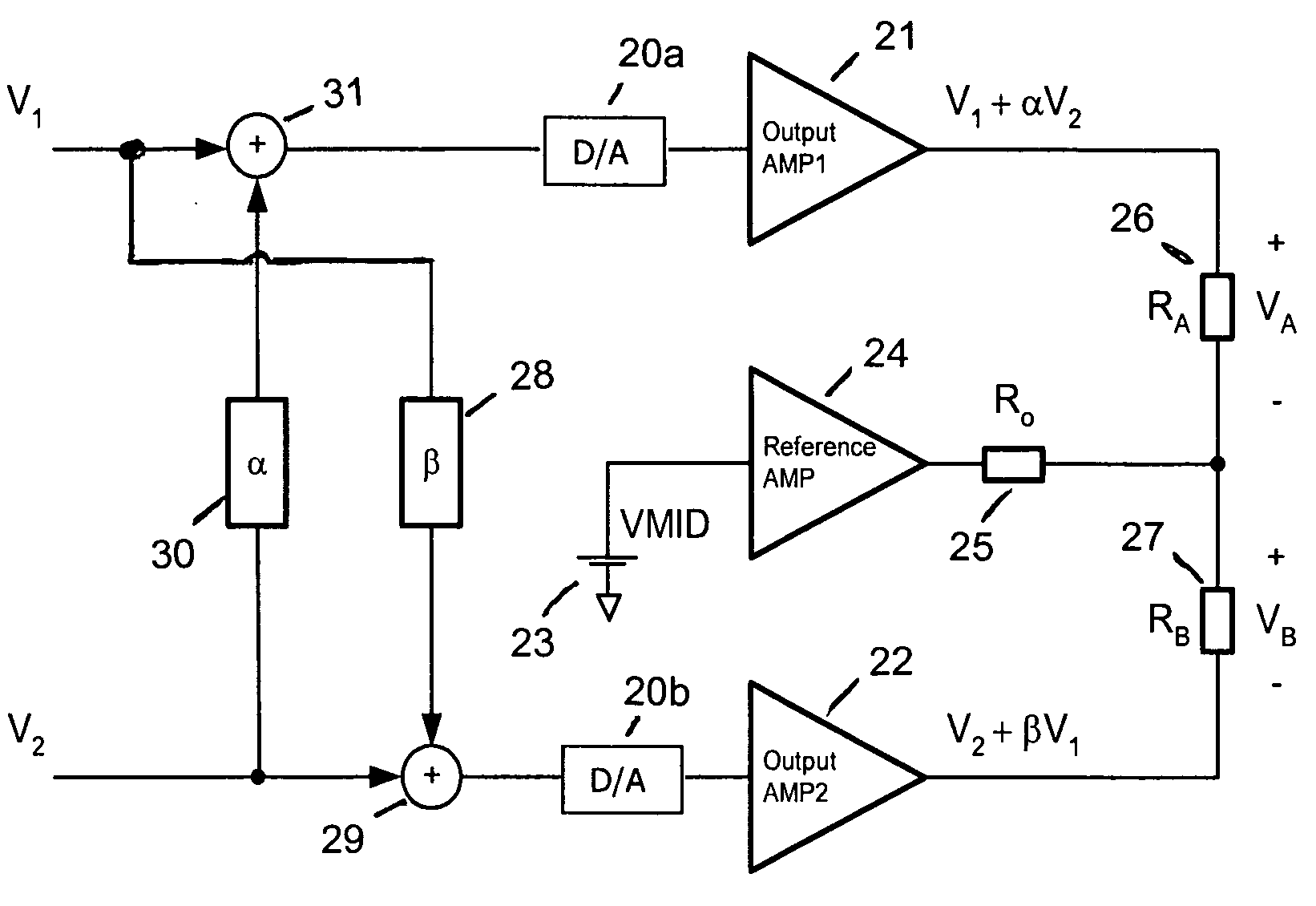

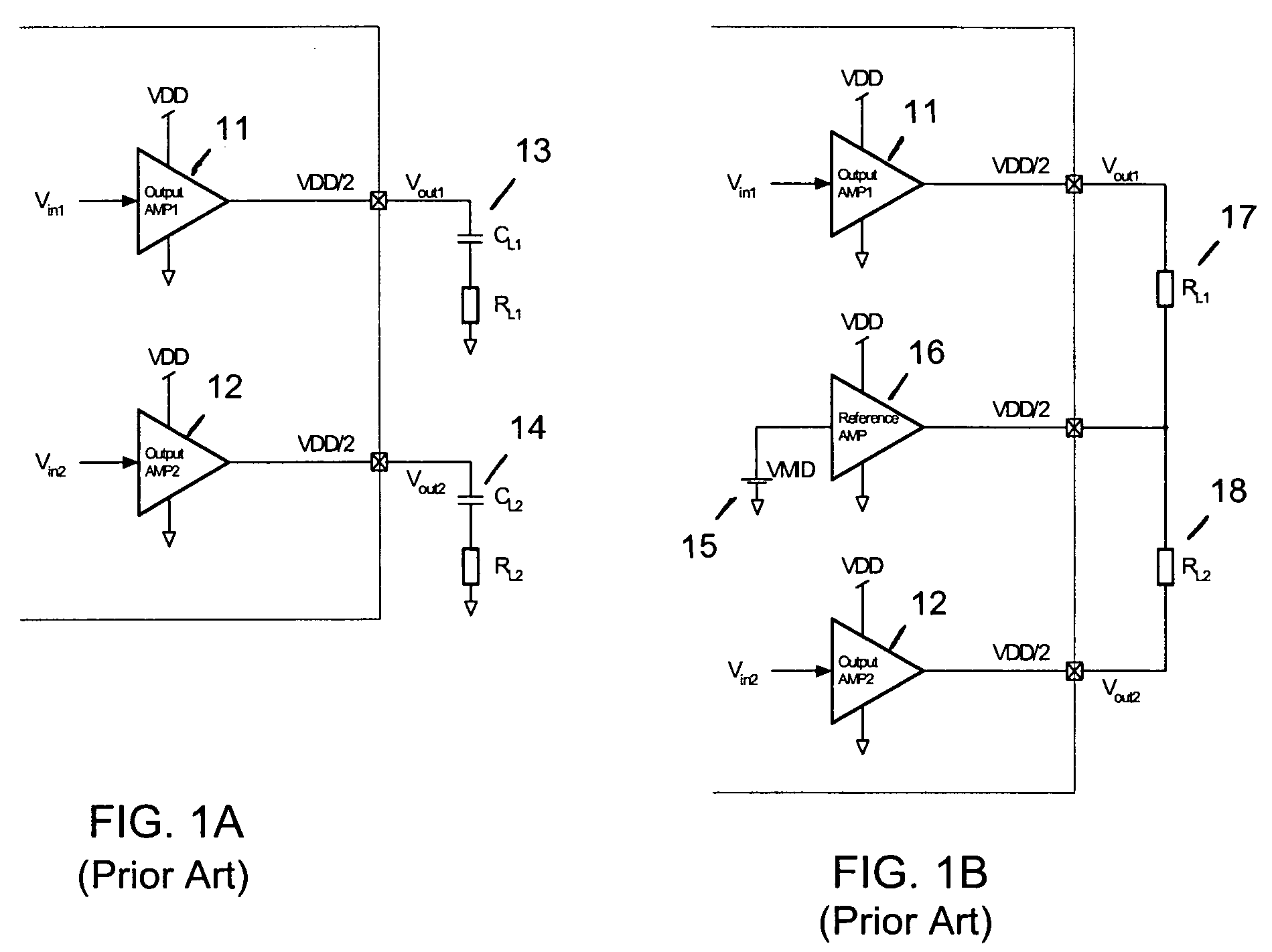

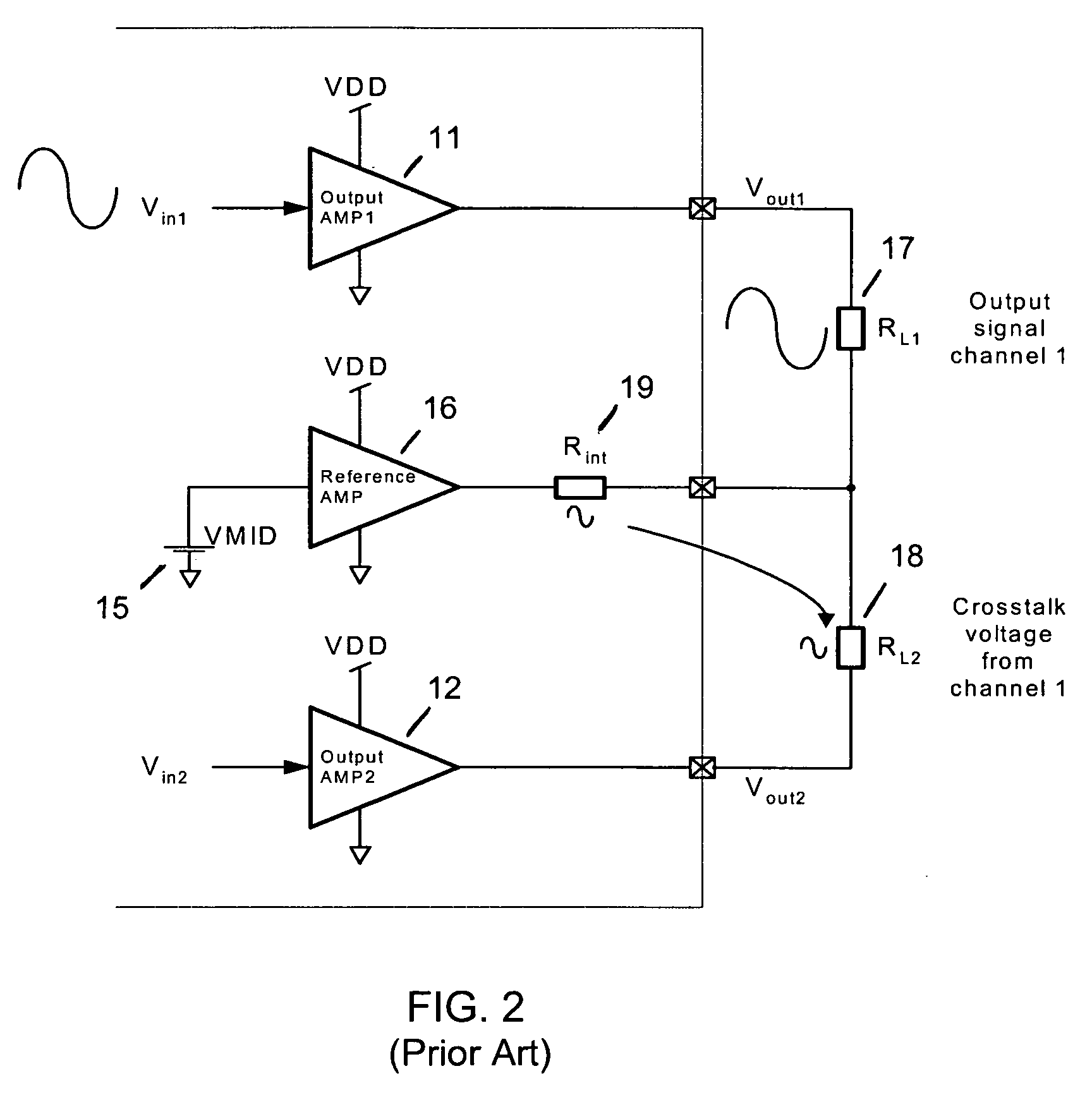

Crosstalk cancellation using load impedence measurements

ActiveUS20080008325A1Low costCancel improvementHeadphones for stereophonic communicationBroadcast circuit arrangementsCrosstalk cancellationAudio power amplifier

A method and ASIC for canceling crosstalk between a first stereo channel and a second stereo channel, wherein a first signal is input to a first output amplifier for the first channel, and a second signal is input to a second output amplifier for the second channel, and an output load for each output amplifier is connected between each output amplifier and a reference amplifier. In one embodiment, the first and second signals are split prior to inputting the signals to the first and second output amplifiers, and a gain-adjusted portion of each signal is added to the other signal on the inputs of the output amplifiers. In another embodiment, the first and second input signals are again split into two paths each. While a first path of each signal is inputted to each signal's respective output amplifier, the second paths of the first and second signals are adding together. The resulting sum is adjusted by a gain function, biased by a suitable DC voltage, and input to the reference amplifier.

Owner:TELEFON AB LM ERICSSON (PUBL)

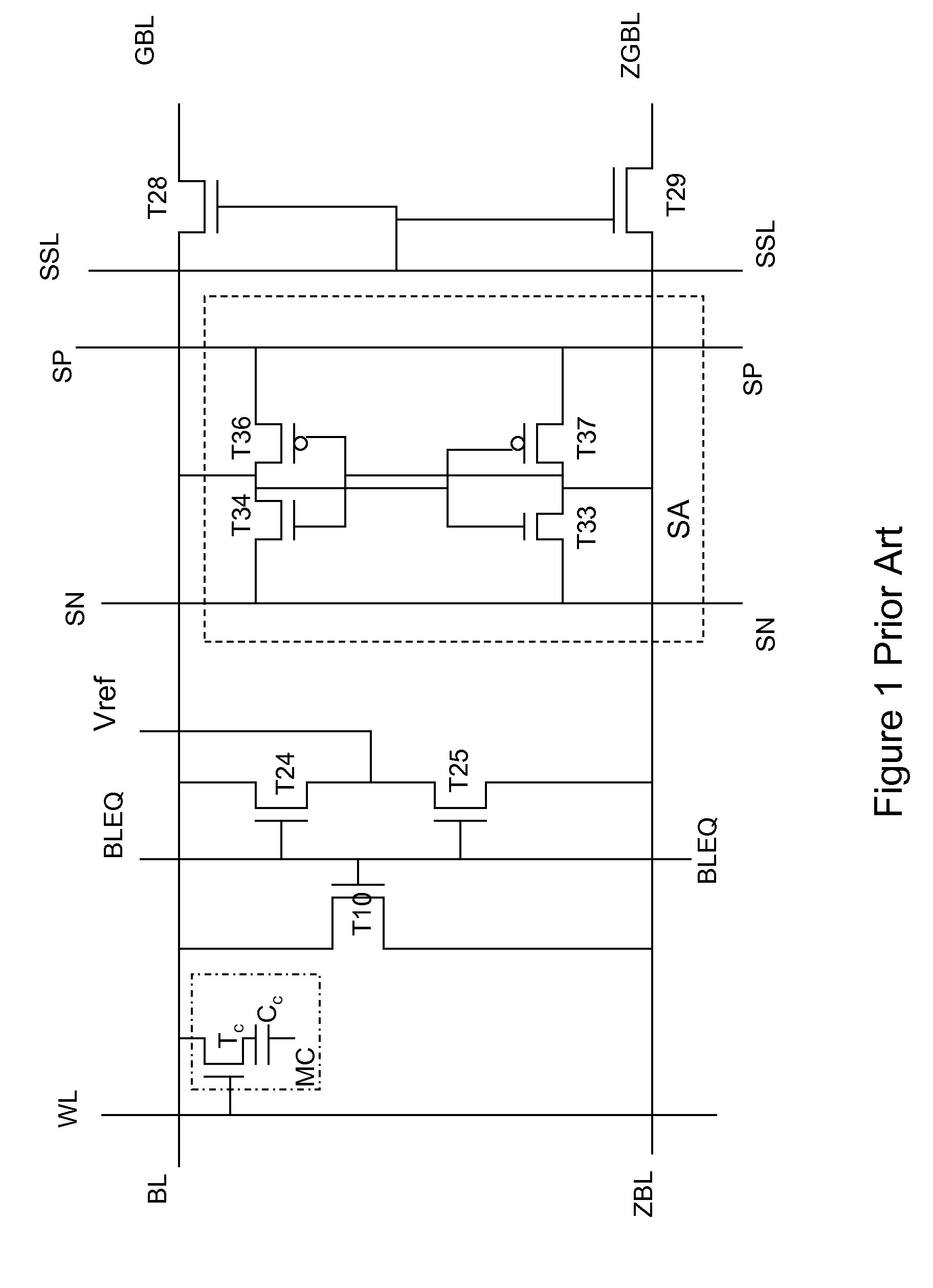

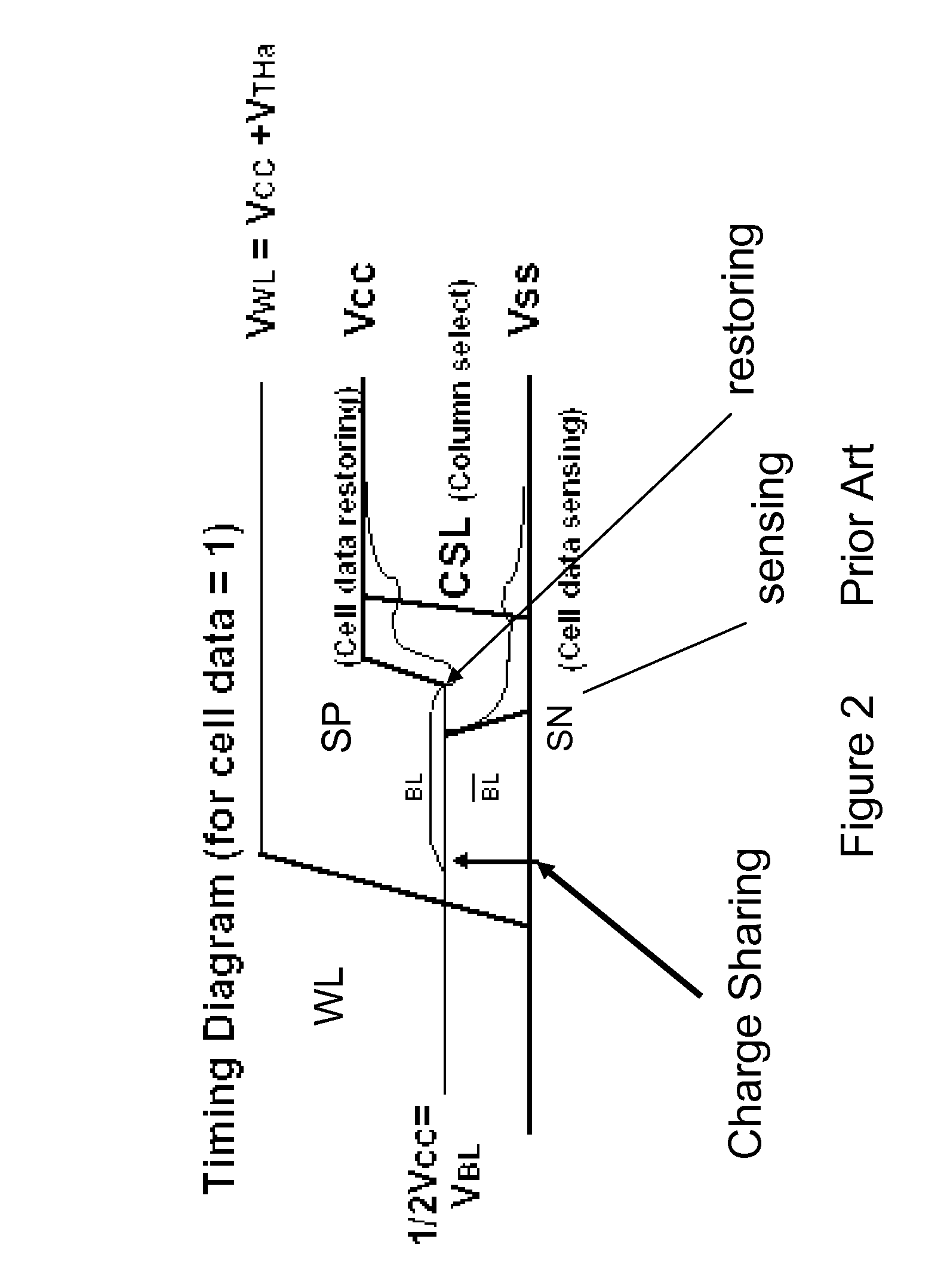

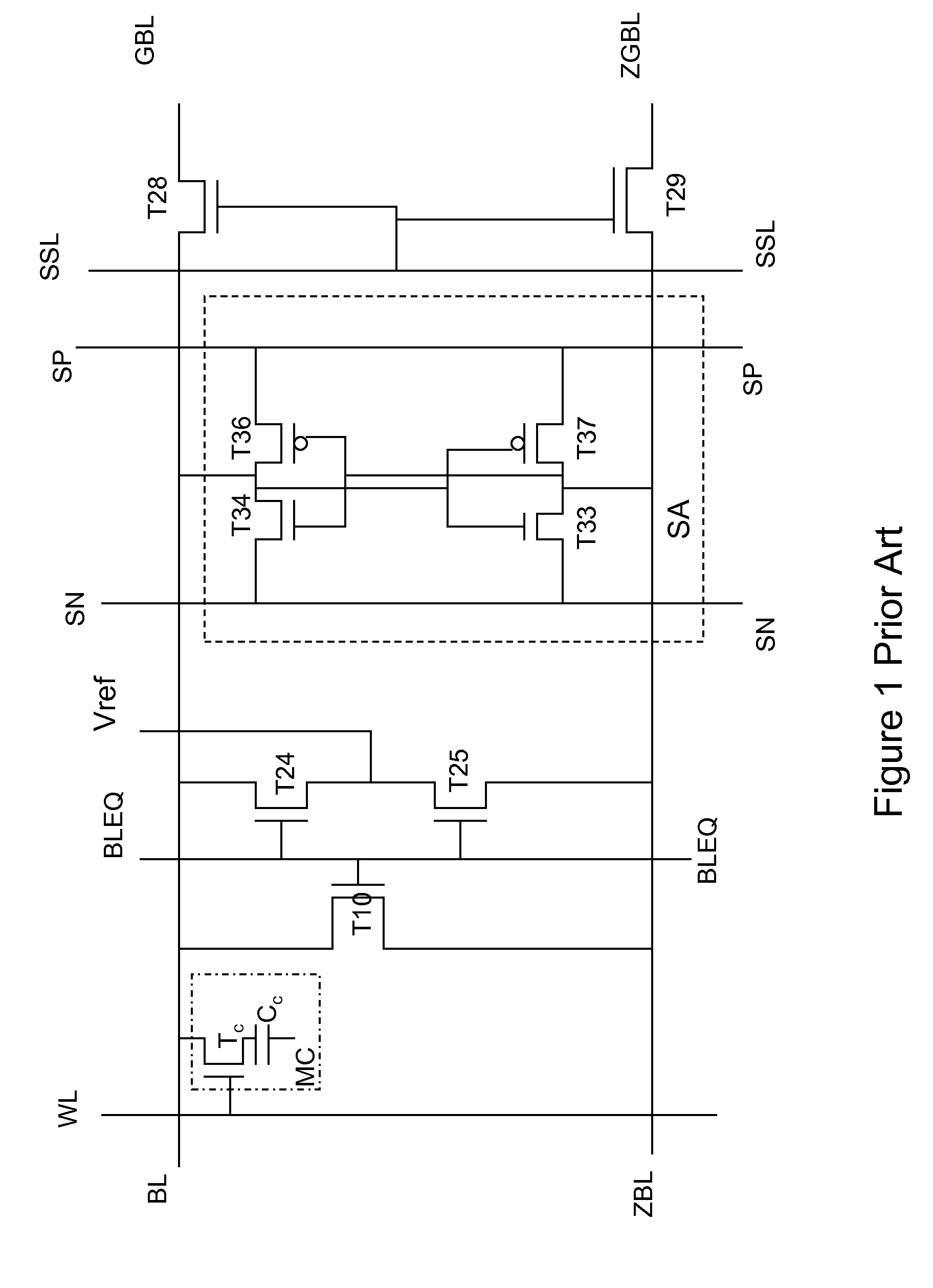

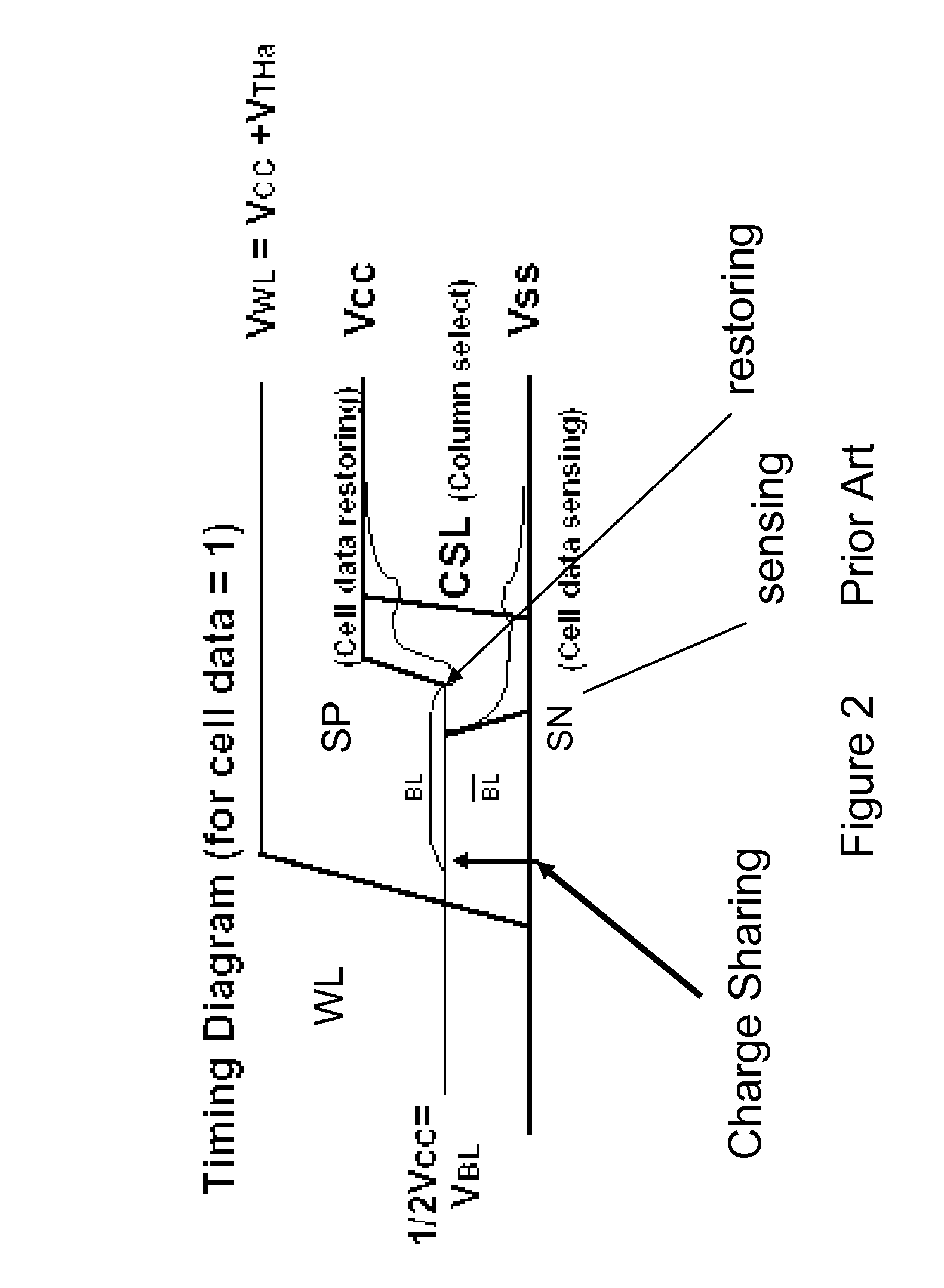

Circuit and Method for a Vdd Level Memory Sense Amplifier

A circuit and method for a sense amplifier for sensing the charge stored by a memory cell is disclosed. The memory cell is coupled to a bit line, a complementary bit line and a differential sense amplifier is coupled to the bit line and the complementary bit line. A control signal couples a reference voltage to the complementary bit line. A positive precharge voltage is applied to the bit line and complementary bit line prior to the sense amplifier being enabled. The memory cell outputs a voltage to the bit line responsive to a word line, and the sense amplifier senses the differential voltage between the bit line and the complementary bit line responsive to a sense enable signal. A voltage regulator for generating the reference voltage, preferably about 80% of a positive supply voltage, is disclosed. A method of sensing data stored by a memory cell is disclosed.

Owner:TAIWAN SEMICON MFG CO LTD

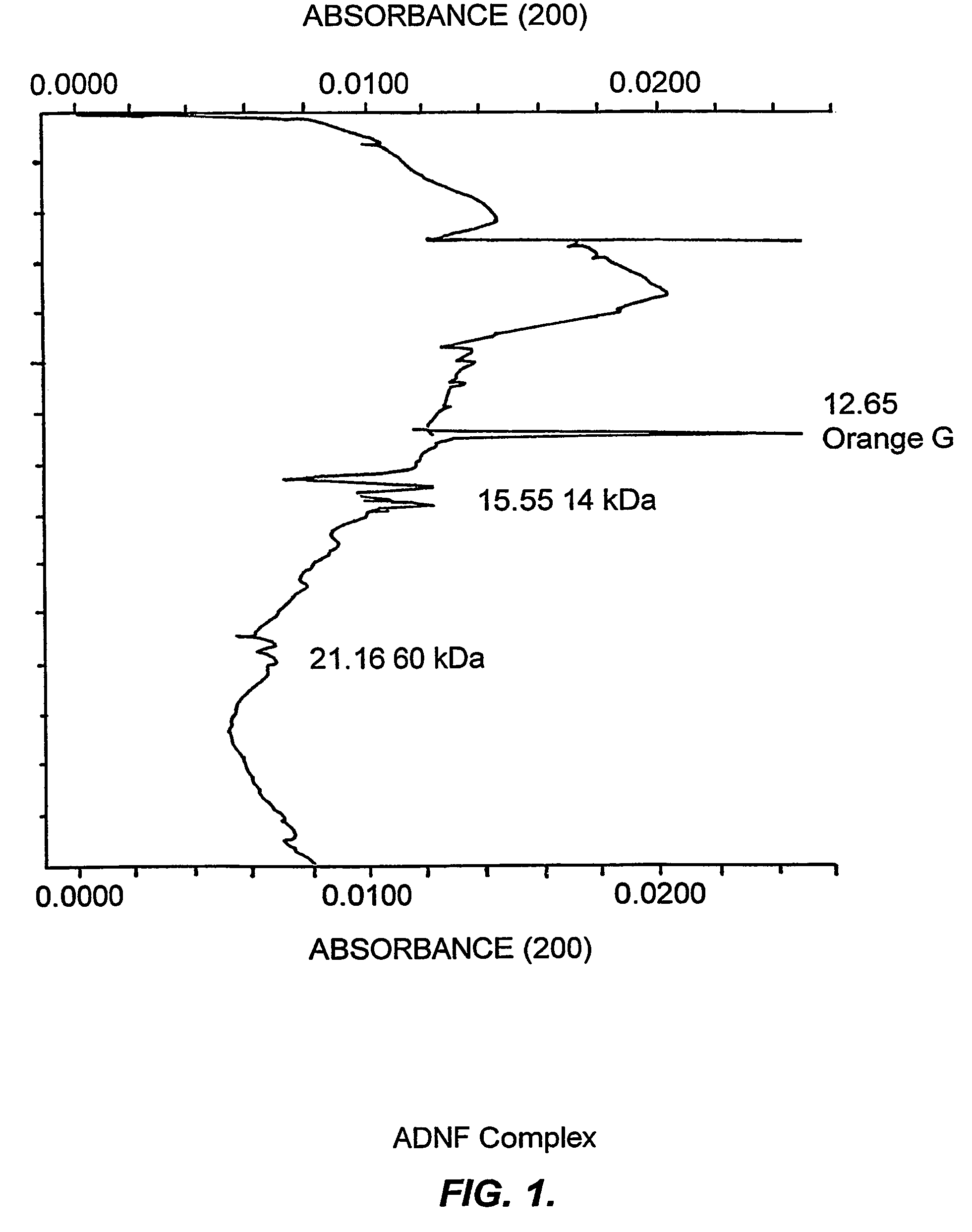

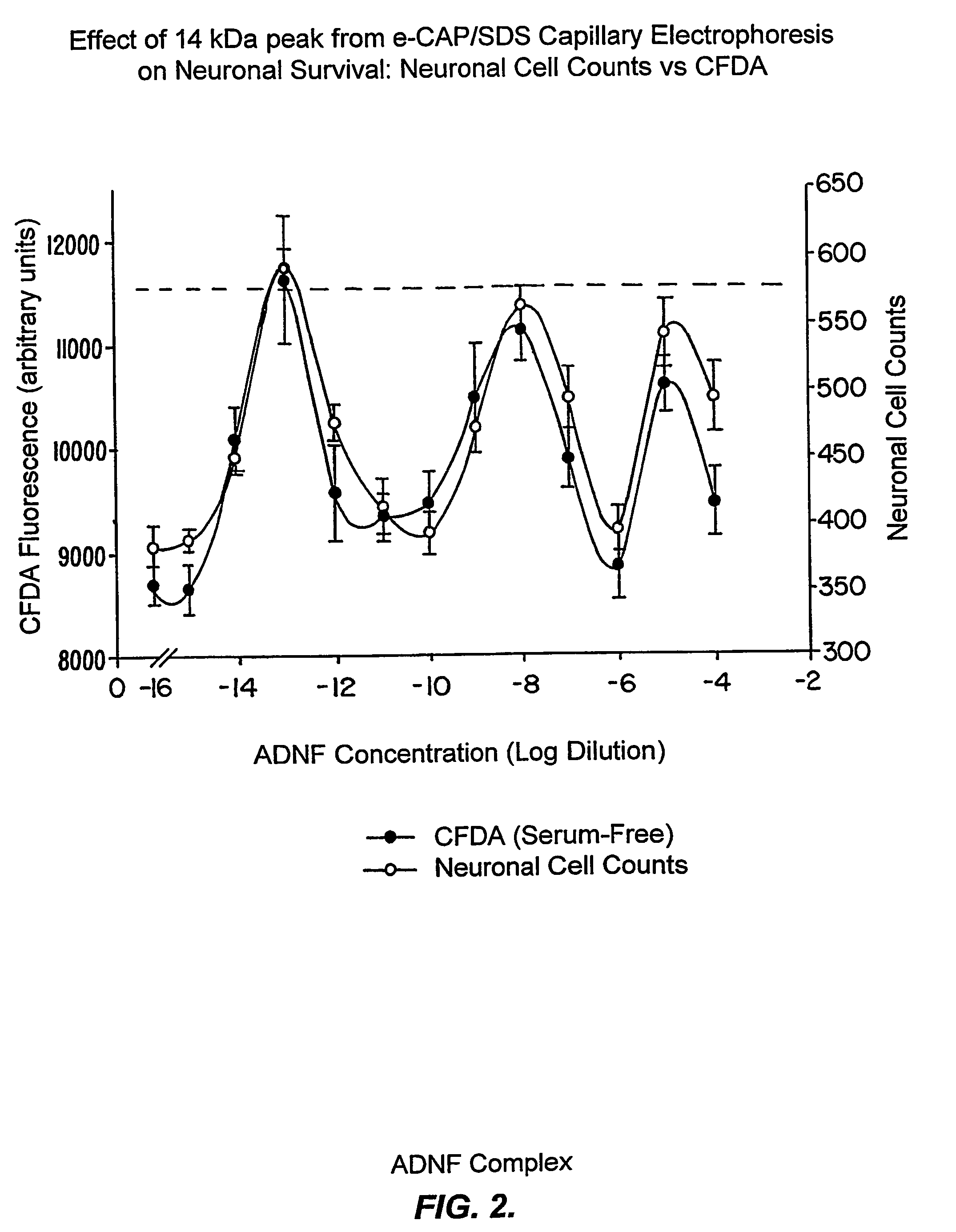

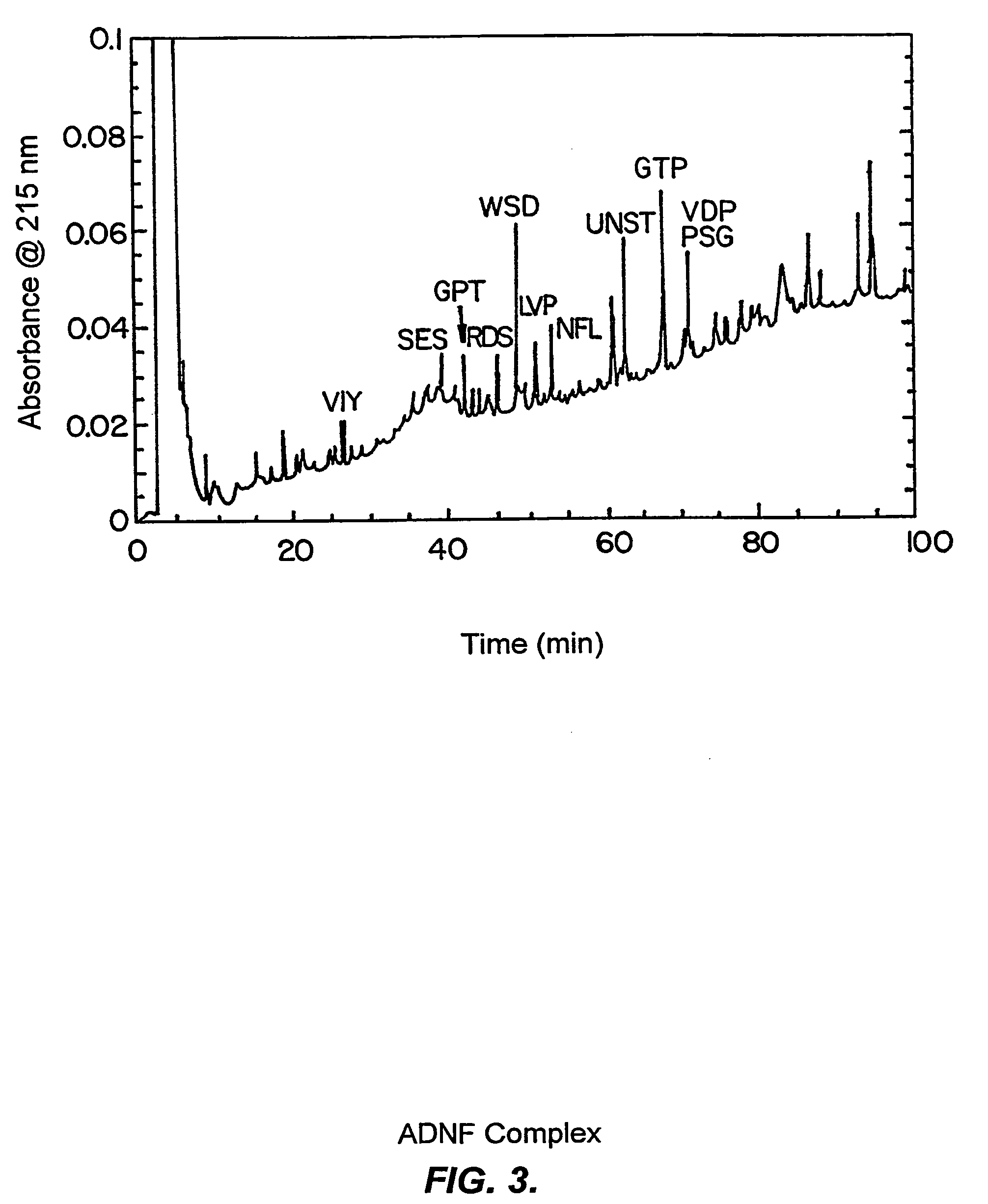

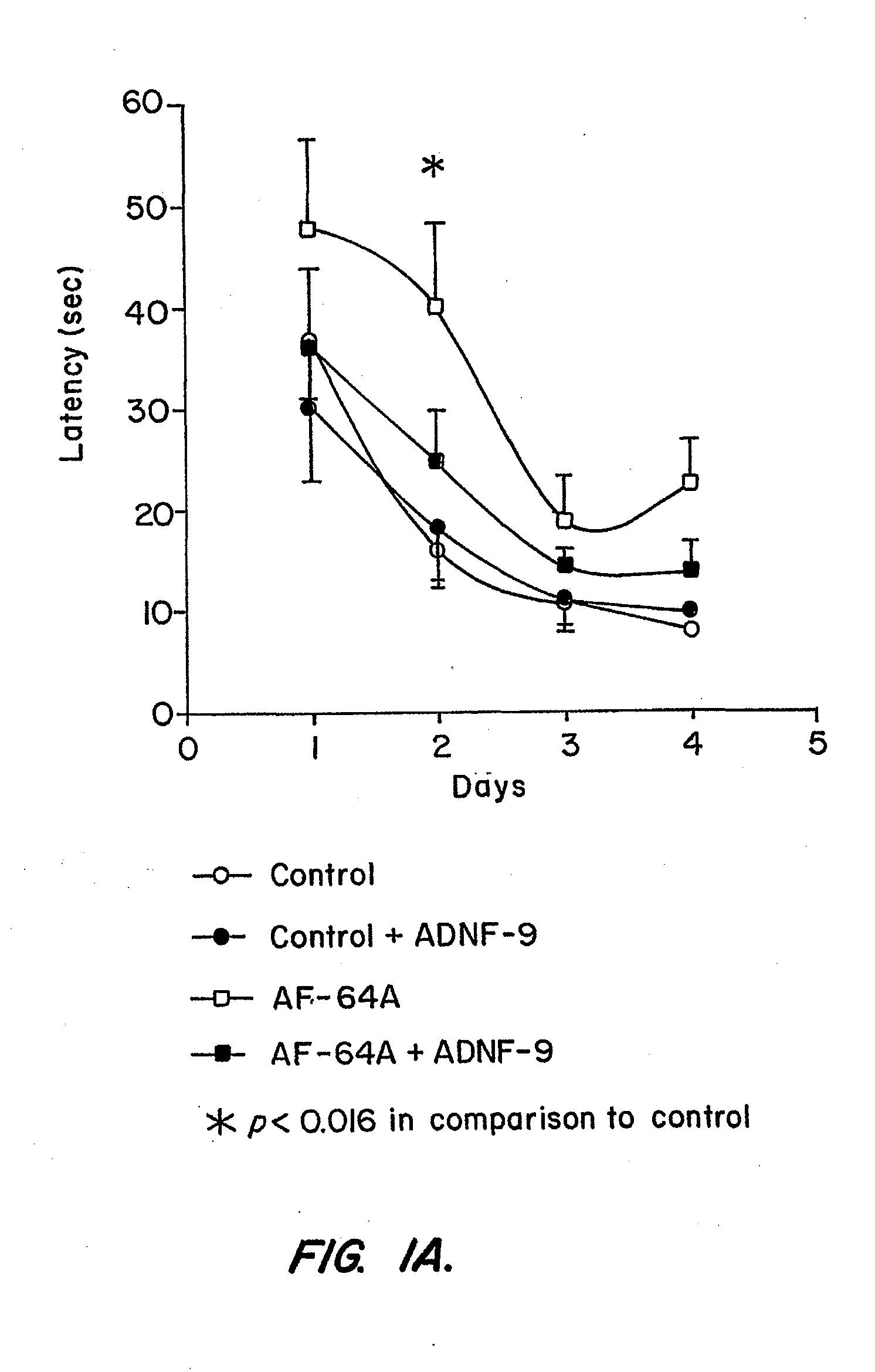

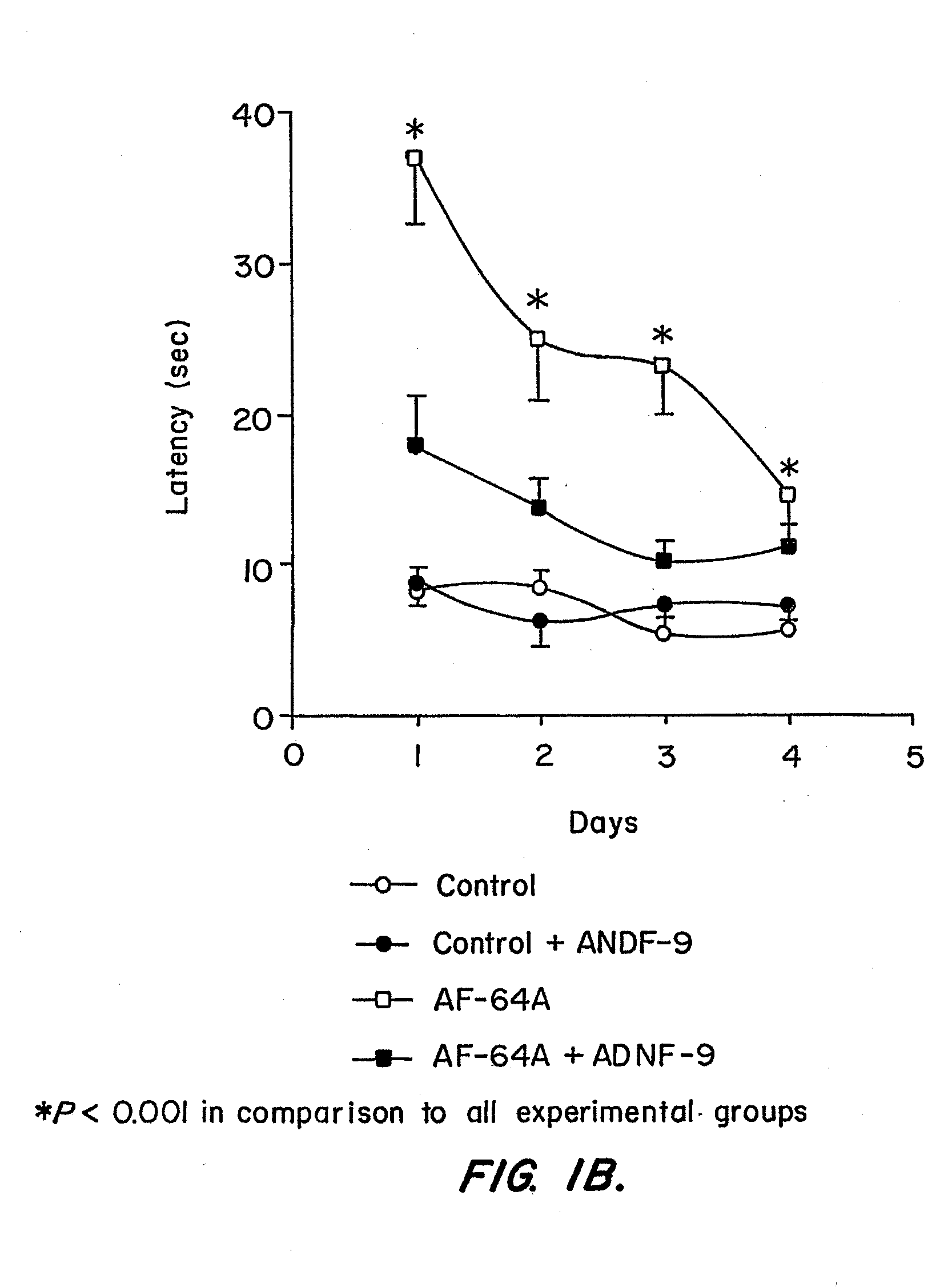

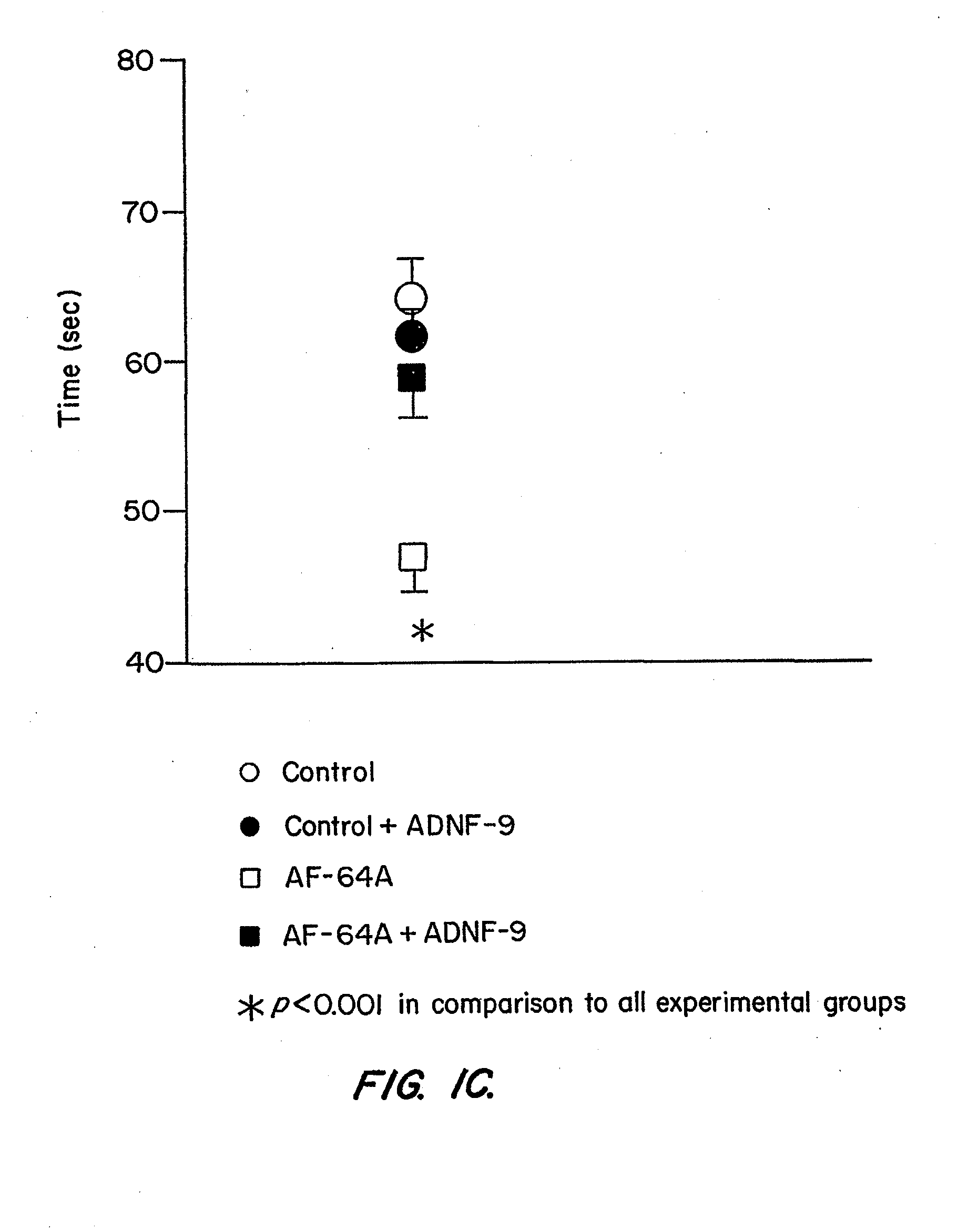

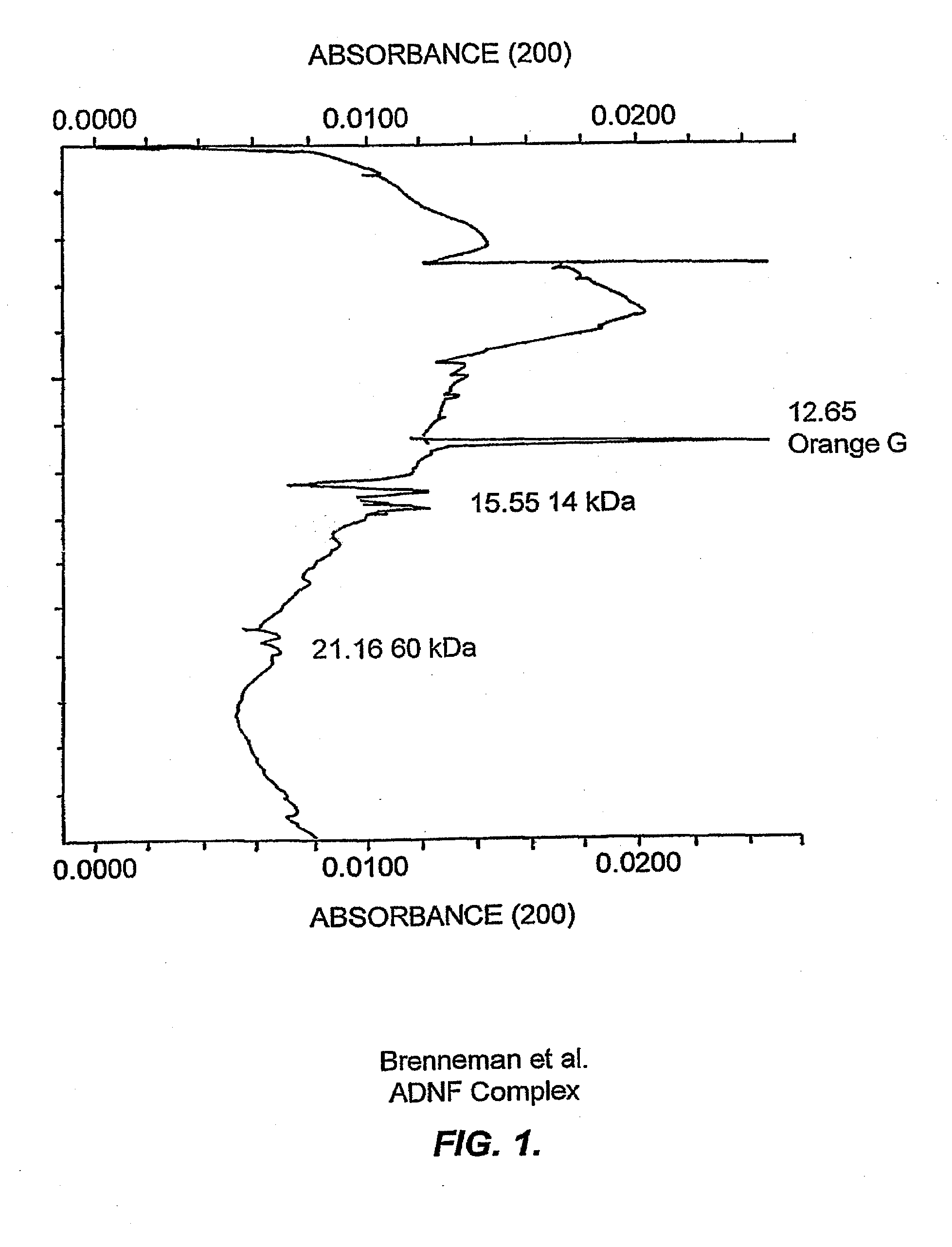

Neurothrophic components of the ADNF I complex

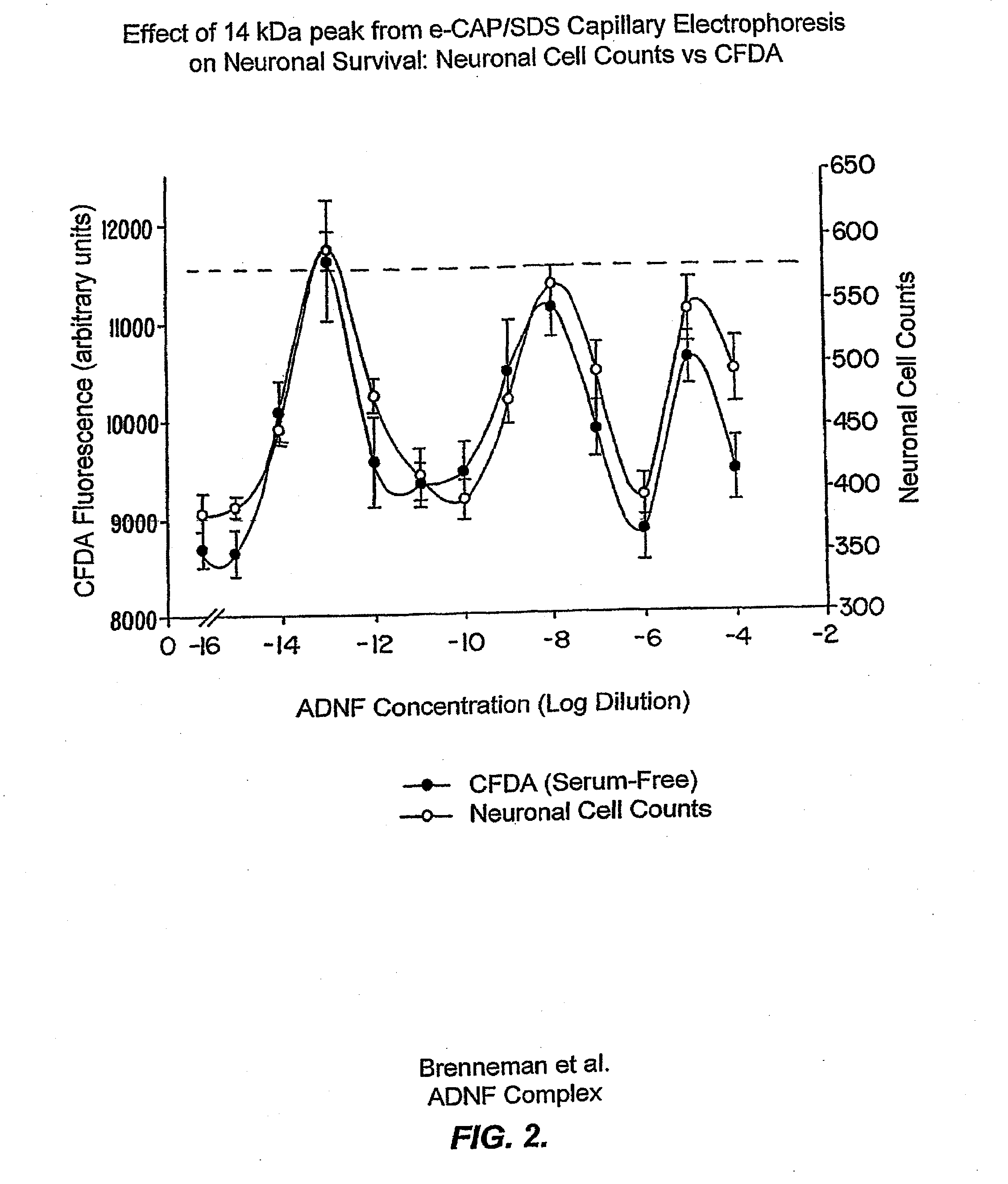

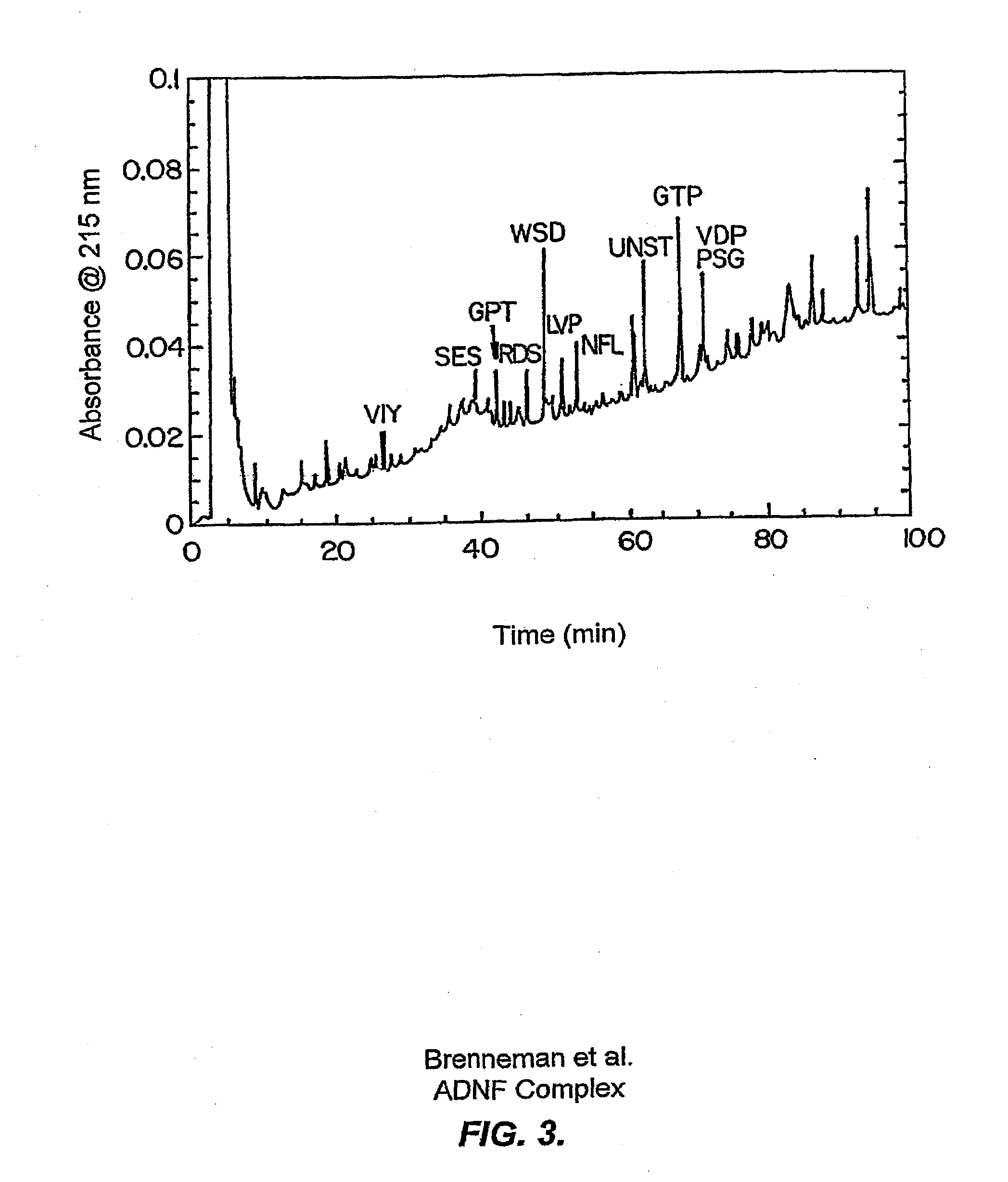

InactiveUS7427590B2Inhibitory activityHigh activityNervous disorderPeptide/protein ingredientsNeuron cell deathProteinase activity

This invention relates to Activity Dependent Neurotrophic Factor I complex (ADNF I complex) and polypeptides of this complex, which produce their neurotrophic effects through multiple proteases intrinsic to the ADNF I complex. The invention also relates to pharmaceutical compositions comprising ADNF I complex polypeptides, as well as methods for reducing neuronal cell death in vitro and in vivo, methods for treating oxidative stress in a patient, methods for reducing a condition associated with fetal alcohol syndrome in a subject, and methods of enhancing learning and memory both pre- and post-natally, all of which methods use the ADNF I complex polypeptides of the invention.

Owner:THE GOVERNMENT OF THE UNITED SATES OF AMERICA AS REPRESENTED BY THE SEC OF THE DEPT OF HEALTH & HUMAN SERVICES +1

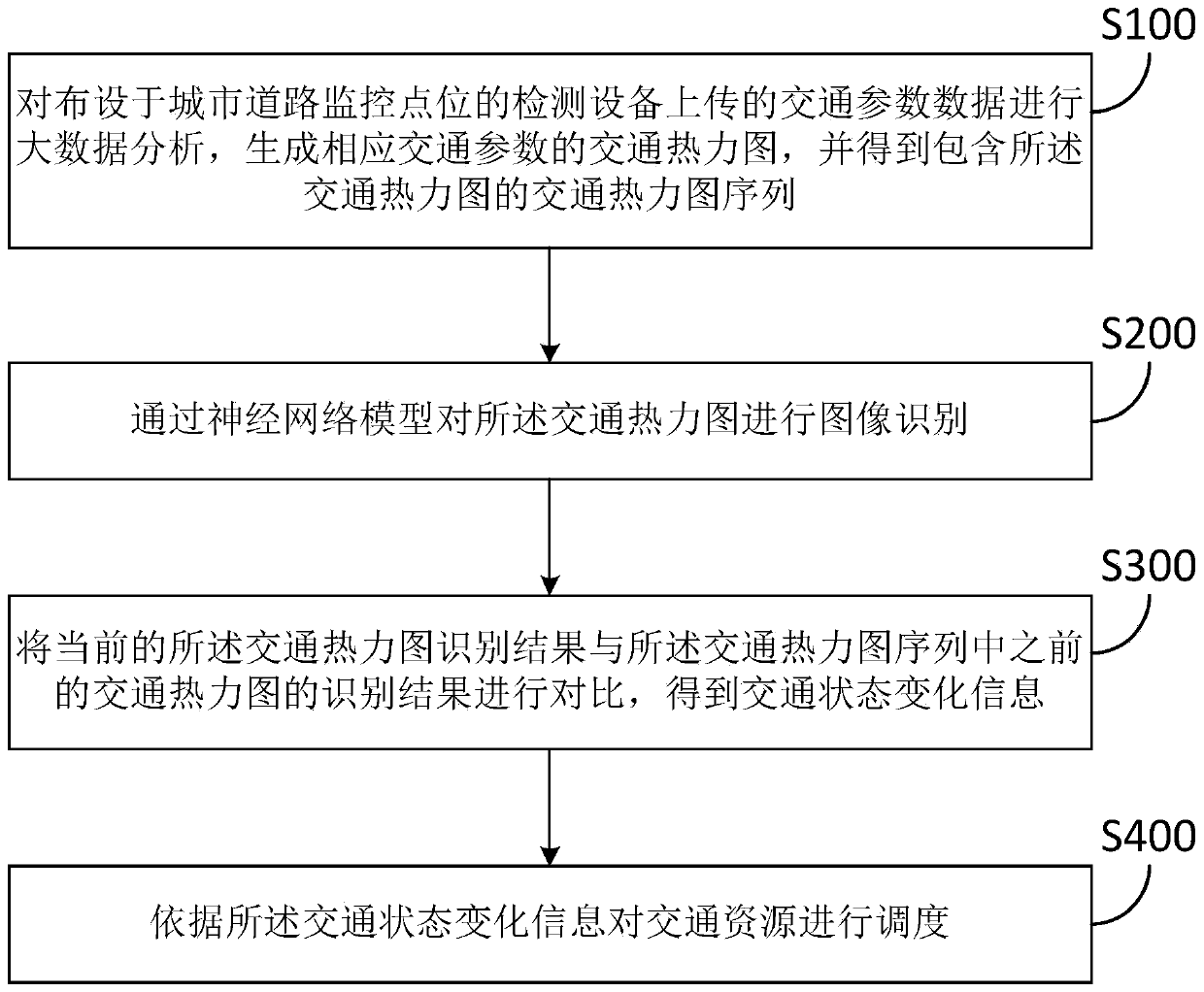

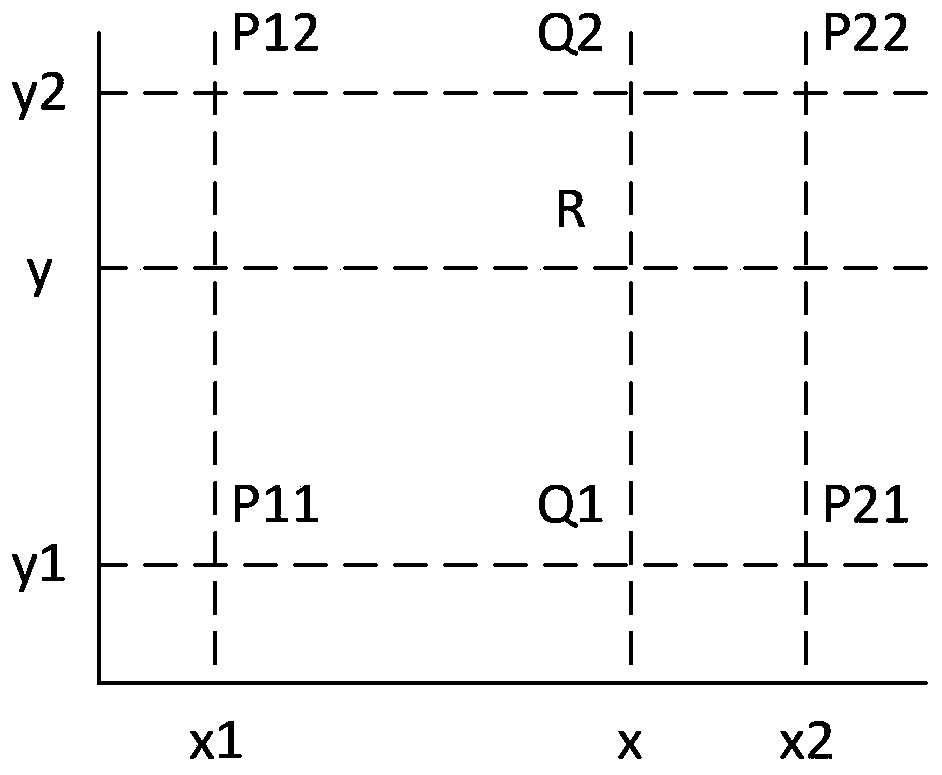

Thermodynamic diagram change identification-based urban area traffic resource regulation and control method and system

ActiveCN110517487AHigh degree of processing completionImprove rationalityDetection of traffic movementCharacter and pattern recognitionResource utilizationNetwork model

The embodiments of the invention disclose a thermodynamic diagram change identification-based urban area traffic resource regulation and control method. The method includes the following steps that: big data analysis is carried out on traffic parameter data uploaded by detection devices arranged at urban road monitoring points, so that the traffic thermodynamic diagrams of corresponding traffic parameters are generated, and a traffic thermodynamic diagram sequence containing the traffic thermodynamic diagrams is generated; image recognition is performed on the traffic thermodynamic diagrams through a neural network model; current traffic thermodynamic diagram recognition results are compared with the recognition results of the previous traffic thermodynamic diagrams in the traffic thermodynamic diagram sequence, so that traffic state change information is obtained; and traffic resources are scheduled according to the traffic state change information. With the method adopted, the rationality and reference of a finally generated resource allocation scheme are improved, so that the finally generated traffic resource scheduling scheme is more reasonable and evidence-based, and the problems of traffic jam and low traffic resource utilization rate are better solved.

Owner:重庆特斯联智慧科技股份有限公司

Use of activity dependent neurotrophic factor for enhancing learning and memory: pre-and post-natal administration

InactiveUS20090203615A1Improve performanceImprove referenceNervous disorderPeptide/protein ingredientsActivity-dependent neurotrophic factorCell biology

Owner:THE GOVERNMENT OF THE US SEC THE DEPT +2

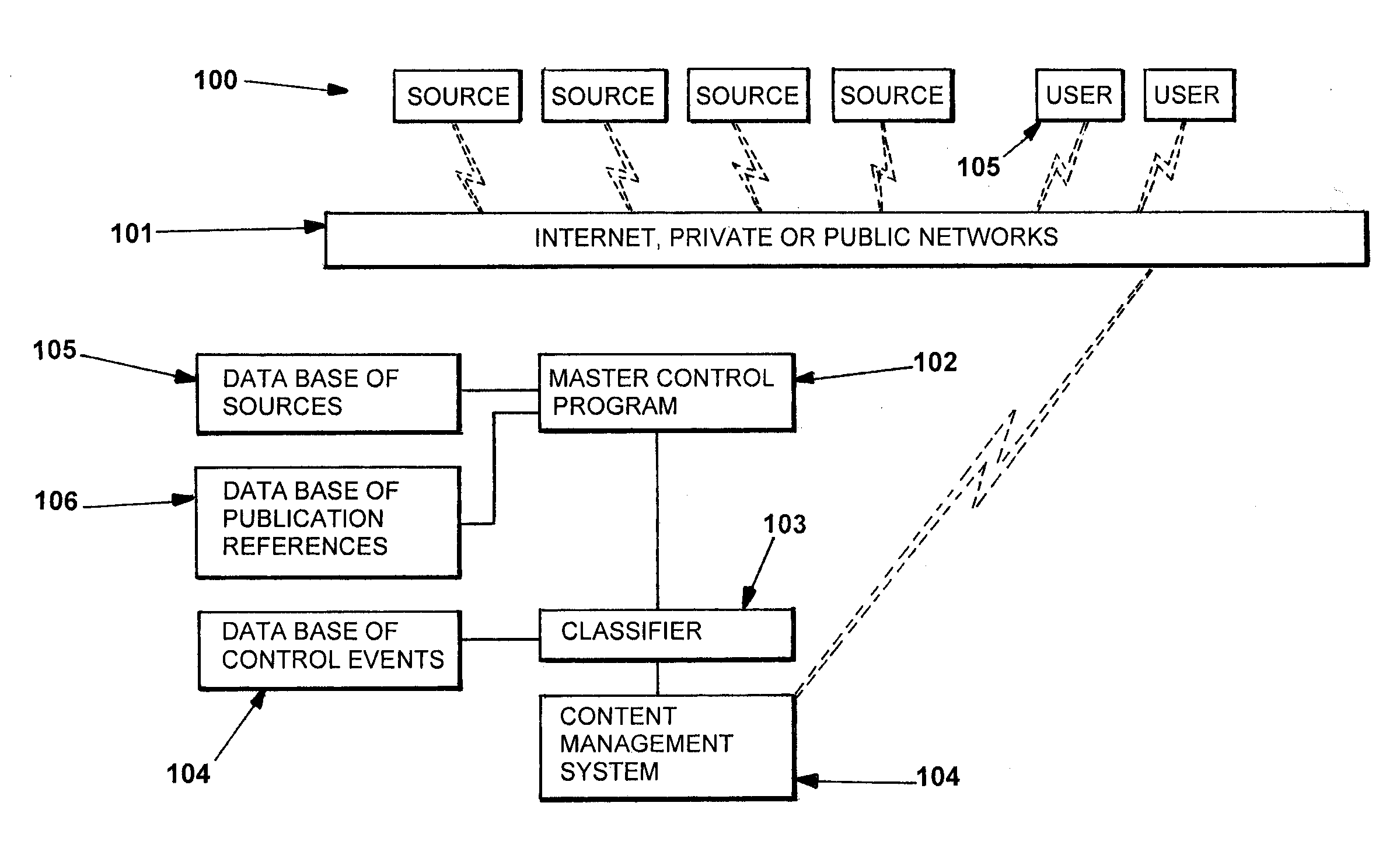

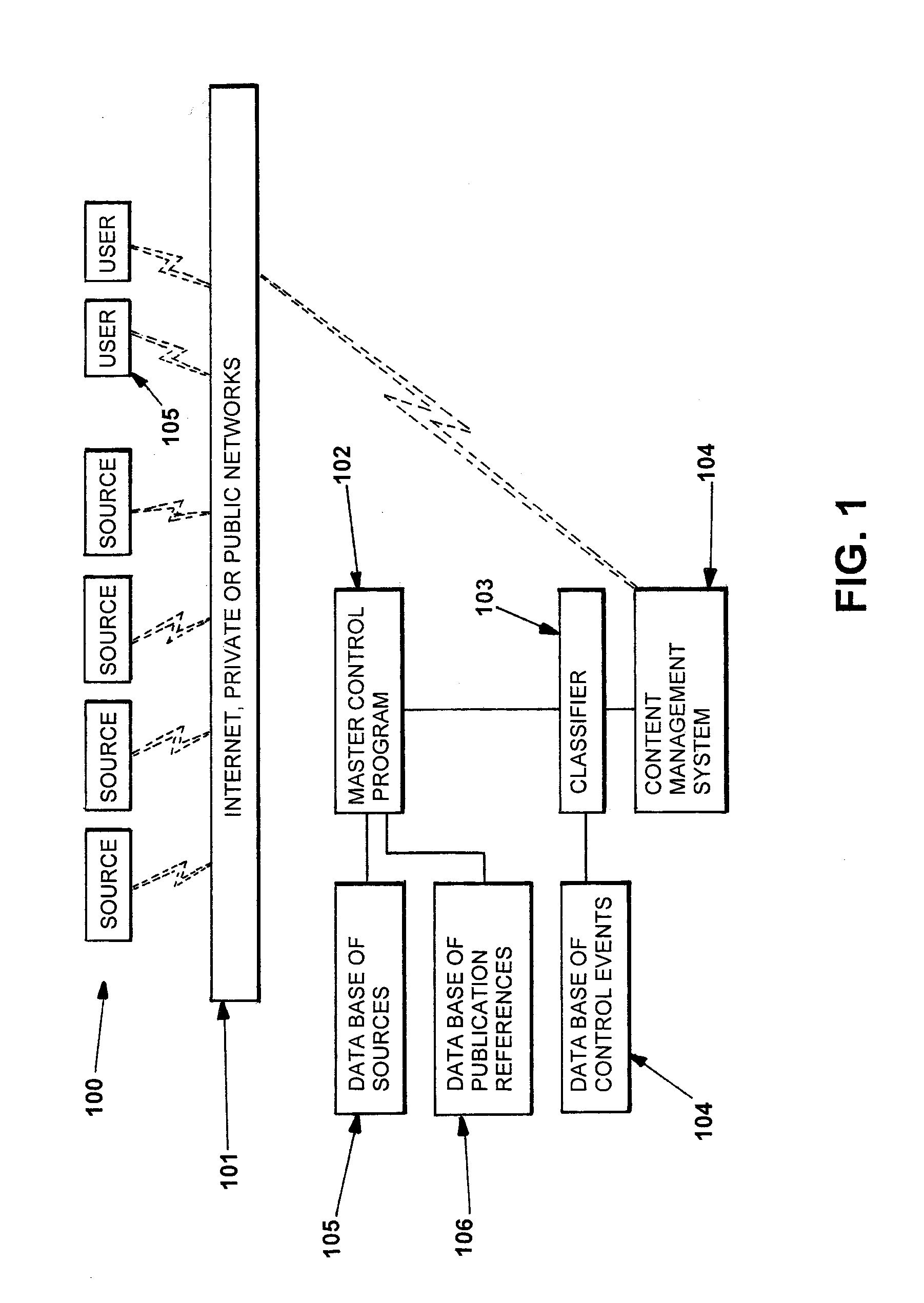

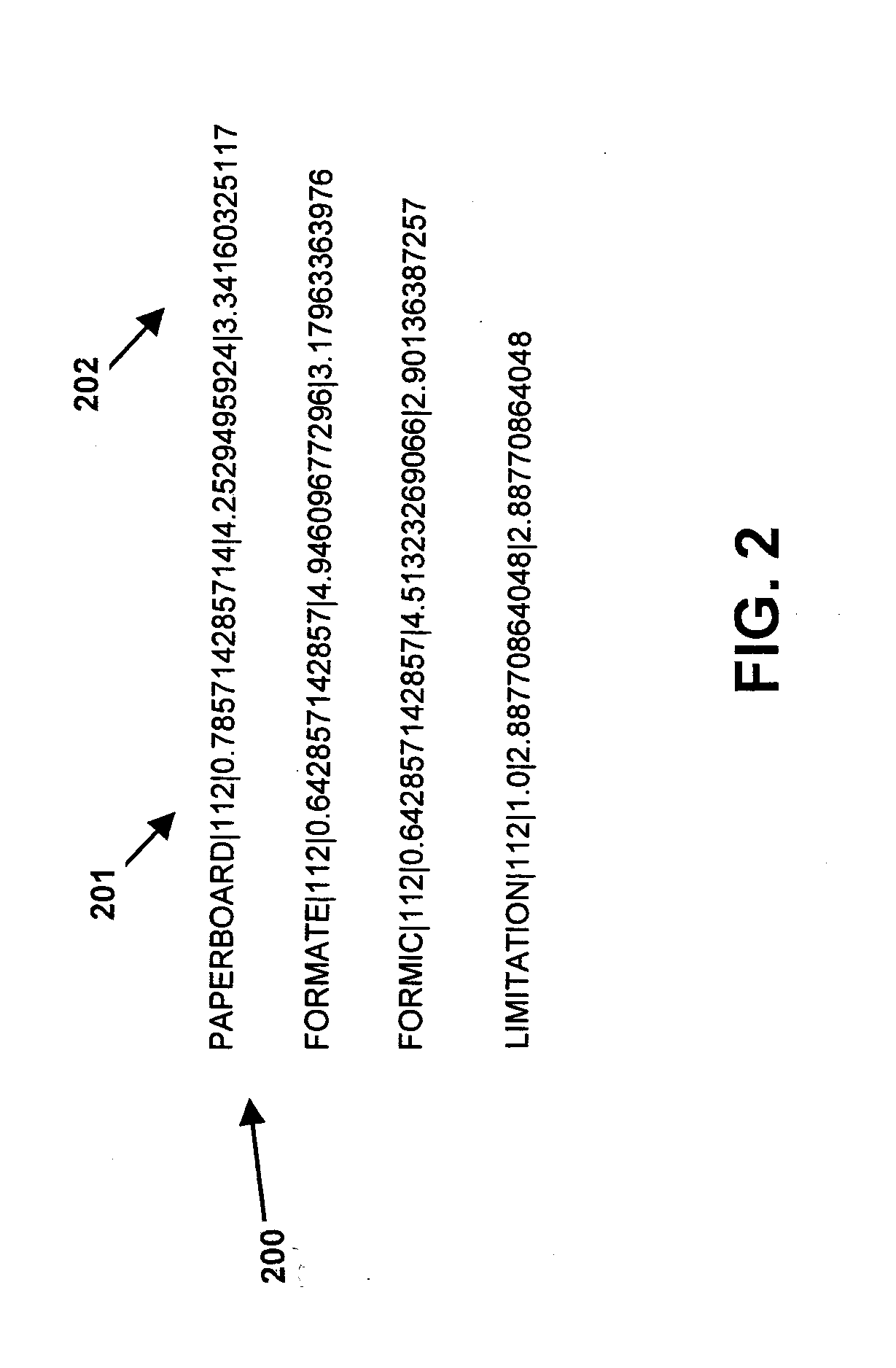

Apparatus and Method for the Automatic Discovery of Control Events from the Publication of Documents

ActiveUS20110302171A1Reduce amount of timeFacilitate transaction controlFinanceDigital data processing detailsTaxonomic databaseData mining

A method and system for discovering a control event from electronically published documents and received data streams is provided, in which a computer control program identifies electronically published documents and data stored in a plurality of network servers which potentially contain control events relevant to the control of goods and / or services, the control events identified by reference to user interest identifiers. Identified material is analyzed by a classification program to determine whether control events are present. A control event classification is assigned to documents and received data determined to contain at least one discovered control event, the assigned control event classification and information identifying the associated document and data is stored in a classification database, and a report of discovery of documents and data containing control events is be provided to a user. The report may includes a link to the control event classification and / or its associated document or data.

Owner:DECERNIS

Neurotrophic components of the adnf i complex

InactiveUS20090247457A1Reduce deathReduce oxidative stressNervous disorderPeptide/protein ingredientsOxidative stressNeurotrophic factors

This invention relates to Activity Dependent Neurotrophic Factor I complex (ADNF I complex) and polypeptides of this complex, which produce their neurotrophic effects through multiple proteases intrinsic to the ADNF I complex. The invention also relates to pharmaceutical compositions comprising ADNF I complex polypeptides, as well as methods for reducing neuronal cell death in vitro and in vivo, methods for treating oxidative stress in a patient, methods for reducing a condition associated with fetal alcohol syndrome in a subject, and methods of enhancing learning and memory both pre- and post-natally, all of which methods use the ADNF I complex polypeptides of the invention.

Owner:THE GOVERMENT OF THE UNITED STATES OF AMERICA AS REPRESENTED BY THE +2

Metal oxide semiconductor (MOS) bandgap voltage reference circuit

ActiveUS6858917B1Increase parasitic capacitanceImprove referenceTransistorSolid-state devicesParasitic capacitanceSemiconductor

A metal oxide semiconductor (MOS) bandgap voltage reference circuit with a plurality of dummy bipolar junction transistors (BJTs) coupled to the mismatched parasitic substrate BJTs for improving parasitic capacitance matching, thereby improving startup behavior of the bandgap reference circuitry.

Owner:NAT SEMICON CORP