Double-grid electric charge capturing memory and manufacture method thereof

A technology of charge trapping and manufacturing method, which is applied in the field of microelectronics, can solve the problems of losing information, affecting data access speed, and charge loss, and achieves the effects of dense distribution of thresholds, improving programming and erasing speed, and increasing turn-on current

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0034] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be described in further detail below in conjunction with specific embodiments and with reference to the accompanying drawings.

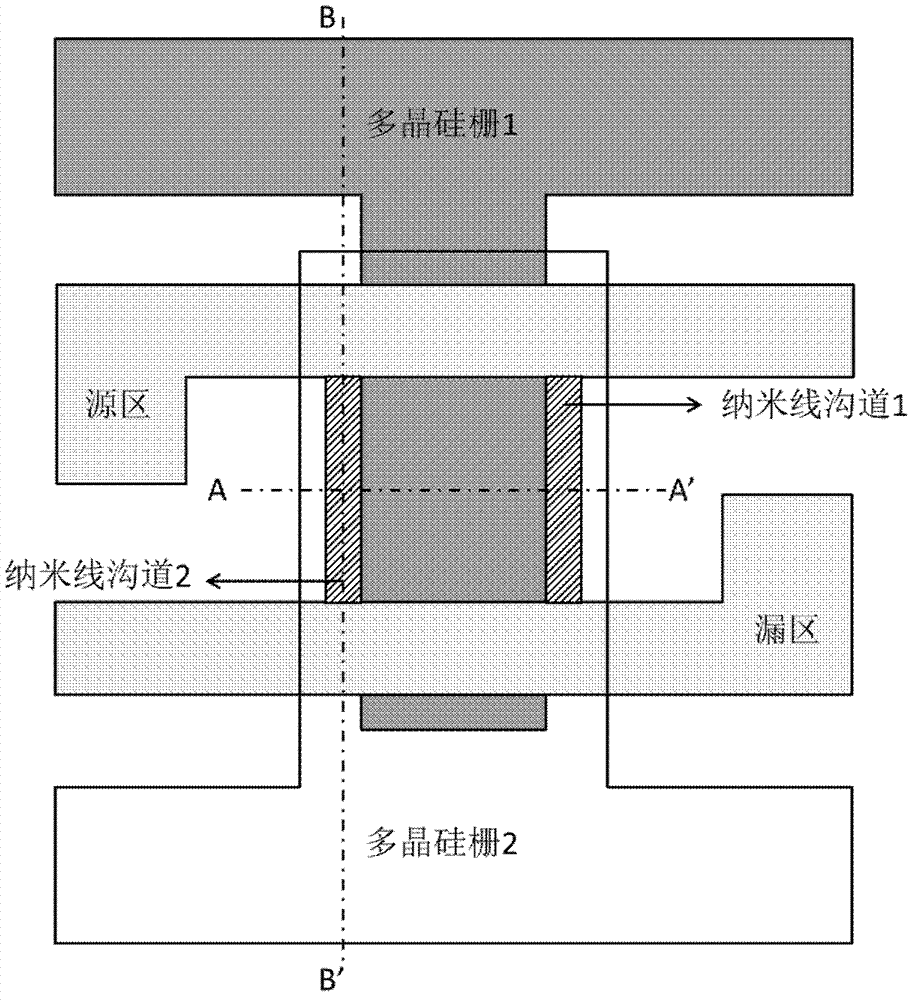

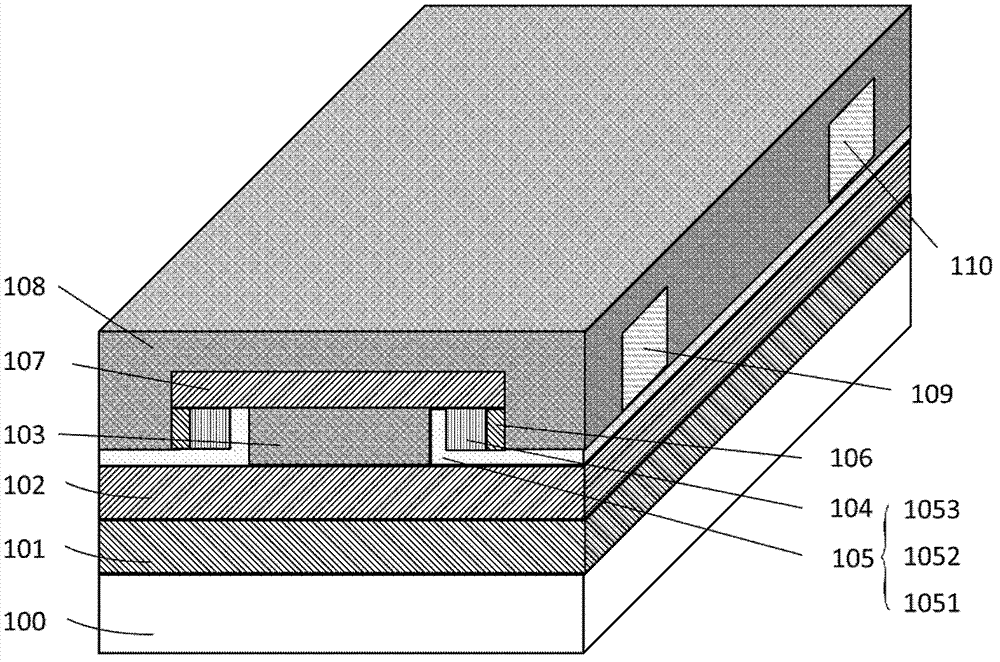

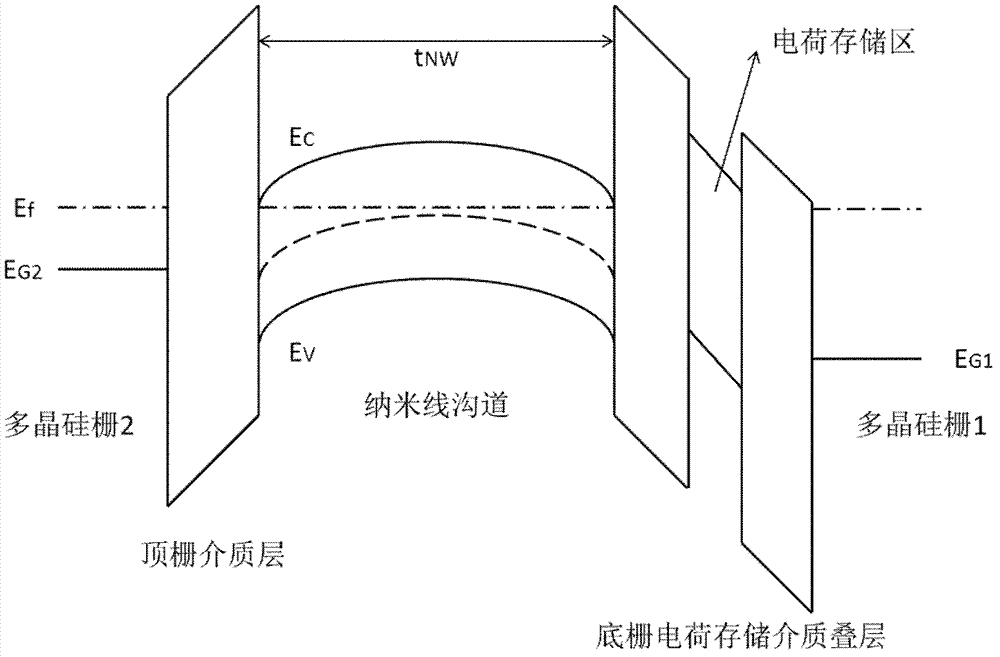

[0035] figure 1 It is a top view structural diagram of a double-gate charge trapping memory based on a polysilicon nanowire field effect transistor according to an embodiment of the present invention. From figure 1 It can be seen in the figure that there are two independent polysilicon gates in the device structure, which are polysilicon gate 1 on the bottom layer of the device and polysilicon gate 2 on the top layer of the device, and the two gates between the two gates are on both sides of polysilicon gate 1 Symmetrically distributed polysilicon nanowires constitute the channel portion of the device. The source region and the drain region of the device pass through the overlapping part between the two gates, connect w...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More