Array substrate, manufacture method of array substrate, liquid crystal display panel and display device

A technology of an array substrate and a manufacturing method, which is applied in the field of liquid crystal display to achieve the effects of increasing turn-on current, increasing Ion, and reducing channel length

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

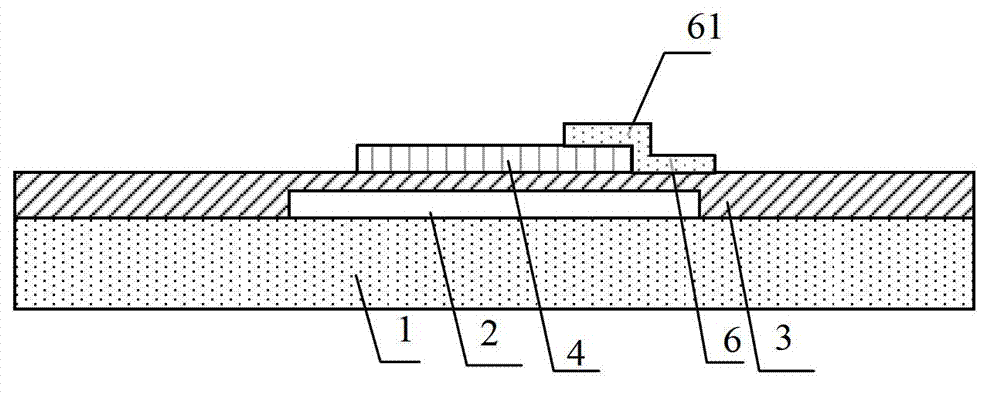

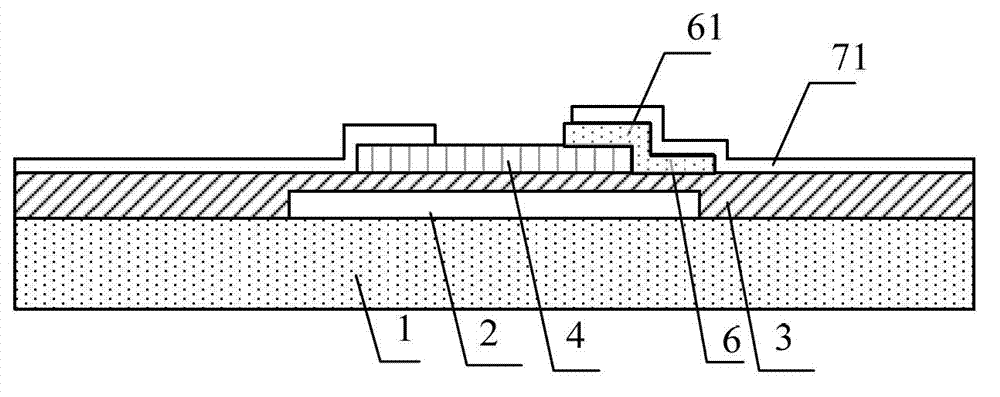

[0143] In this embodiment, the source electrode and the drain electrode are located in different layers, and are formed separately through two patterning processes, wherein the source electrode is formed first and then the drain electrode is formed, as Figure 2-11 As shown, the manufacturing method of the array substrate of this embodiment includes the following steps:

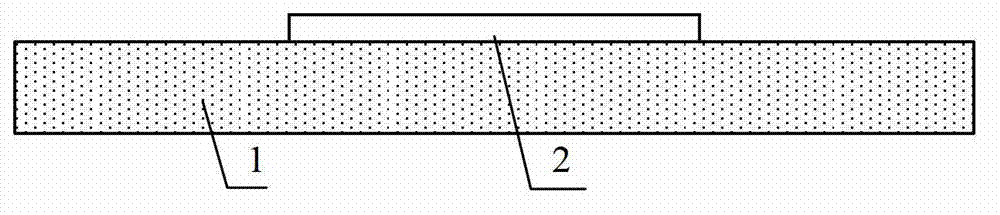

[0144] Step a1: provide a substrate 1, and form a pattern of gate electrodes and gate lines composed of a gate metal layer 2 on the substrate 1 through the first patterning process;

[0145] Specifically, the substrate 1 may be a transparent substrate. Such as figure 2 As shown, a gate metal layer 2 is first deposited on a substrate 1, and then patterns of gate electrodes and gate lines are formed through a first patterning process. Specifically, a gate metal layer 2 can be deposited on the substrate 1 by magnetron sputtering, wherein the gate metal layer 2 can be any one of Nd, Cr, W, Ti, Ta, Mo, Al and C...

Embodiment 2

[0165] In this embodiment, the drain electrode and the source electrode are located in different layers, and are respectively formed through two patterning processes, wherein the drain electrode is formed first and then the source electrode is formed. The manufacturing method of the array substrate of this embodiment includes the following steps:

[0166] Step b1: provide a substrate, and form a pattern of gate electrodes and gate lines consisting of a gate metal layer on the substrate through the first patterning process;

[0167] Specifically, the substrate may be a transparent substrate. A gate metal layer is first deposited on the substrate, and then patterns of gate electrodes and gate lines are formed through the first patterning process. Specifically, a gate metal layer can be deposited on the substrate by magnetron sputtering, wherein the gate metal layer can be any one of Nd, Cr, W, Ti, Tb, Mo, Bl and Cu or at least two of them Metal alloy; after that, a photoresist ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More