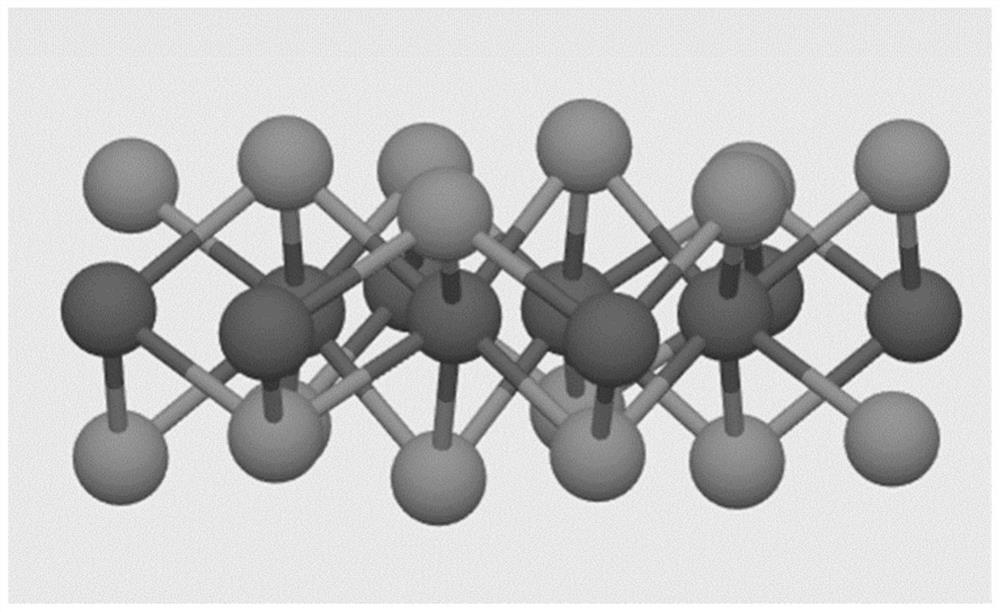

Rhenium disulfide-based field effect transistor and manufacturing method thereof

A rhenium disulfide and field effect transistor technology, which is applied to the field effect transistor based on rhenium disulfide and its manufacturing field, can solve the problems of reducing device length, process and cost constraints, and achieves the effect of controlling the size of the drain-source current

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

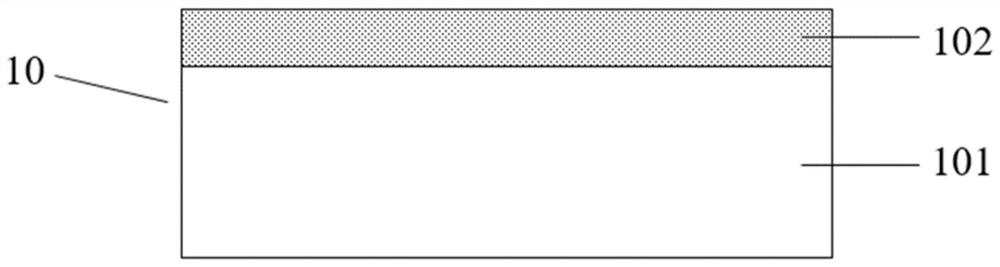

[0028] An field effect tube based on a disulfide-based ruthenium comprising a substrate 10, the substrate 10 comprising a silicon substrate 101 and a oxide layer 102 grown on the silicon substrate 101, the oxide layer 102 Elegly etching there is a sulfide trench 11, the field effect tube further comprising a drain electrode 12 grown in a source leak contact zone, covering the gate oxide layer 13 of the sulfide rutes 11 and at the bottom of the silicon substrate 101. Metal lead 15, the gate electrode 14 is grown on the gate oxide layer 13, which includes a CR electrode 121 and the Au electrode 122 disposed over the oxide layer 102. The silicon substrate 101 is p-type heavy doping, and the doped type is p-type heavy doping (P +), and the impurities may be boron and / or aluminum and / or indium, in the first embodiment, The oxide layer 102 is a silica film having a thickness of 50 to 300 nm. The silicon substrate 101 has a doping concentration greater than 10 19 / cm -3 And less tha...

Embodiment 2

[0036] In the present embodiment, the oxide layer 102 is a silica film having a thickness of 50 to 300 nm. The silicon substrate 101 has a doping concentration of 0. The gate oxide layer 13 has a thickness of from 30 to 50 nm, and the thickness of the sulfide trench 11 is from 5 to 10 nm, and the thickness of the CR electrode 121 is 5-10 nm, and the thickness of the Au electrode 122 is 80- 100nm.

[0037] The specific properties of the field effect tube described in Example 2 are:

[0038] Control V DS When 100mV is unchanged, the back gate voltage V is BG Size from -20V to 10V, i DS From 10 -14 A magnitude change to 10 -8 A level, at this time, the switch current is 10 6 When further increasing V DS , Switch current ratio is greater than 10 6 . It can be seen that when the silicon substrate 101 is not doped, the back gate control voltage V BG The value is larger than the doping, and the recombination of silicon substrate can reduce the voltage.

Embodiment 3

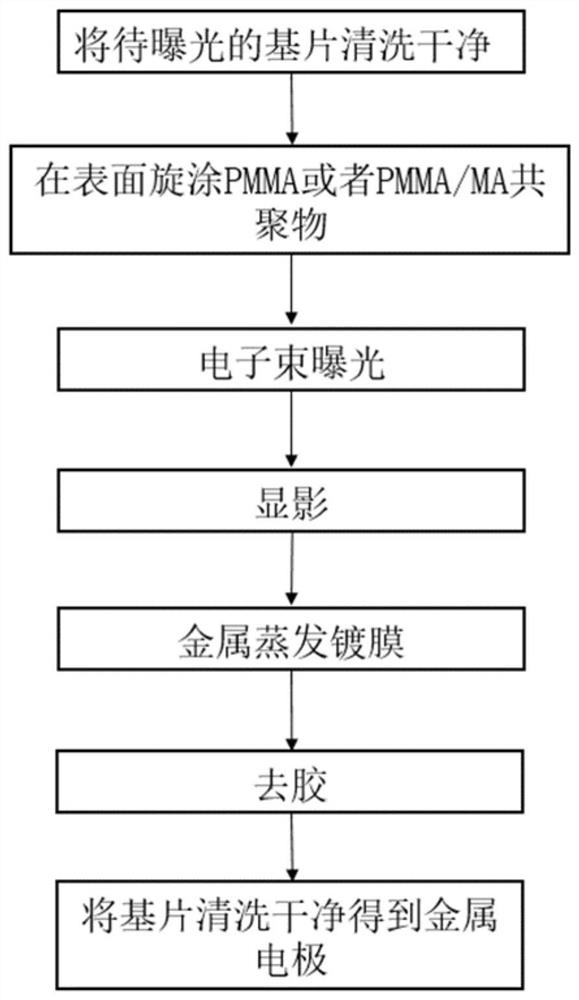

[0040] The method of manufacturing a field effect tube based on a sulfide ruthenium according to the present invention, such as Figure 9 As shown, the specifically includes the steps of:

[0041] A substrate 10 is supplied, the substrate comprising a silicon substrate 101, a layer of oxide layer 102 is grown on the silicon substrate 101, and then the substrate 10 is cleaned, and the surface is dry and flat, no impurities.

[0042] A particular preparation method of the silicon substrate 101 is: injecting boron ions to silicon substrate by a high energy ion implantation machine, doping concentration is 10 19 -10 21 / cm 3 The ion beam energy is 300 keV, annealing at a high temperature for 20-30 min, resulting in a P-type retaining silicon substrate 101, and the substrate 10 is schematically image 3 Indicated. The present invention is used as a back gate with a heavy doped p-type silicon substrate, by adjusting the back gate voltage V. BG And a grid voltage V TG To change the conduc...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com