Integrated chip of enhanced and depletion type HEMT device and preparation method

An integrated chip, depletion-mode technology, used in semiconductor/solid-state device manufacturing, semiconductor devices, electric solid-state devices, etc., can solve problems such as uneven distribution of device threshold voltages, risk of false turn-on, and large gate leakage current. Achieve the effect of weakening the polarization electric field strength of the barrier layer, weakening the polarization electric field strength, and reducing power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

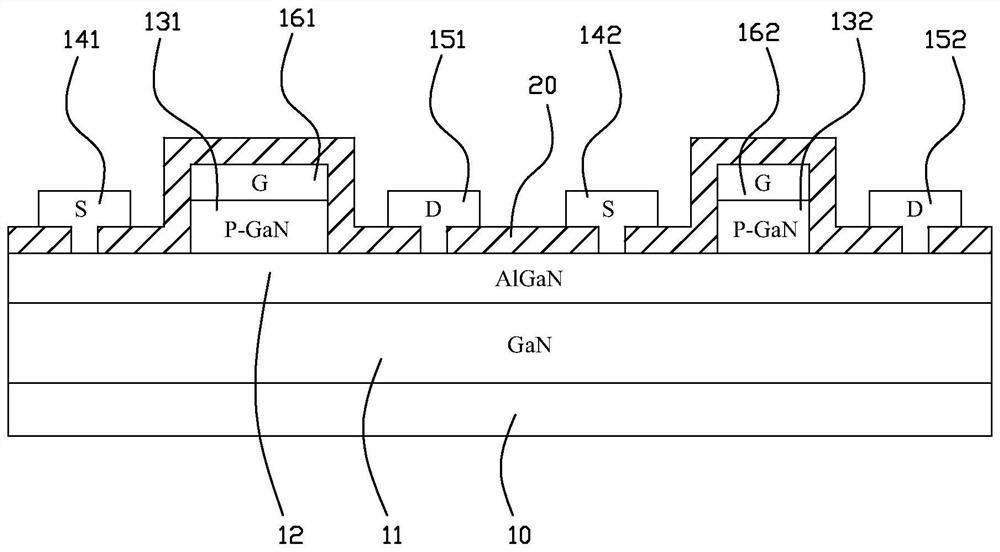

[0031] An integrated chip of enhancement mode and depletion mode HEMT devices, such as figure 1 As shown, it includes a substrate 10, a buffer layer 11, a channel layer, a barrier layer 12, a first P-type nitride gate layer 131, a second P-type nitride gate layer 132, and a first P-type nitride gate layer. The electrode layer 131 and the second P-type nitride gate layer 132 are arranged at intervals; the first P-type nitride gate layer 131 is provided with a first gate metal 161 , and the second P-type nitride gate layer 132 is provided with a second The gate metal 162; the first P-type nitride gate layer 131 and a certain area around it are defined as an enhancement area, and the second P-type nitride gate layer 132 and a certain area around it are defined as a depletion area. The enhancement region usually includes the first P-type nitride gate layer 131, the first gate metal 161, and metal regions such as a certain range around it and a metal-free region; the depletion regi...

Embodiment 2

[0037] The present embodiment provides a method for preparing an integrated chip of an enhanced and depleted HEMT device, for preparing the integrated chip (such as the integrated chip recorded in Example 1), comprising the following steps:

[0038] 1) Prepare a nitride epitaxial structure on the substrate 10. In this embodiment, the nitride epitaxial structure is a P-type nitride HEMT epitaxial structure, including a substrate 10, a GaN buffer layer 11, a channel layer, and an AlGaN barrier layer 12 , P-type nitride gate layer.

[0039] 2) Selectively etch the P-type nitride gate layer to form a first P-type nitride gate layer 131 and a second P-type nitride gate layer 132; wherein, the gate of the first P-type nitride gate layer 131 The electrode line width is greater than the gate line width of the second P-type nitride gate layer 132 . In this embodiment, the gate line width of the first P-type nitride gate layer is 1 μm˜2 μm, and the gate line width of the second P-type ...

Embodiment 3

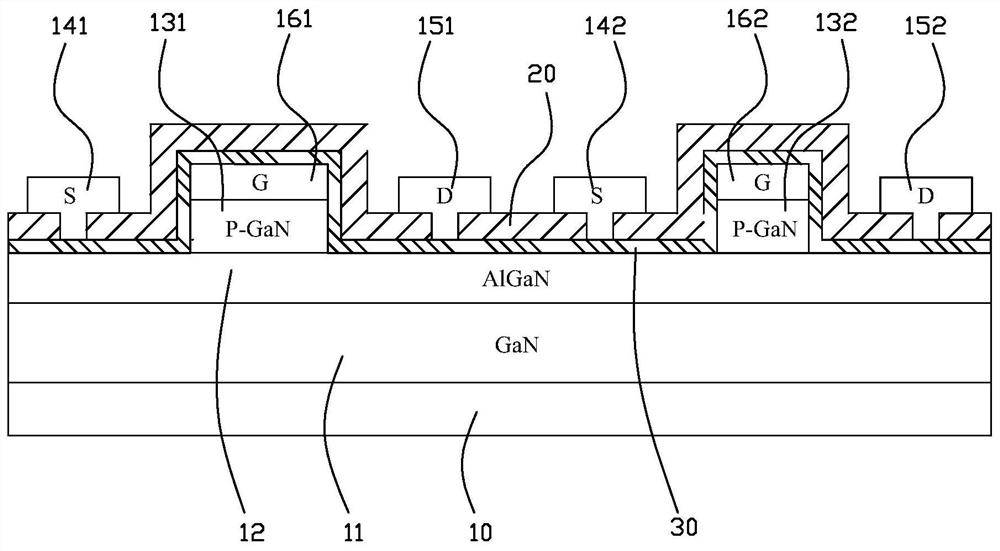

[0046] Such as figure 2 As shown, the difference between this embodiment and Embodiment 1 is that the enhancement region and the depletion region cover the passivation layer 30, and the tensile stress dielectric layer 20 is covered on the passivation layer 30; when PECVD is used to deposit the tensile stress dielectric layer 20 , the plasma bombardment causes damage to the surface of the non-gate region, and a large number of traps are generated on the surface, which reduces the dynamic characteristics of the device.

[0047] In this embodiment, the thickness of the passivation layer 30 is smaller than the thickness of the tensile stress medium layer 20 ; the tensile stress value of the passivation layer 30 is lower than the stress value of the tensile stress medium layer 20 . During specific implementation, the stress value of the passivation layer 30 is -250MPa˜150MPa; the thickness of the passivation layer 30 is less than 20nm. The passivation layer 30 is one or a combina...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More