Patents

Literature

89results about How to "Reduce hot carrier effect" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

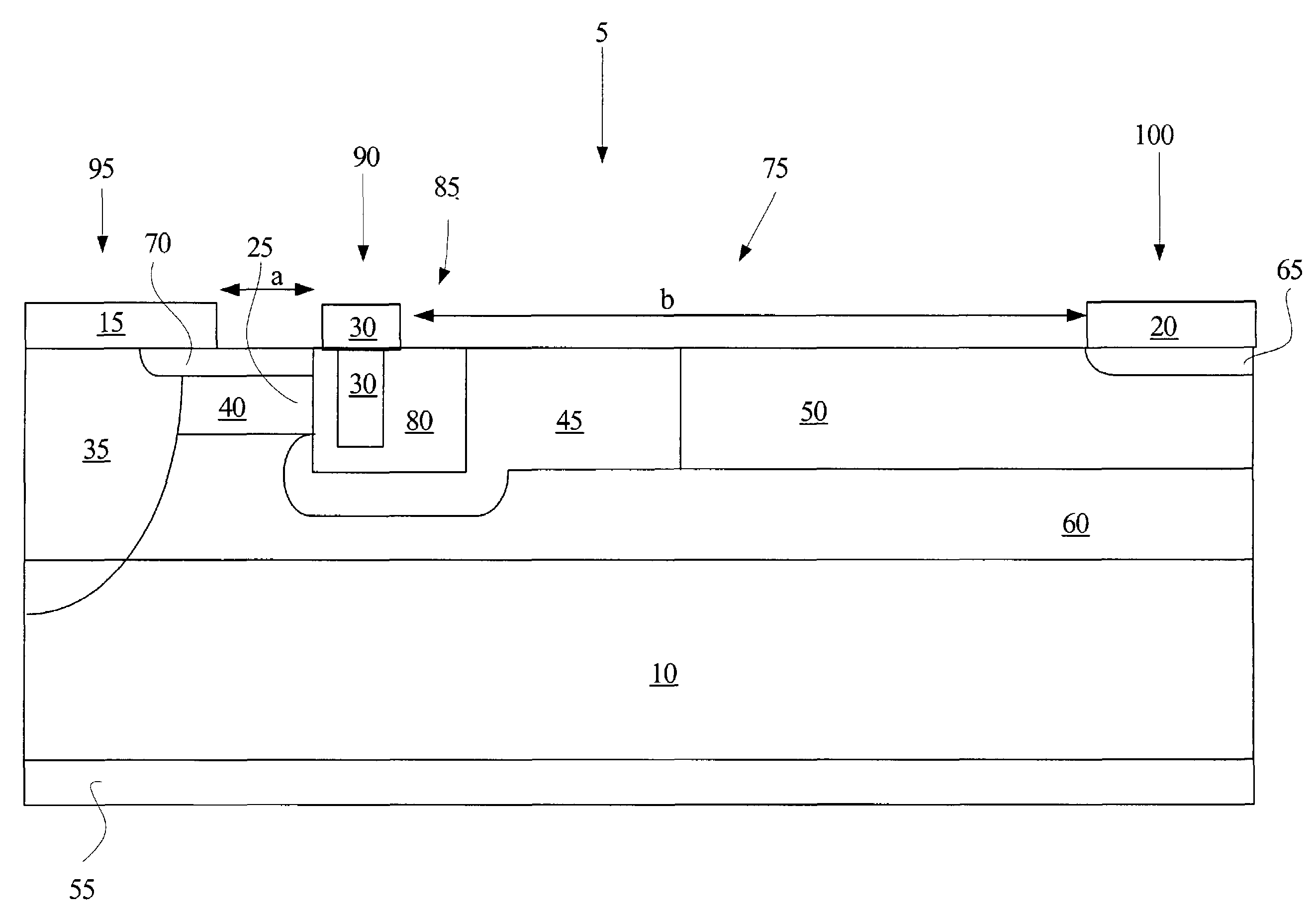

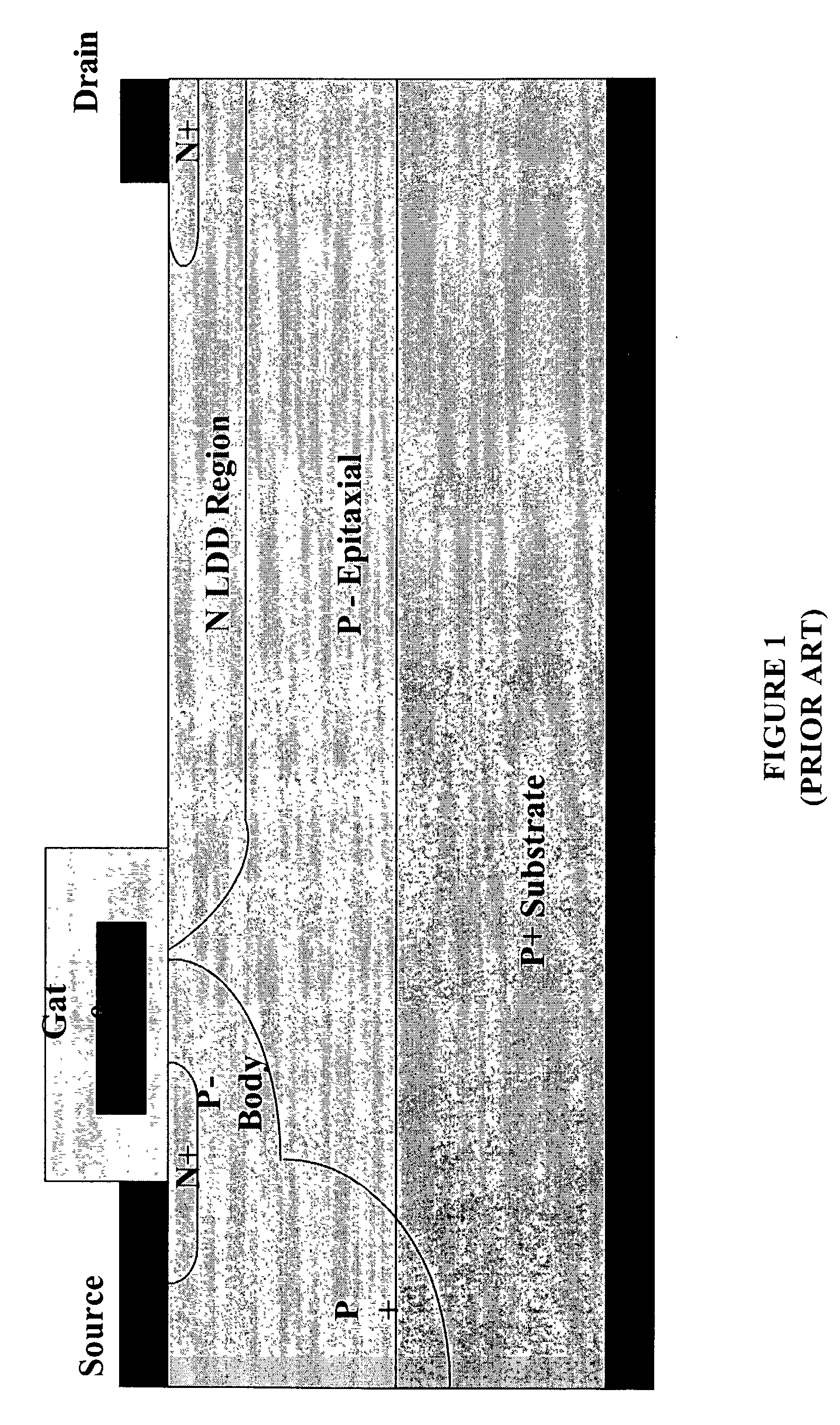

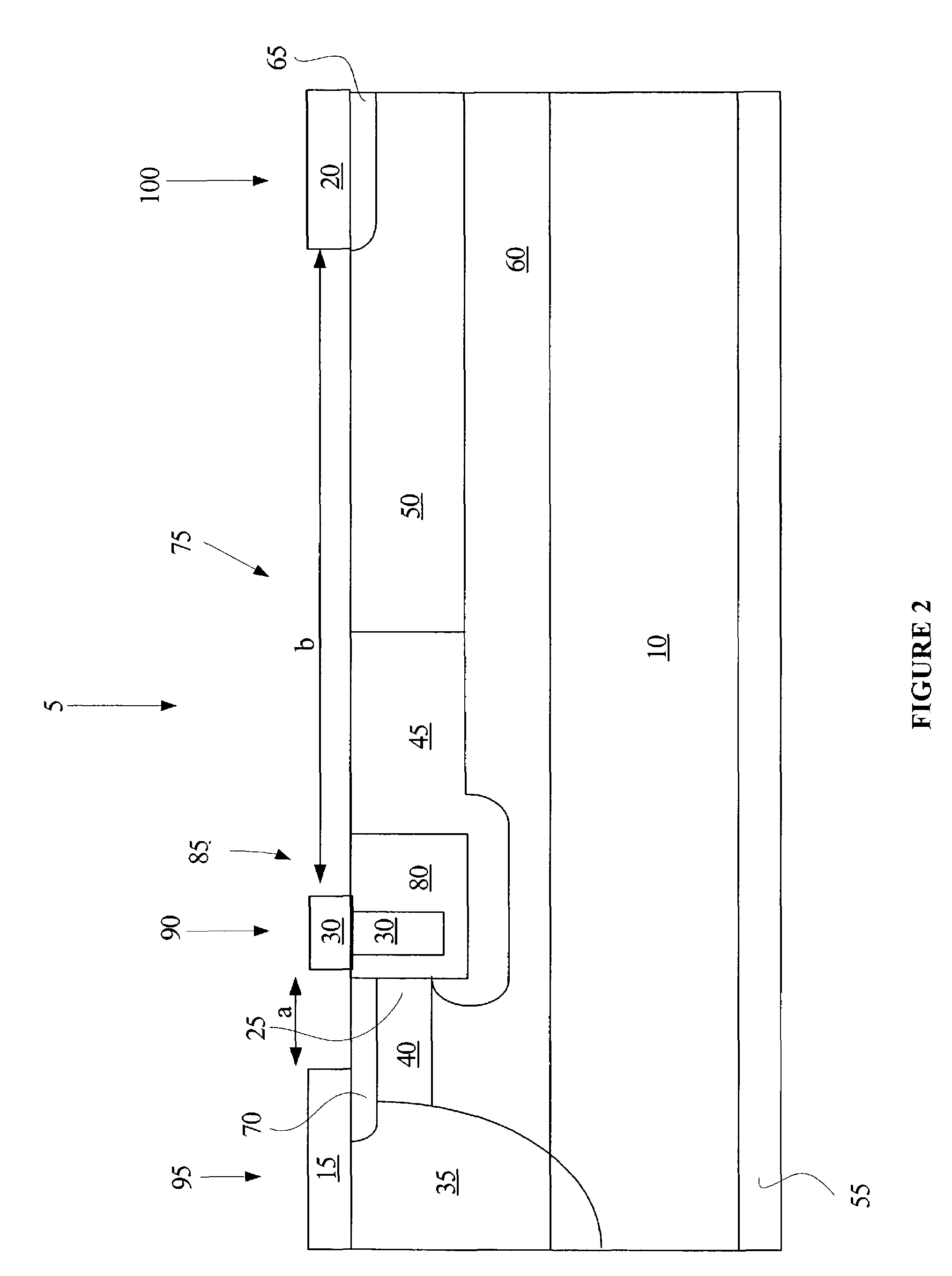

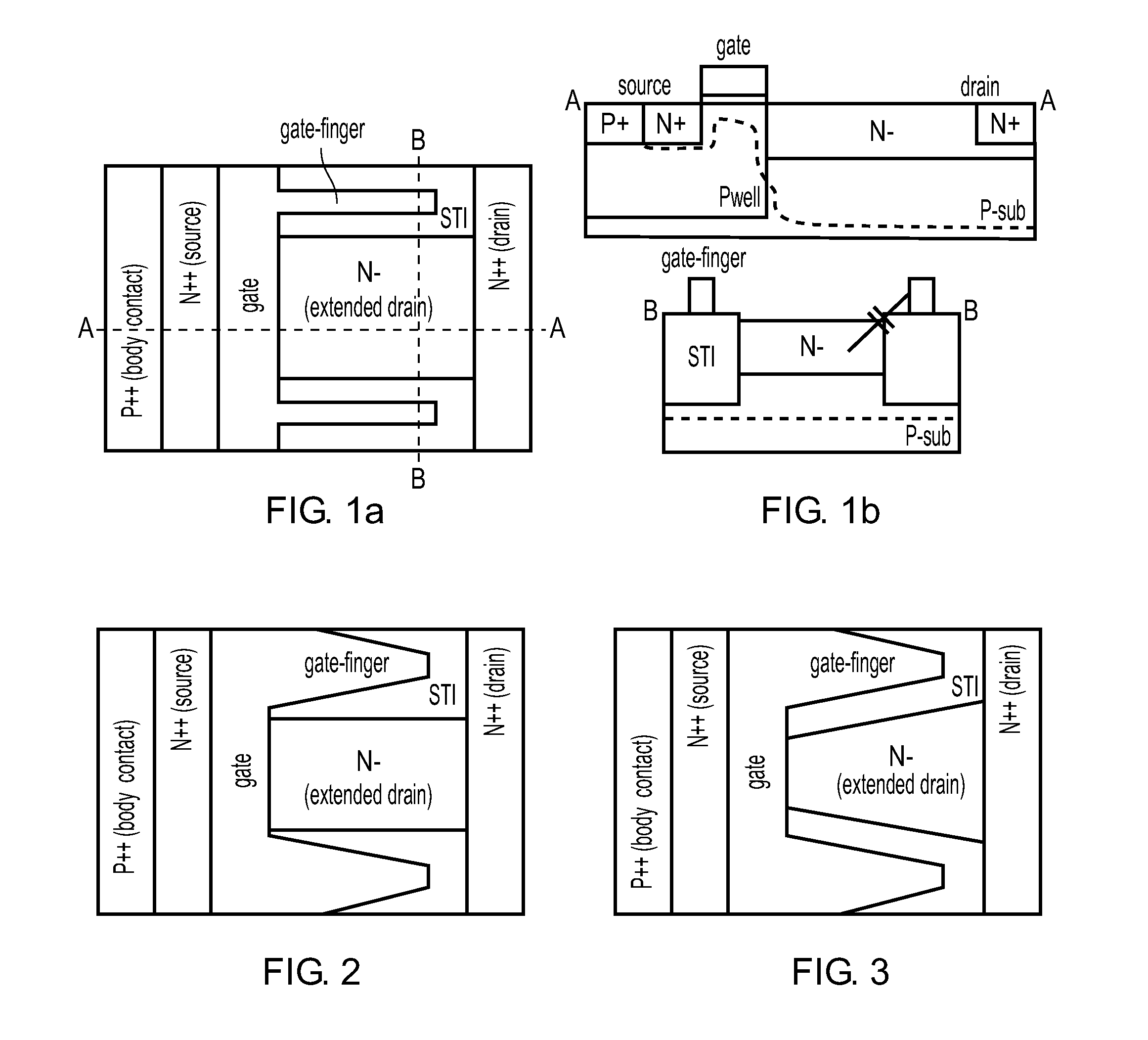

Trench gate laterally diffused MOSFET devices and methods for making such devices

InactiveUS7033891B2Well breakdown capabilityLow gate-drain capacitanceSemiconductor/solid-state device manufacturingSemiconductor devicesHot carrier effectElectric field

A MOSFET device for RF applications that uses a trench gate in place of the lateral gate used in lateral MOSFET devices is described. The trench gate in the devices of the invention is provided with a single, short channel for high frequency gain. The device of the invention is also provided with an asymmetric oxide in the trench gate, as well as LDD regions that lower the gate-drain capacitance for improved RF performance. Such features allow these devices to maintain the advantages of the LDMOS structure (better linearity), thereby increasing the RF power gain. The trench gate LDMOS of the invention also reduces the hot carrier effects when compared to regular LDMOS devices by reducing the peak electric field and impact ionization. Thus, the devices of the invention will have a better breakdown capability.

Owner:SEMICON COMPONENTS IND LLC

High voltage semiconductor device

InactiveUS20100213517A1Conveniently exploitedEnhances Rds-on versus breakdown FigureSemiconductor/solid-state device manufacturingSemiconductor devicesElectrical resistance and conductanceCMOS

This invention describes implementation of medium / high voltage semiconductor devices with a better voltage-blocking capability versus specific on-resistanσe trade off. This approach can be implemented in baseline and submicron CMOS without any additional process steps. Said devices comprise dielectric regions and semiconductor regions formed between them. Conductive extentions are formed on the dielectric regions, said extentions interacting capacitively with the semiconducter regions.

Owner:NXP BV

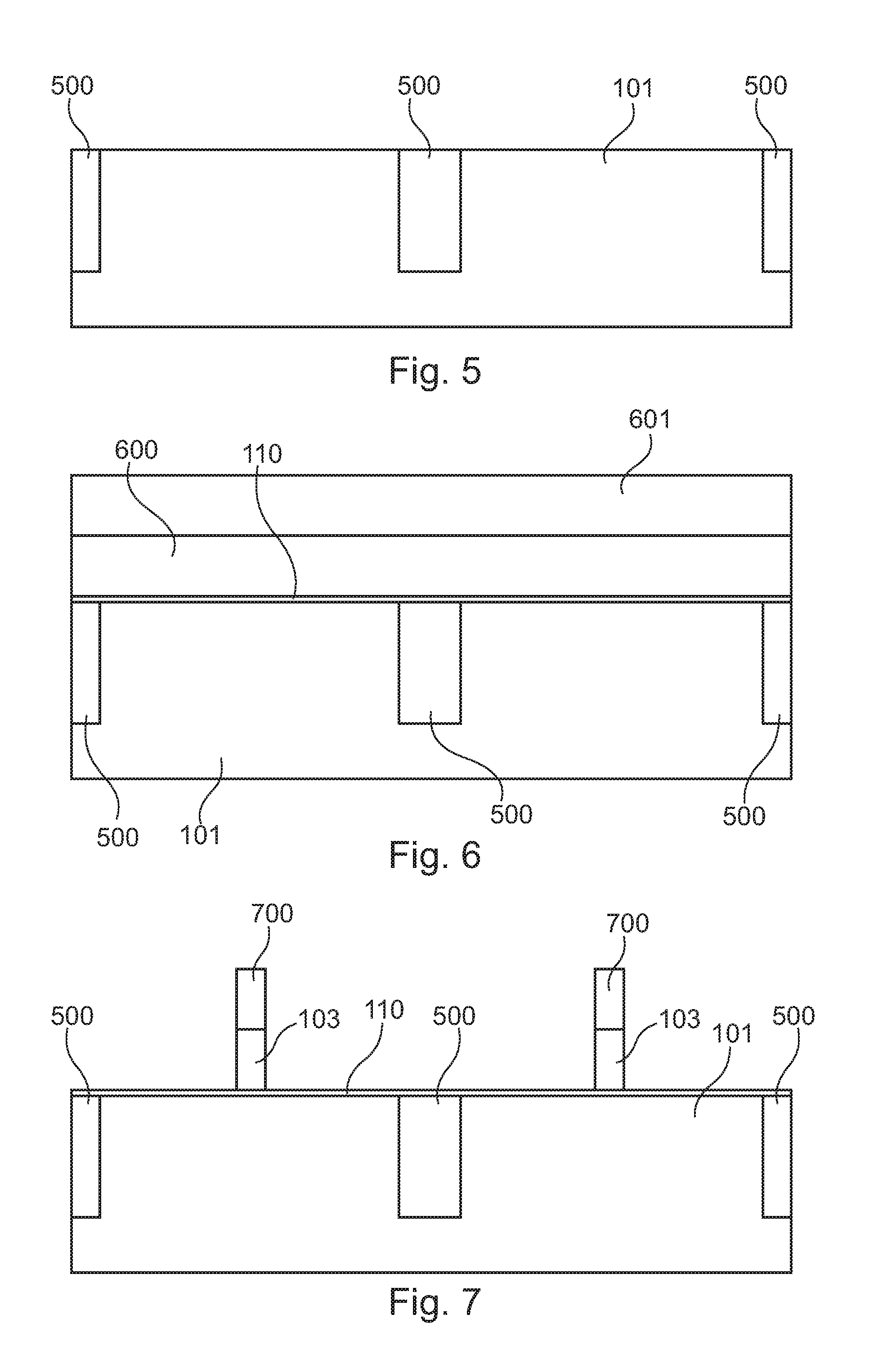

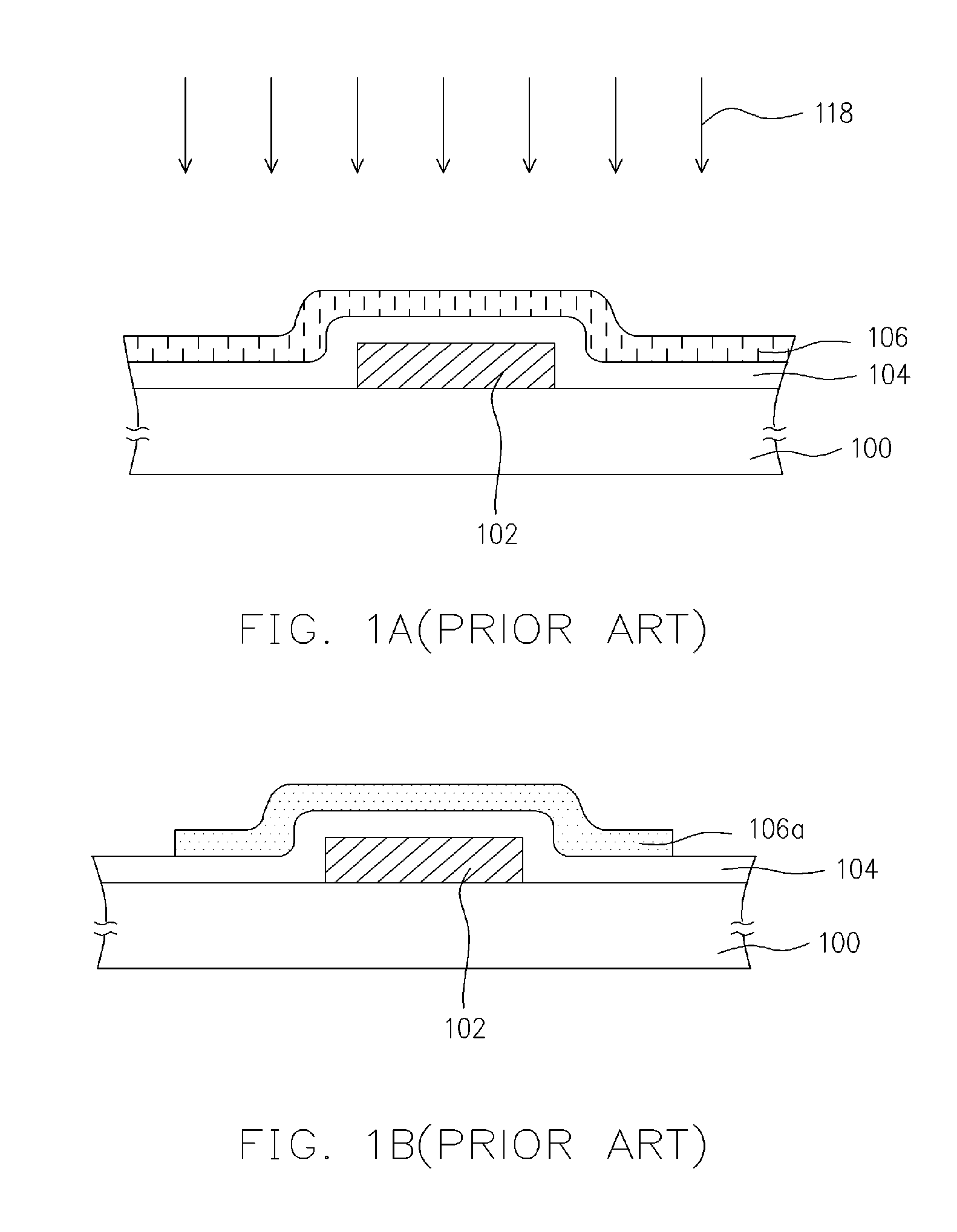

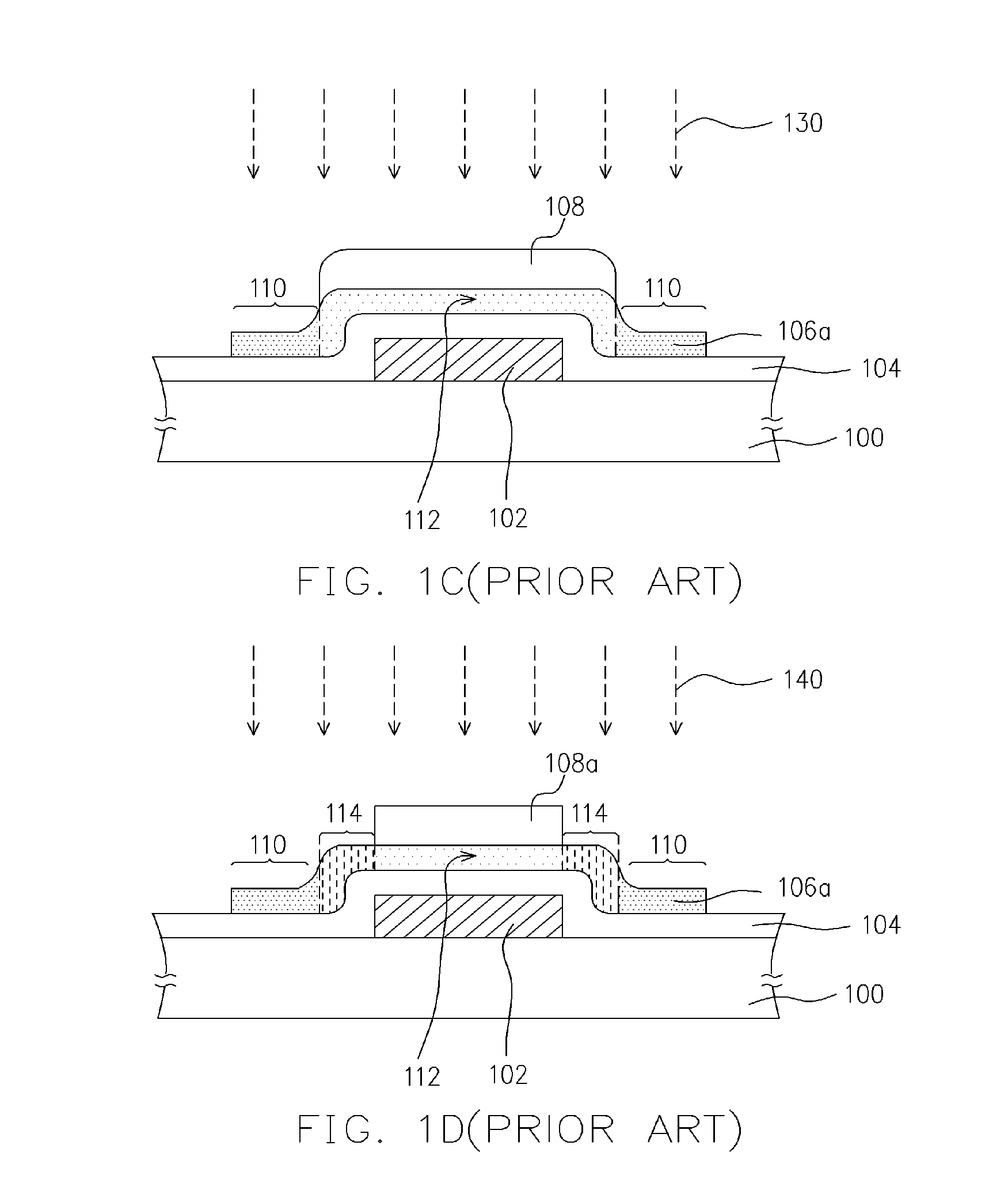

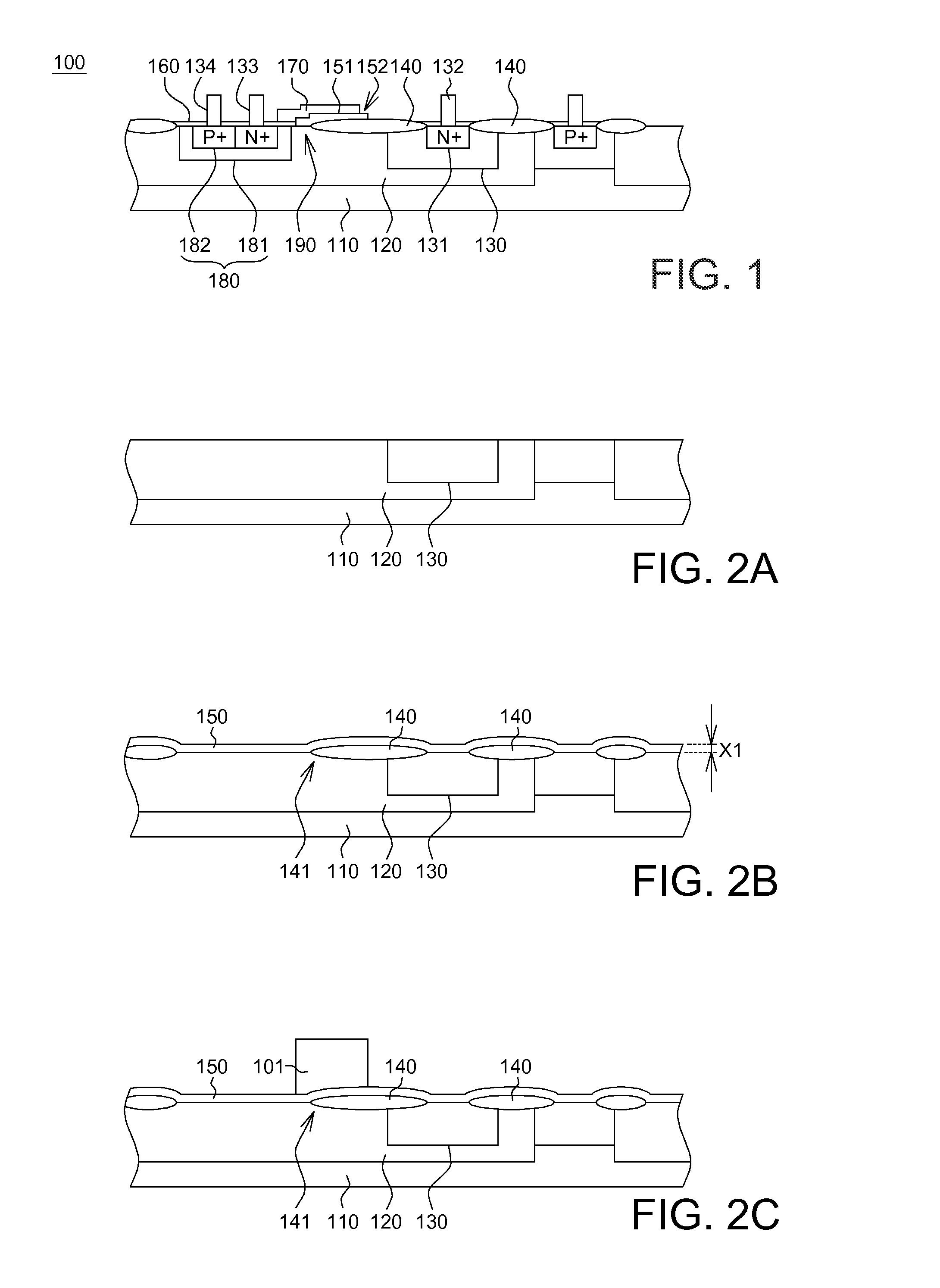

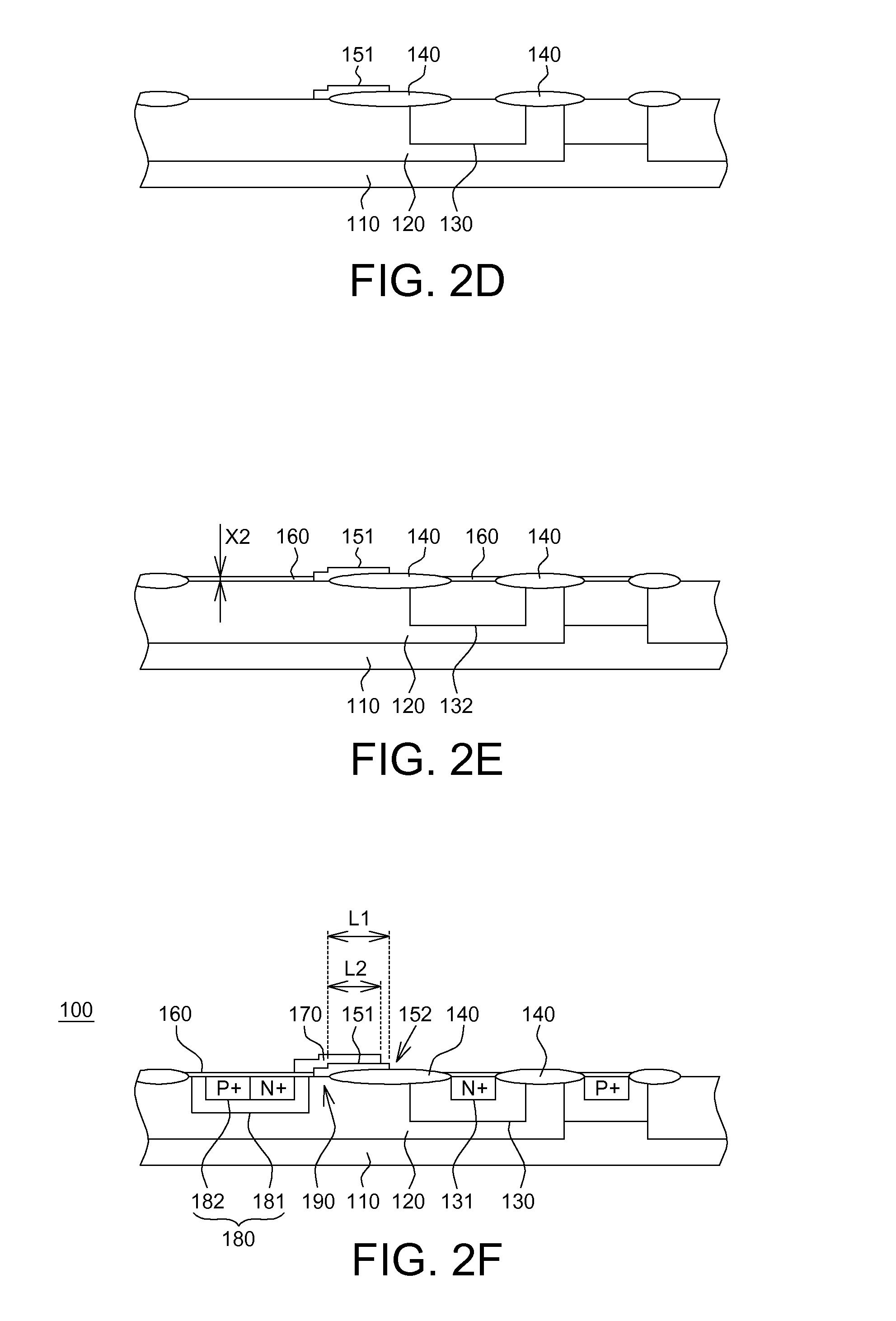

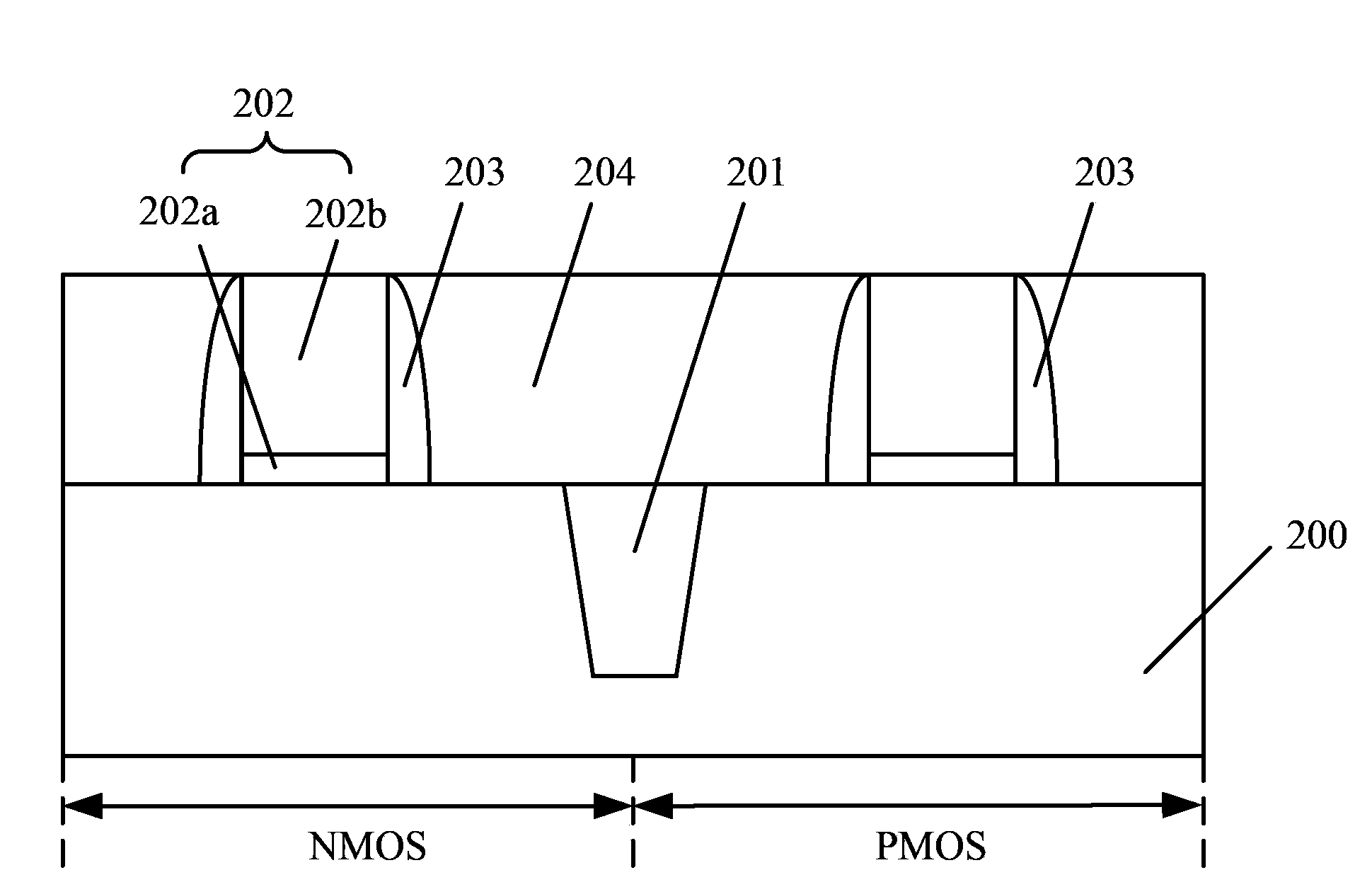

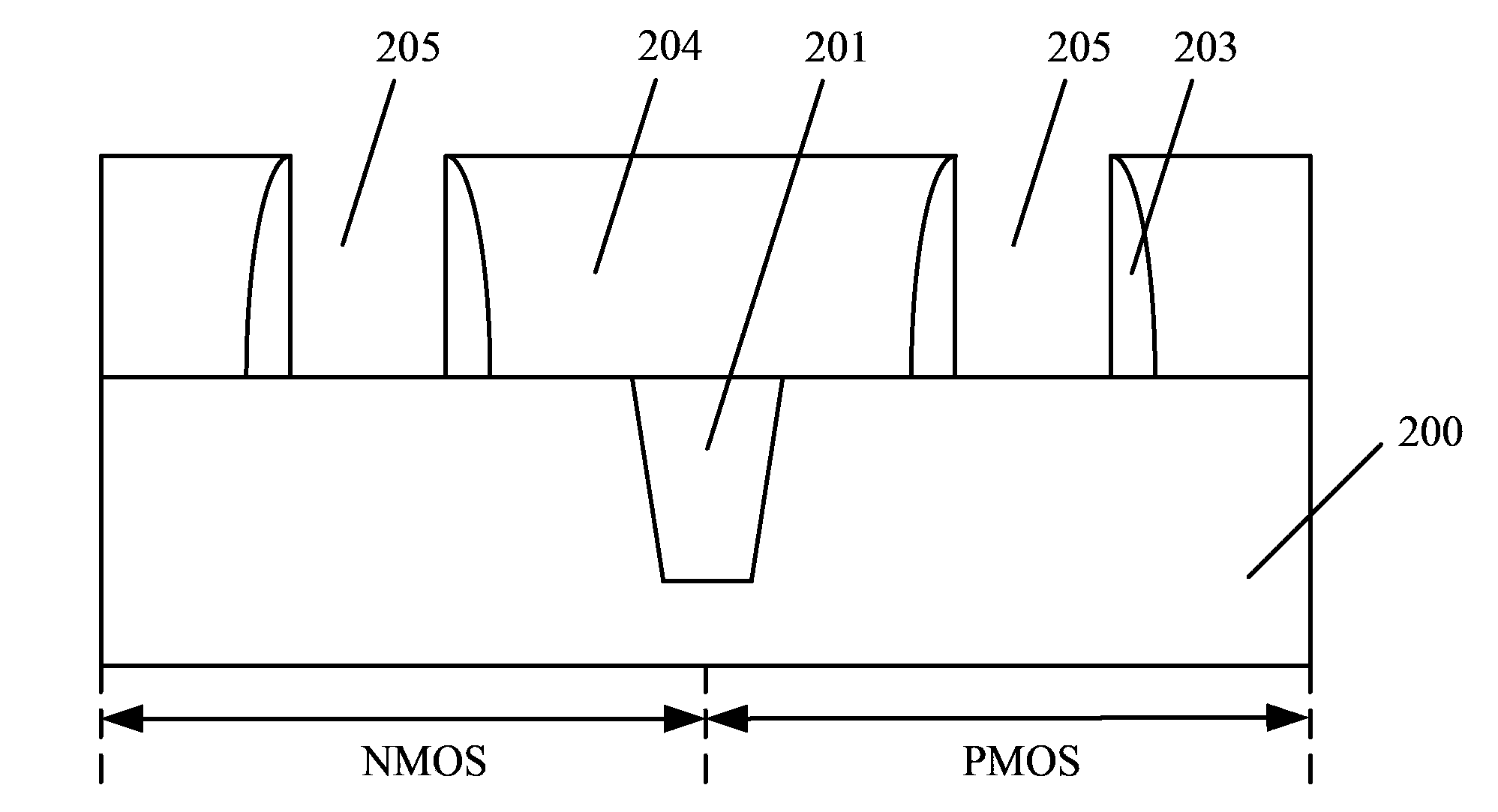

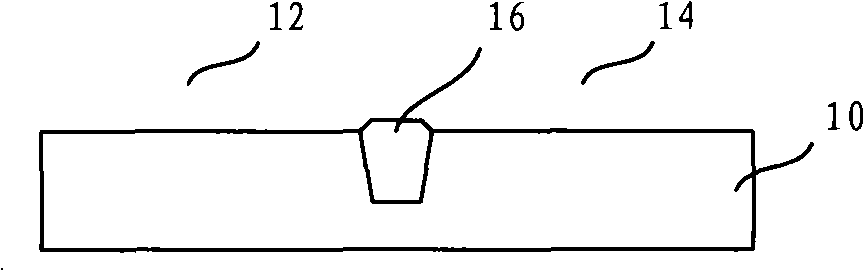

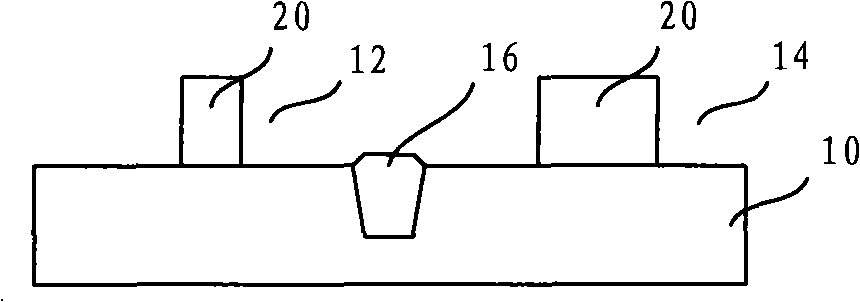

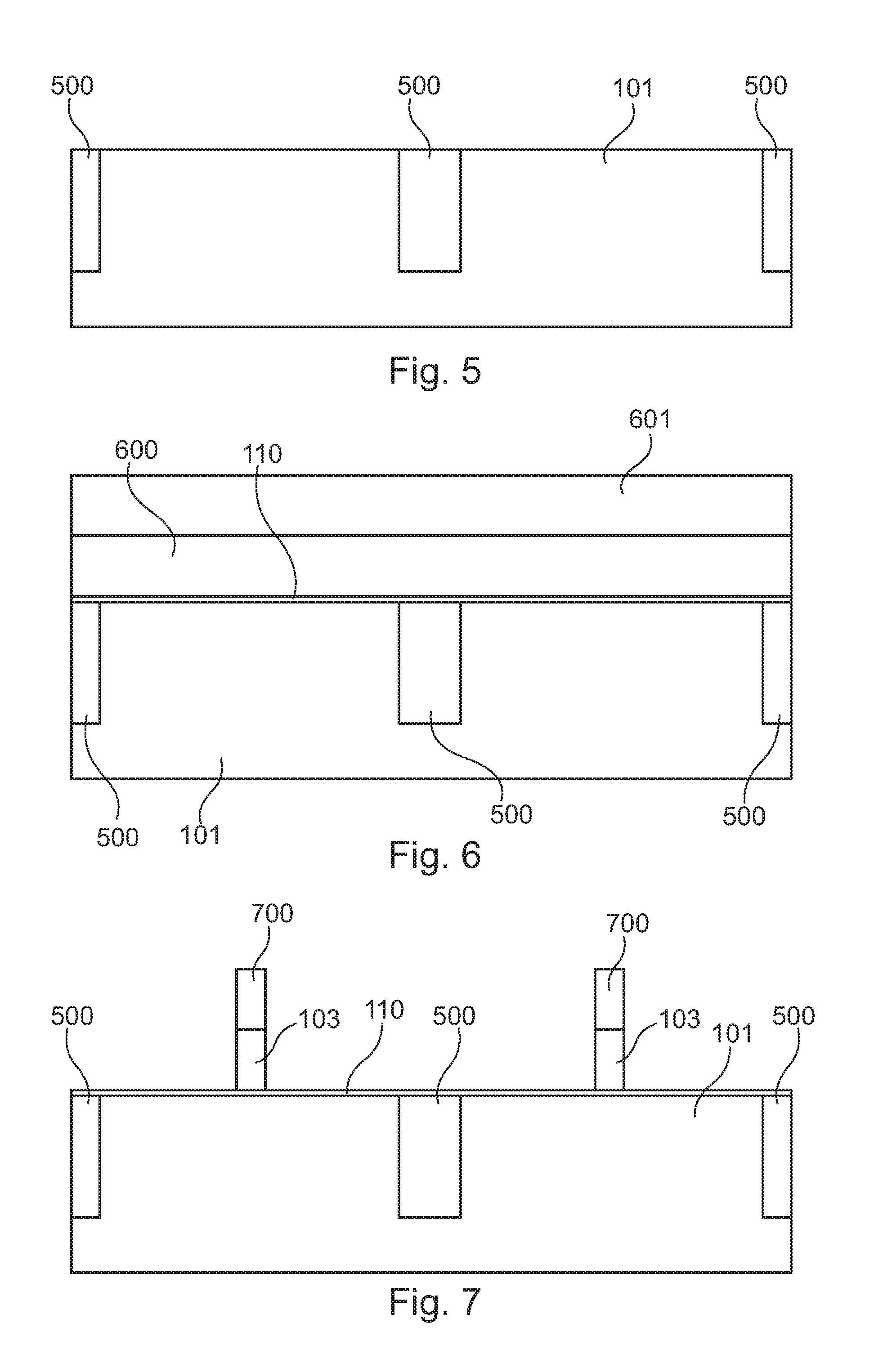

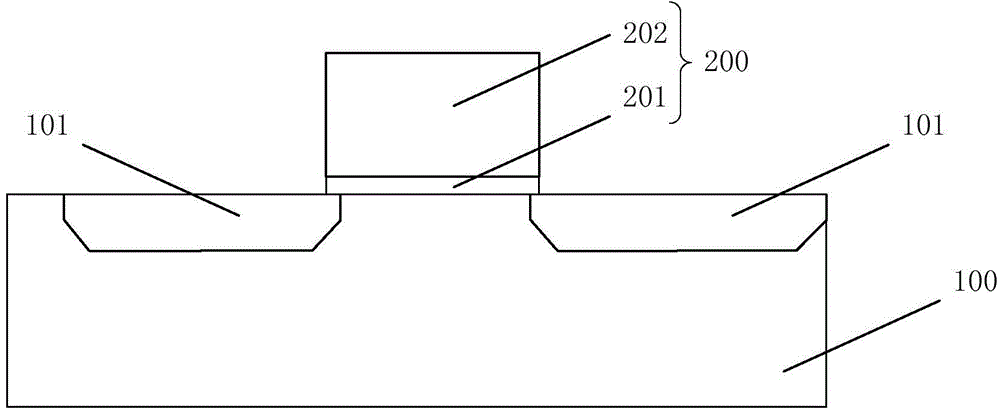

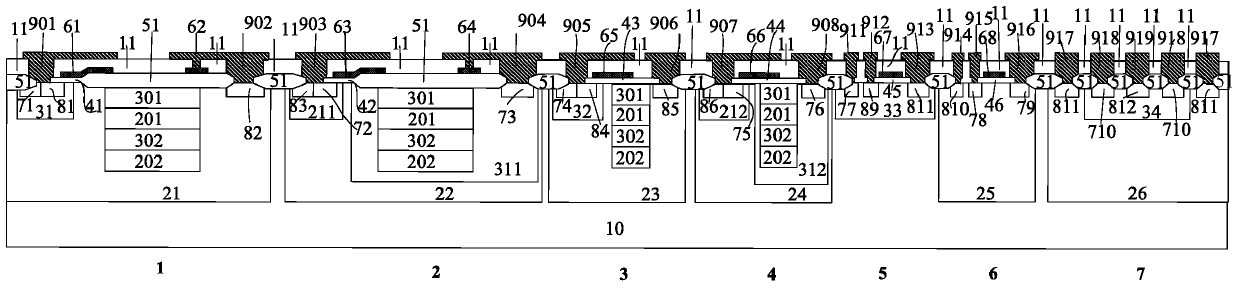

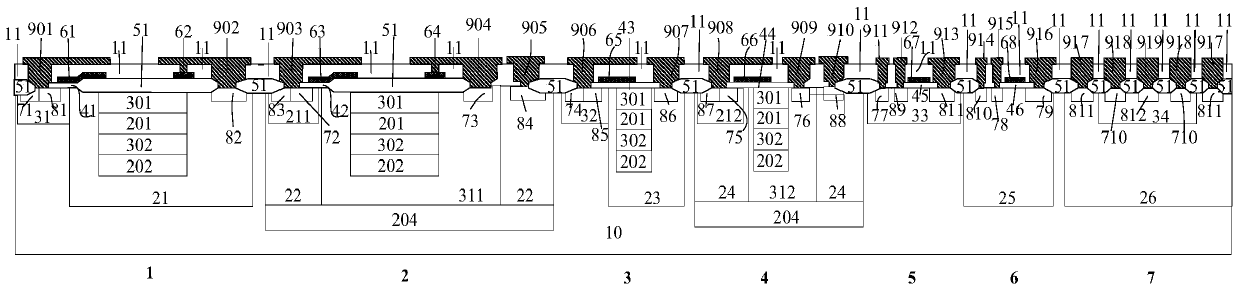

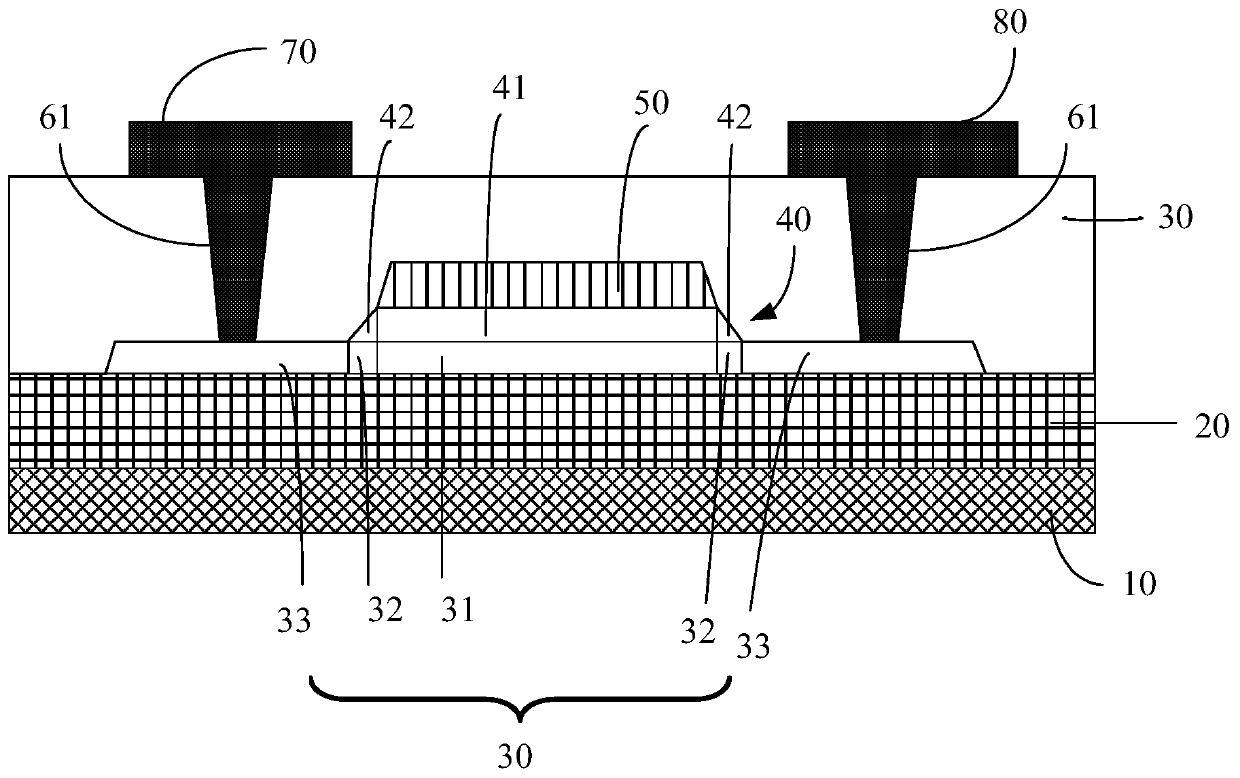

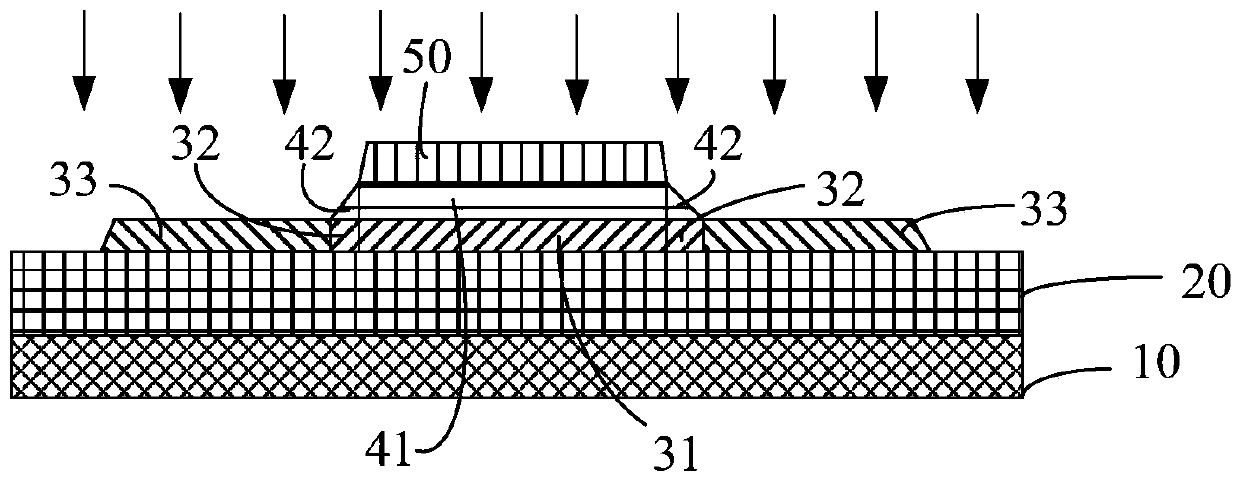

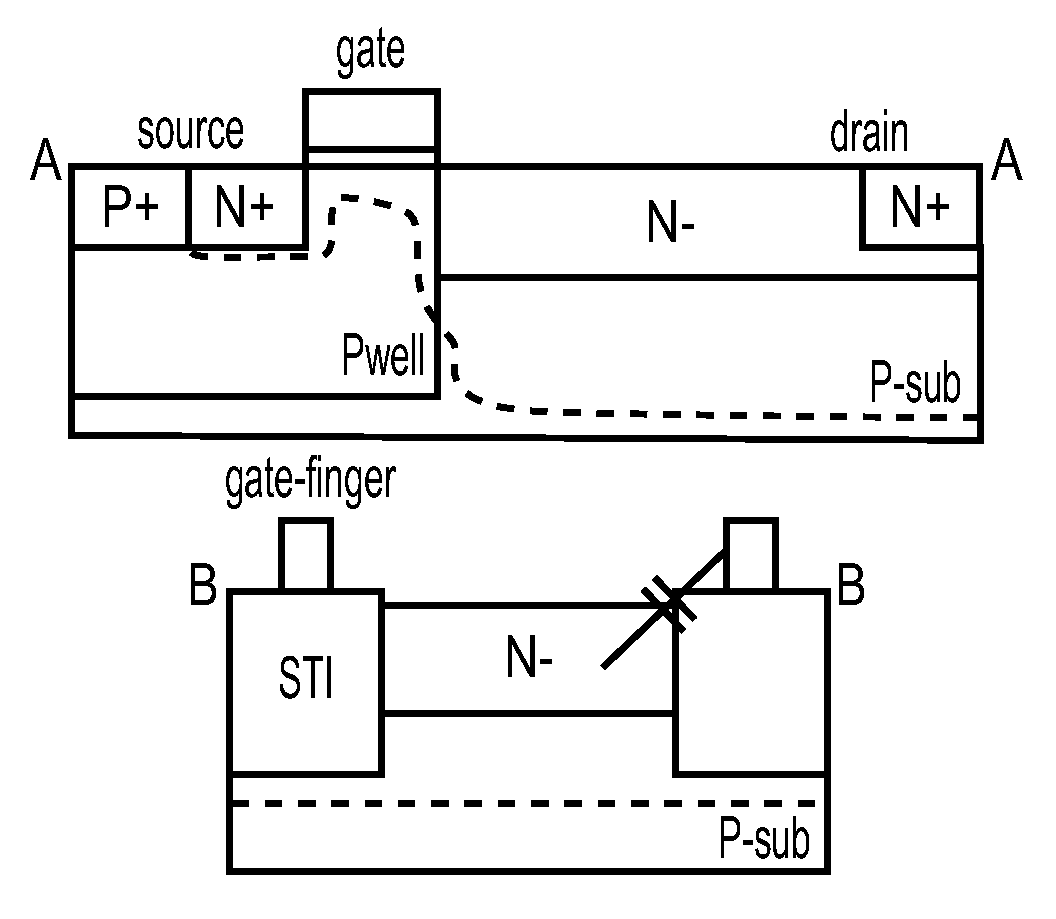

[low-temperature polysilicon thin film transistor and fabrication method thereof]

InactiveUS20050218403A1Improve device performanceReduce manufacturing costTransistorSolid-state devicesGate dielectricOhmic contact

An LTPS-TFT structure comprises a gate, a gate dielectric layer, a patterned silicon layer, a patterned insulating layer, an ohmic contact layer and a source / drain layer. The gate and the gate dielectric layer are disposed on the substrate. The patterned silicon layer and the patterned insulating layer are disposed on the gate dielectric layer over the gate. The patterned silicon layer comprises a polysilicon channel region and an amorphous silicon hot carrier restrain region. The ohmic contact layer is disposed on a portion of the patterned silicon layer other than the polysilicon channel region and the amorphous silicon hot carrier restrain region and a portion of the patterned insulating layer over the amorphous silicon hot carrier restrain region. The source / drain layer is disposed on the ohmic contact layer and the gate dielectric layer.

Owner:AU OPTRONICS CORP

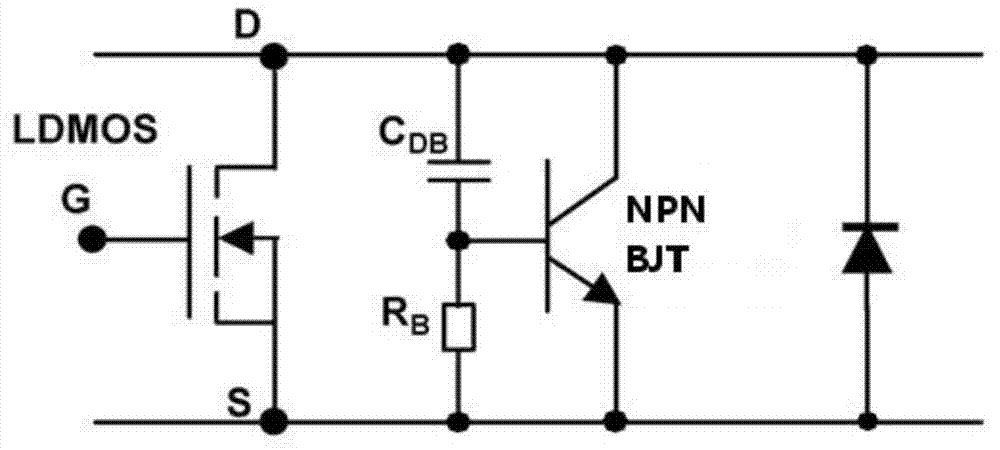

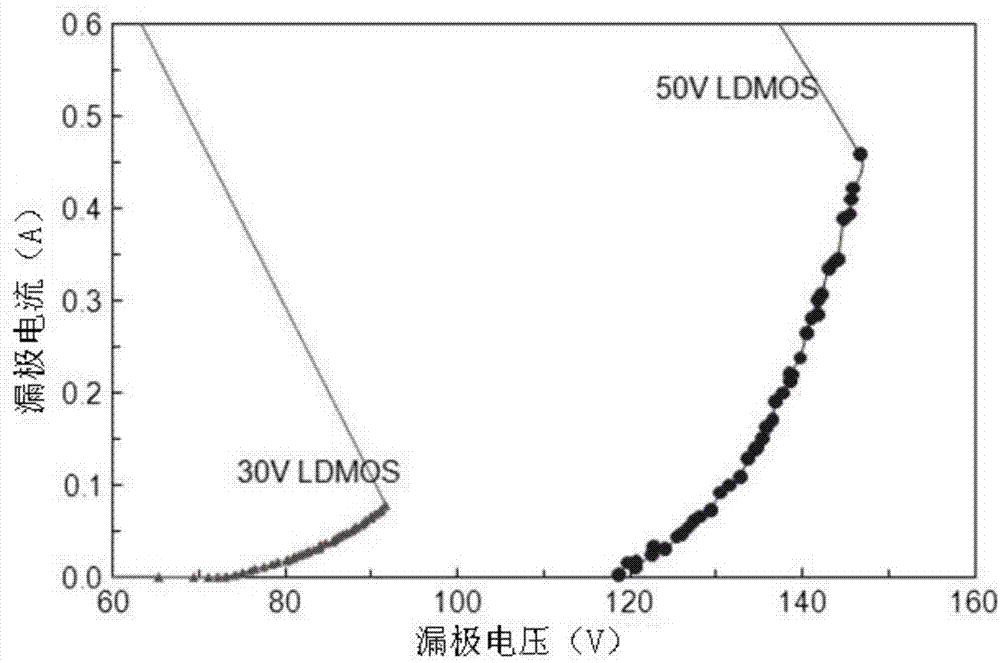

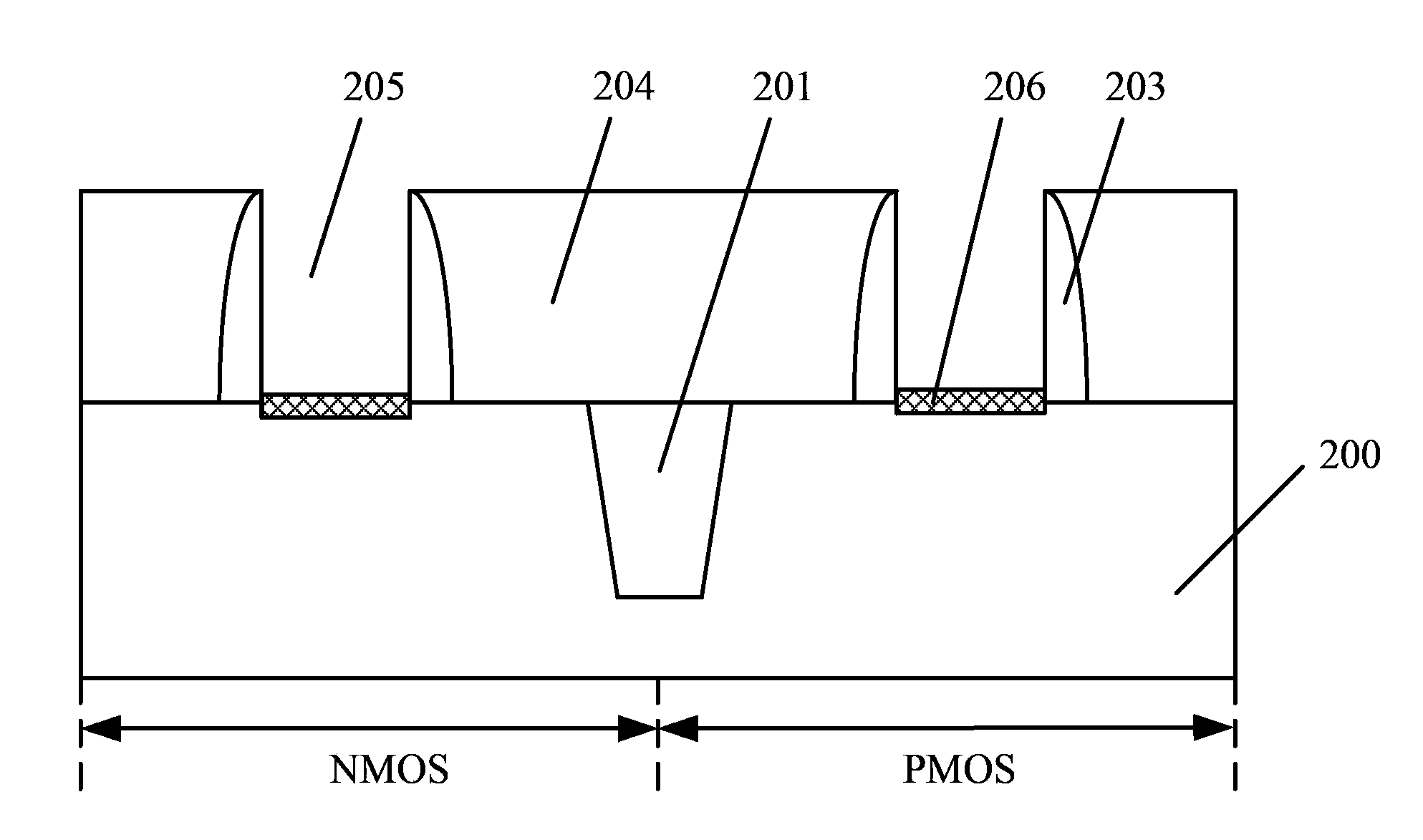

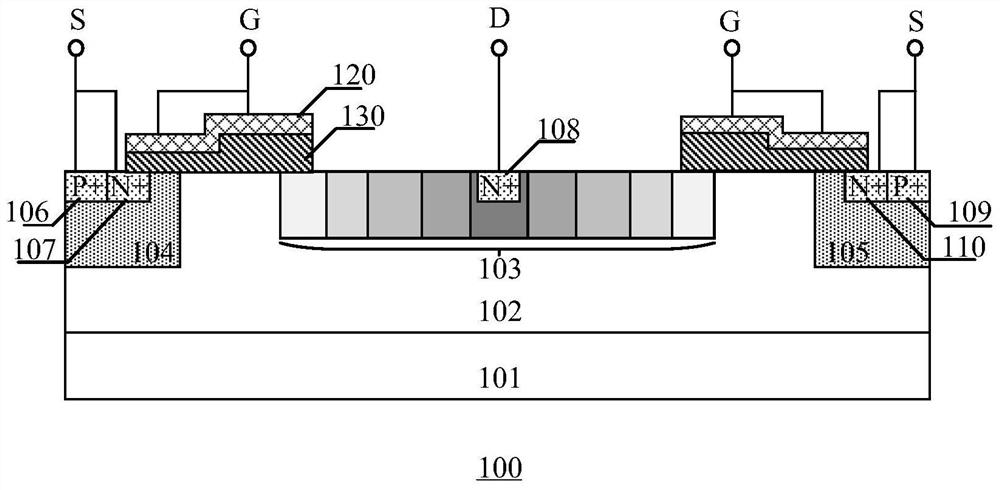

Radio frequency (RF) laterally diffused metal oxide semiconductor (LDMOS) component and manufacture method

ActiveCN103035727AImprove transconductanceLower base resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesRadio frequencyTransconductance

The invention discloses a radio frequency (RF) laterally diffused metal oxide semiconductor (LDMOS) component. A light dope P type buried layer and a middle dope buried layer in the light dope P type buried layer are additionally arranged under a P type channel region. The base electrode resistance of a parasitic non-protein nitrogen (NPN) pipe can be reduced, so that snapback effect is not prone to be generated. A reversed diode formed by a source electrode, the channel and the buried layer can strangulate drain-source voltage of an LDMOS and can sink extra current on a substrate. Thick gate oxide at the drain electrode end can reduce hot carrier effect, and thin gate oxide at the source electrode end can improve transconductance of the component. The invention further discloses a manufacture method of the RF LDMOS component. In process realization, the manufacture method only adds two photoetching steps in an existing process so as to be easy to implement.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

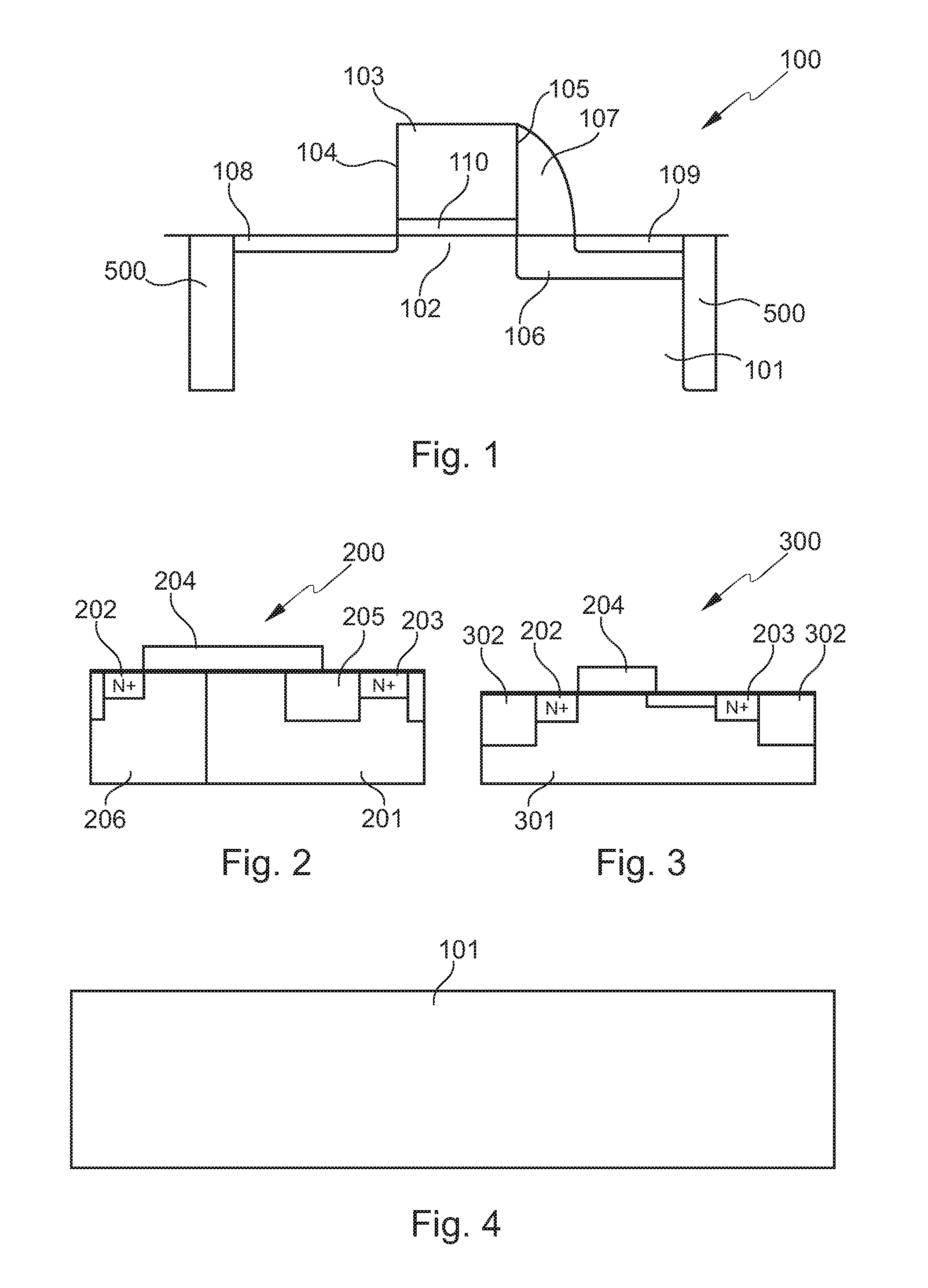

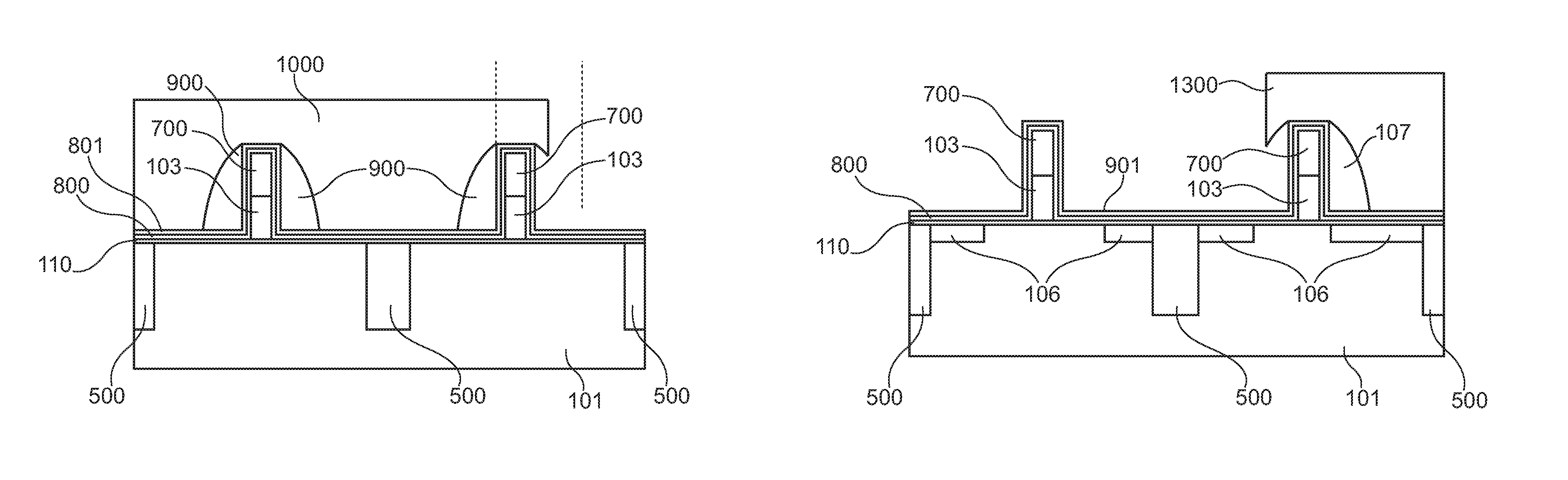

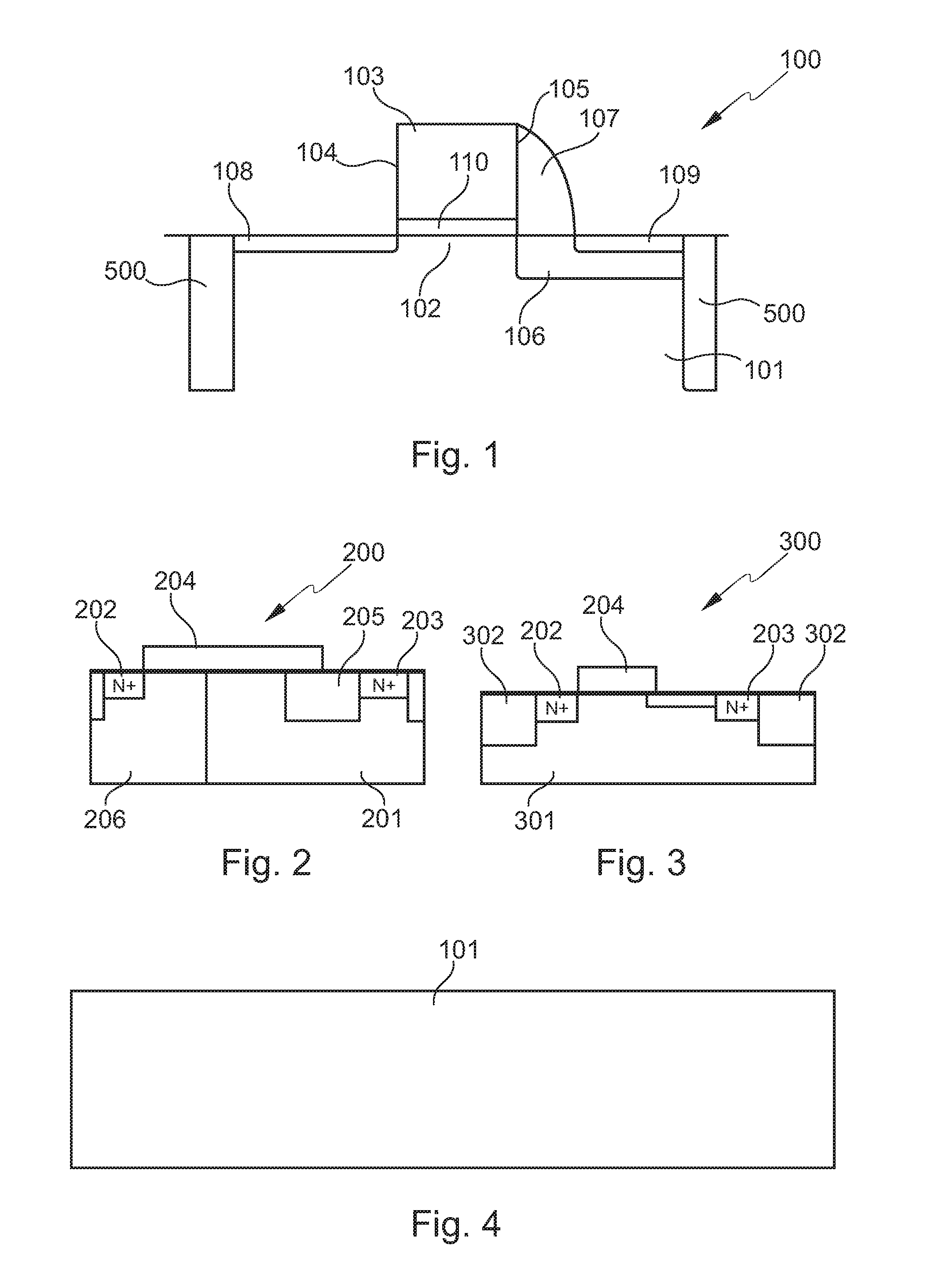

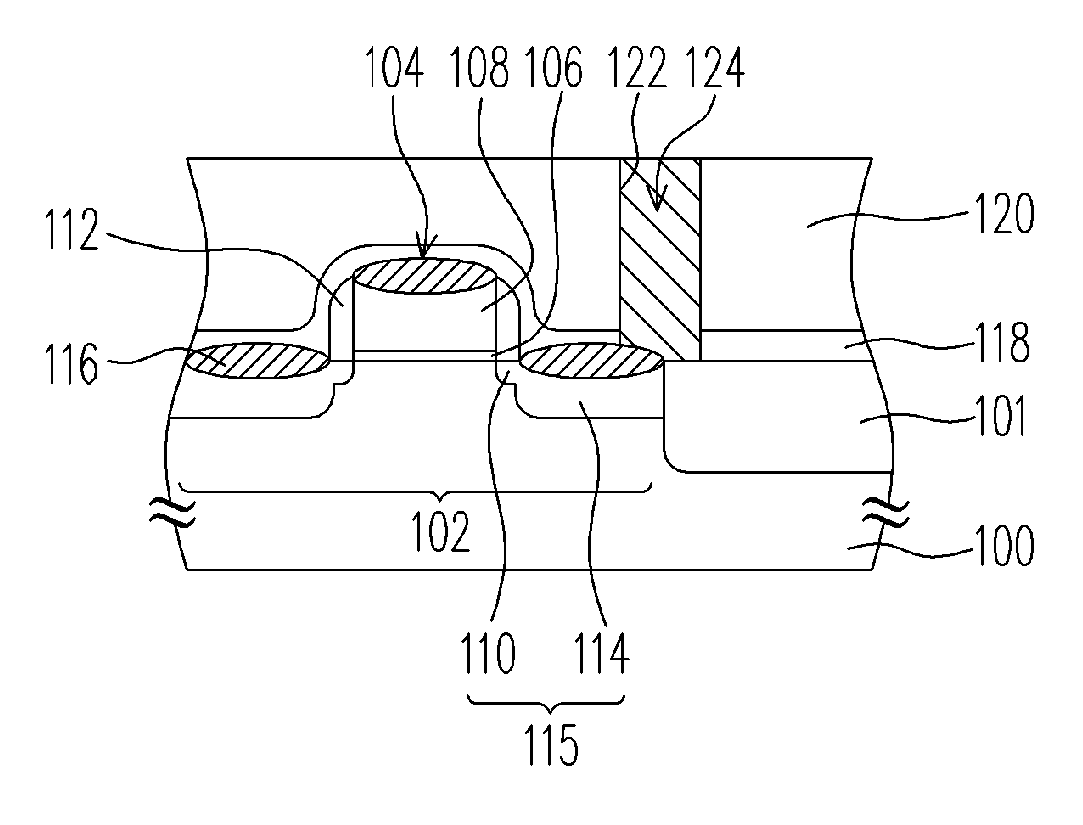

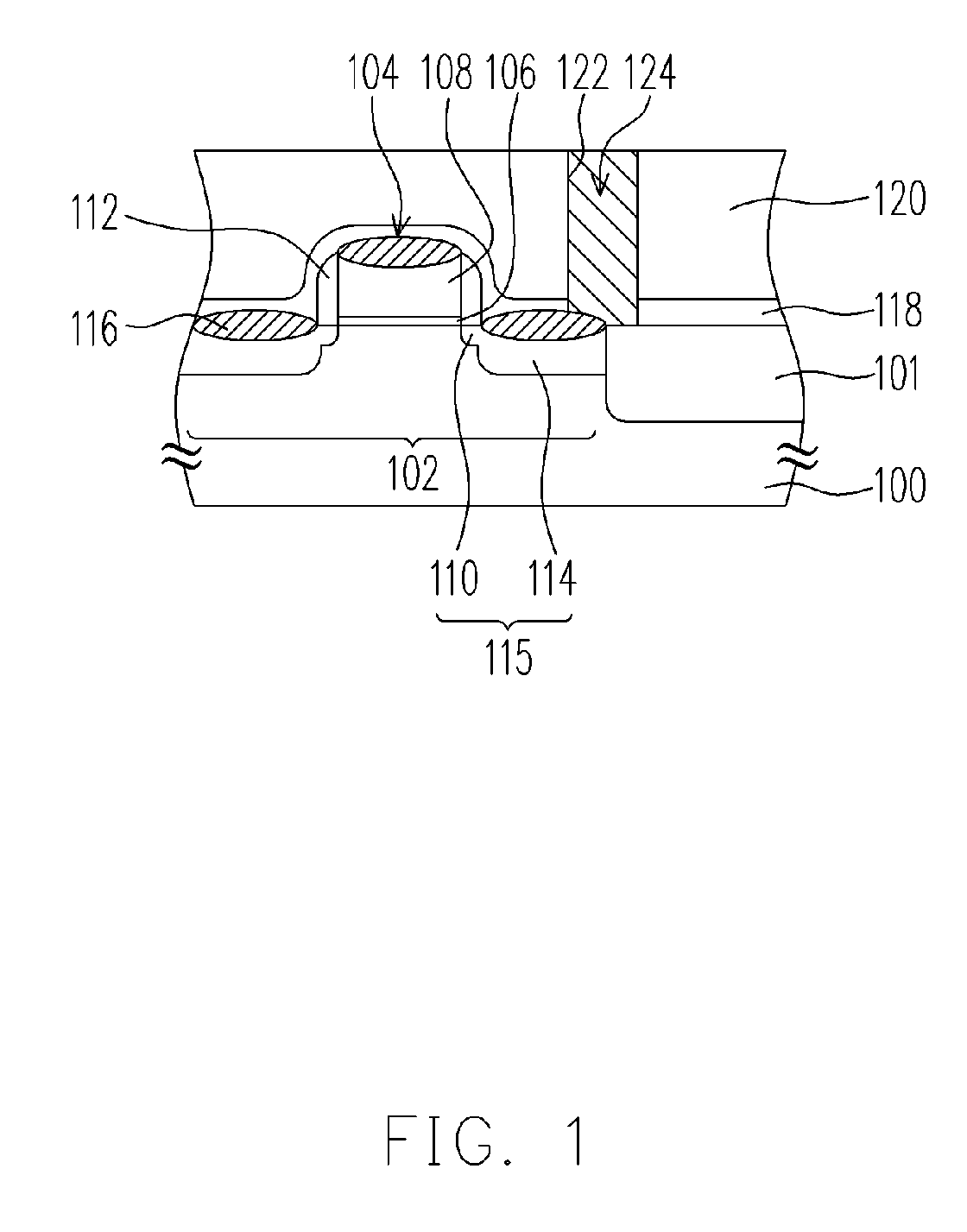

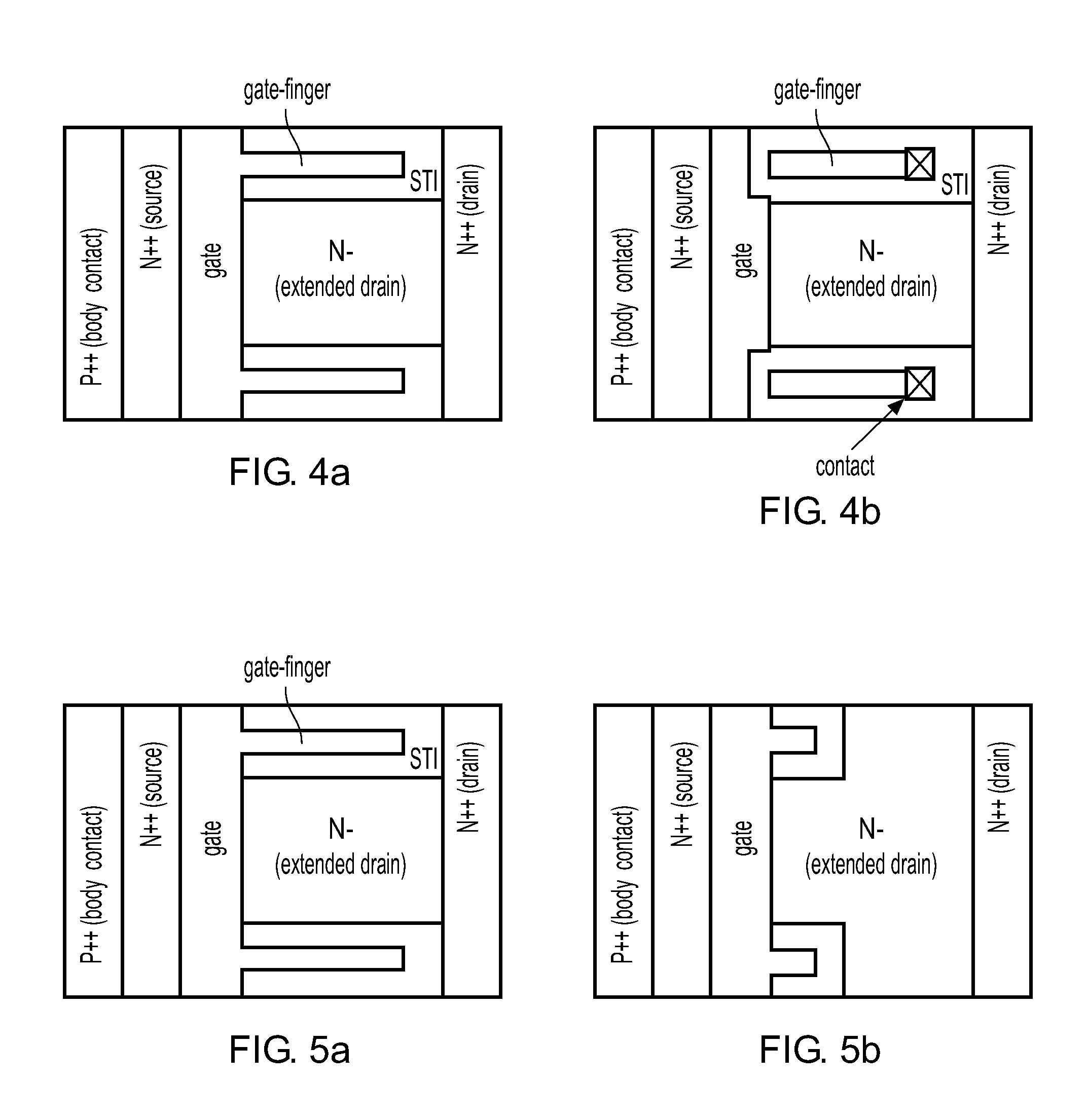

Extended drain transistor and method of manufacturing the same

ActiveUS20100181618A1Reduce dopingReduce hot carrier effectSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringTransistor

An extended drain transistor (100) comprising a substrate (101), a gate (103) formed on the substrate (100), the gate (103) having a first side wall (104) and a second side wall (105) opposing the first side wall (104), an extended drain (106) implanted in a surface portion of the substrate (101) adjacent the second side wall (105) of the gate (103), a spacer (107) on the second side wall (105) of the gate (103), a source (108) implanted in a surface portion of the substrate (101) adjacent the first side wall (104) of the gate (103), and a drain (109) implanted in a surface portion of the substrate (101) adjacent the spacer (107) in such a manner that the extended drain (106) is arranged between the gate (103) and the drain (109).

Owner:NXP BV

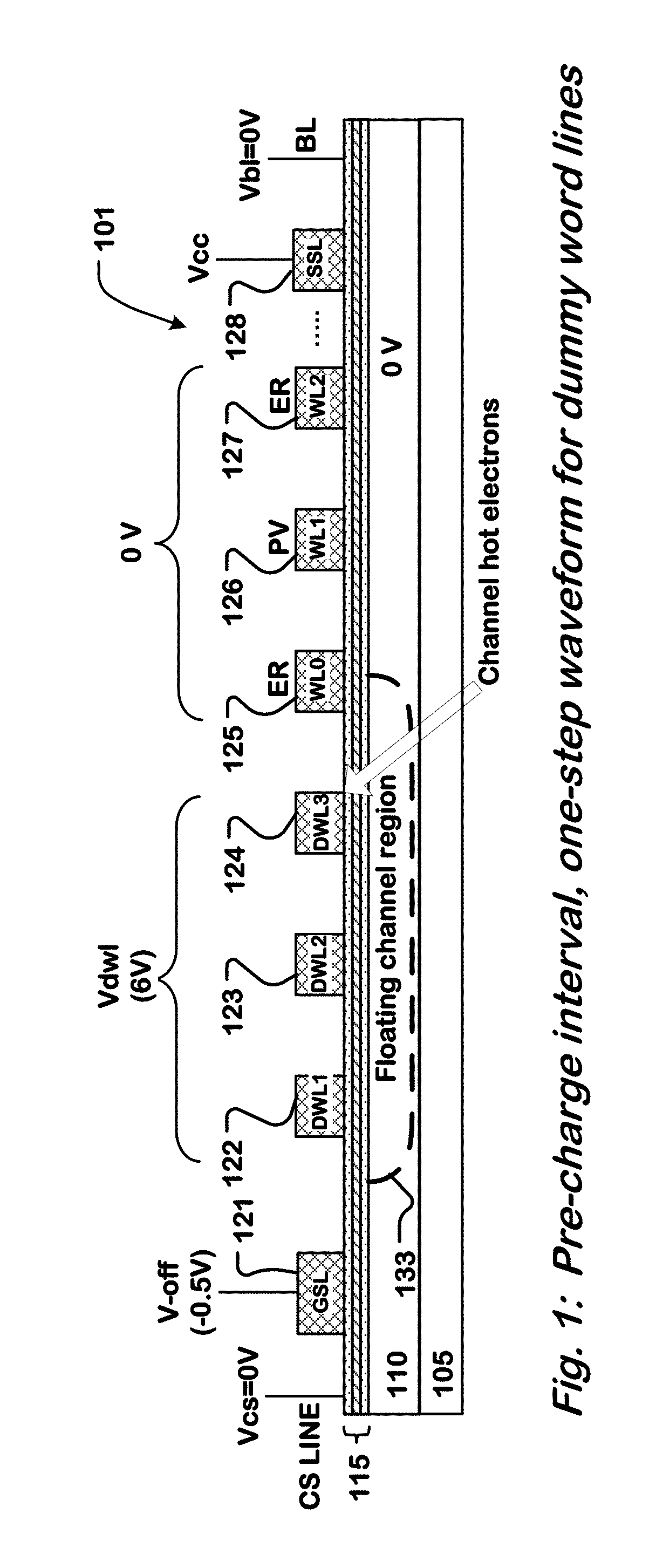

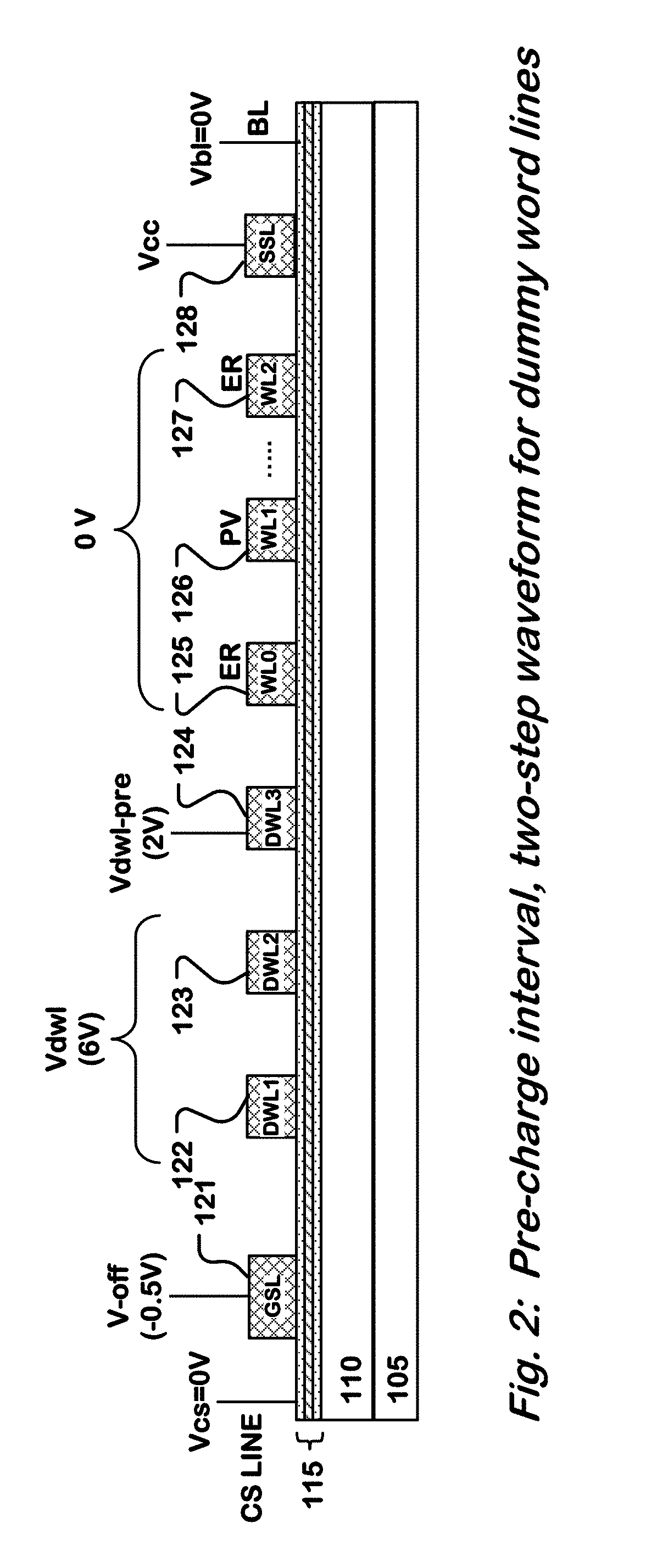

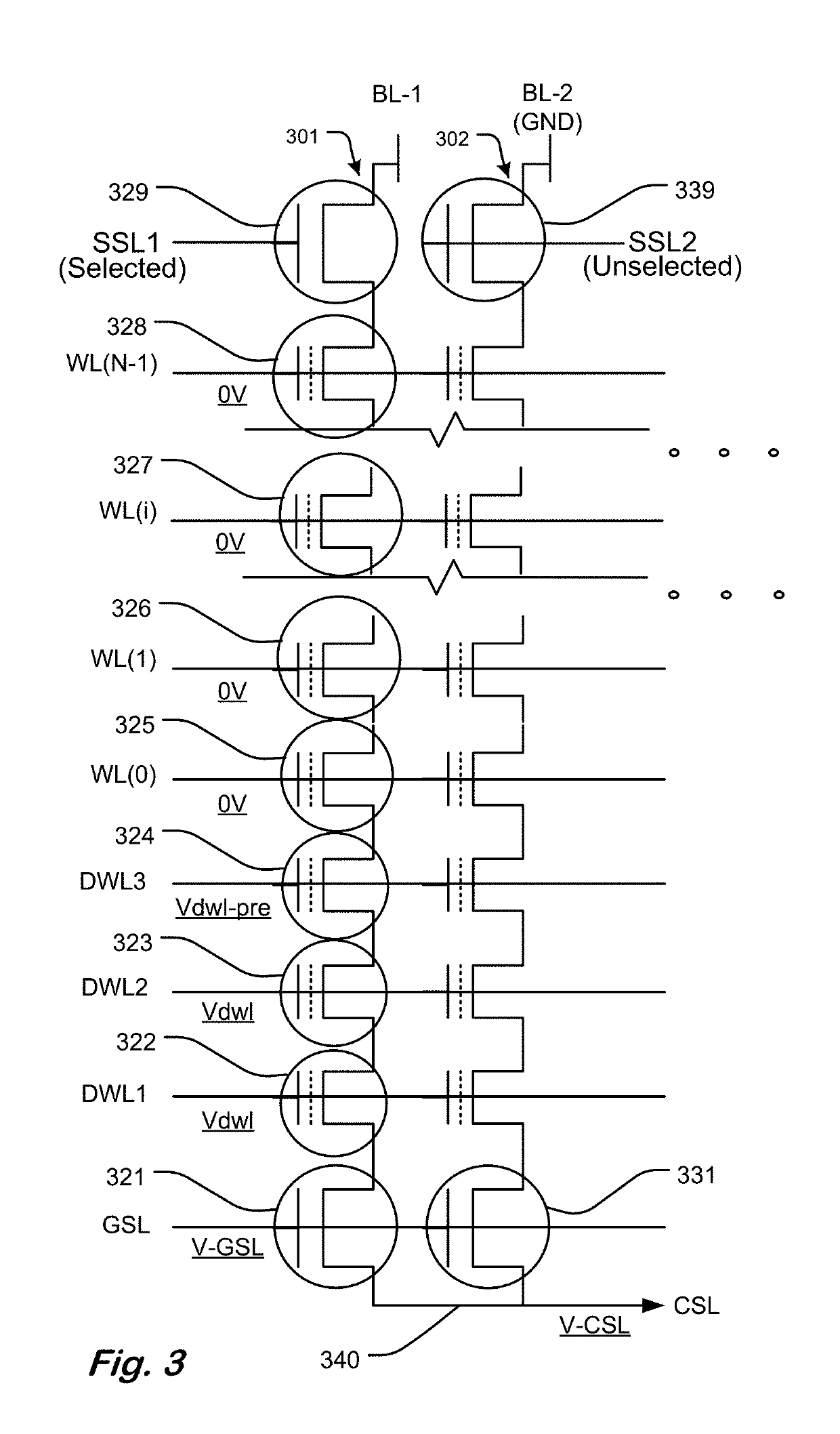

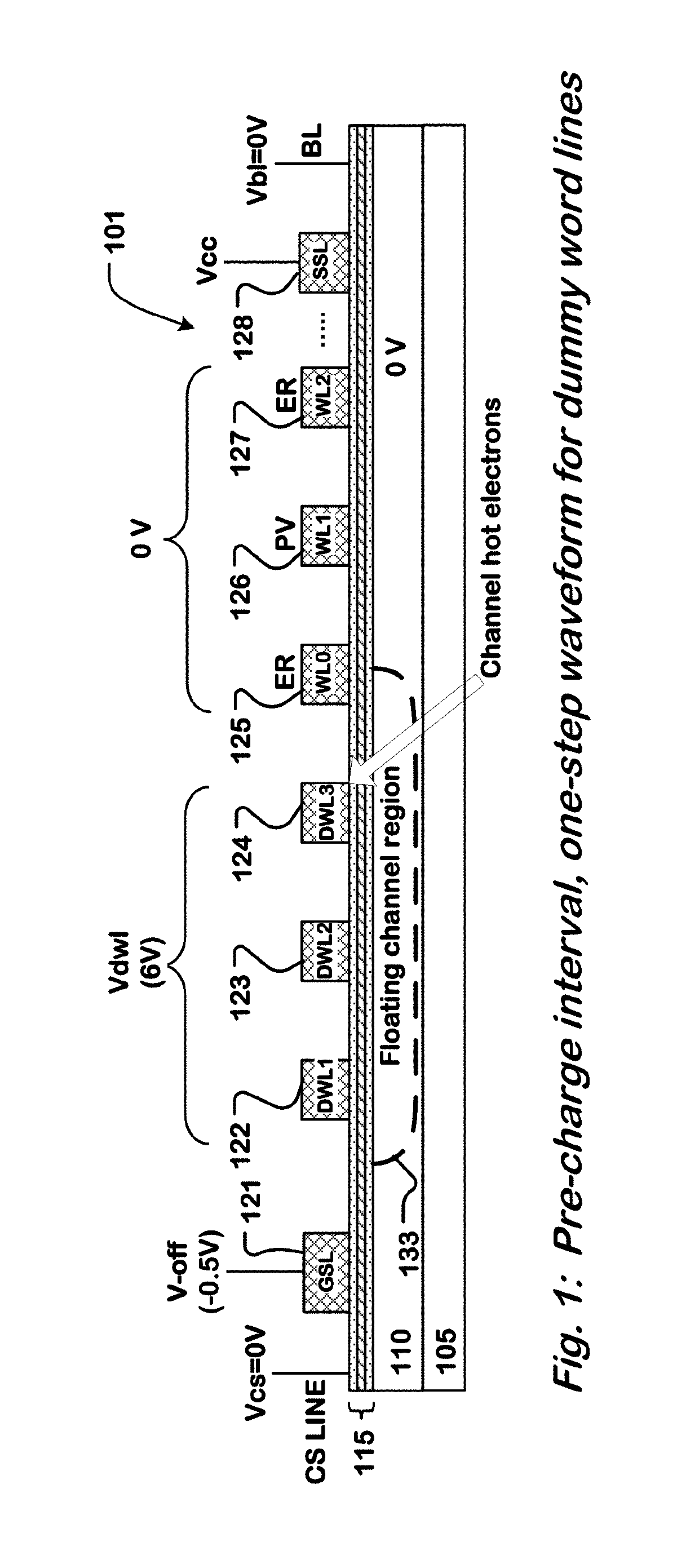

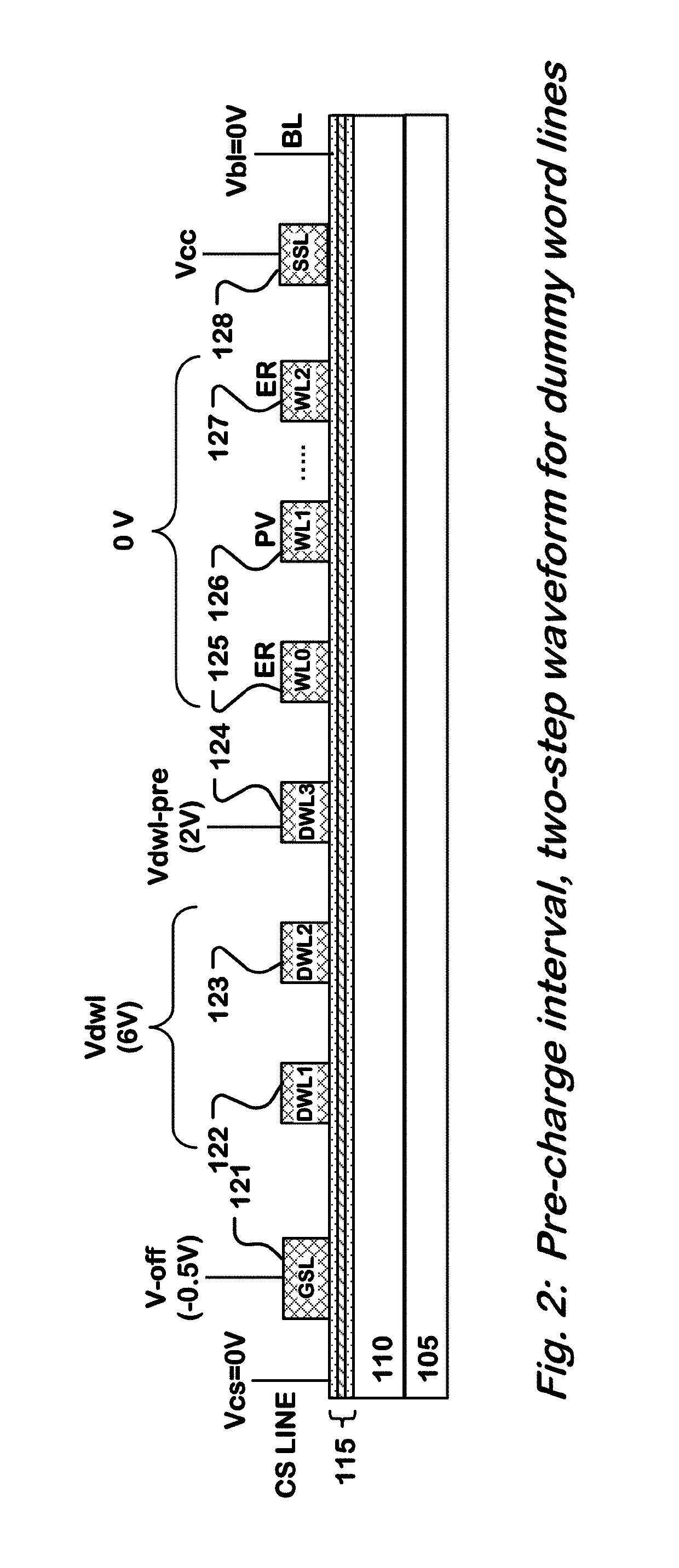

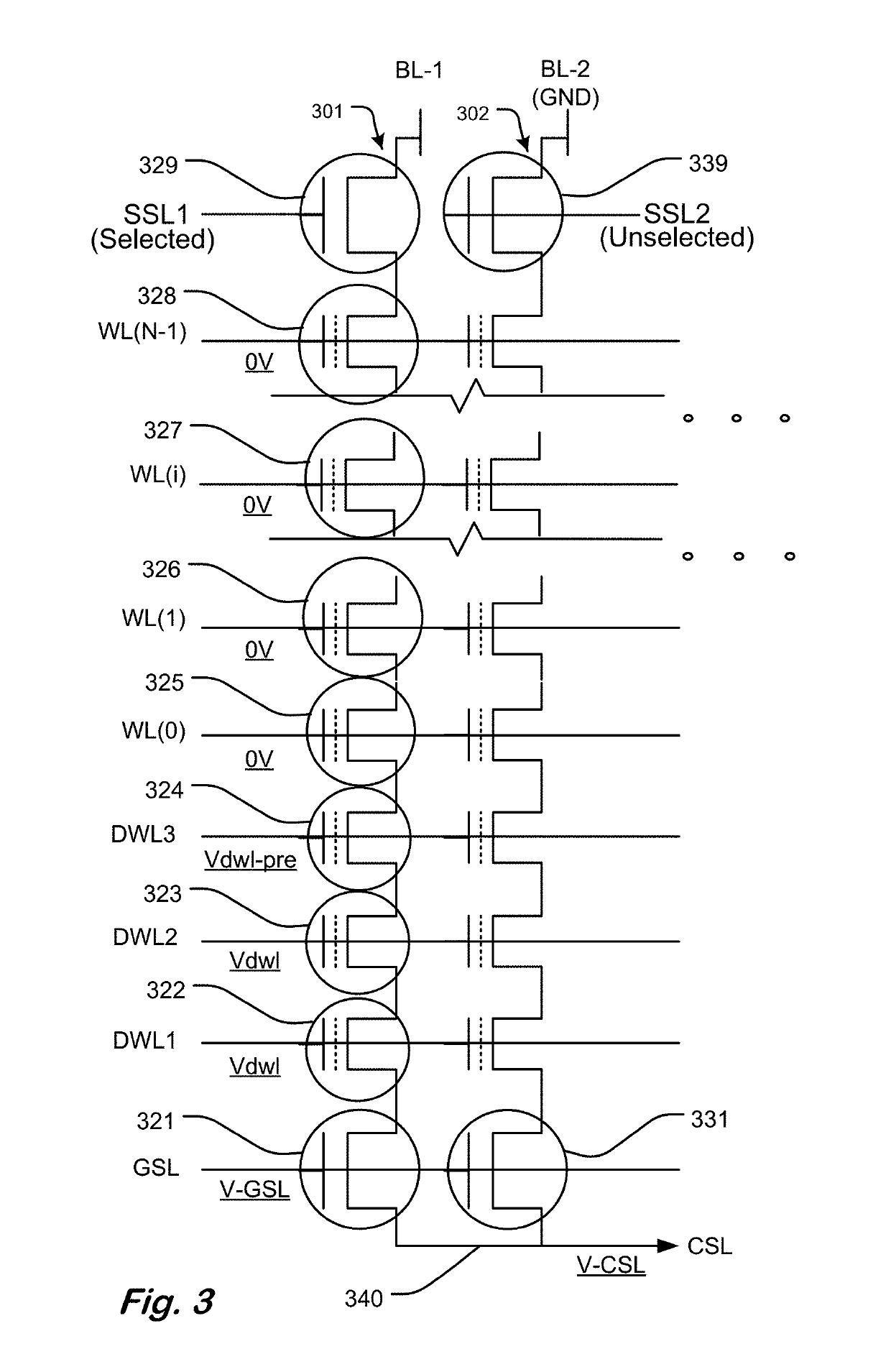

Programming NAND flash with improved robustness against dummy wl disturbance

ActiveUS20190156901A1Diminish boosted potentialReduce distractionsSolid-state devicesRead-only memoriesControl circuitComputer science

A memory device includes a plurality of memory cells arranged in series in a semiconductor body. First and second dummy memory cells arranged in series between a first string select switch and a first edge memory cell at a first end of the plurality of memory cells. The first dummy memory cell is adjacent the first edge memory cell, and the second dummy memory cell is adjacent the first string select switch. A channel line includes channels for the plurality of memory cells and the first and second dummy memory cells. Control circuitry is adapted for programming a selected memory cell in the plurality of memory cells corresponding to a selected word line by applying a switching voltage to the first dummy memory cell, the switching voltage having a first voltage level during a first time interval, and thereafter changing to a second voltage level higher than the first voltage level.

Owner:MACRONIX INT CO LTD

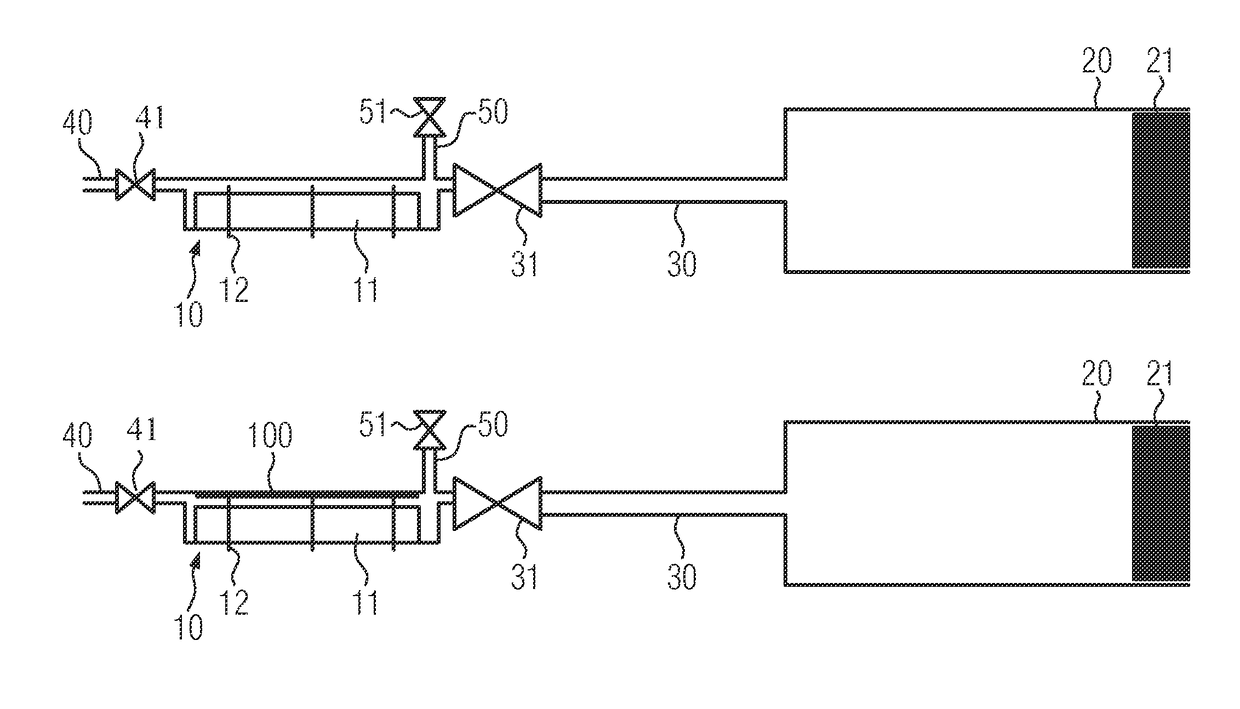

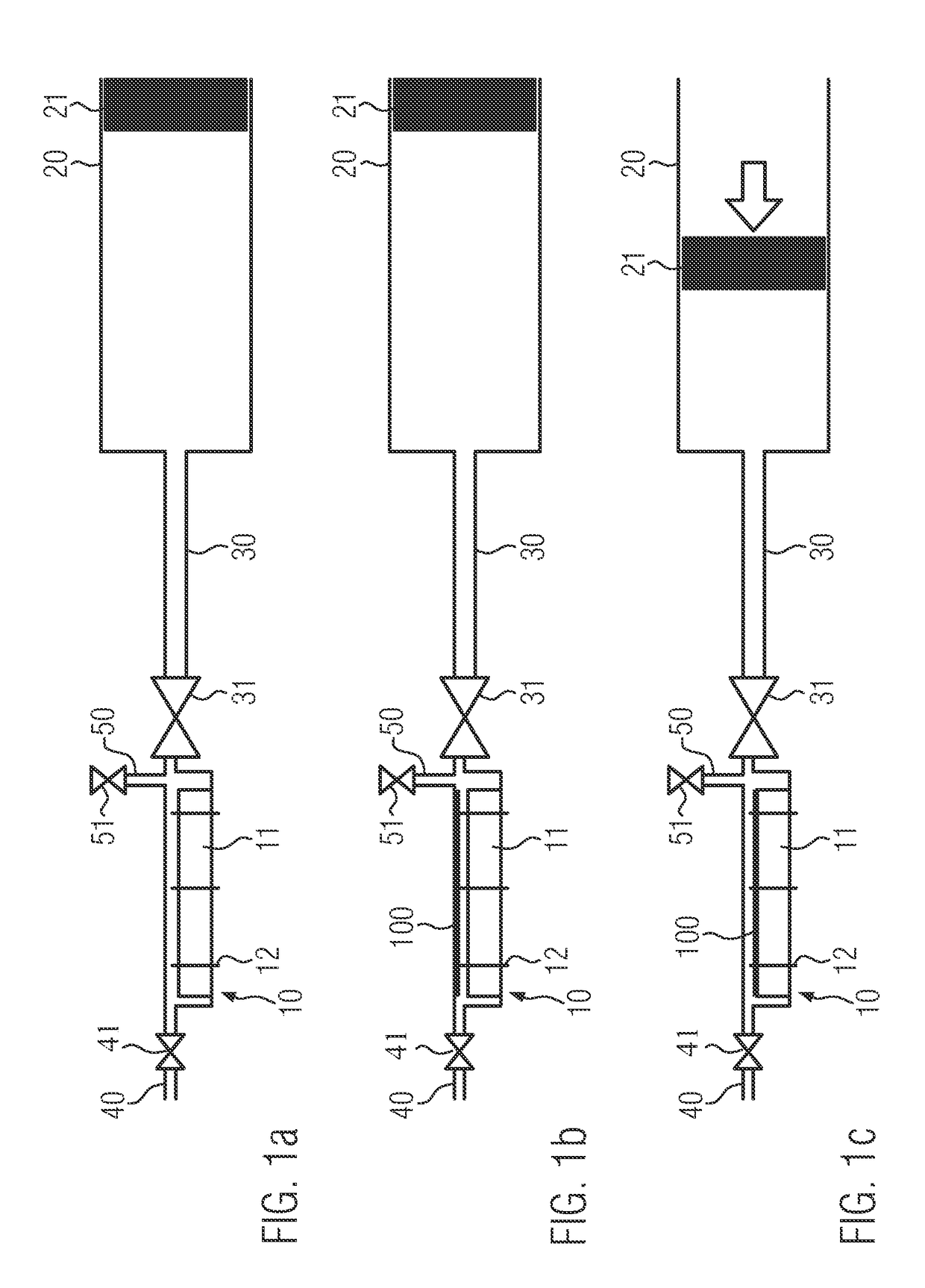

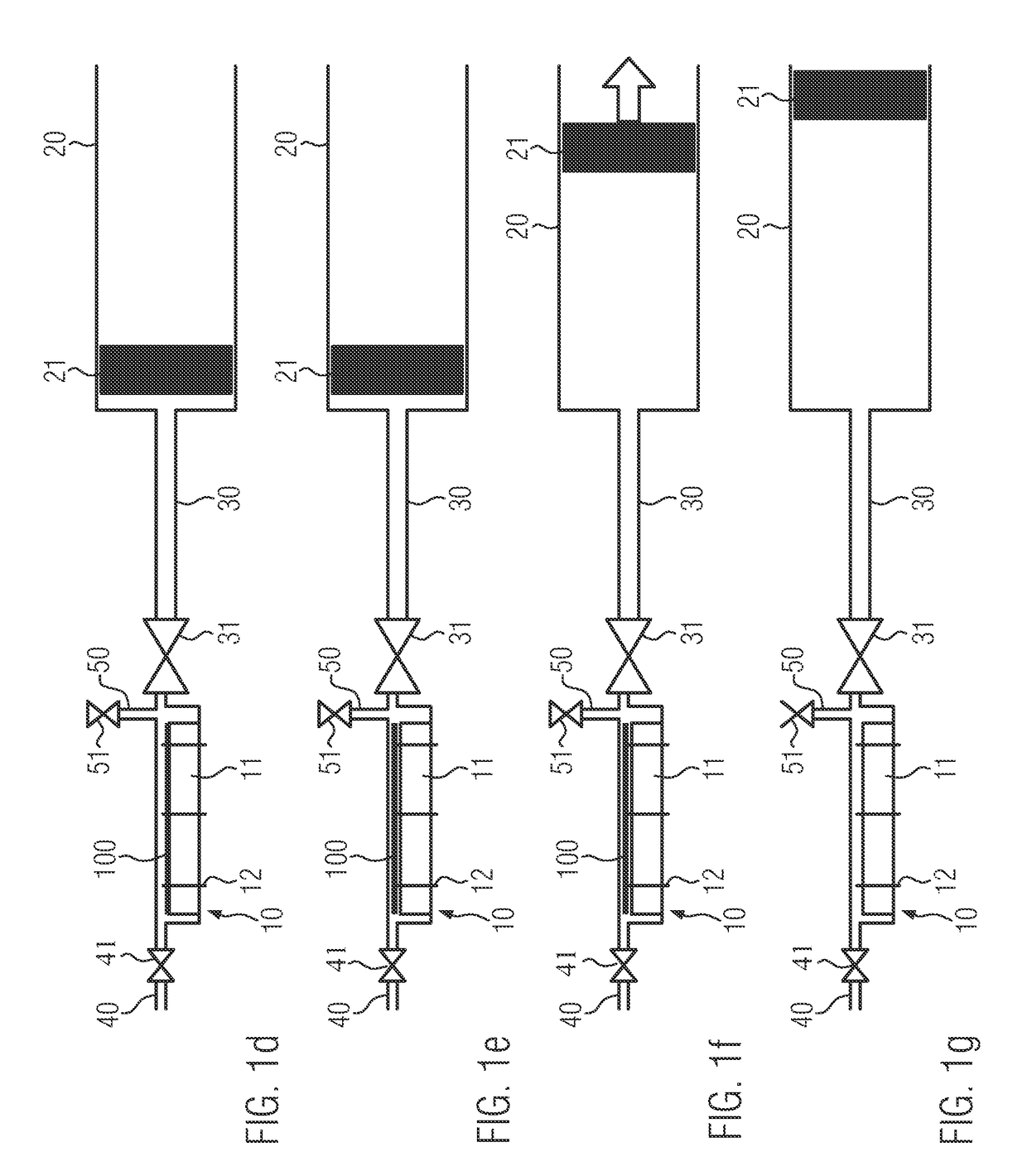

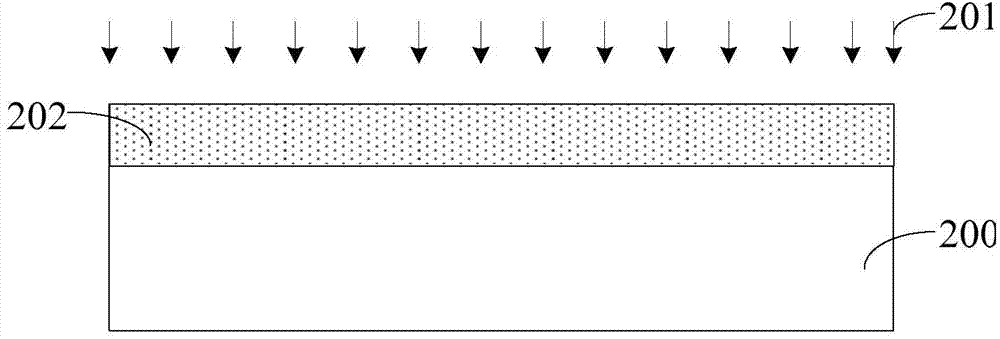

High-pressure anneal

InactiveUS9646850B2Reduce hot carrier effectReduce degradationTransistorSemiconductor/solid-state device detailsEngineeringHigh pressure

A method of treating a semiconductor device is provided including the steps of loading the semiconductor device in a processing chamber, pressurizing the processing chamber by supplying a processing gas from a pressure chamber to the processing chamber, performing a thermal anneal of the semiconductor device in the processing chamber, and depressurizing the processing chamber by supplying the processing gas from the processing chamber to the pressure chamber.

Owner:GLOBALFOUNDRIES INC

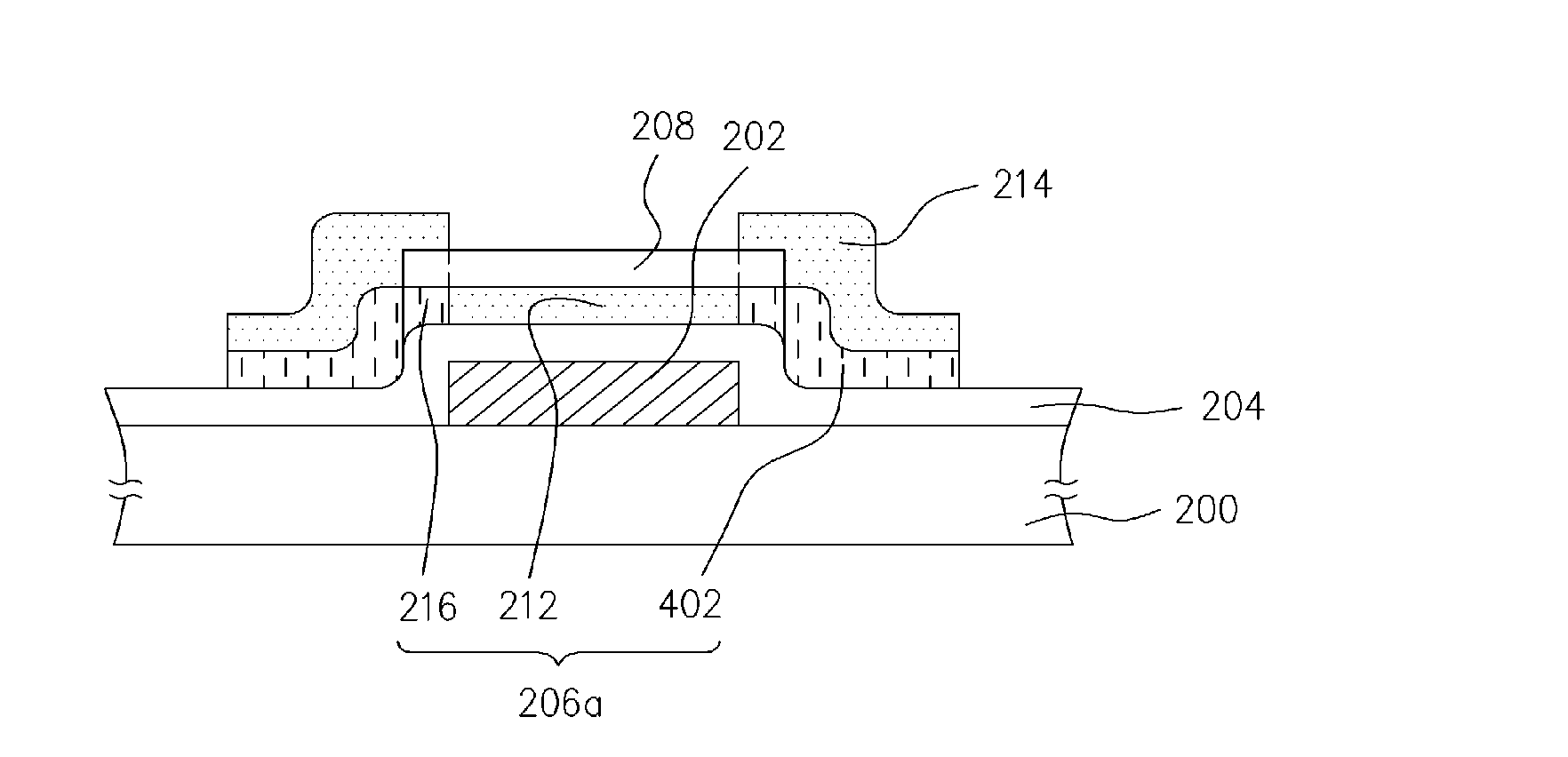

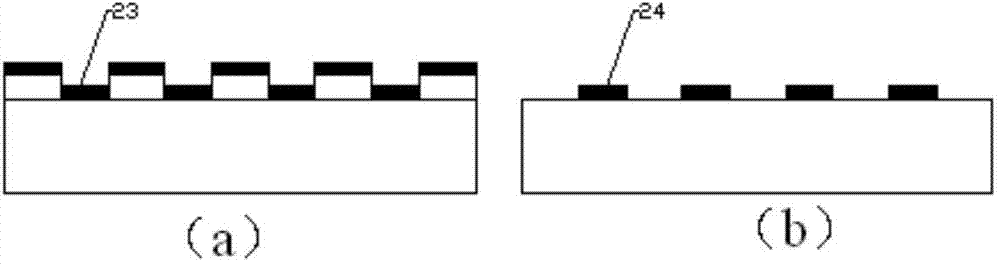

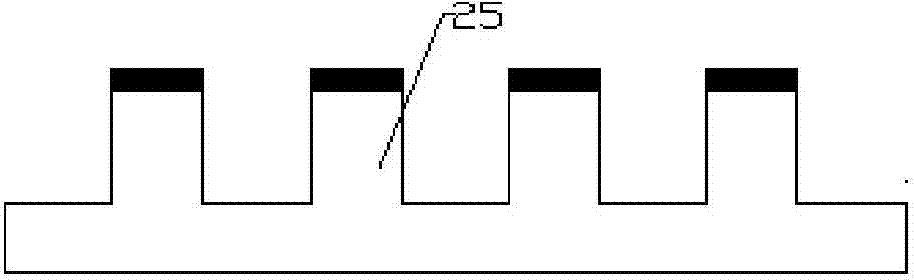

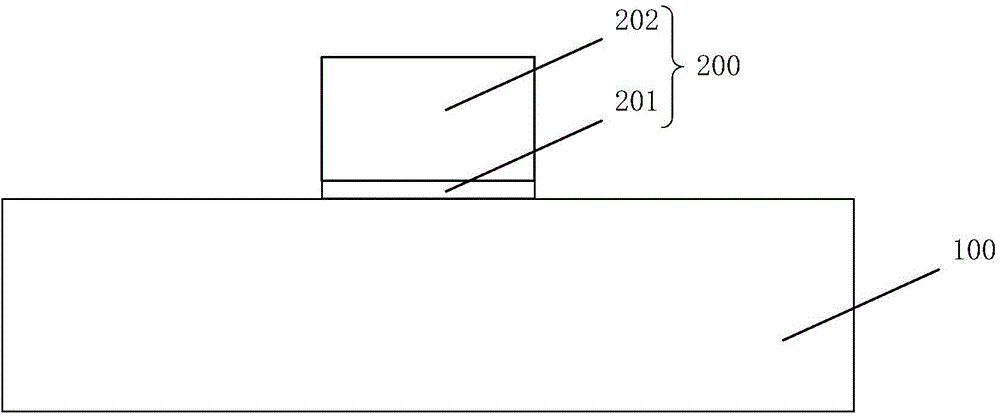

Fabrication method of a low-temperature polysilicon thin film transistor

ActiveUS20060199316A1Improve device performanceReduce manufacturing costTransistorSemiconductor/solid-state device manufacturingGate dielectricOhmic contact

An LTPS-TFT structure comprises a gate, a gate dielectric layer, a patterned silicon layer, a patterned insulating layer, an ohmic contact layer and a source / drain layer. The gate and the gate dielectric layer are disposed on the substrate. The patterned silicon layer and the patterned insulating layer are disposed on the gate dielectric layer over the gate. The patterned silicon layer comprises a polysilicon channel region and an amorphous silicon hot carrier restrain region. The ohmic contact layer is disposed on a portion of the patterned silicon layer other than the polysilicon channel region and the amorphous silicon hot carrier restrain region and a portion of the patterned insulating layer over the amorphous silicon hot carrier restrain region. The source / drain layer is disposed on the ohmic contact layer and the gate dielectric layer.

Owner:SCHLUMBERGER TECH CORP

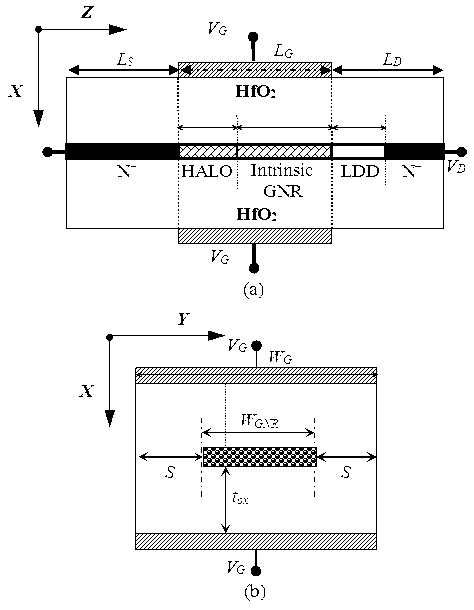

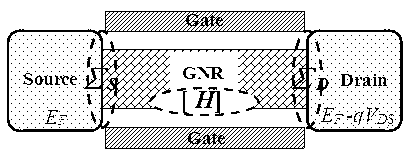

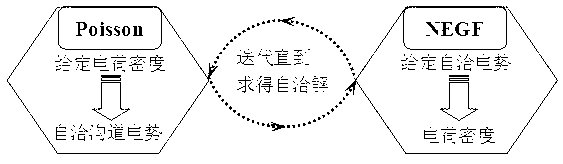

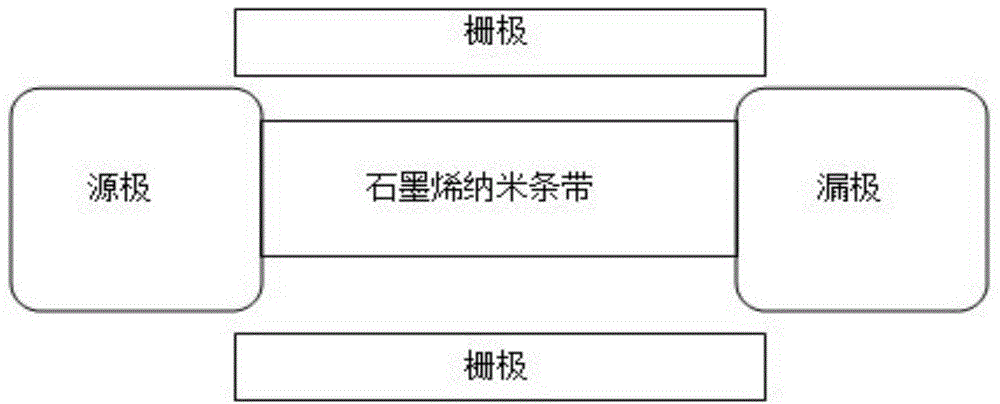

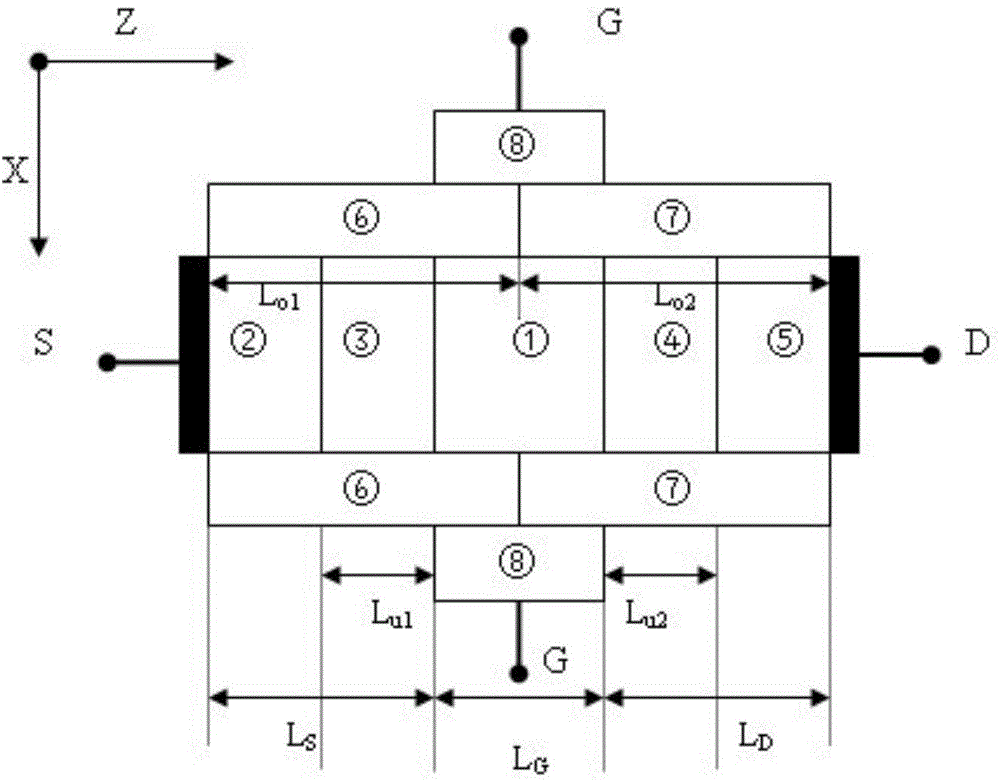

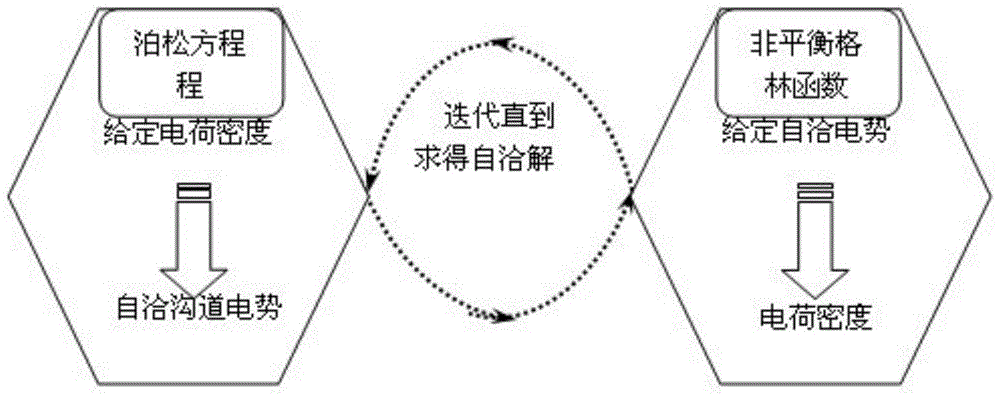

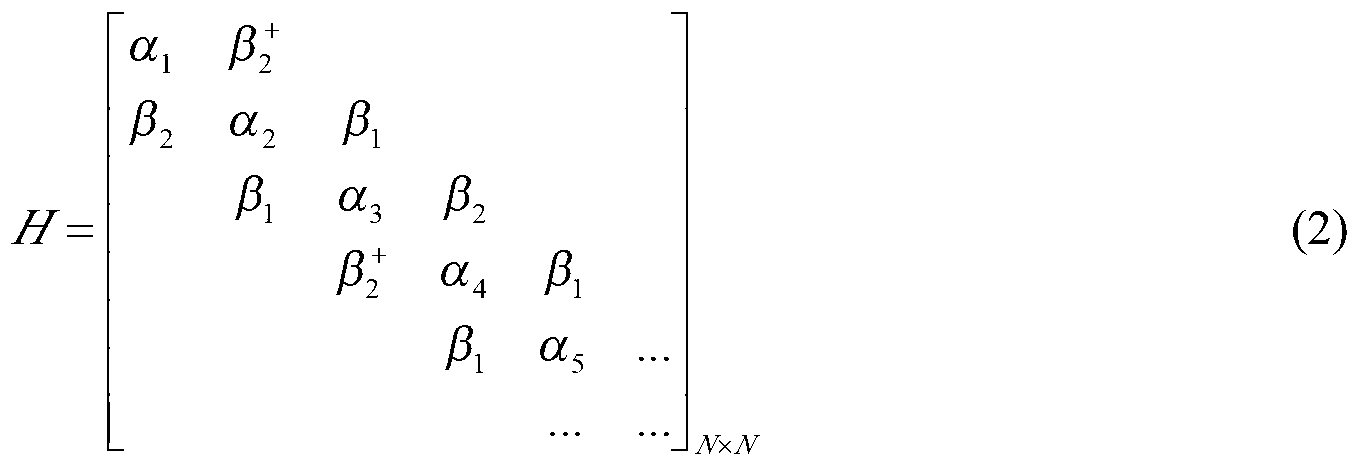

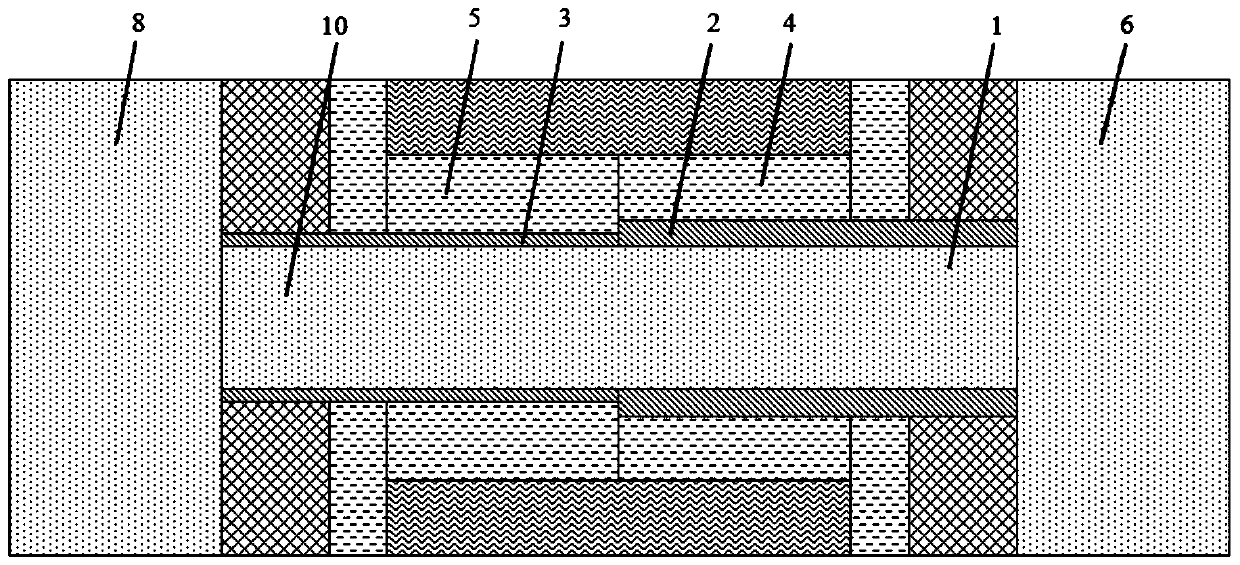

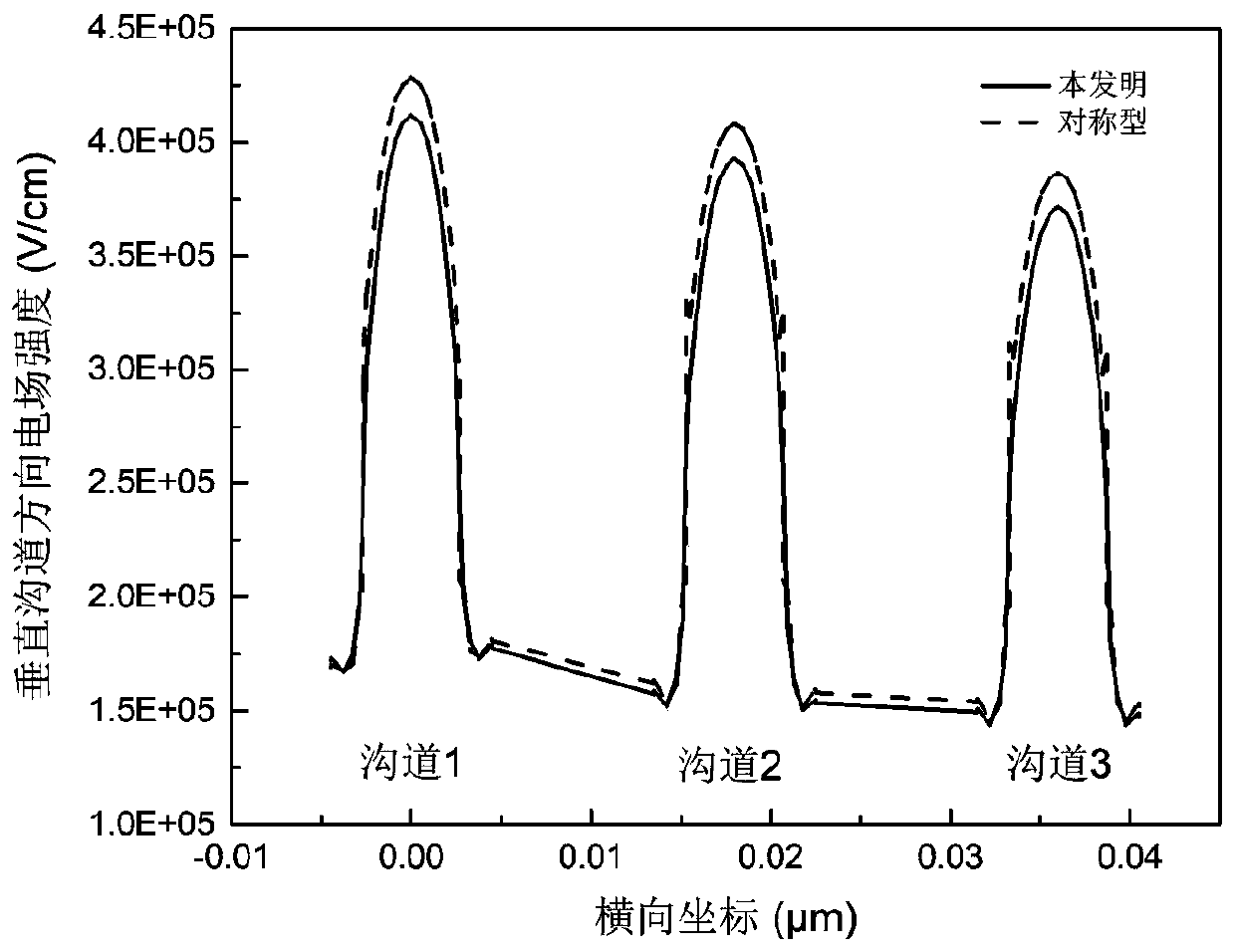

Graphene nanoribbon field-effect tube (GNRFET) with asymmetric HALO-lightly-doped drain (HALO-LDD) structure

InactiveCN103077968AReduce off-state currentGood gating abilitySemiconductor devicesPower flowSwitched current

The invention discloses a graphene nanoribbon field-effect tube (GNRFET) with an asymmetric HALO-lightly-doped drain (HALO-LDD) structure. A transport model which is suitable for a non-uniformly-doped GNRFET is constructed on the basis of a quantum mechanics non-balance Green function theoretical frame under an open boundary condition through self-consistent solution of 3D-Poisson and Schr.dinger equations, and the influence of an asymmetric HALO-LDD doping strategy on the electrical properties of the GNRFET is analyzed and calculated by using the model. As proved by comparison and analysis of the electric properties such as the output properties, transfer properties, switch current ratios, sub-threshold amplitudes and threshold voltage drifts of GNRFETs for which other doping strategies are adopted, the GNRFET with the doping structure has a higher switch current ratio, lower drain current, a smaller sub-threshold amplitude and a smaller threshold voltage drift, i.e., the GNRFET for which the asymmetric HALO-LDD doping strategy is adopted has a better grid control capability, and a short-groove effect and a hot carrier effect can be effectively restrained.

Owner:NANJING UNIV OF POSTS & TELECOMM

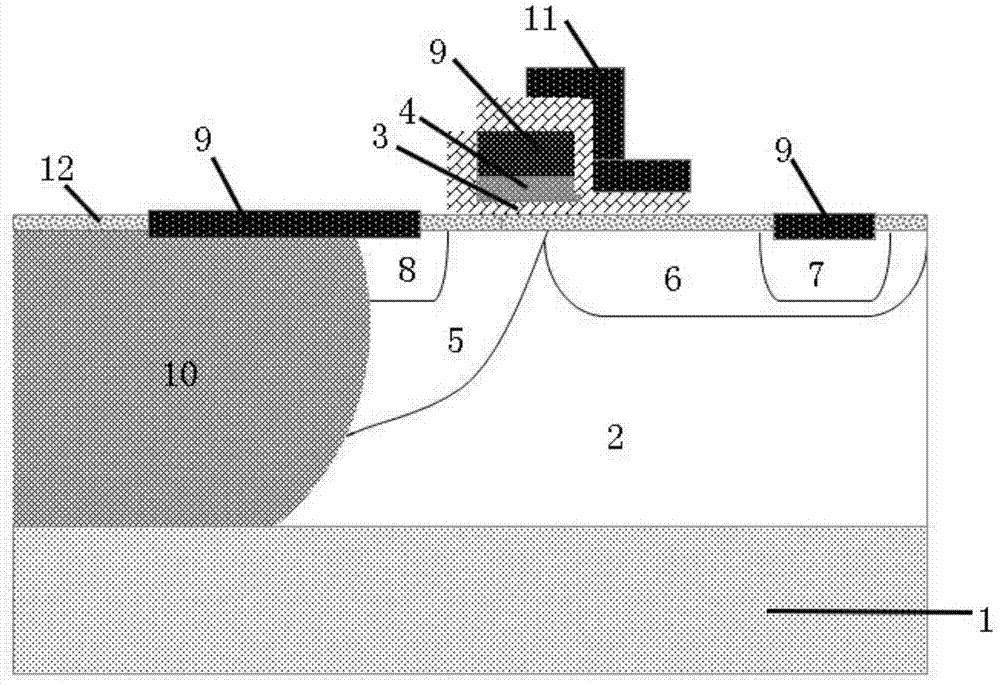

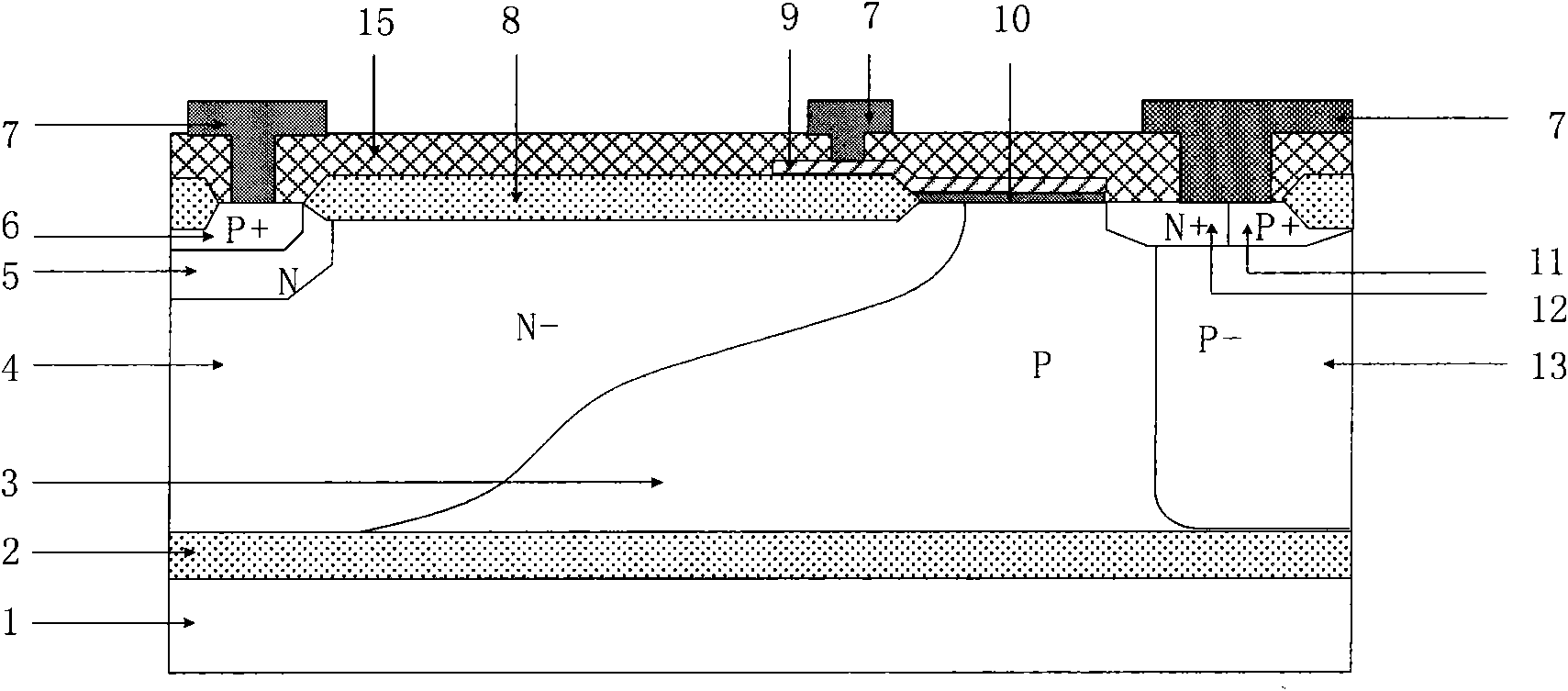

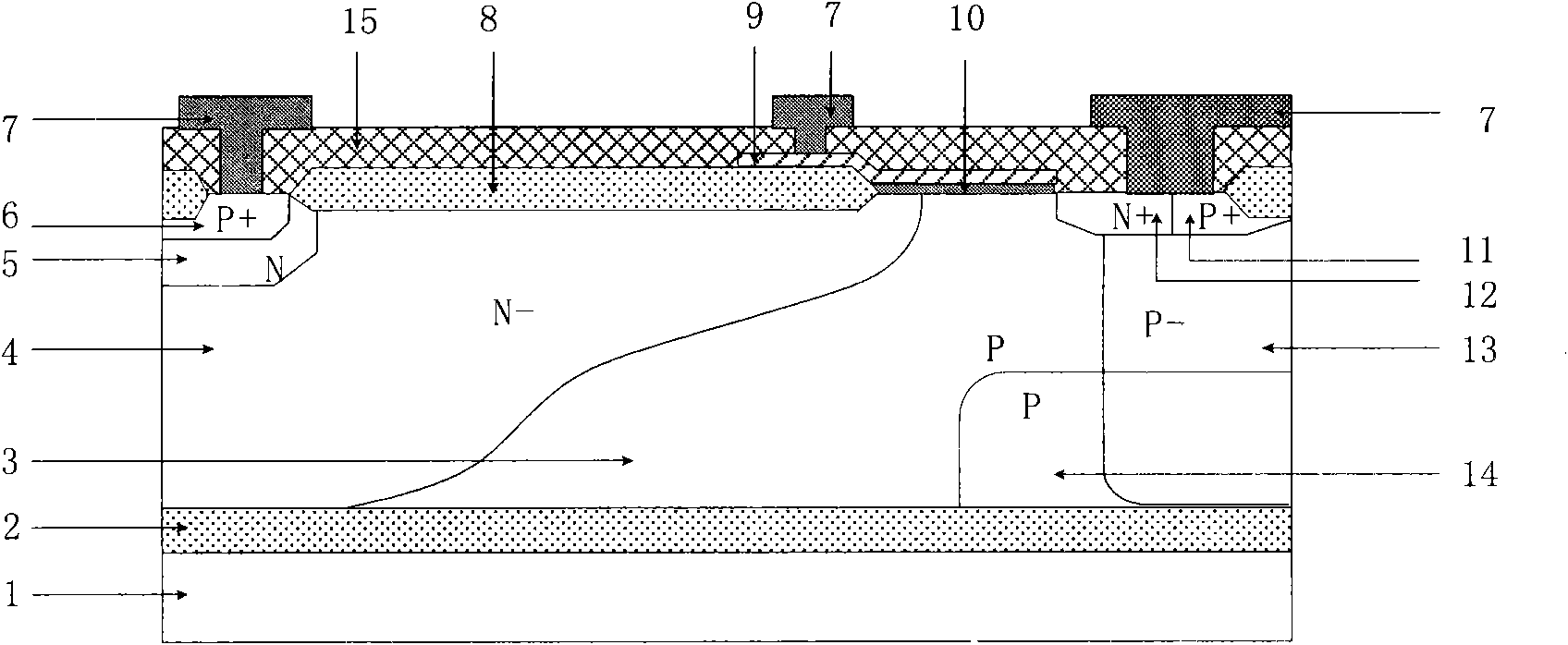

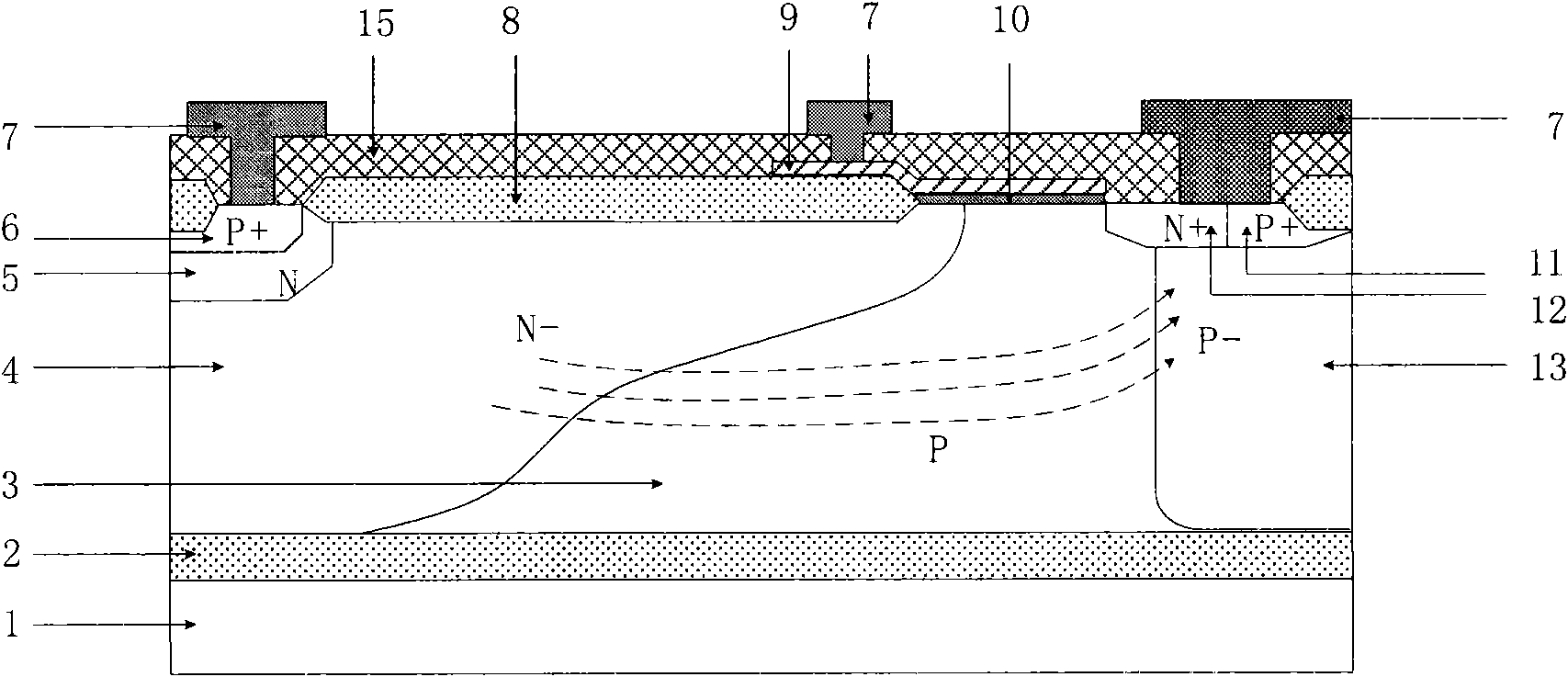

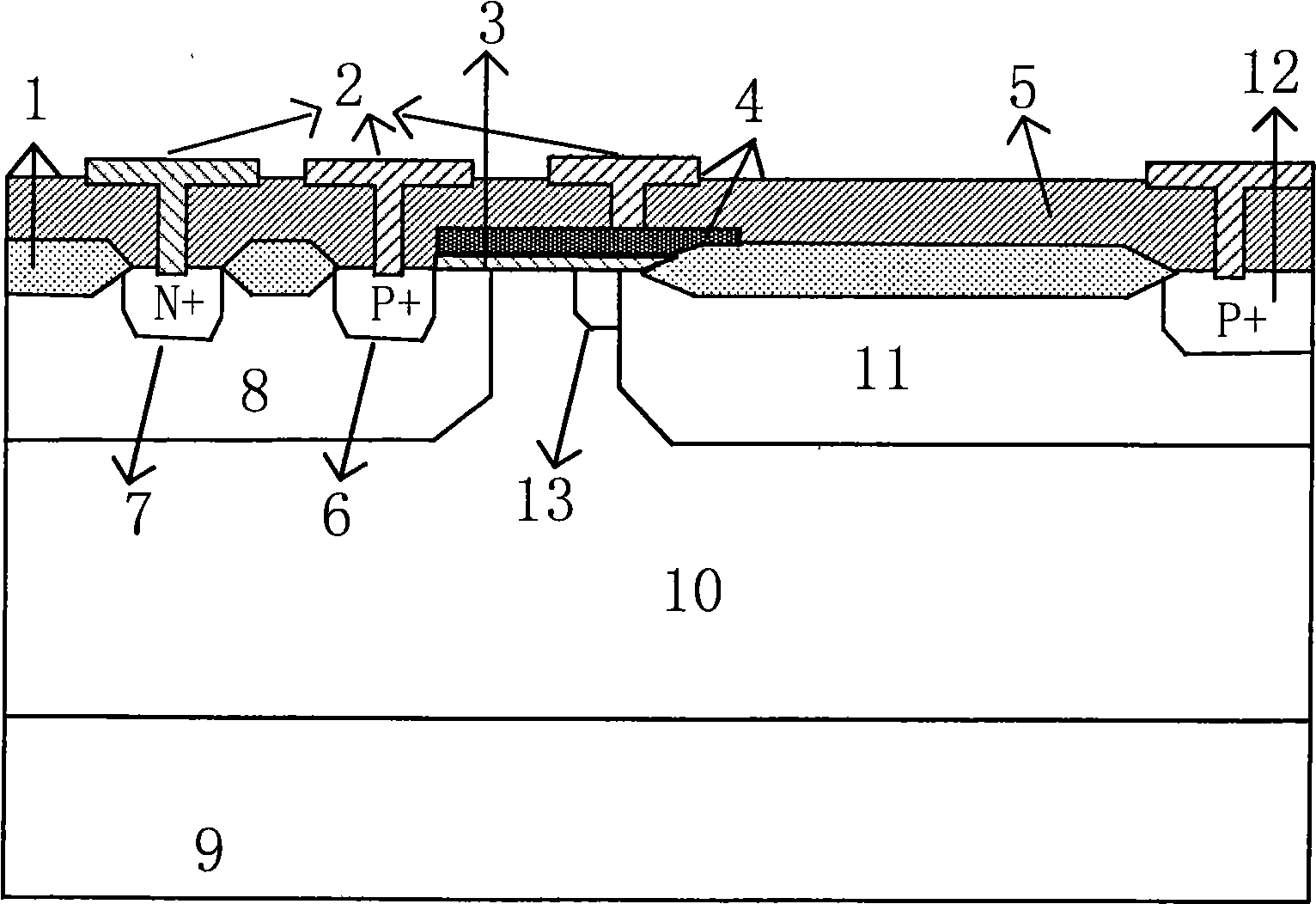

N-type lateral insulated gate bipolar device capable of reducing hot carrier effect

The invention relates to an N-type lateral insulated gate bipolar device capable of reducing hot carrier effect. The N-type lateral insulated gate bipolar device capable of reducing the hot carrier effect comprises a P-type substrate; buried oxide is arranged on the P-type substrate, and is provided with a P-type epitaxial layer; the P-type epitaxial layer is provided with an N-type well and a P-well area, the N-type well is provided with an N-type buffering well which is provided with a P-type positive area, and the P-well area is provided with an N-type negative area and a P-type body contact area; and a field oxide layer, a metal layer, a gate oxide layer, a polysilicon gate and an oxide layer are arranged on the upper surface of the device. The device is characterized in that a P-type buried layer is arranged below the P-well area and above the buried oxide and is inserted into part of the P-type epitaxial layer to form a reversed L-type P-area together with the whole P-well area, and the structure can lead the hole current of the device to the bottom part so as to reduce the iron generation rate and longitudinal electric field in the channel area of the device and lower the temperature of thermion, thereby effectively inhibiting the hot carrier effect of the device.

Owner:SOUTHEAST UNIV

Programming NAND flash with improved robustness against dummy WL disturbance

ActiveUS10276250B1Diminish boosted potentialReduce distractionsSolid-state devicesRead-only memoriesControl circuitComputer science

A memory device includes a plurality of memory cells arranged in series in a semiconductor body. First and second dummy memory cells arranged in series between a first string select switch and a first edge memory cell at a first end of the plurality of memory cells. The first dummy memory cell is adjacent the first edge memory cell, and the second dummy memory cell is adjacent the first string select switch. A channel line includes channels for the plurality of memory cells and the first and second dummy memory cells. Control circuitry is adapted for programming a selected memory cell in the plurality of memory cells corresponding to a selected word line by applying a switching voltage to the first dummy memory cell, the switching voltage having a first voltage level during a first time interval, and thereafter changing to a second voltage level higher than the first voltage level.

Owner:MACRONIX INT CO LTD

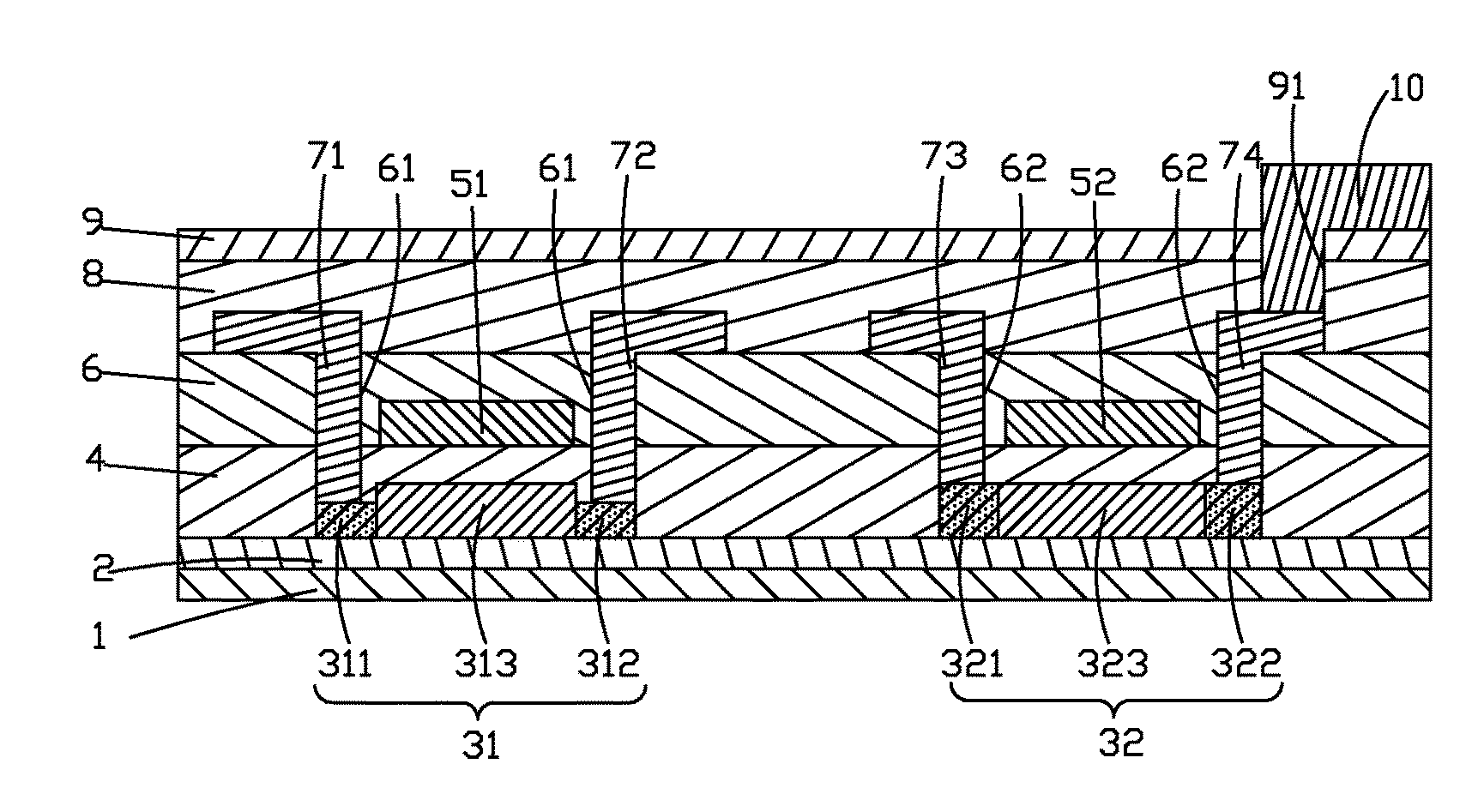

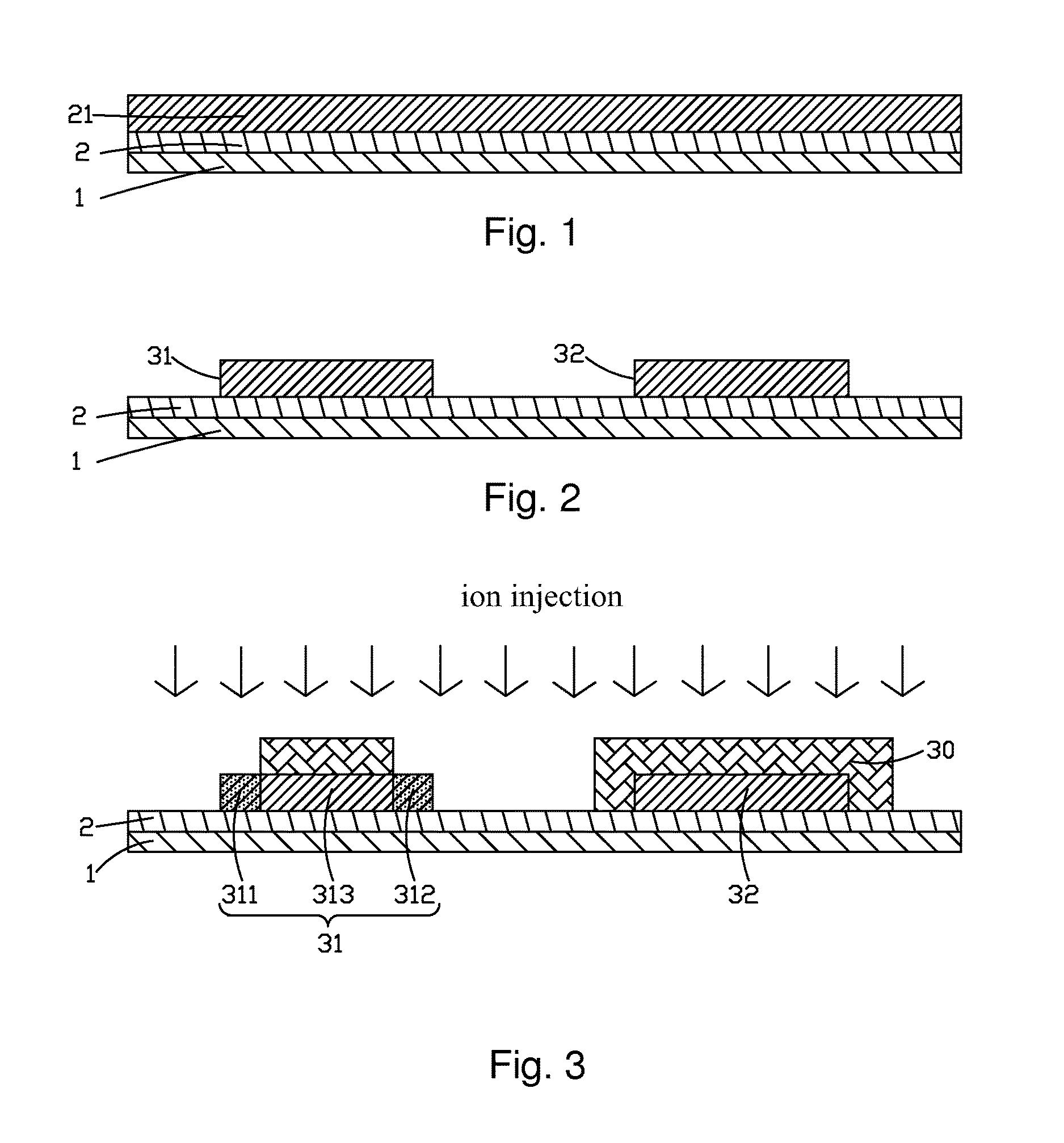

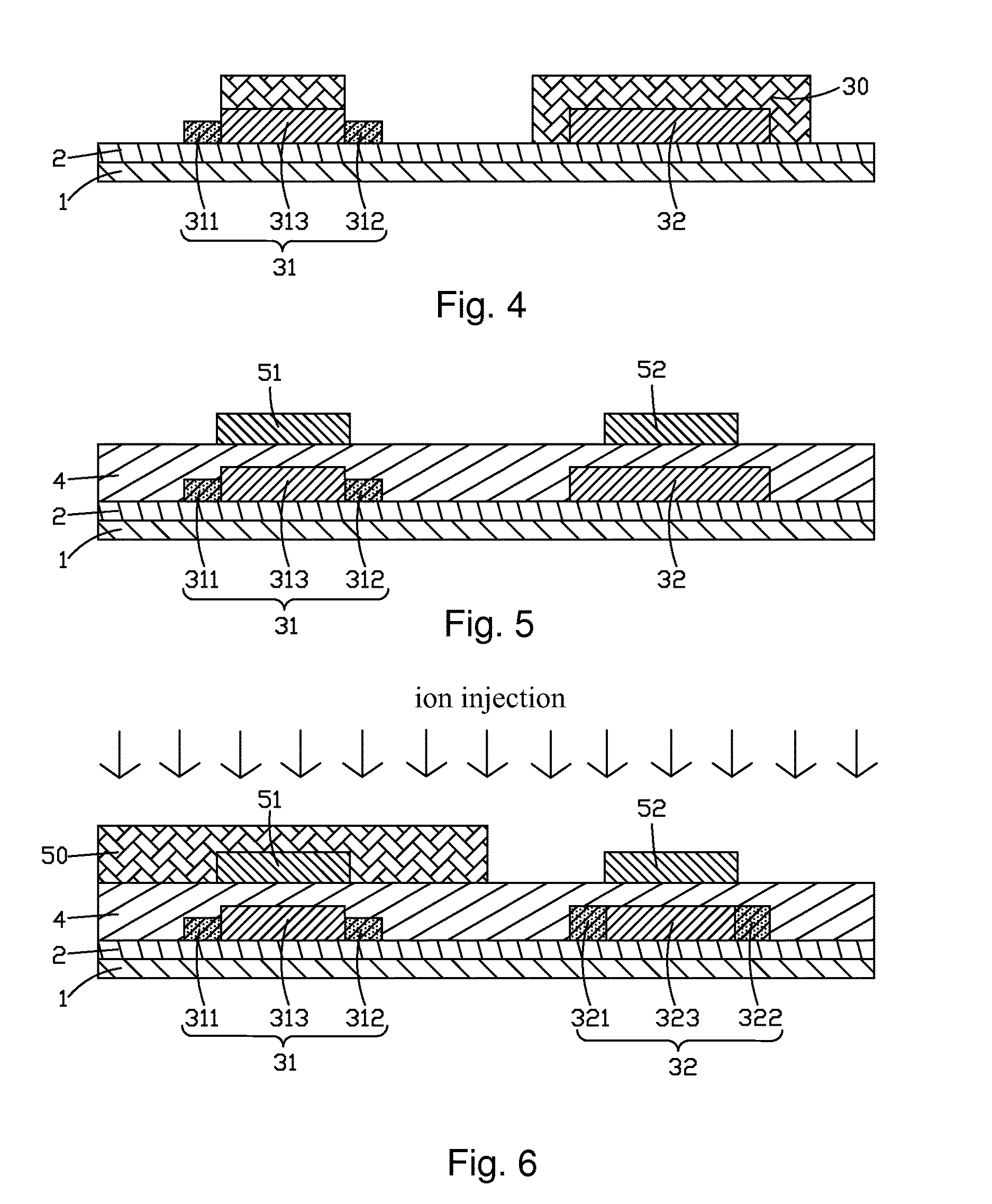

TFT substrate manufacturing method and TFT substrate

ActiveUS20170040462A1Improving TFT reliabilityLower threshold voltageTransistorSolid-state devicesInsulation layerHigh energy

The present invention provides a TFT substrate manufacturing method and a TFT substrate. The TFT substrate manufacturing method of the present invention applies etching to source and drain contact zones of an active layer to have heights thereof lower than a height of a channel zone in the middle and configures the source and drain contact zones in a stepwise form so that charge carriers are affected by an electric field (Vds electric field) that is deviated in a direction away from a poly-silicon / gate insulation layer interface and the migration path thereof is caused to shift away from the poly-silicon / gate insulation layer interface thereby reducing the injection of high energy carriers into the gate insulation layer. Further, due to the formation of the steps in the drain contact zone, the peak intensity of the lateral electric field (Vds electric field) around the drain contact zone and the intensity of a longitudinal electric field (Vgs electric field) of the drain contact zone are both reduced, making a pinch-off point shifted toward an edge of the drain contact zone, reducing drifting of threshold voltage, and improving TFT reliability.

Owner:SHENZHEN CHINA STAR OPTOELECTRONICS TECH CO LTD

Semiconductor structure and manufacturing process thereof

ActiveUS20130228831A1Reduce hot carrier effectImprove breakdown voltageSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor structureDielectric layer

A semiconductor structure includes a substrate having a first conductive type, a well having a second conductive type formed in the substrate, a first doped region and a second doped region formed in the well, a field oxide, a first dielectric layer and a second dielectric layer. The field oxide is formed on a surface region of the well and between the first doped region and the second doped region. The first dielectric layer is formed on the surface region of the well and covers an edge portion of the field oxide. The first dielectric layer has a first thickness. The second dielectric layer is formed on the surface region of the well. The second dielectric layer has a second thickness smaller than the first thickness.

Owner:MACRONIX INT CO LTD

Method for producing MOS transistor

InactiveCN104078358AReduce escapePrevent escapeTransistorSemiconductor/solid-state device manufacturingInterface layerEngineering

A method for producing an MOS transistor comprises the steps that a semiconductor substrate is provided, the surface of the semiconductor substrate is provided with dummy grids, side walls and dielectric layers, wherein the side walls are located at the two sides of the dummy grids, the semiconductor substrate and the side walls are covered with the dielectric layers, and the top surfaces of the dielectric layers are flush with the top surfaces of the dummy grids; the dummy grids are removed, so that openings are formed and parts of the surface of the semiconductor substrate are exposed through the openings; fluoridation is conducted on the parts, exposed through the openings, of the surface of the semiconductor substrate through a fluorine-containing solution, so that fluorine-containing surfaces are formed; interface layers are formed on the fluorine-containing surfaces; grid dielectric layers are formed on the interface layers and grid electrodes are formed on the grid dielectric layers. According to the method for producing the MOS transistor, the negative bias temperature instability effect and the hot carrier injection effect are lowered and the reliability of the MOS transistor is high.

Owner:SEMICON MFG INT (SHANGHAI) CORP

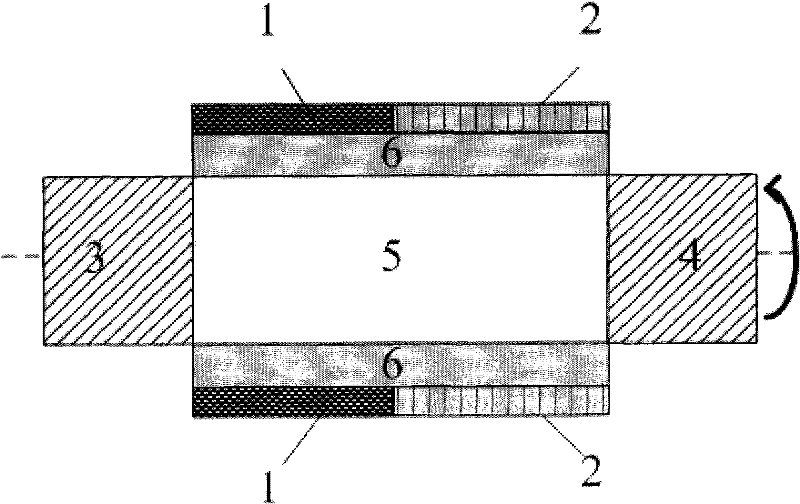

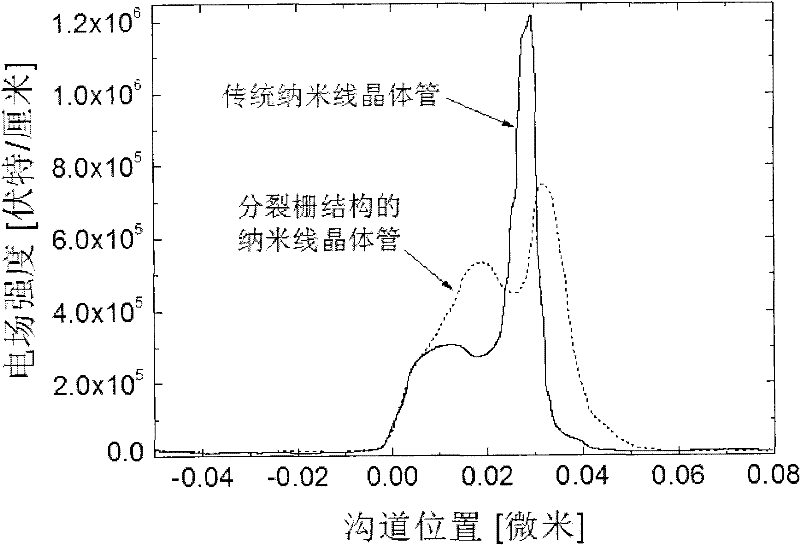

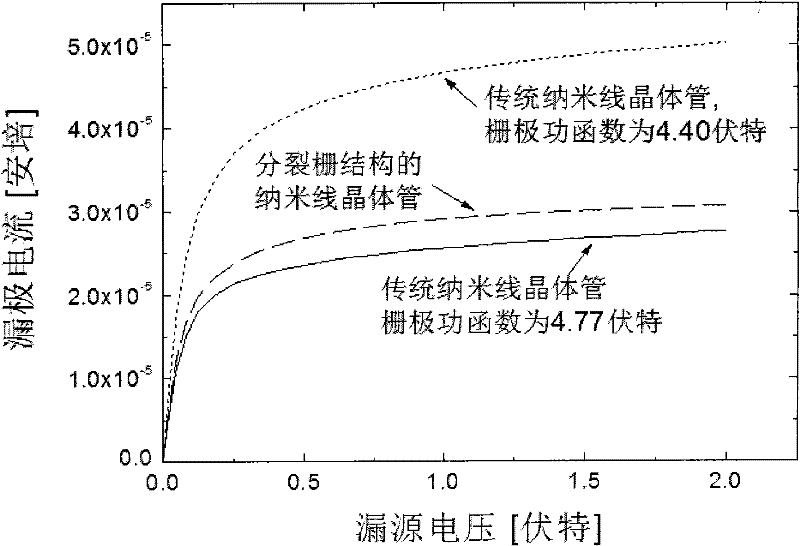

Nanowire field effect transistor with split-gate structure

InactiveCN102544094AIncrease the on-state currentReduce off-state currentSemiconductor devicesShort-channel effectElectricity

The invention discloses a nanowire field effect transistor with a split-gate structure. The transistor is formed by a split-gate electrode, a source region, a drain region, a channel region and a gate dielectric layer, wherein the channel region is columnar and is positioned in the center of the nanowire field effect transistor, and a material forming the channel region is a semiconductor material; the gate dielectric layer totally encircles the channel region coaxially; the split-gate electrode is positioned outside the gate dielectric layer and totally encircles the gate dielectric layer coaxially, and materials forming the split-gate electrode include two kinds of different materials; and the source region and the drain region are positioned at two sides of the channel region respectively. The introduction of the split-gate electrode structure can effectively improve the on-state current of nanowire transistors in prior arts and improve the current switch ratio and the working speed of devices. Simultaneously, the transistor is less affected by threshold voltage shift and drain induced barrier lowering effect resulted from short channel effect, and the performance of size reduction is more excellent.

Owner:PEKING UNIV

Bilinear doping drainage heterogeneous material gate oxide layer graphene tunneling field-effect transistor

InactiveCN104091829AGood gating abilityImprove gate control abilitySemiconductor devicesDelayed timeLow leakage

The invention discloses a bilinear doping drainage heterogeneous material gate oxide layer graphene tunneling field-effect transistor (DL-HTFETs). The field-effect transistor undergoes P / N type heavy doping at a source region and a drain region, linear doping is carried out on regions, close to a channel, of the source end and the drain end, an oxidation layer close to a source electrode is formed by low-K oxide (SiO2), the oxidation layer close to a drain layer is formed by high-K oxide (HfO2), a conveying model of the novel bilinear doping drainage heterogeneous material gate oxide layer graphene tunneling field-effect transistor is built by means of a quantum mechanics model, and electrical properties of a high-K tunneling field-effect transistor (HK-TFETs), a common gate oxide tunneling field-effect transistor (LK-TFETs), a heterogeneous oxide tunneling field-effect transistor (HTFETs), a common filed-effect transistor and the DL-HTFETs are compared and analyzed by means of the model. As is shown by a research result, the DL-HTFETs have the advantages of low leakage currents, a high current switch ratio, low power consumption and short delay time and the like.

Owner:NANJING UNIV OF POSTS & TELECOMM

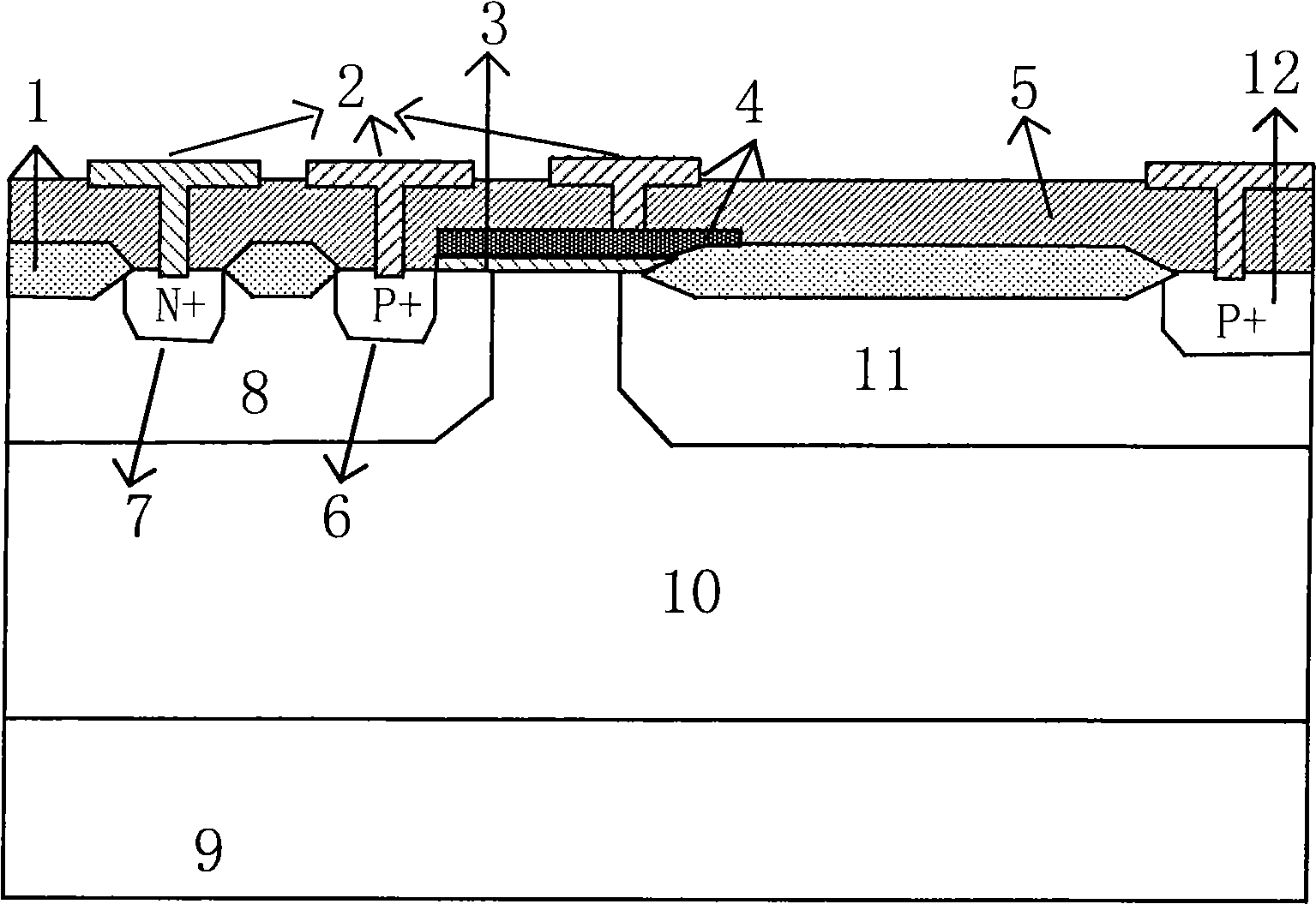

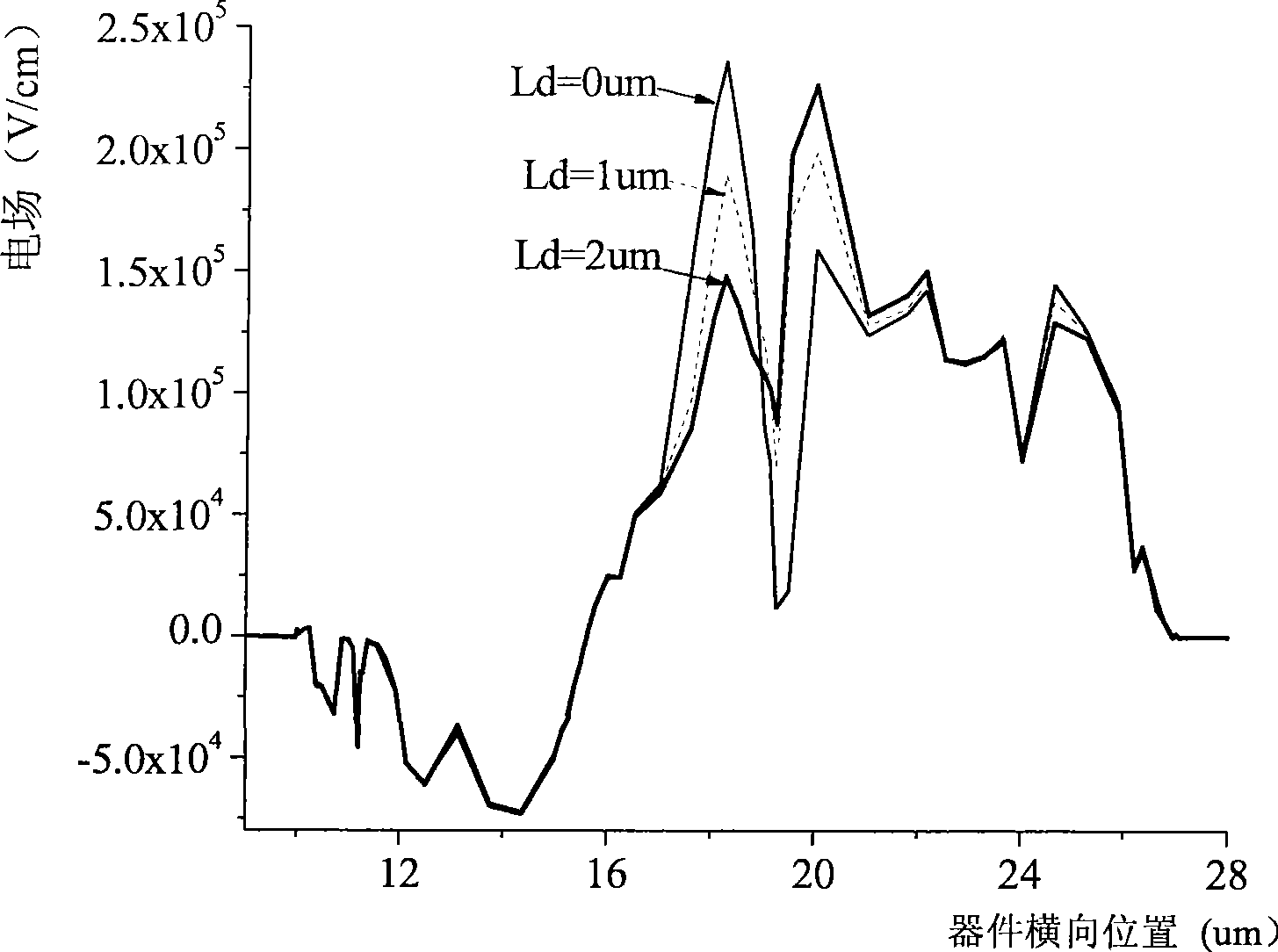

P type transversal bilateral diffusion metal oxide semiconductor tube capable of reducing hot carrier effect

InactiveCN101510560AReduce chargeReduce damageSemiconductor devicesHot carrier effectOxide semiconductor

The invention discloses a P-type lateral double-diffused metal-oxide transistor which is capable of reducing hot-carrier effect and comprises a P-type semiconductor substrate; an N-type well region is arranged on the P-type semiconductor substrate; a P-type well region and a P-type doped semiconductor area are arranged on the N-type well region; a P-type source area and an N-type contact area are arranged on the P-type well region; a P-type drain area is arranged on the P-type doped semiconductor area; and a field oxide layer, a metal layer, a gate oxide layer, a polysilicon grid and an oxide layer are arranged on the upper surface of the device. The P-type lateral double-diffused metal-oxide transistor is characterized in that: a lightly-doped shallow P-type area is arranged in the N-type well region and positioned between the P-type well region and the P-type doped semiconductor area and covers a corner which is formed by the gate oxide layer and the P-type doped semiconductor area.

Owner:SOUTHEAST UNIV

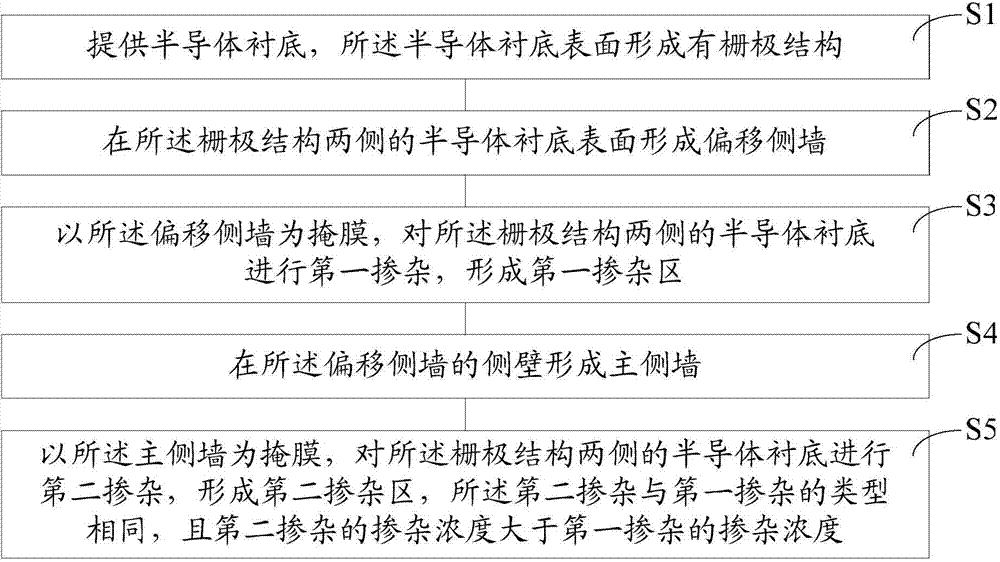

Semiconductor device and forming method thereof

ActiveCN104752205AReduce leakage currentIncrease channel lengthSemiconductor/solid-state device manufacturingSemiconductor devicesElectrical performanceSemiconductor

A semiconductor device and a forming method thereof are provided. The forming method of the semiconductor device comprises the following steps: providing a semiconductor substrate; performing first doping on the semiconductor substrate to form a first doped region; forming a patterned mask layer on the surface of the semiconductor substrate, wherein the patterned mask layer has an opening which exposes the surface of the semiconductor substrate; etching part of the semiconductor substrate in the thickness direction with the patterned mask layer as a mask to form a groove in the semiconductor substrate; and performing second doping on the semiconductor substrate to form a second doped region, wherein the first doping and the second doping are of the same doping type, the doping concentration of the second doping is greater than the doping concentration of the first doping, and the second doped region and the first doped region are connected. By adopting the method of the invention, the opening current of the semiconductor device is increased, the leakage current is reduced, and the electrical performance of the semiconductor device is improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP

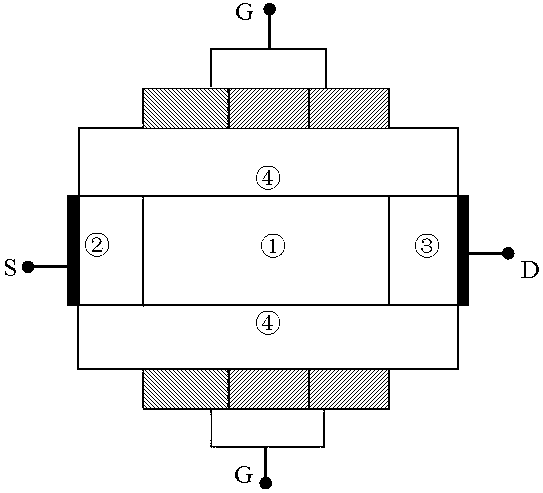

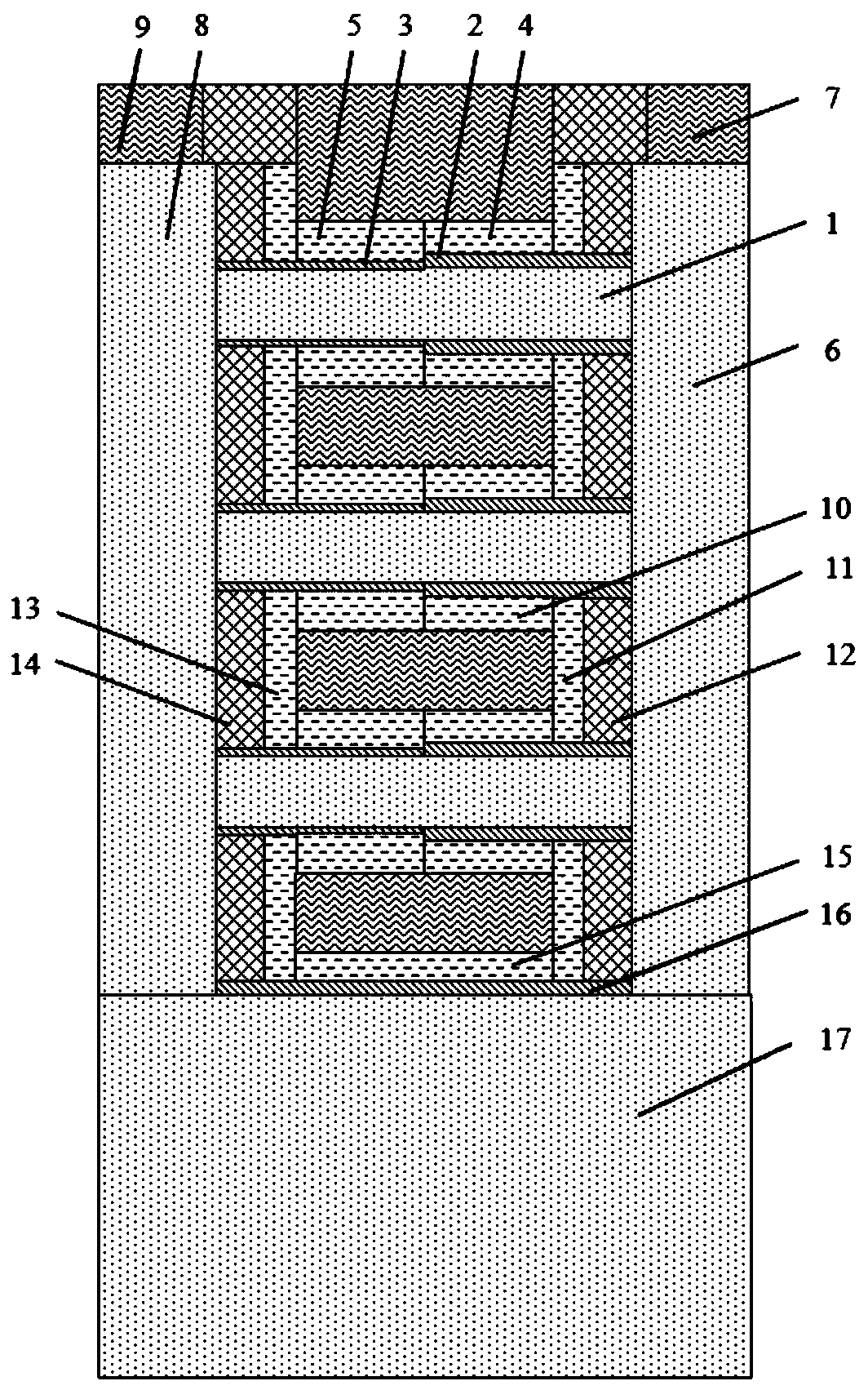

Grapheme nanometer stripe field-effect tube of three-material heterogeneous grid structure

InactiveCN103258858AImprove performanceSuppression of short channel effectsTransistorNanoinformaticsWork functionLow leakage

The invention discloses a grapheme nanometer stripe field-effect tube of a three-material heterogeneous grid structure. A conducting channel (1), a source region (2) and a drain region (3) of the field-effect tube are all made of grapheme nanometer stripe materials. Besides the conducting channel (1), the source region (2) and the drain region (3), a grid oxide layer (4) is generated by methods of atomic deposition and the like, a metal electrode layer is reprecipitated outside the grid oxide layer (4) to serve as a grid (G) of the grapheme nanometer stripe field-effect tube of the three-material heterogeneous grid structure, and the grid (G) is made of conducting metal with three different work functions to form the heterogeneous grid of the grapheme nanometer stripe field-effect tube of the three-material heterogeneous grid structure. When the work functions of three materials gradually decrease from a source to a drain, or when a middle work function is the maximum and a work function close to the side of the drain is minimum, the structure can effectively improve performance, and the field-effect tube has lower leakage currents and a higher current switching ratio, and can suppress a drain induced barrier lowering (DIBL) effect.

Owner:NANJING UNIV OF POSTS & TELECOMM

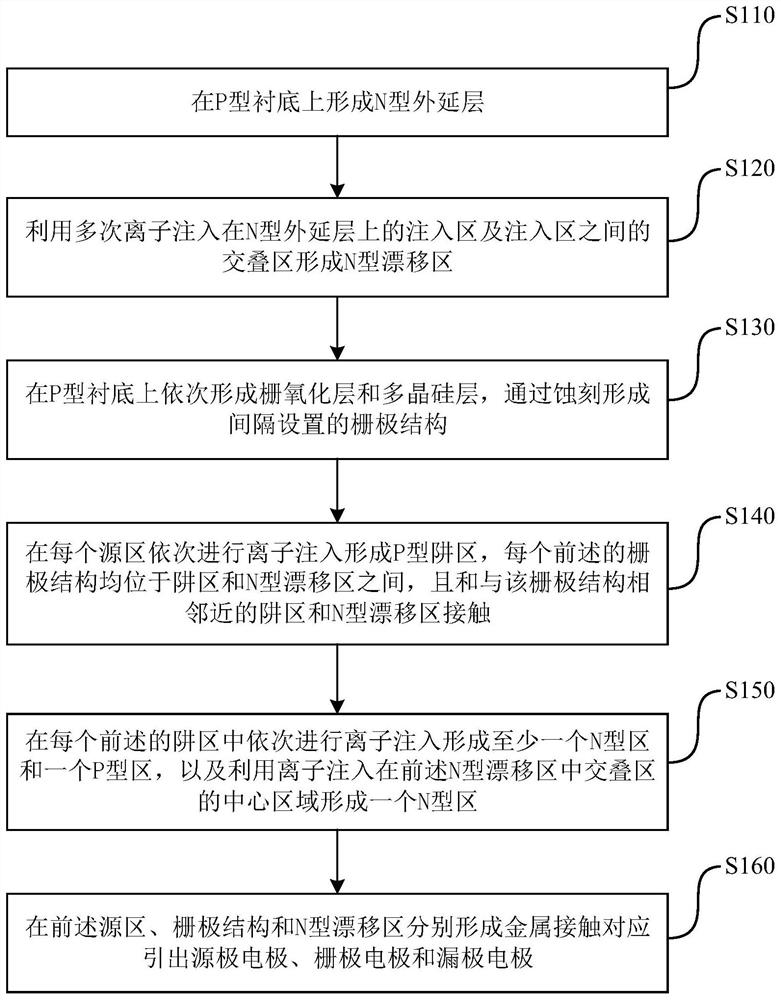

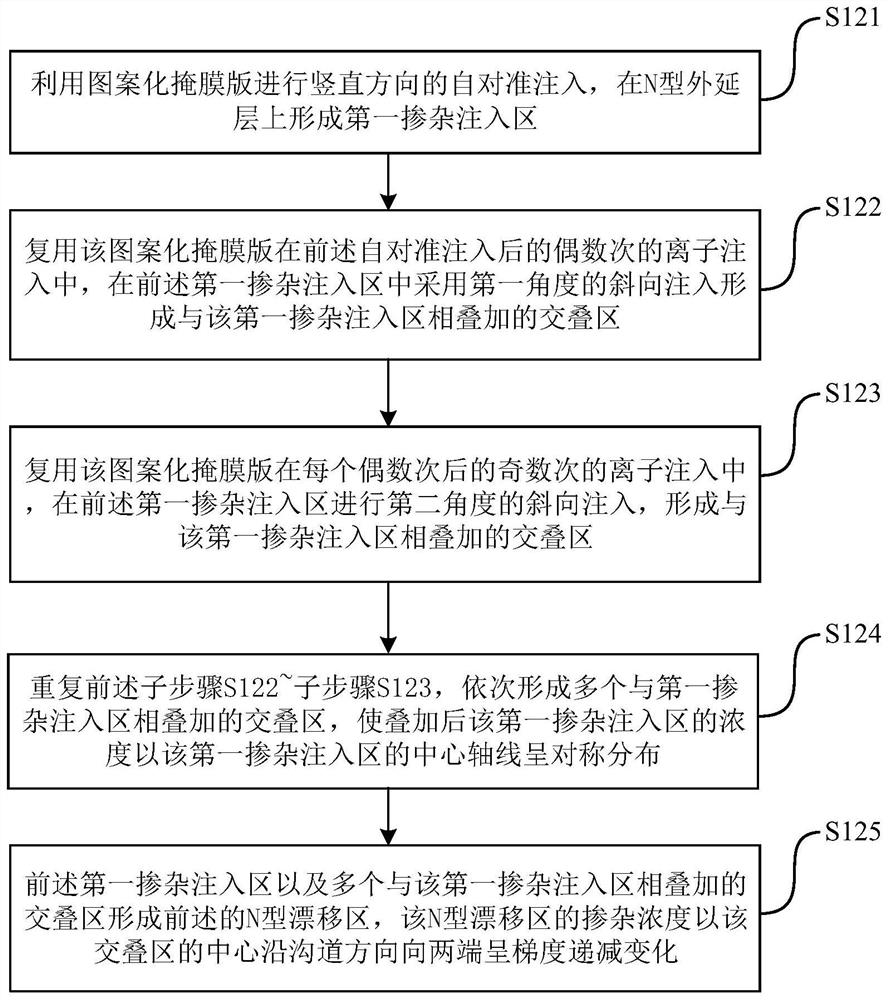

Manufacturing method of lateral double-diffused transistor

ActiveCN111987166AImprove electric field distributionImprove breakdown voltageSemiconductor/solid-state device manufacturingSemiconductor devicesImpurity dopingDiffusion transistor

The invention relates to the technical field of semiconductor power devices. The invention provides a manufacturing method of a lateral double-diffusion transistor. A drift region of a first doping type is formed in injection regions on a substrate and an overlapping region between the injection regions by utilizing multiple times of ion implantation (oblique angle implantation); and the doping concentration of the drift region is distributed in a gradient decreasing (linear variable doping concentration) manner from the center of the overlapping region to the two ends along the channel direction, so that a formed device is of a bilaterally symmetrical structure by taking the central axis of the drift region as the center. The breakdown voltage of the device is improved; enough impurity doping concentration is ensured; therefore, the device has relatively small on-resistance; the performance of the formed device is improved; according to the manufacturing method, the phenomenon that aspecially-made mask with a specific window design is used for forming the linear variable doping drift region in the prior art is avoided, the manufacturing cost is saved, and the linear distributionof the doping concentration of the drift region can be controlled by controlling the ion implantation frequency and angle through the process, so that the applicability of the manufacturing method isimproved.

Owner:JOULWATT TECH INC LTD

Nano-sheet ring gate field effect transistor with asymmetric gate oxygen structure

ActiveCN110690290AReduced Threshold Voltage DriftInhibition of DIBL effectNanoinformaticsSemiconductor devicesEngineeringField effect

The invention discloses a nano-sheet ring gate field effect transistor with an asymmetric gate oxygen structure. The nano-sheet ring gate field effect transistor comprises a vertically stacked nano-sheet channel, a double-layer gate oxide wrapping outside the channel, a source and a drain arranged at the two ends of the channel, a double-layer side wall and a substrate arranged at the bottom. Thenano-sheet ring gate field effect transistor is characterized in that the gate oxide is formed by stacking a low dielectric constant material and a high dielectric constant material and is divided into two parts near the drain and the source with half of the channel length as the boundary. The total physical thickness of gate oxygen in the two parts is the same, and the low dielectric constant gate oxide is thinner and the high dielectric constant gate oxide is thicker in the double-layer gate oxides near the drain so as to form the nano-sheet ring gate field effect transistor with the asymmetric gate oxygen structure. Compared with the prior symmetrical type technology, the drain end electric field is lower and the hot carrier effect of the device can be effectively inhibited; it has moreideal on-state and off-state current and higher current switching ratio;and the leakage potential is more stable, the leakage-induced barrier reduction effect is suppressed and the short channel characteristics are improved.

Owner:EAST CHINA NORMAL UNIV +1

Light dope ion injection method

InactiveCN101330048AIncrease junction depthEnhanced injection diffusionSemiconductor/solid-state device manufacturingOutput deviceIon implantation

The invention relates to a light doping ion injecting method which comprises the following steps of: providing a semiconductor substrate which comprises a core device area and an input and output device area; forming a grid on the semiconductor substrate; implementing the light doping ion injecting to the input and output device area; forming a side wall substrate at the side wall of the grid; and implementing the light doping ion injecting to the core device area. The method can reduce the occurrence of hot-carrier effect.

Owner:SEMICON MFG INT (SHANGHAI) CORP

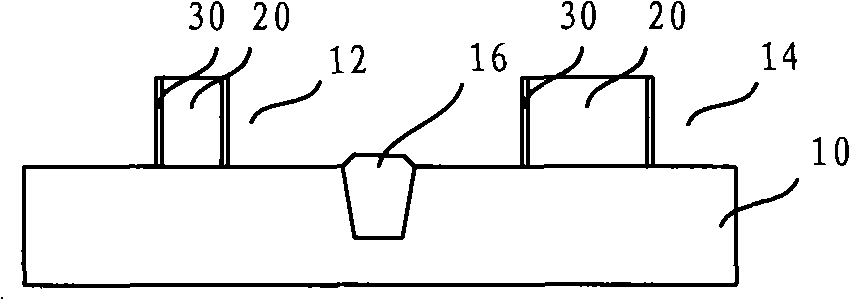

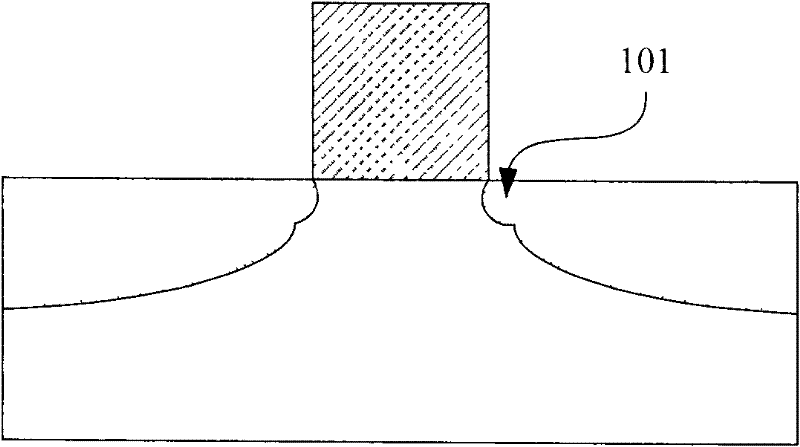

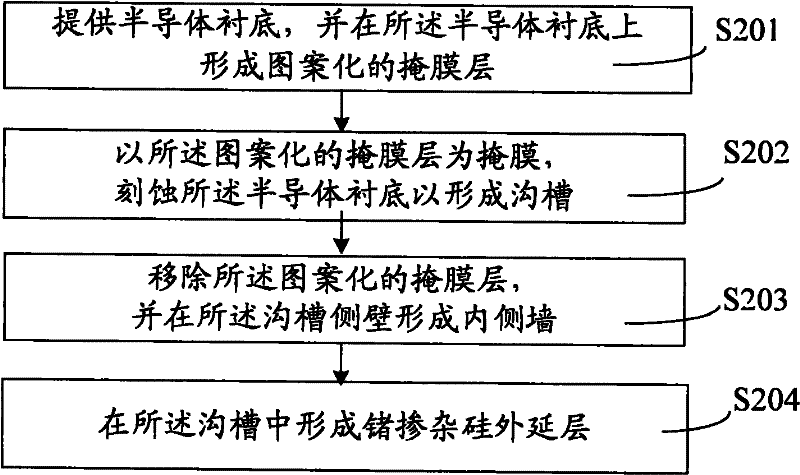

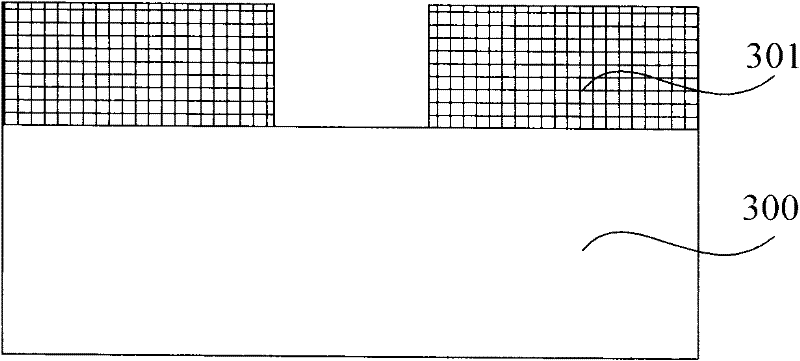

Manufacturing method for MOS transistor

ActiveCN102693915AImprove mobilityInhibition of Radial DiffusionSemiconductor/solid-state device manufacturingSemiconductor devicesRadial diffusionEpitaxy

The invention provides a manufacturing method for an MOS transistor. On one hand, charge mobility is increased by germanium-doped silicon epitaxy to inhibit hot carrier's effect; on the other hand, by an inner wall with a lower top, radial diffusion is inhibited in lightly doped source / drain (LDD) region after ion implantation and the depth of the lightly doped source / drain (LDD) extension region is controlled, which allows ultra-shallow junction shallower. Therefore longer effective channel is obtained, HCI effect is effectively inhibited, SCE and RSCE effects are significantly improved and breakdown effect and electric leakage caused by breakdown effect brought by shrunk device size are reduced, enabling the production of even shallower source / drain region junction in the ultra-shallow junction technology.

Owner:SEMICON MFG INT (SHANGHAI) CORP

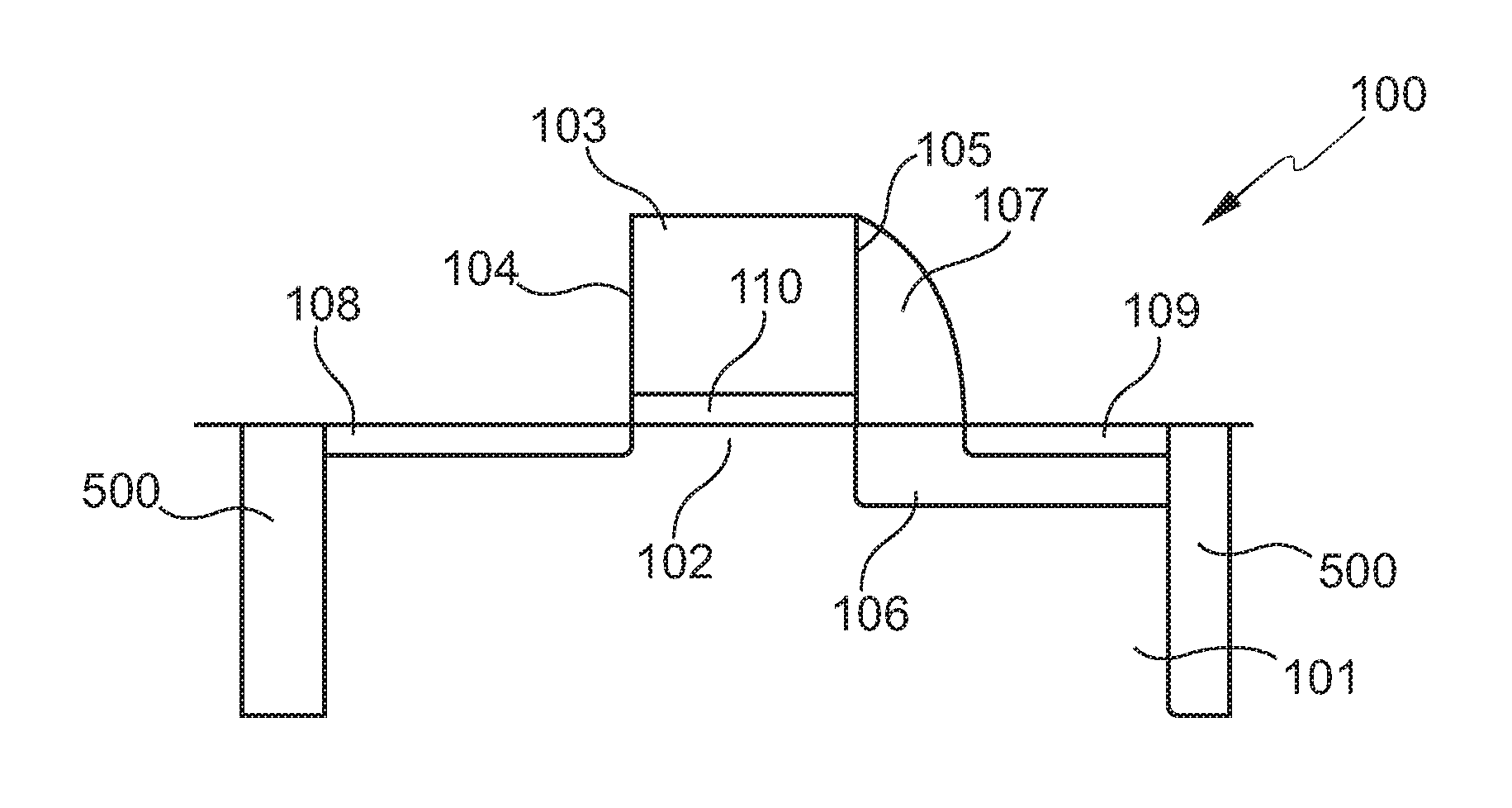

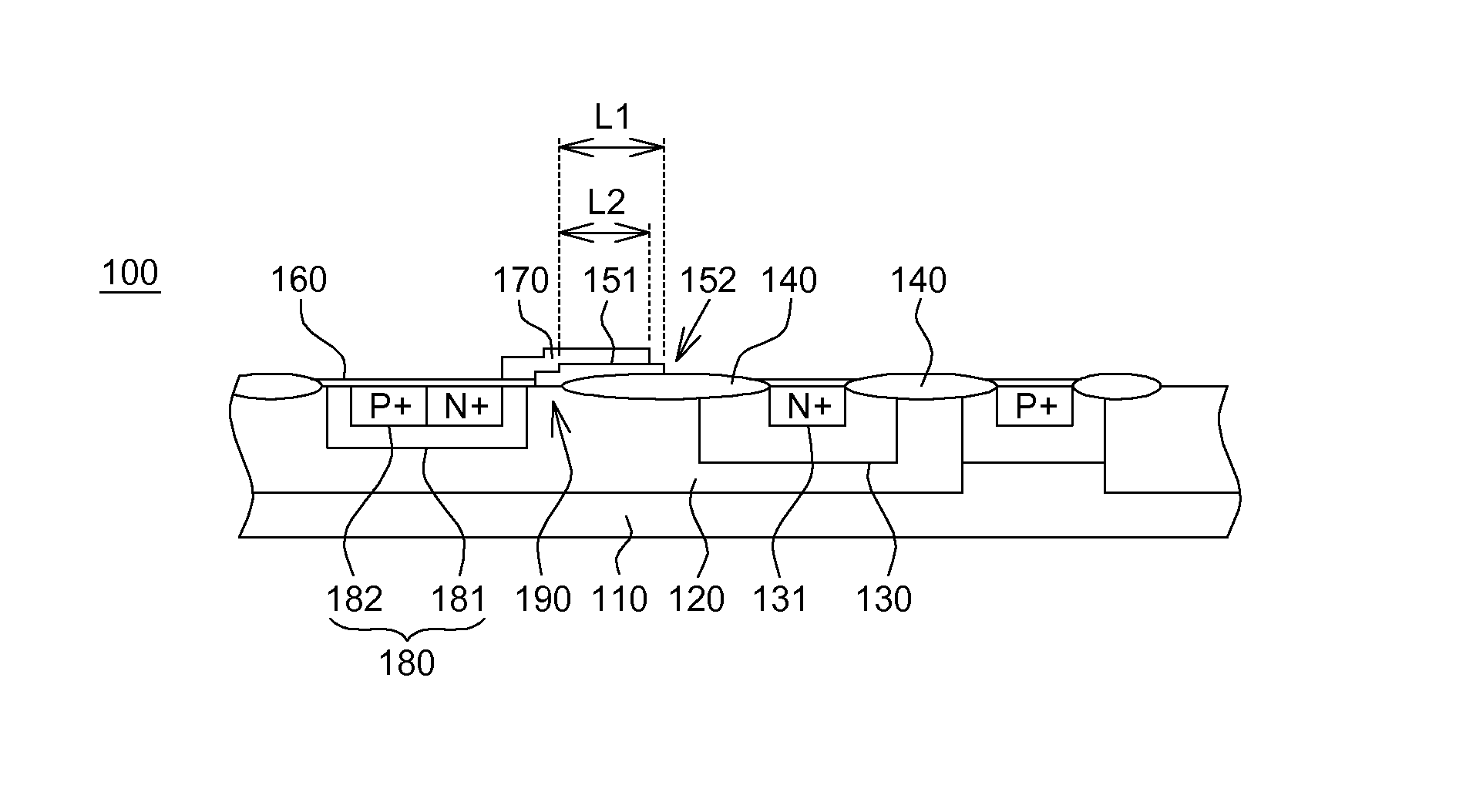

Extended drain transistor and method of manufacturing the same

ActiveUS8216908B2Reduce dopingReduce hot carrier effectSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringTransistor

An extended drain transistor (100) comprising a substrate (101), a gate (103) formed on the substrate (100), the gate (103) having a first side wall (104) and a second side wall (105) opposing the first side wall (104), an extended drain (106) implanted in a surface portion of the substrate (101) adjacent the second side wall (105) of the gate (103), a spacer (107) on the second side wall (105) of the gate (103), a source (108) implanted in a surface portion of the substrate (101) adjacent the first side wall (104) of the gate (103), and a drain (109) implanted in a surface portion of the substrate (101) adjacent the spacer (107) in such a manner that the extended drain (106) is arranged between the gate (103) and the drain (109).

Owner:NXP BV

Strain vertical MOS device manufacturing method

InactiveCN103887178AOvercoming the difficulty of forming small-sized columnar graphsSimple manufacturing processNanoinformaticsSemiconductor/solid-state device manufacturingCharge carrier mobilityAlloy

Disclosed is a strain vertical MOS device manufacturing method. The method comprises the steps of conducting pattern transfer on a substrate, forming a metal mask, forming a silicon column through etching, reducing the diameter of the silicon column, preparing silicon nanowires and growing a gate oxide layer; conducting polycrystalline silicon deposition, doping and foreign ion activation to form an annular grid electrode; depositing a stress silicon nitride film outside the grid electrode to form a stress liner layer; conducting ion injection to form a drain terminal n- doping area; conducting ion injection on the peripheral annular area of the substrate to form a drain terminal n+ doping area; conducting P+ ion injection on the upper portions of the silicon nanowires to form a Halo doping structure, and conducting n type ion injection to form a source terminal; depositing metal and alloy. According to the method, the grid-control capacity of devices in a nanometer node integrated circuit is improved, the short-channel effect and hot carrier effect are restrained, carrier mobility is improved, current driving capacity is improved, the size of the devices is reduced on the premise that the performance of the devices is not reduced, and then requirements for miniaturization of the devices are met.

Owner:XI AN JIAOTONG UNIV

MOS transistor and forming method thereof

InactiveCN104810291AReduce leakage currentExtend your lifeSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricDielectric layer

Disclosed are a MOS transistor and a forming method thereof. The forming method of the MOS transistor includes the following steps: providing a semiconductor substrate; forming a grid electrode structure on the semiconductor substrate, wherein the grid electrode structure includes a gate dielectric layer on the surface of the semiconductor substrate and a grid electrode on the surface of the gate electric layer, part of the semiconductor substrate, beneath the grid electrode structure, is used as a channel area; carrying out ion implantation in part of the semiconductor substrate, at one side of the grid electrode structure so that a pocket area is formed; forming a source electrode and a drain electrode in parts of semiconductor substrate, at the two sides of the grid electrode structure so that the pocket area is between the source electrode and the channel area, wherein the type of doped ions of the source electrode and the drain electrode is opposite to the type of doped ions in the pocket area. The method is capable of reducing a hot carrier effect of the MOS transistor so that the performance of the transistor is improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Semiconductor device structure and method for reducing hot carrier effect of MOS transistor

ActiveUS20060246715A1Reducing hat carrier effectSmall increase in lifetime of deviceTransistorSolid-state devicesElectrical conductorDevice material

A semiconductor device structure is described, including a MOS transistor, a silicon-rich silicon nitride layer having a refractive index of about 2.00-2.30, and a dielectric layer. The silicon-rich silicon nitride layer is disposed between the MOS transistor and the dielectric layer, and covers the source / drain region, the spacer and the gate conductor of the MOS transistor.

Owner:UNITED MICROELECTRONICS CORP

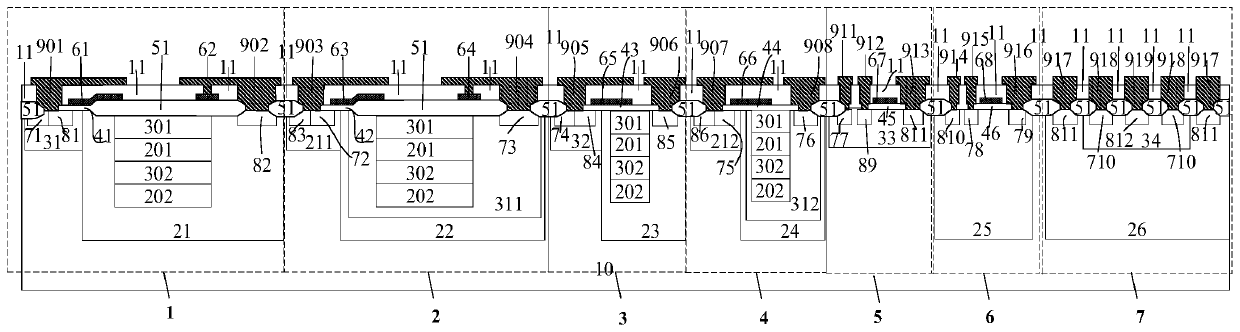

Semiconductor device and manufacturing method thereof

PendingCN111370467ALower on-resistanceImprove reliabilitySolid-state devicesSemiconductor devicesDevice materialInput impedance

The invention provides a semiconductor device and a manufacturing method thereof. The semiconductor device comprises a first-class high-voltage nLDMOS device, a first-class high-voltage pLDMOS device,a second-class high-voltage nLDMOS device, a second-class high-voltage pLDMOS device, a low-voltage NMOS device, a low-voltage PMOS device and a low-voltage NPN device which are integrated on the same chip. The first p-type field reduction layer is located on the surface, so that the conductive channel moves downwards, the hot carrier effect is reduced, and the reliability of the device is improved. The n-type heavily doped layer, the p-type field reduction layer, the n-type deep trap, the p-type trap and the p-type substrate form a multiple RESURF structure, the specific on-resistance of thehigh-voltage device is reduced, and the manufacturing cost of the chip is reduced. Compared with a traditional structure without an n-type heavily doped layer, the n-type heavily doped layer has smaller on-resistance under the condition of the same chip area, the on-resistance and the dynamic resistance of the device can be reduced through the n-type heavily doped layer, and the nLDMOS device further has the advantages of being high in input impedance, low in output impedance and the like.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

Thin film transistor and manufacturing method thereof

InactiveCN109830539AEffect of Reducing Leakage CurrentReduce hot carrier effectTransistorSemiconductor/solid-state device manufacturingOptoelectronicsPolycrystalline silicon

A thin film transistor comprises a substrate, a buffer layer, a polycrystalline silicon layer, a gate insulating layer, a gate layer, an insulating layer, a source electrode and a drain electrode. Thegate insulating layer comprises a central part and two inclination angle parts arranged in the two sides of the central part respectively, the central part covers a channel region of the polycrystalline silicon layer, the inclination angle portions cover lightly-doped regions of the polycrystalline silicon layer respectively, so that the gate insulating layer forms an inclination angle structurecorresponding to the lightly doped regions. Thus, the thin film transistor is heavily and lightly doped in one doping process. The invention also provides a manufacturing method of the thin film transistor.

Owner:WUHAN CHINA STAR OPTOELECTRONICS SEMICON DISPLAY TECH CO LTD

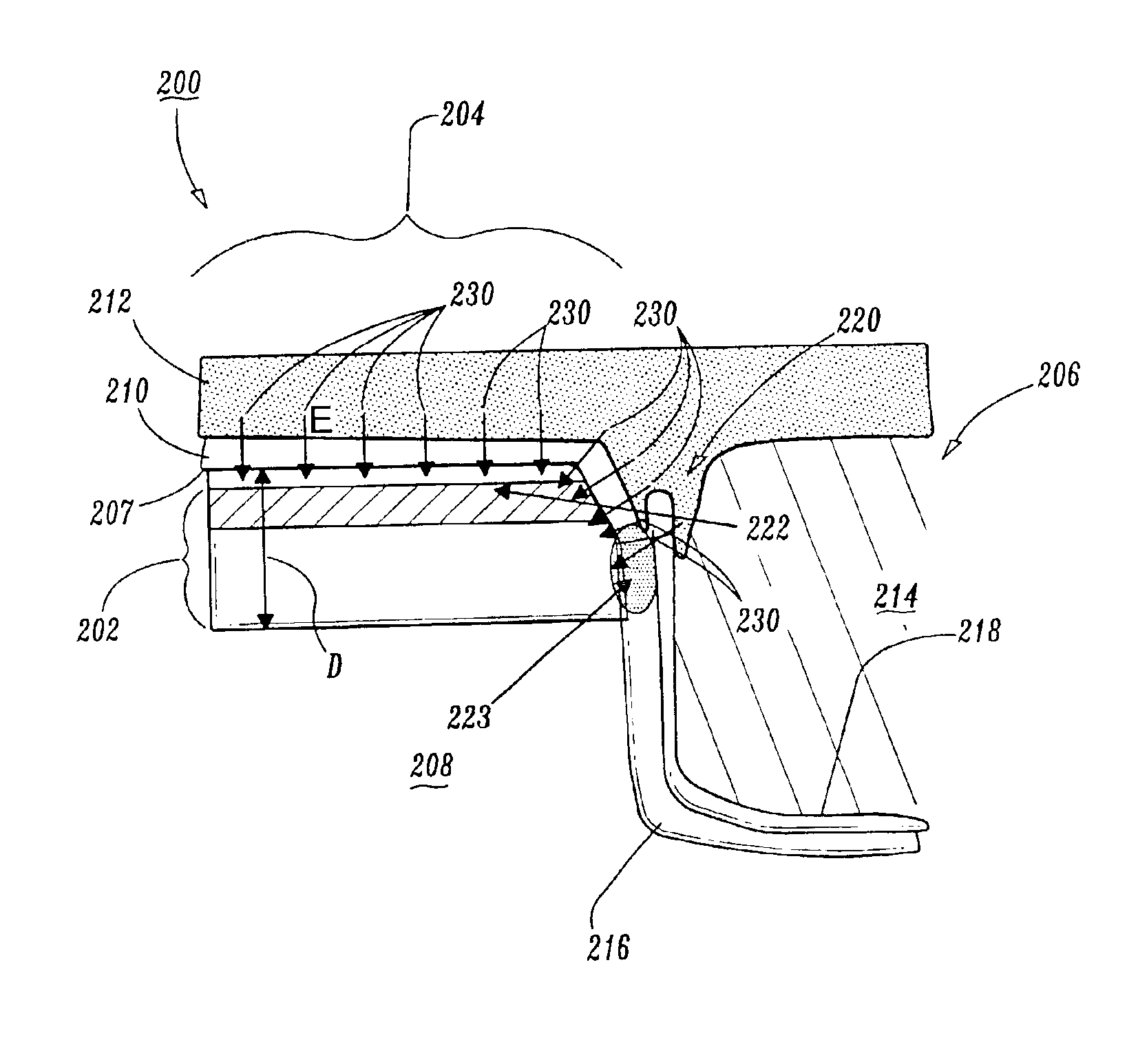

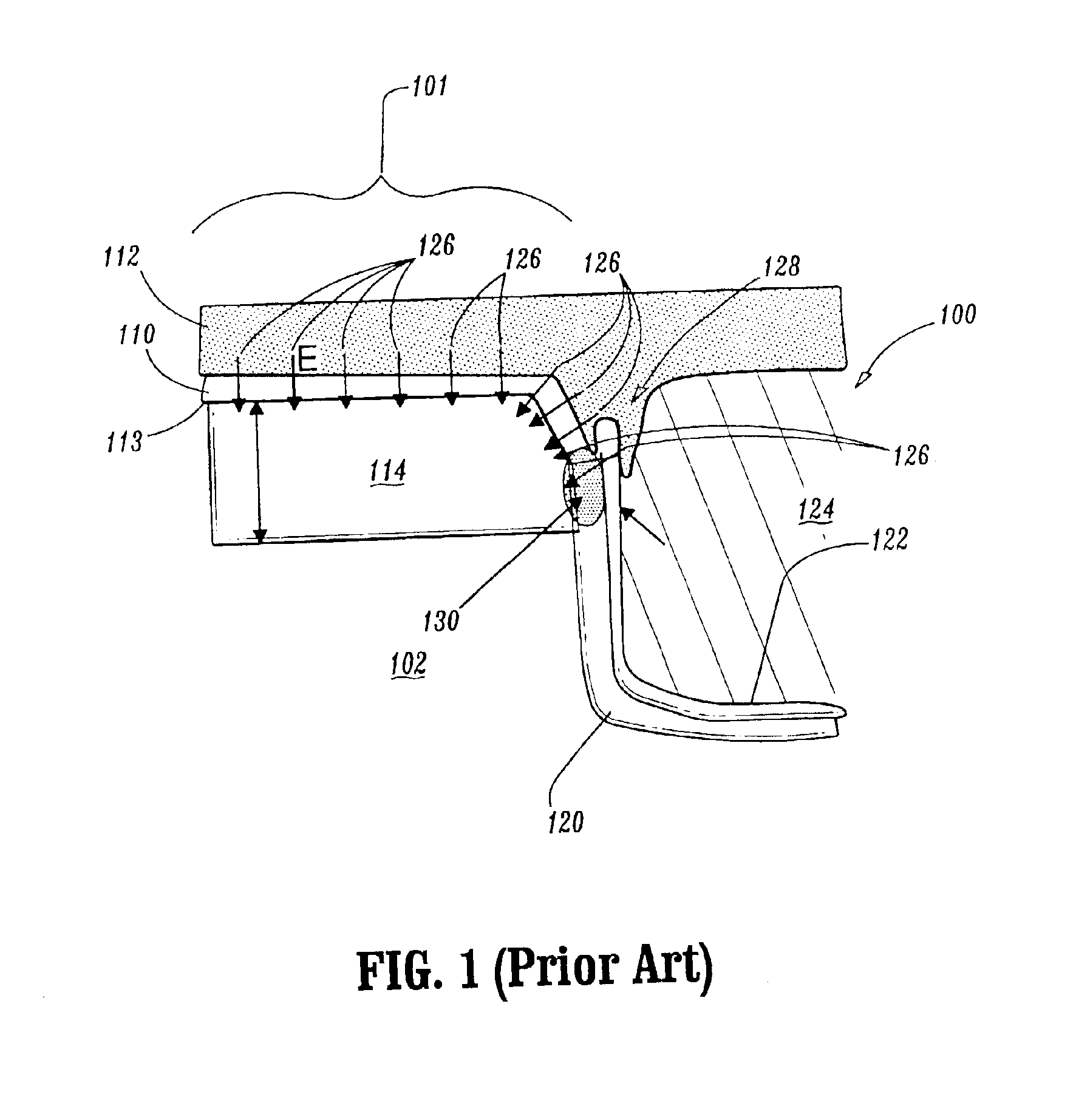

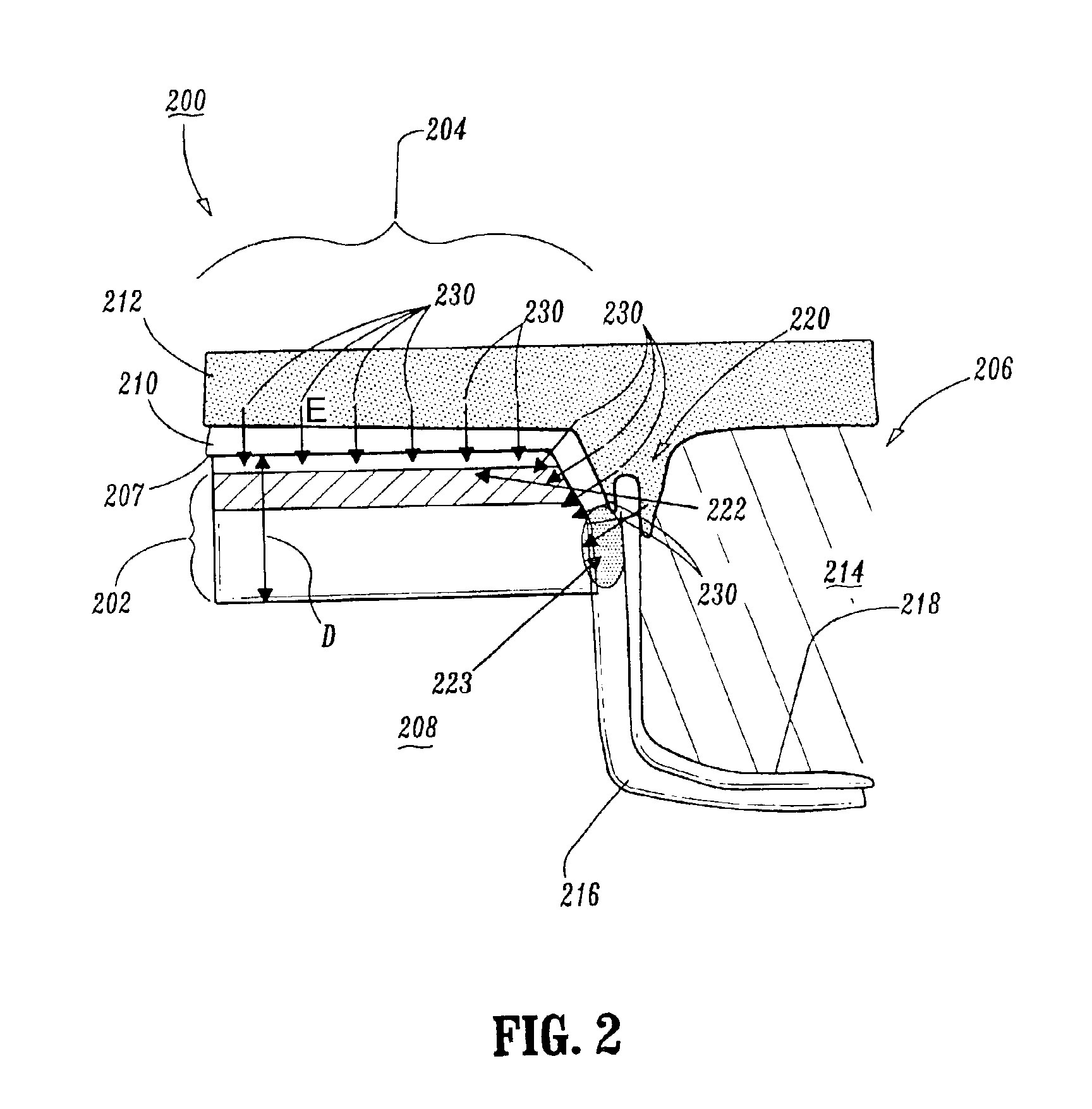

Reduced hot carrier induced parasitic sidewall device activation in isolated buried channel devices by conductive buried channel depth optimization

ActiveUS6867472B2Reduce hot carrier effectImprove performanceTransistorSemiconductor/solid-state device testing/measurementHot carrier effectConductive channel

A semiconductor device includes a transistor junction formed in a substrate adjacent to an isolation region. A region between the transistor junction and the isolation region includes an area susceptible to hot carrier effects. The transistor junction extends from a surface of the substrate to a first depth. A buried conductive channel layer is formed within the transistor junction between the surface of the substrate and the first depth. The buried conductive channel layer has a peak conduction depth, which is different from a depth of the area susceptible to hot carrier effects.

Owner:SAMSUNG ELECTRONICS CO LTD +1

![[low-temperature polysilicon thin film transistor and fabrication method thereof] [low-temperature polysilicon thin film transistor and fabrication method thereof]](https://images-eureka.patsnap.com/patent_img/4dc3a9dc-5b5e-4d88-9831-cc022abd9f60/US20050218403A1-20051006-D00000.png)

![[low-temperature polysilicon thin film transistor and fabrication method thereof] [low-temperature polysilicon thin film transistor and fabrication method thereof]](https://images-eureka.patsnap.com/patent_img/4dc3a9dc-5b5e-4d88-9831-cc022abd9f60/US20050218403A1-20051006-D00001.png)

![[low-temperature polysilicon thin film transistor and fabrication method thereof] [low-temperature polysilicon thin film transistor and fabrication method thereof]](https://images-eureka.patsnap.com/patent_img/4dc3a9dc-5b5e-4d88-9831-cc022abd9f60/US20050218403A1-20051006-D00002.png)