Strain vertical MOS device manufacturing method

A technology of MOS device and manufacturing method, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as device performance degradation, and achieve the effects of improving gate control capability, increasing transconductance, and improving mobility.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

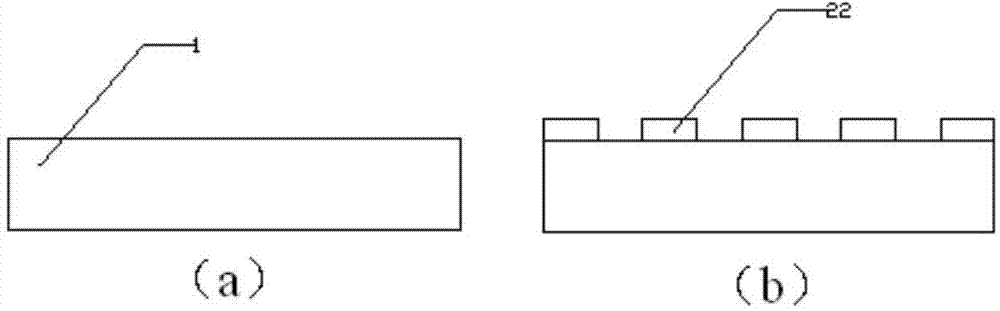

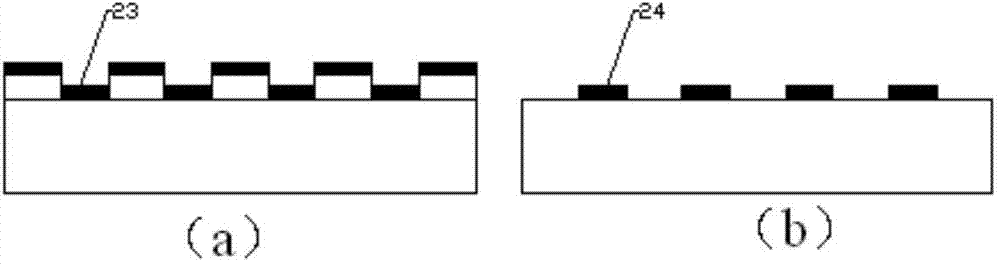

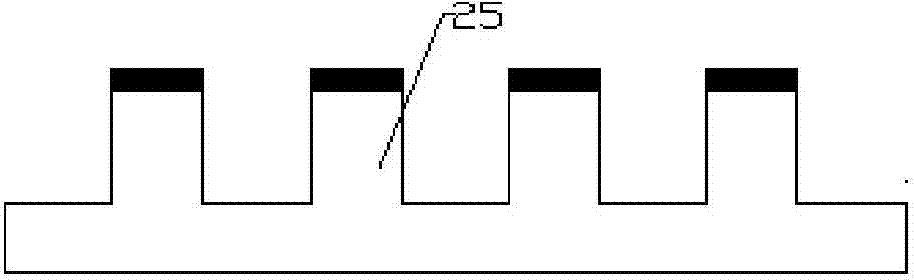

[0054] The present invention will be described in detail below in conjunction with the accompanying drawings.

[0055] see Figure 21 and Figure 22 , the strained vertical MOS device manufactured by the present invention includes a substrate 1, a cylindrical channel region vertically arranged on the substrate, a ring-shaped dielectric layer, polysilicon 9, a stress liner layer 5 and a drain conductive layer 3; the drain The conductive layer, the dielectric layer, the gate conductive layer, and the stress liner layer are evenly distributed, and the active conductive layer is arranged on the channel region, and the top of the cylindrical channel region is doped with n+ impurities as the source n+ region 6, doped with n- impurities As the source n-region 7; the drain region is doped with n+ impurities as the drain n+ doped region 2, and doped with n- impurities as the drain n-doped region 10; meanwhile, the cylindrical center of the channel region An asymmetrical Halo-doped so...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| diameter | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More