Manufacturing method for MOS transistor

A technology for MOS transistors and manufacturing methods, which is applied in the manufacture of semiconductor/solid-state devices, electrical components, circuits, etc., can solve the problems of degradation of short-channel device characteristics, low junction leakage performance, and increased junction leakage, so as to suppress thermal load. Carrier effect, increase in charge mobility, effect of good device characteristics

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

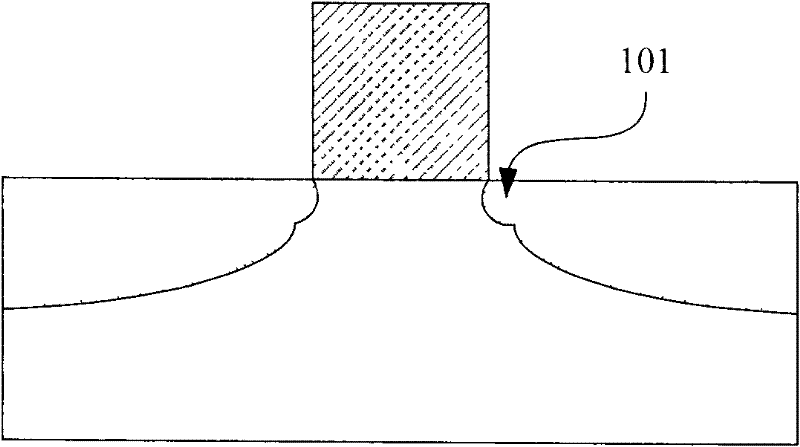

[0030] The manufacturing method of the MOS transistor proposed by the present invention will be further described in detail below with reference to the drawings and specific embodiments. Advantages and features of the present invention will be apparent from the following description and claims. It should be noted that all the drawings are in very simplified form, and are only used for the purpose of conveniently and clearly assisting in describing the embodiments of the present invention.

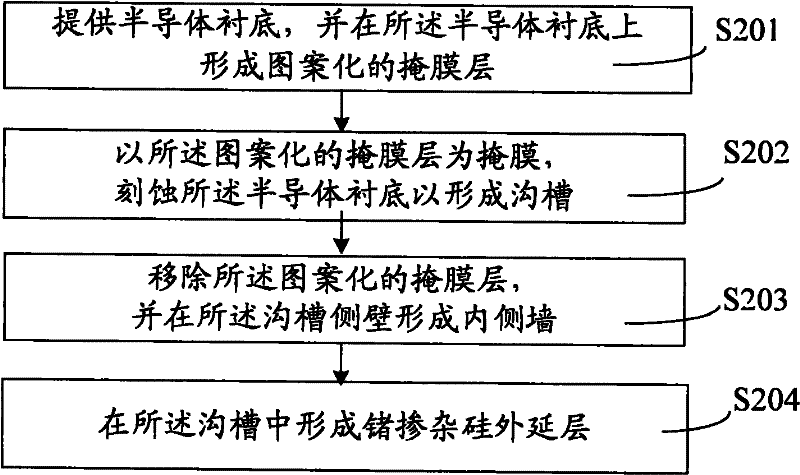

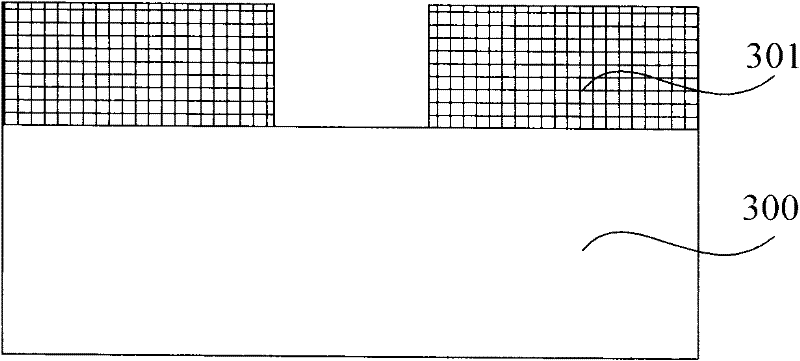

[0031] Such as figure 2 As shown, the present invention provides a method for manufacturing a MOS transistor, which is completed by the steps shown in S201 to S204, combined below figure 2 The flow chart of the fabrication process of the MOS transistor and Figure 3A ~ 3E The schematic cross-sectional structural diagram of the manufacturing process of the MOS transistor is described in detail for the manufacturing method of the above-mentioned MOS transistor.

[0032] S201, providing a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More