Patents

Literature

65results about How to "Reduce junction leakage" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

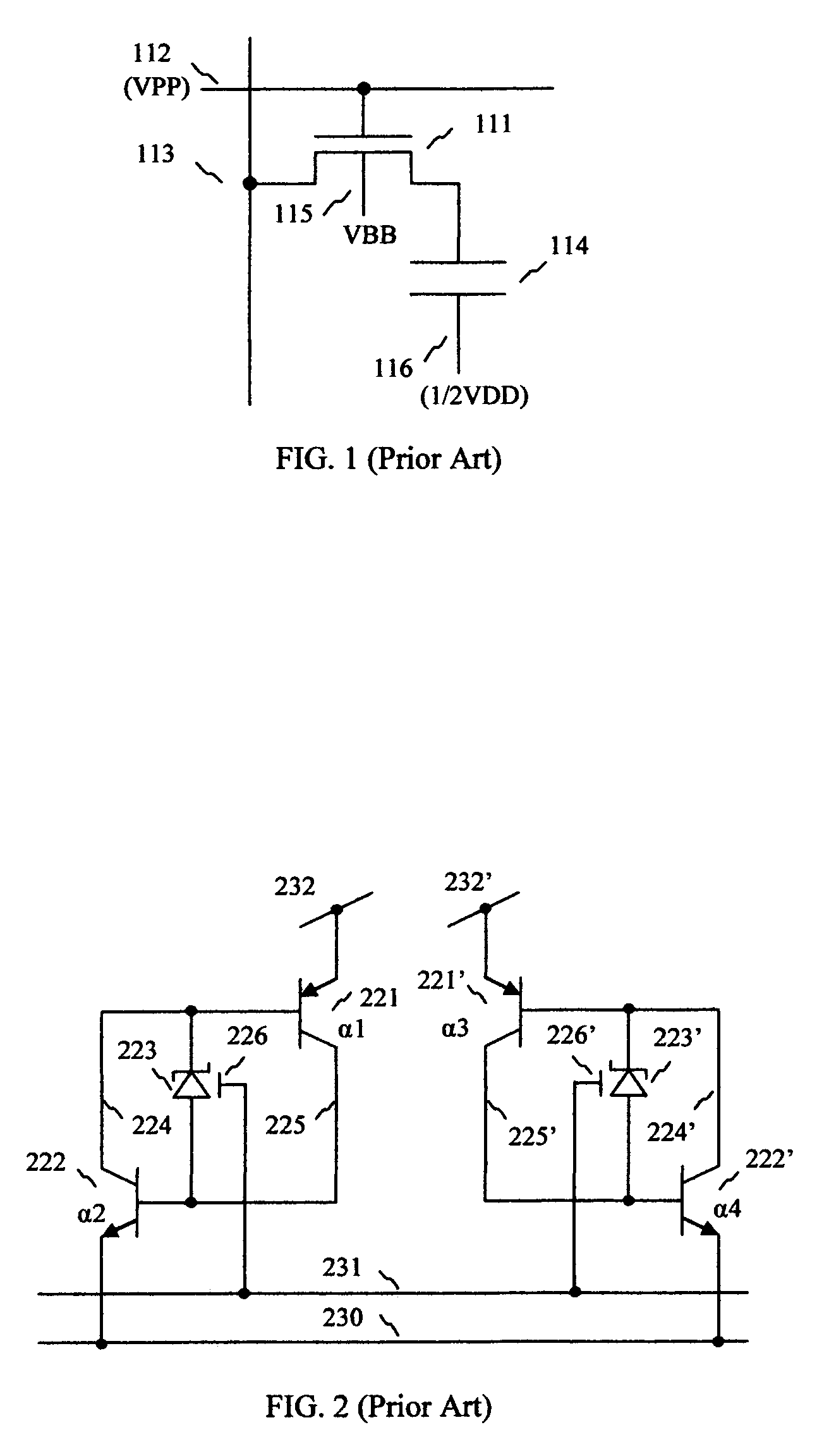

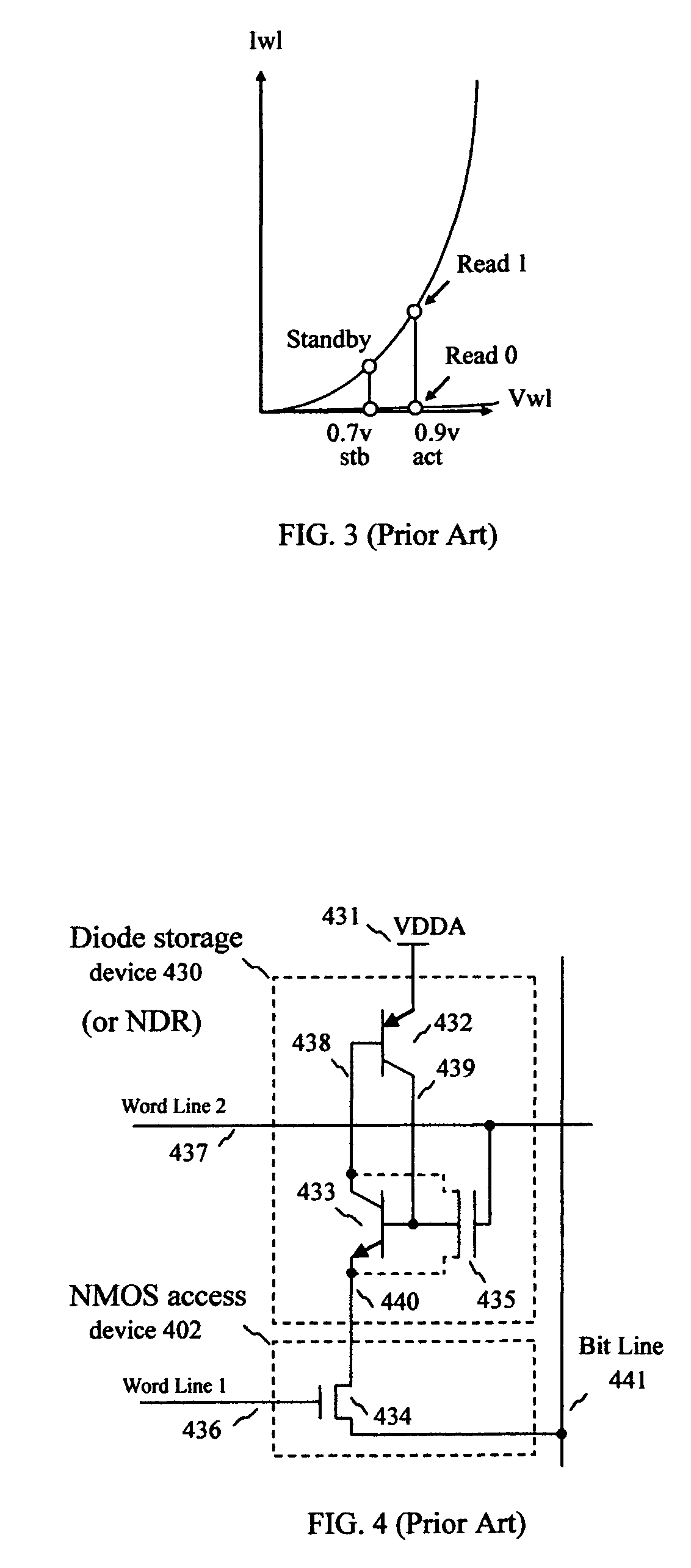

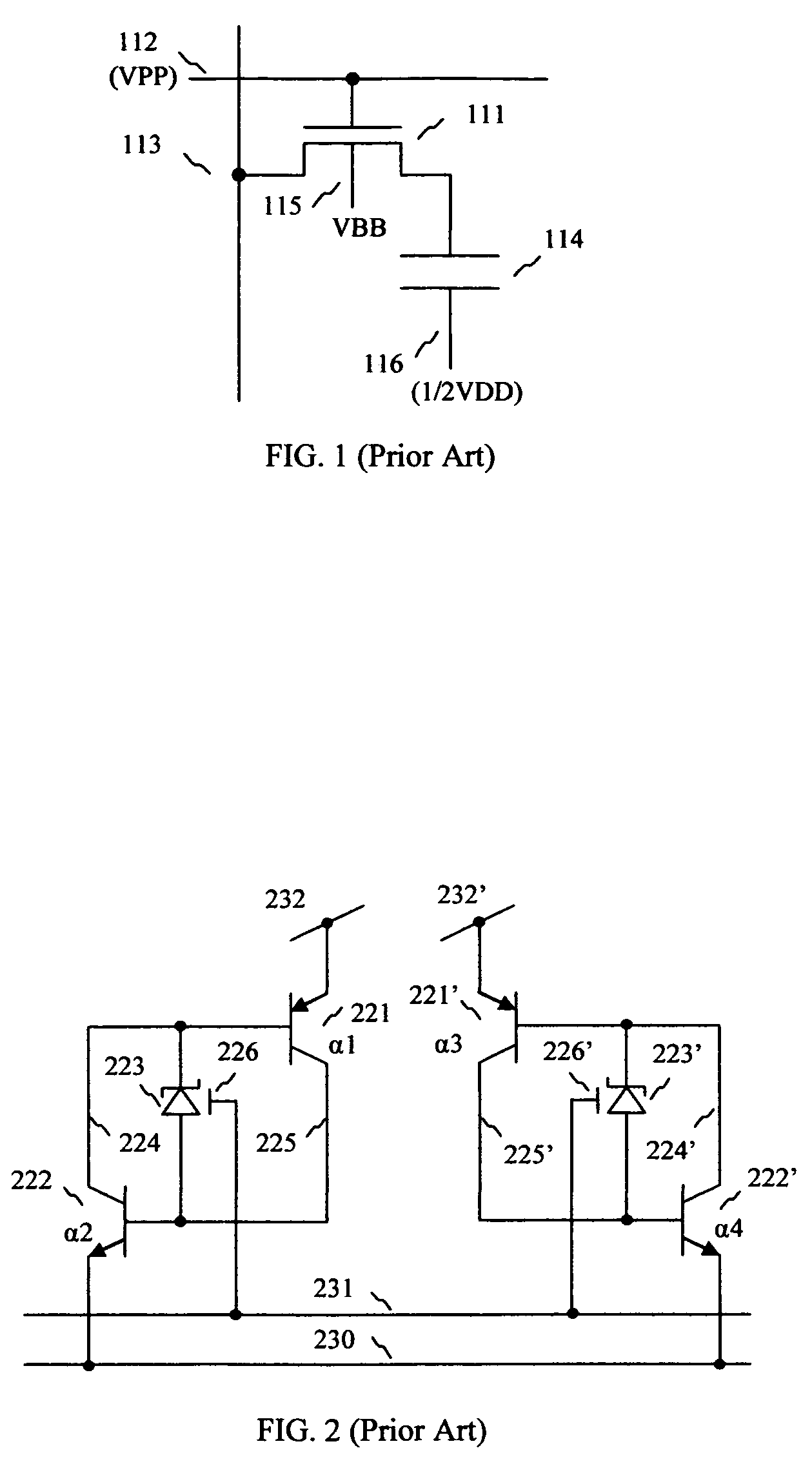

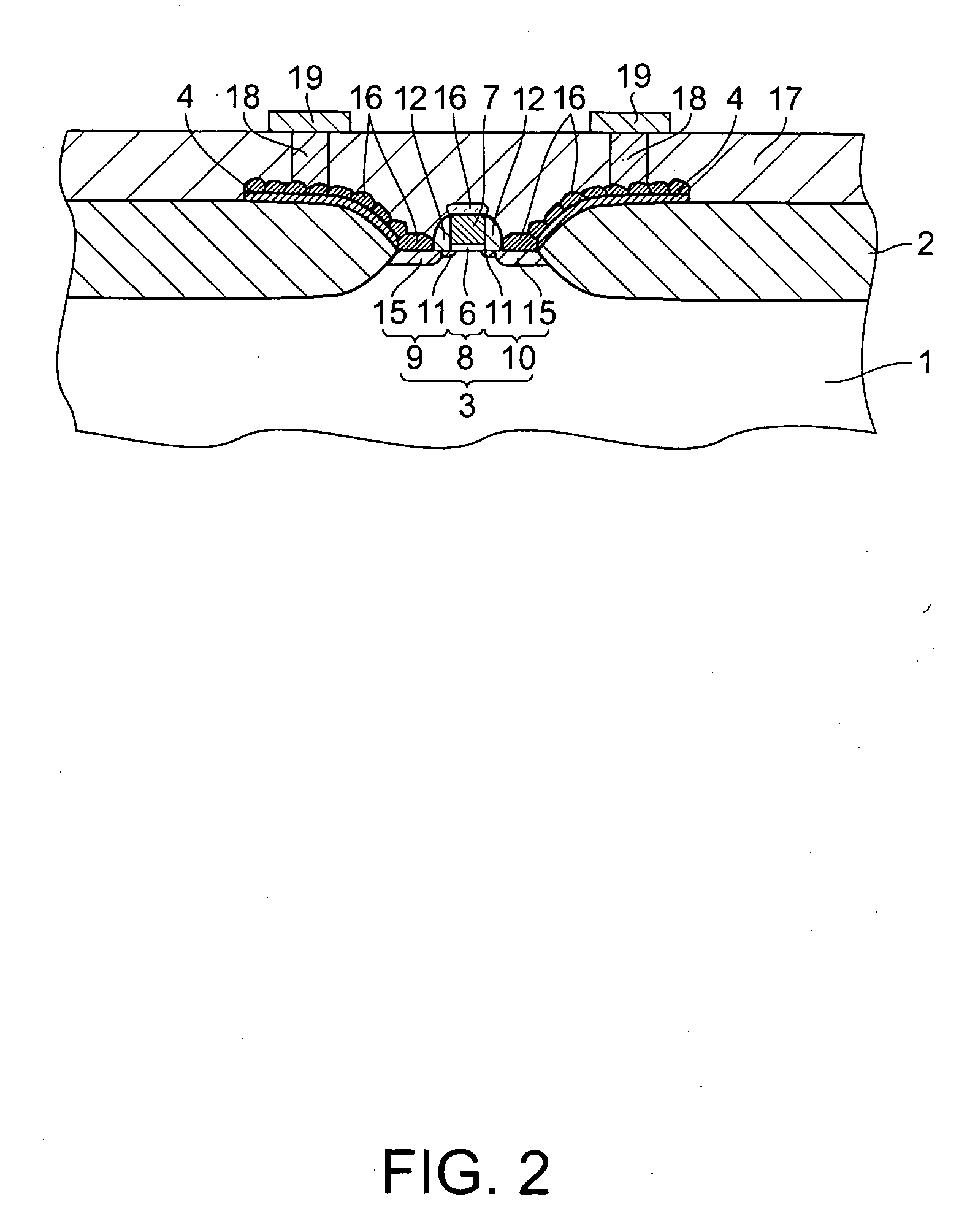

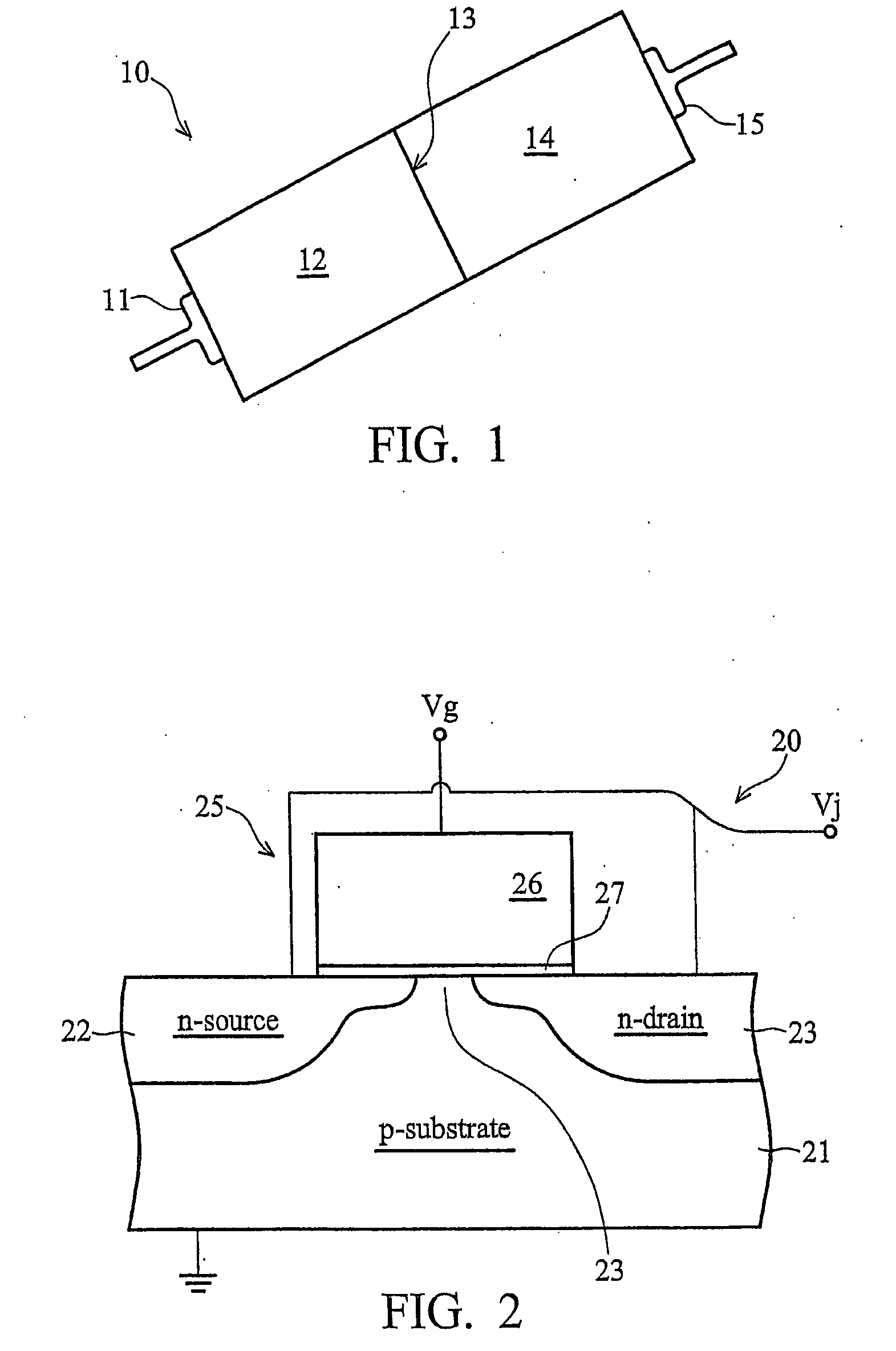

Planar capacitor memory cell and its applications

InactiveUS7209384B1Less complicated to fabricateImprove performanceTransistorSolid-state devicesHemt circuitsEngineering

A capacitor memory is realized, wherein a capacitor stores data and a diode controls to store data “1” or “0”. Diode has four terminals wherein first terminal serves as word line, second terminal serves as storage node, third terminal is floating, and fourth terminal serves as bit line, wherein back channel effect is suppressed adding additional ions in the bottom side of third terminal or applying negative voltage in the well or substrate. A capacitor plate couples to second terminal, which plate has no coupling region to first, third and fourth terminal. With no coupling, the inversion layer of plate in the storage node is isolated from the adjacent nodes. In doing so, the plate can swing ground level to positive supply level to write. As a result, no negative generator is required for controlling plate. Word line and bit line keep ground level during standby, and rise to supply level for read or write operation. In this manner, no holding current is required during standby, and operating current is dramatically reduced with no negative generator. Write has a sequence to clear the state of cell before writing to store data regardless of previous state. Refresh cycle is periodically asserted to sustain data. The present invention can be applied for destructive read, or for nondestructive read adding pull-down device to bit line. The height of cell is almost same as control circuit on the bulk or SOI wafer.

Owner:KIM JUHAN

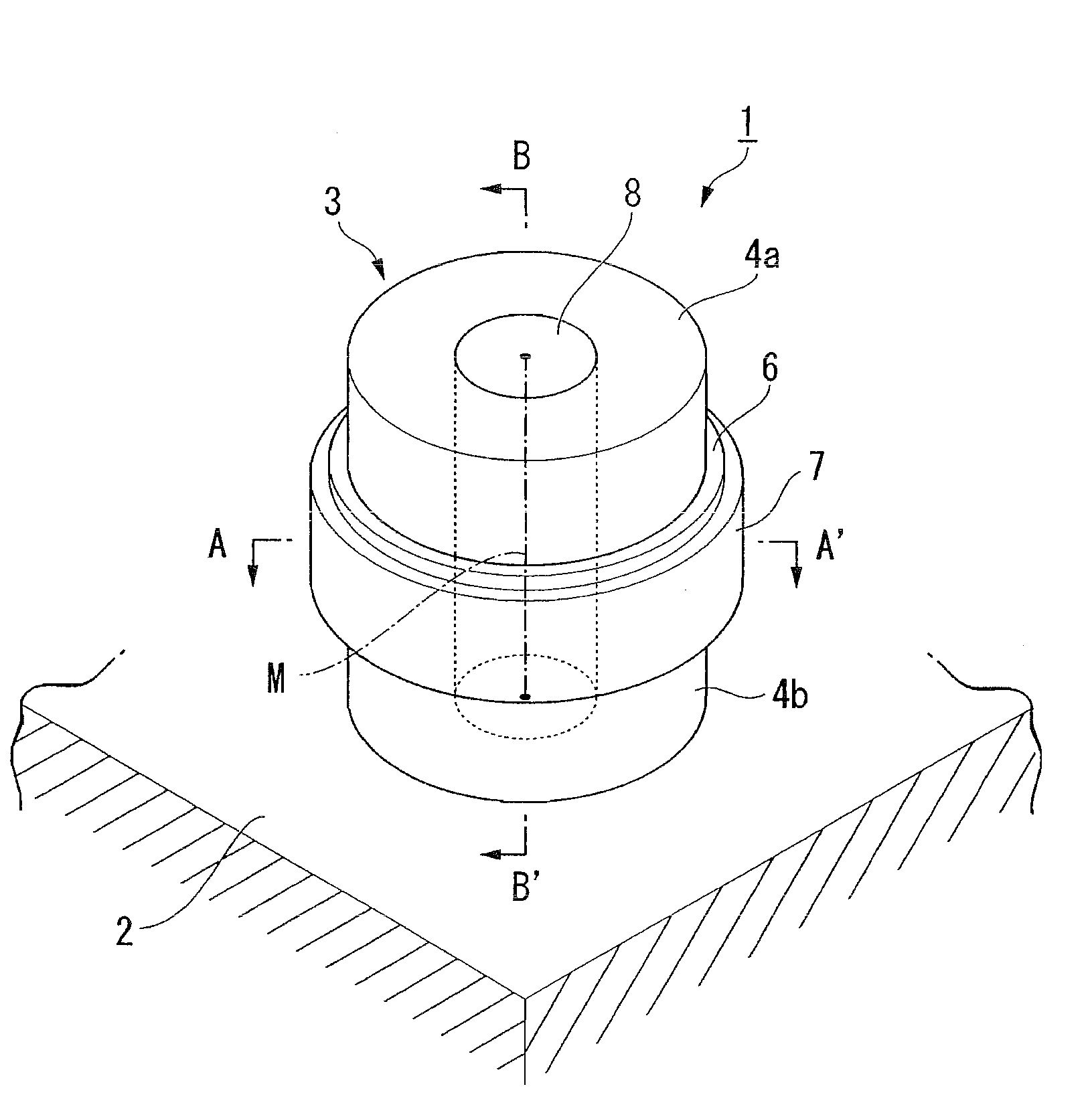

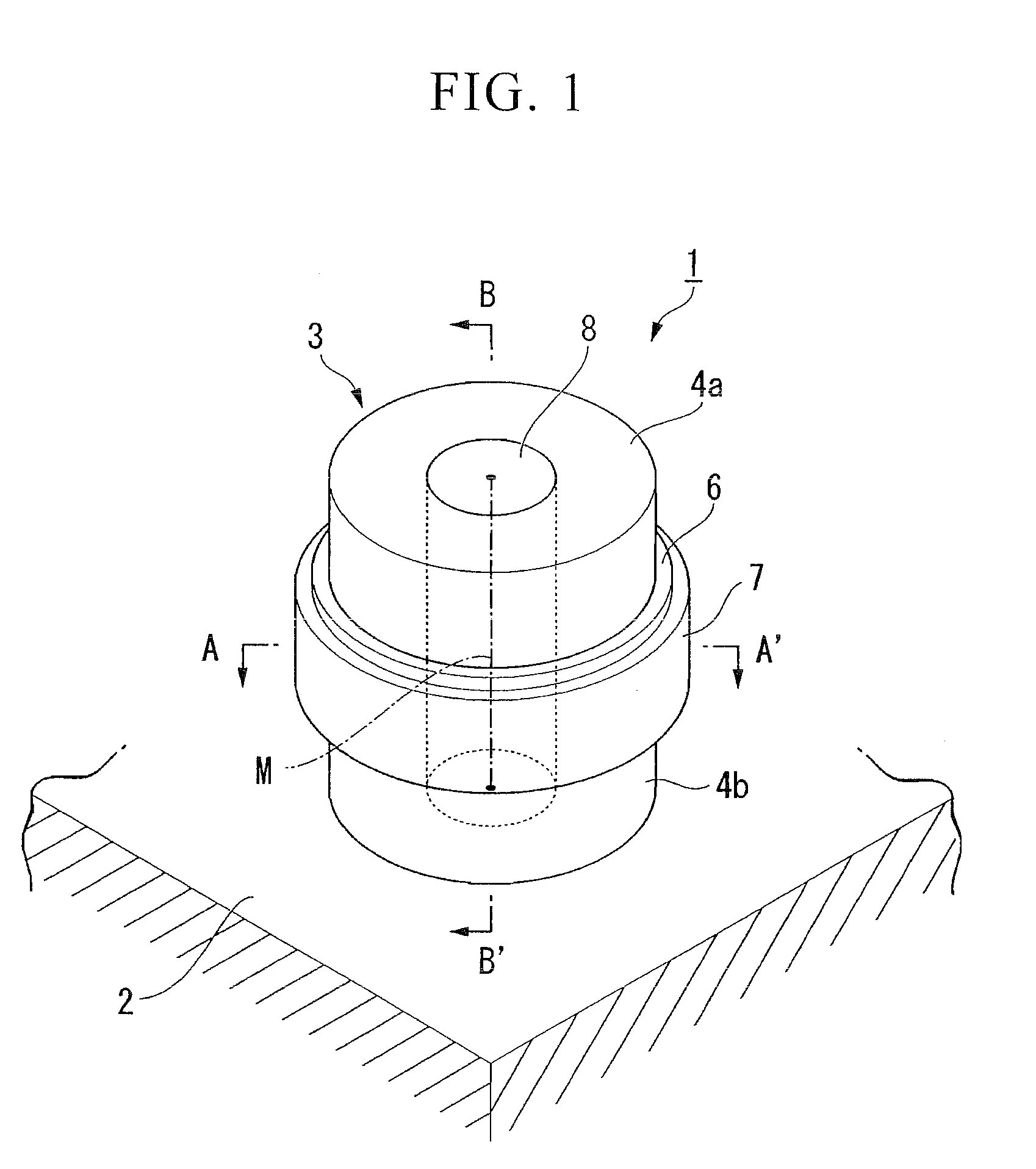

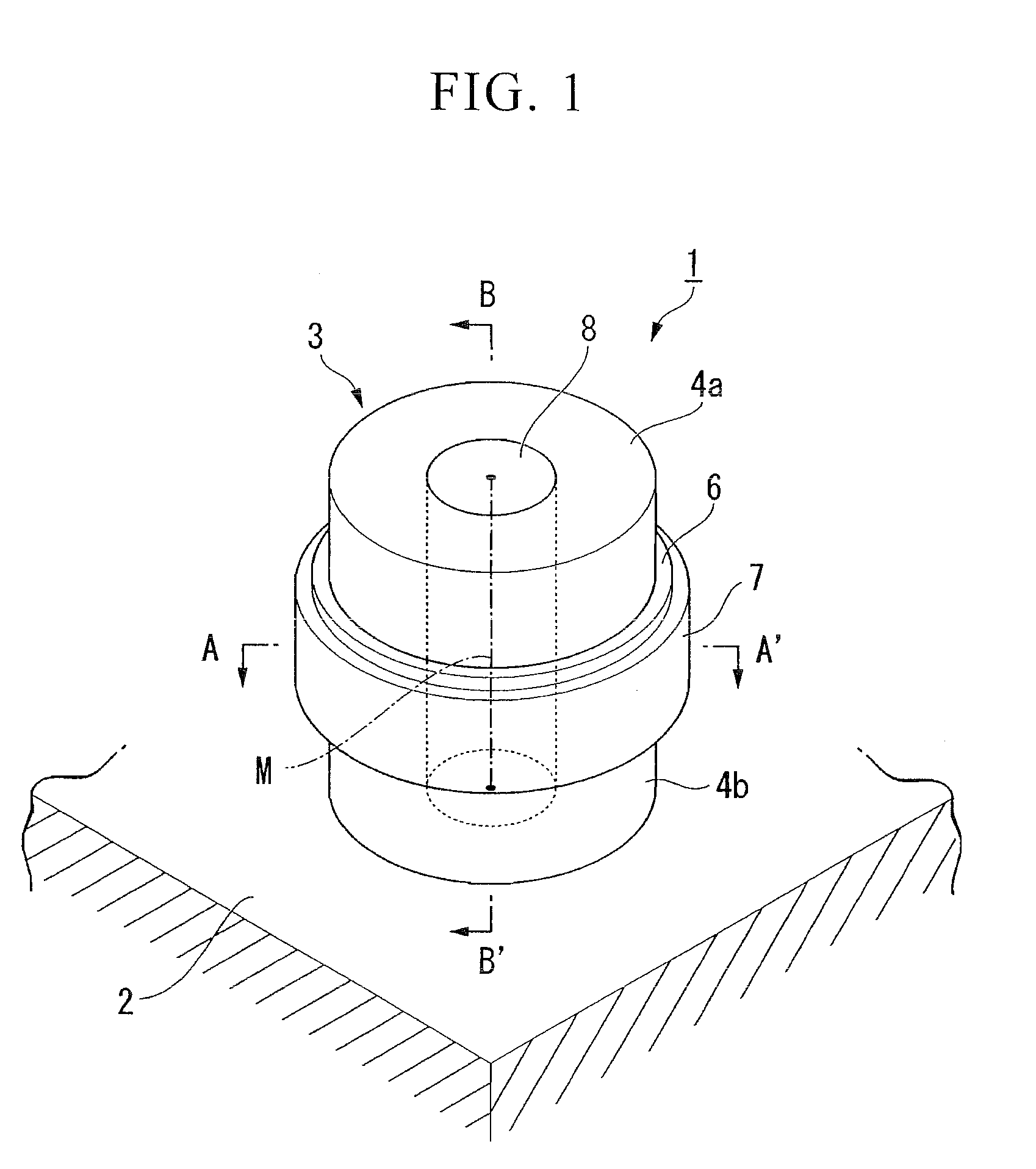

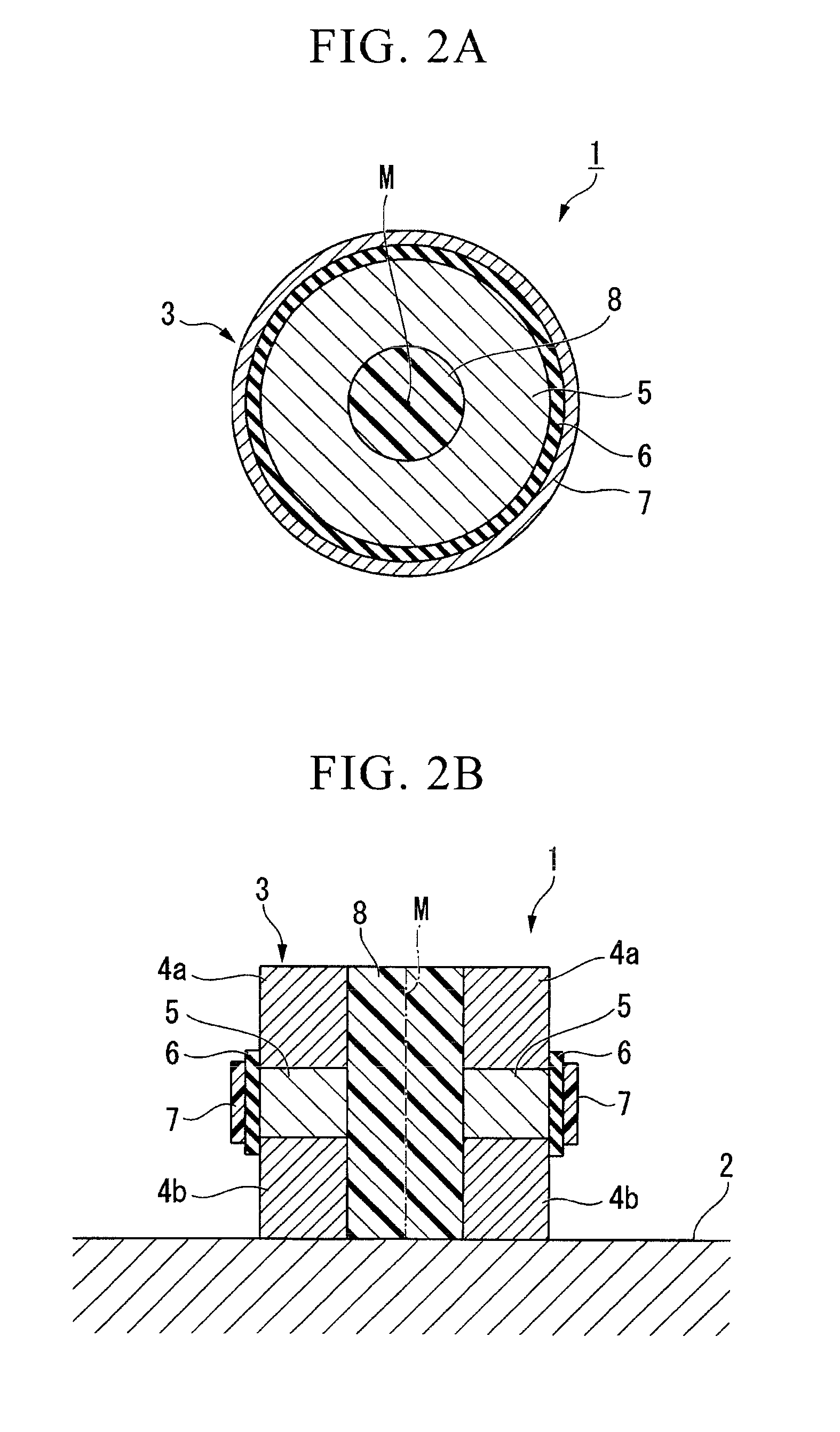

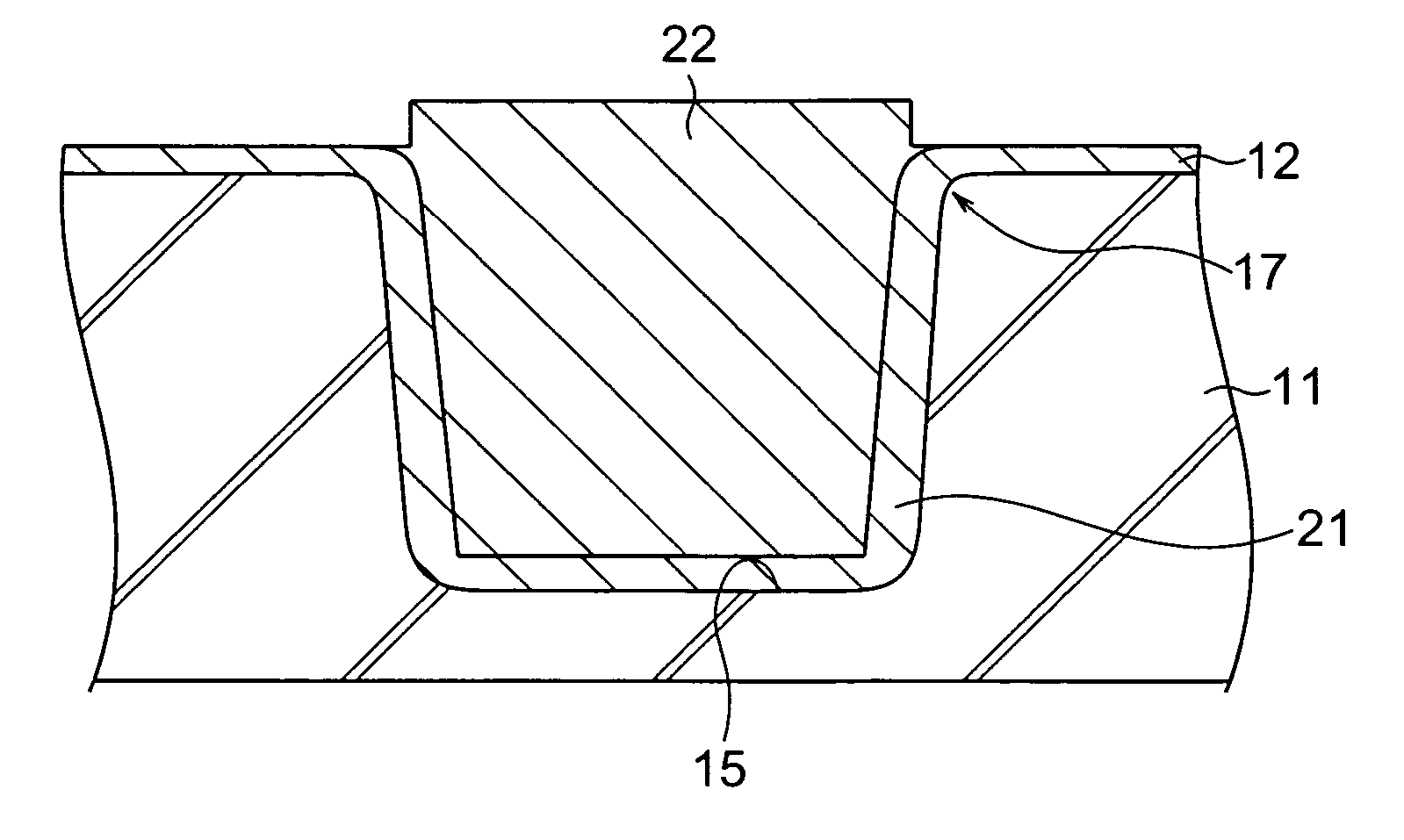

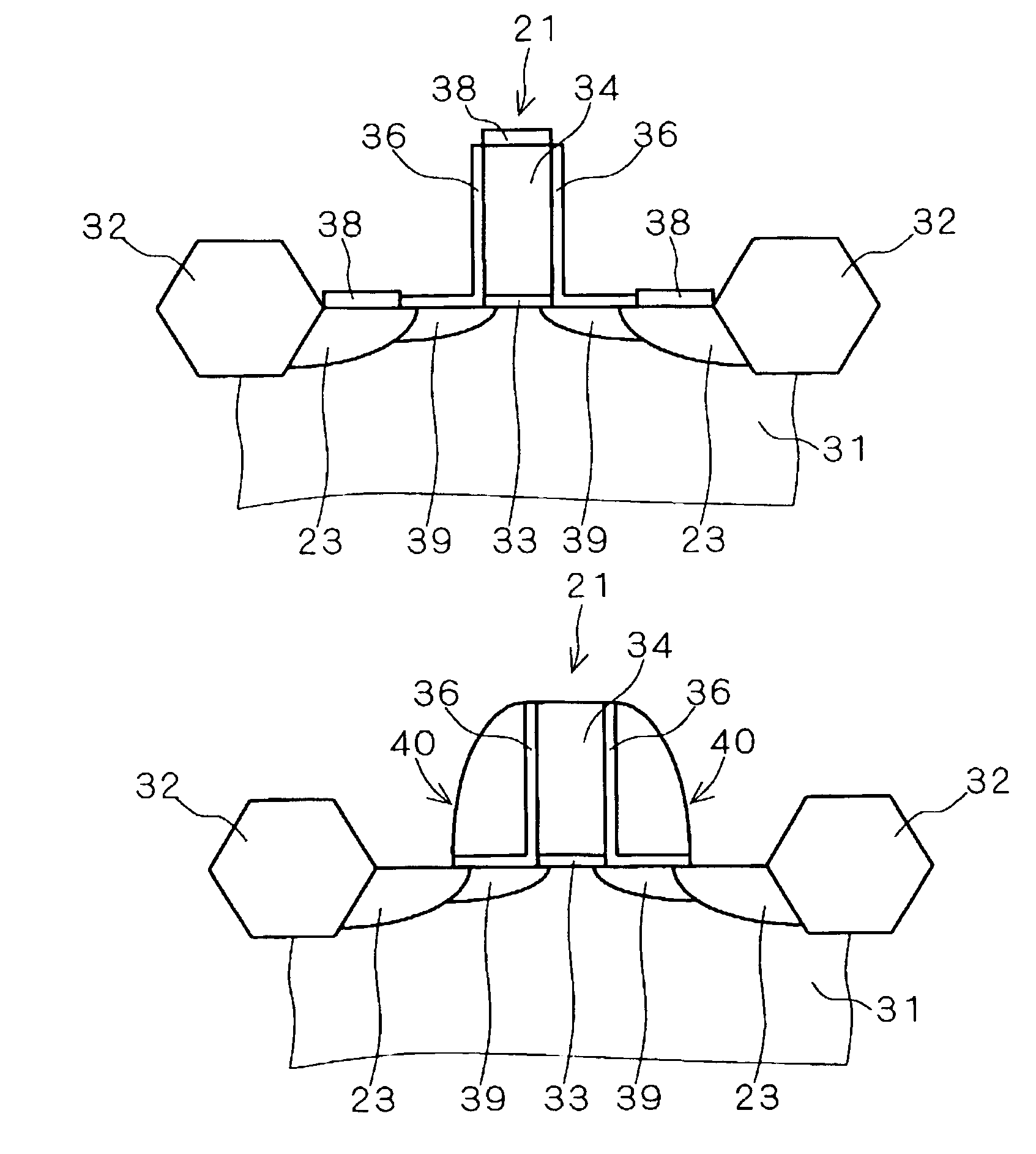

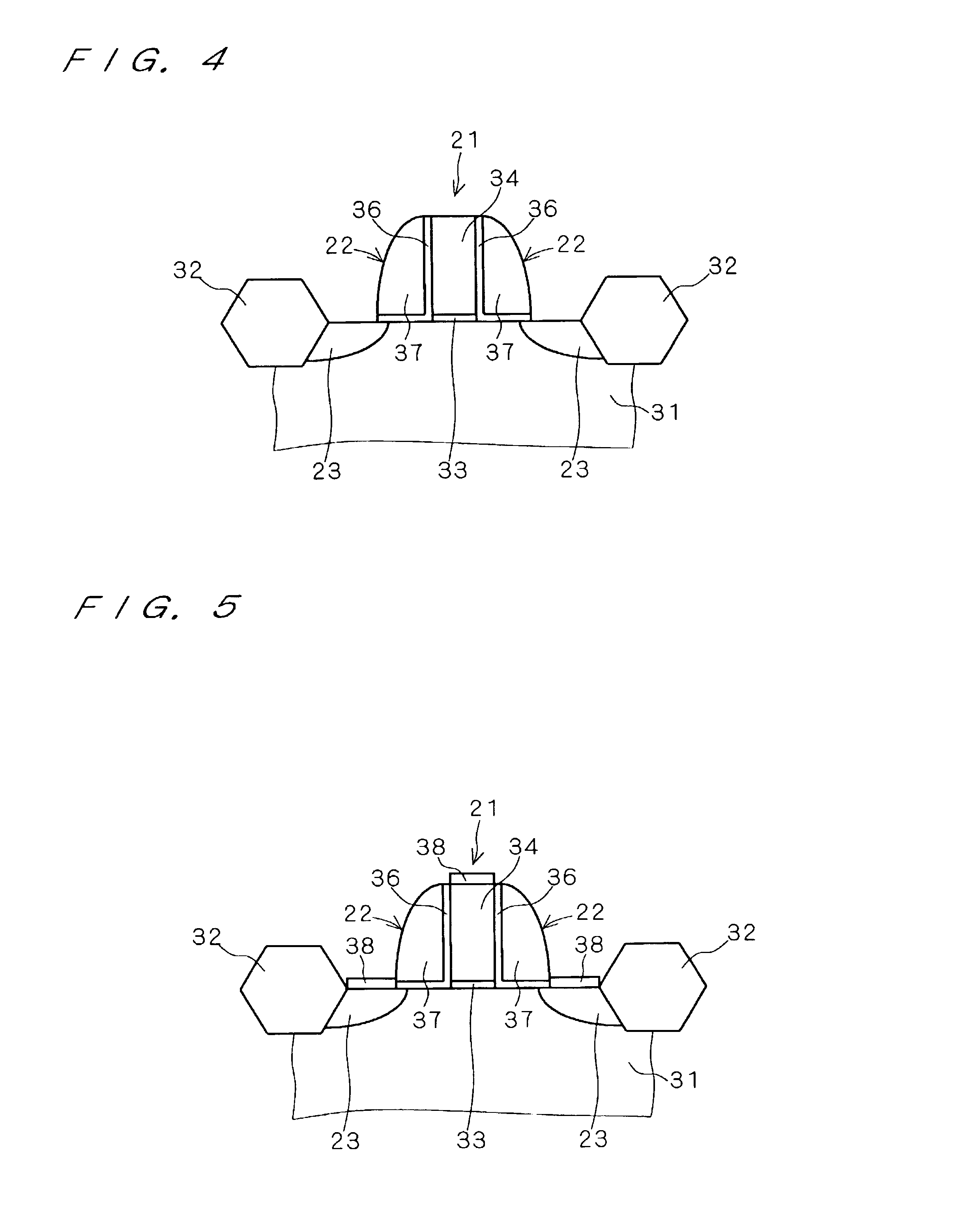

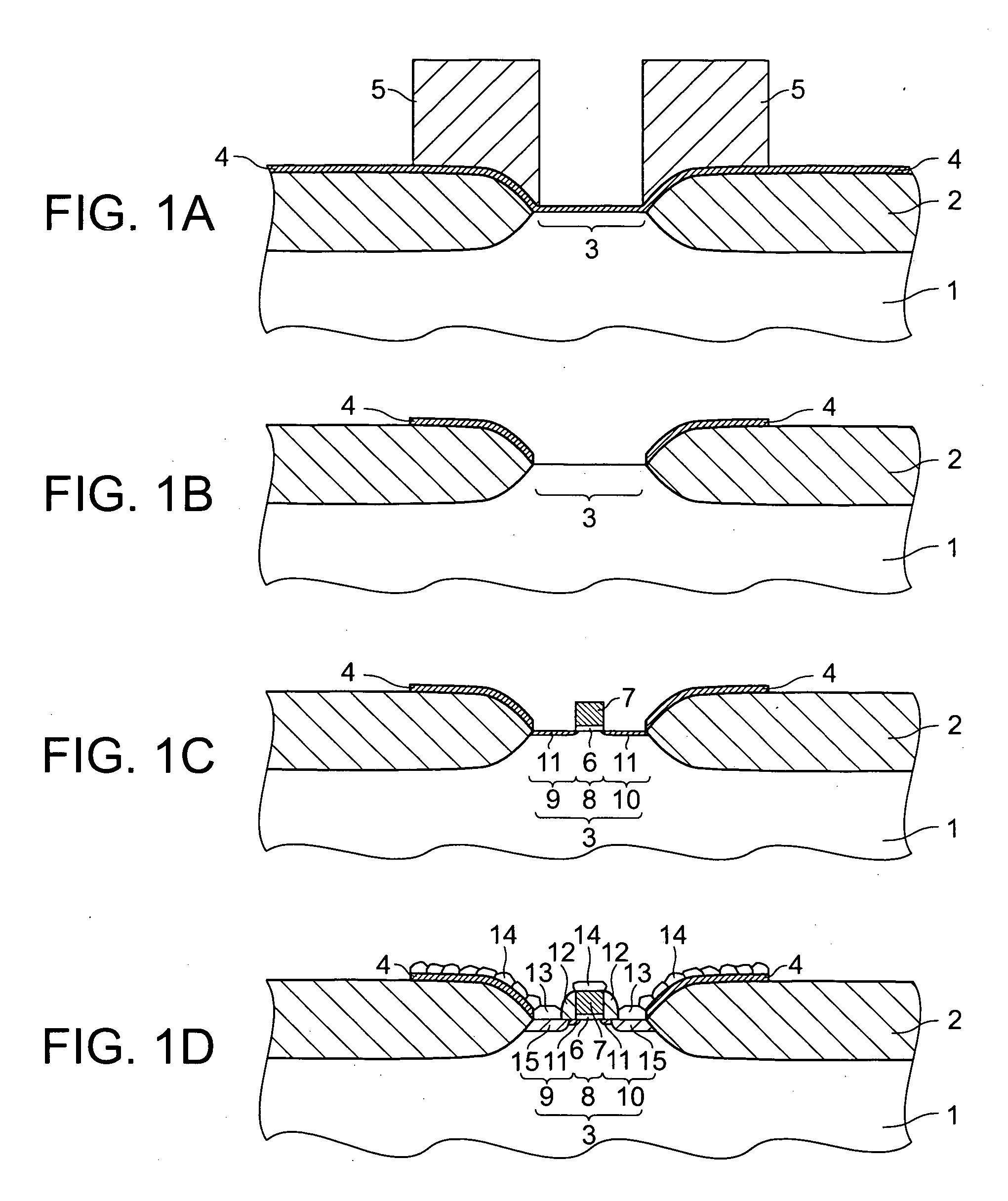

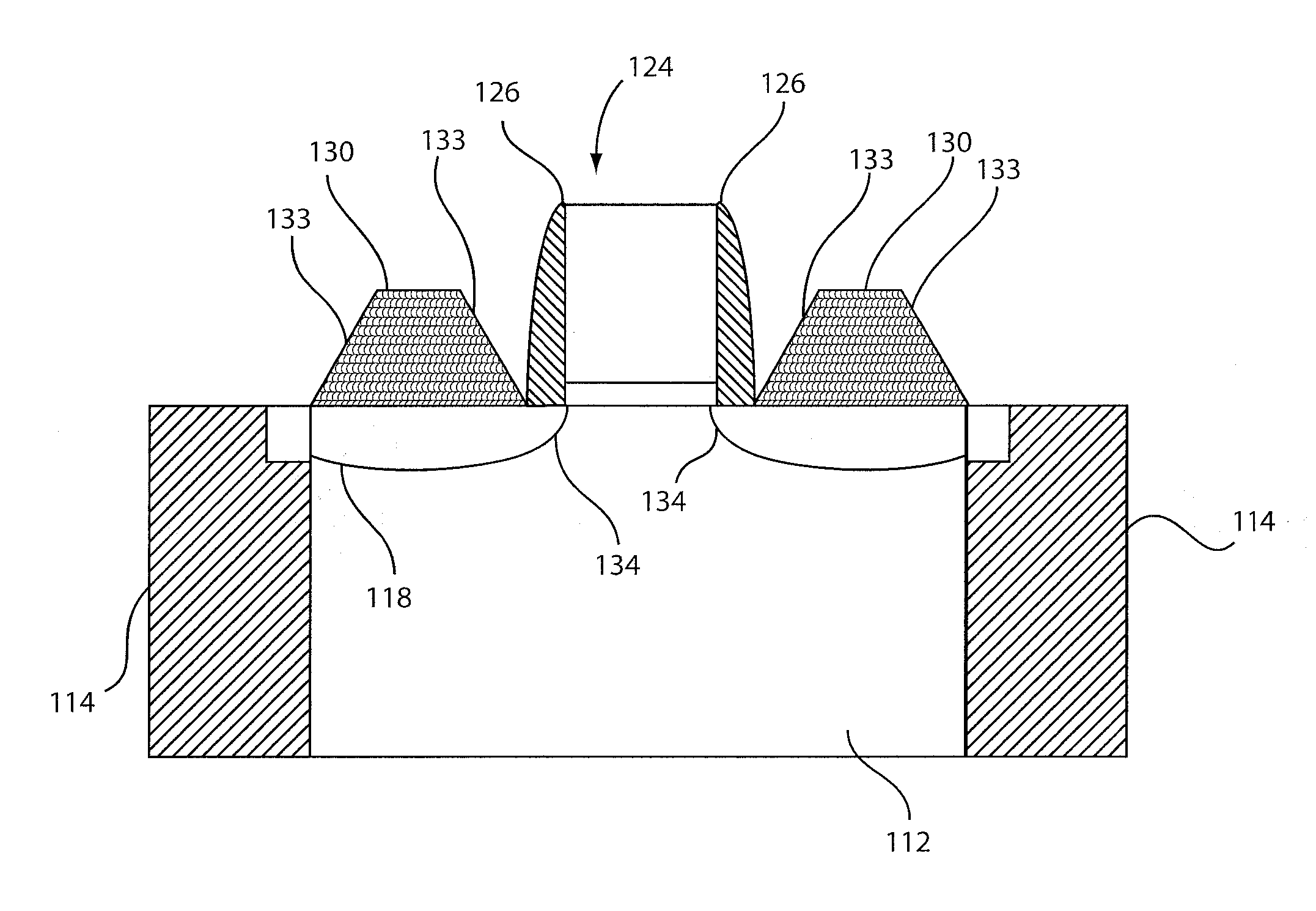

Semiconductor device and method of manufacturing semiconductor device

InactiveUS20090032849A1Increase currentReduce areaSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringSemiconductor device

A semiconductor device includes a cylindrical main pillar that is formed on a substrate and of which a central axis is perpendicular to the surface of the substrate, source and drain diffused layers that are formed in a concentric shape centered on the central axis at upper and lower portions of the main pillar and made from a first-conduction-type material, a body layer that is formed at an intermediate portion of the main pillar sandwiched between the source and drain diffused layers and made from the first-conduction-type material, and a front gate electrode that is formed on a lateral face of the main pillar while placing a gate insulating film therebetween. Moreover, a back gate electrode made from a second-conduction-type material is formed in a pillar shape penetrating from an upper portion to a lower portion on an inner side of the main pillar.

Owner:PS4 LUXCO SARL

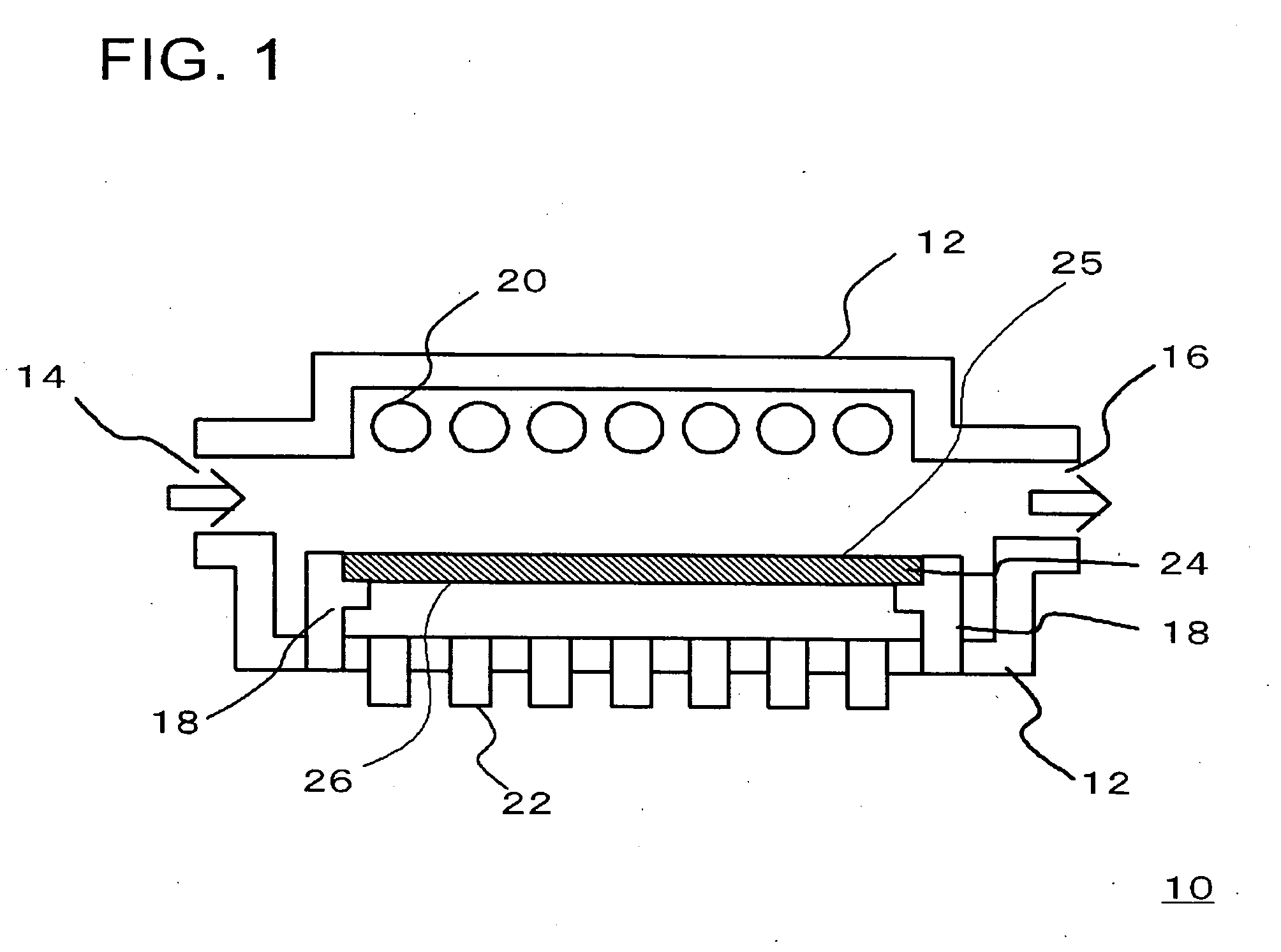

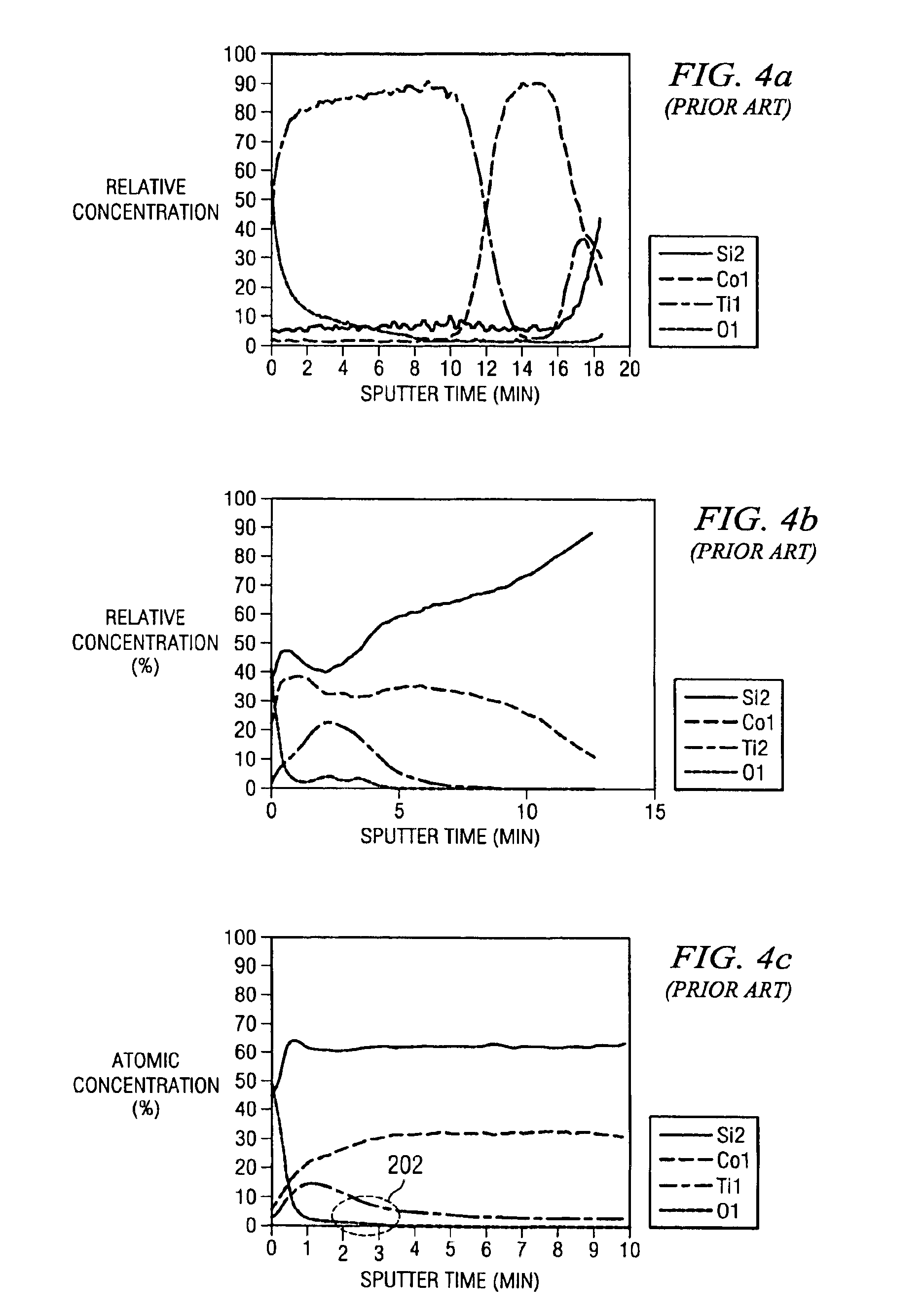

Method for manufacturing semiconductor device

ActiveUS20060240667A1Reduce sheet resistanceReduce the temperatureTransistorSemiconductor/solid-state device manufacturingDevice materialDevice form

Method for manufacturing a semiconductor device, includes: forming a layer of dicobalt monosilicide (Co2Si) or of cobalt (Co) on a device-forming surface of a silicon substrate in a sputter apparatus, by utilizing a predetermined temperature profile; elevating a temperature of the silicon substrate to a predetermined temperature T2, which is equal to or higher than 600° C., conducted after forming the layer of Co or Co2Si; and forming a layer of monocobalt monosilicide (CoSi) on the device-forming surface of the silicon substrate at a temperature equal to or higher than T2, conducted after heating the silicon substrate to T2, wherein, the silicon substrate is elevated to a temperature between a highest reachable temperature T1 of the silicon substrate during forming the layer of Co or Co2Si and the temperature T2 at a temperature ramp rate of equal to or higher than 50° C. / sec.

Owner:RENESAS ELECTRONICS CORP

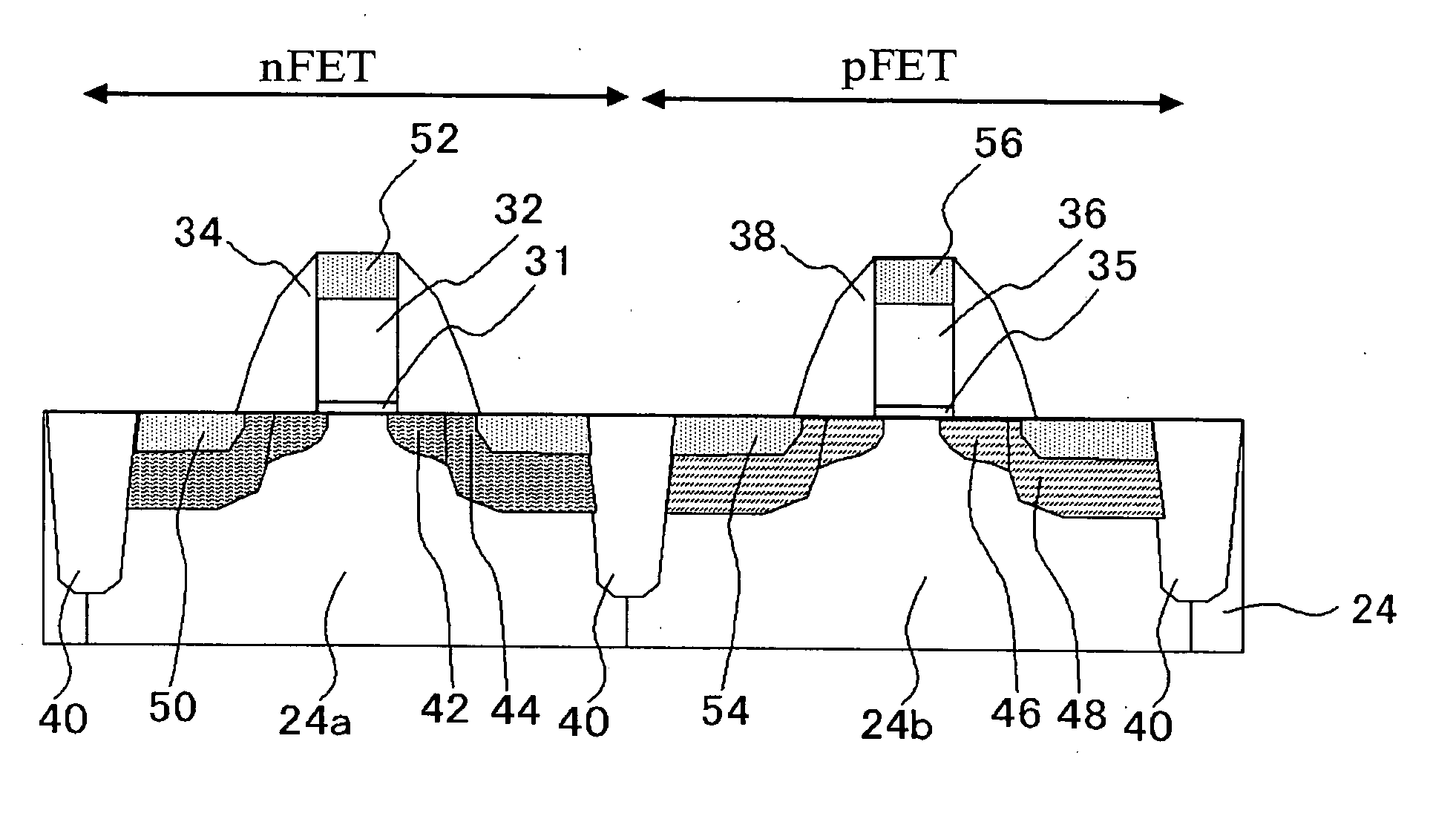

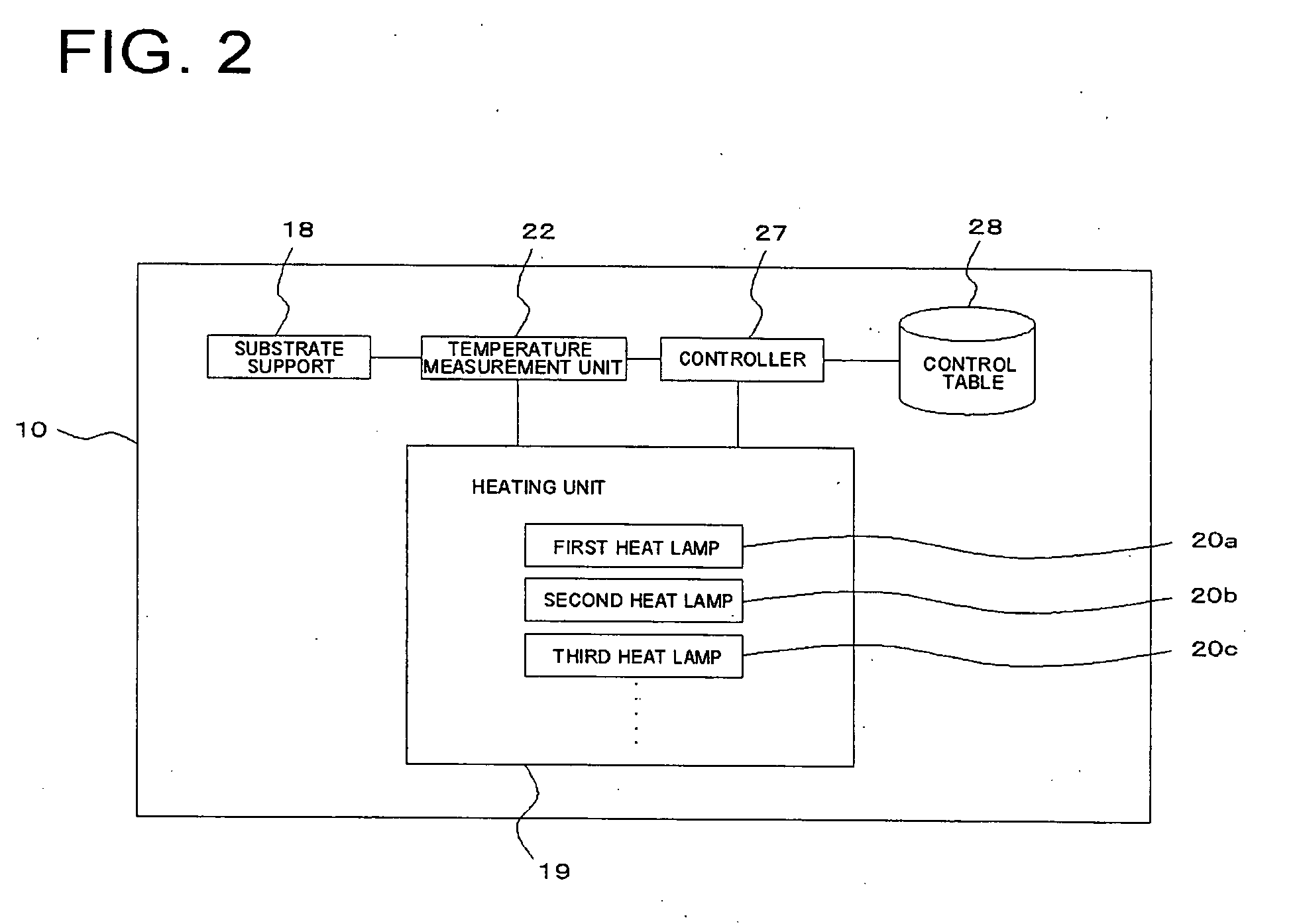

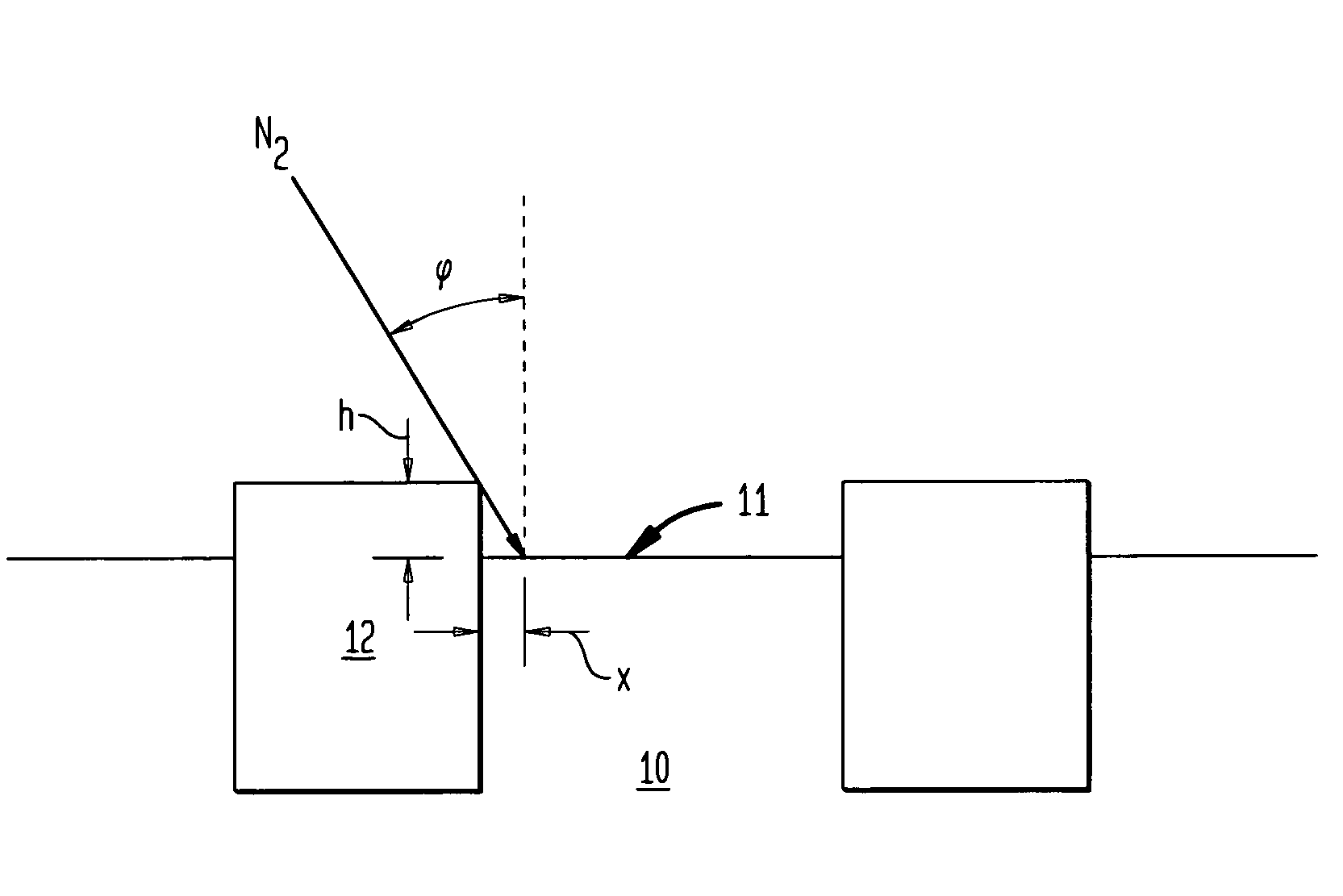

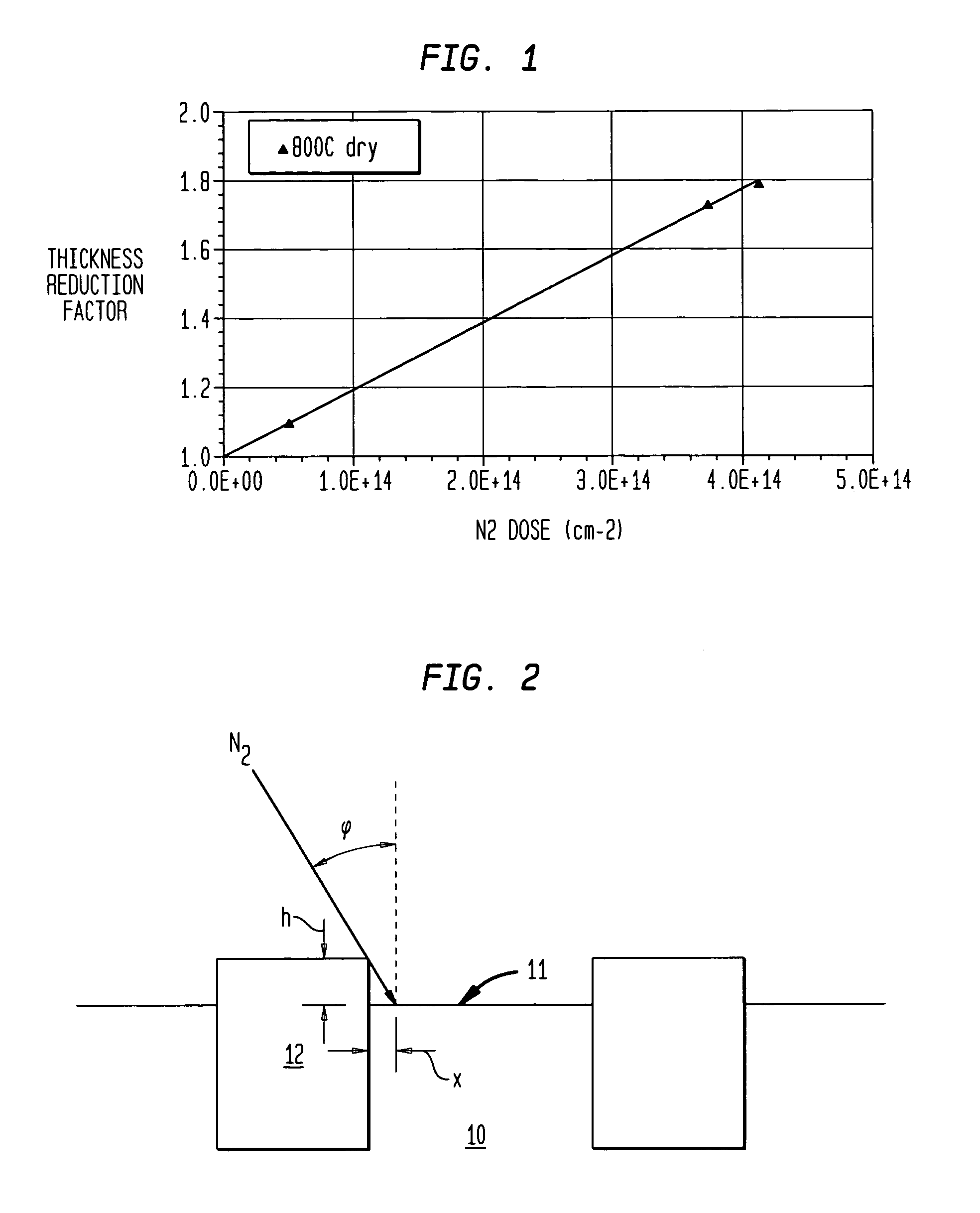

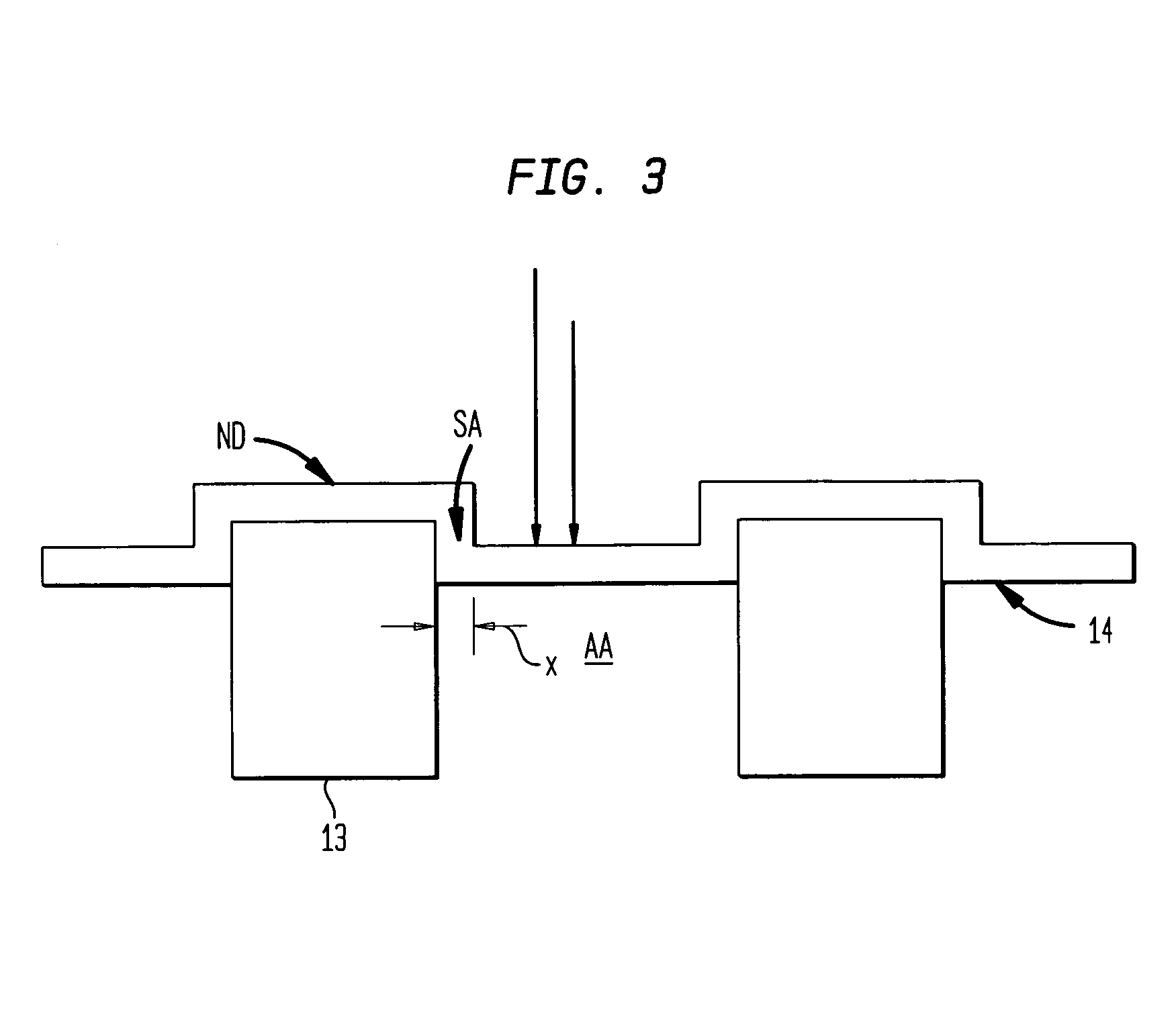

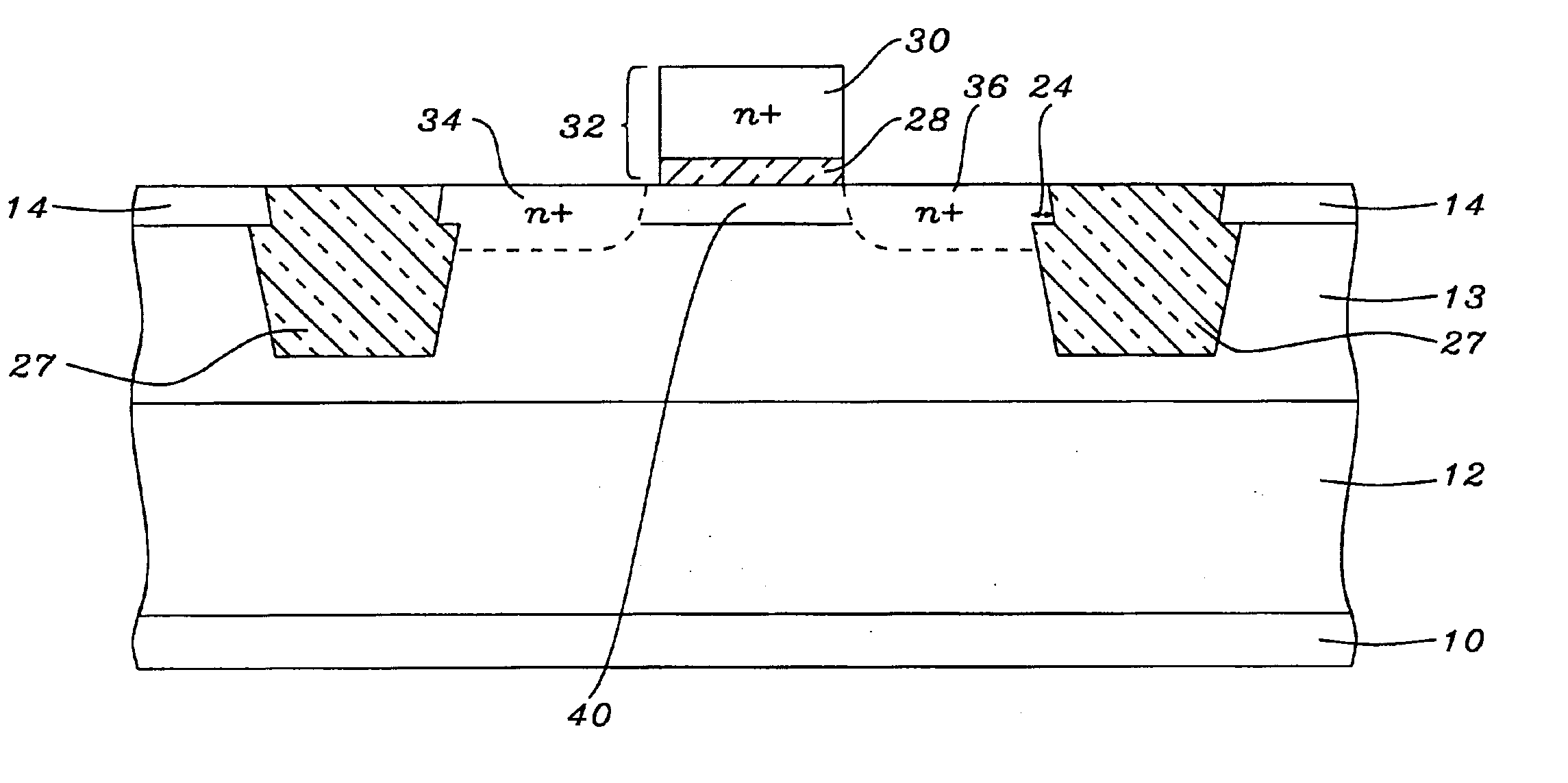

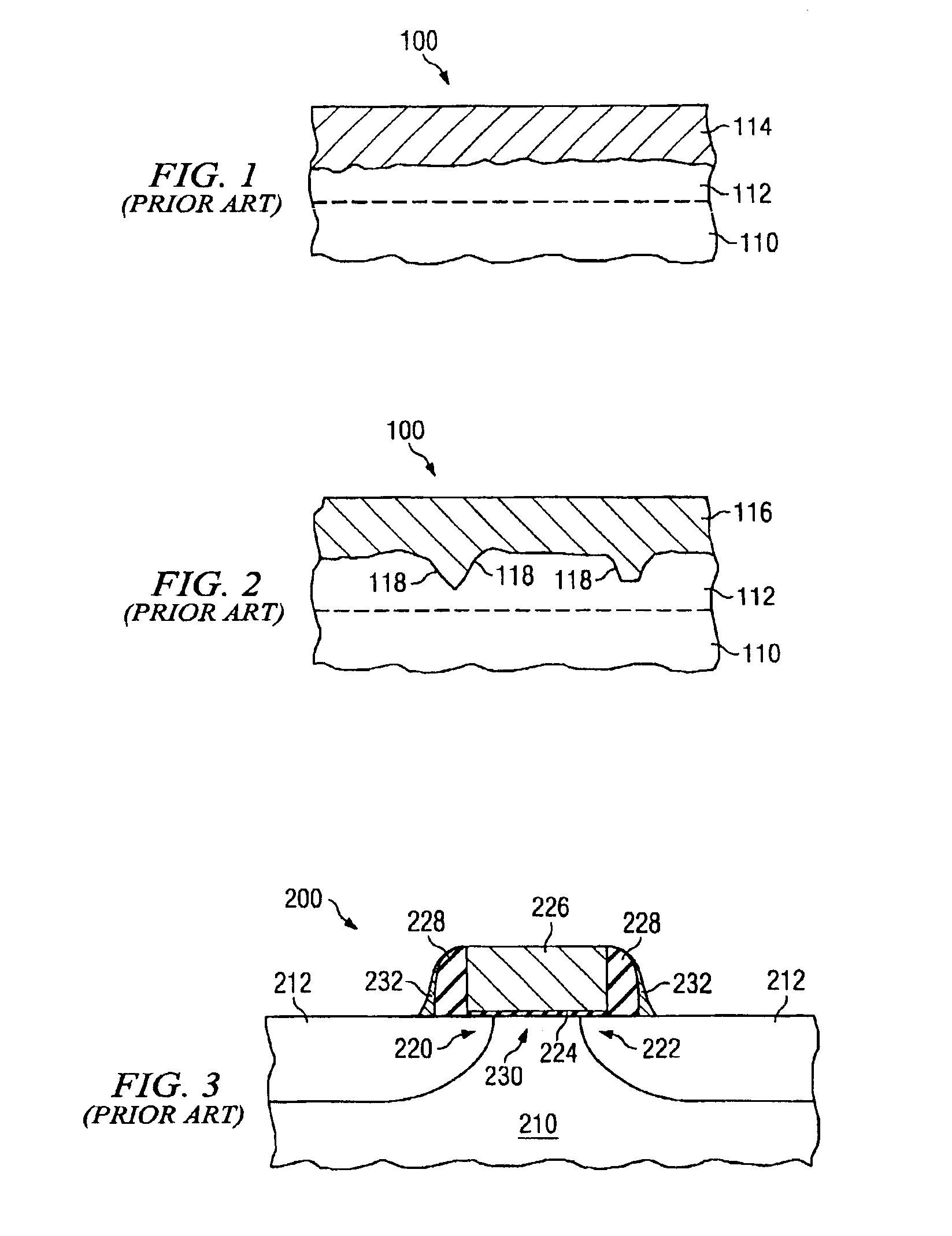

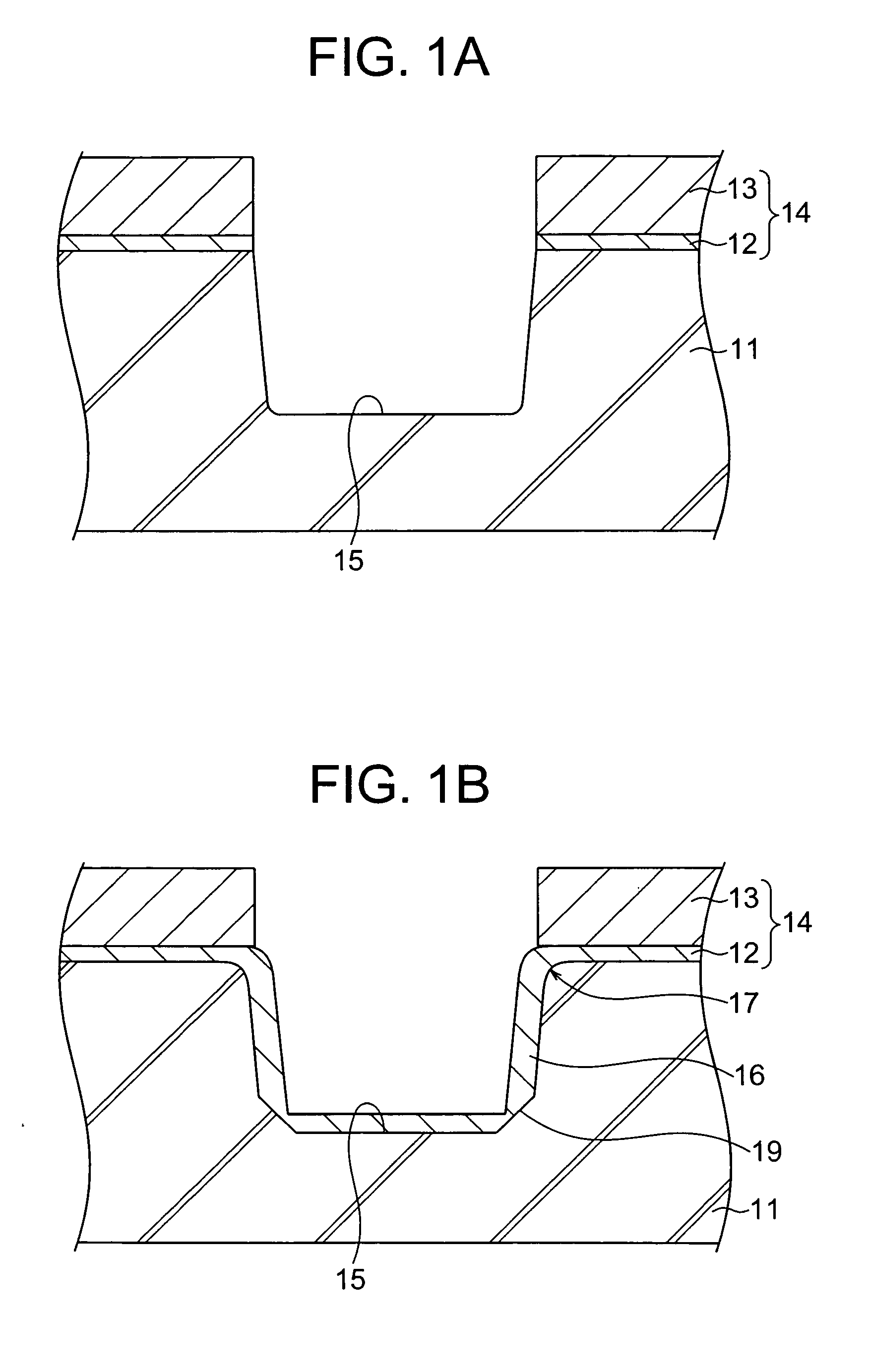

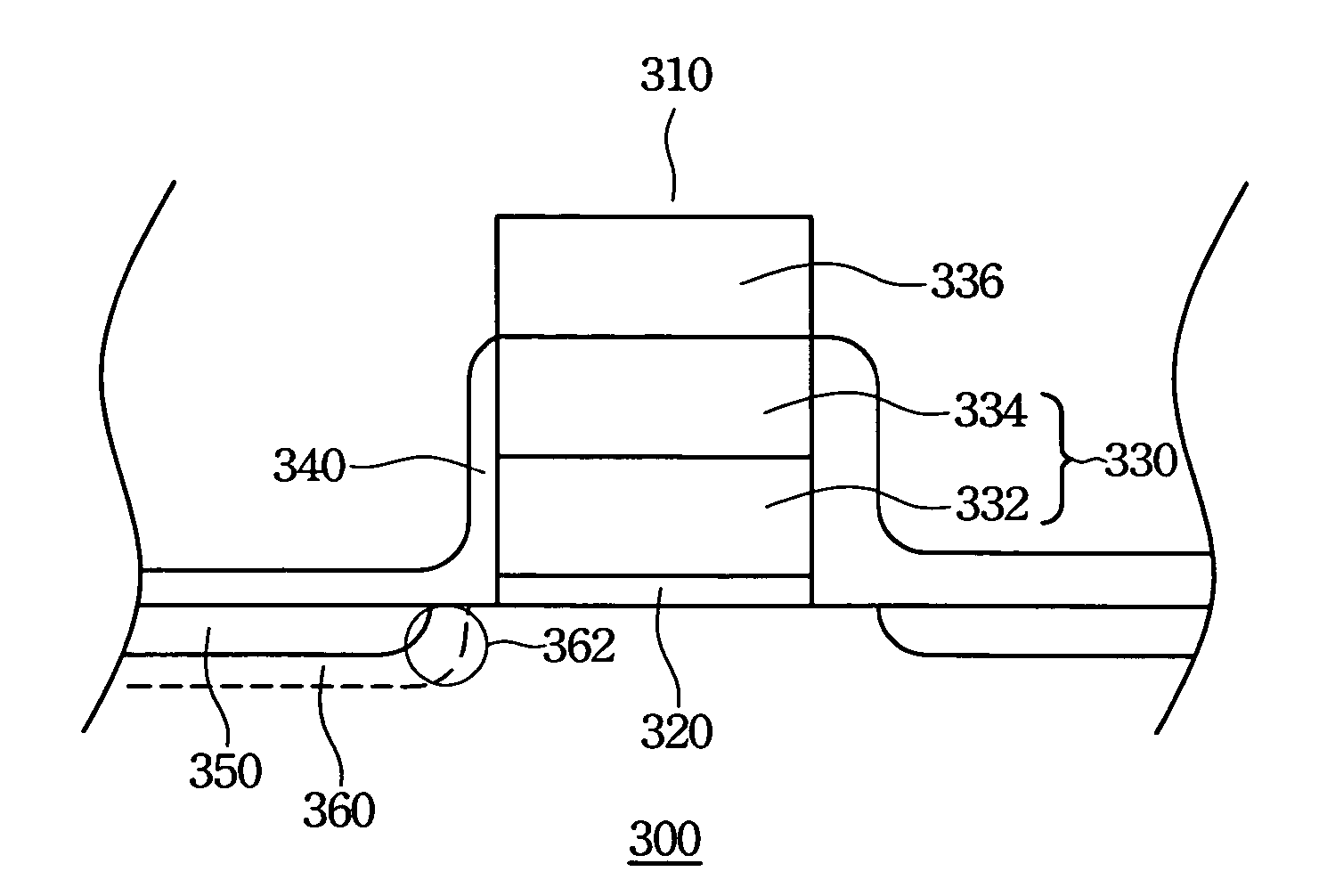

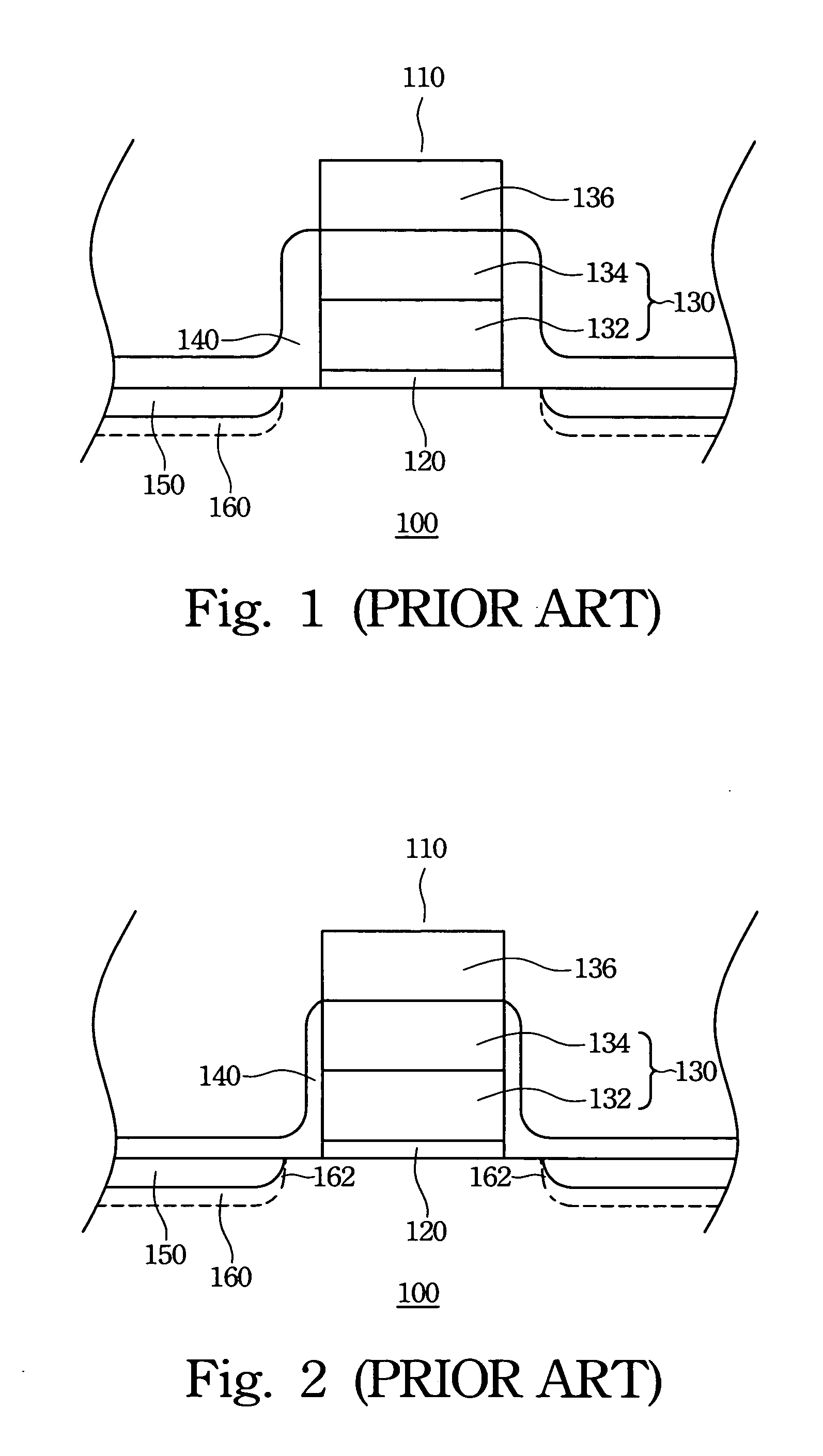

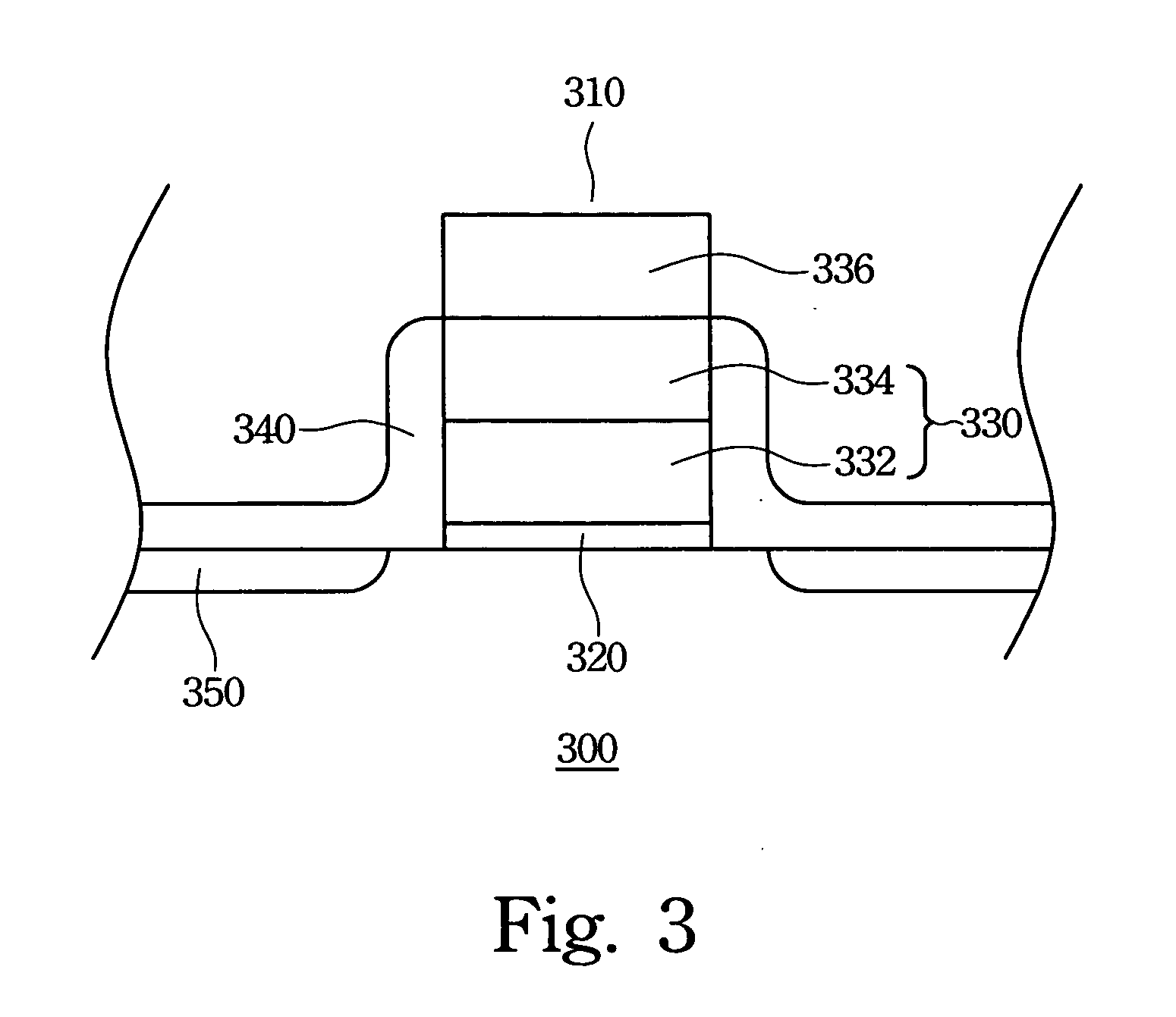

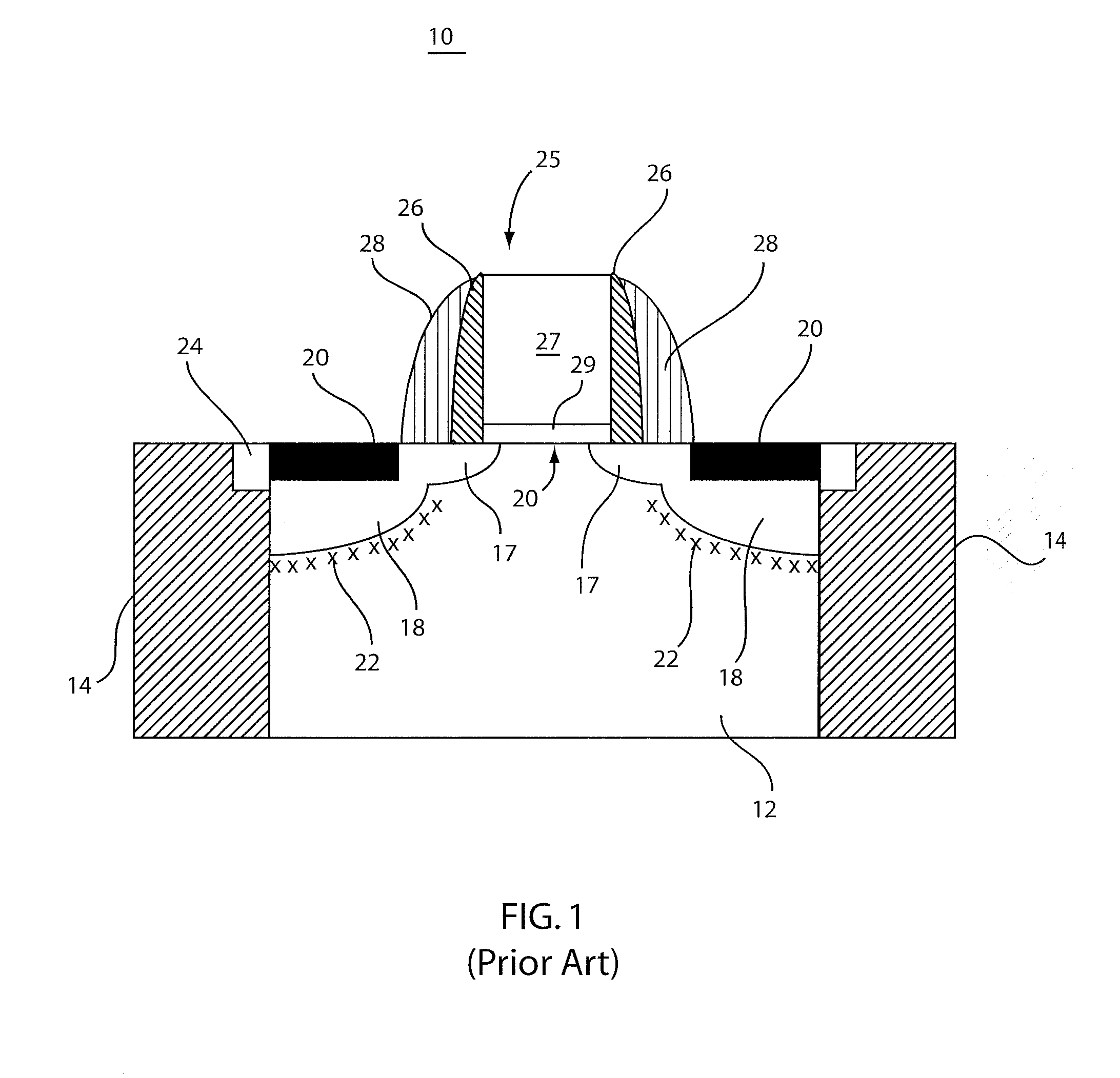

Nitrogen implantation using a shadow effect to control gate oxide thickness in DRAM semiconductor

Process for forming dual gate oxides for DRAMS by incorporating different thicknesses of gate oxides by using nitrogen implantation. Either angled nitrogen implantation or nitride spacers is used to create a “shadow effect” or area, which limits the nitrogen dose close to the edges of the active area. The reduction of nitrogen dose leads to an increased gate oxide thickness at the active area (AA) adjacent to the shallow trench, increases the threshold of the parasitic corner device and reduces sub Vt (threshold voltage) and junction leakage.

Owner:POLARIS INNOVATIONS LTD

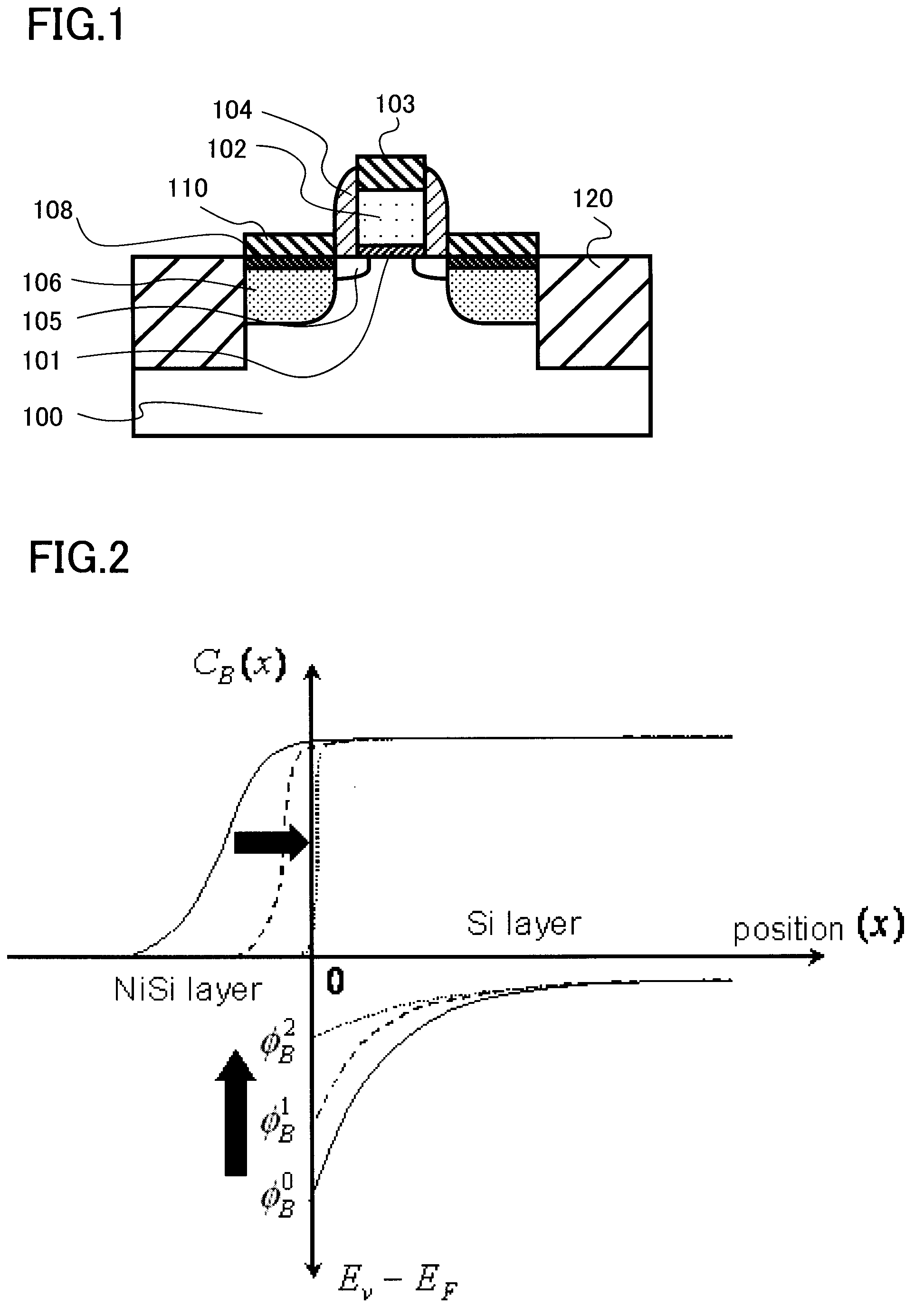

Method of fabricating semiconductor device and semiconductor device

InactiveUS20070298558A1Low resistance junction interfaceInhibitionTransistorSemiconductor/solid-state device manufacturingDevice materialSemiconductor

A semiconductor device includes a first semiconductor region of first type conductivity with a channel region being formed therein, a gate electrode insulatively formed above the channel region, a layer of SixGe1-x (0<x<1) on both sides of the channel region, a pair of second semiconductor regions of second type conductivity as formed on the SixGe1-x layer to have a controlled impurity concentration ranging from 1021 to 1022 atoms / cm3, and a nickel-containing silicide layer above the second semiconductor regions. A fabrication method of the semiconductor device is also disclosed.

Owner:KK TOSHIBA

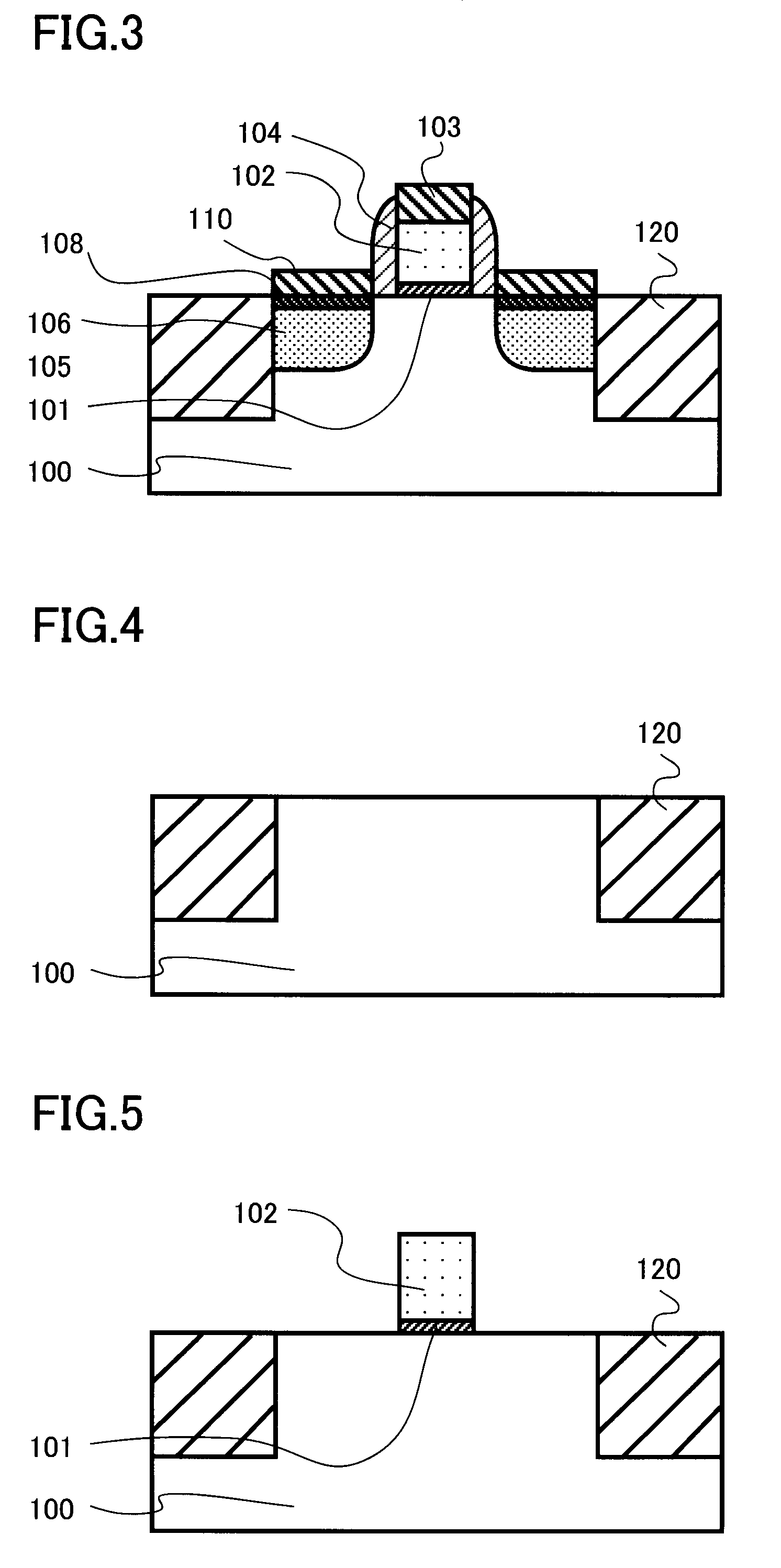

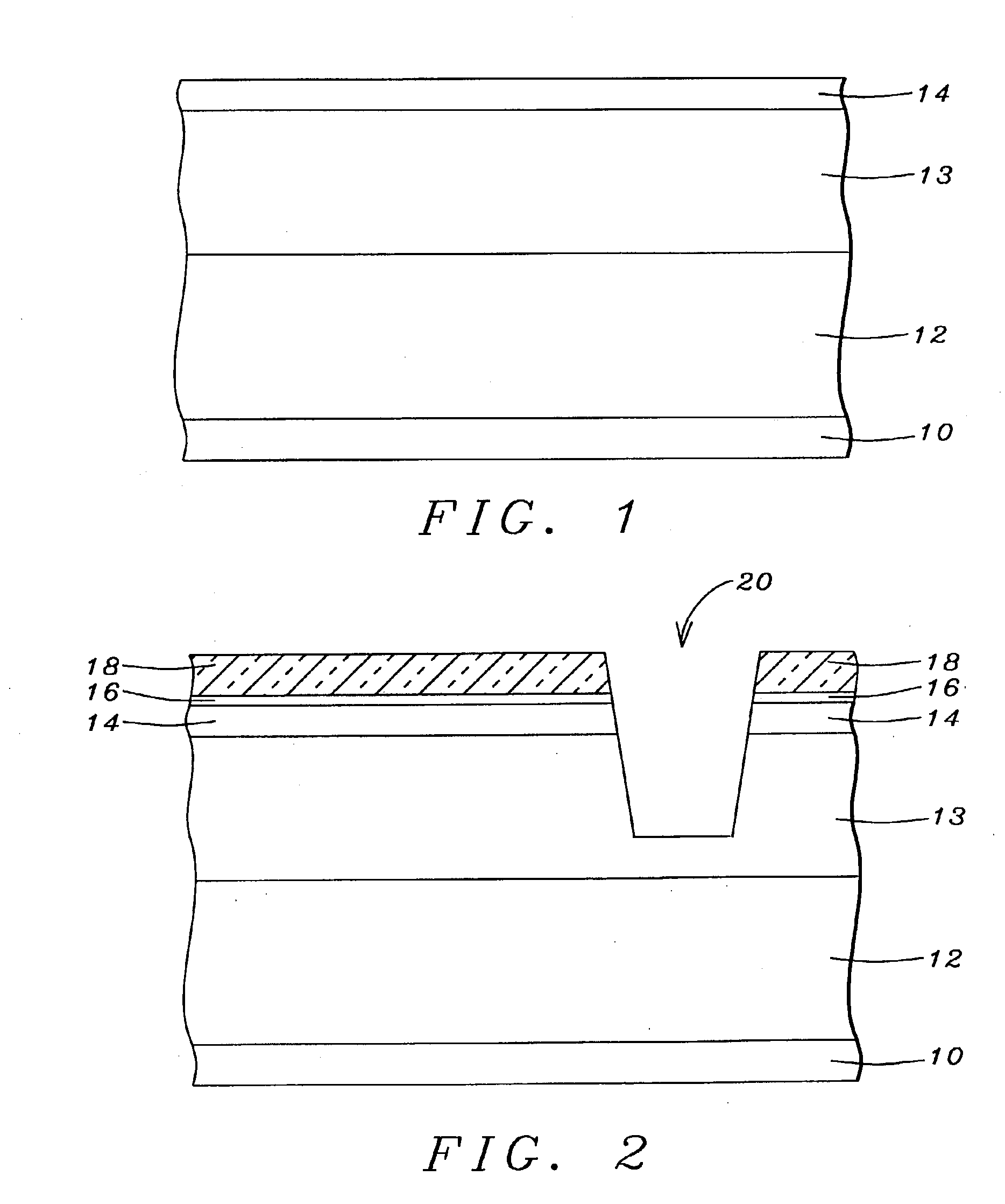

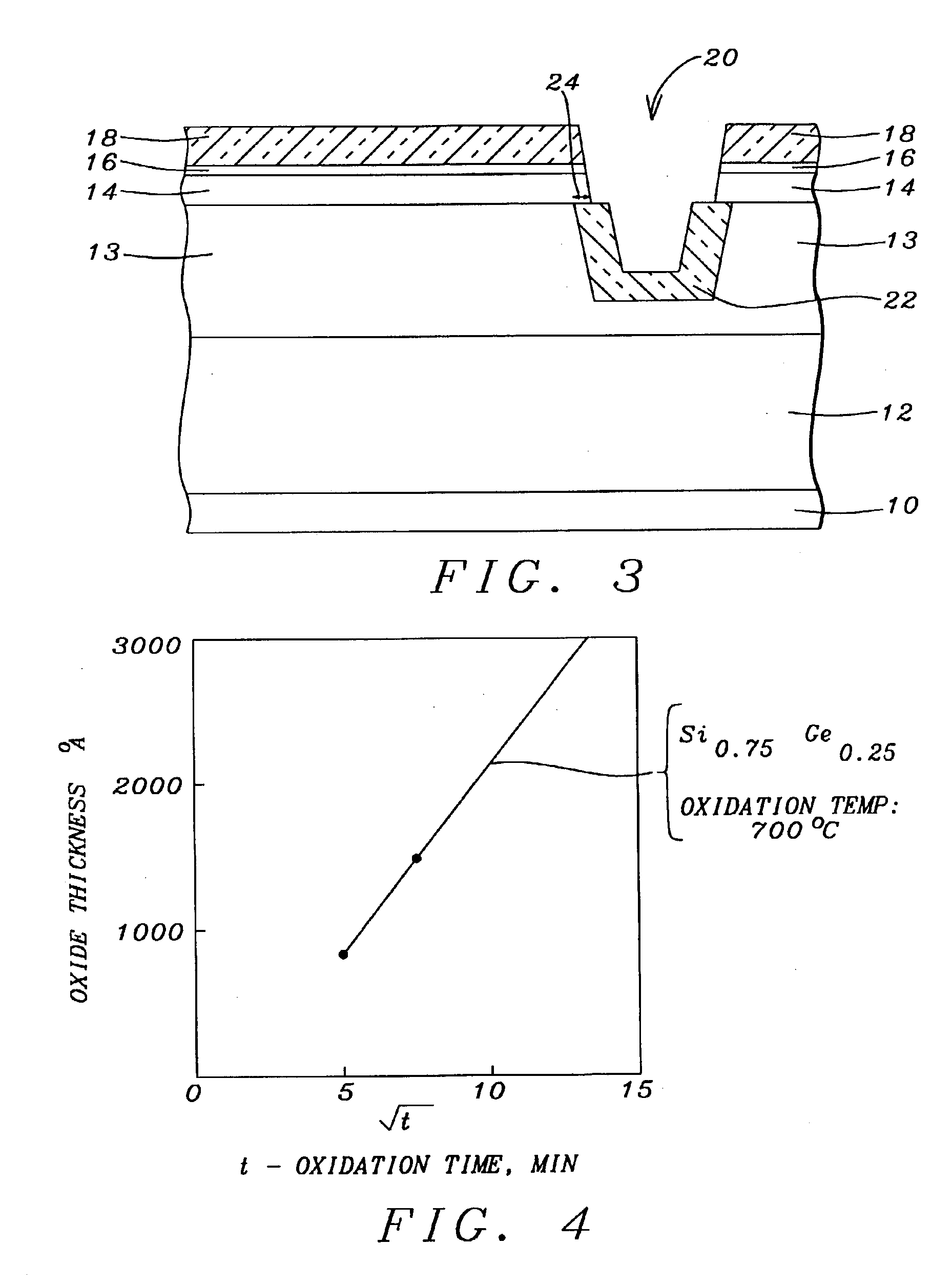

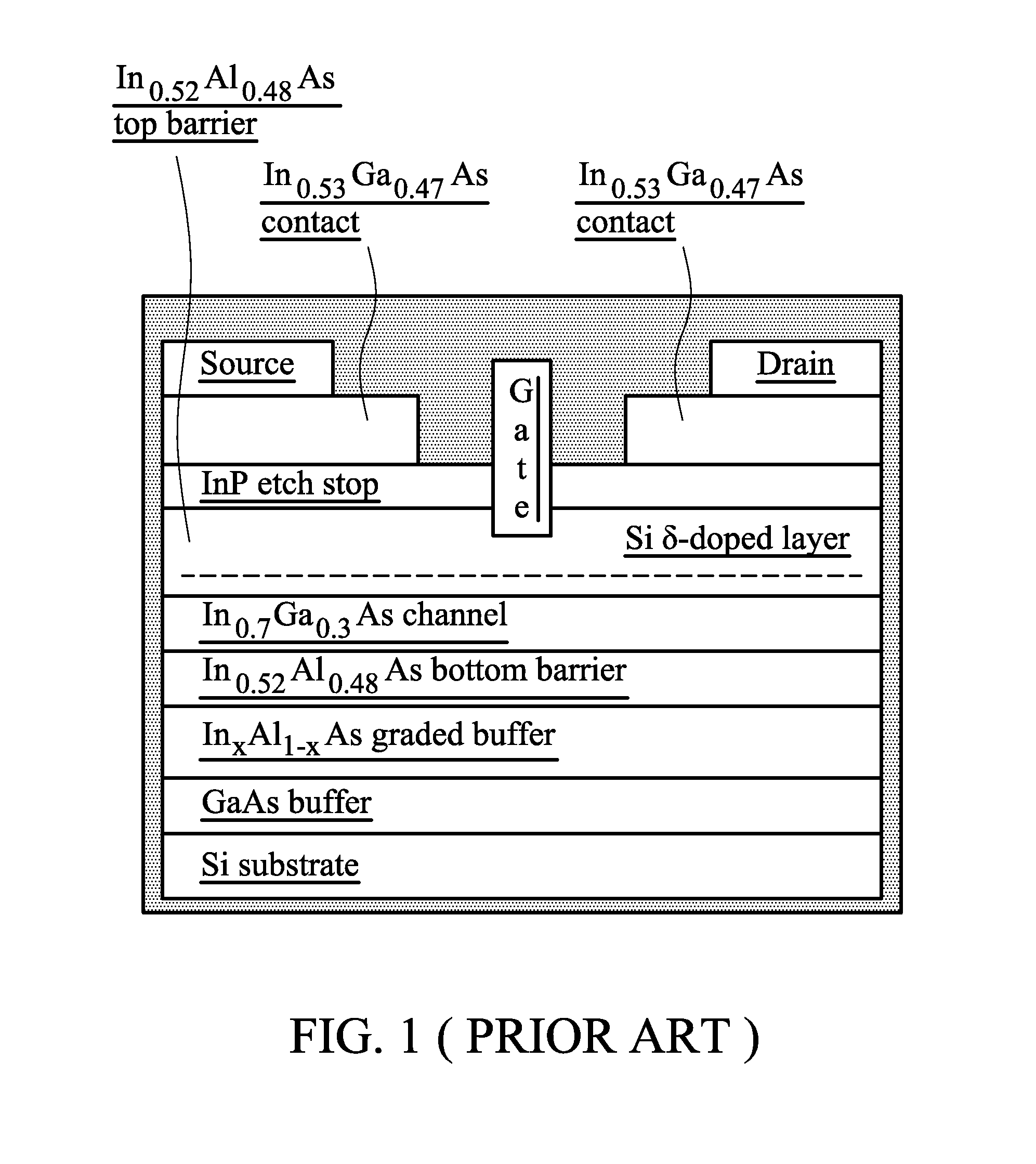

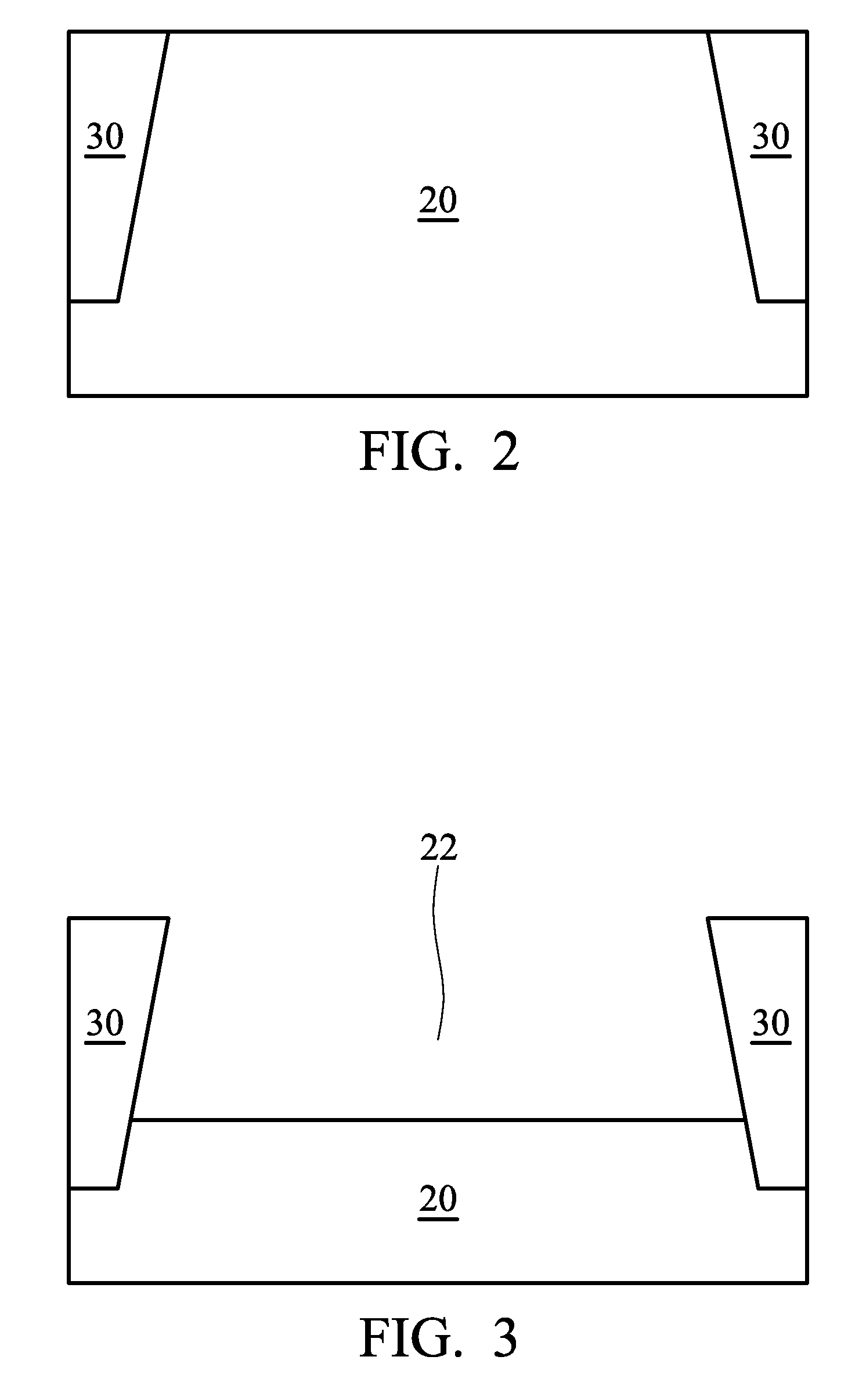

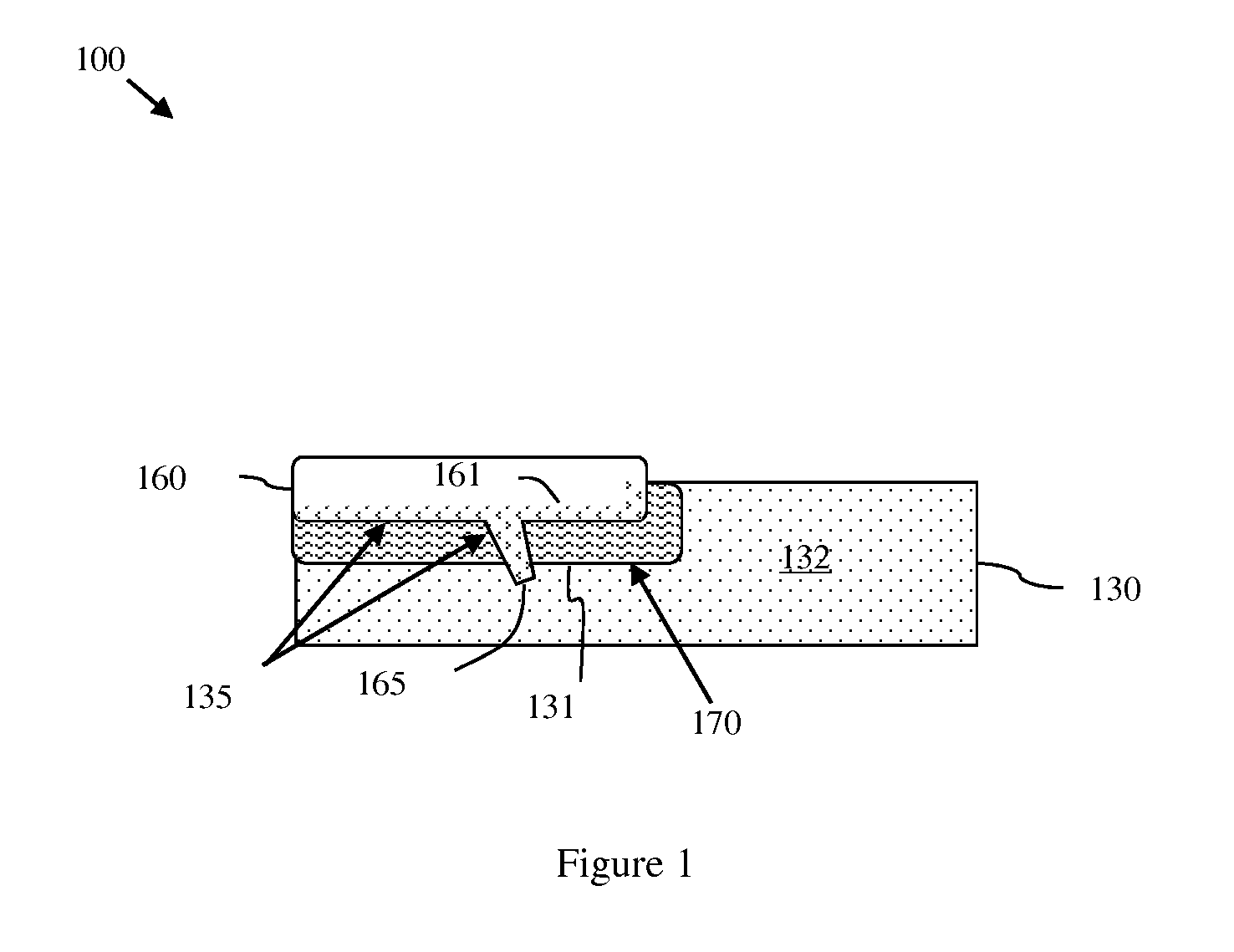

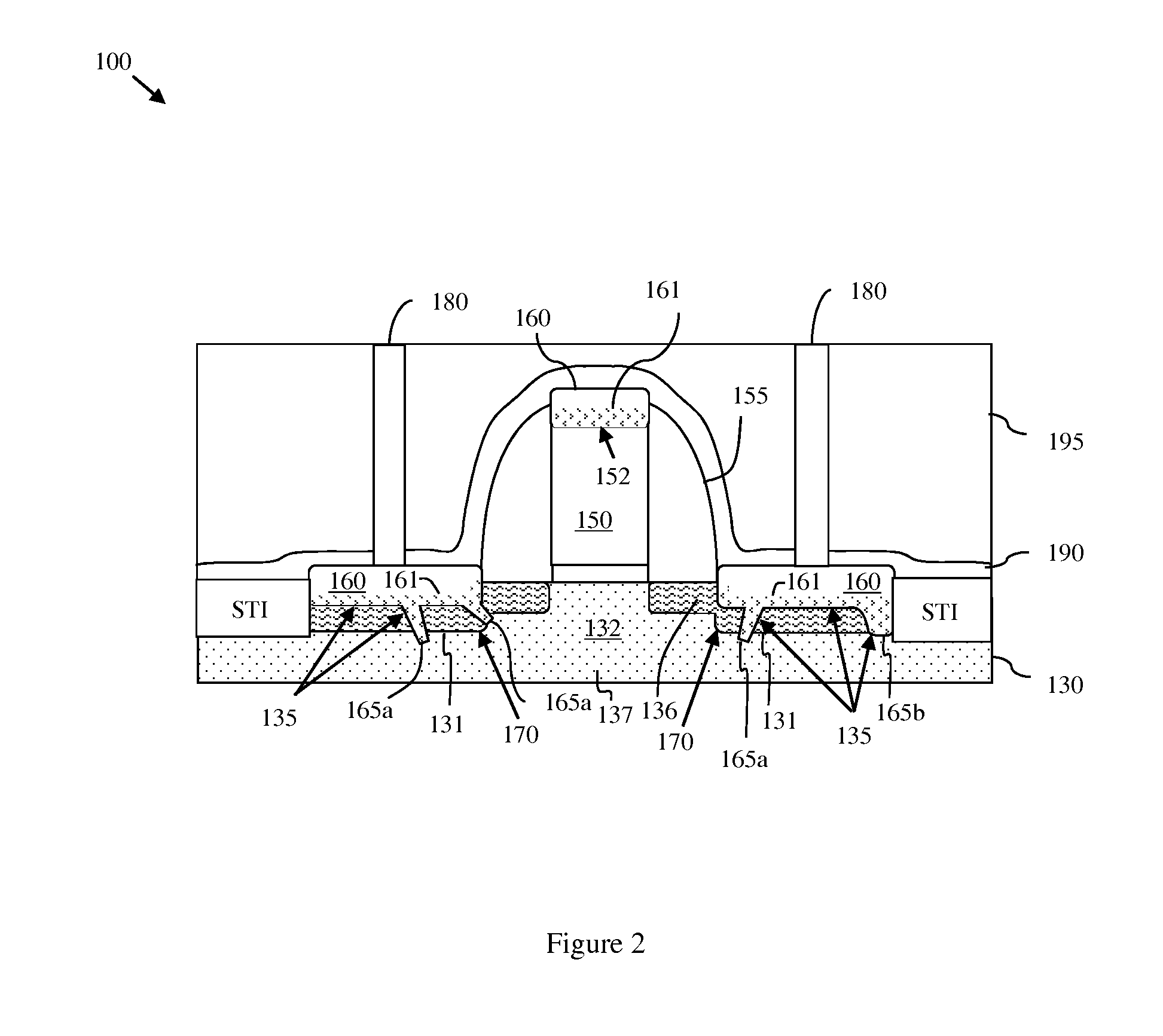

Method to reduce junction leakage current in strained silicon on silicon-germanium devices

InactiveUS6846720B2Reduce connection areaReduce junction leakageSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETJunction leakage

A MOSFET device in strained silicon-on-SiGe and a method of forming the device are described. The said device achieves reduced junction leakage due to the lower band-gap values of SiGe. The method consists of forming isolation trenches in a composite strained-Si / SiGe substrate and growing a liner oxide by wet oxidation such that oxidation is selective to SiGe only, with negligible oxidation of silicon surfaces. Selective oxidation results in oxide encroachment under strained-Si, thereby reducing the junction area after device fabrication is completed. Reduced junction area leads to reduced n+ / p or p+ / n junction leakage current.

Owner:AGENCY FOR SCI TECH & RES

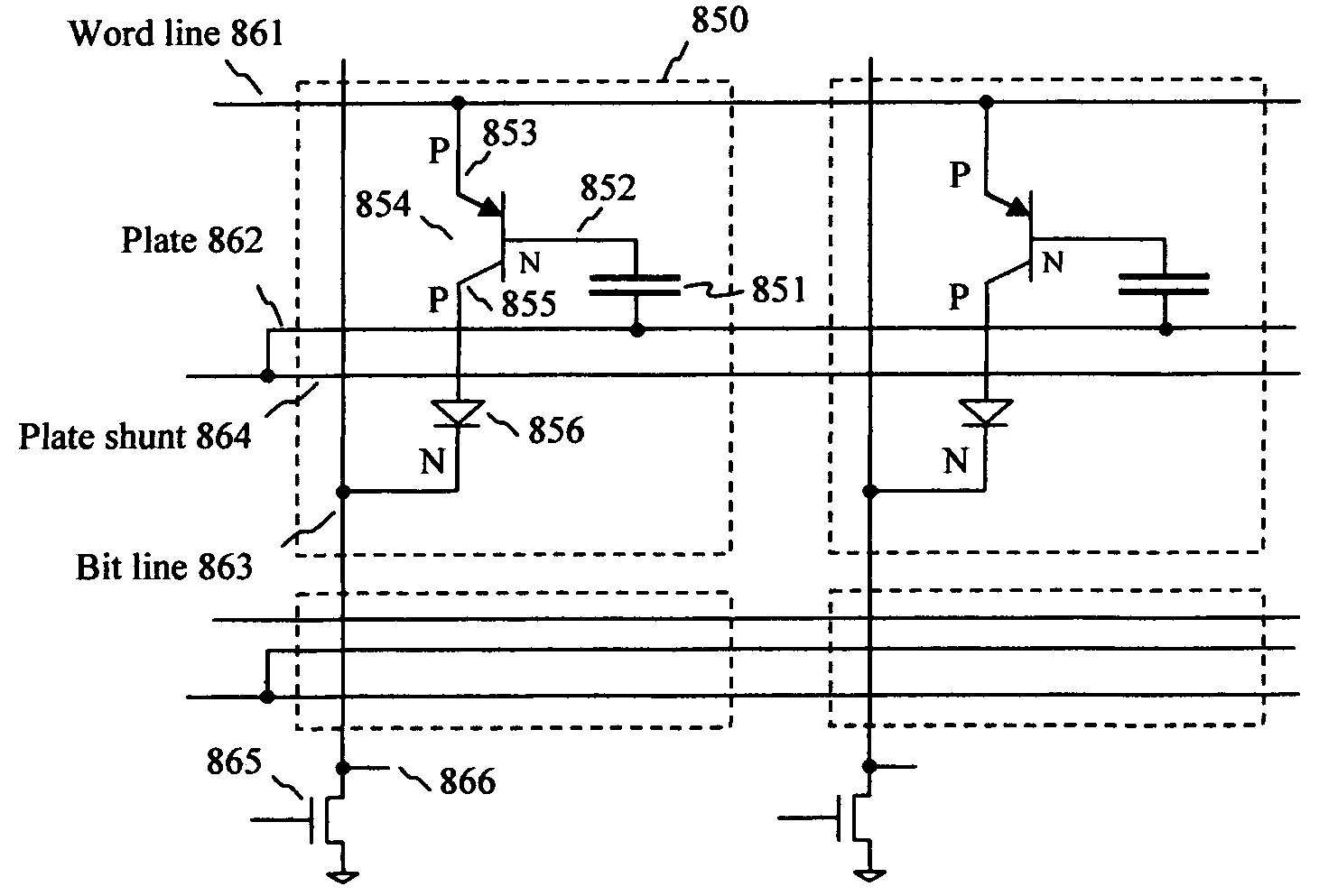

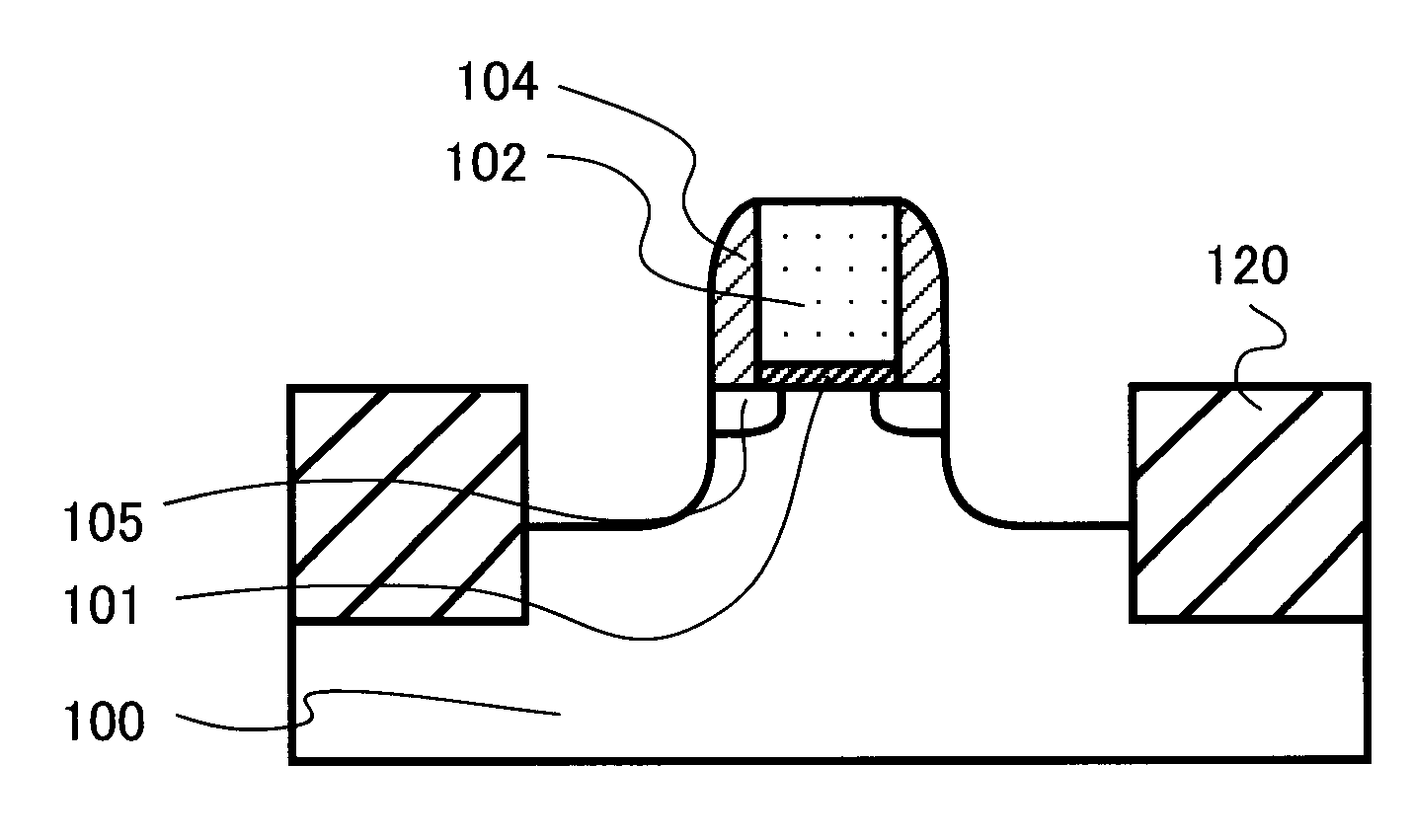

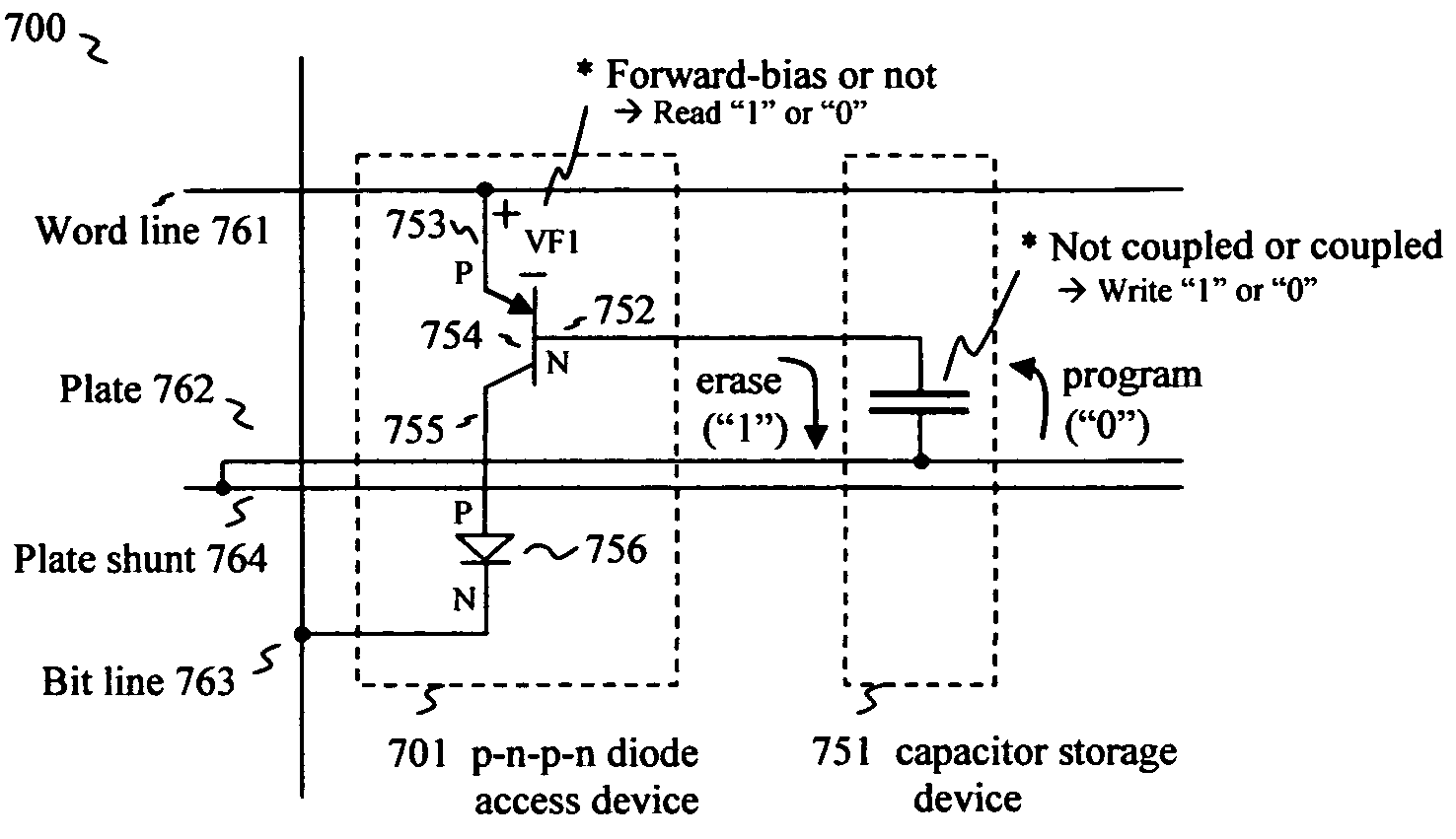

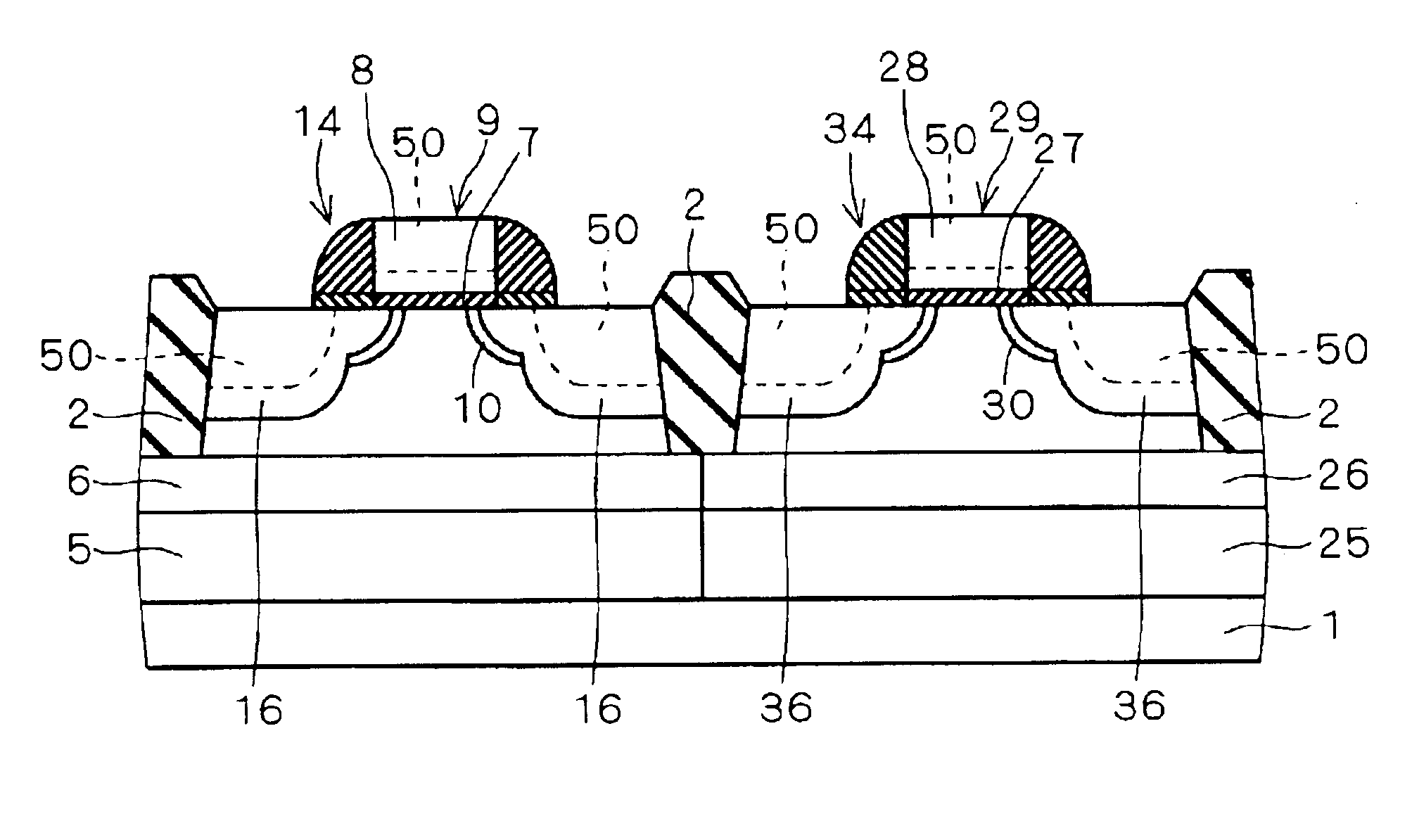

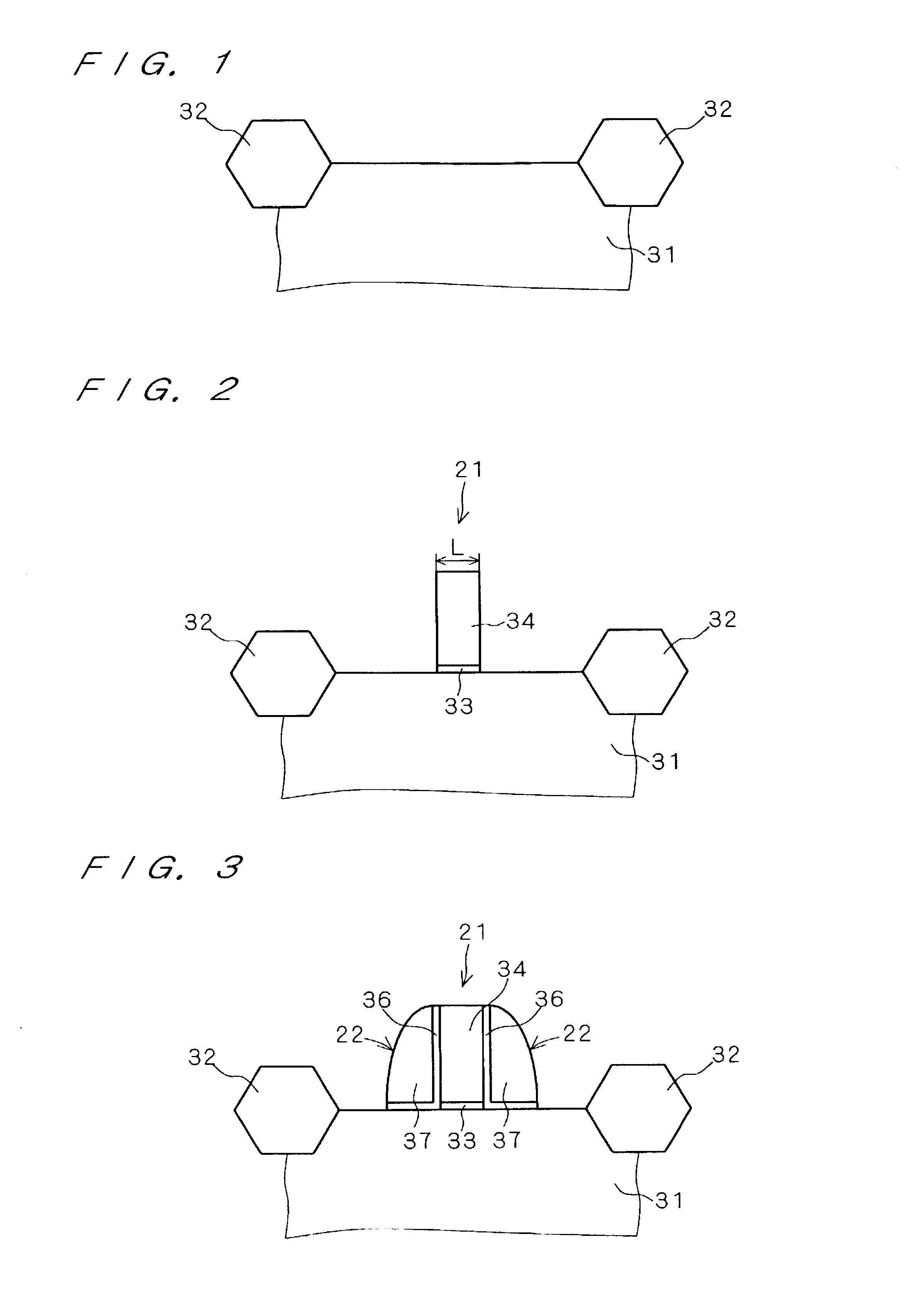

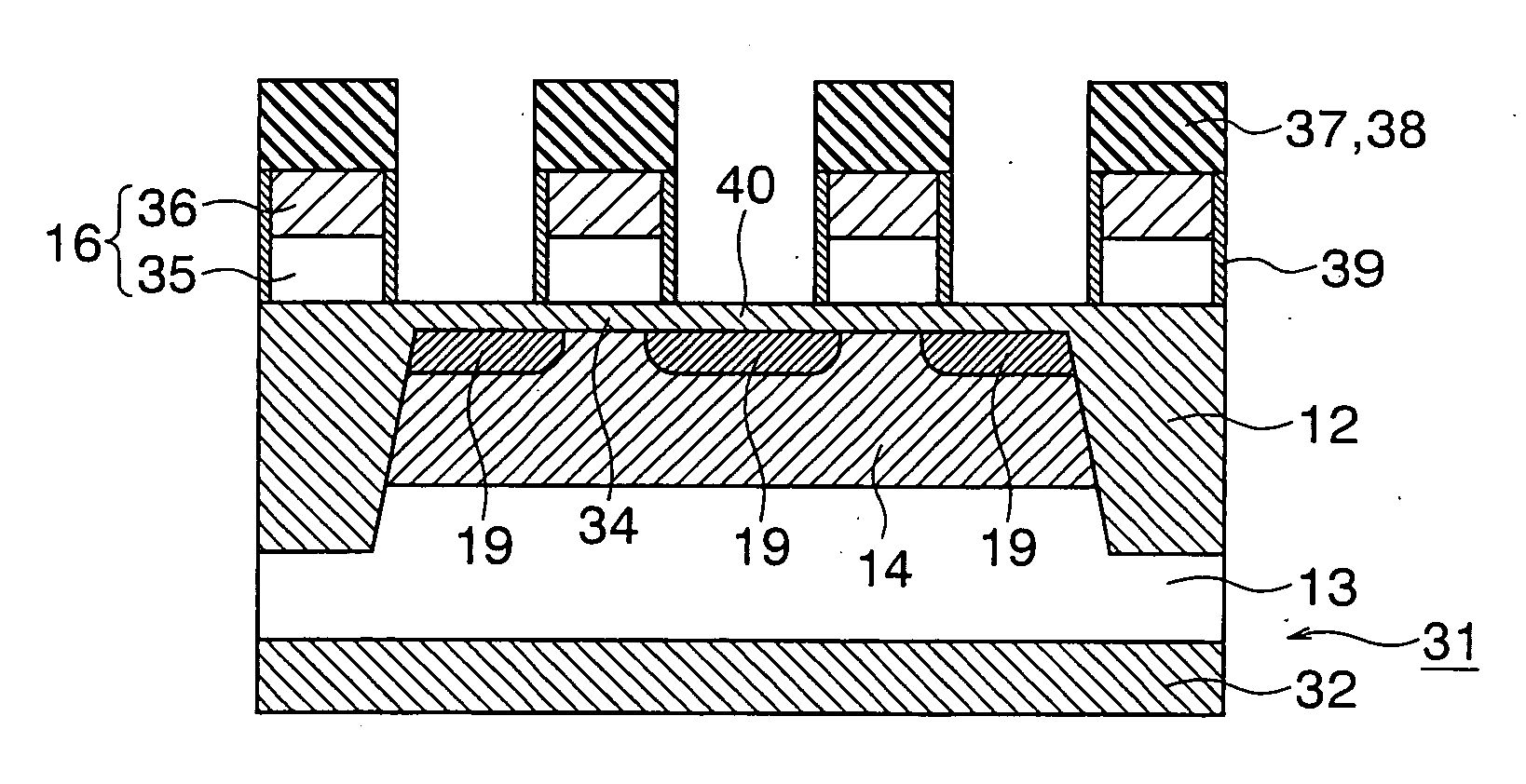

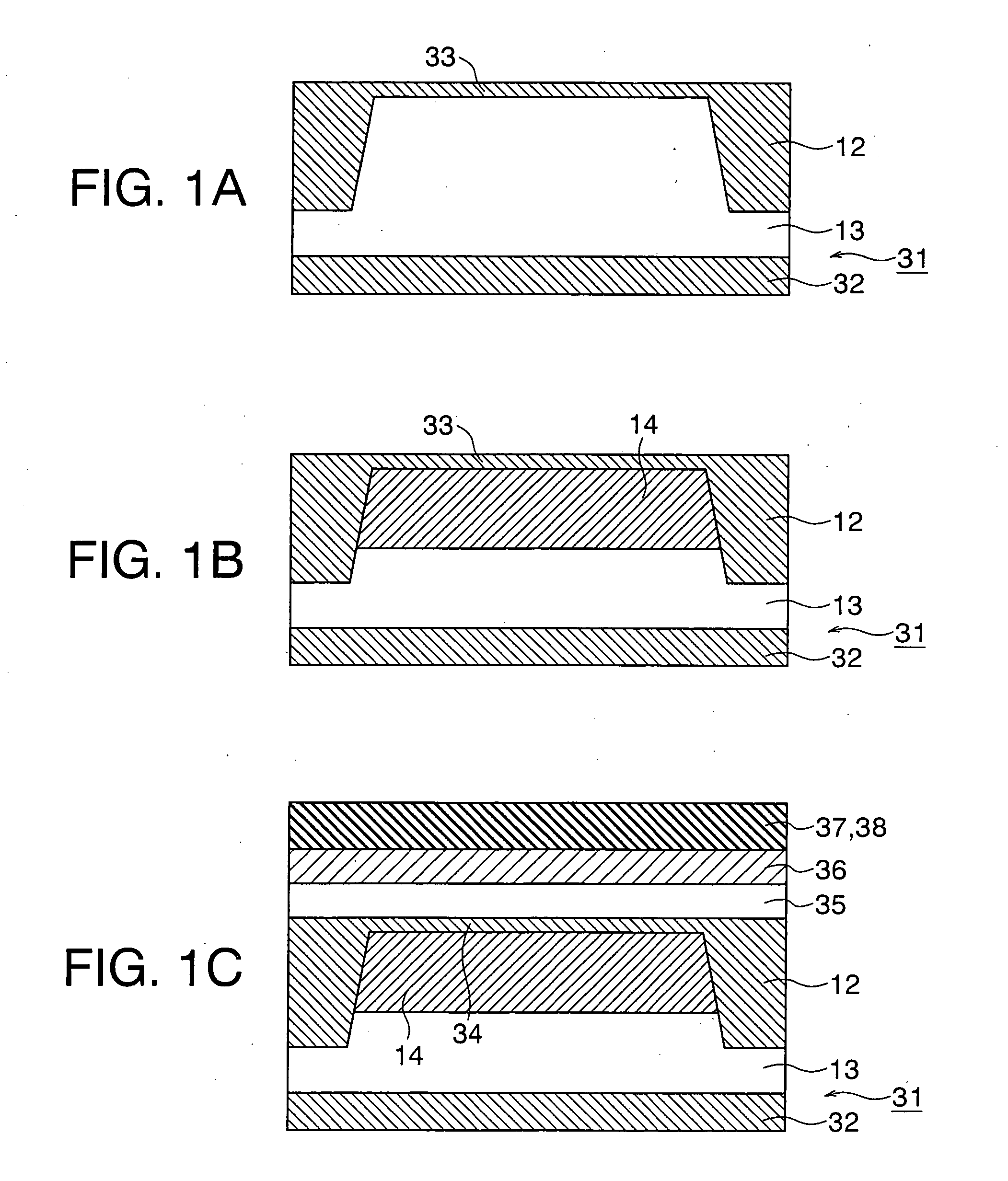

Vertical capacitor memory cell and its applications

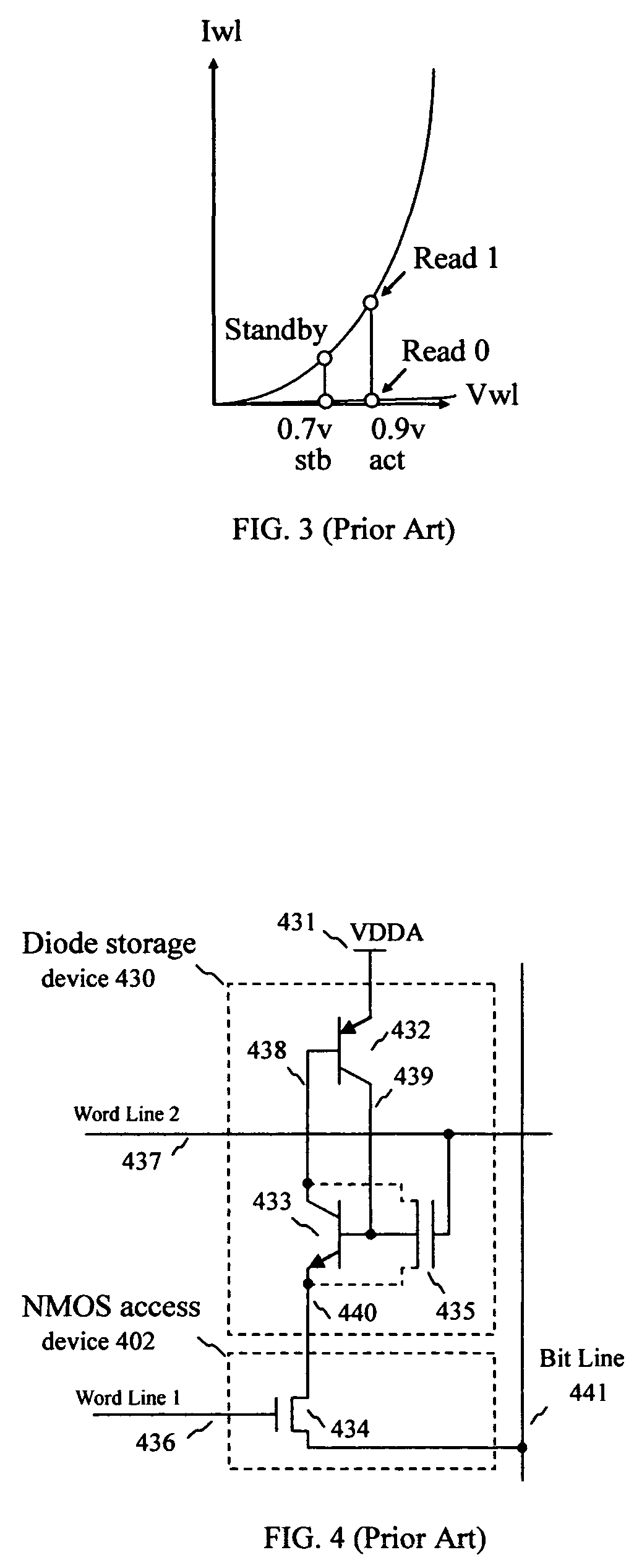

InactiveUS7196926B1Less complicated to fabricateImprove performanceTransistorSolid-state devicesCapacitanceBit line

A capacitor memory is realized, wherein a capacitor stores data and a diode controls to store data “1” or “0”. Diode has four terminals wherein first terminal serves as word line, second terminal serves as storage node, third terminal is floating, fourth terminal serves as bit line, at least one of the terminals is formed vertically, which diode is formed from silicon, metal or compound materials. The cell is isolated from well or substrate, and the height of cell is close to that of control circuit. A capacitor plate couples to second terminal, which plate has no coupling region to first, third and fourth terminal. With no coupling, the inversion layer of plate in the storage node is isolated from the adjacent nodes. In doing so, the plate can swing ground level to positive supply level to write. As a result, no negative generator is required for controlling plate. Word line and bit line keep ground level during standby, and rise to supply level for read or write operation. In this manner, no holding current is required during standby, and operating current is dramatically reduced with no negative generator. Write has a sequence to clear the state of cell before writing to store data regardless of previous state. Refresh cycle is periodically asserted to sustain data. The present invention can be applied for destructive read, or for nondestructive read adding pull-down device to bit line.

Owner:KIM JUHAN

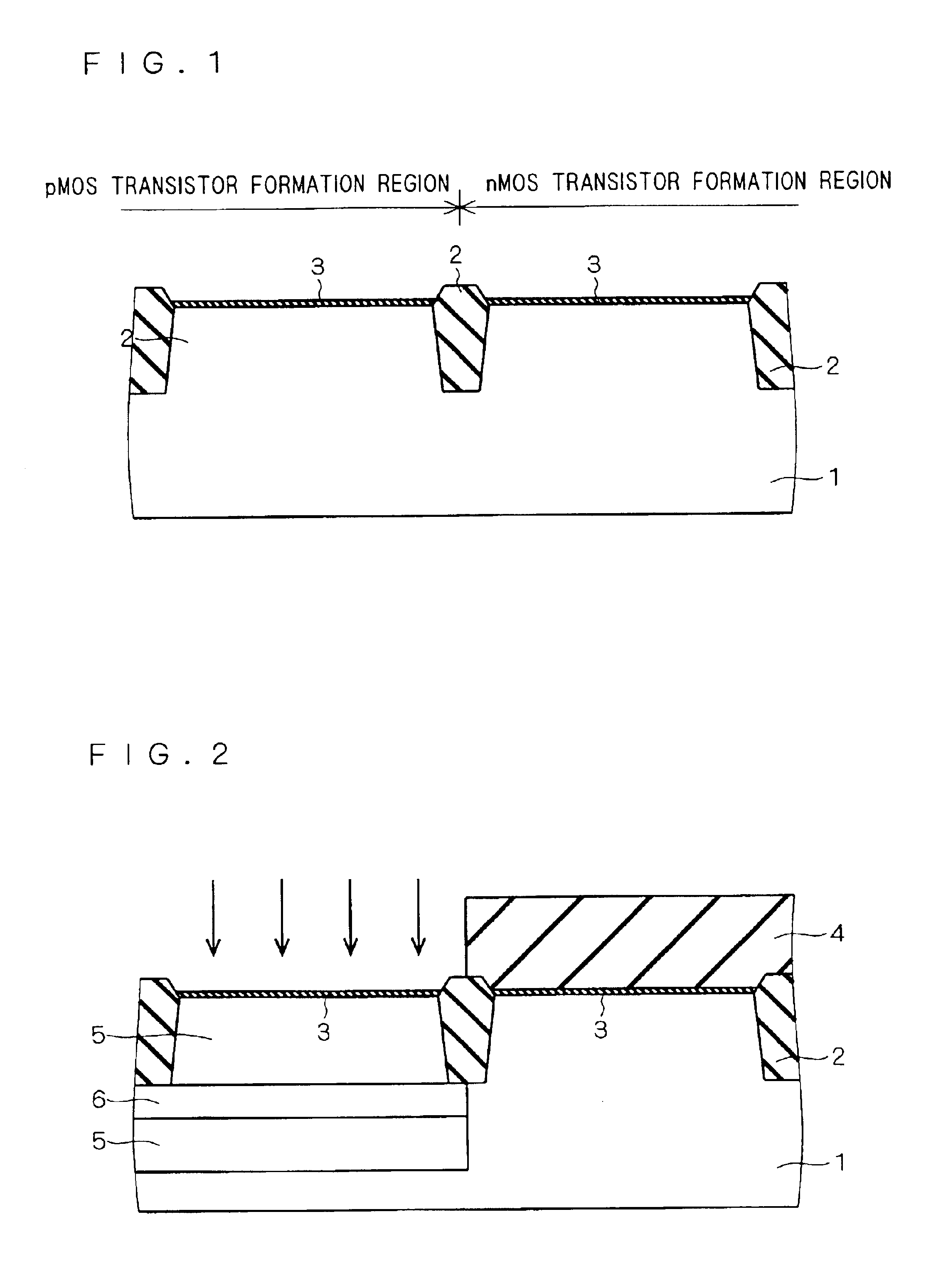

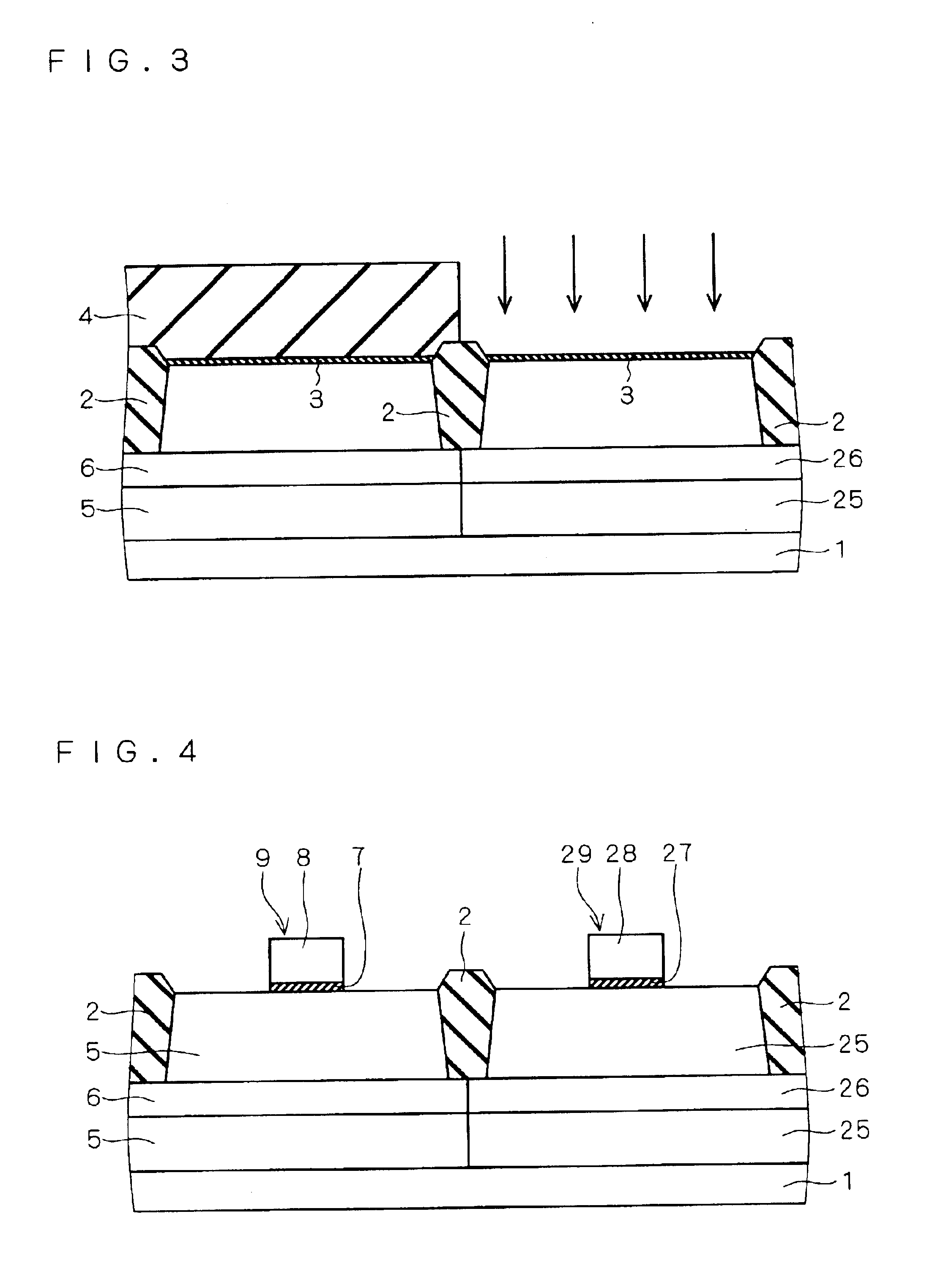

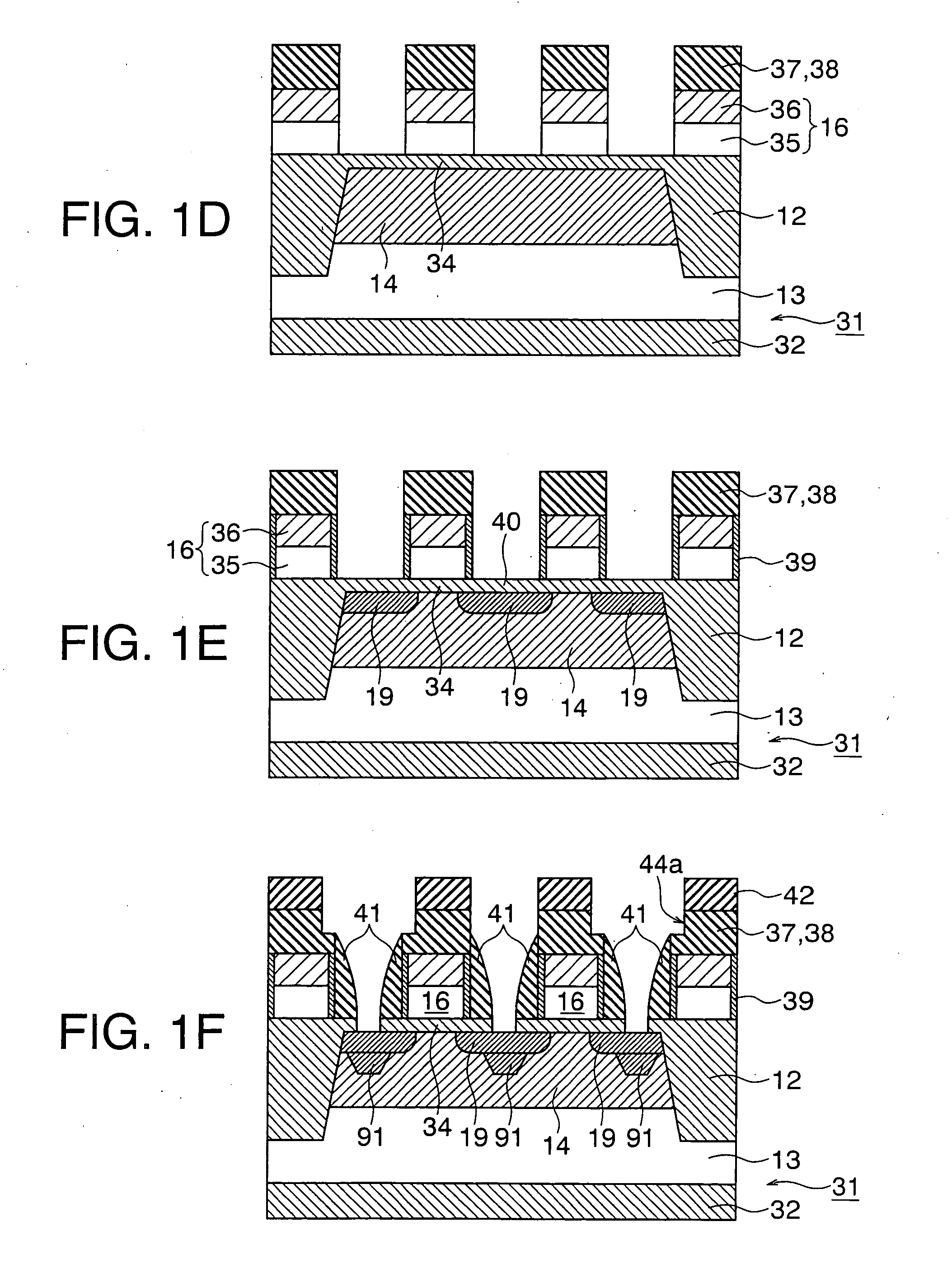

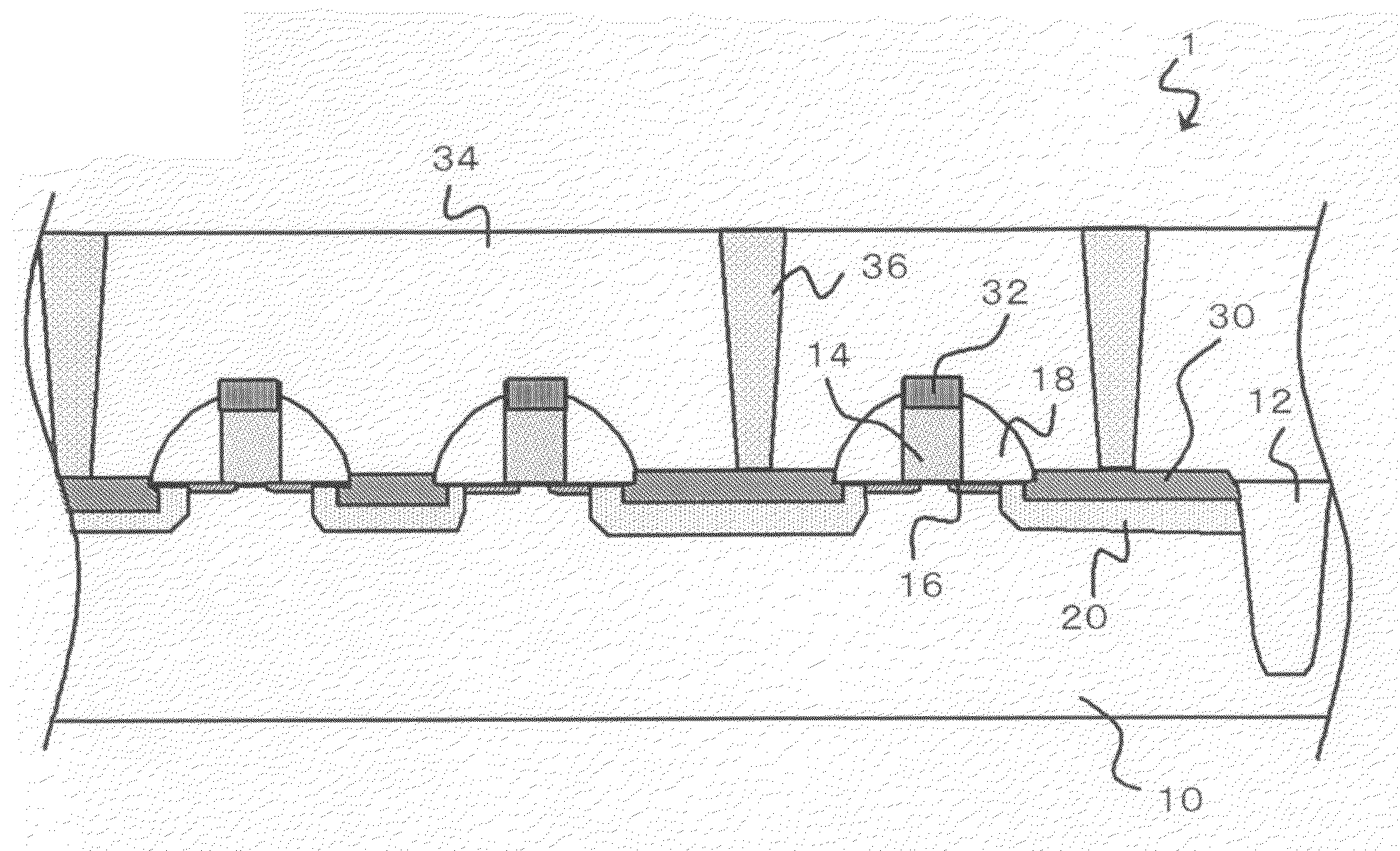

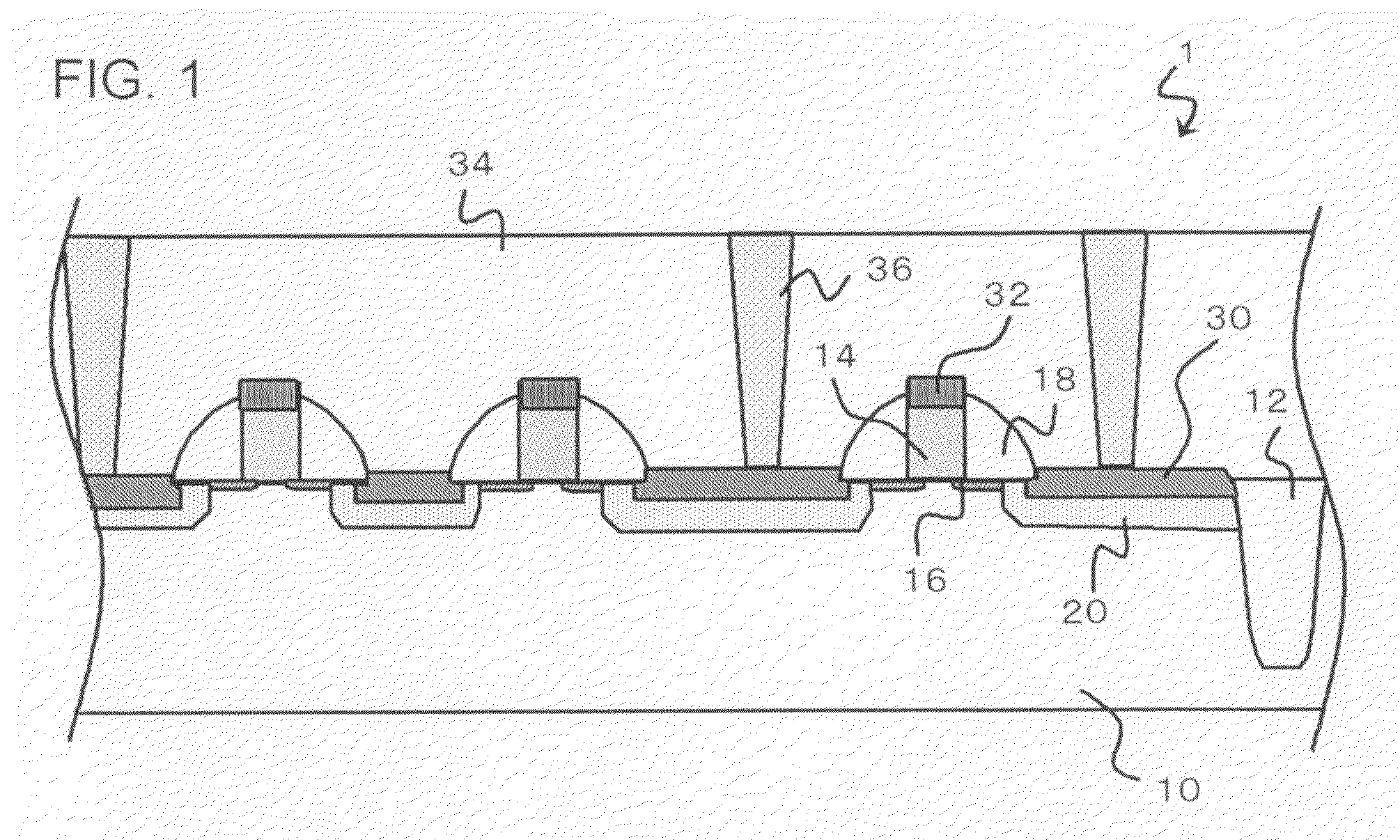

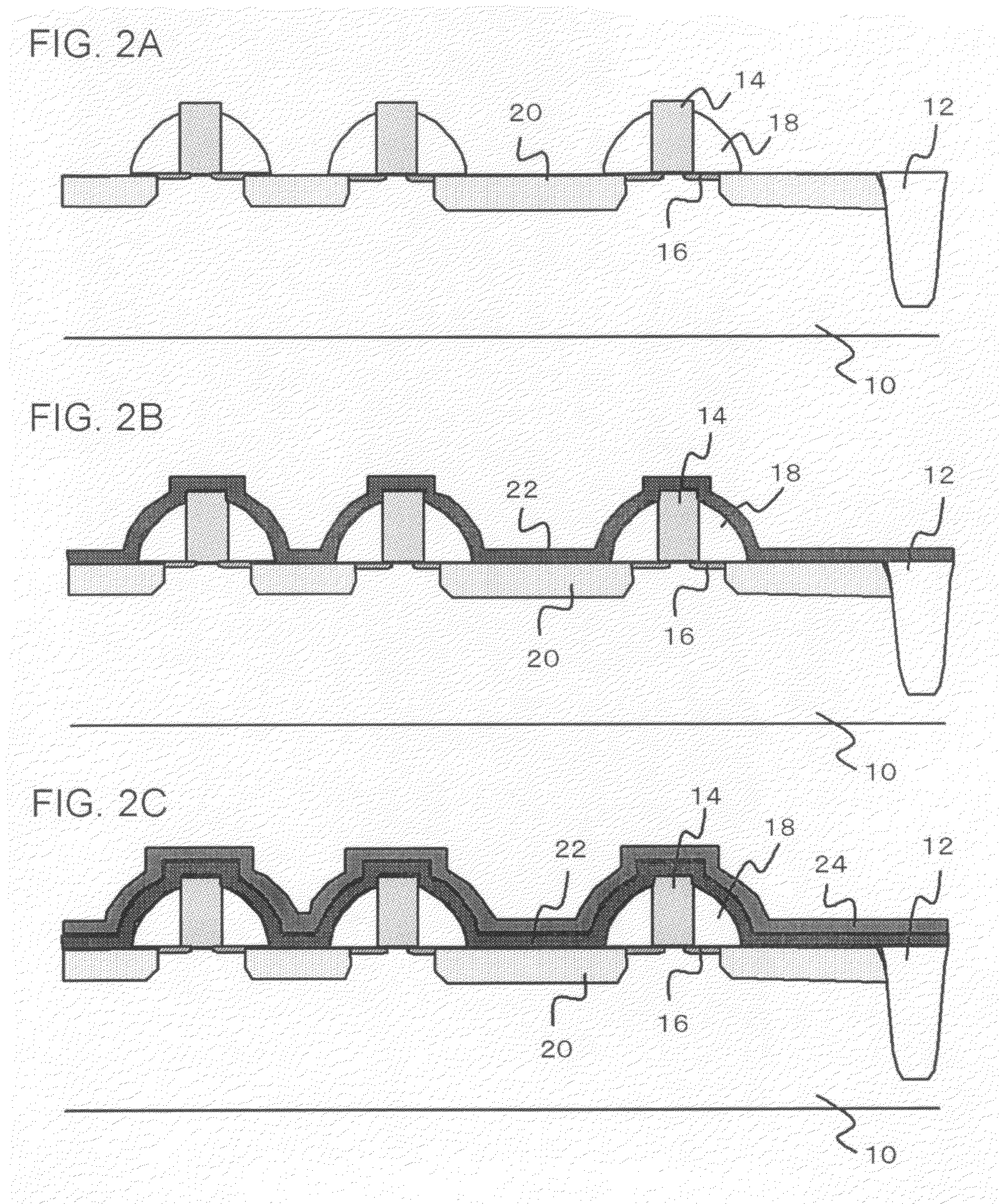

Manufacturing method of semiconductor device

InactiveUS6872642B2Improve performanceIncrease productionTransistorSolid-state devicesJunction leakageEngineering

A method of manufacturing a semiconductor device is provided which can suppress leakage current increases by making into silicide. Impurity that suppresses silicide formation reaction (suppression impurity), such as germanium, is introduced into source / drain regions (16, 36) from their upper surfaces. In the source / drain regions (16, 36), a region shallower than a region where the suppression impurity is distributed (50) is made into silicide, so that a silicide film (51) is formed in the source / drain regions (16, 36). Thus, by making the region shallower than the region (50) into silicide, it is possible to suppress that silicide formation reaction extends to the underside of the region to be made into silicide. This enables to reduce the junction leakage between the source / drain regions (16, 36) and a well region.

Owner:RENESAS ELECTRONICS CORP

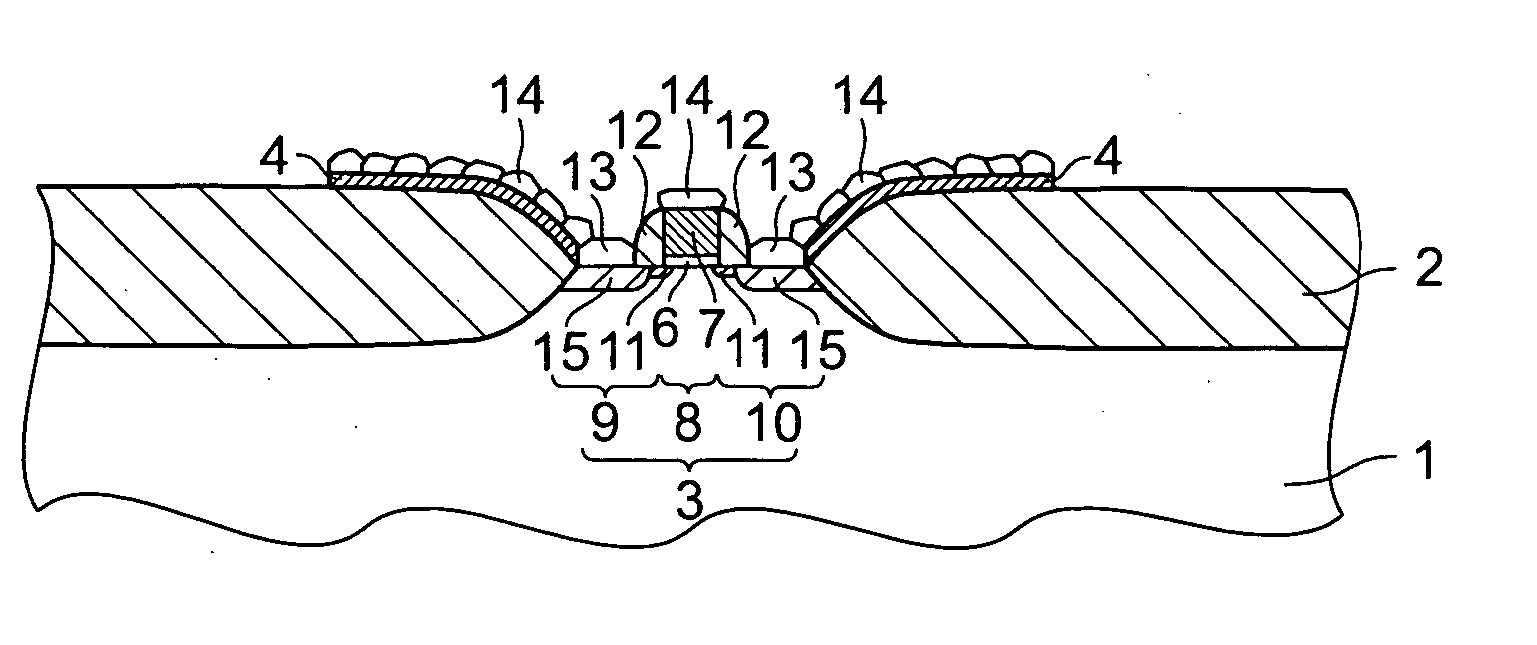

Semiconductor device and method of manufacturing the same

InactiveUS20060084255A1Not easy to damageReduce junction leakageTransistorSemiconductor/solid-state device manufacturingMOSFETDielectric

A gate dielectric film, a poly-silicon film, a film of a refractory metal such as tungsten, and a gate cap dielectric film are sequentially laminated on a semiconductor substrate. The gate cap dielectric film and the refractory metal film are selectively removed by etching. Thereafter, a double protection film including a silicon nitride film and a silicon oxide film is formed on side surfaces of the gate cap dielectric film, the refractory metal film, and the poly-silicon film. The poly-silicon film is etched using the double protection film as a mask. Thereafter, the semiconductor substrate is light oxidized to form a silicon oxide film on side surfaces of the poly-silicon film. Accordingly, a junction leakage of a MOSFET having a gate electrode of a poly-metal structure, particularly, a memory cell transistor of a DRAM, can be further reduced.

Owner:ELPIDA MEMORY INC

Implantation process in semiconductor fabrication

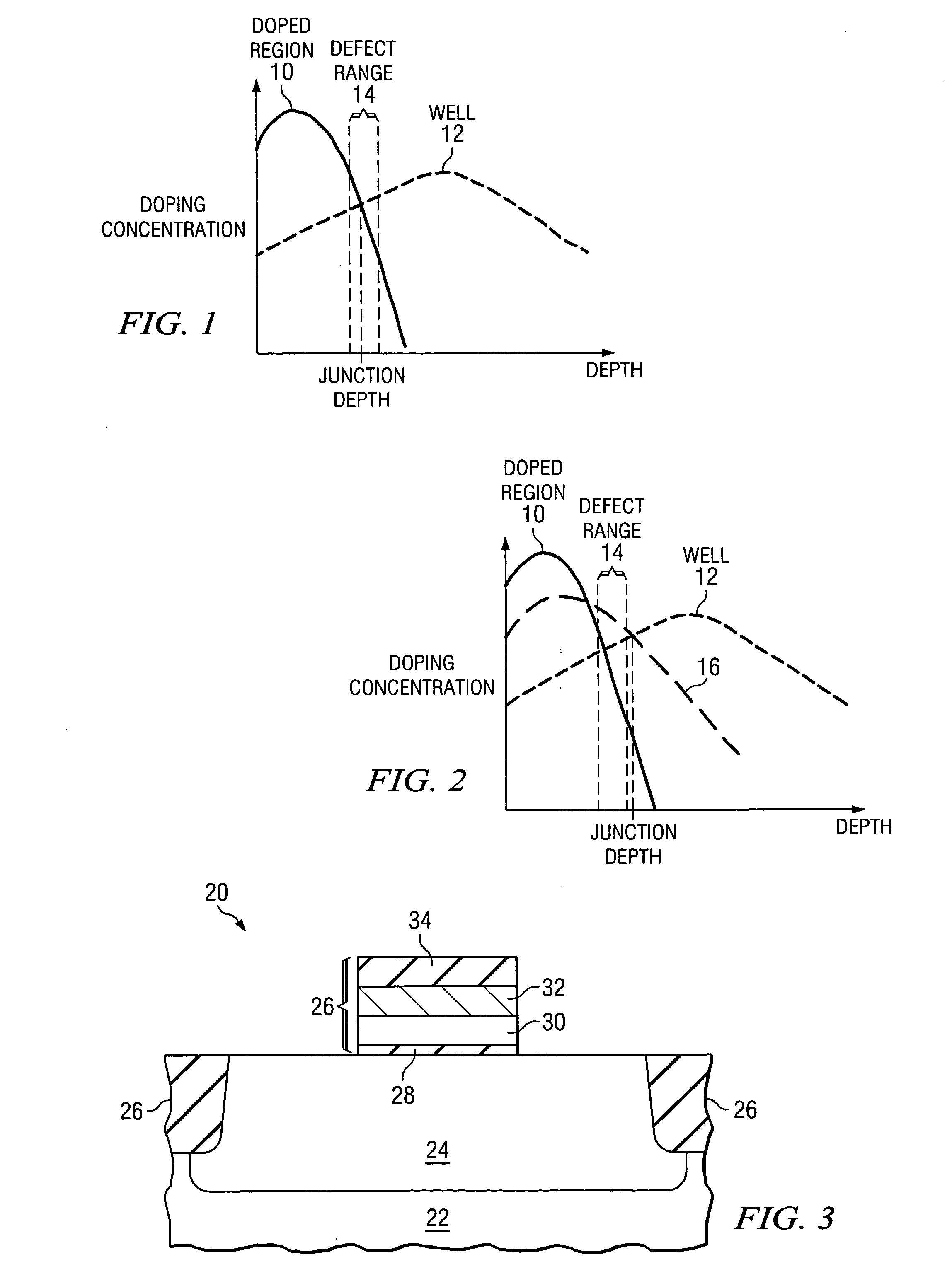

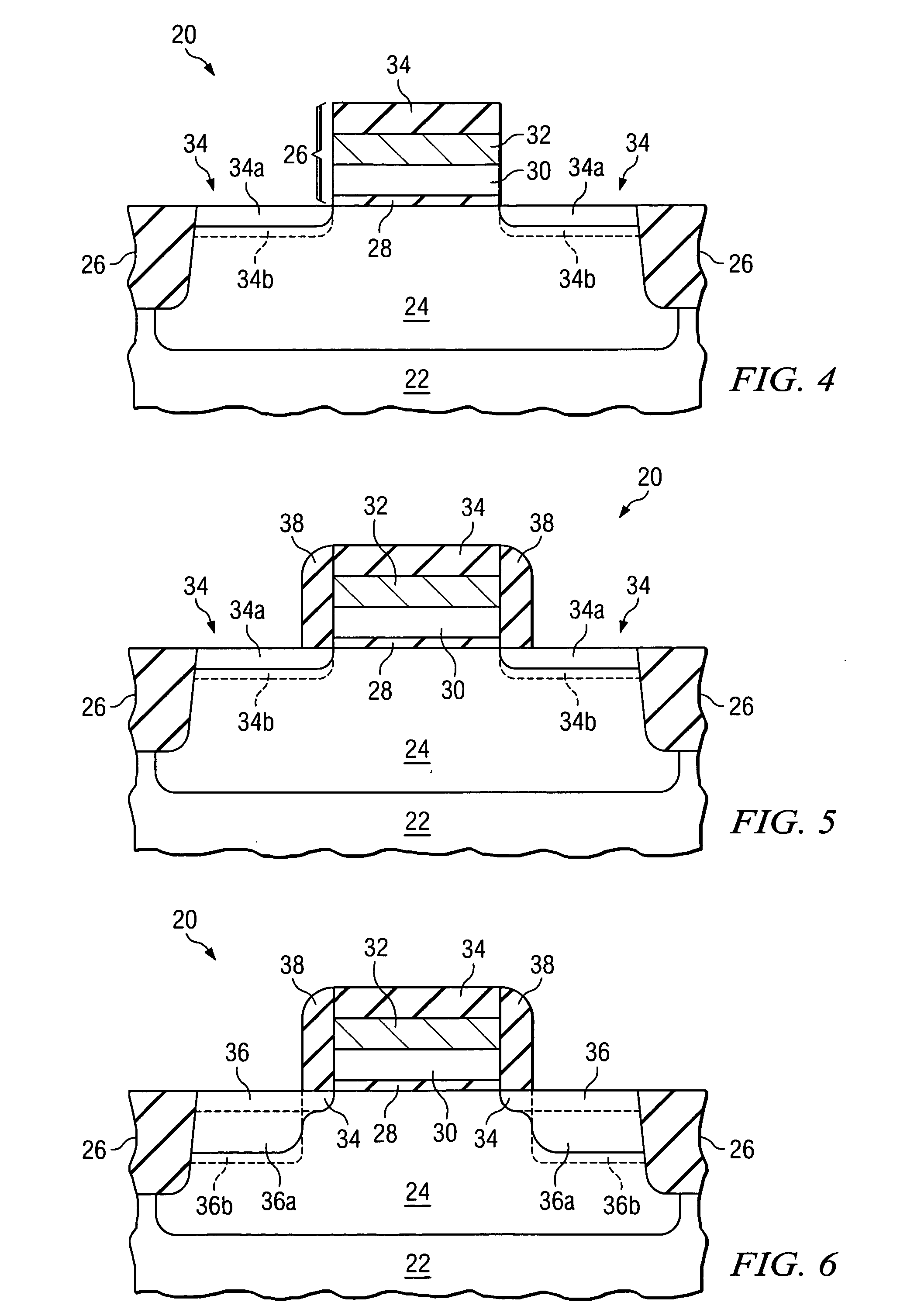

ActiveUS20060252239A1Smoothens junctionReduces band-to-band tunnelingTransistorSemiconductor/solid-state device manufacturingDopantOptoelectronics

A semiconductor device is formed by performing an amorphizing ion implantation to implant dopants of a first conductivity type into a semiconductor body. The first ion implantation causes a defect area (e.g., end-of-range defects) within the semiconductor body at a depth. A non-amorphizing implantation implants dopants of the same conductivity type into the semiconductor body. This ion implantation step implants dopants throughout the defect area. The dopants can then be activated by heating the semiconductor body for less than 10 ms, e.g., using a flash anneal or a laser anneal.

Owner:INFINEON TECH AG

Salicide formation method

InactiveUS6916729B2Reduce junction leakageInhibition formationTransistorSolid-state devicesSalicideJunction leakage

A method of forming a salicide on a semiconductor device includes depositing a first refractory metal layer over a silicon region of a substrate, depositing a near-noble metal layer over the first refractory metal layer, and depositing a second refractory metal layer over the near-noble metal layer. The semiconductor device is annealed in a first annealing process to form a silicide layer abutting the doped region of the semiconductor device. Un-reacted portions of the near-noble metal layer and the second refractory metal layer are removed. The device may be annealed in an optional second annealing process to convert the silicide layer to a low resistance phase silicide material. Junction leakage and bridging are minimized or eliminated by embodiments of the present invention, and a smoother silicided surface is achieved.

Owner:IBM CORP +1

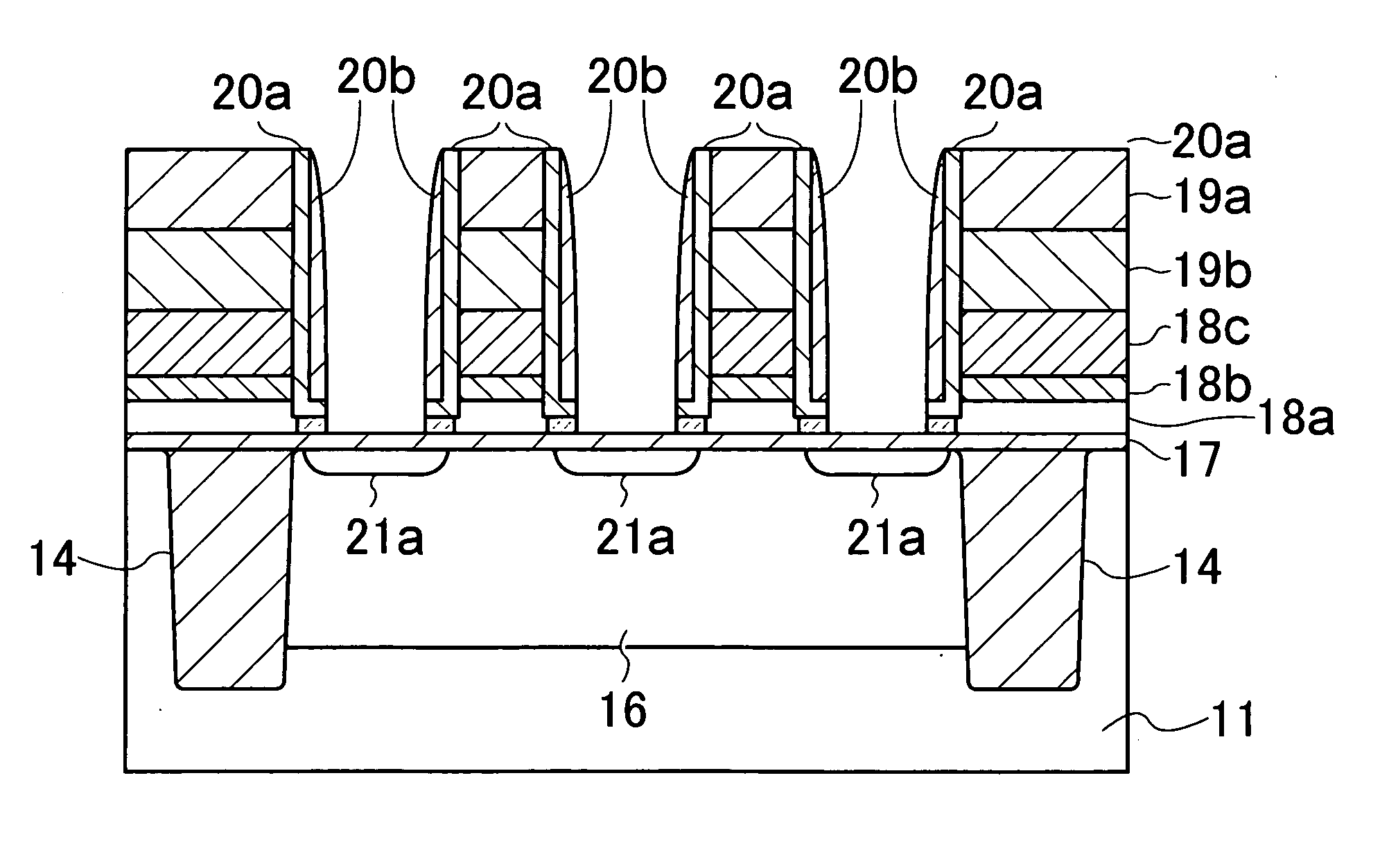

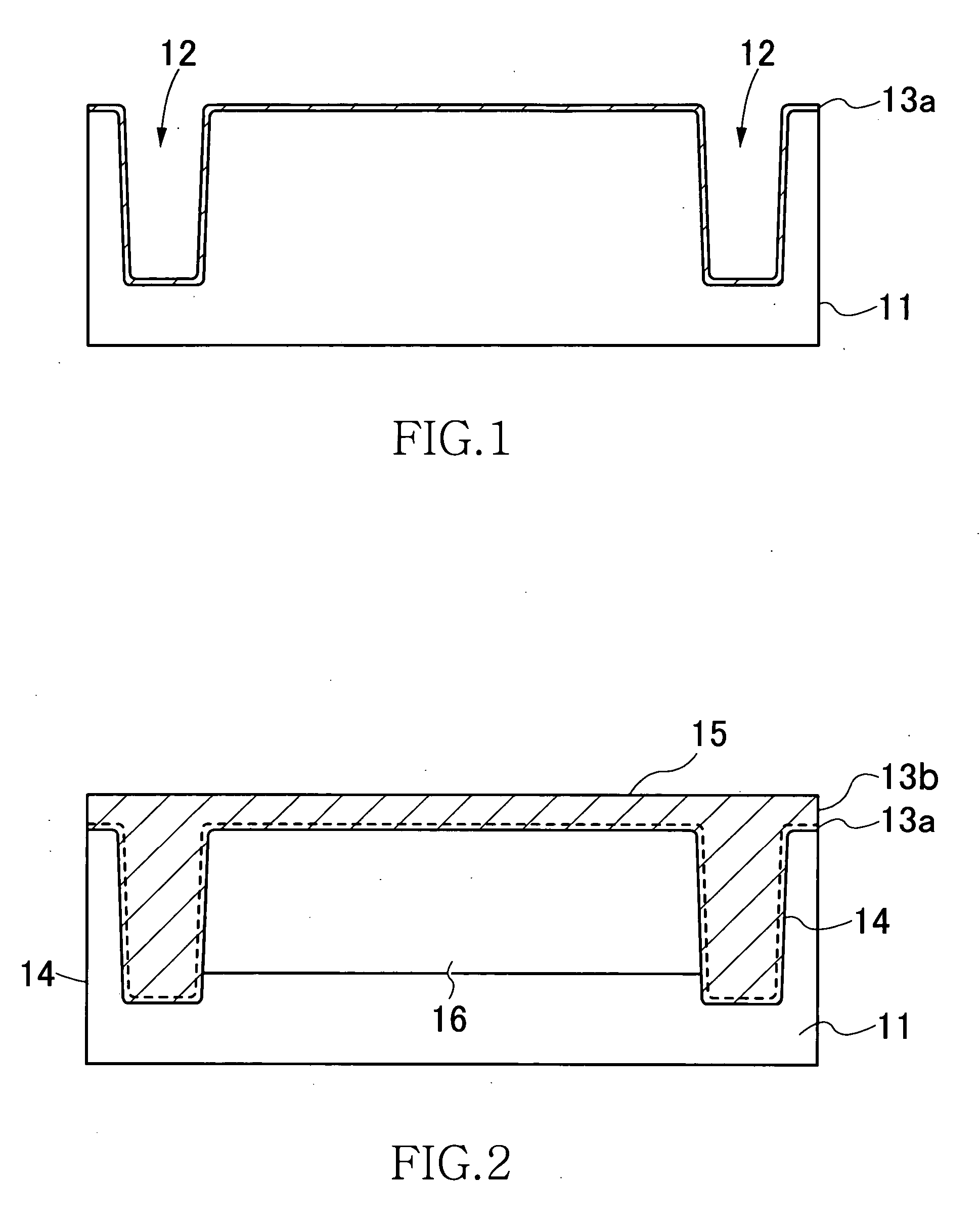

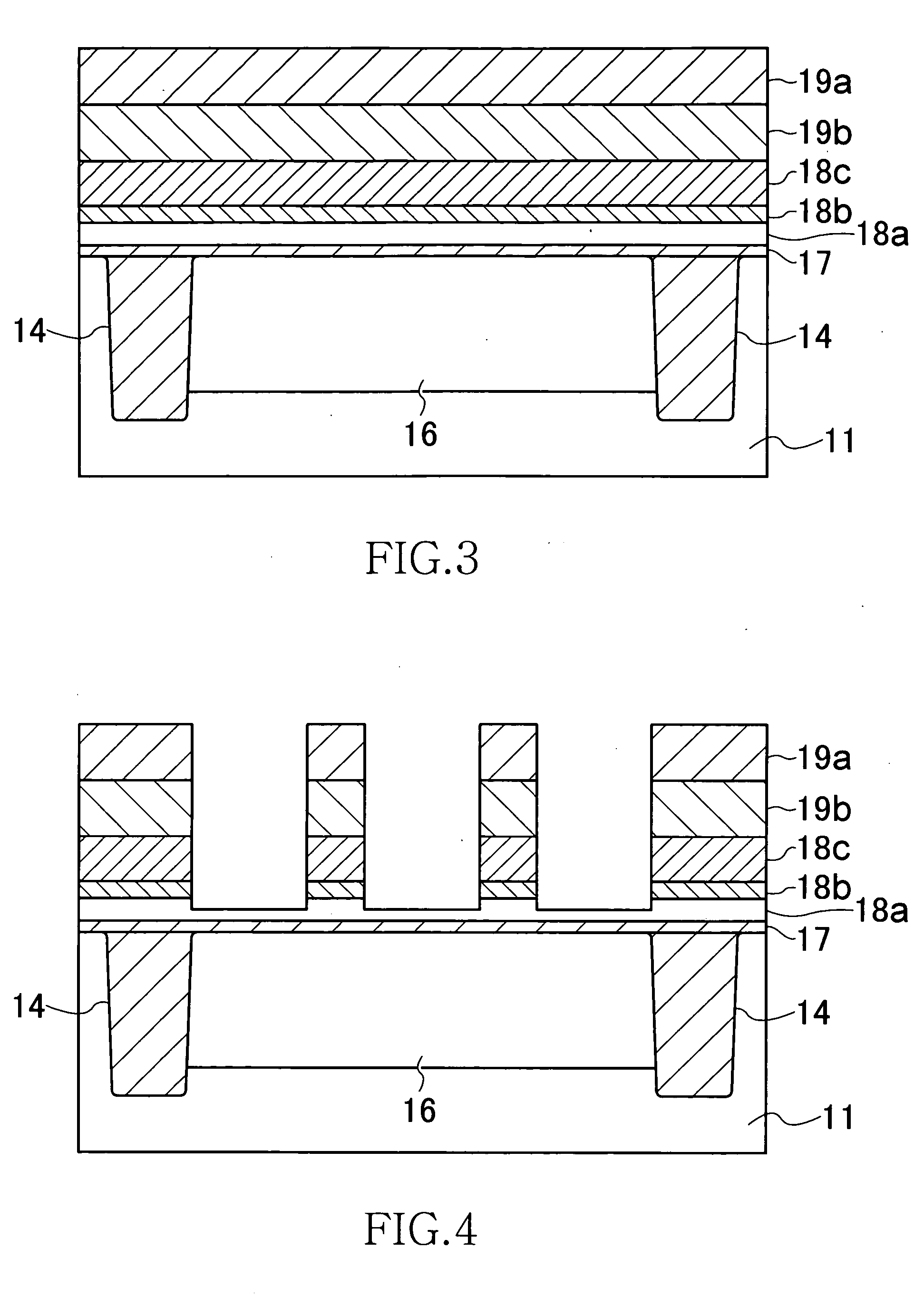

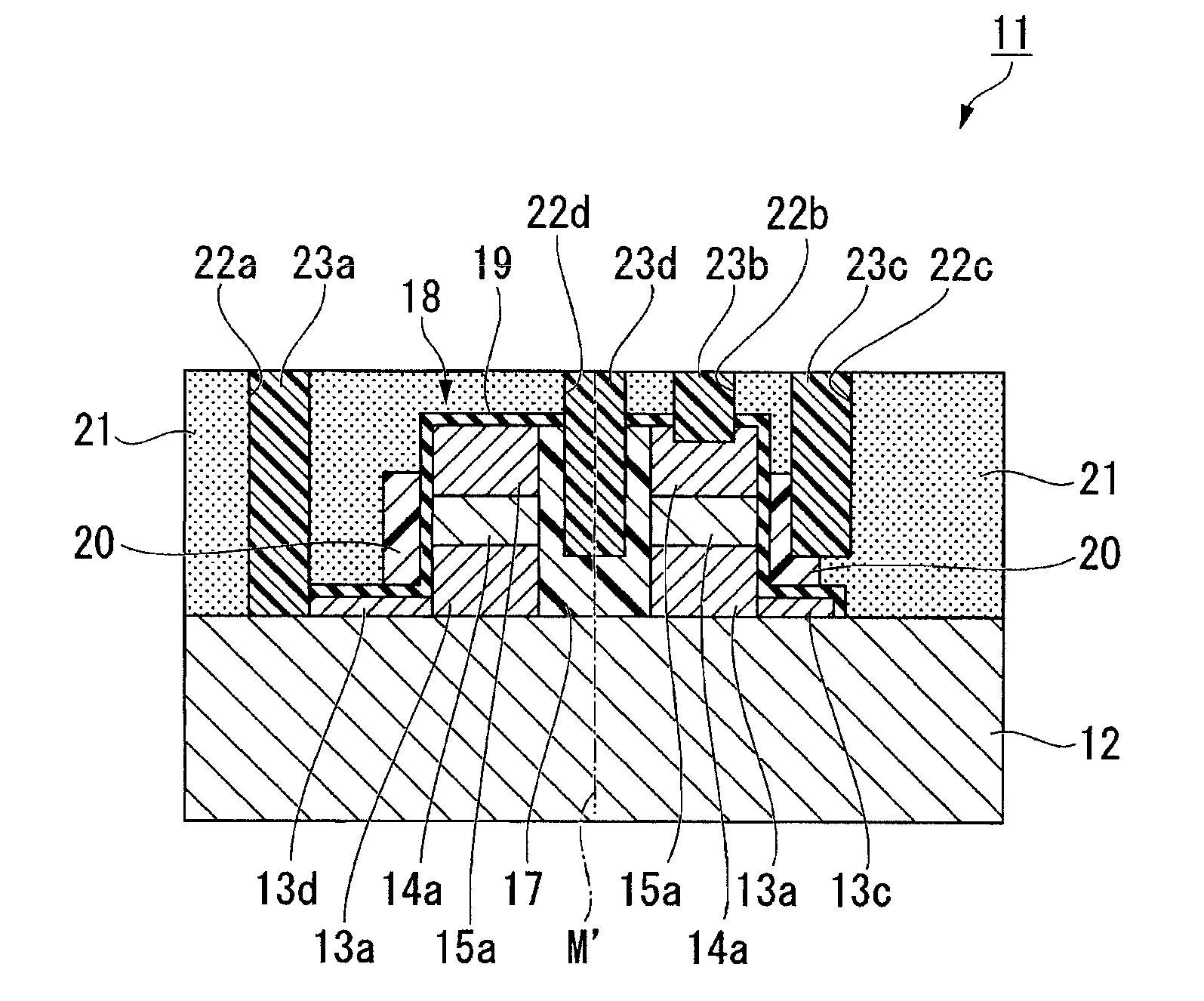

Semiconductor device and method of manufacturing semiconductor device

InactiveUS8378415B2Increase currentReduce areaSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringSemiconductor device

A semiconductor device includes a cylindrical main pillar that is formed on a substrate and of which a central axis is perpendicular to the surface of the substrate, source and drain diffused layers that are formed in a concentric shape centered on the central axis at upper and lower portions of the main pillar and made from a first-conduction-type material, a body layer that is formed at an intermediate portion of the main pillar sandwiched between the source and drain diffused layers and made from the first-conduction-type material, and a front gate electrode that is formed on a lateral face of the main pillar while placing a gate insulating film therebetween. Moreover, a back gate electrode made from a second-conduction-type material is formed in a pillar shape penetrating from an upper portion to a lower portion on an inner side of the main pillar.

Owner:PS4 LUXCO SARL

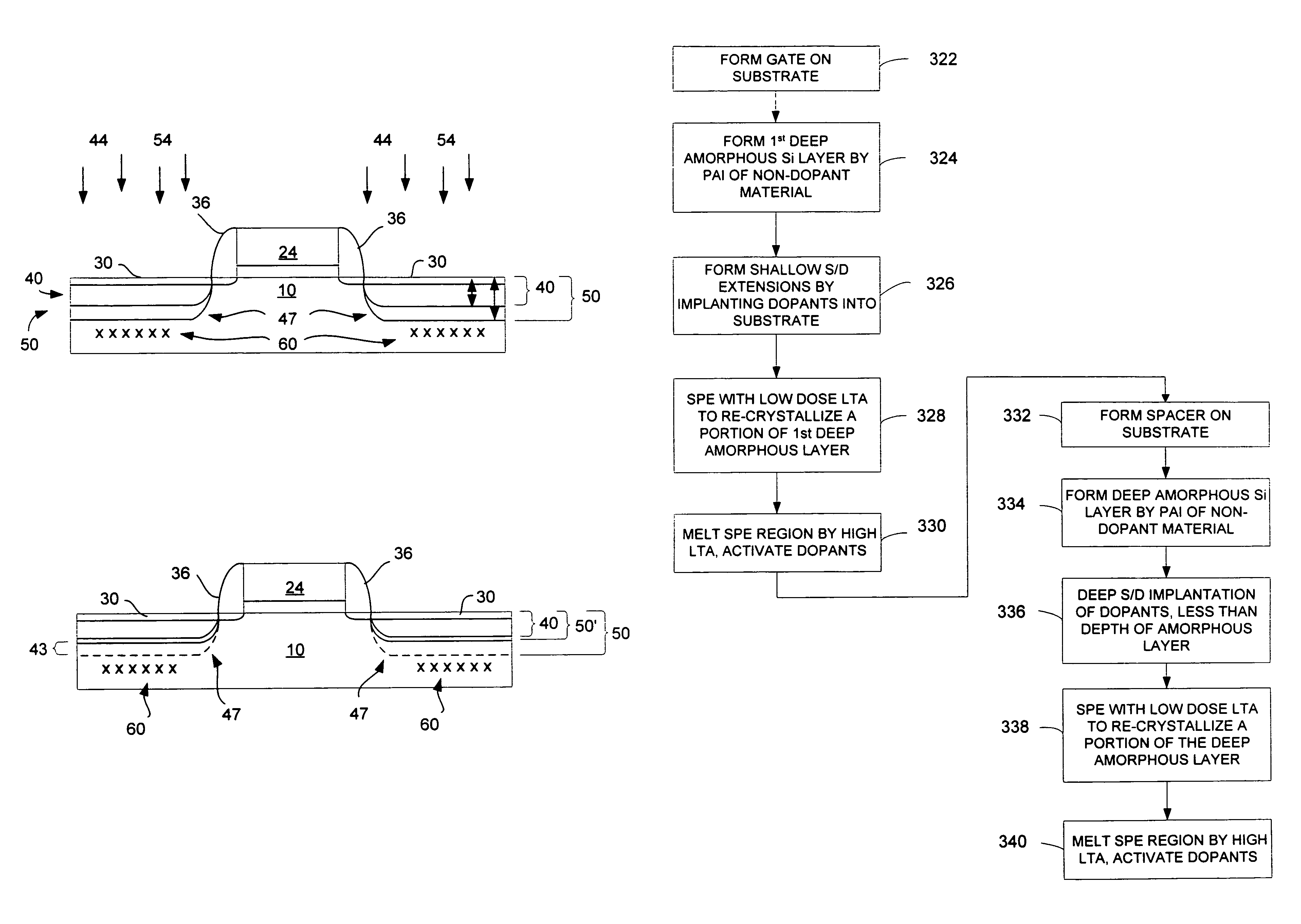

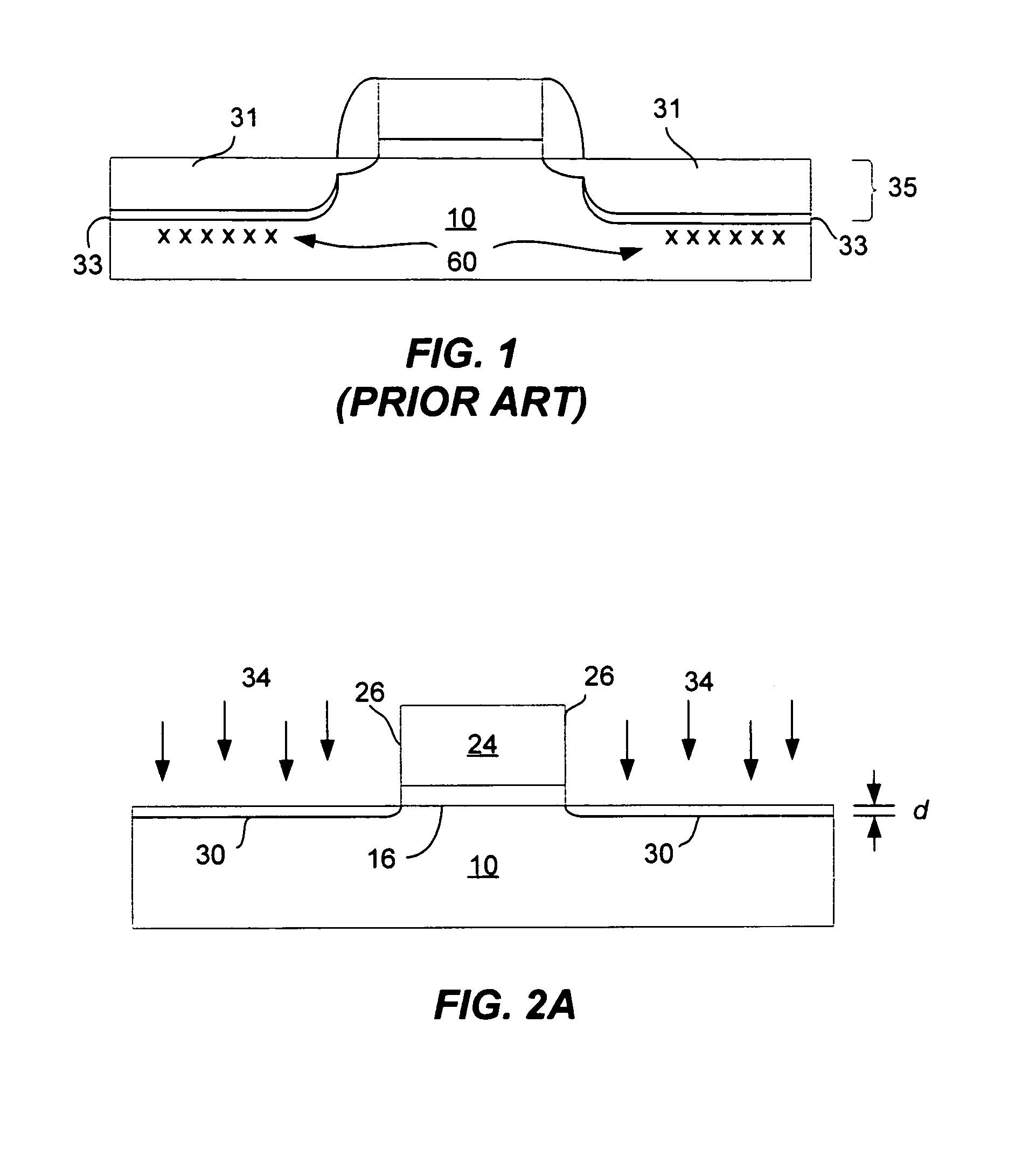

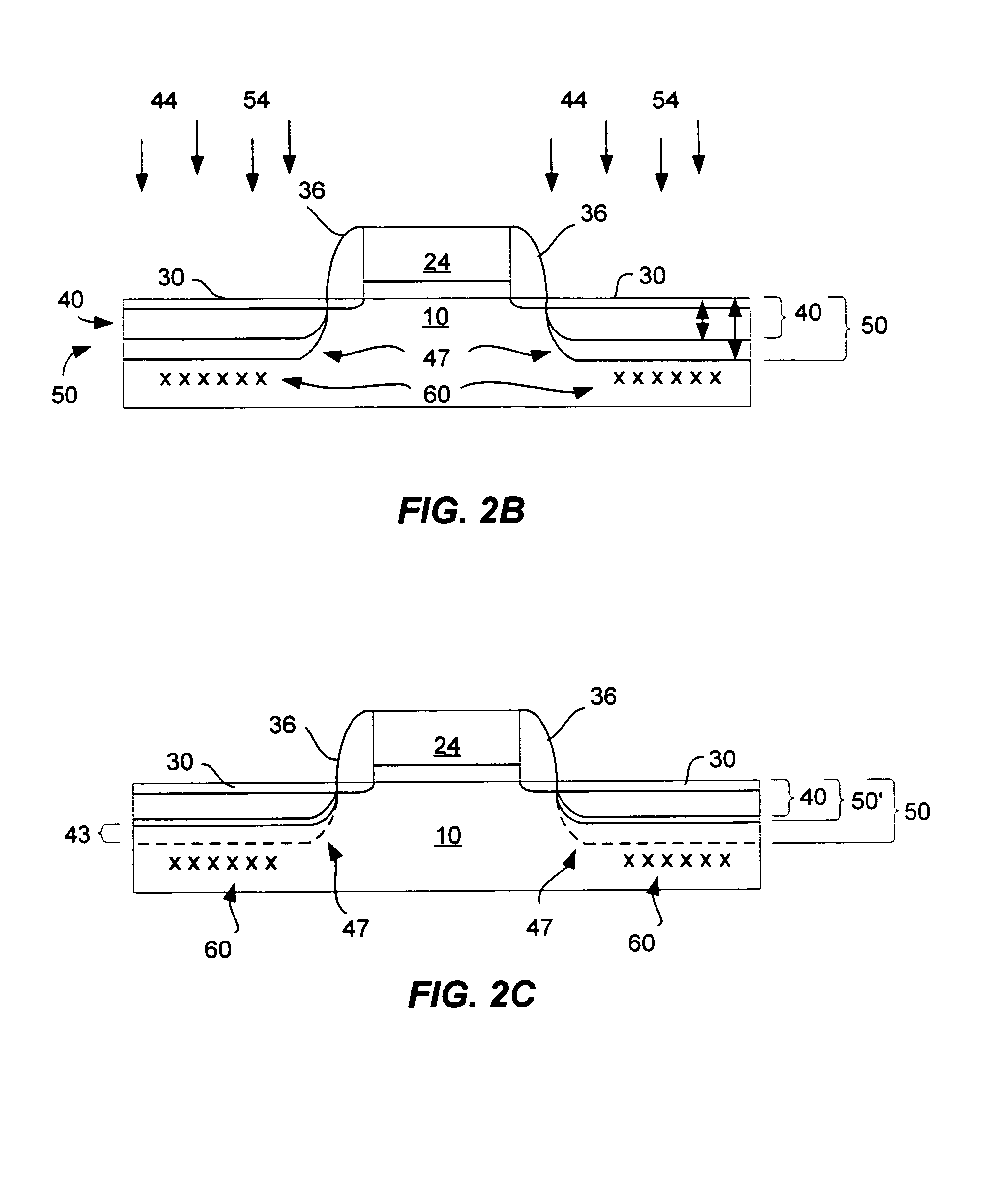

End-of-range defect minimization in semiconductor device

ActiveUS7091097B1Reduce junction leakageTransistorSemiconductor/solid-state device manufacturingDopantSemiconductor

A method of fabricating a semiconductor device comprises forming a gate electrode over a substrate and forming deep amorphous regions within the substrate. And implanting dopants to form deep source / drain regions at a depth less than that of the deep amorphous regions, partially re-crystallizing portions of the deep amorphous regions to reduce their depth, and re-crystallizing the reduced amorphous regions to form activated final source / drain regions.

Owner:CONVERSANT INTPROP MANAGEMENT INC

Method for manufacturing a semiconductor device having a STI structure

InactiveUS20060276001A1Reduction in junction leakage currentImprove reliabilitySemiconductor/solid-state device manufacturingSemiconductor devicesAnisotropic etchingSemiconductor

A method for manufacturing a STI structure includes the steps of anisotropic-etching the surface of a silicon substrate to form a trench, forming a first thermal oxide film on the surface of the trench at a substrate temperature of 1000 degrees C. or above, removing the first oxide film, anisotropic-etching the bottom of the trench to increase the depth of the trench, forming a second oxide film on the surface of the trench, and embedding an insulator in the trench.

Owner:ELPIDA MEMORY INC

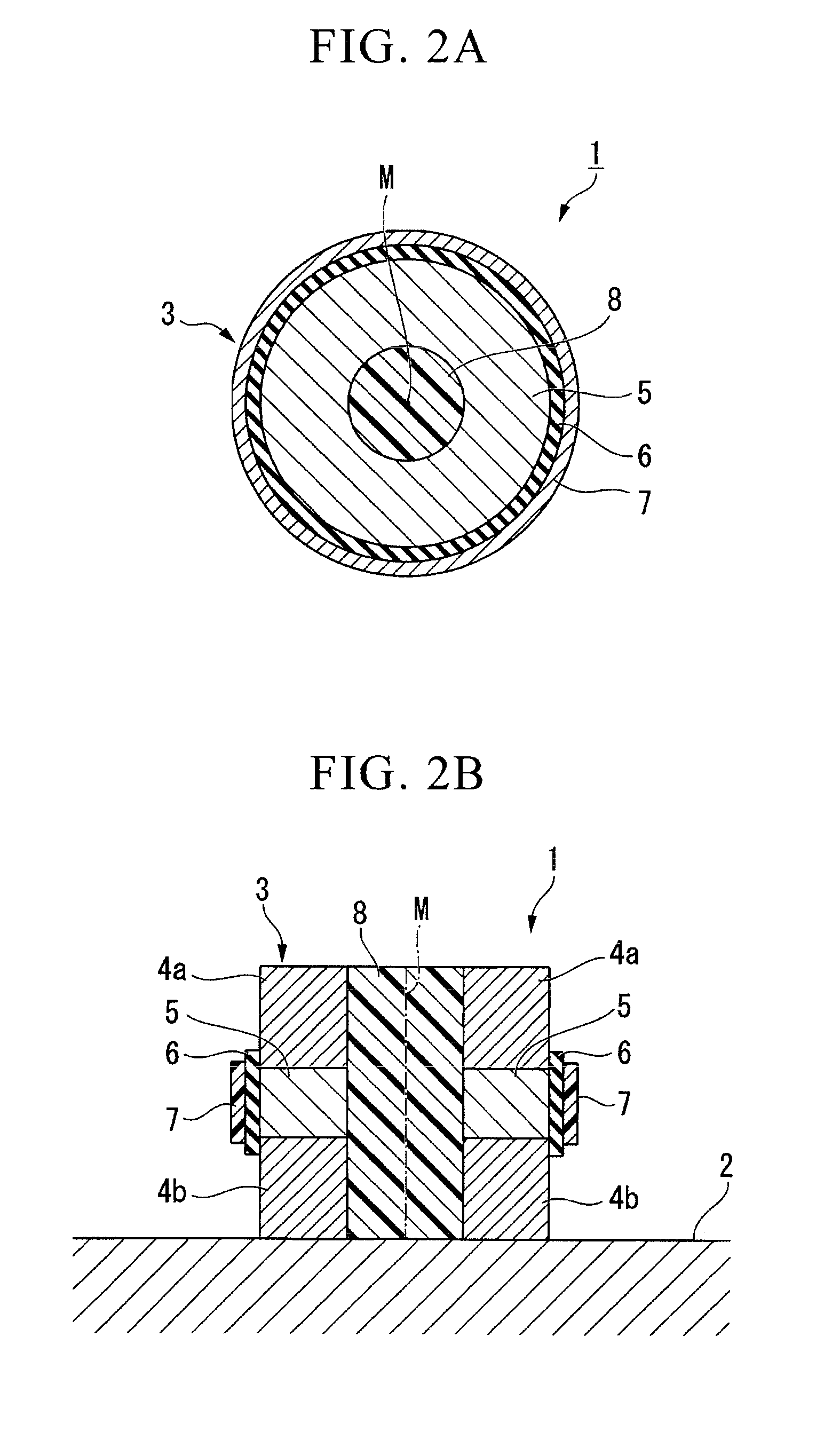

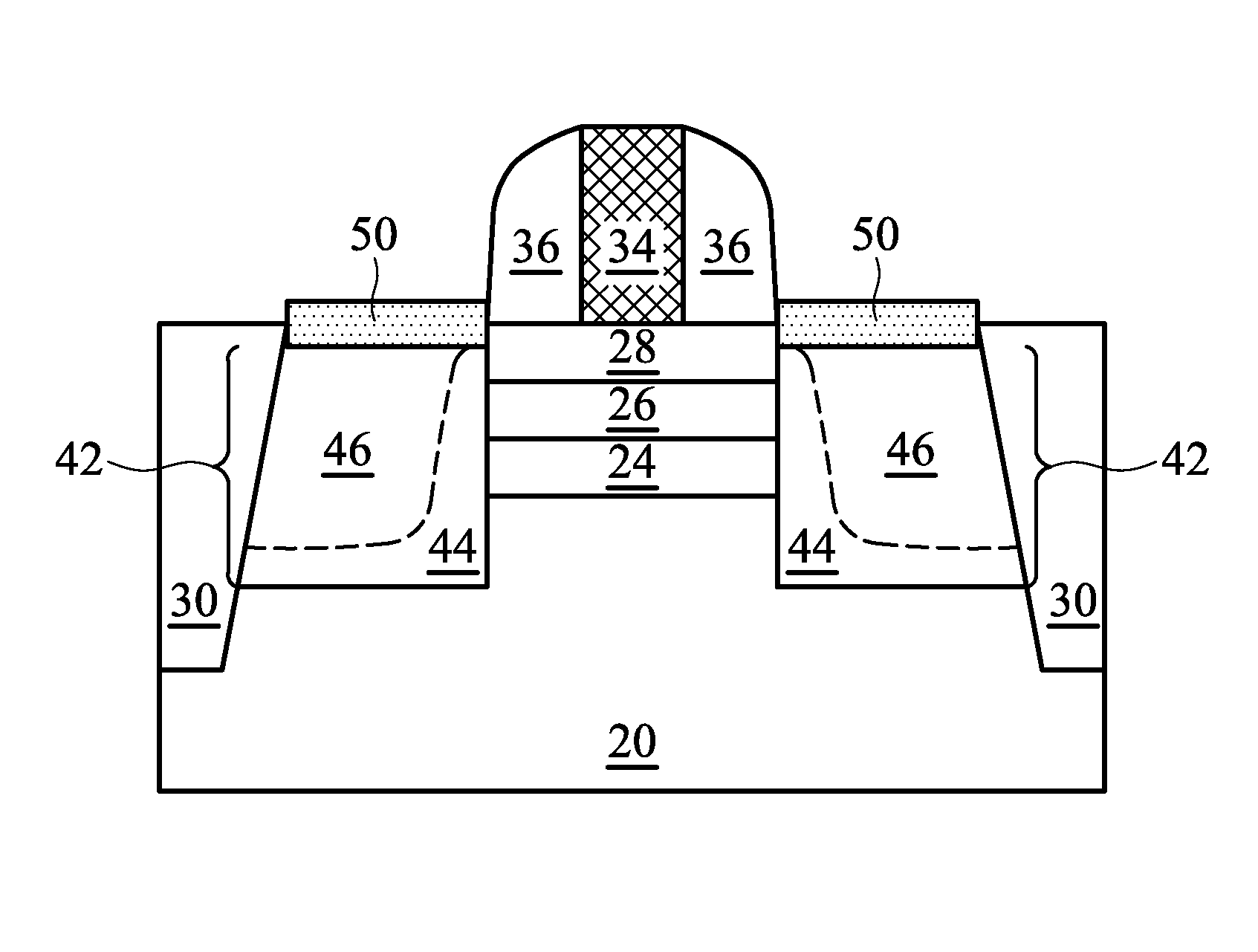

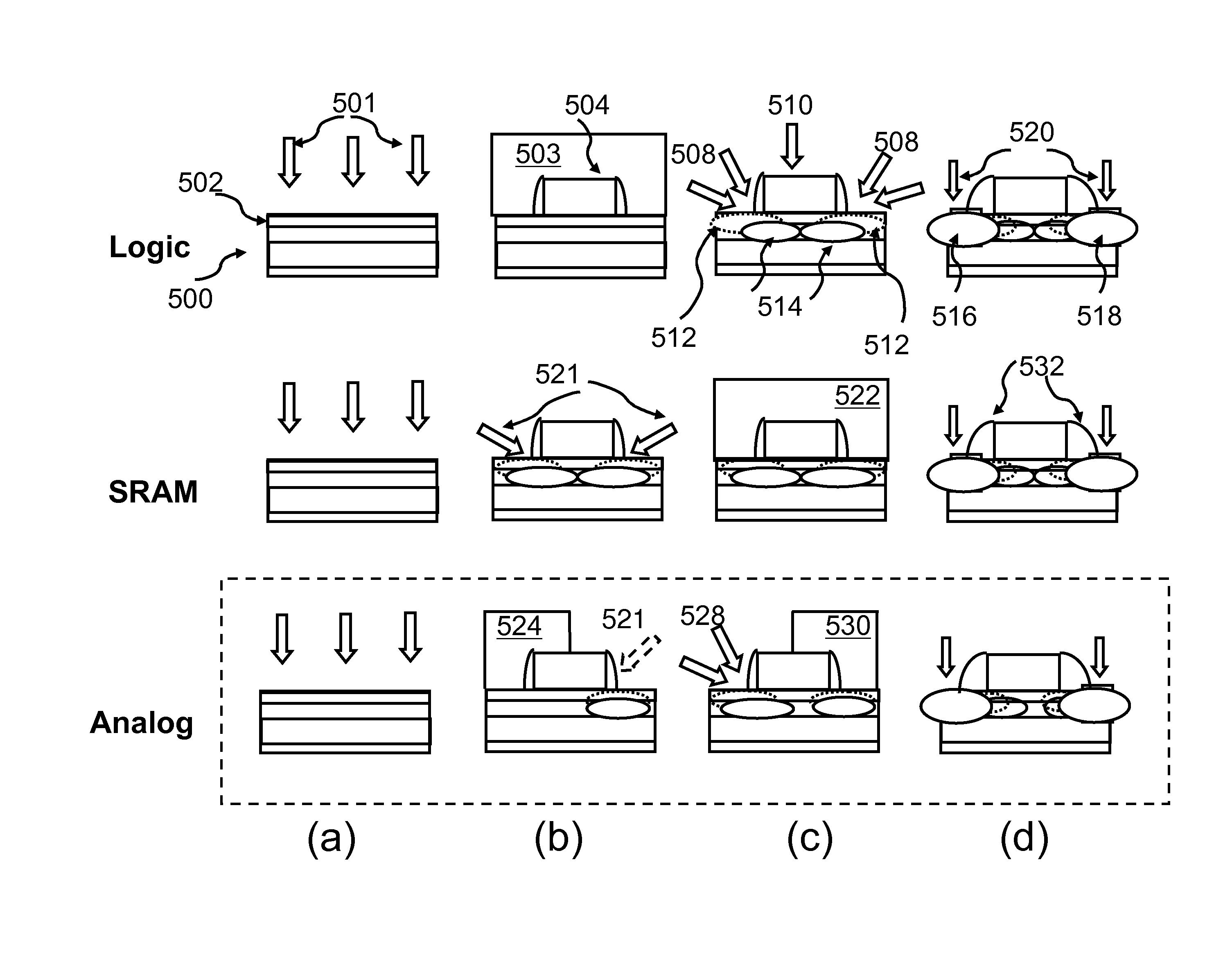

Source/drain engineering of devices with high-mobility channels

ActiveUS8816391B2Improved drive currentReduce resistanceTransistorSemiconductor materialsEngineering

Owner:TAIWAN SEMICON MFG CO LTD

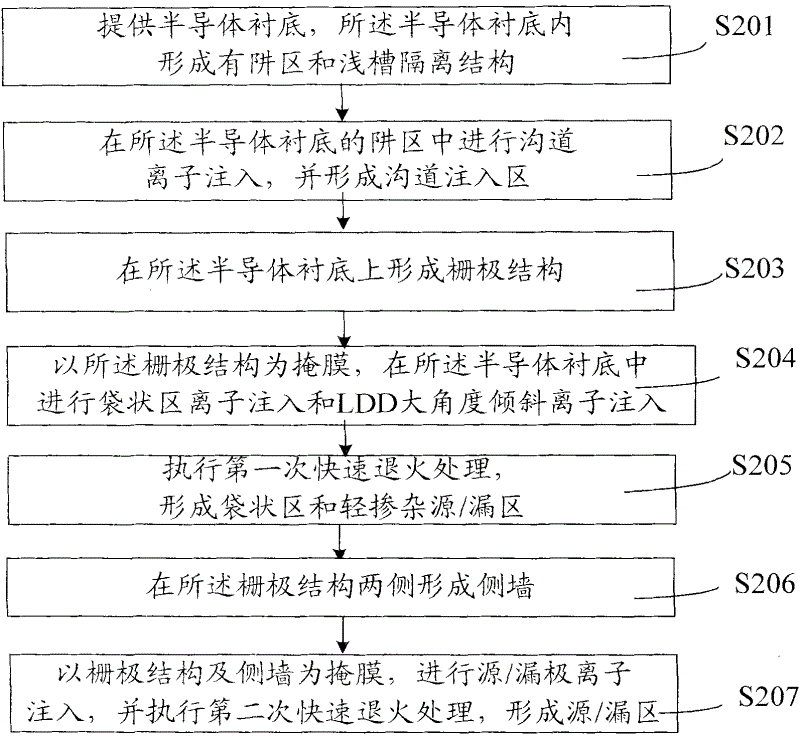

Preparation method of MOS transistor

ActiveCN102623341AReduce junction leakageExcellent electrical propertiesTransistorSemiconductor/solid-state device manufacturingRapid thermal annealingSemiconductor

The invention provides a preparation method of an MOS transistor, comprising: providing a semiconductor substrate, wherein a well region and a shallow-slot isolation structure are formed in the semiconductor substrate; carrying outchannel ion injection in the well region of the semiconductor substrate to form a channel injection region; forming a grid structure on the semiconductor substrate; carrying out a bag-like region ion injection and a lightly doped source / drain region(LDD) large angle inclined ion injection, wherein the grid structure is used as a mask; carrying out a first rapid thermal annealing process to form the bag-like region and the lightly doped source / drain region; forming side walls on two sides of the grid structure; and carrying out a source / drain ion injection and a second rapid thermal annealing process to form source / drain regions, wherein the grid structure and the side walls are used as masks. According to the preparation method of the invention, an ultra-shallow junction MOS transistor with longer effective channels is formed through the LDD large angle inclined ion injection. Thus, HCI effects can be inhibited, SCE effects can be substantially improved, and junction electric leakage can be decreased.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Method of fabricating a MOSFET device

InactiveUS20050106844A1Efficient solutionSolve the real problemTransistorSemiconductor/solid-state device manufacturingMOSFETJunction leakage

Ions are implanted into a substrate, using a gate and its sidewall liner on the substrate as the mask, to form a source / drain region in the substrate beneath the liner and adjacent to the two sides of the gate. The liner is etched to reduce its thickness. Then, ions are implanted into the substrate to form a halo doped region surrounding the source / drain region. The halo doped region is closer to the MOSFET channel region and overlaps less with the source / drain region. Therefore, the device threshold voltage can be sustained and the junction leakage can also be minimized.

Owner:PROMOS TECH INC

Method of manufacturing semiconductor device

InactiveUS7015107B2Suppress surface roughnessImprove gate reliabilitySemiconductor/solid-state device manufacturingSemiconductor devicesSurface roughnessEngineering

When a dummy sidewall and source and drain regions are once formed and then the dummy sidewall is removed to extend the source and drain regions, the removal of the dummy sidewall is performed after formation of a protective oxide film on a gate electrode and on the major surfaces of the source and drain regions. This efficiently prevents conventional surface roughness of the upper surface of the gate electrode and the impurity region due to the removal of the dummy sidewall.

Owner:RENESAS TECH CORP

Semiconductor device and method of manufacturing the same

InactiveUS20050124105A1Reduce areaReduce parasitic capacitanceSemiconductor/solid-state device detailsSolid-state devicesDopantDevice material

A semiconductor device and a method of manufacturing the same are provided. An underlayer film including nitrogen is formed on a predetermined region on an element isolation region, the predetermined region extending from a border of an active element forming region to the element isolation region side. Silicon or a mixed crystal of silicon or germanium is selectively formed on the underlayer film. Then the silicon or the mixed crystal of silicon and germanium is turned into a conductive film by ion implantation of a dopant or further making it to be a silicide. Subsequently, the conductive film formed on the element isolation region is electrically connected to an electrical wiring.

Owner:SEIKO EPSON CORP

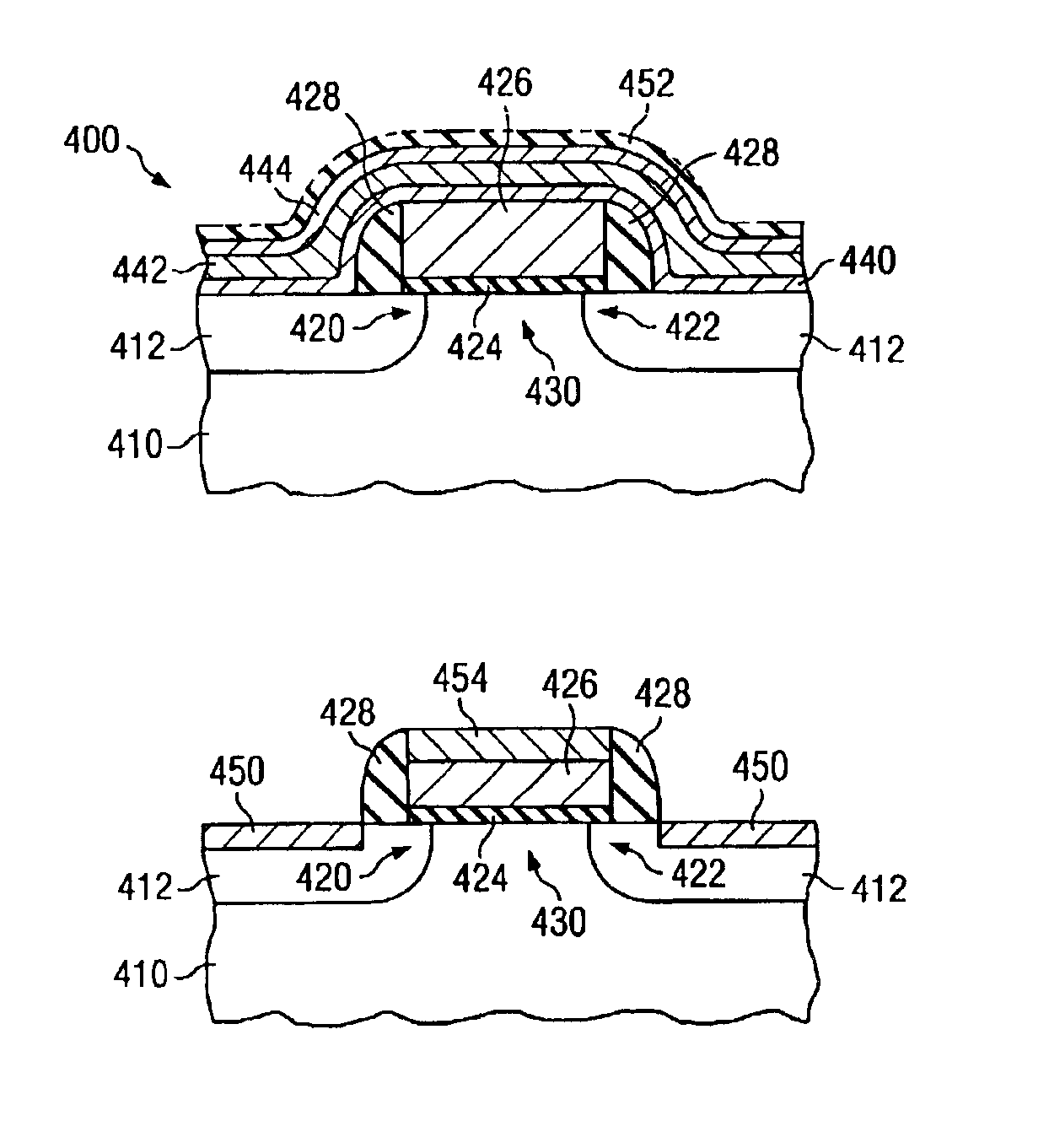

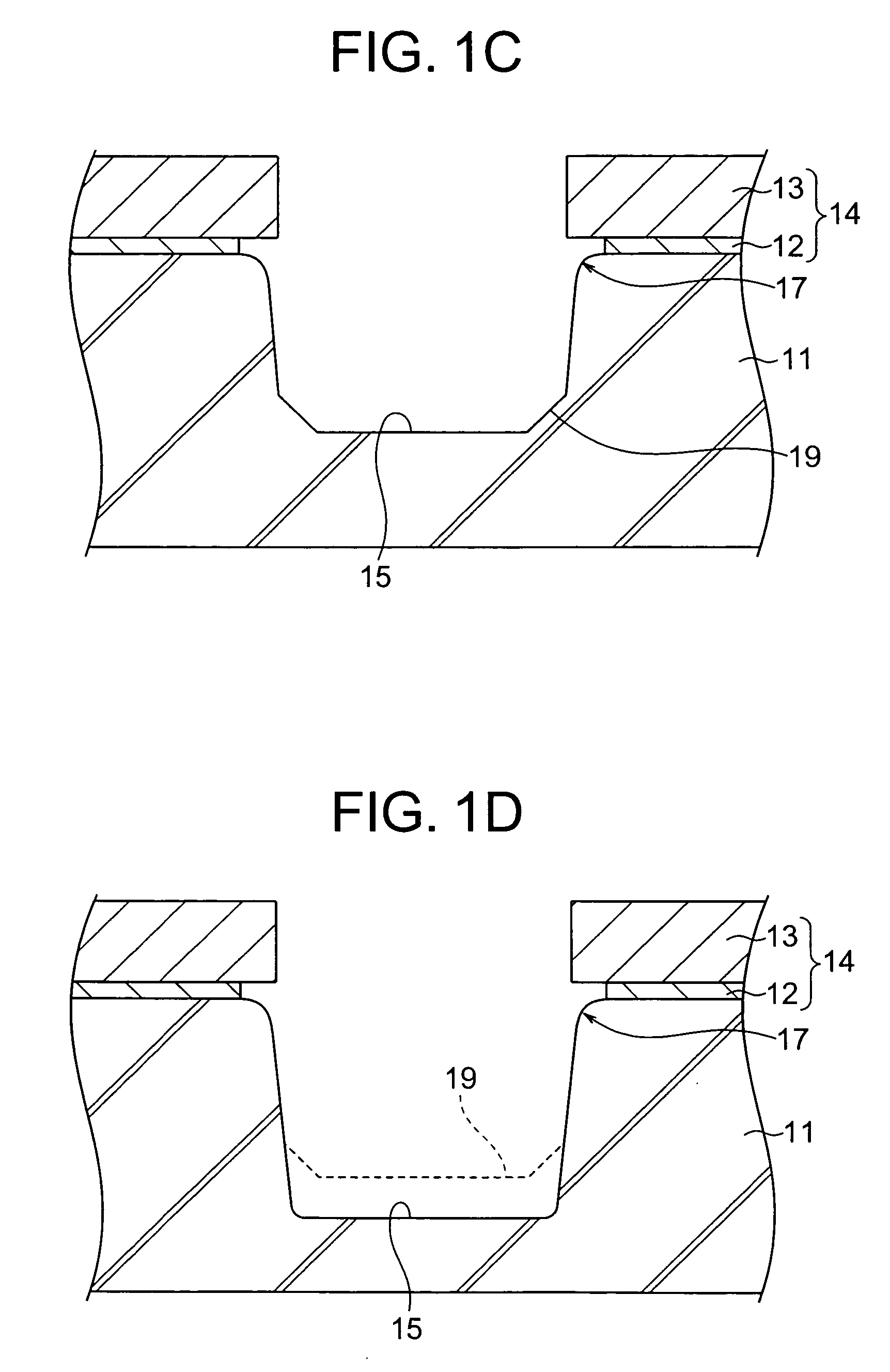

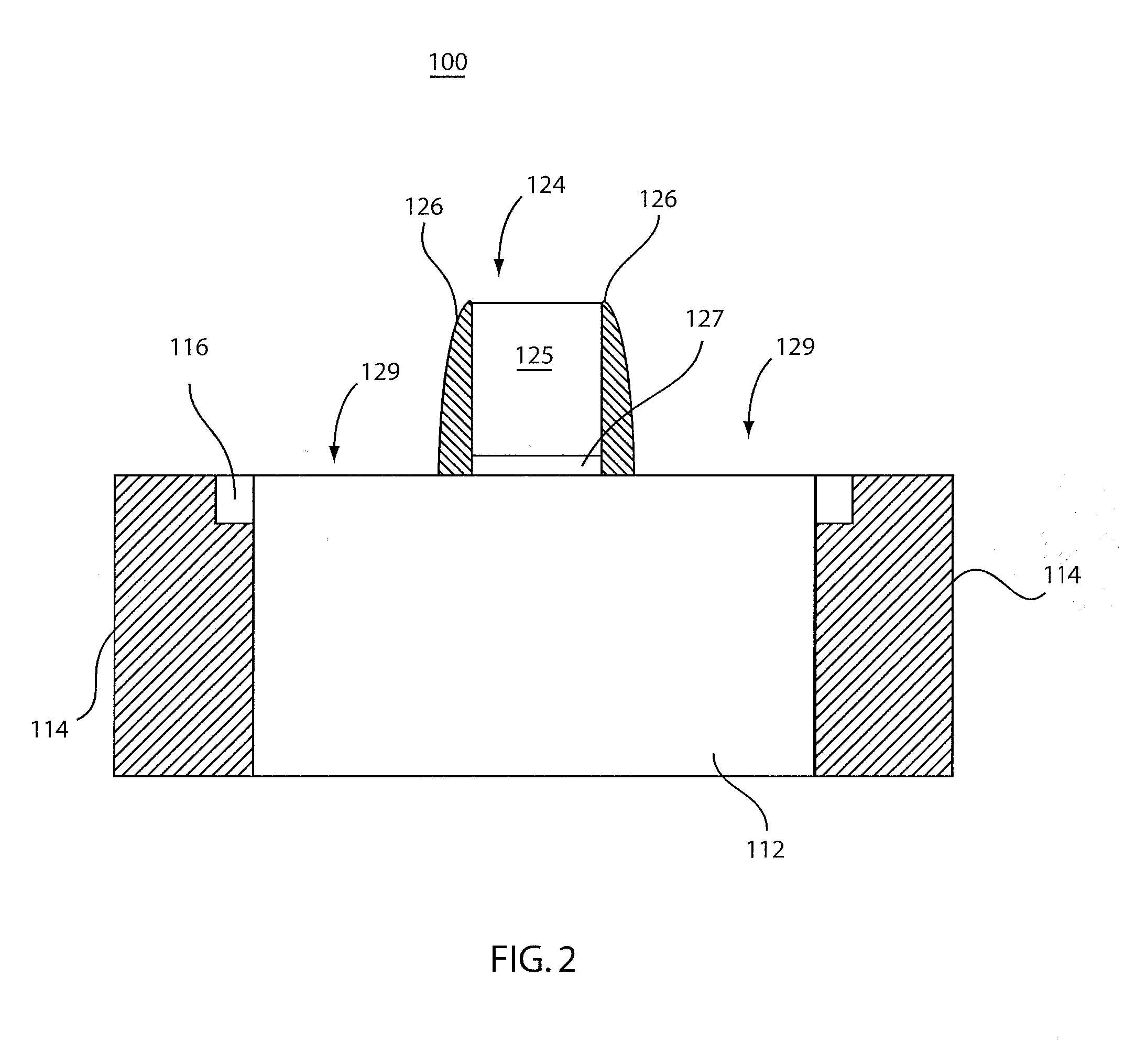

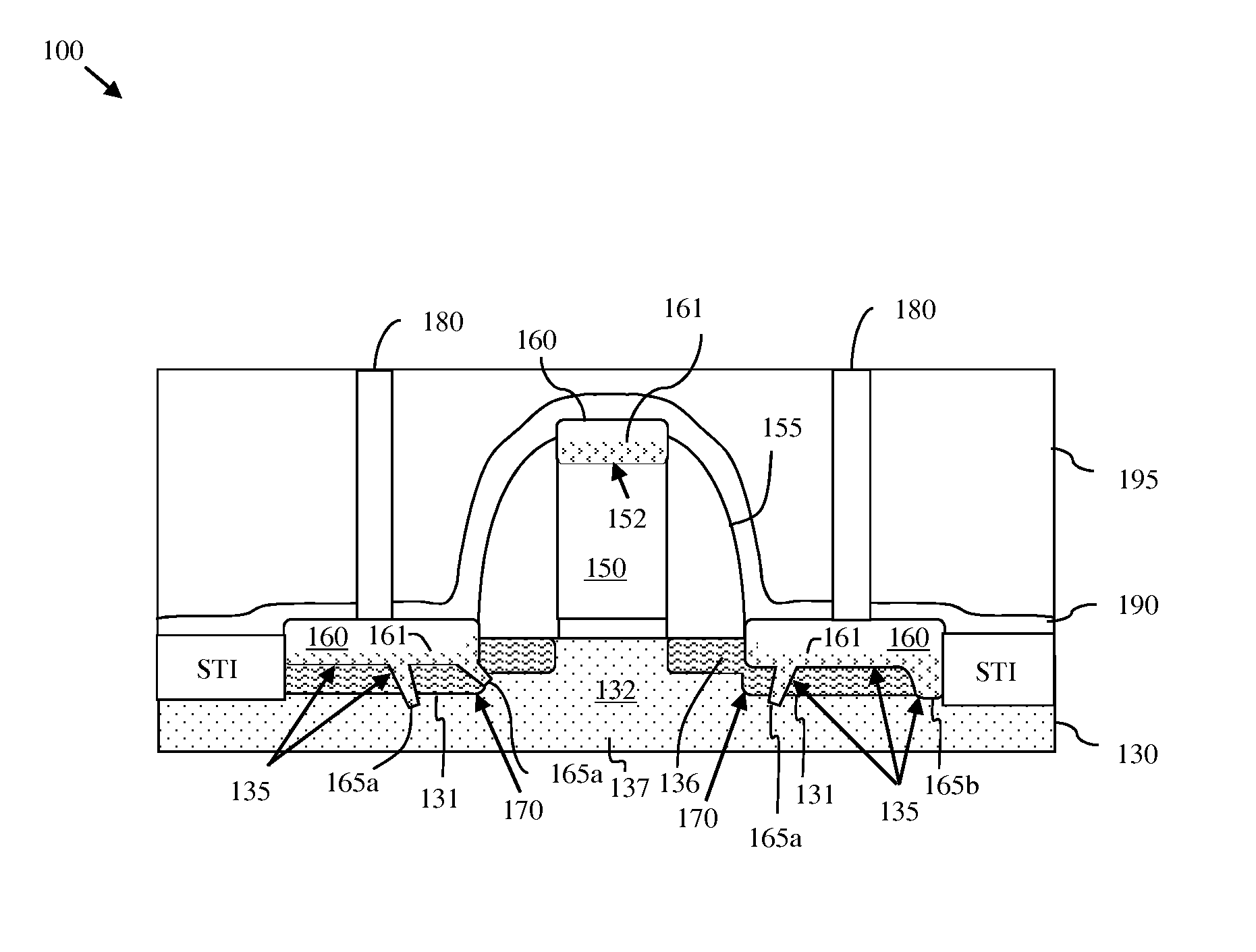

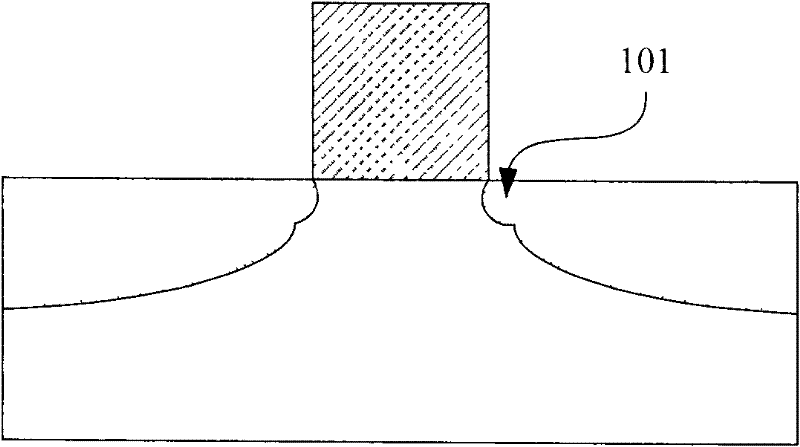

Device and method of reducing junction leakage

InactiveUS8202767B2Reduce junction leakageTransistorSemiconductor/solid-state device manufacturingDopantJunction leakage

A device and method for reducing junction leakage in a semiconductor junction includes forming a faceted raised structure in a source / drain region of the device. Dopants are diffused from the faceted raised structure into a substrate below the faceted raised structure to form source / drain regions. A sprinkle implantation is applied on the faceted raised structure to produce a multi-depth dopant profile in the substrate for the source / drain regions.

Owner:GLOBALFOUNDRIES INC

Method for manufacturing a semiconductor device

InactiveUS20050164448A1Reduced Junction Leakage CurrentImproved data retention capabilityTransistorSolid-state devicesDopantSemiconductor memory

A method for forming a semiconductor memory device includes the steps of: implanting a dopant in a semiconductor substrate; heat treating the semiconductor substrate in an oxidizing ambient to diffuse the dopant for forming diffused regions in the semiconductor substrate; and forming memory cells each including a MOS transistor having the diffused regions as source / drain regions.

Owner:RAMBUS INC

Semiconductor device with reduced junction leakage and an associated method of forming such a semiconductor device

InactiveUS8349716B2Reduce leakageIncrease heightSemiconductor/solid-state device manufacturingSemiconductor devicesSalicideDopant

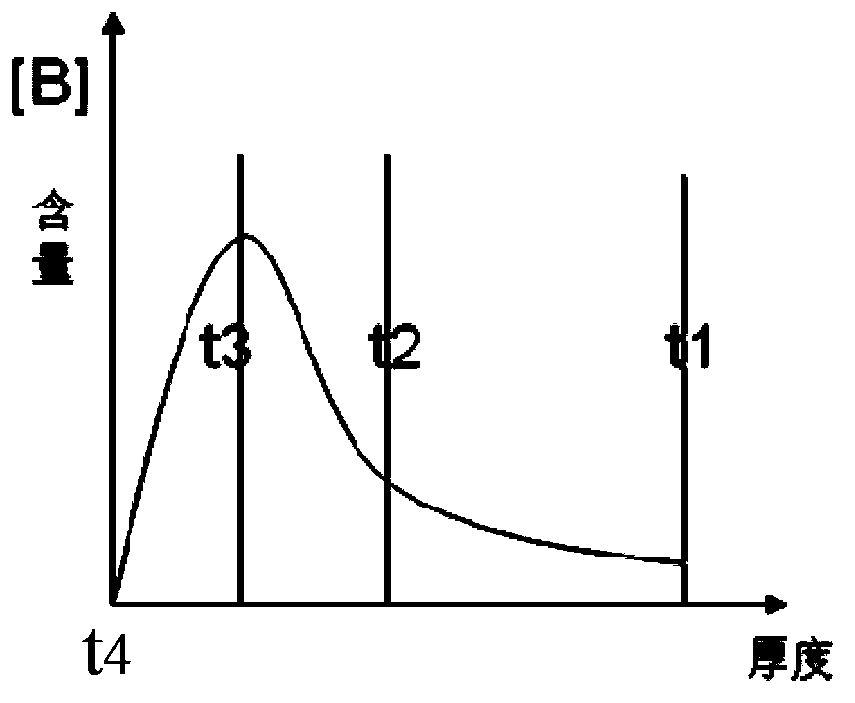

Disclosed is a semiconductor device having a p-n junction with reduced junction leakage in the presence of metal silicide defects that extend to the junction and a method of forming the device. Specifically, a semiconductor layer having a p-n junction is formed. A metal silicide layer is formed on the semiconductor layer and a dopant is implanted into the metal silicide layer. An anneal process is performed causing the dopant to migrate toward the metal silicide-semiconductor layer interface such that the peak concentration of the dopant will be within a portion of the metal silicide layer bordering the metal silicide-semiconductor layer interface and encompassing the defects. As a result, the silicide to silicon contact is effectively engineered to increase the Schottky barrier height at the defect, which in turn drastically reduces any leakage that would otherwise occur, when the p-n junction is in reverse polarity.

Owner:GLOBALFOUNDRIES U S INC +1

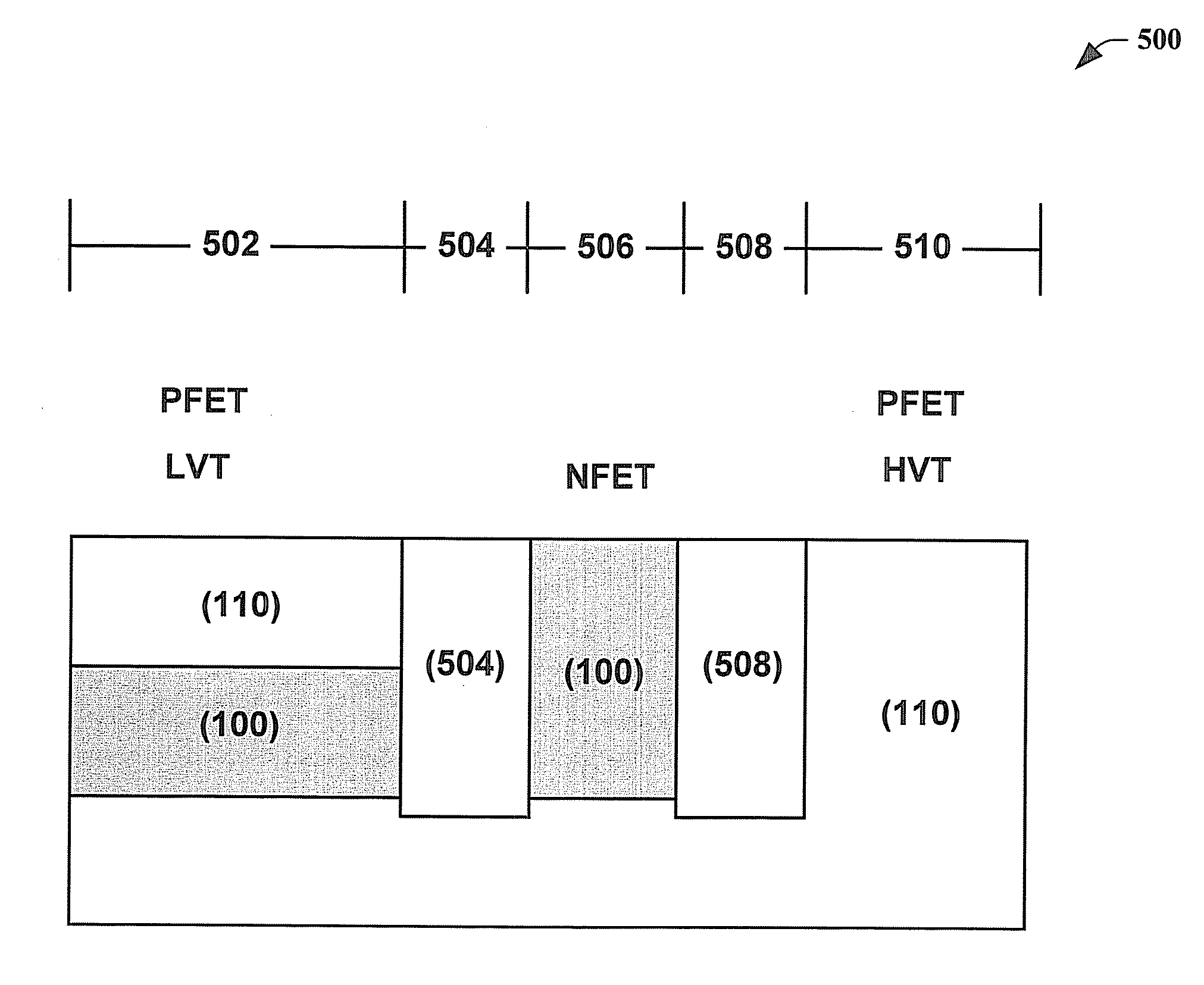

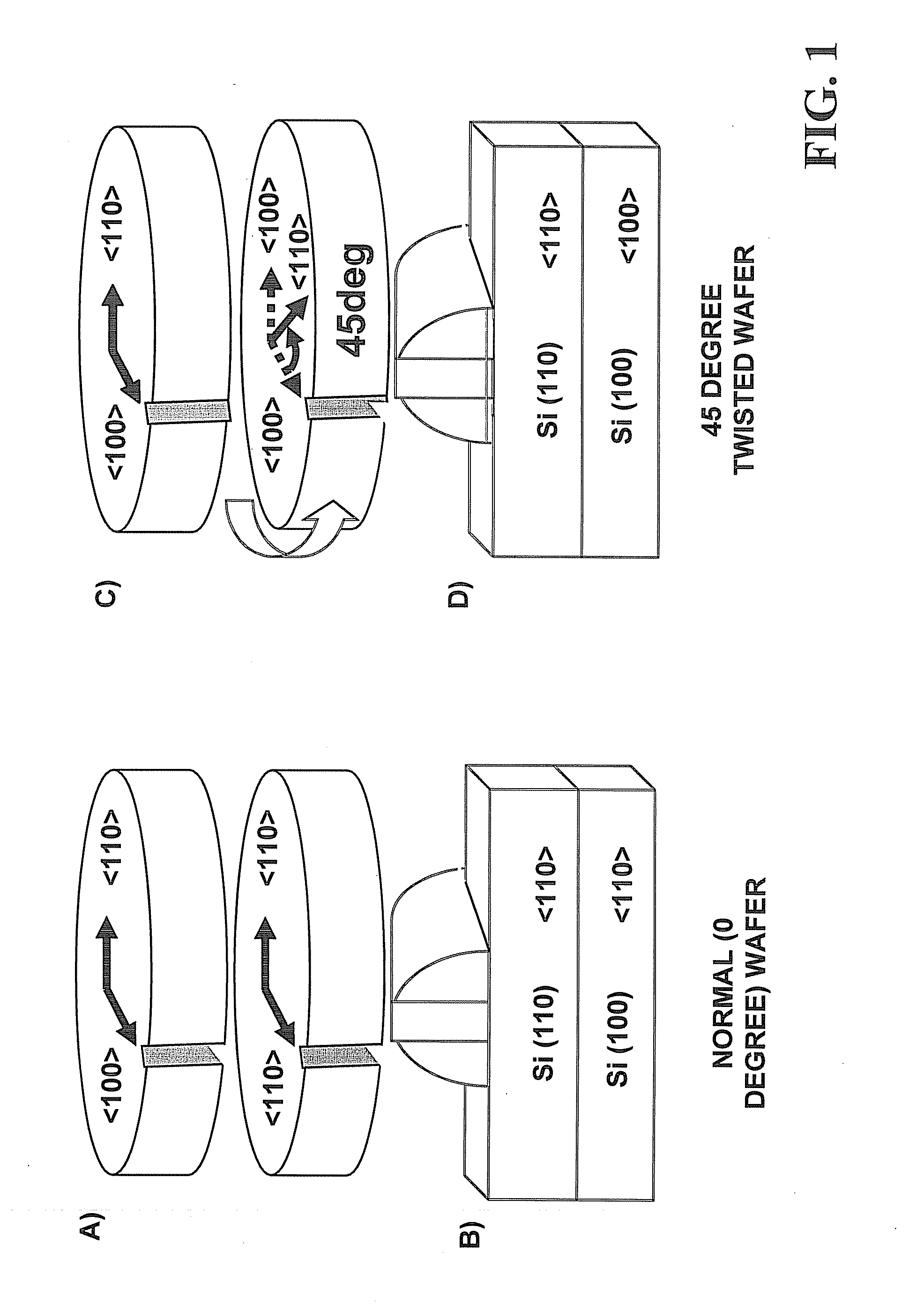

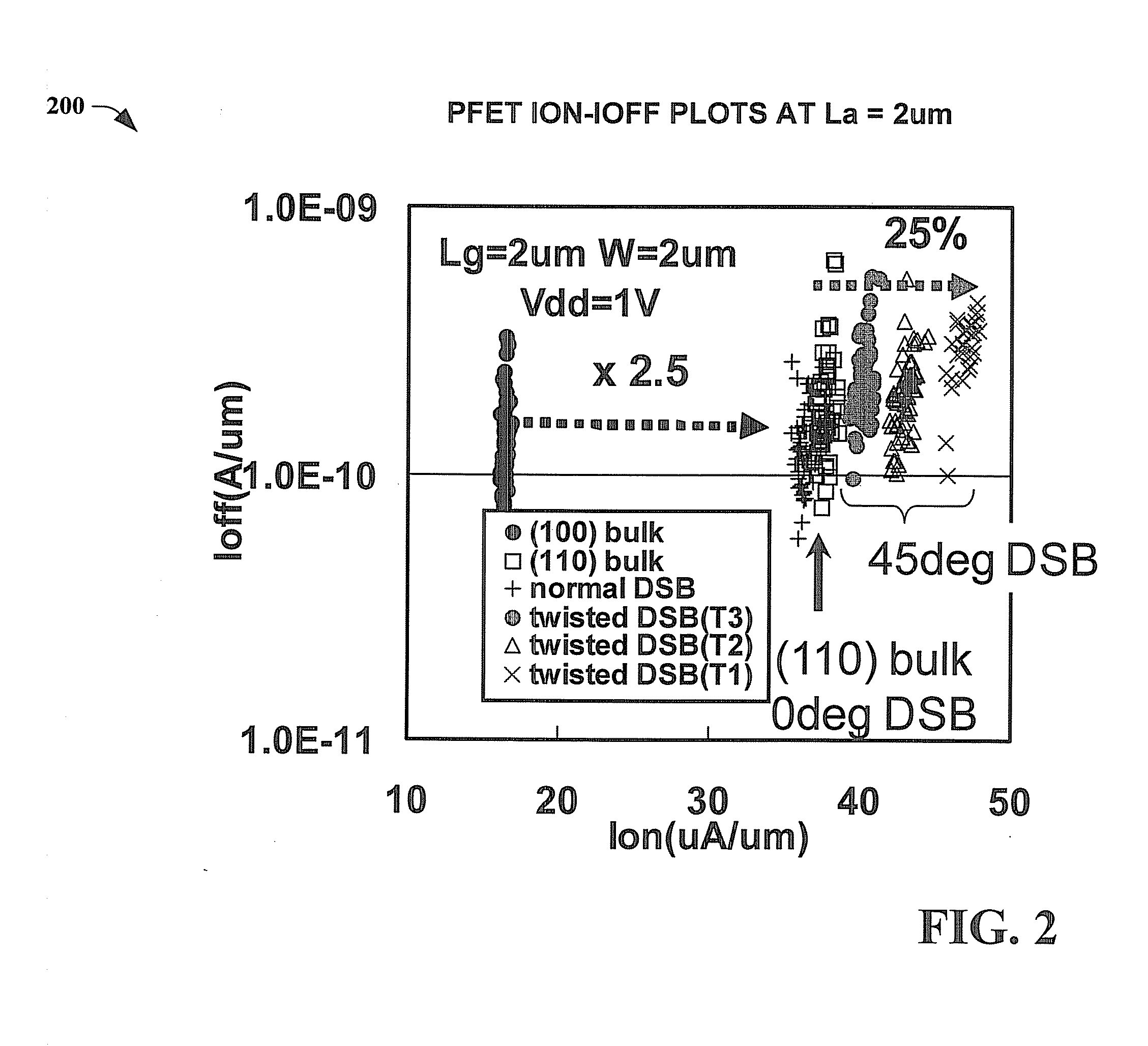

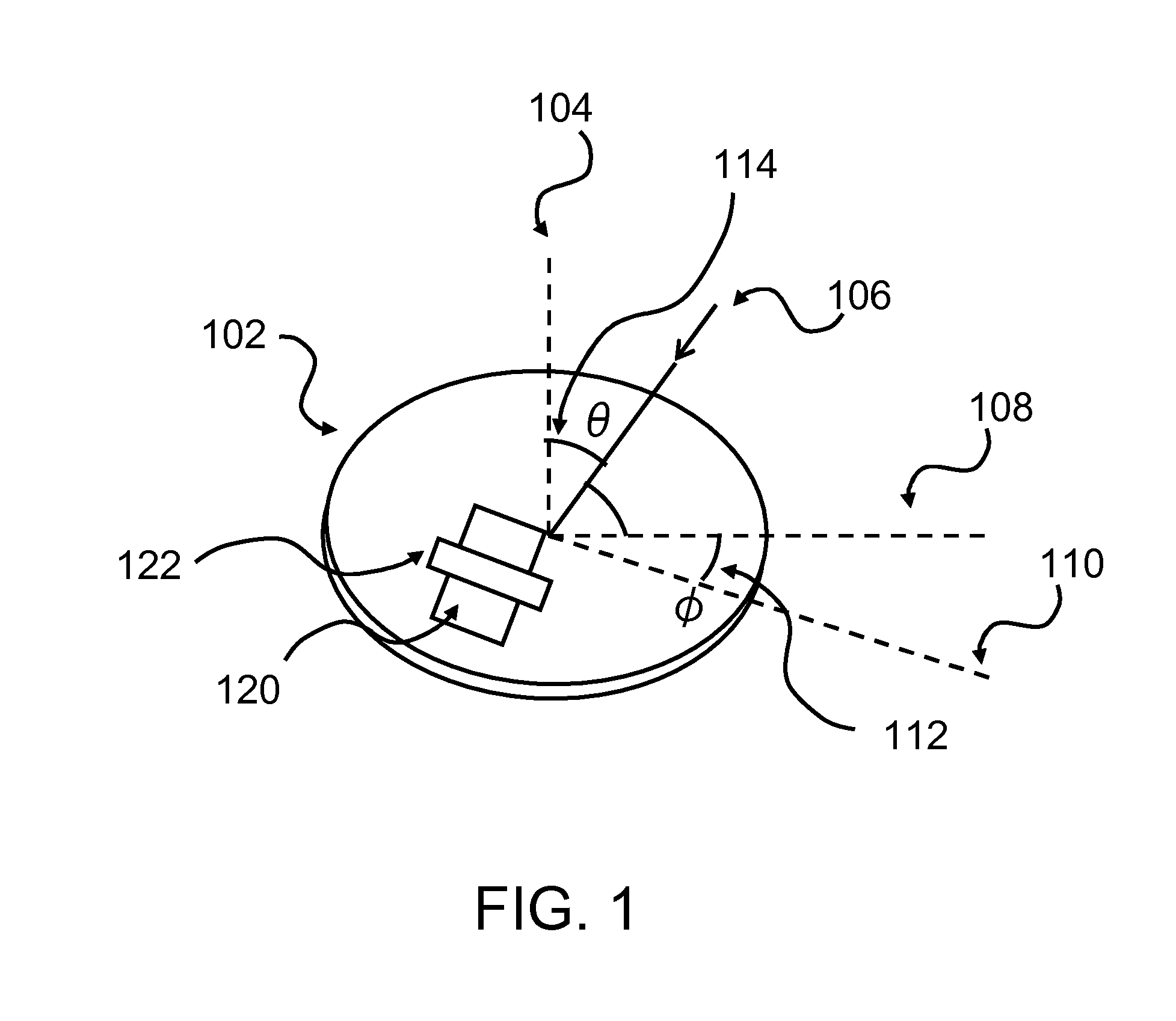

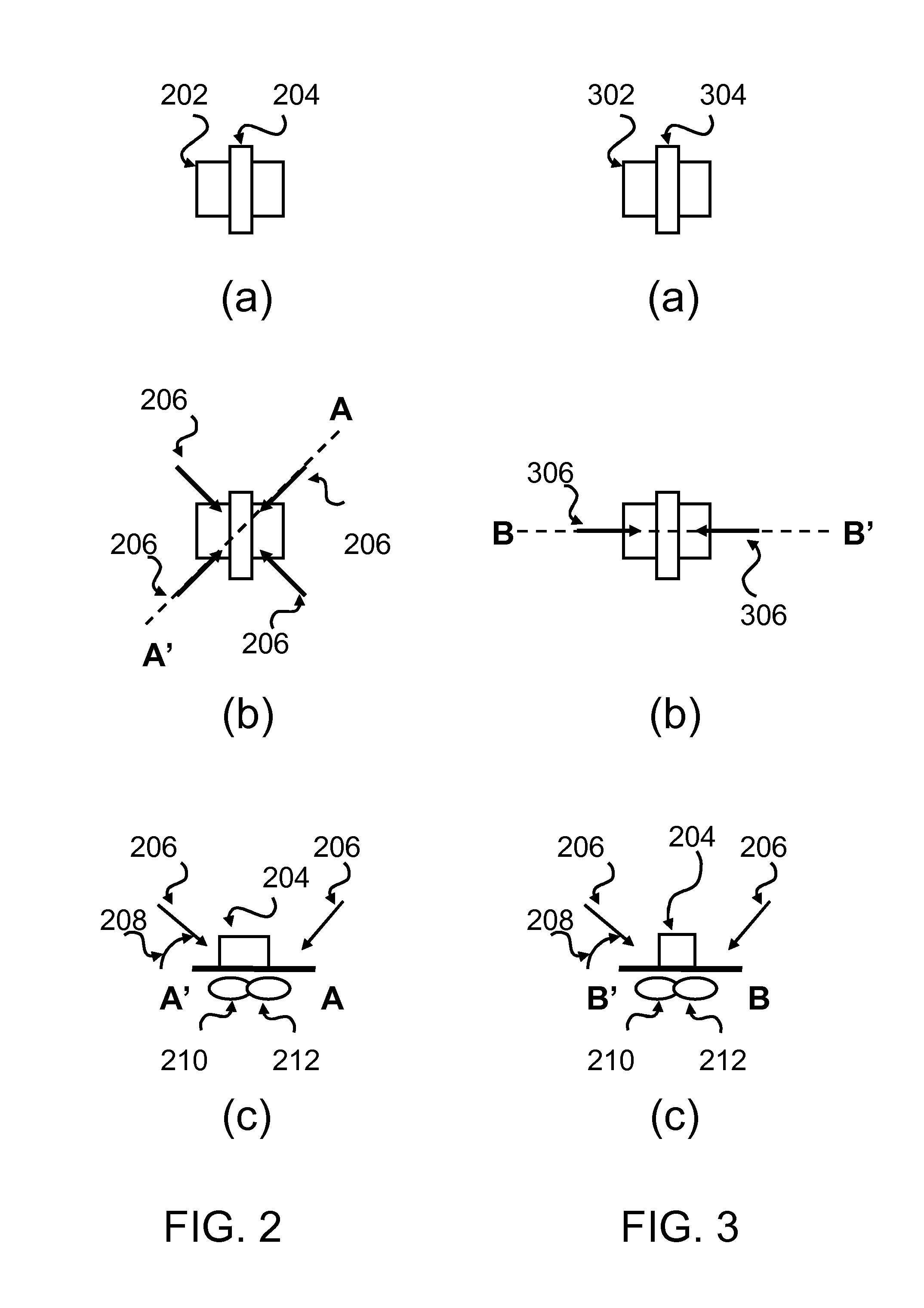

Semiconductor device on direct silicon bonded substrate with different layer thickness

InactiveUS20100327395A1High hole mobilityReduce junction leakageTransistorSolid-state devicesLayer thicknessSemiconductor

A Direct Silicon Bonded substrate can include a first substrate and a second substrate in which the second substrate can be rotated to an azimuthal twist angle of 45 degrees in comparison to the first substrate. Disclosed are a semiconductor device and a method for making a semiconductor device that includes a DSB substrate with an adjusted thickness based upon the threshold voltage (Vt). In other words, a thicker substrate or layer can correspond to a high threshold voltage (HVt) and a thinner substrate or layer can correspond to a low threshold voltage (LVt) in order to improve mobility in LVt devices.

Owner:KK TOSHIBA

Method for fabricating high-gain MOSFETs with asymmetric source/drain doping for analog and RF applications

Owner:IBM CORP

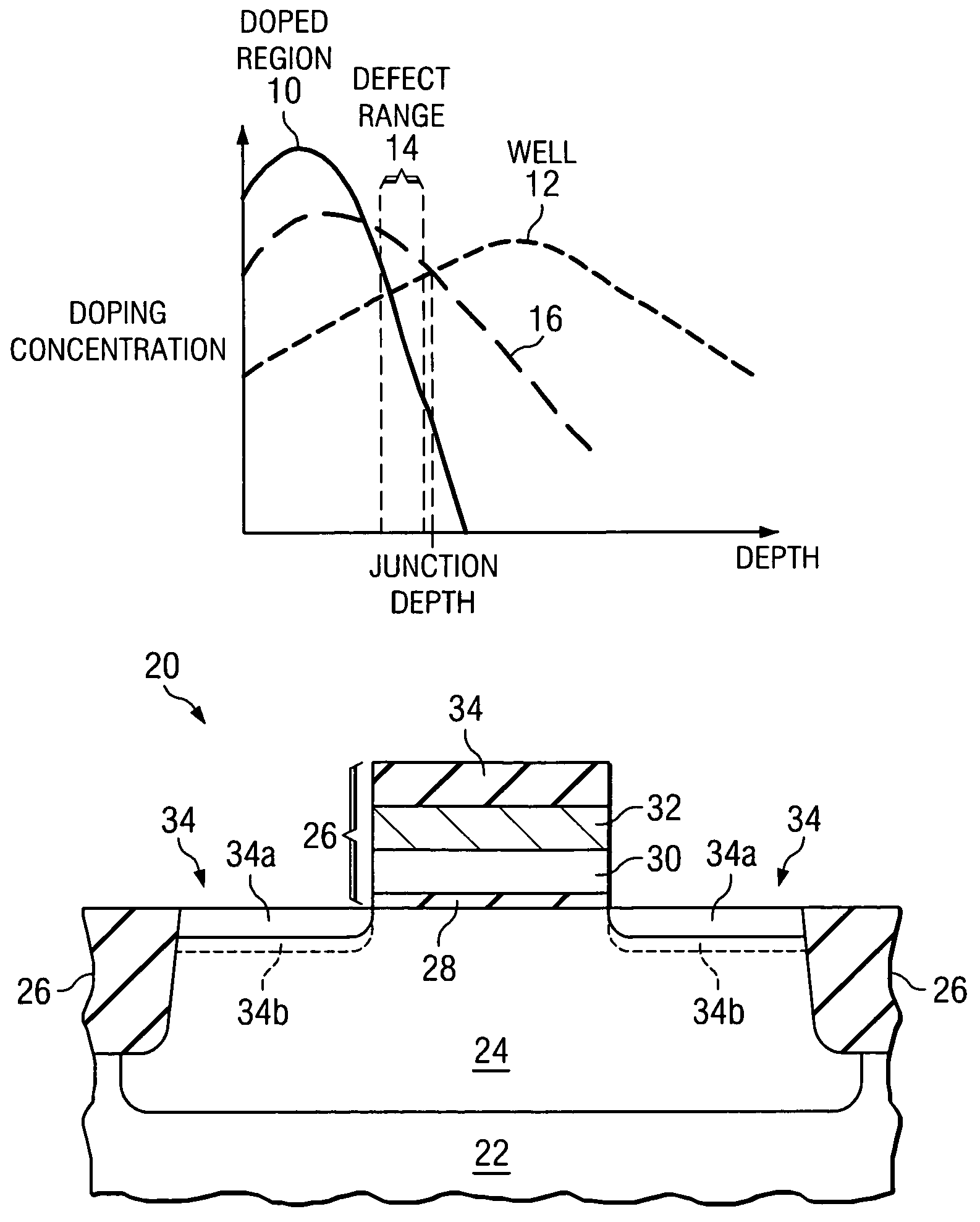

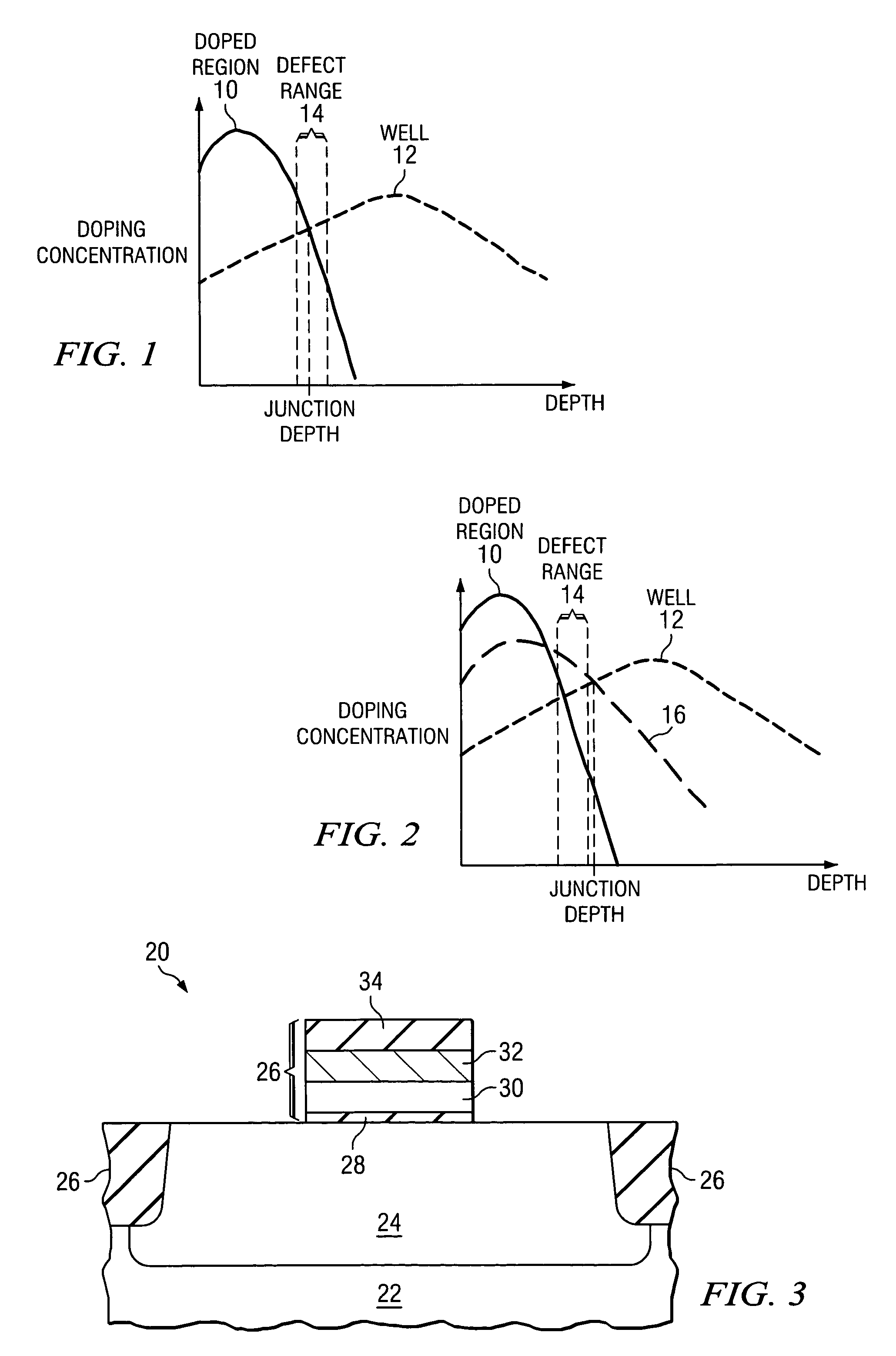

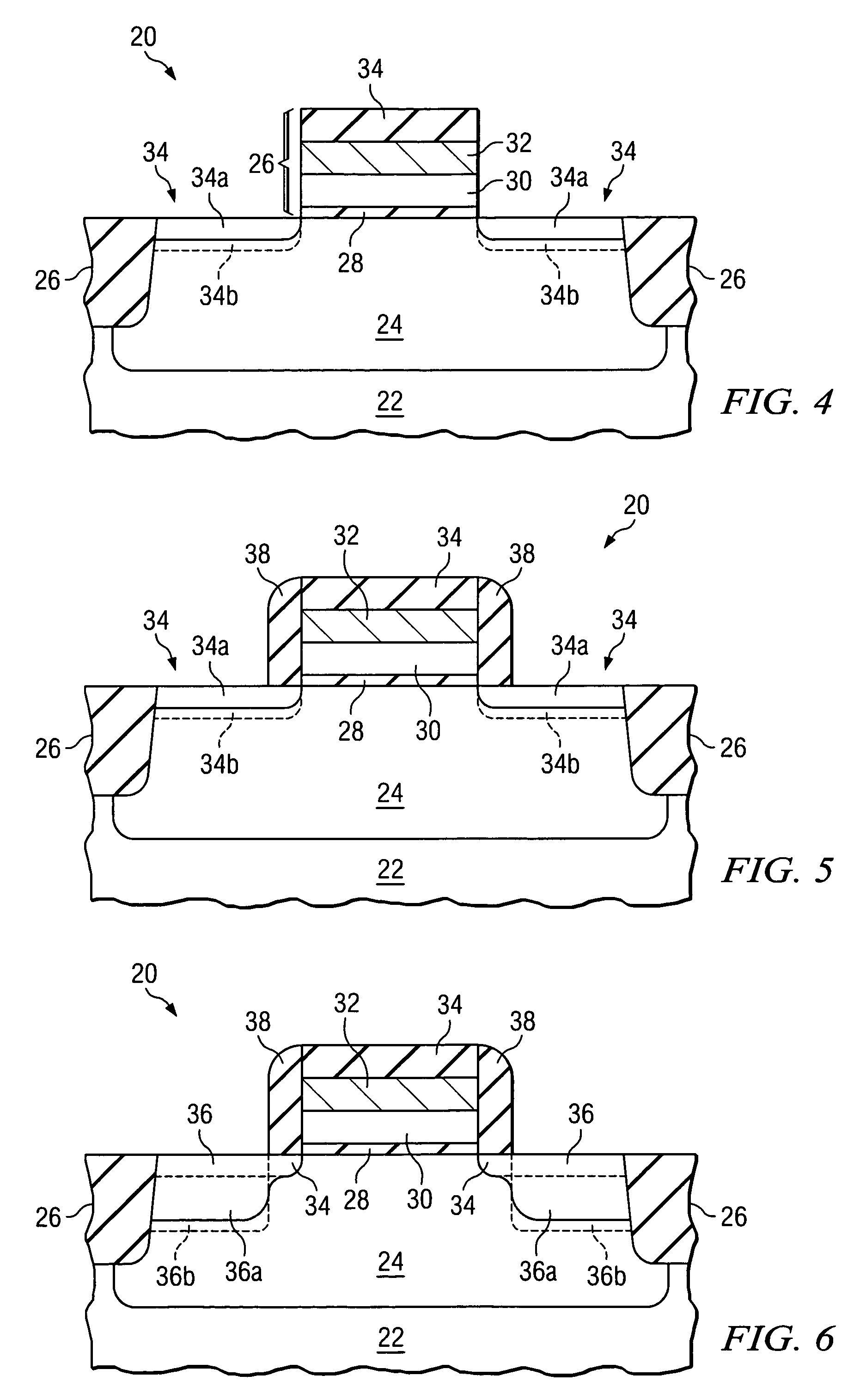

Implantation process in semiconductor fabrication

ActiveUS7172954B2Small diffusionSmoothens junctionTransistorSemiconductor/solid-state device manufacturingDopantIon implantation

A semiconductor device is formed by performing an amorphizing ion implantation to implant dopants of a first conductivity type into a semiconductor body. The first ion implantation causes a defect area (e.g., end-of-range defects) within the semiconductor body at a depth. A non-amorphizing implantation implants dopants of the same conductivity type into the semiconductor body. This ion implantation step implants dopants throughout the defect area. The dopants can then be activated by heating the semiconductor body for less than 10 ms, e.g., using a flash anneal or a laser anneal.

Owner:INFINEON TECH AG

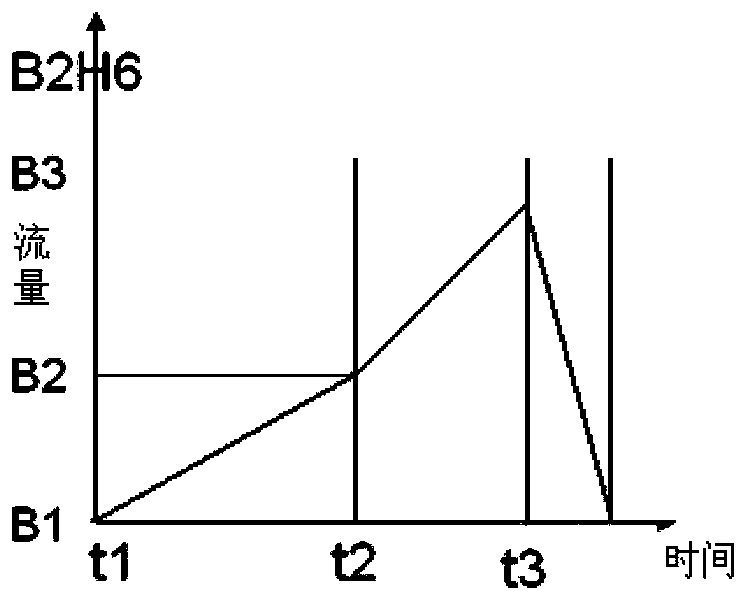

PMOS source and drain formation method

ActiveCN103681278AImprove performanceProlonged ventilation timeSemiconductor/solid-state device manufacturingSemiconductor devicesIon implantationSemiconductor

The invention relates to a PMOS source and drain formation method which includes: a semiconductor substrate which at least includes a gate structure is provided; and grooves are formed at the two sides of a gate and epitaxial growth of SiGeB layers is performed in the grooves. The method is characterized in that during epitaxial growth of SiGe, B is doped at an original position at the same time so as to facilitate epitaxial growth of the SiGeB layers in the grooves. The method includes the following steps specifically: 1) inletting B2H6 gas and controlling gas flow to increase from B1 to B2 and time to be T1; 2) increasing the gas flow of B2H6 from B2 to B3 and time to be T2; 3) adjusting the flow of B2H6 gas to drop from B3 to 0 and time to be T3, wherein T2 is > T3; and the SiGeB layers are the B-doped source and drain of in a PMOS. The method is capable of skipping a separated ion injection process so that stress in a channel region can be maintained and thus a device obtained through manufacturing is better in performance.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Semiconductor device and method of fabricating the same

InactiveUS20090289285A1Reduce junction leakageLow resistivityTransistorSemiconductor/solid-state device manufacturingHigh concentrationImpurity

Provided is a semiconductor device including a transistor that has a silicide layer formed over a semiconductor substrate. The gate electrode of each transistor is composed of a polysilicon electrode and the silicide layer formed thereon. Each transistor further has source / drain impurity-diffused layers composed of low-concentration doped regions and high-concentration doped regions, and silicide layers formed over the source / drain impurity-diffused layers. The surface of each silicide layer is positioned above the surface of the semiconductor substrate. The silicide layers contain a silicidation-suppressive metal, and have a concentration profile of the silicidation-suppressive metal over a region of the silicide layers ranging from the surface to a predetermined depth, such as increasing the concentration from the surface of each silicide layer in the depth-wise direction of the semiconductor substrate.

Owner:RENESAS ELECTRONICS CORP

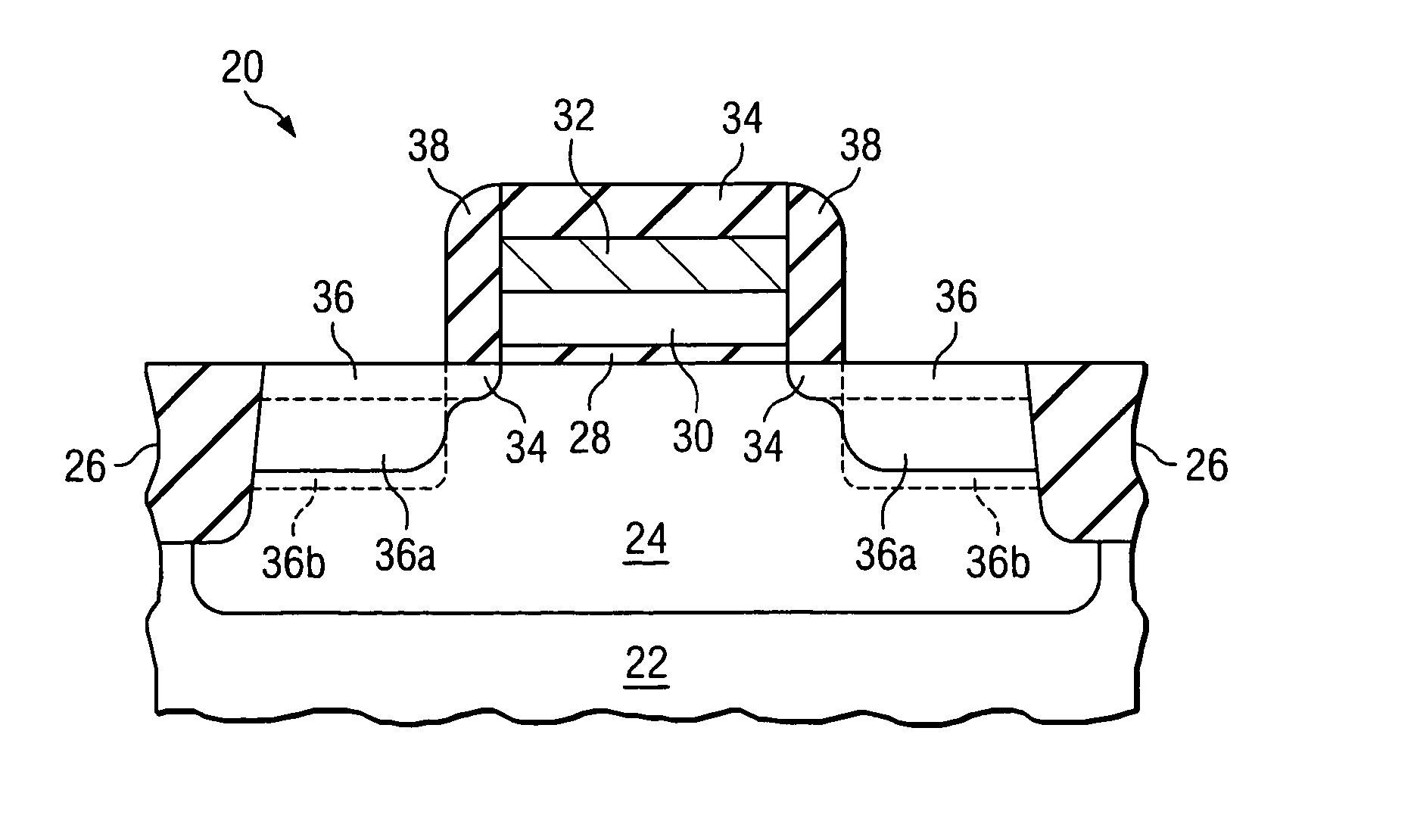

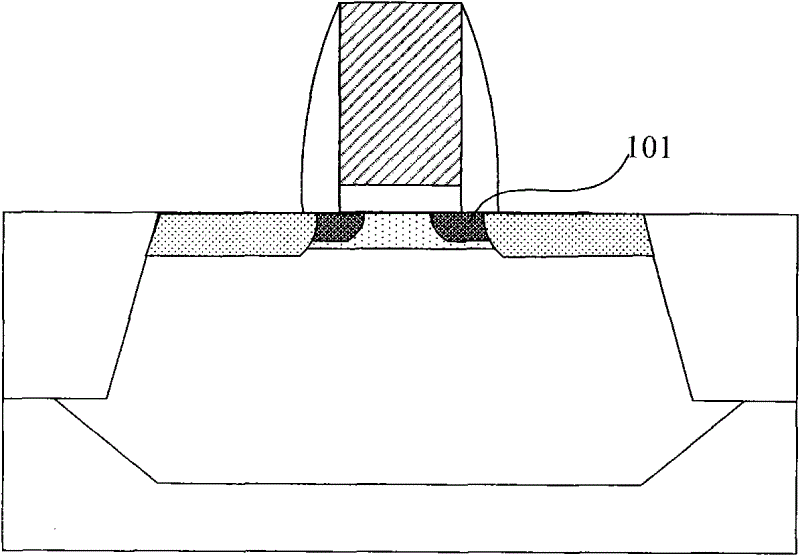

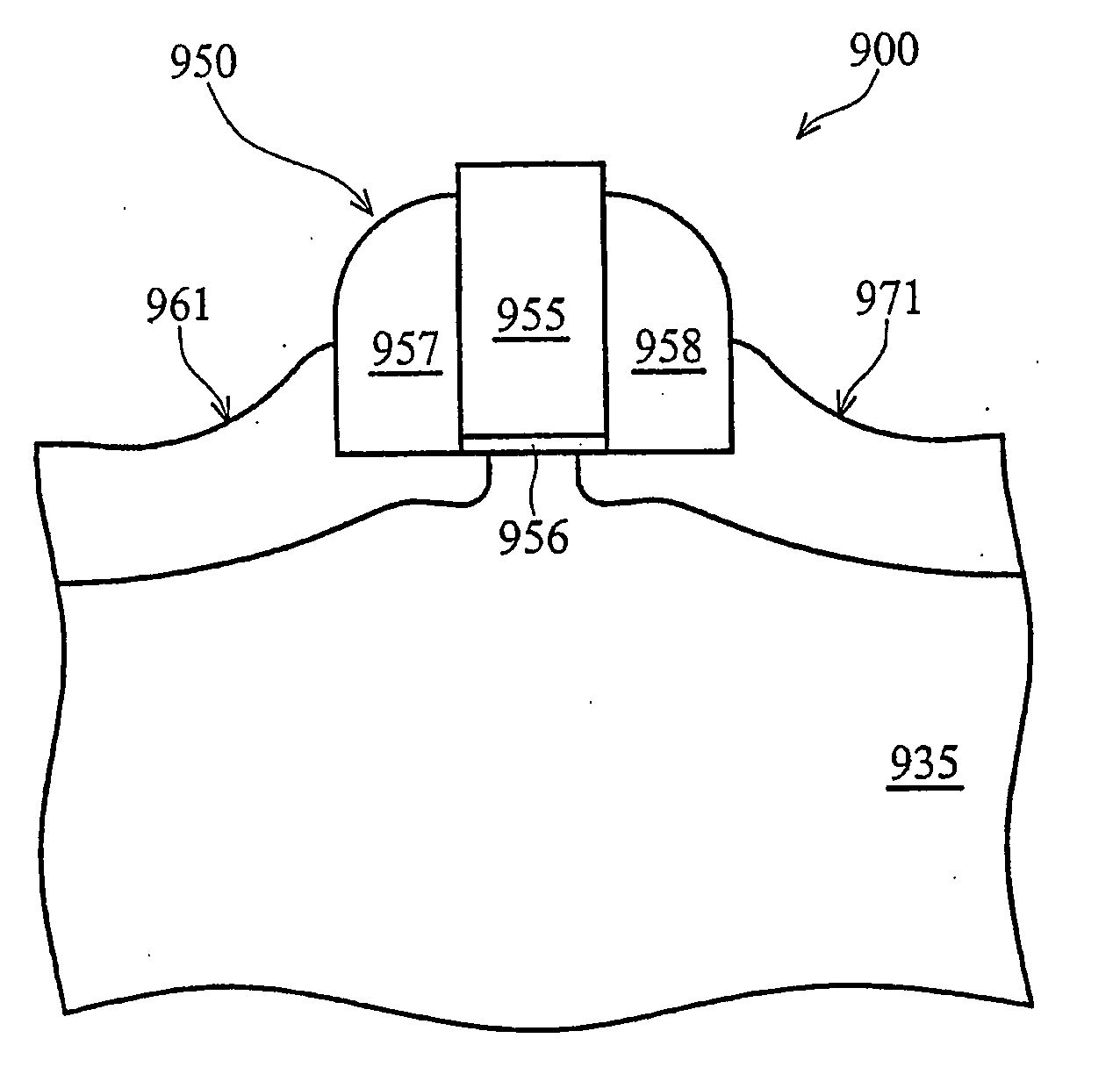

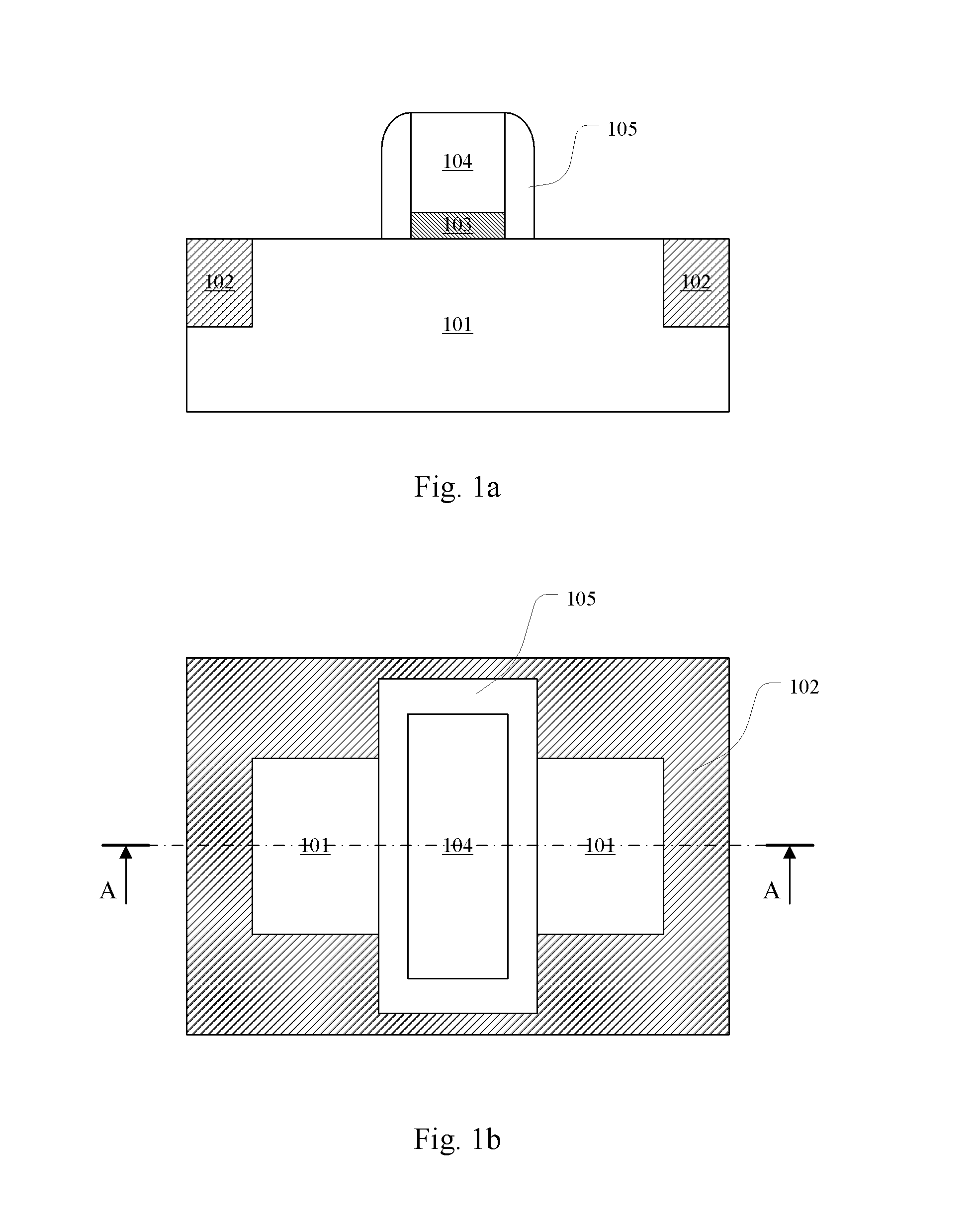

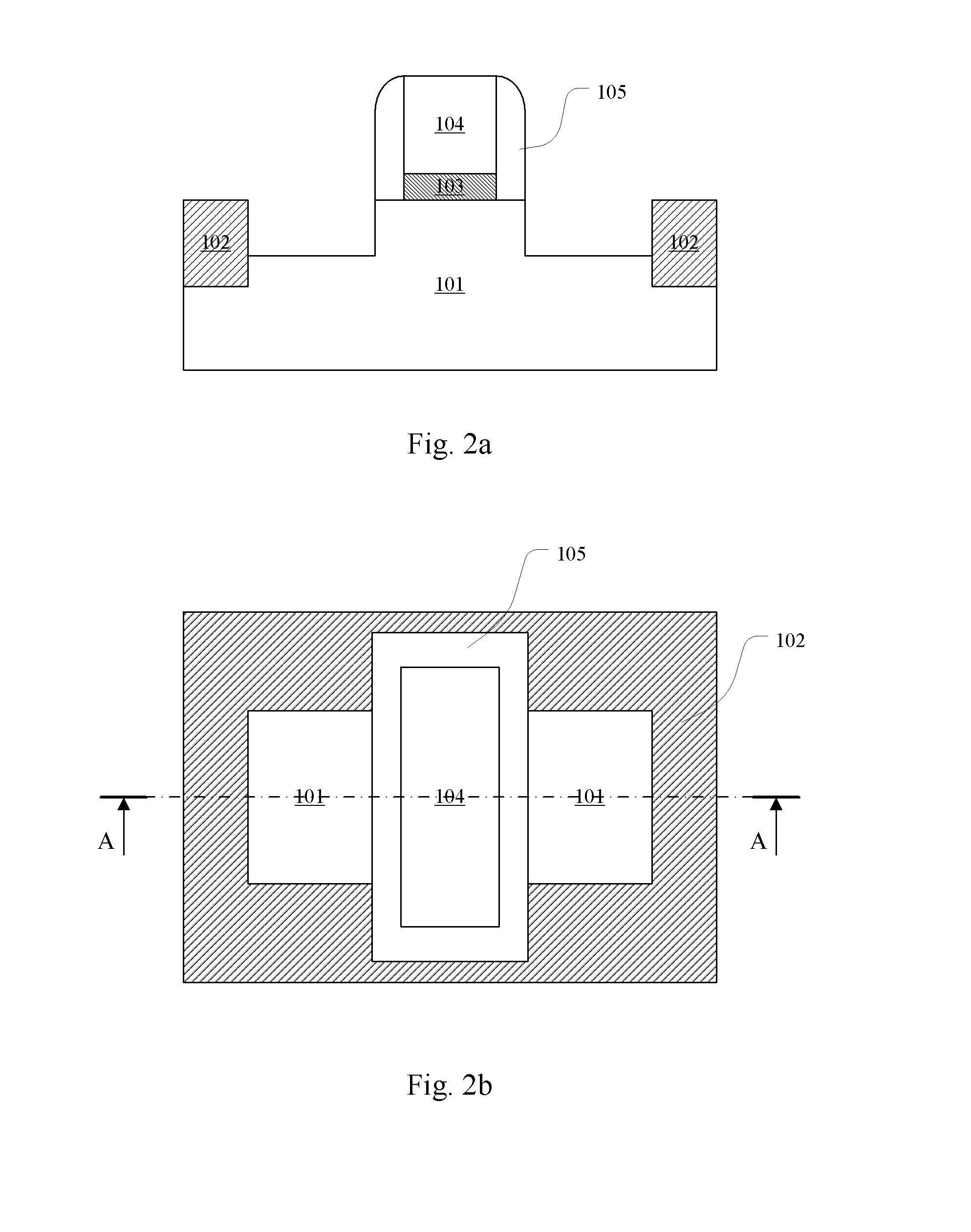

Gated diode with non-planar source region

ActiveUS20080237746A1Lower maximum electric fieldReduce junction leakageSemiconductor/solid-state device manufacturingDiodeDopantHigh elevation

A gated-diode semiconductor device or similar component and a method of fabricating the device. The device features a gate structure disposed on a substrate over a channel and adjacent a source and a drain. The top of the source or drain region, or both, are formed so as to be at a higher elevation, in whole or in part, than the bottom of the gate structure. This configuration may be achieved by overlaying the gate structure and substrate with a profile layer that guides a subsequent etch process to create a sloped profile. The source and drain, if both are present, may be symmetrical or asymmetrical. This configuration significantly reduces dopant encroachment and, as a consequence, reduces junction leakage.

Owner:TAIWAN SEMICON MFG CO LTD

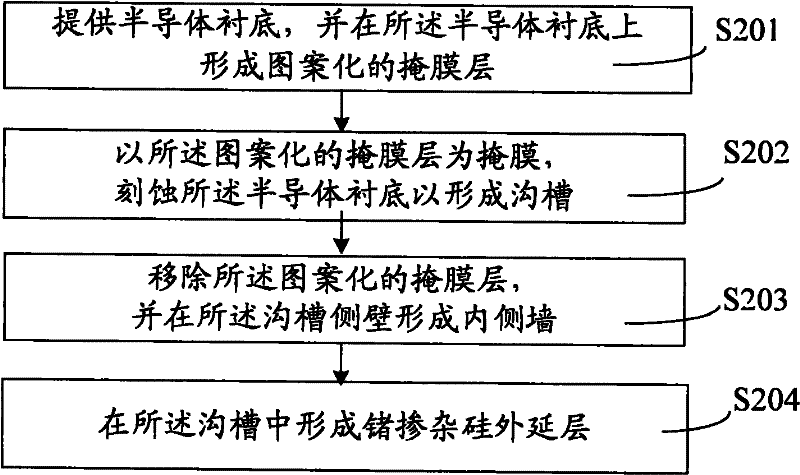

Manufacturing method for MOS transistor

ActiveCN102693915AImprove mobilityInhibition of Radial DiffusionSemiconductor/solid-state device manufacturingSemiconductor devicesRadial diffusionEpitaxy

The invention provides a manufacturing method for an MOS transistor. On one hand, charge mobility is increased by germanium-doped silicon epitaxy to inhibit hot carrier's effect; on the other hand, by an inner wall with a lower top, radial diffusion is inhibited in lightly doped source / drain (LDD) region after ion implantation and the depth of the lightly doped source / drain (LDD) extension region is controlled, which allows ultra-shallow junction shallower. Therefore longer effective channel is obtained, HCI effect is effectively inhibited, SCE and RSCE effects are significantly improved and breakdown effect and electric leakage caused by breakdown effect brought by shrunk device size are reduced, enabling the production of even shallower source / drain region junction in the ultra-shallow junction technology.

Owner:SEMICON MFG INT (SHANGHAI) CORP

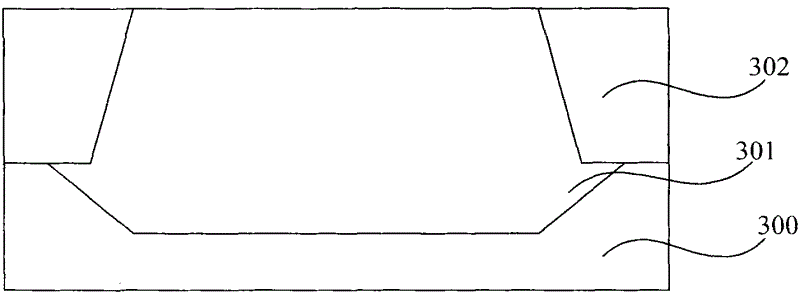

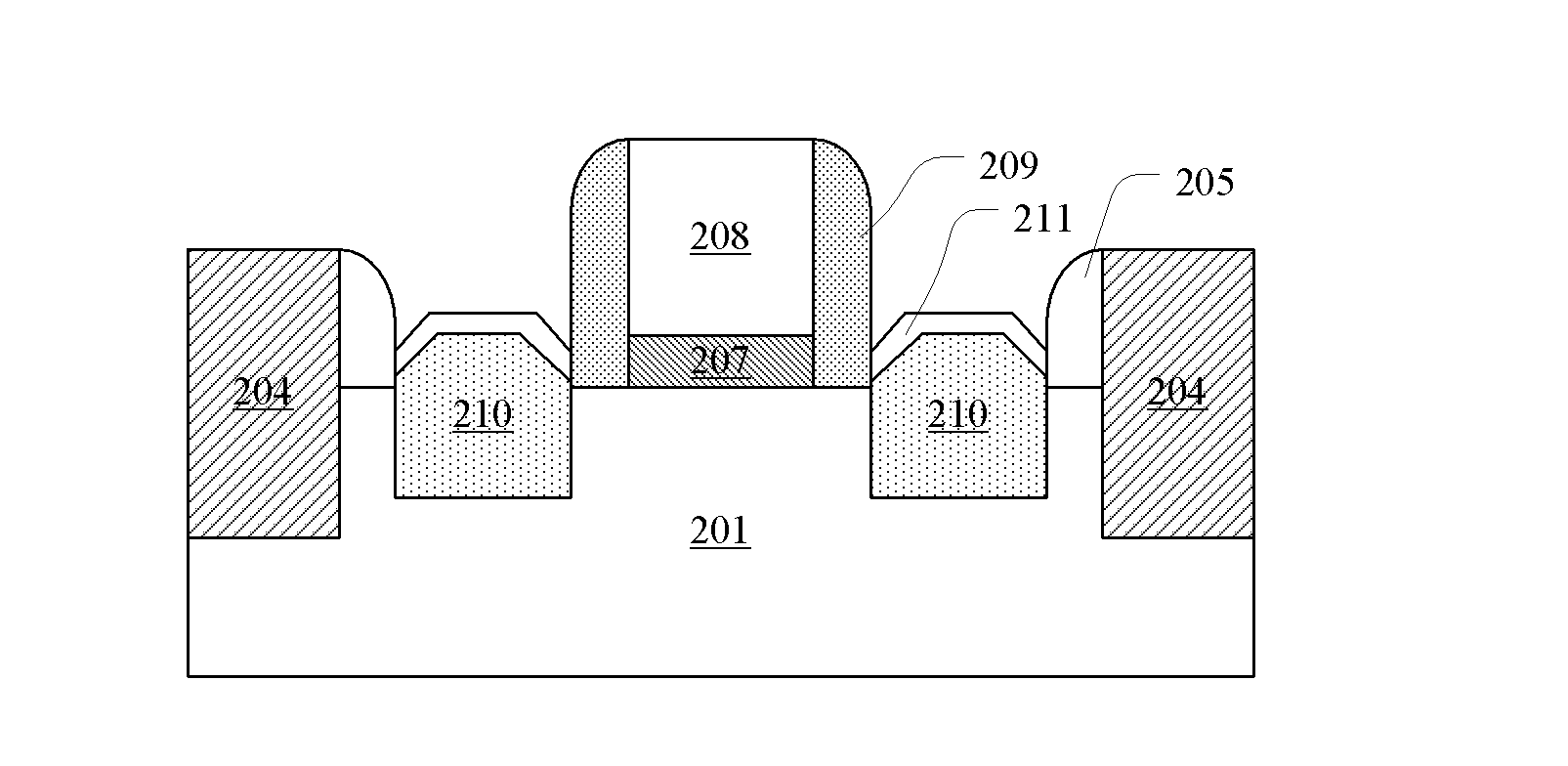

Method of manufacturing mosfet

ActiveUS20150295068A1Reduce edge effectsIncreased channel stressSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETEngineering

Provided is a method for manufacturing a MOSFET, including: forming a shallow trench isolation (STI) in a semiconductor substrate to define an active region for the MOSFET; performing etching with the STI as a mask, to expose a surface of the semiconductor substrate, and to protrude a portion of the STI with respect to the surface of the semiconductor substrate, resulting in a protruding portion; forming a first spacer on sidewalls of the protruding portion; forming a gate stack on the semiconductor substrate; forming a second spacer surrounding the gate stack; forming openings in the semiconductor substrate with the STI, the gate stack, the first spacer and the second spacer as a mask; epitaxially growing a semiconductor layer with a bottom surface and sidewalls of each of the openings as a growth seed layer; and performing ion implantation into the semiconductor layer to form source and drain regions.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI