MOS transistor and forming method thereof

A technology of MOS transistors and transistors, applied in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve problems such as increasing the threshold voltage of NMOS transistors, affecting reliability, and degrading semiconductor device performance, so as to reduce substrate leakage current , improve life, reduce the effect of hot carrier effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

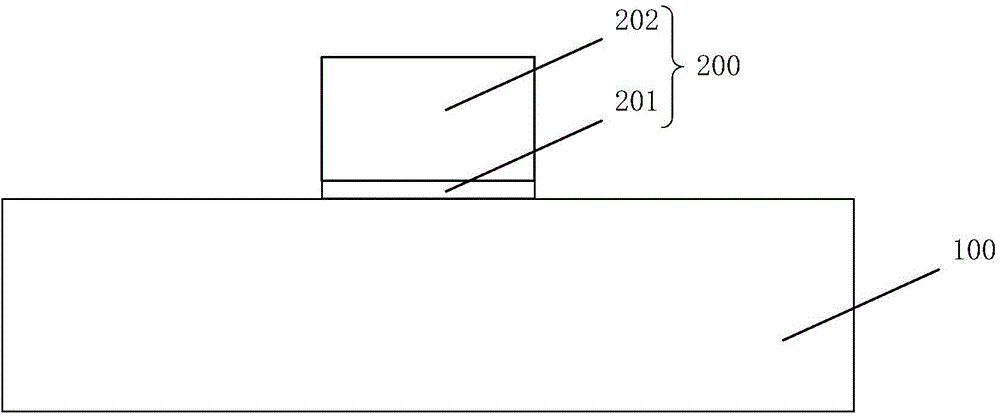

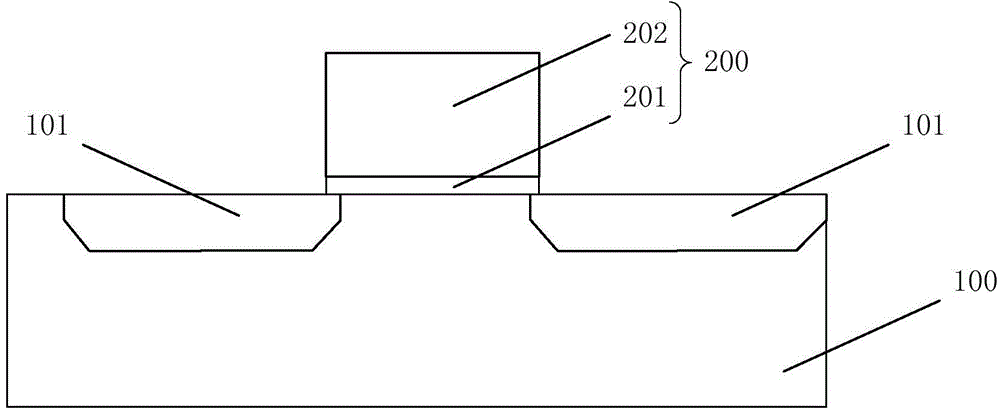

[0028] As mentioned in the background art, the leakage current of the MOS transistor formed in the prior art is relatively high, and the hot carrier effect is significant, so that the performance of the MOS transistor needs to be further improved.

[0029] The short-channel effect of the transistor can be reduced by increasing the channel length to reduce the leakage current of the MOS transistor, but increasing the channel length will increase the channel on-resistance of the MOS transistor, thereby affecting the switching speed of the MOS transistor.

[0030] Research has found that pocket ion implantation can also be carried out in the semiconductor substrate on both sides of the gate structure. The type of doping ions used in the pocket ion implantation is opposite to that of the MOS transistor, and a pocket ion implantation is formed between the source and drain regions and the channel region. The pocket region can suppress the leakage current of the MOS transistor. In or...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More