Semiconductor device and manufacturing method thereof

A semiconductor and device technology, applied in the field of semiconductor power devices, can solve problems such as limited application and rising on-resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

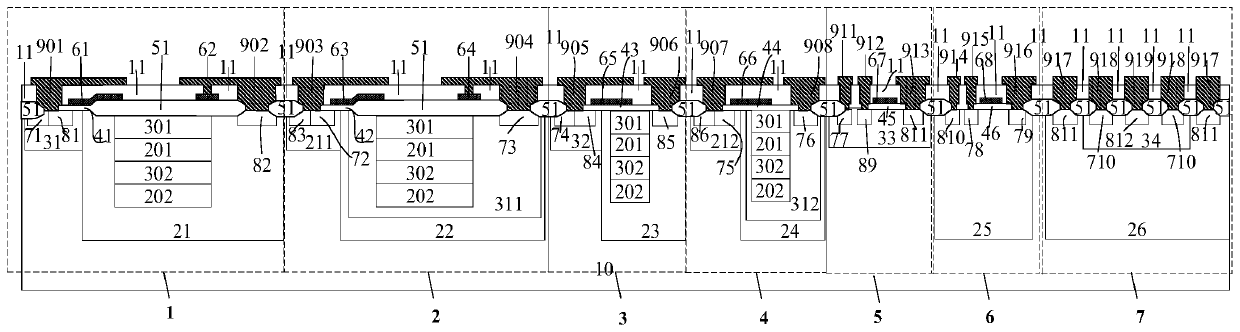

[0047] Such as figure 1As shown, a semiconductor device includes a first-type high-voltage nLDMOS device 1, a first-type high-voltage pLDMOS device 2, a second-type high-voltage nLDMOS device 3, a second-type high-voltage pLDMOS device 4, and a low-voltage NMOS device integrated on the same chip. 5. Low voltage PMOS device 6 and low voltage NPN device 7;

[0048] The first type of high-voltage nLDMOS device 1 is directly made in the p-type substrate 10, and the second n + The contact region 82 is located under the second metal electrode 902 and surrounded by the first n-type deep well 21; under the field oxide layer 51, a first p-type field drop layer 301, a first n-type heavily doped layer 201, a second p-type type drop field layer 302, the second n-type heavily doped layer 202, and the first p-type drop field layer 301, the first n-type heavily doped layer 201, the second p-type drop field layer 302, the second n-type heavily doped layer The doped layers 202 are all surro...

Embodiment 2

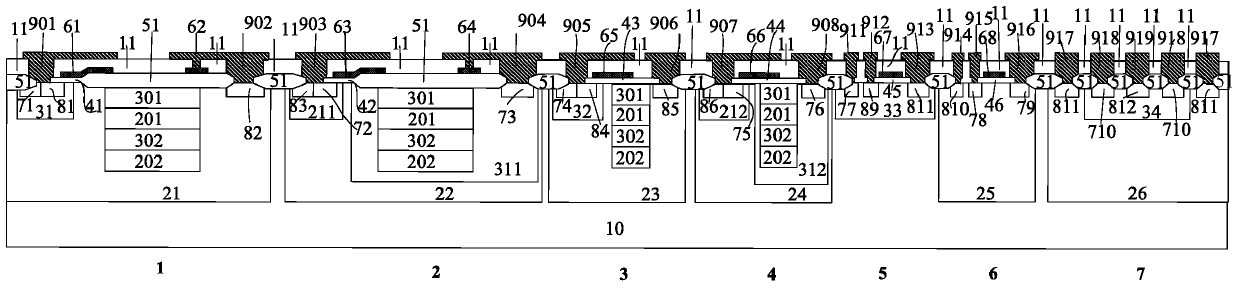

[0073] The difference between this embodiment and Embodiment 1 is: the first n-type well 211 of the device is in the second n-type deep well 22, and the second n-type well 212 is in the fourth n-type well region 24, as figure 2 shown.

Embodiment 3

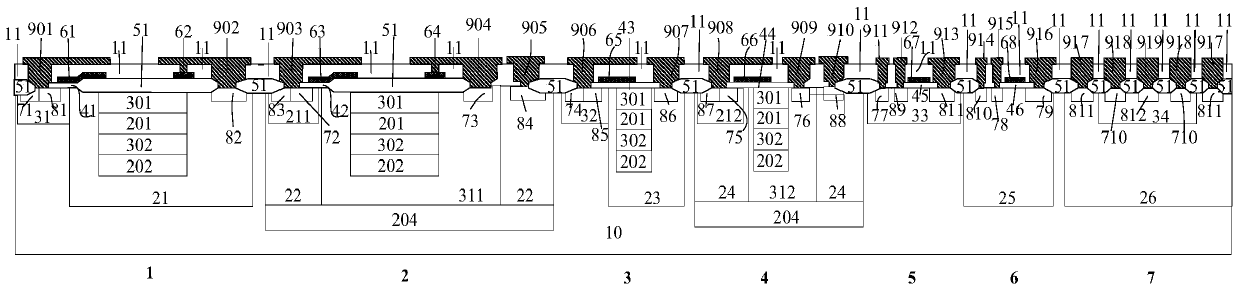

[0075] The difference between this embodiment and Embodiment 2 is that the fourth n+ contact region 84 is surrounded by the second n-type deep well 22, and the first p-type deep well 311 of the device is surrounded by the second n-type well region 22 and the left and right sides of the device. Surrounded by the n-type buried layer 204 at the bottom, the eighth n+ contact region 88 is located in the fourth n-type deep well 24, and the second p-type deep well 312 is surrounded by the fourth n-type well region 24 on the left and right sides and the n-type buried well region at the bottom. Layer 204 surrounds, such as image 3 shown.

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More