Full-surrounded gate synapse transistor, preparation method and circuit connection method

A technology that fully surrounds gates and transistors. It is used in the manufacture of transistors, circuits, and semiconductor/solid-state devices. It can solve the problems of small switching current ratio, large device power consumption, and large channel leakage current, and achieve the reduction of channel leakage current. Small, improve the control ability, the effect of large switching current ratio

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

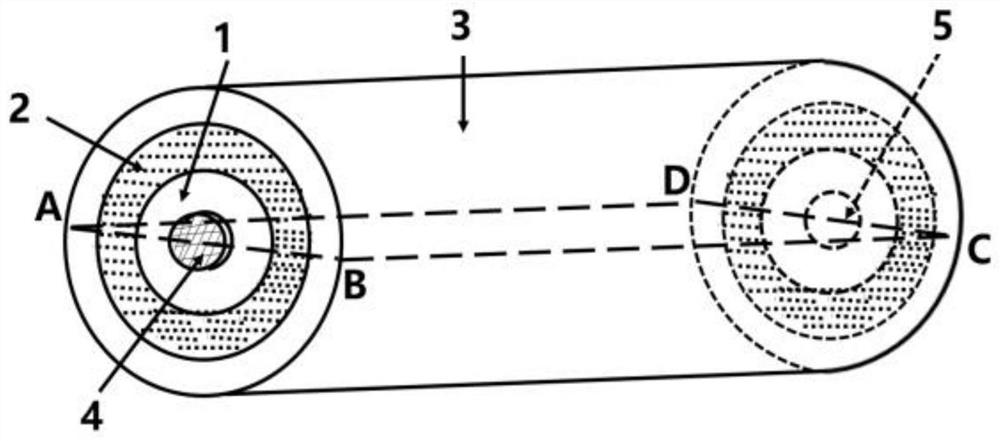

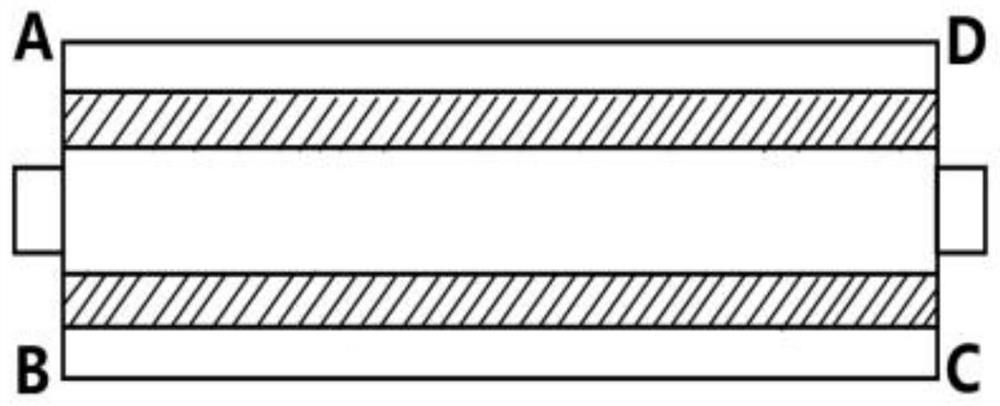

[0041] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only some, not all, embodiments of the present invention. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

[0042] The object of the present invention is to provide a fully-enclosed gate synaptic transistor, a preparation method and a circuit connection method. In the fully-enclosed gate synaptic transistor, the gate wraps the insulating layer and the active layer so that the gate voltage The channel current can be controlled from various directions, the control ability of the gate electrode can be improved, and the power consumption of the device can be reduced.

...

PUM

| Property | Measurement | Unit |

|---|---|---|

| height | aaaaa | aaaaa |

| height | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More