3D Quantum Cellular Automata Adder

A technology of quantum cells and automata, applied in instruments, electrical digital data processing, digital data processing components, etc., can solve the problems of high power consumption and large area, and achieve the effect of low power consumption and less hardware resources

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

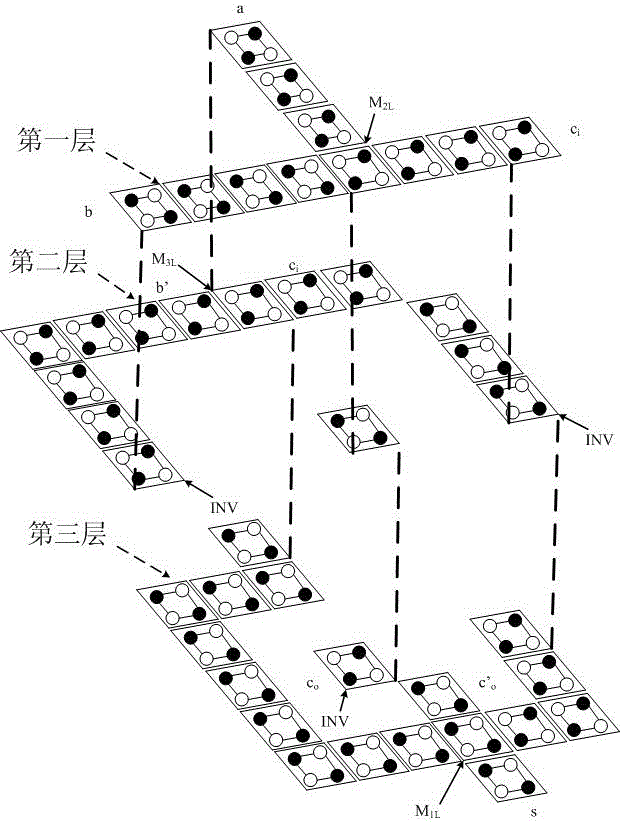

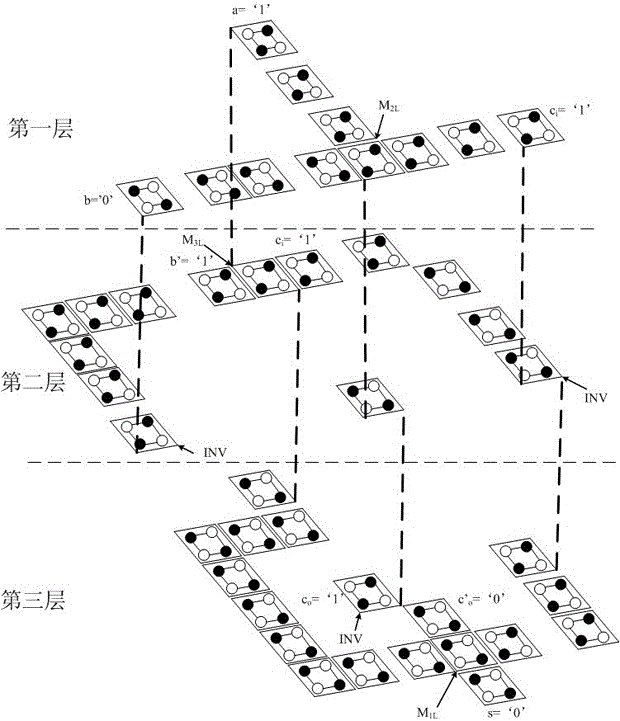

[0044] Below in conjunction with accompanying drawing, technical scheme of the present invention is described in further detail:

[0045] Such as figure 1 and figure 2 As shown, the present invention discloses a three-dimensional quantum cellular automata adder, including seven quantum cellular automata connections, a two-dimensional majority logic gate, a two-layer three-dimensional majority logic gate, a three-layer three-dimensional multiple logic gates, first to fourth three-dimensional inverters, a first two-dimensional inverter and a second two-dimensional inverter;

[0046] The three-dimensional quantum cellular automaton adder is distributed on three circuit layers and has three input terminals and two output terminals;

[0047]The two-layer three-dimensional majority logic gate includes five cells, four of which are located in the upper circuit and are T-shaped, and the other cell is located in the middle circuit and is directly below the junction of the upper T-sh...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More