Patents

Literature

134 results about "Neuron circuit" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

[edit on Wikidata] An interneuron (also called internuncial neuron, relay neuron, association neuron, connector neuron, intermediate neuron or local circuit neuron) is a broad class of neurons found in the human body.

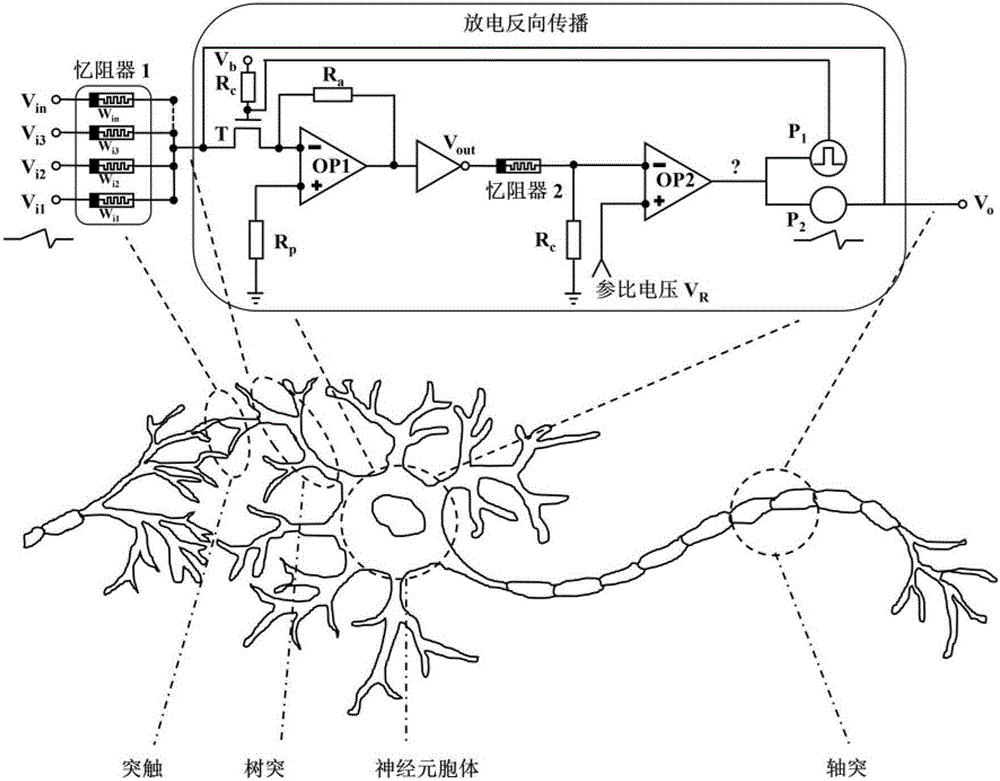

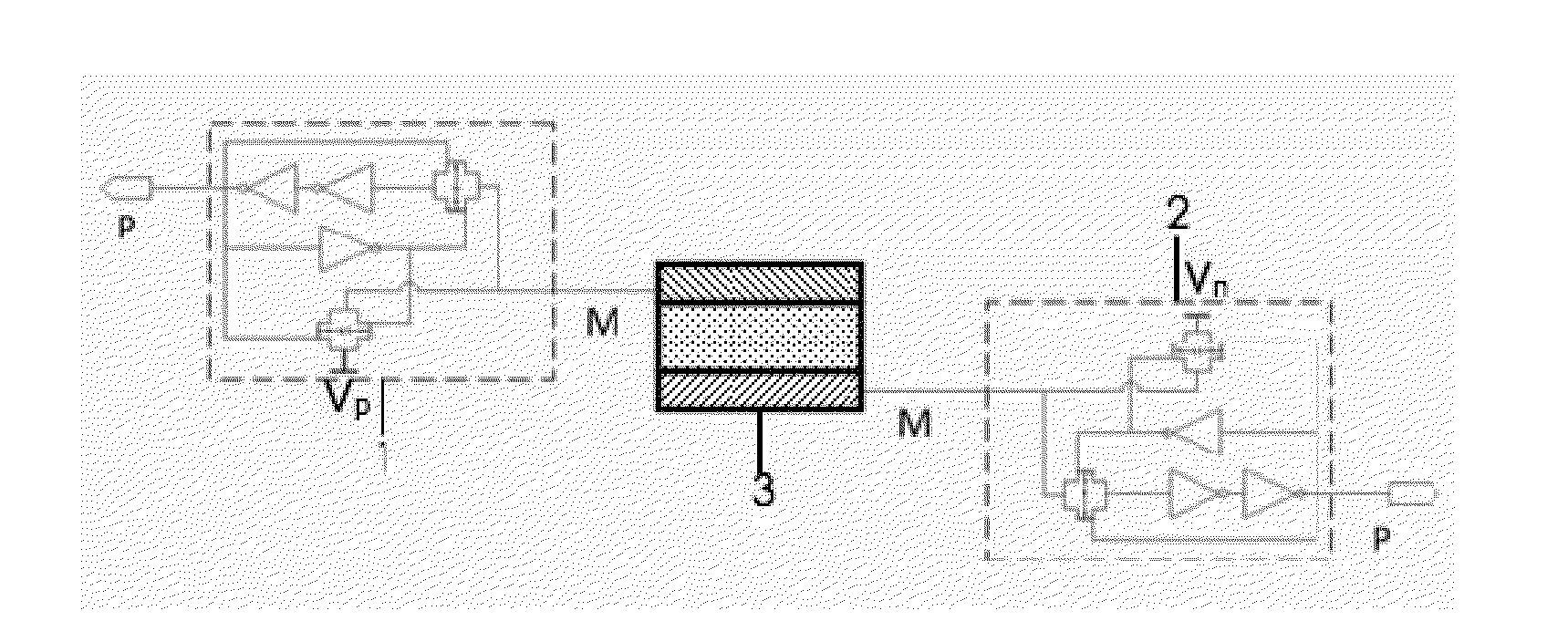

Memristor-based neuron circuit

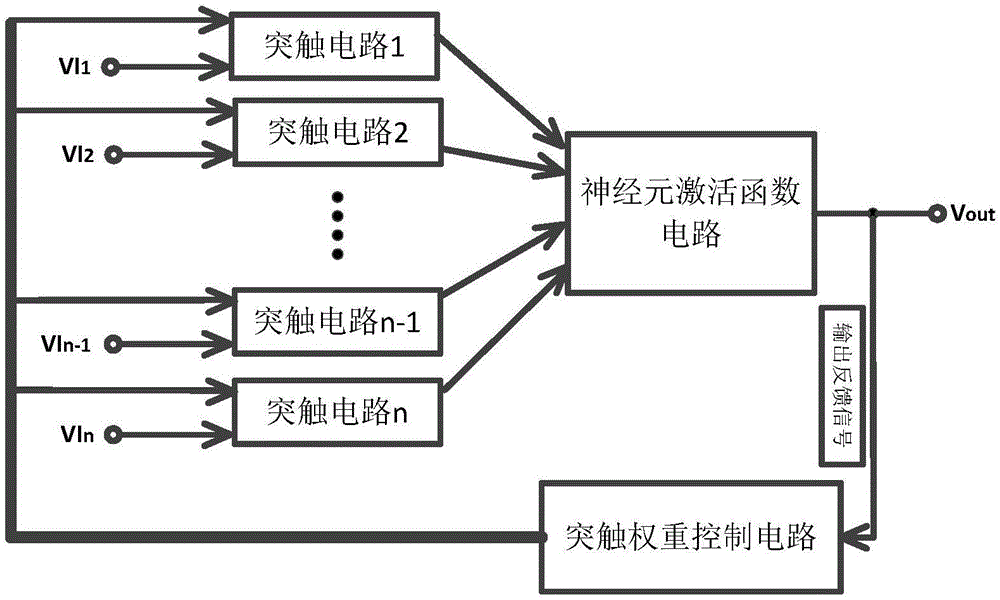

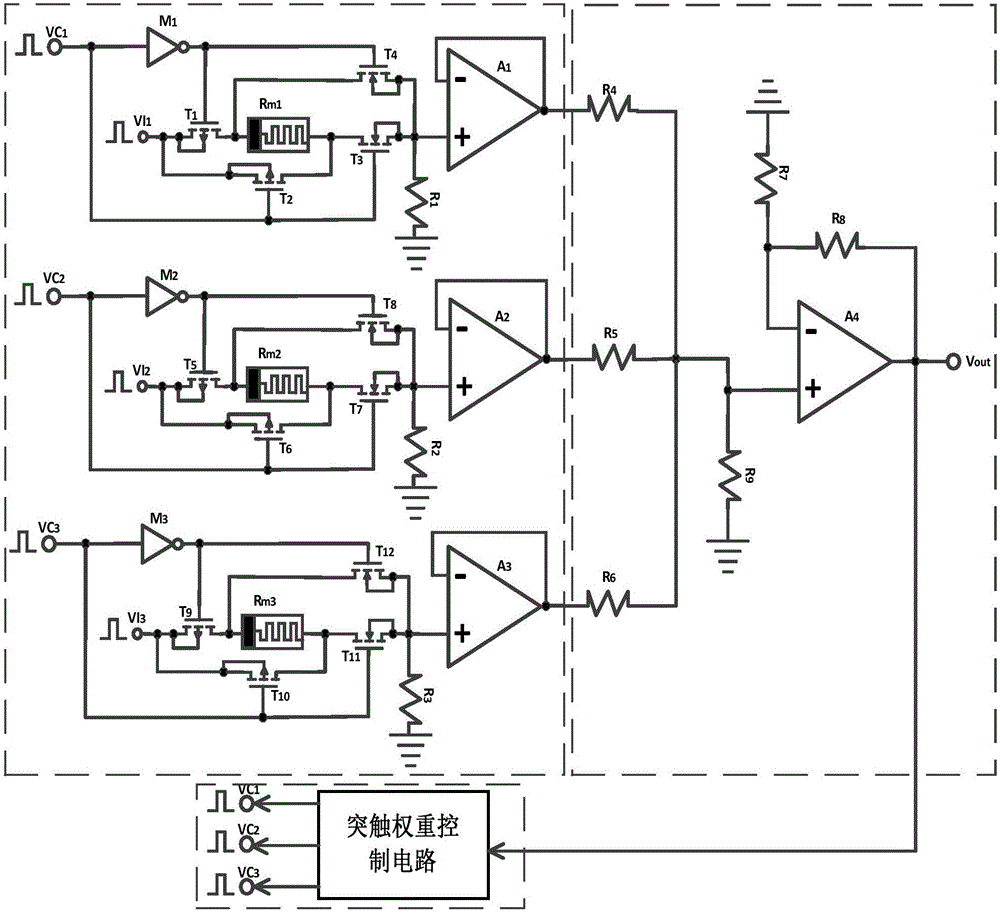

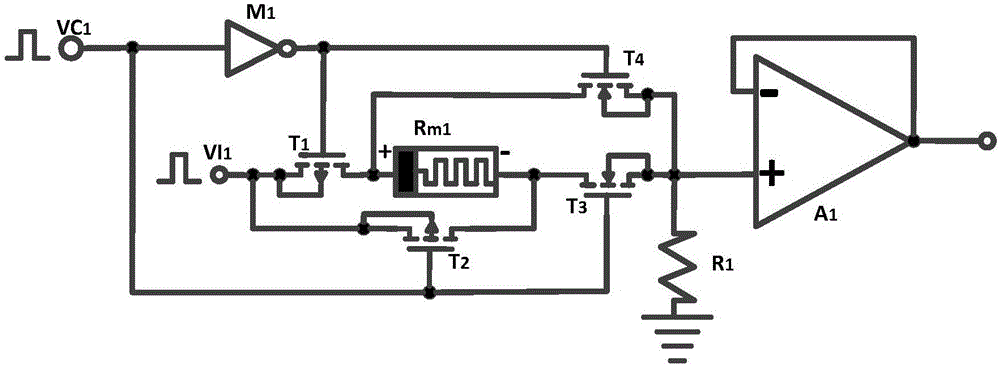

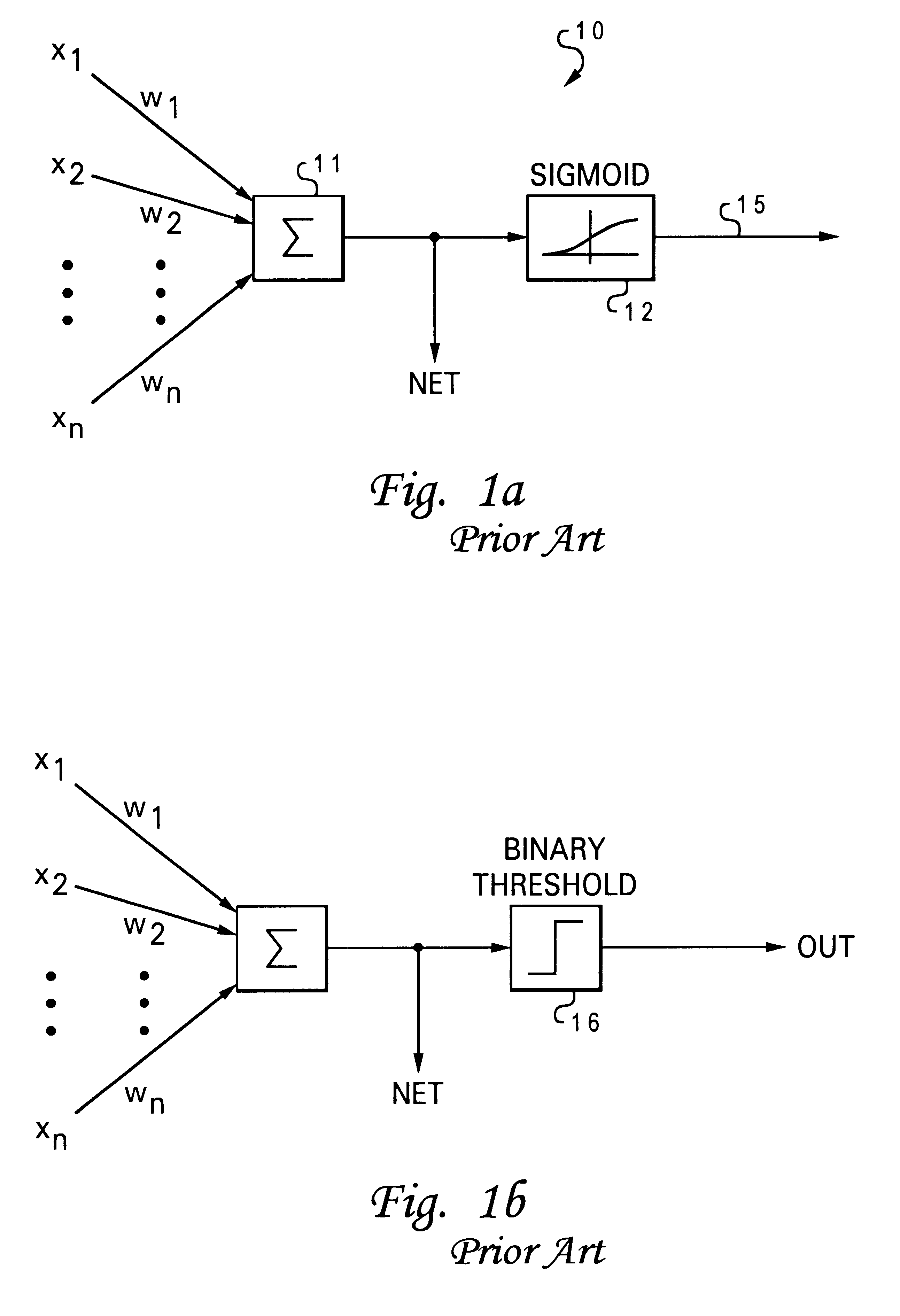

ActiveCN106815636AGood effectEasy compositionNeural architecturesPhysical realisationActivation functionNerve network

The invention discloses a memristor-based neuron circuit, comprising a synaptic circuit, a neuron activation function circuit and a synaptic weight control circuit. In the synaptic circuit, a memristor, under the control of four MOS tubes, changes the memristor value to simulate the change of the synaptic weight in the neuron network. The designed neuron synaptic circuit is capable of being directly connected with a digital logic electrical level so as to achieve convenient and real-time adjustment to the synaptic weight and through the use of the feature that the output voltage of an operational amplifier is restricted by the power supply voltage, the neuron circuit activation function can be realized as a saturated linear function. The neuron synaptic weight change circuit can utilize the existing CMOS micro-controller and at the same time, the micro-controller can be loaded by the neuron network algorithm to change the synaptic weight to realize corresponding functions. According to the invention, a plurality of neuron circuits could be connected into a large-scale neuron network for complicated functions such as mode identification, signal processing, associated memory and non-linear mapping, etc.

Owner:HUAZHONG UNIV OF SCI & TECH

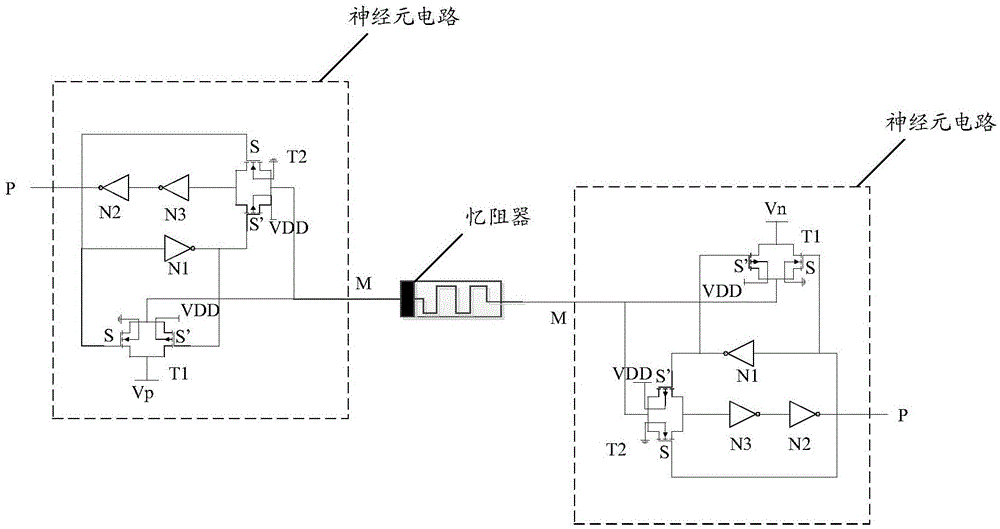

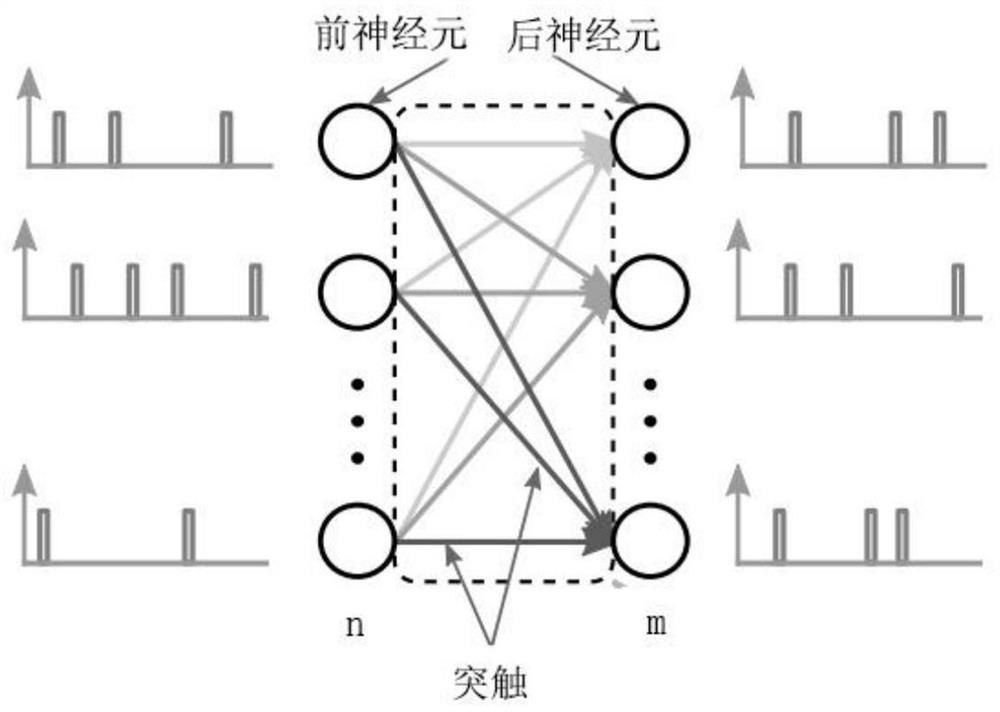

Memristor-based neuron circuit

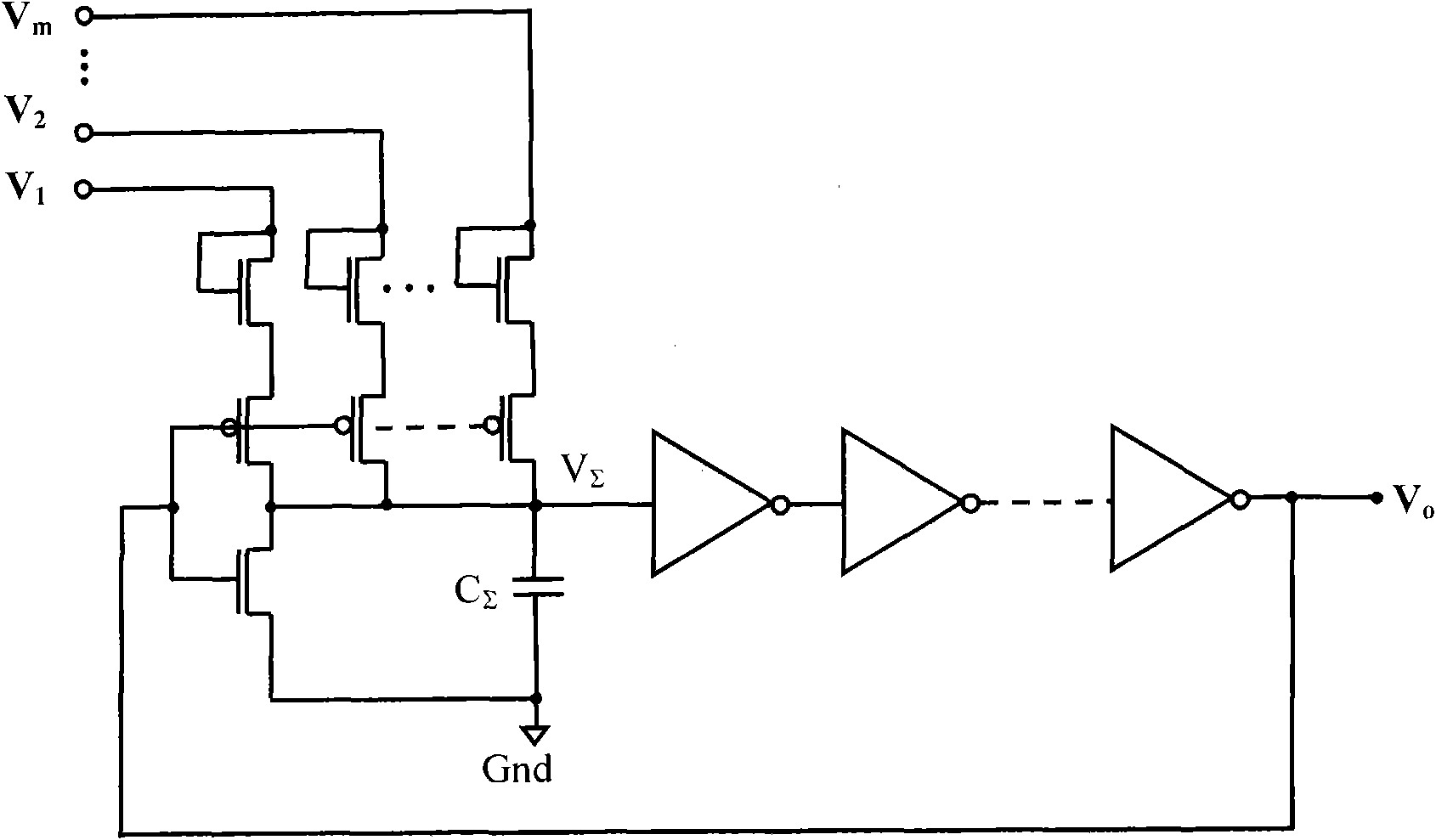

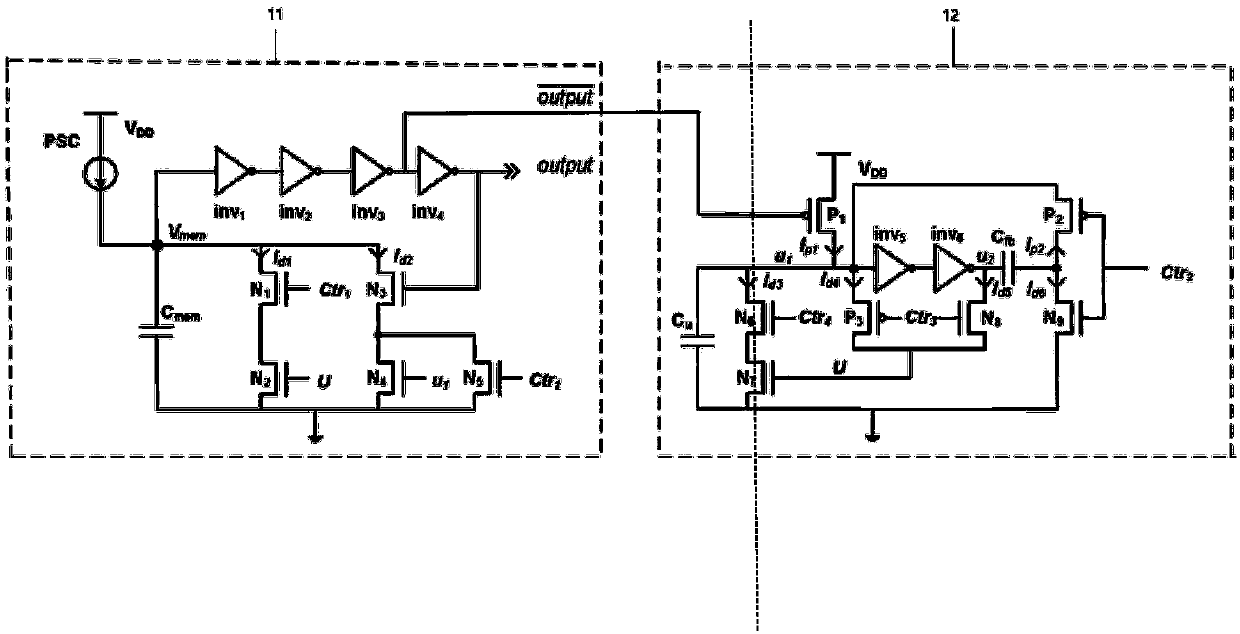

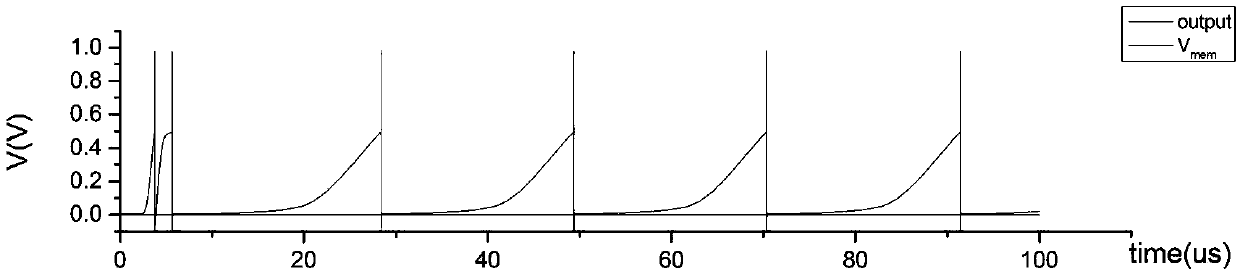

ActiveCN106845634ARealize integrated discharge functionImplement time encodingPhysical realisationInformation processingSynapse

The invention discloses a memristor-based neuron circuit. According to the neuron circuit, partially volatile bipolar resistive transition devices are selected and used as memristors of a synapse array, and a volatile resistive transition device is selected and used as a memristor for expressing membrane potential of neurons, so that the neuron circuit is formed; and synapse basis units are arranged. The neuron circuit can realize an integral discharge function in biological neurons and express local graded potentials; and synapses have partial volatility, can express spike-timing-dependent plasticity, and have great similarity with biological neurons and synapses in the aspects of information storage, transmission and processing. According to the neuron circuit, the basic units can be provided for hardware to simulate a cerebral neural network structure; the technical problems of neuron discharge time delay, difficulty in realizing high-density integration and the like in the prior art are solved; and the neuron circuit can be used for constructing a brain-like information processing system, can quickly process a large amount of information in parallel, and has a greatly high application value in realizing a cerebral neurologic calculation network.

Owner:HUAZHONG UNIV OF SCI & TECH

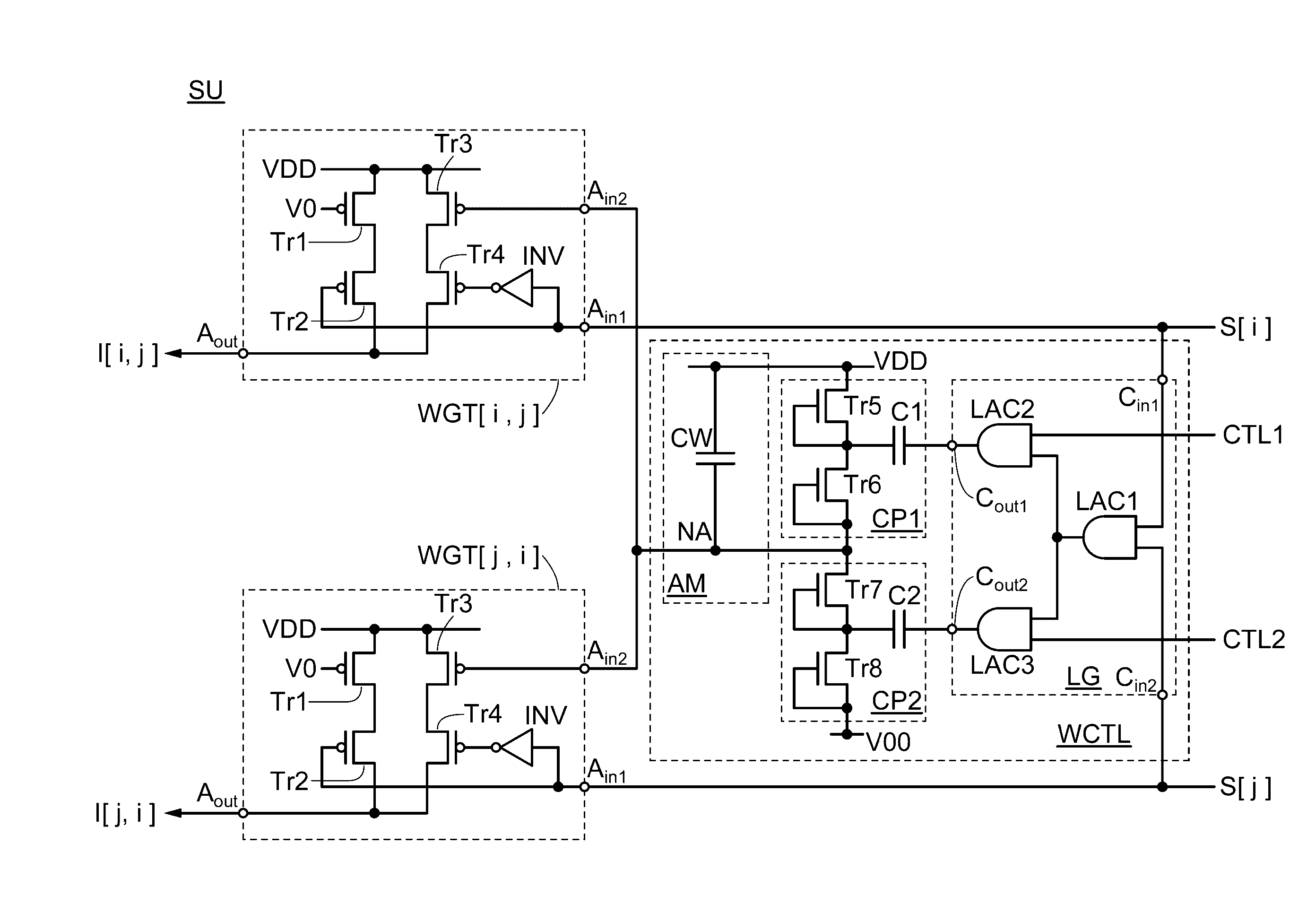

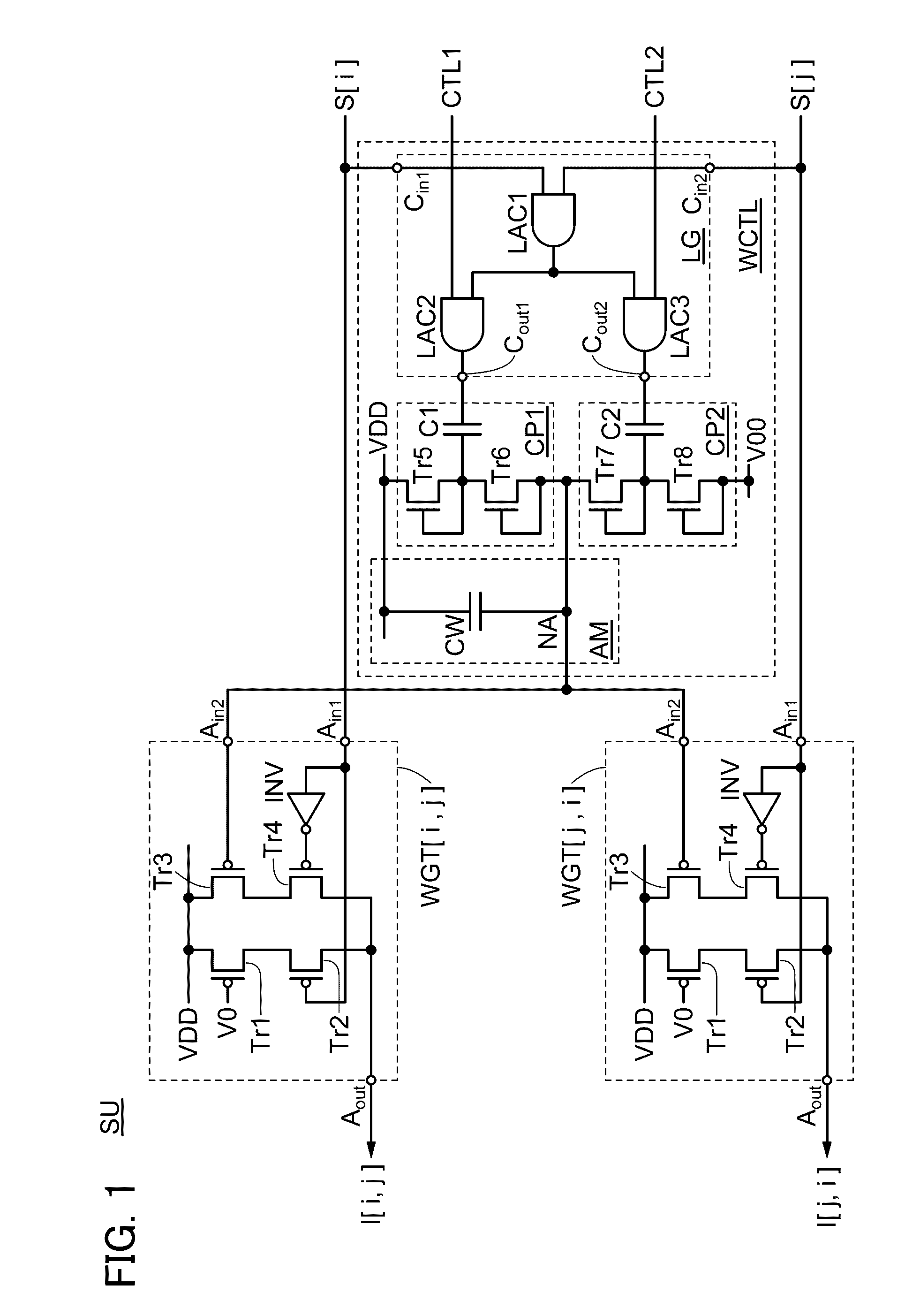

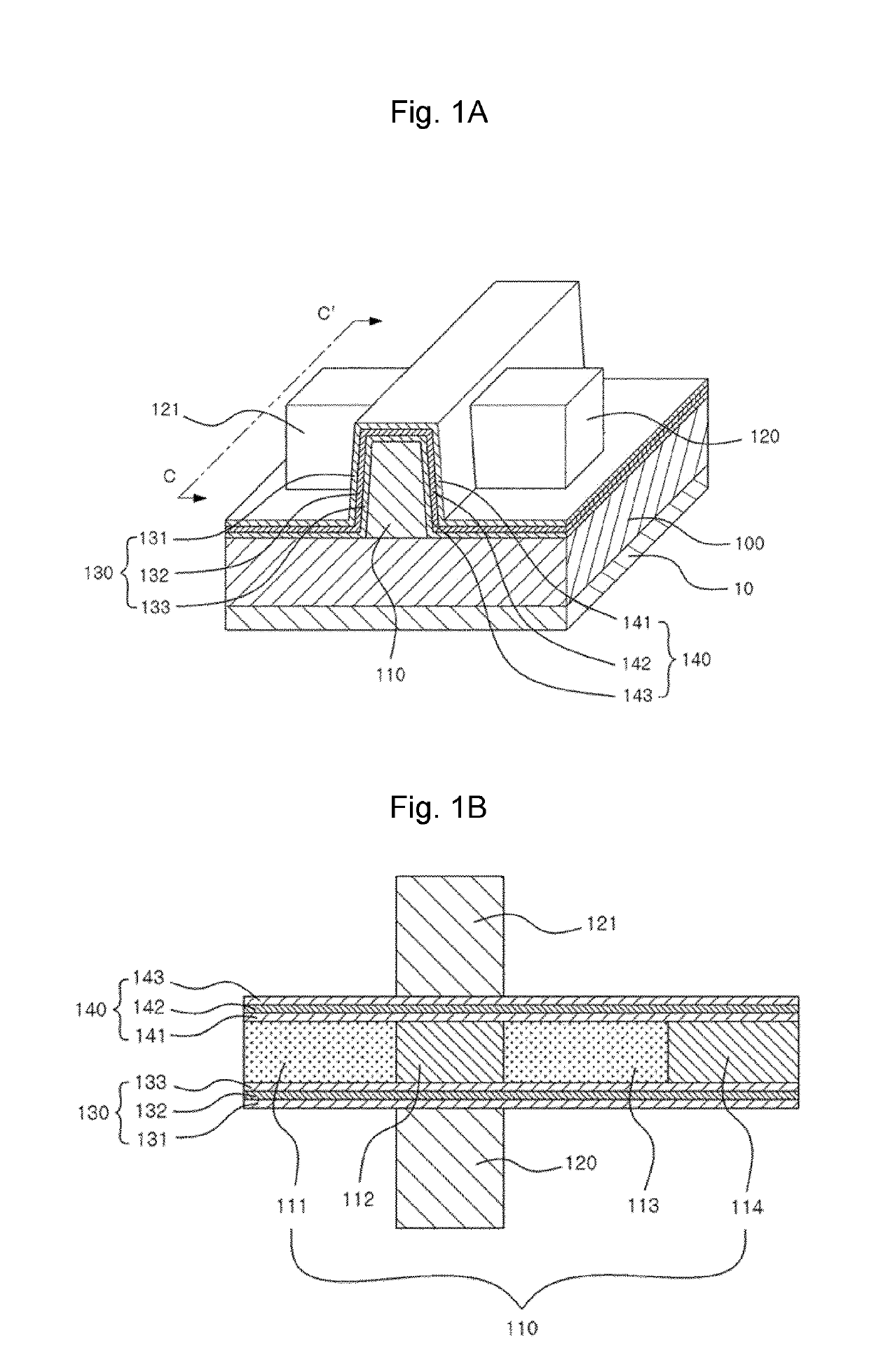

Semiconductor device or electronic device including the semiconductor device

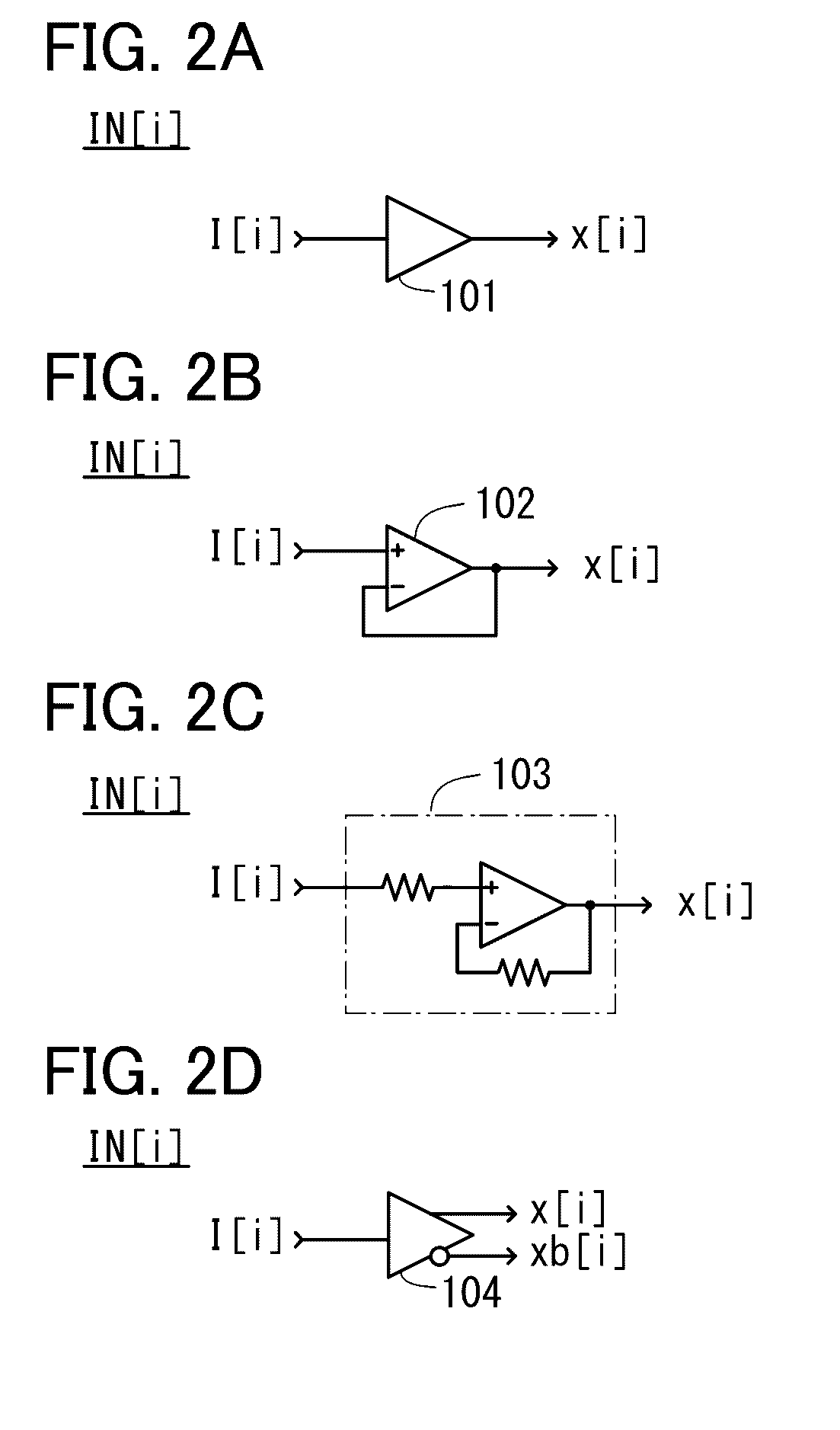

InactiveUS20170063351A1Reduce circuit sizeReduce power consumptionTransistorSolid-state devicesHopfield networkData compression

To provide a semiconductor device with a small circuit size and low power consumption or an electronic device including the semiconductor device and compressing a large volume of image data. A semiconductor device of a Hopfield neural network is formed using neuron circuits and synapse circuits. The synapse circuit includes an analog memory and a writing control circuit, and the writing control circuit is formed using a transistor including an oxide semiconductor in a channel formation region. Thus, data retention lifetime of the analog memory can be extended and refresh operation for data retention can be omitted, so that power consumption of the semiconductor device can be reduced. The semiconductor device enables judgement whether learned image data and arbitrary image data match, are similar, or mismatch by comparing video data. Thus, motion compensation prediction, which is one of data compression methods, can be employed for image data.

Owner:SEMICON ENERGY LAB CO LTD

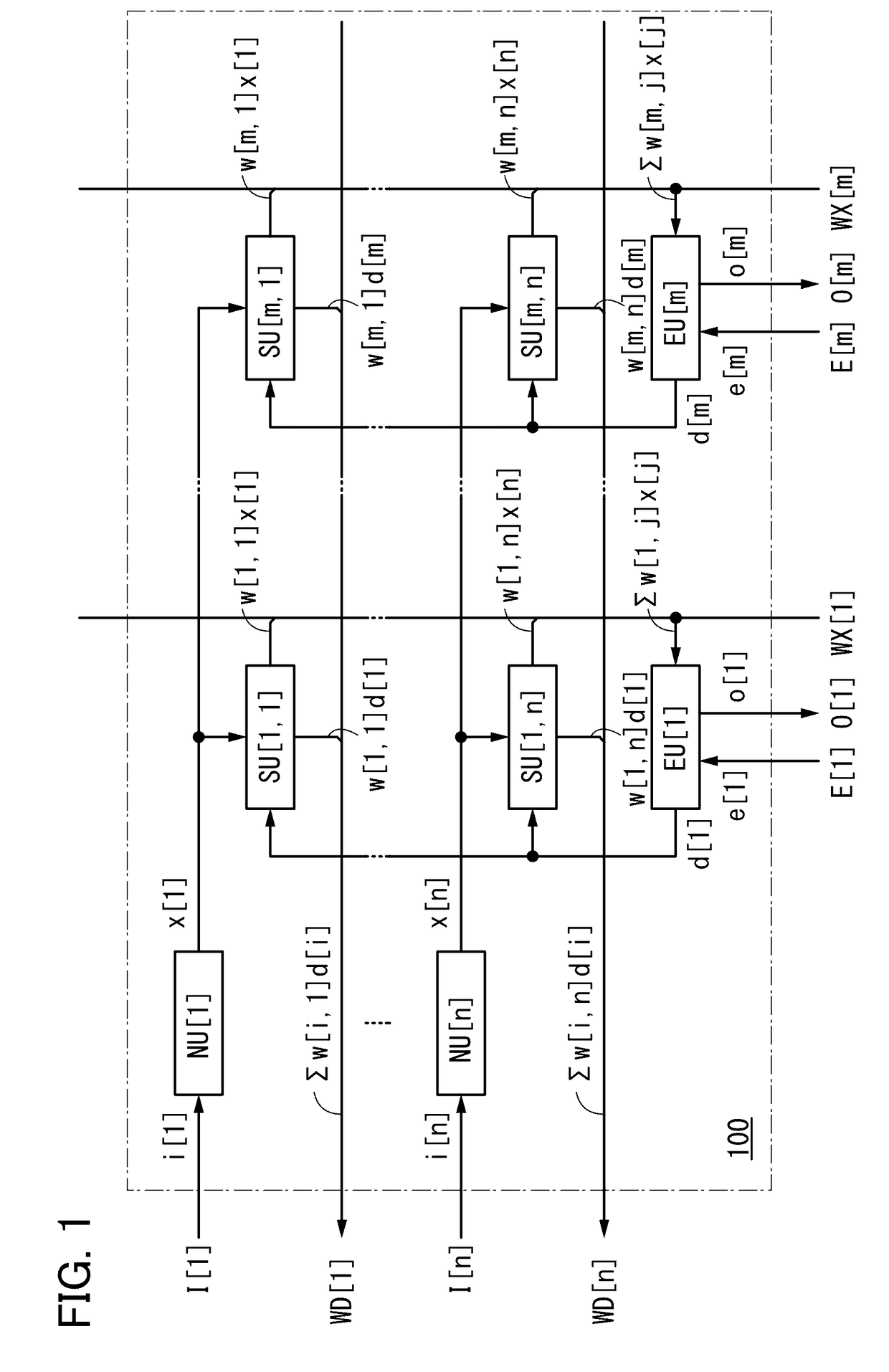

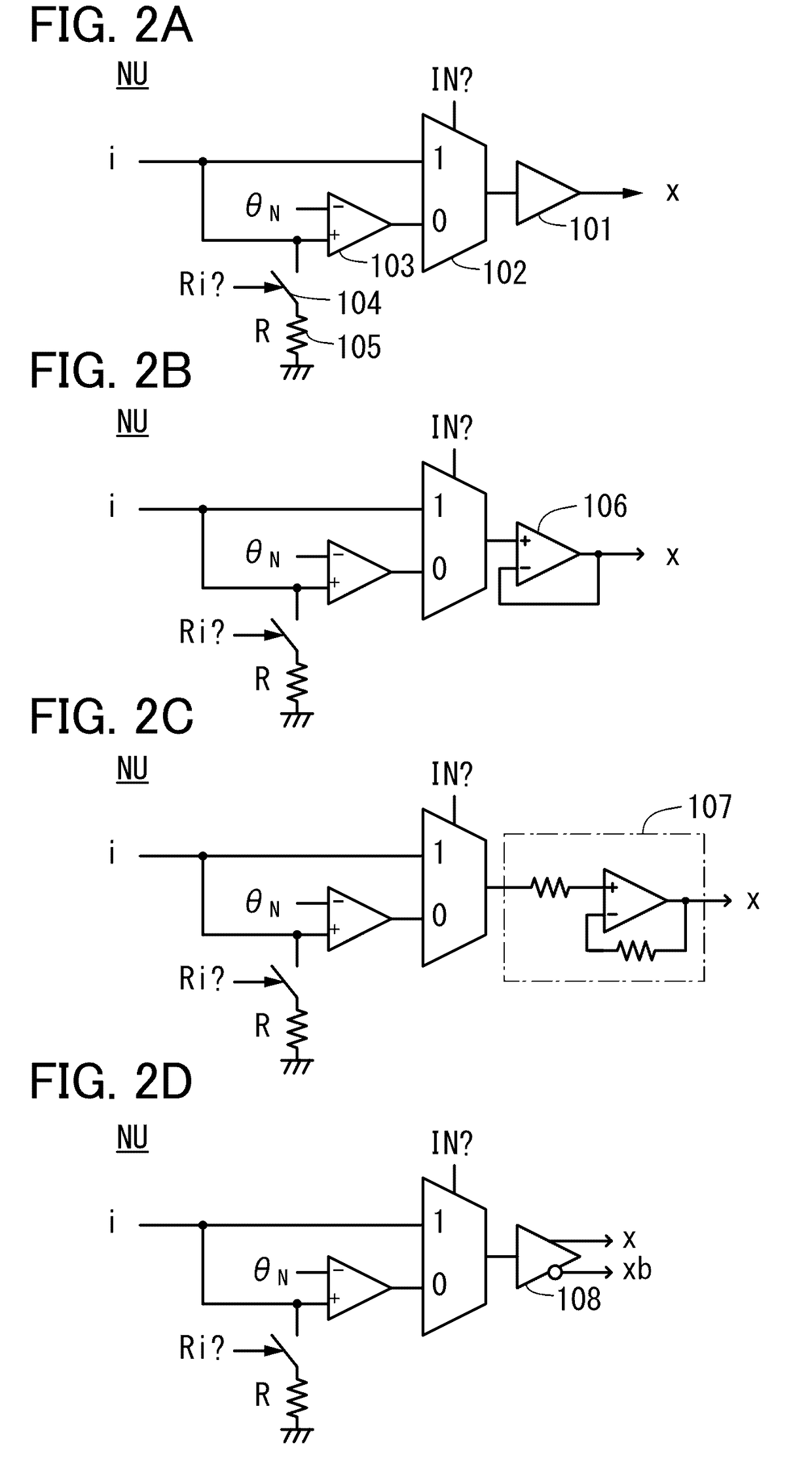

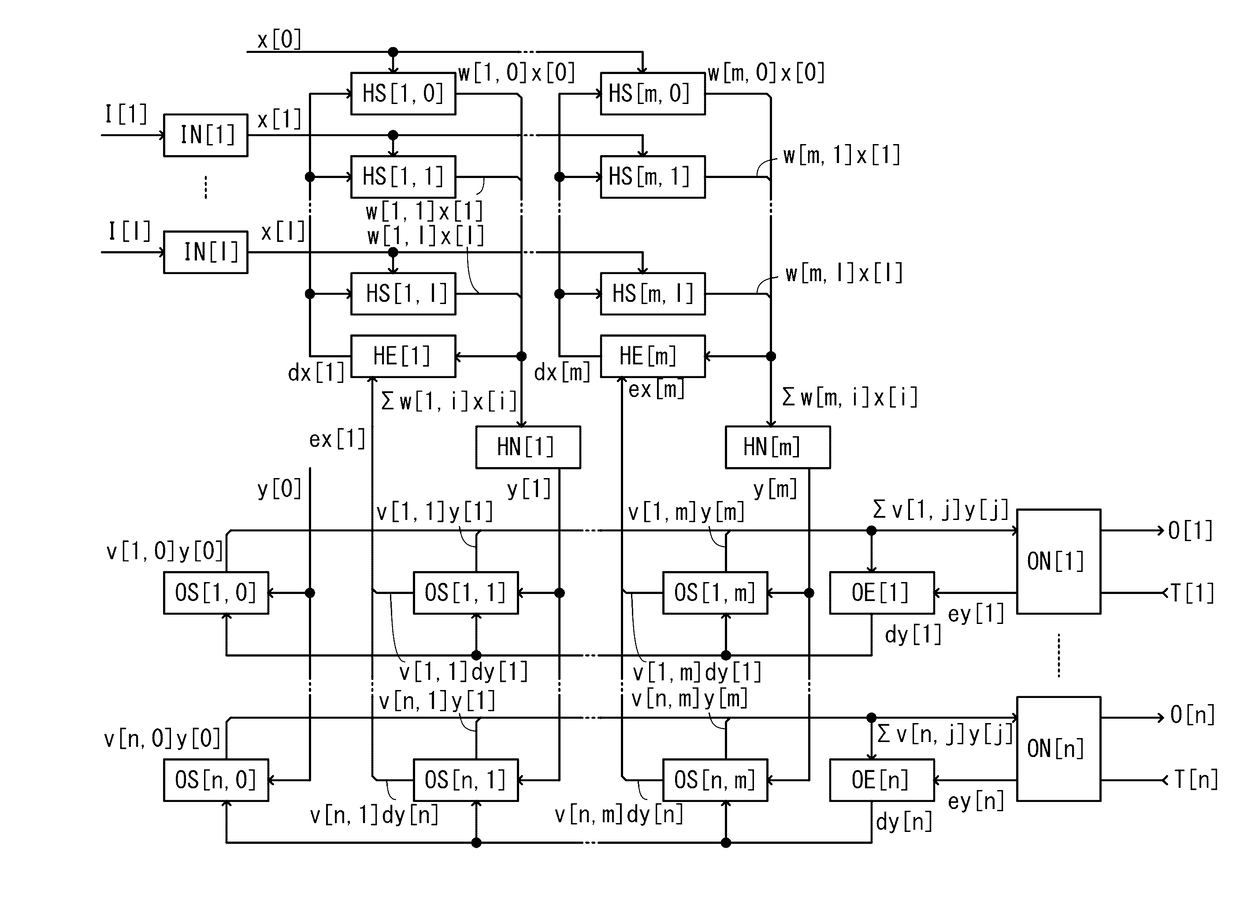

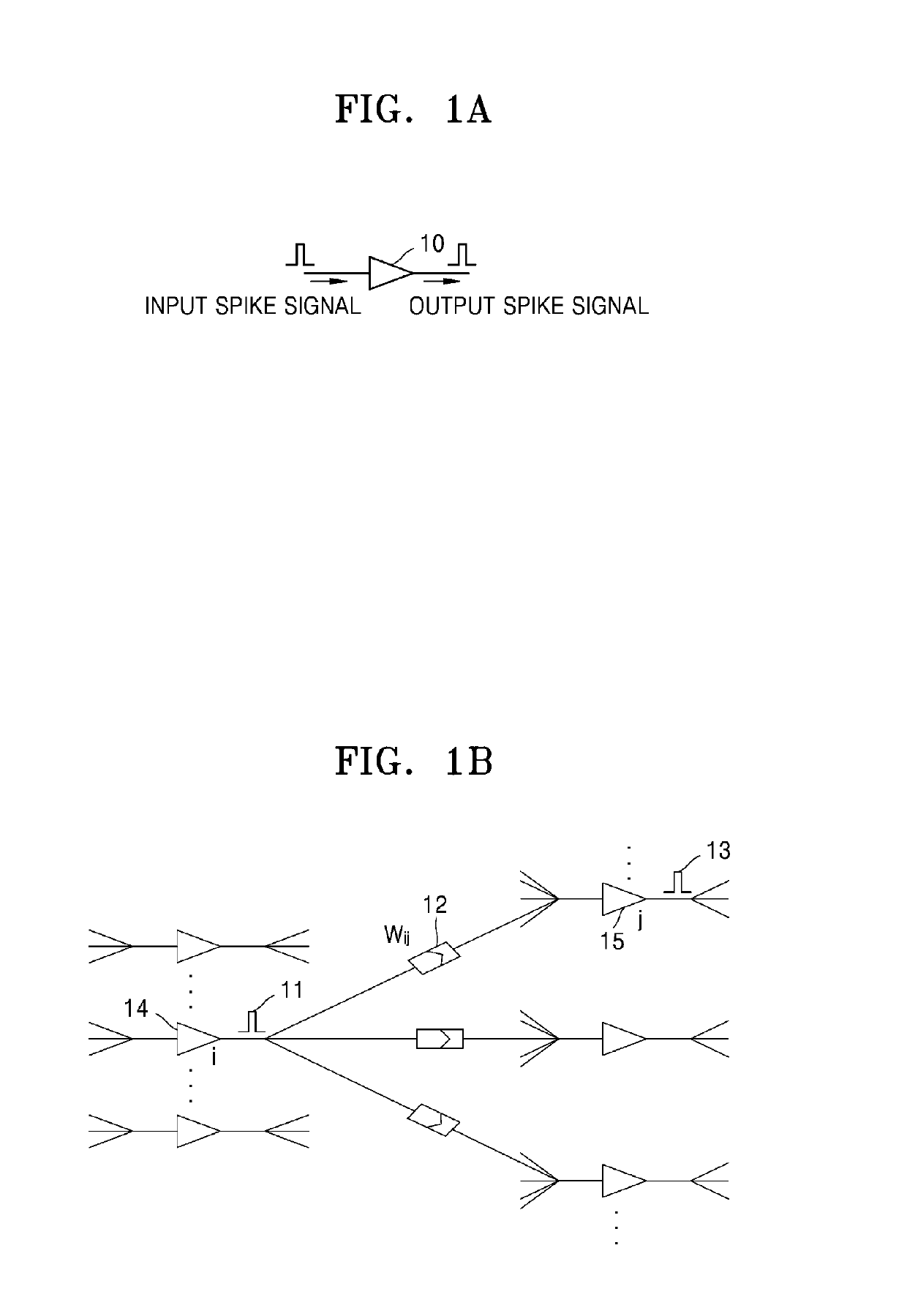

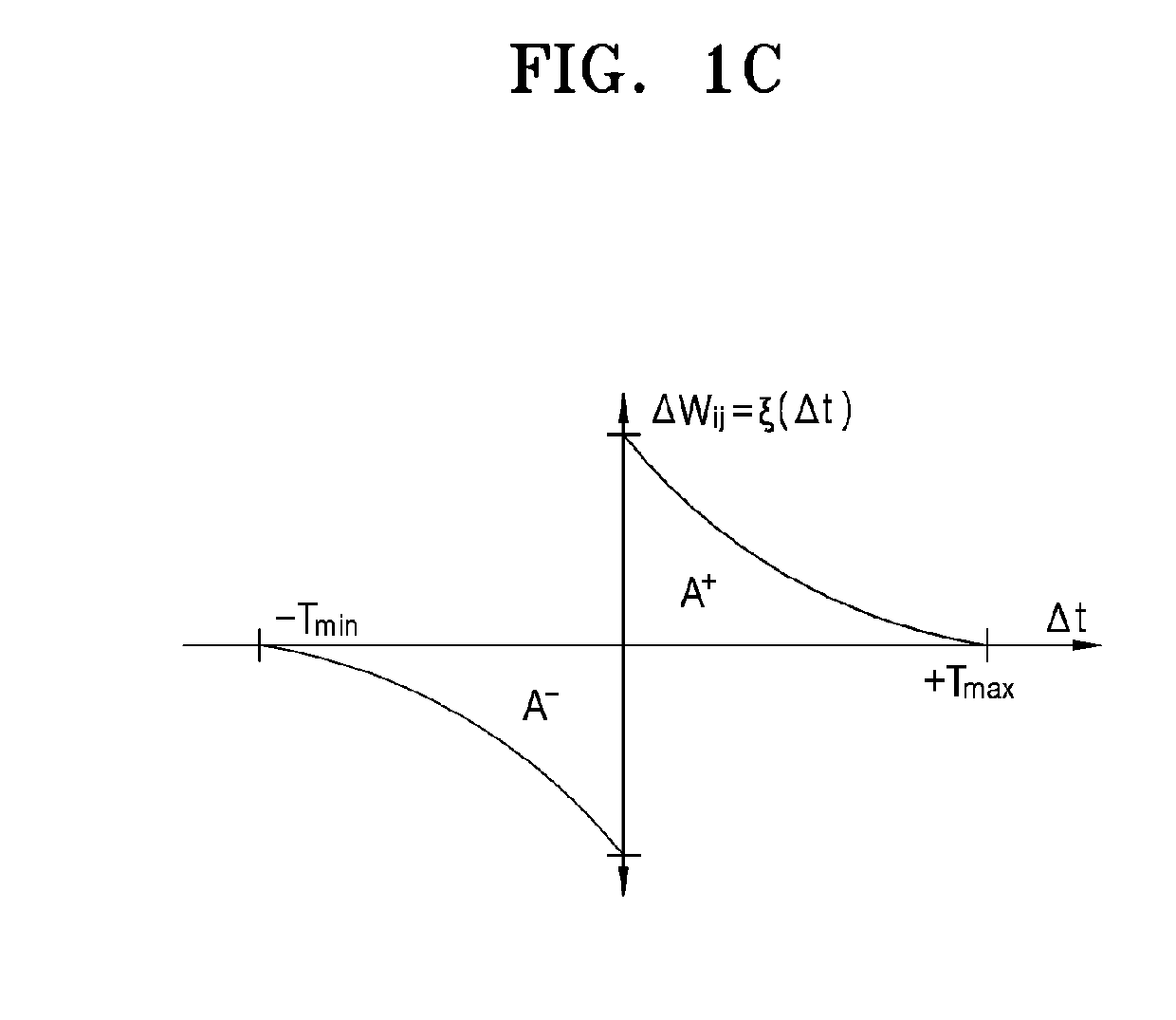

Neural network circuit and learning method thereof

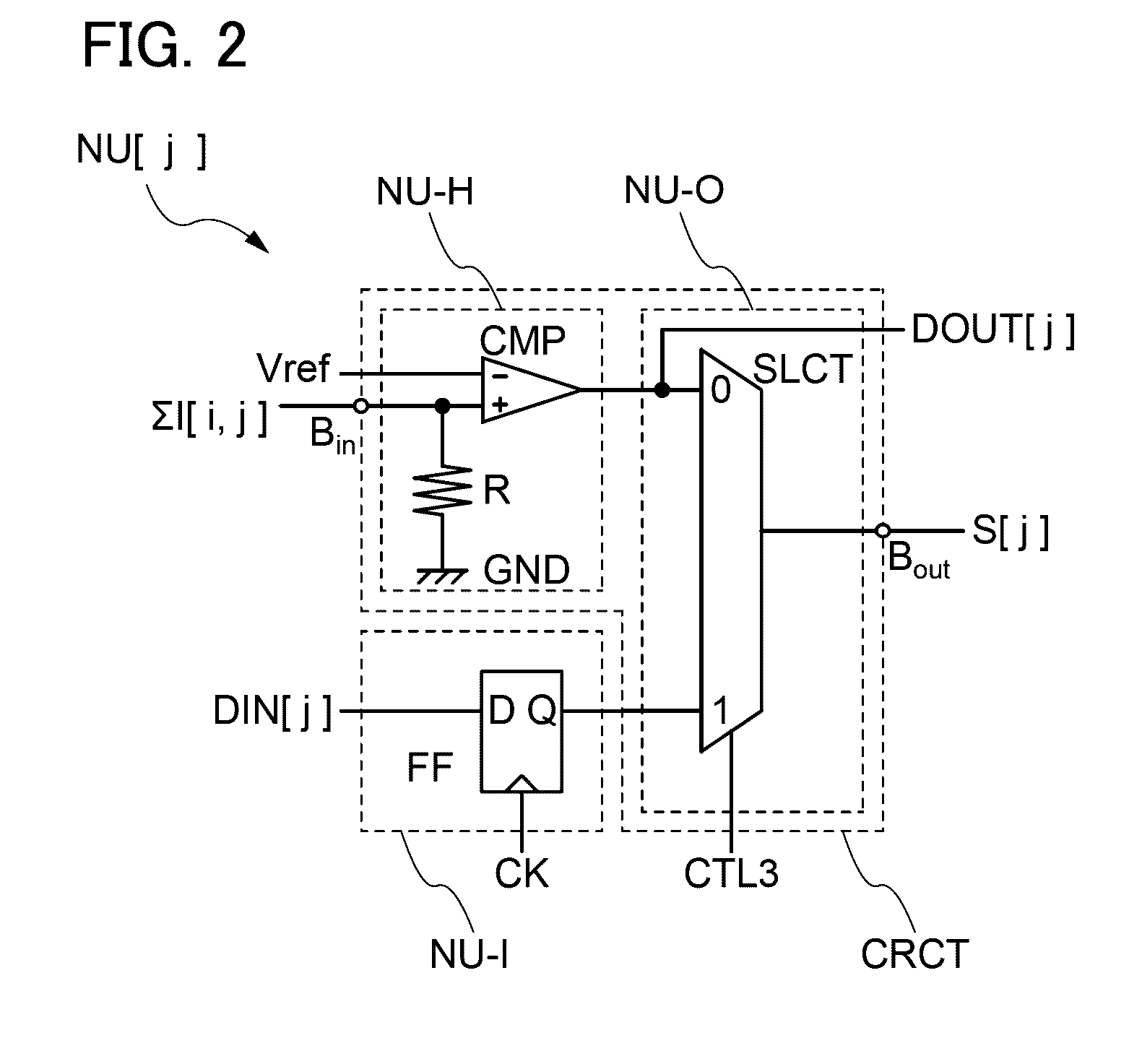

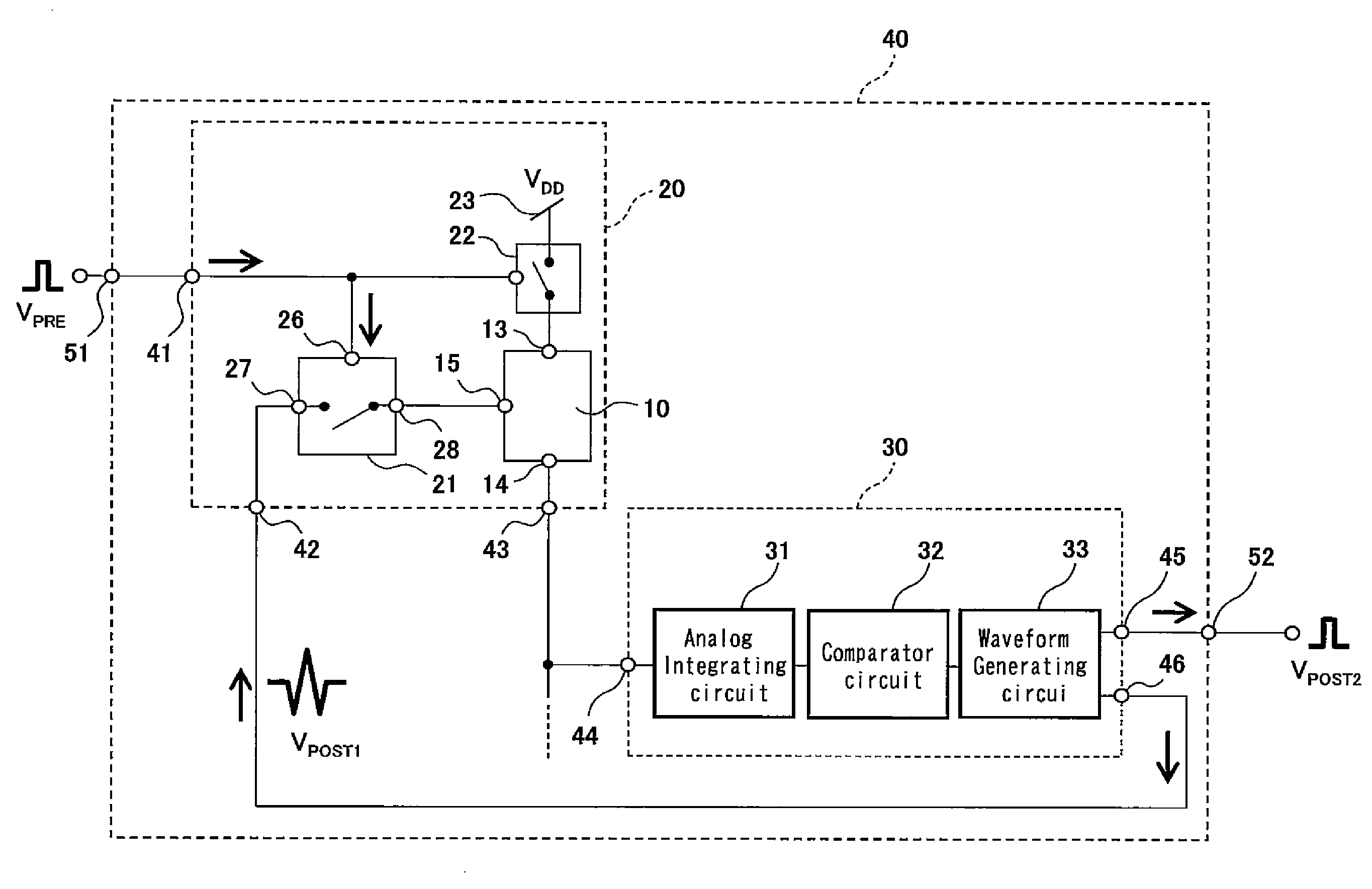

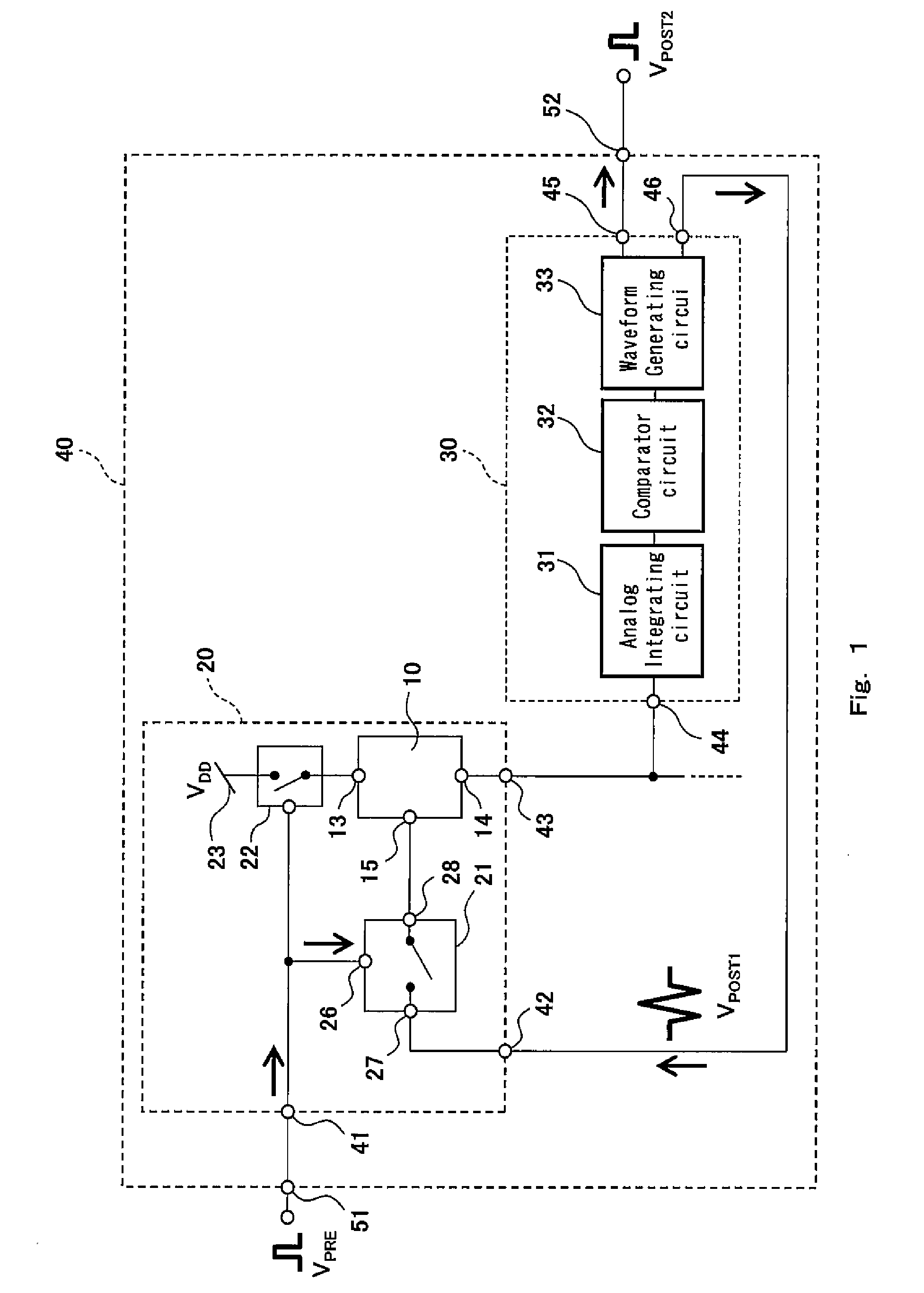

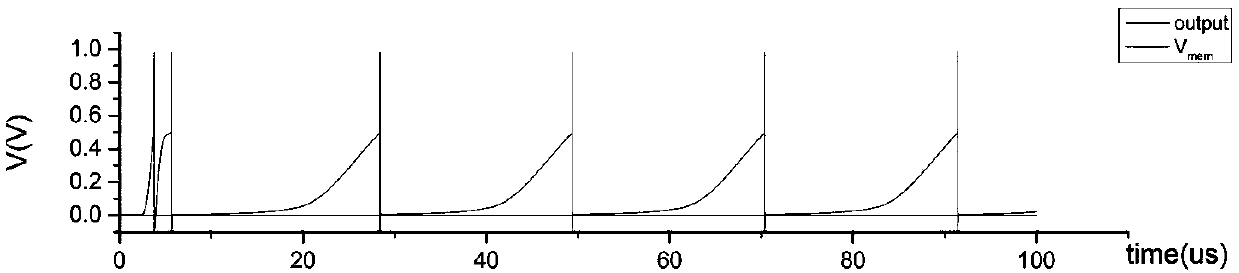

ActiveUS20150178619A1Ensure correct executionAccurate operationDigital computer detailsDigital dataPotential differenceEngineering

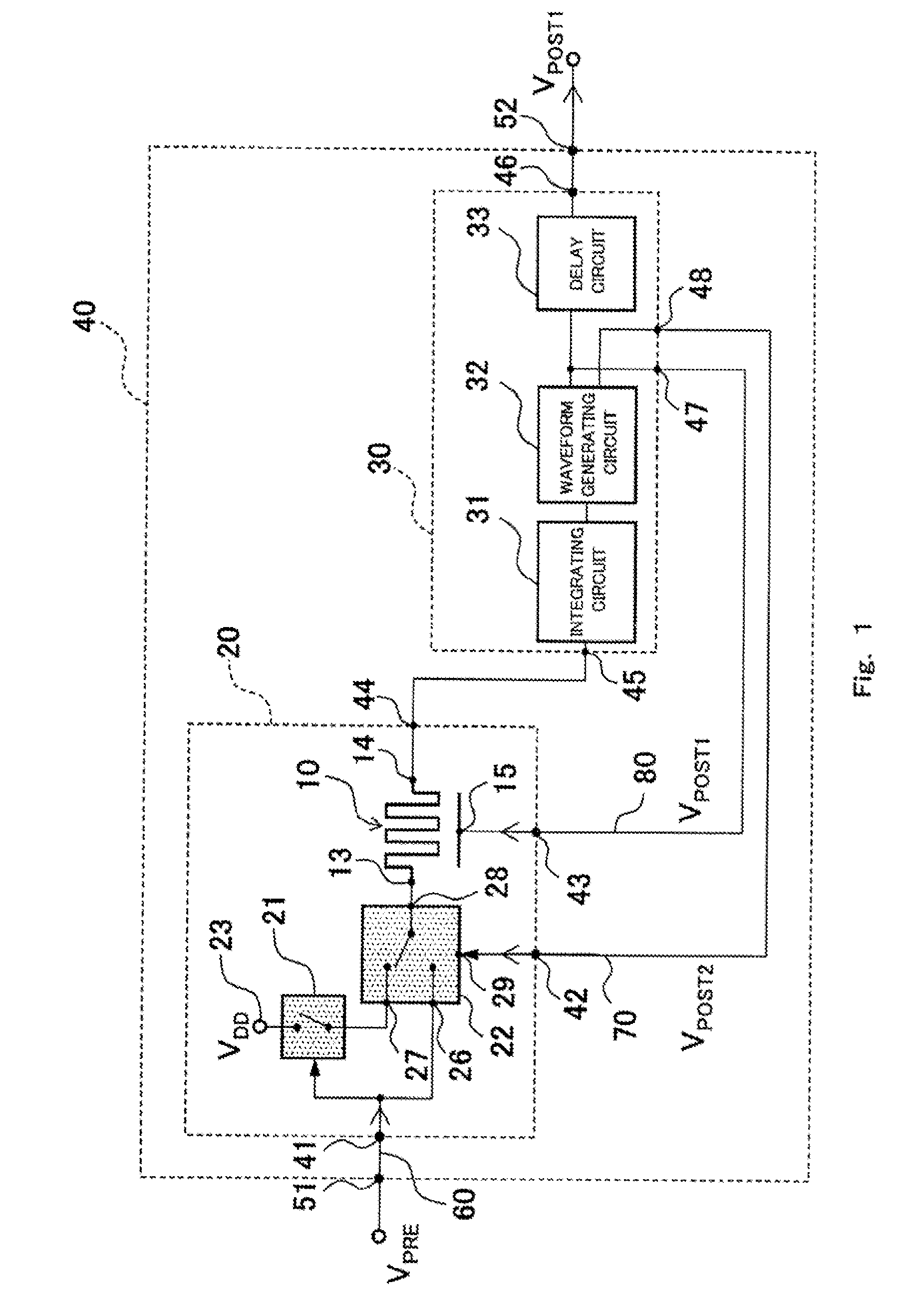

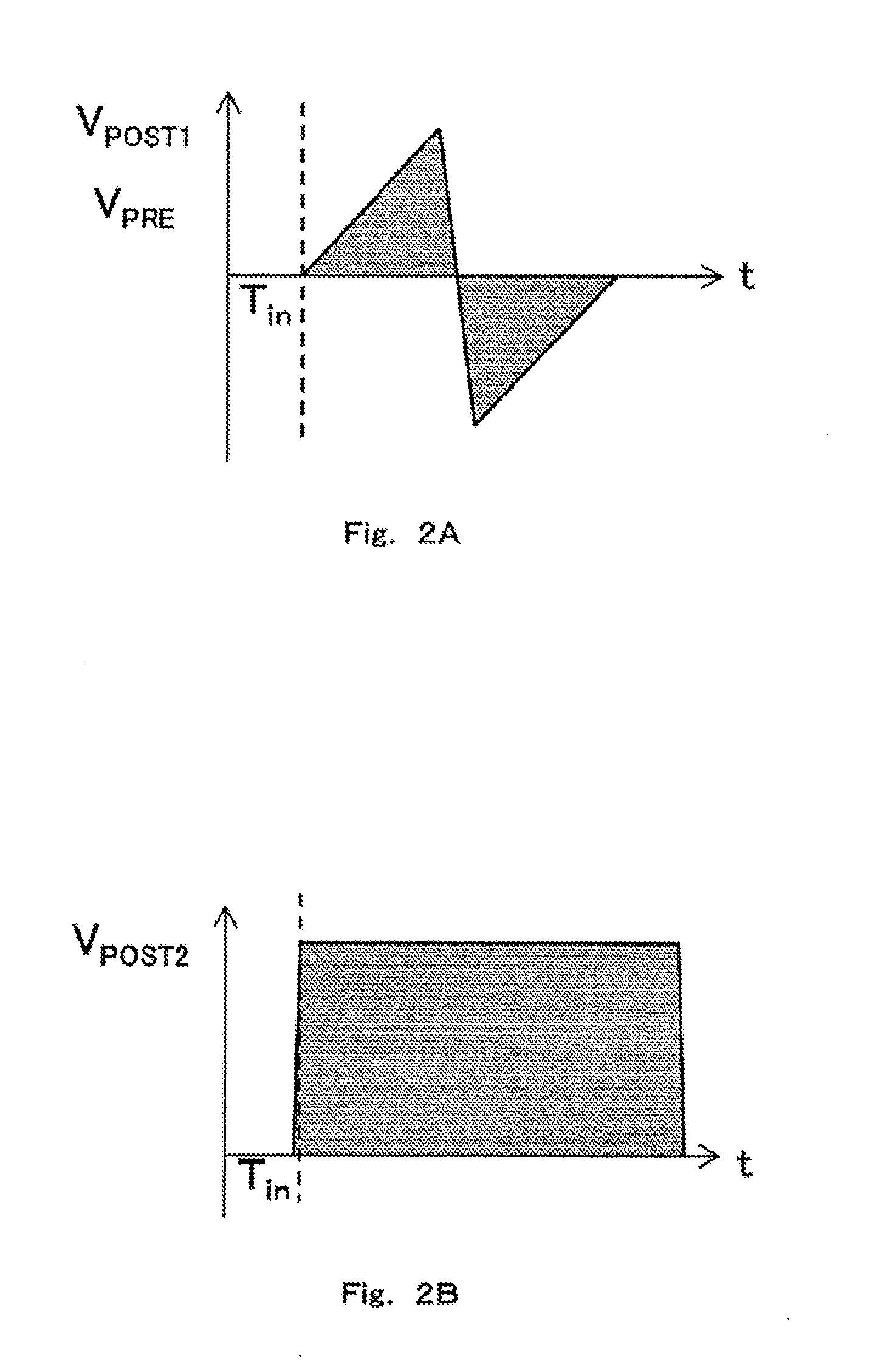

In a neural network circuit element, a neuron circuit includes a waveform generating circuit for generating an analog pulse voltage, and a switching pulse voltage which is input as a first input signal to another neural network circuit element; a synapse circuit is configured such that the analog pulse voltage generated in the neuron circuit of the neural network circuit element including the synapse circuit is input to a third terminal of a variable resistance element of the synapse circuit, for a permissible input period, in the first input signal from another neural network circuit element; and the synapse circuit is configured such that the resistance value of the variable resistance element is changed in response to an electric potential difference between a first terminal and the third terminal, which occurs depending on a magnitude of the analog pulse voltage for the permissible input period.

Owner:PANASONIC INTELLECTUAL PROPERTY MANAGEMENT CO LTD

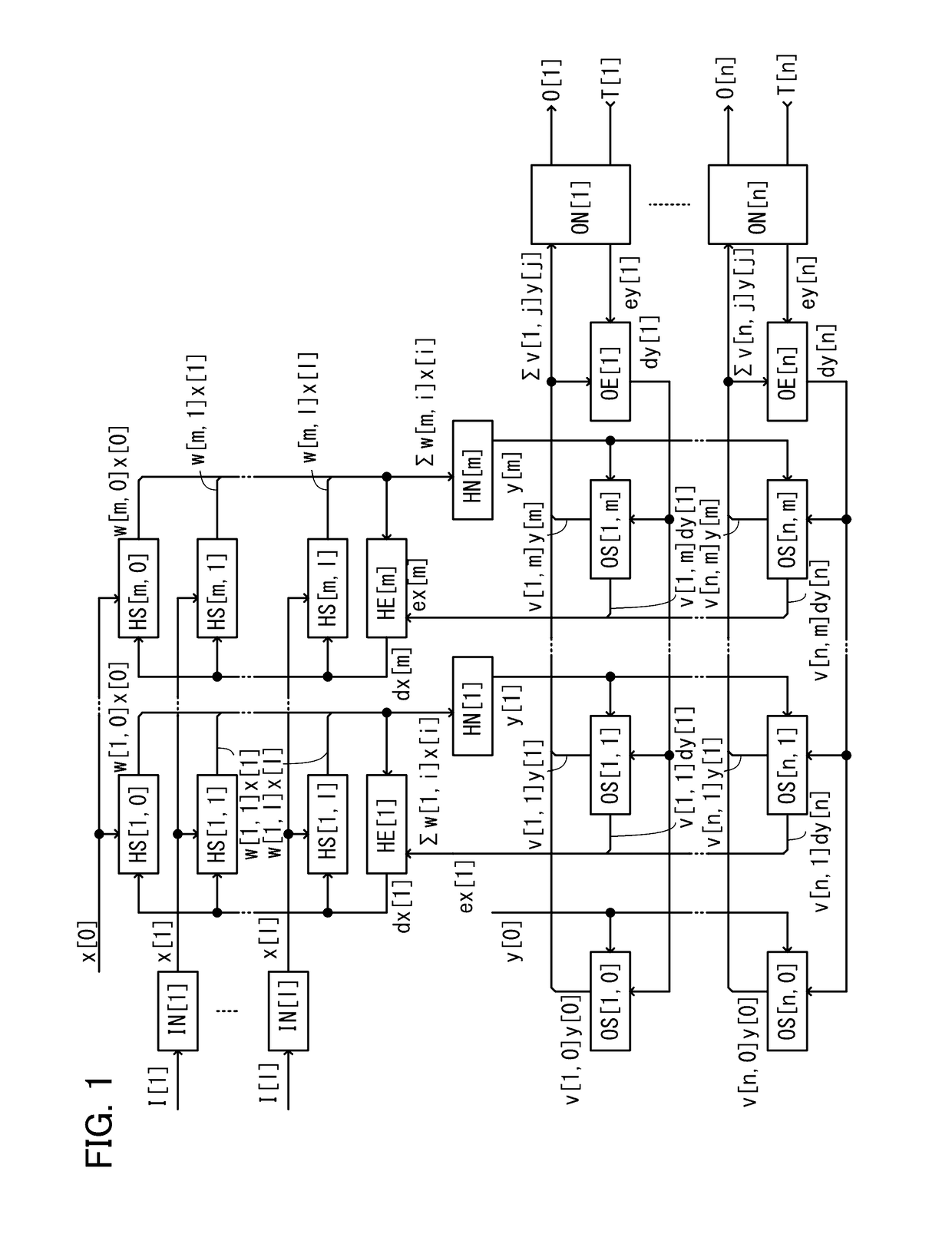

Semiconductor device and electronic device

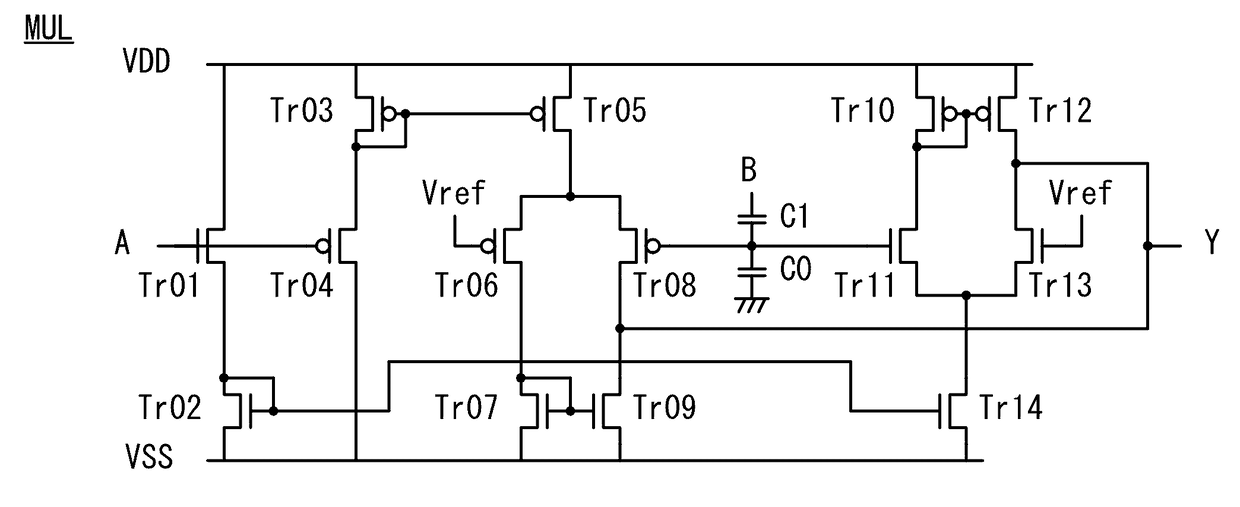

ActiveUS20170116512A1Novel configurationReduce chip areaElectric analogue storesDigital storageSynapseNeuron circuit

A neuron circuit can switch between two functions: as an input neuron circuit, and as a hidden neuron circuit. An error circuit can switch between two functions: as a hidden error circuit, and as an output neuron circuit. A switching circuit is configured to be capable of changing the connections between the neuron circuit, a synapse circuit, and the error circuit. The synapse circuit includes an analog memory that stores data that corresponds to the connection strength between the input neuron circuit and the hidden neuron circuit or between the hidden neuron circuit and the output neuron circuit, a writing circuit that changes the data in the analog memory, and a weighting circuit that weights an input signal in reaction to the data of the analog memory and outputs the weighted output signal. The analog memory includes a transistor comprising an oxide semiconductor with extremely low off-state current.

Owner:SEMICON ENERGY LAB CO LTD

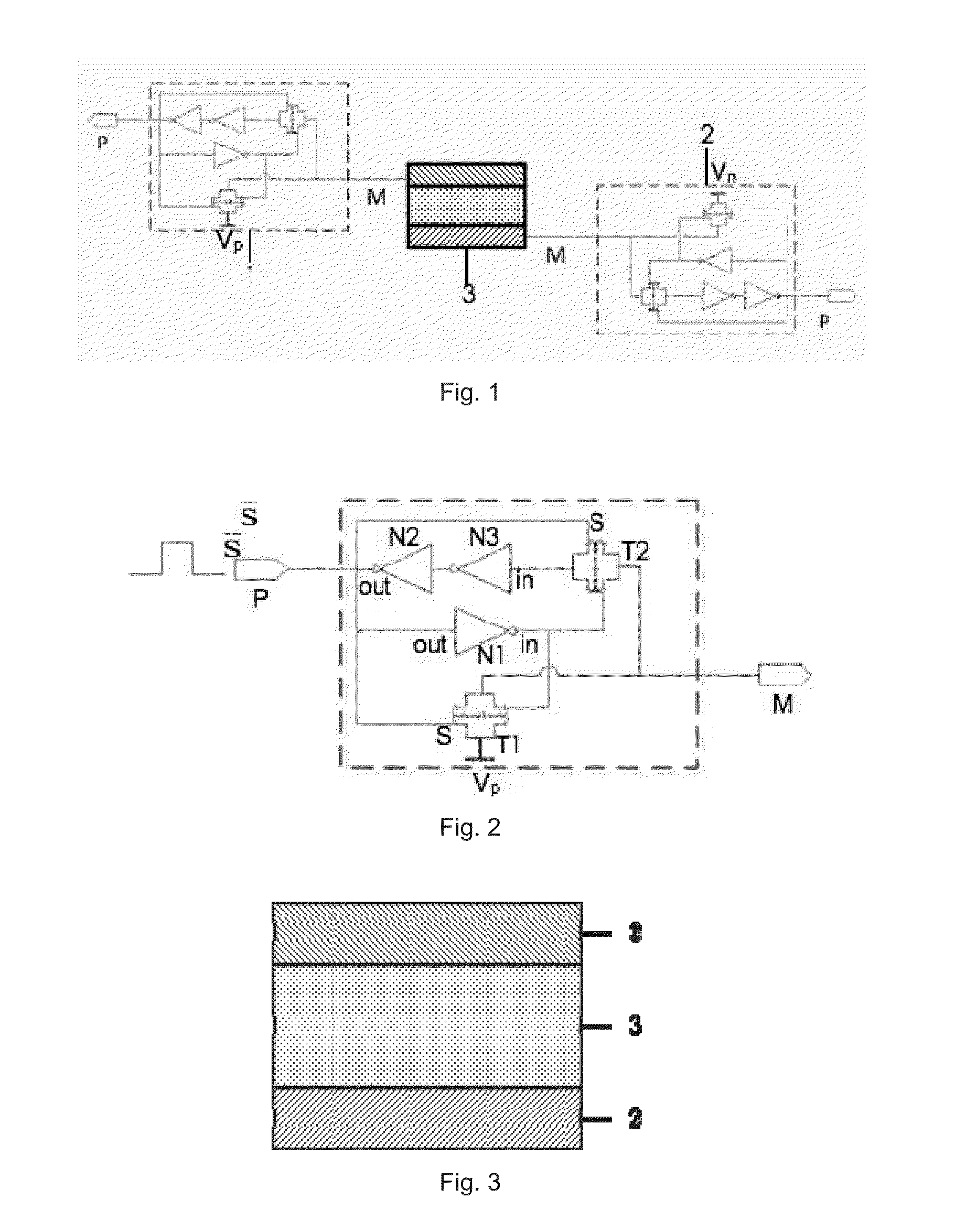

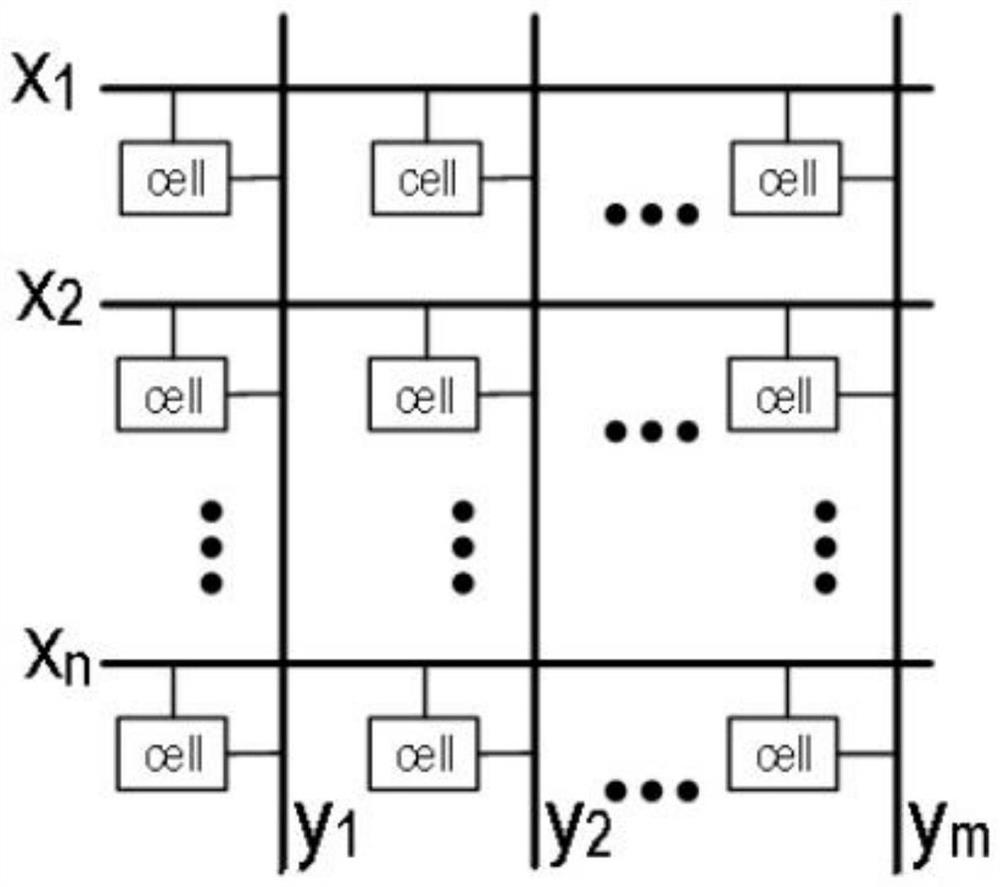

Resistance-adjustable-memristor-based time-related learning neuron circuit and implementation method thereof

ActiveCN103246904ASimple structureHighly integratedDigital storageNeural architecturesSynapseVoltage drop

The invention discloses a resistance-adjustable-memristor-based time-related learning neuron circuit and an implementation method thereof. According to the invention, switching characteristics of a resistance-adjustable memristor are utilized, when two ends of the memristor are synchronously selected by two excitation signals, voltage drop capable of enabling the memristor to generate resistance adjustment is formed at the two ends of a device, the connection or disconnection of a synapse is realized, the correlation or noncorrelation of the two excitation signals is realized, a memory characteristic is realized, and the previous excitation signals can be repeated, so a learning goal is achieved. The resistance-adjustable memristor is simple in structure, and high in integration level, so that the connection of large-scale physical neuron synapses is realized so as to achieve a more complicated learning or even logic function. The neuron circuit and the implementation method thereof disclosed by the invention have a good application prospect in the neuron calculation.

Owner:PEKING UNIV

Semiconductor device and electronic device

InactiveUS20170118479A1Novel structureReduce areaTransistorElectric analogue storesSynapseA-weighting

A semiconductor device with a novel structure is provided. Input neuron circuits, hidden neuron circuits, and output neuron circuits are hierarchically connected to one another through plural synapse circuits. Each synapse circuit includes an analog memory which stores data corresponding to a connection strength between the input neuron circuit and the hidden neuron circuit or between the hidden neuron circuit and the output neuron circuit, a writing circuit which changes the data in the analog memory, and a weighting circuit which outputs an output signal obtained by weighting an input signal in accordance with data in the analog memory. The analog memory is formed using a transistor including an oxide semiconductor having extremely low off-state current. It is not necessary to mount a large-scale capacitor for holding data and to recover analog data by regular refresh operation; thus, reduction in a chip area and reduction in power consumption are possible.

Owner:SEMICON ENERGY LAB CO LTD

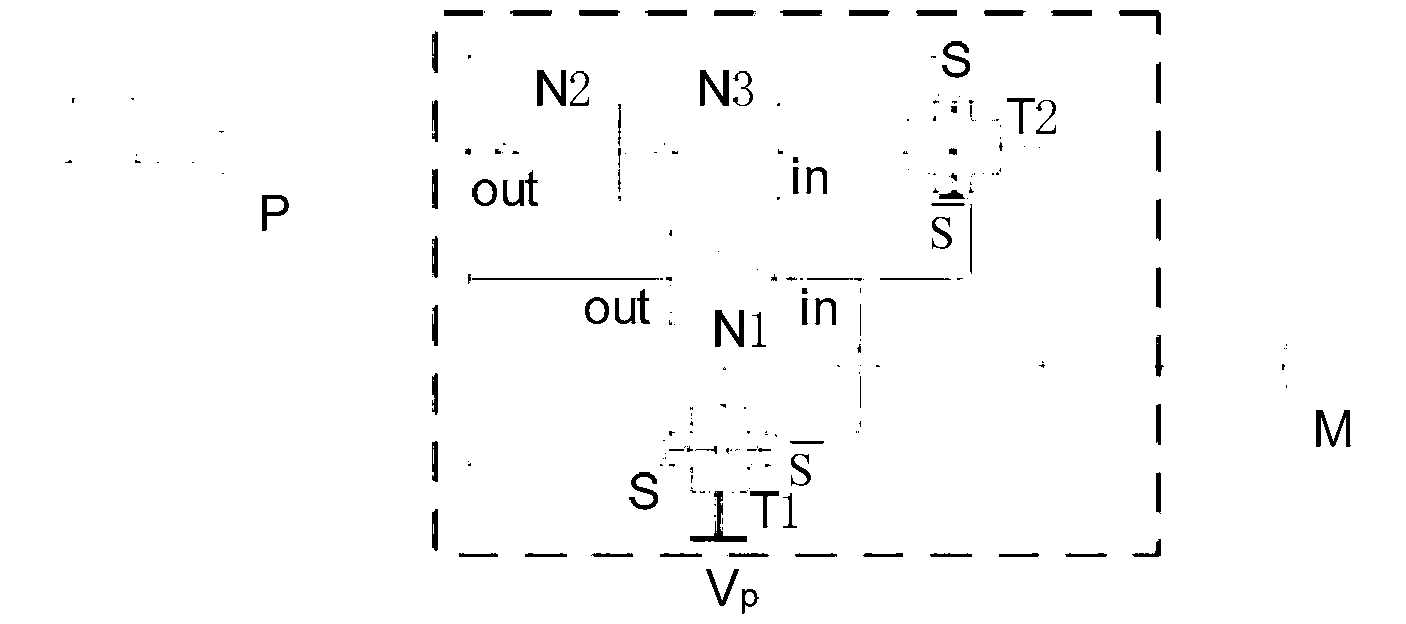

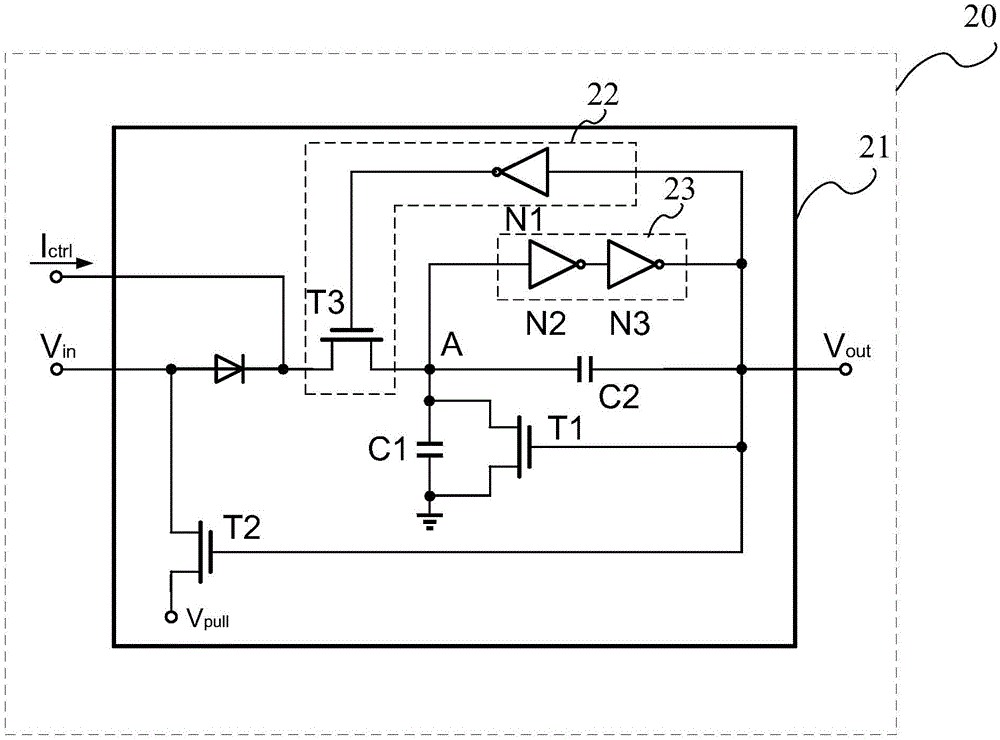

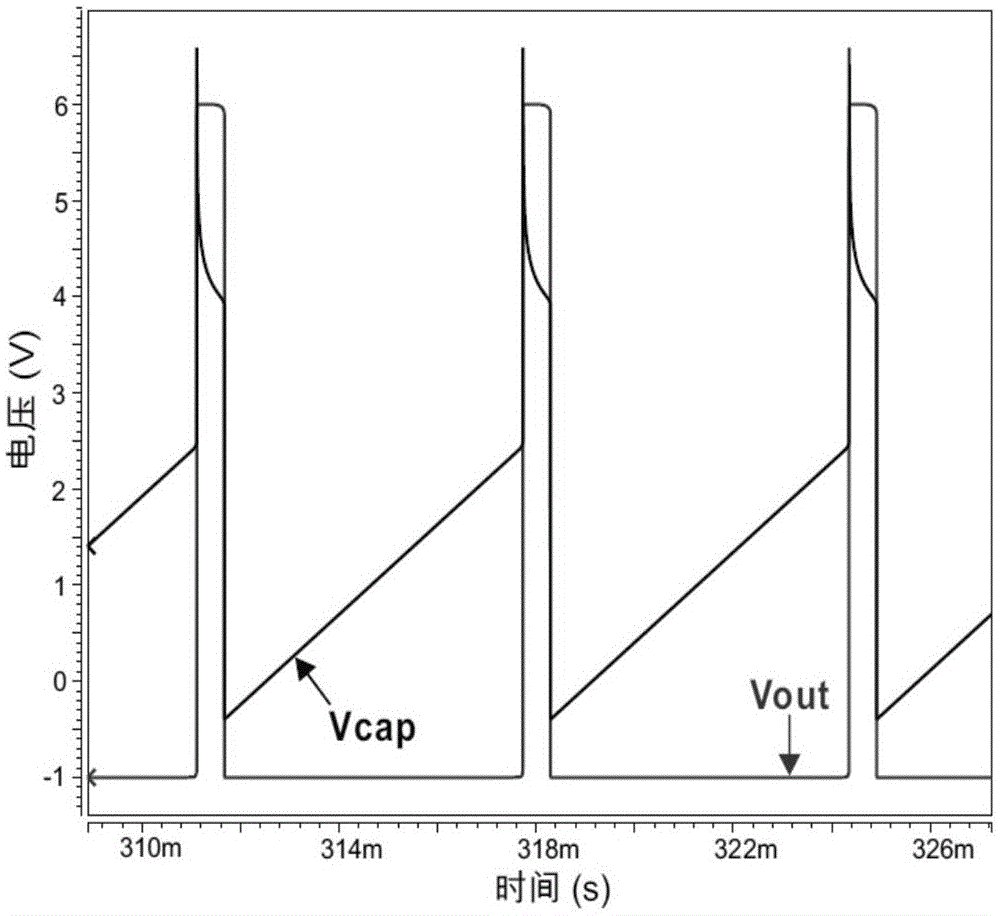

Neural simulation circuit

The embodiment of the invention provides a neural simulation circuit, and the circuit comprises a first circuit, wherein the first end of the first circuit is connected with the input end Vin of a first neuron circuit, and the second end of the first circuit is connected with the output end Vout of the first neuron circuit; a capacitor C1, wherein the first end of the capacitor C1 is connected with the third end of the first circuit, and the second end of the capacitor C1 is connected with the ground; a second circuit, wherein the input end of the second circuit is connected with the third end of the first circuit, the output end of the second circuit is connected with the output end Vout of the first neuron circuit, and the second circuit is switched on when the voltage of the first end of the capacitor C1 is greater than a voltage threshold value; and a switching tube T1, wherein the input end of the switching tube T1 is connected with the third end of the first circuit, the output end of the switching tube T1 is connected with the ground, and the control end of the switching tube T1 is connected with the output end Vout of the first neuron circuit. According to the embodiment of the invention, the circuit can simulate the threshold characteristic of theca cells.

Owner:HUAWEI TECH CO LTD

Time Correlation Learning Neuron Circuit Based on a Resistive Memristor and an Implementation Method Thereof

InactiveUS20160110644A1Simple structureEasy to integrateDigital computer detailsDigital storageSynapseElectrical resistance and conductance

The present invention discloses a time correlation learning neuron circuit based on a resistive memristor and an implementation method thereof. The present invention utilizes switching characteristics of the resistive memristor. When two terminals of the resistive memristor are selected synchronously by two excitation signals, the voltage drop between these two terminals will change the resistance value of memristor, thereby achieving the on-off of a synapse connection and achieving the correction of the two excitation signals. Meanwhile the device also has a memory characteristic. Also, the previous excitation signal can be repeated. That is, the purpose of learning is achieved. Since the resistive memristor has a simple structure and a high degree of integration, it can achieve large-scale physical synapse connection in order to achieve more complex learning and even logic functions. The present invention has a good application prospect in a neuron cell computation.

Owner:PEKING UNIV

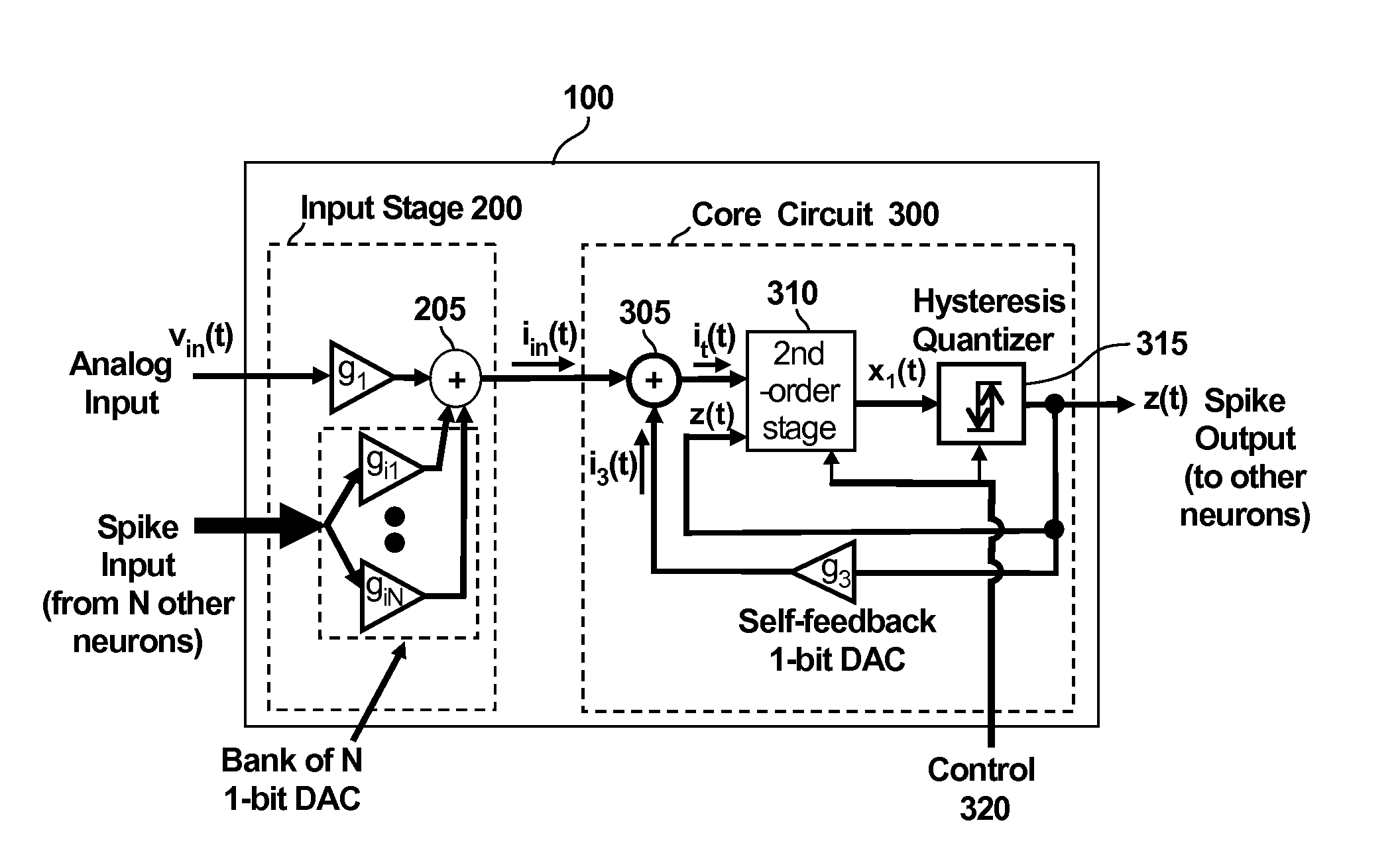

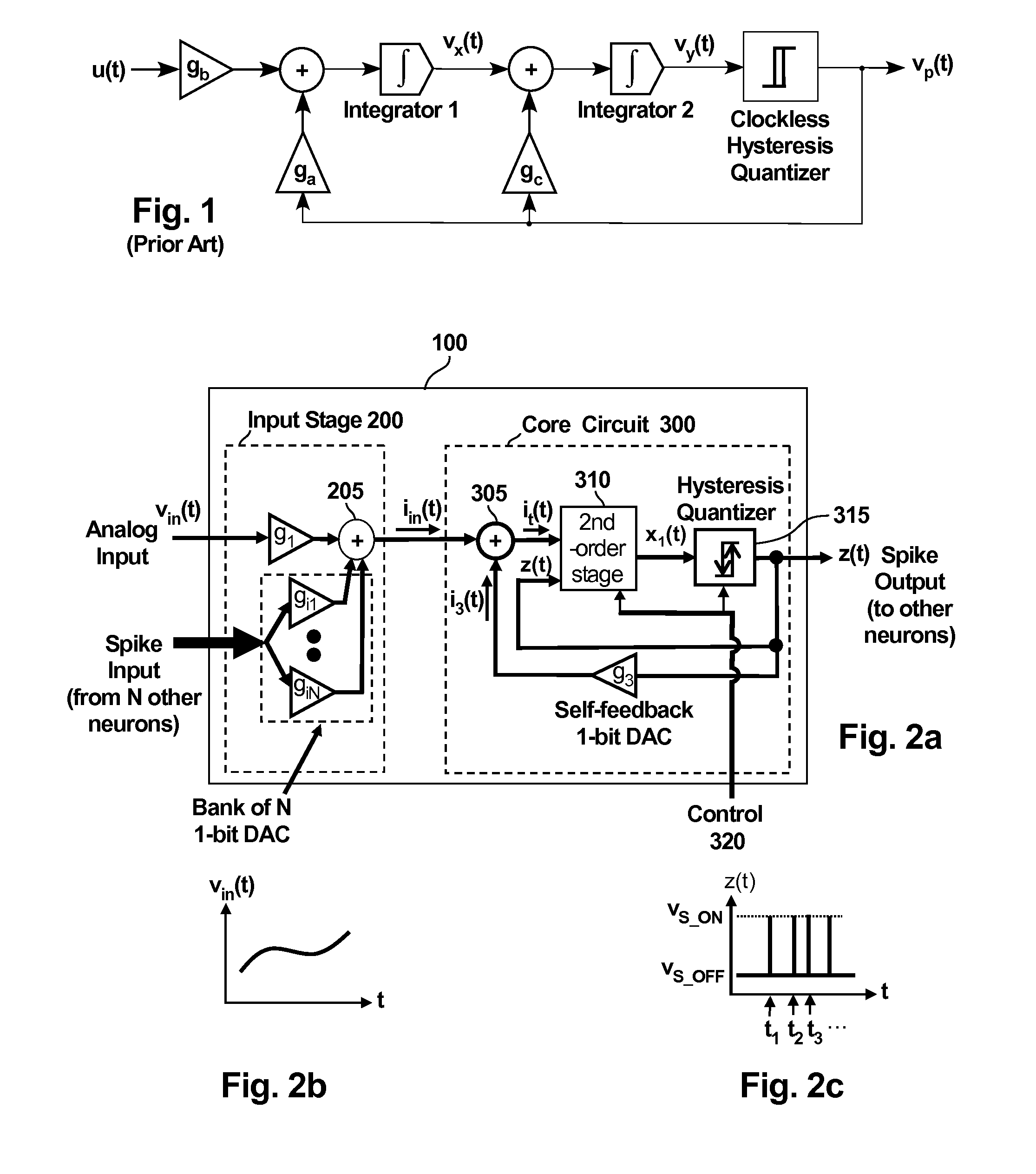

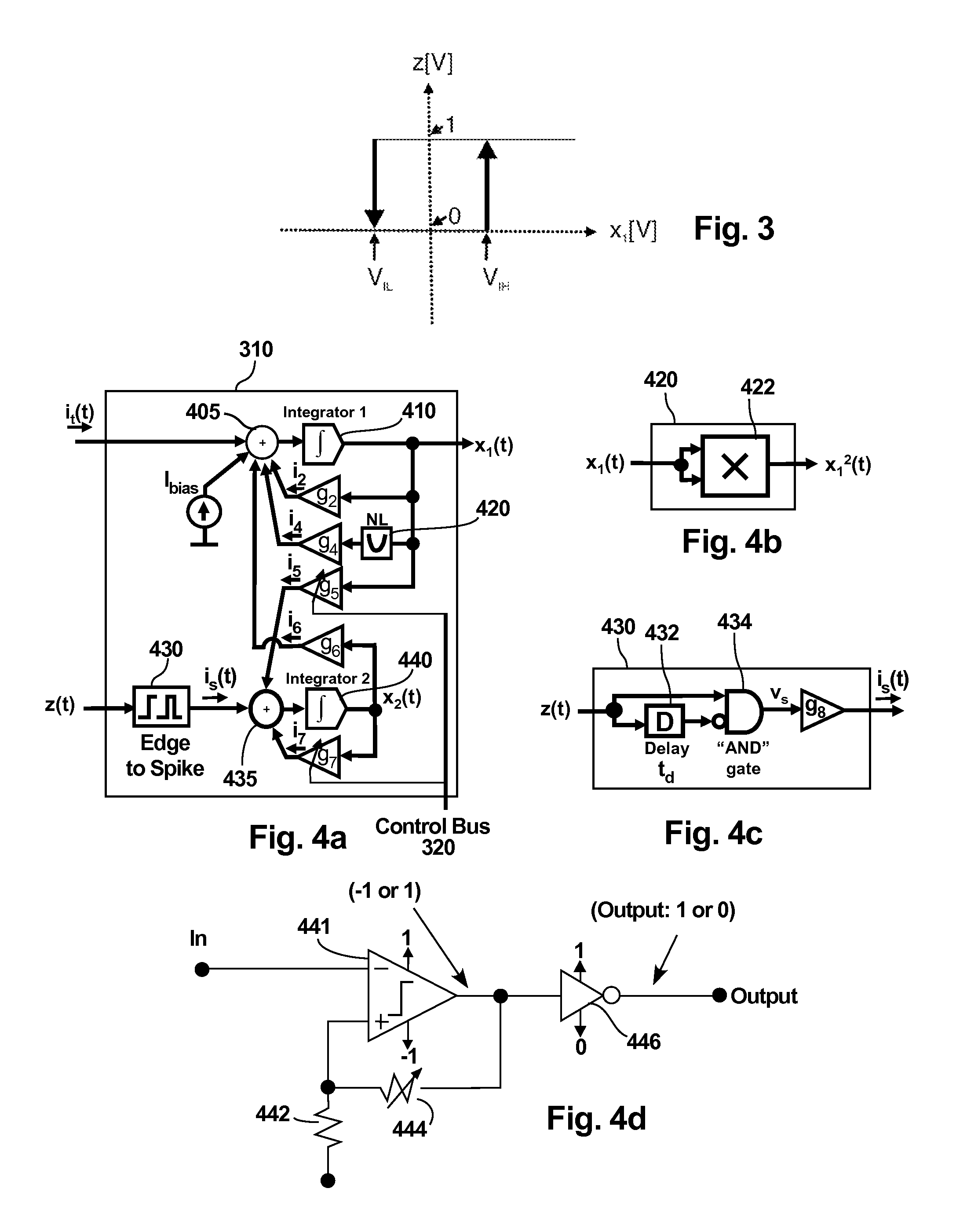

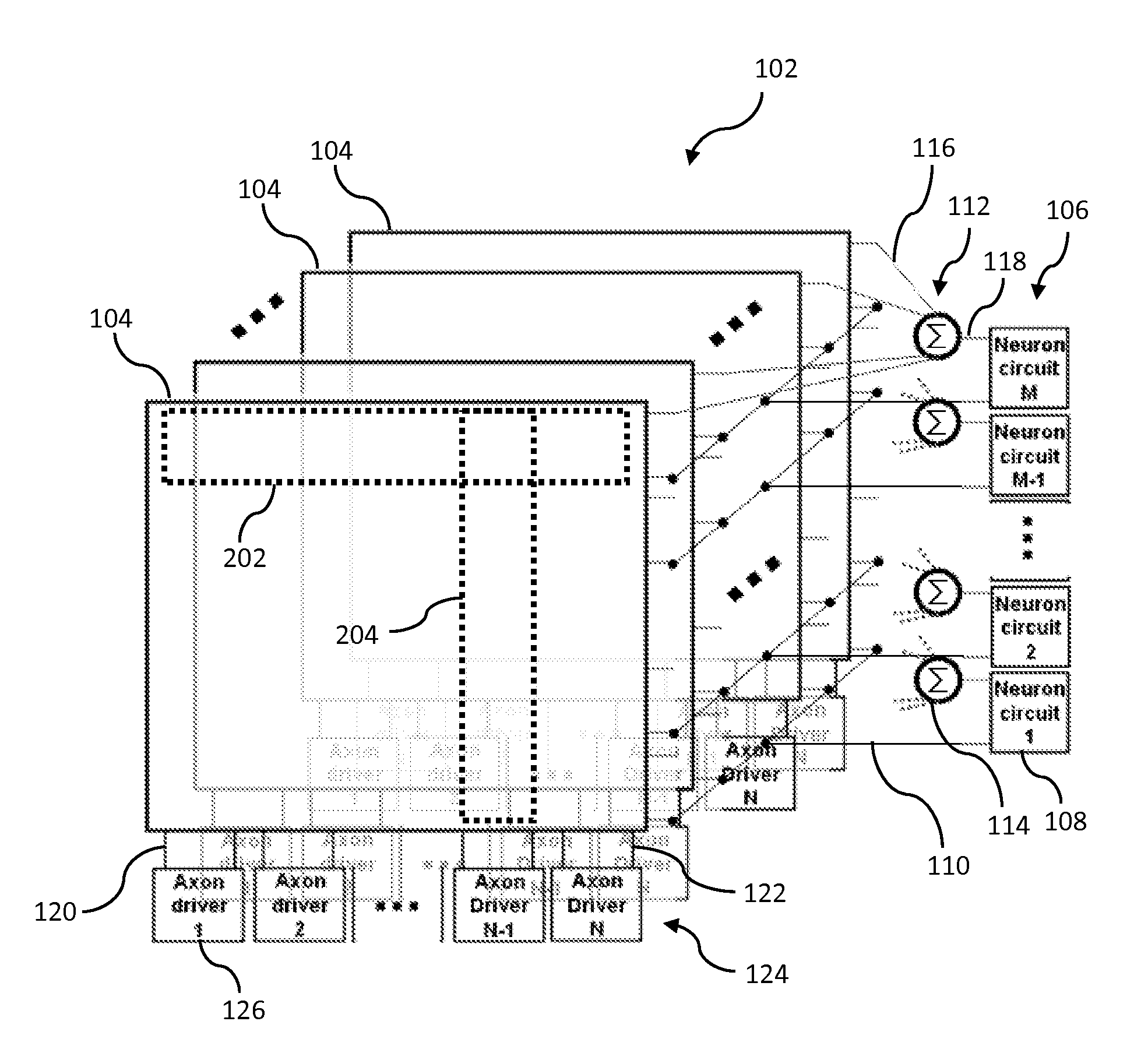

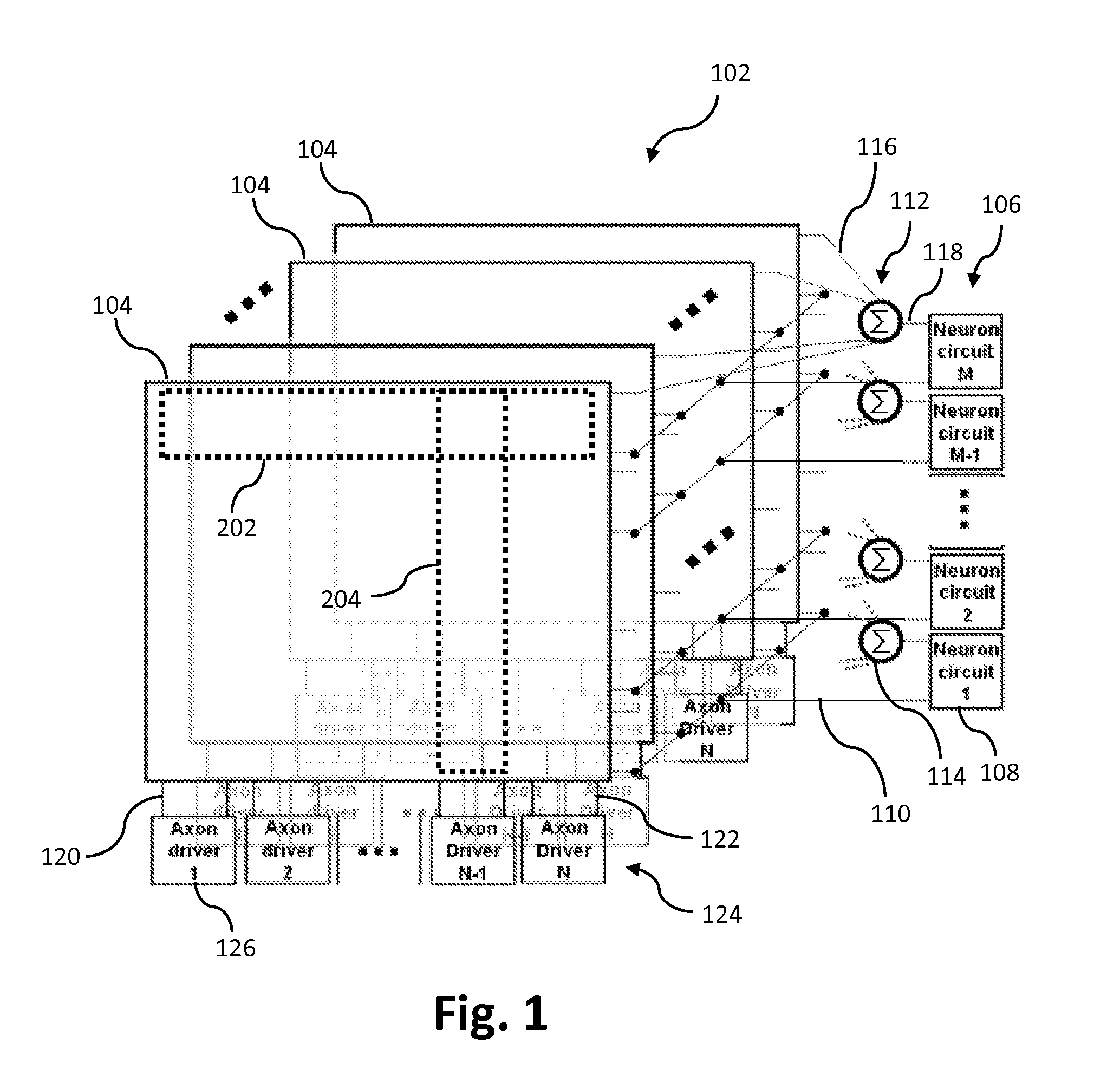

High-order time encoder based neuron circuit using a hysteresis quantizer, a one bit DAC, and a second order filter

Owner:HRL LAB

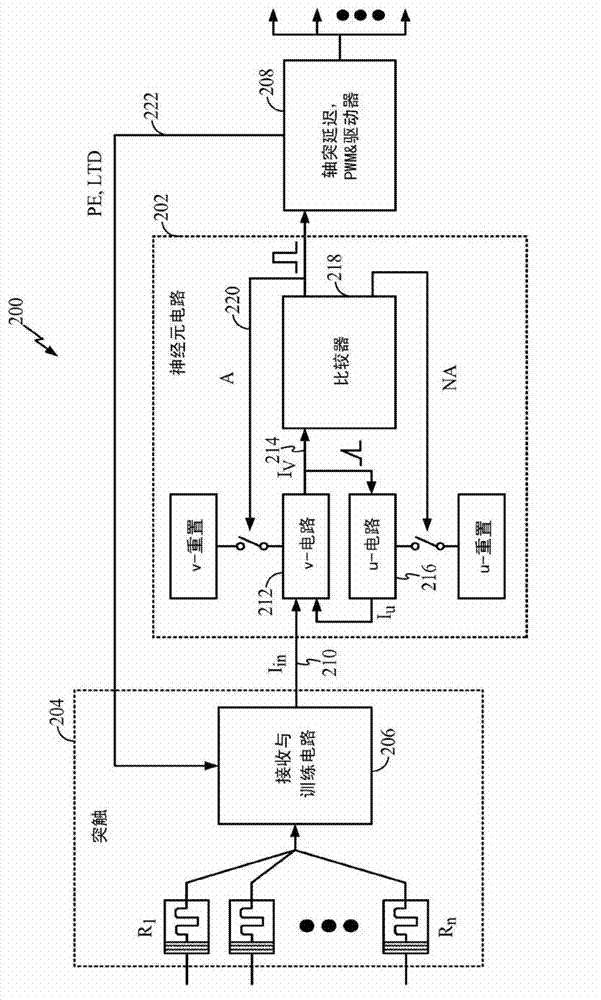

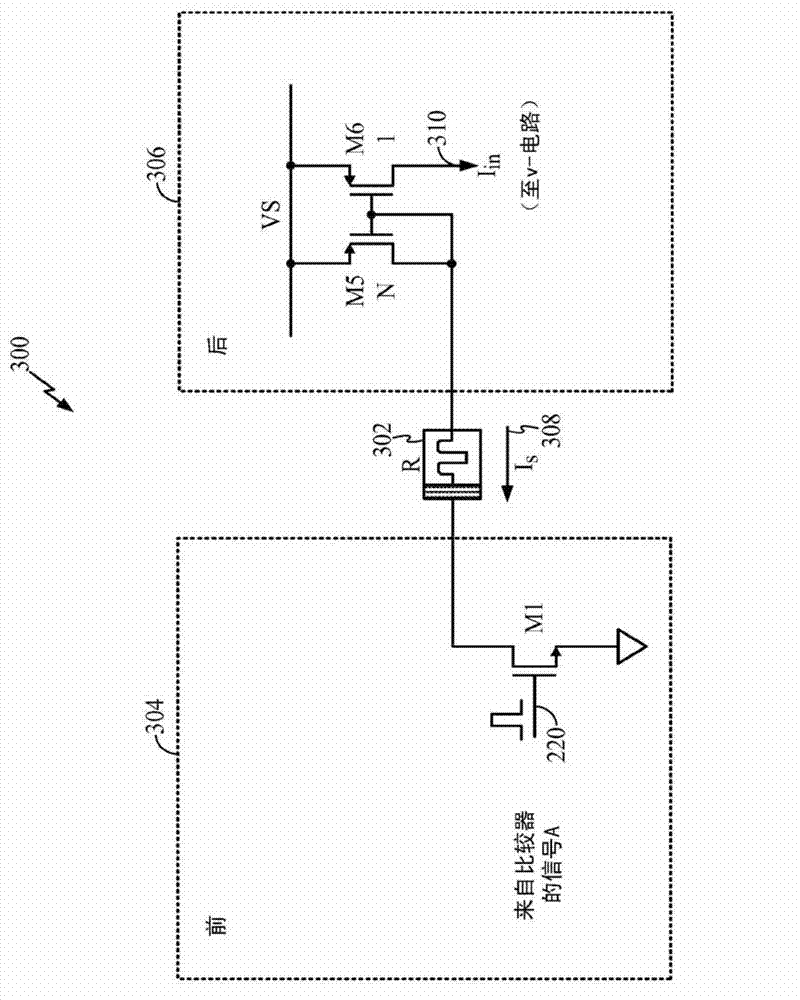

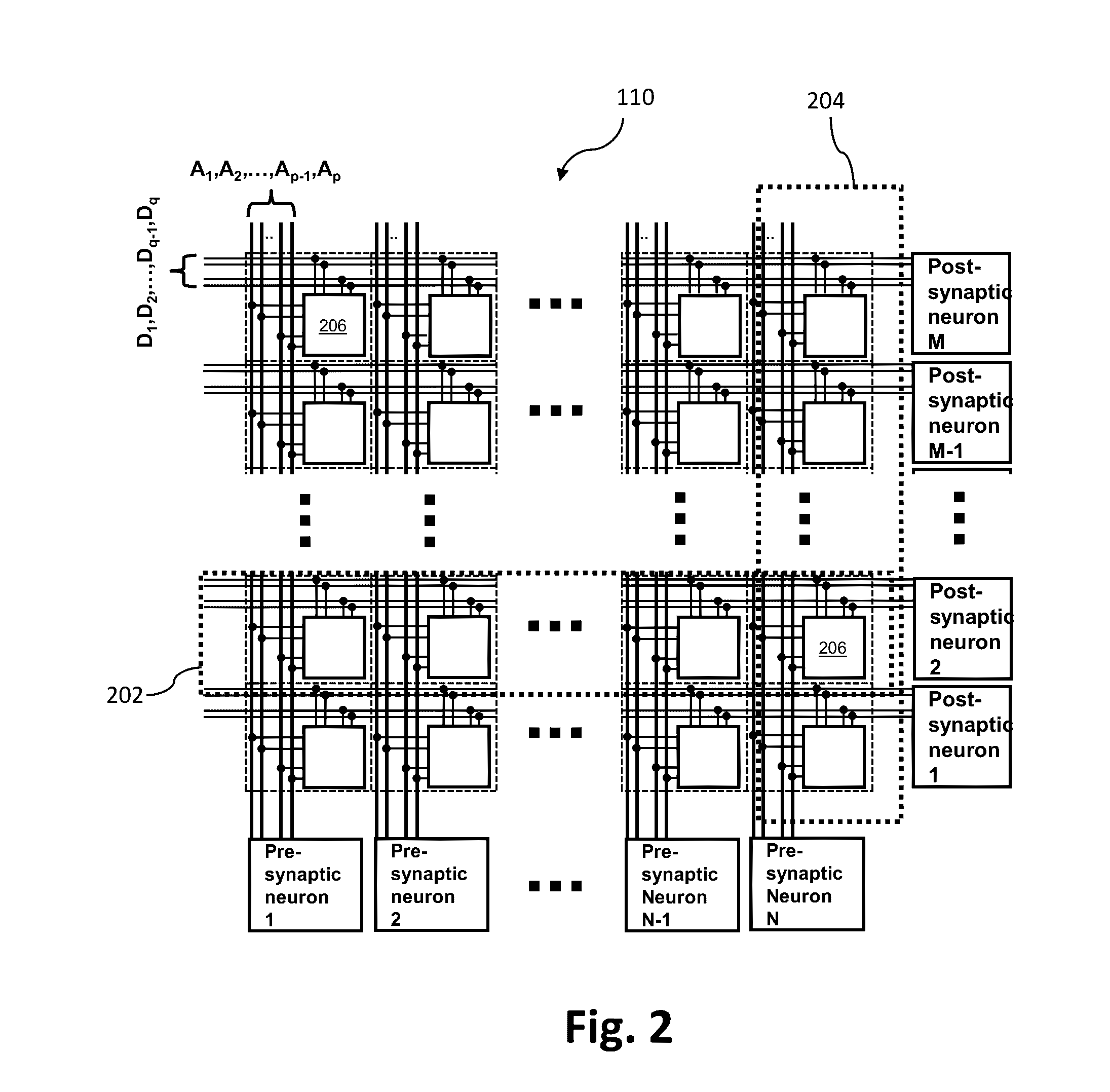

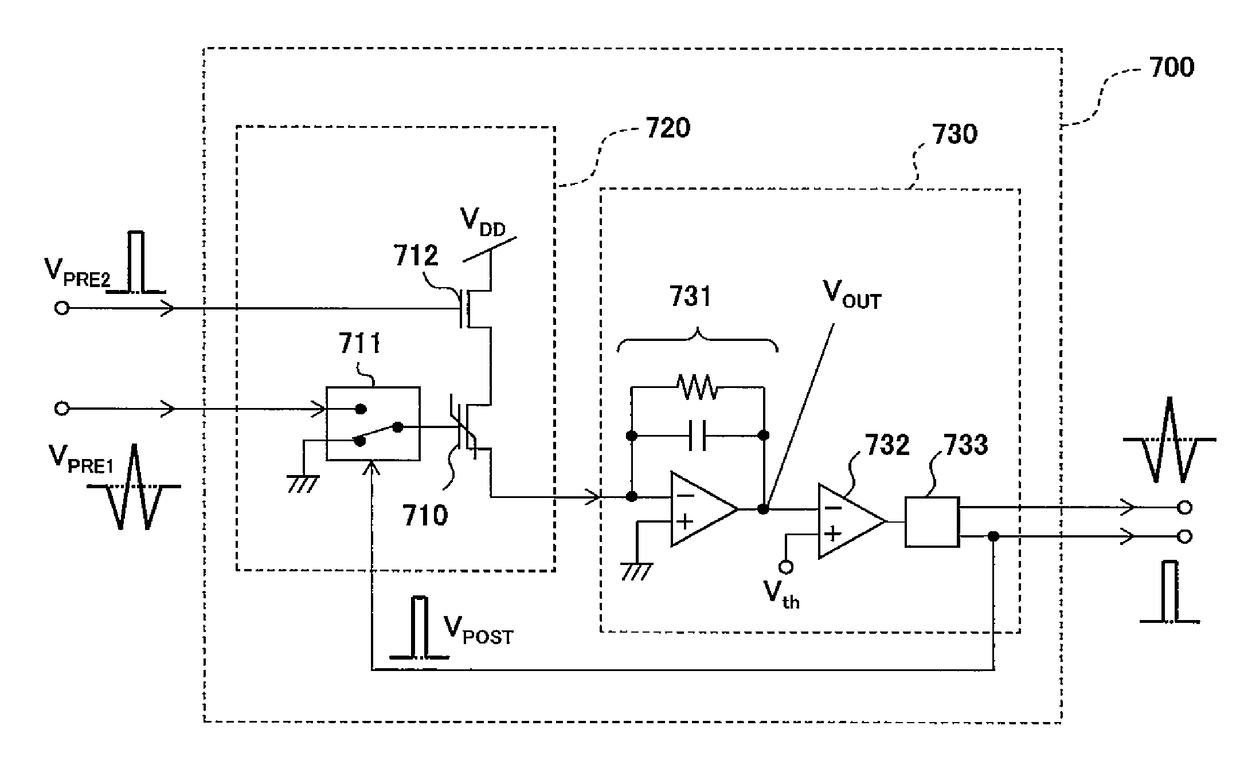

Neuron peripheral circuits for neuromorphic synaptic memory array based on neuron models

ActiveUS20160350647A1Neural architecturesPhysical realisationElectrical resistance and conductanceNeuronal models

A neuromorphic memory system including neuromorphic memory arrays. The neuromorphic memory system includes a presynaptic neuron circuit coupled to a postsynaptic neuron circuit by a resistive memory cell. The method includes generating a presynaptic LIF pulse on a presynaptic LIF line at time t1. An activating operation activates an access transistor coupled to the presynaptic LIF line in response to the presynaptic LIF pulse. The access transistor enables LIF current to pass through the resistive memory cell to a postsynaptic LIF line. An integrating operation integrates the LIF current at the postsynaptic LIF line over time. A comparing operation compares a LIF voltage at the postsynaptic LIF line to a threshold voltage. A generating operation generates a postsynaptic spike timing dependent plasticity (STDP) pulse on a postsynaptic STDP line if the LIF voltage is beyond the threshold voltage.

Owner:SAMSUNG ELECTRONICS CO LTD

Communication and synapse training method and hardware for biologically inspired networks

Owner:QUALCOMM INC

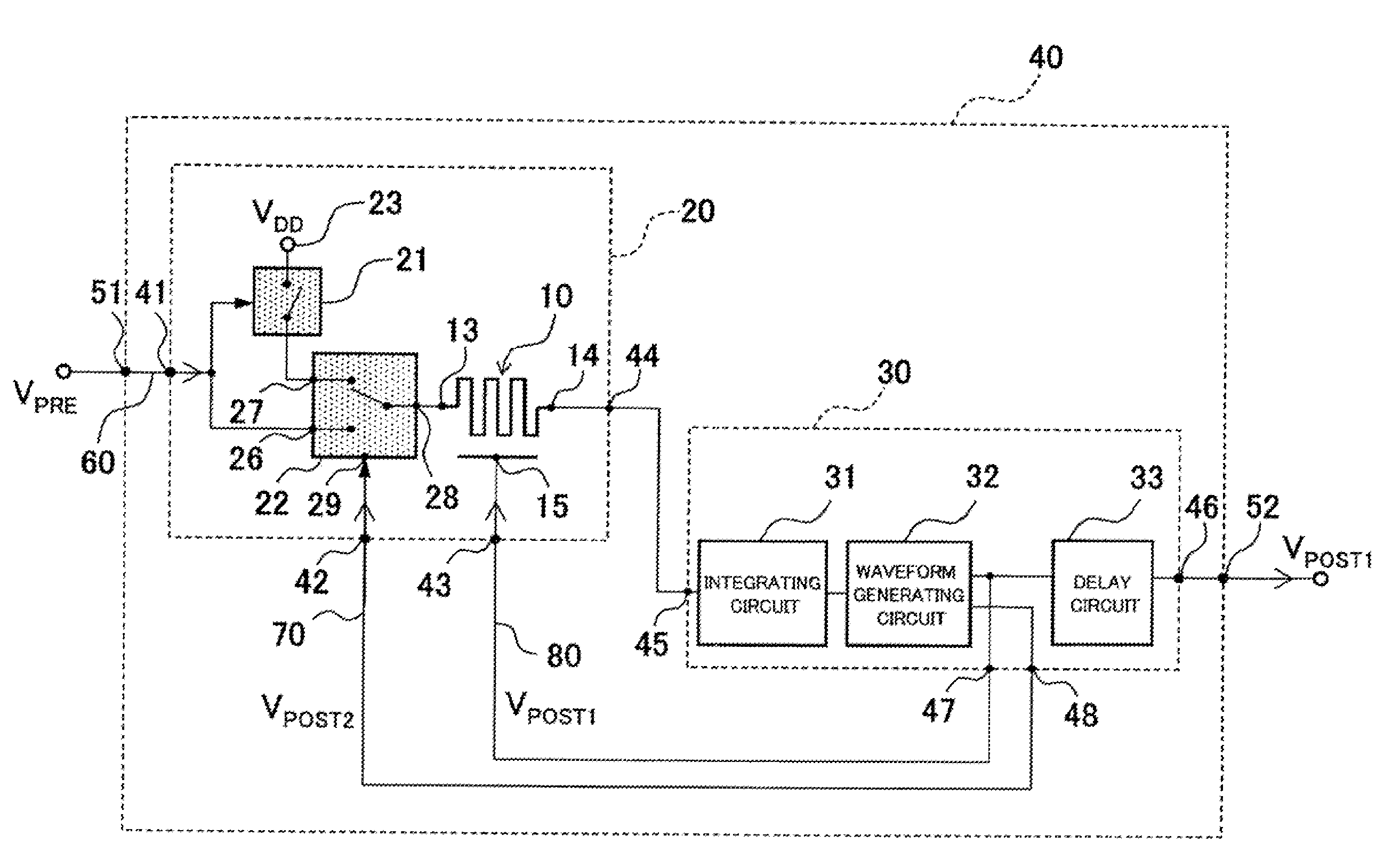

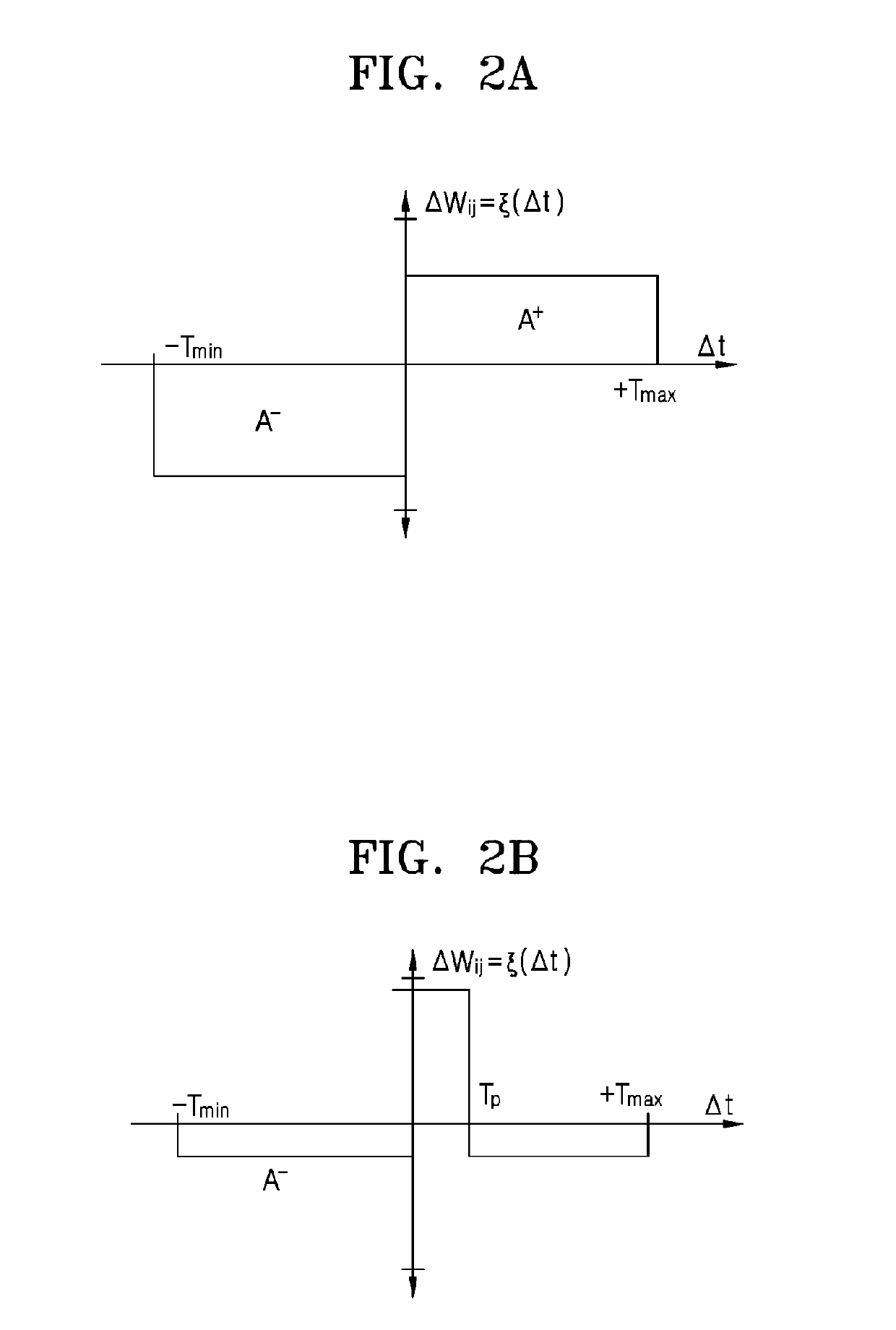

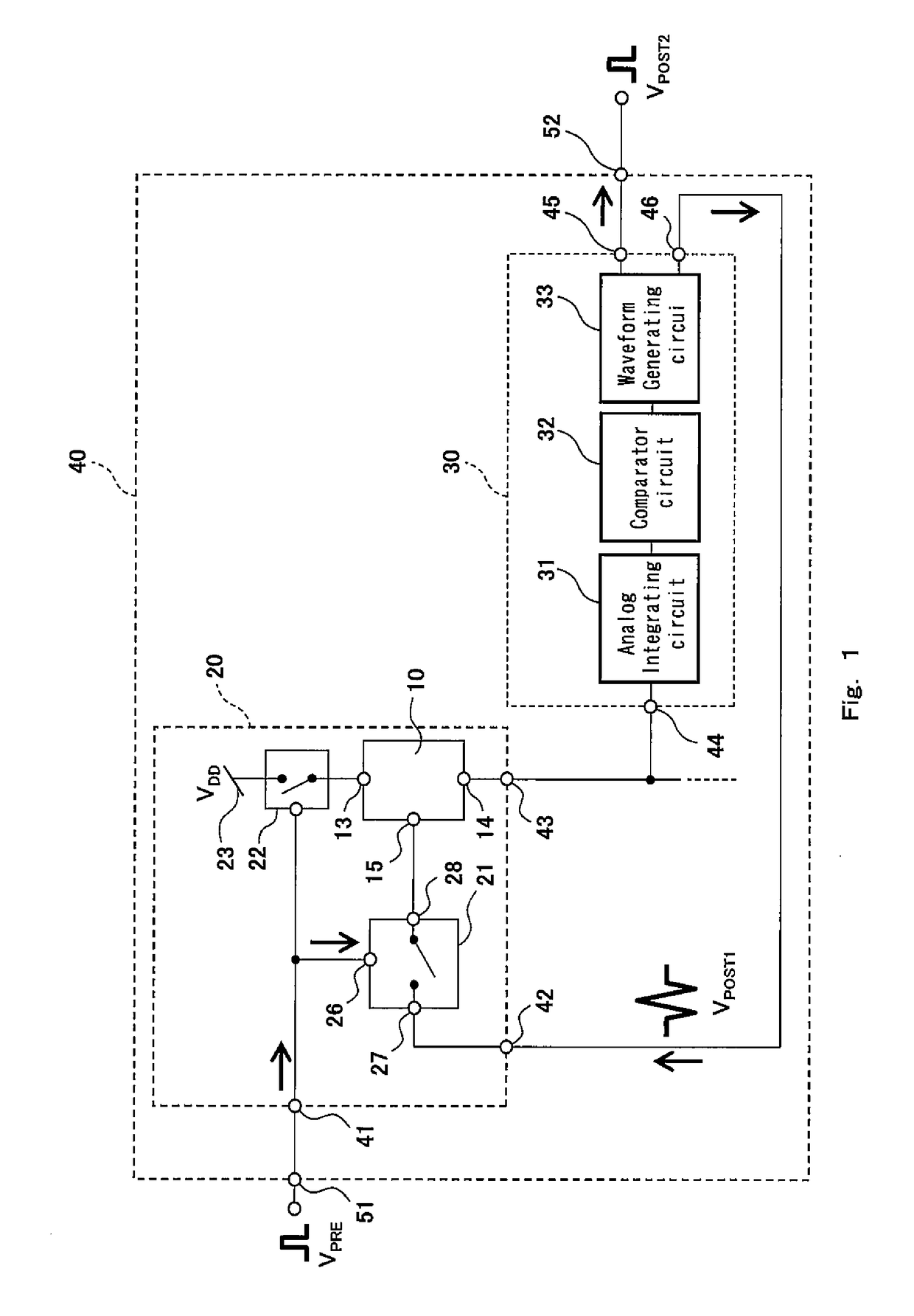

Learning method of neural network circuit

InactiveUS20130311415A1Reduce the numberDigital computer detailsDigital dataElectrical resistance and conductanceNeuron circuit

A neuron circuit in a neural network circuit element includes a waveform generating circuit for generating a bipolar sawtooth pulse voltage, and a first input signal has a bipolar sawtooth pulse waveform. For a period during which the first input signal is permitted to be input to a first electrode of a variable resistance element, the bipolar sawtooth pulse voltage generated within the neural network circuit element including the variable resistance element which is applied with the first input signal from another neural network circuit element is input to a control electrode of the variable resistance element. The resistance value of the variable resistance element changes due to an electric potential difference between the first electrode and the control electrode, the electric potential difference being generated depending on an input timing difference between a voltage applied to the first electrode and the voltage applied to the control electrode.

Owner:PANASONIC INTELLECTUAL PROPERTY MANAGEMENT CO LTD

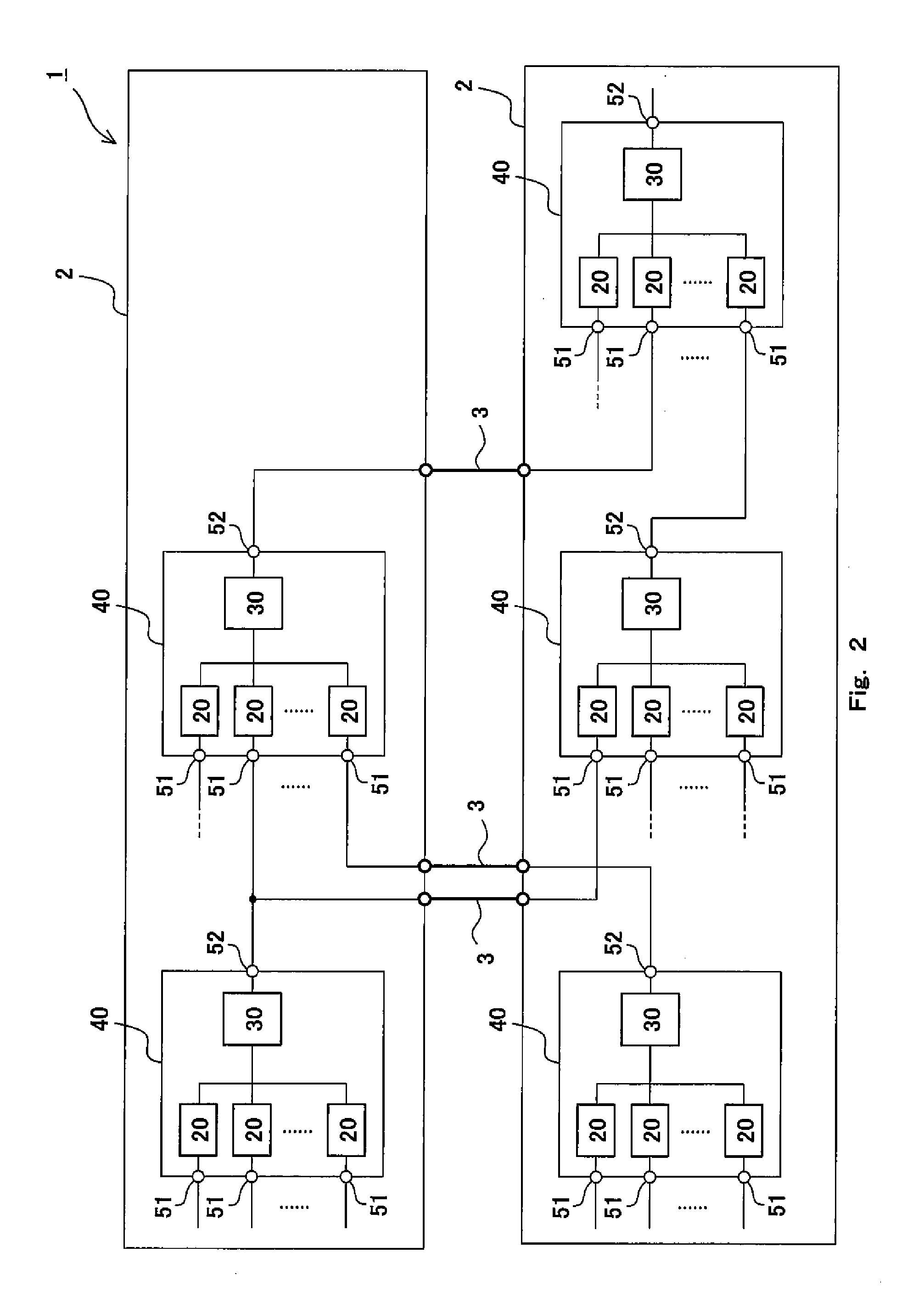

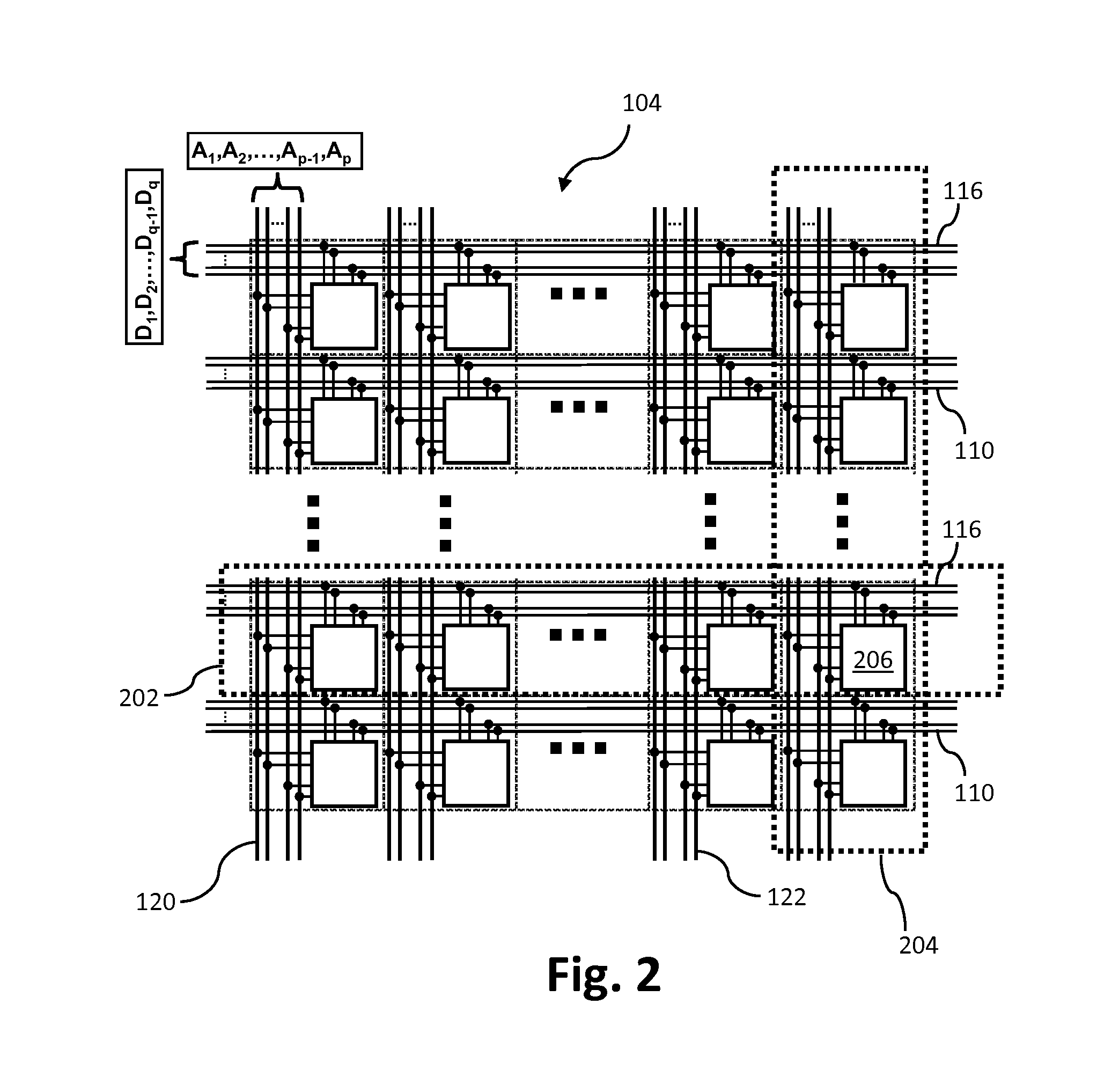

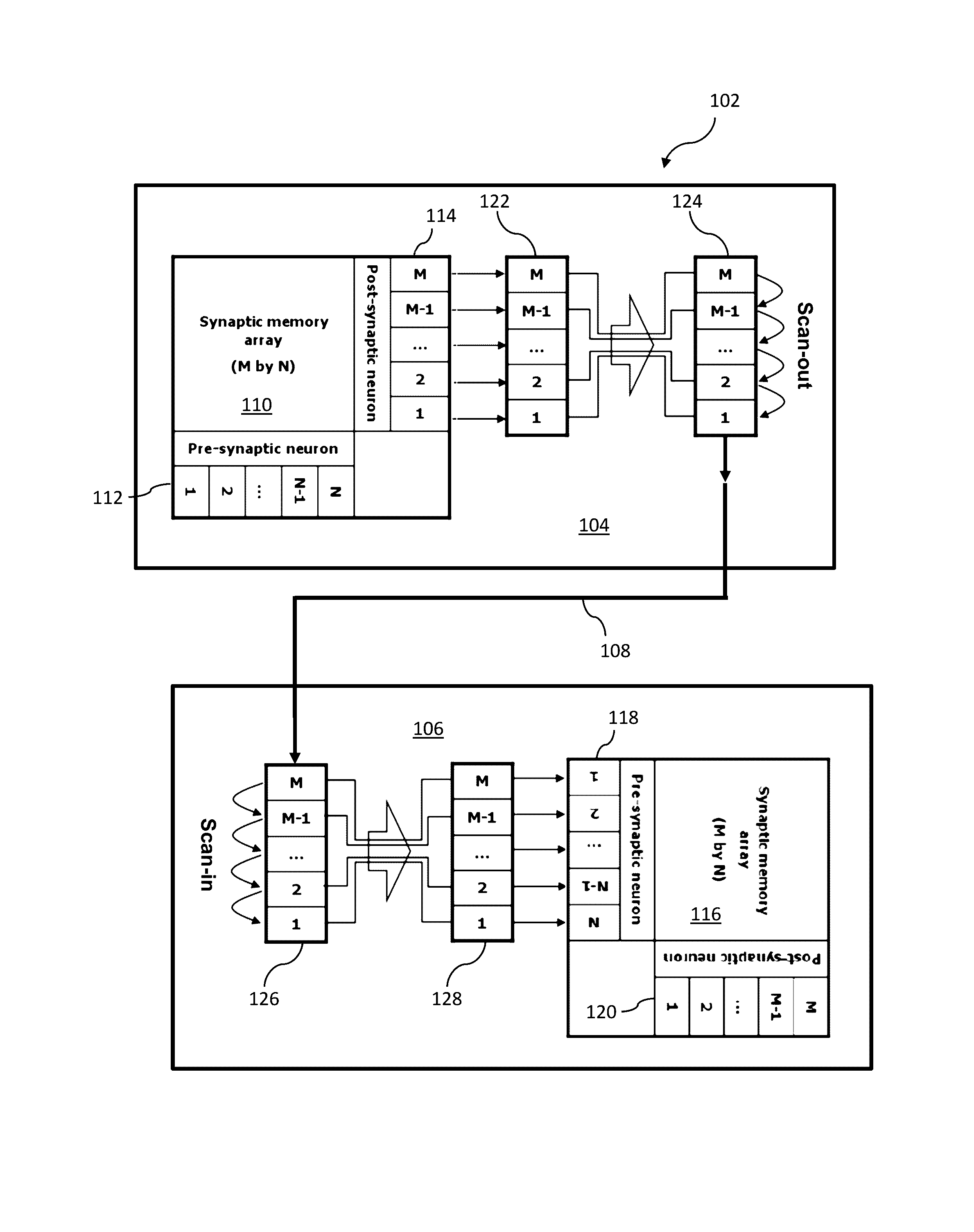

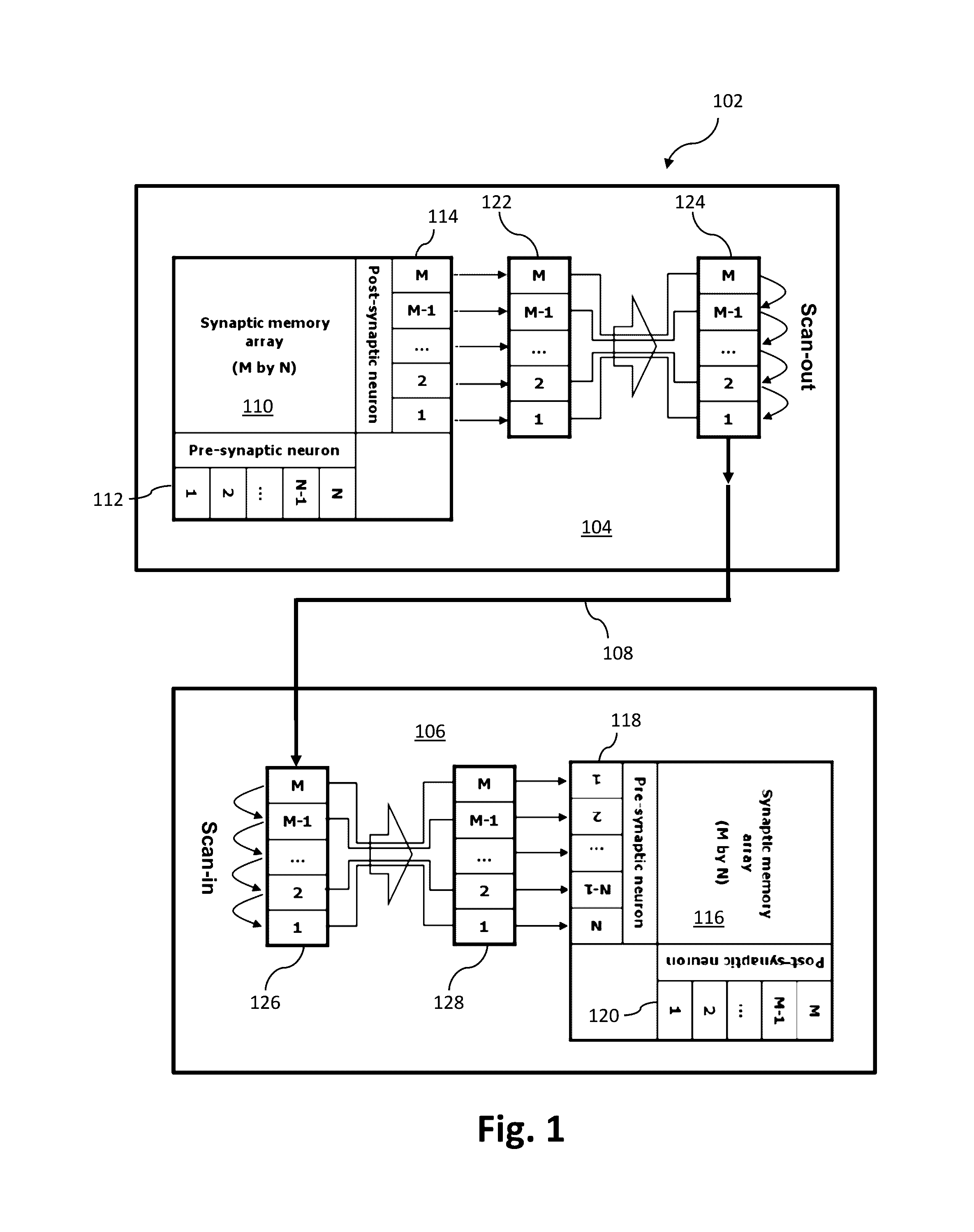

Communicating postsynaptic neuron fires to neuromorphic cores

A system for communicating postsynaptic neuron states. The system includes a first neuromorphic core and a second neuromorphic core. The first neuromorphic core includes a first array of synaptic memory cells and postsynaptic neuron circuits. Each of the postsynaptic neuron circuits is coupled to a row of synaptic memory cells in the first array of synaptic memory cells. Each of the postsynaptic neuron circuits is configured to fire when voltage sensed from the row of synaptic memory cells exceeds a threshold. The second neuromorphic core includes a second array of synaptic memory cells. A neuron bus is configured to serially transmit indications of a postsynaptic neuron circuit fire from the first neuromorphic core to the second neuromorphic core.

Owner:SAMSUNG ELECTRONICS CO LTD

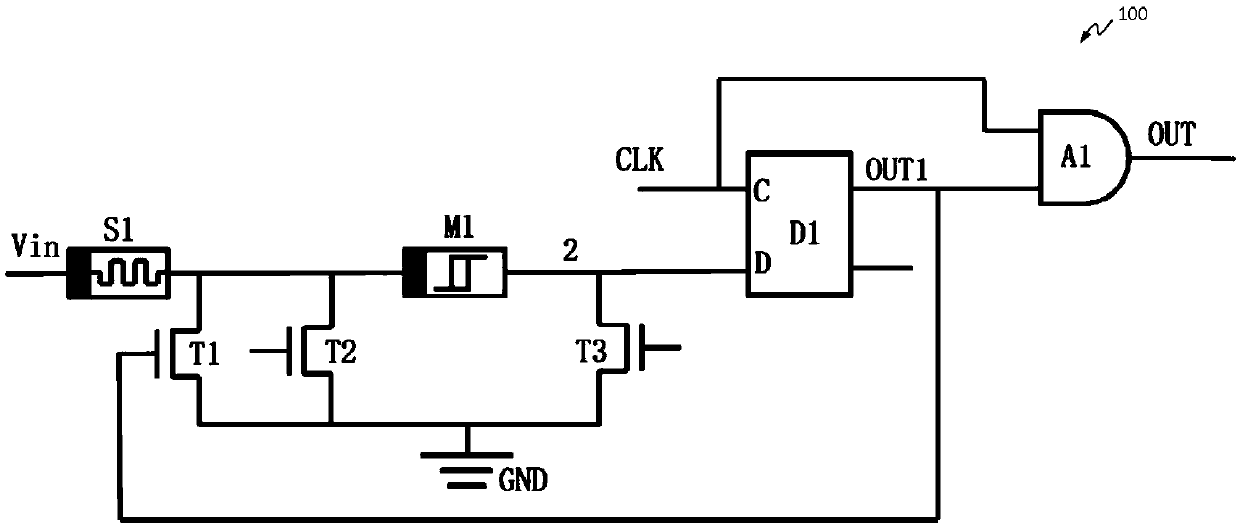

A neuron circuit and a neural network circuit

ActiveCN109102071AAchieve preparationImprove driving abilityPhysical realisationNeuron circuitExcitation signal

The invention discloses a neuron circuit including memristor elements, a trigger element, feedback elements and AND gates, wherein the memristor element is configured to receive an excitation signal,the trigger element is connected to the memristor element, and receives a clock control signal of the circuit and a signal outputted from the memristor element, the feedback element is used for connecting the output terminal of the trigger element and the input terminal of the memristor element, and controlling the voltage of the input terminal of the memristor element. The AND gate circuit is used for performing AND operation on the output signal of the trigger element and the clock control signal, and the output signal of the AND gate circuit is used as the output signal of the neuron circuit. The invention also relates to a neural network circuit.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

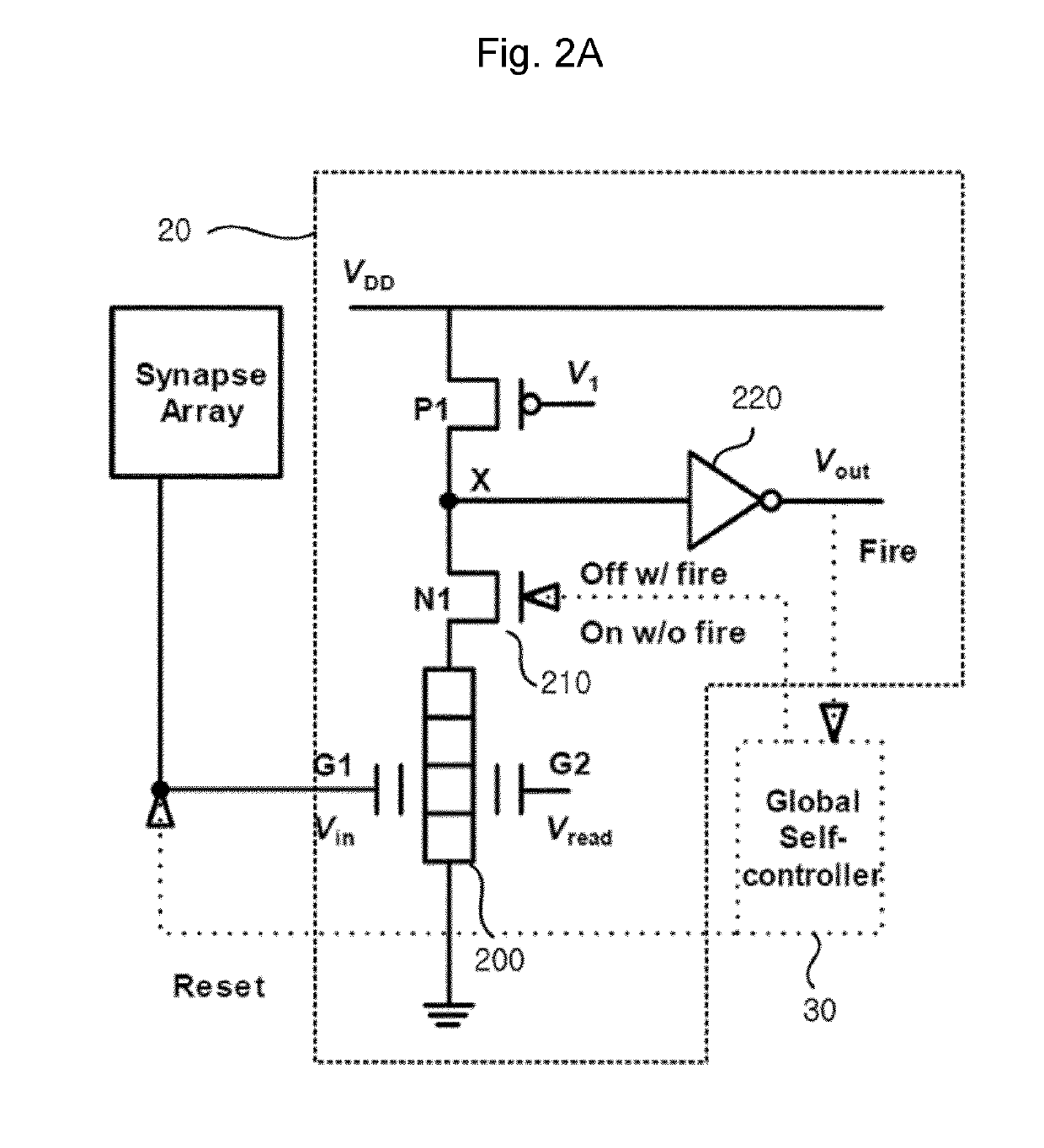

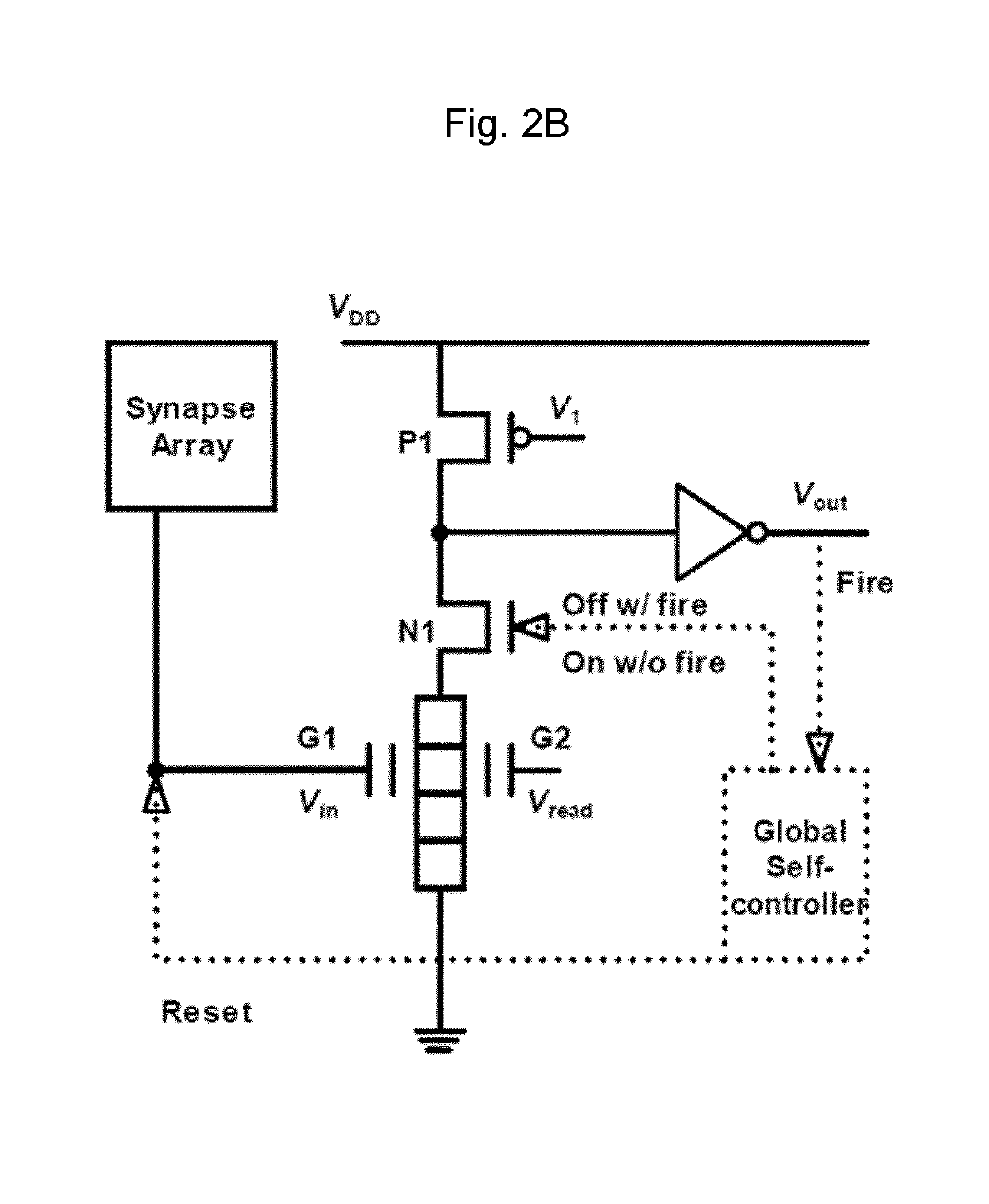

Neuromorphic system

ActiveUS20190171933A1Improve good performanceIncrease the areaNeural architecturesPhysical realisationLateral inhibitionControl signal

Provided is a neuromorphic system using a neuron circuit. The neuromorphic system includes: one or two or more neuron circuits configured to output a firing signal according to signals input from a synapse array; a homeostatic circuit for each neuron circuit; and a global self-controller configured to generate and provide control signals for the neuron circuits by using the firing signal output from the neuron circuits. The neuron circuit includes a neuromorphic device and an output circuit that outputs the firing signal of the neuromorphic device. The global self-controller generates and supplies a reset signal to the neuromorphic device of the fired neuron circuit, and the global self-controller generates and supplies a lateral inhibition signal to the neuromorphic device of the non-fired neuron circuit. The homeostatic circuit alleviates inhibition of other neurons by the neurons with a predominant firing function.

Owner:SEOUL NAT UNIV R&DB FOUND

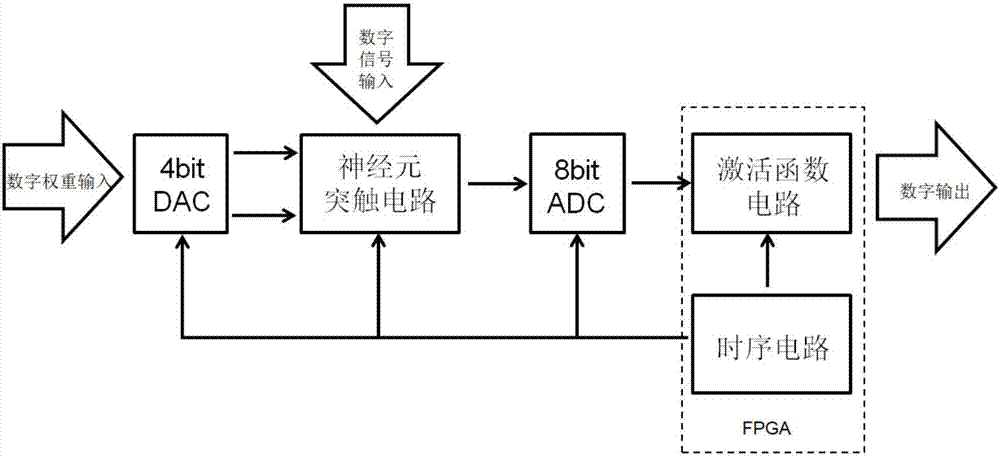

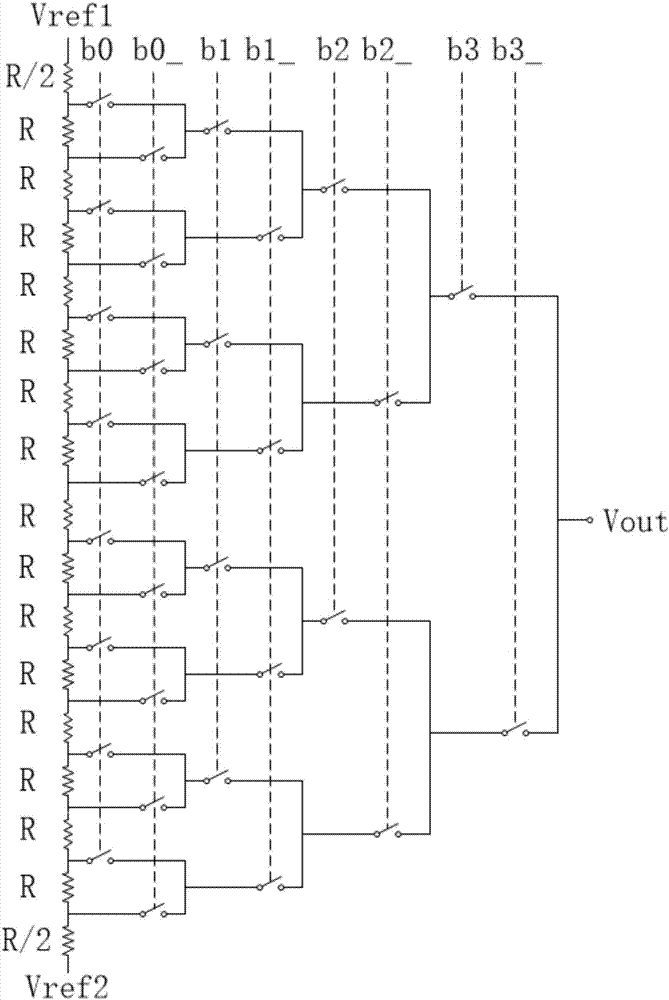

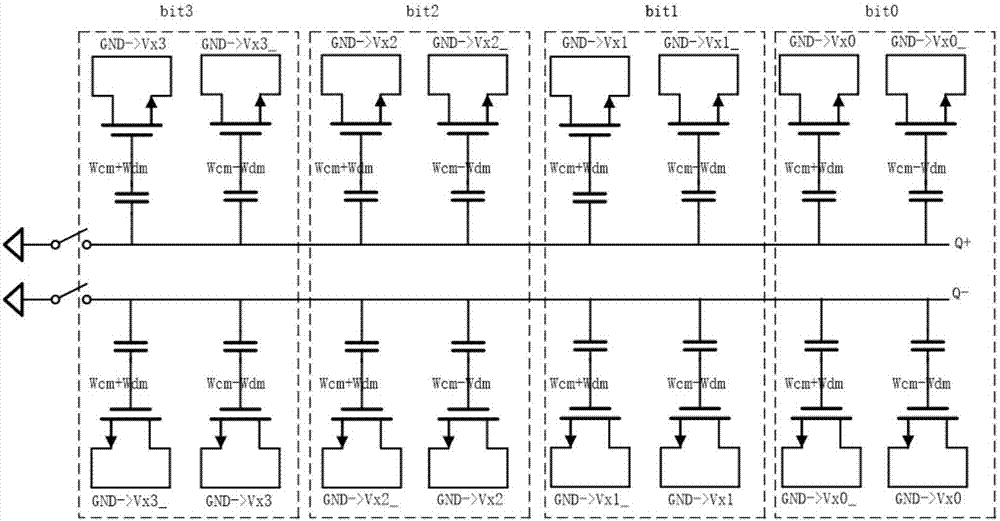

Digital-analog hybrid charge domain neuron circuit based on CMOS process

ActiveCN107545305AAvoid transmission distortionStandard maturePhysical realisationActivation functionNeuron circuit

The invention discloses a digital-analog hybrid charge domain neuron circuit based on the CMOS process. The neuron circuit is characterized by comprising a 4bit DAC, a neuron synapse circuit, an 8bitADC, an activation function circuit and a sequential circuit, wherein the 4bit DAC, the neuron synapse circuit, the 8bit ADC and the activation function circuit are sequentially connected, and the sequential circuit is connected with the 4bit DAC, the neuron synapse circuit, the 8bit ADC and the activation function circuit. The neuron circuit has advantages of mature process, low cost, low power consumption and high universality.

Owner:合肥中科微电子创新中心有限公司

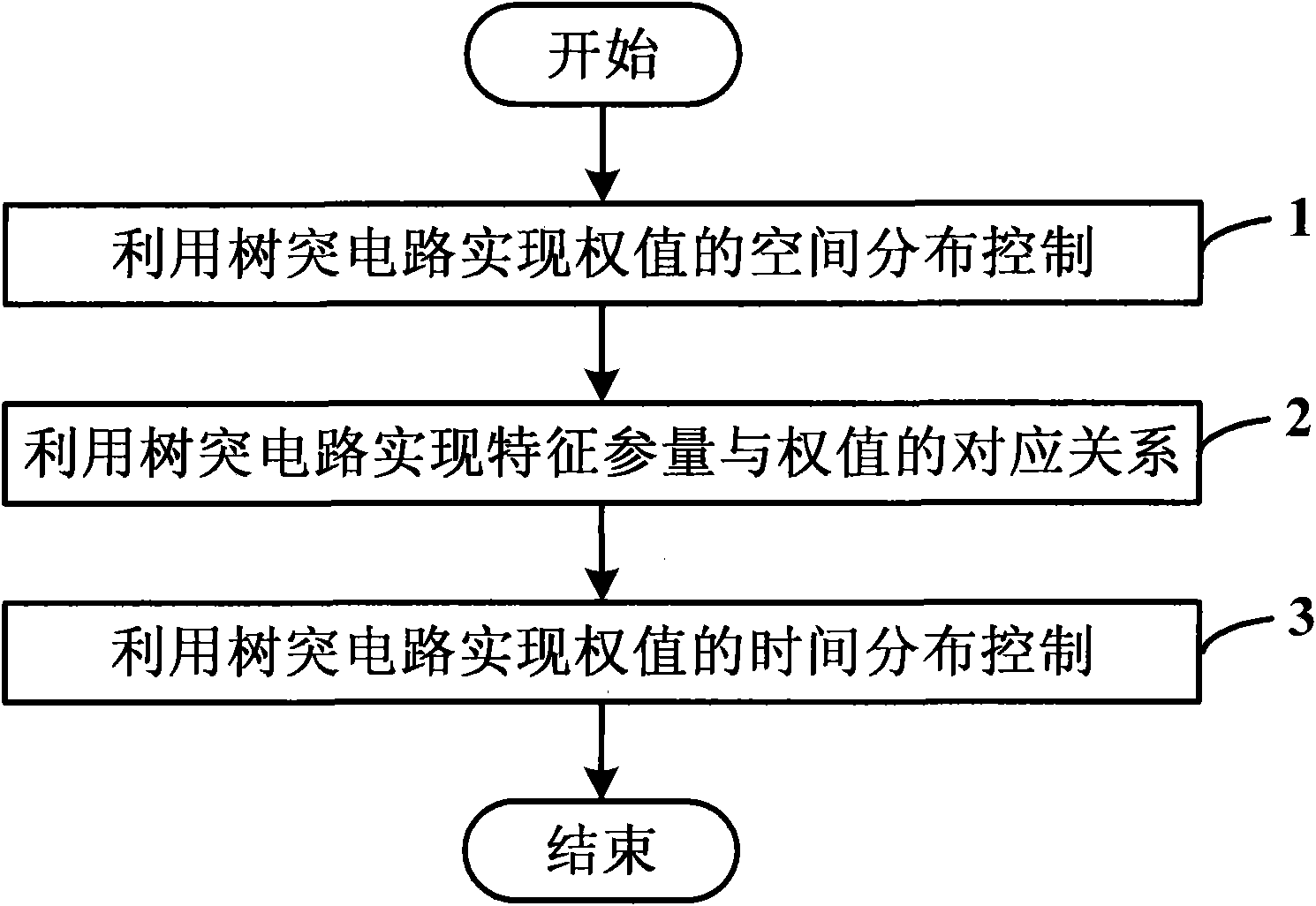

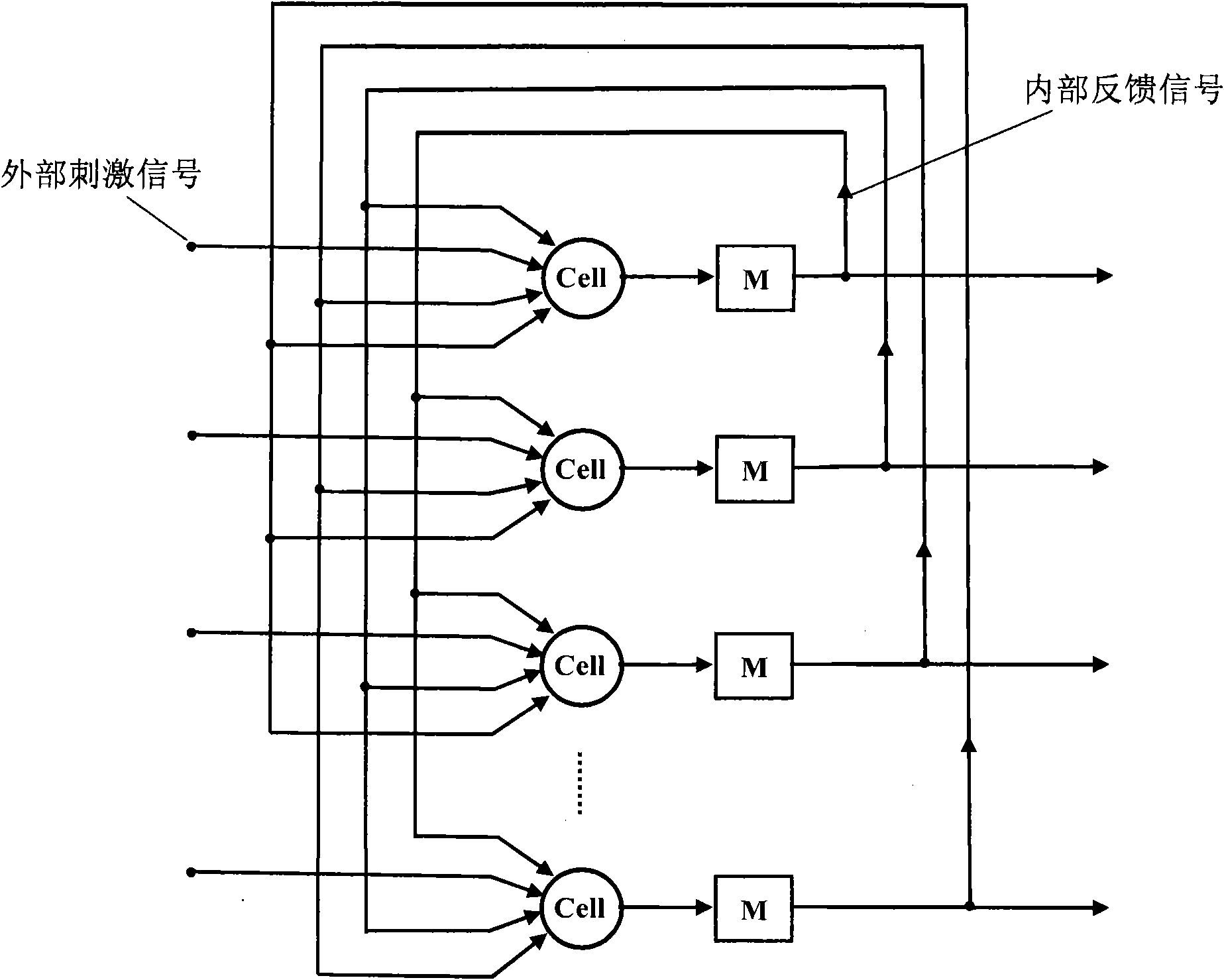

Method for weight control and information integration by utilizing time encoding

InactiveCN101860357ARealize dynamic distributed controlIncrease the simulation variation parameterLogic circuitsInformation processingDistribution control

The invention discloses a method for weight control and information integration by utilizing time encoding, which comprises the following steps: utilizing a dendritic circuit to control the spatial distribution of weight; utilizing the dendritic circuit to realize the corresponding relationship between characteristic parameters and the weight; and utilizing the dendritic circuit to control the time distribution of the weight. The invention utilizes the organic combination of input signals distributed in time and space to realize the dynamic distribution control of the weight, utilizes the noise margin characteristics of a CMOS inverter to change the output pulse frequency of a neuron circuit, so that the digital signals increase simulated change parameter. The invention helps to understand and simulate information processing way of biological neurons.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

Artificial feeling neural circuit and preparation method thereof

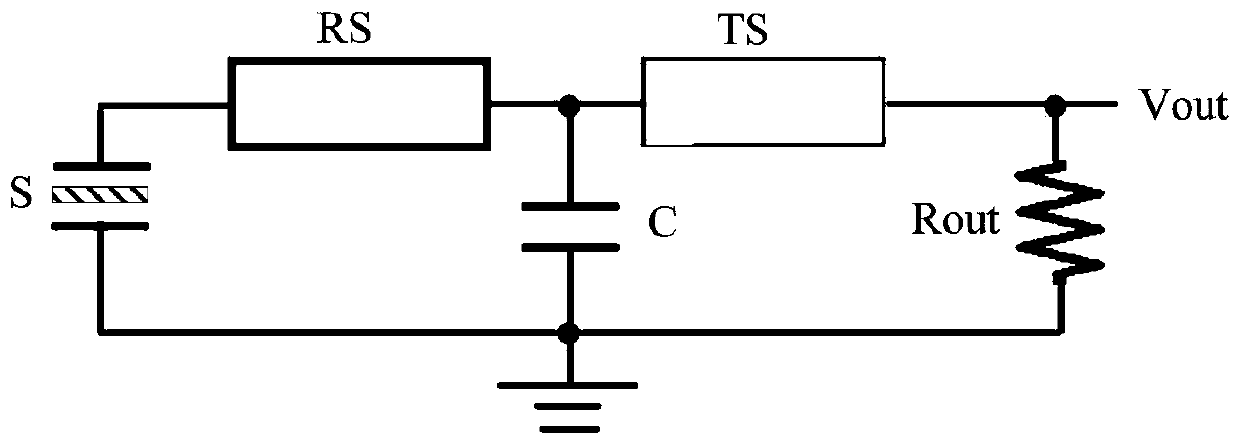

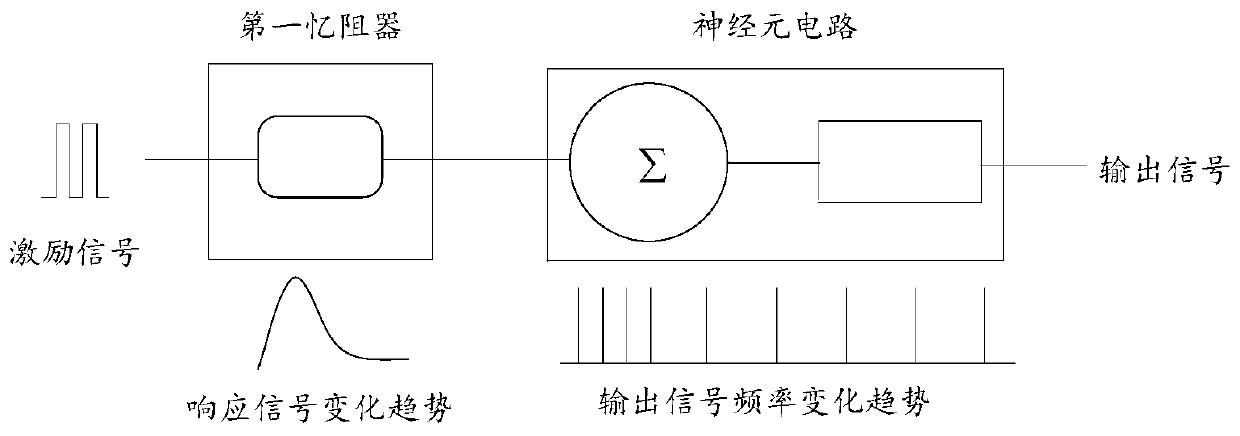

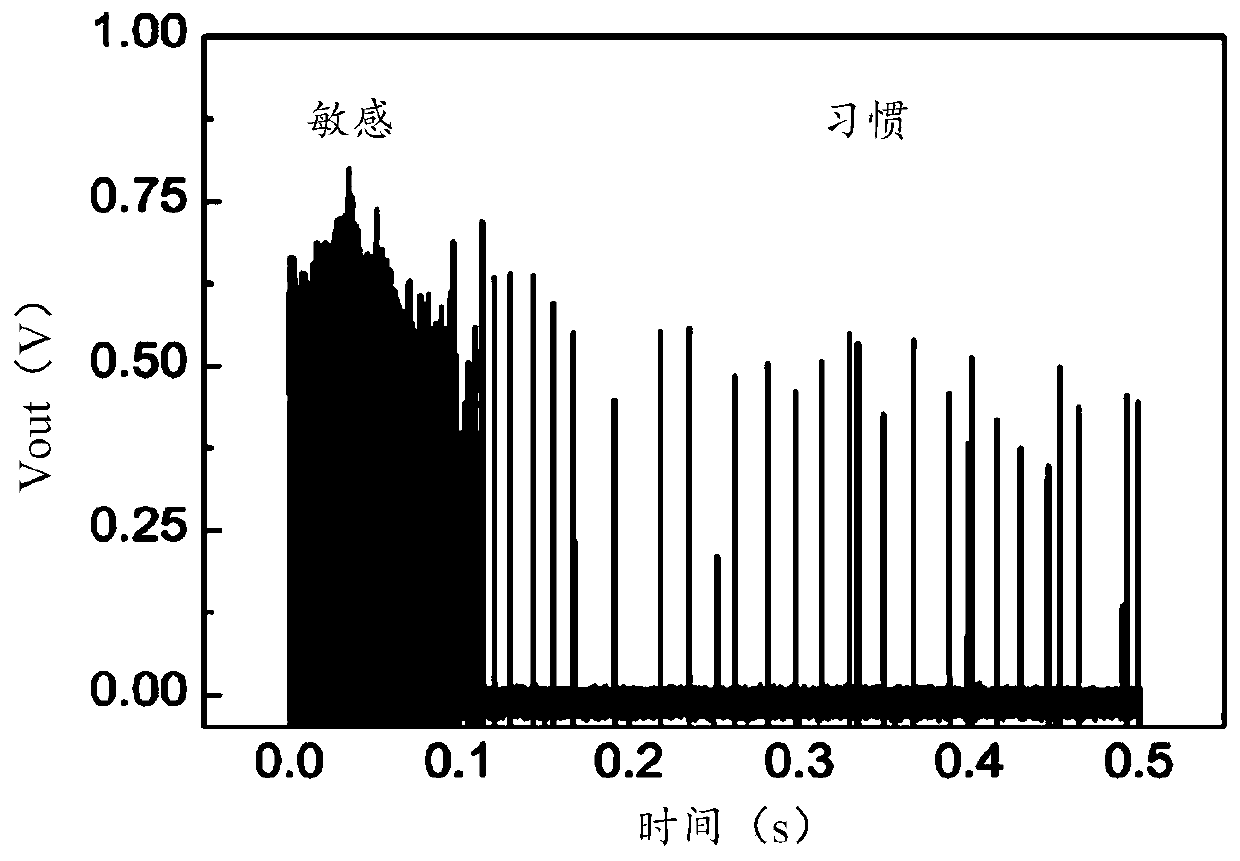

ActiveCN110647982AImplement featuresRealize functionSolid-state devicesPhysical realisationNeuron circuitNeuron

The invention discloses an artificial feeling neural circuit and a preparation method thereof, the artificial feeling neural circuit comprises a sensor, a first memristor and a neuron circuit, and thefirst memristor has a unidirectional resistance change characteristic; the sensor is used for sensing an external signal and generating an excitation signal according to the external signal; the first memristor is used for generating a response signal according to the excitation signal; and the neuron circuit is used for charging and discharging according to the response signal so as to output apulse signal. According to the artificial sensing neural circuit and the preparation method thereof, sensitivity and habit characteristics of biological sensing can be realized by adopting a simple circuit structure.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

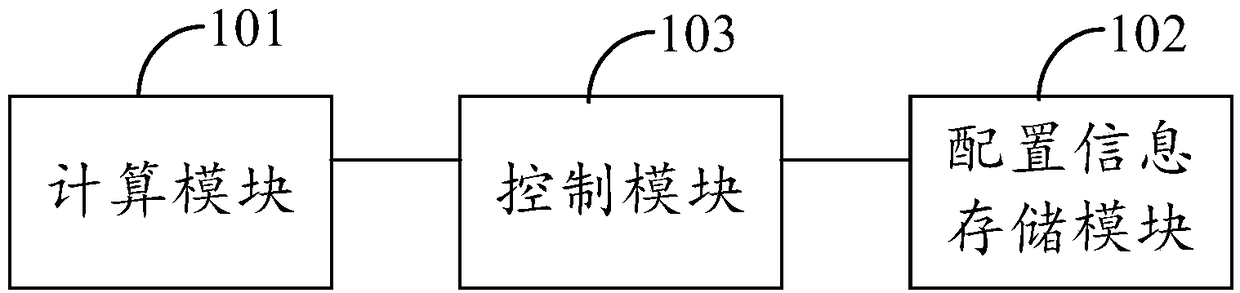

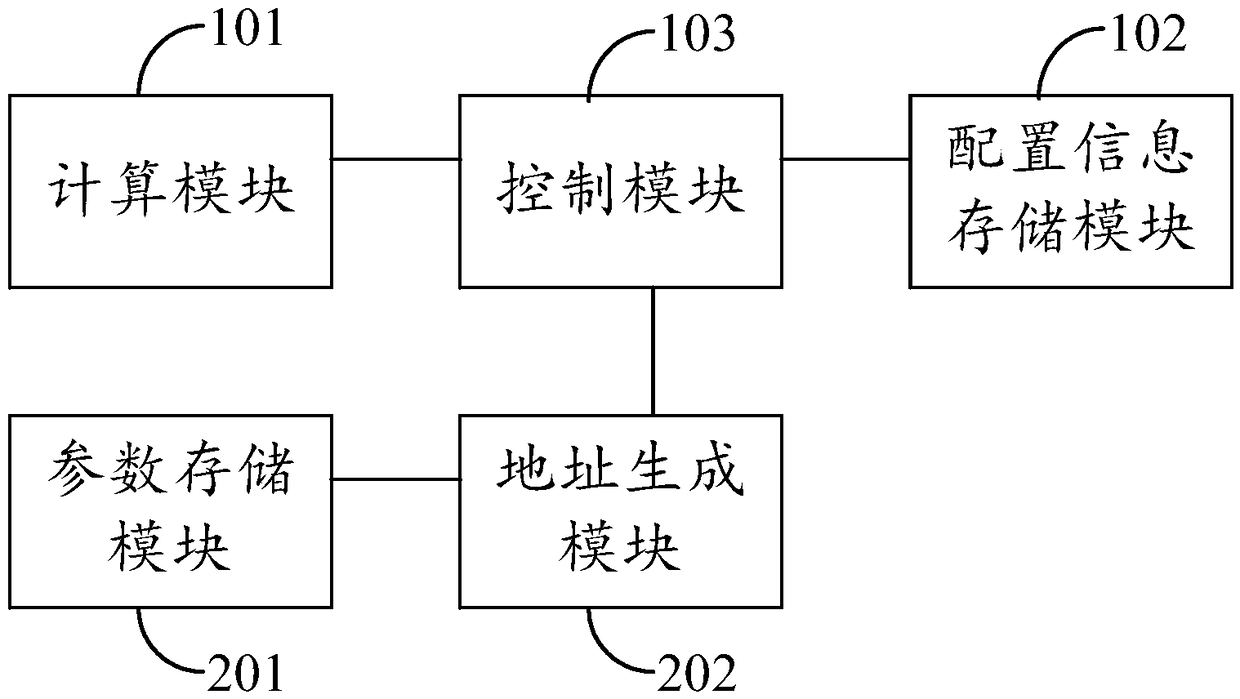

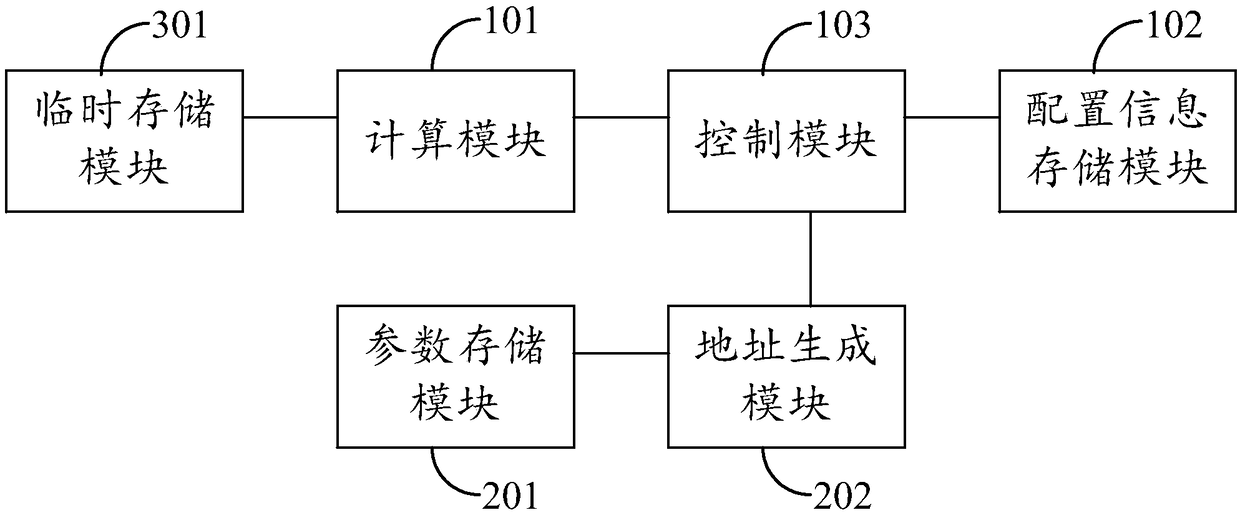

Neuron circuit circuit, chip, system, method and storage medium

ActiveCN109409510AMeet Computing NeedsNeural architecturesPhysical realisationComputer architectureNerve network

The invention is applicable to the computer technical field and provides a neuron circuit, a chip, a system and a method thereof, and a storage medium. The neuron circuit comprises the following structures: a calculation module; a configuration information storage module, configured to store configuration information of a neuron processing mode; and a control module, configured to control the computing module to adjust to the corresponding computing infrastructure and execute the corresponding neural network layer node data processing according to the processing mode configuration information.In this way, it can meet the fast iteration of complex and diverse neural network computing needs, can be widely used in computing resources are limited, the need for a certain neural network architecture reconfigurable areas, expand the depth of learning chip applications.

Owner:深圳市中科元物芯科技有限公司

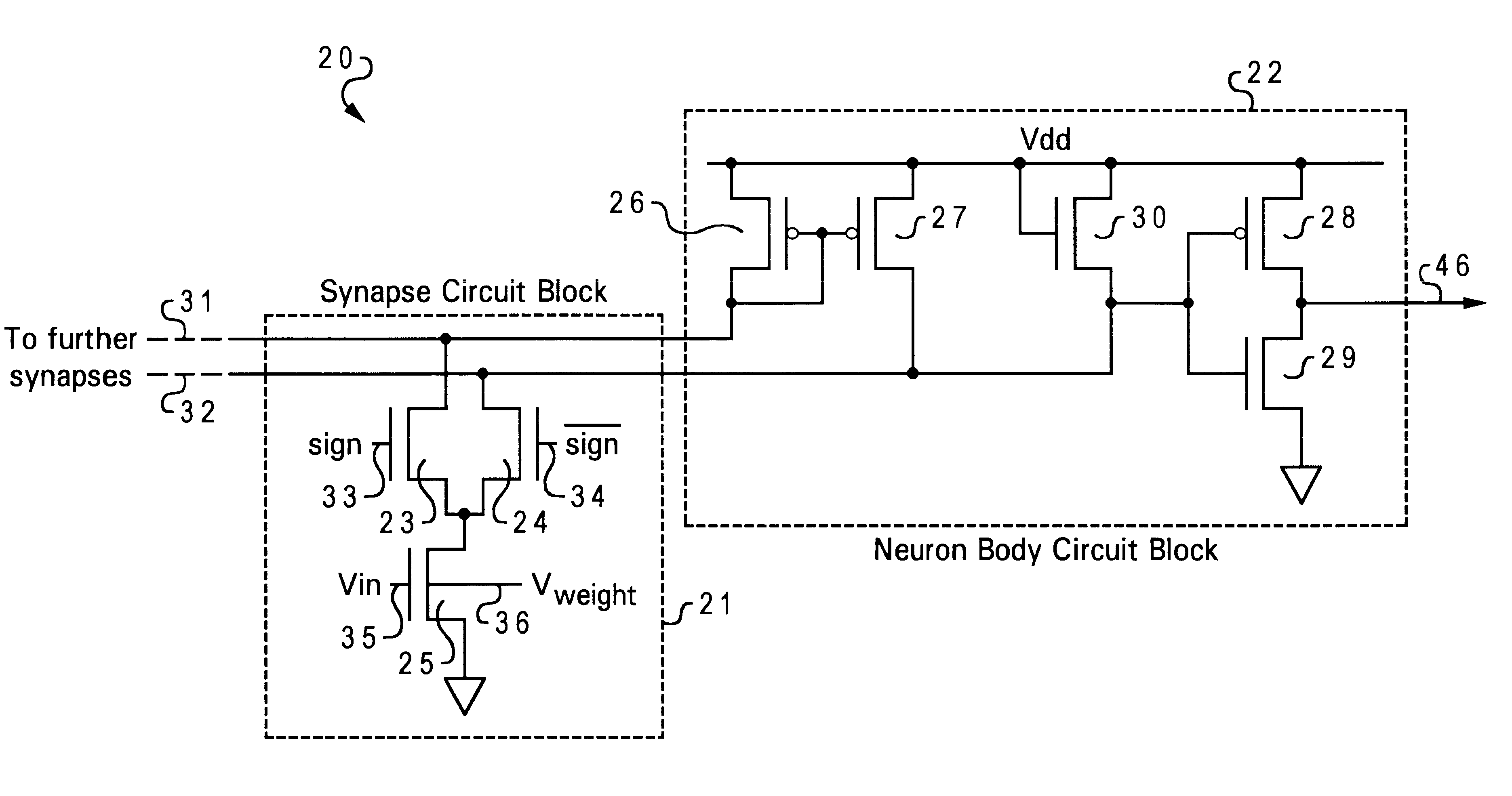

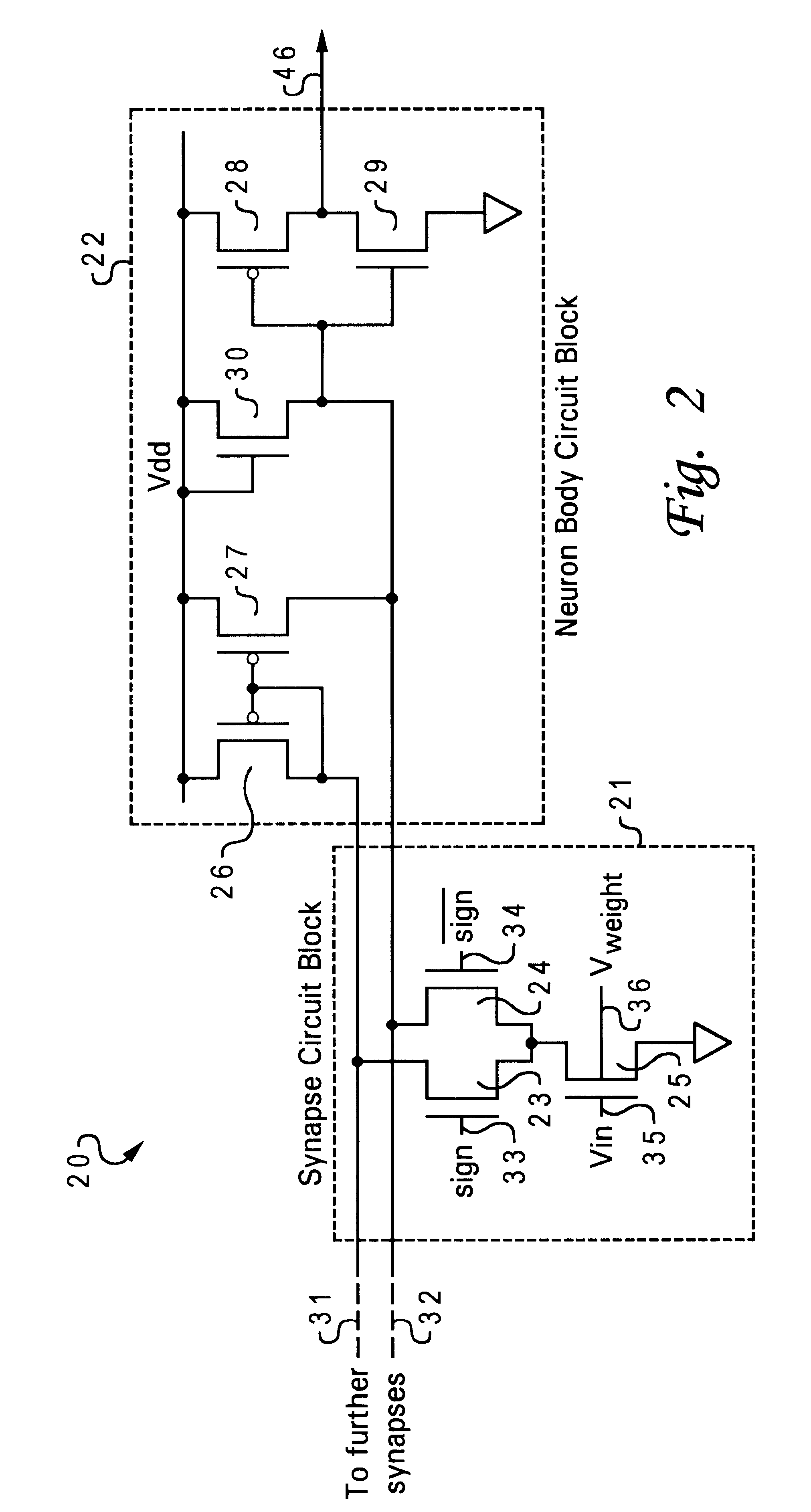

Neuron circuit

InactiveUS6501294B2Reliability increasing modificationsMajority/minority circuitsNeuron circuitSynapse structure

A neuron circuit that can be served as a building block for a neural network implemented in an integrated circuit is disclosed. The neuron circuit includes a synapse circuit block and a neuron body circuit block. The synapse circuit block has three transistors, and the body of one of the three transistors is controlled by a weighted input. The neuron body circuit block includes a current mirror circuit, a summing circuit, and an invertor circuit. The neuron body circuit is coupled to the synapse circuit block to generate an output pulse.

Owner:IBM CORP

Multi-mode neuron circuit and neuron realizing method

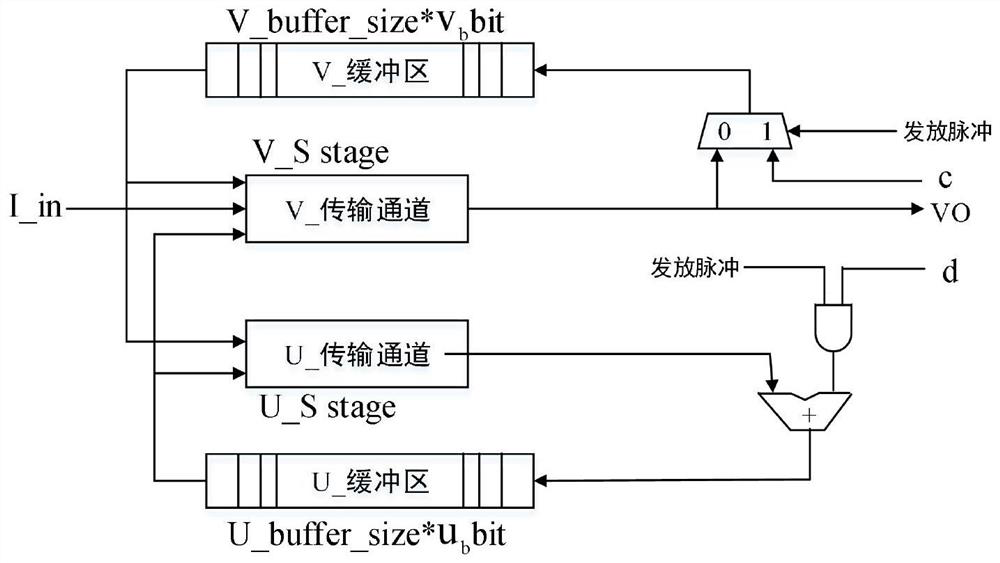

ActiveCN108681772AEasy to implementEasy to operatePhysical realisationNeural network systemControl signal

The invention discloses a multi-mode neuron circuit and a neuron realizing method. The circuit comprises a pulse generating circuit, and an auxiliary U-unit circuit which is connected with the pulse generating circuit. The pulse generating circuit is used for outputting a pulse sequence in a preset mode through function of a control signal and external applied voltage for realizing the corresponding neuron. The U-unit circuit is used for generating the external applied voltage and applies the external applied voltage to the pulse generating circuit. The multi-mode neuron circuit and the neuronrealizing method can effectively realize the neuron when realization of a large-scale pulse neural network system is required, thereby overcoming a problem of high operation difficulty in realizing different neurons through accurately adjusting offset voltage when realization of the large-scale pulse neural network is required.

Owner:PEKING UNIV

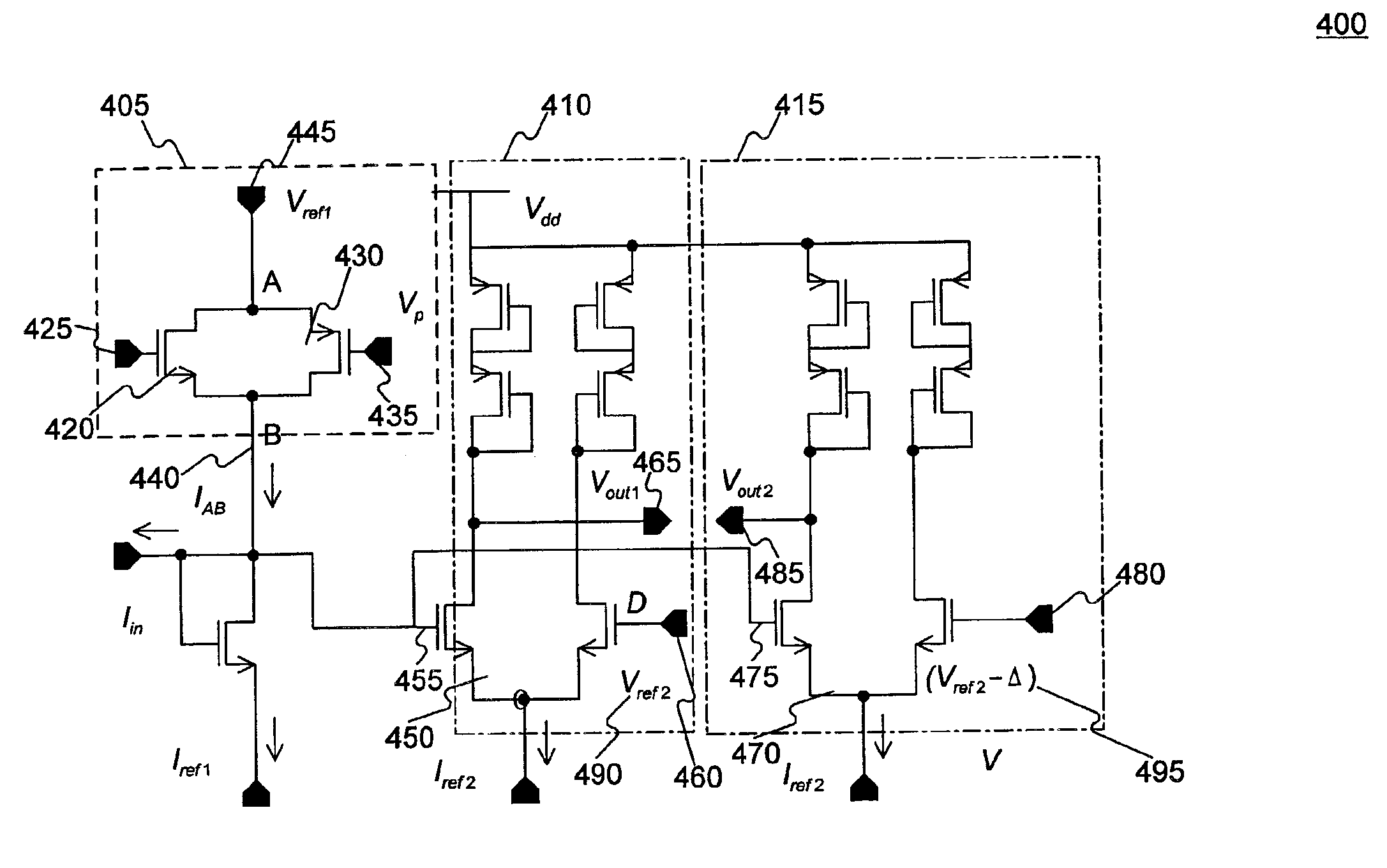

Neuron circuit, system, and method with synapse weight learning

A neuron circuit performing synapse learning on weight values includes a first sub-circuit, a second sub-circuit, and a third sub-circuit. The first sub-circuit is configured to receive an input signal from a pre-synaptic neuron circuit and determine whether the received input signal is an active signal having an active synapse value. The second sub-circuit is configured to compare a first cumulative reception counter of active input signals with a learning threshold value based on results of the determination. The third sub-circuit is configured to perform a potentiating learning process based on a first probability value to set a synaptic weight value of at least one previously received input signal to an active value, upon the first cumulative reception counter reaching the learning threshold value, and perform a depressing learning process based on a second probability value to set each of the synaptic weight values to an inactive value.

Owner:SAMSUNG ELECTRONICS CO LTD +1

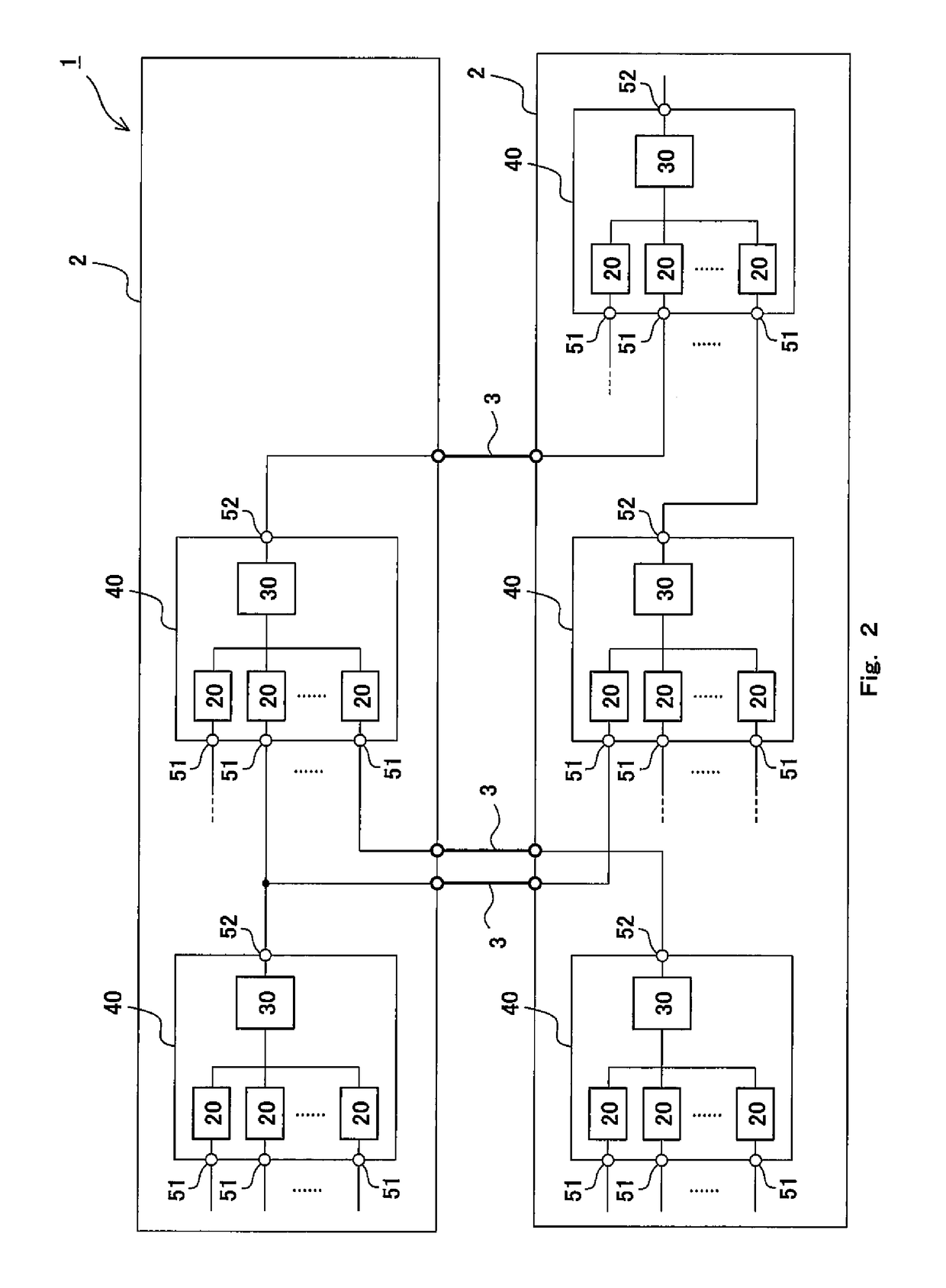

Neural network circuit and learning method thereof

ActiveUS9818057B2Ensure correct executionAccurate operationNeural architecturesPhysical realisationElectrical resistance and conductanceNerve network

In a neural network circuit element, a neuron circuit includes a waveform generating circuit for generating an analog pulse voltage, and a switching pulse voltage which is input as a first input signal to another neural network circuit element; a synapse circuit is configured such that the analog pulse voltage generated in the neuron circuit of the neural network circuit element including the synapse circuit is input to a third terminal of a variable resistance element of the synapse circuit, for a permissible input period, in the first input signal from another neural network circuit element; and the synapse circuit is configured such that the resistance value of the variable resistance element is changed in response to an electric potential difference between a first terminal and the third terminal, which occurs depending on a magnitude of the analog pulse voltage for the permissible input period.

Owner:PANASONIC INTELLECTUAL PROPERTY MANAGEMENT CO LTD

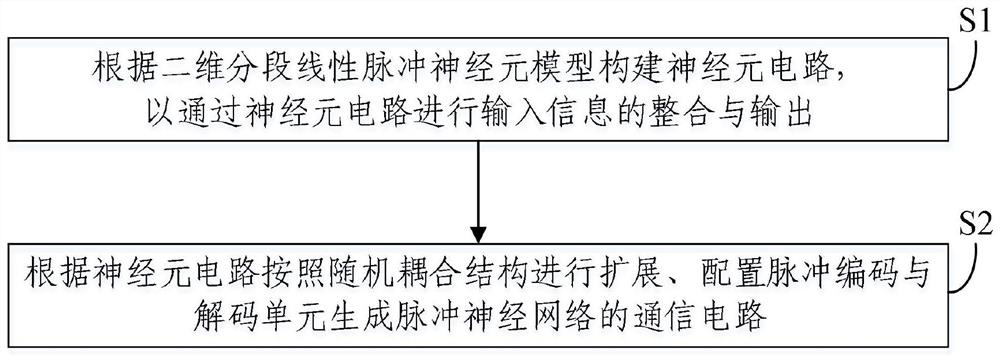

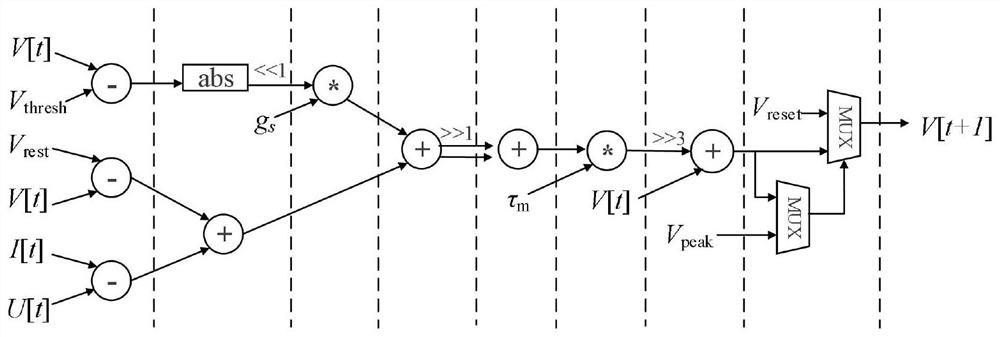

FPGA implementation method based on piecewise linear spiking neural network

PendingCN112101517AFacilitate logical mappingEasy to operateNeural architecturesArchitecture with single central processing unitAlgorithmTheoretical computer science

The embodiment of the invention discloses an FPGA implementation method based on a piecewise linear spiking neural network, and the method comprises the steps of constructing a neuron circuit according to a two-dimensional piecewise linear spiking neural model, so as to carry out the integration and output of input information through the neuron circuit, wherein the two-dimensional piecewise linear spiking neuron model comprises an expression of a membrane potential of a neuron and an expression of a recovery variable; and according to the neuron circuit, performing expansion according to a random coupling structure, and configuring a communication circuit of a pulse neural network generated by a pulse coding and decoding unit. According to the invention, less hardware resources are occupied, rich neuromorphic dynamics can be simulated and presented, meanwhile, higher hardware computing efficiency can be achieved, and the method is convenient to extend to hardware architecture implementation of a large-scale spiking neural network and dynamic simulation of a communication system.

Owner:NORTHWEST NORMAL UNIVERSITY

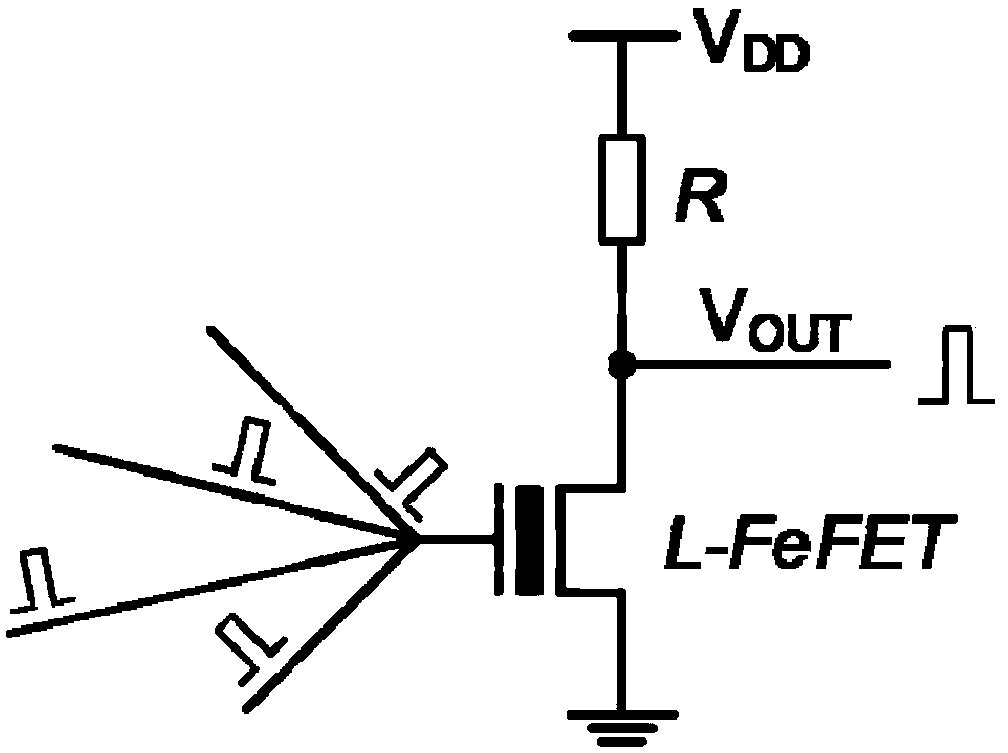

Pulse neuron circuit based on ferroelectric transistor

ActiveCN110232440AGood leaky characteristicsHigh simulationPhysical realisationLogic circuitsSynapseMOSFET

The invention provides a pulse neuron circuit based on a ferroelectric transistor, and belongs to the technical field of pulse neuron in neural morphology calculation. The pulse neuron circuit comprises a ferroelectric transistor FeFET and a resistor, wherein a ferroelectric transistor L-FeFET is formed by enhancing polarization degradation characteristics of ferroelectric materials of the ferroelectric transistor FeFET, and the L-FeFET is used for simulating the accumulation and leakage characteristics of biological neurons, and a voltage pulse signal transmitted from a synapse is applied tothe gate of the L-FeFET; the source end of the L-FeFET is connected with the GND, and the drain end of the L-FeFET is connected to one end of the resistor; and the other end of the resistor is connected with a fixed power supply voltage, and the resistor is used for divides the voltage with the L-FeFET to generate a voltage pulse output of the neurons. Compared with an implementation mode based ona traditional MOSFET, the pulse neuron circuit has the advantages that the hardware expenditure can be obviously reduced, has strong driving capability, and is beneficial to hardware realization of alarge-scale highly interconnected pulse neural network.

Owner:PEKING UNIV

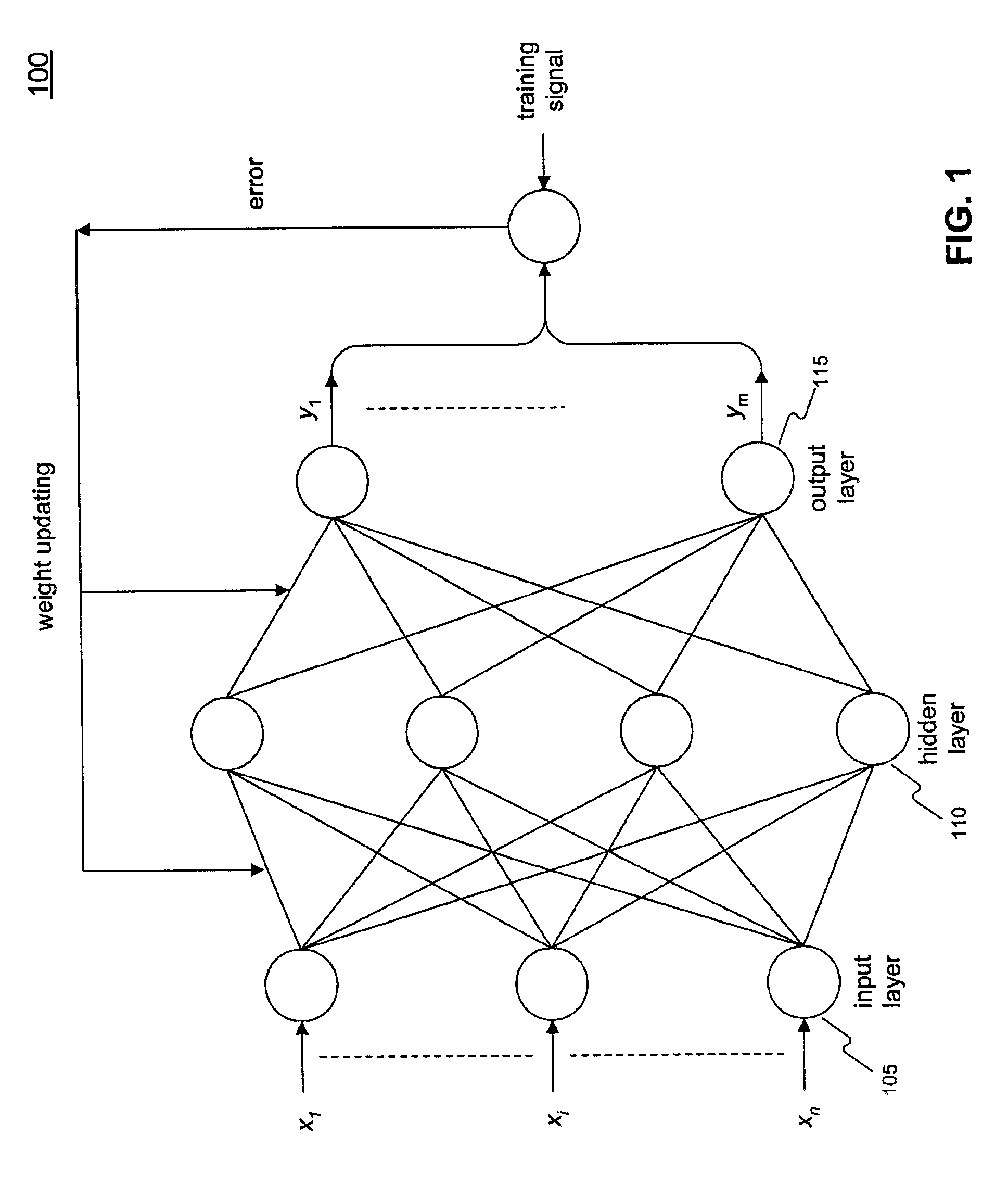

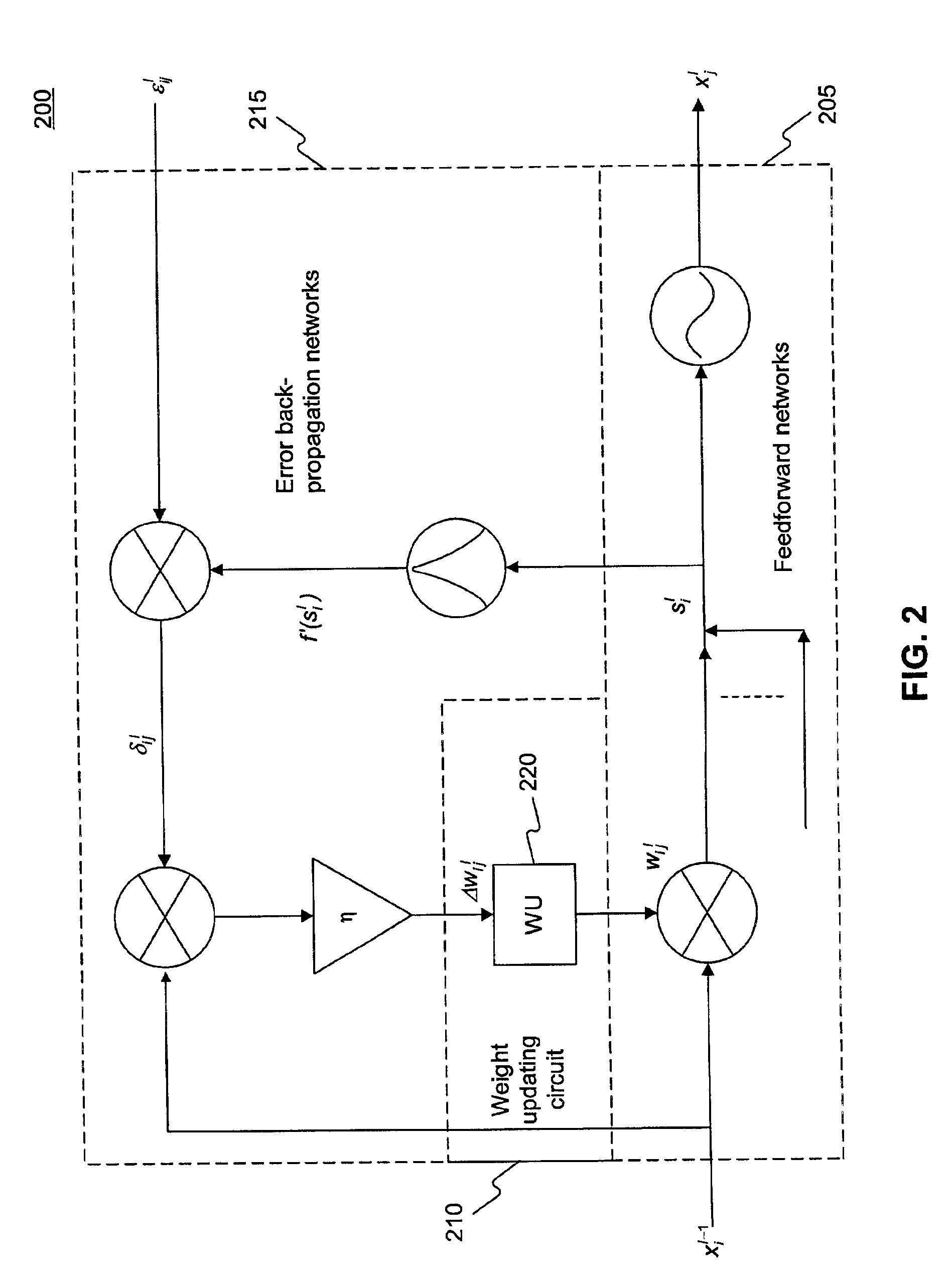

Back-propagation neural network with enhanced neuron characteristics

ActiveUS6876989B2Improve featuresAvoid problemsDigital computer detailsDigital dataActivation functionNeural network system

A neural network system includes a feedforward network comprising at least one neuron circuit for producing an activation function and a first derivative of the activation function and a weight updating circuit for producing updated weights to the feedforward network. The system also includes an error back-propagation network for receiving the first derivative of the activation function and to provide weight change data information to the weight updating circuit.

Owner:WINBOND ELECTRONICS CORP

Internal pulse storage neural network based on current integration

PendingCN114186676ASave energyThe calculation result is accurateNeural architecturesPhysical realisationStatic random-access memorySynaptic weight

The invention provides an in-memory pulse neural network based on current integration. Calculation based on a charge domain is naturally compatible with a working mechanism of neurons. In one aspect, in order to avoid non-ideality of employing NVM materials, memory cells of a synaptic array in an architecture employ silicon-based SRAM cells. In addition, the modified NVM unit can benefit from the architecture of the built-in pulse neural network designed by the invention. When the synaptic array adopts an SRAM (Static Random Access Memory) unit as a storage unit, the design of a post-neuron circuit corresponds to the SRAM unit, so that the SNN architecture in the storage can be used for calculating a multi-bit synaptic weight, and the combined column number is programmable. Further, in order to improve the use efficiency of the area and save energy efficiency, in the calculation of the multi-bit synaptic weight, the circuit is designed to be in a time multiplexing form of resource sharing. Finally, an automatic calibration circuit is provided to counteract the change of the conduction current caused by factors such as process, voltage, temperature (PVT) and the like, so that the calculation result is more accurate.

Owner:REEXEN TECH CO LTD

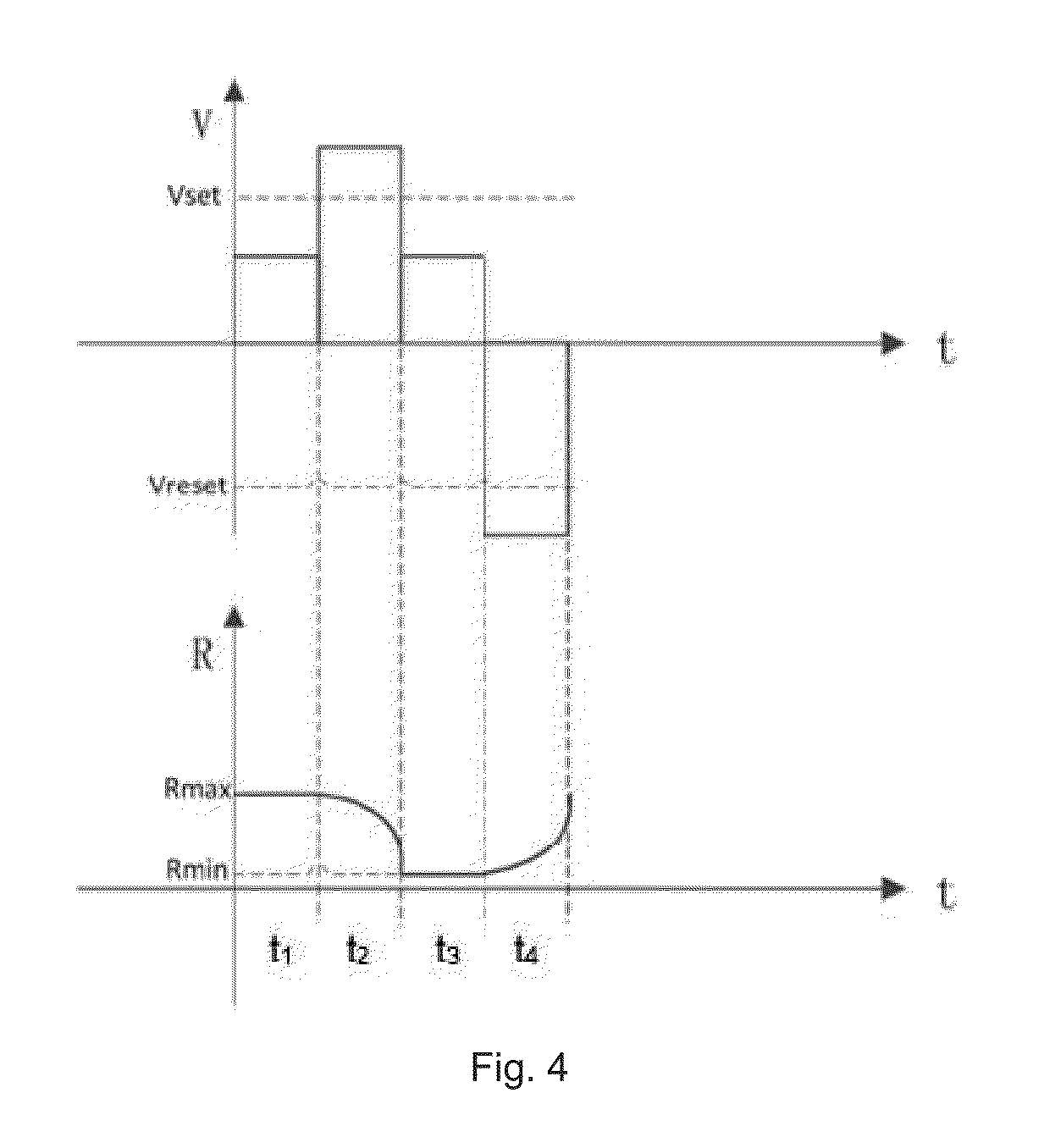

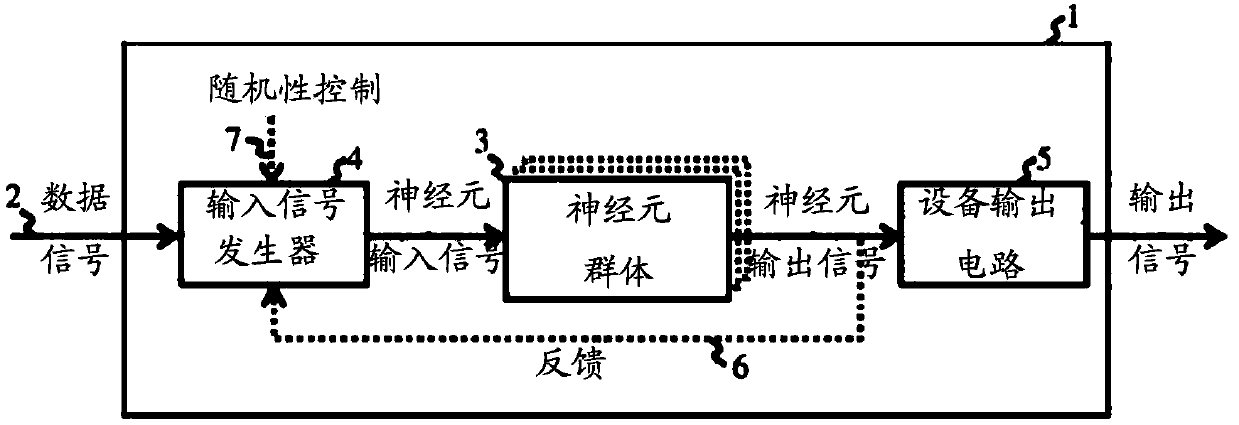

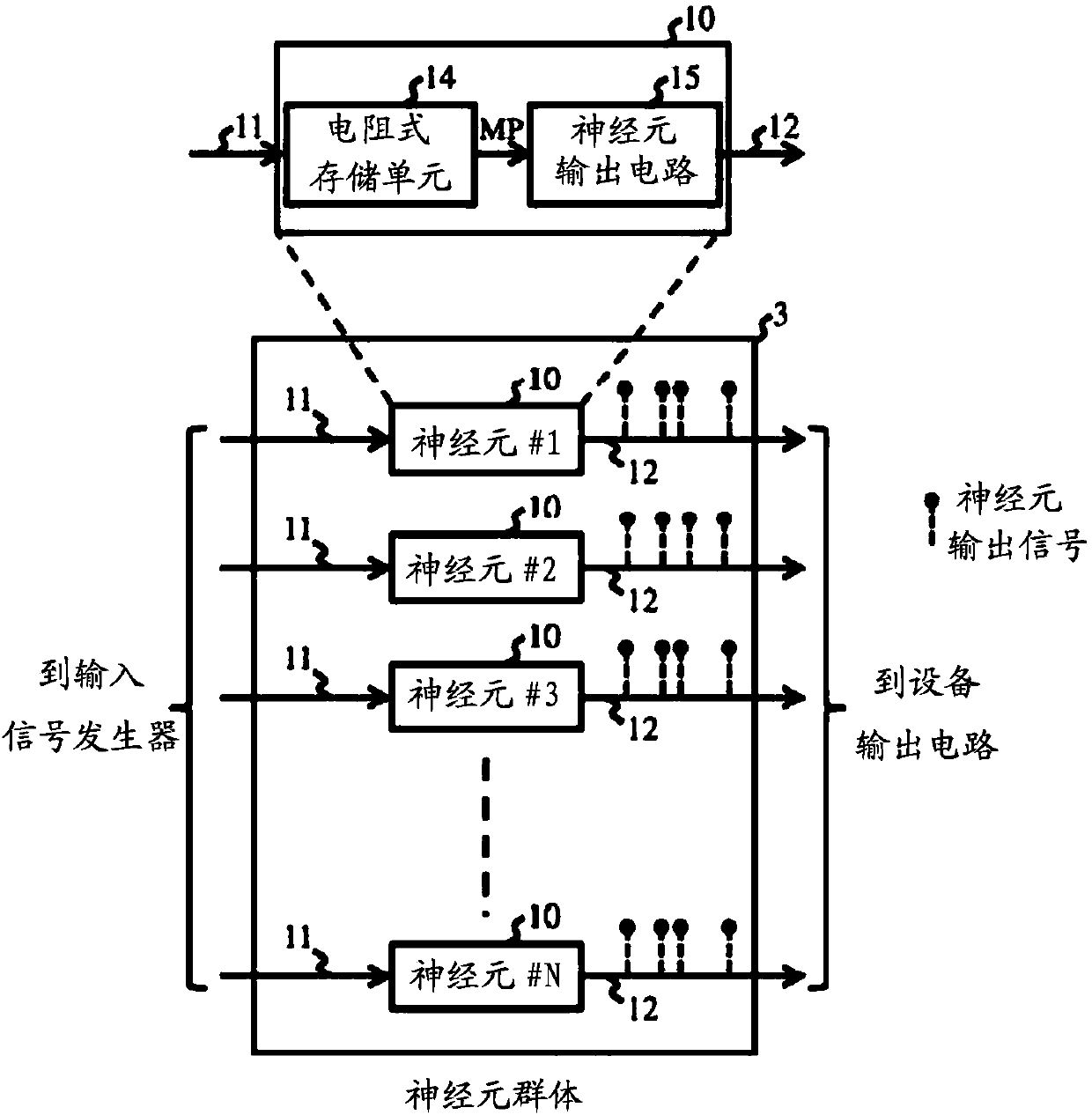

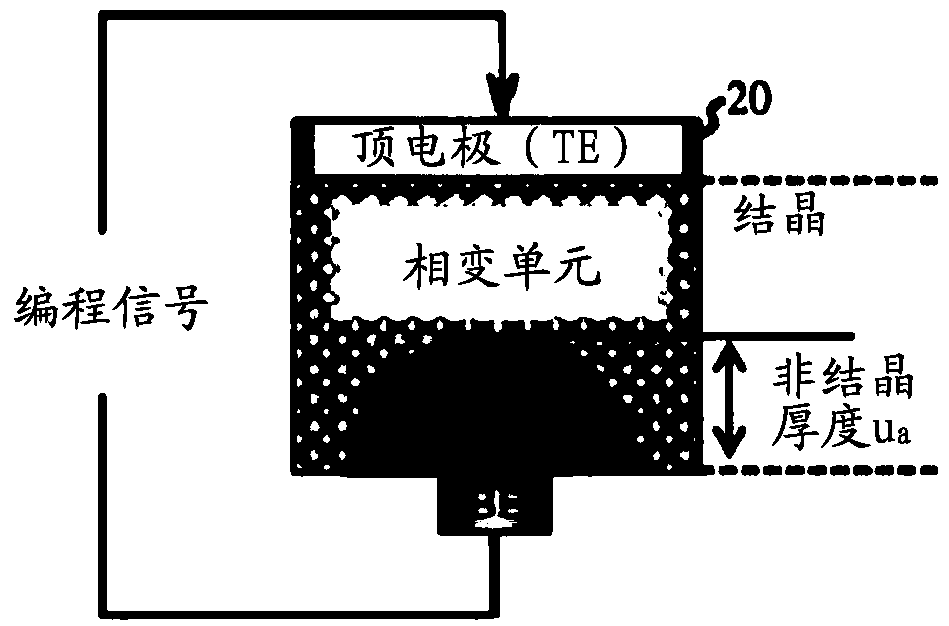

Neuromorphic processing devices

A neuromorphic processing device (1) has a device input (2), for receiving an input data signal, and an assemblage of neuron circuits (3). Each neuron circuit (3) comprises a resistive memory cell (14) which is arranged to store a neuron state, indicated by cell resistance, and to receive neuron input signals (11) for programming cell resistance to vary the neuron state, and a neuron output circuit (15) for supplying a neuron output signals (12) in response to cell resistance traversing a threshold. The device (1) includes an input signal generator (4) connected to the device input (2) and theassemblage of neuron circuits (3), for generating neuron input signals (11) for the assemblage in dependence on the input data signal. The device (1) further includes a device output circuit (5), connected to neuron output circuits (15) of the assemblage, for producing a device output signal dependent on neuron output signals (12) of the assemblage, whereby the processing device (1) exploits stochasticity of resistive memory cells of the assemblage.

Owner:IBM CORP

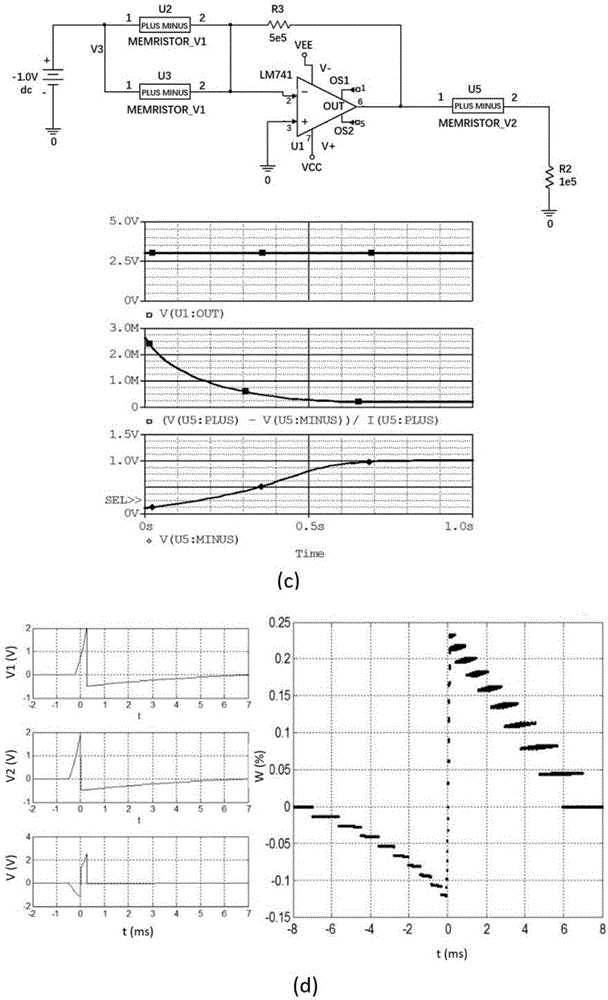

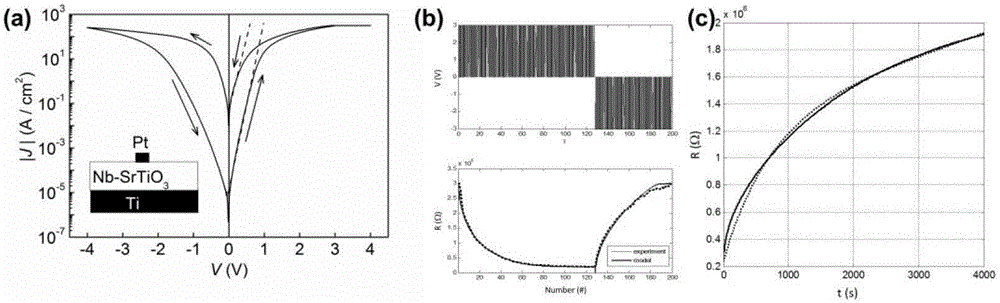

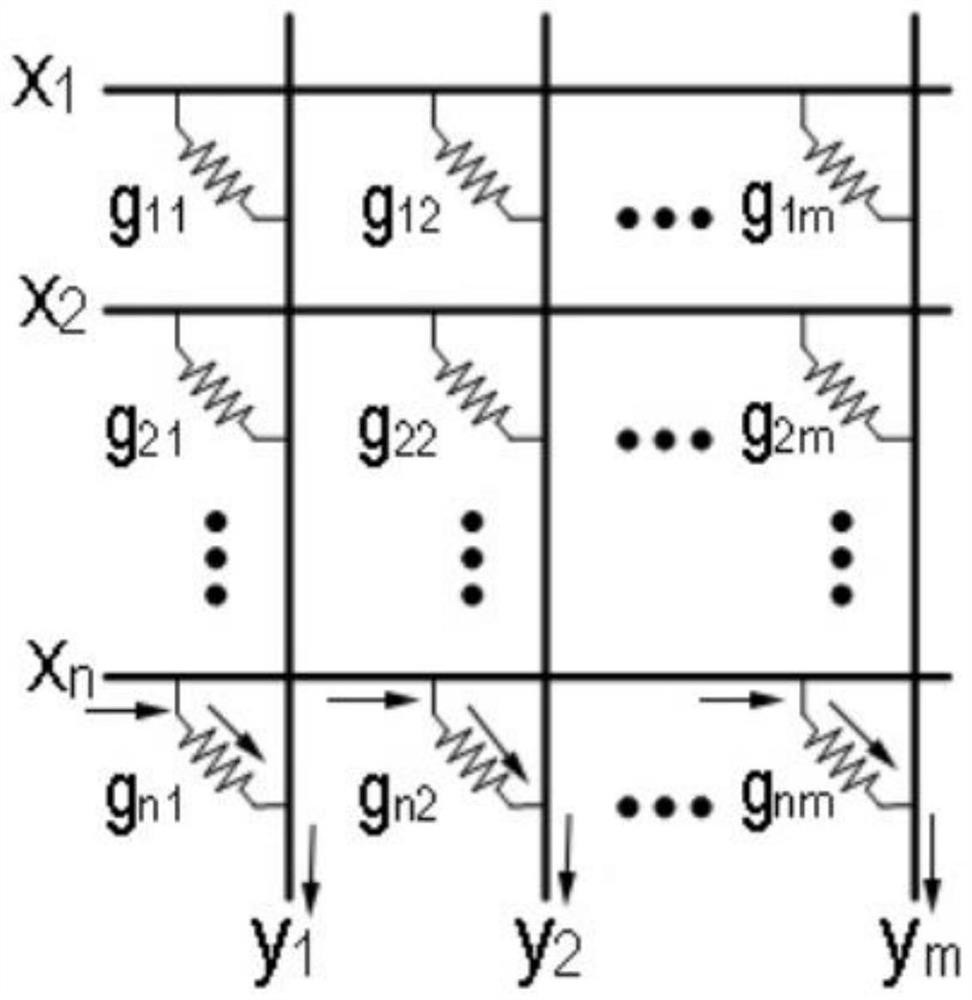

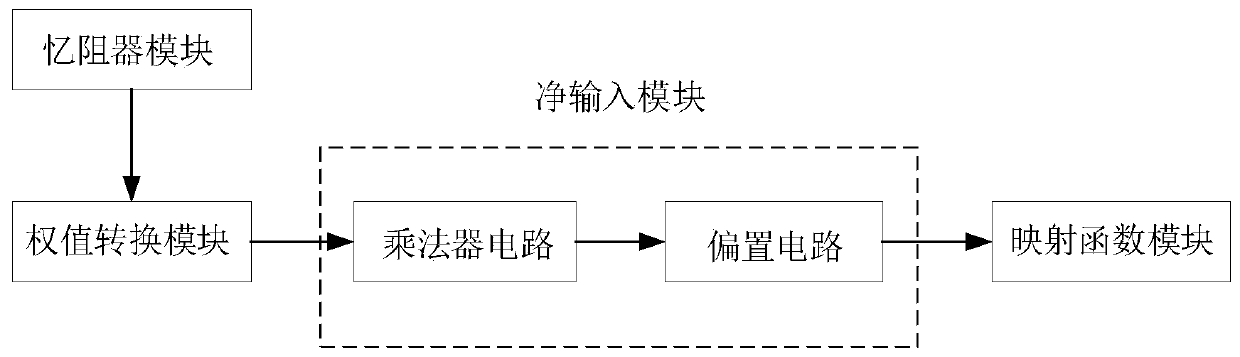

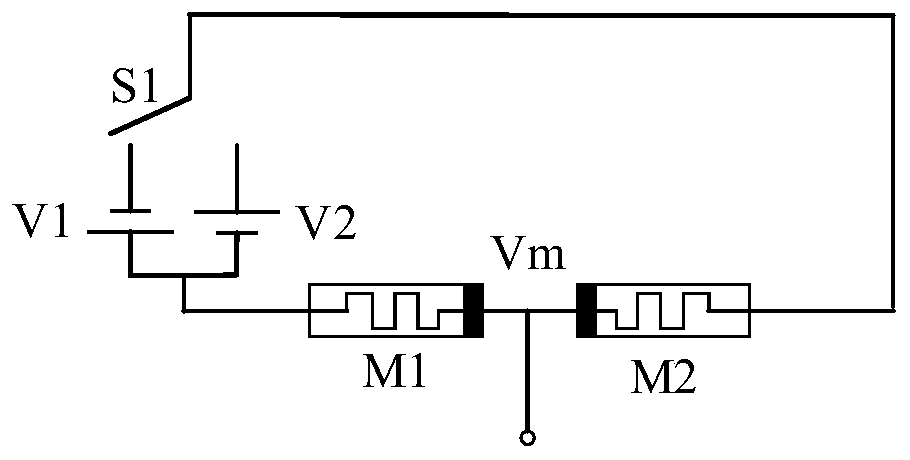

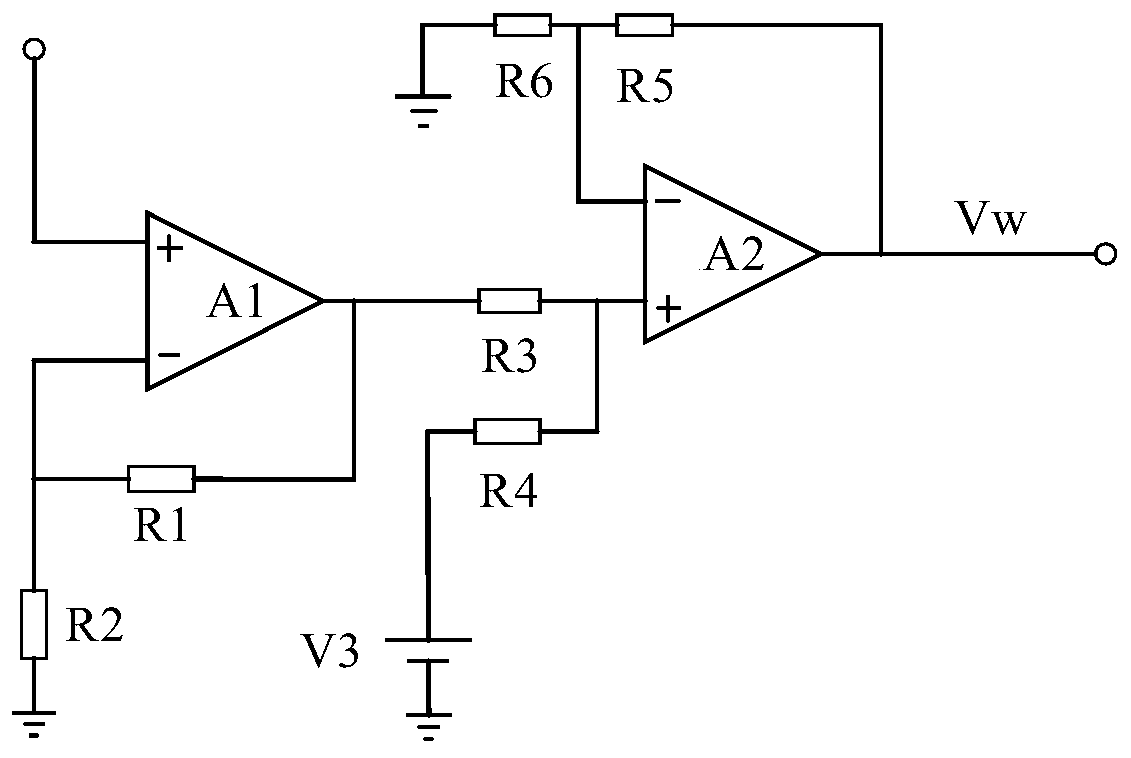

A memristor-based perceptron neural network circuit and an adjusting method thereof

ActiveCN109816096AResistance adjustmentHigh precisionNeural architecturesPhysical realisationSynaptic weightEngineering

The invention discloses a memristor-based perceptron neural network circuit and an adjusting method thereof. The circuit comprises a memristor module, a weight conversion module, a net input module and a mapping function module, wherein the memristor module is connected with the weight conversion module, the weight conversion module is connected with the net input module, and the net input moduleis connected with the mapping function module. According to the method, firstly, an image of a resistance value and time relation of the memristor is adjusted to be approximate to a straight line, andthen an image of a weight value and time relation is adjusted to be approximate to a straight line. The memristor resistance value which is linearly changed can more accurately replace the synaptic weight value of the neural network, and the trained synaptic weight value of the neural network is stored by utilizing the resistance value of the memristor, so that the conversion between the memristor resistance value and the neuron synaptic weight value is realized, and the problem that a traditional neuron circuit cannot accurately adjust the synaptic weight value is solved.

Owner:CHANGAN UNIV